昇圧装置および降圧装置

【課題】平滑容量を持たない基準電源を有する昇圧装置において、デッドタイム期間に発生する基準電源へのノイズを低減する。

【解決手段】昇圧電圧蓄積用の容量素子C0に対して並列接続された第1、第2の昇圧回路部A1,A2は、基準電源電圧蓄積用の容量素子C1,C2に対して電荷蓄積動作を行ったのち、逆方向に基準電源電圧を印加して昇圧電圧蓄積用の容量素子に対してポンプ動作を行い、電荷蓄積動作の期間とポンプ動作の期間との間およびポンプ動作の期間と電荷蓄積動作の期間との間に基準電源との接続を断つデッドタイム期間を有する。制御部10は、両昇圧回路部の複数のスイッチ素子をオン・オフ制御し、両昇圧回路部のうちいずれか一方の昇圧回路部のデッドタイム期間において他方の昇圧回路部では電荷蓄積動作またはポンプ動作を行うという制御を、両昇圧回路部において交互かつサイクリックに行う。

【解決手段】昇圧電圧蓄積用の容量素子C0に対して並列接続された第1、第2の昇圧回路部A1,A2は、基準電源電圧蓄積用の容量素子C1,C2に対して電荷蓄積動作を行ったのち、逆方向に基準電源電圧を印加して昇圧電圧蓄積用の容量素子に対してポンプ動作を行い、電荷蓄積動作の期間とポンプ動作の期間との間およびポンプ動作の期間と電荷蓄積動作の期間との間に基準電源との接続を断つデッドタイム期間を有する。制御部10は、両昇圧回路部の複数のスイッチ素子をオン・オフ制御し、両昇圧回路部のうちいずれか一方の昇圧回路部のデッドタイム期間において他方の昇圧回路部では電荷蓄積動作またはポンプ動作を行うという制御を、両昇圧回路部において交互かつサイクリックに行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は昇圧装置および降圧装置にかかわり、特には基準電源でのノイズ低減の技術に関するものである。

【背景技術】

【0002】

例えば電源Vccよりも低い基準電源Vciの2倍昇圧を行う昇圧回路の場合、通常、4つのスイッチ素子と2つの容量素子で構成され、所与のタイミングの制御信号に基づいたチャージ・ポンプ動作によって所望の出力電圧(Vout)を生成する。出力電圧(Vout)の微調整は、基準電源Vciの調整で行う。それは、昇圧回路自体の出力が基準電源の整数倍のみに限定されるからである。そのため、基準電源Vciは、LSI内部で電源Vccから生成させることが多い。各スイッチ素子がスイッチング動作を行う際に、反転論理の2つのスイッチ素子が同時にオンになり貫通電流が流れてしまうのを防ぐ必要がある。そこで、チャージ・ポンプ動作を行うための制御信号としては、意図的にスイッチング動作時にすべてのスイッチ素子がオフとなるデッドタイム期間を設ける。

【0003】

基準電源Vciの2倍の電圧(Vout)を作成する従来の昇圧回路の構成を図55に示す。

【0004】

基準電源VciとグランドVSSとの間にスイッチ素子S11とスイッチ素子S12の直列回路が接続されている。基準電源Vciと両スイッチ素子S11,S12の接続点との間にスイッチ素子S13と基準電源電圧蓄積用の容量素子C1の直列回路が接続されている。スイッチ素子S13と容量素子C1の接続点とグランドVSSとの間にスイッチ素子S14と昇圧電圧蓄積用の容量素子C0の直列回路が接続されている。容量素子C0は、基準電源Vciの2倍の電圧(Vout)を保持し、出力するものである。Voutは電圧出力端子を表す。基準電源Vciは平滑容量を持たない電源となっている。

【0005】

図56は動作を示すタイミングチャートであり、制御信号A,B,C,Dはそれぞれスイッチ素子S11,S12,S13,S14をオン・オフ制御するものである。ハッチングを施した領域は、デッドタイム期間の状態(DT)を表している。これらの制御信号A,B,C,Dは制御部60によって生成され、それぞれスイッチ素子S11,S12,S13,S14に供給されるようになっている。スイッチ素子はトランジスタ等で構成されている。

【0006】

図55に示す昇圧回路の動作について、図57〜図60を参照しながら以下に説明する。

【0007】

まず、図57のように、スイッチ素子S12とスイッチ素子S13をオンさせ、スイッチ素子S11とスイッチ素子S14をオフさせる。この状態で基準電源電圧蓄積用の容量素子C1には基準電源Vciの電圧が蓄えられる。この期間は、基準電源Vciへ負荷がかかっている状態である。

【0008】

次に、図58のように、スイッチ素子S11とスイッチ素子S14をオフさせたままで、スイッチ素子S12とスイッチ素子S13もオフさせる。この状態は前期デッドタイム期間の状態である。この期間は、基準電源Vciへ負荷がかかっていない状態である。

【0009】

次に、図59のように、スイッチ素子S12とスイッチ素子S13がオフしたままの状態で、スイッチ素子S11とスイッチ素子S14がオンし、基準電源電圧蓄積用の容量素子C1と昇圧電圧蓄積用の容量素子C0が接続され、容量素子C1に蓄えられた電荷が容量素子C0に持ち上げられる。この期間は、基準電源Vciへ負荷がかかっている状態である。

【0010】

次に、図60のように、スイッチ素子S12とスイッチ素子S13をオフさせたままで、スイッチ素子S11とスイッチ素子S14もオフさせる。この状態は後期デッドタイム期間の状態である。この期間は、基準電源Vciへ負荷がかかっていない状態である。

【0011】

図57〜図60の動作を繰り返すことにより、容量素子C0に基準電源Vciの2倍の電圧(Vout)が生成される。

【特許文献1】特開平6−327236号公報(第2−4頁、第3−6図)

【特許文献2】特開平11−299227号公報(第9−10頁、第12−15図)

【発明の開示】

【発明が解決しようとする課題】

【0012】

図55に示す従来の昇圧回路は、動作期間とデッドタイム期間を繰り返している。すなわち、基準電源Vciへの負荷電流がある場合とない場合を交互に繰り返している。そのため、平滑容量を持たない基準電源Vciは、負荷のかかっていないデッドタイム期間に跳ね上がり、ノイズを発生させてしまう。そして、そのノイズが別回路へ回り込み、悪影響を与える可能性がある。降圧回路についても同様の課題がある。

【0013】

本発明は、上記従来の問題点を解決するもので、基準電源Vciにおけるクロック同期のノイズを低減させ、別回路への悪影響をなくすことが可能な昇圧装置、降圧装置を提供することを目的とする。

【課題を解決するための手段】

【0014】

本発明による昇圧装置は、

電圧出力端子に接続された昇圧電圧蓄積用の容量素子に対して第1の昇圧回路部と第2の昇圧回路部とが並列に接続され、

前記第1の昇圧回路部および第2の昇圧回路部はそれぞれ、平滑容量を持たない基準電源と、基準電源電圧蓄積用の容量素子と、複数のスイッチ素子を有し、スイッチング制御により、前記基準電源電圧蓄積用の容量素子に対して前記基準電源電圧による電荷蓄積動作を行ったのち、前記基準電源電圧蓄積用の容量素子に逆方向に前記基準電源電圧を印加して前記昇圧電圧蓄積用の容量素子に対してポンプ動作を行って前記電圧出力端子に昇圧電圧を供給するように構成され、さらに、前記電荷蓄積動作の期間と前記ポンプ動作の期間との間および前記ポンプ動作の期間と前記電荷蓄積動作の期間との間にそれぞれ前記基準電源との接続を断つデッドタイム期間を有するように構成され、

前記両昇圧回路部における前記複数のスイッチ素子をオン・オフ制御するもので、前記両昇圧回路部のうちいずれか一方の昇圧回路部のデッドタイム期間において他方の昇圧回路部では前記電荷蓄積動作または前記ポンプ動作を行うという制御を、前記第1の昇圧回路部と前記第2の昇圧回路部とにおいて交互かつサイクリックに行う制御部を備えたものである。

【0015】

この構成において、第1の昇圧回路部の動作と第2の昇圧回路部の動作とは、タイミングを異にして、互いに同様の動作を行う。すなわち、いずれの昇圧回路部も、制御部からの制御信号によりスイッチ素子のスイッチング制御が行われて、まず基準電源が基準電源電圧蓄積用の容量素子に接続され、この基準電源電圧蓄積用の容量素子に対して基準電源電圧による電荷蓄積動作が行われる。次いで、貫通電流防止のデッドタイム期間をおき、次いで、基準電源電圧蓄積用の容量素子に逆方向に基準電源電圧を印加することにより昇圧電圧蓄積用の容量素子に対してポンプ動作を行い、電圧出力端子に昇圧電圧を供給する。さらに、貫通電流防止のデッドタイム期間をおき、次いで再び、基準電源電圧蓄積用の容量素子に対して基準電源電圧による電荷蓄積動作へと進む。制御部は、第1の昇圧回路部における上記のような動作と第2の昇圧回路部における同様の動作との間に、タイミングのずらしを与える。すなわち、第1の昇圧回路部では、第2の昇圧回路部のデッドタイム期間において電荷蓄積動作を行い、また次の第2の昇圧回路部のデッドタイム期間においてポンプ動作を行う。また、第2の昇圧回路部では、第1の昇圧回路部のデッドタイム期間において電荷蓄積動作を行い、また、次の第1の昇圧回路部のデッドタイム期間においてポンプ動作を行う。

【0016】

まとめると、一方の昇圧回路部での貫通電流防止のためのデッドタイム期間においては、他方の昇圧回路部で基準電源が電荷蓄積動作またはポンプ動作のために基準電源電圧蓄積用の容量素子に接続されており、基準電源が有負荷状態に保たれるため、基準電源が平滑容量を持たないものであっても、デッドタイム期間にノイズが発生することを防止することができる。

【0017】

上記構成において、昇圧回路部を3つ以上有する状態に構成すれば、次のような展開となる。

【0018】

本発明による昇圧装置は、

電圧出力端子に対して3つ以上の昇圧回路部が並列に接続され、

前記昇圧回路部はそれぞれ、平滑容量を持たない基準電源と、基準電源電圧蓄積用の容量素子と、複数のスイッチ素子を有し、スイッチング制御により、前記基準電源電圧蓄積用の容量素子に対して前記基準電源電圧による電荷蓄積動作を行ったのち、前記基準電源電圧蓄積用の容量素子に逆方向に前記基準電源電圧を印加してポンプ動作を行って前記電圧出力端子に昇圧電圧を供給するように構成され、さらに、前記電荷蓄積動作の期間と前記ポンプ動作の期間との間および前記ポンプ動作の期間と前記電荷蓄積動作の期間との間にそれぞれ前記基準電源との接続を断つデッドタイム期間を有するように構成され、

前記複数の昇圧回路部それぞれにおける前記複数のスイッチ素子をオン・オフ制御するもので、前記複数の昇圧回路部のうちいずれか1つの昇圧回路部のデッドタイム期間において他の昇圧回路部では前記電荷蓄積動作または前記ポンプ動作を行うという制御を、前記複数の昇圧回路部において順次かつサイクリックに行う制御部を備えたものである。なお、この場合、昇圧電圧蓄積用の容量素子は必ずしも必要としない。

【0019】

この構成において、各昇圧回路部の機能は上記と同様である。制御部は、昇圧回路部の上記のような動作について複数の昇圧回路部どうし間でタイミングのずらしを与える。すなわち、第3の昇圧回路部のデッドタイム期間において、第1の昇圧回路部では電荷蓄積動作を行い、第2の昇圧回路部ではポンプ動作を行う。また、次の第3の昇圧回路部のデッドタイム期間において、第1の昇圧回路部ではポンプ動作を行い、第2の昇圧回路部では電荷蓄積動作を行う。第2の昇圧回路部のデッドタイム期間において、第1の昇圧回路部では電荷蓄積動作を行い、第3の昇圧回路部ではポンプ動作を行う。また、次の第2の昇圧回路部のデッドタイム期間において、第1の昇圧回路部ではポンプ動作を行い、第3の昇圧回路部では電荷蓄積動作を行う。第1の昇圧回路部のデッドタイム期間において、第2の昇圧回路部では電荷蓄積動作を行い、第3の昇圧回路部ではポンプ動作を行う。また、次の第1の昇圧回路部のデッドタイム期間において、第2の昇圧回路部ではポンプ動作を行い、第3の昇圧回路部では電荷蓄積動作を行う。

【0020】

まとめると、1つの昇圧回路部での貫通電流防止のためのデッドタイム期間においては、他の昇圧回路部では基準電源が電荷蓄積動作またはポンプ動作のために基準電源電圧蓄積用の容量素子に接続されており、基準電源が有負荷状態に保たれるため、基準電源が平滑容量を持たないものであっても、デッドタイム期間にノイズが発生することを防止することができる。

【0021】

前述の昇圧回路部が2つのみの構成では、一方の昇圧回路部のデッドタイム期間で他方の昇圧回路部が電荷蓄積動作を行う期間とポンプ動作を行う期間とに分かれることから、ポンプ動作がなく電荷蓄積動作のみの期間があり、この期間では、電圧出力端子の降圧を避ける必要から、昇圧電圧蓄積用の容量素子を必要としている。しかし、昇圧回路部を3つ以上有する本構成の場合には、いずれの期間においても必ず電圧出力端子に対するポンプ動作があり、電圧出力端子に対して常に少なくともいずれか1つの昇圧回路部から電荷供給が行われる状態が保たれるため、昇圧電圧蓄積用の容量素子は必ずしも必要ではない。この昇圧電圧蓄積用の容量素子は省略することが可能である。もっとも、昇圧電圧蓄積用の容量素子を有する構成とすれば、この容量素子にはポンプ動作により常に少なくとも1つの昇圧回路部から電荷供給が行われる状態になるため、昇圧電圧のリップルを低減させ、電流能力を上げるという効果が得られる。

【0022】

上記のように昇圧回路部を複数並列接続することに代えて、負荷抵抗等の負荷電流源に置き換えた構成もあり、次のように展開される。

【0023】

本発明による昇圧装置は、

電圧出力端子に接続された昇圧電圧蓄積用の容量素子に昇圧回路部が接続され、

前記昇圧回路部は、平滑容量を持たない基準電源と、基準電源電圧蓄積用の容量素子と、複数のスイッチ素子を有し、スイッチング制御により、前記基準電源電圧蓄積用の容量素子に対して前記基準電源電圧による電荷蓄積動作を行ったのち、前記基準電源電圧蓄積用の容量素子に逆方向に前記基準電源電圧を印加して前記昇圧電圧蓄積用の容量素子に対してポンプ動作を行って前記電圧出力端子に昇圧電圧を供給するように構成され、さらに、前記電荷蓄積動作の期間と前記ポンプ動作の期間との間および前記ポンプ動作の期間と前記電荷蓄積動作の期間との間にそれぞれ前記基準電源との接続を断つデッドタイム期間を有するように構成され、

前記基準電源にスイッチ素子を介して接続された負荷電流源と、

前記昇圧回路部における前記複数のスイッチ素子および前記負荷電流源のスイッチ素子をオン・オフ制御するもので、前記昇圧回路部のデッドタイム期間において前記負荷電流源のスイッチ素子を導通させる制御部とを備えたものである。

【0024】

この構成において、昇圧回路部での貫通電流防止のためのデッドタイム期間においては、制御部のスイッチング制御により負荷電流源を基準電源に接続させ、基準電源が有負荷状態に保たれるため、基準電源が平滑容量を持たないものであっても、デッドタイム期間にノイズが発生することを防止することができる。

【0025】

上記の昇圧装置についての技術を降圧装置においても次のように展開することが可能である。

【0026】

本発明による降圧装置は、

電圧出力端子に対して3つ以上の降圧回路部が並列に接続され、

前記降圧回路部はそれぞれ、平滑容量を持たない基準電源と、基準電源電圧蓄積用の容量素子と、複数のスイッチ素子を有し、スイッチング制御により、前記基準電源電圧蓄積用の容量素子に対して前記基準電源電圧による電荷蓄積動作を行ったのち、前記基準電源電圧蓄積用の容量素子に同方向に前記基準電源電圧を印加してポンプ動作を行って前記電圧出力端子に降圧電圧を供給するように構成され、さらに、前記電荷蓄積動作の期間と前記ポンプ動作の期間との間および前記ポンプ動作の期間と前記電荷蓄積動作の期間との間にそれぞれ前記基準電源との接続を断つデッドタイム期間を有するように構成され、

前記複数の降圧回路部それぞれにおける前記複数のスイッチ素子をオン・オフ制御するもので、前記複数の降圧回路部のうちいずれか1つの降圧回路部のデッドタイム期間において他の降圧回路部では前記電荷蓄積動作または前記ポンプ動作を行うという制御を、前記複数の降圧回路部において順次かつサイクリックに行う制御部を備えたものである。なお、この場合、降圧電圧蓄積用の容量素子は必ずしも必要としない。

【0027】

この構成において複数の降圧回路部は、タイミングを異にして、互いに同様の動作を行う。すなわち、いずれの降圧回路部も、制御部からの制御信号によりスイッチ素子のスイッチング制御が行われて、まず基準電源が基準電源電圧蓄積用の容量素子に接続され、この基準電源電圧蓄積用の容量素子に対して基準電源電圧による電荷蓄積動作が行われる。次いで、貫通電流防止のデッドタイム期間をおき、次いで、基準電源電圧蓄積用の容量素子に同方向に基準電源電圧を印加することにより降圧のポンプ動作を行い、電圧出力端子に降圧電圧を供給する。さらに、貫通電流防止のデッドタイム期間をおき、次いで再び、基準電源電圧蓄積用の容量素子に対して基準電源電圧による電荷蓄積動作へと進む。制御部は、第3の降圧回路部のデッドタイム期間において、第1の降圧回路部では電荷蓄積動作を行い、第2の降圧回路部では降圧のポンプ動作を行う。また、次の第3の降圧回路部のデッドタイム期間において、第1の降圧回路部では降圧のポンプ動作を行い、第2の降圧回路部では電荷蓄積動作を行う。第2の降圧回路部のデッドタイム期間において、第1の降圧回路部では電荷蓄積動作を行い、第3の降圧回路部では降圧のポンプ動作を行う。また、次の第2の降圧回路部のデッドタイム期間において、第1の降圧回路部では降圧のポンプ動作を行い、第3の降圧回路部では電荷蓄積動作を行う。第1の降圧回路部のデッドタイム期間において、第2の降圧回路部では電荷蓄積動作を行い、第3の降圧回路部では降圧のポンプ動作を行う。また、次の第1の降圧回路部のデッドタイム期間において、第2の降圧回路部では降圧のポンプ動作を行い、第3の降圧回路部では電荷蓄積動作を行う。

【0028】

まとめると、1つの降圧回路部での貫通電流防止のためのデッドタイム期間においては、他の降圧回路部では基準電源が電荷蓄積動作または降圧のポンプ動作のために基準電源電圧蓄積用の容量素子に接続されており、基準電源が有負荷状態に保たれるため、基準電源が平滑容量を持たないものであっても、デッドタイム期間にノイズが発生することを防止することができる。

【0029】

また、降圧回路部を3つ以上有するので、いずれの期間においても必ず電圧出力端子に対する降圧のポンプ動作があり、電圧出力端子に対して常に少なくともいずれか1つの降圧回路部から電荷供給が行われる状態が保たれるため、電圧出力端子には降圧電圧蓄積用の容量素子は必ずしも必要ではない。この降圧電圧蓄積用の容量素子は省略することが可能である。もっとも、降圧電圧蓄積用の容量素子を有する構成とすれば、この容量素子には降圧のポンプ動作により常に少なくとも1つの降圧回路部から電荷供給が行われる状態になるため、降圧電圧のリップルを低減させ、電流能力を上げるという効果が得られる。

【0030】

上記の昇圧装置についての技術は同一の基準電源から2つの出力電圧を作成する昇圧装置においても次のように展開することが可能である。

【0031】

第1の電圧出力端子に接続された第1の昇圧電圧蓄積用の容量素子に対して第1の昇圧回路部が接続され、第2の電圧出力端子に接続された第2の昇圧電圧蓄積用の容量素子に対して第2の昇圧回路部が接続され、

前記第1の昇圧回路部および前記第2の昇圧回路部はそれぞれ、平滑容量を持たない基準電源と、基準電源電圧蓄積用の容量素子と、複数のスイッチ素子を有し、スイッチング制御により、前記基準電源電圧蓄積用の容量素子に対して前記基準電源電圧による電荷蓄積動作を行ったのち、前記基準電源電圧蓄積用の容量素子に逆方向に前記基準電源電圧を印加してそれぞれ前記第1の昇圧電圧蓄積用の容量素子と前記第2の昇圧電圧蓄積用の容量素子に対してポンプ動作を行って前記第1の電圧出力端子と前記第2の電圧出力端子に昇圧電圧を供給するように構成され、さらに、前記電荷蓄積動作の期間と前記ポンプ動作の期間との間および前記ポンプ動作の期間と前記電荷蓄積動作の期間との間にそれぞれ前記基準電源との接続を断つデッドタイム期間を有するように構成され、

前記両昇圧回路部における前記複数のスイッチ素子をオン・オフ制御するもので、前記両昇圧回路部のうちいずれか一方の昇圧回路部のデッドタイム期間において他方の昇圧回路部では前記電荷蓄積動作または前記ポンプ動作を行うという制御を、前記第1の昇圧回路部と前記第2の昇圧回路部とにおいて交互かつサイクリックに行う制御部を備えたものである。

【0032】

この構成において、第1の昇圧回路部の動作と第2の昇圧回路部の動作とは、タイミングを異にして、互いに同様の動作を行う。すなわち、いずれの昇圧回路部も、制御部からの制御信号によりスイッチ素子のスイッチング制御が行われて、まず基準電源が基準電源電圧蓄積用の容量素子に接続され、この基準電源電圧蓄積用の容量素子に対して基準電源電圧による電荷蓄積動作が行われる。次いで、貫通電流防止のデッドタイム期間をおき、次いで、基準電源電圧蓄積用の容量素子に逆方向に基準電源電圧を印加することにより昇圧電圧蓄積用の容量素子に対してポンプ動作を行い、第1の電圧出力端子と第2の電圧出力端子に昇圧電圧を供給する。さらに、貫通電流防止のデッドタイム期間をおき、次いで再び、基準電源電圧蓄積用の容量素子に対して基準電源電圧による電荷蓄積動作へと進む。制御部は、第1の昇圧回路部における上記のような動作と第2の昇圧回路部における同様の動作との間に、タイミングのずらしを与える。すなわち、第1の昇圧回路部では、第2の昇圧回路部のデッドタイム期間において電荷蓄積動作を行い、また次の第2の昇圧回路部のデッドタイム期間においてポンプ動作を行う。また、第2の昇圧回路部では、第1の昇圧回路部のデッドタイム期間において電荷蓄積動作を行い、また、次の第1の昇圧回路部のデッドタイム期間においてポンプ動作を行う。

【0033】

まとめると、一方の昇圧回路部での貫通電流防止のためのデッドタイム期間においては、他方の昇圧回路部で基準電源が電荷蓄積動作またはポンプ動作のために基準電源電圧蓄積用の容量素子に接続されており、基準電源が有負荷状態に保たれるため、基準電源が平滑容量を持たないものであっても、デッドタイム期間にノイズが発生することを防止することができる。

【発明の効果】

【0034】

本発明の昇圧装置または降圧装置によれば、貫通電流防止のためのデッドタイム期間においては、他の昇圧回路部または降圧回路部で基準電源が電荷蓄積動作またはポンプ動作のために基準電源電圧蓄積用の容量素子に接続されており、基準電源が有負荷状態に保たれるため、基準電源が平滑容量を持たないものであっても、デッドタイム期間にノイズが発生することを防止することができる。この結果、別回路への悪影響をなくし、安定動作が可能となる。

【発明を実施するための最良の形態】

【0035】

以下、本発明にかかわる昇圧装置、降圧装置の実施の形態を図面に基づいて詳細に説明する。

【0036】

(実施の形態1)

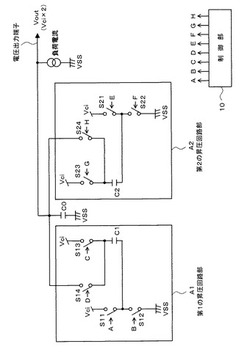

図1は、本発明の実施の形態1における昇圧装置の構成を示す回路図である。図1に示すように、電圧出力端子Voutに昇圧電圧蓄積用の容量素子C0が接続され、この昇圧電圧蓄積用の容量素子C0に対して第1の昇圧回路部A1と第2の昇圧回路部A2とが並列に接続されている。昇圧電圧蓄積用の容量素子C0は、基準電源Vciの2倍の電圧(Vout)を保持し、出力するものである。

【0037】

第1の昇圧回路部A1において、基準電源VciとグランドVSSとの間にスイッチ素子S11とスイッチ素子S12の直列回路が接続されている。基準電源Vciと両スイッチ素子S11,S12の接続点との間にスイッチ素子S13と基準電源電圧蓄積用の容量素子C1の直列回路が接続されている。スイッチ素子S13と容量素子C1の接続点とグランドVSSとの間にスイッチ素子S14と容量素子C0の直列回路が接続されている。スイッチ素子S11,S12,S13,S14と基準電源電圧蓄積用の容量素子C1で第1の昇圧回路部A1を形成している。

【0038】

第2の昇圧回路部A2において、基準電源VciとグランドVSSとの間にスイッチ素子S21とスイッチ素子S22の直列回路が接続されている。基準電源Vciと両スイッチ素子S21,S22の接続点との間にスイッチ素子S23と基準電源電圧蓄積用の容量素子C2の直列回路が接続されている。スイッチ素子S23と容量素子C2の接続点とグランドVSSとの間にスイッチ素子S24と容量素子C0の直列回路が接続されている。スイッチ素子S21,S22,S23,S24と基準電源電圧蓄積用の容量素子C2で第2の昇圧回路部A2を形成している。

【0039】

昇圧電圧蓄積用の容量素子C0は、一方でグランドVSSに接続され、もう一方はスイッチ素子S14とスイッチ素子S24に接続されている。結果的にはこの箇所に基準電源Vciの2倍の電圧(Vout)が出力される。

【0040】

10は、第1の昇圧回路部A1におけるスイッチ素子S11,S12,S13,S14をオン・オフ制御する制御信号A,B,C,Dと第2の昇圧回路部A2におけるスイッチ素子S21,S22,S23,S24をオン・オフ制御する制御信号E,F,G,Hを生成出力する制御部である。この制御部10は、第1の昇圧回路部A1および第2の昇圧回路部A2のうちいずれか一方の昇圧回路部のデッドタイム期間において他方の昇圧回路部では電荷蓄積動作またはポンプ動作を行うという制御を、両昇圧回路部A1,A2間で交互かつサイクリックに行うように構成されている。スイッチ素子はトランジスタ等で構成されている。基準電源Vciは平滑容量を持たない電源となっている。

【0041】

図2は本実施の形態の昇圧装置の動作を示すタイミングチャートである。図2において、第1の昇圧回路部A1におけるスイッチ素子S11,S12,S13,S14をオン・オフ制御する制御信号A,B,C,Dは、昇圧回路用の第1のクロックCK1に基づいて生成され、第2の昇圧回路部A2におけるスイッチ素子S21,S22,S23,S24をオン・オフ制御する制御信号E,F,G,Hは、昇圧回路用の第2のクロックCK2に基づいて生成される。

【0042】

また、図2において、ハッチングを施した領域は、デッドタイム期間の状態(DT)を表している。

【0043】

次に、上記のように構成された本実施の形態の昇圧装置の動作を、図3〜図10を参照しながら説明する。

【0044】

まず、図3のように、第1の昇圧回路部A1におけるスイッチ素子S12とスイッチ素子S13と、第2の昇圧回路部A2におけるスイッチ素子S21とスイッチ素子S24をオンさせ、スイッチ素子S11とスイッチ素子S14とスイッチ素子S22とスイッチ素子S23をオフさせる。この期間で、第1の昇圧回路部A1における基準電源電圧蓄積用の容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2における基準電源電圧蓄積用の容量素子C2は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)である。この期間は、基準電源Vciへ負荷が2箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔CH,UP〕である。

【0045】

次に、図4のように、図3の状態から第2の昇圧回路部A2におけるスイッチ素子S21とスイッチ素子S24をオフさせる。この期間で、第1の昇圧回路部A1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。第1の昇圧回路部A1は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔CH,DT〕である。

【0046】

次に、図5のように、図4の状態から第2の昇圧回路部A2におけるスイッチ素子S22とスイッチ素子S23をオンさせる。この期間で、第1の昇圧回路部A1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)である。この期間は、基準電源Vciへ負荷が2箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔CH,CH〕である。

【0047】

次に、図6のように、図5の状態から第1の昇圧回路部A1におけるスイッチ素子S12とスイッチ素子S13をオフさせる。この期間で、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。第2の昇圧回路部A2は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔DT,CH〕である。

【0048】

次に、図7のように、図6の状態から第1の昇圧回路部A1におけるスイッチ素子S11とスイッチ素子S14をオンさせ、基準電源電圧蓄積用の容量素子C1に対して基準電源Vciを逆方向に印加する。この期間で、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)である。この期間は、基準電源Vciへ負荷が2箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔UP,CH〕である。

【0049】

次に、図8のように、図7の状態から第2の昇圧回路部A2におけるスイッチ素子S22とスイッチ素子S23をオフさせる。この期間で、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。第1の昇圧回路部A1は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔UP,DT〕である。

【0050】

次に、図9のように、図8の状態から第2の昇圧回路部A2におけるスイッチ素子S21とスイッチ素子S24をオンさせ、基準電源電圧蓄積用の容量素子C2に対して基準電源Vciを逆方向に印加する。この期間で、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第2の昇圧回路部A2における容量素子C2は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)である。この期間は、基準電源Vciへ負荷が2箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔UP,UP〕である。

【0051】

次に、図10のように、図9の状態から第1の昇圧回路部A1におけるスイッチ素子S11とスイッチ素子S14をオフさせる。この期間で、第2の昇圧回路部A2における容量素子C2は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。第2の昇圧回路部A2は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔DT,UP〕である。

【0052】

図3〜図10の動作を繰り返すことにより、昇圧電圧蓄積用の容量素子C0に基準電源Vciの2倍の電圧(Vout)が生成される。

【0053】

図2において、図4相当の期間では、第2の昇圧回路部A2における4つのスイッチ素子S21,S22,S23,S24がすべてオフとなっていて、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。このとき、第1の昇圧回路部A1において、スイッチ素子S12,S13がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。

【0054】

また、図2において、図6相当の期間では、第1の昇圧回路部A1における4つのスイッチ素子S11,S12,S13,S14がすべてオフとなっていて、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。このとき、第2の昇圧回路部A2において、スイッチ素子S22,S23がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。

【0055】

また、図2において、図8相当の期間では、第2の昇圧回路部A2における4つのスイッチ素子S21,S22,S23,S24がすべてオフとなっていて、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。このとき、第1の昇圧回路部A1において、スイッチ素子S11,S14がオンであることから、蓄えている電荷を昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)となっている。

【0056】

また、図2において、図10相当の期間では、第1の昇圧回路部A1における4つのスイッチ素子S11,S12,S13,S14がすべてオフとなっていて、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。このとき、第2の昇圧回路部A2において、スイッチ素子S21,S24がオンであることから、蓄えている電荷を昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)となっている。

【0057】

以上の経過をまとめると、

図3……〔A1,A2〕=〔CH,UP〕

図4……〔A1,A2〕=〔CH,DT〕

図5……〔A1,A2〕=〔CH,CH〕

図6……〔A1,A2〕=〔DT,CH〕

図7……〔A1,A2〕=〔UP,CH〕

図8……〔A1,A2〕=〔UP,DT〕

図9……〔A1,A2〕=〔UP,UP〕

図10…〔A1,A2〕=〔DT,UP〕

となる。第1の昇圧回路部A1における動作履歴をみると、CH→CH→CH→DT→UP→UP→UP→DTのサイクリック動作となっている。また、第2の昇圧回路部A2における動作履歴をみると、UP→DT→CH→CH→CH→DT→UP→UPのサイクリック動作となっている。両昇圧回路部A1,A2の動作は、タイミングこそ異なるが、同一パターンのサイクリック動作となっている。

【0058】

第2の昇圧回路部A2がデッドタイム期間の状態(DT)であるときは(図4または図8)、第1の昇圧回路部A1は基準電源Vciの電圧を蓄える状態(CH)または蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)となっている。

【0059】

また、第1の昇圧回路部A1がデッドタイム期間の状態(DT)であるときは(図6または図10)、第2の昇圧回路部A2は基準電源Vciの電圧を蓄える状態(CH)または蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)となっている。

【0060】

まとめると、

〔A1,A2〕=〔有負荷,DT〕

〔A1,A2〕=〔DT,有負荷〕

の原則が保たれている。

【0061】

すなわち、いずれの昇圧回路部がデッドタイム期間の状態(DT)であっても、他方の昇圧回路部において、必ず、平滑容量を持たない基準電源Vciに負荷がかかっている状態を維持させることができている。これで、従来の技術の場合の、〔DT,無負荷〕の状態を脱却でき、〔DT,無負荷〕の状態に起因するノイズの発生を抑制することができる。

【0062】

まとめると、本実施の形態によれば、基準電源Vciには常に負荷がかかっている状態で、昇圧動作が可能となり、基準電源Vciのノイズの低減が可能となる。

【0063】

(実施の形態2)

上記においては、昇圧回路部を2つ並列接続した昇圧装置について説明したが、3つ以上接続した場合の昇圧装置でも、上記同様の効果が得られる。これが本発明の実施の形態2である。以下に、本発明の実施の形態2における昇圧装置について説明する。

【0064】

図11は、本発明の実施の形態2における昇圧装置の構成を示す回路図である。図11に示すように、電圧出力端子Voutに昇圧電圧蓄積用の容量素子C0が接続され、この昇圧電圧蓄積用の容量素子C0に対して第1の昇圧回路部A1と第2の昇圧回路部A2と第3の昇圧回路部A3が並列に接続されている。昇圧電圧蓄積用の容量素子C0は、基準電源Vciの2倍の電圧(Vout)を保持し、出力するものである。

【0065】

第1の昇圧回路部A1および第2の昇圧回路部A2については、実施の形態1の場合と同様である。

【0066】

第3の昇圧回路部A3において、基準電源VciとグランドVSSとの間にスイッチ素子S31とスイッチ素子S32の直列回路が接続されている。基準電源Vciと両スイッチ素子S31,S32の接続点との間にスイッチ素子S33と基準電源電圧蓄積用の容量素子C3の直列回路が接続されている。スイッチ素子S33と容量素子C3の接続点とグランドVSSとの間にスイッチ素子S34と容量素子C0の直列回路が接続されている。スイッチ素子S31,S32,S33,S34と基準電源電圧蓄積用の容量素子C3で第3の昇圧回路部A3を形成している。

【0067】

昇圧電圧蓄積用の容量素子C0は、一方でグランドVSSに接続され、もう一方はスイッチ素子S14とスイッチ素子S24とスイッチ素子S34に接続されている。結果的にはこの箇所に基準電源Vciの2倍の電圧(Vout)が出力される。

【0068】

20は、第1の昇圧回路部A1におけるスイッチ素子S11,S12,S13,S14をオン・オフ制御する制御信号A,B,C,Dと第2の昇圧回路部A2におけるスイッチ素子S21,S22,S23,S24をオン・オフ制御する制御信号E,F,G,Hと第3の昇圧回路部A3におけるスイッチ素子S31,S32,S33,S34をオン・オフ制御する制御信号I,J,K,Lを生成出力する制御部である。この制御部20は、第1の昇圧回路部A1、第2の昇圧回路部A2および第3の昇圧回路部A3のうちいずれか1つの昇圧回路部のデッドタイム期間において他の昇圧回路部では電荷蓄積動作またはポンプ動作を行うという制御を、前記3つの昇圧回路部A1,A2,A3において順次かつサイクリックに行うように構成されている。基準電源Vciは平滑容量を持たない電源となっている。

【0069】

図12は本実施の形態の昇圧装置の動作を示すタイミングチャートである。図12において、第1の昇圧回路部A1におけるスイッチ素子S11,S12,S13,S14をオン・オフ制御する制御信号A,B,C,Dは、昇圧回路用の第1のクロックCK1に基づいて生成され、第2の昇圧回路部A2におけるスイッチ素子S21,S22,S23,S24をオン・オフ制御する制御信号E,F,G,Hは、昇圧回路用の第2のクロックCK2に基づいて生成され、第3の昇圧回路部A3におけるスイッチ素子S31,S32,S33,S34は、昇圧回路用の第3のクロックCK3に基づいて生成される。

【0070】

また、図12において、ハッチングを施した領域は、デッドタイム期間の状態(DT)を表している。

【0071】

次に、上記のように構成された本実施の形態の昇圧装置の動作を、図13〜図24を参照しながら説明する。

【0072】

まず、図13のように、第1の昇圧回路部A1におけるスイッチ素子S12とスイッチ素子S13と、第2の昇圧回路部A2におけるスイッチ素子S21とスイッチ素子S24と、第3の昇圧回路部A3におけるスイッチ素子S32とスイッチ素子S33をオンさせ、スイッチ素子S11とスイッチ素子S14とスイッチ素子S22とスイッチ素子S23とスイッチ素子S31とスイッチ素子S34をオフさせる。この期間で、第1の昇圧回路部A1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2における容量素子C2は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第3の昇圧回路部A3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)である。この期間は、基準電源Vciへ負荷が3箇所からかかっている状態であり、第2の昇圧回路部A2から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔CH,UP,CH〕である。

【0073】

次に、図14のように、図13の状態から第3の昇圧回路部A3におけるスイッチ素子S32とスイッチ素子S33をオフさせる。この期間で、第1の昇圧回路部A1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2における容量素子C2は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第3の昇圧回路部A3はデッドタイム期間の状態(DT)である。第1の昇圧回路部A1および第2の昇圧回路部A2は動作状態のままであるため、基準電源Vciへ負荷が2箇所からかかっている状態であり、第2の昇圧回路部A2から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔CH,UP,DT〕である。

【0074】

次に、図15のように、図14の状態から第3の昇圧回路部A3におけるスイッチ素子S31とスイッチ素子S34をオンさせ、基準電源電圧蓄積用の容量素子C3に対して基準電源Vciを逆方向に印加する。この期間で、第1の昇圧回路部A1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2における容量素子C2は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第3の昇圧回路部A3における容量素子C3は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)である。この期間は、基準電源Vciへ負荷が3箇所からかかっている状態であり、第2の昇圧回路部A2および第3の昇圧回路部A3から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔CH,UP,UP〕である。

【0075】

次に、図16のように、図15の状態から第2の昇圧回路部A2におけるスイッチ素子S21とスイッチ素子S24をオフさせる。この期間で、第1の昇圧回路部A1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第3の昇圧回路部A3における容量素子C3は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。第1の昇圧回路部A1および第3の昇圧回路部A3は動作状態のままであるため、基準電源Vciへ負荷が2箇所からかかっている状態であり、第3の昇圧回路部A3から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔CH,DT,UP〕である。

【0076】

次に、図17のように、図16の状態から第2の昇圧回路部A2におけるスイッチ素子S22とスイッチ素子S23をオンさせる。この期間で、第1の昇圧回路部A1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の昇圧回路部A3における容量素子C3は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)である。この期間は、基準電源Vciへ負荷が3箇所からかかっている状態であり、第3の昇圧回路部A3から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔CH,CH,UP〕である。

【0077】

次に、図18のように、図17の状態から第1の昇圧回路部A1におけるスイッチ素子S12とスイッチ素子S13をオフさせる。この期間で、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の昇圧回路部A3における容量素子C3は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。第2の昇圧回路部A2および第3の昇圧回路部A3は動作状態のままであるため、基準電源Vciへ負荷が2箇所からかかっている状態であり、第3の昇圧回路部A3から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔DT,CH,UP〕である。

【0078】

次に、図19のように、図18の状態から第1の昇圧回路部A1におけるスイッチ素子S11とスイッチ素子S14をオンさせ、基準電源電圧蓄積用の容量素子C1に対して基準電源Vciを逆方向に印加する。この期間で、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の昇圧回路部A3における容量素子C3は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)である。この期間は、基準電源Vciへ負荷が3箇所からかかっている状態であり、第1の昇圧回路部A1および第3の昇圧回路部A3から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔UP,CH,UP〕である。

【0079】

次に、図20のように、図19の状態から第3の昇圧回路部A3におけるスイッチ素子S31とスイッチ素子S34をオフさせる。この期間で、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の昇圧回路部A3はデッドタイム期間の状態(DT)である。第1の昇圧回路部A1および第2の昇圧回路部A2は動作状態のままであるため、基準電源Vciへ負荷が2箇所からかかっている状態であり、第1の昇圧回路部A1から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔UP,CH,DT〕である。

【0080】

次に、図21のように、図20の状態から第3の昇圧回路部A3におけるスイッチ素子S32とスイッチ素子S33をオンさせる。この期間で、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の昇圧回路部A3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)である。この期間は、基準電源Vciへ負荷が3箇所からかかっている状態であり、第1の昇圧回路部A1から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔UP,CH,CH〕である。

【0081】

次に、図22のように、図21の状態から第2の昇圧回路部A2におけるスイッチ素子S22とスイッチ素子S23をオフさせる。この期間で、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第3の昇圧回路部A3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。第1の昇圧回路部A1および第3の昇圧回路部A3は動作状態のままであるため、基準電源Vciへ負荷が2箇所からかかっている状態であり、第1の昇圧回路部A1から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔UP,DT,CH〕である。

【0082】

次に、図23のように、図22の状態から第2の昇圧回路部A2におけるスイッチ素子S21とスイッチ素子S24をオンさせ、基準電源電圧蓄積用の容量素子C2に対して基準電源Vciを逆方向に印加する。この期間で、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第2の昇圧回路部A2における容量素子C2は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第3の昇圧回路部A3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)である。この期間は、基準電源Vciへ負荷が3箇所からかかっている状態であり、第1の昇圧回路部A1および第2の昇圧回路部A2から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔UP,UP,CH〕である。

【0083】

次に、図24のように、図23の状態から第1の昇圧回路部A1におけるスイッチ素子S11とスイッチ素子S14をオフさせる。この期間で、第2の昇圧回路部A2における容量素子C2は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第3の昇圧回路部A3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)であり、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。第2の昇圧回路部A2および第3の昇圧回路部A3は動作状態のままであるため、基準電源Vciへ負荷が2箇所からかかっている状態であり、第2の昇圧回路部A2から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔DT,UP,CH〕である。

【0084】

図13〜図24の動作を繰り返すことにより、昇圧電圧蓄積用の容量素子C0に基準電源Vciの2倍の電圧(Vout)が生成される。

【0085】

図12において、図14相当の期間では、第3の昇圧回路部A3における4つのスイッチ素子S31,S32,S33,S34がすべてオフとなっていて、第3の昇圧回路部A3はデッドタイム期間の状態(DT)である。このとき、第1の昇圧回路部A1において、スイッチ素子S12,S13がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。さらに、第2の昇圧回路部A2において、スイッチ素子S21,S24がオンであることから、昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態(UP)も確保されている。

【0086】

また、図12において、図16相当の期間では、第2の昇圧回路部A2における4つのスイッチ素子S21,S22,S23,S24がすべてオフとなっていて、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。このとき、第1の昇圧回路部A1において、スイッチ素子S12,S13がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。さらに、第3の昇圧回路部A3において、スイッチ素子S31,S34がオンであることから、昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態(UP)も確保されている。

【0087】

また、図12において、図18相当の期間では、第1の昇圧回路部A1における4つのスイッチ素子S11,S12,S13,S14がすべてオフとなっていて、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。このとき、第2の昇圧回路部A2において、スイッチ素子S22,S23がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。さらに、第3の昇圧回路部A3において、スイッチ素子S31,S34がオンであることから、昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態(UP)も確保されている。

【0088】

また、図12において、図20相当の期間では、第3の昇圧回路部A3における4つのスイッチ素子S31,S32,S33,S34がすべてオフとなっていて、第3の昇圧回路部A3はデッドタイム期間の状態(DT)である。このとき、第2の昇圧回路部A2において、スイッチ素子S22,S23がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。さらに、第1の昇圧回路部A1において、スイッチ素子S11,S14がオンであることから、昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態(UP)も確保されている。

【0089】

また、図12において、図22相当の期間では、第2の昇圧回路部A2における4つのスイッチ素子S21,S22,S23,S24がすべてオフとなっていて、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。このとき、第3の昇圧回路部A3において、スイッチ素子S32,S33がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。さらに、第1の昇圧回路部A1において、スイッチ素子S11,S14がオンであることから、昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態(UP)も確保されている。

【0090】

また、図12において、図24相当の期間では、第1の昇圧回路部A1における4つのスイッチ素子S11,S12,S13,S14がすべてオフとなっていて、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。このとき、第3の昇圧回路部A3において、スイッチ素子S32,S33がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。さらに、第2の昇圧回路部A2において、スイッチ素子S21,S24がオンであることから、昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態(UP)も確保されている。

【0091】

以上の経過をまとめると、

図13……〔A1,A2,A3〕=〔CH,UP,CH〕

図14……〔A1,A2,A3〕=〔CH,UP,DT〕

図15……〔A1,A2,A3〕=〔CH,UP,UP〕

図16……〔A1,A2,A3〕=〔CH,DT,UP〕

図17……〔A1,A2,A3〕=〔CH,CH,UP〕

図18……〔A1,A2,A3〕=〔DT,CH,UP〕

図19……〔A1,A2,A3〕=〔UP,CH,UP〕

図20……〔A1,A2,A3〕=〔UP,CH,DT〕

図21……〔A1,A2,A3〕=〔UP,CH,CH〕

図22……〔A1,A2,A3〕=〔UP,DT,CH〕

図23……〔A1,A2,A3〕=〔UP,UP,CH〕

図24……〔A1,A2,A3〕=〔DT,UP,CH〕

となる。第1の昇圧回路部A1における動作履歴をみると、CH→CH→CH→CH→CH→DT→UP→UP→UP→UP→UP→DTのサイクリック動作となっている。また、第2の昇圧回路部A2における動作履歴をみると、UP→UP→UP→DT→CH→CH→CH→CH→CH→DT→UP→UPのサイクリック動作となっている。また、第3の昇圧回路部A3における動作履歴をみると、CH→DT→UP→UP→UP→UP→UP→DT→CH→CH→CH→CHのサイクリック動作となっている。3つの昇圧回路部A1,A2,A3の動作は、タイミングこそ異なるが、同一パターンのサイクリック動作となっている。

【0092】

第3の昇圧回路部A3がデッドタイム期間の状態(DT)であるときは(図14または図20)、第1の昇圧回路部A1が基準電源Vciの電圧を蓄える状態(CH)または蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第2の昇圧回路部A2が蓄えられた電荷を昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)または基準電源Vciの電圧を蓄える状態(CH)となっている。

【0093】

また、第2の昇圧回路部A2がデッドタイム期間の状態(DT)であるときは(図16または図22)、第1の昇圧回路部A1が基準電源Vciの電圧を蓄える状態(CH)または蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第3の昇圧回路部A3が蓄えられた電荷を昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)または基準電源Vciの電圧を蓄える状態(CH)となっている。

【0094】

また、第1の昇圧回路部A1がデッドタイム期間の状態(DT)であるときは(図18または図24)、第2の昇圧回路部A2が基準電源Vciの電圧を蓄える状態(CH)または蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第3の昇圧回路部A3が蓄えられた電荷を昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)または基準電源Vciの電圧を蓄える状態(CH)となっている。

【0095】

すなわち、いずれの1つの昇圧回路部がデッドタイム期間の状態(DT)であっても、他の1つの昇圧回路部において、必ず、平滑容量を持たない基準電源Vciに負荷がかかっている状態を維持させることができている。これで、従来の技術の場合の、〔DT,無負荷〕の状態を脱却でき、〔DT,無負荷〕の状態に起因するノイズの発生を抑制することができる。また、別の1つの昇圧回路部において、必ず、昇圧電圧蓄積用の容量素子C0に電荷の供給が行われている状態を維持させることができている。これで、基準電源Vciの2倍の電圧(Vout)のリップルを低減させ、電流能力を上げるという効果も得られる。

【0096】

まとめると、本実施の形態によれば、基準電源Vciには常に負荷がかかっている状態で、昇圧動作が可能となり、基準電源Vciのノイズの低減が可能となり、さらに昇圧電圧蓄積用の容量素子C0には常に少なくとも1つの昇圧回路部から電荷の供給が行われている状態になるため、基準電源Vciの2倍の電圧(Vout)のリップルを低減させ、電流能力を上げるという効果も得られる。

【0097】

なお、本実施の形態の昇圧装置においては、基準電源Vciの2倍の電圧(Vout)の出力端子に対しては、常に少なくとも1つの昇圧回路部から電荷の供給が行われている状態になるため、基準電源Vciの2倍の電圧(Vout)を保持する役割の昇圧電圧蓄積用の容量素子C0はなくてもよい。

【0098】

(実施の形態3)

上記においては、昇圧装置について説明したが、降圧回路部を3つ以上接続した場合の降圧装置でも、上記同様の効果が得られる。これが本発明の実施の形態3である。以下に、本発明の実施の形態3における降圧装置について説明する。

【0099】

図25は、本発明の実施の形態3における降圧装置の構成を示す回路図である。図25に示すように、電圧出力端子Voutに降圧電圧蓄積用の容量素子C0が接続され、この降圧電圧蓄積用の容量素子C0に対して第1の降圧回路部B1と第2の降圧回路部B2と第3の降圧回路部B3が並列に接続されている。降圧電圧蓄積用の容量素子C0は、基準電源Vciの(−1)倍の電圧(Vout)を保持し、出力するものである。

【0100】

第1の降圧回路部B1において、グランドVSSと基準電源Vciとの間にスイッチ素子S11とスイッチ素子S12の直列回路が接続されており、また、グランドVSSと両スイッチ素子S11,S12の接続点との間にスイッチ素子S13と基準電源電圧蓄積用の容量素子C1の直列回路が接続されている。スイッチ素子S13と基準電源電圧蓄積用の容量素子C1の接続点とグランドVSSとの間にスイッチ素子S14と降圧電圧蓄積用の容量素子C0の直列回路が接続されている。降圧電圧蓄積用の容量素子C0は、基準電源Vciの(−1)倍の電圧(Vout)を保持し、出力するものである。スイッチ素子S11,S12,S13,S14と基準電源電圧蓄積用の容量素子C1で第1の降圧回路部B1を形成している。

【0101】

第2の降圧回路部B2において、グランドVSSと基準電源Vciとの間にスイッチ素子S21とスイッチ素子S22の直列回路が接続されており、また、グランドVSSと両スイッチ素子S21,S22の接続点との間にスイッチ素子S23と基準電源電圧蓄積用の容量素子C2の直列回路が接続されている。スイッチ素子S23と基準電源電圧蓄積用の容量素子C2の接続点とグランドVSSとの間にスイッチ素子S24と降圧電圧蓄積用の容量素子C0の直列回路が接続されている。スイッチ素子S21,S22,S23,S24と基準電源電圧蓄積用の容量素子C2で第2の降圧回路部B2を形成している。

【0102】

第3の降圧回路部B3において、グランドVSSと基準電源Vciとの間にスイッチ素子S31とスイッチ素子S32の直列回路が接続されており、また、グランドVSSと両スイッチ素子S31,S32の接続点との間にスイッチ素子S33と基準電源電圧蓄積用の容量素子C3の直列回路が接続されている。スイッチ素子S33と基準電源電圧蓄積用の容量素子C3の接続点とグランドVSSとの間にスイッチ素子S34と降圧電圧蓄積用の容量素子C0の直列回路が接続されている。スイッチ素子S31,S32,S33,S34と基準電源電圧蓄積用の容量素子C3で第3の降圧回路部B3を形成している。

【0103】

30は、第1の降圧回路部B1におけるスイッチ素子S11,S12,S13,S14をオン・オフ制御する制御信号A,B,C,Dと第2の降圧回路部B2におけるスイッチ素子S21,S22,S23,S24をオン・オフ制御する制御信号E,F,G,Hと第3の降圧回路部B3におけるスイッチ素子S31,S32,S33,S34をオン・オフ制御する制御信号I,J,K,Lを生成出力する制御部である。この制御部30は、第1の降圧回路部B1、第2の降圧回路部B2および第3の降圧回路部B3のうちいずれか1つの降圧回路部のデッドタイム期間において他の降圧回路部では電荷蓄積動作またはポンプ動作を行うという制御を、前記3つの降圧回路部B1,B2,B3において順次かつサイクリックに行うように構成されている。基準電源Vciは平滑容量を持たない電源となっている。

【0104】

上記のように、本実施の形態における降圧装置は、基準電源Vciの(−1)倍の電圧(Vout)を保持する降圧電圧蓄積用の容量素子C0に対して、第1の降圧回路部B1と第2の降圧回路部B2と第3の降圧回路部B3とが並列に接続された構成となっている。

【0105】

図26は本実施の形態の降圧装置の動作を示すタイミングチャートである。図26のタイミングチャートにおいて、第1の降圧回路部B1におけるスイッチ素子S11,S12,S13,S14をオン・オフ制御する制御信号A,B,C,Dは、降圧回路用の第1のクロックCK1に基づいて生成され、第2の降圧回路部B2におけるスイッチ素子S21,S22,S23,S24をオン・オフ制御する制御信号E,F,G,Hは、降圧回路用の第2のクロックCK2に基づいて生成され、第3の降圧回路部B3におけるスイッチ素子S31,S32,S33,S34は、降圧回路用の第3のクロックCK3に基づいて生成される。

【0106】

また、図26において、ハッチングを施した領域は、デッドタイム期間の状態(DT)を表している。

【0107】

次に、上記のように構成された本実施の形態の降圧装置動作を、図27〜図38を参照しながら以下に説明する。

【0108】

まず、図27のように、第1の降圧回路部B1におけるスイッチ素子S12とスイッチ素子S13と、第2の降圧回路部B2におけるスイッチ素子S21とスイッチ素子S24と、第3の降圧回路部B3におけるスイッチ素子S32とスイッチ素子S33をオンさせ、スイッチ素子S11とスイッチ素子S14とスイッチ素子S22とスイッチ素子S23とスイッチ素子S31とスイッチ素子S34をオフさせる。この期間で、第1の降圧回路部B1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の降圧回路部B2における容量素子C2は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第3の降圧回路部B3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)である。この期間は、基準電源Vciへ負荷が2箇所からかかっている状態であり、第2の降圧回路部B2から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔CH,DN,CH〕である。

【0109】

次に、図28のように、図27の状態から第3の降圧回路部B3におけるスイッチ素子S32とスイッチ素子S33をオフさせる。この期間で、第1の降圧回路部B1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の降圧回路部B2における容量素子C2は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第3の降圧回路部B3はデッドタイム期間の状態(DT)である。第1の降圧回路部B1および第2の降圧回路部B2は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態であり、第2の降圧回路部B2から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔CH,DN,DT〕である。

【0110】

次に、図29のように、図28の状態から第3の降圧回路部B3におけるスイッチ素子S31とスイッチ素子S34をオンさせ、基準電源電圧蓄積用の容量素子C3に対して基準電源Vciを同方向に印加する。この期間で、第1の降圧回路部B1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の降圧回路部B2における容量素子C2は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第3の降圧回路部B3における容量素子C3は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)である。この期間は、基準電源Vciへ負荷が1箇所からかかっている状態であり、第2の降圧回路部B2および第3の降圧回路部B3から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔CH,DN,DN〕である。

【0111】

次に、図30のように、図29の状態から第2の降圧回路部B2におけるスイッチ素子S21とスイッチ素子S24をオフさせる。この期間で、第1の降圧回路部B1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第3の降圧回路部B3における容量素子C3は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第2の降圧回路部B2はデッドタイム期間の状態(DT)である。第1の降圧回路部B1および第3の降圧回路部B3は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態であり、第3の降圧回路部B3から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔CH,DT,DN〕である。

【0112】

次に、図31のように、図30の状態から第2の降圧回路部B2におけるスイッチ素子S22とスイッチ素子S23をオンさせる。この期間で、第1の降圧回路部B1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の降圧回路部B2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の降圧回路部B3における容量素子C3は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)である。この期間は、基準電源Vciへ負荷が2箇所からかかっている状態であり、第3の降圧回路部B3から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔CH,CH,DN〕である。

【0113】

次に、図32のように、図31の状態から第1の降圧回路部B1におけるスイッチ素子S12とスイッチ素子S13をオフさせる。この期間で、第2の降圧回路部B2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の降圧回路部B3における容量素子C3は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第1の降圧回路部B1はデッドタイム期間の状態(DT)である。第2の降圧回路部B2および第3の降圧回路部B3は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態であり、第3の降圧回路部B3から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔DT,CH,DN〕である。

【0114】

次に、図33のように、図32の状態から第1の降圧回路部B1におけるスイッチ素子S11とスイッチ素子S14をオンさせ、基準電源電圧蓄積用の容量素子C1に対して基準電源Vciを同方向に印加する。この期間で、第1の降圧回路部B1における容量素子C1は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第2の降圧回路部B2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の降圧回路部B3における容量素子C3は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)である。この期間は、基準電源Vciへ負荷が1箇所からかかっている状態であり、第1の降圧回路部B1および第3の降圧回路部B3から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔DN,CH,DN〕である。

【0115】

次に、図34のように、図33の状態から第3の降圧回路部B3におけるスイッチ素子S31とスイッチ素子S34をオフさせる。この期間で、第1の降圧回路部B1における容量素子C1は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第2の降圧回路部B2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の降圧回路部B3はデッドタイム期間の状態(DT)である。第1の降圧回路部B1および第2の降圧回路部B2は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態であり、第1の降圧回路部B1から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔DN,CH,DT〕である。

【0116】

次に、図35のように、図34の状態から第3の降圧回路部B3におけるスイッチ素子S32とスイッチ素子S33をオンさせる。この期間で、第1の降圧回路部B1における容量素子C1は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第2の降圧回路部B2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の降圧回路部B3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)である。この期間は、基準電源Vciへ負荷が2箇所からかかっている状態であり、第1の降圧回路部B1から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔DN,CH,CH〕である。

【0117】

次に、図36のように、図35の状態から第2の降圧回路部B2におけるスイッチ素子S22とスイッチ素子S23をオフさせる。この期間で、第1の降圧回路部B1における容量素子C1は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第3の降圧回路部B3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)であり、第2の降圧回路部B2はデッドタイム期間の状態(DT)である。第1の降圧回路部B1および第3の降圧回路部B3は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態であり、第1の降圧回路部B1から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔DN,DT,CH〕である。

【0118】

次に、図37のように、図36の状態から第2の降圧回路部B2におけるスイッチ素子S21とスイッチ素子S24をオンさせ、基準電源電圧蓄積用の容量素子C2に対して基準電源Vciを同方向に印加する。この期間で、第1の降圧回路部B1における容量素子C1は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第2の降圧回路部B2における容量素子C2は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第3の降圧回路部B3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)である。この期間は、基準電源Vciへ負荷が1箇所からかかっている状態であり、第1の降圧回路部B1および第2の降圧回路部B2から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔DN,DN,CH〕である。

【0119】

次に、図38のように、図37の状態から第1の降圧回路部B1におけるスイッチ素子S11とスイッチ素子S14をオフさせる。この期間で、第2の降圧回路部B2における容量素子C2は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第3の降圧回路部B3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)であり、第1の降圧回路部B1はデッドタイム期間の状態(DT)である。第2の降圧回路部B2および第3の降圧回路部B3は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態であり、第2の降圧回路部B2から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔DT,DN,CH〕である。

【0120】

図27〜図38の動作を繰り返すことにより、降圧電圧蓄積用の容量素子C0に基準電源Vciの(−1)倍の電圧(Vout)が生成される。

【0121】

図26において、図28相当の期間では、第3の降圧回路部B3における4つのスイッチ素子S31,S32,S33,S34がすべてオフとなっていて、第3の降圧回路部B3はデッドタイム期間の状態(DT)である。このとき、第1の降圧回路部B1において、スイッチ素子S12,S13がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。さらに、第2の降圧回路部B2において、スイッチ素子S21,S24がオンであることから、降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態(DN)も確保されている。

【0122】

また、図26において、図30相当の期間では、第2の降圧回路部B2における4つのスイッチ素子S21,S22,S23,S24がすべてオフとなっていて、第2の降圧回路部B2はデッドタイム期間の状態(DT)である。このとき、第1の降圧回路部B1において、スイッチ素子S12,S13がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。さらに、第3の降圧回路部B3において、スイッチ素子S31,S34がオンであることから、降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態(DN)も確保されている。

【0123】

また、図26において、図32相当の期間では、第1の降圧回路部B1における4つのスイッチ素子S11,S12,S13,S14がすべてオフとなっていて、第1の降圧回路部B1はデッドタイム期間の状態(DT)である。このとき、第2の降圧回路部B2において、スイッチ素子S22,S23がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。さらに、第3の降圧回路部B3において、スイッチ素子S31,S34がオンであることから、降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態(DN)も確保されている。

【0124】

また、図26において、図34相当の期間では、第3の降圧回路部B3における4つのスイッチ素子S31,S32,S33,S34がすべてオフとなっていて、第3の降圧回路部B3はデッドタイム期間の状態(DT)である。このとき、第2の降圧回路部B2において、スイッチ素子S22,S23がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。さらに、第1の降圧回路部B1において、スイッチ素子S11,S14がオンであることから、降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態(DN)も確保されている。

【0125】

また、図26において、図36相当の期間では、第2の降圧回路部B2における4つのスイッチ素子S21,S22,S23,S24がすべてオフとなっていて、第2の降圧回路部B2はデッドタイム期間の状態(DT)である。このとき、第3の降圧回路部B3において、スイッチ素子S32,S33がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。さらに、第1の降圧回路部B1において、スイッチ素子S11,S14がオンであることから、降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態(DN)も確保されている。

【0126】

また、図26において、図38相当の期間では、第1の降圧回路部B1における4つのスイッチ素子S11,S12,S13,S14がすべてオフとなっていて、第1の降圧回路部B1はデッドタイム期間の状態(DT)である。このとき、第3の降圧回路部B3において、スイッチ素子S32,S33がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。さらに、第2の降圧回路部B2において、スイッチ素子S21,S24がオンであることから、降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態(DN)も確保されている。

【0127】

以上の経過をまとめると、

図27……〔B1,B2,B3〕=〔CH,DN,CH〕

図28……〔B1,B2,B3〕=〔CH,DN,DT〕

図29……〔B1,B2,B3〕=〔CH,DN,DN〕

図30……〔B1,B2,B3〕=〔CH,DT,DN〕

図31……〔B1,B2,B3〕=〔CH,CH,DN〕

図32……〔B1,B2,B3〕=〔DT,CH,DN〕

図33……〔B1,B2,B3〕=〔DN,CH,DN〕

図34……〔B1,B2,B3〕=〔DN,CH,DT〕

図35……〔B1,B2,B3〕=〔DN,CH,CH〕

図36……〔B1,B2,B3〕=〔DN,DT,CH〕

図37……〔B1,B2,B3〕=〔DN,DN,CH〕

図38……〔B1,B2,B3〕=〔DT,DN,CH〕

となる。第1の降圧回路部B1における動作履歴をみると、CH→CH→CH→CH→CH→DT→DN→DN→DN→DN→DN→DTのサイクリック動作となっている。また、第2の降圧回路部B2における動作履歴をみると、DN→DN→DN→DT→CH→CH→CH→CH→CH→DT→DN→DNのサイクリック動作となっている。また、第3の降圧回路部B3における動作履歴をみると、CH→DT→DN→DN→DN→DN→DN→DT→CH→CH→CH→CHのサイクリック動作となっている。3つの降圧回路部B1,B2,B3の動作は、タイミングこそ異なるが、同一パターンのサイクリック動作となっている。

【0128】

第3の降圧回路部B3がデッドタイム期間の状態(DT)であるときは(図28または図34)、第2の降圧回路部B2が蓄えられた電荷を降圧電圧蓄積用の容量素子C0に持ち下げる状態(DN)または基準電源Vciの電圧を蓄える状態(CH)であり、第1の降圧回路部B1が基準電源Vciの電圧を蓄える状態(CH)または蓄えている電荷を降圧電圧蓄積用の容量素子C0に持ち下げる状態(DN)となっている。

【0129】

また、第2の降圧回路部B2がデッドタイム期間の状態(DT)であるときは(図30または図36)、第1の降圧回路部B1が基準電源Vciの電圧を蓄える状態(CH)または蓄えている電荷を降圧電圧蓄積用の容量素子C0に持ち下げる状態(DN)であり、第3の降圧回路部B3が蓄えられた電荷を降圧電圧蓄積用の容量素子C0に持ち下げる状態(DN)または基準電源Vciの電圧を蓄える状態(CH)となっている。

【0130】

また、第1の降圧回路部B1がデッドタイム期間の状態(DT)であるときは(図32または図38)、第2の降圧回路部B2が基準電源Vciの電圧を蓄える状態(CH)または蓄えている電荷を降圧電圧蓄積用の容量素子C0に持ち下げる状態(DN)であり、第3の降圧回路部B3が蓄えられた電荷を降圧電圧蓄積用の容量素子C0に持ち下げる状態(DN)または基準電源Vciの電圧を蓄える状態(CH)となっている。

【0131】

すなわち、いずれの1つの降圧回路部がデッドタイム期間の状態(DT)であっても、他の1つの降圧回路部において、必ず、平滑容量を持たない基準電源Vciに負荷がかかっている状態を維持させることができている。これで、従来の技術の場合の、〔DT,無負荷〕の状態を脱却でき、〔DT,無負荷〕の状態に起因するノイズの発生を抑制することができる。また、別の1つの降圧回路部において、必ず、降圧電圧蓄積用の容量素子C0に電荷の供給が行われている状態を維持させることができている。これで、基準電源Vciの(−1)倍の電圧(Vout)のリップルを低減させ、電流能力を上げるという効果も得られる。

【0132】

まとめると、本実施の形態によれば、基準電源Vciには常に負荷がかかっている状態で、降圧動作が可能となり、基準電源Vciのノイズの低減が可能となり、さらに降圧電圧蓄積用の容量素子C0には常に少なくとも1つの降圧回路部から電荷の供給が行われている状態になるため、基準電源Vciの(−1)倍の電圧(Vout)のリップルを低減させ、電流能力を上げるという効果も得られる。

【0133】

なお、本実施の形態の降圧装置においては、基準電源Vciの(−1)倍の電圧(Vout)の出力端子に対しては、常に少なくとも1つの降圧回路部から電荷の供給が行われている状態になるため、基準電源Vciの(−1)倍の電圧(Vout)を保持する役割の降圧電圧蓄積用の容量素子C0はなくてもよい。

【0134】

(実施の形態4)

上記においては、昇圧回路部または降圧回路部を2つ以上接続させることでの基準電源Vciのノイズの低減法について説明したが、昇圧回路部または降圧回路部にデッドタイム期間のみ、基準電源Vciに強制的に負荷を与える回路を追加することでも、上記同様の効果が得られる。これが本発明の実施の形態4である。

【0135】

図39は、本発明の実施の形態4における昇圧装置の構成を示す回路図である。図39に示すように、本実施の形態の昇圧装置は、昇圧回路部に、スイッチ素子を介して負荷電流源である抵抗が設けられている。

【0136】

基準電源VciとグランドVSSとの間にスイッチ素子S11とスイッチ素子S12の直列回路が接続されている。基準電源Vciと両スイッチ素子S11,S12の接続点との間にスイッチ素子S13と基準電源電圧蓄積用の容量素子C1の直列回路が接続されている。スイッチ素子S13と基準電源電圧蓄積用の容量素子C1の接続点とグランドVSSとの間にスイッチ素子S14と昇圧電圧蓄積用の容量素子C0の直列回路が接続されている。昇圧電圧蓄積用の容量素子C0は、基準電源Vciの2倍の電圧(Vout)を保持し、出力するものである。図40のタイミングチャートにおいて、制御信号A,B,C,Dはそれぞれスイッチ素子S11,S12,S13,S14をオン・オフ制御するものである。スイッチ素子S11,S12,S13,S14と基準電源電圧蓄積用の容量素子C1で昇圧回路部Aを形成している。

【0137】

さらに、基準電源VciとグランドVSSとの間にスイッチ素子S41と抵抗R1の直列回路が接続されており、スイッチ素子S41は図40の信号Mで制御されている。図40において、ハッチングを施した領域は、デッドタイム期間の状態(DT)を表している。

【0138】

40は、昇圧回路部Aにおけるスイッチ素子S11,S12,S13,S14をオン・オフ制御する制御信号A,B,C,Dと負荷電流源の抵抗R1のスイッチS41をオン・オフ制御する制御信号Mを生成出力する制御部である。

【0139】

次に、上記のように構成された本実施の形態の昇圧装置の動作について、図41から図44を参照しながら説明する。

【0140】

まず、図41のように、スイッチ素子S12とスイッチ素子S13をオンさせ、スイッチ素子S11とスイッチ素子S14とスイッチ素子S41をオフさせる。この状態で基準電源電圧蓄積用の容量素子C1には基準電源Vciの電圧が蓄えられる状態(CH)であり、抵抗R1には電流が流れていない状態である。この期間は、基準電源Vciへは昇圧回路部Aから負荷がかかっている状態である。

【0141】

次に、図42のように、図41の状態から昇圧回路部Aにおけるスイッチ素子S12とスイッチ素子S13をオフさせ、スイッチ素子S41をオンさせる。この期間は、昇圧回路部Aのデッドタイム期間(DT)であるが、抵抗R1を介して基準電源Vciへ負荷がかかっている状態である。

【0142】

次に、図43のように、図42の状態からスイッチ素子S11とスイッチ素子S14をオンさせ、スイッチ素子S41をオフさせる。この状態で基準電源電圧蓄積用の容量素子C1と昇圧電圧蓄積用の容量素子C0が接続され、容量素子C1に蓄えられた電荷が容量素子C0に持ち上げられる状態(UP)であり、抵抗R1には電流が流れていない状態である。この期間は、基準電源Vciへは昇圧回路部Aから負荷がかかっている状態である。

【0143】

次に、図44のように、図43の状態からスイッチ素子S11とスイッチ素子S14をオフさせ、スイッチ素子S41をオンさせる。この状態は昇圧回路部Aのデッドタイム期間(DT)であるが、抵抗R1を介して基準電源Vciへ負荷がかかっている状態である。

【0144】

図41〜図44の動作を繰り返すことにより、昇圧電圧蓄積用の容量素子C0に基準電源Vciの2倍の電圧(Vout)が生成される。

【0145】

本実施の形態によれば、基準電源Vciには常に負荷がかかっている状態で、昇圧動作が可能となり、基準電源Vciのノイズの低減が可能となる。

【0146】

なお、以上の実施の形態の説明におけるスイッチ素子については、MOSトランジスタやバイポーラトランジスタなどが知られているが、それに限定されるものではなく、スイッチング機能を有する素子であれば構わない。

【0147】

(実施の形態5)

図45は、本発明の実施の形態5における昇圧装置の構成を示す回路図である。図45に示すように、第1の電圧出力端子Vout1に第1の昇圧電圧蓄積用の容量素子C01が接続され、この第1の昇圧電圧蓄積用の容量素子C01に対して第1の昇圧回路部A1が接続されている。さらに、第2の電圧出力端子Vout2に第2の昇圧電圧蓄積用の容量素子C02が接続され、この第2の昇圧電圧蓄積用の容量素子C02に対して第2の昇圧回路部A2が接続されている。第1の昇圧電圧蓄積用の容量素子C01は、基準電源Vciの2倍の電圧(Vout1)を保持し、出力するものであり、第2の昇圧電圧蓄積用の容量素子C02は、基準電源Vciの2倍の電圧(Vout2)を保持し、出力するものである。

【0148】

第1の昇圧回路部A1において、基準電源VciとグランドVSSとの間にスイッチ素子S11とスイッチ素子S12の直列回路が接続されている。基準電源Vciと両スイッチ素子S11,S12の接続点との間にスイッチ素子S13と基準電源電圧蓄積用の容量素子C1の直列回路が接続されている。スイッチ素子S13と容量素子C1の接続点とグランドVSSとの間にスイッチ素子S14と第1の昇圧電圧蓄積用の容量素子C01の直列回路が接続されている。スイッチ素子S11,S12,S13,S14と基準電源電圧蓄積用の容量素子C1で第1の昇圧回路部A1を形成している。

【0149】

第2の昇圧回路部A2において、基準電源VciとグランドVSSとの間にスイッチ素子S21とスイッチ素子S22の直列回路が接続されている。基準電源Vciと両スイッチ素子S21,S22の接続点との間にスイッチ素子S23と基準電源電圧蓄積用の容量素子C2の直列回路が接続されている。スイッチ素子S23と容量素子C2の接続点とグランドVSSとの間にスイッチ素子S24と第2の昇圧電圧蓄積用の容量素子C02の直列回路が接続されている。スイッチ素子S21,S22,S23,S24と基準電源電圧蓄積用の容量素子C2で第2の昇圧回路部A2を形成している。

【0150】

第1の昇圧電圧蓄積用の容量素子C01は、一方でグランドVSSに接続され、もう一方はスイッチ素子S14に接続されている。結果的にはこの箇所に基準電源Vciの2倍の電圧(Vout1)が出力される。

【0151】

第2の昇圧電圧蓄積用の容量素子C02は、一方でグランドVSSに接続され、もう一方はスイッチ素子S24に接続されている。結果的にはこの箇所に基準電源Vciの2倍の電圧(Vout2)が出力される。

【0152】

50は、第1の昇圧回路部A1におけるスイッチ素子S11,S12,S13,S14をオン・オフ制御する制御信号A,B,C,Dと第2の昇圧回路部A2におけるスイッチ素子S21,S22,S23,S24をオン・オフ制御する制御信号E,F,G,Hを生成出力する制御部である。この制御部50は、第1の昇圧回路部A1および第2の昇圧回路部A2のうちいずれか一方の昇圧回路部のデッドタイム期間において他方の昇圧回路部では電荷蓄積動作またはポンプ動作を行うという制御を、両昇圧回路部A1,A2間で交互かつサイクリックに行うように構成されている。スイッチ素子はトランジスタ等で構成されている。基準電源Vciは平滑容量を持たない電源となっている。

【0153】

図46は本実施の形態の昇圧装置の動作を示すタイミングチャートである。図46において、第1の昇圧回路部A1におけるスイッチ素子S11,S12,S13,S14をオン・オフ制御する制御信号A,B,C,Dは、昇圧回路用の第1のクロックCK1に基づいて生成され、第2の昇圧回路部A2におけるスイッチ素子S21,S22,S23,S24をオン・オフ制御する制御信号E,F,G,Hは、昇圧回路用の第2のクロックCK2に基づいて生成される。

【0154】

また、図46において、ハッチングを施した領域は、デッドタイム期間の状態(DT)を表している。

【0155】

次に、上記のように構成された本実施の形態の昇圧装置の動作を、図47〜図54を参照しながら説明する。

【0156】

まず、図47のように、第1の昇圧回路部A1におけるスイッチ素子S12とスイッチ素子S13と、第2の昇圧回路部A2におけるスイッチ素子S21とスイッチ素子S24をオンさせ、スイッチ素子S11とスイッチ素子S14とスイッチ素子S22とスイッチ素子S23をオフさせる。この期間で、第1の昇圧回路部A1における基準電源電圧蓄積用の容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2における基準電源電圧蓄積用の容量素子C2は蓄えている電荷をポンプ動作により第2の昇圧電圧蓄積用の容量素子C02に持ち上げる状態(UP)である。この期間は、基準電源Vciへ負荷が2箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔CH,UP〕である。

【0157】

次に、図48のように、図47の状態から第2の昇圧回路部A2におけるスイッチ素子S21とスイッチ素子S24をオフさせる。この期間で、第1の昇圧回路部A1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。第1の昇圧回路部A1は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔CH,DT〕である。

【0158】

次に、図49のように、図48の状態から第2の昇圧回路部A2におけるスイッチ素子S22とスイッチ素子S23をオンさせる。この期間で、第1の昇圧回路部A1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)である。この期間は、基準電源Vciへ負荷が2箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔CH,CH〕である。

【0159】

次に、図50のように、図49の状態から第1の昇圧回路部A1におけるスイッチ素子S12とスイッチ素子S13をオフさせる。この期間で、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。第2の昇圧回路部A2は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔DT,CH〕である。

【0160】

次に、図51のように、図50の状態から第1の昇圧回路部A1におけるスイッチ素子S11とスイッチ素子S14をオンさせ、基準電源電圧蓄積用の容量素子C1に対して基準電源Vciを逆方向に印加する。この期間で、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により第1の昇圧電圧蓄積用の容量素子C01に持ち上げる状態(UP)である。この期間は、基準電源Vciへ負荷が2箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔UP,CH〕である。

【0161】

次に、図52のように、図51の状態から第2の昇圧回路部A2におけるスイッチ素子S22とスイッチ素子S23をオフさせる。この期間で、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により第1の昇圧電圧蓄積用の容量素子C01に持ち上げる状態(UP)であり、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。第1の昇圧回路部A1は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔UP,DT〕である。

【0162】

次に、図53のように、図52の状態から第2の昇圧回路部A2におけるスイッチ素子S21とスイッチ素子S24をオンさせ、基準電源電圧蓄積用の容量素子C2に対して基準電源Vciを逆方向に印加する。この期間で、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により第1の昇圧電圧蓄積用の容量素子C01に持ち上げる状態(UP)であり、第2の昇圧回路部A2における容量素子C2は蓄えている電荷をポンプ動作により第2の昇圧電圧蓄積用の容量素子C02に持ち上げる状態(UP)である。この期間は、基準電源Vciへ負荷が2箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔UP,UP〕である。

【0163】

次に、図54のように、図53の状態から第1の昇圧回路部A1におけるスイッチ素子S11とスイッチ素子S14をオフさせる。この期間で、第2の昇圧回路部A2における容量素子C2は蓄えている電荷をポンプ動作により第2の昇圧電圧蓄積用の容量素子C02に持ち上げる状態(UP)であり、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。第2の昇圧回路部A2は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔DT,UP〕である。

【0164】

図47〜図54の動作を繰り返すことにより、第1の昇圧電圧蓄積用の容量素子C01に基準電源Vciの2倍の電圧(Vout1)が生成され、第2の昇圧電圧蓄積用の容量素子C02に基準電源Vciの2倍の電圧(Vout2)が生成される。

【0165】

図46において、図48相当の期間では、第2の昇圧回路部A2における4つのスイッチ素子S21,S22,S23,S24がすべてオフとなっていて、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。このとき、第1の昇圧回路部A1において、スイッチ素子S12,S13がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。

【0166】

また、図46において、図50相当の期間では、第1の昇圧回路部A1における4つのスイッチ素子S11,S12,S13,S14がすべてオフとなっていて、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。このとき、第2の昇圧回路部A2において、スイッチ素子S22,S23がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。

【0167】

また、図46において、図52相当の期間では、第2の昇圧回路部A2における4つのスイッチ素子S21,S22,S23,S24がすべてオフとなっていて、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。このとき、第1の昇圧回路部A1において、スイッチ素子S11,S14がオンであることから、蓄えている電荷を第1の昇圧電圧蓄積用の容量素子C01に持ち上げる状態(UP)となっている。

【0168】

また、図46において、図54相当の期間では、第1の昇圧回路部A1における4つのスイッチ素子S11,S12,S13,S14がすべてオフとなっていて、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。このとき、第2の昇圧回路部A2において、スイッチ素子S21,S24がオンであることから、蓄えている電荷を第2の昇圧電圧蓄積用の容量素子C02に持ち上げる状態(UP)となっている。

【0169】

以上の経過をまとめると、

図47……〔A1,A2〕=〔CH,UP〕

図48……〔A1,A2〕=〔CH,DT〕

図49……〔A1,A2〕=〔CH,CH〕

図50……〔A1,A2〕=〔DT,CH〕

図51……〔A1,A2〕=〔UP,CH〕

図52……〔A1,A2〕=〔UP,DT〕

図53……〔A1,A2〕=〔UP,UP〕

図54……〔A1,A2〕=〔DT,UP〕

となる。第1の昇圧回路部A1における動作履歴をみると、CH→CH→CH→DT→UP→UP→UP→DTのサイクリック動作となっている。また、第2の昇圧回路部A2における動作履歴をみると、UP→DT→CH→CH→CH→DT→UP→UPのサイクリック動作となっている。両昇圧回路部A1,A2の動作は、タイミングこそ異なるが、同一パターンのサイクリック動作となっている。

【0170】

第2の昇圧回路部A2がデッドタイム期間の状態(DT)であるときは(図48または図52)、第1の昇圧回路部A1は基準電源Vciの電圧を蓄える状態(CH)または蓄えている電荷をポンプ動作により第1の昇圧電圧蓄積用の容量素子C01に持ち上げる状態(UP)となっている。

【0171】

また、第1の昇圧回路部A1がデッドタイム期間の状態(DT)であるときは(図50または図54)、第2の昇圧回路部A2は基準電源Vciの電圧を蓄える状態(CH)または蓄えている電荷をポンプ動作により第2の昇圧電圧蓄積用の容量素子C02に持ち上げる状態(UP)となっている。

【0172】

まとめると、

〔A1,A2〕=〔有負荷,DT〕

〔A1,A2〕=〔DT,有負荷〕

の原則が保たれている。

【0173】

すなわち、いずれの昇圧回路部がデッドタイム期間の状態(DT)であっても、他方の昇圧回路部において、必ず、平滑容量を持たない基準電源Vciに負荷がかかっている状態を維持させることができている。これで、従来の技術の場合の、〔DT,無負荷〕の状態を脱却でき、〔DT,無負荷〕の状態に起因するノイズの発生を抑制することができる。

【0174】

まとめると、本実施の形態によれば、基準電源Vciには常に負荷がかかっている状態で、昇圧動作が可能となり、基準電源Vciのノイズの低減が可能となる。

【産業上の利用可能性】

【0175】

本発明の昇圧装置または降圧装置は、平滑容量を持たない基準電源発生源の出力電圧を基準電源とする昇圧装置の基準電源のノイズを低減させ、そのノイズの別回路への悪影響を低減させる等の効果があり、昇圧装置または降圧装置を内蔵した電源回路等として有用である。

【図面の簡単な説明】

【0176】

【図1】本発明の実施の形態1における昇圧装置の構成を示す回路図

【図2】本発明の実施の形態1における昇圧装置の動作を示す信号波形図

【図3】本発明の実施の形態1における昇圧装置の動作説明図(その1)

【図4】本発明の実施の形態1における昇圧装置の動作説明図(その2)

【図5】本発明の実施の形態1における昇圧装置の動作説明図(その3)

【図6】本発明の実施の形態1における昇圧装置の動作説明図(その4)

【図7】本発明の実施の形態1における昇圧装置の動作説明図(その5)

【図8】本発明の実施の形態1における昇圧装置の動作説明図(その6)

【図9】本発明の実施の形態1における昇圧装置の動作説明図(その7)

【図10】本発明の実施の形態1における昇圧装置の動作説明図(その8)

【図11】本発明の実施の形態2における昇圧装置の構成を示す回路図

【図12】本発明の実施の形態2における昇圧装置の動作を示す信号波形図

【図13】本発明の実施の形態2における昇圧装置の動作説明図(その1)

【図14】本発明の実施の形態2における昇圧装置の動作説明図(その2)

【図15】本発明の実施の形態2における昇圧装置の動作説明図(その3)

【図16】本発明の実施の形態2における昇圧装置の動作説明図(その4)

【図17】本発明の実施の形態2における昇圧装置の動作説明図(その5)

【図18】本発明の実施の形態2における昇圧装置の動作説明図(その6)

【図19】本発明の実施の形態2における昇圧装置の動作説明図(その7)

【図20】本発明の実施の形態2における昇圧装置の動作説明図(その8)

【図21】本発明の実施の形態2における昇圧装置の動作説明図(その9)

【図22】本発明の実施の形態2における昇圧装置の動作説明図(その10)

【図23】本発明の実施の形態2における昇圧装置の動作説明図(その11)

【図24】本発明の実施の形態2における昇圧装置の動作説明図(その12)

【図25】本発明の実施の形態3における降圧装置の構成を示す回路図

【図26】本発明の実施の形態3における降圧装置の動作を示す信号波形図

【図27】本発明の実施の形態3における降圧装置の動作説明図(その1)

【図28】本発明の実施の形態3における降圧装置の動作説明図(その2)

【図29】本発明の実施の形態3における降圧装置の動作説明図(その3)

【図30】本発明の実施の形態3における降圧装置の動作説明図(その4)

【図31】本発明の実施の形態3における降圧装置の動作説明図(その5)

【図32】本発明の実施の形態3における降圧装置の動作説明図(その6)

【図33】本発明の実施の形態3における降圧装置の動作説明図(その7)

【図34】本発明の実施の形態3における降圧装置の動作説明図(その8)

【図35】本発明の実施の形態3における降圧装置の動作説明図(その9)

【図36】本発明の実施の形態3における降圧装置の動作説明図(その10)

【図37】本発明の実施の形態3における降圧装置の動作説明図(その11)

【図38】本発明の実施の形態3における降圧装置の動作説明図(その12)

【図39】本発明の実施の形態4における昇圧装置の構成を示す回路図

【図40】本発明の実施の形態4における昇圧装置の動作を示す信号波形図

【図41】本発明の実施の形態4における昇圧装置の動作説明図(その1)

【図42】本発明の実施の形態4における昇圧装置の動作説明図(その2)

【図43】本発明の実施の形態4における昇圧装置の動作説明図(その3)

【図44】本発明の実施の形態4における昇圧装置の動作説明図(その4)

【図45】本発明の実施の形態5における昇圧装置の構成を示す回路図

【図46】本発明の実施の形態5における昇圧装置の動作を示す信号波形図

【図47】本発明の実施の形態5における昇圧装置の動作説明図(その1)

【図48】本発明の実施の形態5における昇圧装置の動作説明図(その2)

【図49】本発明の実施の形態5における昇圧装置の動作説明図(その3)

【図50】本発明の実施の形態5における昇圧装置の動作説明図(その4)

【図51】本発明の実施の形態5における昇圧装置の動作説明図(その5)

【図52】本発明の実施の形態5における昇圧装置の動作説明図(その6)

【図53】本発明の実施の形態5における昇圧装置の動作説明図(その7)

【図54】本発明の実施の形態5における昇圧装置の動作説明図(その8)

【図55】従来の技術における昇圧装置の構成を示す回路図

【図56】従来の技術における昇圧装置の動作を示す信号波形図

【図57】従来の技術における昇圧装置の動作説明図(その1)

【図58】従来の技術における昇圧装置の動作説明図(その2)

【図59】従来の技術における昇圧装置の動作説明図(その3)

【図60】従来の技術における昇圧装置の動作説明図(その4)

【符号の説明】

【0177】

10,20,30,40,50,60 制御部

A1 第1の昇圧回路部

A2 第2の昇圧回路部

A3 第3の昇圧回路部

B1 第1の降圧回路部

B2 第2の降圧回路部

B3 第3の降圧回路部

C0 昇圧電圧蓄積用の容量素子(降圧電圧蓄積用の容量素子)

C01 第1の昇圧電圧蓄積用の容量素子(降圧電圧蓄積用の容量素子)

C02 第2の昇圧電圧蓄積用の容量素子(降圧電圧蓄積用の容量素子)

C1,C2 基準電源電圧蓄積用の容量素子

R1 抵抗

S11〜S14 スイッチ素子

S21〜S24 スイッチ素子

S31〜S34 スイッチ素子

S41 スイッチ素子

Vci 基準電源

VSS グランド

Vout,Vout1,Vout2 電圧出力端子

【技術分野】

【0001】

本発明は昇圧装置および降圧装置にかかわり、特には基準電源でのノイズ低減の技術に関するものである。

【背景技術】

【0002】

例えば電源Vccよりも低い基準電源Vciの2倍昇圧を行う昇圧回路の場合、通常、4つのスイッチ素子と2つの容量素子で構成され、所与のタイミングの制御信号に基づいたチャージ・ポンプ動作によって所望の出力電圧(Vout)を生成する。出力電圧(Vout)の微調整は、基準電源Vciの調整で行う。それは、昇圧回路自体の出力が基準電源の整数倍のみに限定されるからである。そのため、基準電源Vciは、LSI内部で電源Vccから生成させることが多い。各スイッチ素子がスイッチング動作を行う際に、反転論理の2つのスイッチ素子が同時にオンになり貫通電流が流れてしまうのを防ぐ必要がある。そこで、チャージ・ポンプ動作を行うための制御信号としては、意図的にスイッチング動作時にすべてのスイッチ素子がオフとなるデッドタイム期間を設ける。

【0003】

基準電源Vciの2倍の電圧(Vout)を作成する従来の昇圧回路の構成を図55に示す。

【0004】

基準電源VciとグランドVSSとの間にスイッチ素子S11とスイッチ素子S12の直列回路が接続されている。基準電源Vciと両スイッチ素子S11,S12の接続点との間にスイッチ素子S13と基準電源電圧蓄積用の容量素子C1の直列回路が接続されている。スイッチ素子S13と容量素子C1の接続点とグランドVSSとの間にスイッチ素子S14と昇圧電圧蓄積用の容量素子C0の直列回路が接続されている。容量素子C0は、基準電源Vciの2倍の電圧(Vout)を保持し、出力するものである。Voutは電圧出力端子を表す。基準電源Vciは平滑容量を持たない電源となっている。

【0005】

図56は動作を示すタイミングチャートであり、制御信号A,B,C,Dはそれぞれスイッチ素子S11,S12,S13,S14をオン・オフ制御するものである。ハッチングを施した領域は、デッドタイム期間の状態(DT)を表している。これらの制御信号A,B,C,Dは制御部60によって生成され、それぞれスイッチ素子S11,S12,S13,S14に供給されるようになっている。スイッチ素子はトランジスタ等で構成されている。

【0006】

図55に示す昇圧回路の動作について、図57〜図60を参照しながら以下に説明する。

【0007】

まず、図57のように、スイッチ素子S12とスイッチ素子S13をオンさせ、スイッチ素子S11とスイッチ素子S14をオフさせる。この状態で基準電源電圧蓄積用の容量素子C1には基準電源Vciの電圧が蓄えられる。この期間は、基準電源Vciへ負荷がかかっている状態である。

【0008】

次に、図58のように、スイッチ素子S11とスイッチ素子S14をオフさせたままで、スイッチ素子S12とスイッチ素子S13もオフさせる。この状態は前期デッドタイム期間の状態である。この期間は、基準電源Vciへ負荷がかかっていない状態である。

【0009】

次に、図59のように、スイッチ素子S12とスイッチ素子S13がオフしたままの状態で、スイッチ素子S11とスイッチ素子S14がオンし、基準電源電圧蓄積用の容量素子C1と昇圧電圧蓄積用の容量素子C0が接続され、容量素子C1に蓄えられた電荷が容量素子C0に持ち上げられる。この期間は、基準電源Vciへ負荷がかかっている状態である。

【0010】

次に、図60のように、スイッチ素子S12とスイッチ素子S13をオフさせたままで、スイッチ素子S11とスイッチ素子S14もオフさせる。この状態は後期デッドタイム期間の状態である。この期間は、基準電源Vciへ負荷がかかっていない状態である。

【0011】

図57〜図60の動作を繰り返すことにより、容量素子C0に基準電源Vciの2倍の電圧(Vout)が生成される。

【特許文献1】特開平6−327236号公報(第2−4頁、第3−6図)

【特許文献2】特開平11−299227号公報(第9−10頁、第12−15図)

【発明の開示】

【発明が解決しようとする課題】

【0012】

図55に示す従来の昇圧回路は、動作期間とデッドタイム期間を繰り返している。すなわち、基準電源Vciへの負荷電流がある場合とない場合を交互に繰り返している。そのため、平滑容量を持たない基準電源Vciは、負荷のかかっていないデッドタイム期間に跳ね上がり、ノイズを発生させてしまう。そして、そのノイズが別回路へ回り込み、悪影響を与える可能性がある。降圧回路についても同様の課題がある。

【0013】

本発明は、上記従来の問題点を解決するもので、基準電源Vciにおけるクロック同期のノイズを低減させ、別回路への悪影響をなくすことが可能な昇圧装置、降圧装置を提供することを目的とする。

【課題を解決するための手段】

【0014】

本発明による昇圧装置は、

電圧出力端子に接続された昇圧電圧蓄積用の容量素子に対して第1の昇圧回路部と第2の昇圧回路部とが並列に接続され、

前記第1の昇圧回路部および第2の昇圧回路部はそれぞれ、平滑容量を持たない基準電源と、基準電源電圧蓄積用の容量素子と、複数のスイッチ素子を有し、スイッチング制御により、前記基準電源電圧蓄積用の容量素子に対して前記基準電源電圧による電荷蓄積動作を行ったのち、前記基準電源電圧蓄積用の容量素子に逆方向に前記基準電源電圧を印加して前記昇圧電圧蓄積用の容量素子に対してポンプ動作を行って前記電圧出力端子に昇圧電圧を供給するように構成され、さらに、前記電荷蓄積動作の期間と前記ポンプ動作の期間との間および前記ポンプ動作の期間と前記電荷蓄積動作の期間との間にそれぞれ前記基準電源との接続を断つデッドタイム期間を有するように構成され、

前記両昇圧回路部における前記複数のスイッチ素子をオン・オフ制御するもので、前記両昇圧回路部のうちいずれか一方の昇圧回路部のデッドタイム期間において他方の昇圧回路部では前記電荷蓄積動作または前記ポンプ動作を行うという制御を、前記第1の昇圧回路部と前記第2の昇圧回路部とにおいて交互かつサイクリックに行う制御部を備えたものである。

【0015】

この構成において、第1の昇圧回路部の動作と第2の昇圧回路部の動作とは、タイミングを異にして、互いに同様の動作を行う。すなわち、いずれの昇圧回路部も、制御部からの制御信号によりスイッチ素子のスイッチング制御が行われて、まず基準電源が基準電源電圧蓄積用の容量素子に接続され、この基準電源電圧蓄積用の容量素子に対して基準電源電圧による電荷蓄積動作が行われる。次いで、貫通電流防止のデッドタイム期間をおき、次いで、基準電源電圧蓄積用の容量素子に逆方向に基準電源電圧を印加することにより昇圧電圧蓄積用の容量素子に対してポンプ動作を行い、電圧出力端子に昇圧電圧を供給する。さらに、貫通電流防止のデッドタイム期間をおき、次いで再び、基準電源電圧蓄積用の容量素子に対して基準電源電圧による電荷蓄積動作へと進む。制御部は、第1の昇圧回路部における上記のような動作と第2の昇圧回路部における同様の動作との間に、タイミングのずらしを与える。すなわち、第1の昇圧回路部では、第2の昇圧回路部のデッドタイム期間において電荷蓄積動作を行い、また次の第2の昇圧回路部のデッドタイム期間においてポンプ動作を行う。また、第2の昇圧回路部では、第1の昇圧回路部のデッドタイム期間において電荷蓄積動作を行い、また、次の第1の昇圧回路部のデッドタイム期間においてポンプ動作を行う。

【0016】

まとめると、一方の昇圧回路部での貫通電流防止のためのデッドタイム期間においては、他方の昇圧回路部で基準電源が電荷蓄積動作またはポンプ動作のために基準電源電圧蓄積用の容量素子に接続されており、基準電源が有負荷状態に保たれるため、基準電源が平滑容量を持たないものであっても、デッドタイム期間にノイズが発生することを防止することができる。

【0017】

上記構成において、昇圧回路部を3つ以上有する状態に構成すれば、次のような展開となる。

【0018】

本発明による昇圧装置は、

電圧出力端子に対して3つ以上の昇圧回路部が並列に接続され、

前記昇圧回路部はそれぞれ、平滑容量を持たない基準電源と、基準電源電圧蓄積用の容量素子と、複数のスイッチ素子を有し、スイッチング制御により、前記基準電源電圧蓄積用の容量素子に対して前記基準電源電圧による電荷蓄積動作を行ったのち、前記基準電源電圧蓄積用の容量素子に逆方向に前記基準電源電圧を印加してポンプ動作を行って前記電圧出力端子に昇圧電圧を供給するように構成され、さらに、前記電荷蓄積動作の期間と前記ポンプ動作の期間との間および前記ポンプ動作の期間と前記電荷蓄積動作の期間との間にそれぞれ前記基準電源との接続を断つデッドタイム期間を有するように構成され、

前記複数の昇圧回路部それぞれにおける前記複数のスイッチ素子をオン・オフ制御するもので、前記複数の昇圧回路部のうちいずれか1つの昇圧回路部のデッドタイム期間において他の昇圧回路部では前記電荷蓄積動作または前記ポンプ動作を行うという制御を、前記複数の昇圧回路部において順次かつサイクリックに行う制御部を備えたものである。なお、この場合、昇圧電圧蓄積用の容量素子は必ずしも必要としない。

【0019】

この構成において、各昇圧回路部の機能は上記と同様である。制御部は、昇圧回路部の上記のような動作について複数の昇圧回路部どうし間でタイミングのずらしを与える。すなわち、第3の昇圧回路部のデッドタイム期間において、第1の昇圧回路部では電荷蓄積動作を行い、第2の昇圧回路部ではポンプ動作を行う。また、次の第3の昇圧回路部のデッドタイム期間において、第1の昇圧回路部ではポンプ動作を行い、第2の昇圧回路部では電荷蓄積動作を行う。第2の昇圧回路部のデッドタイム期間において、第1の昇圧回路部では電荷蓄積動作を行い、第3の昇圧回路部ではポンプ動作を行う。また、次の第2の昇圧回路部のデッドタイム期間において、第1の昇圧回路部ではポンプ動作を行い、第3の昇圧回路部では電荷蓄積動作を行う。第1の昇圧回路部のデッドタイム期間において、第2の昇圧回路部では電荷蓄積動作を行い、第3の昇圧回路部ではポンプ動作を行う。また、次の第1の昇圧回路部のデッドタイム期間において、第2の昇圧回路部ではポンプ動作を行い、第3の昇圧回路部では電荷蓄積動作を行う。

【0020】

まとめると、1つの昇圧回路部での貫通電流防止のためのデッドタイム期間においては、他の昇圧回路部では基準電源が電荷蓄積動作またはポンプ動作のために基準電源電圧蓄積用の容量素子に接続されており、基準電源が有負荷状態に保たれるため、基準電源が平滑容量を持たないものであっても、デッドタイム期間にノイズが発生することを防止することができる。

【0021】

前述の昇圧回路部が2つのみの構成では、一方の昇圧回路部のデッドタイム期間で他方の昇圧回路部が電荷蓄積動作を行う期間とポンプ動作を行う期間とに分かれることから、ポンプ動作がなく電荷蓄積動作のみの期間があり、この期間では、電圧出力端子の降圧を避ける必要から、昇圧電圧蓄積用の容量素子を必要としている。しかし、昇圧回路部を3つ以上有する本構成の場合には、いずれの期間においても必ず電圧出力端子に対するポンプ動作があり、電圧出力端子に対して常に少なくともいずれか1つの昇圧回路部から電荷供給が行われる状態が保たれるため、昇圧電圧蓄積用の容量素子は必ずしも必要ではない。この昇圧電圧蓄積用の容量素子は省略することが可能である。もっとも、昇圧電圧蓄積用の容量素子を有する構成とすれば、この容量素子にはポンプ動作により常に少なくとも1つの昇圧回路部から電荷供給が行われる状態になるため、昇圧電圧のリップルを低減させ、電流能力を上げるという効果が得られる。

【0022】

上記のように昇圧回路部を複数並列接続することに代えて、負荷抵抗等の負荷電流源に置き換えた構成もあり、次のように展開される。

【0023】

本発明による昇圧装置は、

電圧出力端子に接続された昇圧電圧蓄積用の容量素子に昇圧回路部が接続され、

前記昇圧回路部は、平滑容量を持たない基準電源と、基準電源電圧蓄積用の容量素子と、複数のスイッチ素子を有し、スイッチング制御により、前記基準電源電圧蓄積用の容量素子に対して前記基準電源電圧による電荷蓄積動作を行ったのち、前記基準電源電圧蓄積用の容量素子に逆方向に前記基準電源電圧を印加して前記昇圧電圧蓄積用の容量素子に対してポンプ動作を行って前記電圧出力端子に昇圧電圧を供給するように構成され、さらに、前記電荷蓄積動作の期間と前記ポンプ動作の期間との間および前記ポンプ動作の期間と前記電荷蓄積動作の期間との間にそれぞれ前記基準電源との接続を断つデッドタイム期間を有するように構成され、

前記基準電源にスイッチ素子を介して接続された負荷電流源と、

前記昇圧回路部における前記複数のスイッチ素子および前記負荷電流源のスイッチ素子をオン・オフ制御するもので、前記昇圧回路部のデッドタイム期間において前記負荷電流源のスイッチ素子を導通させる制御部とを備えたものである。

【0024】

この構成において、昇圧回路部での貫通電流防止のためのデッドタイム期間においては、制御部のスイッチング制御により負荷電流源を基準電源に接続させ、基準電源が有負荷状態に保たれるため、基準電源が平滑容量を持たないものであっても、デッドタイム期間にノイズが発生することを防止することができる。

【0025】

上記の昇圧装置についての技術を降圧装置においても次のように展開することが可能である。

【0026】

本発明による降圧装置は、

電圧出力端子に対して3つ以上の降圧回路部が並列に接続され、

前記降圧回路部はそれぞれ、平滑容量を持たない基準電源と、基準電源電圧蓄積用の容量素子と、複数のスイッチ素子を有し、スイッチング制御により、前記基準電源電圧蓄積用の容量素子に対して前記基準電源電圧による電荷蓄積動作を行ったのち、前記基準電源電圧蓄積用の容量素子に同方向に前記基準電源電圧を印加してポンプ動作を行って前記電圧出力端子に降圧電圧を供給するように構成され、さらに、前記電荷蓄積動作の期間と前記ポンプ動作の期間との間および前記ポンプ動作の期間と前記電荷蓄積動作の期間との間にそれぞれ前記基準電源との接続を断つデッドタイム期間を有するように構成され、

前記複数の降圧回路部それぞれにおける前記複数のスイッチ素子をオン・オフ制御するもので、前記複数の降圧回路部のうちいずれか1つの降圧回路部のデッドタイム期間において他の降圧回路部では前記電荷蓄積動作または前記ポンプ動作を行うという制御を、前記複数の降圧回路部において順次かつサイクリックに行う制御部を備えたものである。なお、この場合、降圧電圧蓄積用の容量素子は必ずしも必要としない。

【0027】

この構成において複数の降圧回路部は、タイミングを異にして、互いに同様の動作を行う。すなわち、いずれの降圧回路部も、制御部からの制御信号によりスイッチ素子のスイッチング制御が行われて、まず基準電源が基準電源電圧蓄積用の容量素子に接続され、この基準電源電圧蓄積用の容量素子に対して基準電源電圧による電荷蓄積動作が行われる。次いで、貫通電流防止のデッドタイム期間をおき、次いで、基準電源電圧蓄積用の容量素子に同方向に基準電源電圧を印加することにより降圧のポンプ動作を行い、電圧出力端子に降圧電圧を供給する。さらに、貫通電流防止のデッドタイム期間をおき、次いで再び、基準電源電圧蓄積用の容量素子に対して基準電源電圧による電荷蓄積動作へと進む。制御部は、第3の降圧回路部のデッドタイム期間において、第1の降圧回路部では電荷蓄積動作を行い、第2の降圧回路部では降圧のポンプ動作を行う。また、次の第3の降圧回路部のデッドタイム期間において、第1の降圧回路部では降圧のポンプ動作を行い、第2の降圧回路部では電荷蓄積動作を行う。第2の降圧回路部のデッドタイム期間において、第1の降圧回路部では電荷蓄積動作を行い、第3の降圧回路部では降圧のポンプ動作を行う。また、次の第2の降圧回路部のデッドタイム期間において、第1の降圧回路部では降圧のポンプ動作を行い、第3の降圧回路部では電荷蓄積動作を行う。第1の降圧回路部のデッドタイム期間において、第2の降圧回路部では電荷蓄積動作を行い、第3の降圧回路部では降圧のポンプ動作を行う。また、次の第1の降圧回路部のデッドタイム期間において、第2の降圧回路部では降圧のポンプ動作を行い、第3の降圧回路部では電荷蓄積動作を行う。

【0028】

まとめると、1つの降圧回路部での貫通電流防止のためのデッドタイム期間においては、他の降圧回路部では基準電源が電荷蓄積動作または降圧のポンプ動作のために基準電源電圧蓄積用の容量素子に接続されており、基準電源が有負荷状態に保たれるため、基準電源が平滑容量を持たないものであっても、デッドタイム期間にノイズが発生することを防止することができる。

【0029】

また、降圧回路部を3つ以上有するので、いずれの期間においても必ず電圧出力端子に対する降圧のポンプ動作があり、電圧出力端子に対して常に少なくともいずれか1つの降圧回路部から電荷供給が行われる状態が保たれるため、電圧出力端子には降圧電圧蓄積用の容量素子は必ずしも必要ではない。この降圧電圧蓄積用の容量素子は省略することが可能である。もっとも、降圧電圧蓄積用の容量素子を有する構成とすれば、この容量素子には降圧のポンプ動作により常に少なくとも1つの降圧回路部から電荷供給が行われる状態になるため、降圧電圧のリップルを低減させ、電流能力を上げるという効果が得られる。

【0030】

上記の昇圧装置についての技術は同一の基準電源から2つの出力電圧を作成する昇圧装置においても次のように展開することが可能である。

【0031】

第1の電圧出力端子に接続された第1の昇圧電圧蓄積用の容量素子に対して第1の昇圧回路部が接続され、第2の電圧出力端子に接続された第2の昇圧電圧蓄積用の容量素子に対して第2の昇圧回路部が接続され、

前記第1の昇圧回路部および前記第2の昇圧回路部はそれぞれ、平滑容量を持たない基準電源と、基準電源電圧蓄積用の容量素子と、複数のスイッチ素子を有し、スイッチング制御により、前記基準電源電圧蓄積用の容量素子に対して前記基準電源電圧による電荷蓄積動作を行ったのち、前記基準電源電圧蓄積用の容量素子に逆方向に前記基準電源電圧を印加してそれぞれ前記第1の昇圧電圧蓄積用の容量素子と前記第2の昇圧電圧蓄積用の容量素子に対してポンプ動作を行って前記第1の電圧出力端子と前記第2の電圧出力端子に昇圧電圧を供給するように構成され、さらに、前記電荷蓄積動作の期間と前記ポンプ動作の期間との間および前記ポンプ動作の期間と前記電荷蓄積動作の期間との間にそれぞれ前記基準電源との接続を断つデッドタイム期間を有するように構成され、

前記両昇圧回路部における前記複数のスイッチ素子をオン・オフ制御するもので、前記両昇圧回路部のうちいずれか一方の昇圧回路部のデッドタイム期間において他方の昇圧回路部では前記電荷蓄積動作または前記ポンプ動作を行うという制御を、前記第1の昇圧回路部と前記第2の昇圧回路部とにおいて交互かつサイクリックに行う制御部を備えたものである。

【0032】

この構成において、第1の昇圧回路部の動作と第2の昇圧回路部の動作とは、タイミングを異にして、互いに同様の動作を行う。すなわち、いずれの昇圧回路部も、制御部からの制御信号によりスイッチ素子のスイッチング制御が行われて、まず基準電源が基準電源電圧蓄積用の容量素子に接続され、この基準電源電圧蓄積用の容量素子に対して基準電源電圧による電荷蓄積動作が行われる。次いで、貫通電流防止のデッドタイム期間をおき、次いで、基準電源電圧蓄積用の容量素子に逆方向に基準電源電圧を印加することにより昇圧電圧蓄積用の容量素子に対してポンプ動作を行い、第1の電圧出力端子と第2の電圧出力端子に昇圧電圧を供給する。さらに、貫通電流防止のデッドタイム期間をおき、次いで再び、基準電源電圧蓄積用の容量素子に対して基準電源電圧による電荷蓄積動作へと進む。制御部は、第1の昇圧回路部における上記のような動作と第2の昇圧回路部における同様の動作との間に、タイミングのずらしを与える。すなわち、第1の昇圧回路部では、第2の昇圧回路部のデッドタイム期間において電荷蓄積動作を行い、また次の第2の昇圧回路部のデッドタイム期間においてポンプ動作を行う。また、第2の昇圧回路部では、第1の昇圧回路部のデッドタイム期間において電荷蓄積動作を行い、また、次の第1の昇圧回路部のデッドタイム期間においてポンプ動作を行う。

【0033】

まとめると、一方の昇圧回路部での貫通電流防止のためのデッドタイム期間においては、他方の昇圧回路部で基準電源が電荷蓄積動作またはポンプ動作のために基準電源電圧蓄積用の容量素子に接続されており、基準電源が有負荷状態に保たれるため、基準電源が平滑容量を持たないものであっても、デッドタイム期間にノイズが発生することを防止することができる。

【発明の効果】

【0034】

本発明の昇圧装置または降圧装置によれば、貫通電流防止のためのデッドタイム期間においては、他の昇圧回路部または降圧回路部で基準電源が電荷蓄積動作またはポンプ動作のために基準電源電圧蓄積用の容量素子に接続されており、基準電源が有負荷状態に保たれるため、基準電源が平滑容量を持たないものであっても、デッドタイム期間にノイズが発生することを防止することができる。この結果、別回路への悪影響をなくし、安定動作が可能となる。

【発明を実施するための最良の形態】

【0035】

以下、本発明にかかわる昇圧装置、降圧装置の実施の形態を図面に基づいて詳細に説明する。

【0036】

(実施の形態1)

図1は、本発明の実施の形態1における昇圧装置の構成を示す回路図である。図1に示すように、電圧出力端子Voutに昇圧電圧蓄積用の容量素子C0が接続され、この昇圧電圧蓄積用の容量素子C0に対して第1の昇圧回路部A1と第2の昇圧回路部A2とが並列に接続されている。昇圧電圧蓄積用の容量素子C0は、基準電源Vciの2倍の電圧(Vout)を保持し、出力するものである。

【0037】

第1の昇圧回路部A1において、基準電源VciとグランドVSSとの間にスイッチ素子S11とスイッチ素子S12の直列回路が接続されている。基準電源Vciと両スイッチ素子S11,S12の接続点との間にスイッチ素子S13と基準電源電圧蓄積用の容量素子C1の直列回路が接続されている。スイッチ素子S13と容量素子C1の接続点とグランドVSSとの間にスイッチ素子S14と容量素子C0の直列回路が接続されている。スイッチ素子S11,S12,S13,S14と基準電源電圧蓄積用の容量素子C1で第1の昇圧回路部A1を形成している。

【0038】

第2の昇圧回路部A2において、基準電源VciとグランドVSSとの間にスイッチ素子S21とスイッチ素子S22の直列回路が接続されている。基準電源Vciと両スイッチ素子S21,S22の接続点との間にスイッチ素子S23と基準電源電圧蓄積用の容量素子C2の直列回路が接続されている。スイッチ素子S23と容量素子C2の接続点とグランドVSSとの間にスイッチ素子S24と容量素子C0の直列回路が接続されている。スイッチ素子S21,S22,S23,S24と基準電源電圧蓄積用の容量素子C2で第2の昇圧回路部A2を形成している。

【0039】

昇圧電圧蓄積用の容量素子C0は、一方でグランドVSSに接続され、もう一方はスイッチ素子S14とスイッチ素子S24に接続されている。結果的にはこの箇所に基準電源Vciの2倍の電圧(Vout)が出力される。

【0040】

10は、第1の昇圧回路部A1におけるスイッチ素子S11,S12,S13,S14をオン・オフ制御する制御信号A,B,C,Dと第2の昇圧回路部A2におけるスイッチ素子S21,S22,S23,S24をオン・オフ制御する制御信号E,F,G,Hを生成出力する制御部である。この制御部10は、第1の昇圧回路部A1および第2の昇圧回路部A2のうちいずれか一方の昇圧回路部のデッドタイム期間において他方の昇圧回路部では電荷蓄積動作またはポンプ動作を行うという制御を、両昇圧回路部A1,A2間で交互かつサイクリックに行うように構成されている。スイッチ素子はトランジスタ等で構成されている。基準電源Vciは平滑容量を持たない電源となっている。

【0041】

図2は本実施の形態の昇圧装置の動作を示すタイミングチャートである。図2において、第1の昇圧回路部A1におけるスイッチ素子S11,S12,S13,S14をオン・オフ制御する制御信号A,B,C,Dは、昇圧回路用の第1のクロックCK1に基づいて生成され、第2の昇圧回路部A2におけるスイッチ素子S21,S22,S23,S24をオン・オフ制御する制御信号E,F,G,Hは、昇圧回路用の第2のクロックCK2に基づいて生成される。

【0042】

また、図2において、ハッチングを施した領域は、デッドタイム期間の状態(DT)を表している。

【0043】

次に、上記のように構成された本実施の形態の昇圧装置の動作を、図3〜図10を参照しながら説明する。

【0044】

まず、図3のように、第1の昇圧回路部A1におけるスイッチ素子S12とスイッチ素子S13と、第2の昇圧回路部A2におけるスイッチ素子S21とスイッチ素子S24をオンさせ、スイッチ素子S11とスイッチ素子S14とスイッチ素子S22とスイッチ素子S23をオフさせる。この期間で、第1の昇圧回路部A1における基準電源電圧蓄積用の容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2における基準電源電圧蓄積用の容量素子C2は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)である。この期間は、基準電源Vciへ負荷が2箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔CH,UP〕である。

【0045】

次に、図4のように、図3の状態から第2の昇圧回路部A2におけるスイッチ素子S21とスイッチ素子S24をオフさせる。この期間で、第1の昇圧回路部A1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。第1の昇圧回路部A1は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔CH,DT〕である。

【0046】

次に、図5のように、図4の状態から第2の昇圧回路部A2におけるスイッチ素子S22とスイッチ素子S23をオンさせる。この期間で、第1の昇圧回路部A1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)である。この期間は、基準電源Vciへ負荷が2箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔CH,CH〕である。

【0047】

次に、図6のように、図5の状態から第1の昇圧回路部A1におけるスイッチ素子S12とスイッチ素子S13をオフさせる。この期間で、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。第2の昇圧回路部A2は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔DT,CH〕である。

【0048】

次に、図7のように、図6の状態から第1の昇圧回路部A1におけるスイッチ素子S11とスイッチ素子S14をオンさせ、基準電源電圧蓄積用の容量素子C1に対して基準電源Vciを逆方向に印加する。この期間で、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)である。この期間は、基準電源Vciへ負荷が2箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔UP,CH〕である。

【0049】

次に、図8のように、図7の状態から第2の昇圧回路部A2におけるスイッチ素子S22とスイッチ素子S23をオフさせる。この期間で、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。第1の昇圧回路部A1は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔UP,DT〕である。

【0050】

次に、図9のように、図8の状態から第2の昇圧回路部A2におけるスイッチ素子S21とスイッチ素子S24をオンさせ、基準電源電圧蓄積用の容量素子C2に対して基準電源Vciを逆方向に印加する。この期間で、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第2の昇圧回路部A2における容量素子C2は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)である。この期間は、基準電源Vciへ負荷が2箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔UP,UP〕である。

【0051】

次に、図10のように、図9の状態から第1の昇圧回路部A1におけるスイッチ素子S11とスイッチ素子S14をオフさせる。この期間で、第2の昇圧回路部A2における容量素子C2は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。第2の昇圧回路部A2は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態である。総合状態は、〔A1,A2〕=〔DT,UP〕である。

【0052】

図3〜図10の動作を繰り返すことにより、昇圧電圧蓄積用の容量素子C0に基準電源Vciの2倍の電圧(Vout)が生成される。

【0053】

図2において、図4相当の期間では、第2の昇圧回路部A2における4つのスイッチ素子S21,S22,S23,S24がすべてオフとなっていて、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。このとき、第1の昇圧回路部A1において、スイッチ素子S12,S13がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。

【0054】

また、図2において、図6相当の期間では、第1の昇圧回路部A1における4つのスイッチ素子S11,S12,S13,S14がすべてオフとなっていて、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。このとき、第2の昇圧回路部A2において、スイッチ素子S22,S23がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。

【0055】

また、図2において、図8相当の期間では、第2の昇圧回路部A2における4つのスイッチ素子S21,S22,S23,S24がすべてオフとなっていて、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。このとき、第1の昇圧回路部A1において、スイッチ素子S11,S14がオンであることから、蓄えている電荷を昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)となっている。

【0056】

また、図2において、図10相当の期間では、第1の昇圧回路部A1における4つのスイッチ素子S11,S12,S13,S14がすべてオフとなっていて、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。このとき、第2の昇圧回路部A2において、スイッチ素子S21,S24がオンであることから、蓄えている電荷を昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)となっている。

【0057】

以上の経過をまとめると、

図3……〔A1,A2〕=〔CH,UP〕

図4……〔A1,A2〕=〔CH,DT〕

図5……〔A1,A2〕=〔CH,CH〕

図6……〔A1,A2〕=〔DT,CH〕

図7……〔A1,A2〕=〔UP,CH〕

図8……〔A1,A2〕=〔UP,DT〕

図9……〔A1,A2〕=〔UP,UP〕

図10…〔A1,A2〕=〔DT,UP〕

となる。第1の昇圧回路部A1における動作履歴をみると、CH→CH→CH→DT→UP→UP→UP→DTのサイクリック動作となっている。また、第2の昇圧回路部A2における動作履歴をみると、UP→DT→CH→CH→CH→DT→UP→UPのサイクリック動作となっている。両昇圧回路部A1,A2の動作は、タイミングこそ異なるが、同一パターンのサイクリック動作となっている。

【0058】

第2の昇圧回路部A2がデッドタイム期間の状態(DT)であるときは(図4または図8)、第1の昇圧回路部A1は基準電源Vciの電圧を蓄える状態(CH)または蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)となっている。

【0059】

また、第1の昇圧回路部A1がデッドタイム期間の状態(DT)であるときは(図6または図10)、第2の昇圧回路部A2は基準電源Vciの電圧を蓄える状態(CH)または蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)となっている。

【0060】

まとめると、

〔A1,A2〕=〔有負荷,DT〕

〔A1,A2〕=〔DT,有負荷〕

の原則が保たれている。

【0061】

すなわち、いずれの昇圧回路部がデッドタイム期間の状態(DT)であっても、他方の昇圧回路部において、必ず、平滑容量を持たない基準電源Vciに負荷がかかっている状態を維持させることができている。これで、従来の技術の場合の、〔DT,無負荷〕の状態を脱却でき、〔DT,無負荷〕の状態に起因するノイズの発生を抑制することができる。

【0062】

まとめると、本実施の形態によれば、基準電源Vciには常に負荷がかかっている状態で、昇圧動作が可能となり、基準電源Vciのノイズの低減が可能となる。

【0063】

(実施の形態2)

上記においては、昇圧回路部を2つ並列接続した昇圧装置について説明したが、3つ以上接続した場合の昇圧装置でも、上記同様の効果が得られる。これが本発明の実施の形態2である。以下に、本発明の実施の形態2における昇圧装置について説明する。

【0064】

図11は、本発明の実施の形態2における昇圧装置の構成を示す回路図である。図11に示すように、電圧出力端子Voutに昇圧電圧蓄積用の容量素子C0が接続され、この昇圧電圧蓄積用の容量素子C0に対して第1の昇圧回路部A1と第2の昇圧回路部A2と第3の昇圧回路部A3が並列に接続されている。昇圧電圧蓄積用の容量素子C0は、基準電源Vciの2倍の電圧(Vout)を保持し、出力するものである。

【0065】

第1の昇圧回路部A1および第2の昇圧回路部A2については、実施の形態1の場合と同様である。

【0066】

第3の昇圧回路部A3において、基準電源VciとグランドVSSとの間にスイッチ素子S31とスイッチ素子S32の直列回路が接続されている。基準電源Vciと両スイッチ素子S31,S32の接続点との間にスイッチ素子S33と基準電源電圧蓄積用の容量素子C3の直列回路が接続されている。スイッチ素子S33と容量素子C3の接続点とグランドVSSとの間にスイッチ素子S34と容量素子C0の直列回路が接続されている。スイッチ素子S31,S32,S33,S34と基準電源電圧蓄積用の容量素子C3で第3の昇圧回路部A3を形成している。

【0067】

昇圧電圧蓄積用の容量素子C0は、一方でグランドVSSに接続され、もう一方はスイッチ素子S14とスイッチ素子S24とスイッチ素子S34に接続されている。結果的にはこの箇所に基準電源Vciの2倍の電圧(Vout)が出力される。

【0068】

20は、第1の昇圧回路部A1におけるスイッチ素子S11,S12,S13,S14をオン・オフ制御する制御信号A,B,C,Dと第2の昇圧回路部A2におけるスイッチ素子S21,S22,S23,S24をオン・オフ制御する制御信号E,F,G,Hと第3の昇圧回路部A3におけるスイッチ素子S31,S32,S33,S34をオン・オフ制御する制御信号I,J,K,Lを生成出力する制御部である。この制御部20は、第1の昇圧回路部A1、第2の昇圧回路部A2および第3の昇圧回路部A3のうちいずれか1つの昇圧回路部のデッドタイム期間において他の昇圧回路部では電荷蓄積動作またはポンプ動作を行うという制御を、前記3つの昇圧回路部A1,A2,A3において順次かつサイクリックに行うように構成されている。基準電源Vciは平滑容量を持たない電源となっている。

【0069】

図12は本実施の形態の昇圧装置の動作を示すタイミングチャートである。図12において、第1の昇圧回路部A1におけるスイッチ素子S11,S12,S13,S14をオン・オフ制御する制御信号A,B,C,Dは、昇圧回路用の第1のクロックCK1に基づいて生成され、第2の昇圧回路部A2におけるスイッチ素子S21,S22,S23,S24をオン・オフ制御する制御信号E,F,G,Hは、昇圧回路用の第2のクロックCK2に基づいて生成され、第3の昇圧回路部A3におけるスイッチ素子S31,S32,S33,S34は、昇圧回路用の第3のクロックCK3に基づいて生成される。

【0070】

また、図12において、ハッチングを施した領域は、デッドタイム期間の状態(DT)を表している。

【0071】

次に、上記のように構成された本実施の形態の昇圧装置の動作を、図13〜図24を参照しながら説明する。

【0072】

まず、図13のように、第1の昇圧回路部A1におけるスイッチ素子S12とスイッチ素子S13と、第2の昇圧回路部A2におけるスイッチ素子S21とスイッチ素子S24と、第3の昇圧回路部A3におけるスイッチ素子S32とスイッチ素子S33をオンさせ、スイッチ素子S11とスイッチ素子S14とスイッチ素子S22とスイッチ素子S23とスイッチ素子S31とスイッチ素子S34をオフさせる。この期間で、第1の昇圧回路部A1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2における容量素子C2は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第3の昇圧回路部A3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)である。この期間は、基準電源Vciへ負荷が3箇所からかかっている状態であり、第2の昇圧回路部A2から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔CH,UP,CH〕である。

【0073】

次に、図14のように、図13の状態から第3の昇圧回路部A3におけるスイッチ素子S32とスイッチ素子S33をオフさせる。この期間で、第1の昇圧回路部A1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2における容量素子C2は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第3の昇圧回路部A3はデッドタイム期間の状態(DT)である。第1の昇圧回路部A1および第2の昇圧回路部A2は動作状態のままであるため、基準電源Vciへ負荷が2箇所からかかっている状態であり、第2の昇圧回路部A2から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔CH,UP,DT〕である。

【0074】

次に、図15のように、図14の状態から第3の昇圧回路部A3におけるスイッチ素子S31とスイッチ素子S34をオンさせ、基準電源電圧蓄積用の容量素子C3に対して基準電源Vciを逆方向に印加する。この期間で、第1の昇圧回路部A1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2における容量素子C2は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第3の昇圧回路部A3における容量素子C3は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)である。この期間は、基準電源Vciへ負荷が3箇所からかかっている状態であり、第2の昇圧回路部A2および第3の昇圧回路部A3から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔CH,UP,UP〕である。

【0075】

次に、図16のように、図15の状態から第2の昇圧回路部A2におけるスイッチ素子S21とスイッチ素子S24をオフさせる。この期間で、第1の昇圧回路部A1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第3の昇圧回路部A3における容量素子C3は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。第1の昇圧回路部A1および第3の昇圧回路部A3は動作状態のままであるため、基準電源Vciへ負荷が2箇所からかかっている状態であり、第3の昇圧回路部A3から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔CH,DT,UP〕である。

【0076】

次に、図17のように、図16の状態から第2の昇圧回路部A2におけるスイッチ素子S22とスイッチ素子S23をオンさせる。この期間で、第1の昇圧回路部A1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の昇圧回路部A3における容量素子C3は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)である。この期間は、基準電源Vciへ負荷が3箇所からかかっている状態であり、第3の昇圧回路部A3から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔CH,CH,UP〕である。

【0077】

次に、図18のように、図17の状態から第1の昇圧回路部A1におけるスイッチ素子S12とスイッチ素子S13をオフさせる。この期間で、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の昇圧回路部A3における容量素子C3は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。第2の昇圧回路部A2および第3の昇圧回路部A3は動作状態のままであるため、基準電源Vciへ負荷が2箇所からかかっている状態であり、第3の昇圧回路部A3から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔DT,CH,UP〕である。

【0078】

次に、図19のように、図18の状態から第1の昇圧回路部A1におけるスイッチ素子S11とスイッチ素子S14をオンさせ、基準電源電圧蓄積用の容量素子C1に対して基準電源Vciを逆方向に印加する。この期間で、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の昇圧回路部A3における容量素子C3は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)である。この期間は、基準電源Vciへ負荷が3箇所からかかっている状態であり、第1の昇圧回路部A1および第3の昇圧回路部A3から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔UP,CH,UP〕である。

【0079】

次に、図20のように、図19の状態から第3の昇圧回路部A3におけるスイッチ素子S31とスイッチ素子S34をオフさせる。この期間で、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の昇圧回路部A3はデッドタイム期間の状態(DT)である。第1の昇圧回路部A1および第2の昇圧回路部A2は動作状態のままであるため、基準電源Vciへ負荷が2箇所からかかっている状態であり、第1の昇圧回路部A1から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔UP,CH,DT〕である。

【0080】

次に、図21のように、図20の状態から第3の昇圧回路部A3におけるスイッチ素子S32とスイッチ素子S33をオンさせる。この期間で、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第2の昇圧回路部A2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の昇圧回路部A3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)である。この期間は、基準電源Vciへ負荷が3箇所からかかっている状態であり、第1の昇圧回路部A1から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔UP,CH,CH〕である。

【0081】

次に、図22のように、図21の状態から第2の昇圧回路部A2におけるスイッチ素子S22とスイッチ素子S23をオフさせる。この期間で、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第3の昇圧回路部A3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)であり、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。第1の昇圧回路部A1および第3の昇圧回路部A3は動作状態のままであるため、基準電源Vciへ負荷が2箇所からかかっている状態であり、第1の昇圧回路部A1から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔UP,DT,CH〕である。

【0082】

次に、図23のように、図22の状態から第2の昇圧回路部A2におけるスイッチ素子S21とスイッチ素子S24をオンさせ、基準電源電圧蓄積用の容量素子C2に対して基準電源Vciを逆方向に印加する。この期間で、第1の昇圧回路部A1における容量素子C1は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第2の昇圧回路部A2における容量素子C2は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第3の昇圧回路部A3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)である。この期間は、基準電源Vciへ負荷が3箇所からかかっている状態であり、第1の昇圧回路部A1および第2の昇圧回路部A2から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔UP,UP,CH〕である。

【0083】

次に、図24のように、図23の状態から第1の昇圧回路部A1におけるスイッチ素子S11とスイッチ素子S14をオフさせる。この期間で、第2の昇圧回路部A2における容量素子C2は蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第3の昇圧回路部A3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)であり、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。第2の昇圧回路部A2および第3の昇圧回路部A3は動作状態のままであるため、基準電源Vciへ負荷が2箇所からかかっている状態であり、第2の昇圧回路部A2から昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔A1,A2,A3〕=〔DT,UP,CH〕である。

【0084】

図13〜図24の動作を繰り返すことにより、昇圧電圧蓄積用の容量素子C0に基準電源Vciの2倍の電圧(Vout)が生成される。

【0085】

図12において、図14相当の期間では、第3の昇圧回路部A3における4つのスイッチ素子S31,S32,S33,S34がすべてオフとなっていて、第3の昇圧回路部A3はデッドタイム期間の状態(DT)である。このとき、第1の昇圧回路部A1において、スイッチ素子S12,S13がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。さらに、第2の昇圧回路部A2において、スイッチ素子S21,S24がオンであることから、昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態(UP)も確保されている。

【0086】

また、図12において、図16相当の期間では、第2の昇圧回路部A2における4つのスイッチ素子S21,S22,S23,S24がすべてオフとなっていて、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。このとき、第1の昇圧回路部A1において、スイッチ素子S12,S13がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。さらに、第3の昇圧回路部A3において、スイッチ素子S31,S34がオンであることから、昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態(UP)も確保されている。

【0087】

また、図12において、図18相当の期間では、第1の昇圧回路部A1における4つのスイッチ素子S11,S12,S13,S14がすべてオフとなっていて、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。このとき、第2の昇圧回路部A2において、スイッチ素子S22,S23がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。さらに、第3の昇圧回路部A3において、スイッチ素子S31,S34がオンであることから、昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態(UP)も確保されている。

【0088】

また、図12において、図20相当の期間では、第3の昇圧回路部A3における4つのスイッチ素子S31,S32,S33,S34がすべてオフとなっていて、第3の昇圧回路部A3はデッドタイム期間の状態(DT)である。このとき、第2の昇圧回路部A2において、スイッチ素子S22,S23がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。さらに、第1の昇圧回路部A1において、スイッチ素子S11,S14がオンであることから、昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態(UP)も確保されている。

【0089】

また、図12において、図22相当の期間では、第2の昇圧回路部A2における4つのスイッチ素子S21,S22,S23,S24がすべてオフとなっていて、第2の昇圧回路部A2はデッドタイム期間の状態(DT)である。このとき、第3の昇圧回路部A3において、スイッチ素子S32,S33がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。さらに、第1の昇圧回路部A1において、スイッチ素子S11,S14がオンであることから、昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態(UP)も確保されている。

【0090】

また、図12において、図24相当の期間では、第1の昇圧回路部A1における4つのスイッチ素子S11,S12,S13,S14がすべてオフとなっていて、第1の昇圧回路部A1はデッドタイム期間の状態(DT)である。このとき、第3の昇圧回路部A3において、スイッチ素子S32,S33がオンであることから、基準電源Vciの電圧を蓄える状態(CH)が確保されている。さらに、第2の昇圧回路部A2において、スイッチ素子S21,S24がオンであることから、昇圧電圧蓄積用の容量素子C0へ電荷が供給されている状態(UP)も確保されている。

【0091】

以上の経過をまとめると、

図13……〔A1,A2,A3〕=〔CH,UP,CH〕

図14……〔A1,A2,A3〕=〔CH,UP,DT〕

図15……〔A1,A2,A3〕=〔CH,UP,UP〕

図16……〔A1,A2,A3〕=〔CH,DT,UP〕

図17……〔A1,A2,A3〕=〔CH,CH,UP〕

図18……〔A1,A2,A3〕=〔DT,CH,UP〕

図19……〔A1,A2,A3〕=〔UP,CH,UP〕

図20……〔A1,A2,A3〕=〔UP,CH,DT〕

図21……〔A1,A2,A3〕=〔UP,CH,CH〕

図22……〔A1,A2,A3〕=〔UP,DT,CH〕

図23……〔A1,A2,A3〕=〔UP,UP,CH〕

図24……〔A1,A2,A3〕=〔DT,UP,CH〕

となる。第1の昇圧回路部A1における動作履歴をみると、CH→CH→CH→CH→CH→DT→UP→UP→UP→UP→UP→DTのサイクリック動作となっている。また、第2の昇圧回路部A2における動作履歴をみると、UP→UP→UP→DT→CH→CH→CH→CH→CH→DT→UP→UPのサイクリック動作となっている。また、第3の昇圧回路部A3における動作履歴をみると、CH→DT→UP→UP→UP→UP→UP→DT→CH→CH→CH→CHのサイクリック動作となっている。3つの昇圧回路部A1,A2,A3の動作は、タイミングこそ異なるが、同一パターンのサイクリック動作となっている。

【0092】

第3の昇圧回路部A3がデッドタイム期間の状態(DT)であるときは(図14または図20)、第1の昇圧回路部A1が基準電源Vciの電圧を蓄える状態(CH)または蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第2の昇圧回路部A2が蓄えられた電荷を昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)または基準電源Vciの電圧を蓄える状態(CH)となっている。

【0093】

また、第2の昇圧回路部A2がデッドタイム期間の状態(DT)であるときは(図16または図22)、第1の昇圧回路部A1が基準電源Vciの電圧を蓄える状態(CH)または蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第3の昇圧回路部A3が蓄えられた電荷を昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)または基準電源Vciの電圧を蓄える状態(CH)となっている。

【0094】

また、第1の昇圧回路部A1がデッドタイム期間の状態(DT)であるときは(図18または図24)、第2の昇圧回路部A2が基準電源Vciの電圧を蓄える状態(CH)または蓄えている電荷をポンプ動作により昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)であり、第3の昇圧回路部A3が蓄えられた電荷を昇圧電圧蓄積用の容量素子C0に持ち上げる状態(UP)または基準電源Vciの電圧を蓄える状態(CH)となっている。

【0095】

すなわち、いずれの1つの昇圧回路部がデッドタイム期間の状態(DT)であっても、他の1つの昇圧回路部において、必ず、平滑容量を持たない基準電源Vciに負荷がかかっている状態を維持させることができている。これで、従来の技術の場合の、〔DT,無負荷〕の状態を脱却でき、〔DT,無負荷〕の状態に起因するノイズの発生を抑制することができる。また、別の1つの昇圧回路部において、必ず、昇圧電圧蓄積用の容量素子C0に電荷の供給が行われている状態を維持させることができている。これで、基準電源Vciの2倍の電圧(Vout)のリップルを低減させ、電流能力を上げるという効果も得られる。

【0096】

まとめると、本実施の形態によれば、基準電源Vciには常に負荷がかかっている状態で、昇圧動作が可能となり、基準電源Vciのノイズの低減が可能となり、さらに昇圧電圧蓄積用の容量素子C0には常に少なくとも1つの昇圧回路部から電荷の供給が行われている状態になるため、基準電源Vciの2倍の電圧(Vout)のリップルを低減させ、電流能力を上げるという効果も得られる。

【0097】

なお、本実施の形態の昇圧装置においては、基準電源Vciの2倍の電圧(Vout)の出力端子に対しては、常に少なくとも1つの昇圧回路部から電荷の供給が行われている状態になるため、基準電源Vciの2倍の電圧(Vout)を保持する役割の昇圧電圧蓄積用の容量素子C0はなくてもよい。

【0098】

(実施の形態3)

上記においては、昇圧装置について説明したが、降圧回路部を3つ以上接続した場合の降圧装置でも、上記同様の効果が得られる。これが本発明の実施の形態3である。以下に、本発明の実施の形態3における降圧装置について説明する。

【0099】

図25は、本発明の実施の形態3における降圧装置の構成を示す回路図である。図25に示すように、電圧出力端子Voutに降圧電圧蓄積用の容量素子C0が接続され、この降圧電圧蓄積用の容量素子C0に対して第1の降圧回路部B1と第2の降圧回路部B2と第3の降圧回路部B3が並列に接続されている。降圧電圧蓄積用の容量素子C0は、基準電源Vciの(−1)倍の電圧(Vout)を保持し、出力するものである。

【0100】

第1の降圧回路部B1において、グランドVSSと基準電源Vciとの間にスイッチ素子S11とスイッチ素子S12の直列回路が接続されており、また、グランドVSSと両スイッチ素子S11,S12の接続点との間にスイッチ素子S13と基準電源電圧蓄積用の容量素子C1の直列回路が接続されている。スイッチ素子S13と基準電源電圧蓄積用の容量素子C1の接続点とグランドVSSとの間にスイッチ素子S14と降圧電圧蓄積用の容量素子C0の直列回路が接続されている。降圧電圧蓄積用の容量素子C0は、基準電源Vciの(−1)倍の電圧(Vout)を保持し、出力するものである。スイッチ素子S11,S12,S13,S14と基準電源電圧蓄積用の容量素子C1で第1の降圧回路部B1を形成している。

【0101】

第2の降圧回路部B2において、グランドVSSと基準電源Vciとの間にスイッチ素子S21とスイッチ素子S22の直列回路が接続されており、また、グランドVSSと両スイッチ素子S21,S22の接続点との間にスイッチ素子S23と基準電源電圧蓄積用の容量素子C2の直列回路が接続されている。スイッチ素子S23と基準電源電圧蓄積用の容量素子C2の接続点とグランドVSSとの間にスイッチ素子S24と降圧電圧蓄積用の容量素子C0の直列回路が接続されている。スイッチ素子S21,S22,S23,S24と基準電源電圧蓄積用の容量素子C2で第2の降圧回路部B2を形成している。

【0102】

第3の降圧回路部B3において、グランドVSSと基準電源Vciとの間にスイッチ素子S31とスイッチ素子S32の直列回路が接続されており、また、グランドVSSと両スイッチ素子S31,S32の接続点との間にスイッチ素子S33と基準電源電圧蓄積用の容量素子C3の直列回路が接続されている。スイッチ素子S33と基準電源電圧蓄積用の容量素子C3の接続点とグランドVSSとの間にスイッチ素子S34と降圧電圧蓄積用の容量素子C0の直列回路が接続されている。スイッチ素子S31,S32,S33,S34と基準電源電圧蓄積用の容量素子C3で第3の降圧回路部B3を形成している。

【0103】

30は、第1の降圧回路部B1におけるスイッチ素子S11,S12,S13,S14をオン・オフ制御する制御信号A,B,C,Dと第2の降圧回路部B2におけるスイッチ素子S21,S22,S23,S24をオン・オフ制御する制御信号E,F,G,Hと第3の降圧回路部B3におけるスイッチ素子S31,S32,S33,S34をオン・オフ制御する制御信号I,J,K,Lを生成出力する制御部である。この制御部30は、第1の降圧回路部B1、第2の降圧回路部B2および第3の降圧回路部B3のうちいずれか1つの降圧回路部のデッドタイム期間において他の降圧回路部では電荷蓄積動作またはポンプ動作を行うという制御を、前記3つの降圧回路部B1,B2,B3において順次かつサイクリックに行うように構成されている。基準電源Vciは平滑容量を持たない電源となっている。

【0104】

上記のように、本実施の形態における降圧装置は、基準電源Vciの(−1)倍の電圧(Vout)を保持する降圧電圧蓄積用の容量素子C0に対して、第1の降圧回路部B1と第2の降圧回路部B2と第3の降圧回路部B3とが並列に接続された構成となっている。

【0105】

図26は本実施の形態の降圧装置の動作を示すタイミングチャートである。図26のタイミングチャートにおいて、第1の降圧回路部B1におけるスイッチ素子S11,S12,S13,S14をオン・オフ制御する制御信号A,B,C,Dは、降圧回路用の第1のクロックCK1に基づいて生成され、第2の降圧回路部B2におけるスイッチ素子S21,S22,S23,S24をオン・オフ制御する制御信号E,F,G,Hは、降圧回路用の第2のクロックCK2に基づいて生成され、第3の降圧回路部B3におけるスイッチ素子S31,S32,S33,S34は、降圧回路用の第3のクロックCK3に基づいて生成される。

【0106】

また、図26において、ハッチングを施した領域は、デッドタイム期間の状態(DT)を表している。

【0107】

次に、上記のように構成された本実施の形態の降圧装置動作を、図27〜図38を参照しながら以下に説明する。

【0108】

まず、図27のように、第1の降圧回路部B1におけるスイッチ素子S12とスイッチ素子S13と、第2の降圧回路部B2におけるスイッチ素子S21とスイッチ素子S24と、第3の降圧回路部B3におけるスイッチ素子S32とスイッチ素子S33をオンさせ、スイッチ素子S11とスイッチ素子S14とスイッチ素子S22とスイッチ素子S23とスイッチ素子S31とスイッチ素子S34をオフさせる。この期間で、第1の降圧回路部B1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の降圧回路部B2における容量素子C2は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第3の降圧回路部B3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)である。この期間は、基準電源Vciへ負荷が2箇所からかかっている状態であり、第2の降圧回路部B2から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔CH,DN,CH〕である。

【0109】

次に、図28のように、図27の状態から第3の降圧回路部B3におけるスイッチ素子S32とスイッチ素子S33をオフさせる。この期間で、第1の降圧回路部B1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の降圧回路部B2における容量素子C2は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第3の降圧回路部B3はデッドタイム期間の状態(DT)である。第1の降圧回路部B1および第2の降圧回路部B2は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態であり、第2の降圧回路部B2から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔CH,DN,DT〕である。

【0110】

次に、図29のように、図28の状態から第3の降圧回路部B3におけるスイッチ素子S31とスイッチ素子S34をオンさせ、基準電源電圧蓄積用の容量素子C3に対して基準電源Vciを同方向に印加する。この期間で、第1の降圧回路部B1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の降圧回路部B2における容量素子C2は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第3の降圧回路部B3における容量素子C3は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)である。この期間は、基準電源Vciへ負荷が1箇所からかかっている状態であり、第2の降圧回路部B2および第3の降圧回路部B3から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔CH,DN,DN〕である。

【0111】

次に、図30のように、図29の状態から第2の降圧回路部B2におけるスイッチ素子S21とスイッチ素子S24をオフさせる。この期間で、第1の降圧回路部B1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第3の降圧回路部B3における容量素子C3は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第2の降圧回路部B2はデッドタイム期間の状態(DT)である。第1の降圧回路部B1および第3の降圧回路部B3は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態であり、第3の降圧回路部B3から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔CH,DT,DN〕である。

【0112】

次に、図31のように、図30の状態から第2の降圧回路部B2におけるスイッチ素子S22とスイッチ素子S23をオンさせる。この期間で、第1の降圧回路部B1における容量素子C1は基準電源Vciの電圧を蓄える状態(CH)であり、第2の降圧回路部B2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の降圧回路部B3における容量素子C3は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)である。この期間は、基準電源Vciへ負荷が2箇所からかかっている状態であり、第3の降圧回路部B3から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔CH,CH,DN〕である。

【0113】

次に、図32のように、図31の状態から第1の降圧回路部B1におけるスイッチ素子S12とスイッチ素子S13をオフさせる。この期間で、第2の降圧回路部B2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の降圧回路部B3における容量素子C3は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第1の降圧回路部B1はデッドタイム期間の状態(DT)である。第2の降圧回路部B2および第3の降圧回路部B3は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態であり、第3の降圧回路部B3から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔DT,CH,DN〕である。

【0114】

次に、図33のように、図32の状態から第1の降圧回路部B1におけるスイッチ素子S11とスイッチ素子S14をオンさせ、基準電源電圧蓄積用の容量素子C1に対して基準電源Vciを同方向に印加する。この期間で、第1の降圧回路部B1における容量素子C1は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第2の降圧回路部B2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の降圧回路部B3における容量素子C3は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)である。この期間は、基準電源Vciへ負荷が1箇所からかかっている状態であり、第1の降圧回路部B1および第3の降圧回路部B3から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔DN,CH,DN〕である。

【0115】

次に、図34のように、図33の状態から第3の降圧回路部B3におけるスイッチ素子S31とスイッチ素子S34をオフさせる。この期間で、第1の降圧回路部B1における容量素子C1は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第2の降圧回路部B2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の降圧回路部B3はデッドタイム期間の状態(DT)である。第1の降圧回路部B1および第2の降圧回路部B2は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態であり、第1の降圧回路部B1から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔DN,CH,DT〕である。

【0116】

次に、図35のように、図34の状態から第3の降圧回路部B3におけるスイッチ素子S32とスイッチ素子S33をオンさせる。この期間で、第1の降圧回路部B1における容量素子C1は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第2の降圧回路部B2における容量素子C2は基準電源Vciの電圧を蓄える状態(CH)であり、第3の降圧回路部B3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)である。この期間は、基準電源Vciへ負荷が2箇所からかかっている状態であり、第1の降圧回路部B1から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔DN,CH,CH〕である。

【0117】

次に、図36のように、図35の状態から第2の降圧回路部B2におけるスイッチ素子S22とスイッチ素子S23をオフさせる。この期間で、第1の降圧回路部B1における容量素子C1は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第3の降圧回路部B3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)であり、第2の降圧回路部B2はデッドタイム期間の状態(DT)である。第1の降圧回路部B1および第3の降圧回路部B3は動作状態のままであるため、基準電源Vciへ負荷が1箇所からかかっている状態であり、第1の降圧回路部B1から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔DN,DT,CH〕である。

【0118】

次に、図37のように、図36の状態から第2の降圧回路部B2におけるスイッチ素子S21とスイッチ素子S24をオンさせ、基準電源電圧蓄積用の容量素子C2に対して基準電源Vciを同方向に印加する。この期間で、第1の降圧回路部B1における容量素子C1は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第2の降圧回路部B2における容量素子C2は蓄えている電荷を降圧電圧蓄積用の容量素子C0に引き下げる状態(DN)であり、第3の降圧回路部B3における容量素子C3は基準電源Vciの電圧を蓄える状態(CH)である。この期間は、基準電源Vciへ負荷が1箇所からかかっている状態であり、第1の降圧回路部B1および第2の降圧回路部B2から降圧電圧蓄積用の容量素子C0へ電荷が供給されている状態である。総合状態は、〔B1,B2,B3〕=〔DN,DN,CH〕である。

【0119】