映像信号の表示制御装置および表示制御方法

【課題】少ない容量の映像メモリを利用しつつ、映像表示の不具合および電源回路に過負荷をもたらす問題を解消することができる映像信号の表示制御装置を提供すること。

【解決手段】少なくとも1フレーム期間の映像信号が書き込み可能な映像メモリ1に対して、入力される映像信号が書き換えられつつ格納される。平均輝度算出手段2は、1フレーム期間内における複数回のタイミングにおいて、映像メモリ1に書き込まれた映像信号から平均輝度を算出し、算出された前記平均輝度に基づいて、輝度制御手段3において、映像メモリ1から読み出された映像信号の輝度制御を実行する。

【解決手段】少なくとも1フレーム期間の映像信号が書き込み可能な映像メモリ1に対して、入力される映像信号が書き換えられつつ格納される。平均輝度算出手段2は、1フレーム期間内における複数回のタイミングにおいて、映像メモリ1に書き込まれた映像信号から平均輝度を算出し、算出された前記平均輝度に基づいて、輝度制御手段3において、映像メモリ1から読み出された映像信号の輝度制御を実行する。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、表示すべき映像信号の平均輝度レベル(APL=Average Picture Level)を求めて、この平均輝度レベルにより映像表示装置における表示輝度を制御する例えばPLE(Peak Luminance Enhancement)制御手段を備えた映像信号の表示制御装置および表示制御方法に関する。

【背景技術】

【0002】

例えばPDP(プラズマディスプレイパネル)などにおいては、画像表示を行うにあたっては、前記したPLE制御が行われる。このPLE制御はフィールドもしくはフレーム画面全体に対応する映像信号の平均輝度レベル(APL)を検出し、この平均輝度レベルに基づいて実際に画像表示させるための輝度レベルである表示輝度レベルを設定するようになされる。

【0003】

この場合、前記PLE制御では同じ輝度レベルの映像信号であっても、平均輝度レベルが小さい場合(画像全体が暗い場合)には、表示輝度レベルを高く設定して高輝度な表示が行われるようにされる。これに対して平均輝度レベルが大きい場合(画像全体が明るい場合)には、表示輝度レベルを下げて電力消費量を抑制するようにされる。このようにしてPLE制御が行われることにより、低消費電力化を実現させることができると共に、コントラストの良好な画像を表示させることが可能となる。

【0004】

前記したように、表示すべき映像信号の平均輝度レベルAPLを求め、このAPLにより表示輝度を制御するPLE制御手段を備えた表示装置は、次に示す特許文献1および2などに示されている。

【特許文献1】特開平9−281927号公報

【特許文献2】特開2001−175220号公報

【0005】

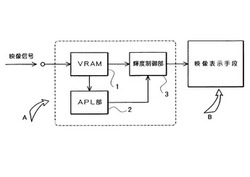

前記したPLE制御手段を利用して、表示画面の輝度調整を行う場合において、表示画像に遅延なくPLE制御による輝度調整を行うためは、一般に複数画面分(少なくとも2フレーム分)の映像メモリが必要になる。図1はその基本構成をブロック図によって示したものであり、符号Aは映像信号が入力される表示制御装置を示し、符号Bは前記表示制御装置Aにおいて輝度制御された映像信号を受けて、これを表示する映像表示手段を示している。

【0006】

前記表示制御装置Aには、それぞれ1フレーム分の映像信号を書き込むことができる第1と第2の映像メモリ1a,1bが具備されている。そして、入力される映像信号は、まず第1の映像メモリ1a(以下、これをVRAMaと称する。)に送られて、これに1フレーム分の映像信号が書き込まれる。これと同時に前記映像信号はAPL部(平均輝度算出手段)2に送られ、前記1フレーム分の映像信号から平均輝度レベル(以下、これをAPLaと称する。)を算出する。そして、APL部2において算出された平均輝度レベルAPLaの情報は輝度制御部(輝度制御手段)3に制御信号として送られる。

【0007】

続いて、次のフレームの映像信号が第2の映像メモリ1b(以下、これをVRAMbと称する。)に送られて、これに前記次の1フレーム分の映像信号が書き込まれる。これと同時に前記次のフレームの映像信号はAPL部2に送られ、この1フレーム分の映像信号から平均輝度レベル(以下、これをAPLbと称する。)を算出する。

【0008】

この間において、VRAMaより読み出された映像信号は、輝度制御部3において先の1フレーム分に対応した平均輝度レベルAPLaに基づいた輝度制御を受け、平均輝度レベルAPLaに対応した表示輝度レベルに設定される。この表示輝度レベルに設定された先の1フレーム分の映像信号は映像表示手段Bに送られて、画像表示されるように動作する。

【0009】

続いてVRAMbより読み出された後の映像信号は、輝度制御部3において後の1フレーム分に対応した平均輝度レベルAPLbに基づいた輝度制御を受け、平均輝度レベルAPLbに対応した表示輝度レベルに設定される。この表示輝度レベルに設定された後の1フレーム分の映像信号は同じく映像表示手段Bに送られて、画像表示される。すなわち、前記した動作が順次繰り返される。

【0010】

ところで、図1に示したように複数フレーム分の映像メモリを備える構成においては、メモリ容量の増加を招き、このメモリ容量の増加はこれを構築するICのコストアップをもたらし、必然的に製品のコストを引き上げる結果となる。したがって、例えば携帯電話機などに用いられる小型の表示装置においては、その体積およびコストの面から複数フレーム分の映像メモリを持たせることが困難になるため、図2に示すような1フレーム分の映像メモリを持つ構成が採用されることが多い。

【0011】

すなわち、図2に示す符号1は、1フレーム分の映像信号を書き込むことができる映像メモリであり、これはすでに説明した図1に符号1a,1bで示したいずれか一方の映像メモリに該当する。そして、図2に示す構成においては、図1に示す各部と同様の機能を果たす部分を同一符号で示しており、したがってその説明は省略する。

【0012】

図2に示す構成において用いられる映像メモリ1は、前記したとおり1フレーム分の映像信号を書き込むことができる容量であるため、映像メモリ1には時間経過と共に新しい映像信号が順次書き替えられつつ格納(オーバライト)されるように動作する。図3はその作用を説明するものであり、横軸は時間経過を示し、縦軸は映像メモリ(VRAM)1への映像信号の書き込み動作の進展状態を示している。なお、縦軸は表示走査の進行度合いを示していると言うこともできる。

【0013】

前記したとおり、映像メモリ1には時間経過と共に1つ手前の旧フレームによる映像信号に対して、次の新フレームによる映像信号が順次オーバライトされる。したがって、前記したPLE制御を実現させようとした場合には、表示フレームとAPLに応じた表示輝度には、最大で1フレーム期間の遅延が生ずる。この結果、図3に斜線部Cで示すように新フレームに対応する表示が、旧フレームによる平均輝度に基づいて表示制御される部分が発生する。

【0014】

ここで、一例として旧フレームによる映像信号は暗い映像であり、新フレームによる映像信号は明るい映像であるとした場合においては、前記したPLE制御は、旧フレームによる暗い映像に基づくAPLにより、新フレームによる明るい映像が輝度制御されるので、新フレームによる明るい映像の各ピーク輝度がさらにレベルアップされるように動作する。このために一瞬において明るい映像がさらに明るく表示されるという不具合が発生すする。同時に映像表示手段における大きな割合を占める点灯対象となる各表示画素に対してそれぞれ大きな駆動電流が流れるために、電源回路に瞬間的に過大な負荷が加わるという別の問題も発生する。

【発明の開示】

【発明が解決しようとする課題】

【0015】

この発明は、前記した問題点に着目してなされたものであり、少ない容量の映像メモリを利用しつつ、前記したような映像表示の不具合および電源回路に過負荷をもたらす問題を解消することができる映像信号の表示制御装置および表示制御方法を提供することを課題とするものである。

【課題を解決するための手段】

【0016】

前記した課題を解決するためになされたこの発明にかかる表示制御装置の基本形態は、請求項1に記載のとおり、入力される映像信号に基づいて映像を表示する表示手段を駆動制御するための表示制御装置であって、前記映像信号の平均輝度を算出する平均輝度算出手段と、前記平均輝度算出手段により得られる前記平均輝度に基づいて、前記映像信号の輝度を制御する輝度制御手段とが具備され、前記平均輝度算出手段は、1フレーム期間内において複数回にわたり映像信号の平均輝度を算出し、算出された前記平均輝度に基づいて前記輝度制御手段の輝度制御を実行するように構成される。

【0017】

また、前記した課題を解決するためになされたこの発明にかかる表示制御方法の基本態様は、請求項6に記載のとおり、入力される映像信号に基づいて映像を表示する表示手段を駆動制御するための表示制御方法であって、1フレーム期間内において複数回にわたり映像信号の平均輝度を算出すると共に、算出された前記平均輝度に基づいて、前記表示手段に与える映像信号の輝度を制御する輝度制御動作を実行する点に特徴を有する。

【発明を実施するための最良の形態】

【0018】

以下、この発明にかかる映像信号の表示制御装置について、図に示す実施の形態に基づいて説明する。図4はこの発明にかかる表示制御装置の基本構成をブロック図によって示したものである。なお、図4に示す構成においては、すでに説明した図2に示す各部と同様の機能を果たす部分を同一符号で示しており、したがって、その詳細な説明は適宜省略する。

【0019】

図4に示す映像メモリ1も、図2に示した例と同様に1フレーム分の映像信号を書き込むことができる容量のものが用いられており、したがって、映像メモリ1には時間経過と共に新しい映像信号が順次書き替えられつつ格納(オーバライト)されるように動作する。そして、平均輝度算出手段を構成するAPL部2は、前記映像メモリ1に書き込まれた映像信号を利用して平均輝度を算出するように構成されている。

【0020】

図5は、図4に示す表示制御装置Aの動作を説明するものであり、これはすでに説明した図3と同様の態様で示している。この表示制御装置の実施の形態においては、図5に示されたように1フレーム期間を複数の期間に分けて、各期間毎に映像信号の平均輝度(APL)を算出するように動作する。

【0021】

すなわち、図5に示した例は、説明を単純化するために1フレーム期間を3つの期間に分けた例を示しており、APL算出期間1、同2、同3として示したとおり、APL部2は映像メモリ1に書き込まれた映像信号を利用して、1フレーム期間に3回にわたりAPLを算出し、その都度、算出したAPLを輝度制御部3に制御信号として送出するように動作する。

【0022】

一方、1フレーム期間を3つに分割し、映像メモリ1に書き込まれた映像信号は、前記分割期間単位で順次読み出されて輝度制御部3に供給される。この結果、図5に示す例えばAPL算出期間1において書き込まれた新フレームに該当する映像信号は、APL算出期間2において、順次読み出されて輝度制御部3に供給される。この場合、輝度制御部3にはAPL算出期間1の最後のタイミングであるt1におけるAPLが制御信号として供給されることになる。

【0023】

換言すれば、APL算出期間1において映像メモリ1に書き込まれた映像信号は、前記t1において映像メモリ1に書き込まれている映像信号のAPLよって輝度制御を受けて映像表示手段Bに供給される。同様にAPL算出期間2において映像メモリ1に書き込まれた映像信号は、t2において映像メモリ1に書き込まれている映像信号のAPLよって輝度制御を受けて映像表示手段Bに供給されるように動作し、さらに同様にAPL算出期間3において映像メモリ1に書き込まれた映像信号は、t3において映像メモリ1に書き込まれている映像信号のAPLよって輝度制御を受けて映像表示手段Bに供給されるように動作する。

【0024】

ここで、前記t1において映像メモリ1に書き込まれている映像信号は、旧フレームと新フレームの映像信号のうち旧フレームによる映像信号の割合が大きい。また前記t2において映像メモリ1に書き込まれている映像信号は、旧フレームと新フレームの映像信号のうち新フレームによる映像信号の割合が大きくなる。さらに前記t3において映像メモリ1に書き込まれている映像信号は、全てが新フレームによる映像信号となる。

【0025】

したがって、すでに説明したように旧フレームによる映像信号は例えば暗い映像であり、新フレームによる映像信号は明るい映像であるとした場合においては、APL算出期間1およびAPL算出期間2において映像メモリ1に書き込まれた明るい映像信号は、それぞれ旧フレームに対して新フレームの映像信号が所定の割合で書き込まれた状態のAPLによって輝度制御を受けることになる。

【0026】

それ故、新フレームによる明るい映像が、旧フレームの暗い映像データのみによるAPLにより輝度制御されることにより、極端な輝度の上昇制御がなされる問題を解消させることができる。これは、必然的に電源回路に瞬間的に過大なピーク電流が流れるという問題も解消される。

【0027】

因みに、図5に示された例においては、前記したとおりt3において映像メモリ1に書き込まれている映像信号は、全てが新フレームによる映像信号であり、したがってAPL算出期間3において映像メモリ1に書き込まれた明るい映像信号は、新フレームのみによるAPLにより輝度制御を受けることになり、正常なPLE制御動作を期待することができる。

【0028】

なお以上の説明は、動作を理解し易いように、映像メモリへの映像信号の書き込み動作と、映像メモリからの映像信号の読み出し動作が同期している同期型について説明しているが、非同期型でも同様の作用効果を得ることができる。

【0029】

図6〜図9は、以上説明したこの発明にかかる表示制御装置および表示制御方法を採用した具体例を示したものであり、これは表示パネルの画素に有機EL(エレクトロルミネッセンス)素子を用いたアクティブマトリクス型表示パネルを対象とした表示制御装置の例を示している。

【0030】

図6はその全体構成を示すものであり、符号Aはすでに説明した表示制御装置を示し、符号Bは映像表示手段を示しており、また、符号1はすでに説明した映像メモリを示している。表示制御装置Aには発光制御回路11が具備されており、この発光制御回路11に対して、アナログ/デジタル(A/D)変換回路12、映像メモリ1、輝度設定テーブル13が接続されている。

【0031】

そして、この図6に示す実施の形態においてはアナログ映像信号が発光制御回路11およびA/D変換回路12に供給されるように構成されている。前記発光制御回路11はアナログ映像信号中における水平および垂直同期信号に基づいて、前記A/D変換回路12に対するクロック信号CK、前記映像メモリ1に対する書き込み信号Wおよび読み出し信号Rを生成する。

【0032】

また、発光制御回路11は前記した映像信号中における水平および垂直同期信号に基づいて、後述する映像表示手段Bにおける走査ドライバ21、データドライバ22および消去ドライバ23に対する同期信号を生成するように作用する。

【0033】

前記A/D変換回路12は、発光制御回路11から供給されるクロック信号に基づいて、入力されるアナログ信号をサンプリングし、これを1画素ごとの画像データに変換して映像メモリ1に供給するように作用する。前記映像メモリ1は前記発光制御回路11からの書き込み信号WによってA/D変換回路12から供給される各画素データを映像メモリ1に順次書き込むように動作する。

【0034】

前記映像メモリ1は、すでに説明したとおり1フレーム分の映像信号を書き込むことができる容量にされており、前記した書き込み動作によって、後述する表示パネルにおける一画面分(1フレーム分)のデータの書き込みが行われ、続いて、次の1フレーム分の映像信号が順次書き替えられつつ格納(オーバライト)されるように動作する。

【0035】

これと同時に映像メモリ1に書き込まれた映像信号(画素データ)は、発光制御回路11から供給される読み出し信号Rによって前記メモリ1より順次読み出され、後述するようにPLEによる輝度制御を受けた状態で表示パネルにおいて画像表示される。

【0036】

なお、前記発光制御回路11は、後述するサブフレーム期間に同期して画像メモリに書き込まれている映像データよりAPLを算出するように動作する。この場合、前記APLは前記映像メモリ1に書き込まれた画素データから、後述する表示パネル31において発光制御させる画素の割合(点灯率)を算出することで得るようになされる。したがって、発光制御回路11は点灯率算出手段としての機能を果たし、これはすでに説明したAPL部2と同様に機能する。

【0037】

また、発光制御回路11は、算出された点灯率に基づいて前記輝度設定テーブル13を参照し、PLE動作を実行するように作用する。このPLE動作にあたっては、前記点灯率に基づいて輝度設定テーブル13を参照し、映像表示手段Bを構成するデータドライバ22および消去ドライバ23に対する適切な制御信号を生成するように動作する。なお、この時のデータドライバ22および消去ドライバ23の動作については、後で詳細に説明する。

【0038】

次に、映像表示手段Bにおける符号31は有機EL素子をそれぞれに含む多数の画素32をマトリクス状に配列した表示パネルを示している。この表示パネル31には、前記した走査ドライバ21、データドライバ22、および消去ドライバ23にそれぞれ接続される走査線33、データ線34および消去信号線35が配列されており、これらの交差位置に前記EL素子を含む画素32がそれぞれ配置されている。なお、前記各画素32には、電源供給回路24より画素の点灯駆動用電圧が電源供給線36を介して、それぞれ供給されるように構成されている。

【0039】

図7は前記した表示パネル31に配置された1つの画素32に対応する回路構成を示すものであり、この画素32には前記データドライバ22からの映像信号に対応したデータ信号Vdataが、表示パネルに配列されたデータ線34を介して制御用TFT、すなわちデータ書き込みトランジスタTr1のソースに供給されるように構成されている。

【0040】

前記データ書き込みトランジスタTr1のゲートには、走査ドライバ21に接続された走査線33を介して走査信号Select(これを書き込みパルスとも言う。)が供給されるように構成されている。前記データ書き込みトランジスタTr1のドレインは、点灯駆動用TFT、すなわち点灯駆動トランジスタTr2のゲートに接続されると共に、電荷保持用キャパシタC1の一方の端子に接続されている。

【0041】

また、点灯駆動トランジスタTr2のソースは、前記キャパシタC1の他方の端子に接続されると共に、電源供給線36を介して駆動電圧Vccが供給されるように構成されている。前記点灯駆動トランジスタTr2のドレインは、有機EL素子E1のアノード端子に接続され、この有機EL素子E1のカソード端子は、基準電位点(グランド)に接続されている。

【0042】

さらに、消去用TFTとしての消去トランジスタTr3のゲートには、消去信号線35を介して消去ドライバより消去信号Erase(これを消去パルスとも言う。)が供給されるように構成されている。そして、消去トランジスタTr3のソースおよびドレインが、前記キャパシタC1の両端部にそれぞれ接続されている。

【0043】

なお、図7に示す画素32の回路構成においては、駆動トランジスタTr2のみがpチャンネル型TFTにより構成され、他はnチャンネル型TFTにより構成されている。そして、前記した構成による画素32は、図6に示したように行および列方向にマトリクス状に多数配置されて表示パネル31が構成されている。

【0044】

図7に示した画素32の構成において、制御トランジスタTr1のゲートには、アドレス期間において走査ドライバ21より走査信号としての書き込みパルスSelectが供給される。これにより、制御トランジスタTr1のソース・ドレインを介して、データドライバ22から供給されるデータ信号Vdataに対応した電流がキャパシタC1に流れ、キャパシタC1は充電される。そして、その充電電圧が駆動トランジスタTr2のゲートに供給されて、トランジスタTr2はそのゲート電圧とドレインに供給される駆動電圧Vccに対応した電流を前記EL素子E1に流し、これによりEL素子E1は発光する。

【0045】

前記制御トランジスタTr1のゲートに対する前記書き込みパルスの印加が停止されると、トランジスタTr1はいわゆるカットオフとなる。しかしながら、キャパシタC1に蓄積された電荷により駆動トランジスタTr2のゲート電圧が保持され、これによりEL素子E1への駆動電流が維持される。したがって、EL素子E1は次のアドレス動作に至る期間(後述する1サブフレーム期間)において、前記データ信号Vdataに対応した点灯状態を継続することができる。

【0046】

一方、前記EL素子E1の点灯期間の途中(1サブフレーム期間の途中)において、前記消去ドライバ23より消去トランジスタTr3をオンさせる消去パルスEraseが供給される。これにより、キャパシタC1にチャージされている電荷を瞬時にして消去(放電)させることができる。この結果、駆動トランジスタTr2はカットオフ状態となり、EL素子E1は直ちに消灯される。換言すれば、消去ドライバ23からの消去パルスEraseの出力タイミングを制御することで、EL素子E1の1サブフレームにおける点灯期間が制御され、これにより所定のガンマ特性およびディマー特性を実現することができる。

【0047】

図8は、図6および図7に示した構成によってなされるPLE制御を説明するものである。このPLE制御を実現させるにあたって、この実施の形態においては1フレーム期間を複数のサブフレームに分割し、このサブフレームにおける画素の点灯期間の累計により階調制御を実現する階調制御手段が採用されている。

【0048】

すなわち図8に示す例は、説明を単純化するために1フレーム期間を7つのサブフレーム(SF1〜SF7)に分割し、1フレーム期間における各サブフレームを選択することで、8つの階調表現(100%非点灯も1つの階調と見なすことができ、7+1の階調表現)を実現する例を示している。

【0049】

図8(a)および(b)は、表示パネル31に配列された前記した画素32の点灯率(前記したVRAM1に書き込まれた画素の点灯率)に応じて、サブフレームごとの点灯期間と非点灯期間の割合を制御する例を示したものである。すなわち、(a)はサブフレームごとの点灯期間の割合が大きく、また(b)はサブフレームごとの点灯期間の割合が小さい場合を示している。なお、前記(a)および(b)は共に階調特性のガンマ値が同一で、ディマー特性が変更される例を示している。

【0050】

ここで、画素の点灯率が低い場合(換言すればAPLが小さい場合)においては、図8(a)に示す点灯制御が実行され、画素の点灯率が高い場合(APLが大きい場合)においては図8(b)に示す点灯制御が実行されるように制御される。要するに画素の点灯率の程度に応じて、サブフレームごとの点灯期間の割合が図8(a)と(b)の間で変化するように制御される。これにより、特に画素の点灯率が高い場合においては1フレーム期間内における画素の点灯期間の累計が低く抑えられ、各画素に供給される駆動電流値を抑制することができる。

【0051】

図8(c)および(d)は、図8(b)に示した点灯制御を実現させる場合の前記した書き込みパルスおよび消去パルスの発生タイミングを説明するものである。すなわち、図8に示す例においては、各サブフレームのスタートに同期して(c)に示す書き込みパルスが発生し、これにより画素は点灯状態にされる。そして、そのサブフレームの経過途中において(d)に示す消去パルスが発生し、これにより画素は非点灯状態にされる。

【0052】

ここで、例えば階調“8”を実現しようとした場合には、1フレーム期間において、画素は図8(a)または(b)に示す一連の点灯パターンが実行される。また例えば階調“5”を実現しようとした場合には、図8(a)または(b)に示すSf1〜Sf4の期間において点灯駆動動作が実行され、それ以降の各サブフレームの期間Sf5〜Sf7は全て消灯状態にされる。これにより、1フレーム期間における画素の点灯期間の累計にしたがった発光輝度を得ることができる。

【0053】

図8(d)に示す消去パルスは、次に説明する図9に示す構成によって生成することができる。図9における符号38はサブフレームカウンタを、符号39は論理演算ユニットを、さらに符号13は図6に基づいて説明した輝度設定テーブルを示している。すなわち、前記輝度設定テーブル13が図6に示したように発光制御回路11に対して外付けになされ、サブフレームカウンタ38および論理演算ユニット39は、発光制御回路11に内蔵された構成にされている。

【0054】

前記輝度設定テーブル13には、前記した点灯率に対応して各サブフレームごとの点灯期間がパラメータとして格納されている。そして、サブフレームカウンタ38より、点灯制御されるべきサブフレームナンバが論理演算ユニット39に供給された場合、論理演算ユニット39はテーブル13をアクセスし、サブフレームナンバに対応して格納されている点灯時間のパラメータに基づいて、前記消去パルスの出力タイミング信号を生成するように動作する。

【0055】

これは図8(d)に示したように画素の点灯率にそれぞれ対応してサブフレームごとの消去パルスの出力タイミング信号として生成される。このタイミング信号は前記した消去ドライバ23に供給され、消去ドライバ23からは前記したとおり、各サブフレームごとに消去パルスを出力するように動作する。

【0056】

なお、この実施の形態においてはサブフレームに同期して画像メモリ1に書き込まれている映像信号より前記した点灯率を求め、この点灯率に基づいて、輝度設定テーブル13にアクセスすることにより図9に示した構成により消去パルスの出力タイミング信号を生成するように動作する。

【0057】

したがって、これによるとサブフレーム毎に点灯率(=APL)に基づいた輝度制御(PLE制御)が実行されることになり、図4および図5に示した基本構成で説明した作用効果と同様に、少ない容量(1フレーム分)の映像メモリを利用しつつ、映像表示の不具合の発生を解消させることができると共に、電源回路に過負荷をもたらす問題も解消することができる。

【0058】

なお、図6〜図9に示した実施の形態においては、先に説明したように各サブフレームに同期して、サブフレーム毎にVRAM1にアクセスして点灯率(=APL)を算出し、この算出結果に基づいて、その都度輝度制御(PLE制御)を実行するようにしている。すなわち、この動作を模式的に示すと図10に示すようになる。

【0059】

しかしながら、現実的には1フレーム期間をより多数のサブフレームに分割して、例えば32段階もしくは64段階等の実用的な階調制御を実現するようにされる。このような場合においては、図10に示すようにサブフレーム毎にVRAM1にアクセスして点灯率(=APL)を算出することは必ずしも必要ではなく、例えば図11に示すように複数サブフレーム毎にVRAM1にアクセスして点灯率(=APL)を算出し、次の複数のサブフレームの期間においては、この点灯率に基づいて輝度制御(PLE制御)を実行するようにしてもよい。

【図面の簡単な説明】

【0060】

【図1】従来の表示制御装置の基本構成例を示したブロック図である。

【図2】従来の表示制御装置の他の基本構成例を示したブロック図である。

【図3】図2に示す表示制御装置のPLE作用を説明するタイミング図である。

【図4】この発明にかかる表示制御装置の基本構成を示したブロック図である。

【図5】図4に示す表示制御装置のPLE作用を説明するタイミング図である。

【図6】この発明を採用した表示制御装置の実施の形態を示したブロック図である。

【図7】図6に示す表示パネルに配列された画素の構成例を示した回路構成図である。

【図8】図6に示す表示制御装置における動作を説明するタイミング図である。

【図9】図6に示す構成において利用される輝度設定の基本機能を説明するブロック図である。

【図10】この発明にかかる表示制御装置においてなされるAPL算出動作を説明するタイミング図である。

【図11】同じく他のAPL算出動作を説明するタイミング図である。

【符号の説明】

【0061】

1 映像メモリ

2 平均輝度算出手段

3 輝度制御手段

11 発光制御回路

12 A/D変換回路

13 輝度設定テーブル

21 走査ドライバ

22 データドライバ

23 消去ドライバ

24 電源供給回路

31 表示パネル

32 画素

33 走査線

34 データ線

35 消去信号線

36 電源供給線

A 表示制御装置

B 映像表示手段

C1 電荷保持用キャパシタ

E1 有機EL素子

Tr1 データ書き込みトランジスタ

Tr2 点灯駆動トランジスタ

Tr3 消去トランジスタ

【技術分野】

【0001】

この発明は、表示すべき映像信号の平均輝度レベル(APL=Average Picture Level)を求めて、この平均輝度レベルにより映像表示装置における表示輝度を制御する例えばPLE(Peak Luminance Enhancement)制御手段を備えた映像信号の表示制御装置および表示制御方法に関する。

【背景技術】

【0002】

例えばPDP(プラズマディスプレイパネル)などにおいては、画像表示を行うにあたっては、前記したPLE制御が行われる。このPLE制御はフィールドもしくはフレーム画面全体に対応する映像信号の平均輝度レベル(APL)を検出し、この平均輝度レベルに基づいて実際に画像表示させるための輝度レベルである表示輝度レベルを設定するようになされる。

【0003】

この場合、前記PLE制御では同じ輝度レベルの映像信号であっても、平均輝度レベルが小さい場合(画像全体が暗い場合)には、表示輝度レベルを高く設定して高輝度な表示が行われるようにされる。これに対して平均輝度レベルが大きい場合(画像全体が明るい場合)には、表示輝度レベルを下げて電力消費量を抑制するようにされる。このようにしてPLE制御が行われることにより、低消費電力化を実現させることができると共に、コントラストの良好な画像を表示させることが可能となる。

【0004】

前記したように、表示すべき映像信号の平均輝度レベルAPLを求め、このAPLにより表示輝度を制御するPLE制御手段を備えた表示装置は、次に示す特許文献1および2などに示されている。

【特許文献1】特開平9−281927号公報

【特許文献2】特開2001−175220号公報

【0005】

前記したPLE制御手段を利用して、表示画面の輝度調整を行う場合において、表示画像に遅延なくPLE制御による輝度調整を行うためは、一般に複数画面分(少なくとも2フレーム分)の映像メモリが必要になる。図1はその基本構成をブロック図によって示したものであり、符号Aは映像信号が入力される表示制御装置を示し、符号Bは前記表示制御装置Aにおいて輝度制御された映像信号を受けて、これを表示する映像表示手段を示している。

【0006】

前記表示制御装置Aには、それぞれ1フレーム分の映像信号を書き込むことができる第1と第2の映像メモリ1a,1bが具備されている。そして、入力される映像信号は、まず第1の映像メモリ1a(以下、これをVRAMaと称する。)に送られて、これに1フレーム分の映像信号が書き込まれる。これと同時に前記映像信号はAPL部(平均輝度算出手段)2に送られ、前記1フレーム分の映像信号から平均輝度レベル(以下、これをAPLaと称する。)を算出する。そして、APL部2において算出された平均輝度レベルAPLaの情報は輝度制御部(輝度制御手段)3に制御信号として送られる。

【0007】

続いて、次のフレームの映像信号が第2の映像メモリ1b(以下、これをVRAMbと称する。)に送られて、これに前記次の1フレーム分の映像信号が書き込まれる。これと同時に前記次のフレームの映像信号はAPL部2に送られ、この1フレーム分の映像信号から平均輝度レベル(以下、これをAPLbと称する。)を算出する。

【0008】

この間において、VRAMaより読み出された映像信号は、輝度制御部3において先の1フレーム分に対応した平均輝度レベルAPLaに基づいた輝度制御を受け、平均輝度レベルAPLaに対応した表示輝度レベルに設定される。この表示輝度レベルに設定された先の1フレーム分の映像信号は映像表示手段Bに送られて、画像表示されるように動作する。

【0009】

続いてVRAMbより読み出された後の映像信号は、輝度制御部3において後の1フレーム分に対応した平均輝度レベルAPLbに基づいた輝度制御を受け、平均輝度レベルAPLbに対応した表示輝度レベルに設定される。この表示輝度レベルに設定された後の1フレーム分の映像信号は同じく映像表示手段Bに送られて、画像表示される。すなわち、前記した動作が順次繰り返される。

【0010】

ところで、図1に示したように複数フレーム分の映像メモリを備える構成においては、メモリ容量の増加を招き、このメモリ容量の増加はこれを構築するICのコストアップをもたらし、必然的に製品のコストを引き上げる結果となる。したがって、例えば携帯電話機などに用いられる小型の表示装置においては、その体積およびコストの面から複数フレーム分の映像メモリを持たせることが困難になるため、図2に示すような1フレーム分の映像メモリを持つ構成が採用されることが多い。

【0011】

すなわち、図2に示す符号1は、1フレーム分の映像信号を書き込むことができる映像メモリであり、これはすでに説明した図1に符号1a,1bで示したいずれか一方の映像メモリに該当する。そして、図2に示す構成においては、図1に示す各部と同様の機能を果たす部分を同一符号で示しており、したがってその説明は省略する。

【0012】

図2に示す構成において用いられる映像メモリ1は、前記したとおり1フレーム分の映像信号を書き込むことができる容量であるため、映像メモリ1には時間経過と共に新しい映像信号が順次書き替えられつつ格納(オーバライト)されるように動作する。図3はその作用を説明するものであり、横軸は時間経過を示し、縦軸は映像メモリ(VRAM)1への映像信号の書き込み動作の進展状態を示している。なお、縦軸は表示走査の進行度合いを示していると言うこともできる。

【0013】

前記したとおり、映像メモリ1には時間経過と共に1つ手前の旧フレームによる映像信号に対して、次の新フレームによる映像信号が順次オーバライトされる。したがって、前記したPLE制御を実現させようとした場合には、表示フレームとAPLに応じた表示輝度には、最大で1フレーム期間の遅延が生ずる。この結果、図3に斜線部Cで示すように新フレームに対応する表示が、旧フレームによる平均輝度に基づいて表示制御される部分が発生する。

【0014】

ここで、一例として旧フレームによる映像信号は暗い映像であり、新フレームによる映像信号は明るい映像であるとした場合においては、前記したPLE制御は、旧フレームによる暗い映像に基づくAPLにより、新フレームによる明るい映像が輝度制御されるので、新フレームによる明るい映像の各ピーク輝度がさらにレベルアップされるように動作する。このために一瞬において明るい映像がさらに明るく表示されるという不具合が発生すする。同時に映像表示手段における大きな割合を占める点灯対象となる各表示画素に対してそれぞれ大きな駆動電流が流れるために、電源回路に瞬間的に過大な負荷が加わるという別の問題も発生する。

【発明の開示】

【発明が解決しようとする課題】

【0015】

この発明は、前記した問題点に着目してなされたものであり、少ない容量の映像メモリを利用しつつ、前記したような映像表示の不具合および電源回路に過負荷をもたらす問題を解消することができる映像信号の表示制御装置および表示制御方法を提供することを課題とするものである。

【課題を解決するための手段】

【0016】

前記した課題を解決するためになされたこの発明にかかる表示制御装置の基本形態は、請求項1に記載のとおり、入力される映像信号に基づいて映像を表示する表示手段を駆動制御するための表示制御装置であって、前記映像信号の平均輝度を算出する平均輝度算出手段と、前記平均輝度算出手段により得られる前記平均輝度に基づいて、前記映像信号の輝度を制御する輝度制御手段とが具備され、前記平均輝度算出手段は、1フレーム期間内において複数回にわたり映像信号の平均輝度を算出し、算出された前記平均輝度に基づいて前記輝度制御手段の輝度制御を実行するように構成される。

【0017】

また、前記した課題を解決するためになされたこの発明にかかる表示制御方法の基本態様は、請求項6に記載のとおり、入力される映像信号に基づいて映像を表示する表示手段を駆動制御するための表示制御方法であって、1フレーム期間内において複数回にわたり映像信号の平均輝度を算出すると共に、算出された前記平均輝度に基づいて、前記表示手段に与える映像信号の輝度を制御する輝度制御動作を実行する点に特徴を有する。

【発明を実施するための最良の形態】

【0018】

以下、この発明にかかる映像信号の表示制御装置について、図に示す実施の形態に基づいて説明する。図4はこの発明にかかる表示制御装置の基本構成をブロック図によって示したものである。なお、図4に示す構成においては、すでに説明した図2に示す各部と同様の機能を果たす部分を同一符号で示しており、したがって、その詳細な説明は適宜省略する。

【0019】

図4に示す映像メモリ1も、図2に示した例と同様に1フレーム分の映像信号を書き込むことができる容量のものが用いられており、したがって、映像メモリ1には時間経過と共に新しい映像信号が順次書き替えられつつ格納(オーバライト)されるように動作する。そして、平均輝度算出手段を構成するAPL部2は、前記映像メモリ1に書き込まれた映像信号を利用して平均輝度を算出するように構成されている。

【0020】

図5は、図4に示す表示制御装置Aの動作を説明するものであり、これはすでに説明した図3と同様の態様で示している。この表示制御装置の実施の形態においては、図5に示されたように1フレーム期間を複数の期間に分けて、各期間毎に映像信号の平均輝度(APL)を算出するように動作する。

【0021】

すなわち、図5に示した例は、説明を単純化するために1フレーム期間を3つの期間に分けた例を示しており、APL算出期間1、同2、同3として示したとおり、APL部2は映像メモリ1に書き込まれた映像信号を利用して、1フレーム期間に3回にわたりAPLを算出し、その都度、算出したAPLを輝度制御部3に制御信号として送出するように動作する。

【0022】

一方、1フレーム期間を3つに分割し、映像メモリ1に書き込まれた映像信号は、前記分割期間単位で順次読み出されて輝度制御部3に供給される。この結果、図5に示す例えばAPL算出期間1において書き込まれた新フレームに該当する映像信号は、APL算出期間2において、順次読み出されて輝度制御部3に供給される。この場合、輝度制御部3にはAPL算出期間1の最後のタイミングであるt1におけるAPLが制御信号として供給されることになる。

【0023】

換言すれば、APL算出期間1において映像メモリ1に書き込まれた映像信号は、前記t1において映像メモリ1に書き込まれている映像信号のAPLよって輝度制御を受けて映像表示手段Bに供給される。同様にAPL算出期間2において映像メモリ1に書き込まれた映像信号は、t2において映像メモリ1に書き込まれている映像信号のAPLよって輝度制御を受けて映像表示手段Bに供給されるように動作し、さらに同様にAPL算出期間3において映像メモリ1に書き込まれた映像信号は、t3において映像メモリ1に書き込まれている映像信号のAPLよって輝度制御を受けて映像表示手段Bに供給されるように動作する。

【0024】

ここで、前記t1において映像メモリ1に書き込まれている映像信号は、旧フレームと新フレームの映像信号のうち旧フレームによる映像信号の割合が大きい。また前記t2において映像メモリ1に書き込まれている映像信号は、旧フレームと新フレームの映像信号のうち新フレームによる映像信号の割合が大きくなる。さらに前記t3において映像メモリ1に書き込まれている映像信号は、全てが新フレームによる映像信号となる。

【0025】

したがって、すでに説明したように旧フレームによる映像信号は例えば暗い映像であり、新フレームによる映像信号は明るい映像であるとした場合においては、APL算出期間1およびAPL算出期間2において映像メモリ1に書き込まれた明るい映像信号は、それぞれ旧フレームに対して新フレームの映像信号が所定の割合で書き込まれた状態のAPLによって輝度制御を受けることになる。

【0026】

それ故、新フレームによる明るい映像が、旧フレームの暗い映像データのみによるAPLにより輝度制御されることにより、極端な輝度の上昇制御がなされる問題を解消させることができる。これは、必然的に電源回路に瞬間的に過大なピーク電流が流れるという問題も解消される。

【0027】

因みに、図5に示された例においては、前記したとおりt3において映像メモリ1に書き込まれている映像信号は、全てが新フレームによる映像信号であり、したがってAPL算出期間3において映像メモリ1に書き込まれた明るい映像信号は、新フレームのみによるAPLにより輝度制御を受けることになり、正常なPLE制御動作を期待することができる。

【0028】

なお以上の説明は、動作を理解し易いように、映像メモリへの映像信号の書き込み動作と、映像メモリからの映像信号の読み出し動作が同期している同期型について説明しているが、非同期型でも同様の作用効果を得ることができる。

【0029】

図6〜図9は、以上説明したこの発明にかかる表示制御装置および表示制御方法を採用した具体例を示したものであり、これは表示パネルの画素に有機EL(エレクトロルミネッセンス)素子を用いたアクティブマトリクス型表示パネルを対象とした表示制御装置の例を示している。

【0030】

図6はその全体構成を示すものであり、符号Aはすでに説明した表示制御装置を示し、符号Bは映像表示手段を示しており、また、符号1はすでに説明した映像メモリを示している。表示制御装置Aには発光制御回路11が具備されており、この発光制御回路11に対して、アナログ/デジタル(A/D)変換回路12、映像メモリ1、輝度設定テーブル13が接続されている。

【0031】

そして、この図6に示す実施の形態においてはアナログ映像信号が発光制御回路11およびA/D変換回路12に供給されるように構成されている。前記発光制御回路11はアナログ映像信号中における水平および垂直同期信号に基づいて、前記A/D変換回路12に対するクロック信号CK、前記映像メモリ1に対する書き込み信号Wおよび読み出し信号Rを生成する。

【0032】

また、発光制御回路11は前記した映像信号中における水平および垂直同期信号に基づいて、後述する映像表示手段Bにおける走査ドライバ21、データドライバ22および消去ドライバ23に対する同期信号を生成するように作用する。

【0033】

前記A/D変換回路12は、発光制御回路11から供給されるクロック信号に基づいて、入力されるアナログ信号をサンプリングし、これを1画素ごとの画像データに変換して映像メモリ1に供給するように作用する。前記映像メモリ1は前記発光制御回路11からの書き込み信号WによってA/D変換回路12から供給される各画素データを映像メモリ1に順次書き込むように動作する。

【0034】

前記映像メモリ1は、すでに説明したとおり1フレーム分の映像信号を書き込むことができる容量にされており、前記した書き込み動作によって、後述する表示パネルにおける一画面分(1フレーム分)のデータの書き込みが行われ、続いて、次の1フレーム分の映像信号が順次書き替えられつつ格納(オーバライト)されるように動作する。

【0035】

これと同時に映像メモリ1に書き込まれた映像信号(画素データ)は、発光制御回路11から供給される読み出し信号Rによって前記メモリ1より順次読み出され、後述するようにPLEによる輝度制御を受けた状態で表示パネルにおいて画像表示される。

【0036】

なお、前記発光制御回路11は、後述するサブフレーム期間に同期して画像メモリに書き込まれている映像データよりAPLを算出するように動作する。この場合、前記APLは前記映像メモリ1に書き込まれた画素データから、後述する表示パネル31において発光制御させる画素の割合(点灯率)を算出することで得るようになされる。したがって、発光制御回路11は点灯率算出手段としての機能を果たし、これはすでに説明したAPL部2と同様に機能する。

【0037】

また、発光制御回路11は、算出された点灯率に基づいて前記輝度設定テーブル13を参照し、PLE動作を実行するように作用する。このPLE動作にあたっては、前記点灯率に基づいて輝度設定テーブル13を参照し、映像表示手段Bを構成するデータドライバ22および消去ドライバ23に対する適切な制御信号を生成するように動作する。なお、この時のデータドライバ22および消去ドライバ23の動作については、後で詳細に説明する。

【0038】

次に、映像表示手段Bにおける符号31は有機EL素子をそれぞれに含む多数の画素32をマトリクス状に配列した表示パネルを示している。この表示パネル31には、前記した走査ドライバ21、データドライバ22、および消去ドライバ23にそれぞれ接続される走査線33、データ線34および消去信号線35が配列されており、これらの交差位置に前記EL素子を含む画素32がそれぞれ配置されている。なお、前記各画素32には、電源供給回路24より画素の点灯駆動用電圧が電源供給線36を介して、それぞれ供給されるように構成されている。

【0039】

図7は前記した表示パネル31に配置された1つの画素32に対応する回路構成を示すものであり、この画素32には前記データドライバ22からの映像信号に対応したデータ信号Vdataが、表示パネルに配列されたデータ線34を介して制御用TFT、すなわちデータ書き込みトランジスタTr1のソースに供給されるように構成されている。

【0040】

前記データ書き込みトランジスタTr1のゲートには、走査ドライバ21に接続された走査線33を介して走査信号Select(これを書き込みパルスとも言う。)が供給されるように構成されている。前記データ書き込みトランジスタTr1のドレインは、点灯駆動用TFT、すなわち点灯駆動トランジスタTr2のゲートに接続されると共に、電荷保持用キャパシタC1の一方の端子に接続されている。

【0041】

また、点灯駆動トランジスタTr2のソースは、前記キャパシタC1の他方の端子に接続されると共に、電源供給線36を介して駆動電圧Vccが供給されるように構成されている。前記点灯駆動トランジスタTr2のドレインは、有機EL素子E1のアノード端子に接続され、この有機EL素子E1のカソード端子は、基準電位点(グランド)に接続されている。

【0042】

さらに、消去用TFTとしての消去トランジスタTr3のゲートには、消去信号線35を介して消去ドライバより消去信号Erase(これを消去パルスとも言う。)が供給されるように構成されている。そして、消去トランジスタTr3のソースおよびドレインが、前記キャパシタC1の両端部にそれぞれ接続されている。

【0043】

なお、図7に示す画素32の回路構成においては、駆動トランジスタTr2のみがpチャンネル型TFTにより構成され、他はnチャンネル型TFTにより構成されている。そして、前記した構成による画素32は、図6に示したように行および列方向にマトリクス状に多数配置されて表示パネル31が構成されている。

【0044】

図7に示した画素32の構成において、制御トランジスタTr1のゲートには、アドレス期間において走査ドライバ21より走査信号としての書き込みパルスSelectが供給される。これにより、制御トランジスタTr1のソース・ドレインを介して、データドライバ22から供給されるデータ信号Vdataに対応した電流がキャパシタC1に流れ、キャパシタC1は充電される。そして、その充電電圧が駆動トランジスタTr2のゲートに供給されて、トランジスタTr2はそのゲート電圧とドレインに供給される駆動電圧Vccに対応した電流を前記EL素子E1に流し、これによりEL素子E1は発光する。

【0045】

前記制御トランジスタTr1のゲートに対する前記書き込みパルスの印加が停止されると、トランジスタTr1はいわゆるカットオフとなる。しかしながら、キャパシタC1に蓄積された電荷により駆動トランジスタTr2のゲート電圧が保持され、これによりEL素子E1への駆動電流が維持される。したがって、EL素子E1は次のアドレス動作に至る期間(後述する1サブフレーム期間)において、前記データ信号Vdataに対応した点灯状態を継続することができる。

【0046】

一方、前記EL素子E1の点灯期間の途中(1サブフレーム期間の途中)において、前記消去ドライバ23より消去トランジスタTr3をオンさせる消去パルスEraseが供給される。これにより、キャパシタC1にチャージされている電荷を瞬時にして消去(放電)させることができる。この結果、駆動トランジスタTr2はカットオフ状態となり、EL素子E1は直ちに消灯される。換言すれば、消去ドライバ23からの消去パルスEraseの出力タイミングを制御することで、EL素子E1の1サブフレームにおける点灯期間が制御され、これにより所定のガンマ特性およびディマー特性を実現することができる。

【0047】

図8は、図6および図7に示した構成によってなされるPLE制御を説明するものである。このPLE制御を実現させるにあたって、この実施の形態においては1フレーム期間を複数のサブフレームに分割し、このサブフレームにおける画素の点灯期間の累計により階調制御を実現する階調制御手段が採用されている。

【0048】

すなわち図8に示す例は、説明を単純化するために1フレーム期間を7つのサブフレーム(SF1〜SF7)に分割し、1フレーム期間における各サブフレームを選択することで、8つの階調表現(100%非点灯も1つの階調と見なすことができ、7+1の階調表現)を実現する例を示している。

【0049】

図8(a)および(b)は、表示パネル31に配列された前記した画素32の点灯率(前記したVRAM1に書き込まれた画素の点灯率)に応じて、サブフレームごとの点灯期間と非点灯期間の割合を制御する例を示したものである。すなわち、(a)はサブフレームごとの点灯期間の割合が大きく、また(b)はサブフレームごとの点灯期間の割合が小さい場合を示している。なお、前記(a)および(b)は共に階調特性のガンマ値が同一で、ディマー特性が変更される例を示している。

【0050】

ここで、画素の点灯率が低い場合(換言すればAPLが小さい場合)においては、図8(a)に示す点灯制御が実行され、画素の点灯率が高い場合(APLが大きい場合)においては図8(b)に示す点灯制御が実行されるように制御される。要するに画素の点灯率の程度に応じて、サブフレームごとの点灯期間の割合が図8(a)と(b)の間で変化するように制御される。これにより、特に画素の点灯率が高い場合においては1フレーム期間内における画素の点灯期間の累計が低く抑えられ、各画素に供給される駆動電流値を抑制することができる。

【0051】

図8(c)および(d)は、図8(b)に示した点灯制御を実現させる場合の前記した書き込みパルスおよび消去パルスの発生タイミングを説明するものである。すなわち、図8に示す例においては、各サブフレームのスタートに同期して(c)に示す書き込みパルスが発生し、これにより画素は点灯状態にされる。そして、そのサブフレームの経過途中において(d)に示す消去パルスが発生し、これにより画素は非点灯状態にされる。

【0052】

ここで、例えば階調“8”を実現しようとした場合には、1フレーム期間において、画素は図8(a)または(b)に示す一連の点灯パターンが実行される。また例えば階調“5”を実現しようとした場合には、図8(a)または(b)に示すSf1〜Sf4の期間において点灯駆動動作が実行され、それ以降の各サブフレームの期間Sf5〜Sf7は全て消灯状態にされる。これにより、1フレーム期間における画素の点灯期間の累計にしたがった発光輝度を得ることができる。

【0053】

図8(d)に示す消去パルスは、次に説明する図9に示す構成によって生成することができる。図9における符号38はサブフレームカウンタを、符号39は論理演算ユニットを、さらに符号13は図6に基づいて説明した輝度設定テーブルを示している。すなわち、前記輝度設定テーブル13が図6に示したように発光制御回路11に対して外付けになされ、サブフレームカウンタ38および論理演算ユニット39は、発光制御回路11に内蔵された構成にされている。

【0054】

前記輝度設定テーブル13には、前記した点灯率に対応して各サブフレームごとの点灯期間がパラメータとして格納されている。そして、サブフレームカウンタ38より、点灯制御されるべきサブフレームナンバが論理演算ユニット39に供給された場合、論理演算ユニット39はテーブル13をアクセスし、サブフレームナンバに対応して格納されている点灯時間のパラメータに基づいて、前記消去パルスの出力タイミング信号を生成するように動作する。

【0055】

これは図8(d)に示したように画素の点灯率にそれぞれ対応してサブフレームごとの消去パルスの出力タイミング信号として生成される。このタイミング信号は前記した消去ドライバ23に供給され、消去ドライバ23からは前記したとおり、各サブフレームごとに消去パルスを出力するように動作する。

【0056】

なお、この実施の形態においてはサブフレームに同期して画像メモリ1に書き込まれている映像信号より前記した点灯率を求め、この点灯率に基づいて、輝度設定テーブル13にアクセスすることにより図9に示した構成により消去パルスの出力タイミング信号を生成するように動作する。

【0057】

したがって、これによるとサブフレーム毎に点灯率(=APL)に基づいた輝度制御(PLE制御)が実行されることになり、図4および図5に示した基本構成で説明した作用効果と同様に、少ない容量(1フレーム分)の映像メモリを利用しつつ、映像表示の不具合の発生を解消させることができると共に、電源回路に過負荷をもたらす問題も解消することができる。

【0058】

なお、図6〜図9に示した実施の形態においては、先に説明したように各サブフレームに同期して、サブフレーム毎にVRAM1にアクセスして点灯率(=APL)を算出し、この算出結果に基づいて、その都度輝度制御(PLE制御)を実行するようにしている。すなわち、この動作を模式的に示すと図10に示すようになる。

【0059】

しかしながら、現実的には1フレーム期間をより多数のサブフレームに分割して、例えば32段階もしくは64段階等の実用的な階調制御を実現するようにされる。このような場合においては、図10に示すようにサブフレーム毎にVRAM1にアクセスして点灯率(=APL)を算出することは必ずしも必要ではなく、例えば図11に示すように複数サブフレーム毎にVRAM1にアクセスして点灯率(=APL)を算出し、次の複数のサブフレームの期間においては、この点灯率に基づいて輝度制御(PLE制御)を実行するようにしてもよい。

【図面の簡単な説明】

【0060】

【図1】従来の表示制御装置の基本構成例を示したブロック図である。

【図2】従来の表示制御装置の他の基本構成例を示したブロック図である。

【図3】図2に示す表示制御装置のPLE作用を説明するタイミング図である。

【図4】この発明にかかる表示制御装置の基本構成を示したブロック図である。

【図5】図4に示す表示制御装置のPLE作用を説明するタイミング図である。

【図6】この発明を採用した表示制御装置の実施の形態を示したブロック図である。

【図7】図6に示す表示パネルに配列された画素の構成例を示した回路構成図である。

【図8】図6に示す表示制御装置における動作を説明するタイミング図である。

【図9】図6に示す構成において利用される輝度設定の基本機能を説明するブロック図である。

【図10】この発明にかかる表示制御装置においてなされるAPL算出動作を説明するタイミング図である。

【図11】同じく他のAPL算出動作を説明するタイミング図である。

【符号の説明】

【0061】

1 映像メモリ

2 平均輝度算出手段

3 輝度制御手段

11 発光制御回路

12 A/D変換回路

13 輝度設定テーブル

21 走査ドライバ

22 データドライバ

23 消去ドライバ

24 電源供給回路

31 表示パネル

32 画素

33 走査線

34 データ線

35 消去信号線

36 電源供給線

A 表示制御装置

B 映像表示手段

C1 電荷保持用キャパシタ

E1 有機EL素子

Tr1 データ書き込みトランジスタ

Tr2 点灯駆動トランジスタ

Tr3 消去トランジスタ

【特許請求の範囲】

【請求項1】

入力される映像信号に基づいて映像を表示する表示手段を駆動制御するための表示制御装置であって、

前記映像信号の平均輝度を算出する平均輝度算出手段と、前記平均輝度算出手段により得られる前記平均輝度に基づいて、前記映像信号の輝度を制御する輝度制御手段とが具備され、

前記平均輝度算出手段は、1フレーム期間内において複数回にわたり映像信号の平均輝度を算出し、算出された前記平均輝度に基づいて前記輝度制御手段の輝度制御を実行するように構成されていることを特徴とする映像信号の表示制御装置。

【請求項2】

少なくとも1フレーム期間の映像信号が書き込み可能な映像メモリに対して、入力される映像信号が書き込まれ、前記平均輝度算出手段は1フレーム期間内における前記複数回のタイミングにおいて、前記映像メモリに書き込まれた前記映像信号から平均輝度を算出するように構成されていることを特徴とする請求項1に記載された映像信号の表示制御装置。

【請求項3】

1フレーム期間内において複数回にわたり算出される前記平均輝度のうちの少なくとも1つは、互いに異なるフレームに含まれる前記映像信号に基づいて算出されることを特徴とする請求項1または請求項2に記載された映像信号の表示制御装置。

【請求項4】

1フレーム期間を複数のサブフレームに分割し、前記サブフレームにおける画素の点灯期間の累計により階調制御を実現する表示手段を駆動制御するものであり、

前記平均輝度算出手段は、前記サブフレームに同期して前記平均輝度を算出するように構成されていることを特徴とする請求項1ないし請求項3のいずれか1項に記載された映像信号の表示制御装置。

【請求項5】

前記サブフレーム毎に前記平均輝度を算出するように構成されていることを特徴とする請求項4に記載された映像信号の表示制御装置。

【請求項6】

入力される映像信号に基づいて映像を表示する表示手段を駆動制御するための表示制御方法であって、

1フレーム期間内において複数回にわたり映像信号の平均輝度を算出すると共に、算出された前記平均輝度に基づいて、前記表示手段に与える映像信号の輝度を制御する輝度制御動作を実行することを特徴とする映像信号の表示制御方法。

【請求項7】

少なくとも1フレーム期間の映像信号が書き込み可能な映像メモリに対して、入力される映像信号を書き換えつつ格納すると共に、1フレーム期間内における前記複数回のタイミングにおいて、前記映像メモリに書き込まれた前記映像信号から平均輝度を算出することを特徴とする請求項6に記載された映像信号の表示制御方法。

【請求項8】

1フレーム期間内において複数回にわたり算出される前記平均輝度のうちの少なくとも1つは、互いに異なるフレームに含まれる前記映像信号に基づいて算出されることを特徴とする請求項6または請求項7に記載された映像信号の表示制御方法。

【請求項9】

前記表示手段に与える映像信号の輝度は、算出される前記平均輝度が大きくなるにしたがって小さくなるように制御されることを特徴とする請求項6ないし請求項8のいずれか1項に記載された映像信号の表示制御方法。

【請求項1】

入力される映像信号に基づいて映像を表示する表示手段を駆動制御するための表示制御装置であって、

前記映像信号の平均輝度を算出する平均輝度算出手段と、前記平均輝度算出手段により得られる前記平均輝度に基づいて、前記映像信号の輝度を制御する輝度制御手段とが具備され、

前記平均輝度算出手段は、1フレーム期間内において複数回にわたり映像信号の平均輝度を算出し、算出された前記平均輝度に基づいて前記輝度制御手段の輝度制御を実行するように構成されていることを特徴とする映像信号の表示制御装置。

【請求項2】

少なくとも1フレーム期間の映像信号が書き込み可能な映像メモリに対して、入力される映像信号が書き込まれ、前記平均輝度算出手段は1フレーム期間内における前記複数回のタイミングにおいて、前記映像メモリに書き込まれた前記映像信号から平均輝度を算出するように構成されていることを特徴とする請求項1に記載された映像信号の表示制御装置。

【請求項3】

1フレーム期間内において複数回にわたり算出される前記平均輝度のうちの少なくとも1つは、互いに異なるフレームに含まれる前記映像信号に基づいて算出されることを特徴とする請求項1または請求項2に記載された映像信号の表示制御装置。

【請求項4】

1フレーム期間を複数のサブフレームに分割し、前記サブフレームにおける画素の点灯期間の累計により階調制御を実現する表示手段を駆動制御するものであり、

前記平均輝度算出手段は、前記サブフレームに同期して前記平均輝度を算出するように構成されていることを特徴とする請求項1ないし請求項3のいずれか1項に記載された映像信号の表示制御装置。

【請求項5】

前記サブフレーム毎に前記平均輝度を算出するように構成されていることを特徴とする請求項4に記載された映像信号の表示制御装置。

【請求項6】

入力される映像信号に基づいて映像を表示する表示手段を駆動制御するための表示制御方法であって、

1フレーム期間内において複数回にわたり映像信号の平均輝度を算出すると共に、算出された前記平均輝度に基づいて、前記表示手段に与える映像信号の輝度を制御する輝度制御動作を実行することを特徴とする映像信号の表示制御方法。

【請求項7】

少なくとも1フレーム期間の映像信号が書き込み可能な映像メモリに対して、入力される映像信号を書き換えつつ格納すると共に、1フレーム期間内における前記複数回のタイミングにおいて、前記映像メモリに書き込まれた前記映像信号から平均輝度を算出することを特徴とする請求項6に記載された映像信号の表示制御方法。

【請求項8】

1フレーム期間内において複数回にわたり算出される前記平均輝度のうちの少なくとも1つは、互いに異なるフレームに含まれる前記映像信号に基づいて算出されることを特徴とする請求項6または請求項7に記載された映像信号の表示制御方法。

【請求項9】

前記表示手段に与える映像信号の輝度は、算出される前記平均輝度が大きくなるにしたがって小さくなるように制御されることを特徴とする請求項6ないし請求項8のいずれか1項に記載された映像信号の表示制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2007−147731(P2007−147731A)

【公開日】平成19年6月14日(2007.6.14)

【国際特許分類】

【出願番号】特願2005−338725(P2005−338725)

【出願日】平成17年11月24日(2005.11.24)

【出願人】(000221926)東北パイオニア株式会社 (474)

【Fターム(参考)】

【公開日】平成19年6月14日(2007.6.14)

【国際特許分類】

【出願日】平成17年11月24日(2005.11.24)

【出願人】(000221926)東北パイオニア株式会社 (474)

【Fターム(参考)】

[ Back to top ]