映像信号処理装置

【課題】量子化された映像信号のノイズを低減させることができる映像信号処理装置を提供することを目的とするものである。

【解決手段】入力映像信号の最下位ビット側にビット数(m−n)のビット列を付加したビット付加映像信号、及びこのビット付加映像信号に対して平滑化処理を施して得られた平滑化映像信号の内のいずれか一方を、上記ビット付加映像信号及び平滑化映像信号の差分値と所定閾値との大小比較結果に応じて選択し、これをビット拡張映像信号として出力する。

【解決手段】入力映像信号の最下位ビット側にビット数(m−n)のビット列を付加したビット付加映像信号、及びこのビット付加映像信号に対して平滑化処理を施して得られた平滑化映像信号の内のいずれか一方を、上記ビット付加映像信号及び平滑化映像信号の差分値と所定閾値との大小比較結果に応じて選択し、これをビット拡張映像信号として出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、量子化された映像信号のビット数を拡張する映像信号処理装置に関する。

【背景技術】

【0002】

現在、量子化された映像信号の量子化誤差を低減させるべく、量子化後の映像信号のビット数を増加させるようにした映像信号処理装置が知られている(例えば特許文献1)。

【0003】

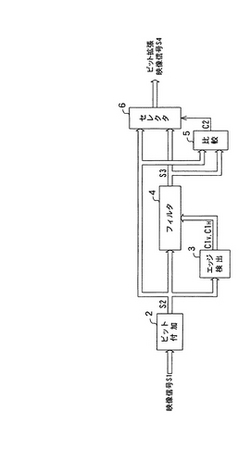

図1は、かかる映像信号処理装置の構成を示す図である。

【0004】

図1において、10ビット化回路102は、入力された8ビットの映像信号S1のLSB(最下位ビット)側に2ビットの[00]なるビット列を付加して、10ビットの映像信号S2を生成する。ローパスフィルタ103は、映像信号S2に対してフィルタ処理を施して得られた映像信号S3をLSB抽出器104及び制御信号出力手段120の加算器105に供給する。加算器105は、10ビットの映像信号S2から上記映像信号S3を減算し、これを差分信号S5として比較器106に供給する。比較器106は、この差分信号S5の絶対値が所定閾値よりも大であるか否かを判定しその判定結果に対応した制御信号C1を生成する。尚、所定閾値とは、10ビット化回路102において付加されるビット列に対する桁上げの値、つまりこのビット列によって表現可能な最大値よりも「1」だけ大なる値である。例えば、10ビット化回路102において付加されるビット列が2ビットである場合、所定閾値は、かかるビット列によって表現可能な最大値「3」に「1」を加算した「4」となる。又、比較器106は、差分信号S5が上記所定閾値より小なる正の数であるか否かを判定しその判定結果に対応した制御信号C2を生成する。加算器107は、差分信号S5が所定閾値より小なる正の数であるという判定結果を示す制御信号C2が供給された場合には、上記映像信号S2から上記所定閾値を減算した信号を映像信号S6として加算器109に供給する。一方、差分信号S5が所定閾値より小なる正の数ではないという判定結果を示す制御信号C2が供給された場合、つまり差分信号S5が所定閾値よりも大又は負の数である場合に、加算器107は、かかる差分信号S5をそのまま映像信号S6として加算器109に供給する。LSB抽出器104は、10ビットの映像信号S3中から最下位の2ビット分を抽出しこれを信号S4としてスイッチ108に供給する。スイッチ108は、上記差分信号S5の絶対値が所定閾値よりも小であるという判定結果に対応した制御信号C1が供給された場合に限りオン状態となって、上記信号S4を加算器109に供給する。一方、上記差分信号S5の絶対値が所定閾値よりも小ではないという判定結果に対応した制御信号C1が供給された場合には、スイッチ108はオフ状態となる。つまり、この際、加算器109にはレベル「0」の信号が供給されることになる。加算器109は、上記映像信号S6に、スイッチ108から供給された信号を加算した加算結果を、量子化誤差を低減させた映像信号S7として出力する。

【0005】

すなわち、図1に示される映像信号処理装置においては、先ず、8ビットの映像信号S1のLSB側に2ビット分のビット列[00]を強制的に付加して10ビットの映像信号S2を生成する。次に、かかる映像信号S2を平滑化(LPF103)した映像信号S3中から最下位の2ビット分を抽出(LSB抽出器104)することにより、拡張分の下位2ビット(S4)を生成する。そして、上記映像信号S2に、この拡張分の下位2ビットの値を加算(加算器109)することにより、8ビットから10ビットに拡張した映像信号S7を生成するのである。

【0006】

ここで、図1に示される映像信号処理では、拡張分の下位2ビットのデータを生成する為に、ローパスフィルタを用いて映像信号を平滑化するようにしている。ところが、映像信号に対してローパスフィルタによるフィルタリング処理を施すと、その信号レベルが変化するエッジ部周辺の平坦部において不要なリンギングが発生する。この際、比較器106における所定閾値よりも大のリンギングは排除されるが、所定閾値よりも大ではないリンギングは排除されずに残ってしまい、これが新たなノイズとなって映像信号に重畳してしまうという問題があった。

【特許文献1】特開平08−237669号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明は、かかる問題を解決すべく為されたものであり、量子化された映像信号のノイズを低減させることができる映像信号処理装置を提供することを目的とするものである。

【課題を解決するための手段】

【0008】

請求項1記載による映像信号処理装置は、量子化されたnビットの入力映像信号からmビット(m>n)のビット拡張映像信号を生成する映像信号処理装置であって、前記入力映像信号の最下位ビット側にビット数(m−n)のビット列を付加してビット付加映像信号を生成するビット付加手段と、前記ビット付加映像信号に対して平滑化処理を施して平滑化映像信号を生成するフィルタと、前記ビット付加映像信号と前記平滑化映像信号との差分値と、所定閾値との大小を比較する比較手段と、前記ビット付加映像信号及び前記平滑化映像信号の内のいずれか一方を前記比較手段による比較結果に応じて選択しこれを前記ビット拡張映像信号として出力するセレクタと、を有する。

【発明を実施するための最良の形態】

【0009】

入力映像信号の最下位ビット側にビット数(m−n)のビット列を付加したビット付加映像信号、及びこのビット付加映像信号に対して平滑化処理を施して得られた平滑化映像信号の内のいずれか一方を、上記ビット付加映像信号及び平滑化映像信号の差分値と所定閾値との大小比較結果に応じて選択し、これをビット拡張映像信号として出力する。

【実施例】

【0010】

図2は、本発明による映像信号処理装置の概略構成を示す図である。

【0011】

図2において、ビット付加回路2は、ディスプレイ装置(図示せぬ)の各画素を発光させる際の輝度レベルを夫々nビットにて表す画素データの系列からなる入力映像信号S1における各画素データのビット数をmビット(n<m)に拡張させたビット付加映像信号S2を生成する。すなわち、ビット付加回路2は、入力映像信号S1における各画素データの最下位ビット側に(m−n)ビットからなる論理レベル0のビット列を付加することにより、各画素データのビット数をnビットからmビットに拡張させるのである。ビット付加回路2は、上記ビット付加映像信号S2をエッジ検出回路3、フィルタ4、比較器5及びセレクタ6に夫々供給する。

【0012】

エッジ検出回路3は、ビット付加映像信号S2に基づき、表示画面中の水平方向において輝度レベルが変化する部分、いわゆるエッジ部の検出を行ってそのエッジ部の画素位置を示す水平方向エッジ位置信号C1Hをフィルタ4に供給する。又、エッジ検出回路3は、上記ビット付加映像信号S2に基づき、表示画面中の垂直方向において輝度レベルが変化するエッジ部の検出を行い、そのエッジ部の画素位置を示す垂直方向エッジ位置信号C1Vをフィルタ4に供給する。尚、エッジ検出回路3は、例えば、以下の如き二次元微分オペレータ法に従って上記の如きエッジ検出を行う。

【0013】

先ず、エッジ検出回路3は、表示画面の水平及び垂直方向に隣接する9つの画素各々に対応したmビットの画素データに対して、夫々、図3(a)に示す如く割り当てられた係数を乗算し、各乗算結果の合計値を水平方向エッジ判定値Ghとして求める。次に、エッジ検出回路3は、水平方向エッジ判定値Ghが所定のエッジ判定閾値よりも大であるか否かを判定する。ここで、大であると判定された場合、エッジ検出回路3は、上記の如き9つの画素の内の中央の画素に対応した画素データがエッジ部に該当するものであると判断して、その画素位置を示す水平方向エッジ位置信号C1Hをフィルタ4に供給する。又、エッジ検出回路3は、表示画面の水平及び垂直方向に隣接する9つの画素各々に対応したmビットの画素データに対して、夫々、図3(b)に示す如く割り当てられた係数を乗算し、各乗算結果の合計値を垂直方向エッジ判定値Gvとして求める。次に、エッジ検出回路3は、垂直方向エッジ判定値Gvが所定のエッジ判定閾値よりも大であるか否かを判定する。ここで、大であると判定された場合、エッジ検出回路3は、上記の如き9つの画素の内の中央の画素に対応した画素データがエッジ部に該当するものであると判断して、その画素位置を示す垂直方向エッジ位置信号C1Vをフィルタ4に供給する。尚、上記エッジ判定閾値としては、例えばnビットの入力映像信号S1中の最下位ビット桁に対応した値(10進数表現)が設定される。つまり、エッジ検出回路3は、隣接する画素間での映像信号のレベル変化が上記最下位ビット桁に対応した値よりも小なる場合には映像の平坦部又は疑似輪郭部であると判断し、大なる場合にはエッジ部であると判断するのである。

【0014】

フィルタ4は、例えばFIR(finite impulse response)フィルタ、又はIIR(in-finite impulse response)フィルタからなる2次元ローパスフィルタを含むものである。

【0015】

図4は、かかるフィルタ4の内部構成の一例を示す図である。

【0016】

図4に示されるように、フィルタ4は、2次元ローパスフィルタ40、フレームメモリ41、及び読出制御回路42から構成される。

【0017】

フレームメモリ41は、ビット付加映像信号S2における各画素データを、図5に示す如き表示画面の各画素G(1,1)〜G(R,P)の画素位置に対応した番地に順次記憶してゆく。読出制御回路42は、フレームメモリ41に記憶されている画素データを、表示画面の水平方向に隣接するN個毎に読み出すべき読出信号をフレームメモリ41に供給する。すなわち、読出制御回路42は、先ず、図5に示す如き第1表示ラインの第1列〜第N列の画素G(1,1)〜G(1,N)各々に対応したN個の画素データを順次読み出すべき読出信号をフレームメモリ41に供給する。次に、読出制御回路42は、第1表示ラインの第2列〜第(N+1)列の画素G(1,2)〜G(1,N+1)各々に対応したN個の画素データを順次読み出すべき読出信号をフレームメモリ41に供給する。次に、読出制御回路42は、第1表示ラインの第3列〜第(N+2)列の画素G(1,3)〜G(1,N+2)各々に対応したN個の画素データを順次読み出すべき読出信号をフレームメモリ41に供給する。以下、同様にして、読出制御回路42は、N個ずつ第1表示ラインの画素各々に対応した画素データを読み出すべき読出信号をフレームメモリ41に供給する。第1表示ラインの各画素に対応した画素データの読み出しが終了すると、次に、読出制御回路42は、第2表示ラインの第1列〜第N列の画素G(2,1)〜G(2,N)各々に対応したN個の画素データを順次読み出すべき読出信号をフレームメモリ41に供給する。次に、読出制御回路42は、第2表示ラインの第2列〜第(N+1)列の画素G(2,2)〜G(2,N+1)各々に対応したN個の画素データを順次読み出すべき読出信号をフレームメモリ41に供給する。次に、読出制御回路42は、第2表示ラインの第3列〜第(N+2)列の画素G(2,3)〜G(2,N+2)各々に対応したN個の画素データを順次読み出すべき読出信号をフレームメモリ41に供給する。以下、同様にして、読出制御回路42は、N個ずつ第2表示ラインの画素各々に対応した画素データを読み出すべき読出信号をフレームメモリ41に供給する。第2表示ラインの各画素に対応した画素データの読み出し終了後、同様にして、読出制御回路42は、図5に示す如き第3表示ライン〜第R表示ラインの画素各々に対応した画素データをN個ずつ読み出すべき読出信号を繰り返しフレームメモリ41に供給する。

【0018】

ここで、フレームメモリ41からN個ずつ画素データの読み出しを行うにあたり、読出制御回路42は、水平方向に隣接するN個の連続する画素データからなる系列中にエッジ部に該当する画素データが存在するか否かを水平方向エッジ位置信号C1Hに基づき判定する。更に、読出制御回路42は、垂直方向に隣接するN個の連続する画素データからなる系列中にエッジ部に該当する画素データが存在するか否かを垂直方向エッジ位置信号C1Vに基づいて判定する。この際、エッジ部に該当する画素データが存在しない場合には、フレームメモリ41に記憶されている画素データを上述した如く各画素毎に順次読み出すべき読出制御を実行する。一方、かかる画素データ系列中にエッジ部に該当する画素データが存在する場合には、このエッジ部及びエッジ部前後の画素に対応した画素データに代わり、そのエッジ部の直前又は直後の画素データを読み出すべき読出制御を実行する。

【0019】

例えば、図6(a)に示す如きN個の画素データの系列中の前半部にエッジ部に該当する画素データPD3が存在する場合には、このエッジ部及びエッジ部周辺の画素データPD1〜PD3各々に代わり、エッジ部の画素データPD3の直後の画素データPD4を繰り返し読み出すべき制御を行う。又、図6(a)に示す如くN個の画素データの系列中の後半部にエッジ部に該当する画素データPD(N−3)が存在する場合には、このエッジ部及びエッジ部周辺の画素データPD(N−3)〜PD(N)各々に代わり、エッジ部の画素データPD(N−3)の直前の画素データPD(N−4)を繰り返し読み出すべき制御を行う。

【0020】

かかる読出制御回路42による読出制御により、フレームメモリ41は、エッジ部に該当しない画素データに対しては、これを各画素毎に順次読み出して2次元ローパルフィルタ40に供給する。この間、フレームメモリ41は、エッジ部及びエッジ部周辺の画素データに対してはこれを読み出す代わりに、このエッジ部の直前又は直後の画素データを読み出す。例えば、水平(又は垂直)方向において隣接するN個の画素各々に対応した画素データの系列が図6(a)の場合、その前半部のエッジ部に該当する画素データPD3及び周辺画素データPD1及びPD2に代わり、画素データPD3の直後の画素データPD4の値が図6(b)の如く繰り返し読み出される。又、後半部のエッジ部に該当する画素データPD(N−3)及び周辺画素データPD(N−2)及び(N−1)に代わり、画素データPD(N−3)の直前の画素データPD(N−4)の値が図6(b)の如く繰り返し読み出されて2次元ローパスフィルタ40に供給されるのである。

【0021】

2次元ローパスフィルタ40は、直列に接続されたN段の単位遅延素子D1〜D(N)及び水平方向重付加算回路43からなる水平方向ローパスフィルタと、直列に接続されたN段の1ライン遅延素子L1〜L(N)及び垂直方向重付加算回路44からなる垂直方向ローパスフィルタと、から構成される。

【0022】

単位遅延素子D1〜D(N)の各々は、フレームメモリ41から供給された各画素毎の画素データを所定時間遅延してから次段の単位遅延素子Dに出力する。よって、上述したようにフレームメモリ41からN個単位で読み出された画素データの各々は、(所定時間×N)なる時間経過後には単位遅延素子D1〜D(N)の各々に保持されることになる。ここで、(所定時間×N)なる時間が経過してN個分の画素データが単位遅延素子D1〜D(N)各々へ保持されると、水平方向重付加算回路43は、単位遅延素子D1〜D(N)各々の出力値を重み付け加算する。尚、水平方向重付加算回路43においては、単位遅延素子D(N/2)の出力値、つまりセンタータップに対する重み付けが最も大となり、このセンタータップから離れた位置に存在するタップほど重み付けが小となる。水平方向重付加算回路43は、その重み付け加算結果を1ライン遅延素子L1に供給する。1ライン遅延素子L1〜L(N)の各々は、水平方向重付加算回路43から供給された加算結果を(1水平走査ライン分の画素数×上記所定時間)なる時間だけ遅延させてから次段の1ライン遅延素子Lに出力する。垂直方向重付加算回路44は、1ライン遅延素子L1〜L(N)各々の出力値を重み付け加算して得られた加算結果を平滑化映像信号S3として出力する。尚、垂直方向重付加算回路44においては、1ライン遅延素子L(N/2)の出力値、つまりセンタータップに対する重み付けが最も大となり、このセンタータップから離れた位置に存在するタップほど重み付けが小となる。

【0023】

以上の如き構成により、フィルタ4は、表示画面の2次元の方向(垂直方向及び水平方向)各々に対して、mビットの画素データの系列からなるビット付加映像信号S2を平滑化したmビットの平滑化映像信号S3を生成する。このような2次元フィルタリング処理により、例えば、図7(a)に示す如きnビットの入力映像信号S1における1LSB分のレベル推移を図7(b)に示す如き2(m-n)段階のレベル推移に平滑化した平滑化映像信号S3が生成される。すなわち、元のnビットの映像信号よりも精細で、且つ量子化ノイズ及び疑似輪郭ノイズを低減させた映像信号が生成されるのである。

【0024】

更に、フィルタ4では、映像信号中において輝度レベルが変化するエッジ部及びエッジ部周辺の各画素データ(ビット付加映像信号S2)に対しては、これらをエッジ部の直前又は直後、つまりフィルタのセンタータップ側に近い方に隣接する画素データに置換したものでフィルタリング処理を行うようにしている。これにより、図6(a)に示す如きリンギングを含んだ映像信号が入力された場合にも、これを除去した図6(b)に示す如き映像信号に対してフィルタリング処理が為されるようになる。よって、かかるフィルタリング処理によって生成された平滑化映像信号S3は図6(c)に示されるように平滑化されたものとなり、疑似輪郭ノイズは目立たなくなる。

【0025】

比較器5は、上記ビット付加映像信号S2における各画素データの値と上記平滑化映像信号S3における各画素データの値との差分値が所定閾値Thよりも小であるか否かの比較を行う。この際、かかる差分値が所定閾値Thよりも小である場合には、比較器5は、平滑化映像信号S3を選択させるべき選択信号C2をセレクタ6に供給する。一方、この差分値が所定閾値Th以上の値である場合には、比較器5は、ビット付加映像信号S2を選択させるべき選択信号C2をセレクタ6に供給する。

【0026】

セレクタ6は、ビット付加映像信号S2及び平滑化映像信号S3の内から、上記選択信号C2によって示される方を択一的に選択し、これを量子化誤差の低減されたビット拡張映像信号S4として出力する。

【0027】

すなわち、セレクタ6は、平滑化映像信号S3における画素データの値と、ビット付加映像信号S2における画素データの値との差が所定閾値Thより小なる場合には平滑化映像信号S3をビット拡張映像信号S4として出力する一方、両者の差が所定閾値Th以上になる場合にはビット付加映像信号S2をビット拡張映像信号S4として出力する。すなわち、セレクタ6は、例えば図8(a)に示す如きビット付加映像信号S2中のエッジ部に関してはこれをそのまま図8(c)に示す如くビット拡張映像信号S4として出力し、それ以外の部分に関してはビット付加映像信号S2を平滑化した図8(b)に示す如き平滑化映像信号S3をビット拡張映像信号S4として出力するのである。

【0028】

従って、解像度向上に大きく関与するエッジ部に対してはその鈍りが抑えられると共に、疑似輪郭部のような輝度レベル変化が微小な映像信号の区間に関してはこれを平滑化して疑似輪郭ノイズを低減させることが可能になる。

【図面の簡単な説明】

【0029】

【図1】従来の映像信号処理装置の構成を示す図である。

【図2】本発明による映像信号処理装置の構成を示す図である。

【図3】二次元微分オペレータ法に従って映像信号からエッジ部を検出する際に用いる係数の一例を示す図である。

【図4】フィルタ4の内部構成の一例を示す図である。

【図5】フレームメモリ41に記憶される各画素データの表示画面内での画素位置を示す図である。

【図6】映像信号中にエッジ部が存在する場合におけるフィルタ4の内部動作の一例を示す図である。

【図7】フィルタ4のフィルタリング処理による映像信号の平滑化を表す図である。

【図8】セレクタ4の動作例を示す図である。

【符号の説明】

【0030】

2 ビット付加回路

3 エッジ検出回路

4 フィルタ

5 比較器

6 セレクタ

【技術分野】

【0001】

本発明は、量子化された映像信号のビット数を拡張する映像信号処理装置に関する。

【背景技術】

【0002】

現在、量子化された映像信号の量子化誤差を低減させるべく、量子化後の映像信号のビット数を増加させるようにした映像信号処理装置が知られている(例えば特許文献1)。

【0003】

図1は、かかる映像信号処理装置の構成を示す図である。

【0004】

図1において、10ビット化回路102は、入力された8ビットの映像信号S1のLSB(最下位ビット)側に2ビットの[00]なるビット列を付加して、10ビットの映像信号S2を生成する。ローパスフィルタ103は、映像信号S2に対してフィルタ処理を施して得られた映像信号S3をLSB抽出器104及び制御信号出力手段120の加算器105に供給する。加算器105は、10ビットの映像信号S2から上記映像信号S3を減算し、これを差分信号S5として比較器106に供給する。比較器106は、この差分信号S5の絶対値が所定閾値よりも大であるか否かを判定しその判定結果に対応した制御信号C1を生成する。尚、所定閾値とは、10ビット化回路102において付加されるビット列に対する桁上げの値、つまりこのビット列によって表現可能な最大値よりも「1」だけ大なる値である。例えば、10ビット化回路102において付加されるビット列が2ビットである場合、所定閾値は、かかるビット列によって表現可能な最大値「3」に「1」を加算した「4」となる。又、比較器106は、差分信号S5が上記所定閾値より小なる正の数であるか否かを判定しその判定結果に対応した制御信号C2を生成する。加算器107は、差分信号S5が所定閾値より小なる正の数であるという判定結果を示す制御信号C2が供給された場合には、上記映像信号S2から上記所定閾値を減算した信号を映像信号S6として加算器109に供給する。一方、差分信号S5が所定閾値より小なる正の数ではないという判定結果を示す制御信号C2が供給された場合、つまり差分信号S5が所定閾値よりも大又は負の数である場合に、加算器107は、かかる差分信号S5をそのまま映像信号S6として加算器109に供給する。LSB抽出器104は、10ビットの映像信号S3中から最下位の2ビット分を抽出しこれを信号S4としてスイッチ108に供給する。スイッチ108は、上記差分信号S5の絶対値が所定閾値よりも小であるという判定結果に対応した制御信号C1が供給された場合に限りオン状態となって、上記信号S4を加算器109に供給する。一方、上記差分信号S5の絶対値が所定閾値よりも小ではないという判定結果に対応した制御信号C1が供給された場合には、スイッチ108はオフ状態となる。つまり、この際、加算器109にはレベル「0」の信号が供給されることになる。加算器109は、上記映像信号S6に、スイッチ108から供給された信号を加算した加算結果を、量子化誤差を低減させた映像信号S7として出力する。

【0005】

すなわち、図1に示される映像信号処理装置においては、先ず、8ビットの映像信号S1のLSB側に2ビット分のビット列[00]を強制的に付加して10ビットの映像信号S2を生成する。次に、かかる映像信号S2を平滑化(LPF103)した映像信号S3中から最下位の2ビット分を抽出(LSB抽出器104)することにより、拡張分の下位2ビット(S4)を生成する。そして、上記映像信号S2に、この拡張分の下位2ビットの値を加算(加算器109)することにより、8ビットから10ビットに拡張した映像信号S7を生成するのである。

【0006】

ここで、図1に示される映像信号処理では、拡張分の下位2ビットのデータを生成する為に、ローパスフィルタを用いて映像信号を平滑化するようにしている。ところが、映像信号に対してローパスフィルタによるフィルタリング処理を施すと、その信号レベルが変化するエッジ部周辺の平坦部において不要なリンギングが発生する。この際、比較器106における所定閾値よりも大のリンギングは排除されるが、所定閾値よりも大ではないリンギングは排除されずに残ってしまい、これが新たなノイズとなって映像信号に重畳してしまうという問題があった。

【特許文献1】特開平08−237669号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

本発明は、かかる問題を解決すべく為されたものであり、量子化された映像信号のノイズを低減させることができる映像信号処理装置を提供することを目的とするものである。

【課題を解決するための手段】

【0008】

請求項1記載による映像信号処理装置は、量子化されたnビットの入力映像信号からmビット(m>n)のビット拡張映像信号を生成する映像信号処理装置であって、前記入力映像信号の最下位ビット側にビット数(m−n)のビット列を付加してビット付加映像信号を生成するビット付加手段と、前記ビット付加映像信号に対して平滑化処理を施して平滑化映像信号を生成するフィルタと、前記ビット付加映像信号と前記平滑化映像信号との差分値と、所定閾値との大小を比較する比較手段と、前記ビット付加映像信号及び前記平滑化映像信号の内のいずれか一方を前記比較手段による比較結果に応じて選択しこれを前記ビット拡張映像信号として出力するセレクタと、を有する。

【発明を実施するための最良の形態】

【0009】

入力映像信号の最下位ビット側にビット数(m−n)のビット列を付加したビット付加映像信号、及びこのビット付加映像信号に対して平滑化処理を施して得られた平滑化映像信号の内のいずれか一方を、上記ビット付加映像信号及び平滑化映像信号の差分値と所定閾値との大小比較結果に応じて選択し、これをビット拡張映像信号として出力する。

【実施例】

【0010】

図2は、本発明による映像信号処理装置の概略構成を示す図である。

【0011】

図2において、ビット付加回路2は、ディスプレイ装置(図示せぬ)の各画素を発光させる際の輝度レベルを夫々nビットにて表す画素データの系列からなる入力映像信号S1における各画素データのビット数をmビット(n<m)に拡張させたビット付加映像信号S2を生成する。すなわち、ビット付加回路2は、入力映像信号S1における各画素データの最下位ビット側に(m−n)ビットからなる論理レベル0のビット列を付加することにより、各画素データのビット数をnビットからmビットに拡張させるのである。ビット付加回路2は、上記ビット付加映像信号S2をエッジ検出回路3、フィルタ4、比較器5及びセレクタ6に夫々供給する。

【0012】

エッジ検出回路3は、ビット付加映像信号S2に基づき、表示画面中の水平方向において輝度レベルが変化する部分、いわゆるエッジ部の検出を行ってそのエッジ部の画素位置を示す水平方向エッジ位置信号C1Hをフィルタ4に供給する。又、エッジ検出回路3は、上記ビット付加映像信号S2に基づき、表示画面中の垂直方向において輝度レベルが変化するエッジ部の検出を行い、そのエッジ部の画素位置を示す垂直方向エッジ位置信号C1Vをフィルタ4に供給する。尚、エッジ検出回路3は、例えば、以下の如き二次元微分オペレータ法に従って上記の如きエッジ検出を行う。

【0013】

先ず、エッジ検出回路3は、表示画面の水平及び垂直方向に隣接する9つの画素各々に対応したmビットの画素データに対して、夫々、図3(a)に示す如く割り当てられた係数を乗算し、各乗算結果の合計値を水平方向エッジ判定値Ghとして求める。次に、エッジ検出回路3は、水平方向エッジ判定値Ghが所定のエッジ判定閾値よりも大であるか否かを判定する。ここで、大であると判定された場合、エッジ検出回路3は、上記の如き9つの画素の内の中央の画素に対応した画素データがエッジ部に該当するものであると判断して、その画素位置を示す水平方向エッジ位置信号C1Hをフィルタ4に供給する。又、エッジ検出回路3は、表示画面の水平及び垂直方向に隣接する9つの画素各々に対応したmビットの画素データに対して、夫々、図3(b)に示す如く割り当てられた係数を乗算し、各乗算結果の合計値を垂直方向エッジ判定値Gvとして求める。次に、エッジ検出回路3は、垂直方向エッジ判定値Gvが所定のエッジ判定閾値よりも大であるか否かを判定する。ここで、大であると判定された場合、エッジ検出回路3は、上記の如き9つの画素の内の中央の画素に対応した画素データがエッジ部に該当するものであると判断して、その画素位置を示す垂直方向エッジ位置信号C1Vをフィルタ4に供給する。尚、上記エッジ判定閾値としては、例えばnビットの入力映像信号S1中の最下位ビット桁に対応した値(10進数表現)が設定される。つまり、エッジ検出回路3は、隣接する画素間での映像信号のレベル変化が上記最下位ビット桁に対応した値よりも小なる場合には映像の平坦部又は疑似輪郭部であると判断し、大なる場合にはエッジ部であると判断するのである。

【0014】

フィルタ4は、例えばFIR(finite impulse response)フィルタ、又はIIR(in-finite impulse response)フィルタからなる2次元ローパスフィルタを含むものである。

【0015】

図4は、かかるフィルタ4の内部構成の一例を示す図である。

【0016】

図4に示されるように、フィルタ4は、2次元ローパスフィルタ40、フレームメモリ41、及び読出制御回路42から構成される。

【0017】

フレームメモリ41は、ビット付加映像信号S2における各画素データを、図5に示す如き表示画面の各画素G(1,1)〜G(R,P)の画素位置に対応した番地に順次記憶してゆく。読出制御回路42は、フレームメモリ41に記憶されている画素データを、表示画面の水平方向に隣接するN個毎に読み出すべき読出信号をフレームメモリ41に供給する。すなわち、読出制御回路42は、先ず、図5に示す如き第1表示ラインの第1列〜第N列の画素G(1,1)〜G(1,N)各々に対応したN個の画素データを順次読み出すべき読出信号をフレームメモリ41に供給する。次に、読出制御回路42は、第1表示ラインの第2列〜第(N+1)列の画素G(1,2)〜G(1,N+1)各々に対応したN個の画素データを順次読み出すべき読出信号をフレームメモリ41に供給する。次に、読出制御回路42は、第1表示ラインの第3列〜第(N+2)列の画素G(1,3)〜G(1,N+2)各々に対応したN個の画素データを順次読み出すべき読出信号をフレームメモリ41に供給する。以下、同様にして、読出制御回路42は、N個ずつ第1表示ラインの画素各々に対応した画素データを読み出すべき読出信号をフレームメモリ41に供給する。第1表示ラインの各画素に対応した画素データの読み出しが終了すると、次に、読出制御回路42は、第2表示ラインの第1列〜第N列の画素G(2,1)〜G(2,N)各々に対応したN個の画素データを順次読み出すべき読出信号をフレームメモリ41に供給する。次に、読出制御回路42は、第2表示ラインの第2列〜第(N+1)列の画素G(2,2)〜G(2,N+1)各々に対応したN個の画素データを順次読み出すべき読出信号をフレームメモリ41に供給する。次に、読出制御回路42は、第2表示ラインの第3列〜第(N+2)列の画素G(2,3)〜G(2,N+2)各々に対応したN個の画素データを順次読み出すべき読出信号をフレームメモリ41に供給する。以下、同様にして、読出制御回路42は、N個ずつ第2表示ラインの画素各々に対応した画素データを読み出すべき読出信号をフレームメモリ41に供給する。第2表示ラインの各画素に対応した画素データの読み出し終了後、同様にして、読出制御回路42は、図5に示す如き第3表示ライン〜第R表示ラインの画素各々に対応した画素データをN個ずつ読み出すべき読出信号を繰り返しフレームメモリ41に供給する。

【0018】

ここで、フレームメモリ41からN個ずつ画素データの読み出しを行うにあたり、読出制御回路42は、水平方向に隣接するN個の連続する画素データからなる系列中にエッジ部に該当する画素データが存在するか否かを水平方向エッジ位置信号C1Hに基づき判定する。更に、読出制御回路42は、垂直方向に隣接するN個の連続する画素データからなる系列中にエッジ部に該当する画素データが存在するか否かを垂直方向エッジ位置信号C1Vに基づいて判定する。この際、エッジ部に該当する画素データが存在しない場合には、フレームメモリ41に記憶されている画素データを上述した如く各画素毎に順次読み出すべき読出制御を実行する。一方、かかる画素データ系列中にエッジ部に該当する画素データが存在する場合には、このエッジ部及びエッジ部前後の画素に対応した画素データに代わり、そのエッジ部の直前又は直後の画素データを読み出すべき読出制御を実行する。

【0019】

例えば、図6(a)に示す如きN個の画素データの系列中の前半部にエッジ部に該当する画素データPD3が存在する場合には、このエッジ部及びエッジ部周辺の画素データPD1〜PD3各々に代わり、エッジ部の画素データPD3の直後の画素データPD4を繰り返し読み出すべき制御を行う。又、図6(a)に示す如くN個の画素データの系列中の後半部にエッジ部に該当する画素データPD(N−3)が存在する場合には、このエッジ部及びエッジ部周辺の画素データPD(N−3)〜PD(N)各々に代わり、エッジ部の画素データPD(N−3)の直前の画素データPD(N−4)を繰り返し読み出すべき制御を行う。

【0020】

かかる読出制御回路42による読出制御により、フレームメモリ41は、エッジ部に該当しない画素データに対しては、これを各画素毎に順次読み出して2次元ローパルフィルタ40に供給する。この間、フレームメモリ41は、エッジ部及びエッジ部周辺の画素データに対してはこれを読み出す代わりに、このエッジ部の直前又は直後の画素データを読み出す。例えば、水平(又は垂直)方向において隣接するN個の画素各々に対応した画素データの系列が図6(a)の場合、その前半部のエッジ部に該当する画素データPD3及び周辺画素データPD1及びPD2に代わり、画素データPD3の直後の画素データPD4の値が図6(b)の如く繰り返し読み出される。又、後半部のエッジ部に該当する画素データPD(N−3)及び周辺画素データPD(N−2)及び(N−1)に代わり、画素データPD(N−3)の直前の画素データPD(N−4)の値が図6(b)の如く繰り返し読み出されて2次元ローパスフィルタ40に供給されるのである。

【0021】

2次元ローパスフィルタ40は、直列に接続されたN段の単位遅延素子D1〜D(N)及び水平方向重付加算回路43からなる水平方向ローパスフィルタと、直列に接続されたN段の1ライン遅延素子L1〜L(N)及び垂直方向重付加算回路44からなる垂直方向ローパスフィルタと、から構成される。

【0022】

単位遅延素子D1〜D(N)の各々は、フレームメモリ41から供給された各画素毎の画素データを所定時間遅延してから次段の単位遅延素子Dに出力する。よって、上述したようにフレームメモリ41からN個単位で読み出された画素データの各々は、(所定時間×N)なる時間経過後には単位遅延素子D1〜D(N)の各々に保持されることになる。ここで、(所定時間×N)なる時間が経過してN個分の画素データが単位遅延素子D1〜D(N)各々へ保持されると、水平方向重付加算回路43は、単位遅延素子D1〜D(N)各々の出力値を重み付け加算する。尚、水平方向重付加算回路43においては、単位遅延素子D(N/2)の出力値、つまりセンタータップに対する重み付けが最も大となり、このセンタータップから離れた位置に存在するタップほど重み付けが小となる。水平方向重付加算回路43は、その重み付け加算結果を1ライン遅延素子L1に供給する。1ライン遅延素子L1〜L(N)の各々は、水平方向重付加算回路43から供給された加算結果を(1水平走査ライン分の画素数×上記所定時間)なる時間だけ遅延させてから次段の1ライン遅延素子Lに出力する。垂直方向重付加算回路44は、1ライン遅延素子L1〜L(N)各々の出力値を重み付け加算して得られた加算結果を平滑化映像信号S3として出力する。尚、垂直方向重付加算回路44においては、1ライン遅延素子L(N/2)の出力値、つまりセンタータップに対する重み付けが最も大となり、このセンタータップから離れた位置に存在するタップほど重み付けが小となる。

【0023】

以上の如き構成により、フィルタ4は、表示画面の2次元の方向(垂直方向及び水平方向)各々に対して、mビットの画素データの系列からなるビット付加映像信号S2を平滑化したmビットの平滑化映像信号S3を生成する。このような2次元フィルタリング処理により、例えば、図7(a)に示す如きnビットの入力映像信号S1における1LSB分のレベル推移を図7(b)に示す如き2(m-n)段階のレベル推移に平滑化した平滑化映像信号S3が生成される。すなわち、元のnビットの映像信号よりも精細で、且つ量子化ノイズ及び疑似輪郭ノイズを低減させた映像信号が生成されるのである。

【0024】

更に、フィルタ4では、映像信号中において輝度レベルが変化するエッジ部及びエッジ部周辺の各画素データ(ビット付加映像信号S2)に対しては、これらをエッジ部の直前又は直後、つまりフィルタのセンタータップ側に近い方に隣接する画素データに置換したものでフィルタリング処理を行うようにしている。これにより、図6(a)に示す如きリンギングを含んだ映像信号が入力された場合にも、これを除去した図6(b)に示す如き映像信号に対してフィルタリング処理が為されるようになる。よって、かかるフィルタリング処理によって生成された平滑化映像信号S3は図6(c)に示されるように平滑化されたものとなり、疑似輪郭ノイズは目立たなくなる。

【0025】

比較器5は、上記ビット付加映像信号S2における各画素データの値と上記平滑化映像信号S3における各画素データの値との差分値が所定閾値Thよりも小であるか否かの比較を行う。この際、かかる差分値が所定閾値Thよりも小である場合には、比較器5は、平滑化映像信号S3を選択させるべき選択信号C2をセレクタ6に供給する。一方、この差分値が所定閾値Th以上の値である場合には、比較器5は、ビット付加映像信号S2を選択させるべき選択信号C2をセレクタ6に供給する。

【0026】

セレクタ6は、ビット付加映像信号S2及び平滑化映像信号S3の内から、上記選択信号C2によって示される方を択一的に選択し、これを量子化誤差の低減されたビット拡張映像信号S4として出力する。

【0027】

すなわち、セレクタ6は、平滑化映像信号S3における画素データの値と、ビット付加映像信号S2における画素データの値との差が所定閾値Thより小なる場合には平滑化映像信号S3をビット拡張映像信号S4として出力する一方、両者の差が所定閾値Th以上になる場合にはビット付加映像信号S2をビット拡張映像信号S4として出力する。すなわち、セレクタ6は、例えば図8(a)に示す如きビット付加映像信号S2中のエッジ部に関してはこれをそのまま図8(c)に示す如くビット拡張映像信号S4として出力し、それ以外の部分に関してはビット付加映像信号S2を平滑化した図8(b)に示す如き平滑化映像信号S3をビット拡張映像信号S4として出力するのである。

【0028】

従って、解像度向上に大きく関与するエッジ部に対してはその鈍りが抑えられると共に、疑似輪郭部のような輝度レベル変化が微小な映像信号の区間に関してはこれを平滑化して疑似輪郭ノイズを低減させることが可能になる。

【図面の簡単な説明】

【0029】

【図1】従来の映像信号処理装置の構成を示す図である。

【図2】本発明による映像信号処理装置の構成を示す図である。

【図3】二次元微分オペレータ法に従って映像信号からエッジ部を検出する際に用いる係数の一例を示す図である。

【図4】フィルタ4の内部構成の一例を示す図である。

【図5】フレームメモリ41に記憶される各画素データの表示画面内での画素位置を示す図である。

【図6】映像信号中にエッジ部が存在する場合におけるフィルタ4の内部動作の一例を示す図である。

【図7】フィルタ4のフィルタリング処理による映像信号の平滑化を表す図である。

【図8】セレクタ4の動作例を示す図である。

【符号の説明】

【0030】

2 ビット付加回路

3 エッジ検出回路

4 フィルタ

5 比較器

6 セレクタ

【特許請求の範囲】

【請求項1】

量子化されたnビットの入力映像信号からmビット(m>n)のビット拡張映像信号を生成する映像信号処理装置であって、

前記入力映像信号の最下位ビット側にビット数(m−n)のビット列を付加してビット付加映像信号を生成するビット付加手段と、

前記ビット付加映像信号に対して平滑化処理を施して平滑化映像信号を生成するフィルタと、

前記ビット付加映像信号と前記平滑化映像信号との差分値と、所定閾値との大小を比較する比較手段と、

前記ビット付加映像信号及び前記平滑化映像信号の内のいずれか一方を前記比較手段による比較結果に応じて選択しこれを前記ビット拡張映像信号として出力するセレクタと、を有することを特徴とする映像信号処理装置。

【請求項2】

前記ビット付加映像信号中において輝度レベルが変化するエッジ部を検出するエッジ検出手段を更に備え、

前記フィルタは、前記ビット付加映像信号中における前記エッジ部及びこのエッジ部周辺の値に対してはこれを前記エッジ部の直前又は直後の値に置換したもので前記平滑化処理を行うことを特徴とする請求項1記載の映像信号処理装置。

【請求項3】

前記セレクタは、前記差分値が前記所定閾値よりも大なる場合には前記ビット付加映像信号を前記ビット拡張映像信号として出力する一方、前記差分値が前記所定閾値よりも小なる場合には前記平滑化映像信号を前記ビット拡張映像信号として出力することを特徴とする請求項1記載の映像信号処理装置。

【請求項4】

前記ビット列内の全てのビットは論理レベル0であることを特徴とする請求項1記載の映像信号処理装置。

【請求項1】

量子化されたnビットの入力映像信号からmビット(m>n)のビット拡張映像信号を生成する映像信号処理装置であって、

前記入力映像信号の最下位ビット側にビット数(m−n)のビット列を付加してビット付加映像信号を生成するビット付加手段と、

前記ビット付加映像信号に対して平滑化処理を施して平滑化映像信号を生成するフィルタと、

前記ビット付加映像信号と前記平滑化映像信号との差分値と、所定閾値との大小を比較する比較手段と、

前記ビット付加映像信号及び前記平滑化映像信号の内のいずれか一方を前記比較手段による比較結果に応じて選択しこれを前記ビット拡張映像信号として出力するセレクタと、を有することを特徴とする映像信号処理装置。

【請求項2】

前記ビット付加映像信号中において輝度レベルが変化するエッジ部を検出するエッジ検出手段を更に備え、

前記フィルタは、前記ビット付加映像信号中における前記エッジ部及びこのエッジ部周辺の値に対してはこれを前記エッジ部の直前又は直後の値に置換したもので前記平滑化処理を行うことを特徴とする請求項1記載の映像信号処理装置。

【請求項3】

前記セレクタは、前記差分値が前記所定閾値よりも大なる場合には前記ビット付加映像信号を前記ビット拡張映像信号として出力する一方、前記差分値が前記所定閾値よりも小なる場合には前記平滑化映像信号を前記ビット拡張映像信号として出力することを特徴とする請求項1記載の映像信号処理装置。

【請求項4】

前記ビット列内の全てのビットは論理レベル0であることを特徴とする請求項1記載の映像信号処理装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2006−50358(P2006−50358A)

【公開日】平成18年2月16日(2006.2.16)

【国際特許分類】

【出願番号】特願2004−230066(P2004−230066)

【出願日】平成16年8月6日(2004.8.6)

【出願人】(000005016)パイオニア株式会社 (3,620)

【出願人】(503213291)パイオニア・マイクロ・テクノロジー株式会社 (25)

【Fターム(参考)】

【公開日】平成18年2月16日(2006.2.16)

【国際特許分類】

【出願日】平成16年8月6日(2004.8.6)

【出願人】(000005016)パイオニア株式会社 (3,620)

【出願人】(503213291)パイオニア・マイクロ・テクノロジー株式会社 (25)

【Fターム(参考)】

[ Back to top ]