時間−デジタル変換器及びPLL回路

【課題】本発明は、発振器が出力する出力信号の1周期に小数分周の分解能つまり位相の分解能が依存しないTDCを提供することを目的とする。

【解決手段】本発明は、直列に接続され入力端で発振器が出力する出力信号CKVを入力される複数の遅延素子21と、複数の遅延素子21が出力する複数の遅延クロック信号を、PLL回路が入力される基準信号FREFのエッジタイミングでそれぞれラッチする複数のラッチ回路22と、直列接続された複数の遅延素子21の入力端で入力される出力信号CKVと、直列接続された複数の遅延素子21の出力端で出力される出力デジタル信号が、エッジタイミングを等しくするように、複数の遅延素子21の遅延時間を調整する遅延時間調整回路32と、を備えることを特徴とするTDC2である。

【解決手段】本発明は、直列に接続され入力端で発振器が出力する出力信号CKVを入力される複数の遅延素子21と、複数の遅延素子21が出力する複数の遅延クロック信号を、PLL回路が入力される基準信号FREFのエッジタイミングでそれぞれラッチする複数のラッチ回路22と、直列接続された複数の遅延素子21の入力端で入力される出力信号CKVと、直列接続された複数の遅延素子21の出力端で出力される出力デジタル信号が、エッジタイミングを等しくするように、複数の遅延素子21の遅延時間を調整する遅延時間調整回路32と、を備えることを特徴とするTDC2である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、基準信号に基づいて所望の周波数の信号を出力するPLL(Phase−Locked Loop)回路等に適用される時間−デジタル変換器に関する。

【背景技術】

【0002】

無線通信回路の周波数シンセサイザやクロック生成回路においてPLL回路が用いられている。近年、低電源電圧での動作が可能であり、チップサイズを縮小できるオールデジタルPLL(ADPLL)回路が研究されている(例えば、非特許文献1を参照。)。

【0003】

ADPLL回路は、入力される基準信号と発振器出力信号の間の位相差を計測して、分周数の整数部及び小数部に相当するデジタル値を生成し、生成したデジタル値で発振器出力信号の周波数を、発振器出力信号の周波数と基準信号の周波数の比が設定した分周数となるように制御する。TDC(Time−to−Digital Converter)は、分周数の小数部に相当するデジタル値を生成する。この動作について以下に説明する。

【0004】

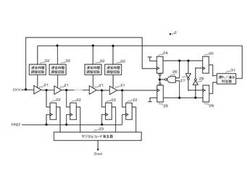

従来技術のTDCの構成を図1に示す。TDC2は、複数の遅延素子21、複数のラッチ回路22及びデジタルコード発生器23から構成される。

【0005】

複数の遅延素子21は、直列に接続され入力端で発振器が出力する出力信号CKVを入力される。複数のラッチ回路22は、複数の遅延素子21が出力する複数の遅延クロック信号を、ADPLL回路が入力される基準信号FREFのエッジタイミングでそれぞれラッチする。デジタルコード発生器23は、複数のラッチ回路22が出力する複数のラッチ出力信号をコーディングすることにより、基準信号FREFのエッジタイミングに対する出力信号CKVの相対的な時間の関係を示すデジタルコードDoutを発生する。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】“ALL−DIGITAL FREQUENCY SYNTHEZSIZER in DEEP−SUBMICRON CMOS” Robert Bogdan Staszewski/Poras T.Balsara 著

【発明の概要】

【発明が解決しようとする課題】

【0007】

小数分周の分解能つまり位相の分解能は、1個の遅延素子21の遅延時間が出力信号CKVの1周期に何個含まれるかにより決定される。しかし、1個の遅延素子21の遅延時間は、一定時間をとっている。よって、出力信号CKVの1周期が異なれば、使用する遅延素子21の段数が異なり、小数分周の分解能つまり位相の分解能が異なる。

【0008】

そこで、前記課題を解決するために、本発明は、発振器が出力する出力信号の1周期に小数分周の分解能つまり位相の分解能が依存しないTDCを提供することを目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成するために、複数の遅延素子全体の遅延時間が発振器が出力する出力信号の1周期と等しくなるように、発振器が出力する出力信号の1周期に応じて、1個の遅延素子各々の遅延時間を調整することとした。

【0010】

本発明は、直列に接続され入力端でクロック信号を入力される複数の遅延素子と、前記複数の遅延素子が出力する複数の遅延クロック信号を、基準デジタル信号のエッジタイミングでそれぞれラッチする複数のラッチ回路と、前記複数のラッチ回路が出力する複数のラッチ出力信号をコーディングすることにより、前記基準デジタル信号のエッジタイミングに対する前記クロック信号の相対的な時間の関係を示すデジタルコードを発生するデジタルコード発生器と、直列接続された前記複数の遅延素子の入力端で入力される前記クロック信号と、直列接続された前記複数の遅延素子の出力端で出力される出力デジタル信号が、エッジタイミングを等しくするように、前記複数の遅延素子の遅延時間を調整する遅延時間調整回路と、を備えることを特徴とする時間−デジタル変換器である。

【0011】

この構成によれば、発振器が出力する出力信号の1周期に小数分周の分解能つまり位相の分解能が依存しない時間−デジタル変換器を提供することができる。また、発振器が出力する出力信号及びPLL回路が入力される基準信号に代えて、それぞれ一般的なクロック信号及び一般的な基準デジタル信号を採用すれば、本発明の時間−デジタル変換器をPLL回路以外の回路構成にも適用することができる。

【0012】

また、本発明は、前記遅延時間調整回路は、直列接続された前記複数の遅延素子の入力端で入力される前記クロック信号と、前記複数の遅延素子が出力する前記複数の遅延クロック信号のうちいずれかが、エッジタイミングを等しくするように、前記複数の遅延素子の遅延時間を調整することを特徴とする時間−デジタル変換器である。

【0013】

この構成によれば、小数分周の計測つまり位相の計測に関わる遅延素子の個数を可変とすることにより、小数分周の分解能つまり位相の分解能を可変とすることができる。また、発振器が出力する出力信号及びPLL回路が入力される基準信号に代えて、それぞれ一般的なクロック信号及び一般的な基準デジタル信号を採用すれば、本発明の時間−デジタル変換器をPLL回路以外の回路構成にも適用することができる。

【0014】

また、本発明は、基準信号と出力信号の間の位相差が0になるような前記出力信号を出力する発振器と、前記クロック信号として、前記出力信号を入力され、前記基準デジタル信号として、前記基準信号を入力される時間−デジタル変換器と、前記基準信号のエッジタイミングに対する前記出力信号の相対的な時間の関係を示すデジタルコードに基づいて、前記位相差を示す情報を出力する位相比較器と、を備えることを特徴とするPLL回路である。

【0015】

この構成によれば、発振器が出力する出力信号の1周期に小数分周の分解能つまり位相の分解能が依存しないPLL回路を提供することができる。

【発明の効果】

【0016】

本発明は、発振器が出力する出力信号の1周期に小数分周の分解能つまり位相の分解能が依存しないTDCを提供することができる。

【図面の簡単な説明】

【0017】

【図1】従来技術のTDCの構成を示す図である。

【図2】PLL回路の構成を示す図である。

【図3】実施形態1のTDCの構成を示す図である。

【図4】実施形態2のTDCの構成を示す図である。

【発明を実施するための形態】

【0018】

添付の図面を参照して本発明の実施形態を説明する。以下に説明する実施形態は本発明の実施の例であり、本発明は以下の実施形態に制限されるものではない。なお、本明細書及び図面において符号が同じ構成要素は、相互に同一のものを示すものとする。

【0019】

(PLL回路の概要)

PLL回路の構成を図2に示す。PLL回路Pは、DCO1、TDC2、サンプラ3、基準位相アキュムレータ4、乗算器5、可変位相アキュムレータ6、サンプラ7、位相検出器8、ループフィルタ9及びゲイン正規化回路10から構成される。

【0020】

DCO1は、バラクタ(可変容量ダイオード)配列を持ち、発振周波数を2進数コードで制御する。TDC2は、DCO1の出力信号CKVと基準信号FREFのパルスエッジの差を時間間隔として計測する。出力値は小数部分周に相当するデジタル値となる。

【0021】

サンプラ3は、基準信号FREFの立上りエッジをDCO1の出力信号CKVの立上りエッジに同期させ、リタイミングされた基準信号CKRを出力する。基準信号CKRにより系全体が同期動作する。例えば、基準位相アキュムレータ4やサンプラ7は、基準信号CKRに基づいてデータ更新タイミングを同期させる。

【0022】

基準位相アキュムレータ4は、分周データFCWを基準信号CKRのタイミングで累積し、位相検出器8に出力する。乗算器5は、DCO1におけるDCO分周周期とTDC2の出力の周期を調整するための正規化係数を乗じる。

【0023】

可変位相アキュムレータ6は、DCO1の出力信号CKVの立ち上がりエッジ毎に+1カウントアップし、そのデジタル値を出力する。サンプラ7は、基準信号CKRの立ち上がりエッジで可変位相アキュムレータ6からの出力値を位相検出器8へ出力する。すなわち、基準信号CKRの周期にDCO1の出力信号CKVの周期が何パルスあるかを計測していることになる。これは整数分周に相当するデジタルデータとなる。

【0024】

位相検出器8は、基準位相アキュムレータ4の出力値、乗算器5の出力値、サンプラ7の出力値を演算により比較し、位相誤差としてループフィルタ9へ出力する。ループフィルタ9の出力は、ゲイン正規化回路10へ入力される。ゲイン正規化回路10は、ループフィルタ9の出力を元に、発振周波数を制御する2進数コードをDCO1に出力する。

【0025】

(実施形態1)

実施形態1のTDCの構成を図3に示す。TDC2は、複数の遅延素子21、複数のラッチ回路22、デジタルコード発生器23、D−フリップフロップ回路24、25、NAND回路26、NOT回路27、28、D−フリップフロップ回路29、30、遅れ/進み判定器31及び遅延時間調整回路32から構成される。

【0026】

複数の遅延素子21は、直列に接続され入力端でDCO1の出力信号CKVを入力される。複数のラッチ回路22は、複数の遅延素子21が出力する複数の遅延クロック信号を、基準信号FREFのエッジタイミングでそれぞれラッチする。デジタルコード発生器23は、複数のラッチ回路22が出力する複数のラッチ出力信号をコーディングすることにより、基準信号FREFのエッジタイミングに対するDCO1の出力信号CKVの相対的な時間の関係を示すデジタルコードDoutを発生する。

【0027】

遅延時間調整回路32は、直列接続された複数の遅延素子21の入力端で入力される出力信号CKVと、直列接続された複数の遅延素子21の出力端で出力される出力デジタル信号が、エッジタイミングを等しくするように、複数の遅延素子21の遅延時間を調整する。つまり、遅延時間調整回路32は、複数の遅延素子21全体の遅延時間がDCO1が出力する出力信号CKVの1周期と等しくなるように、DCO1が出力する出力信号CKVの1周期に応じて、1個の遅延素子21各々の遅延時間を調整する。

【0028】

遅れ/進み判定器31は、直列接続された複数の遅延素子21の入力端で入力される出力信号CKVのエッジタイミングと、直列接続された複数の遅延素子21の出力端で出力される出力デジタル信号のエッジタイミングと、の比較結果を遅延時間調整回路32に出力する。遅延時間調整回路32は、当該比較結果に基づいて、上述の処理を実行する。

【0029】

D−フリップフロップ回路24は、C端子で、直列接続された複数の遅延素子21の入力端で入力される出力信号CKVを入力し、D端子で、‘1’を入力し、Q端子で、ラッチ結果を出力し、R端子で、後述のNAND回路26の出力を入力する。なお、当該R端子はローアクティブである。

【0030】

D−フリップフロップ回路25は、C端子で、直列接続された複数の遅延素子21の出力端で出力される出力デジタル信号を入力し、D端子で、‘1’を入力し、Q端子で、ラッチ結果を出力し、R端子で、後述のNAND回路26の出力を入力する。なお、当該R端子はローアクティブである。

【0031】

NAND回路26は、D−フリップフロップ回路24、25の出力を入力し、これらの出力の論理積をD−フリップフロップ回路24、25のR端子に出力する。

【0032】

D−フリップフロップ回路29は、C端子で、D−フリップフロップ回路24の出力をNOT回路27で反転させた信号を入力し、D端子で、D−フリップフロップ回路25の出力を入力し、Q端子で、ラッチ結果を遅れ/進み判定器31に出力する。

【0033】

D−フリップフロップ回路30は、C端子で、D−フリップフロップ回路25の出力をNOT回路28で反転させた信号を入力し、D端子で、D−フリップフロップ回路24の出力を入力し、Q端子で、ラッチ結果を遅れ/進み判定器31に出力する。

【0034】

直列接続された複数の遅延素子21の入力端で入力される出力信号CKVのエッジタイミングと、直列接続された複数の遅延素子21の出力端で出力される出力デジタル信号のエッジタイミングと、が等しくなるときを考える。D−フリップフロップ回路24、25の出力は、パルス信号となるが、D−フリップフロップ回路29、30の出力は、連続信号となる。遅れ/進み判定器31は、エッジタイミングの比較結果を正しく得るためには、D−フリップフロップ回路24、25の出力を入力するより、D−フリップフロップ回路29、30の出力を入力するのが望ましい。

【0035】

実施形態1では、DCO1が出力する出力信号CKVの1周期に、小数分周の分解能つまり位相の分解能が依存しない、TDC2を提供することができる。また、DCO1が出力する出力信号CKV及びPLL回路Pが入力される基準信号FREFに代えて、それぞれ一般的なクロック信号及び一般的な基準デジタル信号を採用すれば、TDC2をPLL回路P以外の回路構成にも適用することができる。

【0036】

(実施形態2)

実施形態2のTDCの構成を図4に示す。TDC2は、複数の遅延素子21、複数のラッチ回路22、デジタルコード発生器23、D−フリップフロップ回路24、25、NAND回路26、NOT回路27、28、D−フリップフロップ回路29、30、遅れ/進み判定器31、遅延時間調整回路32及びセレクタ33から構成される。

【0037】

遅延時間調整回路32は、直列接続された複数の遅延素子21の入力端で入力される出力信号CKVと、複数の遅延素子21が出力する複数の遅延クロック信号のうちいずれかが、エッジタイミングを等しくするように、複数の遅延素子21の遅延時間を調整する。そのためには、セレクタ33は、複数の遅延素子21の出力のうちいずれかの遅延素子21の出力を選択し、選択した遅延素子21の出力をD−フリップフロップ回路25のC端子に出力する。他の構成及び処理は、実施形態1、2で同様である。

【0038】

実施形態2では、小数分周の計測つまり位相の計測に関わる遅延素子21の個数を可変とすることにより、小数分周の分解能つまり位相の分解能を可変とすることができる。また、DCO1が出力する出力信号CKV及びPLL回路Pが入力される基準信号FREFに代えて、それぞれ一般的なクロック信号及び一般的な基準デジタル信号を採用すれば、TDC2をPLL回路P以外の回路構成にも適用することができる。

【0039】

実施形態1および実施形態2において、D−フリップフロップ回路24および25のR端子はローアクティブとしたが、NAND回路26をAND回路に置き換えれば、当該R端子がハイアクティブであるD−フリップフロップ回路を使用しても良い。

【産業上の利用可能性】

【0040】

本発明に係るTDCは、PLL回路に適用でき、DCOが出力する出力信号CKV及びPLL回路が入力される基準信号FREFに代えて、それぞれ一般的なクロック信号及び一般的な基準デジタル信号を採用すれば、PLL回路以外の回路構成にも適用できる。

【符号の説明】

【0041】

P:PLL回路

1:DCO

2:TDC

3:サンプラ

4:基準位相アキュムレータ

5:乗算器

6:可変位相アキュムレータ

7:サンプラ

8:位相検出器

9:ループフィルタ

10:ゲイン正規化回路

21:遅延素子

22:ラッチ回路

23:デジタルコード発生器

24、25:D−フリップフロップ回路

26:NAND回路

27、28:NOT回路

29、30:D−フリップフロップ回路

31:遅れ/進み判定器

32:遅延時間調整回路

33:セレクタ

【技術分野】

【0001】

本発明は、基準信号に基づいて所望の周波数の信号を出力するPLL(Phase−Locked Loop)回路等に適用される時間−デジタル変換器に関する。

【背景技術】

【0002】

無線通信回路の周波数シンセサイザやクロック生成回路においてPLL回路が用いられている。近年、低電源電圧での動作が可能であり、チップサイズを縮小できるオールデジタルPLL(ADPLL)回路が研究されている(例えば、非特許文献1を参照。)。

【0003】

ADPLL回路は、入力される基準信号と発振器出力信号の間の位相差を計測して、分周数の整数部及び小数部に相当するデジタル値を生成し、生成したデジタル値で発振器出力信号の周波数を、発振器出力信号の周波数と基準信号の周波数の比が設定した分周数となるように制御する。TDC(Time−to−Digital Converter)は、分周数の小数部に相当するデジタル値を生成する。この動作について以下に説明する。

【0004】

従来技術のTDCの構成を図1に示す。TDC2は、複数の遅延素子21、複数のラッチ回路22及びデジタルコード発生器23から構成される。

【0005】

複数の遅延素子21は、直列に接続され入力端で発振器が出力する出力信号CKVを入力される。複数のラッチ回路22は、複数の遅延素子21が出力する複数の遅延クロック信号を、ADPLL回路が入力される基準信号FREFのエッジタイミングでそれぞれラッチする。デジタルコード発生器23は、複数のラッチ回路22が出力する複数のラッチ出力信号をコーディングすることにより、基準信号FREFのエッジタイミングに対する出力信号CKVの相対的な時間の関係を示すデジタルコードDoutを発生する。

【先行技術文献】

【非特許文献】

【0006】

【非特許文献1】“ALL−DIGITAL FREQUENCY SYNTHEZSIZER in DEEP−SUBMICRON CMOS” Robert Bogdan Staszewski/Poras T.Balsara 著

【発明の概要】

【発明が解決しようとする課題】

【0007】

小数分周の分解能つまり位相の分解能は、1個の遅延素子21の遅延時間が出力信号CKVの1周期に何個含まれるかにより決定される。しかし、1個の遅延素子21の遅延時間は、一定時間をとっている。よって、出力信号CKVの1周期が異なれば、使用する遅延素子21の段数が異なり、小数分周の分解能つまり位相の分解能が異なる。

【0008】

そこで、前記課題を解決するために、本発明は、発振器が出力する出力信号の1周期に小数分周の分解能つまり位相の分解能が依存しないTDCを提供することを目的とする。

【課題を解決するための手段】

【0009】

上記目的を達成するために、複数の遅延素子全体の遅延時間が発振器が出力する出力信号の1周期と等しくなるように、発振器が出力する出力信号の1周期に応じて、1個の遅延素子各々の遅延時間を調整することとした。

【0010】

本発明は、直列に接続され入力端でクロック信号を入力される複数の遅延素子と、前記複数の遅延素子が出力する複数の遅延クロック信号を、基準デジタル信号のエッジタイミングでそれぞれラッチする複数のラッチ回路と、前記複数のラッチ回路が出力する複数のラッチ出力信号をコーディングすることにより、前記基準デジタル信号のエッジタイミングに対する前記クロック信号の相対的な時間の関係を示すデジタルコードを発生するデジタルコード発生器と、直列接続された前記複数の遅延素子の入力端で入力される前記クロック信号と、直列接続された前記複数の遅延素子の出力端で出力される出力デジタル信号が、エッジタイミングを等しくするように、前記複数の遅延素子の遅延時間を調整する遅延時間調整回路と、を備えることを特徴とする時間−デジタル変換器である。

【0011】

この構成によれば、発振器が出力する出力信号の1周期に小数分周の分解能つまり位相の分解能が依存しない時間−デジタル変換器を提供することができる。また、発振器が出力する出力信号及びPLL回路が入力される基準信号に代えて、それぞれ一般的なクロック信号及び一般的な基準デジタル信号を採用すれば、本発明の時間−デジタル変換器をPLL回路以外の回路構成にも適用することができる。

【0012】

また、本発明は、前記遅延時間調整回路は、直列接続された前記複数の遅延素子の入力端で入力される前記クロック信号と、前記複数の遅延素子が出力する前記複数の遅延クロック信号のうちいずれかが、エッジタイミングを等しくするように、前記複数の遅延素子の遅延時間を調整することを特徴とする時間−デジタル変換器である。

【0013】

この構成によれば、小数分周の計測つまり位相の計測に関わる遅延素子の個数を可変とすることにより、小数分周の分解能つまり位相の分解能を可変とすることができる。また、発振器が出力する出力信号及びPLL回路が入力される基準信号に代えて、それぞれ一般的なクロック信号及び一般的な基準デジタル信号を採用すれば、本発明の時間−デジタル変換器をPLL回路以外の回路構成にも適用することができる。

【0014】

また、本発明は、基準信号と出力信号の間の位相差が0になるような前記出力信号を出力する発振器と、前記クロック信号として、前記出力信号を入力され、前記基準デジタル信号として、前記基準信号を入力される時間−デジタル変換器と、前記基準信号のエッジタイミングに対する前記出力信号の相対的な時間の関係を示すデジタルコードに基づいて、前記位相差を示す情報を出力する位相比較器と、を備えることを特徴とするPLL回路である。

【0015】

この構成によれば、発振器が出力する出力信号の1周期に小数分周の分解能つまり位相の分解能が依存しないPLL回路を提供することができる。

【発明の効果】

【0016】

本発明は、発振器が出力する出力信号の1周期に小数分周の分解能つまり位相の分解能が依存しないTDCを提供することができる。

【図面の簡単な説明】

【0017】

【図1】従来技術のTDCの構成を示す図である。

【図2】PLL回路の構成を示す図である。

【図3】実施形態1のTDCの構成を示す図である。

【図4】実施形態2のTDCの構成を示す図である。

【発明を実施するための形態】

【0018】

添付の図面を参照して本発明の実施形態を説明する。以下に説明する実施形態は本発明の実施の例であり、本発明は以下の実施形態に制限されるものではない。なお、本明細書及び図面において符号が同じ構成要素は、相互に同一のものを示すものとする。

【0019】

(PLL回路の概要)

PLL回路の構成を図2に示す。PLL回路Pは、DCO1、TDC2、サンプラ3、基準位相アキュムレータ4、乗算器5、可変位相アキュムレータ6、サンプラ7、位相検出器8、ループフィルタ9及びゲイン正規化回路10から構成される。

【0020】

DCO1は、バラクタ(可変容量ダイオード)配列を持ち、発振周波数を2進数コードで制御する。TDC2は、DCO1の出力信号CKVと基準信号FREFのパルスエッジの差を時間間隔として計測する。出力値は小数部分周に相当するデジタル値となる。

【0021】

サンプラ3は、基準信号FREFの立上りエッジをDCO1の出力信号CKVの立上りエッジに同期させ、リタイミングされた基準信号CKRを出力する。基準信号CKRにより系全体が同期動作する。例えば、基準位相アキュムレータ4やサンプラ7は、基準信号CKRに基づいてデータ更新タイミングを同期させる。

【0022】

基準位相アキュムレータ4は、分周データFCWを基準信号CKRのタイミングで累積し、位相検出器8に出力する。乗算器5は、DCO1におけるDCO分周周期とTDC2の出力の周期を調整するための正規化係数を乗じる。

【0023】

可変位相アキュムレータ6は、DCO1の出力信号CKVの立ち上がりエッジ毎に+1カウントアップし、そのデジタル値を出力する。サンプラ7は、基準信号CKRの立ち上がりエッジで可変位相アキュムレータ6からの出力値を位相検出器8へ出力する。すなわち、基準信号CKRの周期にDCO1の出力信号CKVの周期が何パルスあるかを計測していることになる。これは整数分周に相当するデジタルデータとなる。

【0024】

位相検出器8は、基準位相アキュムレータ4の出力値、乗算器5の出力値、サンプラ7の出力値を演算により比較し、位相誤差としてループフィルタ9へ出力する。ループフィルタ9の出力は、ゲイン正規化回路10へ入力される。ゲイン正規化回路10は、ループフィルタ9の出力を元に、発振周波数を制御する2進数コードをDCO1に出力する。

【0025】

(実施形態1)

実施形態1のTDCの構成を図3に示す。TDC2は、複数の遅延素子21、複数のラッチ回路22、デジタルコード発生器23、D−フリップフロップ回路24、25、NAND回路26、NOT回路27、28、D−フリップフロップ回路29、30、遅れ/進み判定器31及び遅延時間調整回路32から構成される。

【0026】

複数の遅延素子21は、直列に接続され入力端でDCO1の出力信号CKVを入力される。複数のラッチ回路22は、複数の遅延素子21が出力する複数の遅延クロック信号を、基準信号FREFのエッジタイミングでそれぞれラッチする。デジタルコード発生器23は、複数のラッチ回路22が出力する複数のラッチ出力信号をコーディングすることにより、基準信号FREFのエッジタイミングに対するDCO1の出力信号CKVの相対的な時間の関係を示すデジタルコードDoutを発生する。

【0027】

遅延時間調整回路32は、直列接続された複数の遅延素子21の入力端で入力される出力信号CKVと、直列接続された複数の遅延素子21の出力端で出力される出力デジタル信号が、エッジタイミングを等しくするように、複数の遅延素子21の遅延時間を調整する。つまり、遅延時間調整回路32は、複数の遅延素子21全体の遅延時間がDCO1が出力する出力信号CKVの1周期と等しくなるように、DCO1が出力する出力信号CKVの1周期に応じて、1個の遅延素子21各々の遅延時間を調整する。

【0028】

遅れ/進み判定器31は、直列接続された複数の遅延素子21の入力端で入力される出力信号CKVのエッジタイミングと、直列接続された複数の遅延素子21の出力端で出力される出力デジタル信号のエッジタイミングと、の比較結果を遅延時間調整回路32に出力する。遅延時間調整回路32は、当該比較結果に基づいて、上述の処理を実行する。

【0029】

D−フリップフロップ回路24は、C端子で、直列接続された複数の遅延素子21の入力端で入力される出力信号CKVを入力し、D端子で、‘1’を入力し、Q端子で、ラッチ結果を出力し、R端子で、後述のNAND回路26の出力を入力する。なお、当該R端子はローアクティブである。

【0030】

D−フリップフロップ回路25は、C端子で、直列接続された複数の遅延素子21の出力端で出力される出力デジタル信号を入力し、D端子で、‘1’を入力し、Q端子で、ラッチ結果を出力し、R端子で、後述のNAND回路26の出力を入力する。なお、当該R端子はローアクティブである。

【0031】

NAND回路26は、D−フリップフロップ回路24、25の出力を入力し、これらの出力の論理積をD−フリップフロップ回路24、25のR端子に出力する。

【0032】

D−フリップフロップ回路29は、C端子で、D−フリップフロップ回路24の出力をNOT回路27で反転させた信号を入力し、D端子で、D−フリップフロップ回路25の出力を入力し、Q端子で、ラッチ結果を遅れ/進み判定器31に出力する。

【0033】

D−フリップフロップ回路30は、C端子で、D−フリップフロップ回路25の出力をNOT回路28で反転させた信号を入力し、D端子で、D−フリップフロップ回路24の出力を入力し、Q端子で、ラッチ結果を遅れ/進み判定器31に出力する。

【0034】

直列接続された複数の遅延素子21の入力端で入力される出力信号CKVのエッジタイミングと、直列接続された複数の遅延素子21の出力端で出力される出力デジタル信号のエッジタイミングと、が等しくなるときを考える。D−フリップフロップ回路24、25の出力は、パルス信号となるが、D−フリップフロップ回路29、30の出力は、連続信号となる。遅れ/進み判定器31は、エッジタイミングの比較結果を正しく得るためには、D−フリップフロップ回路24、25の出力を入力するより、D−フリップフロップ回路29、30の出力を入力するのが望ましい。

【0035】

実施形態1では、DCO1が出力する出力信号CKVの1周期に、小数分周の分解能つまり位相の分解能が依存しない、TDC2を提供することができる。また、DCO1が出力する出力信号CKV及びPLL回路Pが入力される基準信号FREFに代えて、それぞれ一般的なクロック信号及び一般的な基準デジタル信号を採用すれば、TDC2をPLL回路P以外の回路構成にも適用することができる。

【0036】

(実施形態2)

実施形態2のTDCの構成を図4に示す。TDC2は、複数の遅延素子21、複数のラッチ回路22、デジタルコード発生器23、D−フリップフロップ回路24、25、NAND回路26、NOT回路27、28、D−フリップフロップ回路29、30、遅れ/進み判定器31、遅延時間調整回路32及びセレクタ33から構成される。

【0037】

遅延時間調整回路32は、直列接続された複数の遅延素子21の入力端で入力される出力信号CKVと、複数の遅延素子21が出力する複数の遅延クロック信号のうちいずれかが、エッジタイミングを等しくするように、複数の遅延素子21の遅延時間を調整する。そのためには、セレクタ33は、複数の遅延素子21の出力のうちいずれかの遅延素子21の出力を選択し、選択した遅延素子21の出力をD−フリップフロップ回路25のC端子に出力する。他の構成及び処理は、実施形態1、2で同様である。

【0038】

実施形態2では、小数分周の計測つまり位相の計測に関わる遅延素子21の個数を可変とすることにより、小数分周の分解能つまり位相の分解能を可変とすることができる。また、DCO1が出力する出力信号CKV及びPLL回路Pが入力される基準信号FREFに代えて、それぞれ一般的なクロック信号及び一般的な基準デジタル信号を採用すれば、TDC2をPLL回路P以外の回路構成にも適用することができる。

【0039】

実施形態1および実施形態2において、D−フリップフロップ回路24および25のR端子はローアクティブとしたが、NAND回路26をAND回路に置き換えれば、当該R端子がハイアクティブであるD−フリップフロップ回路を使用しても良い。

【産業上の利用可能性】

【0040】

本発明に係るTDCは、PLL回路に適用でき、DCOが出力する出力信号CKV及びPLL回路が入力される基準信号FREFに代えて、それぞれ一般的なクロック信号及び一般的な基準デジタル信号を採用すれば、PLL回路以外の回路構成にも適用できる。

【符号の説明】

【0041】

P:PLL回路

1:DCO

2:TDC

3:サンプラ

4:基準位相アキュムレータ

5:乗算器

6:可変位相アキュムレータ

7:サンプラ

8:位相検出器

9:ループフィルタ

10:ゲイン正規化回路

21:遅延素子

22:ラッチ回路

23:デジタルコード発生器

24、25:D−フリップフロップ回路

26:NAND回路

27、28:NOT回路

29、30:D−フリップフロップ回路

31:遅れ/進み判定器

32:遅延時間調整回路

33:セレクタ

【特許請求の範囲】

【請求項1】

直列に接続され入力端でクロック信号を入力される複数の遅延素子と、

前記複数の遅延素子が出力する複数の遅延クロック信号を、基準デジタル信号のエッジタイミングでそれぞれラッチする複数のラッチ回路と、

前記複数のラッチ回路が出力する複数のラッチ出力信号をコーディングすることにより、前記基準デジタル信号のエッジタイミングに対する前記クロック信号の相対的な時間の関係を示すデジタルコードを発生するデジタルコード発生器と、

直列接続された前記複数の遅延素子の入力端で入力される前記クロック信号と、直列接続された前記複数の遅延素子の出力端で出力される出力デジタル信号が、エッジタイミングを等しくするように、前記複数の遅延素子の遅延時間を調整する遅延時間調整回路と、

を備えることを特徴とする時間−デジタル変換器。

【請求項2】

前記遅延時間調整回路は、直列接続された前記複数の遅延素子の入力端で入力される前記クロック信号と、前記複数の遅延素子が出力する前記複数の遅延クロック信号のうちいずれかが、エッジタイミングを等しくするように、前記複数の遅延素子の遅延時間を調整することを特徴とする、請求項1に記載の時間−デジタル変換器。

【請求項3】

基準信号と出力信号の間の位相差が0になるような前記出力信号を出力する発振器と、

前記クロック信号として、前記出力信号を入力され、前記基準デジタル信号として、前記基準信号を入力される、請求項1又は2に記載の時間−デジタル変換器と、

前記基準信号のエッジタイミングに対する前記出力信号の相対的な時間の関係を示すデジタルコードに基づいて、前記位相差を示す情報を出力する位相比較器と、

を備えることを特徴とするPLL回路。

【請求項1】

直列に接続され入力端でクロック信号を入力される複数の遅延素子と、

前記複数の遅延素子が出力する複数の遅延クロック信号を、基準デジタル信号のエッジタイミングでそれぞれラッチする複数のラッチ回路と、

前記複数のラッチ回路が出力する複数のラッチ出力信号をコーディングすることにより、前記基準デジタル信号のエッジタイミングに対する前記クロック信号の相対的な時間の関係を示すデジタルコードを発生するデジタルコード発生器と、

直列接続された前記複数の遅延素子の入力端で入力される前記クロック信号と、直列接続された前記複数の遅延素子の出力端で出力される出力デジタル信号が、エッジタイミングを等しくするように、前記複数の遅延素子の遅延時間を調整する遅延時間調整回路と、

を備えることを特徴とする時間−デジタル変換器。

【請求項2】

前記遅延時間調整回路は、直列接続された前記複数の遅延素子の入力端で入力される前記クロック信号と、前記複数の遅延素子が出力する前記複数の遅延クロック信号のうちいずれかが、エッジタイミングを等しくするように、前記複数の遅延素子の遅延時間を調整することを特徴とする、請求項1に記載の時間−デジタル変換器。

【請求項3】

基準信号と出力信号の間の位相差が0になるような前記出力信号を出力する発振器と、

前記クロック信号として、前記出力信号を入力され、前記基準デジタル信号として、前記基準信号を入力される、請求項1又は2に記載の時間−デジタル変換器と、

前記基準信号のエッジタイミングに対する前記出力信号の相対的な時間の関係を示すデジタルコードに基づいて、前記位相差を示す情報を出力する位相比較器と、

を備えることを特徴とするPLL回路。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2013−77869(P2013−77869A)

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願番号】特願2011−214857(P2011−214857)

【出願日】平成23年9月29日(2011.9.29)

【出願人】(000004330)日本無線株式会社 (1,186)

【Fターム(参考)】

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願日】平成23年9月29日(2011.9.29)

【出願人】(000004330)日本無線株式会社 (1,186)

【Fターム(参考)】

[ Back to top ]