時間デジタル変換器、時間デジタル変換方法及びガンマ線検出システム

【課題】測定精度および分解能を向上させることができる時間デジタル変換器、時間デジタル変換方法及びガンマ線検出システムを提供すること。

【解決手段】時間デジタル変換器は、開始信号と停止信号との間の遅延時間に対応する第1の値を生成する第1遅延列回路を備える。時間デジタル変換器は、また、遅延開始信号と停止信号との間の遅延時間に対応する第2の値を生成する少なくとも一つの第2遅延列回路を備える。少なくとも一つの遅延素子は開始信号に所定の遅延を与えることにより遅延開始信号を生成し、合成回路は、第1の値および第2の値に基づく出力値を生成する。実施形態に係る時間デジタル変換器では、出力値は開始信号と停止信号との間の遅延時間に対応する。

【解決手段】時間デジタル変換器は、開始信号と停止信号との間の遅延時間に対応する第1の値を生成する第1遅延列回路を備える。時間デジタル変換器は、また、遅延開始信号と停止信号との間の遅延時間に対応する第2の値を生成する少なくとも一つの第2遅延列回路を備える。少なくとも一つの遅延素子は開始信号に所定の遅延を与えることにより遅延開始信号を生成し、合成回路は、第1の値および第2の値に基づく出力値を生成する。実施形態に係る時間デジタル変換器では、出力値は開始信号と停止信号との間の遅延時間に対応する。

【発明の詳細な説明】

【技術分野】

【0001】

本明細書で説明する実施形態は、測定精度および分解能を向上させる時間デジタル変換器、時間デジタル変換方法及びガンマ線検出システムに関する。

【背景技術】

【0002】

市販のガンマ線検出器は透明のライトガイドに接続されるシンチレータ結晶アレイを備え、透明ライトガイドは透明ライトガイド全体に配置される光電子倍増管(PMT:Photomultiplier Tube)全体にシンチレーション光を分散する。同一領域でのPMTからの信号は、通常アナログドメインで合計され、その後合計された信号の主要エッジまたはイベントに基づきタイミングが測定される。

【0003】

時間デジタル変換器(TDC:Time−to−Digital−Converter)は、ガンマ線検出器でのタイミング測定に用いられることが多い。TDCは、イベントの実現をイベントが発生した時間に関連づけることができる数に変換する。このタスクを行う様々な方法がある。他の方法には、粗いクロック周期間での多数の超高速論理遷移の計数を用いこのタスクを行うものがある。また、連続して生成されるものとして知られる一連のイベントの発生を示すことが好ましい場合もある。例えば、上昇信号が取得して所定の一連の閾値に到達するタイムマークは、非常に有効な情報になり得る。

【0004】

また、時間デジタル変換器(TDC)は、各種構造で実装されている。まず一つ目の従来構造は、直列に接続された同一遅延素子の単一の列を有するクラシック遅延列である。また、このクラシック遅延列は1ビットメモリ素子一式を備え、各1ビットメモリ素子は遅延素子の一つの出力に接続される。開始信号が遅延素子列の入力へ供給されて、測定される期間の開始を示す。開始信号は遅延素子列全体に伝播する。遅延素子列内で伝播した開始信号の位置をキャプチャするために全てのメモリ素子のクロック入力に同時に与えられる停止信号が、測定される期間の終了を表す。その後、キャプチャされた位置をデコードして開始信号と停止信号との間の遅延が演算され、この遅延は、各遅延素子により与えられる遅延の倍数として測定される期間の長さを演算するために用いられる。

【0005】

よって、クラシック遅延列の分解能は、遅延列内の各遅延素子の時間遅延に限定される。例えば、列内の各遅延素子が遅延tuを与えると、クラシック遅延列の分解能はtuになる。同様に、半導体素子などのクラシック遅延列の物理的実装では、半導体の物理的特徴により最小値tuが制限される。クラシック遅延列内の各遅延素子に対し同じ時点でサンプリングが行われるので、遅延tuへの物理的制限により測定分解能が制限される。

【0006】

もう一つの従来遅延列は、バーニア遅延列である。クラシック遅延列同様、バーニア遅延列は、直列に接続された同一遅延素子の列と、各々が遅延素子の一つの出力に接続される1ビットメモリ素子一式とを有する。また、バーニア遅延列は、直列に接続される同一の遅延素子の第2の遅延列を備える。第2の遅延列内の各遅延素子の出力は、メモリ素子の一つのクロック出力に接続される。ここで、第1遅延列内の遅延素子はそれぞれ遅延tuを与え、第2の遅延列の遅延素子はそれぞれtc<tuとなる遅延tcを与える。

【0007】

操作中、開始信号がバーニア遅延列の第1遅延列に供給され、停止信号が第2の遅延列に供給される。第2遅延列の素子が与える遅延が第1遅延列の素子による遅延よりも少ないので、停止信号が最終的に開始信号に追い付く。停止信号が開始信号に追い付くと、第1遅延列内の開始信号の伝播がメモリ素子によりキャプチャされ、デコードされて開始信号と停止信号との時間間隔が決定される。この測定される期間は、第1遅延列の遅延と第2遅延列の遅延との差の倍数またはtu−tcとして算出される。

【0008】

クラシック遅延列同様、バーニア遅延列内の遅延は、バーニア遅延列が実装される半導体の物理特性により制限される。よって、バーニア遅延列を用いて達成できる最小の遅延差(tu−tc)(つまり、分解能)がある。従って、バーニア遅延列を用いて正確に期間を測定することは困難である。

【0009】

その結果、クラシック遅延列およびバーニア遅延列の制限を改善し、精度および分解能を向上させる装置およびそれに関連する方法が求められている。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2007−41007号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

本発明が解決しようとする課題は、測定精度および分解能を向上させることができる時間デジタル変換器、時間デジタル変換方法及びガンマ線検出システムを提供することである。

【課題を解決するための手段】

【0012】

実施の形態の時間デジタル変換器は、第1遅延列回路と、少なくとも一つの遅延素子と、少なくとも一つの第2遅延列回路と、合成回路とを備える。第1遅延列回路は、開始信号と停止信号との間の遅延時間に対応する第1の値を生成する。少なくとも一つの遅延素子は、前記開始信号に所定の遅延を与えることにより遅延開始信号を生成する。少なくとも一つの第2遅延列回路は、前記遅延開始信号と前記停止信号との間の遅延時間に対応する第2の値を生成する。合成回路は、前記第1の値および前記第2の値に基づいて、前記開始信号と前記停止信号との間の遅延時間に対応する出力値を生成する。

【図面の簡単な説明】

【0013】

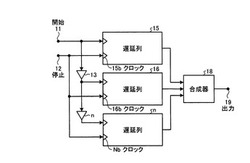

【図1】図1は、実施形態に係る時間デジタル変換器の模式図である。

【図2】図2は、実施形態に係る時間デジタル変換器内で用いられる遅延列の模式図である。

【図3】図3は、実施形態に係る時間デジタル変換器内で用いられる別の遅延列の模式図である。

【図4】図4は、実施形態に係る別の時間デジタル変換器の模式図である。

【図5】図5は、実施形態に係る時間デジタル変換方法のフロー図である。

【図6】図6は、実施形態に係る時間デジタル変換のタイミング図である。

【図7】図7は、実施形態に係るガンマ線検出システムの模式図である。

【発明を実施するための形態】

【0014】

実施形態に係る時間デジタル変換器は、通常、開始信号と停止信号との間の時間遅延に対応する第1の値を生成する第1遅延列回路を備える。時間デジタル変換器は、また、遅延開始信号と停止信号との間の時間遅延に対応する第2の値を生成する少なくとも一つの第2遅延列回路を備える。少なくとも一つの遅延素子は、所定の遅延を開始信号に与えることにより遅延開始信号を生成し、合成回路は、第1の値および第2の値に基づく出力値を生成する。実施形態の時間デジタル変換器では、出力値が開始信号と停止信号との間の時間遅延に対応する。

【0015】

ここで、複数の図面に渡り同じ参照符号は同一または対応する部分を示す図面を参照する。図1は、実施形態に係る時間デジタル変換器の模式図である。図1では、複数の遅延列15…Nが端子11に接続されて開始信号を受信し、また、端子12に接続されて停止信号を受信する。遅延列ク15、16…Nのクロック入力15b、16b…Nbは端子12に直接接続されるが、遅延列15だけは、端子11に直接接続される。遅延列16は遅延素子13を介して端子11に接続され、遅延列Nはnと通じ遅延素子13を介して端子11に接続される。遅延列15、16…Nの出力は、時間デジタル変換器の全出力を生成しその全出力を端子19に与える合成器18に接続される。

【0016】

更に、図1では、以下に詳細に示すように、各遅延列15、16…Nは、ほぼ同様の構造およびほぼ同様の分解能を有する。遅延素子13…nは、遅延列15、16…Nの分解能の関数とほぼ同じ遅延量を与える。具体的には、遅延素子13…nそれぞれの遅延は、時間デジタル変換器が備える遅延列回路の数に反比例する。例えば、各遅延列が分解能Rを有する場合、各遅延素子13…nは、遅延量R/Nを与え、その結果、時間デジタル変換器全体の分解能はR/Nになる。

【0017】

当業者であればわかるように、図1の時間デジタル変換器は、遅延列15、16…Nとそれに対応する数の遅延素子13…nをいくつ備えてもよい。更に、合成器18は、時間デジタル変換器が有する全ての遅延列15、16…Nに対応する十分な出力を有する単一の合成器でもよく、また、集まると遅延列15、16…N全てに対応する十分な出力を有する直列の合成器一式であってもよい。合成器18は、また、加算により遅延列15、16…Nの出力を合成してもよく、また、遅延列15、16…Nの出力の平均値を求めてもよい。すなわち、合成器18は、加算器、或いは、平均器であってもよい。また、当業者であればわかるように、合成器18での遅延列15、16…Nの出力の他の合成とすることができる。

【0018】

図1の時間デジタル変換器は、ディスクリート論理ゲート、ASIC(Application Specific Integrated Circuit)、FPGA(Field Programmable Gate Array)、または他のCPLD(Complex Programmable Logic Device)として実装されても良い。FPGAやCPLDの実装では、時間デジタル変換器は、VHDL(Very high speed integrated circuits Hardware Description Language)、Verilog、また他のハードウェア記述言語によりコンピュータ読み取り可能な一連の命令としてコード化されてもよく、このコンピュータ読み取り可能な命令は直接FPGAやCPLD内の電子メモリ、または、独立した電子メモリに記憶されてもよい。更に、電子メモリは、ROM(Read Only Memory)、EPROM(Erasable Programmable Read Only Memory)、EEPROM(Electrically Erasable Programmable Read Only Memory)、またはFLASHメモリなどの不揮発性メモリであってもよい。電子メモリは、また、ダイナミックRAM(Random Access Memory)、などの揮発性メモリであってもよく、マイクロコントローラやマイクロプロセッサなどのプロセッサを設けて電子メモリだけでなくFPGAまたはCPLDと電子メモリとの相互作用を制御してもよい。

【0019】

次に、実施形態に係る時間デジタル変換器に備えられる複数の遅延列の詳細について説明する。複数の遅延列は、同一の所定の遅延を与える複数の遅延列素子を有し、遅延列に前記開始信号が与えられる遅延列素子をそれぞれ備える。また、複数の遅延列は、前記遅延列内の前記複数の遅延列素子の一つにそれぞれ接続され、前記停止信号を受信する共通のクロック入力を有する複数のメモリ素子をそれぞれ備える。また、複数の遅延列は、前記複数のメモリ素子の出力に基づくデジタル値を生成するデコーダ回路をそれぞれ備える。

【0020】

図2は、遅延列15、16…Nの例示の遅延列構造の模式図である。図2では、複数の遅延列素子203…210が端子201と直列に接続される。各遅延列素子203…210は、同じ遅延、例えば、遅延tuを与える。1ビットメモリ素子211…218は、遅延列素子203…210各々の出力に接続され、メモリ素子のクロック出力は端子202に共通に接続される。メモリ素子211…218の出力は、出力が遅延列の出力に対応するデコーダ回路219に接続される。

【0021】

図2に8つの遅延列素子203…210が示されているが、当業者であれば、本発明の範囲から逸脱することなく、8より多数の遅延列素子または8より少数の遅延列素子を備える遅延列とすることができるとわかるだろう。また、図2に正の論理素子が示されるが、当業者であれば、負の論理素子を用いて図2の遅延列を実装することは本発明の範囲内であるとわかるだろう。

【0022】

操作中、測定される期間の開始時に図2の端子201に開始信号が与えられる。開始信号はその後、遅延列素子203…210全体に伝播し、各遅延素子は開始信号をtu遅らせる。測定期間の終了を表す停止信号が端子202を介して各メモリ素子211…218のクロック出力に与えられる。その後、メモリ素子211…218の出力はデコーダ219に与えられ、デコーダ219は測定される期間を表す値を生成しその値を端子220に与える。

【0023】

当業者であればわかるように、開始信号の遅延列素子203…210全体への伝播は、遅延の境界で測定される。言い換えれば、伝播された開始信号は、各遅延列素子203…210の出力で抽出される。よって、遅延列素子203…210により与えられた遅延tuの整数より後に、開始信号がキャプチャされる。tuの分数は測定されない。同様に、図2の遅延列の分解能は、各遅延列素子203…210により与えられる遅延量またはtuである。

【0024】

ここで、実施形態に係る時間デジタル変換器が備える複数の遅延列は、それぞれバーニア時間デジタル変換回路であってもよい。

【0025】

図3は、遅延列15、16、…Nの別の例示の遅延列構造の模式図である。図3では、遅延列素子203…210は端子201に直列に接続され、遅延列素子203…210の出力は1ビットメモリ素子211…218により抽出される。メモリ素子211…218の出力はデコーダ219に接続される。遅延列素子203…210同様、メモリ素子211…218およびデコーダ219は図2を参照して上述されており、更なる説明は簡単にするために省略する。

【0026】

図3では、遅延素子321…327は、端子202とメモリ素子211…218のクロック入力との間に直列に接続される。具体的には、メモリ素子211のクロック入力は端子202に直接接続され、メモリ素子212のクロック入力は遅延素子321を介して端子202に接続され、メモリ素子213のクロック入力は遅延素子321を介して端子202に接続される。よって、メモリ素子218のクロック入力は全ての遅延素子321…327を介して端子202に接続される。図3の各遅延素子321…327は、遅延列素子203…210により与えられる遅延tuよりも少ない同じ遅延量tcを与える。

【0027】

操作中、開始信号は、測定される期間の開始時に端子201を介して遅延列素子203…210に与えられ、停止信号は測定される時間の終了時に端子202に与えられる。開始信号は、遅延列素子203…210全体に伝播し、停止信号は遅延列素子321…327全体に伝播する。遅延素子321…327の遅延が遅延列素子203…210の遅延よりも少ないので、停止信号は最終的に開始信号に追い付く。停止信号の伝播が遅延素子327の出力に到達すると、メモリ素子211…218の出力がデコーダ219に与えられ、測定される期間を表す結果となる出力が端子220に与えられる。図3の遅延列は分解能tu−tcを有する。

【0028】

図2同様、当業者であれば、図3の遅延列は、本発明の範囲から逸脱することなく、より多数または少数の遅延列素子203…210とそれに関連するメモリ素子211…218および遅延素子321…327とで実装されてもよい。

【0029】

次に、図4を参照し、時間デジタル変換器回路の例示の実装を説明する。図4の時間デジタル変換器は、2つの遅延列42および43を備える。遅延列42および43はどちらかが上述の図2の遅延列または図3の遅延列であってもよい。言うまでもなく、当業者であれば、本発明の範囲から逸脱することなく他の遅延列構造とすることができるとわかるだろう。

【0030】

図4では、遅延列42が端子11に直接接続される一方、遅延列43は遅延素子40を介して端子11に接続される。更に、遅延素子40は、図2の遅延素子が遅延列42および43として用いられる場合、tu/2に等しい遅延を与え、遅延素子40は図3の遅延列が遅延列42およびに43として用いられる場合、(tu−tc)/2を与える。

【0031】

端子12は、遅延列42および43のクロック入力42bおよび43bに直接接続される。遅延列42および43の出力は合成器41で合成され、出力端子19に与えられる。

【0032】

次に、図5のフロー図を参照して図4の時間デジタル変換器の操作を説明する。図5のステップS1では、開始信号が端子11に与えられ、これにより開始信号が遅延列42および遅延素子40に与えられる。遅延素子40の遅延が経過すると、開始信号が遅延列43にも与えられる。同様に、開始信号は同じ速さで遅延列42および43全体に伝播するが、開始信号は遅延列43内で遅延素子40の遅延で遅延またはオフセットされる。

【0033】

図5のステップS2では、停止信号が端子12に供給され、それにより遅延列42および43にも同時に与えられる。S3のように、図2および図3に関し上述したように各遅延列内の開始信号の位置が処理され、各遅延列42および43が対応する出力を合成器41に与える。その後、合成器41は遅延列42および43の出力をステップS4の時間デジタル変換器の全出力へと合成する。

【0034】

次に、図6のタイミング図を説明する。図6は、図4および図5を参照して上述された処理のタイミング図である。図6では、遅延列43がtu/2後に開始信号61を受信する一方、遅延列42は遅延なく開始信号を受信する。開始信号61が遅延列42全体に伝播するので、各遅延素子b1…b8の出力はLow状態からHigh状態へと移る。遅延素子40により与えられた遅延tu/2後、開始信号61bが遅延列43全体に伝播し、各遅延列素子の出力b9…b16をlow状態からhigh状態へと移らせる。

【0035】

所定の時間に、停止信号60が停止端子12に与えられる。停止信号60は、遅延なく遅延列42および43へと直接与えられる。時間65で、停止信号は、遅延列に遅延列素子b1…b16各々の現在の値を「キャプチャ」させる。例えば、時間65では、遅延列42では、b1…b4がhighでb5…b8がlowである一方、遅延列43では、b9…b11がhighでb12…b16がlowである。よって、遅延列42のキャプチャした列の値は「11110000」または4であり、遅延列43のキャプチャした値は「11100000」または3である。演算時間の違いは、遅延素子40により与えられた遅延で除算された値の和となる。

【0036】

理解されるように、図6の遅延列42、43、開始信号61、61b、および停止信号60は一例であり、他の値や構成とすることができる。例えば、本発明の範囲から逸脱することなく、他のレベルおよび信号内での他の相対タイミングとすることができる。同様に、図6は正の論理で説明されており、大きい正の電圧が論理「high」を表し、ゼロまたは小さな電圧は論理「low」を表す。しかし、小さいまたはゼロの電圧が論理「high」を意味し、正の電圧が論理「low」を表す負の論理を用いることもできる。

【0037】

次に、図7を参照し、実施形態に係るガンマ線検出システムを説明する。図7では、光電子倍増管135および140がライトガイド130全体に配置され、シンチレーション結晶アレイ105がライトガイド130の下に配置される。第2のシンチレーション結晶アレイ125がライトガイド115および光電子倍増管(PMT:Photomultiplier Tube)195および110とともにシンチレーション結晶105の反対に配置される。

【0038】

図7では、被検体(不図示)からガンマ線が放出されると、ガンマ線は互いにおよそ180度反対の方向に進む。ガンマ線検出はシンチレーション結晶100および120で同時に起こり、ガンマ線が所定の制限時間内にシンチレーション結晶100および120で検出されるとシンチレーションイベントが決定される。これにより、ガンマ線タイミング検出システムは、シンチレーション結晶110および120で同時にガンマ線を検出する。しかし、簡潔にするため、シンチレーション結晶100に関するガンマ線検出のみを説明する。しかし、当業者であれば、シンチレーション結晶100についての説明がシンチレーション結晶120でのガンマ線検出に同等に適用されることがわかるだろう。

【0039】

各光電子倍増管110、135、140および195は、それぞれ可変ゲイン増幅器、つまり、VGA(Variable Gain Amplifier)150、152、154、および156に接続される。VGA150、152、154、および156は、信号バッファとして機能し、例えば、PMT製造工程の一部として起こる、または、PMTの劣化により起こるPMTゲインの変化に対応するように取得システムを調整させる。VGA150、152、154、および156各々からの信号出力は二つの独立した電子経路に分割される。

【0040】

一つの電子経路がガンマ線の到達時間の測定に用いられる。この経路への信号は、通常、加算増幅器184または186内の同一検出部からの二つ以上の信号を加算することにより形成される。同一検出部からの複数の信号を加算することにより、タイミング試算のために信号対雑音比を改善し、必要となる電子部品の数を減らすことができる。加算後、信号は弁別器187または188へと通過する。通常調整可能な閾値を有する弁別器187または188は、加算後の信号が閾値設定を通過すると、正確に調整された電子パルスを生成する。弁別器の出力が時間デジタル変換器またはTDC189および190を始動させる。TDC189または190は、システムクロック(不図示)に対する弁別器パルスの時間をコード化するデジタル出力を生成する。飛行時間PETシステムでは、TDC189または190は通常15〜25psの精度でタイムスタンプを生成する。

【0041】

各PMT110、135、140、および195は、各PMT110、135、140、および195の信号の振幅の測定に用いられる独立した電子通路がある。この通路は、フィルター160、162、164、166およびアナログ・デジタル変換器、または、ADC(Analog−to−Digital Converter)176、177、178、179から構成される。通常、バンドパスフィルターであるフィルター160、162、164、または166は、測定の信号対雑音比を最適化するために用いられ、ADC176、177、178、または179によるデジタル信号への変換前に、アンチエイリアス機能を行う。ADC176、177、178、または179は、自走式で、100MHzで可動とすることができ、例えば、その場合、中央演算処理部、つまりCPU(Central Processing Unit)、170がデジタル積分行う、または、ADCはピーク感知型としてもよい。ADC出力およびTDC出力は、処理のため、CPU170に与えられる。処理は、ADC出力からのエネルギーおよび位置と、各イベントに対するTDC出力からの到達時間とを試算することを含み、また、エネルギー、位置、および時間の試算を向上させるために過去の校正に基づく多数の補正ステップの利用を処理に含めてもよい。

【0042】

当業者であればわかるように、CPU170は、ディスクリート論理ゲート、ASIC(Application Specific Integrated Circuit)、FPGA(Field Programmable Gate Array)、または他のCPLD(Complex Programmable Logic Device)として実装することができる。FPGAやCPLDの実装は、VHDL、Verilog、また他のハードウェア記述言語によりコード化されてもよく、このコードは、直接FPGAやCPLD内の電子メモリ、または、独立した電子メモリに記憶されてもよい。更に、電子メモリは、ROM、EPEOM、EEPROM、またはFLASHメモリなどの不揮発性メモリであってもよい。電子メモリは、また、ダイナミックRAM、などの揮発性メモリであってもよく、マイクロコントローラやマイクロプロセッサなどのプロセッサを設けて電子メモリだけでなくFPGAまたはCPLDと電子メモリとの相互作用を制御してもよい。

【0043】

代わりに、CPU170は、上記した電子メモリおよび/またはハードディスクドライブ、CD(Compact Disc)、DVD(Digital Versatile Disc)、FLASHドライブまたは他の公知のいずれかの記憶媒体にコンピュータ読み取り可能な一連の命令として実装されてもよい。更に、コンピュータ読み取り可能な命令は、実用用途、バックグラウンドデーモン、またはオペレーティングシステムのコンポーネントとして、または、それらの組み合わせとして与えられてもよく、米国のIntel社のXenon(登録商標)プロセッサや米国のAMD社のOpteron(登録商標)プロセッサなどのプロセッサとマイクロソフト社のVISTA(登録商標)、UNIX(登録商標)、Solaris(登録商標)、LINUX(登録商標)、Apple社のMAC−OS(登録商標)および他の当業者に公知のオペレーティングシステムと合わせて実行する。

【0044】

CPU170により処理されると、処理信号は電子記憶部180に記憶および/または表示部145に表示される。当業者であればわかるように、電子記憶部180は、ハードディスクドライブ、CD−ROMドライブ、DVDドライブ、FLASHドライブ、RAM、ROM、または本技術分野で公知の他の記憶部であってもよい。表示部145はLCD(Liquid Crystal Display)ディスプレイ、CRTディスプレイ、プラズマディスプレイ、OLED(Organic light Emitting Diode)ディスプレイ、LED(Light Emitting Diode)ディスプレイまたは本技術分野で公知の他のディスプレイとして実装されてもよい。同様に、電子記憶部180および表示部145は単なる一例として説明されており、決して本発明の範囲を制限するものではない。

【0045】

図7は、また、インターフェース175を含み、これを介してガンマ線検出システムは他の外部装置および/またはユーザーと接続する。例えば、インターフェース175は、USBインターフェース、PCMCIA(Personal Computer Memory Card International Association)インターフェース、Ethernet(登録商標)インターフェース、または本技術分野で公知の他のインターフェースであってもよい。インターフェース175は、有線でも無線でもよく、キーボードおよび/またはマウスまたは他の本技術分野で公知のユーザーと接続するための他のヒューマンインターフェース装置を備えてもよい。

【0046】

上記説明では、フロー図内のどんな処理、説明、またはブロックも、処理内の特定の論理機能またはステップを達成するための1以上の実行可能な命令を含むコードのモジュール、セグメント、または一部を示すものとして理解されるべきであり、実施形態の範囲内に代替的実施が含まれ、当業者に理解されるように、機能性に応じて、機能が上述の順番と異なる順番でほぼ同時にまたは反対の順番で実行されてもよい。

【0047】

特定の実施形態を説明してきたが、これらの実施形態は例示を目的としたものにすぎず、発明の範囲を制限することを目的としていない。よって、ここで説明した新規の方法、装置、およびシステムが他の様々な形で具体化されてもよく、更に、本発明の主旨から逸脱せずに、ここに説明した方法、装置、およびシステムの形態に各種の削除や入れ替えや変更を行ってもよい。添付の請求項およびその均等物は、これらの形態や変形が本発明の範囲と主旨に当たるものとして対象となることを目的としている。

【符号の説明】

【0048】

13 遅延素子

15、16 遅延列

18 合成器

【技術分野】

【0001】

本明細書で説明する実施形態は、測定精度および分解能を向上させる時間デジタル変換器、時間デジタル変換方法及びガンマ線検出システムに関する。

【背景技術】

【0002】

市販のガンマ線検出器は透明のライトガイドに接続されるシンチレータ結晶アレイを備え、透明ライトガイドは透明ライトガイド全体に配置される光電子倍増管(PMT:Photomultiplier Tube)全体にシンチレーション光を分散する。同一領域でのPMTからの信号は、通常アナログドメインで合計され、その後合計された信号の主要エッジまたはイベントに基づきタイミングが測定される。

【0003】

時間デジタル変換器(TDC:Time−to−Digital−Converter)は、ガンマ線検出器でのタイミング測定に用いられることが多い。TDCは、イベントの実現をイベントが発生した時間に関連づけることができる数に変換する。このタスクを行う様々な方法がある。他の方法には、粗いクロック周期間での多数の超高速論理遷移の計数を用いこのタスクを行うものがある。また、連続して生成されるものとして知られる一連のイベントの発生を示すことが好ましい場合もある。例えば、上昇信号が取得して所定の一連の閾値に到達するタイムマークは、非常に有効な情報になり得る。

【0004】

また、時間デジタル変換器(TDC)は、各種構造で実装されている。まず一つ目の従来構造は、直列に接続された同一遅延素子の単一の列を有するクラシック遅延列である。また、このクラシック遅延列は1ビットメモリ素子一式を備え、各1ビットメモリ素子は遅延素子の一つの出力に接続される。開始信号が遅延素子列の入力へ供給されて、測定される期間の開始を示す。開始信号は遅延素子列全体に伝播する。遅延素子列内で伝播した開始信号の位置をキャプチャするために全てのメモリ素子のクロック入力に同時に与えられる停止信号が、測定される期間の終了を表す。その後、キャプチャされた位置をデコードして開始信号と停止信号との間の遅延が演算され、この遅延は、各遅延素子により与えられる遅延の倍数として測定される期間の長さを演算するために用いられる。

【0005】

よって、クラシック遅延列の分解能は、遅延列内の各遅延素子の時間遅延に限定される。例えば、列内の各遅延素子が遅延tuを与えると、クラシック遅延列の分解能はtuになる。同様に、半導体素子などのクラシック遅延列の物理的実装では、半導体の物理的特徴により最小値tuが制限される。クラシック遅延列内の各遅延素子に対し同じ時点でサンプリングが行われるので、遅延tuへの物理的制限により測定分解能が制限される。

【0006】

もう一つの従来遅延列は、バーニア遅延列である。クラシック遅延列同様、バーニア遅延列は、直列に接続された同一遅延素子の列と、各々が遅延素子の一つの出力に接続される1ビットメモリ素子一式とを有する。また、バーニア遅延列は、直列に接続される同一の遅延素子の第2の遅延列を備える。第2の遅延列内の各遅延素子の出力は、メモリ素子の一つのクロック出力に接続される。ここで、第1遅延列内の遅延素子はそれぞれ遅延tuを与え、第2の遅延列の遅延素子はそれぞれtc<tuとなる遅延tcを与える。

【0007】

操作中、開始信号がバーニア遅延列の第1遅延列に供給され、停止信号が第2の遅延列に供給される。第2遅延列の素子が与える遅延が第1遅延列の素子による遅延よりも少ないので、停止信号が最終的に開始信号に追い付く。停止信号が開始信号に追い付くと、第1遅延列内の開始信号の伝播がメモリ素子によりキャプチャされ、デコードされて開始信号と停止信号との時間間隔が決定される。この測定される期間は、第1遅延列の遅延と第2遅延列の遅延との差の倍数またはtu−tcとして算出される。

【0008】

クラシック遅延列同様、バーニア遅延列内の遅延は、バーニア遅延列が実装される半導体の物理特性により制限される。よって、バーニア遅延列を用いて達成できる最小の遅延差(tu−tc)(つまり、分解能)がある。従って、バーニア遅延列を用いて正確に期間を測定することは困難である。

【0009】

その結果、クラシック遅延列およびバーニア遅延列の制限を改善し、精度および分解能を向上させる装置およびそれに関連する方法が求められている。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2007−41007号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

本発明が解決しようとする課題は、測定精度および分解能を向上させることができる時間デジタル変換器、時間デジタル変換方法及びガンマ線検出システムを提供することである。

【課題を解決するための手段】

【0012】

実施の形態の時間デジタル変換器は、第1遅延列回路と、少なくとも一つの遅延素子と、少なくとも一つの第2遅延列回路と、合成回路とを備える。第1遅延列回路は、開始信号と停止信号との間の遅延時間に対応する第1の値を生成する。少なくとも一つの遅延素子は、前記開始信号に所定の遅延を与えることにより遅延開始信号を生成する。少なくとも一つの第2遅延列回路は、前記遅延開始信号と前記停止信号との間の遅延時間に対応する第2の値を生成する。合成回路は、前記第1の値および前記第2の値に基づいて、前記開始信号と前記停止信号との間の遅延時間に対応する出力値を生成する。

【図面の簡単な説明】

【0013】

【図1】図1は、実施形態に係る時間デジタル変換器の模式図である。

【図2】図2は、実施形態に係る時間デジタル変換器内で用いられる遅延列の模式図である。

【図3】図3は、実施形態に係る時間デジタル変換器内で用いられる別の遅延列の模式図である。

【図4】図4は、実施形態に係る別の時間デジタル変換器の模式図である。

【図5】図5は、実施形態に係る時間デジタル変換方法のフロー図である。

【図6】図6は、実施形態に係る時間デジタル変換のタイミング図である。

【図7】図7は、実施形態に係るガンマ線検出システムの模式図である。

【発明を実施するための形態】

【0014】

実施形態に係る時間デジタル変換器は、通常、開始信号と停止信号との間の時間遅延に対応する第1の値を生成する第1遅延列回路を備える。時間デジタル変換器は、また、遅延開始信号と停止信号との間の時間遅延に対応する第2の値を生成する少なくとも一つの第2遅延列回路を備える。少なくとも一つの遅延素子は、所定の遅延を開始信号に与えることにより遅延開始信号を生成し、合成回路は、第1の値および第2の値に基づく出力値を生成する。実施形態の時間デジタル変換器では、出力値が開始信号と停止信号との間の時間遅延に対応する。

【0015】

ここで、複数の図面に渡り同じ参照符号は同一または対応する部分を示す図面を参照する。図1は、実施形態に係る時間デジタル変換器の模式図である。図1では、複数の遅延列15…Nが端子11に接続されて開始信号を受信し、また、端子12に接続されて停止信号を受信する。遅延列ク15、16…Nのクロック入力15b、16b…Nbは端子12に直接接続されるが、遅延列15だけは、端子11に直接接続される。遅延列16は遅延素子13を介して端子11に接続され、遅延列Nはnと通じ遅延素子13を介して端子11に接続される。遅延列15、16…Nの出力は、時間デジタル変換器の全出力を生成しその全出力を端子19に与える合成器18に接続される。

【0016】

更に、図1では、以下に詳細に示すように、各遅延列15、16…Nは、ほぼ同様の構造およびほぼ同様の分解能を有する。遅延素子13…nは、遅延列15、16…Nの分解能の関数とほぼ同じ遅延量を与える。具体的には、遅延素子13…nそれぞれの遅延は、時間デジタル変換器が備える遅延列回路の数に反比例する。例えば、各遅延列が分解能Rを有する場合、各遅延素子13…nは、遅延量R/Nを与え、その結果、時間デジタル変換器全体の分解能はR/Nになる。

【0017】

当業者であればわかるように、図1の時間デジタル変換器は、遅延列15、16…Nとそれに対応する数の遅延素子13…nをいくつ備えてもよい。更に、合成器18は、時間デジタル変換器が有する全ての遅延列15、16…Nに対応する十分な出力を有する単一の合成器でもよく、また、集まると遅延列15、16…N全てに対応する十分な出力を有する直列の合成器一式であってもよい。合成器18は、また、加算により遅延列15、16…Nの出力を合成してもよく、また、遅延列15、16…Nの出力の平均値を求めてもよい。すなわち、合成器18は、加算器、或いは、平均器であってもよい。また、当業者であればわかるように、合成器18での遅延列15、16…Nの出力の他の合成とすることができる。

【0018】

図1の時間デジタル変換器は、ディスクリート論理ゲート、ASIC(Application Specific Integrated Circuit)、FPGA(Field Programmable Gate Array)、または他のCPLD(Complex Programmable Logic Device)として実装されても良い。FPGAやCPLDの実装では、時間デジタル変換器は、VHDL(Very high speed integrated circuits Hardware Description Language)、Verilog、また他のハードウェア記述言語によりコンピュータ読み取り可能な一連の命令としてコード化されてもよく、このコンピュータ読み取り可能な命令は直接FPGAやCPLD内の電子メモリ、または、独立した電子メモリに記憶されてもよい。更に、電子メモリは、ROM(Read Only Memory)、EPROM(Erasable Programmable Read Only Memory)、EEPROM(Electrically Erasable Programmable Read Only Memory)、またはFLASHメモリなどの不揮発性メモリであってもよい。電子メモリは、また、ダイナミックRAM(Random Access Memory)、などの揮発性メモリであってもよく、マイクロコントローラやマイクロプロセッサなどのプロセッサを設けて電子メモリだけでなくFPGAまたはCPLDと電子メモリとの相互作用を制御してもよい。

【0019】

次に、実施形態に係る時間デジタル変換器に備えられる複数の遅延列の詳細について説明する。複数の遅延列は、同一の所定の遅延を与える複数の遅延列素子を有し、遅延列に前記開始信号が与えられる遅延列素子をそれぞれ備える。また、複数の遅延列は、前記遅延列内の前記複数の遅延列素子の一つにそれぞれ接続され、前記停止信号を受信する共通のクロック入力を有する複数のメモリ素子をそれぞれ備える。また、複数の遅延列は、前記複数のメモリ素子の出力に基づくデジタル値を生成するデコーダ回路をそれぞれ備える。

【0020】

図2は、遅延列15、16…Nの例示の遅延列構造の模式図である。図2では、複数の遅延列素子203…210が端子201と直列に接続される。各遅延列素子203…210は、同じ遅延、例えば、遅延tuを与える。1ビットメモリ素子211…218は、遅延列素子203…210各々の出力に接続され、メモリ素子のクロック出力は端子202に共通に接続される。メモリ素子211…218の出力は、出力が遅延列の出力に対応するデコーダ回路219に接続される。

【0021】

図2に8つの遅延列素子203…210が示されているが、当業者であれば、本発明の範囲から逸脱することなく、8より多数の遅延列素子または8より少数の遅延列素子を備える遅延列とすることができるとわかるだろう。また、図2に正の論理素子が示されるが、当業者であれば、負の論理素子を用いて図2の遅延列を実装することは本発明の範囲内であるとわかるだろう。

【0022】

操作中、測定される期間の開始時に図2の端子201に開始信号が与えられる。開始信号はその後、遅延列素子203…210全体に伝播し、各遅延素子は開始信号をtu遅らせる。測定期間の終了を表す停止信号が端子202を介して各メモリ素子211…218のクロック出力に与えられる。その後、メモリ素子211…218の出力はデコーダ219に与えられ、デコーダ219は測定される期間を表す値を生成しその値を端子220に与える。

【0023】

当業者であればわかるように、開始信号の遅延列素子203…210全体への伝播は、遅延の境界で測定される。言い換えれば、伝播された開始信号は、各遅延列素子203…210の出力で抽出される。よって、遅延列素子203…210により与えられた遅延tuの整数より後に、開始信号がキャプチャされる。tuの分数は測定されない。同様に、図2の遅延列の分解能は、各遅延列素子203…210により与えられる遅延量またはtuである。

【0024】

ここで、実施形態に係る時間デジタル変換器が備える複数の遅延列は、それぞれバーニア時間デジタル変換回路であってもよい。

【0025】

図3は、遅延列15、16、…Nの別の例示の遅延列構造の模式図である。図3では、遅延列素子203…210は端子201に直列に接続され、遅延列素子203…210の出力は1ビットメモリ素子211…218により抽出される。メモリ素子211…218の出力はデコーダ219に接続される。遅延列素子203…210同様、メモリ素子211…218およびデコーダ219は図2を参照して上述されており、更なる説明は簡単にするために省略する。

【0026】

図3では、遅延素子321…327は、端子202とメモリ素子211…218のクロック入力との間に直列に接続される。具体的には、メモリ素子211のクロック入力は端子202に直接接続され、メモリ素子212のクロック入力は遅延素子321を介して端子202に接続され、メモリ素子213のクロック入力は遅延素子321を介して端子202に接続される。よって、メモリ素子218のクロック入力は全ての遅延素子321…327を介して端子202に接続される。図3の各遅延素子321…327は、遅延列素子203…210により与えられる遅延tuよりも少ない同じ遅延量tcを与える。

【0027】

操作中、開始信号は、測定される期間の開始時に端子201を介して遅延列素子203…210に与えられ、停止信号は測定される時間の終了時に端子202に与えられる。開始信号は、遅延列素子203…210全体に伝播し、停止信号は遅延列素子321…327全体に伝播する。遅延素子321…327の遅延が遅延列素子203…210の遅延よりも少ないので、停止信号は最終的に開始信号に追い付く。停止信号の伝播が遅延素子327の出力に到達すると、メモリ素子211…218の出力がデコーダ219に与えられ、測定される期間を表す結果となる出力が端子220に与えられる。図3の遅延列は分解能tu−tcを有する。

【0028】

図2同様、当業者であれば、図3の遅延列は、本発明の範囲から逸脱することなく、より多数または少数の遅延列素子203…210とそれに関連するメモリ素子211…218および遅延素子321…327とで実装されてもよい。

【0029】

次に、図4を参照し、時間デジタル変換器回路の例示の実装を説明する。図4の時間デジタル変換器は、2つの遅延列42および43を備える。遅延列42および43はどちらかが上述の図2の遅延列または図3の遅延列であってもよい。言うまでもなく、当業者であれば、本発明の範囲から逸脱することなく他の遅延列構造とすることができるとわかるだろう。

【0030】

図4では、遅延列42が端子11に直接接続される一方、遅延列43は遅延素子40を介して端子11に接続される。更に、遅延素子40は、図2の遅延素子が遅延列42および43として用いられる場合、tu/2に等しい遅延を与え、遅延素子40は図3の遅延列が遅延列42およびに43として用いられる場合、(tu−tc)/2を与える。

【0031】

端子12は、遅延列42および43のクロック入力42bおよび43bに直接接続される。遅延列42および43の出力は合成器41で合成され、出力端子19に与えられる。

【0032】

次に、図5のフロー図を参照して図4の時間デジタル変換器の操作を説明する。図5のステップS1では、開始信号が端子11に与えられ、これにより開始信号が遅延列42および遅延素子40に与えられる。遅延素子40の遅延が経過すると、開始信号が遅延列43にも与えられる。同様に、開始信号は同じ速さで遅延列42および43全体に伝播するが、開始信号は遅延列43内で遅延素子40の遅延で遅延またはオフセットされる。

【0033】

図5のステップS2では、停止信号が端子12に供給され、それにより遅延列42および43にも同時に与えられる。S3のように、図2および図3に関し上述したように各遅延列内の開始信号の位置が処理され、各遅延列42および43が対応する出力を合成器41に与える。その後、合成器41は遅延列42および43の出力をステップS4の時間デジタル変換器の全出力へと合成する。

【0034】

次に、図6のタイミング図を説明する。図6は、図4および図5を参照して上述された処理のタイミング図である。図6では、遅延列43がtu/2後に開始信号61を受信する一方、遅延列42は遅延なく開始信号を受信する。開始信号61が遅延列42全体に伝播するので、各遅延素子b1…b8の出力はLow状態からHigh状態へと移る。遅延素子40により与えられた遅延tu/2後、開始信号61bが遅延列43全体に伝播し、各遅延列素子の出力b9…b16をlow状態からhigh状態へと移らせる。

【0035】

所定の時間に、停止信号60が停止端子12に与えられる。停止信号60は、遅延なく遅延列42および43へと直接与えられる。時間65で、停止信号は、遅延列に遅延列素子b1…b16各々の現在の値を「キャプチャ」させる。例えば、時間65では、遅延列42では、b1…b4がhighでb5…b8がlowである一方、遅延列43では、b9…b11がhighでb12…b16がlowである。よって、遅延列42のキャプチャした列の値は「11110000」または4であり、遅延列43のキャプチャした値は「11100000」または3である。演算時間の違いは、遅延素子40により与えられた遅延で除算された値の和となる。

【0036】

理解されるように、図6の遅延列42、43、開始信号61、61b、および停止信号60は一例であり、他の値や構成とすることができる。例えば、本発明の範囲から逸脱することなく、他のレベルおよび信号内での他の相対タイミングとすることができる。同様に、図6は正の論理で説明されており、大きい正の電圧が論理「high」を表し、ゼロまたは小さな電圧は論理「low」を表す。しかし、小さいまたはゼロの電圧が論理「high」を意味し、正の電圧が論理「low」を表す負の論理を用いることもできる。

【0037】

次に、図7を参照し、実施形態に係るガンマ線検出システムを説明する。図7では、光電子倍増管135および140がライトガイド130全体に配置され、シンチレーション結晶アレイ105がライトガイド130の下に配置される。第2のシンチレーション結晶アレイ125がライトガイド115および光電子倍増管(PMT:Photomultiplier Tube)195および110とともにシンチレーション結晶105の反対に配置される。

【0038】

図7では、被検体(不図示)からガンマ線が放出されると、ガンマ線は互いにおよそ180度反対の方向に進む。ガンマ線検出はシンチレーション結晶100および120で同時に起こり、ガンマ線が所定の制限時間内にシンチレーション結晶100および120で検出されるとシンチレーションイベントが決定される。これにより、ガンマ線タイミング検出システムは、シンチレーション結晶110および120で同時にガンマ線を検出する。しかし、簡潔にするため、シンチレーション結晶100に関するガンマ線検出のみを説明する。しかし、当業者であれば、シンチレーション結晶100についての説明がシンチレーション結晶120でのガンマ線検出に同等に適用されることがわかるだろう。

【0039】

各光電子倍増管110、135、140および195は、それぞれ可変ゲイン増幅器、つまり、VGA(Variable Gain Amplifier)150、152、154、および156に接続される。VGA150、152、154、および156は、信号バッファとして機能し、例えば、PMT製造工程の一部として起こる、または、PMTの劣化により起こるPMTゲインの変化に対応するように取得システムを調整させる。VGA150、152、154、および156各々からの信号出力は二つの独立した電子経路に分割される。

【0040】

一つの電子経路がガンマ線の到達時間の測定に用いられる。この経路への信号は、通常、加算増幅器184または186内の同一検出部からの二つ以上の信号を加算することにより形成される。同一検出部からの複数の信号を加算することにより、タイミング試算のために信号対雑音比を改善し、必要となる電子部品の数を減らすことができる。加算後、信号は弁別器187または188へと通過する。通常調整可能な閾値を有する弁別器187または188は、加算後の信号が閾値設定を通過すると、正確に調整された電子パルスを生成する。弁別器の出力が時間デジタル変換器またはTDC189および190を始動させる。TDC189または190は、システムクロック(不図示)に対する弁別器パルスの時間をコード化するデジタル出力を生成する。飛行時間PETシステムでは、TDC189または190は通常15〜25psの精度でタイムスタンプを生成する。

【0041】

各PMT110、135、140、および195は、各PMT110、135、140、および195の信号の振幅の測定に用いられる独立した電子通路がある。この通路は、フィルター160、162、164、166およびアナログ・デジタル変換器、または、ADC(Analog−to−Digital Converter)176、177、178、179から構成される。通常、バンドパスフィルターであるフィルター160、162、164、または166は、測定の信号対雑音比を最適化するために用いられ、ADC176、177、178、または179によるデジタル信号への変換前に、アンチエイリアス機能を行う。ADC176、177、178、または179は、自走式で、100MHzで可動とすることができ、例えば、その場合、中央演算処理部、つまりCPU(Central Processing Unit)、170がデジタル積分行う、または、ADCはピーク感知型としてもよい。ADC出力およびTDC出力は、処理のため、CPU170に与えられる。処理は、ADC出力からのエネルギーおよび位置と、各イベントに対するTDC出力からの到達時間とを試算することを含み、また、エネルギー、位置、および時間の試算を向上させるために過去の校正に基づく多数の補正ステップの利用を処理に含めてもよい。

【0042】

当業者であればわかるように、CPU170は、ディスクリート論理ゲート、ASIC(Application Specific Integrated Circuit)、FPGA(Field Programmable Gate Array)、または他のCPLD(Complex Programmable Logic Device)として実装することができる。FPGAやCPLDの実装は、VHDL、Verilog、また他のハードウェア記述言語によりコード化されてもよく、このコードは、直接FPGAやCPLD内の電子メモリ、または、独立した電子メモリに記憶されてもよい。更に、電子メモリは、ROM、EPEOM、EEPROM、またはFLASHメモリなどの不揮発性メモリであってもよい。電子メモリは、また、ダイナミックRAM、などの揮発性メモリであってもよく、マイクロコントローラやマイクロプロセッサなどのプロセッサを設けて電子メモリだけでなくFPGAまたはCPLDと電子メモリとの相互作用を制御してもよい。

【0043】

代わりに、CPU170は、上記した電子メモリおよび/またはハードディスクドライブ、CD(Compact Disc)、DVD(Digital Versatile Disc)、FLASHドライブまたは他の公知のいずれかの記憶媒体にコンピュータ読み取り可能な一連の命令として実装されてもよい。更に、コンピュータ読み取り可能な命令は、実用用途、バックグラウンドデーモン、またはオペレーティングシステムのコンポーネントとして、または、それらの組み合わせとして与えられてもよく、米国のIntel社のXenon(登録商標)プロセッサや米国のAMD社のOpteron(登録商標)プロセッサなどのプロセッサとマイクロソフト社のVISTA(登録商標)、UNIX(登録商標)、Solaris(登録商標)、LINUX(登録商標)、Apple社のMAC−OS(登録商標)および他の当業者に公知のオペレーティングシステムと合わせて実行する。

【0044】

CPU170により処理されると、処理信号は電子記憶部180に記憶および/または表示部145に表示される。当業者であればわかるように、電子記憶部180は、ハードディスクドライブ、CD−ROMドライブ、DVDドライブ、FLASHドライブ、RAM、ROM、または本技術分野で公知の他の記憶部であってもよい。表示部145はLCD(Liquid Crystal Display)ディスプレイ、CRTディスプレイ、プラズマディスプレイ、OLED(Organic light Emitting Diode)ディスプレイ、LED(Light Emitting Diode)ディスプレイまたは本技術分野で公知の他のディスプレイとして実装されてもよい。同様に、電子記憶部180および表示部145は単なる一例として説明されており、決して本発明の範囲を制限するものではない。

【0045】

図7は、また、インターフェース175を含み、これを介してガンマ線検出システムは他の外部装置および/またはユーザーと接続する。例えば、インターフェース175は、USBインターフェース、PCMCIA(Personal Computer Memory Card International Association)インターフェース、Ethernet(登録商標)インターフェース、または本技術分野で公知の他のインターフェースであってもよい。インターフェース175は、有線でも無線でもよく、キーボードおよび/またはマウスまたは他の本技術分野で公知のユーザーと接続するための他のヒューマンインターフェース装置を備えてもよい。

【0046】

上記説明では、フロー図内のどんな処理、説明、またはブロックも、処理内の特定の論理機能またはステップを達成するための1以上の実行可能な命令を含むコードのモジュール、セグメント、または一部を示すものとして理解されるべきであり、実施形態の範囲内に代替的実施が含まれ、当業者に理解されるように、機能性に応じて、機能が上述の順番と異なる順番でほぼ同時にまたは反対の順番で実行されてもよい。

【0047】

特定の実施形態を説明してきたが、これらの実施形態は例示を目的としたものにすぎず、発明の範囲を制限することを目的としていない。よって、ここで説明した新規の方法、装置、およびシステムが他の様々な形で具体化されてもよく、更に、本発明の主旨から逸脱せずに、ここに説明した方法、装置、およびシステムの形態に各種の削除や入れ替えや変更を行ってもよい。添付の請求項およびその均等物は、これらの形態や変形が本発明の範囲と主旨に当たるものとして対象となることを目的としている。

【符号の説明】

【0048】

13 遅延素子

15、16 遅延列

18 合成器

【特許請求の範囲】

【請求項1】

開始信号と停止信号との間の遅延時間に対応する第1の値を生成する第1遅延列回路と、

前記開始信号に所定の遅延を与えることにより遅延開始信号を生成する少なくとも一つの遅延素子と、

前記遅延開始信号と前記停止信号との間の遅延時間に対応する第2の値を生成する少なくとも一つの第2遅延列回路と、

前記第1の値および前記第2の値に基づいて、前記開始信号と前記停止信号との間の遅延時間に対応する出力値を生成する合成回路と、

を備えることを特徴とする時間デジタル変換器。

【請求項2】

前記第1の遅延列回路および前記第の2遅延列回路は、

同一の所定の遅延を与える複数の遅延列素子を有し、遅延列に前記開始信号が与えられる遅延列素子と、

前記遅延列内の前記複数の遅延列素子の一つにそれぞれ接続され、前記停止信号を受信する共通のクロック入力を有する複数のメモリ素子と、

前記複数のメモリ素子の出力に基づくデジタル値を生成するデコーダ回路と、

をそれぞれ有することを特徴とする請求項1に記載の時間デジタル変換器。

【請求項3】

前記第1遅延列回路および前記少なくとも一つの第2遅延列回路はそれぞれバーニア時間デジタル変換回路であることを特徴とする請求項1又は2に記載の時間デジタル変換器。

【請求項4】

前記合成回路は加算器であることを特徴とする請求項1又は2に記載の時間デジタル変換器。

【請求項5】

前記合成回路は平均器であることを特徴とする請求項1又は2に記載の時間デジタル変換器。

【請求項6】

前記遅延素子の前記所定の遅延は、該時間デジタル変換器が備える遅延列回路の数に反比例することを特徴とする請求項1又は2に記載の時間デジタル変換器。

【請求項7】

時間デジタル変換器の分解能を向上させる方法であり、

第1の時間デジタル変換器で開始信号と停止信号との間の遅延時間を表す第1の値を生成するステップと、

前記開始信号を所定の遅延で遅延させる少なくとも一つのステップと、

遅延させた前記開始信号と前記停止信号との間の遅延時間を表す第2の値を生成する少なくとも一つのステップと、

前記第1の値および前記第2の値を前記開始信号と前記停止信号との間の遅延時間を表す出力値へと合成するステップと、

を含むことを特徴とする時間デジタル変換方法。

【請求項8】

前記第1の値を生成することおよび前記第2の値を生成するステップは、

複数の遅延列素子を備える遅延列内の前記開始信号を遅延するステップと、

前記停止信号に応じて、複数のメモリ素子内の前記遅延列素子各々の出力をキャプチャするステップと、

前記複数のメモリ素子の出力に基づくデジタル値を生成するステップと、

をそれぞれ含むことを特徴とする請求項7に記載の時間デジタル変換方法。

【請求項9】

前記合成ステップは、前記第1の値および前記第2の値を加算するステップを含むことを特徴とする請求項7又は8に記載の時間デジタル変換方法。

【請求項10】

前記合成ステップは、前記第1の値および前記第2の値を平均するステップを含むことを特徴とする請求項7又は8に記載の時間デジタル変換方法。

【請求項11】

前記遅延ステップは、生成される第1の値および第2の値の逆数で前記開始信号を遅延させるステップを含むことを特徴とする請求項7又は8に記載の時間デジタル変換方法。

【請求項12】

ガンマ線との相互作用に応じてシンチレーション光を生成する複数のシンチレーション結晶と、

前記シンチレーション結晶により生成される前記シンチレーション光を検出するために配置され、前記シンチレーション光の検出に応じて検出信号を生成する複数の光電子倍増管と、

前記ガンマ線の到達時間を決定する時間デジタル変換器と、

を備え、

前記時間デジタル変換器は、

前記検出信号のエッジに対応する開始信号と停止信号との間の遅延時間に対応する第1の値を生成する第1遅延列回路と、

前記開始信号に所定の遅延を与えることにより遅延開始信号を生成する少なくとも一つの遅延素子と、

前記遅延開始信号と前記停止信号との間の遅延時間に対応する第2の値を生成する少なくとも一つの第2遅延列回路と、

前記第1の値および前記第2の値に基づいて、前記ガンマ線の前記到達時間に対応する出力値を生成する合成回路と、

を有することを特徴とするガンマ線検出システム。

【請求項1】

開始信号と停止信号との間の遅延時間に対応する第1の値を生成する第1遅延列回路と、

前記開始信号に所定の遅延を与えることにより遅延開始信号を生成する少なくとも一つの遅延素子と、

前記遅延開始信号と前記停止信号との間の遅延時間に対応する第2の値を生成する少なくとも一つの第2遅延列回路と、

前記第1の値および前記第2の値に基づいて、前記開始信号と前記停止信号との間の遅延時間に対応する出力値を生成する合成回路と、

を備えることを特徴とする時間デジタル変換器。

【請求項2】

前記第1の遅延列回路および前記第の2遅延列回路は、

同一の所定の遅延を与える複数の遅延列素子を有し、遅延列に前記開始信号が与えられる遅延列素子と、

前記遅延列内の前記複数の遅延列素子の一つにそれぞれ接続され、前記停止信号を受信する共通のクロック入力を有する複数のメモリ素子と、

前記複数のメモリ素子の出力に基づくデジタル値を生成するデコーダ回路と、

をそれぞれ有することを特徴とする請求項1に記載の時間デジタル変換器。

【請求項3】

前記第1遅延列回路および前記少なくとも一つの第2遅延列回路はそれぞれバーニア時間デジタル変換回路であることを特徴とする請求項1又は2に記載の時間デジタル変換器。

【請求項4】

前記合成回路は加算器であることを特徴とする請求項1又は2に記載の時間デジタル変換器。

【請求項5】

前記合成回路は平均器であることを特徴とする請求項1又は2に記載の時間デジタル変換器。

【請求項6】

前記遅延素子の前記所定の遅延は、該時間デジタル変換器が備える遅延列回路の数に反比例することを特徴とする請求項1又は2に記載の時間デジタル変換器。

【請求項7】

時間デジタル変換器の分解能を向上させる方法であり、

第1の時間デジタル変換器で開始信号と停止信号との間の遅延時間を表す第1の値を生成するステップと、

前記開始信号を所定の遅延で遅延させる少なくとも一つのステップと、

遅延させた前記開始信号と前記停止信号との間の遅延時間を表す第2の値を生成する少なくとも一つのステップと、

前記第1の値および前記第2の値を前記開始信号と前記停止信号との間の遅延時間を表す出力値へと合成するステップと、

を含むことを特徴とする時間デジタル変換方法。

【請求項8】

前記第1の値を生成することおよび前記第2の値を生成するステップは、

複数の遅延列素子を備える遅延列内の前記開始信号を遅延するステップと、

前記停止信号に応じて、複数のメモリ素子内の前記遅延列素子各々の出力をキャプチャするステップと、

前記複数のメモリ素子の出力に基づくデジタル値を生成するステップと、

をそれぞれ含むことを特徴とする請求項7に記載の時間デジタル変換方法。

【請求項9】

前記合成ステップは、前記第1の値および前記第2の値を加算するステップを含むことを特徴とする請求項7又は8に記載の時間デジタル変換方法。

【請求項10】

前記合成ステップは、前記第1の値および前記第2の値を平均するステップを含むことを特徴とする請求項7又は8に記載の時間デジタル変換方法。

【請求項11】

前記遅延ステップは、生成される第1の値および第2の値の逆数で前記開始信号を遅延させるステップを含むことを特徴とする請求項7又は8に記載の時間デジタル変換方法。

【請求項12】

ガンマ線との相互作用に応じてシンチレーション光を生成する複数のシンチレーション結晶と、

前記シンチレーション結晶により生成される前記シンチレーション光を検出するために配置され、前記シンチレーション光の検出に応じて検出信号を生成する複数の光電子倍増管と、

前記ガンマ線の到達時間を決定する時間デジタル変換器と、

を備え、

前記時間デジタル変換器は、

前記検出信号のエッジに対応する開始信号と停止信号との間の遅延時間に対応する第1の値を生成する第1遅延列回路と、

前記開始信号に所定の遅延を与えることにより遅延開始信号を生成する少なくとも一つの遅延素子と、

前記遅延開始信号と前記停止信号との間の遅延時間に対応する第2の値を生成する少なくとも一つの第2遅延列回路と、

前記第1の値および前記第2の値に基づいて、前記ガンマ線の前記到達時間に対応する出力値を生成する合成回路と、

を有することを特徴とするガンマ線検出システム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2012−100252(P2012−100252A)

【公開日】平成24年5月24日(2012.5.24)

【国際特許分類】

【出願番号】特願2011−210428(P2011−210428)

【出願日】平成23年9月27日(2011.9.27)

【出願人】(000003078)株式会社東芝 (54,554)

【出願人】(594164542)東芝メディカルシステムズ株式会社 (4,066)

【Fターム(参考)】

【公開日】平成24年5月24日(2012.5.24)

【国際特許分類】

【出願日】平成23年9月27日(2011.9.27)

【出願人】(000003078)株式会社東芝 (54,554)

【出願人】(594164542)東芝メディカルシステムズ株式会社 (4,066)

【Fターム(参考)】

[ Back to top ]