暗号処理装置

【課題】DPA攻撃に対する耐性を高めることのできる、暗号処理装置および暗号処理方法を提供する。

【解決手段】処理対象データを取得し、前記処理対象データにラウンド処理を施して中間データを生成する、ラウンド処理部と、乱数データを生成する乱数データ生成部と、前記中間データまたは前記乱数データを格納する記憶回路と、前記記憶回路に前記中間データと前記乱数データとのうちのどちらを格納するかを選択する選択制御部とを具備する。前記選択制御部は、前記中間データが格納された後に前記乱数データが格納されるように、前記記憶回路に格納するデータを選択する。

【解決手段】処理対象データを取得し、前記処理対象データにラウンド処理を施して中間データを生成する、ラウンド処理部と、乱数データを生成する乱数データ生成部と、前記中間データまたは前記乱数データを格納する記憶回路と、前記記憶回路に前記中間データと前記乱数データとのうちのどちらを格納するかを選択する選択制御部とを具備する。前記選択制御部は、前記中間データが格納された後に前記乱数データが格納されるように、前記記憶回路に格納するデータを選択する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、暗号処理装置及び暗号処理方法に関する。

【背景技術】

【0002】

セキュリティの必要性が高まっている。これに伴い、大容量のデータを高速に暗号化することのできる暗号処理装置の必要性が、高まっている。大容量データに対応するために、共通鍵暗号機能を用いることが有効である。その共有鍵暗号としては、例えば、TDES(Triple Data Encryption Standard)、及びAES(Advanced Encryption Standard)などが挙げられる。また、高速化を実現するためには、例えば、ハードウェアによって暗号処理装置を実現することが有効である。

【0003】

共通鍵暗号機能を搭載した暗号処理装置においては、サイドチャネル攻撃の一つである電力差分解析(DPA :Differential Power Analysis)の脅威が拡大している(例えば、非特許文献1;Paul Kocher、 Joshua Jaffe、 Benjamin Jun、 “Introduction to Differential Power Analysis and Related Attacks”、 1998.参照)。

【0004】

サイドチャネル攻撃では、暗号化処理時に生じるサイドチャネル情報(例えば、消費電力、電磁波、及び処理時間など)を利用して、暗号の秘密鍵が推定される。暗号処理装置においては、暗号化処理の途中で生成される中間データにより、消費電力が異なることがある。DPAでは、消費電力を計測することにより、中間データを推測し、秘密鍵が推測される。なお、サイドチャネル情報として電磁波などを用いた場合も、同様である(例えば、非特許文献2;K. Gandolfi、 C. Mourtel、 and F. Olivier、 “Electromagnetic Analysis: Concrete Results、” CHES 2001、 LNCS 2162、 pp.251−262、 2001.参照)。

【0005】

DPAの対策に関連する技術として、特許文献1(特開2000−305453)に記載された暗号化装置が挙げられる。この暗号化装置においては、中間データ制御手段が、乱数を入力として、中間データを乱数に依存して変化させる乱数依存中間データ変更操作を中間データ変更要求の発生時点で行う点が記載されている。この暗号化装置では、暗号化処理の中間段階で必要なデータが乱数に依存して変化する。中間データ間の演算を行なっている時点の電力を測定することによって中間データの情報を引き出そうとしても、中間データの値が乱数の影響を受けているために、乱数の影響によって消費電力が変化しているのか、実際の暗号化処理に必要なデータの影響によって消費電力が変化しているのかを判断することが困難となる。そのため、DAPに対する耐性を高めることができる。

【0006】

しかしながら、特許文献1に記載された暗号化装置では、乱数によって変化されたデータに対して暗号化処理が行われるため、処理が複雑化し、回路規模の増大してしまう。また、及び処理能力も低下してしまう。

【0007】

一方、特許文献2(特開2005−31471)には、処理アルゴリズムを複雑化させることなく、暗号解析の困難性を高めることを課題とした、暗号処理装置が開示されている。図1は、特許文献2に記載された暗号処理装置を示す図である。図1に示されるように、この暗号処理装置は、F関数部300、第1データ格納部310、及び第2データ格納部320を有している。この暗号処理装置においては、F関数部300で得られた中間データ出力値は、排他論理和部306を介して、第1データ格納部310に含まれるRレジスタ312およびLレジスタ311にそのまま格納される。また、排他論理和部306の出力データの反転データが、第2データ格納部320に含まれるR’レジスタ322及びL’レジスタ332に格納される。この結果、レジスタ格納処理におけるハミングウェイトの和を一定に保つことができる。ハミングウェイトは、消費電力に影響を与える。ハミングウェイトの和を一定に保つことにより、消費電力からハミングウェイトを推測することが困難になり、消費電力の変化に基づき解析の困難性を高めることができる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2000−305453

【特許文献2】特開2005−31471

【非特許文献】

【0009】

【非特許文献1】Paul Kocher、 Joshua Jaffe、 Benjamin Jun、 “Introduction to Differential Power Analysis and Related Attacks”、 1998.

【非特許文献2】K. Gandolfi、 C. Mourtel、 and F. Olivier、 “Electromagnetic Analysis: Concrete Results、” CHES 2001、 LNCS 2162、 pp.251−262、 2001.

【発明の概要】

【発明が解決しようとする課題】

【0010】

暗号処理装置では、通常、入力データに対して、複数回のラウンド処理が実施され、出力データが得られる。各ラウンド処理で得られる中間データは、レジスタに格納される。レジスタに格納される中間データは、ラウンド処理が実行されるたびに、変化する。消費電力の変化量は、レジスタに格納されたデータが変化したときのハミング重み及びハミング距離に依存する。従って、消費電力の変化を計測することにより、計測結果からハミング重み又はハミング距離が推測され、その推測結果により秘密鍵が特定される可能性がある。なお、暗号処理装置がソフトウェアにより実現される場合には、ハミング重みが消費電力に影響を与え易い。一方、暗号処理装置がハードウェアにより実現される場合には、ハミング距離(データ遷移量)が消費電力に影響を与え易い。

【0011】

既述の特許文献2に記載された暗号処理装置によれば、ハミング重みが消費電力に影響を与える主要因である場合には、DPA耐性を有する。しかし、特許文献2には、データ遷移量に関する記載がない。特許文献2に記載された暗号処理装置においては、データ遷移量の点では、DPA耐性がむしろ悪化していると考えられる。以下に、この点について説明する。

【0012】

図2は、図1に記載の暗号化処理回路における、排他論理和部306の出力データ、ハミング重み、及びデータ遷移量の関係の一例を示す図である。図1には、排他論理和部306の出力データ、Rレジスタ312に格納されるデータ、R’レジスタに格納されるデータ、ハミング重み、及びデータ遷移量の関係が示されている。ハミング重みは、Rレジスタ、R’レジスタ、及びRレジスタとR’レジスタとの和、について、示されている。データ遷移量も、同様に、Rレジスタ、R’レジスタ、及びRレジスタとR’レジスタとの和について、示されている。なお、実際には、各データは32ビットであるが、以下では、32ビット中の特定の4ビットに着目して説明する。

【0013】

図2に示されるように、時刻t=0の排他的論理和部306の出力データ(Rレジスタ312に格納されるデータ)が、「4’b0000」であるものとする。そして、時刻t=0〜時刻t4までの間において、ハミング重みが1ずつ増えるように、出力データが変化するものとする。また、時刻t=5〜時刻t=9までの間においては、データの遷移量が0から1ずつ増えるように、出力データが変化しているものとする。

【0014】

まず、ハミング重みについて説明する。時刻t=0〜時刻t=4において、Rレジスタでは、ハミング重みはが、0から4まで、1ずつ増加する。これに対して、R’レジスタでは、ハミング重みが、4から0まで、1ずつ減少する。その結果、各時刻では、Rレジスタのハミング重みとR’レジスタのハミング重みの和が、常に4になる。また、t=5以降も同様に、各時刻におけるハミング重みの和は4であり、ハミング重みの和が一定であることが確認できる。

【0015】

次いで、データ遷移量について説明する。時刻t=5〜時刻t=9において、Rレジスタでは、前時刻からのデータ遷移量が、0から4まで、1ずつ増加する。R’レジスタでも、同様に、データ遷移量が0から4まで、1ずつ増加する。その結果、Rレジスタのデータ遷移量とR’レジスタのデータ遷移量との和は、0から8まで、2ずつ増加している。従って、データ遷移量の変化が消費電力を変化させる場合には、消費電力からデータ遷移量が推測されてしまう可能性がある。その結果、DPAによる攻撃を許してしまう可能性がある。また、データ遷移量の和は、未対策時と比較して2倍になる。したがって、データ遷移量の観点からは、DPA耐性がむしろ悪化しているともいえる。

【課題を解決するための手段】

【0016】

本発明に係る暗号処理装置は、処理対象データを取得し、前記処理対象データにラウンド処理を施して中間データを生成する、ラウンド処理部と、乱数データを生成する乱数データ生成部と、前記中間データまたは前記乱数データを格納する記憶回路と、前記記憶回路に前記中間データと前記乱数データとのうちのどちらを格納するかを選択する選択制御部とを具備する。前記選択制御部は、前記中間データが格納された後に前記乱数データが格納されるように、前記記憶回路に格納するデータを選択する。

【0017】

本発明に係る暗号処理方法は、処理対象データを取得し、前記処理対象データにラウンド処理を施して中間データを生成するステップと、乱数データを生成するステップと、記憶回路に、前記中間データまたは前記乱数データを格納するステップと、前記記憶回路に前記中間データと前記乱数データとのうちのどちらを格納するかを選択するステップとを具備する。前記選択するステップは、前記中間データが格納された後に前記乱数データが格納されるように、前記記憶回路に格納するデータを選択するステップを含む。

【発明の効果】

【0018】

本発明によれば、DPA攻撃に対する耐性を高めることのできる、暗号処理装置および暗号処理方法が提供される。

【図面の簡単な説明】

【0019】

【図1】特許文献2に記載された暗号処理装置を示す図である。

【図2】出力データ、ハミング重み、及びデータ遷移量の関係の一例を示す図である。

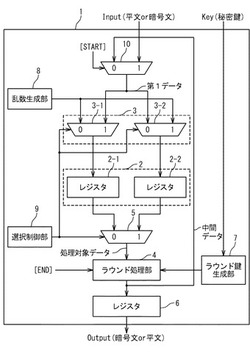

【図3】暗号処理装置を示す構成図である。

【図4】暗号処理装置の動作方法を示すタイミングチャートである。

【図5】変形例に係る暗号処理装置を示す概略図である。

【発明を実施するための形態】

【0020】

以下に、図面を参照しつつ、本発明の実施形態について説明する。

【0021】

図3は、本実施形態に係る暗号処理装置1を示す構成図である。この暗号処理装置1は、入力データ(Input;平文)と、秘密鍵データとに基づいて、入力データに対して暗号処理を施して暗号文を示す出力データを生成するように構成されている。この暗号処理装置1は、ハードウェアにより実現される。

【0022】

図3に示されるように、暗号処理装置1は、セレクタ10、レジスタ部2(記憶回路部)、レジスタ入力セレクタ(3−1、3−2)、レジスタ出力セレクタ5、ラウンド処理部4、レジスタ6、ラウンド鍵生成部7、乱数生成部8、及び選択制御部9を備えている。レジスタ部2は、複数の記憶回路として、複数のレジスタ(2−1、2−2)を備えている。

【0023】

セレクタ10は、入力データ(平文)と、ラウンド処理部4の出力データ(中間データ)とのうちの一方を選択し、出力するように構成されている。セレクタ10は、開始信号Startを取得し、開始信号Startに基づいて、入力データと中間データとのうちのいずれかを選択する。なお、開始信号Startは、図示しない開始信号生成回路により生成される。選択されたデータ(以下、第1データと称す)は、レジスタ入力セレクタ3−1及びレジスタ入力セレクタ3−2に、供給される。

【0024】

乱数生成部8は、乱数データを生成する回路である。生成された乱数データは、レジスタ入力セレクタ3−1及びレジスタ入力セレクタ3−2に供給される。

【0025】

選択制御部9は、レジスタ入力セレクタ3−1、レジスタ入力セレクタ3−2、及びセレクタ5の動作を制御する回路である。選択制御回路9は、選択制御信号を生成し、レジスタ入力セレクタ3−1、レジスタ入力セレクタ3−2、及びセレクタ5に供給する。

【0026】

レジスタ入力セレクタ3−1は、選択制御信号に基づいて、第1データと、乱数データとのうちの一方を選択する。具体的には、レジスタ入力セレクタ3−1は、選択制御信号がハイレベル「1」である場合に第1データを選択し、選択制御信号がローレベル「0」である場合に乱数データを選択するように構成されている。そして、クロック信号CLKがハイレベルに立ち上がったタイミングで、選択したデータをレジスタ2−1に格納する。なお、クロック信号CLKは、図示しないクロック信号生成回路により生成される。

【0027】

同様に、レジスタ入力セレクタ3−2も、選択制御信号に基づいて、第1選択データと乱数データとのうちの一方を選択する。そして、クロック信号CLKがハイレベルに立ち上がったタイミングで、選択したデータをレジスタ2−2に格納する。なお、レジスタ入力セレクタ3−1及びレジスタ入力セレクタ3−2は、一方のセレクタが第1データを選択している場合に、他方のセレクタが乱数データを選択するように、設定されている。すなわち、レジスタ入力セレクタ3−2は、選択制御信号がローレベル「0」である場合に第1データを選択し、選択制御信号がハイレベル「1」である場合に乱数データを選択するように構成されている。

【0028】

各レジスタ2(2−1、2−2)は、第1データ又は乱数データを格納する。また、各レジスタ2は、保持しているデータを、セレクタ5に供給する。

【0029】

セレクタ5は、選択制御信号に基づいて、複数のレジスタ2から供給された複数のデータから、第1データを選択する。そして、クロック信号CLKがハイレベルに立ち上がったタイミングで、選択した第1データを、処理対象データとしてラウンド処理部4に供給する。具体的には、セレクタ5は、選択制御信号がローレベル「0」である場合にレジスタ2−1に格納されたデータを選択し、選択制御信号がハイレベル「1」である場合にレジスタ2−2に格納されたデータを選択するように、構成されている。

【0030】

ラウンド鍵生成部7は、予め準備された秘密鍵データを取得し、秘密鍵データに基づいて、ラウンド鍵データを生成する。ラウンド鍵データは、ラウンド処理部4に供給される。

【0031】

ラウンド処理部4は、セレクタ5から処理対象データを取得すると、ラウンド鍵データを用いて処理対象データにラウンド処理を施す。ラウンド処理の結果、中間データが生成される。中間データは、既述のように、セレクタ10に供給される。なお、ラウンド処理の実行回数が規定回数に達している場合には、ラウンド処理の結果得られたデータは、出力データとして、レジスタ6に格納される。具体的には、ラウンド処理の実行回数が規定回数に達した場合には、図示しない終了信号生成回路が、ハイレベルレベルの信号を終了信号ENDとしてラウンド処理部4に供給する。ラウンド処理部4は、終了信号ENDを取得した場合に、出力データをレジスタ6に格納する。

【0032】

レジスタ6は、本暗号処理装置1の結果として、出力データを出力する。

【0033】

続いて、本実施形態に係る暗号処理装置1の動作方法について説明する。図4は、暗号処理装置1の動作方法を示すタイミングチャートである。図4には、クロック信号[CLK]、秘密鍵データ[Key]、入力データ[D_in]、乱数データ[Random]、ラウンド鍵データ[Ki]、開始信号[Start]、選択制御信号[Sel]、レジスタ2−1に格納されるデータ[Reg_1]、レジスタ2−2に格納されるデータ[Reg_2]、ラウンド処理部4に供給されるデータ(処理対象データ)[F_in]、ラウンド処理部4が出力するデータ[F_out]、終了信号[End]、及び出力データ[Reg_o]が示されている。

【0034】

図4に示されるように、クロック信号CLKがローレベルからハイレベルに立ち上がるタイミングが、時刻t0、時刻t1、時刻t2、・・・時刻tnとして記載されている。

【0035】

まず、時刻t0から時刻t1までの動作について説明する。

【0036】

時刻t0において、暗号処理装置1が動作を開始したとする。すると、開始信号Startとして、ハイレベルの信号が供給される。また、秘密鍵データ[Key]として、秘密鍵データKeyが供給される。また、入力データ[D_in]として、入力データD0が供給される。

【0037】

開始信号Startとしてハイレベルの信号が供給されると、セレクタ10が、第1データとして、入力データD0を選択する。また、選択制御部9は、選択制御信号Selとして、ハイレベルの信号を供給する。これにより、レジスタ入力セレクタ3−1は第1データ(入力データD0)を選択し、レジスタ入力セレクタ3−2は乱数データR0を選択する。すなwち、選択制御部9は、第1データを格納するレジスタ(選択レジスタ)として、レジスタ2−1を選択したことになる。なお、以下の説明において、選択レジスタとして選択されなかったレジスタ2−2は、非選択レジスタと記載される。

【0038】

次いで、時刻t1から時刻t2までの動作について説明する。

【0039】

クロック信号CLKがハイレベルに立ち上がったとき(時刻t1)に、レジスタ入力セレクタ3−1は、選択した第1データ(入力データD0)をレジスタ2−1(選択レジスタ)に格納する。これにより、レジスタ2−1に格納されるデータReg_1は、入力データD0になる。また、レジスタ入力セレクタ3−1は、選択した乱数データR0を、レジスタ2−2(非選択レジスタ)に格納する。これにより、レジスタ2−2に格納されるデータReg_2は、乱数データR0になる。各レジスタ2にデータが格納された後、開始信号Startは、ロウレベルに戻される。

【0040】

また、ラウンド鍵生成部7は、秘密鍵データKeyに基づいて、ラウンド鍵データK1を生成する。

【0041】

その後、選択制御部9は、選択制御信号Selのレベルを反転させ、ロウレベルの信号を供給する。これにより、セレクタ5は、レジスタ2−1に格納されているデータ(第1データ=入力データD0)を選択し、ラウンド処理部4へ処理対象データとして供給する。すなわち、処理対象データ[F_in]は、入力データD0になる。また、選択制御部9は、選択制御信号Selのレベルを反転させたことにより、選択レジスタ(第1データが格納されるレジスタ)を、レジスタ2−1からレジスタ2−2に変更したことになる。すなわち、変更後の選択レジスタは、レジスタ2−2になる。また、レジスタ2−1は、変更後の非選択レジスタになる。

【0042】

ラウンド処理部4は、処理対象データ(入力データD0)を取得すると、処理対象データに対して、ラウンド処理を施し、中間データD1を生成する。すなわち、ラウンド処理部4が出力するデータ[F_out]は、中間データD1になる。

【0043】

中間データD1が生成された段階では、開始信号Startは、ロウレベルに戻されている。そのため、セレクタ10は、第1データとして、中間データD1を選択する。このとき、選択制御信号Selがロウレベルであるため、セレクタ3−1が乱数データR1を選択し、セレクタ3−2が中間データD1を選択する。

【0044】

次いで、時刻t2以降の動作について説明する。クロック信号CLKが立ち上がったタイミング(時刻t2)において、セレクタ3−1が乱数データR1をレジスタ2−1(変更後の非選択レジスタ)に格納する。すなわち、レジスタ2−1に格納されるデータ[Reg_1]は、乱数データR1になる。また、セレクタ3−2は、中間データD1を、レジスタ2−2(変更後の選択レジスタ)に格納する。すなわち、レジスタ2−2に格納されるデータ[Reg_2]は、中間データD1になる。

【0045】

上述のような処理が、選択制御信号Selが反転されながら、規定の回数(n回)繰り返される。そして、ラウンド処理部4がラウンド処理を行った回数が規定回数に達すると、終了信号Endとして、ハイレベルの信号が供給される。すると、クロック信号CLKがハイレベルに立ち上がったタイミング(時刻tn)において、ラウンド処理部4から出力データDnがレジスタ6に格納される。レジスタ6は、出力データDnを、暗号文として出力する。

【0046】

上述のような動作によれば、中間データを格納する各レジスタ(2−1、2−2)では、中間データと乱数データに格納されることになる。そのため、各レジスタ(2−1、2−2)におけるデータ遷移量は、ランダムな値になる。従って、攻撃者は、消費電力などのサイドチャネル情報を取得できたとしても、乱数データに示される値を知ることが出来なければ、実際のデータ遷移量を推測することはできない。すなわち、本実施形態に係る暗号処理装置1は、ハードウェアにより実現されるものであるにもかかわらず、DPAに対する耐性を高めることができる。

【0047】

また、本実施形態によれば、入力データ又は中間データが、処理対象データとして、ラウンド処理部4に供給される。そのため、ラウンド処理部4は、一般的な暗号アルゴリズムをそのまま使用し、ラウンド処理を実行することが可能である。処理対象データ自体が乱数などによって操作されることはないので、暗号アルゴリズムの複雑化、及び回路規模の増加を抑えることが可能である。

【0048】

なお、本実施形態では、入力データとして平文が用いられ、出力データとして暗号文が出力される場合について説明した。ただし、但し、入力データとして暗号文を用い、出力データとして平文が出力されてもよい。

【0049】

また、本実施形態では、図4に示されるように、乱数生成部8が、クロック信号CLKが立ち上がるタイミングで、乱数データの値を変化させている場合について説明した。但し、乱数データは、固定値であってもよい。

【0050】

また、本実施形態では、レジスタ部2が2個のレジスタを有する場合について説明した。但し、レジスタ部2に含まれるレジスタの数は2個に限定されない。各レジスタが、中間データが格納された後に乱数データが格納されるように構成されていれば、レジスタ部2に含まれるレジスタの個数は3個以上であっても構わない。

【0051】

また、本実施形態では、ラウンド処理部4が出力した中間データが、セレクタ10及びレジスタ入力セレクタ3を介して、再びレジスタ部2に格納される場合について説明した。すなわち、本実施形態では、暗号処理装置1が、同一のラウンド処理部4を用いてラウンド処理が複数回繰り返される、ループ構成を有している場合について説明した。但し、暗号処理装置1として、複数の回路が直列に接続されたパイプライン構成が用いられてもよい。以下に、この点について説明する。

【0052】

図5は、本実施形態の変形例に係る暗号処理装置1を示す概略図である。この変形例に係る暗号処理装置1は、複数の回路部分(第1回路部分11−1、第2回路部分11−2、・・・)を備えている。なお、セレクタ10は省略されている。各回路部分11は、図3に示した本実施形態に係る暗号処理装置1と同様に、レジスタ入力セレクタ3、レジスタ部2、セレクタ5、及びラウンド処理部4を備えており、その動作も図3に示した装置と同様である。初段の回路部分(第1回路部分11−1)に対しては、入力データが、レジスタ入力セレクタ3に供給される。また、上段の回路部分11においてラウンド処理部4により生成された中間データは、後段の回路部分11に含まれるレジスタ入力セレクタ3に供給される。このようなパイプライン構成を採用した場合であっても、レジスタ部2に含まれる各レジスタ(2−1、2−2)には、中間データが格納されたあとに乱数データが格納されることになる。従って、各レジスタ(2−1、2−2)におけるデータ遷移量が攻撃者に推測されることが防止され、DPA耐性を高めることが可能である。

【符号の説明】

【0053】

1 暗号処理装置

2 レジスタ部

3 レジスタ入力セレクタ

4 ラウンド処理部

5 レジスタ出力セレクタ

6 レジスタ

7 ラウンド鍵生成部

8 乱数生成部

9 選択制御部

10 セレクタ

11−1 第1回路

11−2 第2回路

300 F関数部

306 排他論理和(XOR)部

310 第1データ格納部

311 Lレジスタ

312 Rレジスタ

320 第2データ格納部

322 R’レジスタ

332 L’レジスタ

【技術分野】

【0001】

本発明は、暗号処理装置及び暗号処理方法に関する。

【背景技術】

【0002】

セキュリティの必要性が高まっている。これに伴い、大容量のデータを高速に暗号化することのできる暗号処理装置の必要性が、高まっている。大容量データに対応するために、共通鍵暗号機能を用いることが有効である。その共有鍵暗号としては、例えば、TDES(Triple Data Encryption Standard)、及びAES(Advanced Encryption Standard)などが挙げられる。また、高速化を実現するためには、例えば、ハードウェアによって暗号処理装置を実現することが有効である。

【0003】

共通鍵暗号機能を搭載した暗号処理装置においては、サイドチャネル攻撃の一つである電力差分解析(DPA :Differential Power Analysis)の脅威が拡大している(例えば、非特許文献1;Paul Kocher、 Joshua Jaffe、 Benjamin Jun、 “Introduction to Differential Power Analysis and Related Attacks”、 1998.参照)。

【0004】

サイドチャネル攻撃では、暗号化処理時に生じるサイドチャネル情報(例えば、消費電力、電磁波、及び処理時間など)を利用して、暗号の秘密鍵が推定される。暗号処理装置においては、暗号化処理の途中で生成される中間データにより、消費電力が異なることがある。DPAでは、消費電力を計測することにより、中間データを推測し、秘密鍵が推測される。なお、サイドチャネル情報として電磁波などを用いた場合も、同様である(例えば、非特許文献2;K. Gandolfi、 C. Mourtel、 and F. Olivier、 “Electromagnetic Analysis: Concrete Results、” CHES 2001、 LNCS 2162、 pp.251−262、 2001.参照)。

【0005】

DPAの対策に関連する技術として、特許文献1(特開2000−305453)に記載された暗号化装置が挙げられる。この暗号化装置においては、中間データ制御手段が、乱数を入力として、中間データを乱数に依存して変化させる乱数依存中間データ変更操作を中間データ変更要求の発生時点で行う点が記載されている。この暗号化装置では、暗号化処理の中間段階で必要なデータが乱数に依存して変化する。中間データ間の演算を行なっている時点の電力を測定することによって中間データの情報を引き出そうとしても、中間データの値が乱数の影響を受けているために、乱数の影響によって消費電力が変化しているのか、実際の暗号化処理に必要なデータの影響によって消費電力が変化しているのかを判断することが困難となる。そのため、DAPに対する耐性を高めることができる。

【0006】

しかしながら、特許文献1に記載された暗号化装置では、乱数によって変化されたデータに対して暗号化処理が行われるため、処理が複雑化し、回路規模の増大してしまう。また、及び処理能力も低下してしまう。

【0007】

一方、特許文献2(特開2005−31471)には、処理アルゴリズムを複雑化させることなく、暗号解析の困難性を高めることを課題とした、暗号処理装置が開示されている。図1は、特許文献2に記載された暗号処理装置を示す図である。図1に示されるように、この暗号処理装置は、F関数部300、第1データ格納部310、及び第2データ格納部320を有している。この暗号処理装置においては、F関数部300で得られた中間データ出力値は、排他論理和部306を介して、第1データ格納部310に含まれるRレジスタ312およびLレジスタ311にそのまま格納される。また、排他論理和部306の出力データの反転データが、第2データ格納部320に含まれるR’レジスタ322及びL’レジスタ332に格納される。この結果、レジスタ格納処理におけるハミングウェイトの和を一定に保つことができる。ハミングウェイトは、消費電力に影響を与える。ハミングウェイトの和を一定に保つことにより、消費電力からハミングウェイトを推測することが困難になり、消費電力の変化に基づき解析の困難性を高めることができる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2000−305453

【特許文献2】特開2005−31471

【非特許文献】

【0009】

【非特許文献1】Paul Kocher、 Joshua Jaffe、 Benjamin Jun、 “Introduction to Differential Power Analysis and Related Attacks”、 1998.

【非特許文献2】K. Gandolfi、 C. Mourtel、 and F. Olivier、 “Electromagnetic Analysis: Concrete Results、” CHES 2001、 LNCS 2162、 pp.251−262、 2001.

【発明の概要】

【発明が解決しようとする課題】

【0010】

暗号処理装置では、通常、入力データに対して、複数回のラウンド処理が実施され、出力データが得られる。各ラウンド処理で得られる中間データは、レジスタに格納される。レジスタに格納される中間データは、ラウンド処理が実行されるたびに、変化する。消費電力の変化量は、レジスタに格納されたデータが変化したときのハミング重み及びハミング距離に依存する。従って、消費電力の変化を計測することにより、計測結果からハミング重み又はハミング距離が推測され、その推測結果により秘密鍵が特定される可能性がある。なお、暗号処理装置がソフトウェアにより実現される場合には、ハミング重みが消費電力に影響を与え易い。一方、暗号処理装置がハードウェアにより実現される場合には、ハミング距離(データ遷移量)が消費電力に影響を与え易い。

【0011】

既述の特許文献2に記載された暗号処理装置によれば、ハミング重みが消費電力に影響を与える主要因である場合には、DPA耐性を有する。しかし、特許文献2には、データ遷移量に関する記載がない。特許文献2に記載された暗号処理装置においては、データ遷移量の点では、DPA耐性がむしろ悪化していると考えられる。以下に、この点について説明する。

【0012】

図2は、図1に記載の暗号化処理回路における、排他論理和部306の出力データ、ハミング重み、及びデータ遷移量の関係の一例を示す図である。図1には、排他論理和部306の出力データ、Rレジスタ312に格納されるデータ、R’レジスタに格納されるデータ、ハミング重み、及びデータ遷移量の関係が示されている。ハミング重みは、Rレジスタ、R’レジスタ、及びRレジスタとR’レジスタとの和、について、示されている。データ遷移量も、同様に、Rレジスタ、R’レジスタ、及びRレジスタとR’レジスタとの和について、示されている。なお、実際には、各データは32ビットであるが、以下では、32ビット中の特定の4ビットに着目して説明する。

【0013】

図2に示されるように、時刻t=0の排他的論理和部306の出力データ(Rレジスタ312に格納されるデータ)が、「4’b0000」であるものとする。そして、時刻t=0〜時刻t4までの間において、ハミング重みが1ずつ増えるように、出力データが変化するものとする。また、時刻t=5〜時刻t=9までの間においては、データの遷移量が0から1ずつ増えるように、出力データが変化しているものとする。

【0014】

まず、ハミング重みについて説明する。時刻t=0〜時刻t=4において、Rレジスタでは、ハミング重みはが、0から4まで、1ずつ増加する。これに対して、R’レジスタでは、ハミング重みが、4から0まで、1ずつ減少する。その結果、各時刻では、Rレジスタのハミング重みとR’レジスタのハミング重みの和が、常に4になる。また、t=5以降も同様に、各時刻におけるハミング重みの和は4であり、ハミング重みの和が一定であることが確認できる。

【0015】

次いで、データ遷移量について説明する。時刻t=5〜時刻t=9において、Rレジスタでは、前時刻からのデータ遷移量が、0から4まで、1ずつ増加する。R’レジスタでも、同様に、データ遷移量が0から4まで、1ずつ増加する。その結果、Rレジスタのデータ遷移量とR’レジスタのデータ遷移量との和は、0から8まで、2ずつ増加している。従って、データ遷移量の変化が消費電力を変化させる場合には、消費電力からデータ遷移量が推測されてしまう可能性がある。その結果、DPAによる攻撃を許してしまう可能性がある。また、データ遷移量の和は、未対策時と比較して2倍になる。したがって、データ遷移量の観点からは、DPA耐性がむしろ悪化しているともいえる。

【課題を解決するための手段】

【0016】

本発明に係る暗号処理装置は、処理対象データを取得し、前記処理対象データにラウンド処理を施して中間データを生成する、ラウンド処理部と、乱数データを生成する乱数データ生成部と、前記中間データまたは前記乱数データを格納する記憶回路と、前記記憶回路に前記中間データと前記乱数データとのうちのどちらを格納するかを選択する選択制御部とを具備する。前記選択制御部は、前記中間データが格納された後に前記乱数データが格納されるように、前記記憶回路に格納するデータを選択する。

【0017】

本発明に係る暗号処理方法は、処理対象データを取得し、前記処理対象データにラウンド処理を施して中間データを生成するステップと、乱数データを生成するステップと、記憶回路に、前記中間データまたは前記乱数データを格納するステップと、前記記憶回路に前記中間データと前記乱数データとのうちのどちらを格納するかを選択するステップとを具備する。前記選択するステップは、前記中間データが格納された後に前記乱数データが格納されるように、前記記憶回路に格納するデータを選択するステップを含む。

【発明の効果】

【0018】

本発明によれば、DPA攻撃に対する耐性を高めることのできる、暗号処理装置および暗号処理方法が提供される。

【図面の簡単な説明】

【0019】

【図1】特許文献2に記載された暗号処理装置を示す図である。

【図2】出力データ、ハミング重み、及びデータ遷移量の関係の一例を示す図である。

【図3】暗号処理装置を示す構成図である。

【図4】暗号処理装置の動作方法を示すタイミングチャートである。

【図5】変形例に係る暗号処理装置を示す概略図である。

【発明を実施するための形態】

【0020】

以下に、図面を参照しつつ、本発明の実施形態について説明する。

【0021】

図3は、本実施形態に係る暗号処理装置1を示す構成図である。この暗号処理装置1は、入力データ(Input;平文)と、秘密鍵データとに基づいて、入力データに対して暗号処理を施して暗号文を示す出力データを生成するように構成されている。この暗号処理装置1は、ハードウェアにより実現される。

【0022】

図3に示されるように、暗号処理装置1は、セレクタ10、レジスタ部2(記憶回路部)、レジスタ入力セレクタ(3−1、3−2)、レジスタ出力セレクタ5、ラウンド処理部4、レジスタ6、ラウンド鍵生成部7、乱数生成部8、及び選択制御部9を備えている。レジスタ部2は、複数の記憶回路として、複数のレジスタ(2−1、2−2)を備えている。

【0023】

セレクタ10は、入力データ(平文)と、ラウンド処理部4の出力データ(中間データ)とのうちの一方を選択し、出力するように構成されている。セレクタ10は、開始信号Startを取得し、開始信号Startに基づいて、入力データと中間データとのうちのいずれかを選択する。なお、開始信号Startは、図示しない開始信号生成回路により生成される。選択されたデータ(以下、第1データと称す)は、レジスタ入力セレクタ3−1及びレジスタ入力セレクタ3−2に、供給される。

【0024】

乱数生成部8は、乱数データを生成する回路である。生成された乱数データは、レジスタ入力セレクタ3−1及びレジスタ入力セレクタ3−2に供給される。

【0025】

選択制御部9は、レジスタ入力セレクタ3−1、レジスタ入力セレクタ3−2、及びセレクタ5の動作を制御する回路である。選択制御回路9は、選択制御信号を生成し、レジスタ入力セレクタ3−1、レジスタ入力セレクタ3−2、及びセレクタ5に供給する。

【0026】

レジスタ入力セレクタ3−1は、選択制御信号に基づいて、第1データと、乱数データとのうちの一方を選択する。具体的には、レジスタ入力セレクタ3−1は、選択制御信号がハイレベル「1」である場合に第1データを選択し、選択制御信号がローレベル「0」である場合に乱数データを選択するように構成されている。そして、クロック信号CLKがハイレベルに立ち上がったタイミングで、選択したデータをレジスタ2−1に格納する。なお、クロック信号CLKは、図示しないクロック信号生成回路により生成される。

【0027】

同様に、レジスタ入力セレクタ3−2も、選択制御信号に基づいて、第1選択データと乱数データとのうちの一方を選択する。そして、クロック信号CLKがハイレベルに立ち上がったタイミングで、選択したデータをレジスタ2−2に格納する。なお、レジスタ入力セレクタ3−1及びレジスタ入力セレクタ3−2は、一方のセレクタが第1データを選択している場合に、他方のセレクタが乱数データを選択するように、設定されている。すなわち、レジスタ入力セレクタ3−2は、選択制御信号がローレベル「0」である場合に第1データを選択し、選択制御信号がハイレベル「1」である場合に乱数データを選択するように構成されている。

【0028】

各レジスタ2(2−1、2−2)は、第1データ又は乱数データを格納する。また、各レジスタ2は、保持しているデータを、セレクタ5に供給する。

【0029】

セレクタ5は、選択制御信号に基づいて、複数のレジスタ2から供給された複数のデータから、第1データを選択する。そして、クロック信号CLKがハイレベルに立ち上がったタイミングで、選択した第1データを、処理対象データとしてラウンド処理部4に供給する。具体的には、セレクタ5は、選択制御信号がローレベル「0」である場合にレジスタ2−1に格納されたデータを選択し、選択制御信号がハイレベル「1」である場合にレジスタ2−2に格納されたデータを選択するように、構成されている。

【0030】

ラウンド鍵生成部7は、予め準備された秘密鍵データを取得し、秘密鍵データに基づいて、ラウンド鍵データを生成する。ラウンド鍵データは、ラウンド処理部4に供給される。

【0031】

ラウンド処理部4は、セレクタ5から処理対象データを取得すると、ラウンド鍵データを用いて処理対象データにラウンド処理を施す。ラウンド処理の結果、中間データが生成される。中間データは、既述のように、セレクタ10に供給される。なお、ラウンド処理の実行回数が規定回数に達している場合には、ラウンド処理の結果得られたデータは、出力データとして、レジスタ6に格納される。具体的には、ラウンド処理の実行回数が規定回数に達した場合には、図示しない終了信号生成回路が、ハイレベルレベルの信号を終了信号ENDとしてラウンド処理部4に供給する。ラウンド処理部4は、終了信号ENDを取得した場合に、出力データをレジスタ6に格納する。

【0032】

レジスタ6は、本暗号処理装置1の結果として、出力データを出力する。

【0033】

続いて、本実施形態に係る暗号処理装置1の動作方法について説明する。図4は、暗号処理装置1の動作方法を示すタイミングチャートである。図4には、クロック信号[CLK]、秘密鍵データ[Key]、入力データ[D_in]、乱数データ[Random]、ラウンド鍵データ[Ki]、開始信号[Start]、選択制御信号[Sel]、レジスタ2−1に格納されるデータ[Reg_1]、レジスタ2−2に格納されるデータ[Reg_2]、ラウンド処理部4に供給されるデータ(処理対象データ)[F_in]、ラウンド処理部4が出力するデータ[F_out]、終了信号[End]、及び出力データ[Reg_o]が示されている。

【0034】

図4に示されるように、クロック信号CLKがローレベルからハイレベルに立ち上がるタイミングが、時刻t0、時刻t1、時刻t2、・・・時刻tnとして記載されている。

【0035】

まず、時刻t0から時刻t1までの動作について説明する。

【0036】

時刻t0において、暗号処理装置1が動作を開始したとする。すると、開始信号Startとして、ハイレベルの信号が供給される。また、秘密鍵データ[Key]として、秘密鍵データKeyが供給される。また、入力データ[D_in]として、入力データD0が供給される。

【0037】

開始信号Startとしてハイレベルの信号が供給されると、セレクタ10が、第1データとして、入力データD0を選択する。また、選択制御部9は、選択制御信号Selとして、ハイレベルの信号を供給する。これにより、レジスタ入力セレクタ3−1は第1データ(入力データD0)を選択し、レジスタ入力セレクタ3−2は乱数データR0を選択する。すなwち、選択制御部9は、第1データを格納するレジスタ(選択レジスタ)として、レジスタ2−1を選択したことになる。なお、以下の説明において、選択レジスタとして選択されなかったレジスタ2−2は、非選択レジスタと記載される。

【0038】

次いで、時刻t1から時刻t2までの動作について説明する。

【0039】

クロック信号CLKがハイレベルに立ち上がったとき(時刻t1)に、レジスタ入力セレクタ3−1は、選択した第1データ(入力データD0)をレジスタ2−1(選択レジスタ)に格納する。これにより、レジスタ2−1に格納されるデータReg_1は、入力データD0になる。また、レジスタ入力セレクタ3−1は、選択した乱数データR0を、レジスタ2−2(非選択レジスタ)に格納する。これにより、レジスタ2−2に格納されるデータReg_2は、乱数データR0になる。各レジスタ2にデータが格納された後、開始信号Startは、ロウレベルに戻される。

【0040】

また、ラウンド鍵生成部7は、秘密鍵データKeyに基づいて、ラウンド鍵データK1を生成する。

【0041】

その後、選択制御部9は、選択制御信号Selのレベルを反転させ、ロウレベルの信号を供給する。これにより、セレクタ5は、レジスタ2−1に格納されているデータ(第1データ=入力データD0)を選択し、ラウンド処理部4へ処理対象データとして供給する。すなわち、処理対象データ[F_in]は、入力データD0になる。また、選択制御部9は、選択制御信号Selのレベルを反転させたことにより、選択レジスタ(第1データが格納されるレジスタ)を、レジスタ2−1からレジスタ2−2に変更したことになる。すなわち、変更後の選択レジスタは、レジスタ2−2になる。また、レジスタ2−1は、変更後の非選択レジスタになる。

【0042】

ラウンド処理部4は、処理対象データ(入力データD0)を取得すると、処理対象データに対して、ラウンド処理を施し、中間データD1を生成する。すなわち、ラウンド処理部4が出力するデータ[F_out]は、中間データD1になる。

【0043】

中間データD1が生成された段階では、開始信号Startは、ロウレベルに戻されている。そのため、セレクタ10は、第1データとして、中間データD1を選択する。このとき、選択制御信号Selがロウレベルであるため、セレクタ3−1が乱数データR1を選択し、セレクタ3−2が中間データD1を選択する。

【0044】

次いで、時刻t2以降の動作について説明する。クロック信号CLKが立ち上がったタイミング(時刻t2)において、セレクタ3−1が乱数データR1をレジスタ2−1(変更後の非選択レジスタ)に格納する。すなわち、レジスタ2−1に格納されるデータ[Reg_1]は、乱数データR1になる。また、セレクタ3−2は、中間データD1を、レジスタ2−2(変更後の選択レジスタ)に格納する。すなわち、レジスタ2−2に格納されるデータ[Reg_2]は、中間データD1になる。

【0045】

上述のような処理が、選択制御信号Selが反転されながら、規定の回数(n回)繰り返される。そして、ラウンド処理部4がラウンド処理を行った回数が規定回数に達すると、終了信号Endとして、ハイレベルの信号が供給される。すると、クロック信号CLKがハイレベルに立ち上がったタイミング(時刻tn)において、ラウンド処理部4から出力データDnがレジスタ6に格納される。レジスタ6は、出力データDnを、暗号文として出力する。

【0046】

上述のような動作によれば、中間データを格納する各レジスタ(2−1、2−2)では、中間データと乱数データに格納されることになる。そのため、各レジスタ(2−1、2−2)におけるデータ遷移量は、ランダムな値になる。従って、攻撃者は、消費電力などのサイドチャネル情報を取得できたとしても、乱数データに示される値を知ることが出来なければ、実際のデータ遷移量を推測することはできない。すなわち、本実施形態に係る暗号処理装置1は、ハードウェアにより実現されるものであるにもかかわらず、DPAに対する耐性を高めることができる。

【0047】

また、本実施形態によれば、入力データ又は中間データが、処理対象データとして、ラウンド処理部4に供給される。そのため、ラウンド処理部4は、一般的な暗号アルゴリズムをそのまま使用し、ラウンド処理を実行することが可能である。処理対象データ自体が乱数などによって操作されることはないので、暗号アルゴリズムの複雑化、及び回路規模の増加を抑えることが可能である。

【0048】

なお、本実施形態では、入力データとして平文が用いられ、出力データとして暗号文が出力される場合について説明した。ただし、但し、入力データとして暗号文を用い、出力データとして平文が出力されてもよい。

【0049】

また、本実施形態では、図4に示されるように、乱数生成部8が、クロック信号CLKが立ち上がるタイミングで、乱数データの値を変化させている場合について説明した。但し、乱数データは、固定値であってもよい。

【0050】

また、本実施形態では、レジスタ部2が2個のレジスタを有する場合について説明した。但し、レジスタ部2に含まれるレジスタの数は2個に限定されない。各レジスタが、中間データが格納された後に乱数データが格納されるように構成されていれば、レジスタ部2に含まれるレジスタの個数は3個以上であっても構わない。

【0051】

また、本実施形態では、ラウンド処理部4が出力した中間データが、セレクタ10及びレジスタ入力セレクタ3を介して、再びレジスタ部2に格納される場合について説明した。すなわち、本実施形態では、暗号処理装置1が、同一のラウンド処理部4を用いてラウンド処理が複数回繰り返される、ループ構成を有している場合について説明した。但し、暗号処理装置1として、複数の回路が直列に接続されたパイプライン構成が用いられてもよい。以下に、この点について説明する。

【0052】

図5は、本実施形態の変形例に係る暗号処理装置1を示す概略図である。この変形例に係る暗号処理装置1は、複数の回路部分(第1回路部分11−1、第2回路部分11−2、・・・)を備えている。なお、セレクタ10は省略されている。各回路部分11は、図3に示した本実施形態に係る暗号処理装置1と同様に、レジスタ入力セレクタ3、レジスタ部2、セレクタ5、及びラウンド処理部4を備えており、その動作も図3に示した装置と同様である。初段の回路部分(第1回路部分11−1)に対しては、入力データが、レジスタ入力セレクタ3に供給される。また、上段の回路部分11においてラウンド処理部4により生成された中間データは、後段の回路部分11に含まれるレジスタ入力セレクタ3に供給される。このようなパイプライン構成を採用した場合であっても、レジスタ部2に含まれる各レジスタ(2−1、2−2)には、中間データが格納されたあとに乱数データが格納されることになる。従って、各レジスタ(2−1、2−2)におけるデータ遷移量が攻撃者に推測されることが防止され、DPA耐性を高めることが可能である。

【符号の説明】

【0053】

1 暗号処理装置

2 レジスタ部

3 レジスタ入力セレクタ

4 ラウンド処理部

5 レジスタ出力セレクタ

6 レジスタ

7 ラウンド鍵生成部

8 乱数生成部

9 選択制御部

10 セレクタ

11−1 第1回路

11−2 第2回路

300 F関数部

306 排他論理和(XOR)部

310 第1データ格納部

311 Lレジスタ

312 Rレジスタ

320 第2データ格納部

322 R’レジスタ

332 L’レジスタ

【特許請求の範囲】

【請求項1】

処理対象データを取得し、前記処理対象データにラウンド処理を施して中間データを生成する、ラウンド処理部と、

乱数データを生成する乱数データ生成部と、

前記中間データまたは前記乱数データを格納する記憶回路と、

前記記憶回路に前記中間データと前記乱数データとのうちのどちらを格納するかを選択する選択制御部と、

を具備し、

前記選択制御部は、前記中間データが格納された後に前記乱数データが格納されるように、前記記憶回路に格納するデータを選択する

暗号処理装置。

【請求項2】

請求項1に記載された暗号処理装置であって、

前記記憶回路は複数設けられており、

前記選択制御部は、

前記複数の記憶回路のなかから、選択記憶回路を選択し、前記選択記憶回路に前記中間データを格納し、

前記選択記憶回路から前記中間データが後段へ送られた後に、前記選択記憶回路を変更し、

変更後の前記選択記憶回路として選ばれなかった変更後非選択記憶回路群に、前記乱数データを格納する

暗号処理装置。

【請求項3】

請求項2に記載された暗号処理装置であって、

前記選択記憶回路に格納された前記中間データは、前記処理対象データとして、前記ラウンド処理部に送られる

暗号処理装置。

【請求項4】

請求項2又は3に記載された暗号処理装置であって、

更に、

前記複数の記憶回路に対応して設けられた複数の記憶回路入力セレクタと、

前記複数の記憶回路と前記ラウンド処理部との間に設けられた、記憶回路出力セレクタと、

を具備し、

前記複数の記憶回路入力セレクタの各々は、前記中間データと前記乱数データとのうちのいずれか一方を選択して、対応する前記各記憶回路に向けて出力し、

前記記憶回路出力記憶回路は、前記複数の記憶回路のいずれかに格納されたデータを選択して、前記処理対象データとして前記ラウンド処理部に向けて出力し、

前記選択制御部は、

前記複数の記憶回路入力セレクタの動作を制御することにより、前記選択記憶回路に前記中間データを格納し、

前記記憶回路出力セレクタの動作を制御することにより、前記選択記憶回路から前記ラウンド処理部に前記処理対象データを送る

暗号処理装置。

【請求項5】

請求項1乃至4のいずれかに記載された暗号処理装置であって、

更に、

予め準備された秘密鍵データを取得し、前記非密鍵データに基づいて、ラウンド鍵データを生成する、ラウンド鍵生成部

を具備し、

前記ラウンド処理部は、前記ラウンド鍵データを用いて、前記処理対象データにラウンド処理を施す

暗号処理装置。

【請求項6】

請求項1乃至5のいずれかに記載された暗号処理装置であって、

前記記憶回路は、レジスタである

暗号処理装置。

【請求項7】

処理対象データを取得し、前記処理対象データにラウンド処理を施して中間データを生成するステップと、

乱数データを生成するステップと、

記憶回路に、前記中間データまたは前記乱数データを格納するステップと、

前記記憶回路に前記中間データと前記乱数データとのうちのどちらを格納するかを選択するステップと、

を具備し、

前記選択するステップは、前記中間データが格納された後に前記乱数データが格納されるように、前記記憶回路に格納するデータを選択するステップを含む

暗号処理方法。

【請求項1】

処理対象データを取得し、前記処理対象データにラウンド処理を施して中間データを生成する、ラウンド処理部と、

乱数データを生成する乱数データ生成部と、

前記中間データまたは前記乱数データを格納する記憶回路と、

前記記憶回路に前記中間データと前記乱数データとのうちのどちらを格納するかを選択する選択制御部と、

を具備し、

前記選択制御部は、前記中間データが格納された後に前記乱数データが格納されるように、前記記憶回路に格納するデータを選択する

暗号処理装置。

【請求項2】

請求項1に記載された暗号処理装置であって、

前記記憶回路は複数設けられており、

前記選択制御部は、

前記複数の記憶回路のなかから、選択記憶回路を選択し、前記選択記憶回路に前記中間データを格納し、

前記選択記憶回路から前記中間データが後段へ送られた後に、前記選択記憶回路を変更し、

変更後の前記選択記憶回路として選ばれなかった変更後非選択記憶回路群に、前記乱数データを格納する

暗号処理装置。

【請求項3】

請求項2に記載された暗号処理装置であって、

前記選択記憶回路に格納された前記中間データは、前記処理対象データとして、前記ラウンド処理部に送られる

暗号処理装置。

【請求項4】

請求項2又は3に記載された暗号処理装置であって、

更に、

前記複数の記憶回路に対応して設けられた複数の記憶回路入力セレクタと、

前記複数の記憶回路と前記ラウンド処理部との間に設けられた、記憶回路出力セレクタと、

を具備し、

前記複数の記憶回路入力セレクタの各々は、前記中間データと前記乱数データとのうちのいずれか一方を選択して、対応する前記各記憶回路に向けて出力し、

前記記憶回路出力記憶回路は、前記複数の記憶回路のいずれかに格納されたデータを選択して、前記処理対象データとして前記ラウンド処理部に向けて出力し、

前記選択制御部は、

前記複数の記憶回路入力セレクタの動作を制御することにより、前記選択記憶回路に前記中間データを格納し、

前記記憶回路出力セレクタの動作を制御することにより、前記選択記憶回路から前記ラウンド処理部に前記処理対象データを送る

暗号処理装置。

【請求項5】

請求項1乃至4のいずれかに記載された暗号処理装置であって、

更に、

予め準備された秘密鍵データを取得し、前記非密鍵データに基づいて、ラウンド鍵データを生成する、ラウンド鍵生成部

を具備し、

前記ラウンド処理部は、前記ラウンド鍵データを用いて、前記処理対象データにラウンド処理を施す

暗号処理装置。

【請求項6】

請求項1乃至5のいずれかに記載された暗号処理装置であって、

前記記憶回路は、レジスタである

暗号処理装置。

【請求項7】

処理対象データを取得し、前記処理対象データにラウンド処理を施して中間データを生成するステップと、

乱数データを生成するステップと、

記憶回路に、前記中間データまたは前記乱数データを格納するステップと、

前記記憶回路に前記中間データと前記乱数データとのうちのどちらを格納するかを選択するステップと、

を具備し、

前記選択するステップは、前記中間データが格納された後に前記乱数データが格納されるように、前記記憶回路に格納するデータを選択するステップを含む

暗号処理方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2011−169977(P2011−169977A)

【公開日】平成23年9月1日(2011.9.1)

【国際特許分類】

【出願番号】特願2010−31528(P2010−31528)

【出願日】平成22年2月16日(2010.2.16)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成23年9月1日(2011.9.1)

【国際特許分類】

【出願日】平成22年2月16日(2010.2.16)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]