暗号処理装置

【課題】1Round演算を1クロックサイクルで実行し、なおかつ、回路規模の増大を抑え、DPA耐性の向上を図ることが可能な暗号処理装置を提供する。

【解決手段】第1レジスタ105と、第2レジスタ106と、非線形変換部としてSboxを有し、第2レジスタの格納値に対してラウンド演算を行うラウンド演算部109と、初期置換された第1データと所定の攪乱値とのEXORを行う第1演算部102と、初期置換された第2データと所定の攪乱値とのEXORを行う第2演算部103と、第1レジスタの格納値に対して逆置換を行う逆置換部107と、逆置換した値と所定の攪乱値とのEXORを行い、演算結果をラウンド演算部に供給する第3演算部109と、を有し、ラウンド演算部109は、Sboxにて、第2レジスタに格納された格納値の攪乱状態を解除した値を入力として、非線形変換処理を行い、Sboxの処理結果と第3演算部の演算結果とのEXORした結果を第2レジスタに出力する。

【解決手段】第1レジスタ105と、第2レジスタ106と、非線形変換部としてSboxを有し、第2レジスタの格納値に対してラウンド演算を行うラウンド演算部109と、初期置換された第1データと所定の攪乱値とのEXORを行う第1演算部102と、初期置換された第2データと所定の攪乱値とのEXORを行う第2演算部103と、第1レジスタの格納値に対して逆置換を行う逆置換部107と、逆置換した値と所定の攪乱値とのEXORを行い、演算結果をラウンド演算部に供給する第3演算部109と、を有し、ラウンド演算部109は、Sboxにて、第2レジスタに格納された格納値の攪乱状態を解除した値を入力として、非線形変換処理を行い、Sboxの処理結果と第3演算部の演算結果とのEXORした結果を第2レジスタに出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、たとえばICカードに適用される暗号処理装置に関し、さらに詳細には、低消費電流で、暗号解析処理、攻撃処理として知られる電力解析に対する耐性を向上させた暗号処理装置に関するものである。

【背景技術】

【0002】

ICカードでは、ホストコンピュータとデータのやり取りを行うとき、その過程でICカードに格納されている秘密情報が漏れても問題を発生させないために、やり取りするデータには暗号化したデータを用いる。

【0003】

この暗号化の方法として、現在最も多く用いられているのはDES(Data Encryption Standard)である。

DESでは、データの暗号化にはICカードの所有者とホストコンピュータが同じ鍵を所有し、データの送信側はデータをその鍵で暗号化して送信し、データの受信者は同じ鍵で復号化してメッセージを取り出す。

通信の過程で悪意の第三者が盗聴しても、鍵を有していない限りは復号化してメッセージを取り出すことは困難である。

【0004】

また、暗号化・復号化の時に使う鍵は、ICカード内のEEPROM等の不揮発性メモリに格納される。

そして、暗号化・復号化時にはCPUを介さないで直接ICカード内の暗号エンジンに転送されるような制御により、ICカードの所有者やICカードの開発エンジニアすら鍵データを取り出すことが不可能な構成を採ってセキュリティを保持している。

【0005】

しかし、ICカードの消費電流を測定し、それに統計処理を施して鍵を取り出すという攻撃方法(DPA:Differential Power Analysis)が P.Kocher らにより報告された。 このDPA攻撃は、下記<1>、<2>、<3>の示す手順で行われる。

<1> 異なる1000個程度の平文(M1〜M1000)を用いて暗号化演算を行い、消費電流波形(S1〜S1000)を取得する。

<2> サブSボックス(Sub Sbox:S0〜S7)の1つを選択し(たとえばS0)、その6ビット(bit)の鍵を推定して平文(M1〜M1000)でDESのシミュレーション(simulation)を行う。そして、たとえばS0出力のLSBのシミュレーション結果が“0”か“1”かに応じて対応する消費電流波形を2つのグループ(GP[0],GP[1])に分類する。

<3> 2つのグループの平均波形を計算し、その差分を採る。

このとき、ピーク波形が発生した場合、推定した6ビット鍵は正しいと判断し、上記<2>の処理に戻って、別のSub Sboxで同じ処理を行う。

ピーク波形がない場合、推定した6ビット鍵は間違いと判断し、別の鍵を推定して<2>の処理に戻る。

【0006】

全てのSub Sboxに対してピーク波形が観察されると、これにより6bit×8=48bitの鍵が求まり、残り8ビットは、28=256回の全数攻撃で求まる。

この攻撃の脅威は、必要な装置がパーソナルコンピュータ(パソコン)とデジタルオシロスコープだけである事である。あとは暗号LSIから電流を取得するための改造を施せば攻撃の環境が整い、この攻撃への対策が施されていないものに対しては、数時間で鍵が取得できる点が脅威である。

【0007】

上記例は、Sub Sboxがメモリで構成されている場合で、メモリ出力が攻撃対象となる。

暗号回路をロジック回路で構成する場合、Sub Sboxもロジック回路で構成されるため、メモリの場合と比較してSub Sboxの出力電流は小さくなり、攻撃の難易度は上がる。

このため、回路上で負荷容量が大きく、充放電電流の大きい回路、たとえば右レジスタ(R Register)の値更新時の充放電電流が攻撃の対象となる。これを具体的な例(DES演算回路)で示す。

【0008】

図1は、暗号回路の例としてDES演算回路の一般的な構成を示す図である。

図2は、図2のDES演算回路のタイミングチャートである。

【0009】

このDES演算回路10は、図1に示すように、初期置換部[IP(Initial Permutation)]11、スイッチ12L,12R、左レジスタ(Lレジスタという)13、および右レジスタ(Rレジスタ)14を有する。さらに、DES演算回路10は、F関数部15、EXOR演算部16、逆置換部(IP-1)17、および暗号文出力部(Crypto)18を有する。

【0010】

F関数部15は、図1に示すように、非線形処理を実行する複数(図1では8)のSボックス(Sbox)S0〜S7を有する。前段からの入力値F−in、すなわち、R(n−1)は拡張部(EX)15−1によって48ビットに拡大され、さらに鍵スケジュール部から入力する鍵(48ビット)KnとEXOR演算部15−2でEXOR演算が実行される。EXOR演算部15−2の出力が6ビットずつ非線形変換処理を実行する複数のSboxS0〜S7に入力される。各SboxS0〜S7では、変換テーブルを適用した6ビットから4ビットへの非線形変換処理が実行される。

SboxS0〜S7からの出力ビット4×8=32ビットは、置換部(P)15−3に入力されて、ビット位置の入れ替え処理がなされ、F関数出力32ビットを生成して出力する。

【0011】

このDES演算回路10は、1ラウンド(Round)分の回路が配置され、これを16回動作させることにより暗号演算を実行する。

平文は、IP置換後に32ビットずつに分けられて、L/Rレジスタ12L,12Rに格納される。これにより、Rレジスタ12Rの値はF関数に入力され、データ拡張,Round鍵とのEOR演算後にSboxに入力される。

Sboxの出力は、P置換による並べ替えの後、Lレジスタ12Lの値とEOR演算されて、Rレジスタ12Rの入力に供給される。

そして、クロックの立上りで、Rレジスタ12Rの値が更新される。この動作を16回繰り返す。そして、最初のサイクルで、Rレジスタ12Rの出力は、R0からF(R0,K1)+L0に変化するが、このときのRレジスタ12R出力での変化電流は、{F(R0,K1)+L0+R0}の関数となる。“K1”以外は既知の数であるため、Rレジスタ12Rの出力変化に対してDPA攻撃が可能となる。ここで、+は排他的論理和演算(EOR)を示す。

【0012】

DPA攻撃において、従来は、Sub Sboxの4ビット出力のうちの1ビットに着目して消費電流波形をグループ分けして、両グループの平均波形の差分で、推定した6ビット鍵の妥当性を判断していた。

しかし、プロセスの微細化に伴って、暗号ブロックの回路規模は小さくなり、これによって攻撃対象となる信号配線の幅や長さも小さくなり、その結果、配線容量は小さくなる。

同時に、ゲート酸化膜圧の薄膜化に伴って、電源電圧は低電圧化し、個々のレジスタビットおよびその負荷配線の充放電に伴う電流も小さくなる。そして、これらの相乗効果により、着目ビットの変化に伴う信号成分は小さくなるため、推定鍵の妥当性の判断の基準となるピーク電流の大きさも小さくなり、SN比は悪くなる。

【0013】

SN比を改善する手段として、以下の(1)および(2)に示す手段が採られる。

(1)攻撃に用いる信号波形の数を増やし、グループ平均演算後のノイズ成分を減らす。

(2)攻撃対象を、Sub Sbox出力に対応する4ビットが“全て変化する”/“全て変化しない”場合のみをグループ分けの対象とする。この場合、差分は4ビットであるため、信号成分が増える。

従来のSub Sboxの出力1ビットに着目しての攻撃を“1ビットアタック(1bit Attack) ”と称するのに対して、(2)の攻撃は、“4ビットアタック(4bit Attack) ”と称される。

【0014】

このDPA攻撃に対する対策として、次の方法が提案されている。

第1は、暗号回路を相補構成とし、相補動作によりリーク電流を削減する方法である。

第2は、乱数等を用いてデータおよびそれに起因するリーク電流を攪乱し、統計処理を困難にする方法である。

【0015】

第1の方法としては、たとえば特許文献1に開示された技術が知られている。

この技術では、1ビットのデータをハミング重み(Hamming Weight)の等しい2ビットの数値に展開し(たとえば“0”を“01”、“1”を“10”)、演算によるデータの遷移は、稼動相と休止相の2相を設ける。

そして、休止相で一旦、“0”でも“1”でもない状態(たとえば“00”)に遷移してから演算後のデータに遷移する制御を行う。これにより、各ビットについて、データに関係なく必ず1ビットの変化が起こり、演算値のデータ変化に伴う変化電流の検出を困難にしている。

【0016】

第2の方法としては、たとえば特許文献2に開示された技術が知られている。

この技術では、Sboxの出力を乱数で攪乱することによって、鍵に起因する回路動作に伴う微小電流を攪乱し、消費電流の統計処理を困難にしている。

【先行技術文献】

【特許文献】

【0017】

【特許文献1】特開2004−347975号公報

【特許文献2】USP6,295,606

【発明の概要】

【発明が解決しようとする課題】

【0018】

しかし、上記第1の方法では、本来の演算動作と反対の動作をする回路を並列に配置する必要があり、回路規模および動作電流が2倍かそれ以上になる。

また、1Roundの演算を、2つの相に分ける必要があるため、演算サイクル数は2倍になる。また、相補信号出力の配線容量に差があれば、そのビットが“0”の時と“1”の時で充放電電流に差異が発生し、それが攻撃対象となる。

【0019】

また、第2の方法を実現するためには、攪乱するデータ幅分の乱数を暗号演算に先立って生成しておく必要があり、乱数生成回路を搭載しておく必要がある。

そして、Round毎に乱数値を変える場合、Round演算毎に乱数値を生成、または必要数を事前に生成して格納しておく必要がある。

前者は、動作電流の増加、後者は乱数値生成のためのサイクルおよびそれを格納するための領域が必要になる。

また、第2次(2nd)以降の高次のDPA攻撃によって鍵が取り出される危険性があるため、高次のDPA攻撃に対する防御も考慮した対策をとる必要がある。

【0020】

本発明は、1ラウンド(Round)演算を1クロックサイクルで実行し、なおかつ、回路規模の増大を抑え、DPA耐性の向上を図ることが可能な暗号処理装置を提供することにある。

【課題を解決するための手段】

【0021】

本発明の観点の暗号処理装置は、所定の攪乱データで攪乱処理された演算用データを格納する少なくとも一つのレジスタと、上記レジスタの格納値に対してラウンド演算を行うラウンド演算部と、少なくとも上記ラウンド演算部の出力値を上記レジスタに選択的に入力させるスイッチと、上記ラウンド演算部は、上記記レジスタに格納された格納値を入力し、入力した当該格納値の攪乱状態を解除した値を基に関数処理を行い、上記関数処理結果と所定の攪乱データとの排他的論理和演算した結果を上記スイッチを介して上記レジスタに出力し、上記攪乱データのシードは、上記ラウンド演算部の異なるデコード値である。

好適には、本発明の暗号処理装置は、攪乱処理された演算用データを格納する第1レジスタと、攪乱処理された演算用データを格納する第2レジスタと、非線形変換部としてSboxを有し、上記第2レジスタの格納値に対してラウンド演算を行うラウンド演算部と、初期置換された第1データと所定の攪乱値との排他的論理和演算を行う第1演算部と、初期置換された第2データと所定の攪乱値との排他的論理和演算を行う第2演算部と、上記第1演算部の演算結果または上記第2レジスタの格納値を上記第1レジスタに選択的に入力させる第1スイッチと、上記第2演算部の演算結果または上記ラウンド演算部の出力値を上記第2レジスタに選択的に入力させる第2スイッチと、上記第1レジスタの格納値に対して逆置換を行う逆置換部と、逆置換した値と所定の攪乱値との排他的論理和演算を行い、演算結果を上記ラウンド演算部に供給する第3演算部と、を有し、上記ラウンド演算部は、上記Sboxにて、上記第2レジスタに格納された格納値の攪乱状態を解除した値を入力として、非線形変換処理を行い、上記Sboxの処理結果と上記第3演算部の演算結果との排他的論理和演算した結果を上記第2スイッチを介して上記第2レジスタに出力する。

【発明の効果】

【0022】

本発明によれば、1Round演算を1クロックサイクルで実行し、なおかつ、回路規模の増大を抑え、DPA耐性の向上を図ることができる。

【図面の簡単な説明】

【0023】

【図1】暗号回路の例としてDES演算回路の一般的な構成を示す図である。

【図2】図2のDES演算回路のタイミングチャートである。

【図3】本発明の第1の実施形態に係る暗号処理装置としてのDES演算回路の構成例を示す図である。

【図4】本実施形態に係る攪乱データおよび攪乱データをF関数のP置換に基づいて並べ替えた値を示す図である。

【図5】第1の実施形態に係るDES演算回路の動作を説明するためのタイミングチャートである。

【図6】本実施形態に係る攪乱値生成回路の構成例を示す図である。

【図7】攪乱値シード(Seed)生成部の構成例を示す図である。

【図8】攪乱値生成タイミングを示す図である。

【図9】本実施形態に係るSboxの構成例を示す図である。

【図10】攪乱例をハミング距離( Hamming Distance )と関連付けて示す図である。

【図11】一般的なAES演算回路の構成例を示す図である。

【図12】本第2の実施形態に係るAES演算回路の構成例を示す図である。

【図13】本発明の構成が適用可能な暗号処理実行デバイスとしてのICモジュールの構成例を示す図である。

【発明を実施するための形態】

【0024】

以下、本発明の実施形態を図面に関連付けて詳細について説明する。

なお、説明は以下の順序で行う。

1.第1の実施形態(DES演算回路の構成例)

2.第2の実施形態(AES演算回路の構成例)

【0025】

本実施形態の暗号処理装置は、以下の特徴を持って構成される。

データの撹乱(データと攪乱値のEXOR)により、DPA耐性を向上させる。

撹乱値は、暗号演算回路の中間値2ビットをデコードして用い、撹乱ビット数は各Sub Sboxで1ビットである。

撹乱データは、ラウンド毎にローテイトすることにより、撹乱データを変化させる。

レジスタ等での中間値の更新時に、格納データと更新データは、Sub Sbox単位で異なる1ビット(bit)が反転し、その結果、更新時の変化データは、本来の変化に対してSub Sbox単位で必ず2ビットが反対の変化をする。

Sboxの出力部にラッチ(Latch)またはレジスタ(Register)を配置し、Sbox の出力確定後に出力する制御を行う。

【0026】

<1.第1の実施形態>

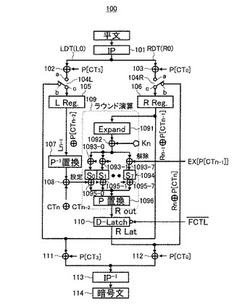

図3は、本発明の第1の実施形態に係る暗号処理装置としてのDES演算回路の構成例を示す図である。

【0027】

本DES演算回路100は、初期置換部[IP(Initial Permutation)部]101、第1EXOR演算部102、第2EXOR演算部103、スイッチ104L,104R、L(左)レジスタ105、およびR(右)レジスタ106を有する。

DES演算回路100は、逆置換部(P-1)107、第3EXOR演算部108、ラウンド演算部としてのF関数部109、およびラッチ(レジスタ)110を有する。

DES演算回路100は、第4EXOR演算部111、第5EXOR演算部112、逆置換部(IP-1)113、および暗号文出力部114を有する。

スイッチ104Lは第1スイッチに相当し、スイッチ104Rは第2スイッチに相当し、Lレジスタ105は第1レジスタに相当し、Rレジスタ106は第2レジスタに相当する。また、F関数部109がラウンド演算部に含まれる。

なお、EXOR演算は排他的論理和演算を意味する。以下の説明で符号+はEXOR演算(排他的論理和演算)を示す。

【0028】

本実施形態のDES演算回路が、通常の回路構成と異なる点は、以下の点である。

IP置換後のデータのうち、L側の第1データは攪乱値P[CT3 ]と、R側の第2データは攪乱値P[CT0 ]とEXOR演算される。

IP-1 置換前のデータのうち、L側は攪乱値P[CT3 ]と、R側は攪乱値P[CT0 ]とEXOR演算される。

F関数部109の入力データは、Sbox入力の直前で攪乱数EX[P[CTn-1]]とEXORされて攪乱を解除され、Sboxの出力でP-1[Ln-1] + CTn とEXOR演算されて、新しい攪乱を設定される。

Round演算出力とRレジスタ106の信号パスの間に、ラッチ(D−Latch回路)110が配置され、Round関数の出力を制御する。

【0029】

図4(A)および(B)は、本実施形態に係る攪乱データおよび攪乱データをF関数のP置換に基づいて並べ替えた値を示す図である。

本実施形態において、CTnは、データを撹乱する32ビットの撹乱データ(攪乱値)を示す。攪乱データCTnは、図4(A)に示すように、2ビット値をデコードした4ビットの攪乱値“ctm[n]”(m=0〜7)を8個並べた構成を採る。

添え字の“n”は、たとえばラウンドを示す。各4ビットは、添え字の“m”に対応するSub Sbox の4ビット値の攪乱に使われる。

P[CTn]は、図4(B)に示すように、CTnを、F関数のP置換に基づいて並べ替えた値を示す。

また、図3において、EX[P[CTn-1]]は、攪乱数“CTn-1”をP置換による並替後に拡張関数に従って拡張した値を示す。

このような特徴を有する図3のDES演算回路100の構成および機能ついて具体的に説明する。

【0030】

IP置換部101は、メッセージを形成する平文に対してIP置換処理を施し、処理後の第1データとしての左データLDTを第1EXOR演算部102に出力し、第2データとしての右データRDTを第2EXOR演算部103に出力する。

なお、IP置換部101による左データLDTおよび右データRDTは32ビットである。

【0031】

第1EXOR演算部102は、IP置換部101による第1データとしての左データLDTとそれに対応する攪乱値P[CT3 ]とのEXOR演算を行う。

第1EXOR演算部102は、EXOR演算結果を、スイッチ104Lを介してLレジスタ105に供給する。

【0032】

第2EXOR演算部103は、IP置換部101による右データRDTとそれに対応する攪乱値P[CT0 ]とのEXOR演算を行う。

第2EXOR演算部103は、EXOR演算結果を、スイッチ104Rを介してRレジスタ106に供給する。

【0033】

第1スイッチとしてのスイッチ104Lの接点aは第1EXOR演算部102の出力に接続され、接点bはRレジスタ106の出力、第4EXOR演算部111に接続され、接点cがLレジスタ105の入力に接続されている。

第2スイッチとしてのスイッチ104Rの接点aは第2EXOR演算部103の出力に接続され、接点bはラッチ110の出力、第5EXOR演算部112に接続され、接点cがRレジスタ106の入力に接続されている。

【0034】

Lレジスタ105は、たとえばクロックの立上りのタイミングでスイッチ104Lを介して入力した、たとえば32ビットのデータをラッチ(格納)する。

Lレジスタ105には、本来の値Ln-1に攪乱値P[CTn-2 ]がEXOR演算された値が格納される。

Rレジスタ106は、たとえばクロックの立上りのタイミングでスイッチ104Rを介して入力した、たとえば32ビットのデータをラッチ(格納)する。

Rレジスタ106には、本来の値Rn-1に攪乱値P[CTn-1 ]がEXOR演算された値が格納される。

【0035】

逆置換部107は、Lレジスタ105に格納されたLn-1に攪乱値P[CTn−2 ]がEXOR演算された値を並べ替えて第3EXOR演算部108に出力する。

【0036】

第3EXOR演算部108は、逆置換部107の出力値と後で詳述する攪乱値生成回路で生成される値CTn + CTn-2とをEXOR演算してF関数部109に出力する。

【0037】

F関数部109は、非線形処理を実行する複数(図1では8)のSボックス(Sbox)S0〜S7を有する。F関数部110は、拡張部1091、第6EXOR演算部1092、第7EXOR演算部1093−0〜1093−7、Sbox1094、第8EXOR演算部1095−0〜1095−7、およびP置換部1096を有する。

【0038】

拡張部1091は、Rレジスタ106の格納値“Rn-1 + P[CTn-1]”を、拡張関数“EX”によって32ビットから48ビットに拡張する。

第6EXOR演算部1092は、拡張後の値とRound鍵“Kn”とEXOR演算して“EX[Rn-1+P[CTn-1]] + Kn”を得る。

第7EXOR演算部1093−0〜1093−7は、Sboxに入る直前で攪乱値“EX[P[CTn-1]]”とEXOR演算して、攪乱成分が取り除かれて通常と同じ値“EX[Rn-1] + Kn”としてSbox1094に入力する。

各SboxS0〜S7では、変換テーブルを適用した6ビットから4ビットへの非線形変換処理が実行され、32ビットのデータを出力する。

第8EXOR演算部1095−0〜1095−7は、Sbox1094の出力と第3EXOR演算部108によるEXOR値“P-1[Ln-1]+CTn”とEXOR演算する。

置換部(P)1096は、ビット位置の入れ替え処理を行い、F関数出力32ビットを生成してラッチ110に出力する。

【0039】

ラッチ110は、制御信号“/FCTL”がローレベル(Low Level)のとき、入力値をそのまま出力し、ハイレベル(High Level)のときは、ハイ(High) に変化するときの値を保持する。

ラッチ110の出力は、スイッチ104Rを介してRレジスタ106に入力される。制御信号“/FCTL”がロー(Low)に変化するタイミングを、Sboxの出力確定からマージンを見込んだタイミングに設定する。

これにより、Round関数出力からRレジスタ106への信号線に、DPA攻撃の対象となりうるSboxの中間値が現れないように制御される。

【0040】

第4EXOR演算部111は、ラウンド演算終了後のデータ(Rレジスタ106のデータ)と攪乱データP[CT3 ]とのEXOR演算を行って、攪乱状態を解除したデータを逆置換部113に出力する。

【0041】

第5EXOR演算部112は、ラウンド演算終了後のデータ(F関数部109の出力データ、ラッチ110の出力データ)と攪乱データP[CT0 ]とのEXOR演算を行って、攪乱状態を解除したデータを逆置換部113に出力する。

【0042】

逆置換部113では、攪乱状態が解除されたデータの逆置換変換(IP-1)を実行し、暗号文出力部114を介して暗号文として出力する。

【0043】

次に、第1の実施形態に係るDES演算回路の要部の具体的な構成および暗号化演算動作について、図5から図10に関連付けて説明する。

図5は、第1の実施形態に係るDES演算回路の動作を説明するためのタイミングチャートである。

通常の16ラウンドの演算の前に、攪乱値のシード(Seed)を生成するサイクルが実行される。このサイクルに関しては後述するため、ここでは省略する。

【0044】

DESの演算サイクル開始直前で、入力データである平文は、IP部101においてIP置換後、左データLDTと右データRDTに分けられる。

第1EXOR演算部102では、IP置換部101による左データLDT(L0)とそれに対応する攪乱値P[CT3 ]とのEXOR演算が行われる。

第2EXOR演算部103では、IP置換部101による右データRDT(R0)とそれに対応する攪乱値P[CT0 ]とのEXOR演算が行われる。

そして、R側は“R0”と攪乱値“P[CT0]”のEXOR演算値が、L側は“L0”と攪乱値“P[CT3]”とのEOR演算値が各々Rレジスタ106、Lレジスタ105の入力に供給され、クロックの立上りでレジスタに取り込まれる。

【0045】

Round nでは、Rレジスタ106には、本来の値“Rn-1”に対して攪乱値“P[CTn-1]”がEXOR演算された値が、Lレジスタ105には、本来の値“Ln-1”に対して攪乱値“P[CTn-2]”がEXOR演算された値が格納される。

Rレジスタ106の格納値“Rn-1 + P[CTn-1]”はスイッチ104Rを介してF関数部109に入力される。

F関数部109において、拡張部1091で拡張関数“EX”によって32ビットから48ビットに拡張後、Round鍵“Kn”とEXORされて“EX[Rn-1 + P[CTn-1]] + Kn”となる。

そして、Sbox1094に入る直前で、第7EXOR演算部1093−0〜1093−7において、攪乱値“EX[P[CTn-1]]”とEXOR演算されて攪乱成分が取り除かれて通常と同じ値“EX[Rn-1] + Kn”となってSboxに入力される。

Sbox1094の出力は、第8EXOR演算部1095−0〜1095−7に入力される。第8EXOR演算部1095−0〜1095−7にてLレジスタ105の格納値“Ln-1 + P[CTn-2]”をP-1 置換に基づいて並べ替えた値と攪乱値生成回路からの値“CTn + CTn-2”のEXOR値“P-1[Ln-1] + CTn”とEXOR演算される。

【0046】

第8EXOR演算部1095−0〜1095−7の出力は、P置換部1096におけるP置換処理を経てラッチ110に入力される。

ラッチ110では、制御信号“/FCTL”がローレベルのとき、入力値がそのまま出力され、ハイレベルのときは、ハイに変化するときの値が保持される。

ラッチ110の出力は、スイッチ104Rを介してRレジスタ106に入力される。前述したように、制御信号“/FCTL”がローに変化するタイミングが、Sboxの出力確定からマージンを見込んだタイミングに設定されている。これにより、Round関数出力からRレジスタ106への信号線に、DPA攻撃の対象となりうるSboxの中間値が現れないように制御される。

【0047】

図4に示す4ビットの各撹乱データおよびそのSeedを生成する回路および動作タイミングを各々図6、図7、および図8に示す。

図6は、本実施形態に係る攪乱値生成回路の構成例を示す図である。

図7は、攪乱値シード(Seed)生成部の構成例を示す図である。

図8は、攪乱値生成タイミングを示す図である。

【0048】

攪乱値“CTn”の各要素“ctm[n]”は、本来のDES演算に先立って追加される1サイクルで攪乱値のSeedから生成され、その後は、クロック動作により更新される。詳細を以下に記す。

【0049】

[回路構成]

図6の攪乱値生成回路200は、ロード(Load)機能付の2ビットカウンタ(2bit counter)201とデコード(Decode)回路202−0〜202−nが8個配置される。

2ビットカウンタ201のデータ入力D1,D0の入力段には2入力ORゲートORG1、ORG2が配置されている。また、デコード回路202−0の入力段にはインバータINV1、INV2が配置されている。

また、デコード回路202−0は、3入力NORゲートNRG1〜NRG4を有する。また、デコード回路202−n(n≠0)は、2入力NORゲートNRG11〜NRG14を有する。

各2ビットカウンタ201のデータ入力は、Sbox出力32ビットから適宜、換言すれば異なるSub Sboxから1ビットずつ選択された2ビットの供給ラインに接続されている。

2ビットカウンタ201は、Load 機能により、制御信号“/LD”がローレベルの期間、クロックCLKの立上りに同期して入力データをカウンタ内部に取り込む。

そして、このLoad 機能のためSboxの出力負荷の増加を抑えるため、図7に示すように、Sbox出力信号線の近くに配置されたORゲートORG21〜ORG26により2ビットカウンタ201までの負荷が切り離される構成を採っている。

2ビットカウンタ201に取り込まれた各2ビット値からは、デコード回路202で4ビットデコード(4bit decode)値“ctm[n]”が生成される。

Seed取込時は、ラウンド値“n”は0である。DES演算が開始されると、“n”および2ビットカウンタ値はインクリメントされる。

それに伴って攪乱値“ctm[n]”の“1”の位置は上位側にローテイトしていくが、“1000”(カウンタ値:11)になった後は“0001” (カウンタ値:00)に戻って再びローテイトを繰り返す。すなわち、4サイクル毎に同じ値になり、ctm[n]=ctm[n±4] が成り立つ。

また、攪乱値“ctm[n]”はデコード値であるため、ctm[n-1]およびctm[n+1] はctm[n]の信号線の並べ替えで生成できる。

また、2ビットカウンタ201の入力信号もデコードされ、その出力は制御信号“/LD”で制御され、Seed生成時のみ“CT0”,“CT3”をIP置換データとのEXOR演算部に供給される。

【0050】

[Seed生成]

制御信号“/LD”がハイレベルのとき、図8に示すように、攪乱データ“CT0”は全ビットローレベルになり、同様に攪乱データ“CT3”もローレベルとなる。そして、図示しない鍵スケジュール(Key Schedule)回路からは、たとえばダミーの鍵から生成したRound鍵がF関数部109に供給されているものとする。

DES演算命令が発行されると、まず攪乱値のSeed生成サイクルが実行される。このとき、制御信号“/LD”はハイレベルであるため、攪乱データ“CT0”はローレベルであることから、Rレジスタ106には“R0”が取り込まれる。

このとき、Lレジスタ105には、“L0”ではなく、直前のRレジスタ106の格納値が取り込まれるものとし、ラウンド鍵はダミー鍵から生成したものが供給されるものとする。

これらにより、攪乱値のSeed“CT0”は、平文のうちの“R0”から生成され、その過程でダミー鍵および直前のRレジスタ106の格納値によって攪乱された値となる。

Rレジスタ106の格納値“R0”は、F関数部109に入力されて拡張、ラウンド鍵“Kx+1”とEXOR演算された後、攪乱値“EX[P[CTx+1]]”とEXORされてSbox1094に入力される。

通常の演算サイクルでは、“EX[P[CTx+1]]”とのEXORで攪乱値が解除されるが、Seed生成サイクルのみはRレジスタ106の値が攪乱値でないため、この演算により攪乱が設定されてSbox1094に入力される。

Sbox1094の出力は、Lレジスタ105からの値“P-1[Rx] + CTx+2”により攪乱され、その中の選択された信号線が制御信号“/LD”がローレベルの期間、2ビットカウンタ201の入力およびデコード回路202−0の入力に供給される。

また、制御信号“/LD”がローレベルの期間、平文の攪乱値“CT0”,“CT3”が有効となり、IP置換後の値“R0”および“L0”は、各々“CT0”,“CT3”とEXORされてRレジスタ106およびLレジスタ105の入力に供給される。

なお、ラッチ(D−Latch回路)110の制御信号“/FCTL”が Seed生成サイクルではハイレベルに保持される。このため、Sbox演算の中間値および演算結果はRレジスタ106へのBus信号線に現れることはなく、動作電流に重畳するのはラッチ(D−Latch回路)110までの動作電流のみとなる。

【0051】

[DES演算サイクル]

クロックの立上りで、Sboxからの値が Counter に取り込まれ、Seed生成が終了すると、以降は通常のDES演算サイクルが実行される。そして、クロックCLKの立上りでカウンタ201はインクリメントされ、各デコード値“ctm[n]”の“1”の位置はローテイト(循環)する。

【0052】

図9は、本実施形態に係るSboxの構成例を示す図である。

図9は、1つのSub Sbox“S0”について示している。

図9のSub Sbox“S0”は、8つの4AND NOR210〜217、および4AND NOR210〜217の隣接する2つの出力を受ける4つのOR NAND220〜223を有する。

Sub Sbox“S0”は、OR NAND220〜223の出力を受ける4入力NORゲート224を有する。

また、Sub Sbox“S0”の入力側には、各攪乱用EXOR演算部EOR10〜EOR15、相補入力を得るインバータINV10〜INV15、およびデコード回路230〜232を有する。

【0053】

デコード回路230は、EXOR演算部EOR10,EOR15の出力信号およびインバータINV10,INV15を介した信号をデコードしてデータ/d0〜/d3を生成し、対応するOR NAND220〜223に供給する。

デコード回路231は、EXOR演算部EOR11、EOR12の出力信号およびインバータINV11,INV12を介した信号をデコードしてデータd0〜d3を生成し、対応する4AND OR210〜217に供給する。

デコード回路232は、EXOR演算部EOR13、EOR14の出力信号およびインバータINV13,INV14を介した信号をデコードしてデータd0〜d3を生成し、対応する4AND OR210〜217に供給する。

【0054】

本構成のSbox1094は、入力信号の6ビットから2ビットずつデコードして3つのデコード信号を生成する。そして、Sbox1094は、生成したデコード信号のうちの2つのデコード信号からSboxテーブル( Table)に基づいて生成した信号を、残りのデコード信号で選択して最終的な出力を生成する構成を採る。

Sub Sbox“S0”の入力は“b0’”〜“b5’”の6ビットであるが、“ '”が付加してある。これは、本来の値に対して、攪乱値によって攪乱されていることを示している。したがって、Sbox入力までは、攪乱値によって攪乱されたデータが来ている。

【0055】

まず、Sbox直前で、各々の攪乱値とEXOR演算することにより、攪乱を解除する。EXOR演算部EOR10〜EOR15の出力からは、EXOR信号そのままとその反転信号が出力され、これらの信号は相補動作をする。

そして、各2ビットの相補信号から4ビットのデコード信号が生成されている。相補信号は、付加容量の差分が小さければ、リーク(Leak)電流の抽出は困難である。

また、デコード信号は、データにかかわらず4本の信号の中で選択された1本だけが残りの信号線と反対の信号になる。したがって、4本の負荷容量の差分が小さければ、リーク(Leak)信号の抽出は困難である。

Sbox1094のTableに相当する部分は、{b1, b2} のデコード信号と、{b3, b4} のデコード信号からTable値で“1”となっている組み合わせを4AND−NOR210〜217で受ける。

さらにこの中から {b0, b5}のデコード信号で選択された信号がSub Sbox “S0”の出力信号として生成される。

このSboxの演算と平行して、Lレジスタ105のデータ“Ln-1 + P[CT[n-2]]”はP-1 置換後に“CTn + CTn+2”とEXOR演算されて“P-1[Ln-1] + CT[n]”となってSboxの出力“P-1[F(Rn-1,Kn)]”とEXOR演算される。

この出力信号は、P-1[F(Rn-1,Kn)] + P-1[Ln-1] + CT[n]=P-1[Rn] + CT[n]、となり、Sbox出力直後に攪乱数“CT[n]”で攪乱された値になってRレジスタ106に供給される。これより、Sbox1094の入出力信号は、攪乱数で攪乱された信号となっている。

以上より、Sbox1094の入力データは攪乱値により攪乱されたデータであり、Sbox1094の入力直後に攪乱を解除されたデータは、相補信号、デコード信号に変換され、Sboxの後半の2ゲート分でSboxの本来のデータが現れる。

ただし、この配線領域は僅かであり、その後Sbox出力となる直前で次の攪乱値“CT[n+1]”により攪乱される。これより、Sbox内部のリーク電流に対してDPA攻撃を仕掛けても、鍵の取出しは容易ではない。

【0056】

DPA攻撃では、変化電流の大きい信号線の充放電電流がまず攻撃対象となる。

本実施形態の場合、たとえばRound n の期間およびRound nからRound n+1に変化するとき、図5に示されているように、次のデータに基づく電流が流れる。

【0057】

[1] Rレジスタ106の出力変化は、Rn-1 + Rn + P[CT[n-1]] + P[CT[n]]に基づく電流が流れる。

[2] Lレジスタ105の出力変化は、Ln-1 + Ln + P[CT[n-2]] + P[CT[n-1]]に基づく電流が流れる。

[3] ラッチ(D−Latch回路)110の出力変化は、Rn-1 + Rn + P[CT[n-1]] + P[CT[n]]に基づく電流が流れる。

【0058】

しかし、これらはいずれも2つの攪乱数のEXOR値で攪乱されていて、各攪乱値はデコード値で、なおかつ1ビットローテイトした関係にあるため、本来の変化に対して常に2ビットが反転の動作をする関係にある。

このため、DPA攻撃で、たとえば1つのSub Sboxに対して4ビットアタック(4bit Attack)を行った場合、次のようになる。

推定した6ビット鍵が正しい場合、データ変化が“0000”のグループと“1111”のグループに消費電流を分けてその差分を採っても、実際には出力の2ビットは各々反転している。このため、2つのグループは共に2ビットの変化をしていて、ピーク電流は現れない。

1ビットアタック(1bit Attack)を行う場合、攻撃対象の1ビットは50%の確率で反転されているため、こちらでもピーク電流は現れない。

なお、攪乱値の初期値は平文データから生成しているため、平文毎に異なるビット位置で反転は起こる。

【0059】

図10(A)〜(K)は、攪乱例をハミング距離( Hamming Distance )と関連付けて示す図である。

図10(A)は元データを、図10(B)は攪乱値1を、図10(C)は攪乱値2を、図10(D)は攪乱値3を、図10(E)は攪乱値4を、それぞれ示している。図10(F)は元データのハミング距離(Hamming Distance :HD)を、図10(G)は攪乱値1から攪乱値2への変換時のHDを、図10(H)は攪乱値2から攪乱値3への変換時のHDを、それぞれ示している。図10(I)は攪乱値3から攪乱値4への変換時のHDを、図10(J)は攪乱値4から攪乱値1への変換時のHDを、図10(K)はHDビットの平均を、それぞれ示している。

【0060】

図10(A)の元データとは、たとえば、あるラウンド(Round)において、本来の4ビットのSub Sbox出力のRレジスタ106の格納値を示している。

図10(B)〜(E)は、その格納値に対してデコードされた攪乱値が“0001”,“0010”,“0100”,“1000”の場合についての、実際のRレジスタ106の格納値を示している。

そして、たとえば元のデータが“1011”で、ラウンドが更新されて更新データが“0000”〜“1111”に変化した場合について、攪乱がない場合の各レジスタ出力でのビット変化を表すHDは図10(F)に示す通りである。

ただし、攪乱されている場合、変化前の値の攪乱値と変化後の値の攪乱値がどの値かにより、図10(G)〜(H)の間のいずれかのHD値を採る。

各4ビットのHDは、攪乱値がどの値からどの値に変化したかにより、同じデータの更新であっても様々な値を採る。

そして、本来のHD値が(b3, b2, b1, b0)=(0, 0, 0, 0),(1, 1, 1, 1),(0, 1, 0, 1),(1, 0, 1, 0)の場合は、攪乱値にかかわらず常にHDは“2”で同じ値を採る。

さらに、4つの変化について、各ビットのHDの平均値は図10(K)に示すようになり、どの場合でも、どのビットでも常に“2”となる。

各演算において、攪乱値の初期値は平文を元に生成するが、平文を十分大きくすると、図10(G)〜(H)はほぼ同じ割合で発生する。

このため、いずれの遷移でも平均のHDは“2”となり、統計処理により、1ビットに着目した1ビットアタック(1bit Attack)および4ビットに着目した4ビットアタック(4bit Attack)でも、2つのグループ間の差分は現れない。したがって、DPA耐性は向上する。

【0061】

本第1の実施形態によれば、1ラウンドを、1クロックサイクルで実行でき、なおかつ、DPA耐性の向上した暗号演算回路が実現できる。これにより、暗号演算は、ラウンド数+1クロックサイクルで実行できる。

また、相補構成を採らないため、電流の増加を抑えられ、攪乱値は平文とSboxで生成するため、乱数発生回路等の付加回路が必要ない。

【0062】

以上の説明は、DES暗号について行ってきたが、この概念はAES暗号にも適用できる。

【0063】

<2.第2の実施形態>

第1の実施形態においては、本発明をDESに適用した場合について述べてきた。

本第2の実施形態においては、この概念をAES(Advanced Encryption Standard)に適用した場合について説明する。

【0064】

図11は、一般的なAES演算回路の構成例を示す図である。

図12は、本第2の実施形態に係るAES演算回路の構成例を示す図である。

【0065】

AESは、データが128ビットであるが、鍵は128ビット、192ビット、256ビットのものが定義され、各々AES−128,AES−192,AES−256が仕様としてFIPSに登録されている。演算のラウンド数も鍵長によって10,12,14と異なっている。

ここでは、AES−128の場合について説明する。

このAESは、128ビット単位でデータ処理を行い、サブバイト(Sub Byte)、シフトロウ(Shift_Row)およびミックスカラム(Mix_Column)とも8ビットを処理の最小単位としている。

このため、攪乱値は、たとえば32個の2ビット値をデコードした値を並べたものを攪乱値として用いれば良い。これにより、レジスタの出力変化および各演算ブロックの出力変化の平均は、4ビット単位で2ビットとなり、DPA攻撃をかけてもグループ間の差異はほとんど現れず、DPA耐性は向上する。

【0066】

図11のAES演算回路300は、サブバイト(Sub Bytes)変換部301、シフトロウ(Shift Rows)変換部302、ミックスカラム(Mix Columns)変換部303、スイッチ304、EXOR演算部305、および128ビットのレジスタ306を有する。

【0067】

サブバイト変換部301は、Sub_Bytes() 関数を実行し、Sboxによる換字変換を行う。

シフトロウ変換部302は、Shift_Row() 関数を実行し、サブバイト変換部301によるバイトデータをシフトする。

ミックスカラム変換部303は、Mix_Column() 関数を実行し、GF(28)での行列演算を実行する機能を有する。

【0068】

この例の場合は、レジスタ306をサブバイト変換部( Sub_Bytes() 関数)301の直前に配置しているが、別の位置でも構わない。

【0069】

暗号演算時、平文はまずラウンド0の鍵とEXOR演算した後、レジスタ306に取り込まれる。

そして、レジスタ306の出力が変化することによってSub_Bytes() 関数およびShift_Row() 関数が実行され、ラウンド9まではMix_Column() 関数が続けて実行されて、その演算結果がラウンド鍵とEXORされる。

ラウンド10ではMix_Column() 関数がスキップされてShift_Rows() 関数後の演算結果がラウンド鍵とEXORされてレジスタ306に取り込まれる。

以上がAES演算回路300の基本的な処理である。

【0070】

本第2の実施形態に係るAES演算回路300Aは、サブバイト変換部301の入力側に、レジスタ306の格納値と攪乱値CTn-1とのEXOR演算を行うEXOR演算部307が配置されている。

サブバイト変換部301の出力側、すなわちシフトロウ変換部302の入力側に、サブバイト変換部301の出力値と攪乱値CTnとのEXOR演算を行うEXOR演算部308が配置されている。

シフトロウ変換部302の出力側、すなわちミックスカラム変換部303の入力側に、シフトロウ変換部302の出力値と攪乱値CTnとのEXOR演算を行うEXOR演算部309が配置されている。

ミックスカラム変換部303の出力側に、ミックスカラム変換部303の出力と攪乱値CTnとのEXOR演算を行うEXOR演算部310が配置されている。

そして、レジスタ306の出力側に、その出力値と攪乱値CT10とのEXOR演算を行うEXOR演算部311が配置されている。

【0071】

図12のAES演算回路300Aは、攪乱値は、たとえば32個の2ビット値をデコードした値を並べたものを攪乱値として用いれば良い。この各攪乱値はラウンド毎にローテイトする。これにより、レジスタの出力変化および各演算ブロックの出力変化の平均は、4ビット単位で2ビットとなり、DPA攻撃をかけてもグループ間の差異はほとんど現れず、DPA耐性は向上する。

【0072】

このように、本第2の実施形態によれば、上述した第1の実施形態と同様の効果を得ることができる。

【0073】

以上説明したように、本実施形態によれば、1ラウンドを、1クロックサイクルで実行でき、なおかつ、DPA耐性の向上した暗号演算回路が実現できる。これにより、暗号演算は、ラウンド数+1クロックサイクルで実行できる。

また、相補構成を採らないため、電流の増加を抑えられ、攪乱値は平文とSboxで生成するため、乱数発生回路等の付加回路が必要ない。

【0074】

ここで、上述の暗号処理を実行するデバイスとしてのICモジュール400の構成例を図13に関連付けて説明する。

上述の処理は、たとえばPC、ICカード、リーダライタ、その他、様々な情報処理装置において実行可能であり、図13に示すICモジュール400は、これら様々な機器に採用することが可能である。

【0075】

図13において、CPU(Central Processing Unit)401は、暗号処理の開始や、終了、データの送受信の制御、各構成部間のデータ転送制御、その他の各種プログラムを実行するプロセッサである。

メモリ402は、CPU401が実行するプログラム、あるいは演算パラメータとしての固定データを格納するROM(Read-Only-Memory)を含む。

また、メモリ402は、CPU401の処理において実行されるプログラム、およびプログラム処理において適宜変化するパラメータの格納エリア、ワーク領域として使用されるRAM(Random Access Memory)等からなる。

また、メモリ402は暗号処理に必要な鍵データ等の格納領域として使用可能である。データ等の格納領域は、耐タンパ構造を持つメモリとして構成されることが好ましい。

【0076】

暗号処理部403は、たとえば上述したDESアルゴリズムなど複数段のラウンド関数の繰り返し処理を含む暗号アルゴリズムを実行する暗号処理装置である。

すなわち、暗号処理部403には、第1の実施形態に係るDES演算回路、および第2の実施形態に係るAES演算回路が適用される。

【0077】

送受信部404は、外部とのデータ通信を実行するデータ通信処理部であり、たとえばリーダライタ等、ICモジュールとのデータ通信を実行し、ICモジュール内で生成した暗号文の出力、あるいは外部のリーダライタ等の機器からのデータ入力などを実行する。

【0078】

なお、暗号処理部403において適用される各種の制御信号、たとえば前述したスイッチの切り替え制御信号は、クロック生成回路405からのクロック信号をトリガにして動作するタイミング発生回路406において生成する。そして、生成した信号を暗号処理部403に供給することが可能である。

【0079】

以上、特定の実施形態を参照しながら、本発明について詳解してきた。しかしながら、本発明の要旨を逸脱しない範囲で当業者が実施形態の修正や代用を成し得ることは自明である。すなわち、例示という形態で本発明を開示してきたのであり、限定的に解釈されるべきではない。

【符号の説明】

【0080】

100・・・DES演算回路、101・・・初期置換部[IP(Initial Permutation)部]、102・・・第1EXOR演算部、103・・・第2EXOR演算部、104L,104R・・・スイッチ、105・・・Lレジスタ、106・・・Rレジスタ、107・・・逆置換部(P-1)、108・・・第3EXOR演算部、109・・・F関数部、1091・・・拡張部、1092・・・第6EXOR演算部、1093(−0〜−7)・・・第7EXOR演算部、1094・・・Sbox、1095(−0〜−7)・・・第8EXOR演算部、1096・・・置換部、110・・・ラッチ(L−Latch回路)、111・・・第4EXOR演算部、112・・・第5EXOR演算部、113・・・逆置換部(IP-1)、114・・・暗号文出力部。

【技術分野】

【0001】

本発明は、たとえばICカードに適用される暗号処理装置に関し、さらに詳細には、低消費電流で、暗号解析処理、攻撃処理として知られる電力解析に対する耐性を向上させた暗号処理装置に関するものである。

【背景技術】

【0002】

ICカードでは、ホストコンピュータとデータのやり取りを行うとき、その過程でICカードに格納されている秘密情報が漏れても問題を発生させないために、やり取りするデータには暗号化したデータを用いる。

【0003】

この暗号化の方法として、現在最も多く用いられているのはDES(Data Encryption Standard)である。

DESでは、データの暗号化にはICカードの所有者とホストコンピュータが同じ鍵を所有し、データの送信側はデータをその鍵で暗号化して送信し、データの受信者は同じ鍵で復号化してメッセージを取り出す。

通信の過程で悪意の第三者が盗聴しても、鍵を有していない限りは復号化してメッセージを取り出すことは困難である。

【0004】

また、暗号化・復号化の時に使う鍵は、ICカード内のEEPROM等の不揮発性メモリに格納される。

そして、暗号化・復号化時にはCPUを介さないで直接ICカード内の暗号エンジンに転送されるような制御により、ICカードの所有者やICカードの開発エンジニアすら鍵データを取り出すことが不可能な構成を採ってセキュリティを保持している。

【0005】

しかし、ICカードの消費電流を測定し、それに統計処理を施して鍵を取り出すという攻撃方法(DPA:Differential Power Analysis)が P.Kocher らにより報告された。 このDPA攻撃は、下記<1>、<2>、<3>の示す手順で行われる。

<1> 異なる1000個程度の平文(M1〜M1000)を用いて暗号化演算を行い、消費電流波形(S1〜S1000)を取得する。

<2> サブSボックス(Sub Sbox:S0〜S7)の1つを選択し(たとえばS0)、その6ビット(bit)の鍵を推定して平文(M1〜M1000)でDESのシミュレーション(simulation)を行う。そして、たとえばS0出力のLSBのシミュレーション結果が“0”か“1”かに応じて対応する消費電流波形を2つのグループ(GP[0],GP[1])に分類する。

<3> 2つのグループの平均波形を計算し、その差分を採る。

このとき、ピーク波形が発生した場合、推定した6ビット鍵は正しいと判断し、上記<2>の処理に戻って、別のSub Sboxで同じ処理を行う。

ピーク波形がない場合、推定した6ビット鍵は間違いと判断し、別の鍵を推定して<2>の処理に戻る。

【0006】

全てのSub Sboxに対してピーク波形が観察されると、これにより6bit×8=48bitの鍵が求まり、残り8ビットは、28=256回の全数攻撃で求まる。

この攻撃の脅威は、必要な装置がパーソナルコンピュータ(パソコン)とデジタルオシロスコープだけである事である。あとは暗号LSIから電流を取得するための改造を施せば攻撃の環境が整い、この攻撃への対策が施されていないものに対しては、数時間で鍵が取得できる点が脅威である。

【0007】

上記例は、Sub Sboxがメモリで構成されている場合で、メモリ出力が攻撃対象となる。

暗号回路をロジック回路で構成する場合、Sub Sboxもロジック回路で構成されるため、メモリの場合と比較してSub Sboxの出力電流は小さくなり、攻撃の難易度は上がる。

このため、回路上で負荷容量が大きく、充放電電流の大きい回路、たとえば右レジスタ(R Register)の値更新時の充放電電流が攻撃の対象となる。これを具体的な例(DES演算回路)で示す。

【0008】

図1は、暗号回路の例としてDES演算回路の一般的な構成を示す図である。

図2は、図2のDES演算回路のタイミングチャートである。

【0009】

このDES演算回路10は、図1に示すように、初期置換部[IP(Initial Permutation)]11、スイッチ12L,12R、左レジスタ(Lレジスタという)13、および右レジスタ(Rレジスタ)14を有する。さらに、DES演算回路10は、F関数部15、EXOR演算部16、逆置換部(IP-1)17、および暗号文出力部(Crypto)18を有する。

【0010】

F関数部15は、図1に示すように、非線形処理を実行する複数(図1では8)のSボックス(Sbox)S0〜S7を有する。前段からの入力値F−in、すなわち、R(n−1)は拡張部(EX)15−1によって48ビットに拡大され、さらに鍵スケジュール部から入力する鍵(48ビット)KnとEXOR演算部15−2でEXOR演算が実行される。EXOR演算部15−2の出力が6ビットずつ非線形変換処理を実行する複数のSboxS0〜S7に入力される。各SboxS0〜S7では、変換テーブルを適用した6ビットから4ビットへの非線形変換処理が実行される。

SboxS0〜S7からの出力ビット4×8=32ビットは、置換部(P)15−3に入力されて、ビット位置の入れ替え処理がなされ、F関数出力32ビットを生成して出力する。

【0011】

このDES演算回路10は、1ラウンド(Round)分の回路が配置され、これを16回動作させることにより暗号演算を実行する。

平文は、IP置換後に32ビットずつに分けられて、L/Rレジスタ12L,12Rに格納される。これにより、Rレジスタ12Rの値はF関数に入力され、データ拡張,Round鍵とのEOR演算後にSboxに入力される。

Sboxの出力は、P置換による並べ替えの後、Lレジスタ12Lの値とEOR演算されて、Rレジスタ12Rの入力に供給される。

そして、クロックの立上りで、Rレジスタ12Rの値が更新される。この動作を16回繰り返す。そして、最初のサイクルで、Rレジスタ12Rの出力は、R0からF(R0,K1)+L0に変化するが、このときのRレジスタ12R出力での変化電流は、{F(R0,K1)+L0+R0}の関数となる。“K1”以外は既知の数であるため、Rレジスタ12Rの出力変化に対してDPA攻撃が可能となる。ここで、+は排他的論理和演算(EOR)を示す。

【0012】

DPA攻撃において、従来は、Sub Sboxの4ビット出力のうちの1ビットに着目して消費電流波形をグループ分けして、両グループの平均波形の差分で、推定した6ビット鍵の妥当性を判断していた。

しかし、プロセスの微細化に伴って、暗号ブロックの回路規模は小さくなり、これによって攻撃対象となる信号配線の幅や長さも小さくなり、その結果、配線容量は小さくなる。

同時に、ゲート酸化膜圧の薄膜化に伴って、電源電圧は低電圧化し、個々のレジスタビットおよびその負荷配線の充放電に伴う電流も小さくなる。そして、これらの相乗効果により、着目ビットの変化に伴う信号成分は小さくなるため、推定鍵の妥当性の判断の基準となるピーク電流の大きさも小さくなり、SN比は悪くなる。

【0013】

SN比を改善する手段として、以下の(1)および(2)に示す手段が採られる。

(1)攻撃に用いる信号波形の数を増やし、グループ平均演算後のノイズ成分を減らす。

(2)攻撃対象を、Sub Sbox出力に対応する4ビットが“全て変化する”/“全て変化しない”場合のみをグループ分けの対象とする。この場合、差分は4ビットであるため、信号成分が増える。

従来のSub Sboxの出力1ビットに着目しての攻撃を“1ビットアタック(1bit Attack) ”と称するのに対して、(2)の攻撃は、“4ビットアタック(4bit Attack) ”と称される。

【0014】

このDPA攻撃に対する対策として、次の方法が提案されている。

第1は、暗号回路を相補構成とし、相補動作によりリーク電流を削減する方法である。

第2は、乱数等を用いてデータおよびそれに起因するリーク電流を攪乱し、統計処理を困難にする方法である。

【0015】

第1の方法としては、たとえば特許文献1に開示された技術が知られている。

この技術では、1ビットのデータをハミング重み(Hamming Weight)の等しい2ビットの数値に展開し(たとえば“0”を“01”、“1”を“10”)、演算によるデータの遷移は、稼動相と休止相の2相を設ける。

そして、休止相で一旦、“0”でも“1”でもない状態(たとえば“00”)に遷移してから演算後のデータに遷移する制御を行う。これにより、各ビットについて、データに関係なく必ず1ビットの変化が起こり、演算値のデータ変化に伴う変化電流の検出を困難にしている。

【0016】

第2の方法としては、たとえば特許文献2に開示された技術が知られている。

この技術では、Sboxの出力を乱数で攪乱することによって、鍵に起因する回路動作に伴う微小電流を攪乱し、消費電流の統計処理を困難にしている。

【先行技術文献】

【特許文献】

【0017】

【特許文献1】特開2004−347975号公報

【特許文献2】USP6,295,606

【発明の概要】

【発明が解決しようとする課題】

【0018】

しかし、上記第1の方法では、本来の演算動作と反対の動作をする回路を並列に配置する必要があり、回路規模および動作電流が2倍かそれ以上になる。

また、1Roundの演算を、2つの相に分ける必要があるため、演算サイクル数は2倍になる。また、相補信号出力の配線容量に差があれば、そのビットが“0”の時と“1”の時で充放電電流に差異が発生し、それが攻撃対象となる。

【0019】

また、第2の方法を実現するためには、攪乱するデータ幅分の乱数を暗号演算に先立って生成しておく必要があり、乱数生成回路を搭載しておく必要がある。

そして、Round毎に乱数値を変える場合、Round演算毎に乱数値を生成、または必要数を事前に生成して格納しておく必要がある。

前者は、動作電流の増加、後者は乱数値生成のためのサイクルおよびそれを格納するための領域が必要になる。

また、第2次(2nd)以降の高次のDPA攻撃によって鍵が取り出される危険性があるため、高次のDPA攻撃に対する防御も考慮した対策をとる必要がある。

【0020】

本発明は、1ラウンド(Round)演算を1クロックサイクルで実行し、なおかつ、回路規模の増大を抑え、DPA耐性の向上を図ることが可能な暗号処理装置を提供することにある。

【課題を解決するための手段】

【0021】

本発明の観点の暗号処理装置は、所定の攪乱データで攪乱処理された演算用データを格納する少なくとも一つのレジスタと、上記レジスタの格納値に対してラウンド演算を行うラウンド演算部と、少なくとも上記ラウンド演算部の出力値を上記レジスタに選択的に入力させるスイッチと、上記ラウンド演算部は、上記記レジスタに格納された格納値を入力し、入力した当該格納値の攪乱状態を解除した値を基に関数処理を行い、上記関数処理結果と所定の攪乱データとの排他的論理和演算した結果を上記スイッチを介して上記レジスタに出力し、上記攪乱データのシードは、上記ラウンド演算部の異なるデコード値である。

好適には、本発明の暗号処理装置は、攪乱処理された演算用データを格納する第1レジスタと、攪乱処理された演算用データを格納する第2レジスタと、非線形変換部としてSboxを有し、上記第2レジスタの格納値に対してラウンド演算を行うラウンド演算部と、初期置換された第1データと所定の攪乱値との排他的論理和演算を行う第1演算部と、初期置換された第2データと所定の攪乱値との排他的論理和演算を行う第2演算部と、上記第1演算部の演算結果または上記第2レジスタの格納値を上記第1レジスタに選択的に入力させる第1スイッチと、上記第2演算部の演算結果または上記ラウンド演算部の出力値を上記第2レジスタに選択的に入力させる第2スイッチと、上記第1レジスタの格納値に対して逆置換を行う逆置換部と、逆置換した値と所定の攪乱値との排他的論理和演算を行い、演算結果を上記ラウンド演算部に供給する第3演算部と、を有し、上記ラウンド演算部は、上記Sboxにて、上記第2レジスタに格納された格納値の攪乱状態を解除した値を入力として、非線形変換処理を行い、上記Sboxの処理結果と上記第3演算部の演算結果との排他的論理和演算した結果を上記第2スイッチを介して上記第2レジスタに出力する。

【発明の効果】

【0022】

本発明によれば、1Round演算を1クロックサイクルで実行し、なおかつ、回路規模の増大を抑え、DPA耐性の向上を図ることができる。

【図面の簡単な説明】

【0023】

【図1】暗号回路の例としてDES演算回路の一般的な構成を示す図である。

【図2】図2のDES演算回路のタイミングチャートである。

【図3】本発明の第1の実施形態に係る暗号処理装置としてのDES演算回路の構成例を示す図である。

【図4】本実施形態に係る攪乱データおよび攪乱データをF関数のP置換に基づいて並べ替えた値を示す図である。

【図5】第1の実施形態に係るDES演算回路の動作を説明するためのタイミングチャートである。

【図6】本実施形態に係る攪乱値生成回路の構成例を示す図である。

【図7】攪乱値シード(Seed)生成部の構成例を示す図である。

【図8】攪乱値生成タイミングを示す図である。

【図9】本実施形態に係るSboxの構成例を示す図である。

【図10】攪乱例をハミング距離( Hamming Distance )と関連付けて示す図である。

【図11】一般的なAES演算回路の構成例を示す図である。

【図12】本第2の実施形態に係るAES演算回路の構成例を示す図である。

【図13】本発明の構成が適用可能な暗号処理実行デバイスとしてのICモジュールの構成例を示す図である。

【発明を実施するための形態】

【0024】

以下、本発明の実施形態を図面に関連付けて詳細について説明する。

なお、説明は以下の順序で行う。

1.第1の実施形態(DES演算回路の構成例)

2.第2の実施形態(AES演算回路の構成例)

【0025】

本実施形態の暗号処理装置は、以下の特徴を持って構成される。

データの撹乱(データと攪乱値のEXOR)により、DPA耐性を向上させる。

撹乱値は、暗号演算回路の中間値2ビットをデコードして用い、撹乱ビット数は各Sub Sboxで1ビットである。

撹乱データは、ラウンド毎にローテイトすることにより、撹乱データを変化させる。

レジスタ等での中間値の更新時に、格納データと更新データは、Sub Sbox単位で異なる1ビット(bit)が反転し、その結果、更新時の変化データは、本来の変化に対してSub Sbox単位で必ず2ビットが反対の変化をする。

Sboxの出力部にラッチ(Latch)またはレジスタ(Register)を配置し、Sbox の出力確定後に出力する制御を行う。

【0026】

<1.第1の実施形態>

図3は、本発明の第1の実施形態に係る暗号処理装置としてのDES演算回路の構成例を示す図である。

【0027】

本DES演算回路100は、初期置換部[IP(Initial Permutation)部]101、第1EXOR演算部102、第2EXOR演算部103、スイッチ104L,104R、L(左)レジスタ105、およびR(右)レジスタ106を有する。

DES演算回路100は、逆置換部(P-1)107、第3EXOR演算部108、ラウンド演算部としてのF関数部109、およびラッチ(レジスタ)110を有する。

DES演算回路100は、第4EXOR演算部111、第5EXOR演算部112、逆置換部(IP-1)113、および暗号文出力部114を有する。

スイッチ104Lは第1スイッチに相当し、スイッチ104Rは第2スイッチに相当し、Lレジスタ105は第1レジスタに相当し、Rレジスタ106は第2レジスタに相当する。また、F関数部109がラウンド演算部に含まれる。

なお、EXOR演算は排他的論理和演算を意味する。以下の説明で符号+はEXOR演算(排他的論理和演算)を示す。

【0028】

本実施形態のDES演算回路が、通常の回路構成と異なる点は、以下の点である。

IP置換後のデータのうち、L側の第1データは攪乱値P[CT3 ]と、R側の第2データは攪乱値P[CT0 ]とEXOR演算される。

IP-1 置換前のデータのうち、L側は攪乱値P[CT3 ]と、R側は攪乱値P[CT0 ]とEXOR演算される。

F関数部109の入力データは、Sbox入力の直前で攪乱数EX[P[CTn-1]]とEXORされて攪乱を解除され、Sboxの出力でP-1[Ln-1] + CTn とEXOR演算されて、新しい攪乱を設定される。

Round演算出力とRレジスタ106の信号パスの間に、ラッチ(D−Latch回路)110が配置され、Round関数の出力を制御する。

【0029】

図4(A)および(B)は、本実施形態に係る攪乱データおよび攪乱データをF関数のP置換に基づいて並べ替えた値を示す図である。

本実施形態において、CTnは、データを撹乱する32ビットの撹乱データ(攪乱値)を示す。攪乱データCTnは、図4(A)に示すように、2ビット値をデコードした4ビットの攪乱値“ctm[n]”(m=0〜7)を8個並べた構成を採る。

添え字の“n”は、たとえばラウンドを示す。各4ビットは、添え字の“m”に対応するSub Sbox の4ビット値の攪乱に使われる。

P[CTn]は、図4(B)に示すように、CTnを、F関数のP置換に基づいて並べ替えた値を示す。

また、図3において、EX[P[CTn-1]]は、攪乱数“CTn-1”をP置換による並替後に拡張関数に従って拡張した値を示す。

このような特徴を有する図3のDES演算回路100の構成および機能ついて具体的に説明する。

【0030】

IP置換部101は、メッセージを形成する平文に対してIP置換処理を施し、処理後の第1データとしての左データLDTを第1EXOR演算部102に出力し、第2データとしての右データRDTを第2EXOR演算部103に出力する。

なお、IP置換部101による左データLDTおよび右データRDTは32ビットである。

【0031】

第1EXOR演算部102は、IP置換部101による第1データとしての左データLDTとそれに対応する攪乱値P[CT3 ]とのEXOR演算を行う。

第1EXOR演算部102は、EXOR演算結果を、スイッチ104Lを介してLレジスタ105に供給する。

【0032】

第2EXOR演算部103は、IP置換部101による右データRDTとそれに対応する攪乱値P[CT0 ]とのEXOR演算を行う。

第2EXOR演算部103は、EXOR演算結果を、スイッチ104Rを介してRレジスタ106に供給する。

【0033】

第1スイッチとしてのスイッチ104Lの接点aは第1EXOR演算部102の出力に接続され、接点bはRレジスタ106の出力、第4EXOR演算部111に接続され、接点cがLレジスタ105の入力に接続されている。

第2スイッチとしてのスイッチ104Rの接点aは第2EXOR演算部103の出力に接続され、接点bはラッチ110の出力、第5EXOR演算部112に接続され、接点cがRレジスタ106の入力に接続されている。

【0034】

Lレジスタ105は、たとえばクロックの立上りのタイミングでスイッチ104Lを介して入力した、たとえば32ビットのデータをラッチ(格納)する。

Lレジスタ105には、本来の値Ln-1に攪乱値P[CTn-2 ]がEXOR演算された値が格納される。

Rレジスタ106は、たとえばクロックの立上りのタイミングでスイッチ104Rを介して入力した、たとえば32ビットのデータをラッチ(格納)する。

Rレジスタ106には、本来の値Rn-1に攪乱値P[CTn-1 ]がEXOR演算された値が格納される。

【0035】

逆置換部107は、Lレジスタ105に格納されたLn-1に攪乱値P[CTn−2 ]がEXOR演算された値を並べ替えて第3EXOR演算部108に出力する。

【0036】

第3EXOR演算部108は、逆置換部107の出力値と後で詳述する攪乱値生成回路で生成される値CTn + CTn-2とをEXOR演算してF関数部109に出力する。

【0037】

F関数部109は、非線形処理を実行する複数(図1では8)のSボックス(Sbox)S0〜S7を有する。F関数部110は、拡張部1091、第6EXOR演算部1092、第7EXOR演算部1093−0〜1093−7、Sbox1094、第8EXOR演算部1095−0〜1095−7、およびP置換部1096を有する。

【0038】

拡張部1091は、Rレジスタ106の格納値“Rn-1 + P[CTn-1]”を、拡張関数“EX”によって32ビットから48ビットに拡張する。

第6EXOR演算部1092は、拡張後の値とRound鍵“Kn”とEXOR演算して“EX[Rn-1+P[CTn-1]] + Kn”を得る。

第7EXOR演算部1093−0〜1093−7は、Sboxに入る直前で攪乱値“EX[P[CTn-1]]”とEXOR演算して、攪乱成分が取り除かれて通常と同じ値“EX[Rn-1] + Kn”としてSbox1094に入力する。

各SboxS0〜S7では、変換テーブルを適用した6ビットから4ビットへの非線形変換処理が実行され、32ビットのデータを出力する。

第8EXOR演算部1095−0〜1095−7は、Sbox1094の出力と第3EXOR演算部108によるEXOR値“P-1[Ln-1]+CTn”とEXOR演算する。

置換部(P)1096は、ビット位置の入れ替え処理を行い、F関数出力32ビットを生成してラッチ110に出力する。

【0039】

ラッチ110は、制御信号“/FCTL”がローレベル(Low Level)のとき、入力値をそのまま出力し、ハイレベル(High Level)のときは、ハイ(High) に変化するときの値を保持する。

ラッチ110の出力は、スイッチ104Rを介してRレジスタ106に入力される。制御信号“/FCTL”がロー(Low)に変化するタイミングを、Sboxの出力確定からマージンを見込んだタイミングに設定する。

これにより、Round関数出力からRレジスタ106への信号線に、DPA攻撃の対象となりうるSboxの中間値が現れないように制御される。

【0040】

第4EXOR演算部111は、ラウンド演算終了後のデータ(Rレジスタ106のデータ)と攪乱データP[CT3 ]とのEXOR演算を行って、攪乱状態を解除したデータを逆置換部113に出力する。

【0041】

第5EXOR演算部112は、ラウンド演算終了後のデータ(F関数部109の出力データ、ラッチ110の出力データ)と攪乱データP[CT0 ]とのEXOR演算を行って、攪乱状態を解除したデータを逆置換部113に出力する。

【0042】

逆置換部113では、攪乱状態が解除されたデータの逆置換変換(IP-1)を実行し、暗号文出力部114を介して暗号文として出力する。

【0043】

次に、第1の実施形態に係るDES演算回路の要部の具体的な構成および暗号化演算動作について、図5から図10に関連付けて説明する。

図5は、第1の実施形態に係るDES演算回路の動作を説明するためのタイミングチャートである。

通常の16ラウンドの演算の前に、攪乱値のシード(Seed)を生成するサイクルが実行される。このサイクルに関しては後述するため、ここでは省略する。

【0044】

DESの演算サイクル開始直前で、入力データである平文は、IP部101においてIP置換後、左データLDTと右データRDTに分けられる。

第1EXOR演算部102では、IP置換部101による左データLDT(L0)とそれに対応する攪乱値P[CT3 ]とのEXOR演算が行われる。

第2EXOR演算部103では、IP置換部101による右データRDT(R0)とそれに対応する攪乱値P[CT0 ]とのEXOR演算が行われる。

そして、R側は“R0”と攪乱値“P[CT0]”のEXOR演算値が、L側は“L0”と攪乱値“P[CT3]”とのEOR演算値が各々Rレジスタ106、Lレジスタ105の入力に供給され、クロックの立上りでレジスタに取り込まれる。

【0045】

Round nでは、Rレジスタ106には、本来の値“Rn-1”に対して攪乱値“P[CTn-1]”がEXOR演算された値が、Lレジスタ105には、本来の値“Ln-1”に対して攪乱値“P[CTn-2]”がEXOR演算された値が格納される。

Rレジスタ106の格納値“Rn-1 + P[CTn-1]”はスイッチ104Rを介してF関数部109に入力される。

F関数部109において、拡張部1091で拡張関数“EX”によって32ビットから48ビットに拡張後、Round鍵“Kn”とEXORされて“EX[Rn-1 + P[CTn-1]] + Kn”となる。

そして、Sbox1094に入る直前で、第7EXOR演算部1093−0〜1093−7において、攪乱値“EX[P[CTn-1]]”とEXOR演算されて攪乱成分が取り除かれて通常と同じ値“EX[Rn-1] + Kn”となってSboxに入力される。

Sbox1094の出力は、第8EXOR演算部1095−0〜1095−7に入力される。第8EXOR演算部1095−0〜1095−7にてLレジスタ105の格納値“Ln-1 + P[CTn-2]”をP-1 置換に基づいて並べ替えた値と攪乱値生成回路からの値“CTn + CTn-2”のEXOR値“P-1[Ln-1] + CTn”とEXOR演算される。

【0046】

第8EXOR演算部1095−0〜1095−7の出力は、P置換部1096におけるP置換処理を経てラッチ110に入力される。

ラッチ110では、制御信号“/FCTL”がローレベルのとき、入力値がそのまま出力され、ハイレベルのときは、ハイに変化するときの値が保持される。

ラッチ110の出力は、スイッチ104Rを介してRレジスタ106に入力される。前述したように、制御信号“/FCTL”がローに変化するタイミングが、Sboxの出力確定からマージンを見込んだタイミングに設定されている。これにより、Round関数出力からRレジスタ106への信号線に、DPA攻撃の対象となりうるSboxの中間値が現れないように制御される。

【0047】

図4に示す4ビットの各撹乱データおよびそのSeedを生成する回路および動作タイミングを各々図6、図7、および図8に示す。

図6は、本実施形態に係る攪乱値生成回路の構成例を示す図である。

図7は、攪乱値シード(Seed)生成部の構成例を示す図である。

図8は、攪乱値生成タイミングを示す図である。

【0048】

攪乱値“CTn”の各要素“ctm[n]”は、本来のDES演算に先立って追加される1サイクルで攪乱値のSeedから生成され、その後は、クロック動作により更新される。詳細を以下に記す。

【0049】

[回路構成]

図6の攪乱値生成回路200は、ロード(Load)機能付の2ビットカウンタ(2bit counter)201とデコード(Decode)回路202−0〜202−nが8個配置される。

2ビットカウンタ201のデータ入力D1,D0の入力段には2入力ORゲートORG1、ORG2が配置されている。また、デコード回路202−0の入力段にはインバータINV1、INV2が配置されている。

また、デコード回路202−0は、3入力NORゲートNRG1〜NRG4を有する。また、デコード回路202−n(n≠0)は、2入力NORゲートNRG11〜NRG14を有する。

各2ビットカウンタ201のデータ入力は、Sbox出力32ビットから適宜、換言すれば異なるSub Sboxから1ビットずつ選択された2ビットの供給ラインに接続されている。

2ビットカウンタ201は、Load 機能により、制御信号“/LD”がローレベルの期間、クロックCLKの立上りに同期して入力データをカウンタ内部に取り込む。

そして、このLoad 機能のためSboxの出力負荷の増加を抑えるため、図7に示すように、Sbox出力信号線の近くに配置されたORゲートORG21〜ORG26により2ビットカウンタ201までの負荷が切り離される構成を採っている。

2ビットカウンタ201に取り込まれた各2ビット値からは、デコード回路202で4ビットデコード(4bit decode)値“ctm[n]”が生成される。

Seed取込時は、ラウンド値“n”は0である。DES演算が開始されると、“n”および2ビットカウンタ値はインクリメントされる。

それに伴って攪乱値“ctm[n]”の“1”の位置は上位側にローテイトしていくが、“1000”(カウンタ値:11)になった後は“0001” (カウンタ値:00)に戻って再びローテイトを繰り返す。すなわち、4サイクル毎に同じ値になり、ctm[n]=ctm[n±4] が成り立つ。

また、攪乱値“ctm[n]”はデコード値であるため、ctm[n-1]およびctm[n+1] はctm[n]の信号線の並べ替えで生成できる。

また、2ビットカウンタ201の入力信号もデコードされ、その出力は制御信号“/LD”で制御され、Seed生成時のみ“CT0”,“CT3”をIP置換データとのEXOR演算部に供給される。

【0050】

[Seed生成]

制御信号“/LD”がハイレベルのとき、図8に示すように、攪乱データ“CT0”は全ビットローレベルになり、同様に攪乱データ“CT3”もローレベルとなる。そして、図示しない鍵スケジュール(Key Schedule)回路からは、たとえばダミーの鍵から生成したRound鍵がF関数部109に供給されているものとする。

DES演算命令が発行されると、まず攪乱値のSeed生成サイクルが実行される。このとき、制御信号“/LD”はハイレベルであるため、攪乱データ“CT0”はローレベルであることから、Rレジスタ106には“R0”が取り込まれる。

このとき、Lレジスタ105には、“L0”ではなく、直前のRレジスタ106の格納値が取り込まれるものとし、ラウンド鍵はダミー鍵から生成したものが供給されるものとする。

これらにより、攪乱値のSeed“CT0”は、平文のうちの“R0”から生成され、その過程でダミー鍵および直前のRレジスタ106の格納値によって攪乱された値となる。

Rレジスタ106の格納値“R0”は、F関数部109に入力されて拡張、ラウンド鍵“Kx+1”とEXOR演算された後、攪乱値“EX[P[CTx+1]]”とEXORされてSbox1094に入力される。

通常の演算サイクルでは、“EX[P[CTx+1]]”とのEXORで攪乱値が解除されるが、Seed生成サイクルのみはRレジスタ106の値が攪乱値でないため、この演算により攪乱が設定されてSbox1094に入力される。

Sbox1094の出力は、Lレジスタ105からの値“P-1[Rx] + CTx+2”により攪乱され、その中の選択された信号線が制御信号“/LD”がローレベルの期間、2ビットカウンタ201の入力およびデコード回路202−0の入力に供給される。

また、制御信号“/LD”がローレベルの期間、平文の攪乱値“CT0”,“CT3”が有効となり、IP置換後の値“R0”および“L0”は、各々“CT0”,“CT3”とEXORされてRレジスタ106およびLレジスタ105の入力に供給される。

なお、ラッチ(D−Latch回路)110の制御信号“/FCTL”が Seed生成サイクルではハイレベルに保持される。このため、Sbox演算の中間値および演算結果はRレジスタ106へのBus信号線に現れることはなく、動作電流に重畳するのはラッチ(D−Latch回路)110までの動作電流のみとなる。

【0051】

[DES演算サイクル]

クロックの立上りで、Sboxからの値が Counter に取り込まれ、Seed生成が終了すると、以降は通常のDES演算サイクルが実行される。そして、クロックCLKの立上りでカウンタ201はインクリメントされ、各デコード値“ctm[n]”の“1”の位置はローテイト(循環)する。

【0052】

図9は、本実施形態に係るSboxの構成例を示す図である。

図9は、1つのSub Sbox“S0”について示している。

図9のSub Sbox“S0”は、8つの4AND NOR210〜217、および4AND NOR210〜217の隣接する2つの出力を受ける4つのOR NAND220〜223を有する。

Sub Sbox“S0”は、OR NAND220〜223の出力を受ける4入力NORゲート224を有する。

また、Sub Sbox“S0”の入力側には、各攪乱用EXOR演算部EOR10〜EOR15、相補入力を得るインバータINV10〜INV15、およびデコード回路230〜232を有する。

【0053】

デコード回路230は、EXOR演算部EOR10,EOR15の出力信号およびインバータINV10,INV15を介した信号をデコードしてデータ/d0〜/d3を生成し、対応するOR NAND220〜223に供給する。

デコード回路231は、EXOR演算部EOR11、EOR12の出力信号およびインバータINV11,INV12を介した信号をデコードしてデータd0〜d3を生成し、対応する4AND OR210〜217に供給する。

デコード回路232は、EXOR演算部EOR13、EOR14の出力信号およびインバータINV13,INV14を介した信号をデコードしてデータd0〜d3を生成し、対応する4AND OR210〜217に供給する。

【0054】

本構成のSbox1094は、入力信号の6ビットから2ビットずつデコードして3つのデコード信号を生成する。そして、Sbox1094は、生成したデコード信号のうちの2つのデコード信号からSboxテーブル( Table)に基づいて生成した信号を、残りのデコード信号で選択して最終的な出力を生成する構成を採る。

Sub Sbox“S0”の入力は“b0’”〜“b5’”の6ビットであるが、“ '”が付加してある。これは、本来の値に対して、攪乱値によって攪乱されていることを示している。したがって、Sbox入力までは、攪乱値によって攪乱されたデータが来ている。

【0055】

まず、Sbox直前で、各々の攪乱値とEXOR演算することにより、攪乱を解除する。EXOR演算部EOR10〜EOR15の出力からは、EXOR信号そのままとその反転信号が出力され、これらの信号は相補動作をする。

そして、各2ビットの相補信号から4ビットのデコード信号が生成されている。相補信号は、付加容量の差分が小さければ、リーク(Leak)電流の抽出は困難である。

また、デコード信号は、データにかかわらず4本の信号の中で選択された1本だけが残りの信号線と反対の信号になる。したがって、4本の負荷容量の差分が小さければ、リーク(Leak)信号の抽出は困難である。

Sbox1094のTableに相当する部分は、{b1, b2} のデコード信号と、{b3, b4} のデコード信号からTable値で“1”となっている組み合わせを4AND−NOR210〜217で受ける。

さらにこの中から {b0, b5}のデコード信号で選択された信号がSub Sbox “S0”の出力信号として生成される。

このSboxの演算と平行して、Lレジスタ105のデータ“Ln-1 + P[CT[n-2]]”はP-1 置換後に“CTn + CTn+2”とEXOR演算されて“P-1[Ln-1] + CT[n]”となってSboxの出力“P-1[F(Rn-1,Kn)]”とEXOR演算される。

この出力信号は、P-1[F(Rn-1,Kn)] + P-1[Ln-1] + CT[n]=P-1[Rn] + CT[n]、となり、Sbox出力直後に攪乱数“CT[n]”で攪乱された値になってRレジスタ106に供給される。これより、Sbox1094の入出力信号は、攪乱数で攪乱された信号となっている。

以上より、Sbox1094の入力データは攪乱値により攪乱されたデータであり、Sbox1094の入力直後に攪乱を解除されたデータは、相補信号、デコード信号に変換され、Sboxの後半の2ゲート分でSboxの本来のデータが現れる。

ただし、この配線領域は僅かであり、その後Sbox出力となる直前で次の攪乱値“CT[n+1]”により攪乱される。これより、Sbox内部のリーク電流に対してDPA攻撃を仕掛けても、鍵の取出しは容易ではない。

【0056】

DPA攻撃では、変化電流の大きい信号線の充放電電流がまず攻撃対象となる。

本実施形態の場合、たとえばRound n の期間およびRound nからRound n+1に変化するとき、図5に示されているように、次のデータに基づく電流が流れる。

【0057】

[1] Rレジスタ106の出力変化は、Rn-1 + Rn + P[CT[n-1]] + P[CT[n]]に基づく電流が流れる。

[2] Lレジスタ105の出力変化は、Ln-1 + Ln + P[CT[n-2]] + P[CT[n-1]]に基づく電流が流れる。

[3] ラッチ(D−Latch回路)110の出力変化は、Rn-1 + Rn + P[CT[n-1]] + P[CT[n]]に基づく電流が流れる。

【0058】

しかし、これらはいずれも2つの攪乱数のEXOR値で攪乱されていて、各攪乱値はデコード値で、なおかつ1ビットローテイトした関係にあるため、本来の変化に対して常に2ビットが反転の動作をする関係にある。

このため、DPA攻撃で、たとえば1つのSub Sboxに対して4ビットアタック(4bit Attack)を行った場合、次のようになる。

推定した6ビット鍵が正しい場合、データ変化が“0000”のグループと“1111”のグループに消費電流を分けてその差分を採っても、実際には出力の2ビットは各々反転している。このため、2つのグループは共に2ビットの変化をしていて、ピーク電流は現れない。

1ビットアタック(1bit Attack)を行う場合、攻撃対象の1ビットは50%の確率で反転されているため、こちらでもピーク電流は現れない。

なお、攪乱値の初期値は平文データから生成しているため、平文毎に異なるビット位置で反転は起こる。

【0059】

図10(A)〜(K)は、攪乱例をハミング距離( Hamming Distance )と関連付けて示す図である。

図10(A)は元データを、図10(B)は攪乱値1を、図10(C)は攪乱値2を、図10(D)は攪乱値3を、図10(E)は攪乱値4を、それぞれ示している。図10(F)は元データのハミング距離(Hamming Distance :HD)を、図10(G)は攪乱値1から攪乱値2への変換時のHDを、図10(H)は攪乱値2から攪乱値3への変換時のHDを、それぞれ示している。図10(I)は攪乱値3から攪乱値4への変換時のHDを、図10(J)は攪乱値4から攪乱値1への変換時のHDを、図10(K)はHDビットの平均を、それぞれ示している。

【0060】

図10(A)の元データとは、たとえば、あるラウンド(Round)において、本来の4ビットのSub Sbox出力のRレジスタ106の格納値を示している。

図10(B)〜(E)は、その格納値に対してデコードされた攪乱値が“0001”,“0010”,“0100”,“1000”の場合についての、実際のRレジスタ106の格納値を示している。

そして、たとえば元のデータが“1011”で、ラウンドが更新されて更新データが“0000”〜“1111”に変化した場合について、攪乱がない場合の各レジスタ出力でのビット変化を表すHDは図10(F)に示す通りである。

ただし、攪乱されている場合、変化前の値の攪乱値と変化後の値の攪乱値がどの値かにより、図10(G)〜(H)の間のいずれかのHD値を採る。

各4ビットのHDは、攪乱値がどの値からどの値に変化したかにより、同じデータの更新であっても様々な値を採る。

そして、本来のHD値が(b3, b2, b1, b0)=(0, 0, 0, 0),(1, 1, 1, 1),(0, 1, 0, 1),(1, 0, 1, 0)の場合は、攪乱値にかかわらず常にHDは“2”で同じ値を採る。

さらに、4つの変化について、各ビットのHDの平均値は図10(K)に示すようになり、どの場合でも、どのビットでも常に“2”となる。

各演算において、攪乱値の初期値は平文を元に生成するが、平文を十分大きくすると、図10(G)〜(H)はほぼ同じ割合で発生する。

このため、いずれの遷移でも平均のHDは“2”となり、統計処理により、1ビットに着目した1ビットアタック(1bit Attack)および4ビットに着目した4ビットアタック(4bit Attack)でも、2つのグループ間の差分は現れない。したがって、DPA耐性は向上する。

【0061】

本第1の実施形態によれば、1ラウンドを、1クロックサイクルで実行でき、なおかつ、DPA耐性の向上した暗号演算回路が実現できる。これにより、暗号演算は、ラウンド数+1クロックサイクルで実行できる。

また、相補構成を採らないため、電流の増加を抑えられ、攪乱値は平文とSboxで生成するため、乱数発生回路等の付加回路が必要ない。

【0062】

以上の説明は、DES暗号について行ってきたが、この概念はAES暗号にも適用できる。

【0063】

<2.第2の実施形態>

第1の実施形態においては、本発明をDESに適用した場合について述べてきた。

本第2の実施形態においては、この概念をAES(Advanced Encryption Standard)に適用した場合について説明する。

【0064】

図11は、一般的なAES演算回路の構成例を示す図である。

図12は、本第2の実施形態に係るAES演算回路の構成例を示す図である。

【0065】

AESは、データが128ビットであるが、鍵は128ビット、192ビット、256ビットのものが定義され、各々AES−128,AES−192,AES−256が仕様としてFIPSに登録されている。演算のラウンド数も鍵長によって10,12,14と異なっている。

ここでは、AES−128の場合について説明する。

このAESは、128ビット単位でデータ処理を行い、サブバイト(Sub Byte)、シフトロウ(Shift_Row)およびミックスカラム(Mix_Column)とも8ビットを処理の最小単位としている。

このため、攪乱値は、たとえば32個の2ビット値をデコードした値を並べたものを攪乱値として用いれば良い。これにより、レジスタの出力変化および各演算ブロックの出力変化の平均は、4ビット単位で2ビットとなり、DPA攻撃をかけてもグループ間の差異はほとんど現れず、DPA耐性は向上する。

【0066】

図11のAES演算回路300は、サブバイト(Sub Bytes)変換部301、シフトロウ(Shift Rows)変換部302、ミックスカラム(Mix Columns)変換部303、スイッチ304、EXOR演算部305、および128ビットのレジスタ306を有する。

【0067】

サブバイト変換部301は、Sub_Bytes() 関数を実行し、Sboxによる換字変換を行う。

シフトロウ変換部302は、Shift_Row() 関数を実行し、サブバイト変換部301によるバイトデータをシフトする。

ミックスカラム変換部303は、Mix_Column() 関数を実行し、GF(28)での行列演算を実行する機能を有する。

【0068】

この例の場合は、レジスタ306をサブバイト変換部( Sub_Bytes() 関数)301の直前に配置しているが、別の位置でも構わない。

【0069】

暗号演算時、平文はまずラウンド0の鍵とEXOR演算した後、レジスタ306に取り込まれる。

そして、レジスタ306の出力が変化することによってSub_Bytes() 関数およびShift_Row() 関数が実行され、ラウンド9まではMix_Column() 関数が続けて実行されて、その演算結果がラウンド鍵とEXORされる。

ラウンド10ではMix_Column() 関数がスキップされてShift_Rows() 関数後の演算結果がラウンド鍵とEXORされてレジスタ306に取り込まれる。

以上がAES演算回路300の基本的な処理である。

【0070】

本第2の実施形態に係るAES演算回路300Aは、サブバイト変換部301の入力側に、レジスタ306の格納値と攪乱値CTn-1とのEXOR演算を行うEXOR演算部307が配置されている。

サブバイト変換部301の出力側、すなわちシフトロウ変換部302の入力側に、サブバイト変換部301の出力値と攪乱値CTnとのEXOR演算を行うEXOR演算部308が配置されている。

シフトロウ変換部302の出力側、すなわちミックスカラム変換部303の入力側に、シフトロウ変換部302の出力値と攪乱値CTnとのEXOR演算を行うEXOR演算部309が配置されている。

ミックスカラム変換部303の出力側に、ミックスカラム変換部303の出力と攪乱値CTnとのEXOR演算を行うEXOR演算部310が配置されている。

そして、レジスタ306の出力側に、その出力値と攪乱値CT10とのEXOR演算を行うEXOR演算部311が配置されている。

【0071】

図12のAES演算回路300Aは、攪乱値は、たとえば32個の2ビット値をデコードした値を並べたものを攪乱値として用いれば良い。この各攪乱値はラウンド毎にローテイトする。これにより、レジスタの出力変化および各演算ブロックの出力変化の平均は、4ビット単位で2ビットとなり、DPA攻撃をかけてもグループ間の差異はほとんど現れず、DPA耐性は向上する。

【0072】

このように、本第2の実施形態によれば、上述した第1の実施形態と同様の効果を得ることができる。

【0073】

以上説明したように、本実施形態によれば、1ラウンドを、1クロックサイクルで実行でき、なおかつ、DPA耐性の向上した暗号演算回路が実現できる。これにより、暗号演算は、ラウンド数+1クロックサイクルで実行できる。

また、相補構成を採らないため、電流の増加を抑えられ、攪乱値は平文とSboxで生成するため、乱数発生回路等の付加回路が必要ない。

【0074】

ここで、上述の暗号処理を実行するデバイスとしてのICモジュール400の構成例を図13に関連付けて説明する。

上述の処理は、たとえばPC、ICカード、リーダライタ、その他、様々な情報処理装置において実行可能であり、図13に示すICモジュール400は、これら様々な機器に採用することが可能である。

【0075】

図13において、CPU(Central Processing Unit)401は、暗号処理の開始や、終了、データの送受信の制御、各構成部間のデータ転送制御、その他の各種プログラムを実行するプロセッサである。

メモリ402は、CPU401が実行するプログラム、あるいは演算パラメータとしての固定データを格納するROM(Read-Only-Memory)を含む。

また、メモリ402は、CPU401の処理において実行されるプログラム、およびプログラム処理において適宜変化するパラメータの格納エリア、ワーク領域として使用されるRAM(Random Access Memory)等からなる。

また、メモリ402は暗号処理に必要な鍵データ等の格納領域として使用可能である。データ等の格納領域は、耐タンパ構造を持つメモリとして構成されることが好ましい。

【0076】

暗号処理部403は、たとえば上述したDESアルゴリズムなど複数段のラウンド関数の繰り返し処理を含む暗号アルゴリズムを実行する暗号処理装置である。

すなわち、暗号処理部403には、第1の実施形態に係るDES演算回路、および第2の実施形態に係るAES演算回路が適用される。

【0077】

送受信部404は、外部とのデータ通信を実行するデータ通信処理部であり、たとえばリーダライタ等、ICモジュールとのデータ通信を実行し、ICモジュール内で生成した暗号文の出力、あるいは外部のリーダライタ等の機器からのデータ入力などを実行する。

【0078】

なお、暗号処理部403において適用される各種の制御信号、たとえば前述したスイッチの切り替え制御信号は、クロック生成回路405からのクロック信号をトリガにして動作するタイミング発生回路406において生成する。そして、生成した信号を暗号処理部403に供給することが可能である。

【0079】

以上、特定の実施形態を参照しながら、本発明について詳解してきた。しかしながら、本発明の要旨を逸脱しない範囲で当業者が実施形態の修正や代用を成し得ることは自明である。すなわち、例示という形態で本発明を開示してきたのであり、限定的に解釈されるべきではない。

【符号の説明】

【0080】

100・・・DES演算回路、101・・・初期置換部[IP(Initial Permutation)部]、102・・・第1EXOR演算部、103・・・第2EXOR演算部、104L,104R・・・スイッチ、105・・・Lレジスタ、106・・・Rレジスタ、107・・・逆置換部(P-1)、108・・・第3EXOR演算部、109・・・F関数部、1091・・・拡張部、1092・・・第6EXOR演算部、1093(−0〜−7)・・・第7EXOR演算部、1094・・・Sbox、1095(−0〜−7)・・・第8EXOR演算部、1096・・・置換部、110・・・ラッチ(L−Latch回路)、111・・・第4EXOR演算部、112・・・第5EXOR演算部、113・・・逆置換部(IP-1)、114・・・暗号文出力部。

【特許請求の範囲】

【請求項1】

所定の攪乱データで攪乱処理された演算用データを格納する少なくとも一つのレジスタと、

上記レジスタの格納値に対してラウンド演算を行うラウンド演算部と、

少なくとも上記ラウンド演算部の出力値を上記レジスタに選択的に入力させるスイッチと、

上記ラウンド演算部は、

上記記レジスタに格納された格納値を入力し、入力した当該格納値の攪乱状態を解除した値を基に関数処理を行い、

上記関数処理結果と所定の攪乱データとの排他的論理和演算した結果を上記スイッチを介して上記レジスタに出力し、

上記攪乱データのシードは、

上記ラウンド演算部の異なるデコード値である

暗号処理装置。

【請求項2】

上記ラウンド演算部は、複数のサブSboxを含むSboxを有し、

上記攪乱値は、上記ラウンド演算部の中間値2ビットをデコードして用い、攪乱ビット数は上記各サブboxで1ビットである

請求項1記載の暗号処理装置。

【請求項3】

上記ラウンド演算部は、複数のサブSboxを含むSboxを有し、

上記攪乱データのシードは、

異なるサブSboxからの信号のデコード値である

請求項1または2記載の暗号処理装置。

【請求項4】

攪乱データは、ラウンドごとに循環させて変化させる

請求項1から3のいずれか一に記載の暗号処理装置。

【請求項5】

上記ラウンド演算部は、複数のサブSboxを含むSboxを有し、

中間値の更新時に、格納データと更新データは、サブSbox単位で異なる1ビットが反転し、更新時の変化データは、本来の変化に対してサブSbox単位で2ビットが反対の変化をする

請求項1から4のいずれか一に記載の暗号処理装置。

【請求項6】

上記ラウンド演算部の出力側に配置されたラッチを有し、

上記ラッチは、

上記Sboxの出力確定後に出力するように制御される

請求項1から5のいずれか一に記載の暗号処理装置。

【請求項7】

攪乱処理された演算用データを格納する第1レジスタと、

攪乱処理された演算用データを格納する第2レジスタと、

非線形変換部としてSboxを有し、上記第2レジスタの格納値に対してラウンド演算を行うラウンド演算部と、

初期置換された第1データと所定の攪乱値との排他的論理和演算を行う第1演算部と、

初期置換された第2データと所定の攪乱値との排他的論理和演算を行う第2演算部と、

上記第1演算部の演算結果または上記第2レジスタの格納値を上記第1レジスタに選択的に入力させる第1スイッチと、

上記第2演算部の演算結果または上記ラウンド演算部の出力値を上記第2レジスタに選択的に入力させる第2スイッチと、

上記第1レジスタの格納値に対して逆置換を行う逆置換部と、

逆置換した値と所定の攪乱値との排他的論理和演算を行い、演算結果を上記ラウンド演算部に供給する第3演算部と、を有し、

上記ラウンド演算部は、

上記Sboxにて、上記第2レジスタに格納された格納値の攪乱状態を解除した値を入力として、非線形変換処理を行い、

上記Sboxの処理結果と上記第3演算部の演算結果との排他的論理和演算した結果を上記第2スイッチを介して上記第2レジスタに出力する

請求項1から6のいずれか一に記載の暗号処理装置。

【請求項8】

上記第2レジスタの格納値および上記ラウンド演算部におけるラウンド演算終了後のデータと攪乱データとの排他的論理和演算を行って、上記第2レジスタの格納値および上記ラウンド演算部の出力値の攪乱状態を解除する第4演算部および第5演算部を有する

請求項7記載の暗号処理装置。

【請求項9】

上記ラウンド演算部は、

上記第2レジスタの格納値データのビットを拡張する拡張部と、

上記拡張部の拡張データと鍵との排他的論理演算を行う第6演算部と、

上記第6演算部の出力値と所定の攪乱値との排他的論理演算を行って、上記拡張部の出力値の攪乱状態を解除して上記Sboxに供給する第7演算部と、

上記Sboxの出力値と上記第3演算部の出力値との排他的論理和演算を行う第8演算部と、

上記第8演算部の出力におけるビット位置の入れ替え処理を行う置換部と、を含む

請求項7または8記載の暗号処理装置。

【請求項10】

前記暗号処理装置は、DES(Data Encryption Standard)アルゴリズムに従った暗号処理演算を実行する

請求項1から9のいずれか一に記載の暗号処理装置。

【請求項1】

所定の攪乱データで攪乱処理された演算用データを格納する少なくとも一つのレジスタと、

上記レジスタの格納値に対してラウンド演算を行うラウンド演算部と、

少なくとも上記ラウンド演算部の出力値を上記レジスタに選択的に入力させるスイッチと、

上記ラウンド演算部は、

上記記レジスタに格納された格納値を入力し、入力した当該格納値の攪乱状態を解除した値を基に関数処理を行い、

上記関数処理結果と所定の攪乱データとの排他的論理和演算した結果を上記スイッチを介して上記レジスタに出力し、

上記攪乱データのシードは、

上記ラウンド演算部の異なるデコード値である

暗号処理装置。

【請求項2】

上記ラウンド演算部は、複数のサブSboxを含むSboxを有し、

上記攪乱値は、上記ラウンド演算部の中間値2ビットをデコードして用い、攪乱ビット数は上記各サブboxで1ビットである

請求項1記載の暗号処理装置。

【請求項3】

上記ラウンド演算部は、複数のサブSboxを含むSboxを有し、

上記攪乱データのシードは、

異なるサブSboxからの信号のデコード値である

請求項1または2記載の暗号処理装置。

【請求項4】

攪乱データは、ラウンドごとに循環させて変化させる

請求項1から3のいずれか一に記載の暗号処理装置。

【請求項5】

上記ラウンド演算部は、複数のサブSboxを含むSboxを有し、

中間値の更新時に、格納データと更新データは、サブSbox単位で異なる1ビットが反転し、更新時の変化データは、本来の変化に対してサブSbox単位で2ビットが反対の変化をする

請求項1から4のいずれか一に記載の暗号処理装置。

【請求項6】

上記ラウンド演算部の出力側に配置されたラッチを有し、

上記ラッチは、

上記Sboxの出力確定後に出力するように制御される

請求項1から5のいずれか一に記載の暗号処理装置。

【請求項7】

攪乱処理された演算用データを格納する第1レジスタと、

攪乱処理された演算用データを格納する第2レジスタと、

非線形変換部としてSboxを有し、上記第2レジスタの格納値に対してラウンド演算を行うラウンド演算部と、

初期置換された第1データと所定の攪乱値との排他的論理和演算を行う第1演算部と、

初期置換された第2データと所定の攪乱値との排他的論理和演算を行う第2演算部と、

上記第1演算部の演算結果または上記第2レジスタの格納値を上記第1レジスタに選択的に入力させる第1スイッチと、

上記第2演算部の演算結果または上記ラウンド演算部の出力値を上記第2レジスタに選択的に入力させる第2スイッチと、

上記第1レジスタの格納値に対して逆置換を行う逆置換部と、

逆置換した値と所定の攪乱値との排他的論理和演算を行い、演算結果を上記ラウンド演算部に供給する第3演算部と、を有し、

上記ラウンド演算部は、

上記Sboxにて、上記第2レジスタに格納された格納値の攪乱状態を解除した値を入力として、非線形変換処理を行い、

上記Sboxの処理結果と上記第3演算部の演算結果との排他的論理和演算した結果を上記第2スイッチを介して上記第2レジスタに出力する

請求項1から6のいずれか一に記載の暗号処理装置。

【請求項8】

上記第2レジスタの格納値および上記ラウンド演算部におけるラウンド演算終了後のデータと攪乱データとの排他的論理和演算を行って、上記第2レジスタの格納値および上記ラウンド演算部の出力値の攪乱状態を解除する第4演算部および第5演算部を有する

請求項7記載の暗号処理装置。

【請求項9】

上記ラウンド演算部は、

上記第2レジスタの格納値データのビットを拡張する拡張部と、

上記拡張部の拡張データと鍵との排他的論理演算を行う第6演算部と、

上記第6演算部の出力値と所定の攪乱値との排他的論理演算を行って、上記拡張部の出力値の攪乱状態を解除して上記Sboxに供給する第7演算部と、

上記Sboxの出力値と上記第3演算部の出力値との排他的論理和演算を行う第8演算部と、

上記第8演算部の出力におけるビット位置の入れ替え処理を行う置換部と、を含む

請求項7または8記載の暗号処理装置。

【請求項10】

前記暗号処理装置は、DES(Data Encryption Standard)アルゴリズムに従った暗号処理演算を実行する

請求項1から9のいずれか一に記載の暗号処理装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2012−108401(P2012−108401A)

【公開日】平成24年6月7日(2012.6.7)

【国際特許分類】

【出願番号】特願2010−258553(P2010−258553)

【出願日】平成22年11月19日(2010.11.19)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成24年6月7日(2012.6.7)

【国際特許分類】

【出願日】平成22年11月19日(2010.11.19)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]