暗号化処理回路、及び、暗号化処理方法

【課題】外部クロック信号の周期が変更された場合であっても鍵が特定される可能性を低減することが可能な暗号化処理回路を提供すること。

【解決手段】暗号化処理回路100は、レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する、ラウンド処理を実行することにより、入力された情報を暗号化する暗号化処理回路である。暗号化処理回路100は、外部から外部クロック信号が入力され、フィードバック制御を行うことにより、当該入力された外部クロック信号と同期した内部クロック信号を生成する位相同期回路101と、上記生成された内部クロック信号に同期して作動するように構成され、且つ、上記ラウンド処理を繰り返し実行することにより、上記入力された情報を暗号化するラウンド処理回路102と、を備える。

【解決手段】暗号化処理回路100は、レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する、ラウンド処理を実行することにより、入力された情報を暗号化する暗号化処理回路である。暗号化処理回路100は、外部から外部クロック信号が入力され、フィードバック制御を行うことにより、当該入力された外部クロック信号と同期した内部クロック信号を生成する位相同期回路101と、上記生成された内部クロック信号に同期して作動するように構成され、且つ、上記ラウンド処理を繰り返し実行することにより、上記入力された情報を暗号化するラウンド処理回路102と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ラウンド処理を実行することにより情報を暗号化する暗号化処理回路に関する。

【背景技術】

【0002】

ラウンド処理を実行することにより情報を暗号化する暗号化処理回路が知られている。この種の暗号化処理回路の一つとして、特許文献1に記載の暗号化処理回路は、外部クロック信号に同期してラウンド処理を繰り返し実行することにより、入力された情報を暗号化する。ラウンド処理は、レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する処理である。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−245753号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、レジスタに格納するために当該レジスタに入力される情報が、予め設定されたデータ維持要求期間内に変更された場合を想定する。ここで、データ維持要求期間は、外部クロック信号の立ち上がりエッジ(又は、立ち下がりエッジ)よりもセットアップタイムだけ前の時点から、当該エッジよりもホールドタイムだけ後の時点までの期間である。この場合、レジスタに格納される情報が、変更前の情報であるか、変更後の情報であるか、が保証されなくなる。

【0005】

そこで、ラウンド処理の実行結果を表す情報がレジスタに入力される際に、外部クロック信号の周期を短くすることにより、暗号化処理回路に異常な処理を実行させることができる。また、暗号化処理回路が異常な処理を実行した場合における、暗号化された情報と、暗号化処理回路が正常な処理を実行した場合における、暗号化された情報と、の差を表す情報に基づいて(即ち、フォールト攻撃によって)、鍵を特定できる場合があることが知られている。

【0006】

このように、上記暗号化処理回路においては、外部クロック信号の周期が変更されることにより鍵が特定されてしまう虞があった。

【0007】

このため、本発明の目的は、上述した課題である「外部クロック信号の周期が変更されることにより鍵が特定されてしまう場合が生じること」を解決することが可能な暗号化処理回路を提供することにある。

【課題を解決するための手段】

【0008】

かかる目的を達成するため本発明の一形態である暗号化処理回路は、

レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する、ラウンド処理を実行することにより、入力された情報を暗号化する暗号化処理回路である。

【0009】

更に、この暗号化処理回路は、

外部から外部クロック信号が入力され、フィードバック制御を行うことにより、当該入力された外部クロック信号と同期した内部クロック信号を生成する位相同期回路と、

上記生成された内部クロック信号に同期して作動するように構成され、且つ、上記ラウンド処理を繰り返し実行することにより、上記入力された情報を暗号化するラウンド処理回路と、

を備える。

【0010】

また、本発明の他の形態である暗号化処理方法は、

レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する、ラウンド処理を実行することにより、入力された情報を暗号化する方法である。

【0011】

更に、この暗号化処理方法は、

外部から外部クロック信号が入力され、フィードバック制御を行うことにより、当該入力された外部クロック信号と同期した内部クロック信号を生成し、

上記生成された内部クロック信号に同期して作動することによって、上記ラウンド処理を繰り返し実行することにより、上記入力された情報を暗号化する方法である。

【発明の効果】

【0012】

本発明は、以上のように構成されることにより、外部クロック信号の周期が変更された場合であっても鍵が特定される可能性を低減することができる。

【図面の簡単な説明】

【0013】

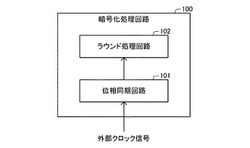

【図1】本発明の第1実施形態に係る暗号化処理回路の概略構成を表す図である。

【図2】本発明の第1実施形態に係る暗号化処理回路が実行する処理を示したフローチャートである。

【図3】本発明の第2実施形態に係る暗号化処理回路の概略構成を表す図である。

【図4】本発明の第3実施形態に係る暗号化処理回路の概略構成を表す図である。

【発明を実施するための形態】

【0014】

以下、本発明に係る、暗号化処理回路、及び、暗号化処理方法、の各実施形態について図1〜図4を参照しながら説明する。

【0015】

<第1実施形態>

(構成)

図1に示したように、第1実施形態に係る暗号化処理回路1は、集積回路である。暗号化処理回路1には、暗号化処理回路1の外部から情報(平文)が入力される。暗号化処理回路1は、入力された情報を鍵(としての情報)に基づいて暗号化する。そして、暗号化処理回路1は、暗号化された情報(暗号文)を暗号化処理回路1の外部へ出力する。

【0016】

本例では、暗号化処理回路1は、共通鍵暗号方式の1つであるAES(Advanced Encryption Standard)暗号方式に従って、入力された情報を暗号化する。AES暗号方式は、ブロック暗号方式の1つである。なお、暗号化処理回路1は、DES(Data Encryption Standard)暗号方式等の他の暗号方式に従って、入力された情報を暗号化するように構成されていてもよい。

【0017】

暗号化処理回路1は、ラウンド処理回路10と、鍵スケジュール処理回路20と、位相同期回路(PLL;Phase Locked Loop)30と、を備える。

【0018】

位相同期回路30には、暗号化処理回路1の外部からクロック信号(外部クロック信号)が入力される。位相同期回路30は、フィードバック制御を行うことにより、入力された外部クロック信号と同期したクロック信号(内部クロック信号)を生成する。位相同期回路30は、生成した内部クロック信号を、ラウンド処理回路10及び鍵スケジュール処理回路20のそれぞれへ出力(供給)する。

【0019】

ラウンド処理回路10は、位相同期回路30により生成された内部クロック信号に同期して作動するように構成される。ラウンド処理回路10は、ラウンド処理を、予め設定された反復回数だけ繰り返し実行することにより、暗号化処理回路1に入力された情報(平文)を暗号化する。ラウンド処理回路10は、内部クロック信号の立ち上がりエッジ(なお、立ち下がりエッジでもよい)が到来する毎に、ラウンド処理を1回だけ実行する。

【0020】

ラウンド処理回路10は、位相同期回路30が生成する内部クロック信号が、外部クロック信号と同期した時点以降の時点にて、ラウンド処理の実行を開始する。本例では、ラウンド処理回路10は、位相同期回路30に入力される外部クロック信号の立ち上がりエッジが到来した回数(エッジ到来回数)が、予め設定された待機回数に到達した時点にて、ラウンド処理の実行を開始する。

【0021】

ラウンド処理回路10は、レジスタ11と、変換処理回路12と、を備える。

変換処理回路12は、ラウンド処理を実行する。

具体的には、変換処理回路12は、1回目のラウンド処理においては、入力された平文を、変換処理の対象となる情報(変換処理対象情報)として取得する。変換処理回路12は、2回目以降のラウンド処理においては、レジスタ11に格納されている情報を変換処理対象情報として取得する。

【0022】

変換処理回路12には、鍵スケジュール処理回路20により生成された拡大鍵が入力される。変換処理回路12は、入力された拡大鍵に基づいて、取得された情報(変換処理対象情報)を、予め設定された方式に従って変換する(即ち、変換処理対象情報に対する変換処理を実行する)。変換処理回路12は、変換された情報をレジスタ11に格納する。

このようにして、変換処理回路12は、ラウンド処理を実行する。

【0023】

ラウンド処理回路10は、変換処理回路12によって、反復回数だけラウンド処理が実行された後、レジスタ11に格納されている情報を取得し、取得された情報を暗号化された情報(暗号文)として暗号化処理回路1の外部へ出力する。

【0024】

鍵スケジュール処理回路20は、拡大鍵生成回路21を備える。拡大鍵生成回路21は、予め記憶している鍵に基づいて、各ラウンド処理に対する拡大(拡張)鍵(ラウンド鍵)を生成する。本例では、拡大鍵生成回路21は、各ラウンド処理に対する拡大鍵が、互いに異なる情報となるように拡大鍵を生成する。そして、拡大鍵生成回路21は、生成された拡大鍵を変換処理回路12へ出力する。なお、拡大鍵生成回路21は、暗号化処理回路1の外部から鍵が入力されるように構成されていてもよい。

【0025】

(作動)

次に、上述した暗号化処理回路1の作動について説明する。

暗号化処理回路1は、図2にフローチャートにより示した処理を、暗号化処理回路1の起動時に実行するようになっている。

【0026】

具体的に述べると、暗号化処理回路1は、ステップS101にて、エッジ到来回数が待機回数に到達(一致)するまで待機する。そして、エッジ到来回数が待機回数に到達すると、暗号化処理回路1は、「Yes」と判定してステップS102へ進み、平文が入力されるまで待機する。

【0027】

次いで、暗号化処理回路1に平文が入力されると、暗号化処理回路1は、「Yes」と判定してステップS103へ進み、入力された平文を、1回目のラウンド処理における変換処理対象情報として取得する。

【0028】

そして、暗号化処理回路1は、予め記憶している鍵に基づいて、1回目のラウンド処理に対する拡大鍵を生成する(ステップS104)。次いで、暗号化処理回路1は、カウンタ値iを1に設定する(ステップS105)。

【0029】

そして、暗号化処理回路1は、ステップS104にて生成された拡大鍵に基づいて、ステップS103にて取得された変換処理対象情報に対する1回目の変換処理を実行する(ステップS106)。そして、暗号化処理回路1は、変換された情報をレジスタ11に格納する(ステップS107)。

なお、ステップS103、ステップS106及びステップS107の処理は、1回目のラウンド処理を構成している。

【0030】

次いで、暗号化処理回路1は、カウンタ値iが反復回数Nよりも小さいか否かを判定する(ステップS108)。いま、カウンタ値iが反復回数Nよりも小さい場合を想定する。この場合、暗号化処理回路1は、「Yes」と判定してステップS109へ進み、レジスタに格納されている情報を、i回目のラウンド処理における変換処理対象情報として取得する。

【0031】

そして、暗号化処理回路1は、予め記憶している鍵に基づいて、i回目のラウンド処理に対する拡大鍵を生成する(ステップS110)。次いで、暗号化処理回路1は、カウンタ値iに1を加算する(ステップS111)。

【0032】

そして、暗号化処理回路1は、ステップS110にて生成された拡大鍵に基づいて、ステップS109にて取得された変換処理対象情報に対するi回目の変換処理を実行する(ステップS112)。そして、暗号化処理回路1は、変換された情報をレジスタ11に格納する(ステップS113)。

なお、ステップS109、ステップS112及びステップS113の処理は、i回目のラウンド処理を構成している。

【0033】

その後、カウンタ値iが反復回数Nに到達(一致)すると、暗号化処理回路1は、ステップS108に進んだとき、「No」と判定してステップS114へ進む。そして、暗号化処理回路1は、レジスタに格納されている情報を、入力された平文が暗号化された情報(暗号文)として取得する。次いで、暗号化処理回路1は、取得された暗号文を、暗号化処理回路1の外部へ出力する。その後、暗号化処理回路1は、ステップS102へ戻る。

【0034】

以上、説明したように、本発明の第1実施形態に係る暗号化処理回路1によれば、暗号化処理回路1は、位相同期回路30により生成された内部クロック信号に同期してラウンド処理を繰り返し実行することにより、入力された情報を暗号化する。これにより、外部クロック信号の周期が変更された場合であっても、暗号化処理回路1に正常な処理を実行させることができる。この結果、外部クロック信号の周期が変更された場合であっても鍵が特定される可能性を低減することができる。

【0035】

更に、本発明の第1実施形態に係る暗号化処理回路1によれば、ラウンド処理回路10は、位相同期回路30が生成する内部クロック信号が、外部クロック信号と同期した時点以降の時点にて、ラウンド処理の実行を開始するように構成される。

【0036】

ところで、位相同期回路30は、フィードバック制御を行うことにより、外部クロック信号と同期した内部クロック信号を生成する。従って、位相同期回路30が生成する内部クロック信号が外部クロック信号と同期するまでには、所定の遅延時間(ロックアップタイム)を要する。そこで、上記のように暗号化処理回路1を構成することにより、暗号化処理回路1に、より一層確実に正常な処理を実行させることができる。

【0037】

<第2実施形態>

次に、本発明の第2実施形態に係る暗号化処理回路について説明する。第2実施形態に係る暗号化処理回路は、上記第1実施形態に係る暗号化処理回路に対して、外部クロック信号が異常であることが検出された場合、レジスタに格納されている情報を消去する点において相違している。従って、以下、かかる相違点を中心として説明する。

【0038】

第2実施形態に係る暗号化処理回路1は、図3に示したように、第1実施形態に係る暗号化処理回路1が備える構成に加えて、異常検出回路(異常検出手段)40を備える。異常検出回路40は、作動増幅回路41を備える。

【0039】

作動増幅回路41は、暗号化処理回路1の外部から暗号化処理回路1に入力される外部クロック信号と、位相同期回路30により生成される内部クロック信号と、の差を検出する。

【0040】

異常検出回路40は、作動増幅回路41により検出された差が、予め設定された閾値差よりも大きい場合に、外部クロック信号が異常であることを検出する。更に、異常検出回路40は、外部クロック信号が異常であることが検出された場合、レジスタ11に格納されている情報を消去する。

【0041】

ところで、外部クロック信号が異常である場合(例えば、外部クロック信号の周期が変更された場合等)、暗号化処理回路1が攻撃(フォールト攻撃、及び、サイドチャネル攻撃等)されている可能性が比較的高い。

【0042】

そこで、上記のように暗号化処理回路1を構成することにより、外部クロック信号が異常であることが検出された時点にて、暗号化処理回路1が入力された情報を暗号化する処理を実質的に中止することができる。この結果、鍵が特定される可能性をより一層低減することができる。

【0043】

<第3実施形態>

次に、本発明の第3実施形態に係る暗号化処理回路について図4を参照しながら説明する。

第3実施形態に係る暗号化処理回路100は、

レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する、ラウンド処理を実行することにより、入力された情報を暗号化する暗号化処理回路である。

【0044】

更に、この暗号化処理回路100は、

外部から外部クロック信号が入力され、フィードバック制御を行うことにより、当該入力された外部クロック信号と同期した内部クロック信号を生成する位相同期回路101と、

上記生成された内部クロック信号に同期して作動するように構成され、且つ、上記ラウンド処理を繰り返し実行することにより、上記入力された情報を暗号化するラウンド処理回路102と、

を備える。

【0045】

これによれば、暗号化処理回路100は、位相同期回路101により生成された内部クロック信号に同期してラウンド処理を繰り返し実行することにより、入力された情報を暗号化する。これにより、外部クロック信号の周期が変更された場合であっても、暗号化処理回路100に正常な処理を実行させることができる。この結果、外部クロック信号の周期が変更された場合であっても鍵が特定される可能性を低減することができる。

【0046】

以上、上記実施形態を参照して本願発明を説明したが、本願発明は、上述した実施形態に限定されるものではない。本願発明の構成及び詳細に、本願発明の範囲内において当業者が理解し得る様々な変更をすることができる。

【0047】

また、上記実施形態の他の変形例として、上述した実施形態及び変形例の任意の組み合わせが採用されてもよい。

【0048】

<付記>

上記実施形態の一部又は全部は、以下の付記のように記載され得るが、以下には限られない。

【0049】

(付記1)

レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する、ラウンド処理を実行することにより、入力された情報を暗号化する暗号化処理回路であって、

外部から外部クロック信号が入力され、フィードバック制御を行うことにより、当該入力された外部クロック信号と同期した内部クロック信号を生成する位相同期回路と、

前記生成された内部クロック信号に同期して作動するように構成され、且つ、前記ラウンド処理を繰り返し実行することにより、前記入力された情報を暗号化するラウンド処理回路と、

を備える暗号化処理回路。

【0050】

これによれば、暗号化処理回路は、位相同期回路により生成された内部クロック信号に同期してラウンド処理を繰り返し実行することにより、入力された情報を暗号化する。これにより、外部クロック信号の周期が変更された場合であっても、暗号化処理回路に正常な処理を実行させることができる。この結果、外部クロック信号の周期が変更された場合であっても鍵が特定される可能性を低減することができる。

【0051】

(付記2)

付記1に記載の暗号化処理回路であって、

前記ラウンド処理回路は、前記位相同期回路が生成する前記内部クロック信号が、前記外部クロック信号と同期した時点以降の時点にて、前記ラウンド処理の実行を開始するように構成された暗号化処理回路。

【0052】

ところで、位相同期回路は、フィードバック制御を行うことにより、外部クロック信号と同期した内部クロック信号を生成する。従って、位相同期回路が生成する内部クロック信号が外部クロック信号と同期するまでには、所定の遅延時間を要する。そこで、上記のように暗号化処理回路を構成することにより、暗号化処理回路に、より一層確実に正常な処理を実行させることができる。

【0053】

(付記3)

付記1又は付記2に記載の暗号化処理回路であって、

前記外部クロック信号が異常であることを検出する異常検出手段を備え、

前記外部クロック信号が異常であることが検出された場合、前記レジスタに格納されている情報を消去するように構成された暗号化処理回路。

【0054】

ところで、外部クロック信号が異常である場合(例えば、外部クロック信号の周期が変更された場合等)、暗号化処理回路が攻撃(フォールト攻撃、及び、サイドチャネル攻撃等)されている可能性が比較的高い。そこで、上記のように暗号化処理回路を構成することにより、外部クロック信号が異常であることが検出された時点にて、暗号化処理回路が入力された情報を暗号化する処理を実質的に中止することができる。この結果、鍵が特定される可能性をより一層低減することができる。

【0055】

(付記4)

付記3に記載の暗号化処理回路であって、

前記異常検出手段は、前記外部クロック信号と、前記内部クロック信号と、の差を検出する作動増幅回路を含むとともに、当該検出された差が、予め設定された閾値差よりも大きい場合に、当該外部クロック信号が異常であることを検出するように構成された暗号化処理回路。

【0056】

(付記5)

付記1乃至付記4のいずれか一項に記載の暗号化処理回路であって、

ブロック暗号方式に従って、前記入力された情報を暗号化するように構成された暗号化処理回路。

【0057】

(付記6)

レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する、ラウンド処理を実行することにより、入力された情報を暗号化する暗号化処理方法であって、

外部から外部クロック信号が入力され、フィードバック制御を行うことにより、当該入力された外部クロック信号と同期した内部クロック信号を生成し、

前記生成された内部クロック信号に同期して作動することによって、前記ラウンド処理を繰り返し実行することにより、前記入力された情報を暗号化する、暗号化処理方法。

【0058】

(付記7)

付記6に記載の暗号化処理方法であって、

前記内部クロック信号が前記外部クロック信号と同期した時点以降の時点にて、前記ラウンド処理の実行を開始する、暗号化処理方法。

【0059】

(付記8)

付記6又は付記7に記載の暗号化処理方法であって、

前記外部クロック信号が異常であることを検出し、

前記外部クロック信号が異常であることが検出された場合、前記レジスタに格納されている情報を消去する、暗号化処理方法。

【産業上の利用可能性】

【0060】

本発明は、ラウンド処理を実行することにより情報を暗号化する暗号化処理回路等に適用可能である。

【符号の説明】

【0061】

1 暗号化処理回路

10 ラウンド処理回路

11 レジスタ

12 変換処理回路

20 鍵スケジュール処理回路

21 拡大鍵生成回路

30 位相同期回路

40 異常検出回路

41 作動増幅回路

100 暗号化処理回路

101 位相同期回路

102 ラウンド処理回路

【技術分野】

【0001】

本発明は、ラウンド処理を実行することにより情報を暗号化する暗号化処理回路に関する。

【背景技術】

【0002】

ラウンド処理を実行することにより情報を暗号化する暗号化処理回路が知られている。この種の暗号化処理回路の一つとして、特許文献1に記載の暗号化処理回路は、外部クロック信号に同期してラウンド処理を繰り返し実行することにより、入力された情報を暗号化する。ラウンド処理は、レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する処理である。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−245753号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、レジスタに格納するために当該レジスタに入力される情報が、予め設定されたデータ維持要求期間内に変更された場合を想定する。ここで、データ維持要求期間は、外部クロック信号の立ち上がりエッジ(又は、立ち下がりエッジ)よりもセットアップタイムだけ前の時点から、当該エッジよりもホールドタイムだけ後の時点までの期間である。この場合、レジスタに格納される情報が、変更前の情報であるか、変更後の情報であるか、が保証されなくなる。

【0005】

そこで、ラウンド処理の実行結果を表す情報がレジスタに入力される際に、外部クロック信号の周期を短くすることにより、暗号化処理回路に異常な処理を実行させることができる。また、暗号化処理回路が異常な処理を実行した場合における、暗号化された情報と、暗号化処理回路が正常な処理を実行した場合における、暗号化された情報と、の差を表す情報に基づいて(即ち、フォールト攻撃によって)、鍵を特定できる場合があることが知られている。

【0006】

このように、上記暗号化処理回路においては、外部クロック信号の周期が変更されることにより鍵が特定されてしまう虞があった。

【0007】

このため、本発明の目的は、上述した課題である「外部クロック信号の周期が変更されることにより鍵が特定されてしまう場合が生じること」を解決することが可能な暗号化処理回路を提供することにある。

【課題を解決するための手段】

【0008】

かかる目的を達成するため本発明の一形態である暗号化処理回路は、

レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する、ラウンド処理を実行することにより、入力された情報を暗号化する暗号化処理回路である。

【0009】

更に、この暗号化処理回路は、

外部から外部クロック信号が入力され、フィードバック制御を行うことにより、当該入力された外部クロック信号と同期した内部クロック信号を生成する位相同期回路と、

上記生成された内部クロック信号に同期して作動するように構成され、且つ、上記ラウンド処理を繰り返し実行することにより、上記入力された情報を暗号化するラウンド処理回路と、

を備える。

【0010】

また、本発明の他の形態である暗号化処理方法は、

レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する、ラウンド処理を実行することにより、入力された情報を暗号化する方法である。

【0011】

更に、この暗号化処理方法は、

外部から外部クロック信号が入力され、フィードバック制御を行うことにより、当該入力された外部クロック信号と同期した内部クロック信号を生成し、

上記生成された内部クロック信号に同期して作動することによって、上記ラウンド処理を繰り返し実行することにより、上記入力された情報を暗号化する方法である。

【発明の効果】

【0012】

本発明は、以上のように構成されることにより、外部クロック信号の周期が変更された場合であっても鍵が特定される可能性を低減することができる。

【図面の簡単な説明】

【0013】

【図1】本発明の第1実施形態に係る暗号化処理回路の概略構成を表す図である。

【図2】本発明の第1実施形態に係る暗号化処理回路が実行する処理を示したフローチャートである。

【図3】本発明の第2実施形態に係る暗号化処理回路の概略構成を表す図である。

【図4】本発明の第3実施形態に係る暗号化処理回路の概略構成を表す図である。

【発明を実施するための形態】

【0014】

以下、本発明に係る、暗号化処理回路、及び、暗号化処理方法、の各実施形態について図1〜図4を参照しながら説明する。

【0015】

<第1実施形態>

(構成)

図1に示したように、第1実施形態に係る暗号化処理回路1は、集積回路である。暗号化処理回路1には、暗号化処理回路1の外部から情報(平文)が入力される。暗号化処理回路1は、入力された情報を鍵(としての情報)に基づいて暗号化する。そして、暗号化処理回路1は、暗号化された情報(暗号文)を暗号化処理回路1の外部へ出力する。

【0016】

本例では、暗号化処理回路1は、共通鍵暗号方式の1つであるAES(Advanced Encryption Standard)暗号方式に従って、入力された情報を暗号化する。AES暗号方式は、ブロック暗号方式の1つである。なお、暗号化処理回路1は、DES(Data Encryption Standard)暗号方式等の他の暗号方式に従って、入力された情報を暗号化するように構成されていてもよい。

【0017】

暗号化処理回路1は、ラウンド処理回路10と、鍵スケジュール処理回路20と、位相同期回路(PLL;Phase Locked Loop)30と、を備える。

【0018】

位相同期回路30には、暗号化処理回路1の外部からクロック信号(外部クロック信号)が入力される。位相同期回路30は、フィードバック制御を行うことにより、入力された外部クロック信号と同期したクロック信号(内部クロック信号)を生成する。位相同期回路30は、生成した内部クロック信号を、ラウンド処理回路10及び鍵スケジュール処理回路20のそれぞれへ出力(供給)する。

【0019】

ラウンド処理回路10は、位相同期回路30により生成された内部クロック信号に同期して作動するように構成される。ラウンド処理回路10は、ラウンド処理を、予め設定された反復回数だけ繰り返し実行することにより、暗号化処理回路1に入力された情報(平文)を暗号化する。ラウンド処理回路10は、内部クロック信号の立ち上がりエッジ(なお、立ち下がりエッジでもよい)が到来する毎に、ラウンド処理を1回だけ実行する。

【0020】

ラウンド処理回路10は、位相同期回路30が生成する内部クロック信号が、外部クロック信号と同期した時点以降の時点にて、ラウンド処理の実行を開始する。本例では、ラウンド処理回路10は、位相同期回路30に入力される外部クロック信号の立ち上がりエッジが到来した回数(エッジ到来回数)が、予め設定された待機回数に到達した時点にて、ラウンド処理の実行を開始する。

【0021】

ラウンド処理回路10は、レジスタ11と、変換処理回路12と、を備える。

変換処理回路12は、ラウンド処理を実行する。

具体的には、変換処理回路12は、1回目のラウンド処理においては、入力された平文を、変換処理の対象となる情報(変換処理対象情報)として取得する。変換処理回路12は、2回目以降のラウンド処理においては、レジスタ11に格納されている情報を変換処理対象情報として取得する。

【0022】

変換処理回路12には、鍵スケジュール処理回路20により生成された拡大鍵が入力される。変換処理回路12は、入力された拡大鍵に基づいて、取得された情報(変換処理対象情報)を、予め設定された方式に従って変換する(即ち、変換処理対象情報に対する変換処理を実行する)。変換処理回路12は、変換された情報をレジスタ11に格納する。

このようにして、変換処理回路12は、ラウンド処理を実行する。

【0023】

ラウンド処理回路10は、変換処理回路12によって、反復回数だけラウンド処理が実行された後、レジスタ11に格納されている情報を取得し、取得された情報を暗号化された情報(暗号文)として暗号化処理回路1の外部へ出力する。

【0024】

鍵スケジュール処理回路20は、拡大鍵生成回路21を備える。拡大鍵生成回路21は、予め記憶している鍵に基づいて、各ラウンド処理に対する拡大(拡張)鍵(ラウンド鍵)を生成する。本例では、拡大鍵生成回路21は、各ラウンド処理に対する拡大鍵が、互いに異なる情報となるように拡大鍵を生成する。そして、拡大鍵生成回路21は、生成された拡大鍵を変換処理回路12へ出力する。なお、拡大鍵生成回路21は、暗号化処理回路1の外部から鍵が入力されるように構成されていてもよい。

【0025】

(作動)

次に、上述した暗号化処理回路1の作動について説明する。

暗号化処理回路1は、図2にフローチャートにより示した処理を、暗号化処理回路1の起動時に実行するようになっている。

【0026】

具体的に述べると、暗号化処理回路1は、ステップS101にて、エッジ到来回数が待機回数に到達(一致)するまで待機する。そして、エッジ到来回数が待機回数に到達すると、暗号化処理回路1は、「Yes」と判定してステップS102へ進み、平文が入力されるまで待機する。

【0027】

次いで、暗号化処理回路1に平文が入力されると、暗号化処理回路1は、「Yes」と判定してステップS103へ進み、入力された平文を、1回目のラウンド処理における変換処理対象情報として取得する。

【0028】

そして、暗号化処理回路1は、予め記憶している鍵に基づいて、1回目のラウンド処理に対する拡大鍵を生成する(ステップS104)。次いで、暗号化処理回路1は、カウンタ値iを1に設定する(ステップS105)。

【0029】

そして、暗号化処理回路1は、ステップS104にて生成された拡大鍵に基づいて、ステップS103にて取得された変換処理対象情報に対する1回目の変換処理を実行する(ステップS106)。そして、暗号化処理回路1は、変換された情報をレジスタ11に格納する(ステップS107)。

なお、ステップS103、ステップS106及びステップS107の処理は、1回目のラウンド処理を構成している。

【0030】

次いで、暗号化処理回路1は、カウンタ値iが反復回数Nよりも小さいか否かを判定する(ステップS108)。いま、カウンタ値iが反復回数Nよりも小さい場合を想定する。この場合、暗号化処理回路1は、「Yes」と判定してステップS109へ進み、レジスタに格納されている情報を、i回目のラウンド処理における変換処理対象情報として取得する。

【0031】

そして、暗号化処理回路1は、予め記憶している鍵に基づいて、i回目のラウンド処理に対する拡大鍵を生成する(ステップS110)。次いで、暗号化処理回路1は、カウンタ値iに1を加算する(ステップS111)。

【0032】

そして、暗号化処理回路1は、ステップS110にて生成された拡大鍵に基づいて、ステップS109にて取得された変換処理対象情報に対するi回目の変換処理を実行する(ステップS112)。そして、暗号化処理回路1は、変換された情報をレジスタ11に格納する(ステップS113)。

なお、ステップS109、ステップS112及びステップS113の処理は、i回目のラウンド処理を構成している。

【0033】

その後、カウンタ値iが反復回数Nに到達(一致)すると、暗号化処理回路1は、ステップS108に進んだとき、「No」と判定してステップS114へ進む。そして、暗号化処理回路1は、レジスタに格納されている情報を、入力された平文が暗号化された情報(暗号文)として取得する。次いで、暗号化処理回路1は、取得された暗号文を、暗号化処理回路1の外部へ出力する。その後、暗号化処理回路1は、ステップS102へ戻る。

【0034】

以上、説明したように、本発明の第1実施形態に係る暗号化処理回路1によれば、暗号化処理回路1は、位相同期回路30により生成された内部クロック信号に同期してラウンド処理を繰り返し実行することにより、入力された情報を暗号化する。これにより、外部クロック信号の周期が変更された場合であっても、暗号化処理回路1に正常な処理を実行させることができる。この結果、外部クロック信号の周期が変更された場合であっても鍵が特定される可能性を低減することができる。

【0035】

更に、本発明の第1実施形態に係る暗号化処理回路1によれば、ラウンド処理回路10は、位相同期回路30が生成する内部クロック信号が、外部クロック信号と同期した時点以降の時点にて、ラウンド処理の実行を開始するように構成される。

【0036】

ところで、位相同期回路30は、フィードバック制御を行うことにより、外部クロック信号と同期した内部クロック信号を生成する。従って、位相同期回路30が生成する内部クロック信号が外部クロック信号と同期するまでには、所定の遅延時間(ロックアップタイム)を要する。そこで、上記のように暗号化処理回路1を構成することにより、暗号化処理回路1に、より一層確実に正常な処理を実行させることができる。

【0037】

<第2実施形態>

次に、本発明の第2実施形態に係る暗号化処理回路について説明する。第2実施形態に係る暗号化処理回路は、上記第1実施形態に係る暗号化処理回路に対して、外部クロック信号が異常であることが検出された場合、レジスタに格納されている情報を消去する点において相違している。従って、以下、かかる相違点を中心として説明する。

【0038】

第2実施形態に係る暗号化処理回路1は、図3に示したように、第1実施形態に係る暗号化処理回路1が備える構成に加えて、異常検出回路(異常検出手段)40を備える。異常検出回路40は、作動増幅回路41を備える。

【0039】

作動増幅回路41は、暗号化処理回路1の外部から暗号化処理回路1に入力される外部クロック信号と、位相同期回路30により生成される内部クロック信号と、の差を検出する。

【0040】

異常検出回路40は、作動増幅回路41により検出された差が、予め設定された閾値差よりも大きい場合に、外部クロック信号が異常であることを検出する。更に、異常検出回路40は、外部クロック信号が異常であることが検出された場合、レジスタ11に格納されている情報を消去する。

【0041】

ところで、外部クロック信号が異常である場合(例えば、外部クロック信号の周期が変更された場合等)、暗号化処理回路1が攻撃(フォールト攻撃、及び、サイドチャネル攻撃等)されている可能性が比較的高い。

【0042】

そこで、上記のように暗号化処理回路1を構成することにより、外部クロック信号が異常であることが検出された時点にて、暗号化処理回路1が入力された情報を暗号化する処理を実質的に中止することができる。この結果、鍵が特定される可能性をより一層低減することができる。

【0043】

<第3実施形態>

次に、本発明の第3実施形態に係る暗号化処理回路について図4を参照しながら説明する。

第3実施形態に係る暗号化処理回路100は、

レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する、ラウンド処理を実行することにより、入力された情報を暗号化する暗号化処理回路である。

【0044】

更に、この暗号化処理回路100は、

外部から外部クロック信号が入力され、フィードバック制御を行うことにより、当該入力された外部クロック信号と同期した内部クロック信号を生成する位相同期回路101と、

上記生成された内部クロック信号に同期して作動するように構成され、且つ、上記ラウンド処理を繰り返し実行することにより、上記入力された情報を暗号化するラウンド処理回路102と、

を備える。

【0045】

これによれば、暗号化処理回路100は、位相同期回路101により生成された内部クロック信号に同期してラウンド処理を繰り返し実行することにより、入力された情報を暗号化する。これにより、外部クロック信号の周期が変更された場合であっても、暗号化処理回路100に正常な処理を実行させることができる。この結果、外部クロック信号の周期が変更された場合であっても鍵が特定される可能性を低減することができる。

【0046】

以上、上記実施形態を参照して本願発明を説明したが、本願発明は、上述した実施形態に限定されるものではない。本願発明の構成及び詳細に、本願発明の範囲内において当業者が理解し得る様々な変更をすることができる。

【0047】

また、上記実施形態の他の変形例として、上述した実施形態及び変形例の任意の組み合わせが採用されてもよい。

【0048】

<付記>

上記実施形態の一部又は全部は、以下の付記のように記載され得るが、以下には限られない。

【0049】

(付記1)

レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する、ラウンド処理を実行することにより、入力された情報を暗号化する暗号化処理回路であって、

外部から外部クロック信号が入力され、フィードバック制御を行うことにより、当該入力された外部クロック信号と同期した内部クロック信号を生成する位相同期回路と、

前記生成された内部クロック信号に同期して作動するように構成され、且つ、前記ラウンド処理を繰り返し実行することにより、前記入力された情報を暗号化するラウンド処理回路と、

を備える暗号化処理回路。

【0050】

これによれば、暗号化処理回路は、位相同期回路により生成された内部クロック信号に同期してラウンド処理を繰り返し実行することにより、入力された情報を暗号化する。これにより、外部クロック信号の周期が変更された場合であっても、暗号化処理回路に正常な処理を実行させることができる。この結果、外部クロック信号の周期が変更された場合であっても鍵が特定される可能性を低減することができる。

【0051】

(付記2)

付記1に記載の暗号化処理回路であって、

前記ラウンド処理回路は、前記位相同期回路が生成する前記内部クロック信号が、前記外部クロック信号と同期した時点以降の時点にて、前記ラウンド処理の実行を開始するように構成された暗号化処理回路。

【0052】

ところで、位相同期回路は、フィードバック制御を行うことにより、外部クロック信号と同期した内部クロック信号を生成する。従って、位相同期回路が生成する内部クロック信号が外部クロック信号と同期するまでには、所定の遅延時間を要する。そこで、上記のように暗号化処理回路を構成することにより、暗号化処理回路に、より一層確実に正常な処理を実行させることができる。

【0053】

(付記3)

付記1又は付記2に記載の暗号化処理回路であって、

前記外部クロック信号が異常であることを検出する異常検出手段を備え、

前記外部クロック信号が異常であることが検出された場合、前記レジスタに格納されている情報を消去するように構成された暗号化処理回路。

【0054】

ところで、外部クロック信号が異常である場合(例えば、外部クロック信号の周期が変更された場合等)、暗号化処理回路が攻撃(フォールト攻撃、及び、サイドチャネル攻撃等)されている可能性が比較的高い。そこで、上記のように暗号化処理回路を構成することにより、外部クロック信号が異常であることが検出された時点にて、暗号化処理回路が入力された情報を暗号化する処理を実質的に中止することができる。この結果、鍵が特定される可能性をより一層低減することができる。

【0055】

(付記4)

付記3に記載の暗号化処理回路であって、

前記異常検出手段は、前記外部クロック信号と、前記内部クロック信号と、の差を検出する作動増幅回路を含むとともに、当該検出された差が、予め設定された閾値差よりも大きい場合に、当該外部クロック信号が異常であることを検出するように構成された暗号化処理回路。

【0056】

(付記5)

付記1乃至付記4のいずれか一項に記載の暗号化処理回路であって、

ブロック暗号方式に従って、前記入力された情報を暗号化するように構成された暗号化処理回路。

【0057】

(付記6)

レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する、ラウンド処理を実行することにより、入力された情報を暗号化する暗号化処理方法であって、

外部から外部クロック信号が入力され、フィードバック制御を行うことにより、当該入力された外部クロック信号と同期した内部クロック信号を生成し、

前記生成された内部クロック信号に同期して作動することによって、前記ラウンド処理を繰り返し実行することにより、前記入力された情報を暗号化する、暗号化処理方法。

【0058】

(付記7)

付記6に記載の暗号化処理方法であって、

前記内部クロック信号が前記外部クロック信号と同期した時点以降の時点にて、前記ラウンド処理の実行を開始する、暗号化処理方法。

【0059】

(付記8)

付記6又は付記7に記載の暗号化処理方法であって、

前記外部クロック信号が異常であることを検出し、

前記外部クロック信号が異常であることが検出された場合、前記レジスタに格納されている情報を消去する、暗号化処理方法。

【産業上の利用可能性】

【0060】

本発明は、ラウンド処理を実行することにより情報を暗号化する暗号化処理回路等に適用可能である。

【符号の説明】

【0061】

1 暗号化処理回路

10 ラウンド処理回路

11 レジスタ

12 変換処理回路

20 鍵スケジュール処理回路

21 拡大鍵生成回路

30 位相同期回路

40 異常検出回路

41 作動増幅回路

100 暗号化処理回路

101 位相同期回路

102 ラウンド処理回路

【特許請求の範囲】

【請求項1】

レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する、ラウンド処理を実行することにより、入力された情報を暗号化する暗号化処理回路であって、

外部から外部クロック信号が入力され、フィードバック制御を行うことにより、当該入力された外部クロック信号と同期した内部クロック信号を生成する位相同期回路と、

前記生成された内部クロック信号に同期して作動するように構成され、且つ、前記ラウンド処理を繰り返し実行することにより、前記入力された情報を暗号化するラウンド処理回路と、

を備える暗号化処理回路。

【請求項2】

請求項1に記載の暗号化処理回路であって、

前記ラウンド処理回路は、前記位相同期回路が生成する前記内部クロック信号が、前記外部クロック信号と同期した時点以降の時点にて、前記ラウンド処理の実行を開始するように構成された暗号化処理回路。

【請求項3】

請求項1又は請求項2に記載の暗号化処理回路であって、

前記外部クロック信号が異常であることを検出する異常検出手段を備え、

前記外部クロック信号が異常であることが検出された場合、前記レジスタに格納されている情報を消去するように構成された暗号化処理回路。

【請求項4】

請求項3に記載の暗号化処理回路であって、

前記異常検出手段は、前記外部クロック信号と、前記内部クロック信号と、の差を検出する作動増幅回路を含むとともに、当該検出された差が、予め設定された閾値差よりも大きい場合に、当該外部クロック信号が異常であることを検出するように構成された暗号化処理回路。

【請求項5】

請求項1乃至請求項4のいずれか一項に記載の暗号化処理回路であって、

ブロック暗号方式に従って、前記入力された情報を暗号化するように構成された暗号化処理回路。

【請求項6】

レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する、ラウンド処理を実行することにより、入力された情報を暗号化する暗号化処理方法であって、

外部から外部クロック信号が入力され、フィードバック制御を行うことにより、当該入力された外部クロック信号と同期した内部クロック信号を生成し、

前記生成された内部クロック信号に同期して作動することによって、前記ラウンド処理を繰り返し実行することにより、前記入力された情報を暗号化する、暗号化処理方法。

【請求項7】

請求項6に記載の暗号化処理方法であって、

前記内部クロック信号が前記外部クロック信号と同期した時点以降の時点にて、前記ラウンド処理の実行を開始する、暗号化処理方法。

【請求項8】

請求項6又は請求項7に記載の暗号化処理方法であって、

前記外部クロック信号が異常であることを検出し、

前記外部クロック信号が異常であることが検出された場合、前記レジスタに格納されている情報を消去する、暗号化処理方法。

【請求項1】

レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する、ラウンド処理を実行することにより、入力された情報を暗号化する暗号化処理回路であって、

外部から外部クロック信号が入力され、フィードバック制御を行うことにより、当該入力された外部クロック信号と同期した内部クロック信号を生成する位相同期回路と、

前記生成された内部クロック信号に同期して作動するように構成され、且つ、前記ラウンド処理を繰り返し実行することにより、前記入力された情報を暗号化するラウンド処理回路と、

を備える暗号化処理回路。

【請求項2】

請求項1に記載の暗号化処理回路であって、

前記ラウンド処理回路は、前記位相同期回路が生成する前記内部クロック信号が、前記外部クロック信号と同期した時点以降の時点にて、前記ラウンド処理の実行を開始するように構成された暗号化処理回路。

【請求項3】

請求項1又は請求項2に記載の暗号化処理回路であって、

前記外部クロック信号が異常であることを検出する異常検出手段を備え、

前記外部クロック信号が異常であることが検出された場合、前記レジスタに格納されている情報を消去するように構成された暗号化処理回路。

【請求項4】

請求項3に記載の暗号化処理回路であって、

前記異常検出手段は、前記外部クロック信号と、前記内部クロック信号と、の差を検出する作動増幅回路を含むとともに、当該検出された差が、予め設定された閾値差よりも大きい場合に、当該外部クロック信号が異常であることを検出するように構成された暗号化処理回路。

【請求項5】

請求項1乃至請求項4のいずれか一項に記載の暗号化処理回路であって、

ブロック暗号方式に従って、前記入力された情報を暗号化するように構成された暗号化処理回路。

【請求項6】

レジスタに格納されている情報を取得し、当該取得された情報を予め設定された方式に従って鍵に基づいて変換し、当該変換された情報を当該レジスタに格納する、ラウンド処理を実行することにより、入力された情報を暗号化する暗号化処理方法であって、

外部から外部クロック信号が入力され、フィードバック制御を行うことにより、当該入力された外部クロック信号と同期した内部クロック信号を生成し、

前記生成された内部クロック信号に同期して作動することによって、前記ラウンド処理を繰り返し実行することにより、前記入力された情報を暗号化する、暗号化処理方法。

【請求項7】

請求項6に記載の暗号化処理方法であって、

前記内部クロック信号が前記外部クロック信号と同期した時点以降の時点にて、前記ラウンド処理の実行を開始する、暗号化処理方法。

【請求項8】

請求項6又は請求項7に記載の暗号化処理方法であって、

前記外部クロック信号が異常であることを検出し、

前記外部クロック信号が異常であることが検出された場合、前記レジスタに格納されている情報を消去する、暗号化処理方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2012−169721(P2012−169721A)

【公開日】平成24年9月6日(2012.9.6)

【国際特許分類】

【出願番号】特願2011−26734(P2011−26734)

【出願日】平成23年2月10日(2011.2.10)

【出願人】(000242666)北陸日本電気ソフトウェア株式会社 (11)

【Fターム(参考)】

【公開日】平成24年9月6日(2012.9.6)

【国際特許分類】

【出願日】平成23年2月10日(2011.2.10)

【出願人】(000242666)北陸日本電気ソフトウェア株式会社 (11)

【Fターム(参考)】

[ Back to top ]