暗号機能を実行するための装置及び方法

【課題】ハードウェアのリバースエンジニアリングを十分に困難にする高度なセキュリティを提供する一方で、ハードウェア内でデジタル暗号アルゴリズムを実現する方法及び装置を提供する。

【解決手段】少なくとも1つの第1のデジタル値(XD)を少なくとも1つの第1のアナログ値(XA)に変換するステップと、少なくとも1つの第2のデジタル値(KD)を少なくとも1つのアナログ鍵値(KA)に変換するステップと、少なくとも1つの第1のアナログ値(XA)及び前記少なくとも1つのアナログ鍵値(KA)上で、少なくとも1つのアナログ出力値(RA)を与えるためにアナログ機能(F)を実行するステップと、デジタル暗号機能の前記実行結果を表わすデジタル出力値(RD)を与えるためにアナログ出力値(RA)を変換するステップとを含む。

【解決手段】少なくとも1つの第1のデジタル値(XD)を少なくとも1つの第1のアナログ値(XA)に変換するステップと、少なくとも1つの第2のデジタル値(KD)を少なくとも1つのアナログ鍵値(KA)に変換するステップと、少なくとも1つの第1のアナログ値(XA)及び前記少なくとも1つのアナログ鍵値(KA)上で、少なくとも1つのアナログ出力値(RA)を与えるためにアナログ機能(F)を実行するステップと、デジタル暗号機能の前記実行結果を表わすデジタル出力値(RD)を与えるためにアナログ出力値(RA)を変換するステップとを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、コンピュータを用いて伝送された情報の暗号化及び復号化の分野に関する。特に、本発明は、暗号化されたデジタル情報を与えるための鍵の下でのデジタル情報の暗号化と、暗号化されたデジタル情報の対象とする受信者による更なる復号化に関わる。

【背景技術】

【0002】

昨今では、デジタル電子情報の暗号化及び復号化は一般的であり、銀行業務、ソフトウェア保護、データ保護、デジタル著作権管理、機密情報の伝送が保証されるべき電気通信、及び特に高価値のコンテンツの伝送を伴っている放送の分野で容易に見出すことができる。

【0003】

大部分の暗号アルゴリズムは、鍵共有プロトコルを利用しており、暗号化された情報の送信者及び受信者は、鍵を共有する。同一の鍵が暗号化及び復号化するために利用される場合、鍵は対称性を有することができる。対称鍵技術は、容易に計算可能な方法で相関させた異なる鍵の利用もカバーする。一方、非対称暗号鍵技術において、公開鍵は、暗号化するために利用され、秘密鍵は、公開鍵とは異なり、復号化するために利用される。そのようなアルゴリズムは、例えば、DES、RSAもしくはディフィーヘルマン鍵交換プロトコル(Diffie-Hellman Key Exchange Protocol)等のような標準規格、又は米商務省標準技術局(NIST:National Institute for Standards and Technology)により推奨されたような次世代標準暗号化方式(AES:Advanced Encryption Standard)等のような他の標準規格に記述されている。これらのタイプのアルゴリズムにおいて利用される暗号化の耐力は、特定のアルゴリズムがどの程度利用されるか、及び鍵の秘密が保たれるという前提で利用される鍵の長さ及び型に依存する。

【0004】

技術分野で述べたように、本発明の分野は、デジタル情報の暗号化及び復号化である。しかしながら、本発明はアナログ電子情報処理技術を含んでいるので、最先端技術の記述にアナログ暗号化/復号化技術を含むことは適切である。

【0005】

アナログ暗号化技術は、音声符号化の目的のために、通信工学の分野及び電話工学の分野において一般に使用される。現在使われている技術は、時間領域又は周波数領域のいずれかでスクランブルすることを含んでいる。

【0006】

スクランブリングの代わりに、他の技術もアナログ暗号化において利用されている。例えば、特許文献1には、それによって暗号化されるアナログ信号の一部が分離されて変調信号と組み合わされる、アナログ暗号化技術が記載されている。変調信号は、暗号化されたアナログ信号を与えるためにオリジナルのアナログ信号と組み合わされる。

【0007】

デジタル領域内の暗号化を実行してその結果を状況に応じてアナログ領域に再変換する前に、アナログ信号がまずサンプリングされてデジタル領域に変換される、混合モード(Mixed-mode)の暗号化技術が存在する。特許文献2には、それによってアナログ入力信号がデジタル入力信号に変換される、電話通信の暗号化に対する広く認められた取り組みが記載されている。デジタル入力信号は、デジタル鍵の下で暗号化され、その結果として生じる暗号化されたデジタル入力信号は、アナログ入力信号を表現したアナログ出力信号に再変換される。

【0008】

特許文献3には、リアルタイムの音声通信を保証するために、音声信号の暗号化/復号化のための混合モードの方法及び装置が記載されている。アナログ音声信号は、デジタル音声信号に変換され、その後、既知の手段を利用して、暗号化/スクランブルされる。リアルタイムにサンプリングされる音声信号(又はその遅延バージョン)は、暗号化/スクランブルされた音声信号に追加される。

【0009】

特許文献4には、デジタルの音声信号及び映像信号を受信し、アナログ領域内の信号を処理することを可能にするためのデジタル/アナログ変換器を含む音声入力インタフェースが記載されている。特許文献4では、既に上述した文献のように、同一のコンテキストでアナログ復号化が説明されている。

【0010】

特許文献5には、アナログデータを暗号化するための装置及び方法が記載されている。これによると、デジタル領域とアナログ領域との間の変換は、利用されない。アナログ信号を取得し、取得したアナログ信号を変調信号に組み合わせる回路が記載されている。

【0011】

従って、最先端技術の暗号化技術は、業界基準の鍵共有アルゴリズムを利用して、デジタル情報を暗号化し復号化することを可能にし、又は業界基準の同じ技術を利用して、次にアナログ情報を暗号化し復号化することができるデジタル情報に変換することを可能にする。アナログ情報のための最先端技術の暗号化技術も存在する。しかし、そのような技術により与えられた暗号化は、デジタル暗号化程安全ではないと一般に見なされている。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】米国特許第7545929号明細書

【特許文献2】米国特許出願公開第2001/0021252号明細書

【特許文献3】国際特許出願公開第2007/120006号パンフレット

【特許文献4】米国特許公開第7647615号明細書

【特許文献5】米国特許公開第7545929号明細書

【発明の概要】

【発明が解決しようとする課題】

【0013】

電子暗号手法の分野において、デジタルハードウェア内で実行された暗号アルゴリズムを解析して模倣(リバースエンジニアリング)し、ソフトウェア(それは第三者が、暗号アルゴリズムを利用して、暗号化された情報にアクセスすることを可能にするハードウェア暗号アルゴリズムを回避するために利用されてもよい)内にそのアルゴリズムのエミュレーションを組み込むことは第三者にとって通常可能である。本発明の目的の1つは、現在の最先端技術の暗号化ハードウェアと比較してハードウェアのリバースエンジニアリングを十分に困難にする高度なセキュリティを提供する一方で、ハードウェア内でデジタル暗号アルゴリズムを実現する新しい方法及び装置を提供することである。

【課題を解決するための手段】

【0014】

従って、本発明は、暗号鍵の発見により、又はその逆に暗号アルゴリズムを回避することにより、情報を復号化することができる、本発明により暗号化された情報の意図しない受信者の可能性を最小限にすることを追求する。

【0015】

この目的は、少なくとも1つの第1のデジタル値(XD)及び少なくとも1つの第2のデジタル値(KD)上でデジタル暗号機能を実行する方法を利用して達成され、前記デジタル暗号機能は少なくとも1つのデジタル結果を有しており、本方法は、

a)前記少なくとも1つの第1のデジタル値(XD)を少なくとも1つの第1のアナログ値(XA)に変換するステップと、

b)前記少なくとも1つの第2のデジタル値(KD)を少なくとも1つのアナログ鍵値(KA)に変換するステップと、

c)前記少なくとも1つの第1のアナログ値(XA)及び前記少なくとも1つのアナログ鍵値(KA)上で、少なくとも1つのアナログ出力値(RA)を与えるためにアナログ機能(F)を実行するステップと、

d)前記デジタル暗号機能の前記結果を表わすデジタル出力値(RD)を与えるために前記アナログ出力値(RA)を変換するステップと、

を含むことを特徴とする方法である。

【0016】

本発明は、少なくとも1つの第2のデジタル値(KD)を用いて少なくとも1つの第1のデジタル値(XD)上で上記方法によるデジタル暗号機能を実行するための装置を更に提供するものであり、前記デジタル暗号機能は少なくとも1つのデジタル結果を有しており、本装置は、

前記少なくとも1つの第1のデジタル値(XD)を少なくとも1つの第1のアナログ値(XA)に変換する手段と、

前記少なくとも1つの第2のデジタル値(KSD)を少なくとも1つのアナログ鍵値(KA)に変換する手段と、

アナログ結果(RA)を与えるために前記第1のアナログ値及び前記アナログ鍵値上でアナログ機能(F)を実行する手段と、

前記デジタル暗号機能の前記結果を表わすデジタル出力値(RD)を与えるために前記アナログ結果をデジタル値に変換する手段と、

を備えることを特徴とする装置である。

【発明の効果】

【0017】

従って、第三者が、実現された暗号機能のソフトウエアエミュレータをデジタルハードウェア内に組み込むことを防止するという課題は、暗号化アルゴリズムと復号化アルゴリズムを構成するための混合モードのデジタル/アナログハードウェア技術を提供することにより解決される。

【図面の簡単な説明】

【0018】

本発明は、以上の発明の詳細な説明、及び以下の添付の図面(本発明の実施形態の非限定的な例として示される)により一層よく理解されるであろう。

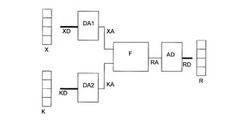

【図1】本発明の実施形態により展開される暗号化システムの一部のブロック図を示す。

【図2】図1に記載の暗号化システムの一部の他の実施形態を示す。

【図3】図1に記載の暗号化システムの一部の他の実施形態を示す。

【図4】図1に記載の暗号化システムの一部の他の実施形態を示す。

【図5】図1に記載の暗号化システムの一部の他の実施形態を示す。

【図6】図1に記載の暗号化システムの一部の他の実施形態を示す。

【図7】本発明の実施形態により展開される復号化システムの一部のブロック図を示す。

【発明を実施するための形態】

【0019】

本発明の実施形態は、暗号化又は復号化された出力を与えるために第2の値下の第1の値上で暗号機能を実行するためのシステム内で展開することができる。

図1は、その中で本発明の実施形態が展開される、デジタル情報を暗号化(又は復号化)するためのシステムの一部の概略図を示している。この概略図に示されるブロックは、暗号化(又は復号化)される入力としての第1のデジタル値(XD)と、暗号化(又は復号化)の鍵として第2のデジタル値(KD)とを得て、出力として暗号化(又は復号化)されたデジタル値(RD)を与える。従って、言いかえれば、このブロックは、デジタル結果(RD)を出力するために第1のデジタルオペランド(XD)及び第2のデジタルオペランド(KD)上でデジタル暗号機能を実行する。

【0020】

本発明の実施形態によれば、第1のデジタル値(XD)は、第1のデジタル/アナログ変換器(DA1)を利用して、第1のアナログ値(XA)を与えるために変換される。同様に、第2のデジタル値(KD)は、第2のデジタル/アナログ変換器(DA2)を利用して、アナログ鍵値(KA)に変換される。アナログ機能(F)は、アナログ結果(RA)を与えるために2つのアナログ値に適用される。アナログ/デジタル変換器(AD)を利用して、アナログ結果(RA)は、入力(XD)での第1のデジタル値の暗号化を表わす、暗号化されたデジタル出力(RD)をそれにより与えるデジタル値に変換される。図1に示されるように、暗号化される入力(XD)は、入力レジスタ(X)に格納されてもよい。また、この場合には暗号鍵値を表わす第2のデジタル値(KD)は、暗号鍵レジスタ(K)に格納されてもよい。同様に、アナログ/デジタル変換結果(RD)は、結果レジスタ(R)に格納されてもよい。実際上、完全な暗号アルゴリズム(その多くは後述される)を構成するために、更に他の調整回路構成を含むことができる完全な暗号化システムの一部のみを、図1に示されるブロックが表わしてもよいことは、注目するに価する。

【0021】

デジタルエレクトロニクスにおいてよく知られているように、nビットのデジタル値は、1セットのn状態により表わすことができ、各々の状態は2つの2進値(即ち0又は1)の1つを有する。他のタイプの状態は、極性や周波数値等の方向等としても可能であるが、これらの状態は、例えば電圧状態又は電流状態として定義することができる。デジタル/アナログ変換器(DA1、DA2)は、好適には、値を例えばデジタル領域からアナログ領域(電圧、電流、周波数又は電荷等のような任意のアナログ量に結びつくような変換の形式)に変換するべきである。同様に、アナログ/デジタル変換器(AD)は、例えば電圧、電流、周波数又は電荷等のようなアナログ量を、例えば電圧又は電流により表わされるデジタル領域に変換するべきである。

【0022】

アナログ機能(F)は、少なくとも2つのアナログ入力に作用してアナログ出力を与える、任意の所定のアナログ機能であってもよい。例えば、加算、減算、乗算に関する算術機能若しくはログ機能、又はその任意の組み合わせを利用してもよい。本発明の実施形態において、アナログ値が電荷として表わされる場合の算術機能を実現するためにスイッチキャパシタ回路を利用することは便利である。実際は、除算機能又は加算機能を実現する慣例は、スイッチキャパシタ回路設計の当業者によく知られている。本発明の別の実施形態において、デジタル値は、電圧状態により表わされ、デジタル/アナログ変換器は、デジタル電圧領域からアナログ電流領域に変換する。当業者にとってよく知られているように、加算機能の実現は、電流領域で作動する回路を単純に利用している。同様に、周波数領域において、周波数逓倍回路は、異なる数学的機能を実現する他のタイプの混合回路と同様に容易に入手可能である。

【0023】

上記のようなアナログ電子回路内の基本的な算術機能又は数学的機能を実現することができる基本構成要素を利用して、2の累乗又は3の累乗等にオペランドを引き上げることに関する機能を含む多項式機能に関する、より複雑な数学的機能を実現するアナログ回路を組み込むことも、更に可能である。前述の数学的機能のいずれも、本発明のアナログ機能(F)を実現するために利用することができる。

【0024】

図2に示される本発明の別の実施形態によれば、第1のデジタル値(XD)は、第1の前処理ステージ(PREX)を利用して、入力値(XIN)のすべて又は一部から取り出されてもよい。当該前処理ステージ(PREX)は、所定値の入力値(XIN)への加算又は入力値(XIN)からの所定値の減算、入力値(XIN)の切捨て(truncation)又は回転(rotation)、又は入力値(XIN)のすべて又は一部に基づいて第1のデジタル値(XD)を与えることができる任意の恣意的な論理機能等のような様々な機能に基づいてもよい。

【0025】

図3に示される本発明の更なる実施形態によれば、第2のデジタル値(KD)は、第2の前処理ステージ(PREK)を利用して、鍵値(KIN)のすべて又は一部から取り出されてもよい。当該前処理ステージ(PREX)は、所定値の鍵値(KIN)への加算若しくは鍵値(KIN)からの所定値の減算、鍵値(KIN)の切捨て若しくは回転、又は鍵値(KIN)のすべて若しくは一部に基づいて第2のデジタル値(KD)を与えることができる任意の恣意的な論理機能等のような様々な機能に基づいてもよい。更に、図3に示されるように、出力側で、出力(RD)は、後処理された出力(RPD)を与える後処理ステージ(POST)に従ってもよい。

【0026】

本発明の好ましい実施形態によれば、上記の前処理作業のいずれも、例えば切捨てのいくつかの形式、又は複数の繰り返し若しくは複数の同時の並列分岐において暗号化手続きが実行されるための入力値(XIN)若しくは鍵値(KIN)の一部分を更に含んでもよい。第1の前処理ステージ(PREX)がより複雑なロジックを含んでいてもよいし、暗号鍵(又は復号鍵)の利用を要してさえもよいことは、注目に値する。実際は、鍵は、第2のデジタル値(KD)又は鍵値(KIN)の他のデリバティブであってもよい。図4は、この例を図示しており、入力値(XIN)に適用された第1の前処理ステージ(PREX)は、鍵値(KIN)から取り出された前処理の鍵値(KPRE)を利用する。前処理の鍵値(KPRE)は、第2のデジタル値(KD)のように同じ値を有していてもよいし、有していなくてもよい。実際は、図4に示されるように、更なる鍵(例えば、あるいは後処理ステージ(POST)内の暗号鍵(又は復号鍵)として機能する更なる入力として利用できる後処理の鍵値(KPOST))が取り出されてもよい。図4は、第2のデジタル値、前処理の鍵値(KPRE)及び同じ鍵値(KIN)から取り出されるような後処理の鍵値(KPOST)を示しているが、これらの鍵の各々が完全に独立していてもよいことは、注目に値する。同じ理由で、第2のデジタル値(KD)、前処理の鍵値(KPRE)、及び後処理の鍵値(KPOST)は、実際は同一のものであってもよい。より一般的には、デジタルハードウェアにおいて実現可能な完全な暗号アルゴリズムは、アナログハードウェアを利用して、サブアルゴリズムの少なくとも1つが、アナログ機能として実現されるために、複数のサブアルゴリズムに分割されてもよい。このように、ソフトウエアエミュレータ又は任意の他の種類のエミュレータを構築する目的のために、回路を解析して模倣することを困難にするという目的は満たされている。

【0027】

本発明の実施形態において、暗号化の再現性を保証するために注意が必要である。xボルトの範囲を備えたnビットのデジタル/アナログ変換器において、入力の各ステップは、出力でのx/nボルトの差分に対応する。逆に、yボルトの入力範囲を持ったmビットのアナログ/デジタル変換器については、入力でのy/mボルトの変化は、出力での単位変化又はステップに結びつくであろう。これは、2Vの範囲を有する16ビットの変換器については、約30μVのステップサイズを与える。デジタル/アナログ変換とデジタル/アナログ変換の当業者により十分に理解されているように、そのような変換器は、温度差、電源電圧偏差又は基準電圧偏差、電気雑音、変換速度等のような要因によるある量の誤差に影響され得る。誤差値のサイズが変換器のステップサイズに匹敵する場合には、デジタル入力がアナログ値に変換され、その後デジタル出力に変換されるシステムにおいて、デジタル出力がシステム内の誤差に依存して変化するので、あるデジタル入力が同じデジタル出力に常に結びつくであろうという保証はない。

【0028】

更に、上述の誤差に対する可能性と同様に、アナログ/デジタル変換器により後続するアナログ機能により後続する少なくとも1つのデジタル/アナログ変換器を含む連鎖において、更なる誤差が、電気雑音、電源変動のような要因により、又は変換器により生じる誤差に例えば累積的効果若しくは乗法的効果を有するアナログ機能自体により単純に、アナログ機能に導入されてもよい。例えば、もし連鎖が2つのデジタル/アナログ変換器を有しており、アナログ機能がデジタル/アナログ変換器の2つの出力の乗算であるならば、双方のデジタル/アナログ変換器からの誤差もアナログ機能の出力で乗算されるであろう。

【0029】

デジタル電子ハードウェア内で実現される暗号アルゴリズムのための適切なセキュリティレベルを維持するために、暗号鍵を表わすために用いられるビット数が適切に高く保たれなければならないことが、暗号手法の分野でよく知られている。一方、上述の説明で理解できるように、暗号アルゴリズム(又はアルゴリズムの少なくとも一部)が、アナログ機能として実現されるべきである場合、使用されるビット数が、変換器及び/又はアナログ機能における本来の誤差のサイズに匹敵するステップサイズに結びつく場合、そのようなシステムの再現性は損なわれてしまう。言いかえれば、より多くのビットが利用されると、再現可能な結果をもたらす確定系を構築することができる点でより少ない機会となる。

【0030】

この問題を回避するために、アナログ機能が暗号アルゴリズムの一部を再現する本発明の実施形態によれば、アナログ機能は複数のアナログサブ機能に分割される。それらがアナログ機能を実現するために組み合わせられるように、アナログサブ機能が選択される。各アナログサブ機能は、デジタル/アナログ変換器を通じて、少なくとも2入力(即ち第1オペランド及び第2オペランド)を受信し、サブ機能からの出力は、サブソリューションを与えるためにアナログ/デジタル変換器に進む。変換器のステップサイズ及び許容誤差(及び従ってビット(b)の最適数)は、デジタル/アナログ変換器、サブ機能、及びアナログ/デジタル変換器を含む連鎖に対する全体的な許容誤差が、与えられた第1のオペランド及び第2のオペランドに対して確定的サブソリューションに結びつくように選択される。上述の複数の連鎖は、選択されたアナログ機能を実現する目的で実行される。鍵値が複数のbビットの部分的な鍵値に分割される一方で(これらは上述の第2のオペランドである)、第1のデジタル値は複数のbビットの部分的な第1のデジタル値に分割される(これらは上述の第1のオペランドである)。各々の連鎖を通じて、各々の部分的な第1のデジタル値及び部分的な第2のデジタル値の処理は、上述したような複数の部分結果又はサブソリューションをもたらす。部分結果は、その後アナログ機能にソリューションを与えるために、デジタル領域又はアナログ領域のいずれかに組み合わせられる。アナログ機能は、全体的な暗号アルゴリズムの選択された部分を実現するために利用される。

【0031】

図5に示されるように、第2のデジタル値(KD)及び第1のデジタル値(XD)の両方が、複数の部分的な第1のデジタル値(XD1、XD2)及び部分的な第2のデジタル値(KD1、KD2)に分割される。この例は、2つの部分に各々分割されている第1のデジタル値及び鍵値を示しているが、双方の値が各々一部の任意の所望数に分割されてもよいことは、十分に理解されるべきである。各々の部分的な第1のデジタル値は、部分的な第1のアナログ値(XA1、XA2)に変換され、各々の部分的な第2のデジタル値は、部分的なアナログ鍵値(KA1、KA2)に変換される。複数のアナログサブ機能ブロック(SF1、SF2)は、複数の部分的な第1のアナログ値からの1つ、及び複数の部分的なアナログ結果(RAP1、RAP2)を与える複数のアナログ鍵値からの1つのペアで、アナログ機能を実行する。部分的なアナログ結果は、複数のアナログ/デジタル変換器(AD1、AD2)を利用して、複数の部分的なデジタル結果(RDP1、RDP2)に変換され、複数の部分的なデジタル結果は、暗号化された(又は復号化された)デジタル出力値(RD)を与える所定のデジタル結合機能(CD)を利用して組み合わせられる。前述のように、もしアナログ機能(F)を利用して、第1のデジタル値(XD)及び第2のデジタル値(KD)が処理されていたならば、部分的なデジタル結果の組み合わせは、得られたのと同じデジタル出力値をもたらす。所定のデジタル結合機能(CD)が、後処理の鍵値(POST)又は他の所定の鍵を利用することを更に含んでもよいことは、注目に値する。あるいは、部分的なアナログ結果(RAP1、RAP2)は、暗号化された(又は復号化された)デジタル出力値(RD)に結びつくアナログ/デジタル変換(AD)を適用する前に、アナログ結果(RA)を与えるアナログ結合機能(CA)を利用して、アナログ領域に組み合わせることができる。これは図6に示されている。アナログ結合機能(CA)は、例えばアナログ暗号鍵(KA)等のように、暗号鍵を利用してもよいし、利用しなくてもよい。本発明の他の実施形態において、部分的な第1のデジタル値及び部分的な第2のデジタル値の処理は、連続する方式で行われてもよいし、又は上記のパラレルアーキテクチャーよりもむしろパイプライン化された機構を利用して行われてもよい。

【0032】

本発明の別の実施形態において、更に暗号化の結果を変化させるために、暗号化された出力値は、更なる暗号化のラウンド、又は複数の更なる暗号化のラウンドを経る。どれだけのラウンドを構成しなければならないかに関する判断は、必要とされる速度又は性能と、結果として生じる暗号アルゴリズムの複雑性との間の兼ね合いに基づく。更に、各暗号化のラウンドは、必ずしも同じ暗号鍵を利用する必要はない。更なる暗号化のラウンドを実現するために、暗号化されたデジタル出力値(RD)(又は後処理された出力値(RPD))は、新規の第1のデジタル値(XD)(又は新規の入力値(XIN))になるために入力にフィードバックすることができ、又は、ハードウェアの更なるブロックは、第1のブロックの出力上に転送することができる。あるいは、更なる暗号化のラウンドは、部分的なアナログ結果がアナログサブ機能を通じて更なる処理を経ることにより、アナログ領域内で達成することができる。

【0033】

図7は、本発明の実施形態により、暗号化された値の復号化が、機能Fを利用して、どのように達成されるのかを示している。暗号化された値(RD)は、デジタル/アナログ変換器(DA1)を利用して、アナログ値に変換される。同様に、復号鍵(KD)は、デジタル/アナログ変換器(DA2)を利用して、デジタル領域からアナログ領域に変換される。2つのアナログ値(RA、KDA)は、復号化アナログ機能(F−1)を利用して組み合わせられる。復号化アナログ機能(XA)の結果は、復号化された値(XD)を与えるために、アナログ/デジタル変換器(AD)を利用して、アナログ領域からデジタル領域に変換される。暗号化の場合のように、復号鍵(KD)は、復号化サブ鍵(KSD)を取り出すために利用されてもよい。本発明の1つの実施形態において、復号鍵は、暗号鍵と同一であり、復号化機能は、暗号化機能の逆である。別の実施形態において、暗号化機能が復号化機能と同一である一方、復号鍵は暗号鍵とは異なる。暗号化の部分で記載されているように、復号化は、複数のより短い鍵に分割されている鍵、及びアナログ領域又はデジタル領域のいずれかに結合した部分結果により複数のアナログ機能により処理される複数のより短い暗号化された値に分割されている暗号化された値により、低減されたビット数を処理する複数のブロック内で行われてもよい。

【0034】

上記の確定的暗号化システムの達成に寄与する技術、即ち、デジタル値を複数のより小さな部分に分割することも、本復号化システムに適用されてもよい。同様に、複数のラウンドの利用が復号化システムに適用されてもよい。

【技術分野】

【0001】

本発明は、コンピュータを用いて伝送された情報の暗号化及び復号化の分野に関する。特に、本発明は、暗号化されたデジタル情報を与えるための鍵の下でのデジタル情報の暗号化と、暗号化されたデジタル情報の対象とする受信者による更なる復号化に関わる。

【背景技術】

【0002】

昨今では、デジタル電子情報の暗号化及び復号化は一般的であり、銀行業務、ソフトウェア保護、データ保護、デジタル著作権管理、機密情報の伝送が保証されるべき電気通信、及び特に高価値のコンテンツの伝送を伴っている放送の分野で容易に見出すことができる。

【0003】

大部分の暗号アルゴリズムは、鍵共有プロトコルを利用しており、暗号化された情報の送信者及び受信者は、鍵を共有する。同一の鍵が暗号化及び復号化するために利用される場合、鍵は対称性を有することができる。対称鍵技術は、容易に計算可能な方法で相関させた異なる鍵の利用もカバーする。一方、非対称暗号鍵技術において、公開鍵は、暗号化するために利用され、秘密鍵は、公開鍵とは異なり、復号化するために利用される。そのようなアルゴリズムは、例えば、DES、RSAもしくはディフィーヘルマン鍵交換プロトコル(Diffie-Hellman Key Exchange Protocol)等のような標準規格、又は米商務省標準技術局(NIST:National Institute for Standards and Technology)により推奨されたような次世代標準暗号化方式(AES:Advanced Encryption Standard)等のような他の標準規格に記述されている。これらのタイプのアルゴリズムにおいて利用される暗号化の耐力は、特定のアルゴリズムがどの程度利用されるか、及び鍵の秘密が保たれるという前提で利用される鍵の長さ及び型に依存する。

【0004】

技術分野で述べたように、本発明の分野は、デジタル情報の暗号化及び復号化である。しかしながら、本発明はアナログ電子情報処理技術を含んでいるので、最先端技術の記述にアナログ暗号化/復号化技術を含むことは適切である。

【0005】

アナログ暗号化技術は、音声符号化の目的のために、通信工学の分野及び電話工学の分野において一般に使用される。現在使われている技術は、時間領域又は周波数領域のいずれかでスクランブルすることを含んでいる。

【0006】

スクランブリングの代わりに、他の技術もアナログ暗号化において利用されている。例えば、特許文献1には、それによって暗号化されるアナログ信号の一部が分離されて変調信号と組み合わされる、アナログ暗号化技術が記載されている。変調信号は、暗号化されたアナログ信号を与えるためにオリジナルのアナログ信号と組み合わされる。

【0007】

デジタル領域内の暗号化を実行してその結果を状況に応じてアナログ領域に再変換する前に、アナログ信号がまずサンプリングされてデジタル領域に変換される、混合モード(Mixed-mode)の暗号化技術が存在する。特許文献2には、それによってアナログ入力信号がデジタル入力信号に変換される、電話通信の暗号化に対する広く認められた取り組みが記載されている。デジタル入力信号は、デジタル鍵の下で暗号化され、その結果として生じる暗号化されたデジタル入力信号は、アナログ入力信号を表現したアナログ出力信号に再変換される。

【0008】

特許文献3には、リアルタイムの音声通信を保証するために、音声信号の暗号化/復号化のための混合モードの方法及び装置が記載されている。アナログ音声信号は、デジタル音声信号に変換され、その後、既知の手段を利用して、暗号化/スクランブルされる。リアルタイムにサンプリングされる音声信号(又はその遅延バージョン)は、暗号化/スクランブルされた音声信号に追加される。

【0009】

特許文献4には、デジタルの音声信号及び映像信号を受信し、アナログ領域内の信号を処理することを可能にするためのデジタル/アナログ変換器を含む音声入力インタフェースが記載されている。特許文献4では、既に上述した文献のように、同一のコンテキストでアナログ復号化が説明されている。

【0010】

特許文献5には、アナログデータを暗号化するための装置及び方法が記載されている。これによると、デジタル領域とアナログ領域との間の変換は、利用されない。アナログ信号を取得し、取得したアナログ信号を変調信号に組み合わせる回路が記載されている。

【0011】

従って、最先端技術の暗号化技術は、業界基準の鍵共有アルゴリズムを利用して、デジタル情報を暗号化し復号化することを可能にし、又は業界基準の同じ技術を利用して、次にアナログ情報を暗号化し復号化することができるデジタル情報に変換することを可能にする。アナログ情報のための最先端技術の暗号化技術も存在する。しかし、そのような技術により与えられた暗号化は、デジタル暗号化程安全ではないと一般に見なされている。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】米国特許第7545929号明細書

【特許文献2】米国特許出願公開第2001/0021252号明細書

【特許文献3】国際特許出願公開第2007/120006号パンフレット

【特許文献4】米国特許公開第7647615号明細書

【特許文献5】米国特許公開第7545929号明細書

【発明の概要】

【発明が解決しようとする課題】

【0013】

電子暗号手法の分野において、デジタルハードウェア内で実行された暗号アルゴリズムを解析して模倣(リバースエンジニアリング)し、ソフトウェア(それは第三者が、暗号アルゴリズムを利用して、暗号化された情報にアクセスすることを可能にするハードウェア暗号アルゴリズムを回避するために利用されてもよい)内にそのアルゴリズムのエミュレーションを組み込むことは第三者にとって通常可能である。本発明の目的の1つは、現在の最先端技術の暗号化ハードウェアと比較してハードウェアのリバースエンジニアリングを十分に困難にする高度なセキュリティを提供する一方で、ハードウェア内でデジタル暗号アルゴリズムを実現する新しい方法及び装置を提供することである。

【課題を解決するための手段】

【0014】

従って、本発明は、暗号鍵の発見により、又はその逆に暗号アルゴリズムを回避することにより、情報を復号化することができる、本発明により暗号化された情報の意図しない受信者の可能性を最小限にすることを追求する。

【0015】

この目的は、少なくとも1つの第1のデジタル値(XD)及び少なくとも1つの第2のデジタル値(KD)上でデジタル暗号機能を実行する方法を利用して達成され、前記デジタル暗号機能は少なくとも1つのデジタル結果を有しており、本方法は、

a)前記少なくとも1つの第1のデジタル値(XD)を少なくとも1つの第1のアナログ値(XA)に変換するステップと、

b)前記少なくとも1つの第2のデジタル値(KD)を少なくとも1つのアナログ鍵値(KA)に変換するステップと、

c)前記少なくとも1つの第1のアナログ値(XA)及び前記少なくとも1つのアナログ鍵値(KA)上で、少なくとも1つのアナログ出力値(RA)を与えるためにアナログ機能(F)を実行するステップと、

d)前記デジタル暗号機能の前記結果を表わすデジタル出力値(RD)を与えるために前記アナログ出力値(RA)を変換するステップと、

を含むことを特徴とする方法である。

【0016】

本発明は、少なくとも1つの第2のデジタル値(KD)を用いて少なくとも1つの第1のデジタル値(XD)上で上記方法によるデジタル暗号機能を実行するための装置を更に提供するものであり、前記デジタル暗号機能は少なくとも1つのデジタル結果を有しており、本装置は、

前記少なくとも1つの第1のデジタル値(XD)を少なくとも1つの第1のアナログ値(XA)に変換する手段と、

前記少なくとも1つの第2のデジタル値(KSD)を少なくとも1つのアナログ鍵値(KA)に変換する手段と、

アナログ結果(RA)を与えるために前記第1のアナログ値及び前記アナログ鍵値上でアナログ機能(F)を実行する手段と、

前記デジタル暗号機能の前記結果を表わすデジタル出力値(RD)を与えるために前記アナログ結果をデジタル値に変換する手段と、

を備えることを特徴とする装置である。

【発明の効果】

【0017】

従って、第三者が、実現された暗号機能のソフトウエアエミュレータをデジタルハードウェア内に組み込むことを防止するという課題は、暗号化アルゴリズムと復号化アルゴリズムを構成するための混合モードのデジタル/アナログハードウェア技術を提供することにより解決される。

【図面の簡単な説明】

【0018】

本発明は、以上の発明の詳細な説明、及び以下の添付の図面(本発明の実施形態の非限定的な例として示される)により一層よく理解されるであろう。

【図1】本発明の実施形態により展開される暗号化システムの一部のブロック図を示す。

【図2】図1に記載の暗号化システムの一部の他の実施形態を示す。

【図3】図1に記載の暗号化システムの一部の他の実施形態を示す。

【図4】図1に記載の暗号化システムの一部の他の実施形態を示す。

【図5】図1に記載の暗号化システムの一部の他の実施形態を示す。

【図6】図1に記載の暗号化システムの一部の他の実施形態を示す。

【図7】本発明の実施形態により展開される復号化システムの一部のブロック図を示す。

【発明を実施するための形態】

【0019】

本発明の実施形態は、暗号化又は復号化された出力を与えるために第2の値下の第1の値上で暗号機能を実行するためのシステム内で展開することができる。

図1は、その中で本発明の実施形態が展開される、デジタル情報を暗号化(又は復号化)するためのシステムの一部の概略図を示している。この概略図に示されるブロックは、暗号化(又は復号化)される入力としての第1のデジタル値(XD)と、暗号化(又は復号化)の鍵として第2のデジタル値(KD)とを得て、出力として暗号化(又は復号化)されたデジタル値(RD)を与える。従って、言いかえれば、このブロックは、デジタル結果(RD)を出力するために第1のデジタルオペランド(XD)及び第2のデジタルオペランド(KD)上でデジタル暗号機能を実行する。

【0020】

本発明の実施形態によれば、第1のデジタル値(XD)は、第1のデジタル/アナログ変換器(DA1)を利用して、第1のアナログ値(XA)を与えるために変換される。同様に、第2のデジタル値(KD)は、第2のデジタル/アナログ変換器(DA2)を利用して、アナログ鍵値(KA)に変換される。アナログ機能(F)は、アナログ結果(RA)を与えるために2つのアナログ値に適用される。アナログ/デジタル変換器(AD)を利用して、アナログ結果(RA)は、入力(XD)での第1のデジタル値の暗号化を表わす、暗号化されたデジタル出力(RD)をそれにより与えるデジタル値に変換される。図1に示されるように、暗号化される入力(XD)は、入力レジスタ(X)に格納されてもよい。また、この場合には暗号鍵値を表わす第2のデジタル値(KD)は、暗号鍵レジスタ(K)に格納されてもよい。同様に、アナログ/デジタル変換結果(RD)は、結果レジスタ(R)に格納されてもよい。実際上、完全な暗号アルゴリズム(その多くは後述される)を構成するために、更に他の調整回路構成を含むことができる完全な暗号化システムの一部のみを、図1に示されるブロックが表わしてもよいことは、注目するに価する。

【0021】

デジタルエレクトロニクスにおいてよく知られているように、nビットのデジタル値は、1セットのn状態により表わすことができ、各々の状態は2つの2進値(即ち0又は1)の1つを有する。他のタイプの状態は、極性や周波数値等の方向等としても可能であるが、これらの状態は、例えば電圧状態又は電流状態として定義することができる。デジタル/アナログ変換器(DA1、DA2)は、好適には、値を例えばデジタル領域からアナログ領域(電圧、電流、周波数又は電荷等のような任意のアナログ量に結びつくような変換の形式)に変換するべきである。同様に、アナログ/デジタル変換器(AD)は、例えば電圧、電流、周波数又は電荷等のようなアナログ量を、例えば電圧又は電流により表わされるデジタル領域に変換するべきである。

【0022】

アナログ機能(F)は、少なくとも2つのアナログ入力に作用してアナログ出力を与える、任意の所定のアナログ機能であってもよい。例えば、加算、減算、乗算に関する算術機能若しくはログ機能、又はその任意の組み合わせを利用してもよい。本発明の実施形態において、アナログ値が電荷として表わされる場合の算術機能を実現するためにスイッチキャパシタ回路を利用することは便利である。実際は、除算機能又は加算機能を実現する慣例は、スイッチキャパシタ回路設計の当業者によく知られている。本発明の別の実施形態において、デジタル値は、電圧状態により表わされ、デジタル/アナログ変換器は、デジタル電圧領域からアナログ電流領域に変換する。当業者にとってよく知られているように、加算機能の実現は、電流領域で作動する回路を単純に利用している。同様に、周波数領域において、周波数逓倍回路は、異なる数学的機能を実現する他のタイプの混合回路と同様に容易に入手可能である。

【0023】

上記のようなアナログ電子回路内の基本的な算術機能又は数学的機能を実現することができる基本構成要素を利用して、2の累乗又は3の累乗等にオペランドを引き上げることに関する機能を含む多項式機能に関する、より複雑な数学的機能を実現するアナログ回路を組み込むことも、更に可能である。前述の数学的機能のいずれも、本発明のアナログ機能(F)を実現するために利用することができる。

【0024】

図2に示される本発明の別の実施形態によれば、第1のデジタル値(XD)は、第1の前処理ステージ(PREX)を利用して、入力値(XIN)のすべて又は一部から取り出されてもよい。当該前処理ステージ(PREX)は、所定値の入力値(XIN)への加算又は入力値(XIN)からの所定値の減算、入力値(XIN)の切捨て(truncation)又は回転(rotation)、又は入力値(XIN)のすべて又は一部に基づいて第1のデジタル値(XD)を与えることができる任意の恣意的な論理機能等のような様々な機能に基づいてもよい。

【0025】

図3に示される本発明の更なる実施形態によれば、第2のデジタル値(KD)は、第2の前処理ステージ(PREK)を利用して、鍵値(KIN)のすべて又は一部から取り出されてもよい。当該前処理ステージ(PREX)は、所定値の鍵値(KIN)への加算若しくは鍵値(KIN)からの所定値の減算、鍵値(KIN)の切捨て若しくは回転、又は鍵値(KIN)のすべて若しくは一部に基づいて第2のデジタル値(KD)を与えることができる任意の恣意的な論理機能等のような様々な機能に基づいてもよい。更に、図3に示されるように、出力側で、出力(RD)は、後処理された出力(RPD)を与える後処理ステージ(POST)に従ってもよい。

【0026】

本発明の好ましい実施形態によれば、上記の前処理作業のいずれも、例えば切捨てのいくつかの形式、又は複数の繰り返し若しくは複数の同時の並列分岐において暗号化手続きが実行されるための入力値(XIN)若しくは鍵値(KIN)の一部分を更に含んでもよい。第1の前処理ステージ(PREX)がより複雑なロジックを含んでいてもよいし、暗号鍵(又は復号鍵)の利用を要してさえもよいことは、注目に値する。実際は、鍵は、第2のデジタル値(KD)又は鍵値(KIN)の他のデリバティブであってもよい。図4は、この例を図示しており、入力値(XIN)に適用された第1の前処理ステージ(PREX)は、鍵値(KIN)から取り出された前処理の鍵値(KPRE)を利用する。前処理の鍵値(KPRE)は、第2のデジタル値(KD)のように同じ値を有していてもよいし、有していなくてもよい。実際は、図4に示されるように、更なる鍵(例えば、あるいは後処理ステージ(POST)内の暗号鍵(又は復号鍵)として機能する更なる入力として利用できる後処理の鍵値(KPOST))が取り出されてもよい。図4は、第2のデジタル値、前処理の鍵値(KPRE)及び同じ鍵値(KIN)から取り出されるような後処理の鍵値(KPOST)を示しているが、これらの鍵の各々が完全に独立していてもよいことは、注目に値する。同じ理由で、第2のデジタル値(KD)、前処理の鍵値(KPRE)、及び後処理の鍵値(KPOST)は、実際は同一のものであってもよい。より一般的には、デジタルハードウェアにおいて実現可能な完全な暗号アルゴリズムは、アナログハードウェアを利用して、サブアルゴリズムの少なくとも1つが、アナログ機能として実現されるために、複数のサブアルゴリズムに分割されてもよい。このように、ソフトウエアエミュレータ又は任意の他の種類のエミュレータを構築する目的のために、回路を解析して模倣することを困難にするという目的は満たされている。

【0027】

本発明の実施形態において、暗号化の再現性を保証するために注意が必要である。xボルトの範囲を備えたnビットのデジタル/アナログ変換器において、入力の各ステップは、出力でのx/nボルトの差分に対応する。逆に、yボルトの入力範囲を持ったmビットのアナログ/デジタル変換器については、入力でのy/mボルトの変化は、出力での単位変化又はステップに結びつくであろう。これは、2Vの範囲を有する16ビットの変換器については、約30μVのステップサイズを与える。デジタル/アナログ変換とデジタル/アナログ変換の当業者により十分に理解されているように、そのような変換器は、温度差、電源電圧偏差又は基準電圧偏差、電気雑音、変換速度等のような要因によるある量の誤差に影響され得る。誤差値のサイズが変換器のステップサイズに匹敵する場合には、デジタル入力がアナログ値に変換され、その後デジタル出力に変換されるシステムにおいて、デジタル出力がシステム内の誤差に依存して変化するので、あるデジタル入力が同じデジタル出力に常に結びつくであろうという保証はない。

【0028】

更に、上述の誤差に対する可能性と同様に、アナログ/デジタル変換器により後続するアナログ機能により後続する少なくとも1つのデジタル/アナログ変換器を含む連鎖において、更なる誤差が、電気雑音、電源変動のような要因により、又は変換器により生じる誤差に例えば累積的効果若しくは乗法的効果を有するアナログ機能自体により単純に、アナログ機能に導入されてもよい。例えば、もし連鎖が2つのデジタル/アナログ変換器を有しており、アナログ機能がデジタル/アナログ変換器の2つの出力の乗算であるならば、双方のデジタル/アナログ変換器からの誤差もアナログ機能の出力で乗算されるであろう。

【0029】

デジタル電子ハードウェア内で実現される暗号アルゴリズムのための適切なセキュリティレベルを維持するために、暗号鍵を表わすために用いられるビット数が適切に高く保たれなければならないことが、暗号手法の分野でよく知られている。一方、上述の説明で理解できるように、暗号アルゴリズム(又はアルゴリズムの少なくとも一部)が、アナログ機能として実現されるべきである場合、使用されるビット数が、変換器及び/又はアナログ機能における本来の誤差のサイズに匹敵するステップサイズに結びつく場合、そのようなシステムの再現性は損なわれてしまう。言いかえれば、より多くのビットが利用されると、再現可能な結果をもたらす確定系を構築することができる点でより少ない機会となる。

【0030】

この問題を回避するために、アナログ機能が暗号アルゴリズムの一部を再現する本発明の実施形態によれば、アナログ機能は複数のアナログサブ機能に分割される。それらがアナログ機能を実現するために組み合わせられるように、アナログサブ機能が選択される。各アナログサブ機能は、デジタル/アナログ変換器を通じて、少なくとも2入力(即ち第1オペランド及び第2オペランド)を受信し、サブ機能からの出力は、サブソリューションを与えるためにアナログ/デジタル変換器に進む。変換器のステップサイズ及び許容誤差(及び従ってビット(b)の最適数)は、デジタル/アナログ変換器、サブ機能、及びアナログ/デジタル変換器を含む連鎖に対する全体的な許容誤差が、与えられた第1のオペランド及び第2のオペランドに対して確定的サブソリューションに結びつくように選択される。上述の複数の連鎖は、選択されたアナログ機能を実現する目的で実行される。鍵値が複数のbビットの部分的な鍵値に分割される一方で(これらは上述の第2のオペランドである)、第1のデジタル値は複数のbビットの部分的な第1のデジタル値に分割される(これらは上述の第1のオペランドである)。各々の連鎖を通じて、各々の部分的な第1のデジタル値及び部分的な第2のデジタル値の処理は、上述したような複数の部分結果又はサブソリューションをもたらす。部分結果は、その後アナログ機能にソリューションを与えるために、デジタル領域又はアナログ領域のいずれかに組み合わせられる。アナログ機能は、全体的な暗号アルゴリズムの選択された部分を実現するために利用される。

【0031】

図5に示されるように、第2のデジタル値(KD)及び第1のデジタル値(XD)の両方が、複数の部分的な第1のデジタル値(XD1、XD2)及び部分的な第2のデジタル値(KD1、KD2)に分割される。この例は、2つの部分に各々分割されている第1のデジタル値及び鍵値を示しているが、双方の値が各々一部の任意の所望数に分割されてもよいことは、十分に理解されるべきである。各々の部分的な第1のデジタル値は、部分的な第1のアナログ値(XA1、XA2)に変換され、各々の部分的な第2のデジタル値は、部分的なアナログ鍵値(KA1、KA2)に変換される。複数のアナログサブ機能ブロック(SF1、SF2)は、複数の部分的な第1のアナログ値からの1つ、及び複数の部分的なアナログ結果(RAP1、RAP2)を与える複数のアナログ鍵値からの1つのペアで、アナログ機能を実行する。部分的なアナログ結果は、複数のアナログ/デジタル変換器(AD1、AD2)を利用して、複数の部分的なデジタル結果(RDP1、RDP2)に変換され、複数の部分的なデジタル結果は、暗号化された(又は復号化された)デジタル出力値(RD)を与える所定のデジタル結合機能(CD)を利用して組み合わせられる。前述のように、もしアナログ機能(F)を利用して、第1のデジタル値(XD)及び第2のデジタル値(KD)が処理されていたならば、部分的なデジタル結果の組み合わせは、得られたのと同じデジタル出力値をもたらす。所定のデジタル結合機能(CD)が、後処理の鍵値(POST)又は他の所定の鍵を利用することを更に含んでもよいことは、注目に値する。あるいは、部分的なアナログ結果(RAP1、RAP2)は、暗号化された(又は復号化された)デジタル出力値(RD)に結びつくアナログ/デジタル変換(AD)を適用する前に、アナログ結果(RA)を与えるアナログ結合機能(CA)を利用して、アナログ領域に組み合わせることができる。これは図6に示されている。アナログ結合機能(CA)は、例えばアナログ暗号鍵(KA)等のように、暗号鍵を利用してもよいし、利用しなくてもよい。本発明の他の実施形態において、部分的な第1のデジタル値及び部分的な第2のデジタル値の処理は、連続する方式で行われてもよいし、又は上記のパラレルアーキテクチャーよりもむしろパイプライン化された機構を利用して行われてもよい。

【0032】

本発明の別の実施形態において、更に暗号化の結果を変化させるために、暗号化された出力値は、更なる暗号化のラウンド、又は複数の更なる暗号化のラウンドを経る。どれだけのラウンドを構成しなければならないかに関する判断は、必要とされる速度又は性能と、結果として生じる暗号アルゴリズムの複雑性との間の兼ね合いに基づく。更に、各暗号化のラウンドは、必ずしも同じ暗号鍵を利用する必要はない。更なる暗号化のラウンドを実現するために、暗号化されたデジタル出力値(RD)(又は後処理された出力値(RPD))は、新規の第1のデジタル値(XD)(又は新規の入力値(XIN))になるために入力にフィードバックすることができ、又は、ハードウェアの更なるブロックは、第1のブロックの出力上に転送することができる。あるいは、更なる暗号化のラウンドは、部分的なアナログ結果がアナログサブ機能を通じて更なる処理を経ることにより、アナログ領域内で達成することができる。

【0033】

図7は、本発明の実施形態により、暗号化された値の復号化が、機能Fを利用して、どのように達成されるのかを示している。暗号化された値(RD)は、デジタル/アナログ変換器(DA1)を利用して、アナログ値に変換される。同様に、復号鍵(KD)は、デジタル/アナログ変換器(DA2)を利用して、デジタル領域からアナログ領域に変換される。2つのアナログ値(RA、KDA)は、復号化アナログ機能(F−1)を利用して組み合わせられる。復号化アナログ機能(XA)の結果は、復号化された値(XD)を与えるために、アナログ/デジタル変換器(AD)を利用して、アナログ領域からデジタル領域に変換される。暗号化の場合のように、復号鍵(KD)は、復号化サブ鍵(KSD)を取り出すために利用されてもよい。本発明の1つの実施形態において、復号鍵は、暗号鍵と同一であり、復号化機能は、暗号化機能の逆である。別の実施形態において、暗号化機能が復号化機能と同一である一方、復号鍵は暗号鍵とは異なる。暗号化の部分で記載されているように、復号化は、複数のより短い鍵に分割されている鍵、及びアナログ領域又はデジタル領域のいずれかに結合した部分結果により複数のアナログ機能により処理される複数のより短い暗号化された値に分割されている暗号化された値により、低減されたビット数を処理する複数のブロック内で行われてもよい。

【0034】

上記の確定的暗号化システムの達成に寄与する技術、即ち、デジタル値を複数のより小さな部分に分割することも、本復号化システムに適用されてもよい。同様に、複数のラウンドの利用が復号化システムに適用されてもよい。

【特許請求の範囲】

【請求項1】

少なくとも1つの第1のデジタル値(XD)、及び少なくとも1つの第2のデジタル値(KD)上でデジタル暗号機能を実行する方法であって、前記デジタル暗号機能は少なくとも1つのデジタル結果を有し、

a)前記少なくとも1つの第1のデジタル値(XD)を少なくとも1つの第1のアナログ値(XA)に変換するステップと、

b)前記少なくとも1つの第2のデジタル値(KD)を少なくとも1つのアナログ鍵値(KA)に変換するステップと、

c)前記少なくとも1つの第1のアナログ値(XA)及び前記少なくとも1つのアナログ鍵値(KA)上で、少なくとも1つのアナログ出力値(RA)を与えるためにアナログ機能(F)を実行するステップと、

d)前記デジタル暗号機能の前記結果を表わすデジタル出力値(RD)を与えるために前記アナログ出力値(RA)を変換するステップと、

を含むことを特徴とする方法。

【請求項2】

前記少なくとも1つの第1のデジタル値(XD)は、入力値(XIN)の少なくともすべて又は一部に対して実行された第1の前処理動作(PREX)から生じることを特徴とする請求項1記載の方法。

【請求項3】

前記少なくとも1つの第2のデジタル数値結果は、鍵値(KIN)の少なくともすべて又は一部に対して実行された第2の前処理動作(PREK)から生じることを特徴とする請求項1又は2のいずれかに記載の方法。

【請求項4】

前記第2の前処理動作(PREK)は、前処理の鍵値(KPRE)を更に生成することを特徴とする請求項3記載の方法。

【請求項5】

前記第1の前処理動作(PREX)は、前記前処理の鍵値(KPRE)に更に従って動作することを特徴とする請求項2、3又は4のいずれかに記載の方法。

【請求項6】

後処理されたデジタル出力値(RPD)を与えるために、前記デジタル出力値(RD)の少なくともすべて又は一部には、後処理動作(POST)が実行されることを特徴とする請求項1ないし5のいずれかに記載の方法。

【請求項7】

前記第2の前処理動作(PREK)は、後処理の鍵値(KPOST)を更に生成することを特徴とする請求項3ないし6のいずれかに記載の方法。

【請求項8】

前記後処理動作(POST)は、前記後処理の鍵値(KPOST)に更に従って動作することを特徴とする請求項7記載の方法。

【請求項9】

前記第1の前処理動作(PREX)又は前記第2の前処理動作(PREK)のいずれかは、複数の第1のデジタル値(XD1、XD2)又は複数の第2のデジタル値(KD1、KD2)を生成することを含み、前記複数の第1のデジタル値(XD1、XD2)は複数の第1のアナログ値(XA1、XA2)に変換され、前記複数の第2のデジタル値(KD1、KD2)は複数のアナログ鍵値(KA1、KA2)に変換されることを特徴とする請求項3ないし8のいずれかに記載の方法。

【請求項10】

前記アナログ機能(F)は、複数のアナログサブ機能(SF1、SF2、CA)に分割され、前記アナログサブ機能(SF1、SF2、CA)の少なくとも2つは、複数の部分的なアナログ結果(RAP1、RAP2)を与えるために、前記少なくとも1つの第1のアナログ値(XA1、XA2)の少なくとも1つと前記少なくとも1つのアナログ鍵値(KA1、KA2)の少なくとも1つとに従って動作し、前記複数の部分的なアナログ結果(RAP1、RAP2)には、アナログ出力値(RA)をもたらすために結合サブ機能(CA)が実行されることを特徴とする請求項1ないし9のいずれかに記載の方法。

【請求項11】

前記アナログ機能(F)は、複数のアナログサブ機能(SF1、SF2)に分割され、前記アナログサブ機能(SF1、SF2)の各々は、複数の部分的なアナログ結果(RAP1、RAP2)を与えるために、前記少なくとも1つの第1のアナログ値(XA1、XA2)の少なくとも1つと、前記少なくとも1つのアナログ鍵値(KA1、KA2)の少なくとも1つとに従って動作し、前記複数の部分的なアナログ結果(RAP1、RAP2)は、複数の部分的なデジタル結果(RDP1、RDP2)に変換され、前記複数の部分的なデジタル結果(RDP1、RDP2)は、前記デジタル出力値(RD)をもたらすために組み合わせられる(CD)ことを特徴とする請求項1ないし9のいずれかに記載の方法。

【請求項12】

前記少なくとも1つの第1のデジタル値又は前記少なくとも1つの第2のデジタル値の前記変換は、電圧から電流、電圧から電荷、又は電圧から周波数への選択物から変換し、前記アナログ出力値の前記変換は、電流から電圧、電荷から電圧、又は周波数から電圧への選択物間を変換することを特徴とする請求項1ないし11のいずれかに記載の方法。

【請求項13】

前記入力値(XIN)又は前記鍵値(KIN)のいずれかは、nビット又はmビットをそれぞれ含み、前記第1のデジタル値(XD、XD1、XD2)又は前記デジタル鍵値(KD、KD1、KD2)のいずれかは、nビット又はmビット未満であるビット数をそれぞれ含むことを特徴とする請求項3ないし12のいずれかに記載の方法。

【請求項14】

前記デジタル出力値(RD)又は前記後処理されたデジタル出力値(RPD)は、請求項1〜13のいずれかに記載のデジタル暗号機能により少なくとも1度更に処理されることを特徴とする請求項1ないし13のいずれかに記載の方法。

【請求項15】

少なくとも1つの第1のデジタル値(XD)及び少なくとも1つの第2のデジタル値(KD)上でデジタル暗号機能を実行するための装置であって、前記デジタル暗号機能は少なくとも1つのデジタル結果を有しており、

前記少なくとも1つの第1のデジタル値(XD)を少なくとも1つの第1のアナログ値(XA)に変換するための少なくとも1つの第1のデジタル/アナログ変換器(DA1)と、

前記少なくとも1つの第2のデジタル値(KSD)を少なくとも1つのアナログ鍵値(KA)に変換するための少なくとも1つの第2のデジタル/アナログ変換器(DA2)と、

アナログ結果(RA)を与えるための前記第1のアナログ値(XA)及び前記アナログ鍵値(KA)に従って動作する、アナログ機能(F)を実現するのに適しているハードウェアと、

前記アナログ結果(RA)を、前記デジタル暗号機能の前記結果を表わすデジタル出力値(RD)を与えるためのデジタル値に変換するための少なくとも1つのアナログ/デジタル変換器(AD)とを備えることを特徴とする装置。

【請求項1】

少なくとも1つの第1のデジタル値(XD)、及び少なくとも1つの第2のデジタル値(KD)上でデジタル暗号機能を実行する方法であって、前記デジタル暗号機能は少なくとも1つのデジタル結果を有し、

a)前記少なくとも1つの第1のデジタル値(XD)を少なくとも1つの第1のアナログ値(XA)に変換するステップと、

b)前記少なくとも1つの第2のデジタル値(KD)を少なくとも1つのアナログ鍵値(KA)に変換するステップと、

c)前記少なくとも1つの第1のアナログ値(XA)及び前記少なくとも1つのアナログ鍵値(KA)上で、少なくとも1つのアナログ出力値(RA)を与えるためにアナログ機能(F)を実行するステップと、

d)前記デジタル暗号機能の前記結果を表わすデジタル出力値(RD)を与えるために前記アナログ出力値(RA)を変換するステップと、

を含むことを特徴とする方法。

【請求項2】

前記少なくとも1つの第1のデジタル値(XD)は、入力値(XIN)の少なくともすべて又は一部に対して実行された第1の前処理動作(PREX)から生じることを特徴とする請求項1記載の方法。

【請求項3】

前記少なくとも1つの第2のデジタル数値結果は、鍵値(KIN)の少なくともすべて又は一部に対して実行された第2の前処理動作(PREK)から生じることを特徴とする請求項1又は2のいずれかに記載の方法。

【請求項4】

前記第2の前処理動作(PREK)は、前処理の鍵値(KPRE)を更に生成することを特徴とする請求項3記載の方法。

【請求項5】

前記第1の前処理動作(PREX)は、前記前処理の鍵値(KPRE)に更に従って動作することを特徴とする請求項2、3又は4のいずれかに記載の方法。

【請求項6】

後処理されたデジタル出力値(RPD)を与えるために、前記デジタル出力値(RD)の少なくともすべて又は一部には、後処理動作(POST)が実行されることを特徴とする請求項1ないし5のいずれかに記載の方法。

【請求項7】

前記第2の前処理動作(PREK)は、後処理の鍵値(KPOST)を更に生成することを特徴とする請求項3ないし6のいずれかに記載の方法。

【請求項8】

前記後処理動作(POST)は、前記後処理の鍵値(KPOST)に更に従って動作することを特徴とする請求項7記載の方法。

【請求項9】

前記第1の前処理動作(PREX)又は前記第2の前処理動作(PREK)のいずれかは、複数の第1のデジタル値(XD1、XD2)又は複数の第2のデジタル値(KD1、KD2)を生成することを含み、前記複数の第1のデジタル値(XD1、XD2)は複数の第1のアナログ値(XA1、XA2)に変換され、前記複数の第2のデジタル値(KD1、KD2)は複数のアナログ鍵値(KA1、KA2)に変換されることを特徴とする請求項3ないし8のいずれかに記載の方法。

【請求項10】

前記アナログ機能(F)は、複数のアナログサブ機能(SF1、SF2、CA)に分割され、前記アナログサブ機能(SF1、SF2、CA)の少なくとも2つは、複数の部分的なアナログ結果(RAP1、RAP2)を与えるために、前記少なくとも1つの第1のアナログ値(XA1、XA2)の少なくとも1つと前記少なくとも1つのアナログ鍵値(KA1、KA2)の少なくとも1つとに従って動作し、前記複数の部分的なアナログ結果(RAP1、RAP2)には、アナログ出力値(RA)をもたらすために結合サブ機能(CA)が実行されることを特徴とする請求項1ないし9のいずれかに記載の方法。

【請求項11】

前記アナログ機能(F)は、複数のアナログサブ機能(SF1、SF2)に分割され、前記アナログサブ機能(SF1、SF2)の各々は、複数の部分的なアナログ結果(RAP1、RAP2)を与えるために、前記少なくとも1つの第1のアナログ値(XA1、XA2)の少なくとも1つと、前記少なくとも1つのアナログ鍵値(KA1、KA2)の少なくとも1つとに従って動作し、前記複数の部分的なアナログ結果(RAP1、RAP2)は、複数の部分的なデジタル結果(RDP1、RDP2)に変換され、前記複数の部分的なデジタル結果(RDP1、RDP2)は、前記デジタル出力値(RD)をもたらすために組み合わせられる(CD)ことを特徴とする請求項1ないし9のいずれかに記載の方法。

【請求項12】

前記少なくとも1つの第1のデジタル値又は前記少なくとも1つの第2のデジタル値の前記変換は、電圧から電流、電圧から電荷、又は電圧から周波数への選択物から変換し、前記アナログ出力値の前記変換は、電流から電圧、電荷から電圧、又は周波数から電圧への選択物間を変換することを特徴とする請求項1ないし11のいずれかに記載の方法。

【請求項13】

前記入力値(XIN)又は前記鍵値(KIN)のいずれかは、nビット又はmビットをそれぞれ含み、前記第1のデジタル値(XD、XD1、XD2)又は前記デジタル鍵値(KD、KD1、KD2)のいずれかは、nビット又はmビット未満であるビット数をそれぞれ含むことを特徴とする請求項3ないし12のいずれかに記載の方法。

【請求項14】

前記デジタル出力値(RD)又は前記後処理されたデジタル出力値(RPD)は、請求項1〜13のいずれかに記載のデジタル暗号機能により少なくとも1度更に処理されることを特徴とする請求項1ないし13のいずれかに記載の方法。

【請求項15】

少なくとも1つの第1のデジタル値(XD)及び少なくとも1つの第2のデジタル値(KD)上でデジタル暗号機能を実行するための装置であって、前記デジタル暗号機能は少なくとも1つのデジタル結果を有しており、

前記少なくとも1つの第1のデジタル値(XD)を少なくとも1つの第1のアナログ値(XA)に変換するための少なくとも1つの第1のデジタル/アナログ変換器(DA1)と、

前記少なくとも1つの第2のデジタル値(KSD)を少なくとも1つのアナログ鍵値(KA)に変換するための少なくとも1つの第2のデジタル/アナログ変換器(DA2)と、

アナログ結果(RA)を与えるための前記第1のアナログ値(XA)及び前記アナログ鍵値(KA)に従って動作する、アナログ機能(F)を実現するのに適しているハードウェアと、

前記アナログ結果(RA)を、前記デジタル暗号機能の前記結果を表わすデジタル出力値(RD)を与えるためのデジタル値に変換するための少なくとも1つのアナログ/デジタル変換器(AD)とを備えることを特徴とする装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2011−223577(P2011−223577A)

【公開日】平成23年11月4日(2011.11.4)

【国際特許分類】

【出願番号】特願2011−84293(P2011−84293)

【出願日】平成23年4月6日(2011.4.6)

【出願人】(504344495)ナグラビジョン エス アー (20)

【Fターム(参考)】

【公開日】平成23年11月4日(2011.11.4)

【国際特許分類】

【出願日】平成23年4月6日(2011.4.6)

【出願人】(504344495)ナグラビジョン エス アー (20)

【Fターム(参考)】

[ Back to top ]