最尤復号装置、信号評価方法

【課題】PRMLのビット検出によるビットエラーレートに直接相関のある指標を用いて精度良く信号評価を行う。

【解決手段】

ビタビ検出で生き残りパスの選択の際における生き残りパスと比較された消滅パスのパスメモリ間での違い、即ち消滅パスの誤りの種類を示す情報を記憶し、最終的に生き残ったパスにおいて、パス選択の際に消滅したパスが同じ種類の誤りとなっているステート遷移のみを選択して、その差メトリックの分布指標(分散、標準偏差)を計算する。ここで、誤りの種類を示す情報とは、たとえば、消滅パスと生き残りパスのパスメモリの違いが、1ビットだけ異なるようなシフトエラーであるか否か、あるいは、2ビット異なる最短マークシフトのエラーであるか否か、の情報である。

【解決手段】

ビタビ検出で生き残りパスの選択の際における生き残りパスと比較された消滅パスのパスメモリ間での違い、即ち消滅パスの誤りの種類を示す情報を記憶し、最終的に生き残ったパスにおいて、パス選択の際に消滅したパスが同じ種類の誤りとなっているステート遷移のみを選択して、その差メトリックの分布指標(分散、標準偏差)を計算する。ここで、誤りの種類を示す情報とは、たとえば、消滅パスと生き残りパスのパスメモリの違いが、1ビットだけ異なるようなシフトエラーであるか否か、あるいは、2ビット異なる最短マークシフトのエラーであるか否か、の情報である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、記録媒体に記録した情報を再生した再生信号に対する最尤復号装置、及び最尤復号装置における信号評価方法に関する。

【背景技術】

【0002】

【特許文献1】特開平10−21651号公報

【特許文献2】特開2003−141823号公報

【特許文献3】特開2003−151220号公報

【特許文献4】特開2003−178537号公報

【0003】

光ディスクの再生信号の信号品質を評価する方法として、タイムインターバルジッタ(TIジッタ)を評価する手法が知られている。TIジッタとは、再生信号と、ビット判定レベルとをコンパレータに入力し、得られた二値レベルのアナログ信号のエッジのタイミングと、再生信号から同期再生されたクロックのエッジのタイミングとの間の時間差(タイムインターバル)のばらつき(ジッタ)のことを意味している。

このような、TIジッタを用いた信号品質の評価法は、アナログの二値信号を用いたビット検出では、二値信号のエッジのタイミングのばらつきがビットエラーレートに直接影響を及ぼすことから、ビットエラーレートと相関のある評価方法として用いられていた。特に、このようなアナログの2値検出を用いていたCD、DVDなどでは、非常に有効な信号評価方法として広く用いられていた。

【0004】

一方、近年、光ディスクの記録情報の密度が高まるにつれて、上述のアナログの二値信号を用いたビット検出では十分に小さなビットエラーレートが確保できないことが判明し、特に、現在、最も高密度な光ディスクであるとされるブルーレイディスク(Blu-Ray Disc)では、ビット検出方法として、パーシャルレスポンス最尤(PRML:Partial Response Maximum Likelihood)検出とよばれる手法が用いる方法が一般的となってきている。

【0005】

PRMLとは、パーシャルレスポンスという過程と最尤検出という技術を組み合わせた技術である。パーシャルレスポンスとは、1ビットの入力に対して、1ビットよりも長く出力を返す過程、すなわち、出力の複数の入力ビットで決定する過程のことをいい、特にブルーレイディスクなどの光ディスクでよく用いられるような、再生信号が、連続する4ビットの情報ビットの入力に対してこれらを順に1、2、2、1を乗じて加算した信号として得られる過程は、PR(1,2,2,1)と表現される。

また、最尤検出とは、2つの信号の間にユークリッド距離とよばれる距離を定義して、実際の信号と想定されるビット系列から予想される信号との間の距離を調べて、その距離が最も近くなるようなビット系列を検出する方法である。なお、ここで、ユークリッド距離とは、同じ時刻での2つの信号の振幅差の二乗を全時刻にわたって加算した距離として定義される距離である。また、この距離を最小とするビット系列の探索には、後述するビタビ検出をもちいる。

これらを組み合わせたパーシャルレスポンス最尤検出は、記録媒体のビット情報から得られた信号をイコライザとよばれるフィルタでパーシャルレスポンスの過程となるように調整し、得られた再生信号と想定されるビット系列のパーシャルレスポンスとの間のユークリッド距離を調べて、その距離が最も近くなるようなビット系列を検出する方法である。

【0006】

実際にユークリッド距離が最小となるビット系列を探索するには、前述のビタビ検出によるアルゴリズムが効果を発揮する。

ビタビ検出は、所定の長さの連続ビットを単位として構成される複数のステートと、それらの間の遷移によって表されるブランチで構成されるビタビ検出器が用いられ、全ての可能なビット系列の中から、効率よく所望のビット系列を検出するように構成されている。

実際の回路では、各ステートに対してパスメトリックレジスタとよばれるそのステートにいたるまでのパーシャルレスポンス系列と信号のユークリッド距離(パスメトリック)を記憶するレジスタ、および、パスメモリレジスタとよばれるそのステートにいたるまでのビット系列の流れ(パスメモリ)を記憶するレジスタの2つのレジスタが用意され、また、各ブランチに対してはブランチメトリックユニットとよばれるそのビットにおけるパーシャルレスポンス系列と信号のユークリッド距離を計算する演算ユニットが用意されている。

このビタビ検出器では、さまざまなビット系列を、上記のステートを通過するパスのひとつによって一対一の関係で対応付けることができる。また、これらのパスを通過するようなパーシャルレスポンス系列と、実際の信号との間のユークリッド距離は、上記のパスを構成するステート間遷移、すなわち、ブランチにおける前述のブランチメトリックを順次加算していくことで得られる。

さらに、上記のユークリッド距離を最小にするようなパスを選択するには、この各ステートにおいて到達する2つ以下のブランチが有するパスメトリックの大小を比較しながら、パスメトリックの小さいパスを順次選択することで実現できる。この選択情報をパスメモリレジスタに転送することで、各ステートに到達するパスをビット系列で表現する情報が記憶される。パスメモリレジスタの値は、順次更新されながら最終的にユークリッド距離を最小にするようなビット系列に収束していくので、その結果を出力する。

以上のようにすると、上述したような、再生信号にユークリッド距離が最も近いパーシャルレスポンス系列を生成するビット系列を効率的に検索することができる。

【0007】

このようなPRMLを用いたビット検出では、時間軸方向の揺らぎであるTIジッタは、ビット検出に直接影響を及ぼすものではない。従って、TIジッタは、PRMLを用いたビット検出におけるビットエラーレートと必ずしも相関があるわけではなく、信号品質の指標として必ずしも適切ではない。PRMLの場合、振幅軸方向のゆらぎがビット検出におけるビットエラーレートに直接関係する。このため、PRMLを用いたビット検出では、ビットエラーレートに対応する指標として、振幅軸方向の揺らぎを取り込んだ指標であることが望ましい。

【0008】

PRMLによるビット検出の能力を決定する指標について以下に記述する。

PRMLによるビット検出では、正しいビット系列から得られるパーシャルレスポンス系列と再生信号とのユークリッド距離、すなわち、正しいビット系列に対するパスメトリックが、誤りのあるビット系列から得られるパーシャルレスポンス系列と再生信号とのユークリッド距離、すなわち、誤りのあるビット系列に対するパスメトリックよりも小なる場合に、正しいビット検出が実行され、逆の場合には誤りが発生する。

従って、PRMLのビット検出の能力は、前者のパスメトリックと後者のパスメトリックの差、すなわち、差メトリックが0からどれだけ離れているか、その大きさによって決定する。換言すれば、差メトリックが小さいほどエラー発生の可能性が高いと推定できる。

また、誤りのあるビット系列の中でも、誤りの大半を占める最も重要な系列は、正しい系列から得られるパーシャルレスポンス系列とのユークリッド距離が最も近くなるような別のパーシャルレスポンス系列を与えるビット系列である。このような系列は、たとえば、ターゲットレスポンスがPR(1,2,2,1)のPRMLでは、1ビットのみ誤りがある場合である。

このため、PRMLによるビット検出では、正しいビット系列から得られるパーシャルレスポンス系列と再生信号のユークリッド距離と、1ビットのみ誤りがあるビット系列のパーシャルレスポンス系列と再生信号のユークリッド距離の差分の大きさがPRMLによるビット検出の能力を決定すると考えられる。

【0009】

上記の2つのパーシャルレスポンス系列(正しいビット系列から得られるパーシャルレスポンス系列と、1ビット単独誤りがあるビット系列から得られるパーシャルレスポンス系列)に対して定義される再生信号とのユークリッド距離の差分について数式を用いて説明する。

まず、正しいビット系列に対するパスメトリック、すなわち、正しいビット系列から得られるパーシャルレスポンス系列と再生信号との間のユークリッド距離Mcは、以下の式でえられる。

Mc=Σni2

ただし、niは再生信号のサンプルにおけるノイズであり、平均0、標準偏差nのガウス分布に従う白色ノイズである。また、Σは全てのチャネルクロックiについて全て加算を意味している。

この式の導出は、PRMLでは、再生信号が正しいビット系列から得られるパーシャルレスポンス系列にノイズを加算した信号として得られるものである、と仮定していることに拠っている。

【0010】

次に、1ビット単独誤りのあるビット系列に対するパスメトリック、すなわち、1ビット単独誤りのあるビット系列から得られるパーシャルレスポンス系列と再生信号との間のユークリッド距離Meは、以下の式で与えられる。

Me=Σ(ci−ni)2

ただし、ciはターゲットレスポンスの係数であり、PR(1,2,2,1)ならば1,2,2,1,0・・・となる。

従って、その差分、すなわち、差メトリックdMは、以下の式で与えられる。

dM=Me−Mc=Σ|ci|2−2Σni・ci

ここで、Σ|ci|2は、1ビット異なる2つのビット系列から得られるパーシャルレスポンス系列のユークリッド距離に相当する。前に述べたように、この差分が、負となる場合に誤りが生ずる。また、この差分が負となるような確率は、ノイズniの標準偏差nが大きくなればなるほど高くなる。

従って、このノイズの分布nが、ビットエラーレートに対して直接寄与する指標である。しかし、nは、検出可能な量ではない。

そこで、nの代わりに、検出可能な量として差メトリックdMと、既知の量Σ|ci|2を用いて、

j=√V(dM)/(2・Σ|ci|2)

を定義すれば、jをビットエラーレートに直接寄与する指標として用いることができる。

ただし、V(dM)は、差メトリックdMの分散を表している。また、Σはチャネルクロックiについて全て加算である。

以上のように定義されたジッタjをSAMジッタと呼ぶ。

なお、jの定義式にdMを代入して変形すると、以下の式が得られる。

j=√(V(ni)・2・Σ|ci|2) /(2・Σ|ci|2)

=n/√(2・Σ|ci|2)

ここで、√Σ|ci|2は、ランダムなビット系列をパーシャルレスポンスチャネルで等化した場合の信号エネルギーに相当する。従って、SAMジッタjは、SN比に反比例していることがわかる。

【0011】

以上のように、PRMLをもちいたビット検出を行う場合、ビットエラーレートに対応する指標としては、振幅軸方向の揺らぎを取り込んだ指標を用いることが望ましいことがわかる。具体的には、正しいビット系列のパスメトリック、1ビット単独の誤りがあるビット系列のパスメトリックの差である差メトリックの標準偏差を、信号パワーで除算した指標、つまり上記SAMジッタが有効であることがわかる。

【発明の開示】

【発明が解決しようとする課題】

【0012】

ところで以上に述べたSAMジッタは、厳密なことを言えば、正しいビット系列がわかっている場合に定義することができる指標である。従って、正しいビット系列がわかっていない場合には定義することができない。そこで、上記特許文献1,2,3,4等では、ビット系列がわかっていない場合でもSAMジッタを定義する方法が提案されている。

これらの特許文献は、いずれも正しいビット系列のかわりに最終的に検出されたビット系列を正しいビット系列と仮定するものである。この仮定は、ビットエラーレートが、最悪でも10-3程度以内であるというような現行の光ディスクの一般的な条件の下では、十分に通用する仮定である。

【0013】

上述の仮定は、正しいビット系列としてどのビット系列を用いるか、についての仮定である。これに対して、1ビット単独誤りのあるビット系列としてどのビット系列を用いるか、についても決めることが必要である。

特許文献1,2,3は、それぞれ相違はあるが、いずれもテーブルを用いてこのビット系列を用意しているものとみなすことができる。つまり、最終的に検出された正しいと仮定されるビット系列に対して、このビット系列で表されるパスを構成するステート遷移のおのおので、誤りのあるビット系列をあらかじめ用意された1ビット誤りのパタンテーブルとステート遷移の対応を調べて、テーブルの結果をもとに推測するという方法である。このような構成ができる理由は、パスの比較選択を行った際に生き残りパスと比較されて消滅したパスが1ビットだけ異なるビット系列のパスであった、と仮定することから成り立っている。さらに、この仮定は、ビットエラーレートが、ほとんど1ビットの単独誤りであるというような現行の光ディスクでは一般的な条件の下では、十分に通用する仮定である。

【0014】

一方、特許文献4は、特許文献1,2、3と異なり、1ビット誤りであったか否かにかかわらず最終パスのステート遷移に対応したパス比較選択の差メトリックを検出し、その分布を評価する。この方法の場合、差メトリックの分布の中心値は、1ビット単独誤りであったか、そうでない別の誤り方だったのか、誤りの仕方によって、離散的な別々の異なる中心値をとっている。このため、分布指標として、通常のように、分散や標準偏差を評価する方法は使えない。しかしながら、1ビット誤りに由来する差メトリックの分布の中心がもっとも0に近い分布である、という仮定のもとでは、分布の左側のみをガウス分布で片側近似することができる。

この結果、このような方法を用いても、1ビット誤りに由来する差メトリックに対する分散や標準偏差を近似的に求めることができる。なお、1ビット誤りに由来する差メトリックの分布の中心がもっとも0に近い分布である、とは、言い換えると、1ビット誤りが2番目に小さいユークリッド距離のパスである、ということを意味している。(なお、最小ユークリッド距離のパスとは、ビタビ検出で検出される生き残りパスのことである。)

【0015】

ここで、特許文献1,2,3に開示された手法が有効であるための、ビットエラーレートの分布は1ビット単独誤りが支配的であるという仮定は、特許文献4の手法が有効であるための、1ビット単独誤りのパスが、2番目に小さいユークリッド距離のパスである、という仮定から得られる帰結でもある。

従って、特許文献1、2、3、4の各手法の全てが、1ビット単独誤りのパスが最小ユークリッド距離のパスであるという条件の下で有効となる方法である、とみなすことができる。

この場合、逆に、これらの手法が本当に有効かどうかを調べるためには、1ビット単独誤りが本当に2番目に小さいユークリッド距離のパスであるかを調べる必要がある。そこで、以下では、1ビット誤り、2ビット誤り、について、そのビット系列から得られるパーシャルレスポンス系列と、正しいビット系列から得られるパーシャルレスポンス系列との間のユークリッド距離を調べた。

【0016】

図15は、PR(1,1)、PR(1,2,1),PR(1,2,2,1)、PR(1,2,2,2,1)について1ビット誤り、2ビット誤りのビット系列のパーシャルレスポンス系列に対するユークリッド距離を調べた表である。

ここで2ビット誤りのうちで重要なものは、拘束長の中に2つ以上の誤りがあるようなものである。そのような例の中でも特に重要なのは、マーク長2のマーク(2Tマーク)の消滅あるいは出現による誤りと、2Tマークのシフトによる誤りである。従ってこの図15では、誤りの種類として、1ビット誤り、最短マークの消滅又は出現による2ビット誤り、及び最短マークシフトによる2ビット誤りの3種類を示している。

【0017】

図15において、00011000などと書かれている列は、誤りのあるビット系列と正しいビット系列の差分をとった列である。

即ち1ビット誤りの差分「00001000」は、例えば、誤りのあるビット系列「111110000」と正しいビット系列「111100000」の差分であり、つまり信号波形のエッジシフトによるエラーである。

また2ビット誤りとして示した差分「00011000」は、例えば誤りのあるビット系列「00000011」と正しいビット系列「000110011」の差分(或いはその正誤が反対の場合)などであり、つまり2Tマークの消滅あるいは出現による誤りである。

また同じく2ビット誤りとして示した差分「00010−1000」は、例えば誤りのあるビット系列「0000110000」と正しいビット系列「0001100000」の差分であり、即ち2Tマークがシフトした誤りである。

【0018】

この図15において、各ターゲットレスポンスで、ユークリッド距離が最小となる誤りの種類を比較すると、PR(1,1)、PR(1,2,1)、PR(1,2,2,1)では、1ビット単独誤りが最小である。ところがPR(1,2,2,2,1)では、最短マークのシフトによる2ビット誤りのユークリッド距離が「12」となってが最小である。つまり1ビット単独誤りの場合のユークリッド距離「14」より小さくなっている。

これはすなわち、PR(1,2,2,2,1)では、1ビット誤りの分布が左端の分布とはならず、また、1ビット誤りが誤りの支配的要因ではないことを示している。従って、特許文献4、および特許文献1,2,3の手法が有効に働くための条件をみたしていないことを意味している。

【0019】

以上は、PR(1,2,2,2,1)において、関連特許1,2,3,4があまり有効ではないことを示すものであるが、PR(1,2,2,1)においても、1ビット誤りのユークリッド距離「10」と、最短マークのシフト誤りのユークリッド距離「12」はそれほど離れているものではない。

従って、PR(1,2,2,1)では、1ビット誤りが支配的であるとはいえ、最短マークのシフト誤りが無視できるものかどうかは、ノイズの大きさにも大きく左右されるものである。

【0020】

以上を鑑みると、特許文献1,2,3のように、1ビット誤りのあるビット系列を決定する際に、検出されたビット系列に対して、誤りのあるビット系列をあらかじめ用意された1ビット誤りのテーブルをもとに推測するという方法は、ターゲットレスポンスがPR(1,2,2,2,1)の場合には適切ではない。また、ターゲットレスポンスがPR(1,2,2,1)の場合でもノイズが大きくなると必ずしも適切ではない。

また、特許文献4のように、差メトリックの分布のうち、1ビット誤りに相当すると考えられる分布の左端をガウス分布で片側近似を行う方法も、同様のことがいえる。

さらに、特許文献1,2,3,4の方法は、ビットシフトのような1ビット単独誤りに対しては、そのジッタの大きさを見積もることができるが、最短マークのシフト誤りに対しては、ジッタの大きさを見積もることもできない。

そこで、1ビット単独誤りに対するSAMジッタの検出確度を向上して、さらに、最短マークのシフト誤りなどに対してもSAMジッタを検出できるような新たな手法が必要となった。

【課題を解決するための手段】

【0021】

このような事情から本発明は、PRMLのビット検出によるビットエラーレートに直接相関のある指標を用いて信号評価を行うことを目的とし、特に1ビット単独誤りに対するSAMジッタ等の評価値の検出確度の向上や、最短マークのシフト誤り(2ビット誤り)などに対してもSAMジッタ等の評価値を検出できる手法を提供することを目的とする。

【0022】

本発明の最尤復号装置は、ビット情報を再生した再生信号からビタビ検出を行ってビット検出するビタビ検出手段と、上記ビタビ検出手段で生き残りパスの選択を行う際における生き残りパスと比較された消滅パスのパスメモリ間での違いである消滅パスの誤りの種類を示す情報を、パスメモリ比較情報として記憶するパスメモリ比較情報記憶手段と、上記ビタビ検出手段において最終的に生き残ったパスを構成しているステートでの差メトリックを得る差メトリック計算手段と、上記差メトリック計算手段により得られた差メトリックのうち、上記パスメモリ比較情報が同じ状態であるステートにおける差メトリックだけを選択する差メトリック選択手段と、上記差メトリック選択手段で選択された差メトリックの分布指標を計算して再生信号品質を評価する指標を得る評価値計算手段とを備える。

【0023】

上記パスメモリ比較情報とは、パスメモリの最新のビットから数えてc番目のビットを除いた1番目から2c−1番目までビットが一致しているか否か、即ち1ビット単独誤りであるか否かの情報である(cはビタビ検出器の拘束長)。

あるいは、上記パスメモリ比較情報とは、パスメモリの最新のビットから数えてc+d+1番目のビットが異なっていて、かつ、c、c+d+1番目のビットを除いた1番目から2c+2d−1番目までビットが一致しているか否か、即ち最短マークのシフト誤りか否かの情報である(dは上記ビタビ検出器の従う最小ランレングス規則における最小ランレングス)。

また上記パスメモリ比較情報記憶手段は、上記ビタビ検出手段でパスの比較が行われるステートにおいて、それぞれパスメモリ比較情報のビット数分のパスメモリ比較情報レジスタをパスメモリの長さと同じだけ用意し、上記パスメモリ比較情報レジスタをビットシフトするとともに、新たなパスメモリ比較情報を暫時追加して記憶するように構成される。

【0024】

また上記ビタビ検出手段は、拘束長c、最小ランレングスdの規則に従うビタビ検出手段であって、ランレングス制約に従うcビットで区別されるブランチのおのおのに対して、基準レベル、ブランチメトリックを記憶するレジスタ、及び上記各レジスタを更新する演算器から成るブランチメトリック計算ユニットと、ランレングス制約に従うc−1ビットで区別されるステートのおのおのに対して、パスメトリックを記憶するレジスタ、及び上記各レジスタを更新する演算器から成るパスメトリック更新ユニットと、ランレングス制約に従うc−1ビットで区別されるステートのおのおのに対して、パスメモリを記憶するレジスタ、及び上記各レジスタを更新する演算器から成るパスメモリ更新ユニットとが設けられる。そして上記パスメモリ更新ユニットは、上記パスメモリを記憶したレジスタからビット情報を決定して出力するとともに、上記ステートのうち、パスの比較選択を行うステートのおのおのについての上記パスメモリ比較情報を出力する。

ここで上記ブランチメトリック計算ユニットにおける演算器とは、上記ブランチに対応した基準レベルと、入力された信号の差の二乗(或いは、それに準ずる値として、入力された信号の二乗を減算した値)を計算し、それを上記ブランチメトリックを記憶するレジスタの値としてチャネルビットクロックごとに更新する演算器である。

また上記パスメトリック更新ユニットにおける演算器とは、上記ステートに到達するブランチのブランチメトリックと、そのブランチに接続されたステートのパスメトリックの加算演算と、上記加算演算をへたブランチのパスメトリックの大きさを比較する比較演算と、上記パスメトリックの小さいパスを選択して、そのパスメトリックを上記パスメトリックを記憶するレジスタの値としてチャネルビットクロックごとの更新を行う演算器である。

また上記パスメモリ更新ユニットにおける演算器とは、上記パスメトリック更新ユニットの演算器におけるパスの選択状況に応じて、選択されたパスの通過したステートのパスメモリにパスの選択状況を追加して、これを上記パスメモリを記憶するレジスタの値としてチャネルビットクロックごとに更新する演算器である。

また上記ビタビ検出手段は、上記再生信号をパーシャルレスポンス等化し、等化された再生信号からビタビ検出を行ってビット情報をPRML検出する。

ここで上記PRML検出におけるビタビ検出の各ブランチに対応した基準レベルは、上記ブランチを表すビット列に対して、ターゲットレスポンスを用いてパーシャルレスポンスを施して得られる基準レベルである。

また上記ターゲットレスポンスは、PR(1,2,2,1)、あるいはPR(1,2,2,2,1)である。

【0025】

上記差メトリックとは、上記ビタビ検出手段におけるパス選択に際して比較される2つのパスのパスメトリックの差分である。

また上記差メトリック計算手段において算出する上記差メトリックとは、消滅パスが1ビット単独誤りに対応するパスであった場合の差メトリックであって、上記ビタビ検出手段によって検出された拘束長分のビット列に同期した再生信号rnから数えてdクロック遡る再生信号rn-dまでのdチャネルクロック分の再生信号rn-1・・rn-dと、これらの再生信号に同期している生き残りパスのパーシャルレスポンス系列qn-1・・qn-dの間の差分に対して、パーシャルレスポンスの元での1チャネルクロックのパルスに対するdチャネルクロックのレスポンスp1・・pdとを順に掛け合わせた後に加算して得られる値であるΣpj・(rn-j−qn-j)である(ただし、Σはjが1からdになるまで項を加算)。

或いは、上記差メトリック計算手段において算出する上記差メトリックとは、消滅パスが最短マークのシフト誤りに対応するパスであった場合の差メトリックであって、上記ビタビ検出手段によって検出された拘束長分のビット列に同期した再生信号rnから数えてd+2クロック遡る再生信号rn-d-2までのdチャネルクロック分の再生信号rn-1・・rn-d-2と、これらの再生信号に同期している生き残りパスのパーシャルレスポンス系列qn-1・・qn-d-2の間の差分に対して、パーシャルレスポンスの元での1チャネルクロックのパルスに対するdチャネルクロックのレスポンスp1・・pdと、これより2クロックシフトしたレスポンスp-1・・pd-2の差分を順に掛け合わせた後に加算して得られる値であるΣ(pj−pj-2)・(rn-j−qn-j)である(ただし、Σはjが1からd+2になるまで項を加算)。

【0026】

また上記差メトリック選択手段は、上記ビタビ検出手段によって検出された拘束長分のビット列に同期した差メトリックのうち、上記拘束長分のビット列の一番新しいビットに同期しているパスメモリ比較情報記憶手段のパスメモリ比較情報が、所定の情報となっているときの差メトリックを選択する。

また上記評価値計算手段によって得られる上記再生信号品質を評価する指標とは、上記選択された差メトリックの標準偏差と、上記差メトリックの元となる2つの比較パスのユークリッド距離との比率である。

上記2つの比較パスのユークリッド距離とは、ターゲットレスポンスがPR(1,2,2,1)であって、パスメモリ比較情報が、パスメモリのc番目のビットを除いた1番目から2c−1番目までビットが一致しているか否かの情報である場合の比較パスのユークリッド距離10(=12+22+22+12)である。

又は、上記2つの比較パスのユークリッド距離とは、ターゲットレスポンスがPR(1,2,2,2,1)であって、パスメモリ比較情報が、パスメモリのc番目のビットを除いた1番目から2c−1番目までビットが一致しているか否かの情報である場合の比較パスのユークリッド距離14(=12+22+22+22+12)である。

又は、上記2つの比較パスのユークリッド距離とは、ターゲットレスポンスがPR(1,2,2,1)であって、パスメモリ比較情報が、パスメモリのc、c+d+1番目のビットを除いた1番目から2c+2d−1番目までビットが一致しているか否かの情報である場合の比較パスのユークリッド距離12(=12+22+(2−1)2+(2−1)2+22+12)である。

又は、上記2つの比較パスのユークリッド距離とは、ターゲットレスポンスがPR(1,2,2,2,1)であって、パスメモリ比較情報が、パスメモリのc、c+d+1番目のビットを除いた1番目から2c+2d−1番目までビットが一致しているか否かの情報である場合の比較パスのユークリッド距離12(=12+22+(2−1)2+(1−2)2+22+12)である。

【0027】

本発明の信号評価方法は、ビット情報を再生した再生信号の信号品質を評価する信号評価方法であって、上記再生信号からビタビ検出手段を用いてビット検出するビット検出ステップと、上記ビタビ検出手段で生き残りパスの選択を行う際における生き残りパスと比較された消滅パスのパスメモリ間での違いである消滅パスの誤りの種類を示す情報を、パスメモリ比較情報として記憶するパスメモリ比較情報記憶ステップと、上記ビタビ検出手段において最終的に生き残ったパスを構成しているステートでの差メトリックを得る差メトリック計算ステップと、上記差メトリック計算ステップにより得られる差メトリックのうち、上記パスメモリ比較情報が同じ状態であるステートにおける差メトリックだけを選択する差メトリック選択ステップと、上記差メトリック選択ステップで選択された差メトリックの分布指標を計算して再生信号品質を評価する指標を得る評価値計算ステップとを備える。

【0028】

このような本発明は、次の考え方に基づく。

上述した課題は、上記特許文献1,2,3,4がいずれも、検出されたビット系列だけをもとに、1ビット単独誤りのパスに対する差メトリックの分布指標を算出しようとしている点から生じている問題である。すなわち、比較された消滅パスを常に1ビット単独誤りであったと仮定しているために生じている問題である。

従って、実際に、パスメトリックの大小比較を行った際に、生き残りパスと比較されて消滅したパスが1ビット誤りのパスであったのかどうかを確認することで、この問題は解決できる。さらに、生き残りパスと消滅パスのパスメモリの違いが、どのような違いであったのかを分類すれば、1ビット単独誤りに対するSAMジッタだけではなく、より、一般的な誤り、たとえば、最短マークのシフト誤り、などでもSAMジッタを定義することができる。

そこで本発明では、ビタビ検出で生き残りパスの選択の際、生き残りパスと比較された消滅パスのパスメモリ間での違い、即ち消滅パスの誤りの種類を示す情報(パスメモリ比較情報)を記憶し、最終的に生き残ったパスを構成しているステートでの差メトリックのうち、パス選択の際に消滅したパスが同じ種類の誤りとなっている、つまりパスメモリ比較情報が同じ状態であるステートの差メトリックのみを選択して、その差メトリックの分布指標(分散、標準偏差)を計算する。ここで、誤りの種類を示す情報とは、たとえば、消滅パスと生き残りパスのパスメモリの違いが、1ビットだけ異なるようなシフトエラーであるか否か、あるいは、2ビット異なる最短マークシフトのエラーであるか否か、の情報である。

【発明の効果】

【0029】

本発明によれば、生き残りパスと比較された消滅パスが、1ビット誤りに相当するパスであったのか、あるいは、最短マークのシフトエラー誤りに相当するパスであったのか、さらに、特定の長さのマークのシフトエラー誤りに相当するパスであったのか、などの誤りの種類に応じて、それぞれ別々に差メトリックを算出し、そのSAMジッタを検出することができる。

従って、まず、PR(1,2,2,2,1)のPRMLビット検出に対する従来の手法では検出することができなかった、誤りの中で最も支配的な最短マークのシフト誤りに対する選択的な差メトリックの標準偏差を求めることができる。

また、上記と同様、従来の手法で検出することのできなかった2番目に支配的な1ビット単独誤りに対する選択的な差メトリックの標準偏差を求めることができる。

次に、PR(1,2,2,1)のPRMLビット検出においても、誤りの中でもっとも支配的な1ビット単独誤りに対する選択的な差メトリックの標準偏差の検出を従来の検出法よりも、高い精度で実現することができる。

また、従来の手法では実現できなかった誤りの中で2番目に支配的である最短マークのシフト誤りについても、その差メトリックを選択的に検出して標準偏差を求めることができる。

このように、精度の高い信号品質の評価方法は、昨今の記録情報の高密度化の流れにおいて強く求められる技術であり、非常に有用となる。

さらに、このように誤りの種類に応じた選択的な評価を簡便に実現することは、特に記録補償のようなビット系列のパタンに応じたマーク長の補償を行う際にもきわめて重要となる。これらのことから、本発明は情報記録再生システムにおける信号品質評価の方法として非常に有用となる。

【発明を実施するための最良の形態】

【0030】

以下、本発明の実施の形態を説明する。

図1は、実施の形態の再生装置の概要を表すブロック図である。

図1に示すように、本例の再生装置は、光ディスクなどの記録媒体90、この記録媒体90からビット情報を再生する光ピックアップ1、光ピックアップ1で読み取られた信号を再生信号(RF信号)に変換するプリアンプ2、再生信号をA/D変換するA/D変換器3、PLL処理のために再生信号の波形を整えるイコライザ4、再生信号からクロックを再生するPLL回路5、再生信号からビット情報を検出するPRML検出器6、PRML検出器6からの情報を元に信号品質を評価する値としてSAMジッタ値を算出する信号評価器7、ビット情報を復調するRLL(1−7)pp復調器などの復調器8、復調された情報の誤り訂正を行うRSデコーダ9、誤り訂正された情報を処理してアプリケーションデータを再生するCPUブロック10などで構成されている。

【0031】

光ピックアップ1、プリアンプ2を通して再生された再生信号(RF)は、A/D変換器3で数値化サンプリングされる(RF(Sampled))。このサンプリングは、PLL回路5で再生されたチャネルビットに同期したクロックと同じタイミングで行われる。

サンプリングされた再生信号のサンプリング情報は、イコライザ4で波形を整えられた後、PRML検出器6に入力されて、ビット情報が判定される。

ここでは、PRMLは、記録時の変調方式の制約に従ってD1制約(最小ランレングスd=1で最短マーク長が2T)を満たすように構成し、さらに、PRMLのターゲットレスポンスはPR(1,2,2,1)か、あるいはPR(1,2,2,2,1)であるとする。

このPRML検出器6で得られたビット情報は、復調器8で記録時の変調方式に従って復調され、さらに、RSデコーダ9でECCブロックのリード・ソロモン符号を復号して誤りを訂正し、CPUブロック10はEDCブロックにおける誤り検出符号に誤りが検出されていないことを確認することで、もとのアプリケーションデータを復元する。

【0032】

なお、本例のPRML検出器6は、信号品質評価指標を検出できるように、その構成において通常のPRML検出器と若干異なるものとされる。具体的には、PRML検出器6内のパスメモリ更新ユニットが新規な構成となる。その構成は後述する。

また、信号評価器7では、PRML検出器6内のイコライザ(後述)から得られる再生信号と、PRML検出器6から得られる消滅パスの誤り情報をもとに、これをゲートとして所定の誤りに対応した信号品質指標(SAMジッタ)を検出する。この信号品質指標によりジッタ評価がなされる。

本発明の実施の形態としては、以下説明していくように、このPRML検出器6と、PRML検出器6からの情報を元に信号品質を評価する信号評価器7、及びこれらによる信号評価方法を特徴とするものである。

【0033】

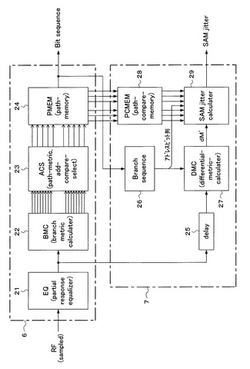

図2は、図1に示したPRML検出器6、及び信号評価器7の構成を表している。

PRML検出器6は、チャネルレスポンスをターゲットレスポンスに等化する波形等化器(イコライザ)21と、このイコライザ21の出力からビタビ検出器の各ブランチに対してブランチメトリックを計算するブランチメトリック計算ユニット(BMC)22と、ブランチメトリックを取り込んでブランチを比較してパスの選択を行いパスメトリックの更新を行うパスメトリック更新ユニット(ACS)23と、選択されたパス情報に従いパスメモリの更新を行うパスメモリ更新ユニット24によって構成される。

また信号評価器7は、パスメモリの比較情報を記憶更新するパス比較メモリ更新ユニット28と、再生信号をビット検出に同期するように遅延させる遅延回路25と、パス比較の際の差メトリックdMに相当する値dM’を算出する差メトリック計算ユニット(DMC)27と、得られた差メトリックdM’を前記パス比較情報に基づいて選択してその標準偏差を計算するジッタ計算ユニット29と、差メトリック計算ユニット27に算出用のビット列を与え、またジッタ計算ユニット29にアドレスビット列を与えるブランチシーケンス26を有して構成されている。

【0034】

この図2におけるイコライザ21の役割は、チャネルレスポンスをPR(1,2,2,1)、あるいは、PR(1,2,2,2,1)のターゲットに等化することである。ターゲットレスポンスは、必ずしもこれに限るものではなく、たとえば、D2制約(最小ランレングスd=2で最短マーク長が3T)のときは、より拘束長の長いターゲットが用いられる。

ここでは、PR(1,2,2,2,1)のような5タップの拘束長を有するものに説明を絞るものとする。最小ランレングス規則としてのD1制約(最小ランレングスd=1で最短マーク長が2T)がある場合、ブランチメトリック計算ユニット22,パスメトリック更新ユニット23、パスメモリ更新ユニット24を有するビタビ検出器6は、4ビットで構成される10個のステートと、5ビットで構成される16のブランチが用意され、これらのブランチが、ステートの間をD1制約に従って接続するように構成されている。

【0035】

ここで、4ビットで構成される10個のステートとは、4ビットで構成される16個のビット列0000、0001、0010、0011、0100、0101、0110、0111、1000、1001、1010、1011、1100、1101、1110、1111のうち、D1制約、すなわち、0、1が単独で現れないという制約(上記の4ビットのビット列では、4ビットの中の真ん中の2ビットに単独で現れない)を満たす10のビット列0000、0001、0011、0110、0111、1000、1001、1011、1100、1110、1111で区別される状態のことである。

また、5ビットで構成される16個のブランチとは、5ビットで構成される32個のビット列00000、00001、00010、00011、00100、00101、00110、00111、01000、01001、01010、01011、01100、01101、01110、01111、10000、10001、10010、10011、10100、10101、10110、10111、11000、11001、11010、11011、11100、11101、11110、11111、のうち、D1制約、すなわち、0、1が単独で現れないという制約(上記の5ビットのビット列では、5ビットの中の真ん中の3ビットに単独で現れない)を満たす16のビット列、00000、00001、00011、00110、00111、01100、01110、01111、10000、10001、10011、11000、11001、11100、11110、11111、で区別される状態のことである。

なお、ターゲットレスポンスがPR(1,2,2,1)の場合は、3ビットで構成される6個のステートと、4ビットで構成される10のブランチが用意されて、D1制約に従ってブランチがステートを接続する。

このステートと、ブランチのビット列の作り方は、PR(1,2,2,2,1)でのステート、ブランチのビット列の作り方と同様である。

【0036】

ブランチメトリック計算ユニット22では、16のブランチに対してブランチメトリックが計算されて、その結果が、パスメトリック更新ユニット23に転送される。

パスメトリック更新ユニット23では、10のステートに対して、そのステートに到達するパスメトリックが更新されると同時に、パスの選択情報が、パスメモリ更新ユニット24に転送される。

パスメモリ更新ユニット24では、10のステートに対して、そのステートに到達するパスメモリが更新されると同時に、そのうちパスの比較が行われる6つのステートにおけるパスの比較情報が、パス比較メモリ更新ユニット28に転送される。また、パスメモリ更新ユニット24では、パスメモリに記憶されているビット系列は、パスの選択を繰り返しながら尤もらしい系列に収束していく。その結果が、ビタビ検出器6による検出結果のビットシーケンスとして出力される。

パス比較メモリ更新ユニット28では、パス比較の行われる6つのステートに対して、パス比較情報を記憶するパス比較情報レジスタ(シフトレジスタ)が用意されて、暫時シフトしながら、パスメモリ更新ユニット24から出力されたパス比較情報を追加していく。

ジッタ計算ユニット29では、パス比較メモリ更新ユニット28から与えられるパス比較情報に基づいて、差メトリック計算ユニット27から供給される差メトリックdM’のうち、消滅パスが所定の誤りの種類(たとえば、1ビット単独誤りや、最短マークのシフトによる2ビット誤りなど)に対応しているものだけを選択して、その差メトリックdM’の標準偏差を計算する。なお、計算結果は、上記の誤りの種類に対応して得られるユークリッド距離で規格化することが望ましい。

【0037】

図3に、PRMLのターゲットレスポンスに等化するために用いるイコライザ21の構成を示す。

本実施の形態におけるイコライザ21は、フリップフロップ31A〜31G、掛け算器32A〜32H、および加算器33によって構成され、波形等化フィルタを成している。

入力された再生信号(図1のイコライザ4からPRML検出器6に供給される再生信号RF(Sampled))は、フリップフロップ31A〜31Gを経て、チャネルクロックで1クロックずつ遅延した8つの信号に分岐される。

次に、分岐された8つの信号は、それぞれ掛け算器32A〜32Hによって、それぞれ異なる倍率で増幅される。

最後にこれらの掛け算器32A〜32Hによって増幅された各信号は、加算器33によって加算されて、その出力が等化信号として出力される。

ここで、掛け算器32A〜32Hの係数は、等化信号のターゲットレスポンスに対する等化誤差が最小となるような係数を用いている。この係数は、たとえばLMSアルゴリズムなどで自動的にもとまるようにすることが望ましい。

【0038】

なお、この図3の例は、8クロックはなれた信号を用いた8タップのイコライザの場合である。このタップ数は、必ずしも8つである必要はなく、より精度よく符号間干渉を取り除くのであればさらに増やしたり、あるいは、規模を小さくするならこれよりも減らしたりして、目的に応じて変更されればよい。

【0039】

図4は、PR(1,2,2,2,1)をターゲットレスポンスとするPRML検出器6におけるブランチメトリック計算ブロック22の構成である。

本実施の形態におけるブランチメトリック計算ユニット22は、基準値レジスタ41A〜41P、減算器42A〜42P、掛け算器43A〜43P、ブランチメトリックレジスタ44A〜44Pを有している。

このブランチメトリック計算ユニット22には、まず上述のイコライザ21を経て得られた等化信号qnが入力される。

基準値レジスタ41Aはビット列00000に対応する基準レベルr00000を記憶する。

基準値レジスタ41Bはビット列00001に対応する基準レベルr00001を記憶する。

基準値レジスタ41Cはビット列00011に対応する基準レベルr00011を記憶する。

基準値レジスタ41Dはビット列10000に対応する基準レベルr10000を記憶する。

基準値レジスタ41Eはビット列10001に対応する基準レベルr10001を記憶する。

基準値レジスタ41Fはビット列10011に対応する基準レベルr10011を記憶する。

基準値レジスタ41Gはビット列00110に対応する基準レベルr00110を記憶する。

基準値レジスタ41Hはビット列00111に対応する基準レベルr00111を記憶する。

基準値レジスタ41Iはビット列11000に対応する基準レベルr11000を記憶する。

基準値レジスタ41Jはビット列11001に対応する基準レベルr11001を記憶する。

基準値レジスタ41Kはビット列01100に対応する基準レベルr01100を記憶する。

基準値レジスタ41Lはビット列01110に対応する基準レベルr01110を記憶する。

基準値レジスタ41Mはビット列01111に対応する基準レベルr01111を記憶する。

基準値レジスタ41Nはビット列11100に対応する基準レベルr11100を記憶する。

基準値レジスタ41Oはビット列11110に対応する基準レベルr11110を記憶する。

基準値レジスタ41Pはビット列11111に対応する基準レベルr11111を記憶する。

なお、ここではパーシャルレスポンスのクラスをPR(1,2,2,2,1)としているので、もとのビット値を±1/2として、各基準レベルは、

r00000=−4、

r00001=−3、

r00011=−1、

r10000=−3、

r10001=−2、

r10011=0、

r00110=0、

r00111=+1、

r11000=−1、

r11001=0、

r01100=0、

r01110=+2、

r01111=+3、

r11100=+1、

r11110=+3、

r11111=+4、

となる。

【0040】

ブランチメトリックレジスタ44Aは、信号qnと基準レベルr00000の間のブランチメトリックm00000を記憶する。

ブランチメトリックレジスタ44Bは、信号qnと基準レベルr00001の間のブランチメトリックm00001を記憶する。

ブランチメトリックレジスタ44Cは、信号qnと基準レベルr00011の間のブランチメトリックm00011を記憶する。

ブランチメトリックレジスタ44Dは、信号qnと基準レベルr10000の間のブランチメトリックm10000を記憶する。

ブランチメトリックレジスタ44Eは、信号qnと基準レベルr10001の間のブランチメトリックm10001を記憶する。

ブランチメトリックレジスタ44Fは、信号qnと基準レベルr10011の間のブランチメトリックm10011を記憶する。

ブランチメトリックレジスタ44Gは、信号qnと基準レベルr00110の間のブランチメトリックm00110を記憶する。

ブランチメトリックレジスタ44Hは、信号qnと基準レベルr00111の間のブランチメトリックm00111を記憶する。

ブランチメトリックレジスタ44Iは、信号qnと基準レベルr11000の間のブランチメトリックm11000を記憶する。

ブランチメトリックレジスタ44Jは、信号qnと基準レベルr11001の間のブランチメトリックm11001を記憶する。

ブランチメトリックレジスタ44Kは、信号qnと基準レベルr01100の間のブランチメトリックm01100を記憶する。

ブランチメトリックレジスタ44Lは、信号qnと基準レベルr01110の間のブランチメトリックm01110を記憶する。

ブランチメトリックレジスタ44Mは、信号qnと基準レベルr01111の間のブランチメトリックm01111を記憶する。

ブランチメトリックレジスタ44Nは、信号qnと基準レベルr11100の間のブランチメトリックm11100を記憶する。

ブランチメトリックレジスタ44Oは、信号qnと基準レベルr11110の間のブランチメトリックm11110を記憶する。

ブランチメトリックレジスタ44Pは、信号qnと基準レベルr11111の間のブランチメトリックm11111を記憶する。

【0041】

基準値レジスタ41Aからブランチメトリックレジスタ44A、

基準値レジスタ41Bからブランチメトリックレジスタ44B、

基準値レジスタ41Cからブランチメトリックレジスタ44C、

基準値レジスタ41Dからブランチメトリックレジスタ44D、

基準値レジスタ41Eからブランチメトリックレジスタ44E、

基準値レジスタ41Fからブランチメトリックレジスタ44F、

基準値レジスタ41Gからブランチメトリックレジスタ44G、

基準値レジスタ41Hからブランチメトリックレジスタ44H

基準値レジスタ41Iからブランチメトリックレジスタ44I、

基準値レジスタ41Jからブランチメトリックレジスタ44J、

基準値レジスタ41Kからブランチメトリックレジスタ44K、

基準値レジスタ41Lからブランチメトリックレジスタ44L、

基準値レジスタ41Mからブランチメトリックレジスタ44M、

基準値レジスタ41Nからブランチメトリックレジスタ44N、

基準値レジスタ41Oからブランチメトリックレジスタ44O、

基準値レジスタ41Pからブランチメトリックレジスタ44P、

にいたる過程には、それぞれ減算器42(42A〜42P)と掛け算器43(43A〜43P)が一つずつ用意されている。

各減算器(42A〜42P)では、入力信号qnと、対応するレジスタ(41A〜41P)から得られた基準レベルの信号を入力し、その差分を出力する。

また、各掛け算器(43A〜43P)は、対応する減算器(42A〜42P)から出力された差分を二乗した値を出力する。このそれぞれの掛け算器(43A〜43P)から出力された値が、各ブランチメトリックレジスタ(44A〜44P)において記憶されるブランチメトリックm00000〜m11111となる。

なお、掛け算器43のかわりに絶対値計算器を配してもよい。

【0042】

以上のようにして得られて各ブランチメトリックレジスタ44A〜44Pに記憶されたブランチメトリックm00000〜m11111は、チャネルビットクロック毎に更新されるとともに、次段のパスメトリック更新ユニット23に出力される。

なお、ブランチメトリックの計算方法として、掛け算器43の容量を削減するために、j番目のブランチメトリックmjをmj=rj・(2qn−rj)、(ただし、rjはj番目の基準レベル)、を用いる方法でもよい。

【0043】

図5は、PR(1,2,2,2,1)をターゲットレスポンスとするPRML検出器6におけるパスメトリック更新ユニット23を示している。

図5のパスメトリック更新ユニット23は、パスメトリックレジスタ51A〜51J、及び52A〜52Jと、フリップフロップ53A〜53Jを有して構成されている。

【0044】

パスメトリックレジスタ51Aには、ステートs0000における生き残りパスのパスメトリックpm0000が記憶されている。パスメトリックレジスタ52Aでは、ステートs0000に至るパスのパスメトリックpm00000=pm0000+m00000、pm10000=pm1000+m10000のうち小さい値が選択される。

ここで、上記パスメトリック値を計算するためのメトリックm00000、m10000は図4のブランチメトリック計算ユニット22から入力される。図5においてブランチメトリック{mijklm}として示しているのは、図4のブランチメトリックレジスタ44A〜44Pから供給されるブランチメトリックm00000〜m11111のことである。

フリップフロップ53Aによってラッチされたパスメトリックレジスタ52Aの値は、パスメトリックレジスタ51Aの値として記憶される。

【0045】

パスメトリックレジスタ51Bには、ステートs0001における生き残りパスのパスメトリックpm0001が記憶されている。パスメトリックレジスタ52Bでは、ステートs0001に至るパスのパスメトリックpm00001=pm0000+m00001、pm10001=pm1000+m10001のうち小さい値が選択される。ここで、上記パスメトリック値を計算するためのメトリックm00001、m10001はブランチメトリック計算ユニット22から入力される。フリップフロップ53Bによってラッチされたパスメトリックレジスタ52Bの値は、パスメトリックレジスタ51Bの値として記憶される。

パスメトリックレジスタ51Cには、ステートs1000における生き残りパスのパスメトリックpm1000が記憶されている。パスメトリックレジスタ52Cには、ステートs1000に至るパスのパスメトリックpm11000=pm1100+m11000が記憶されている。このパスメトリック値を計算するためのメトリックm11000はブランチメトリック計算ユニット22から入力される。フリップフロップ53Cによってラッチされたパスメトリックレジスタ52Cの値は、パスメトリックレジスタ51Cの値として記憶される。

パスメトリックレジスタ51Dには、ステートs1001における生き残りパスのパスメトリックpm1001が記憶されている。パスメトリックレジスタ52Dには、ステートs1001に至るパスのパスメトリックpm11001=pm1100+m11001が記憶されている。このパスメトリック値を計算するためのメトリックm11001はブランチメトリック計算ユニット22から入力される。フリップフロップ53Dによってラッチされたパスメトリックレジスタ52Dの値は、パスメトリックレジスタ51Dの値として記憶される。

パスメトリックレジスタ51Eには、ステートs0011における生き残りパスのパスメトリックpm0011が記憶されている。パスメトリックレジスタ52Eでは、ステートs0011に至るパスのパスメトリックpm00011=pm0001+m00011、pm10011=pm1001+m10011のうち小さい値が選択される。パスメトリック値を計算するためのメトリックm00011、m10011はブランチメトリック計算ユニット22から入力される。フリップフロップ53Eによってラッチされたパスメトリックレジスタ52Eの値は、パスメトリックレジスタ51Eの値として記憶される。

パスメトリックレジスタ51Fには、ステートs1100における生き残りパスのパスメトリックpm1100が記憶されている。パスメトリックレジスタ52Fでは、ステートs1100に至るパスのパスメトリックpm01100=pm0110+m01100、pm11100=pm1110+m11100のうち小さい値が選択される。パスメトリック値を計算するためのメトリックm01100、m11100は、ブランチメトリック計算ユニット22から入力される。フリップフロップ53Fによってラッチされたパスメトリックレジスタ52Fの値は、パスメトリックレジスタ51Fの値として記憶される。

パスメトリックレジスタ51Gには、ステートs0110における生き残りパスのパスメトリックpm0110が記憶されている。パスメトリックレジスタ52Gには、ステートs0110に至るパスのパスメトリックpm00110=pm0011+m00110が記憶されている。このパスメトリック値を計算するためのメトリックm00110は、ブランチメトリック計算ユニット22から入力される。フリップフロップ53Gによってラッチされたパスメトリックレジスタ52Gの値は、パスメトリックレジスタ51Gの値として記憶される。

パスメトリックレジスタ51Hには、ステートs0111における生き残りパスのパスメトリックpm0111が記憶されている。パスメトリックレジスタ52Hには、ステートs0111に至るパスのパスメトリックpm00111=pm0011+m00111が記憶されている。このパスメトリック値を計算するためのメトリックm00111は、ブランチメトリック計算ユニット22から入力される。フリップフロップ53Hによってラッチされたパスメトリックレジスタ52Hの値は、パスメトリックレジスタ51Hの値として記憶される。

パスメトリックレジスタ51Iには、ステートs1110における生き残りパスのパスメトリックpm1110が記憶されている。パスメトリックレジスタ52Iでは、ステートs1110に至るパスのパスメトリックpm01110=pm0111+m01110、pm11110=pm1111+m11110のうち小さい値が選択される。これらのパスメトリック値を計算するためのメトリックm01110、m11110はブランチメトリック計算ユニット22から入力される。フリップフロップ53Iによってラッチされたパスメトリックレジスタ52Iの値は、パスメトリックレジスタ51Iの値として記憶される。

パスメトリックレジスタ51Jには、ステートs1111における生き残りパスのパスメトリックpm1111が記憶されている。パスメトリックレジスタ52Jでは、ステートs1111に至るパスのパスメトリックpm01111=pm0111+m01111、pm11111=pm1111+m11111のうち小さい値が選択される。これらのパスメトリック値を計算するためのメトリックm01111、m11111はブランチメトリック計算ユニット22から入力される。フリップフロップ53Jによってラッチされたパスメトリックレジスタ52Jの値は、パスメトリックレジスタ51Jの値として記憶される。

【0046】

以上のようにして、各ステートにおける、そのステートにいたるまでのパスメトリックが更新される。

一方、各ステートでのパスの選択情報を図5において{Sijkl}として示しているが、このパス選択情報{Sijkl}は、次に述べるパスメモリ更新ユニット24に出力される。

【0047】

図6は、PR(1,2,2,2,1)をターゲットレスポンスとするPRML検出器6におけるパスメモリ更新ユニット24を示している。

図6のパスメモリ更新ユニット24は、パスメモリレジスタ61A〜61J、62A〜62Jと、フリップフロップ63A〜63Jによって構成されている。

なお図6においては、上記パスメトリック更新ユニット23から供給されるパス選択情報を{Sijkl}として示している。

【0048】

パスメモリレジスタ61Aには、ステートs0000における生き残りパスのパスメモリM0000が記憶されている。パスメモリレジスタ62Aでは、ステートs0000に至る2つのパスのパスメモリM0000、M1000うち、パスメトリックが小さくなるパスのパスメモリを選択し、選択されたメモリ値を2倍して0を加算して記憶する。このパスの選択情報は、図5のパスメトリック更新ユニット23におけるステートs0000での比較結果を元にしている。フリップフロップ63Aによってラッチされたパスメモリレジスタ62Aの値は、パスメモリレジスタ61Aの値として記憶される。

パスメモリレジスタ61Bには、ステートs0001における生き残りパスのパスメモリM0001が記憶されている。パスメモリレジスタ62Bでは、ステートs0001に至る2つのパスのパスメモリM0000、M1000うち、パスメトリックが小さくなるパスのパスメモリを選択し、選択されたメモリ値を2倍して1を加算して記憶する。このパスの比較情報は、パスメトリック更新ユニット23におけるステートs0001での比較結果を元にしている。フリップフロップ63Bによってラッチされたパスメモリレジスタ62Bの値は、パスメモリレジスタ61Bの値として記憶される。

パスメモリレジスタ61Cには、ステートs1000における生き残りパスのパスメモリM1000が記憶されている。パスメモリレジスタ62Cでは、ステートs1000に至るパスのパスメモリM1100を2倍し、0を加算して記憶する。フリップフロップ63Cによってラッチされたパスメモリレジスタ62Cの値は、パスメモリレジスタ61Cの値として記憶される。

パスメモリレジスタ61Dには、ステートs1001における生き残りパスのパスメモリM1001が記憶されている。パスメモリレジスタ62Dでは、ステートs1001に至るパスのパスメモリM1100を2倍し、1を加算して記憶する。フリップフロップ63Dによってラッチされたパスメモリレジスタ62Dの値は、パスメモリレジスタ61Dの値として記憶される。

パスメモリレジスタ61Eには、ステートs0011における生き残りパスのパスメモリM0011が記憶されている。パスメモリレジスタ62Eでは、ステートs0011に至る2つのパスのパスメモリM0001、M1001のうち、パスメトリックが小さくなるパスのパスメモリを選択し、選択されたメモリ値を2倍して1を加算して記憶する。このパスの選択情報は、図5のパスメトリック更新ユニット23におけるステートs0011での比較結果を元にしている。フリップフロップ63Eによってラッチされたパスメモリレジスタ62Eの値は、パスメモリレジスタ61Eの値として記憶される。

パスメモリレジスタ61Fには、ステートs1100における生き残りパスのパスメモリM1100が記憶されている。パスメモリレジスタ62Fでは、ステートs1100に至る2つのパスのパスメモリM0001、M1001のうち、パスメトリックが小さくなるパスのパスメモリを選択して、選択されたメモリ値を2倍して0を加算し、記憶する。このパスの選択情報は、パスメトリック更新ユニット23におけるステートs1100での比較結果を元にしている。フリップフロップ63Fによってラッチされたパスメモリレジスタ62Fの値は、パスメモリレジスタ61Fの値として記憶される。

パスメモリレジスタ61Gには、ステートs0110における生き残りパスのパスメモリM0110が記憶されている。パスメモリレジスタ62Gでは、ステートs0110に至るパスのパスメモリM0011を2倍して0を加算し記憶する。フリップフロップ63Gによってラッチされたパスメモリレジスタ62Gの値は、パスメモリレジスタ61Gの値として記憶される。

パスメモリレジスタ61Hには、ステートs0111における生き残りパスのパスメモリM0111が記憶されている。パスメモリレジスタ62Hでは、ステートs0111に至るパスのパスメモリM0011を2倍して1を加算し、記憶する。フリップフロップ63Hによってラッチされたパスメモリレジスタ62Hの値は、パスメモリレジスタ61Hの値として記憶される。

パスメモリレジスタ61Iには、ステートs1110における生き残りパスのパスメモリM1110が記憶されている。パスメモリレジスタ62Iでは、ステートs1110に至る2つのパスのパスメモリM0111、M1111のうち、パスメトリックの小さくなるパスのパスメモリを選択して、選択したメモリ値を2倍して0を加算して記憶する。このパスの選択情報は、パスメトリック更新ユニット23におけるステートs1110での比較結果を元にしている。フリップフロップ63Iによってラッチされたパスメモリレジスタ62Iの値は、パスメモリレジスタ61Iの値として記憶される。

パスメモリレジスタ61Jには、ステートs1111における生き残りパスのパスメトリックM1111が記憶されている。パスメモリレジスタ62Jでは、ステートs1111に至る2つのパスのパスメモリM0111、M1111のうち、パスメトリックの小さくなるパスのパスメモリを選択して、選択したメモリ値を2倍して1を加算し、記憶する。このパスの選択情報は、パスメトリック更新ユニット23におけるステートs1111での比較結果を元にしている。フリップフロップ63Jによってラッチされたパスメモリレジスタ62Jの値は、パスメモリレジスタ61Jの値として記憶される。

【0049】

以上のパスメモリ更新ユニット24に記憶されているビット系列は、上述のパスの選択を繰り返しながら、最終的に尤もらしいビット系列に収束していく。収束するまでにかかる時間は、拘束長の5倍程度といわれている。従って、パスメモリを30ビットのシフトレジスタで構成すれば、パスメモリのうち上位のビットは、収束している。従って、PRML検出器6では、ステートs1111のパスメモリの最上位のビット(MSB)を選択して、これをビット検出結果として出力する。

【0050】

このようにD1制約、ターゲットレスポンスPR(1,2,2,2,1)のPRML検出器6が構成されるが、本例では、特に図6に示すようにパスメモリ更新ユニット24において、パスの選択が行われる6つのステートにおけるパスメモリの比較情報を検出して、出力するように変更を行う。

つまり図6においてパスメモリレジスタ62A、62B、62E、62F、62I、62Jにおいてはパスメモリの選択が行われるが、これらにおいて選択対象となる2つのパスメモリの比較情報を、それぞれ出力する。図6において、出力される6個のパスメモリ比較情報を{cijkl}として示している。

このパスメモリ比較情報{cijkl}は、比較された消滅パスが1ビット単独誤りか、最短マークのシフトによる2ビット誤りとなっているかどうか、の情報である。換言すれば、ビタビ検出で生き残りパスの選択を行う際に、生き残りパスと比較された消滅パスのパスメモリが持っている誤りの種類を示す情報である。

このパスメモリ比較情報を検出する方法を説明する。

【0051】

比較消滅パスが1ビット単独誤りとなっているような場合のパスの選択情報は、2つの比較パスのパスメモリの最新のビットから数えてc番目のビットを除いた1番目から2c−1番目までビットが一致しているか否かの情報である。これはターゲットレスポンスがPR(1,2,2,2,1)であるような拘束長が5のPRML検出では、パスメモリの下位(最新ビット)から数えて5番目のビットを除いた1番目から9番目のビットが一致しているかどうかの情報に相当する。

図7は、その様子を説明する図である。

この図において、実線で表された信号は、最終的に検出されるパスをパーシャルレスポンス系列で表した図であり、また、点線で表された信号は、上記パスと比較された1ビット誤りのパスをパーシャルレスポンス系列で表した図である。

ここで、信号の各点は、チャネルクロックに同期して行われるサンプリングのタイミングを表している。

サンプリングとサンプリングの間のタイミングは、丁度ステートのタイミングに相当するので、ステートの種類を図に示した。

図に示したように、最終検出パスは、s0000、s0001、s0011、s0111、s1111、s1111と遷移している。この結果、最後のステートにおいてパスメモリは、・・・・000011111となっている。

一方、消滅パスは、s0000、s0000、s0001、s0011、s0111、s1111と遷移している。この結果、最後のステートにおいてパスメモリは、・・・・・000001111となっている。

従って、この2つのパスメモリは、5番目のビットを除いて少なくとも1番目から9番目のビットが一致していることがわかる。

ほかの遷移においても同様、1ビットの単独誤りがある場合は、5番目のビットを除いて少なくとも1番目から9番目のビットが一致していることが確認できる。

従って、パスの選択情報として、パス比較の行われるステートのそれぞれで、2つの比較パスの下位(最新ビット)から数えて5番目のビットを除いた1番目から9番目のビットが一致している場合を1、一致していない場合を0とするような情報を出力するように構成すればよい。

【0052】

次に、比較パスが最短マークシフトエラーによる2ビット誤りとなるような場合のパスの選択情報は、2つの比較パスのパスメモリの最新のビットから数えてc+d+1番目のビットが異なっていて、かつ、c、c+d+1番目のビットを除いた1番目から2c+2d−1番目までビットが一致しているか、否かの情報である。これは最短マークのマーク長(最短ランレングス+1)が2で、ターゲットレスポンスがPR(1,2,2,2,1)であるような本例のPRML検出では、この情報は、パスメモリの5番目のビットを除いた1番目から9番目のビットが一致しているかどうかの情報に相当する。

図8は、その様子を模式的に表した図である。

この図において、実線で表された信号は、最終的に検出されるパスをパーシャルレスポンス系列で表した図であり、また、点線で表された信号は、上記パスと比較された1ビット誤りのパスをパーシャルレスポンス系列で表した図である。

ここで、信号の各点は、チャネルクロックに同期して行われるサンプリングのタイミングを表している。

サンプリングとサンプリングの間のタイミングは、丁度ステートのタイミングに相当するので、図7と同様にステートの種類を図示した。

この図8に示したように、最終検出パスは、s0000、s0001、s0011、s0110、s1100、s1000、s0000、s0000と遷移している。この結果、最後のステートにおいてパスメモリは、・・・・00001100000となっている。

一方、消滅パスは、s0000、s0000、s0001、s0011、s0110、s1100、s1000、s0000と遷移している。この結果、最後のステートにおいてパスメモリは、・・・・・00000110000となっている。

この2つのパスメモリは、5番目と7番目のビットが異なっており、それ以外の少なくとも1番目から11番目のビットが一致していることがわかる。

ほかの遷移においても同様、最短マークのシフト誤りがある場合は、5、7番目のビットが異なり、それ以外の少なくとも1番目から11番目のビットが一致していることが確認できる。

従って、パスの選択情報として、パス比較の行われるステートのそれぞれで、2つの比較パスの下位(最新ビット)から数えて7番目のビットが異なっており、かつ、5番目と7番目を除いた1番目から11番目のビットが一致している場合を1、一致していない場合を0とするような情報を出力するように構成すればよい。

【0053】

なお、このほかに、最短マークより一つ大きなマークのシフトエラーなどについても同様にして情報を検出できる。このようなエラーの出現確率は上記2つほど多くは無いが、ユークリッド距離が上記2つに続いて小さいものであるから、上記2つに次ぐ確率で出現されるものである。

この場合は、2つの比較パスのパスメモリの最新のビットから数えてc+d+2番目のビットが異なっていて、かつ、c、c+d+2番目のビットを除いた1番目から2c+2d番目までビットが一致しているか、否かの情報である。これは、最短マークのマーク長(最短ランレングス+1)が2で、ターゲットレスポンスがPR(1,2,2,2,1)であるような本例のPRML検出では、この情報は、パスメモリの6番目のビットを除いた1番目から10番目のビットが一致しているかどうかの情報に相当する。

従って、たとえば、パスの選択情報として、パス比較の行われるステートのそれぞれで、2つの比較パスの下位(最新ビット)から数えて7番目のビットが異なっており、かつ、5番目と7番目を除いた1番目から11番目のビットが一致している場合を1、一致していない場合を0とするような情報を出力するように構成すればよい。

【0054】

以上のようにして、パス比較を行っている6つのステートにおいて検出されたパスメモリ比較情報は、これらの各ステートのパスメモリレジスタ(62A、62B、62E、62F、62I、62J)から、次に述べるパス比較メモリ更新ユニット24に出力される。

【0055】

図9は、以上のようにして得られたパスメモリ比較情報をパス比較メモリ更新ユニット24で記憶し、また、更新していく様子を説明する図である。

図9のパス比較メモリ更新ユニット28は、パスメモリレジスタ71A、71B、71E、71F、71I、71Jと、パスメモリレジスタ72A、72B、72E、72F、72I、72Jと、フリップフロップ73A、73B、73E、73F、73I、73Jによって構成されている。

パスメモリレジスタ71Aには、ステートs0000におけるここまでのパスメモリ比較情報M0000が記憶されている。パスメモリレジスタ72Aでは、図6のステートs0000に対するパスメモリレジスタ62Aから得られたパスメモリ比較情報c0000を、これまでのパスメモリ比較情報M0000のメモリ値を2倍した値に加算する。フリップフロップ73Aによってラッチされたパスメモリレジスタ72Aの値は、パスメモリレジスタ71Aの値として記憶される。

パスメモリレジスタ71Bには、ステートs0001におけるここまでのパスメモリ比較情報M0001が記憶されている。パスメモリレジスタ72Bでは、図6のステートs0001に対するパスメモリレジスタ62Bから得られたパスメモリ比較情報c0001を、これまでのパスメモリ比較情報M0001のメモリ値を2倍した値に加算する。フリップフロップ73Bによってラッチされたパスメモリレジスタ72Bの値は、パスメモリレジスタ71Bの値として記憶される。

パスメモリレジスタ71Eには、ステートs0011におけるここまでのパスメモリ比較情報M1000が記憶されている。パスメモリレジスタ72Eには、図6のステートs0011に対するパスメモリレジスタ62Eから得られたパスメモリ比較情報c0011を、これまでのパスメモリ比較情報M0011のメモリ値を2倍した値に加算する。フリップフロップ73Eによってラッチされたパスメモリレジスタ72Eの値は、パスメモリレジスタ71Eの値として記憶される。

パスメモリレジスタ71Fには、ステートs1100におけるこれまでのパスメモリ比較情報M1100が記憶されている。パスメモリレジスタ72Fでは、図6のステートs1100に対するパスメモリレジスタ62Fから得られたパスメモリ比較情報c1100を、これまでのパスメモリ比較情報M1100のメモリ値を2倍した値に加算する。フリップフロップ73Fによってラッチされたパスメモリレジスタ72Fの値は、パスメモリレジスタ71Fの値として記憶される。

パスメモリレジスタ7Iには、ステートs1110におけるここまでのパスメモリ比較情報M1110が記憶されている。パスメモリレジスタ72Iでは、図6のステートs1110に対するパスメモリレジスタ62Iから得られたパスメモリ比較情報c0111を、これまでのパスメモリ比較情報M1110のメモリ値を2倍した値に加算する。フリップフロップ73Iによってラッチされたパスメモリレジスタ72Iの値は、パスメモリレジスタ71Iの値として記憶される。

パスメモリレジスタ71Jには、ステートs1111におけるここまでのパスメモリ比較情報M1111が記憶されている。パスメモリレジスタ72Jでは、図6のステートs1111に対するパスメモリレジスタ62Jから得られたパスメモリ比較情報c1111を、これまでのパスメモリ比較情報M1111のメモリ値を2倍した値に加算する。フリップフロップ73Jによってラッチされたパスメモリレジスタ72Jの値は、パスメモリレジスタ71Jの値として記憶される。

以上のようにして得られたパスメモリ比較情報{cijkl}は、差メトリックの分布指標を計算するジッタ計算ユニット29に対して出力される。

【0056】

図10は、パスメトリック比較の際に比較されたパスメトリックの差分、すなわち、差メトリックをPRML検出器6の外部で再現するための差メトリック計算ブロック27である。

この差メトリック計算ブロック27は、減算器81と、フリップフロップ82A〜82Dと、掛け算器83A〜83Eと、加算器84によって構成されている。

なお、フリップフロップの数、掛け算器の数は、必要に応じて変更するものとする。

減算器81には、再生信号のサンプリング値をPRML検出器6の遅延量だけ遅延する遅延回路25からの再生信号rと、ブランチシーケンス26からのビット列pが供給される。

【0057】

差メトリックの分布について計算をする前に、計算の簡略化方法について考える。

ここで、r0、r1、r2、r3、r4・・・は、順にPRMLでビタビ検出を行う際に用いられる再生信号を0、1、・・・と添え字分のチャネルクロックだけ遅延させた信号であるものとする。

また、p0、p1、p2、p3、p4・・・は、上記再生信号に同期している生き残りパスに対応したパーシャルレスポンス系列(ブランチシーケンス26からのビット列)であるものとする。

このとき、生き残りパスのパスメトリックは、

M0=(r0−p0)2+(r1−p1)2+(r2−p2)2+(r3−p3)2+(r4−p4)2

である。

また、1ビット単独誤りがある場合の消滅パスのパスメトリックは、

M1=(r0+1−p0)2+(r1+2−p1)2+(r2+2−p2)2+(r3+2−p3)2+(r4+1−p4)2

である。

従って、差メトリックdMは、

dM=M1−M0

=1・(r0−p0)+2・(r1−p1)+2・(r2−p2)+2・(r3−p3)+1・(r4−p4)+14

となる。

なお、「14」は図15でも説明したように、PR(1,2,2,2,1)における1ビット誤りのビット系列のパーシャルレスポンス系列に対するユークリッド距離であるが、これは図7の実線と点線の各サンプル点の差を二乗した値の和に相当する。

【0058】

さらに差メトリックdMの分布を調べるには、分散を計算する必要がある。ここで、消滅パスに1ビット単独誤りがある場合の差メトリックは、「14」を中心として正規分布をしていると考えられるので、差メトリックdMにおいて「14」を除いた項で分散を求めれば充分である。従って、差メトリックの分布指標として、

dM’=(r0−p0)+2・(r1−p1)+2・(r2−p2)+2・(r3−p3)+(r4−p4)

の分散、あるいは、標準偏差を求めれば充分であることがわかる。

なお、ここでは誤りのビット系列として、0が1に変わるタイプの誤りのものを用いているが、逆の特性であっても同様である。

【0059】

図10においては、減算器81には、再生信号のサンプリング値をPRML検出器6の遅延量だけ遅延する遅延回路25からの再生信号rと、ブランチシーケンス26からのビット列pが供給され、r−pの値が得られる。この減算器81の出力値は、フリップフロップ82A〜82Dによるシフトレジスタによって1クロックタイミングづつずれて掛け算器83A〜83Eに供給され、さらに掛け算器83A〜83Eの出力が加算器84で加算されて差メトリックdM’とされる。

この場合、掛け算器83A〜83Eの係数を順に1,2,2,2,1とする。このようにすれば、加算器84の出力は、上記の差メトリックから平均値14を減じた値としての差メトリックdM’を出力することができる。この差メトリックdM’を、ジッタ計算ユニット29において後述する選択方式で選択して、分散、あるいは、標準偏差を計算する。

【0060】

以上の図10の差メトリック計算ユニット27による差メトリックdM’とは、消滅パスが1ビット単独誤りに対応するパスであった場合の差メトリックであって、一般化すれば、

dM’=Σpj・(rn-j−qn-j)

で表すことができる。ただし、Σはjが1からdになるまで項を加算する。

これは、ビタビ検出によって検出された拘束長分のビット列に同期した再生信号rnから数えてdクロック遡る再生信号rn-dまでのdチャネルクロック分の再生信号rn-1・・rn-dと、これらの再生信号に同期している生き残りパスのパーシャルレスポンス系列qn-1・・qn-dの間の差分に対して、パーシャルレスポンスの元での1チャネルクロックのパルスに対するdチャネルクロックのレスポンスp1・・pdとを順に掛け合わせた後に加算して得られる値である。

【0061】

ところで以上の図10は1ビット単独誤りを想定した場合の差メトリックdM’の算出構成である。

一方で、消滅パスが、最短マークのシフトによる2ビット誤りがある場合を考えると差メトリック計算ユニット27は図11のように構成されればよい。

この場合の差メトリック計算ブロック27は、減算器81と、フリップフロップ82A〜82Fと、掛け算器83A〜83Gと、加算器84によって構成される。

【0062】

最短マークシフトによる2ビット誤りを想定すると、生き残りパスのパスメトリックは、

M0=(r0−p0)2+(r1−p1)2+(r2−p2)2+(r3−p3)2+(r4−p4)2+(r5−p5)2+(r6−p6)2

である。

また、最短マークのシフトによる誤りがある場合の消滅パスのパスメトリックは、

M1=(r0+1−p0)2+(r1+2−p1)2+(r2+1−p2)2+(r3+0−p3)2+(r4−1−p4)2+(r5−2−p5)2+(r6−1−p6)2

である。

従って、差メトリックdMは、

dM=M1−M0

=(r0−p0)+2・(r1−p1)+(r2−p2)−(r4−p4)−2・(r5−p5)−(r6−p6)+12

となる。

なお、「12」は図15でも説明したように、PR(1,2,2,2,1)における最短マークシフトによる2ビット誤りのビット系列のパーシャルレスポンス系列に対するユークリッド距離であるが、これは図8の実線と点線の各サンプル点の差を二乗した値の和に相当する。

【0063】

さらに差メトリックdMの分布を調べるには分散を計算する必要があるが、上記1ビット誤りの場合と同様の考え方として、消滅パスに最短マークのシフトによる誤りがある場合の差メトリックdMは、「12」を中心として、正規分布をしていると考えられるので、差メトリックdMにおいて「12」を除いた項で分散を求めれば充分である。

従って、差メトリックの分布指標として

dM’=(r0−p0)+2・(r1−p1)+(r2−p2)−(r4−p4)−2・(r5−p5)−(r6−p6)

の分散、あるいは、標準偏差を求めれば充分である。

なお、ここで、誤りのビット系列として、2つの誤りのうち最初の誤りが、0が1に変わるタイプの誤りのものを用いているが、逆の特性であっても同様である。

【0064】

図11においては、掛け算器83A〜83Gの係数を順に1,2,1,0、−1、−2、−1とする。このようにすれば、加算器84の出力は、上記の差メトリックから平均値12を減じた値(差メトリックdM’)を出力する。この値を、ジッタ計算ユニット29で、後述する選択方式で選択して、分散、あるいは、標準偏差を計算する。

【0065】

この図11の差メトリック計算ユニット27による差メトリックdM’とは、消滅パスが最短マークのシフト誤りに対応するパスであった場合の差メトリックであって、一般化すれば、

dM’=Σ(pj−pj-2)・(rn-j−qn-j)

で表すことができる。ただし、Σはjが1からd+2になるまで項を加算する。

これはビタビ検出によって検出された拘束長分のビット列に同期した再生信号rnから数えてd+2クロック遡る再生信号rn-d-2までのdチャネルクロック分の再生信号rn-1・・rn-d-2と、これらの再生信号に同期している生き残りパスのパーシャルレスポンス系列qn-1・・qn-d-2の間の差分に対して、パーシャルレスポンスの元での1チャネルクロックのパルスに対するdチャネルクロックのレスポンスp1・・pdと、これより2クロックシフトしたレスポンスp-1・・pd-2の差分を順に掛け合わせた後に加算して得られる値である。

【0066】

なお、後述するが、差メトリック計算ユニット27では、この図10,図11のいずれか一方の構成が備えられ、差メトリックdM’として1ビット誤りについての差メトリック、あるいは最短マークシフトによる2ビット誤りについての差メトリックのいずれか一方を出力するものとしても良いし、図10,図11の両方の構成を備えて、1ビット誤りについての差メトリックdM1と最短マークシフトによる2ビット誤りについての差メトリックdM2の両方を出力する構成としても良い。

【0067】

図12は、差メトリック計算ユニット27から供給されてくる差メトリックdM’を選択して、その分散、あるいは、標準偏差など、分布指標を評価する値を出力するジッタ計算ユニット29の構成を表している。このジッタ計算ユニット29では、所定の誤り方のパスと生き残りパスの差メトリックを選択検出して、その標準偏差を評価する。

図12のジッタ計算ユニット29は、マルチプレクサ91,カウンタ92,ゲート93,標準偏差計算部94から成る。

マルチプレクサ91は、拘束長dの長さの検出ビット列をアドレスビット列としてブランチシーケンス26から入力する。そして、そのアドレスビット列に基づいてパス比較メモリ更新ユニット24から供給されるパスメモリ比較情報(c0000、c0001、c0011、c1100、c1110、c1111)のうちから1つを選択して出力する。

ゲート93は、マルチプレクサ91から出力された情報を元に差メトリックdM’の選択を行う。即ち、供給された差メトリックdM’を標準偏差計算部94に供給するか否かのゲート処理を行う。

カウンタ92は、マルチプレクサ91から出力された情報を元に選択したい差メトリックの個数をカウントする。

標準偏差計算部94は、ゲート93から出力された所定の誤りのみに対応した差メトリックdM’と、カウンタ92で数えた差メトリックの個数とを元に、標準偏差の計算を行う。

【0068】

ここで、マルチプレクサ91では、入力されたビット系列のうちの上位のd−1ビットのビット列に基づいて、ステートが選択され、そのステートがパスメモリ比較情報を持っているステートであれば、そのパスメモリ比較情報が出力される。このとき、マルチプレクサ91が出力するパスメモリ比較情報は、ステートを示すビット列の最下位のビット、すなわち、最新の検出ビットに同期しているものとする。

このようにして得られたマルチプレクサ91の出力は、最終決定パスにおける、検出したいタイプ(例えば1ビット誤り、最短マークシフトによる2ビット誤りなどのタイプ)のパスメモリ比較の存在を見つけるものである。

上記のようにマルチプレクサ91によって検出した、最終決定パス内の、検出したいタイプのパスメモリ比較情報は、ゲート93と、その選択回数をカウントするカウンタ92への情報として出力される。ここで、このゲート93は、差メトリックdM’の遅延量とも同期がとれているものとする。すなわち、マルチプレクサ91に入力される長さdのビット系列と前述の差メトリックdM’が同期しているものとする。

【0069】

以上の構成によってゲート93から出力される差メトリックdM’の値は、実際のパス選択の際に比較された差メトリックと同じ値となる。従って、この差メトリックdM’の分布指標を用いれば、パス選択の際に比較された差メトリックの分布指標を求めることができる。

そして、例えば差メトリック計算ユニット27を図10の構成とし、1ビット誤りの場合を想定して差メトリックdM’を出力するものとしたときは、この図12のジッタ計算ユニット29において、ゲート93からは1ビット誤りの場合のみの差メトリックdM’が標準偏差計算部94に供給され、またその1ビット誤りの場合の回数がカウンタ92でカウントされる。従って標準偏差計算部94では、正確に1ビット誤りの場合のみの差メトリックdM’を対象として計算を行う。具体的には、ゲート93で選択されて入力された差メトリックdM’の二乗計算を行い、カウンタ92の値が所定の数になるまで、差メトリック値の二乗を加算する。それをSAMジッタ値とする。このSAMジッタ値は、1ビット誤りの場合のみを対象として(つまり最短マークシフトの誤りでありながら差メトリック計算ユニット27で1ビット誤りとみなされて計算された差メトリックdM’をゲート93で除外して)計算されたものであり、指標として信頼性が高い評価値となる。

【0070】

そして再生信号品質を評価する指標として得られるSAMジッタは、ゲート93で選択された差メトリックdM’の標準偏差と、差メトリックの元となる2つの比較パスのユークリッド距離との比率である。

この場合の2つの比較パスのユークリッド距離とは、ターゲットレスポンスがPR(1,2,2,2,1)であって、パスメモリ比較情報が、パスメモリのc番目のビットを除いた1番目から2c−1番目までビットが一致しているか否かの情報である場合であるため、14(=12+22+22+22+12)である。

なお、ターゲットレスポンスがPR(1,2,2,1)として構成される場合は、比較パスのユークリッド距離は10(=12+22+22+12)となる。

【0071】

また、例えば差メトリック計算ユニット27を図11の構成とし、最短マークシフトによる2ビット誤りの場合を想定して差メトリックdM’を出力するものとしたときは、この図12のジッタ計算ユニット29において、ゲート93からは最短マークシフトによる2ビット誤りの場合のみの差メトリックdM’が標準偏差計算部94に供給され、またその場合の回数がカウンタ92でカウントされる。従って標準偏差計算部94では、正確に最短マークシフトによる2ビット誤りの場合のみの差メトリックdM’を対象として計算を行う(差メトリックdM’の二乗計算を行い、カウンタ92の値が所定の数になるまで、差メトリック値の二乗を加算する)。これにより計算したSAMジッタ値は、最短マークシフトによる2ビット誤りの場合のみを対象として計算されたものであり、信頼性が高い評価値となる。

そして再生信号品質を評価する指標として得られるSAMジッタは、ゲート93で選択された差メトリックdM’の標準偏差と、差メトリックの元となる2つの比較パスのユークリッド距離との比率である。この場合の2つの比較パスのユークリッド距離とは、ターゲットレスポンスがPR(1,2,2,2,1)であって、パスメモリ比較情報が、パスメモリのc、c+d+1番目のビットを除いた1番目から2c+2d−1番目までビットが一致しているか否かの情報である場合であるため、12(=12+22+(2−1)2+(1−2)2+22+12)=12である。

なお、ターゲットレスポンスがPR(1,2,2,1)として構成される場合は、比較パスのユークリッド距離12(=12+22+(2−1)2+(2−1)2+22+12)となる。

【0072】

さらに、差メトリック計算ユニット27として、図10の構成部分と図11の構成部分の両方を備え、1ビット誤りと想定した場合の差メトリックdM’(dM’1とする)と最短マークシフトによる2ビット誤りと想定した場合の差メトリックdM’(dM’2とする)の両方を出力する構成とした場合は、ジッタ計算ユニット29は図13のように構成すればよい。

即ち1ビット誤りについて差メトリックdM’1を選択及びカウントするためのゲート93a、カウンタ92aを設けることに加え、最短マークシフトによる2ビット誤りについての差メトリックdM’2を選択及びカウントするためのゲート93b、カウンタ92bを設ける。

この場合、ゲート93aでは、マルチプレクサ91からの情報に基づいて、1ビット誤りの場合のみ差メトリックdM’1を通過させ、標準偏差計算部94に供給する。またカウンタ92aはマルチプレクサ91からの情報に基づいて、1ビット誤りの場合のみの回数をカウントする。

一方、ゲート93bでは、マルチプレクサ91からの情報に基づいて、最短マークシフトによる2ビット誤りの場合のみ差メトリックdM’2を通過させ、標準偏差計算部94に供給する。またカウンタ92bはマルチプレクサ91からの情報に基づいて、最短マークシフトによる2ビット誤りの場合のみの回数をカウントする。

標準偏差計算部94では、1ビット誤りの場合、最短マークシフトによる2ビット誤りの場合のそれぞれについて計算を行い、計算結果を評価値として出力することができる。

【0073】

なお、以上の各例では、標準偏差を計算することを目的として図12,図13のようなジッタ計算ユニット29を記したが、たとえば差メトリックの分布ヒストグラムを表示したい場合には、ヒストグラム表示器などとしての構成を備えてもよい。

また、ジッタ計算ユニット29で計算した標準偏差を、たとえば記録装置の記録パルス形状、パルスエッジの先行遅延量の微調整等の各種信号補償のために用いてもよい。

【0074】

ところで、以上の実施の形態としての図2の構成例では、差メトリック計算ユニット27は、差メトリックdM’を再生信号から計算するようにした。この他に、図14に示すように、差メトリック計算ユニット27で、実際にパスメトリック更新ユニット23における差メトリックを計算する構成も考えられる。

即ち差メトリック計算ユニット27は、図5のパスメトリックレジスタ52A、52B、52E、52F、52I、52Jにおける、選択されたパスメトリックと選択されなかったパスメトリックの差分を計算する構成とする。

【0075】

また以上の実施の形態の構成は、PR(1,2,2,2,1)をターゲットとするPRMLの場合での構成である。本発明は、パスの比較選択の際に消滅パスの誤りの種類を記憶することで、最終生き残りパスと、これと比較された所定の誤りの消滅パスとの差メトリックを選択的に検出して、分布指標を調べるものである。従って、上述のターゲットレスポンスのものには限定されず、ターゲットレスポンスの長さや、係数に応じて適切な処方に基づいて評価信号生成装置が作成されるものである。たとえば、PR(1,2,2,1)、PR(1,2,1)をターゲットとするPRMLの場合は、上記のPRMLよりも規模の小さい別の構成のPRMLが必要であるが、その評価装置構成の作成手順は、PR(1,2,2,2,1)と同様な方法で消滅パスの誤りの種類を記憶するようにすればよい。

【図面の簡単な説明】

【0076】

【図1】本発明の実施の形態の再生装置のブロック図である。

【図2】実施の形態のPRML検出器及び信号評価器のブロック図である。

【図3】実施の形態のPRML検出器におけるイコライザのブロック図である。

【図4】実施の形態のPRML検出器におけるブランチメトリック計算ユニットのブロック図である。

【図5】実施の形態のPRML検出器におけるパスメトリック更新ユニットのブロック図である。

【図6】実施の形態のPRML検出器におけるパスメモリ更新ユニットのブロック図である。

【図7】生き残りパスのパーシャルレスポンス系列と、1ビット単独誤りのおきている消滅パスのパーシャルレスポンス系列での、それぞれのステート遷移とパスメモリの違いの説明図である。

【図8】生き残りパスのパーシャルレスポンス系列と、最短マークシフト誤りのおきている消滅パスのパーシャルレスポンス系列での、それぞれのステート遷移とパスメモリの違いの説明図である。

【図9】実施の形態の信号評価器におけるパス比較メモリ更新ユニットのブロック図である。

【図10】実施の形態の信号評価器における差メトリック計算ユニットのブロック図である。

【図11】実施の形態の信号評価器における他の差メトリック計算ユニットのブロック図である。

【図12】実施の形態の信号評価器におけるジッタ計算ユニットのブロック図である。

【図13】実施の形態の信号評価器における他のジッタ計算ユニットのブロック図である。

【図14】実施の形態のPRML検出器及び信号評価器の他の構成のブロック図である。

【図15】光ディスクのPRML検出において用いられる各種ターゲットレスポンスに対応した誤りがおこるためのユークリッド距離の説明図である。

【符号の説明】

【0077】

1 光ピックアップ、2 プリアンプ、3 A/D変換器、4 イコライザ、5 PLL回路、6 PRML検出器、7 信号評価器、8 復調器、9 RSデコーダ、10 CPUブロック、21 イコライザ、22 ブランチメトリック計算ユニット、23 パスメトリック更新ユニット、24 パスメモリ更新ユニット、25 遅延回路、26 ブランチシーケンス、27 差メトリック計算ユニット、28 パス比較メモリ更新ユニット、29 ジッタ計算ユニット、91 マルチプレクサ、92 カウンタ、93 ゲート、94 標準偏差計算部

【技術分野】

【0001】

本発明は、記録媒体に記録した情報を再生した再生信号に対する最尤復号装置、及び最尤復号装置における信号評価方法に関する。

【背景技術】

【0002】

【特許文献1】特開平10−21651号公報

【特許文献2】特開2003−141823号公報

【特許文献3】特開2003−151220号公報

【特許文献4】特開2003−178537号公報

【0003】

光ディスクの再生信号の信号品質を評価する方法として、タイムインターバルジッタ(TIジッタ)を評価する手法が知られている。TIジッタとは、再生信号と、ビット判定レベルとをコンパレータに入力し、得られた二値レベルのアナログ信号のエッジのタイミングと、再生信号から同期再生されたクロックのエッジのタイミングとの間の時間差(タイムインターバル)のばらつき(ジッタ)のことを意味している。

このような、TIジッタを用いた信号品質の評価法は、アナログの二値信号を用いたビット検出では、二値信号のエッジのタイミングのばらつきがビットエラーレートに直接影響を及ぼすことから、ビットエラーレートと相関のある評価方法として用いられていた。特に、このようなアナログの2値検出を用いていたCD、DVDなどでは、非常に有効な信号評価方法として広く用いられていた。

【0004】

一方、近年、光ディスクの記録情報の密度が高まるにつれて、上述のアナログの二値信号を用いたビット検出では十分に小さなビットエラーレートが確保できないことが判明し、特に、現在、最も高密度な光ディスクであるとされるブルーレイディスク(Blu-Ray Disc)では、ビット検出方法として、パーシャルレスポンス最尤(PRML:Partial Response Maximum Likelihood)検出とよばれる手法が用いる方法が一般的となってきている。

【0005】

PRMLとは、パーシャルレスポンスという過程と最尤検出という技術を組み合わせた技術である。パーシャルレスポンスとは、1ビットの入力に対して、1ビットよりも長く出力を返す過程、すなわち、出力の複数の入力ビットで決定する過程のことをいい、特にブルーレイディスクなどの光ディスクでよく用いられるような、再生信号が、連続する4ビットの情報ビットの入力に対してこれらを順に1、2、2、1を乗じて加算した信号として得られる過程は、PR(1,2,2,1)と表現される。

また、最尤検出とは、2つの信号の間にユークリッド距離とよばれる距離を定義して、実際の信号と想定されるビット系列から予想される信号との間の距離を調べて、その距離が最も近くなるようなビット系列を検出する方法である。なお、ここで、ユークリッド距離とは、同じ時刻での2つの信号の振幅差の二乗を全時刻にわたって加算した距離として定義される距離である。また、この距離を最小とするビット系列の探索には、後述するビタビ検出をもちいる。

これらを組み合わせたパーシャルレスポンス最尤検出は、記録媒体のビット情報から得られた信号をイコライザとよばれるフィルタでパーシャルレスポンスの過程となるように調整し、得られた再生信号と想定されるビット系列のパーシャルレスポンスとの間のユークリッド距離を調べて、その距離が最も近くなるようなビット系列を検出する方法である。

【0006】

実際にユークリッド距離が最小となるビット系列を探索するには、前述のビタビ検出によるアルゴリズムが効果を発揮する。

ビタビ検出は、所定の長さの連続ビットを単位として構成される複数のステートと、それらの間の遷移によって表されるブランチで構成されるビタビ検出器が用いられ、全ての可能なビット系列の中から、効率よく所望のビット系列を検出するように構成されている。

実際の回路では、各ステートに対してパスメトリックレジスタとよばれるそのステートにいたるまでのパーシャルレスポンス系列と信号のユークリッド距離(パスメトリック)を記憶するレジスタ、および、パスメモリレジスタとよばれるそのステートにいたるまでのビット系列の流れ(パスメモリ)を記憶するレジスタの2つのレジスタが用意され、また、各ブランチに対してはブランチメトリックユニットとよばれるそのビットにおけるパーシャルレスポンス系列と信号のユークリッド距離を計算する演算ユニットが用意されている。

このビタビ検出器では、さまざまなビット系列を、上記のステートを通過するパスのひとつによって一対一の関係で対応付けることができる。また、これらのパスを通過するようなパーシャルレスポンス系列と、実際の信号との間のユークリッド距離は、上記のパスを構成するステート間遷移、すなわち、ブランチにおける前述のブランチメトリックを順次加算していくことで得られる。

さらに、上記のユークリッド距離を最小にするようなパスを選択するには、この各ステートにおいて到達する2つ以下のブランチが有するパスメトリックの大小を比較しながら、パスメトリックの小さいパスを順次選択することで実現できる。この選択情報をパスメモリレジスタに転送することで、各ステートに到達するパスをビット系列で表現する情報が記憶される。パスメモリレジスタの値は、順次更新されながら最終的にユークリッド距離を最小にするようなビット系列に収束していくので、その結果を出力する。

以上のようにすると、上述したような、再生信号にユークリッド距離が最も近いパーシャルレスポンス系列を生成するビット系列を効率的に検索することができる。

【0007】

このようなPRMLを用いたビット検出では、時間軸方向の揺らぎであるTIジッタは、ビット検出に直接影響を及ぼすものではない。従って、TIジッタは、PRMLを用いたビット検出におけるビットエラーレートと必ずしも相関があるわけではなく、信号品質の指標として必ずしも適切ではない。PRMLの場合、振幅軸方向のゆらぎがビット検出におけるビットエラーレートに直接関係する。このため、PRMLを用いたビット検出では、ビットエラーレートに対応する指標として、振幅軸方向の揺らぎを取り込んだ指標であることが望ましい。

【0008】

PRMLによるビット検出の能力を決定する指標について以下に記述する。

PRMLによるビット検出では、正しいビット系列から得られるパーシャルレスポンス系列と再生信号とのユークリッド距離、すなわち、正しいビット系列に対するパスメトリックが、誤りのあるビット系列から得られるパーシャルレスポンス系列と再生信号とのユークリッド距離、すなわち、誤りのあるビット系列に対するパスメトリックよりも小なる場合に、正しいビット検出が実行され、逆の場合には誤りが発生する。

従って、PRMLのビット検出の能力は、前者のパスメトリックと後者のパスメトリックの差、すなわち、差メトリックが0からどれだけ離れているか、その大きさによって決定する。換言すれば、差メトリックが小さいほどエラー発生の可能性が高いと推定できる。

また、誤りのあるビット系列の中でも、誤りの大半を占める最も重要な系列は、正しい系列から得られるパーシャルレスポンス系列とのユークリッド距離が最も近くなるような別のパーシャルレスポンス系列を与えるビット系列である。このような系列は、たとえば、ターゲットレスポンスがPR(1,2,2,1)のPRMLでは、1ビットのみ誤りがある場合である。

このため、PRMLによるビット検出では、正しいビット系列から得られるパーシャルレスポンス系列と再生信号のユークリッド距離と、1ビットのみ誤りがあるビット系列のパーシャルレスポンス系列と再生信号のユークリッド距離の差分の大きさがPRMLによるビット検出の能力を決定すると考えられる。

【0009】

上記の2つのパーシャルレスポンス系列(正しいビット系列から得られるパーシャルレスポンス系列と、1ビット単独誤りがあるビット系列から得られるパーシャルレスポンス系列)に対して定義される再生信号とのユークリッド距離の差分について数式を用いて説明する。

まず、正しいビット系列に対するパスメトリック、すなわち、正しいビット系列から得られるパーシャルレスポンス系列と再生信号との間のユークリッド距離Mcは、以下の式でえられる。

Mc=Σni2

ただし、niは再生信号のサンプルにおけるノイズであり、平均0、標準偏差nのガウス分布に従う白色ノイズである。また、Σは全てのチャネルクロックiについて全て加算を意味している。

この式の導出は、PRMLでは、再生信号が正しいビット系列から得られるパーシャルレスポンス系列にノイズを加算した信号として得られるものである、と仮定していることに拠っている。

【0010】

次に、1ビット単独誤りのあるビット系列に対するパスメトリック、すなわち、1ビット単独誤りのあるビット系列から得られるパーシャルレスポンス系列と再生信号との間のユークリッド距離Meは、以下の式で与えられる。

Me=Σ(ci−ni)2

ただし、ciはターゲットレスポンスの係数であり、PR(1,2,2,1)ならば1,2,2,1,0・・・となる。

従って、その差分、すなわち、差メトリックdMは、以下の式で与えられる。

dM=Me−Mc=Σ|ci|2−2Σni・ci

ここで、Σ|ci|2は、1ビット異なる2つのビット系列から得られるパーシャルレスポンス系列のユークリッド距離に相当する。前に述べたように、この差分が、負となる場合に誤りが生ずる。また、この差分が負となるような確率は、ノイズniの標準偏差nが大きくなればなるほど高くなる。

従って、このノイズの分布nが、ビットエラーレートに対して直接寄与する指標である。しかし、nは、検出可能な量ではない。

そこで、nの代わりに、検出可能な量として差メトリックdMと、既知の量Σ|ci|2を用いて、

j=√V(dM)/(2・Σ|ci|2)

を定義すれば、jをビットエラーレートに直接寄与する指標として用いることができる。

ただし、V(dM)は、差メトリックdMの分散を表している。また、Σはチャネルクロックiについて全て加算である。

以上のように定義されたジッタjをSAMジッタと呼ぶ。

なお、jの定義式にdMを代入して変形すると、以下の式が得られる。

j=√(V(ni)・2・Σ|ci|2) /(2・Σ|ci|2)

=n/√(2・Σ|ci|2)

ここで、√Σ|ci|2は、ランダムなビット系列をパーシャルレスポンスチャネルで等化した場合の信号エネルギーに相当する。従って、SAMジッタjは、SN比に反比例していることがわかる。

【0011】

以上のように、PRMLをもちいたビット検出を行う場合、ビットエラーレートに対応する指標としては、振幅軸方向の揺らぎを取り込んだ指標を用いることが望ましいことがわかる。具体的には、正しいビット系列のパスメトリック、1ビット単独の誤りがあるビット系列のパスメトリックの差である差メトリックの標準偏差を、信号パワーで除算した指標、つまり上記SAMジッタが有効であることがわかる。

【発明の開示】

【発明が解決しようとする課題】

【0012】

ところで以上に述べたSAMジッタは、厳密なことを言えば、正しいビット系列がわかっている場合に定義することができる指標である。従って、正しいビット系列がわかっていない場合には定義することができない。そこで、上記特許文献1,2,3,4等では、ビット系列がわかっていない場合でもSAMジッタを定義する方法が提案されている。

これらの特許文献は、いずれも正しいビット系列のかわりに最終的に検出されたビット系列を正しいビット系列と仮定するものである。この仮定は、ビットエラーレートが、最悪でも10-3程度以内であるというような現行の光ディスクの一般的な条件の下では、十分に通用する仮定である。

【0013】

上述の仮定は、正しいビット系列としてどのビット系列を用いるか、についての仮定である。これに対して、1ビット単独誤りのあるビット系列としてどのビット系列を用いるか、についても決めることが必要である。

特許文献1,2,3は、それぞれ相違はあるが、いずれもテーブルを用いてこのビット系列を用意しているものとみなすことができる。つまり、最終的に検出された正しいと仮定されるビット系列に対して、このビット系列で表されるパスを構成するステート遷移のおのおので、誤りのあるビット系列をあらかじめ用意された1ビット誤りのパタンテーブルとステート遷移の対応を調べて、テーブルの結果をもとに推測するという方法である。このような構成ができる理由は、パスの比較選択を行った際に生き残りパスと比較されて消滅したパスが1ビットだけ異なるビット系列のパスであった、と仮定することから成り立っている。さらに、この仮定は、ビットエラーレートが、ほとんど1ビットの単独誤りであるというような現行の光ディスクでは一般的な条件の下では、十分に通用する仮定である。

【0014】

一方、特許文献4は、特許文献1,2、3と異なり、1ビット誤りであったか否かにかかわらず最終パスのステート遷移に対応したパス比較選択の差メトリックを検出し、その分布を評価する。この方法の場合、差メトリックの分布の中心値は、1ビット単独誤りであったか、そうでない別の誤り方だったのか、誤りの仕方によって、離散的な別々の異なる中心値をとっている。このため、分布指標として、通常のように、分散や標準偏差を評価する方法は使えない。しかしながら、1ビット誤りに由来する差メトリックの分布の中心がもっとも0に近い分布である、という仮定のもとでは、分布の左側のみをガウス分布で片側近似することができる。

この結果、このような方法を用いても、1ビット誤りに由来する差メトリックに対する分散や標準偏差を近似的に求めることができる。なお、1ビット誤りに由来する差メトリックの分布の中心がもっとも0に近い分布である、とは、言い換えると、1ビット誤りが2番目に小さいユークリッド距離のパスである、ということを意味している。(なお、最小ユークリッド距離のパスとは、ビタビ検出で検出される生き残りパスのことである。)

【0015】

ここで、特許文献1,2,3に開示された手法が有効であるための、ビットエラーレートの分布は1ビット単独誤りが支配的であるという仮定は、特許文献4の手法が有効であるための、1ビット単独誤りのパスが、2番目に小さいユークリッド距離のパスである、という仮定から得られる帰結でもある。

従って、特許文献1、2、3、4の各手法の全てが、1ビット単独誤りのパスが最小ユークリッド距離のパスであるという条件の下で有効となる方法である、とみなすことができる。

この場合、逆に、これらの手法が本当に有効かどうかを調べるためには、1ビット単独誤りが本当に2番目に小さいユークリッド距離のパスであるかを調べる必要がある。そこで、以下では、1ビット誤り、2ビット誤り、について、そのビット系列から得られるパーシャルレスポンス系列と、正しいビット系列から得られるパーシャルレスポンス系列との間のユークリッド距離を調べた。

【0016】

図15は、PR(1,1)、PR(1,2,1),PR(1,2,2,1)、PR(1,2,2,2,1)について1ビット誤り、2ビット誤りのビット系列のパーシャルレスポンス系列に対するユークリッド距離を調べた表である。

ここで2ビット誤りのうちで重要なものは、拘束長の中に2つ以上の誤りがあるようなものである。そのような例の中でも特に重要なのは、マーク長2のマーク(2Tマーク)の消滅あるいは出現による誤りと、2Tマークのシフトによる誤りである。従ってこの図15では、誤りの種類として、1ビット誤り、最短マークの消滅又は出現による2ビット誤り、及び最短マークシフトによる2ビット誤りの3種類を示している。

【0017】

図15において、00011000などと書かれている列は、誤りのあるビット系列と正しいビット系列の差分をとった列である。

即ち1ビット誤りの差分「00001000」は、例えば、誤りのあるビット系列「111110000」と正しいビット系列「111100000」の差分であり、つまり信号波形のエッジシフトによるエラーである。

また2ビット誤りとして示した差分「00011000」は、例えば誤りのあるビット系列「00000011」と正しいビット系列「000110011」の差分(或いはその正誤が反対の場合)などであり、つまり2Tマークの消滅あるいは出現による誤りである。

また同じく2ビット誤りとして示した差分「00010−1000」は、例えば誤りのあるビット系列「0000110000」と正しいビット系列「0001100000」の差分であり、即ち2Tマークがシフトした誤りである。

【0018】

この図15において、各ターゲットレスポンスで、ユークリッド距離が最小となる誤りの種類を比較すると、PR(1,1)、PR(1,2,1)、PR(1,2,2,1)では、1ビット単独誤りが最小である。ところがPR(1,2,2,2,1)では、最短マークのシフトによる2ビット誤りのユークリッド距離が「12」となってが最小である。つまり1ビット単独誤りの場合のユークリッド距離「14」より小さくなっている。

これはすなわち、PR(1,2,2,2,1)では、1ビット誤りの分布が左端の分布とはならず、また、1ビット誤りが誤りの支配的要因ではないことを示している。従って、特許文献4、および特許文献1,2,3の手法が有効に働くための条件をみたしていないことを意味している。

【0019】

以上は、PR(1,2,2,2,1)において、関連特許1,2,3,4があまり有効ではないことを示すものであるが、PR(1,2,2,1)においても、1ビット誤りのユークリッド距離「10」と、最短マークのシフト誤りのユークリッド距離「12」はそれほど離れているものではない。

従って、PR(1,2,2,1)では、1ビット誤りが支配的であるとはいえ、最短マークのシフト誤りが無視できるものかどうかは、ノイズの大きさにも大きく左右されるものである。

【0020】

以上を鑑みると、特許文献1,2,3のように、1ビット誤りのあるビット系列を決定する際に、検出されたビット系列に対して、誤りのあるビット系列をあらかじめ用意された1ビット誤りのテーブルをもとに推測するという方法は、ターゲットレスポンスがPR(1,2,2,2,1)の場合には適切ではない。また、ターゲットレスポンスがPR(1,2,2,1)の場合でもノイズが大きくなると必ずしも適切ではない。

また、特許文献4のように、差メトリックの分布のうち、1ビット誤りに相当すると考えられる分布の左端をガウス分布で片側近似を行う方法も、同様のことがいえる。

さらに、特許文献1,2,3,4の方法は、ビットシフトのような1ビット単独誤りに対しては、そのジッタの大きさを見積もることができるが、最短マークのシフト誤りに対しては、ジッタの大きさを見積もることもできない。

そこで、1ビット単独誤りに対するSAMジッタの検出確度を向上して、さらに、最短マークのシフト誤りなどに対してもSAMジッタを検出できるような新たな手法が必要となった。

【課題を解決するための手段】

【0021】

このような事情から本発明は、PRMLのビット検出によるビットエラーレートに直接相関のある指標を用いて信号評価を行うことを目的とし、特に1ビット単独誤りに対するSAMジッタ等の評価値の検出確度の向上や、最短マークのシフト誤り(2ビット誤り)などに対してもSAMジッタ等の評価値を検出できる手法を提供することを目的とする。

【0022】

本発明の最尤復号装置は、ビット情報を再生した再生信号からビタビ検出を行ってビット検出するビタビ検出手段と、上記ビタビ検出手段で生き残りパスの選択を行う際における生き残りパスと比較された消滅パスのパスメモリ間での違いである消滅パスの誤りの種類を示す情報を、パスメモリ比較情報として記憶するパスメモリ比較情報記憶手段と、上記ビタビ検出手段において最終的に生き残ったパスを構成しているステートでの差メトリックを得る差メトリック計算手段と、上記差メトリック計算手段により得られた差メトリックのうち、上記パスメモリ比較情報が同じ状態であるステートにおける差メトリックだけを選択する差メトリック選択手段と、上記差メトリック選択手段で選択された差メトリックの分布指標を計算して再生信号品質を評価する指標を得る評価値計算手段とを備える。

【0023】

上記パスメモリ比較情報とは、パスメモリの最新のビットから数えてc番目のビットを除いた1番目から2c−1番目までビットが一致しているか否か、即ち1ビット単独誤りであるか否かの情報である(cはビタビ検出器の拘束長)。

あるいは、上記パスメモリ比較情報とは、パスメモリの最新のビットから数えてc+d+1番目のビットが異なっていて、かつ、c、c+d+1番目のビットを除いた1番目から2c+2d−1番目までビットが一致しているか否か、即ち最短マークのシフト誤りか否かの情報である(dは上記ビタビ検出器の従う最小ランレングス規則における最小ランレングス)。

また上記パスメモリ比較情報記憶手段は、上記ビタビ検出手段でパスの比較が行われるステートにおいて、それぞれパスメモリ比較情報のビット数分のパスメモリ比較情報レジスタをパスメモリの長さと同じだけ用意し、上記パスメモリ比較情報レジスタをビットシフトするとともに、新たなパスメモリ比較情報を暫時追加して記憶するように構成される。

【0024】

また上記ビタビ検出手段は、拘束長c、最小ランレングスdの規則に従うビタビ検出手段であって、ランレングス制約に従うcビットで区別されるブランチのおのおのに対して、基準レベル、ブランチメトリックを記憶するレジスタ、及び上記各レジスタを更新する演算器から成るブランチメトリック計算ユニットと、ランレングス制約に従うc−1ビットで区別されるステートのおのおのに対して、パスメトリックを記憶するレジスタ、及び上記各レジスタを更新する演算器から成るパスメトリック更新ユニットと、ランレングス制約に従うc−1ビットで区別されるステートのおのおのに対して、パスメモリを記憶するレジスタ、及び上記各レジスタを更新する演算器から成るパスメモリ更新ユニットとが設けられる。そして上記パスメモリ更新ユニットは、上記パスメモリを記憶したレジスタからビット情報を決定して出力するとともに、上記ステートのうち、パスの比較選択を行うステートのおのおのについての上記パスメモリ比較情報を出力する。

ここで上記ブランチメトリック計算ユニットにおける演算器とは、上記ブランチに対応した基準レベルと、入力された信号の差の二乗(或いは、それに準ずる値として、入力された信号の二乗を減算した値)を計算し、それを上記ブランチメトリックを記憶するレジスタの値としてチャネルビットクロックごとに更新する演算器である。

また上記パスメトリック更新ユニットにおける演算器とは、上記ステートに到達するブランチのブランチメトリックと、そのブランチに接続されたステートのパスメトリックの加算演算と、上記加算演算をへたブランチのパスメトリックの大きさを比較する比較演算と、上記パスメトリックの小さいパスを選択して、そのパスメトリックを上記パスメトリックを記憶するレジスタの値としてチャネルビットクロックごとの更新を行う演算器である。

また上記パスメモリ更新ユニットにおける演算器とは、上記パスメトリック更新ユニットの演算器におけるパスの選択状況に応じて、選択されたパスの通過したステートのパスメモリにパスの選択状況を追加して、これを上記パスメモリを記憶するレジスタの値としてチャネルビットクロックごとに更新する演算器である。

また上記ビタビ検出手段は、上記再生信号をパーシャルレスポンス等化し、等化された再生信号からビタビ検出を行ってビット情報をPRML検出する。

ここで上記PRML検出におけるビタビ検出の各ブランチに対応した基準レベルは、上記ブランチを表すビット列に対して、ターゲットレスポンスを用いてパーシャルレスポンスを施して得られる基準レベルである。

また上記ターゲットレスポンスは、PR(1,2,2,1)、あるいはPR(1,2,2,2,1)である。

【0025】

上記差メトリックとは、上記ビタビ検出手段におけるパス選択に際して比較される2つのパスのパスメトリックの差分である。

また上記差メトリック計算手段において算出する上記差メトリックとは、消滅パスが1ビット単独誤りに対応するパスであった場合の差メトリックであって、上記ビタビ検出手段によって検出された拘束長分のビット列に同期した再生信号rnから数えてdクロック遡る再生信号rn-dまでのdチャネルクロック分の再生信号rn-1・・rn-dと、これらの再生信号に同期している生き残りパスのパーシャルレスポンス系列qn-1・・qn-dの間の差分に対して、パーシャルレスポンスの元での1チャネルクロックのパルスに対するdチャネルクロックのレスポンスp1・・pdとを順に掛け合わせた後に加算して得られる値であるΣpj・(rn-j−qn-j)である(ただし、Σはjが1からdになるまで項を加算)。

或いは、上記差メトリック計算手段において算出する上記差メトリックとは、消滅パスが最短マークのシフト誤りに対応するパスであった場合の差メトリックであって、上記ビタビ検出手段によって検出された拘束長分のビット列に同期した再生信号rnから数えてd+2クロック遡る再生信号rn-d-2までのdチャネルクロック分の再生信号rn-1・・rn-d-2と、これらの再生信号に同期している生き残りパスのパーシャルレスポンス系列qn-1・・qn-d-2の間の差分に対して、パーシャルレスポンスの元での1チャネルクロックのパルスに対するdチャネルクロックのレスポンスp1・・pdと、これより2クロックシフトしたレスポンスp-1・・pd-2の差分を順に掛け合わせた後に加算して得られる値であるΣ(pj−pj-2)・(rn-j−qn-j)である(ただし、Σはjが1からd+2になるまで項を加算)。

【0026】

また上記差メトリック選択手段は、上記ビタビ検出手段によって検出された拘束長分のビット列に同期した差メトリックのうち、上記拘束長分のビット列の一番新しいビットに同期しているパスメモリ比較情報記憶手段のパスメモリ比較情報が、所定の情報となっているときの差メトリックを選択する。

また上記評価値計算手段によって得られる上記再生信号品質を評価する指標とは、上記選択された差メトリックの標準偏差と、上記差メトリックの元となる2つの比較パスのユークリッド距離との比率である。

上記2つの比較パスのユークリッド距離とは、ターゲットレスポンスがPR(1,2,2,1)であって、パスメモリ比較情報が、パスメモリのc番目のビットを除いた1番目から2c−1番目までビットが一致しているか否かの情報である場合の比較パスのユークリッド距離10(=12+22+22+12)である。

又は、上記2つの比較パスのユークリッド距離とは、ターゲットレスポンスがPR(1,2,2,2,1)であって、パスメモリ比較情報が、パスメモリのc番目のビットを除いた1番目から2c−1番目までビットが一致しているか否かの情報である場合の比較パスのユークリッド距離14(=12+22+22+22+12)である。

又は、上記2つの比較パスのユークリッド距離とは、ターゲットレスポンスがPR(1,2,2,1)であって、パスメモリ比較情報が、パスメモリのc、c+d+1番目のビットを除いた1番目から2c+2d−1番目までビットが一致しているか否かの情報である場合の比較パスのユークリッド距離12(=12+22+(2−1)2+(2−1)2+22+12)である。

又は、上記2つの比較パスのユークリッド距離とは、ターゲットレスポンスがPR(1,2,2,2,1)であって、パスメモリ比較情報が、パスメモリのc、c+d+1番目のビットを除いた1番目から2c+2d−1番目までビットが一致しているか否かの情報である場合の比較パスのユークリッド距離12(=12+22+(2−1)2+(1−2)2+22+12)である。

【0027】

本発明の信号評価方法は、ビット情報を再生した再生信号の信号品質を評価する信号評価方法であって、上記再生信号からビタビ検出手段を用いてビット検出するビット検出ステップと、上記ビタビ検出手段で生き残りパスの選択を行う際における生き残りパスと比較された消滅パスのパスメモリ間での違いである消滅パスの誤りの種類を示す情報を、パスメモリ比較情報として記憶するパスメモリ比較情報記憶ステップと、上記ビタビ検出手段において最終的に生き残ったパスを構成しているステートでの差メトリックを得る差メトリック計算ステップと、上記差メトリック計算ステップにより得られる差メトリックのうち、上記パスメモリ比較情報が同じ状態であるステートにおける差メトリックだけを選択する差メトリック選択ステップと、上記差メトリック選択ステップで選択された差メトリックの分布指標を計算して再生信号品質を評価する指標を得る評価値計算ステップとを備える。

【0028】

このような本発明は、次の考え方に基づく。

上述した課題は、上記特許文献1,2,3,4がいずれも、検出されたビット系列だけをもとに、1ビット単独誤りのパスに対する差メトリックの分布指標を算出しようとしている点から生じている問題である。すなわち、比較された消滅パスを常に1ビット単独誤りであったと仮定しているために生じている問題である。

従って、実際に、パスメトリックの大小比較を行った際に、生き残りパスと比較されて消滅したパスが1ビット誤りのパスであったのかどうかを確認することで、この問題は解決できる。さらに、生き残りパスと消滅パスのパスメモリの違いが、どのような違いであったのかを分類すれば、1ビット単独誤りに対するSAMジッタだけではなく、より、一般的な誤り、たとえば、最短マークのシフト誤り、などでもSAMジッタを定義することができる。

そこで本発明では、ビタビ検出で生き残りパスの選択の際、生き残りパスと比較された消滅パスのパスメモリ間での違い、即ち消滅パスの誤りの種類を示す情報(パスメモリ比較情報)を記憶し、最終的に生き残ったパスを構成しているステートでの差メトリックのうち、パス選択の際に消滅したパスが同じ種類の誤りとなっている、つまりパスメモリ比較情報が同じ状態であるステートの差メトリックのみを選択して、その差メトリックの分布指標(分散、標準偏差)を計算する。ここで、誤りの種類を示す情報とは、たとえば、消滅パスと生き残りパスのパスメモリの違いが、1ビットだけ異なるようなシフトエラーであるか否か、あるいは、2ビット異なる最短マークシフトのエラーであるか否か、の情報である。

【発明の効果】

【0029】

本発明によれば、生き残りパスと比較された消滅パスが、1ビット誤りに相当するパスであったのか、あるいは、最短マークのシフトエラー誤りに相当するパスであったのか、さらに、特定の長さのマークのシフトエラー誤りに相当するパスであったのか、などの誤りの種類に応じて、それぞれ別々に差メトリックを算出し、そのSAMジッタを検出することができる。

従って、まず、PR(1,2,2,2,1)のPRMLビット検出に対する従来の手法では検出することができなかった、誤りの中で最も支配的な最短マークのシフト誤りに対する選択的な差メトリックの標準偏差を求めることができる。

また、上記と同様、従来の手法で検出することのできなかった2番目に支配的な1ビット単独誤りに対する選択的な差メトリックの標準偏差を求めることができる。

次に、PR(1,2,2,1)のPRMLビット検出においても、誤りの中でもっとも支配的な1ビット単独誤りに対する選択的な差メトリックの標準偏差の検出を従来の検出法よりも、高い精度で実現することができる。

また、従来の手法では実現できなかった誤りの中で2番目に支配的である最短マークのシフト誤りについても、その差メトリックを選択的に検出して標準偏差を求めることができる。

このように、精度の高い信号品質の評価方法は、昨今の記録情報の高密度化の流れにおいて強く求められる技術であり、非常に有用となる。

さらに、このように誤りの種類に応じた選択的な評価を簡便に実現することは、特に記録補償のようなビット系列のパタンに応じたマーク長の補償を行う際にもきわめて重要となる。これらのことから、本発明は情報記録再生システムにおける信号品質評価の方法として非常に有用となる。

【発明を実施するための最良の形態】

【0030】

以下、本発明の実施の形態を説明する。

図1は、実施の形態の再生装置の概要を表すブロック図である。

図1に示すように、本例の再生装置は、光ディスクなどの記録媒体90、この記録媒体90からビット情報を再生する光ピックアップ1、光ピックアップ1で読み取られた信号を再生信号(RF信号)に変換するプリアンプ2、再生信号をA/D変換するA/D変換器3、PLL処理のために再生信号の波形を整えるイコライザ4、再生信号からクロックを再生するPLL回路5、再生信号からビット情報を検出するPRML検出器6、PRML検出器6からの情報を元に信号品質を評価する値としてSAMジッタ値を算出する信号評価器7、ビット情報を復調するRLL(1−7)pp復調器などの復調器8、復調された情報の誤り訂正を行うRSデコーダ9、誤り訂正された情報を処理してアプリケーションデータを再生するCPUブロック10などで構成されている。

【0031】

光ピックアップ1、プリアンプ2を通して再生された再生信号(RF)は、A/D変換器3で数値化サンプリングされる(RF(Sampled))。このサンプリングは、PLL回路5で再生されたチャネルビットに同期したクロックと同じタイミングで行われる。

サンプリングされた再生信号のサンプリング情報は、イコライザ4で波形を整えられた後、PRML検出器6に入力されて、ビット情報が判定される。

ここでは、PRMLは、記録時の変調方式の制約に従ってD1制約(最小ランレングスd=1で最短マーク長が2T)を満たすように構成し、さらに、PRMLのターゲットレスポンスはPR(1,2,2,1)か、あるいはPR(1,2,2,2,1)であるとする。

このPRML検出器6で得られたビット情報は、復調器8で記録時の変調方式に従って復調され、さらに、RSデコーダ9でECCブロックのリード・ソロモン符号を復号して誤りを訂正し、CPUブロック10はEDCブロックにおける誤り検出符号に誤りが検出されていないことを確認することで、もとのアプリケーションデータを復元する。

【0032】

なお、本例のPRML検出器6は、信号品質評価指標を検出できるように、その構成において通常のPRML検出器と若干異なるものとされる。具体的には、PRML検出器6内のパスメモリ更新ユニットが新規な構成となる。その構成は後述する。

また、信号評価器7では、PRML検出器6内のイコライザ(後述)から得られる再生信号と、PRML検出器6から得られる消滅パスの誤り情報をもとに、これをゲートとして所定の誤りに対応した信号品質指標(SAMジッタ)を検出する。この信号品質指標によりジッタ評価がなされる。

本発明の実施の形態としては、以下説明していくように、このPRML検出器6と、PRML検出器6からの情報を元に信号品質を評価する信号評価器7、及びこれらによる信号評価方法を特徴とするものである。

【0033】

図2は、図1に示したPRML検出器6、及び信号評価器7の構成を表している。

PRML検出器6は、チャネルレスポンスをターゲットレスポンスに等化する波形等化器(イコライザ)21と、このイコライザ21の出力からビタビ検出器の各ブランチに対してブランチメトリックを計算するブランチメトリック計算ユニット(BMC)22と、ブランチメトリックを取り込んでブランチを比較してパスの選択を行いパスメトリックの更新を行うパスメトリック更新ユニット(ACS)23と、選択されたパス情報に従いパスメモリの更新を行うパスメモリ更新ユニット24によって構成される。

また信号評価器7は、パスメモリの比較情報を記憶更新するパス比較メモリ更新ユニット28と、再生信号をビット検出に同期するように遅延させる遅延回路25と、パス比較の際の差メトリックdMに相当する値dM’を算出する差メトリック計算ユニット(DMC)27と、得られた差メトリックdM’を前記パス比較情報に基づいて選択してその標準偏差を計算するジッタ計算ユニット29と、差メトリック計算ユニット27に算出用のビット列を与え、またジッタ計算ユニット29にアドレスビット列を与えるブランチシーケンス26を有して構成されている。

【0034】

この図2におけるイコライザ21の役割は、チャネルレスポンスをPR(1,2,2,1)、あるいは、PR(1,2,2,2,1)のターゲットに等化することである。ターゲットレスポンスは、必ずしもこれに限るものではなく、たとえば、D2制約(最小ランレングスd=2で最短マーク長が3T)のときは、より拘束長の長いターゲットが用いられる。

ここでは、PR(1,2,2,2,1)のような5タップの拘束長を有するものに説明を絞るものとする。最小ランレングス規則としてのD1制約(最小ランレングスd=1で最短マーク長が2T)がある場合、ブランチメトリック計算ユニット22,パスメトリック更新ユニット23、パスメモリ更新ユニット24を有するビタビ検出器6は、4ビットで構成される10個のステートと、5ビットで構成される16のブランチが用意され、これらのブランチが、ステートの間をD1制約に従って接続するように構成されている。

【0035】

ここで、4ビットで構成される10個のステートとは、4ビットで構成される16個のビット列0000、0001、0010、0011、0100、0101、0110、0111、1000、1001、1010、1011、1100、1101、1110、1111のうち、D1制約、すなわち、0、1が単独で現れないという制約(上記の4ビットのビット列では、4ビットの中の真ん中の2ビットに単独で現れない)を満たす10のビット列0000、0001、0011、0110、0111、1000、1001、1011、1100、1110、1111で区別される状態のことである。

また、5ビットで構成される16個のブランチとは、5ビットで構成される32個のビット列00000、00001、00010、00011、00100、00101、00110、00111、01000、01001、01010、01011、01100、01101、01110、01111、10000、10001、10010、10011、10100、10101、10110、10111、11000、11001、11010、11011、11100、11101、11110、11111、のうち、D1制約、すなわち、0、1が単独で現れないという制約(上記の5ビットのビット列では、5ビットの中の真ん中の3ビットに単独で現れない)を満たす16のビット列、00000、00001、00011、00110、00111、01100、01110、01111、10000、10001、10011、11000、11001、11100、11110、11111、で区別される状態のことである。

なお、ターゲットレスポンスがPR(1,2,2,1)の場合は、3ビットで構成される6個のステートと、4ビットで構成される10のブランチが用意されて、D1制約に従ってブランチがステートを接続する。

このステートと、ブランチのビット列の作り方は、PR(1,2,2,2,1)でのステート、ブランチのビット列の作り方と同様である。

【0036】

ブランチメトリック計算ユニット22では、16のブランチに対してブランチメトリックが計算されて、その結果が、パスメトリック更新ユニット23に転送される。

パスメトリック更新ユニット23では、10のステートに対して、そのステートに到達するパスメトリックが更新されると同時に、パスの選択情報が、パスメモリ更新ユニット24に転送される。

パスメモリ更新ユニット24では、10のステートに対して、そのステートに到達するパスメモリが更新されると同時に、そのうちパスの比較が行われる6つのステートにおけるパスの比較情報が、パス比較メモリ更新ユニット28に転送される。また、パスメモリ更新ユニット24では、パスメモリに記憶されているビット系列は、パスの選択を繰り返しながら尤もらしい系列に収束していく。その結果が、ビタビ検出器6による検出結果のビットシーケンスとして出力される。

パス比較メモリ更新ユニット28では、パス比較の行われる6つのステートに対して、パス比較情報を記憶するパス比較情報レジスタ(シフトレジスタ)が用意されて、暫時シフトしながら、パスメモリ更新ユニット24から出力されたパス比較情報を追加していく。

ジッタ計算ユニット29では、パス比較メモリ更新ユニット28から与えられるパス比較情報に基づいて、差メトリック計算ユニット27から供給される差メトリックdM’のうち、消滅パスが所定の誤りの種類(たとえば、1ビット単独誤りや、最短マークのシフトによる2ビット誤りなど)に対応しているものだけを選択して、その差メトリックdM’の標準偏差を計算する。なお、計算結果は、上記の誤りの種類に対応して得られるユークリッド距離で規格化することが望ましい。

【0037】

図3に、PRMLのターゲットレスポンスに等化するために用いるイコライザ21の構成を示す。

本実施の形態におけるイコライザ21は、フリップフロップ31A〜31G、掛け算器32A〜32H、および加算器33によって構成され、波形等化フィルタを成している。

入力された再生信号(図1のイコライザ4からPRML検出器6に供給される再生信号RF(Sampled))は、フリップフロップ31A〜31Gを経て、チャネルクロックで1クロックずつ遅延した8つの信号に分岐される。

次に、分岐された8つの信号は、それぞれ掛け算器32A〜32Hによって、それぞれ異なる倍率で増幅される。

最後にこれらの掛け算器32A〜32Hによって増幅された各信号は、加算器33によって加算されて、その出力が等化信号として出力される。

ここで、掛け算器32A〜32Hの係数は、等化信号のターゲットレスポンスに対する等化誤差が最小となるような係数を用いている。この係数は、たとえばLMSアルゴリズムなどで自動的にもとまるようにすることが望ましい。

【0038】

なお、この図3の例は、8クロックはなれた信号を用いた8タップのイコライザの場合である。このタップ数は、必ずしも8つである必要はなく、より精度よく符号間干渉を取り除くのであればさらに増やしたり、あるいは、規模を小さくするならこれよりも減らしたりして、目的に応じて変更されればよい。

【0039】

図4は、PR(1,2,2,2,1)をターゲットレスポンスとするPRML検出器6におけるブランチメトリック計算ブロック22の構成である。

本実施の形態におけるブランチメトリック計算ユニット22は、基準値レジスタ41A〜41P、減算器42A〜42P、掛け算器43A〜43P、ブランチメトリックレジスタ44A〜44Pを有している。

このブランチメトリック計算ユニット22には、まず上述のイコライザ21を経て得られた等化信号qnが入力される。

基準値レジスタ41Aはビット列00000に対応する基準レベルr00000を記憶する。

基準値レジスタ41Bはビット列00001に対応する基準レベルr00001を記憶する。

基準値レジスタ41Cはビット列00011に対応する基準レベルr00011を記憶する。

基準値レジスタ41Dはビット列10000に対応する基準レベルr10000を記憶する。

基準値レジスタ41Eはビット列10001に対応する基準レベルr10001を記憶する。

基準値レジスタ41Fはビット列10011に対応する基準レベルr10011を記憶する。

基準値レジスタ41Gはビット列00110に対応する基準レベルr00110を記憶する。

基準値レジスタ41Hはビット列00111に対応する基準レベルr00111を記憶する。

基準値レジスタ41Iはビット列11000に対応する基準レベルr11000を記憶する。

基準値レジスタ41Jはビット列11001に対応する基準レベルr11001を記憶する。

基準値レジスタ41Kはビット列01100に対応する基準レベルr01100を記憶する。

基準値レジスタ41Lはビット列01110に対応する基準レベルr01110を記憶する。

基準値レジスタ41Mはビット列01111に対応する基準レベルr01111を記憶する。

基準値レジスタ41Nはビット列11100に対応する基準レベルr11100を記憶する。

基準値レジスタ41Oはビット列11110に対応する基準レベルr11110を記憶する。

基準値レジスタ41Pはビット列11111に対応する基準レベルr11111を記憶する。

なお、ここではパーシャルレスポンスのクラスをPR(1,2,2,2,1)としているので、もとのビット値を±1/2として、各基準レベルは、

r00000=−4、

r00001=−3、

r00011=−1、

r10000=−3、

r10001=−2、

r10011=0、

r00110=0、

r00111=+1、

r11000=−1、

r11001=0、

r01100=0、

r01110=+2、

r01111=+3、

r11100=+1、

r11110=+3、

r11111=+4、

となる。

【0040】

ブランチメトリックレジスタ44Aは、信号qnと基準レベルr00000の間のブランチメトリックm00000を記憶する。

ブランチメトリックレジスタ44Bは、信号qnと基準レベルr00001の間のブランチメトリックm00001を記憶する。

ブランチメトリックレジスタ44Cは、信号qnと基準レベルr00011の間のブランチメトリックm00011を記憶する。

ブランチメトリックレジスタ44Dは、信号qnと基準レベルr10000の間のブランチメトリックm10000を記憶する。

ブランチメトリックレジスタ44Eは、信号qnと基準レベルr10001の間のブランチメトリックm10001を記憶する。

ブランチメトリックレジスタ44Fは、信号qnと基準レベルr10011の間のブランチメトリックm10011を記憶する。

ブランチメトリックレジスタ44Gは、信号qnと基準レベルr00110の間のブランチメトリックm00110を記憶する。

ブランチメトリックレジスタ44Hは、信号qnと基準レベルr00111の間のブランチメトリックm00111を記憶する。

ブランチメトリックレジスタ44Iは、信号qnと基準レベルr11000の間のブランチメトリックm11000を記憶する。

ブランチメトリックレジスタ44Jは、信号qnと基準レベルr11001の間のブランチメトリックm11001を記憶する。

ブランチメトリックレジスタ44Kは、信号qnと基準レベルr01100の間のブランチメトリックm01100を記憶する。

ブランチメトリックレジスタ44Lは、信号qnと基準レベルr01110の間のブランチメトリックm01110を記憶する。

ブランチメトリックレジスタ44Mは、信号qnと基準レベルr01111の間のブランチメトリックm01111を記憶する。

ブランチメトリックレジスタ44Nは、信号qnと基準レベルr11100の間のブランチメトリックm11100を記憶する。

ブランチメトリックレジスタ44Oは、信号qnと基準レベルr11110の間のブランチメトリックm11110を記憶する。

ブランチメトリックレジスタ44Pは、信号qnと基準レベルr11111の間のブランチメトリックm11111を記憶する。

【0041】

基準値レジスタ41Aからブランチメトリックレジスタ44A、

基準値レジスタ41Bからブランチメトリックレジスタ44B、

基準値レジスタ41Cからブランチメトリックレジスタ44C、

基準値レジスタ41Dからブランチメトリックレジスタ44D、

基準値レジスタ41Eからブランチメトリックレジスタ44E、

基準値レジスタ41Fからブランチメトリックレジスタ44F、

基準値レジスタ41Gからブランチメトリックレジスタ44G、

基準値レジスタ41Hからブランチメトリックレジスタ44H

基準値レジスタ41Iからブランチメトリックレジスタ44I、

基準値レジスタ41Jからブランチメトリックレジスタ44J、

基準値レジスタ41Kからブランチメトリックレジスタ44K、

基準値レジスタ41Lからブランチメトリックレジスタ44L、

基準値レジスタ41Mからブランチメトリックレジスタ44M、

基準値レジスタ41Nからブランチメトリックレジスタ44N、

基準値レジスタ41Oからブランチメトリックレジスタ44O、

基準値レジスタ41Pからブランチメトリックレジスタ44P、

にいたる過程には、それぞれ減算器42(42A〜42P)と掛け算器43(43A〜43P)が一つずつ用意されている。

各減算器(42A〜42P)では、入力信号qnと、対応するレジスタ(41A〜41P)から得られた基準レベルの信号を入力し、その差分を出力する。

また、各掛け算器(43A〜43P)は、対応する減算器(42A〜42P)から出力された差分を二乗した値を出力する。このそれぞれの掛け算器(43A〜43P)から出力された値が、各ブランチメトリックレジスタ(44A〜44P)において記憶されるブランチメトリックm00000〜m11111となる。

なお、掛け算器43のかわりに絶対値計算器を配してもよい。

【0042】

以上のようにして得られて各ブランチメトリックレジスタ44A〜44Pに記憶されたブランチメトリックm00000〜m11111は、チャネルビットクロック毎に更新されるとともに、次段のパスメトリック更新ユニット23に出力される。

なお、ブランチメトリックの計算方法として、掛け算器43の容量を削減するために、j番目のブランチメトリックmjをmj=rj・(2qn−rj)、(ただし、rjはj番目の基準レベル)、を用いる方法でもよい。

【0043】

図5は、PR(1,2,2,2,1)をターゲットレスポンスとするPRML検出器6におけるパスメトリック更新ユニット23を示している。

図5のパスメトリック更新ユニット23は、パスメトリックレジスタ51A〜51J、及び52A〜52Jと、フリップフロップ53A〜53Jを有して構成されている。

【0044】

パスメトリックレジスタ51Aには、ステートs0000における生き残りパスのパスメトリックpm0000が記憶されている。パスメトリックレジスタ52Aでは、ステートs0000に至るパスのパスメトリックpm00000=pm0000+m00000、pm10000=pm1000+m10000のうち小さい値が選択される。

ここで、上記パスメトリック値を計算するためのメトリックm00000、m10000は図4のブランチメトリック計算ユニット22から入力される。図5においてブランチメトリック{mijklm}として示しているのは、図4のブランチメトリックレジスタ44A〜44Pから供給されるブランチメトリックm00000〜m11111のことである。

フリップフロップ53Aによってラッチされたパスメトリックレジスタ52Aの値は、パスメトリックレジスタ51Aの値として記憶される。

【0045】

パスメトリックレジスタ51Bには、ステートs0001における生き残りパスのパスメトリックpm0001が記憶されている。パスメトリックレジスタ52Bでは、ステートs0001に至るパスのパスメトリックpm00001=pm0000+m00001、pm10001=pm1000+m10001のうち小さい値が選択される。ここで、上記パスメトリック値を計算するためのメトリックm00001、m10001はブランチメトリック計算ユニット22から入力される。フリップフロップ53Bによってラッチされたパスメトリックレジスタ52Bの値は、パスメトリックレジスタ51Bの値として記憶される。

パスメトリックレジスタ51Cには、ステートs1000における生き残りパスのパスメトリックpm1000が記憶されている。パスメトリックレジスタ52Cには、ステートs1000に至るパスのパスメトリックpm11000=pm1100+m11000が記憶されている。このパスメトリック値を計算するためのメトリックm11000はブランチメトリック計算ユニット22から入力される。フリップフロップ53Cによってラッチされたパスメトリックレジスタ52Cの値は、パスメトリックレジスタ51Cの値として記憶される。

パスメトリックレジスタ51Dには、ステートs1001における生き残りパスのパスメトリックpm1001が記憶されている。パスメトリックレジスタ52Dには、ステートs1001に至るパスのパスメトリックpm11001=pm1100+m11001が記憶されている。このパスメトリック値を計算するためのメトリックm11001はブランチメトリック計算ユニット22から入力される。フリップフロップ53Dによってラッチされたパスメトリックレジスタ52Dの値は、パスメトリックレジスタ51Dの値として記憶される。

パスメトリックレジスタ51Eには、ステートs0011における生き残りパスのパスメトリックpm0011が記憶されている。パスメトリックレジスタ52Eでは、ステートs0011に至るパスのパスメトリックpm00011=pm0001+m00011、pm10011=pm1001+m10011のうち小さい値が選択される。パスメトリック値を計算するためのメトリックm00011、m10011はブランチメトリック計算ユニット22から入力される。フリップフロップ53Eによってラッチされたパスメトリックレジスタ52Eの値は、パスメトリックレジスタ51Eの値として記憶される。

パスメトリックレジスタ51Fには、ステートs1100における生き残りパスのパスメトリックpm1100が記憶されている。パスメトリックレジスタ52Fでは、ステートs1100に至るパスのパスメトリックpm01100=pm0110+m01100、pm11100=pm1110+m11100のうち小さい値が選択される。パスメトリック値を計算するためのメトリックm01100、m11100は、ブランチメトリック計算ユニット22から入力される。フリップフロップ53Fによってラッチされたパスメトリックレジスタ52Fの値は、パスメトリックレジスタ51Fの値として記憶される。

パスメトリックレジスタ51Gには、ステートs0110における生き残りパスのパスメトリックpm0110が記憶されている。パスメトリックレジスタ52Gには、ステートs0110に至るパスのパスメトリックpm00110=pm0011+m00110が記憶されている。このパスメトリック値を計算するためのメトリックm00110は、ブランチメトリック計算ユニット22から入力される。フリップフロップ53Gによってラッチされたパスメトリックレジスタ52Gの値は、パスメトリックレジスタ51Gの値として記憶される。

パスメトリックレジスタ51Hには、ステートs0111における生き残りパスのパスメトリックpm0111が記憶されている。パスメトリックレジスタ52Hには、ステートs0111に至るパスのパスメトリックpm00111=pm0011+m00111が記憶されている。このパスメトリック値を計算するためのメトリックm00111は、ブランチメトリック計算ユニット22から入力される。フリップフロップ53Hによってラッチされたパスメトリックレジスタ52Hの値は、パスメトリックレジスタ51Hの値として記憶される。

パスメトリックレジスタ51Iには、ステートs1110における生き残りパスのパスメトリックpm1110が記憶されている。パスメトリックレジスタ52Iでは、ステートs1110に至るパスのパスメトリックpm01110=pm0111+m01110、pm11110=pm1111+m11110のうち小さい値が選択される。これらのパスメトリック値を計算するためのメトリックm01110、m11110はブランチメトリック計算ユニット22から入力される。フリップフロップ53Iによってラッチされたパスメトリックレジスタ52Iの値は、パスメトリックレジスタ51Iの値として記憶される。

パスメトリックレジスタ51Jには、ステートs1111における生き残りパスのパスメトリックpm1111が記憶されている。パスメトリックレジスタ52Jでは、ステートs1111に至るパスのパスメトリックpm01111=pm0111+m01111、pm11111=pm1111+m11111のうち小さい値が選択される。これらのパスメトリック値を計算するためのメトリックm01111、m11111はブランチメトリック計算ユニット22から入力される。フリップフロップ53Jによってラッチされたパスメトリックレジスタ52Jの値は、パスメトリックレジスタ51Jの値として記憶される。

【0046】

以上のようにして、各ステートにおける、そのステートにいたるまでのパスメトリックが更新される。

一方、各ステートでのパスの選択情報を図5において{Sijkl}として示しているが、このパス選択情報{Sijkl}は、次に述べるパスメモリ更新ユニット24に出力される。

【0047】

図6は、PR(1,2,2,2,1)をターゲットレスポンスとするPRML検出器6におけるパスメモリ更新ユニット24を示している。

図6のパスメモリ更新ユニット24は、パスメモリレジスタ61A〜61J、62A〜62Jと、フリップフロップ63A〜63Jによって構成されている。

なお図6においては、上記パスメトリック更新ユニット23から供給されるパス選択情報を{Sijkl}として示している。

【0048】

パスメモリレジスタ61Aには、ステートs0000における生き残りパスのパスメモリM0000が記憶されている。パスメモリレジスタ62Aでは、ステートs0000に至る2つのパスのパスメモリM0000、M1000うち、パスメトリックが小さくなるパスのパスメモリを選択し、選択されたメモリ値を2倍して0を加算して記憶する。このパスの選択情報は、図5のパスメトリック更新ユニット23におけるステートs0000での比較結果を元にしている。フリップフロップ63Aによってラッチされたパスメモリレジスタ62Aの値は、パスメモリレジスタ61Aの値として記憶される。

パスメモリレジスタ61Bには、ステートs0001における生き残りパスのパスメモリM0001が記憶されている。パスメモリレジスタ62Bでは、ステートs0001に至る2つのパスのパスメモリM0000、M1000うち、パスメトリックが小さくなるパスのパスメモリを選択し、選択されたメモリ値を2倍して1を加算して記憶する。このパスの比較情報は、パスメトリック更新ユニット23におけるステートs0001での比較結果を元にしている。フリップフロップ63Bによってラッチされたパスメモリレジスタ62Bの値は、パスメモリレジスタ61Bの値として記憶される。

パスメモリレジスタ61Cには、ステートs1000における生き残りパスのパスメモリM1000が記憶されている。パスメモリレジスタ62Cでは、ステートs1000に至るパスのパスメモリM1100を2倍し、0を加算して記憶する。フリップフロップ63Cによってラッチされたパスメモリレジスタ62Cの値は、パスメモリレジスタ61Cの値として記憶される。

パスメモリレジスタ61Dには、ステートs1001における生き残りパスのパスメモリM1001が記憶されている。パスメモリレジスタ62Dでは、ステートs1001に至るパスのパスメモリM1100を2倍し、1を加算して記憶する。フリップフロップ63Dによってラッチされたパスメモリレジスタ62Dの値は、パスメモリレジスタ61Dの値として記憶される。

パスメモリレジスタ61Eには、ステートs0011における生き残りパスのパスメモリM0011が記憶されている。パスメモリレジスタ62Eでは、ステートs0011に至る2つのパスのパスメモリM0001、M1001のうち、パスメトリックが小さくなるパスのパスメモリを選択し、選択されたメモリ値を2倍して1を加算して記憶する。このパスの選択情報は、図5のパスメトリック更新ユニット23におけるステートs0011での比較結果を元にしている。フリップフロップ63Eによってラッチされたパスメモリレジスタ62Eの値は、パスメモリレジスタ61Eの値として記憶される。

パスメモリレジスタ61Fには、ステートs1100における生き残りパスのパスメモリM1100が記憶されている。パスメモリレジスタ62Fでは、ステートs1100に至る2つのパスのパスメモリM0001、M1001のうち、パスメトリックが小さくなるパスのパスメモリを選択して、選択されたメモリ値を2倍して0を加算し、記憶する。このパスの選択情報は、パスメトリック更新ユニット23におけるステートs1100での比較結果を元にしている。フリップフロップ63Fによってラッチされたパスメモリレジスタ62Fの値は、パスメモリレジスタ61Fの値として記憶される。

パスメモリレジスタ61Gには、ステートs0110における生き残りパスのパスメモリM0110が記憶されている。パスメモリレジスタ62Gでは、ステートs0110に至るパスのパスメモリM0011を2倍して0を加算し記憶する。フリップフロップ63Gによってラッチされたパスメモリレジスタ62Gの値は、パスメモリレジスタ61Gの値として記憶される。

パスメモリレジスタ61Hには、ステートs0111における生き残りパスのパスメモリM0111が記憶されている。パスメモリレジスタ62Hでは、ステートs0111に至るパスのパスメモリM0011を2倍して1を加算し、記憶する。フリップフロップ63Hによってラッチされたパスメモリレジスタ62Hの値は、パスメモリレジスタ61Hの値として記憶される。

パスメモリレジスタ61Iには、ステートs1110における生き残りパスのパスメモリM1110が記憶されている。パスメモリレジスタ62Iでは、ステートs1110に至る2つのパスのパスメモリM0111、M1111のうち、パスメトリックの小さくなるパスのパスメモリを選択して、選択したメモリ値を2倍して0を加算して記憶する。このパスの選択情報は、パスメトリック更新ユニット23におけるステートs1110での比較結果を元にしている。フリップフロップ63Iによってラッチされたパスメモリレジスタ62Iの値は、パスメモリレジスタ61Iの値として記憶される。

パスメモリレジスタ61Jには、ステートs1111における生き残りパスのパスメトリックM1111が記憶されている。パスメモリレジスタ62Jでは、ステートs1111に至る2つのパスのパスメモリM0111、M1111のうち、パスメトリックの小さくなるパスのパスメモリを選択して、選択したメモリ値を2倍して1を加算し、記憶する。このパスの選択情報は、パスメトリック更新ユニット23におけるステートs1111での比較結果を元にしている。フリップフロップ63Jによってラッチされたパスメモリレジスタ62Jの値は、パスメモリレジスタ61Jの値として記憶される。

【0049】

以上のパスメモリ更新ユニット24に記憶されているビット系列は、上述のパスの選択を繰り返しながら、最終的に尤もらしいビット系列に収束していく。収束するまでにかかる時間は、拘束長の5倍程度といわれている。従って、パスメモリを30ビットのシフトレジスタで構成すれば、パスメモリのうち上位のビットは、収束している。従って、PRML検出器6では、ステートs1111のパスメモリの最上位のビット(MSB)を選択して、これをビット検出結果として出力する。

【0050】

このようにD1制約、ターゲットレスポンスPR(1,2,2,2,1)のPRML検出器6が構成されるが、本例では、特に図6に示すようにパスメモリ更新ユニット24において、パスの選択が行われる6つのステートにおけるパスメモリの比較情報を検出して、出力するように変更を行う。

つまり図6においてパスメモリレジスタ62A、62B、62E、62F、62I、62Jにおいてはパスメモリの選択が行われるが、これらにおいて選択対象となる2つのパスメモリの比較情報を、それぞれ出力する。図6において、出力される6個のパスメモリ比較情報を{cijkl}として示している。

このパスメモリ比較情報{cijkl}は、比較された消滅パスが1ビット単独誤りか、最短マークのシフトによる2ビット誤りとなっているかどうか、の情報である。換言すれば、ビタビ検出で生き残りパスの選択を行う際に、生き残りパスと比較された消滅パスのパスメモリが持っている誤りの種類を示す情報である。

このパスメモリ比較情報を検出する方法を説明する。

【0051】

比較消滅パスが1ビット単独誤りとなっているような場合のパスの選択情報は、2つの比較パスのパスメモリの最新のビットから数えてc番目のビットを除いた1番目から2c−1番目までビットが一致しているか否かの情報である。これはターゲットレスポンスがPR(1,2,2,2,1)であるような拘束長が5のPRML検出では、パスメモリの下位(最新ビット)から数えて5番目のビットを除いた1番目から9番目のビットが一致しているかどうかの情報に相当する。

図7は、その様子を説明する図である。

この図において、実線で表された信号は、最終的に検出されるパスをパーシャルレスポンス系列で表した図であり、また、点線で表された信号は、上記パスと比較された1ビット誤りのパスをパーシャルレスポンス系列で表した図である。

ここで、信号の各点は、チャネルクロックに同期して行われるサンプリングのタイミングを表している。

サンプリングとサンプリングの間のタイミングは、丁度ステートのタイミングに相当するので、ステートの種類を図に示した。

図に示したように、最終検出パスは、s0000、s0001、s0011、s0111、s1111、s1111と遷移している。この結果、最後のステートにおいてパスメモリは、・・・・000011111となっている。

一方、消滅パスは、s0000、s0000、s0001、s0011、s0111、s1111と遷移している。この結果、最後のステートにおいてパスメモリは、・・・・・000001111となっている。

従って、この2つのパスメモリは、5番目のビットを除いて少なくとも1番目から9番目のビットが一致していることがわかる。

ほかの遷移においても同様、1ビットの単独誤りがある場合は、5番目のビットを除いて少なくとも1番目から9番目のビットが一致していることが確認できる。

従って、パスの選択情報として、パス比較の行われるステートのそれぞれで、2つの比較パスの下位(最新ビット)から数えて5番目のビットを除いた1番目から9番目のビットが一致している場合を1、一致していない場合を0とするような情報を出力するように構成すればよい。

【0052】

次に、比較パスが最短マークシフトエラーによる2ビット誤りとなるような場合のパスの選択情報は、2つの比較パスのパスメモリの最新のビットから数えてc+d+1番目のビットが異なっていて、かつ、c、c+d+1番目のビットを除いた1番目から2c+2d−1番目までビットが一致しているか、否かの情報である。これは最短マークのマーク長(最短ランレングス+1)が2で、ターゲットレスポンスがPR(1,2,2,2,1)であるような本例のPRML検出では、この情報は、パスメモリの5番目のビットを除いた1番目から9番目のビットが一致しているかどうかの情報に相当する。

図8は、その様子を模式的に表した図である。

この図において、実線で表された信号は、最終的に検出されるパスをパーシャルレスポンス系列で表した図であり、また、点線で表された信号は、上記パスと比較された1ビット誤りのパスをパーシャルレスポンス系列で表した図である。

ここで、信号の各点は、チャネルクロックに同期して行われるサンプリングのタイミングを表している。

サンプリングとサンプリングの間のタイミングは、丁度ステートのタイミングに相当するので、図7と同様にステートの種類を図示した。

この図8に示したように、最終検出パスは、s0000、s0001、s0011、s0110、s1100、s1000、s0000、s0000と遷移している。この結果、最後のステートにおいてパスメモリは、・・・・00001100000となっている。

一方、消滅パスは、s0000、s0000、s0001、s0011、s0110、s1100、s1000、s0000と遷移している。この結果、最後のステートにおいてパスメモリは、・・・・・00000110000となっている。

この2つのパスメモリは、5番目と7番目のビットが異なっており、それ以外の少なくとも1番目から11番目のビットが一致していることがわかる。

ほかの遷移においても同様、最短マークのシフト誤りがある場合は、5、7番目のビットが異なり、それ以外の少なくとも1番目から11番目のビットが一致していることが確認できる。

従って、パスの選択情報として、パス比較の行われるステートのそれぞれで、2つの比較パスの下位(最新ビット)から数えて7番目のビットが異なっており、かつ、5番目と7番目を除いた1番目から11番目のビットが一致している場合を1、一致していない場合を0とするような情報を出力するように構成すればよい。

【0053】

なお、このほかに、最短マークより一つ大きなマークのシフトエラーなどについても同様にして情報を検出できる。このようなエラーの出現確率は上記2つほど多くは無いが、ユークリッド距離が上記2つに続いて小さいものであるから、上記2つに次ぐ確率で出現されるものである。

この場合は、2つの比較パスのパスメモリの最新のビットから数えてc+d+2番目のビットが異なっていて、かつ、c、c+d+2番目のビットを除いた1番目から2c+2d番目までビットが一致しているか、否かの情報である。これは、最短マークのマーク長(最短ランレングス+1)が2で、ターゲットレスポンスがPR(1,2,2,2,1)であるような本例のPRML検出では、この情報は、パスメモリの6番目のビットを除いた1番目から10番目のビットが一致しているかどうかの情報に相当する。

従って、たとえば、パスの選択情報として、パス比較の行われるステートのそれぞれで、2つの比較パスの下位(最新ビット)から数えて7番目のビットが異なっており、かつ、5番目と7番目を除いた1番目から11番目のビットが一致している場合を1、一致していない場合を0とするような情報を出力するように構成すればよい。

【0054】

以上のようにして、パス比較を行っている6つのステートにおいて検出されたパスメモリ比較情報は、これらの各ステートのパスメモリレジスタ(62A、62B、62E、62F、62I、62J)から、次に述べるパス比較メモリ更新ユニット24に出力される。

【0055】

図9は、以上のようにして得られたパスメモリ比較情報をパス比較メモリ更新ユニット24で記憶し、また、更新していく様子を説明する図である。

図9のパス比較メモリ更新ユニット28は、パスメモリレジスタ71A、71B、71E、71F、71I、71Jと、パスメモリレジスタ72A、72B、72E、72F、72I、72Jと、フリップフロップ73A、73B、73E、73F、73I、73Jによって構成されている。

パスメモリレジスタ71Aには、ステートs0000におけるここまでのパスメモリ比較情報M0000が記憶されている。パスメモリレジスタ72Aでは、図6のステートs0000に対するパスメモリレジスタ62Aから得られたパスメモリ比較情報c0000を、これまでのパスメモリ比較情報M0000のメモリ値を2倍した値に加算する。フリップフロップ73Aによってラッチされたパスメモリレジスタ72Aの値は、パスメモリレジスタ71Aの値として記憶される。

パスメモリレジスタ71Bには、ステートs0001におけるここまでのパスメモリ比較情報M0001が記憶されている。パスメモリレジスタ72Bでは、図6のステートs0001に対するパスメモリレジスタ62Bから得られたパスメモリ比較情報c0001を、これまでのパスメモリ比較情報M0001のメモリ値を2倍した値に加算する。フリップフロップ73Bによってラッチされたパスメモリレジスタ72Bの値は、パスメモリレジスタ71Bの値として記憶される。

パスメモリレジスタ71Eには、ステートs0011におけるここまでのパスメモリ比較情報M1000が記憶されている。パスメモリレジスタ72Eには、図6のステートs0011に対するパスメモリレジスタ62Eから得られたパスメモリ比較情報c0011を、これまでのパスメモリ比較情報M0011のメモリ値を2倍した値に加算する。フリップフロップ73Eによってラッチされたパスメモリレジスタ72Eの値は、パスメモリレジスタ71Eの値として記憶される。

パスメモリレジスタ71Fには、ステートs1100におけるこれまでのパスメモリ比較情報M1100が記憶されている。パスメモリレジスタ72Fでは、図6のステートs1100に対するパスメモリレジスタ62Fから得られたパスメモリ比較情報c1100を、これまでのパスメモリ比較情報M1100のメモリ値を2倍した値に加算する。フリップフロップ73Fによってラッチされたパスメモリレジスタ72Fの値は、パスメモリレジスタ71Fの値として記憶される。

パスメモリレジスタ7Iには、ステートs1110におけるここまでのパスメモリ比較情報M1110が記憶されている。パスメモリレジスタ72Iでは、図6のステートs1110に対するパスメモリレジスタ62Iから得られたパスメモリ比較情報c0111を、これまでのパスメモリ比較情報M1110のメモリ値を2倍した値に加算する。フリップフロップ73Iによってラッチされたパスメモリレジスタ72Iの値は、パスメモリレジスタ71Iの値として記憶される。

パスメモリレジスタ71Jには、ステートs1111におけるここまでのパスメモリ比較情報M1111が記憶されている。パスメモリレジスタ72Jでは、図6のステートs1111に対するパスメモリレジスタ62Jから得られたパスメモリ比較情報c1111を、これまでのパスメモリ比較情報M1111のメモリ値を2倍した値に加算する。フリップフロップ73Jによってラッチされたパスメモリレジスタ72Jの値は、パスメモリレジスタ71Jの値として記憶される。

以上のようにして得られたパスメモリ比較情報{cijkl}は、差メトリックの分布指標を計算するジッタ計算ユニット29に対して出力される。

【0056】

図10は、パスメトリック比較の際に比較されたパスメトリックの差分、すなわち、差メトリックをPRML検出器6の外部で再現するための差メトリック計算ブロック27である。

この差メトリック計算ブロック27は、減算器81と、フリップフロップ82A〜82Dと、掛け算器83A〜83Eと、加算器84によって構成されている。

なお、フリップフロップの数、掛け算器の数は、必要に応じて変更するものとする。

減算器81には、再生信号のサンプリング値をPRML検出器6の遅延量だけ遅延する遅延回路25からの再生信号rと、ブランチシーケンス26からのビット列pが供給される。

【0057】

差メトリックの分布について計算をする前に、計算の簡略化方法について考える。

ここで、r0、r1、r2、r3、r4・・・は、順にPRMLでビタビ検出を行う際に用いられる再生信号を0、1、・・・と添え字分のチャネルクロックだけ遅延させた信号であるものとする。

また、p0、p1、p2、p3、p4・・・は、上記再生信号に同期している生き残りパスに対応したパーシャルレスポンス系列(ブランチシーケンス26からのビット列)であるものとする。

このとき、生き残りパスのパスメトリックは、

M0=(r0−p0)2+(r1−p1)2+(r2−p2)2+(r3−p3)2+(r4−p4)2

である。

また、1ビット単独誤りがある場合の消滅パスのパスメトリックは、

M1=(r0+1−p0)2+(r1+2−p1)2+(r2+2−p2)2+(r3+2−p3)2+(r4+1−p4)2

である。

従って、差メトリックdMは、

dM=M1−M0

=1・(r0−p0)+2・(r1−p1)+2・(r2−p2)+2・(r3−p3)+1・(r4−p4)+14

となる。

なお、「14」は図15でも説明したように、PR(1,2,2,2,1)における1ビット誤りのビット系列のパーシャルレスポンス系列に対するユークリッド距離であるが、これは図7の実線と点線の各サンプル点の差を二乗した値の和に相当する。

【0058】

さらに差メトリックdMの分布を調べるには、分散を計算する必要がある。ここで、消滅パスに1ビット単独誤りがある場合の差メトリックは、「14」を中心として正規分布をしていると考えられるので、差メトリックdMにおいて「14」を除いた項で分散を求めれば充分である。従って、差メトリックの分布指標として、

dM’=(r0−p0)+2・(r1−p1)+2・(r2−p2)+2・(r3−p3)+(r4−p4)

の分散、あるいは、標準偏差を求めれば充分であることがわかる。

なお、ここでは誤りのビット系列として、0が1に変わるタイプの誤りのものを用いているが、逆の特性であっても同様である。

【0059】

図10においては、減算器81には、再生信号のサンプリング値をPRML検出器6の遅延量だけ遅延する遅延回路25からの再生信号rと、ブランチシーケンス26からのビット列pが供給され、r−pの値が得られる。この減算器81の出力値は、フリップフロップ82A〜82Dによるシフトレジスタによって1クロックタイミングづつずれて掛け算器83A〜83Eに供給され、さらに掛け算器83A〜83Eの出力が加算器84で加算されて差メトリックdM’とされる。

この場合、掛け算器83A〜83Eの係数を順に1,2,2,2,1とする。このようにすれば、加算器84の出力は、上記の差メトリックから平均値14を減じた値としての差メトリックdM’を出力することができる。この差メトリックdM’を、ジッタ計算ユニット29において後述する選択方式で選択して、分散、あるいは、標準偏差を計算する。

【0060】

以上の図10の差メトリック計算ユニット27による差メトリックdM’とは、消滅パスが1ビット単独誤りに対応するパスであった場合の差メトリックであって、一般化すれば、

dM’=Σpj・(rn-j−qn-j)

で表すことができる。ただし、Σはjが1からdになるまで項を加算する。

これは、ビタビ検出によって検出された拘束長分のビット列に同期した再生信号rnから数えてdクロック遡る再生信号rn-dまでのdチャネルクロック分の再生信号rn-1・・rn-dと、これらの再生信号に同期している生き残りパスのパーシャルレスポンス系列qn-1・・qn-dの間の差分に対して、パーシャルレスポンスの元での1チャネルクロックのパルスに対するdチャネルクロックのレスポンスp1・・pdとを順に掛け合わせた後に加算して得られる値である。

【0061】

ところで以上の図10は1ビット単独誤りを想定した場合の差メトリックdM’の算出構成である。

一方で、消滅パスが、最短マークのシフトによる2ビット誤りがある場合を考えると差メトリック計算ユニット27は図11のように構成されればよい。