検出装置及び検出方法

【課題】本発明は従来よりも設計の自由度を向上させた等価時間サンプリング方式の検出装置を提供する。

【解決手段】送信手段(20)は、各送信パルスが所定の送信パルス繰り返し周期内に配置されるパルス列信号であって、各送信パルスの位相を当該送信パルス繰り返し周期内において段階的にシフトした送信パルス列信号を検出波として送出する。受信手段(30)は、反射波を受信して受信パルス列信号を形成し、受信パルス列信号をサンプリングして複数の受信パルスの波形データを出力する。信号処理手段(40)は、複数の受信パルスの各波形データの時間軸を各送信パルスの位相の段階的シフトに対応して調整し、各波形データを合成して一つの受信パルスの波形データを形成する。

【解決手段】送信手段(20)は、各送信パルスが所定の送信パルス繰り返し周期内に配置されるパルス列信号であって、各送信パルスの位相を当該送信パルス繰り返し周期内において段階的にシフトした送信パルス列信号を検出波として送出する。受信手段(30)は、反射波を受信して受信パルス列信号を形成し、受信パルス列信号をサンプリングして複数の受信パルスの波形データを出力する。信号処理手段(40)は、複数の受信パルスの各波形データの時間軸を各送信パルスの位相の段階的シフトに対応して調整し、各波形データを合成して一つの受信パルスの波形データを形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は等価時間サンプリング方式により対象物からの反射波を検出する検出装置等に関する。

【背景技術】

【0002】

高周波信号のサンプリングにおいて時間分解能向上を図るための手法として、例えば特許文献1(特開平1−235863号公報)に開示されているような等価時間サンプリング方式が知られている。等価時間サンプリングは、繰り返し周期を持った高周波入力信号の順次異なる一部分を入力信号の周期に比して十分長い周期で抽出し、これ等サンプリングされた多数のサンプリング点のデータを用い、入力信号に相当する信号を形成するものである。

【0003】

また、反射波の検出器として等価時間サンプリング方式を用いたパルス型レーダーも特許文献2(特開2008−145236号公報)などで知られている。

【0004】

等価時間サンプリング方式レーダーは、パルス列中の個々の送信パルスに対応する目標からの反射波に対して、1周期毎に少しずつオフセットした時刻でサンプリング(標本化)を行い、得られた複数の送信パルスの反射波のデータを一つの時間軸上に再構成して反射波を再現する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平1−235863号公報

【特許文献2】特開2008−145236号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上述した等価時間サンプリング方式を用いるとAD変換器の時間分解能を等価的に高めることが出来る。

【0007】

しかしながら、例えば、乳がん検査器のように被測定対象が送受信アンテナからごく短距離(2cm程度)に存在するような場合、探知波の往復時間が数100psec(数100×10-12秒)程度しかない。この場合、AD変換の時間分解能は10〜20psec程度必要とされる。現状ではAD変換器のサンプリング間隔は40psec程度が限界である。更に、等価時間サンプリングレーダー方式においてはパルス送出間隔やサンプリングレート等のパラメーター設定に一定の条件が課される。また、AD変換器のサンプリング信号の位相を高速でシフトする回路、例えば、高速で動作するPLL回路の形成が難しい。

【0008】

このため、等価時間サンプリングレーダー方式を採用して所要の時間分解能を持つ検出器を製作しようとするとき装置設計の制約が問題となる。

【0009】

よって、本発明は従来よりも設計の自由度を向上させた等価時間サンプリング方式の検出装置を提供することを課題の一つとする。

【0010】

また、本発明は送受信アンテナから対象物までの距離が極短距離である場合にも適用可能とした等価時間サンプリング方式レーダーを提案することを課題の一つとする。

【0011】

また、本発明は従来よりも設計の自由度を向上させた等価時間サンプリング方法を提供することを課題の一つとする。

【課題を解決するための手段】

【0012】

(第1のグループ)

上記課題を達成する本発明の一つの形態の検出装置は、検出波を対象物に対して送信する送信手段と、上記検出波が当該対象物から反射した反射波を受信して受信信号を生成する受信手段と、上記受信信号を処理する信号処理手段と、を備える検出装置において、上記検出波は、複数の送信パルスが第1の周期で繰り返される送信パルス列信号であり、上記受信手段は、上記反射波を受信して複数のパルスを含む受信パルス列信号を生成し、当該受信パルス列信号を第2の周期で上記第2の周期より長い第3の周期の間にサンプリングして複数の受信パルス信号を形成し、上記信号処理手段は、上記複数の受信パルス信号の各々の時間軸を上記複数の受信パルス信号の各々と上記複数の送信パルスの各々との位相差に応じて補正し、補正された当該複数の受信パルス信号を合成して1つの受信パルス信号を形成することを特徴とする。

【0013】

かかる構成とすることによって、設計の自由度を向上させた等価時間サンプリング方式の検出装置を得ることが可能となる。

【0014】

上記検出装置内部又は外部で上記第3の周期のトリガー信号を生成し、上記送信手段及び上記受信手段は、前記トリガー信号に応答して動作することが望ましい。それにより、送信系及び受信系で用いられる信号の時間軸を合わせることが可能となる。

【0015】

上記複数の受信パルス信号の合成は、1つの時間軸上に当該複数の受信パルス信号のデータを時系列的に配置することで行われることが望ましい。それにより、1つの受信パルス波形が複数の受信パルス信号のデータで形成されるのでより細密な波形が形成され、サンプリングにおける分解能を向上させた場合と同じ結果が得られる。

【0016】

上記送信手段は上記複数の送信パルスの位相設定に関わる第1のPLL回路を含み、上記受信手段は上記サンプリングに関わる第2のPLL回路を含み、上記第1及び第2のPLL回路は基準発振器を共通にする。それによって、回路の簡略化が可能となる。

【0017】

上記検出波が、電磁波、音波、及び光波のいずれかであることが望ましい。、検出波は電磁波が望ましいが、これに限定されるものではない。

【0018】

また、本発明の一つの形態の送信装置は、検出波を対象物に対して送信する送信装置において、上記検出波を上記対象物に対して送信する送信手段を含み、上記検出波は、複数の送信パルスが第1の周期で繰り返される送信パルス列信号であり、上記対象物から反射した反射波は受信装置に受信され、受信パルスが繰り返される受信パルス列信号が生成され、当該受信パルス列信号は第2の周期で前記第2の周期より長い第3の周期の間にサンプリングされ複数の受信パルス信号が生成され、上記複数の受信パルス信号の各々の時間軸は上記複数の受信パルス信号の各々と上記複数の送信パルスの各々との位相差に応じて補正され、補正された当該複数の受信パルス信号は合成されて1つの受信パルス信号が形成される。

【0019】

かかる構成とすることによって、設計の自由度を向上させた等価時間サンプリング方式の送信装置を得ることが可能となる。

【0020】

また、本発明の一つの形態の受信装置は、送信された検出波が対象物から反射した反射波を受信する受信装置において、受信手段と、信号処理手段と、を含み、上記検出波は、複数の送信パルスが第1の周期で繰り返される送信パルス列信号であり、上記受信手段は、上記反射波を受信して複数のパルスを含む受信パルス列信号を生成し、当該受信パルス列信号を第2の周期で上記第2の周期より長い第3の周期の間にサンプリングして複数の受信パルス信号を形成し、上記信号処理手段は、上記複数の受信パルス信号の各々の時間軸を上記複数の受信パルス信号の各々と上記複数の送信パルスの各々との位相差に応じて補正し、補正された当該複数の受信パルス信号を合成して1つの受信パルス信号を形成する。

【0021】

かかる構成とすることによって、設計の自由度を向上させた等価時間サンプリング方式の受信装置を得ることが可能となる。

【0022】

また、本発明の一つの形態の検出方法は、検出波を対象物に対して送信し、当該対象物から反射した反射波を受信して上記反射波を検出する検出方法において、複数の送信パルスが第1の周期で繰り返される送信パルス列信号である上記検出波を上記対象物に送信する過程と、上記反射波を受信して受信パルスが繰り返される受信パルス列信号を生成し、当該受信パルス列信号を第2の周期で上記第2の周期より長い第3の周期の間にサンプリングし、複数の受信パルス信号を生成する過程と、上記複数の受信パルス信号の各々の時間軸を上記複数の受信パルス信号の各々と上記複数の送信パルスの各々との位相差に応じて補正し、補正された当該複数の受信パルス信号を合成して1つの受信パルス信号を形成する過程と、を含む。

【0023】

かかる構成とすることによって、設計の自由度を向上させた等価時間サンプリング方式の検出方法を得ることが可能となる。

【0024】

供給されるトリガー信号に応答して上記検出波の送信及び前記反射波の受信の動作が開始される、ことが望ましい。それにより、信号の位置(時間軸)合わせが容易になる。

【0025】

(第2のグループ)

本発明の一つの形態の検出装置は、検出波を対象物に対して送出する送信手段と当該対象物からの反射波を受信する受信手段と信号処理手段とを備える検出装置において、上記送信手段は、各送信パルスが所定の送信パルス繰り返し周期内に配置されるパルス列信号であって、各送信パルスの位相を当該送信パルス繰り返し周期内において段階的にシフトした送信パルス列信号を上記検出波として送出し、上記受信手段は、上記反射波を受信して各受信パルスが同波形で位相が異なる受信パルス列信号を形成し、当該受信パルス列信号のレベルを所定のサンプリング周期のサンプリング信号でサンプリングして複数の受信パルスの波形データを出力し、上記信号処理手段は、上記複数の受信パルスの各波形データの時間軸を上記各送信パルスの位相の段階的シフトに対応して調整し、当該複数の受信パルスの各波形データを時系列的に配置して一つの受信パルスの波形データを形成する。

【0026】

かかる構成とすることによって、AD変換器においてサンプリングのタイミングをシフトして同じ受信波形についてサンプリング点が異なる複数のデータを得てこれ等データを合成することによってAD変換の時分解能を向上する等価時間サンプリング方式の場合と比べて設計の自由度を向上する(設計の制約を減らす)ことが可能となる。

【0027】

上記送信パルス繰り返し周期がトリガー信号の繰り返しによって形成され、上記サンプリングが当該トリガー信号に対応して開始されることが望ましい。それにより、トリガー信号に応じて送信動作及び受信動作を同期させることが容易になる。

【0028】

上記複数の受信パルスの各波形データの時間軸の調整は、上記複数の受信パルスの各波形データが担う受信パルス波形の位相を合わせるものである、ことが望ましい。それにより、受信波形上にサンプリング点を揃えることができる。

【0029】

上記送信手段は各送信パルスの位相設定に関わる第1のPLL回路を含み、上記受信手段は上記サンプリング信号の形成に関わる第2のPLL回路を含み、上記第1及び第2のPLL回路は基準発振器の周波数を共通にすることが望ましい。

【0030】

上記検出波が、電磁波、音波、光波のいずれかであることが望ましい。これ等を検査対象物の特性に応じて適宜に選択することによって装置の性能をよく発揮することが出来る。

【0031】

また、本発明の一つの形態は、検出波を対象物に対して送出し、当該対象物からの上記検出波の反射波を受信して当該対象物の位置を検出する検出方法において、各送信パルスが所定の送信パルス繰り返し周期内に配置されるパルス列信号であって、各送信パルスの位相を当該送信パルス繰り返し周期内において段階的にシフトした送信パルス列信号を上記検出波として送出する過程と、上記反射波を受信して各受信パルスが同波形で位相が異なる受信パルス列信号を形成する過程と、当該受信パルス列信号のレベルを所定のサンプリング周期のサンプリング信号でサンプリングして複数の受信パルスの波形データを出力する過程と、上記複数の受信パルスの各波形データの時間軸を上記各送信パルスの位相の段階的シフトに対応して調整する過程と、当該複数の受信パルスの各波形データを時系列的に配置して一つの受信パルスの波形データを形成する過程と、を含む。

【0032】

かかる構成とすることによって、AD変換器においてサンプリングのタイミングをシフトして同じ受信波形についてサンプリング点が異なる複数のデータを得てこれ等データを合成することによってAD変換の時分解能を向上する等価時間サンプリング方式の場合と比べて設計の自由度を向上する(設計の制約を減らす)ことが可能となる。

【0033】

上記送信パルス繰り返し周期がトリガー信号の繰り返しによって形成され、上記サンプリングが当該トリガー信号に対応して開始されることが望ましい。それにより、トリガー信号に応じて送信動作及び受信動作を同期させることが容易になる。

【発明の効果】

【0034】

本発明によれば等価時間サンプリング方式を採用する装置の設計の自由度を向上することが可能となる。例えば、AD変換器をその限界動作付近で動作させて等価時間サンプリング方式を実現することが可能となる。

【図面の簡単な説明】

【0035】

【図1】AD変換器における等価時間サンプリング方式を説明する説明図である。

【図2】クロック発生器で作られるクロック信号の例を説明する説明図である。

【図3】、入力信号を複数の各AD変換器でサンプリングする例を説明する説明図である。

【図4】コントローラーにより複数のAD変換器の出力ょ合成する例を説明する説明図である。

【図5】リングオシレーターの構成例を説明する説明図である。

【図6】リングオシレーターを構成するインバーターの出力の例を説明する説明図である。

【図7】図6に示したクロック出力の順番を並べ替え他例を説明する説明図である。

【図8】PLL回路でリングオシレーターの周波数を一定に制御する例を説明する説明図である。

【図9】等価時間サンプリングレーダーにおける受信信号のサンプリングの例を説明する説明図である。

【図10】サンプリングデータを再構成して受信信号の波形を形成する例を説明する説明図である。

【図11】従来の等価時間サンプリング方式における制約を説明する説明図である。

【図12】実施例の送信系(送信機)から出力される送信パルスの送出タイミング(遅延)を説明する説明図である。

【図13】遅延した送信パルスの反射波(受信信号)をサンプリングした例を説明する説明図である。

【図14】各送信パルスの遅延分で受信したサンプリングデータを補正した例を説明する説明図である。

【図15】一つの時間軸上に時間位置を補正した各測定回のサンプリングデータを並べて波形を再現する例を説明する説明図である。

【図16】実例の等価時間サンプリングレーダー(検出装置)の構成例を説明する説明図である。

【図17】検出装置の送信系の構成例を説明する説明図である。

【図18】リング発振回路を説明する説明図である。

【図19】リング発振回路を構成するインバーターの出力例を説明する説明図である。

【図20】インバーターの出力の順番を変えた例を説明する説明図である。

【図21】遅延部が出力する遅延信号の波形例を説明する説明図である。

【図22】パルス発生器の動作例を説明する説明図である。

【図23】パルス発生器の動作例を説明する説明図である。

【図24】パルス発生器の動作例を説明する説明図である。

【図25】パルス発生器の動作例を説明する説明図である。

【図26】パルス発生器の動作例を説明する説明図である。

【図27】パルス発生器の動作例を説明する説明図である。

【図28】パルス発生器のスイッチSW1〜SW3の動作―態様を説明する説明図である。

【図29】パルス発生器のスイッチSW1〜SW3の動作と形成されるパルス電圧を説明する説明図である。

【図30】3つの遅延信号に基づいて出力パルスが形成されことを説明する説明図である。

【図31】本発明の利点を説明する説明図である。

【図32】本発明の利点を説明する説明図である。

【図33】コントローラーの動作を説明するフローチャートである。

【発明を実施するための形態】

【0036】

以下、本発明の実施の形態について説明する。

本発明は、説明の便宜のため以下のような順序で説明されている。

(1)等価時間サンプリング方式

(1−1)リングオシレーター

(1−2)PLL回路

(2)等価時間サンプリングレーダー方式

(3)等価時間サンプリング方式における制約

(4)本発明の実施例

(4−1)検出装置の構成の概略

(4−2)アンテナ系

(4−3)送信系

(4−4)受信系

(4−5)共通系

(4−6)コントローラーの制御動作例

(4−7)送信系の回路要素

(4−8)リング発振回路

(4−9)PLL回路

(4−10)遅延部

(4−11)パルス発生器

(5)実施例の効果

(5−1)従来の等価時間サンプリング方式の場合

(5−2)本実施例の等価時間サンプリング方式の場合

(6)むすび

【0037】

(1)等価時間サンプリング方式

まず、本発明の理解を容易にするために、先に先行する等価時間サンプリング方式の説明をし、続いて本発明の改良された等価時間サンプリング方式について説明する。

【0038】

図1は、AD変換器における等価時間サンプリング方式を説明する説明図である。この例では、一つの入力信号Ainをサンプリング時期をシフトした複数のAD変換器でサンプリングし、各サンプリング値をコントローラーで一つの時間軸上に合成する。

図1において、101〜105は供給されるアナログ信号Ainをデジタル信号に変換するAD変換器、107はAD変換器101〜105から出力された各デジタルデータを合成処理等する(一つの時間軸上に信号波形を合成する。)コントローラーである。106は各AD変換器101〜105及びコントローラー107にクロック信号CK1〜CK5を供給するクロック発生器である。

【0039】

図2は、クロック発生器106で作られるクロック信号CK1〜CK5の例を示している。同図に示されるように、クロック信号CK1〜CK5は時間tdだけ順次遅れている(なお、AD変換器、クロックの数は任意数である。)。各AD変換器はクロックの立ち上がり又は立ち下がりでサンプリングを始めるが、以下の説明では立ち上がりで動作するものとする。

【0040】

図3は、入力信号Ainの同じ波形を各AD変換器101〜105でサンプリングした例を示している。同図において横軸は時間軸、縦軸は遅延時間(相対値)を示している。複数のチャンネルを示している。

【0041】

図4は、コントローラー107の出力例を示しており、各AD変換器101〜105の各出力(サンプリング値)を一つの時間軸上に時系列的に重ねあわせることで、入力信号Ainを等価的に時間間隔tdでサンプリングしたことと同じ結果を得ている。になる。

【0042】

(1−1)リングオシレーター

AD変換器のクロックは、例えば、リングオシレーターと呼ばれる発振回路で作られる。図5はリングオシレーターの構成例を示している。同図において、501〜505は遅延時間taで動作するインバーターである。奇数個のインバーター501〜505は環状(直列)に接続され、後端のインバーター505の出力は始端のインバーター501の入力となる。

【0043】

図6は、インバーター501〜506の各出力(のクロック波形)V1〜V5を示している。同図に示されるように、インバーター502のクロック出力V2はインバーター501のクロック出力V1が立ち上がってから時間taだけ遅れて立ち下る。インバーター503のクロック出力V3はクロック出力V1が立ち上がってから時間2taだけ遅れて立ち上がる。インバーター504のクロック出力V4はクロックV1が立ち上がってから時間3taだけ遅れて立ち下る。インバーター405のクロック出力V5はクロック出力V1が立ち上がってから時間4taだけ遅れて立ち上がる。クロック出力V1はクロック出力V1が立ち上がってから時間5taだけ遅れて立ち下がる。クロック出力V2はクロック出力V1が立ち下がってから時間taだけ遅れて立ち上がる。この結果、クロック出力V2はクロック出力V1が立ち上がってから時間6taだけ遅れて立ち上がる。

【0044】

図7は、図6に示したクロック出力の順番を並べ替えている。図7に示すように、クロック出力V1、V3、V5、V2、V4の順番で並べるとインバーターの遅延時間の2倍の2taだけずれたクロックが得られる。これが等価時間サンプリング方式で使用するAD変換器のクロックとなる。この場合、クロックの周波数はf=1/(2×n×ta)で表される。ここで、nはインバーターの段数(通常は奇数)、taは一段あたりのインバーターの遅延時間である。

このリングオシレーターの出力は常に制御していないとクロック周期が一定にならないため、通常はPLL回路を用いてクロック間隔を制御する。

【0045】

(1−2)PLL回路

図8は、PLL回路でリングオシレーターの周波数(クロック間隔)を一定にする例を示している。同図において、801は基準発振器、802は分周器、803は位相比較器、804はチャージポンプ、805はローパスフィルター、806はリングオシレーター、807は分周器である。

【0046】

基準発振器801は水晶発振器などで構成され、この出力信号の周波数の安定度がクロック間隔を決める。基準発振器801のクロック出力は分周器802によって分周されて位相比較器803の一方の比較入力端に供給される。比較器803の他方の比較入力端には、リングオシレーター806のクロック出力を分周器807で分周したクロック信号が供給される。位相比較器803は両信号の位相差分に相当する信号をチャージポンプ回路804に供給する。チャージポンプ回路804は位相差の大きさに応じた電流に変換され、ローパスフィルーター805に入力される。入力された信号は不要な雑音成分をローパスフィルーターで取り除かれ直流信号としてリングオシレーター806の制御回路に供給される。制御回路は位相差分が減少するようにリングオシレーター806の電源電圧や閾値を制御して発振周波数を安定にする。

【0047】

(2)等価時間サンプリングレーダー方式

等価時間サンプリングレーダーは上述した等価時間サンプリング方式をレーダーに応用したものである。すなわち、送信機側から高周波パルス信号を送信アンテナで電磁波に変換して一定の時間間隔で対象物に対して繰り返し放射する。対象物で反射した電磁波を受信アンテナで高周波信号に変換して受信し、受信信号を1つのAD変換器でサンプリングする。この際、パルス信号の送出の度にAD変換器のサンプリングタイミングをずらして受信信号からデータの採取を行う。各回の送信パルス信号に対応するサンプリング値群を一つの時間軸上に時系列的に再配置することによって解像度が向上した受信信号が得られ、等価時間サンプリングレーダーを実現することができる。

【0048】

例えば、図9に示すように、アンテナから繰り返し発射する送信パルスの周期を10000psec間隔とし、定位置の被測定対象物から反射してアンテナに戻った受信信号のAD変換のサンプリングレートを70psecとして、例えば、7回のパルス送信について計測する。各回の受信信号のサンプリングポイントは同図の各受信波形に示されるように一定量でシフトしている。

【0049】

図10に示すように、これ等の各回のサンプリング値をコントローラーでデータ処理して同一時間軸上に再構築すると、多点でサンプリングした受信信号を得ることができる。この例では、10psecのサンプリングレートでサンプリングを行った場合と同じ結果を得ている。このように等価時間サンプリングレーダーでは通常のレーダーよりも受信信号の時間分解能が向上する。

【0050】

(3)等価時間サンプリング方式における制約

等価時間サンプリング方式を採用することによる制約について説明する。等価時間サンプリングレーダーでは、送信パルスの繰り返し周期をtp、送信パルスの送出回数kp、AD変換器のサンプリング周期をtadとすると、kp=lcm(tp,tad)/tpの関係が成り立つようにする必要がある。ここで、lcm(tp,tad)はtp、tadの最小公倍数を意味する。このとき等価時間サンプリングレーダーのサンプリング周期tsは、ts=tad/kpとなる。

【0051】

図11は、等価時間サンプリングにおける、送信パルスの繰り返し周期tp、AD変換器のサンプリング周期tad、送信パルスの送出回数kp、サンプリング周期ts(時間分解能)の各パラメーターの設定例を示している。

【0052】

同図に示されるように、特定の等価サンプリングパルス周期(等価時間分解能)tsに設定したい場合、送信パルスの繰り返し周期tp、サンプリング周期tadが特定の組合せに限られる。例えば、等価時間分解能tsを10psecに設計したい場合、例えば、送信系と受信系でクロックを共有するためにパルス繰り返し周期tpを10000(psec)に選定することを条件にすると、サンプリング周期tadが70(psec)と90secの場合に限られる。AD変換器のサンプリング周期tadが40psecの場合には、時間分解能tsを10psecに設定することはできない。すなわち、等価時間サンプリングレーダー方式は設計に制約がある(設計の自由度が低い)。

【0053】

(4)本発明の実施例

本発明では、受信系(受信機側)におけるAD変換のタイミングを順次ずらす等価時間サンプリングではなく、送信系(送信機側)に着目する。所定繰り返し発射周期内で各回の送信パルスの送出タイミングを順次にずらして送信(パルス位置変調(PPM)に類似の送信パルスの送信)し、被測定対象物からの反射波である受信信号のサンプリングを行い、各受信パルスについてのサンプリングデータ群(サンプリング点)のずれ(PPMパルス位置のずれ)を補正して一つの時間軸上に再構成することによって時間分解能を向上したサンプリング結果を得る。それにより、AD変換器における制約を減らして設計の自由度を向上する。

【0054】

図12乃至図15は、本発明の着目点を説明する説明図である。

図12は、送信系(送信機)から出力される送信パルスの送出タイミングを説明する説明図である。同図において、点線の矢印は時間軸上における検出動作の開始位置(トリガーのタイミング)、実線の矢印は時間軸上における実際にパルスを送出した位置である。各点線のトリガー位置で被測定対象体からの受信信号のサンプリング(データ取り込み)が開始され、各実線の位置で被測定対象体に向けて送信パルスが送出される。この例では、説明の便宜上各トリガー位置は時間軸上に等間隔で配置されているが、これに限定されるものではない。トリガーのタイミング(あるいはデータ取り込み開始)とパルス送信のタイミングとのずれ(遅延時間)が所要の関係にあれば良い。

【0055】

なお、1つのトリガー信号(トリガータイミング)に対応して1つの送信パルスを送信することを所定周期で複数回繰り返し、各回毎にトリガー信号から送信パルスの送出までの遅延時間を設定する(例えば、回が増す毎に遅延時間を順次増大させる。)ことにより、図12の送信パルス(実線矢印)の列を形成することができる。また、1つのトリガー信号(トリガータイミング)に対応して、遅延時間が順次増大するように予めパルス位置が設定された複数の送信パルス(パルス列)を送信するようにしても良い。トリガー信号(トリガータイミング)から各送信パルスまでの位置(時間)は設計の際に設定され、既知である。送信パルス列のパルス間隔(遅延)と、送信パルスが被測定対象体から反射して戻った受信パルスの列のパルス間隔とは対応している。

【0056】

図12に示すように、1回目のパルス送出のトリガーとパルス送信のタイミングは重なっているが、これらの2つの時間的なタイミングは時間経過に伴い徐々にずれていく。この例では2回目から各トリガーのタイミング毎にパルス送出のタイミングのずれが50psecずつ増える。例えば、2回目の送出のトリガーとパルス送出のタイミングは50psec、3回目の送出のトリガーとパルス送信のタイミングは100psec、4回目の送出のトリガーとパルス送出のタイミングは150psecずれている。

【0057】

図13は、1回目から4回目まで送出したパルス信号の反射波を受信信号としてコントローラー側でトリガーに対応して取り込んだ波形の例である。1回目から4回目で送出したパルス信号が50psecずつずれていることから、受信信号のパルス波形も1回目から4回目まで50psecずつずれている。この受信パルス信号を同じトリガタイミングでサンプリング間隔40psecのAD変換器でサンプリングすると図13中の各グラフに示すような、複数のサンプリング点のデータ(PPM信号)が得られる。これ等の各回のサンプリング・データ群はコントローラー内のメモリーに各送信(あるいは受信)回毎に区別可能に記憶される。

【0058】

AD変換器で取り込まれたデータはコントローラーに送られるが、コントローラー側では1回目の受信パルスはトリガータイミングと比べて0psecのずれ、2回目の受信パルスはトリガータイミングと比べて50psecのずれ、3回目の受信パルスはトリガータイミングと比べて100psecのずれ、4回目のパルスはトリガータイミングと比べて150psecのずれと予め把握している。

【0059】

そこで、コントローラーは、図14に示すように、記憶した各測定回の波形データ(PPM信号類似)をトリガータイミングからのずれ分を補正した波形に変換する。それにより、サンプリングした各回のパルス波形の位相は揃う。

そして、図15に示すように、一つの時間軸上に各測定回の波形データをサンプリング時点の時間順に並べて再構成すると、等価的に10psecのサンプリングによる波形データが実現できる。

【0060】

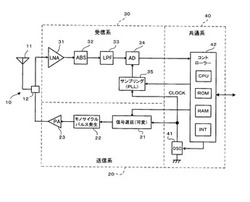

(4−1)検出装置の構成の概略

図16は、上述した送信信号(送信パルス)を順次シフトすることによって等価時間サンプリングを行う等価時間サンプリングレーダー(検出装置)の構成例を示している。

【0061】

この例では、送信系と受信系の動作の同期の容易化(時間軸の共通化)や構成の簡略化、コスト低減等の理由により送信系(送信機)30と受信系(受信機)20の基準信号発生器41を共通(共用)にしている。なお、基準信号発生器41が出力する基準クロック信号の周期をレーダーのパルス発射の繰り返し周期(トリガー周期)に対応するように設定することができる。また、基準クロック信号の立ち上がりや立ち下がりを送受信動作のトリガー信号として利用することができる。また、トリガー信号は図示しない外部の装置(回路)で形成し、これを検出装置に供給することも可能である。

【0062】

図16に示すように、検出装置は、大別して、アンテナ系10、送信系20、受信系30、共通系40によって構成されている。

【0063】

(4−2)アンテナ系

アンテナ系10は、送受信アンテナ11と方向性結合器(あるいはアンテナ切替器)11を備えている。送受信アンテナ11は高周波の送信信号を電磁波に変換して被測定対象物に向けて放射する。また、被測定対象物から反射して戻ってきた電磁波を高周波の受信信号に変換する。方向性結合器11は送信信号をアンテナ11に送り、受信信号を受信系30に送る。このため、アンテナ11を送信と受信で共用することができる。

【0064】

なお、図16に示す例では、送信系20及び受信系30でアンテナ11を共用しているが、アンテナ系11を送信系に接続される送信アンテナと受信系に接続される受信アンテナとで別々に構成しても良い。

【0065】

(4−3)送信系

送信系20は、コントローラー42から供給されるトリガー信号に対応して基準クロック信号から各パルスが所定時間ずつずれた高周波の送信パルス列を発生してアンテナ11に供給する(図12参照)。アンテナ11はこの送信パルスを電磁波として放出する。

【0066】

より具体的に説明すると、送信系20は、基準信号発生器41の基準クロック信号(トリガー)を所定時間遅延させる信号遅延部21、遅延した基準クロック信号の波形の立ち上がり部又は立ち下がり部で短いパルス信号、例えば、モノサイクルガウシアンパルスを発生するパルス発生部22、発生したパルス信号をパワー増幅してアンテナ11へ送るパワーアンプ23等を備えている。

【0067】

送信系20は、例えば、UWB通信と同様に直接高周波パルスをアンテナ11に出力し、図示しない被測定対象物に向けて電磁波パルスを放射する。信号遅延部21の遅延時間は後述するようにコントローラー42によって設定される。送信系20はコントローラー42から供給されるトリガー信号から所定時間遅延した送信パルスを発生する。これ等の具体的な構成については後述する。

【0068】

(4−4)受信系

受信系30は、受信信号の波形を整形し、基準クロック信号に同期したサンプリング信号で動作するAD変換器によって受信信号のレベルをデータ化する。受信系30は、コントローラー42から供給されるトリガー信号に対応して受信信号のサンプリングを開始する。得られたサンプリングデータはコントローラー42に記憶される。

【0069】

より具体的に説明すると、受信系30は、アンテナ11で受信した高周波パルス信号(例えば、モノサイクルパルス信号)を増幅する低雑音増幅器(LNA)31、低雑音増幅器31で増幅されたモノサイクルパルス信号の絶対値を得る絶対値(ABS)回路32、絶対値回路32の出力から高調波成分を除去するローパスフィルター回路(LPF)33、ローパスフィルター回路33から出力されるアナログ信号(パルス信号波形)をサンプリングしてデータ(デジタル)信号に変換してコントローラー42に供給するAD変換器34、AD変換器34に動作クロックを供給するサンプリングクロック発生部35等を備える。

【0070】

サンプリングクロック発生部35は、例えば、位相同期回路(PLL発振回路)を備え、基準信号発生器41から供給される基準クロック信号CLOCKに同期したサンプリング信号を発生する。サンプリングクロック発生部35はいわゆる周波数シンセサイザー(図示せず)を使用することができ、この場合には、サンプリング信号の周期をコントローラー42によって容易に設定することができる。また、サンプリングクロック発生部35はコントローラー42から供給されるトリガー信号に対応してサンプリング信号のAD変換器への供給を開始するように構成される。これによりコントローラー42で、受信系におけるサンプリング動作の開始を制御することができる。

【0071】

(4−5)共通系

共通系40は、基準信号発生器41、コントローラー42等を備えている。基準信号発生器41は、例えば、周波数変動が少ない水晶発振器を使用することができる。上述したように、基準信号発生器41から出力された基準クロック信号CLOCKは信号遅延部21、サンプリングクロック発生部35等に供給される。なお、分周器などを用いて基準信号発生器41が出力する基準クロック信号の周期(周波数)をコントローラー42によって調整可能である。

【0072】

コントローラー42は、マイクロコンピュータシステムによって構成され、CPU、メモリー(RAM,ROM)、インタフェース等を備えている。コントローラー42は、受信したデータの取り込み、データ処理、送信系・受信系のPLLなどの制御等を行う。コントローラーは各種のものが市販されている。

【0073】

コントローラー42は、送信系20に所定周期でトリガー信号を供給して送信パルスを送出させる。上述したように、送信パルスはトリガタイミングに対して順次遅延するパルスとなっている。コントローラー42はトリガー信号を受信系30にも供給することによって送信した送信パルスの反射波をサンプリングさせることができる。コントローラー42は受信した信号波形のサンプリングデータを各トリガー信号毎に記憶する。

【0074】

なお、受信系30にトリガー信号を与えることは必須ではない。例えば、AD変換器34を常時動作させておき、コントローラー42はトリガー信号を送信系20に送出したときにAD変換器34の出力するデータを取り込むようにしても良い。このような場合もトリガー信号に対応してサンプリングデータをコントローラー42に取り込む態様に含まれる。

【0075】

コントローラー42は、各トリガー信号における送信パルスの遅延時間を予め記憶している。そして、これ等の複数の信号波形のデータを送信時のずれ(遅延)を調整して合成して、等価的にサンプリングの解像度を高めた反射波パルスの波形を形成する。

【0076】

このようにして得られた高解像度の信号波形から電磁波の往復時間を計算することによって検出装置(アンテナ)から被測定対象物まで距離が計算される。アンテナを複数点の位置に移動して、あるいはアンテナを複数の方向に向けて計測を繰り返して被測定対象物までの距離を求めることによって被測定対象物の形状が抽出される。これ等の結果を図示しない画面表示器に表示することによってレーダー画像を得ることができる。

【0077】

(4−6)コントローラーの制御動作例

図33は、コントローラー42の動作の概要を説明するフローチャートである。

まず、コントローラー42には、検出装置の各部が動作可能な状態になっているときに、等価時間サンプリングにおける各種パラメーター等(送信パルスの繰り返し周期tp、AD変換器のサンプリング周期tad、送信パルスの送出回数kp、サンプリング周期ts等)が予め設定されている(図31参照)。

【0078】

操作者等によって図示しないインタフェース(スイッチなど)から検出動作が指令されると、コントローラー42(のCPU)は、本ルーチンを実行する。

まず、コントローラー42は検出動作を開始するべくトリガー信号をインタフェースを介して送信系の信号遅延部21及び受信系のサンプリングクロック発生部35に送出する(ステップC12)。

【0079】

信号遅延部21はトリガー信号に応答して遅延信号の出力を開始し(ステップS12)、モノサイクルパルス発生部22は遅延信号に基づいてモノサイクルパルス信号(送信パルス)を形成して出力する(ステップS14)。

【0080】

また、受信系のサンプリングクロック発生部35は上記トリガー信号に応答してAD変換器34にサンプリングクロック(動作クロック)を供給して受信系を活性化させ(ステップR12)。受信信号をサンプリングして送信パルスの反射波を抽出する。サンプリングデータはコントローラー42に供給される(R14)。

【0081】

コントローラー42は、サンプリングされた1つの送信パルスについての受信信号のデータをメモリーに記憶する。この際、他の送信パルスの受信データと区別可能に記憶する(ステップC14)。コントローラー42は、トリガー信号の出力回数(あるいは送信パルスの送出回数)が予め定めた回数kpに達したかどうかを判断する(ステップC16)。

【0082】

所定数に達しない場合には(ステップC15;No)、コントローラー42はステップC12及びC14を繰り返して送信パルスの出力指令と、送信パルスに対応する受信データを取り込みを繰り返す(ステップC12からC14)。送信系において、2回目以降の送信バルスの発射に際しては送信パルスの遅延が行われる。この遅延はトリガー信号の発生タイミングからパルス回数に応じて所定時間ずつ増大される(ステップS12〜S14)。

【0083】

トリガー信号の出力回数が所定数kpを越えると(ステップC18;Yes)、コントローラー42はトリガー信号の送出をやめ、メモリーに取り込んだ各送信パルスに対応する複数の受信データ群(図13参照)の時間軸(位相)を調整する。調整は送信パルスの遅延時間分だけ対応する受信データ群の時間軸の位置を進める(受信波形をずらす)ことによって行われる(ステップC18)。それによって、図14に示すように各受信データ群が担っている潜在的な受信波形の位相が同じになる。コントローラー42はこれ等の波形のデータ群を一つの時間軸上に集めて(各受信波形の合成)、図15に示すような高い時間分解能でサンプリングされた受信信号と等価の受信信号の波形データを形成する(ステップC20)。得られた高時間分解能の受信波形データをメモリーに記憶する(ステップC22)。

【0084】

なお、トリガー信号の繰り返し周期と基準信号発生器41から出力される基準クロック信号CLOCKの周期が同じである場合、基準クロック信号の立ち上がり(あるいは立ち下がり)をトリガー信号として利用することが可能である。

【0085】

更に、図示しない信号処理においてこの受信波形に基づいて送信パルスの往復時間を計算することによってアンテナから被測定対象までの距離が求められる。このようにして、一箇所についての被測定対象物の位置(距離)検出が行われる(ステップC24)。複数の箇所から上述した被測定対象物の位置検出を繰り返してデータを集めることによって被測定対象物の形状を知ることが可能となる。

【0086】

(4−7)送信系30の回路要素

更に、上述した送信系20の要部(信号遅延部、モノサイクルパルス発生部)の具体的な構成例について説明する。

【0087】

図17は、送信系20の信号遅延部21とパルス発生部22に相当する部分を説明するもので、当該部分ではトリガタイミングから所定時間遅延した送信パルス(遅延パルス)を発生させる。

【0088】

信号遅延部21は、複数(奇数)個のインバーターを直列に接続してなるリング発振回路211、ローカル発振器、N分周器、M分周器、位相比較器、ローパスフィルターを備えるPLL回路212、直列に接続された複数(偶数)個のインバーターによって構成される遅延部213等によって構成される。N分周器及びM分周器の分周比はコントローラー42によって設定される。PLL回路212はローカル発振器とリング発振回路211の位相差に基づいて直流電圧を発生し、これをリング発振回路211を構成する各インバーターの電源電圧やMOSトランジスター基板のゲートバイアス電圧としてフィードバックする。それにより、インバーター波形の立ち上がり特性が変化し、リング発振回路211の周波数が調整される。また、PLL回路212の直流電圧は後述の遅延部213を構成するインバーターの電源やMOSトランジスター基板のゲートバイアス電圧としても供給される。これにより、遅延部213の遅延時間が設定される。遅延部213の入力端には基準クロック信号CLOCKが供給され、遅延部213の出力端V1〜V6にそれぞれ所定時間ずつ遅延したクロック信号V1〜V6が得られる。

【0089】

(4−8)リング発振回路

図18は、リング発振回路211を説明する図である。この例では5段のインバーターIV1〜IV5で環状に構成されている。各インバーターIVは同じ動作特性を持っている。各インバーターIVに入力された入力信号は時間tdだけ遅れて出力信号として出力される。インバーターIVの入力レベルと出力レベルをそれぞれVHとVLで表す。例えば、VHは電源電圧(例えば5Vや3.3V)、VLは共通電圧(例えば、0Vやグランド電位)とする。例えば、インバーターIV1の出力電圧がある時間t0で電圧VLから電圧VHに変化した場合、インバーターIV2の出力電圧はt0+td遅延して、電圧VHから電圧VLに変化する。

【0090】

リング発振回路211に電源を投入した当初、インバーターIV1、IV2、IV3、IV4、及びIV5が不定状態(電位が決まらない状態)であるが、何らかの要因(ばらつきなど)で、例えば、インバーターIV1の出力電圧がVLになったとすると、インバーターIV2は時間tdだけ遅れて出力電圧がVHに、インバーターIV3はさらに時間tdだけ遅れて出力電圧がVLとなる。インバーターIV4はさらに時間tdだけ遅れて出力電圧がVH、インバーターIV5はさらに時間tdだけ遅れて出力電圧がVL、インバーターV1はさらに時間tdだけ遅れて電位がVHと変化する。この変化を順次繰り返す。この結果、インバーターIV1〜5の出力電圧はある周期で変化し、この周期はインバーターIVの段数×2tdである。

【0091】

図19は、インバーターIV1〜IV5の出力が遅延時間tdで順次変化する様子を示している。

【0092】

図20は、インバーターIVの出力の順番を図19の状態からインバーターV1、V3、V5、V2、V4と並べ変えると各インバーター出力から2tdだけ遅れた信号が作られることを示している。これにより、各2tdだけ遅延されたクロック信号を作ることができる。

【0093】

(4−9)PLL回路

図18に示したリング発振回路211は温度などの外因の影響で発振周波数が変化しやすい傾向がある。実施例では、図17に示したように、PLL回路212を用いてリング発振回路211の周波数を安定に制御している。また、PLL回路212でリング発振回路211の周波数を制御することによってインバーターIV1〜IV5の遅延時間を調整する。各インバーターIV1〜IV5は、例えば、図示しないインバーターの回路電源の電圧やMOSトランジスターのバックゲート電圧を変えることによって出力波形の立ち上がり・立ち下がり特性が調整可能になされている。この制御電圧をPLL回路212で形成する。

【0094】

上述したように、PLL回路212は、基準発振回路の出力信号の周波数をN分周するN分周器、リング発振回路211の出力信号の周波数をM分周するM分周器、両分周器の出力信号の位相を比較する位相比較器、ローパスフィルター(LPF)を備えている。分周数M,Nはコントローラー42によって設定される。PLL回路212はM分周器の出力信号の位相がN分周器の出力信号の位相と同じになるようにリング発振回路211の周波数をを可変する。位相比較器の出力はローパスフィルターで平滑化されて雑音成分が除去され、リング発振器211及び遅延部213に制御電圧として供給される。

【0095】

(4−10)遅延部

上述したように、PLL回路212は遅延部213を制御する電圧信号を生成する。図17に示すように、遅延部213を構成する遅延素子は、リング発振回路211を構成するインバーターと同じ回路構成のインバーターを使用している。2つのインバーターを一組として一段遅延素子を構成し、これを所要遅延時間に対応して複数段縦列接続して遅延部213を構成している。実施例では遅延素子D1〜D6の六段構成としているが、これに限定されない。遅延素子としてのインバーターはPLL回路212から供給される電圧信号のレベルによって遅延時間tdが設定される。一段の遅延素子Dの遅延時間Δtは2tdとなっている。例えば、遅延素子D1〜D6は、100psecの遅延時間に設定される(インバーター1つ当たりの遅延時間tdが50psec)。遅延部213は一端に入力される基準クロック信号CLOCKを遅延して遅延素子D1〜D6の各出力端にそれぞれ遅延信号V1〜V6を出力する。

【0096】

図21は遅延信号V1〜V6の波形例を示している。遅延信号V1は基準クロック信号CLOCKに対して100psec遅延した信号である。遅延信号V2は基準クロック信号CLOCKに対して200psec遅延した信号である。遅延信号V3はCLOCKに対して300psec遅延した信号である。遅延信号V4は基準クロック信号CLOCKに対して400psec遅延した信号である。遅延信号V5は基準クロック信号CLOCKに対して500psec遅延した信号である。遅延信号V6は基準クロック信号CLOCKに対して600psec遅延した信号である。

【0097】

これら遅延素子D1〜D6の各出力はパルス発生器222〜225に供給される。パルス発生器222は、遅延信号V1〜V3(100psec遅延、200psec遅延、300psec遅延)からモノサイクルパルスPG1を形成する(図21参照)。パルス発生器223は遅延信号V2〜V4(200psec遅延、300psec遅延、400psec遅延)からモノサイクルパルスPG2を形成する。パルス発生器224は、遅延信号V3〜V5(300psec遅延、400psec遅延、500psec遅延)からモノサイクルパルスPG3を形成する。パルス発生器225は、遅延信号V4〜V6(400psec遅延、500psec遅延、600psec遅延)からモノサイクルパルスPG4を形成する。

【0098】

図21に示されるように、基準クロック信号CLOCK(トリガー)から各パルスPG1〜PG4(送信パルスに相当)は100psecずつずれる。パルスPGの幅は遅延素子Dの遅延時間によって設定される。

【0099】

(4−11)パルス発生器

図22はパルス発生回路222を説明する説明図である。パルス発生回路223〜225もパルス発生回路222と同様に構成されるのでその説明は省略する。モノサイクルパルス(短パルス)の形成は、以下に説明するものに限らるものではなく、例えば、特開2007−274681に開示されている短パルス形成の技術を使用することが出来る。

【0100】

図22乃至図27に示すように、パルス発生器222は、3つの電流源I1〜I3、電流源I1〜I3の各電流をそれぞれ制御するスイッチSW1〜SW3、及び電流源I1〜I3の電流が流れる負荷抵抗(例えば、1K[Ω])で構成されている。

電流源I1〜I3は、予め定められた所定の電流値を流す。例えば、電流源I1は1mA、電流源I2は2mA、電流源I3は1mA流すように設定される。電流の向きは、電流源記号内の矢印方向(下向き)である。

【0101】

パルス発生器222のスイッチSW1〜3は、遅延信号V1〜V3(図21の遅延信号V1〜V3参照)で制御されている。遅延信号V1〜V3は、ある一定時間ごとに信号のレベルが反転する。遅延信号V1とV2とV3との間では、遅延信号V2は時間Δt(2td)だけ遅延信号V1より遅れている。遅延信号V3は時間2Δt(4td)だけ遅延信号V1より遅れている。

【0102】

なお、パルス発生器223のスイッチSW1〜3は遅延信号V2〜V4、パルス発生器224のスイッチSW1〜3は遅延信号V3〜V5、パルス発生器225のスイッチSW1〜3は遅延信号V4〜V6で制御されている(図17参照)。

図22〜図27は、パルス発生回路222のスイッチSW1〜SW3の動作態様を示している。

【0103】

図28はスイッチSW1〜3の動作条件を示している。スイッチSW1とSW3は遅延信号V1とV3の電圧レベルがVLのときには、スイッチが非導通状態になり、電流源の電流を負荷抵抗に流さない。また、遅延信号V1とV3のレベルがVHのときにはスイッチSW1とSW3が導通状態となり電流源の電流I1と電流I3を負荷抵抗に流す。スイッチSW2はスイッチSW1及びSW3と逆の特性で、スイッチSW2は遅延信号V2のレベルがVLのときには、スイッチSWが導通状態になり、電流源I2の電流を抵抗に流す。スイッチSW2がVHのときに非導通状態になり、電流源I2の電流を負荷抵抗に流さない。負荷抵抗に発生する電圧V0は、負荷抵抗に流れた電流値×抵抗値の積になる。

【0104】

図29及び図30は、遅延信号V1〜V3がスイッチSW1〜SW3に供給されたときの各スイッチSWの動作と、負荷抵抗に発生する出力電圧V0のパルス波形を示している。図30に示す出力電圧V0の時間軸上の領域A〜FにおけるスイッチSW1〜3の動作が図29に示されている。また、領域A〜FにおけるスイッチSW1〜3の動作が図22〜図27に示されている。

【0105】

図21及び図30に示すように、パルス発生器222は3つの遅延信号V1〜V3に基づいて領域Bで凸状のパルス(正パルス)であり領域Cで凹状のパルス(負パルス)である1サイクルのパルス波形に相当するモノサイクルパルス(出力信号V0)を形成する。パルス発生器222の出力のパルス幅は基準クロック信号の遅延信号(V1,V2,V3,…)の遅延時間で設定されることが判る。

【0106】

パルス発生器223〜225も同様に3つの遅延信号に基づいてモノサイクルパルスを形成する。パルス発生器222〜225は形成したモノサイクルパルスを信号選択器221に供給する。信号選択器221はコントローラー42によって制御され、一連の送信パルスの出力に対応してトリガー信号から所定時間ずつずれた複数のモノサイクルパルスを順次選択する。

【0107】

図12に示すように、選択された複数のモノサイクルパルスは一つの時間軸上に送信パルスとして配置され、周期的な基準時間位置(基準周期、あるいはトリガー位置)から所定時間ずつ遅延した(ずれた)送信パルスの列としてパワーアンプ23に供給される。既述したように、送信パルスは送受信アンテナ11を介して電磁波として被測定対象物に放射され、被測定対象物からの反射波が送受信アンテナ11に戻る。

【0108】

送受信アンテナ11で受信された反射波は受信系30において受信信号(アナログパルス波形)に復調され、サンプリングされる。データのサンプリングは基準周期の間中行っても良いが、例えば、トリガー位置から反射波全体が戻る所定時間以内の時間幅について行うこととしてもよい。それにより、データ量を減らすことができる。

なお、送信パルスの基準時間位置に対するずれとこの送信パルスの受信データの対応が判っていればコントローラー42で時間軸を調整して受信波形の合成ができるので、信号選択器221におけるモノサイクルパルスの選択順序は任意の順序で設定しも良い。

【0109】

(5)実施例の効果

図11及び図31,図32を参照して従来例の等価時間サンプリング方式(一定周期で送信パルスを送信し、受信パルス毎に受信側のサンプリング位置をシフトする形式)と本発明の実施例の等価時間サンプリング方式(送信パルス側の各パルス位置をシフト(パルス位置変調)し、受信側のサンプリング間隔を一定とする形式)との効果の差異について説明する。

【0110】

(5−1)従来の等価時間サンプリング方式の場合

既述したように(図11参照)、パルス発射の繰り返し周期をtp、ADのサンプリング周期をtad、パルスの送出回数をkpとすると、kp=lcm(tp, tad)/tp なる関係がある。ここで、lcm(a,b)はa,bの最小公倍数である。パルスの送出回数は等価時間サンプリング周期が最小となるようにした場合のパルス発射の繰り返し数である。

【0111】

例えば、基準発振器の発振周波数(周期)と同じになるように送信パルス発射の繰り返し周期tpを10000psecとし、AD変換器のサンプリング周期tadを種々に設定してパラメーターを計算すると図11のように特定のパラメーターの組合せになる。もし、パルス発射の繰り返し周期tpを10000psecに限定しないならば、図31に示すようにより多くのパラメーターを選定することが出来る。

【0112】

パルス発射の繰り返し周期tpを10000psecに選定した場合、図11に示すようにAD変換器のサンプリング周期tadが70psec(サンプリング回数kpが7回)及び90psec(サンプリング回数kpが9回)の場合でしかサンプリングの時間分解能10psecを実現できない。すなわち、設計の自由度が少ない。

【0113】

(5−2)本実施例の等価時間サンプリング方式の場合

図32に示すように、実施例ではパルス発射の繰り返し周期tpは10000psecに選定するが、送信パルスの位置(位相)を各送信パルス発射の繰り返し周期tp毎にシフトする。この周期tp内でパルス位置変調(PPM)信号のように送信パルスの位置を移動すると、AD変換器のサンプリング点をシフトした場合と同様の結果を得ることが出来る。

【0114】

例えば、パルス繰り返し周期10000psecでAD変換器のサンプリング周期を40psecに選定した場合、パルス繰り返し周期内での送信パルスの遅延(位相シフト)を50psecに設定し、パルス位置をずらすとパルス送信回数4回で時間分解能10psecが実現できる(図13乃至図15参照)。これは上記(1)の場合(送信回数7回、9回)に比べて送信パルスの送信回数を減らすことが出来る。また、AD変換器の動作性能を発揮させること出来る。

【0115】

また、パルス繰り返し周期10000psecでAD変換器のサンプリング周期が50psecの場合、パルス繰り返し周期内での送信パルスの遅延(位相シフト)を40psecに設定し、この周期内でパルス位置をずらすと送信回数5回で時間分解能10psecのサンプリングを実現できる。これは上記(1)の場合(送信回数7回、9回)に比べて送信パルスの送信回数を減らすことが出来る。また、AD変換器の動作性能を発揮させること出来る。

【0116】

(別途の表現)

また、実施例の発明(検出装置)を別の表現で示せば、検出波を対象物に対して送出する送信手段と当該対象物からの反射波を受信する受信手段と信号処理手段とを備える検出装置において、上記送信手段は、各送信パルスが所定の送信パルス繰り返し周期内に配置されるパルス列信号であって、各送信パルスの位相を当該送信パルス繰り返し周期内において予め段階的にシフトした送信パルス列信号を上記検出波として送出し、上記受信手段は、上記反射波を受信して各受信パルスが同波形で位相が異なる受信パルス列信号を形成し、当該受信パルス列信号のレベルを所定のサンプリング周期のサンプリング信号でサンプリングして複数の受信パルスの波形データを出力し、上記信号処理手段は、上記複数の受信パルスの各波形データの時間軸を上記各送信パルスの位相の段階的シフトに対応して調整し、当該複数の受信パルスの各波形データを時系列的に配置して一つの受信パルスの波形データを形成するもの、であるとも言える。

【0117】

また、実施例の発明(検出装置)を別の表現で示せば、検出波を対象物に対して送信する送信手段と、上記検出波が当該対象物から反射した反射波を受信して受信信号を生成する受信手段と、上記受信信号を処理する信号処理手段と、を備える検出装置であって、上記検出波は、第1の周期のパルス列であって当該周期におけるパルスの位相が互いに異なるようにシフトされた複数の送信パルスを含む送信パルス列信号であり、上記受信手段は、上記反射波を受信して複数のパルスを含む受信パルス列信号を生成し、当該受信パルス列信号を第2の周期でサンプリングして複数の受信パルス信号を形成し、上記信号処理手段は、上記複数の受信パルス信号の各位相を上記複数の送信パルスにおけるパルス位相のシフトに対応して揃えて、当該複数の受信パルス信号を合成して1つの受信パルス信号を形成する、ことを特徴とする検出装置とも言える。

【0118】

また、実施例の発明(方法)を別の表現で示せば、検出波を対象物に対して送出し、当該対象物からの上記検出波の反射波を受信して当該対象物の位置を検出する検出方法において、各送信パルスが所定の送信パルス繰り返し周期内に配置されるパルス列信号であって、各送信パルスの位相を当該送信パルス繰り返し周期内において予め段階的にシフトした送信パルス列信号を上記検出波として送出する過程と、上記反射波を受信して各受信パルスが同波形で位相が異なる受信パルス列信号を形成する過程と、当該受信パルス列信号のレベルを所定のサンプリング周期のサンプリング信号でサンプリングして複数の受信パルスの波形データを出力する過程と、上記複数の受信パルスの各波形データの時間軸を上記各送信パルスの位相の段階的シフトに対応して調整する過程と、当該複数の受信パルスの各波形データを時系列的に配置して一つの受信パルスの波形データを形成する過程と、を含むものであるとも言える。

【0119】

また、実施例の発明(方法)を別の表現で示せば、検出波を対象物に対して送信し、当該対象物から反射した反射波を受信して上記反射波を検出する検出方法であって、第1の周期のパルス列であって当該周期におけるパルスの位相が互いに異なるようにシフトされた複数の送信パルスを含む送信パルス列信号を上記検出波として上記対象物に送信する過程と、上記反射波を受信して受信パルスが繰り返される受信パルス列信号を生成し、当該受信パルス列信号を第2の周期でサンプリングし、複数の受信信号を生成する過程と、上記複数の受信信号の各々の時間軸を前記複数の送信パルスの位相シフトに応じて補正し、1つの時間軸上に合成することにより上記受信パルスの波形データを形成する過程と、を含むものであるとも言える。

【0120】

(6)むすび

以上説明したように、本発明の実施例によれば従来の等価時間サンプリング方式に比べて設計の自由度が増す。また、所要の送信パルスの送信回数を減らすことが出来るので好都合である。

【0121】

前述したように、例えば、乳がん検査器のように被測定対象が送受信アンテナからごく短距離(2cm程度)に存在する場合、探知波の往復時間が数100psec(psec=10-12秒)程度しかない。この場合、AD変換の時間分解能は10〜20psec程度必要とされるが、現状ではAD変換器のサンプリング間隔は40psec程度が限界である。本発明を適用すれば現状のAD変換器(40〜50psec程度)を使用してサンプリングの時間分解能10psecを実現できる。

【0122】

なお、実施例では、センス波(検出波)として電磁波(電波)を使用しているが、これに代えて超音波や光を使用することが可能である。被測定対象の特性に応じて選択することができる。

【0123】

また、上記発明の実施の形態を通じて説明された実施例は、用途に応じて適宜に変更若しくは改良を加えて用いることができ、本発明は上述した実施形態の記載に限定されるものではない。そのような組み合わせ又は変更若しくは改良を加えた形態も本発明の技術的範囲に含まれ得ることが、特許請求の範囲の記載から明らかである。

【0124】

例えば、実施例では送信系と受信系の基準発振器41を共通にしている場合について説明しているが、送信系と受信系とで別々に発振器を備えていても良い。そのような場合に本発明を適用すれば、更に設計の自由度が増して好ましい。また、発振器あるいは発振器の機能をコントローラーに内蔵することが出来る。

【産業上の利用可能性】

【0125】

本発明によれば、等価時間サンプリング方式における設計の自由度を向上することができるので、高い時間分解能を容易に得ることが可能となる。したがって、等価時間サンプリング方式レーダーなどの検出装置の設計の自由度を向上することができる。例えば、乳がんの検査装置のようにアンテナから被測定対象物までの距離が極めて短いために等価時間サンプリング方式におけるパラメーター選定が制約される場合に設計がより容易化されて好ましい。

【符号の説明】

【0126】

10 アンテナ系、11 送受信アンテナ、12 方向性結合器、20 送信系、21 信号遅延部、22 モノサイクルパルス発生部、23 パワー増幅部、30 受信系、31 低雑音増幅器、32 絶対値回路、33 ローパスフィルター、34 AD変換器、40 共通系、41 基準発振器、42 コントローラー

【技術分野】

【0001】

本発明は等価時間サンプリング方式により対象物からの反射波を検出する検出装置等に関する。

【背景技術】

【0002】

高周波信号のサンプリングにおいて時間分解能向上を図るための手法として、例えば特許文献1(特開平1−235863号公報)に開示されているような等価時間サンプリング方式が知られている。等価時間サンプリングは、繰り返し周期を持った高周波入力信号の順次異なる一部分を入力信号の周期に比して十分長い周期で抽出し、これ等サンプリングされた多数のサンプリング点のデータを用い、入力信号に相当する信号を形成するものである。

【0003】

また、反射波の検出器として等価時間サンプリング方式を用いたパルス型レーダーも特許文献2(特開2008−145236号公報)などで知られている。

【0004】

等価時間サンプリング方式レーダーは、パルス列中の個々の送信パルスに対応する目標からの反射波に対して、1周期毎に少しずつオフセットした時刻でサンプリング(標本化)を行い、得られた複数の送信パルスの反射波のデータを一つの時間軸上に再構成して反射波を再現する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平1−235863号公報

【特許文献2】特開2008−145236号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上述した等価時間サンプリング方式を用いるとAD変換器の時間分解能を等価的に高めることが出来る。

【0007】

しかしながら、例えば、乳がん検査器のように被測定対象が送受信アンテナからごく短距離(2cm程度)に存在するような場合、探知波の往復時間が数100psec(数100×10-12秒)程度しかない。この場合、AD変換の時間分解能は10〜20psec程度必要とされる。現状ではAD変換器のサンプリング間隔は40psec程度が限界である。更に、等価時間サンプリングレーダー方式においてはパルス送出間隔やサンプリングレート等のパラメーター設定に一定の条件が課される。また、AD変換器のサンプリング信号の位相を高速でシフトする回路、例えば、高速で動作するPLL回路の形成が難しい。

【0008】

このため、等価時間サンプリングレーダー方式を採用して所要の時間分解能を持つ検出器を製作しようとするとき装置設計の制約が問題となる。

【0009】

よって、本発明は従来よりも設計の自由度を向上させた等価時間サンプリング方式の検出装置を提供することを課題の一つとする。

【0010】

また、本発明は送受信アンテナから対象物までの距離が極短距離である場合にも適用可能とした等価時間サンプリング方式レーダーを提案することを課題の一つとする。

【0011】

また、本発明は従来よりも設計の自由度を向上させた等価時間サンプリング方法を提供することを課題の一つとする。

【課題を解決するための手段】

【0012】

(第1のグループ)

上記課題を達成する本発明の一つの形態の検出装置は、検出波を対象物に対して送信する送信手段と、上記検出波が当該対象物から反射した反射波を受信して受信信号を生成する受信手段と、上記受信信号を処理する信号処理手段と、を備える検出装置において、上記検出波は、複数の送信パルスが第1の周期で繰り返される送信パルス列信号であり、上記受信手段は、上記反射波を受信して複数のパルスを含む受信パルス列信号を生成し、当該受信パルス列信号を第2の周期で上記第2の周期より長い第3の周期の間にサンプリングして複数の受信パルス信号を形成し、上記信号処理手段は、上記複数の受信パルス信号の各々の時間軸を上記複数の受信パルス信号の各々と上記複数の送信パルスの各々との位相差に応じて補正し、補正された当該複数の受信パルス信号を合成して1つの受信パルス信号を形成することを特徴とする。

【0013】

かかる構成とすることによって、設計の自由度を向上させた等価時間サンプリング方式の検出装置を得ることが可能となる。

【0014】

上記検出装置内部又は外部で上記第3の周期のトリガー信号を生成し、上記送信手段及び上記受信手段は、前記トリガー信号に応答して動作することが望ましい。それにより、送信系及び受信系で用いられる信号の時間軸を合わせることが可能となる。

【0015】

上記複数の受信パルス信号の合成は、1つの時間軸上に当該複数の受信パルス信号のデータを時系列的に配置することで行われることが望ましい。それにより、1つの受信パルス波形が複数の受信パルス信号のデータで形成されるのでより細密な波形が形成され、サンプリングにおける分解能を向上させた場合と同じ結果が得られる。

【0016】

上記送信手段は上記複数の送信パルスの位相設定に関わる第1のPLL回路を含み、上記受信手段は上記サンプリングに関わる第2のPLL回路を含み、上記第1及び第2のPLL回路は基準発振器を共通にする。それによって、回路の簡略化が可能となる。

【0017】

上記検出波が、電磁波、音波、及び光波のいずれかであることが望ましい。、検出波は電磁波が望ましいが、これに限定されるものではない。

【0018】

また、本発明の一つの形態の送信装置は、検出波を対象物に対して送信する送信装置において、上記検出波を上記対象物に対して送信する送信手段を含み、上記検出波は、複数の送信パルスが第1の周期で繰り返される送信パルス列信号であり、上記対象物から反射した反射波は受信装置に受信され、受信パルスが繰り返される受信パルス列信号が生成され、当該受信パルス列信号は第2の周期で前記第2の周期より長い第3の周期の間にサンプリングされ複数の受信パルス信号が生成され、上記複数の受信パルス信号の各々の時間軸は上記複数の受信パルス信号の各々と上記複数の送信パルスの各々との位相差に応じて補正され、補正された当該複数の受信パルス信号は合成されて1つの受信パルス信号が形成される。

【0019】

かかる構成とすることによって、設計の自由度を向上させた等価時間サンプリング方式の送信装置を得ることが可能となる。

【0020】

また、本発明の一つの形態の受信装置は、送信された検出波が対象物から反射した反射波を受信する受信装置において、受信手段と、信号処理手段と、を含み、上記検出波は、複数の送信パルスが第1の周期で繰り返される送信パルス列信号であり、上記受信手段は、上記反射波を受信して複数のパルスを含む受信パルス列信号を生成し、当該受信パルス列信号を第2の周期で上記第2の周期より長い第3の周期の間にサンプリングして複数の受信パルス信号を形成し、上記信号処理手段は、上記複数の受信パルス信号の各々の時間軸を上記複数の受信パルス信号の各々と上記複数の送信パルスの各々との位相差に応じて補正し、補正された当該複数の受信パルス信号を合成して1つの受信パルス信号を形成する。

【0021】

かかる構成とすることによって、設計の自由度を向上させた等価時間サンプリング方式の受信装置を得ることが可能となる。

【0022】

また、本発明の一つの形態の検出方法は、検出波を対象物に対して送信し、当該対象物から反射した反射波を受信して上記反射波を検出する検出方法において、複数の送信パルスが第1の周期で繰り返される送信パルス列信号である上記検出波を上記対象物に送信する過程と、上記反射波を受信して受信パルスが繰り返される受信パルス列信号を生成し、当該受信パルス列信号を第2の周期で上記第2の周期より長い第3の周期の間にサンプリングし、複数の受信パルス信号を生成する過程と、上記複数の受信パルス信号の各々の時間軸を上記複数の受信パルス信号の各々と上記複数の送信パルスの各々との位相差に応じて補正し、補正された当該複数の受信パルス信号を合成して1つの受信パルス信号を形成する過程と、を含む。

【0023】

かかる構成とすることによって、設計の自由度を向上させた等価時間サンプリング方式の検出方法を得ることが可能となる。

【0024】

供給されるトリガー信号に応答して上記検出波の送信及び前記反射波の受信の動作が開始される、ことが望ましい。それにより、信号の位置(時間軸)合わせが容易になる。

【0025】

(第2のグループ)

本発明の一つの形態の検出装置は、検出波を対象物に対して送出する送信手段と当該対象物からの反射波を受信する受信手段と信号処理手段とを備える検出装置において、上記送信手段は、各送信パルスが所定の送信パルス繰り返し周期内に配置されるパルス列信号であって、各送信パルスの位相を当該送信パルス繰り返し周期内において段階的にシフトした送信パルス列信号を上記検出波として送出し、上記受信手段は、上記反射波を受信して各受信パルスが同波形で位相が異なる受信パルス列信号を形成し、当該受信パルス列信号のレベルを所定のサンプリング周期のサンプリング信号でサンプリングして複数の受信パルスの波形データを出力し、上記信号処理手段は、上記複数の受信パルスの各波形データの時間軸を上記各送信パルスの位相の段階的シフトに対応して調整し、当該複数の受信パルスの各波形データを時系列的に配置して一つの受信パルスの波形データを形成する。

【0026】

かかる構成とすることによって、AD変換器においてサンプリングのタイミングをシフトして同じ受信波形についてサンプリング点が異なる複数のデータを得てこれ等データを合成することによってAD変換の時分解能を向上する等価時間サンプリング方式の場合と比べて設計の自由度を向上する(設計の制約を減らす)ことが可能となる。

【0027】

上記送信パルス繰り返し周期がトリガー信号の繰り返しによって形成され、上記サンプリングが当該トリガー信号に対応して開始されることが望ましい。それにより、トリガー信号に応じて送信動作及び受信動作を同期させることが容易になる。

【0028】

上記複数の受信パルスの各波形データの時間軸の調整は、上記複数の受信パルスの各波形データが担う受信パルス波形の位相を合わせるものである、ことが望ましい。それにより、受信波形上にサンプリング点を揃えることができる。

【0029】

上記送信手段は各送信パルスの位相設定に関わる第1のPLL回路を含み、上記受信手段は上記サンプリング信号の形成に関わる第2のPLL回路を含み、上記第1及び第2のPLL回路は基準発振器の周波数を共通にすることが望ましい。

【0030】

上記検出波が、電磁波、音波、光波のいずれかであることが望ましい。これ等を検査対象物の特性に応じて適宜に選択することによって装置の性能をよく発揮することが出来る。

【0031】

また、本発明の一つの形態は、検出波を対象物に対して送出し、当該対象物からの上記検出波の反射波を受信して当該対象物の位置を検出する検出方法において、各送信パルスが所定の送信パルス繰り返し周期内に配置されるパルス列信号であって、各送信パルスの位相を当該送信パルス繰り返し周期内において段階的にシフトした送信パルス列信号を上記検出波として送出する過程と、上記反射波を受信して各受信パルスが同波形で位相が異なる受信パルス列信号を形成する過程と、当該受信パルス列信号のレベルを所定のサンプリング周期のサンプリング信号でサンプリングして複数の受信パルスの波形データを出力する過程と、上記複数の受信パルスの各波形データの時間軸を上記各送信パルスの位相の段階的シフトに対応して調整する過程と、当該複数の受信パルスの各波形データを時系列的に配置して一つの受信パルスの波形データを形成する過程と、を含む。

【0032】

かかる構成とすることによって、AD変換器においてサンプリングのタイミングをシフトして同じ受信波形についてサンプリング点が異なる複数のデータを得てこれ等データを合成することによってAD変換の時分解能を向上する等価時間サンプリング方式の場合と比べて設計の自由度を向上する(設計の制約を減らす)ことが可能となる。

【0033】

上記送信パルス繰り返し周期がトリガー信号の繰り返しによって形成され、上記サンプリングが当該トリガー信号に対応して開始されることが望ましい。それにより、トリガー信号に応じて送信動作及び受信動作を同期させることが容易になる。

【発明の効果】

【0034】

本発明によれば等価時間サンプリング方式を採用する装置の設計の自由度を向上することが可能となる。例えば、AD変換器をその限界動作付近で動作させて等価時間サンプリング方式を実現することが可能となる。

【図面の簡単な説明】

【0035】

【図1】AD変換器における等価時間サンプリング方式を説明する説明図である。

【図2】クロック発生器で作られるクロック信号の例を説明する説明図である。

【図3】、入力信号を複数の各AD変換器でサンプリングする例を説明する説明図である。

【図4】コントローラーにより複数のAD変換器の出力ょ合成する例を説明する説明図である。

【図5】リングオシレーターの構成例を説明する説明図である。

【図6】リングオシレーターを構成するインバーターの出力の例を説明する説明図である。

【図7】図6に示したクロック出力の順番を並べ替え他例を説明する説明図である。

【図8】PLL回路でリングオシレーターの周波数を一定に制御する例を説明する説明図である。

【図9】等価時間サンプリングレーダーにおける受信信号のサンプリングの例を説明する説明図である。

【図10】サンプリングデータを再構成して受信信号の波形を形成する例を説明する説明図である。

【図11】従来の等価時間サンプリング方式における制約を説明する説明図である。

【図12】実施例の送信系(送信機)から出力される送信パルスの送出タイミング(遅延)を説明する説明図である。

【図13】遅延した送信パルスの反射波(受信信号)をサンプリングした例を説明する説明図である。

【図14】各送信パルスの遅延分で受信したサンプリングデータを補正した例を説明する説明図である。

【図15】一つの時間軸上に時間位置を補正した各測定回のサンプリングデータを並べて波形を再現する例を説明する説明図である。

【図16】実例の等価時間サンプリングレーダー(検出装置)の構成例を説明する説明図である。

【図17】検出装置の送信系の構成例を説明する説明図である。

【図18】リング発振回路を説明する説明図である。

【図19】リング発振回路を構成するインバーターの出力例を説明する説明図である。

【図20】インバーターの出力の順番を変えた例を説明する説明図である。

【図21】遅延部が出力する遅延信号の波形例を説明する説明図である。

【図22】パルス発生器の動作例を説明する説明図である。

【図23】パルス発生器の動作例を説明する説明図である。

【図24】パルス発生器の動作例を説明する説明図である。

【図25】パルス発生器の動作例を説明する説明図である。

【図26】パルス発生器の動作例を説明する説明図である。

【図27】パルス発生器の動作例を説明する説明図である。

【図28】パルス発生器のスイッチSW1〜SW3の動作―態様を説明する説明図である。

【図29】パルス発生器のスイッチSW1〜SW3の動作と形成されるパルス電圧を説明する説明図である。

【図30】3つの遅延信号に基づいて出力パルスが形成されことを説明する説明図である。

【図31】本発明の利点を説明する説明図である。

【図32】本発明の利点を説明する説明図である。

【図33】コントローラーの動作を説明するフローチャートである。

【発明を実施するための形態】

【0036】

以下、本発明の実施の形態について説明する。

本発明は、説明の便宜のため以下のような順序で説明されている。

(1)等価時間サンプリング方式

(1−1)リングオシレーター

(1−2)PLL回路

(2)等価時間サンプリングレーダー方式

(3)等価時間サンプリング方式における制約

(4)本発明の実施例

(4−1)検出装置の構成の概略

(4−2)アンテナ系

(4−3)送信系

(4−4)受信系

(4−5)共通系

(4−6)コントローラーの制御動作例

(4−7)送信系の回路要素

(4−8)リング発振回路

(4−9)PLL回路

(4−10)遅延部

(4−11)パルス発生器

(5)実施例の効果

(5−1)従来の等価時間サンプリング方式の場合

(5−2)本実施例の等価時間サンプリング方式の場合

(6)むすび

【0037】

(1)等価時間サンプリング方式

まず、本発明の理解を容易にするために、先に先行する等価時間サンプリング方式の説明をし、続いて本発明の改良された等価時間サンプリング方式について説明する。

【0038】

図1は、AD変換器における等価時間サンプリング方式を説明する説明図である。この例では、一つの入力信号Ainをサンプリング時期をシフトした複数のAD変換器でサンプリングし、各サンプリング値をコントローラーで一つの時間軸上に合成する。

図1において、101〜105は供給されるアナログ信号Ainをデジタル信号に変換するAD変換器、107はAD変換器101〜105から出力された各デジタルデータを合成処理等する(一つの時間軸上に信号波形を合成する。)コントローラーである。106は各AD変換器101〜105及びコントローラー107にクロック信号CK1〜CK5を供給するクロック発生器である。

【0039】

図2は、クロック発生器106で作られるクロック信号CK1〜CK5の例を示している。同図に示されるように、クロック信号CK1〜CK5は時間tdだけ順次遅れている(なお、AD変換器、クロックの数は任意数である。)。各AD変換器はクロックの立ち上がり又は立ち下がりでサンプリングを始めるが、以下の説明では立ち上がりで動作するものとする。

【0040】

図3は、入力信号Ainの同じ波形を各AD変換器101〜105でサンプリングした例を示している。同図において横軸は時間軸、縦軸は遅延時間(相対値)を示している。複数のチャンネルを示している。

【0041】

図4は、コントローラー107の出力例を示しており、各AD変換器101〜105の各出力(サンプリング値)を一つの時間軸上に時系列的に重ねあわせることで、入力信号Ainを等価的に時間間隔tdでサンプリングしたことと同じ結果を得ている。になる。

【0042】

(1−1)リングオシレーター

AD変換器のクロックは、例えば、リングオシレーターと呼ばれる発振回路で作られる。図5はリングオシレーターの構成例を示している。同図において、501〜505は遅延時間taで動作するインバーターである。奇数個のインバーター501〜505は環状(直列)に接続され、後端のインバーター505の出力は始端のインバーター501の入力となる。

【0043】

図6は、インバーター501〜506の各出力(のクロック波形)V1〜V5を示している。同図に示されるように、インバーター502のクロック出力V2はインバーター501のクロック出力V1が立ち上がってから時間taだけ遅れて立ち下る。インバーター503のクロック出力V3はクロック出力V1が立ち上がってから時間2taだけ遅れて立ち上がる。インバーター504のクロック出力V4はクロックV1が立ち上がってから時間3taだけ遅れて立ち下る。インバーター405のクロック出力V5はクロック出力V1が立ち上がってから時間4taだけ遅れて立ち上がる。クロック出力V1はクロック出力V1が立ち上がってから時間5taだけ遅れて立ち下がる。クロック出力V2はクロック出力V1が立ち下がってから時間taだけ遅れて立ち上がる。この結果、クロック出力V2はクロック出力V1が立ち上がってから時間6taだけ遅れて立ち上がる。

【0044】

図7は、図6に示したクロック出力の順番を並べ替えている。図7に示すように、クロック出力V1、V3、V5、V2、V4の順番で並べるとインバーターの遅延時間の2倍の2taだけずれたクロックが得られる。これが等価時間サンプリング方式で使用するAD変換器のクロックとなる。この場合、クロックの周波数はf=1/(2×n×ta)で表される。ここで、nはインバーターの段数(通常は奇数)、taは一段あたりのインバーターの遅延時間である。

このリングオシレーターの出力は常に制御していないとクロック周期が一定にならないため、通常はPLL回路を用いてクロック間隔を制御する。

【0045】

(1−2)PLL回路

図8は、PLL回路でリングオシレーターの周波数(クロック間隔)を一定にする例を示している。同図において、801は基準発振器、802は分周器、803は位相比較器、804はチャージポンプ、805はローパスフィルター、806はリングオシレーター、807は分周器である。

【0046】

基準発振器801は水晶発振器などで構成され、この出力信号の周波数の安定度がクロック間隔を決める。基準発振器801のクロック出力は分周器802によって分周されて位相比較器803の一方の比較入力端に供給される。比較器803の他方の比較入力端には、リングオシレーター806のクロック出力を分周器807で分周したクロック信号が供給される。位相比較器803は両信号の位相差分に相当する信号をチャージポンプ回路804に供給する。チャージポンプ回路804は位相差の大きさに応じた電流に変換され、ローパスフィルーター805に入力される。入力された信号は不要な雑音成分をローパスフィルーターで取り除かれ直流信号としてリングオシレーター806の制御回路に供給される。制御回路は位相差分が減少するようにリングオシレーター806の電源電圧や閾値を制御して発振周波数を安定にする。

【0047】

(2)等価時間サンプリングレーダー方式

等価時間サンプリングレーダーは上述した等価時間サンプリング方式をレーダーに応用したものである。すなわち、送信機側から高周波パルス信号を送信アンテナで電磁波に変換して一定の時間間隔で対象物に対して繰り返し放射する。対象物で反射した電磁波を受信アンテナで高周波信号に変換して受信し、受信信号を1つのAD変換器でサンプリングする。この際、パルス信号の送出の度にAD変換器のサンプリングタイミングをずらして受信信号からデータの採取を行う。各回の送信パルス信号に対応するサンプリング値群を一つの時間軸上に時系列的に再配置することによって解像度が向上した受信信号が得られ、等価時間サンプリングレーダーを実現することができる。

【0048】

例えば、図9に示すように、アンテナから繰り返し発射する送信パルスの周期を10000psec間隔とし、定位置の被測定対象物から反射してアンテナに戻った受信信号のAD変換のサンプリングレートを70psecとして、例えば、7回のパルス送信について計測する。各回の受信信号のサンプリングポイントは同図の各受信波形に示されるように一定量でシフトしている。

【0049】

図10に示すように、これ等の各回のサンプリング値をコントローラーでデータ処理して同一時間軸上に再構築すると、多点でサンプリングした受信信号を得ることができる。この例では、10psecのサンプリングレートでサンプリングを行った場合と同じ結果を得ている。このように等価時間サンプリングレーダーでは通常のレーダーよりも受信信号の時間分解能が向上する。

【0050】

(3)等価時間サンプリング方式における制約

等価時間サンプリング方式を採用することによる制約について説明する。等価時間サンプリングレーダーでは、送信パルスの繰り返し周期をtp、送信パルスの送出回数kp、AD変換器のサンプリング周期をtadとすると、kp=lcm(tp,tad)/tpの関係が成り立つようにする必要がある。ここで、lcm(tp,tad)はtp、tadの最小公倍数を意味する。このとき等価時間サンプリングレーダーのサンプリング周期tsは、ts=tad/kpとなる。

【0051】

図11は、等価時間サンプリングにおける、送信パルスの繰り返し周期tp、AD変換器のサンプリング周期tad、送信パルスの送出回数kp、サンプリング周期ts(時間分解能)の各パラメーターの設定例を示している。

【0052】

同図に示されるように、特定の等価サンプリングパルス周期(等価時間分解能)tsに設定したい場合、送信パルスの繰り返し周期tp、サンプリング周期tadが特定の組合せに限られる。例えば、等価時間分解能tsを10psecに設計したい場合、例えば、送信系と受信系でクロックを共有するためにパルス繰り返し周期tpを10000(psec)に選定することを条件にすると、サンプリング周期tadが70(psec)と90secの場合に限られる。AD変換器のサンプリング周期tadが40psecの場合には、時間分解能tsを10psecに設定することはできない。すなわち、等価時間サンプリングレーダー方式は設計に制約がある(設計の自由度が低い)。

【0053】

(4)本発明の実施例

本発明では、受信系(受信機側)におけるAD変換のタイミングを順次ずらす等価時間サンプリングではなく、送信系(送信機側)に着目する。所定繰り返し発射周期内で各回の送信パルスの送出タイミングを順次にずらして送信(パルス位置変調(PPM)に類似の送信パルスの送信)し、被測定対象物からの反射波である受信信号のサンプリングを行い、各受信パルスについてのサンプリングデータ群(サンプリング点)のずれ(PPMパルス位置のずれ)を補正して一つの時間軸上に再構成することによって時間分解能を向上したサンプリング結果を得る。それにより、AD変換器における制約を減らして設計の自由度を向上する。

【0054】

図12乃至図15は、本発明の着目点を説明する説明図である。

図12は、送信系(送信機)から出力される送信パルスの送出タイミングを説明する説明図である。同図において、点線の矢印は時間軸上における検出動作の開始位置(トリガーのタイミング)、実線の矢印は時間軸上における実際にパルスを送出した位置である。各点線のトリガー位置で被測定対象体からの受信信号のサンプリング(データ取り込み)が開始され、各実線の位置で被測定対象体に向けて送信パルスが送出される。この例では、説明の便宜上各トリガー位置は時間軸上に等間隔で配置されているが、これに限定されるものではない。トリガーのタイミング(あるいはデータ取り込み開始)とパルス送信のタイミングとのずれ(遅延時間)が所要の関係にあれば良い。

【0055】

なお、1つのトリガー信号(トリガータイミング)に対応して1つの送信パルスを送信することを所定周期で複数回繰り返し、各回毎にトリガー信号から送信パルスの送出までの遅延時間を設定する(例えば、回が増す毎に遅延時間を順次増大させる。)ことにより、図12の送信パルス(実線矢印)の列を形成することができる。また、1つのトリガー信号(トリガータイミング)に対応して、遅延時間が順次増大するように予めパルス位置が設定された複数の送信パルス(パルス列)を送信するようにしても良い。トリガー信号(トリガータイミング)から各送信パルスまでの位置(時間)は設計の際に設定され、既知である。送信パルス列のパルス間隔(遅延)と、送信パルスが被測定対象体から反射して戻った受信パルスの列のパルス間隔とは対応している。

【0056】

図12に示すように、1回目のパルス送出のトリガーとパルス送信のタイミングは重なっているが、これらの2つの時間的なタイミングは時間経過に伴い徐々にずれていく。この例では2回目から各トリガーのタイミング毎にパルス送出のタイミングのずれが50psecずつ増える。例えば、2回目の送出のトリガーとパルス送出のタイミングは50psec、3回目の送出のトリガーとパルス送信のタイミングは100psec、4回目の送出のトリガーとパルス送出のタイミングは150psecずれている。

【0057】

図13は、1回目から4回目まで送出したパルス信号の反射波を受信信号としてコントローラー側でトリガーに対応して取り込んだ波形の例である。1回目から4回目で送出したパルス信号が50psecずつずれていることから、受信信号のパルス波形も1回目から4回目まで50psecずつずれている。この受信パルス信号を同じトリガタイミングでサンプリング間隔40psecのAD変換器でサンプリングすると図13中の各グラフに示すような、複数のサンプリング点のデータ(PPM信号)が得られる。これ等の各回のサンプリング・データ群はコントローラー内のメモリーに各送信(あるいは受信)回毎に区別可能に記憶される。

【0058】

AD変換器で取り込まれたデータはコントローラーに送られるが、コントローラー側では1回目の受信パルスはトリガータイミングと比べて0psecのずれ、2回目の受信パルスはトリガータイミングと比べて50psecのずれ、3回目の受信パルスはトリガータイミングと比べて100psecのずれ、4回目のパルスはトリガータイミングと比べて150psecのずれと予め把握している。

【0059】

そこで、コントローラーは、図14に示すように、記憶した各測定回の波形データ(PPM信号類似)をトリガータイミングからのずれ分を補正した波形に変換する。それにより、サンプリングした各回のパルス波形の位相は揃う。

そして、図15に示すように、一つの時間軸上に各測定回の波形データをサンプリング時点の時間順に並べて再構成すると、等価的に10psecのサンプリングによる波形データが実現できる。

【0060】

(4−1)検出装置の構成の概略

図16は、上述した送信信号(送信パルス)を順次シフトすることによって等価時間サンプリングを行う等価時間サンプリングレーダー(検出装置)の構成例を示している。

【0061】

この例では、送信系と受信系の動作の同期の容易化(時間軸の共通化)や構成の簡略化、コスト低減等の理由により送信系(送信機)30と受信系(受信機)20の基準信号発生器41を共通(共用)にしている。なお、基準信号発生器41が出力する基準クロック信号の周期をレーダーのパルス発射の繰り返し周期(トリガー周期)に対応するように設定することができる。また、基準クロック信号の立ち上がりや立ち下がりを送受信動作のトリガー信号として利用することができる。また、トリガー信号は図示しない外部の装置(回路)で形成し、これを検出装置に供給することも可能である。

【0062】

図16に示すように、検出装置は、大別して、アンテナ系10、送信系20、受信系30、共通系40によって構成されている。

【0063】

(4−2)アンテナ系

アンテナ系10は、送受信アンテナ11と方向性結合器(あるいはアンテナ切替器)11を備えている。送受信アンテナ11は高周波の送信信号を電磁波に変換して被測定対象物に向けて放射する。また、被測定対象物から反射して戻ってきた電磁波を高周波の受信信号に変換する。方向性結合器11は送信信号をアンテナ11に送り、受信信号を受信系30に送る。このため、アンテナ11を送信と受信で共用することができる。

【0064】

なお、図16に示す例では、送信系20及び受信系30でアンテナ11を共用しているが、アンテナ系11を送信系に接続される送信アンテナと受信系に接続される受信アンテナとで別々に構成しても良い。

【0065】

(4−3)送信系

送信系20は、コントローラー42から供給されるトリガー信号に対応して基準クロック信号から各パルスが所定時間ずつずれた高周波の送信パルス列を発生してアンテナ11に供給する(図12参照)。アンテナ11はこの送信パルスを電磁波として放出する。

【0066】

より具体的に説明すると、送信系20は、基準信号発生器41の基準クロック信号(トリガー)を所定時間遅延させる信号遅延部21、遅延した基準クロック信号の波形の立ち上がり部又は立ち下がり部で短いパルス信号、例えば、モノサイクルガウシアンパルスを発生するパルス発生部22、発生したパルス信号をパワー増幅してアンテナ11へ送るパワーアンプ23等を備えている。

【0067】

送信系20は、例えば、UWB通信と同様に直接高周波パルスをアンテナ11に出力し、図示しない被測定対象物に向けて電磁波パルスを放射する。信号遅延部21の遅延時間は後述するようにコントローラー42によって設定される。送信系20はコントローラー42から供給されるトリガー信号から所定時間遅延した送信パルスを発生する。これ等の具体的な構成については後述する。

【0068】

(4−4)受信系

受信系30は、受信信号の波形を整形し、基準クロック信号に同期したサンプリング信号で動作するAD変換器によって受信信号のレベルをデータ化する。受信系30は、コントローラー42から供給されるトリガー信号に対応して受信信号のサンプリングを開始する。得られたサンプリングデータはコントローラー42に記憶される。

【0069】

より具体的に説明すると、受信系30は、アンテナ11で受信した高周波パルス信号(例えば、モノサイクルパルス信号)を増幅する低雑音増幅器(LNA)31、低雑音増幅器31で増幅されたモノサイクルパルス信号の絶対値を得る絶対値(ABS)回路32、絶対値回路32の出力から高調波成分を除去するローパスフィルター回路(LPF)33、ローパスフィルター回路33から出力されるアナログ信号(パルス信号波形)をサンプリングしてデータ(デジタル)信号に変換してコントローラー42に供給するAD変換器34、AD変換器34に動作クロックを供給するサンプリングクロック発生部35等を備える。

【0070】

サンプリングクロック発生部35は、例えば、位相同期回路(PLL発振回路)を備え、基準信号発生器41から供給される基準クロック信号CLOCKに同期したサンプリング信号を発生する。サンプリングクロック発生部35はいわゆる周波数シンセサイザー(図示せず)を使用することができ、この場合には、サンプリング信号の周期をコントローラー42によって容易に設定することができる。また、サンプリングクロック発生部35はコントローラー42から供給されるトリガー信号に対応してサンプリング信号のAD変換器への供給を開始するように構成される。これによりコントローラー42で、受信系におけるサンプリング動作の開始を制御することができる。

【0071】

(4−5)共通系

共通系40は、基準信号発生器41、コントローラー42等を備えている。基準信号発生器41は、例えば、周波数変動が少ない水晶発振器を使用することができる。上述したように、基準信号発生器41から出力された基準クロック信号CLOCKは信号遅延部21、サンプリングクロック発生部35等に供給される。なお、分周器などを用いて基準信号発生器41が出力する基準クロック信号の周期(周波数)をコントローラー42によって調整可能である。

【0072】

コントローラー42は、マイクロコンピュータシステムによって構成され、CPU、メモリー(RAM,ROM)、インタフェース等を備えている。コントローラー42は、受信したデータの取り込み、データ処理、送信系・受信系のPLLなどの制御等を行う。コントローラーは各種のものが市販されている。

【0073】

コントローラー42は、送信系20に所定周期でトリガー信号を供給して送信パルスを送出させる。上述したように、送信パルスはトリガタイミングに対して順次遅延するパルスとなっている。コントローラー42はトリガー信号を受信系30にも供給することによって送信した送信パルスの反射波をサンプリングさせることができる。コントローラー42は受信した信号波形のサンプリングデータを各トリガー信号毎に記憶する。

【0074】

なお、受信系30にトリガー信号を与えることは必須ではない。例えば、AD変換器34を常時動作させておき、コントローラー42はトリガー信号を送信系20に送出したときにAD変換器34の出力するデータを取り込むようにしても良い。このような場合もトリガー信号に対応してサンプリングデータをコントローラー42に取り込む態様に含まれる。

【0075】

コントローラー42は、各トリガー信号における送信パルスの遅延時間を予め記憶している。そして、これ等の複数の信号波形のデータを送信時のずれ(遅延)を調整して合成して、等価的にサンプリングの解像度を高めた反射波パルスの波形を形成する。

【0076】

このようにして得られた高解像度の信号波形から電磁波の往復時間を計算することによって検出装置(アンテナ)から被測定対象物まで距離が計算される。アンテナを複数点の位置に移動して、あるいはアンテナを複数の方向に向けて計測を繰り返して被測定対象物までの距離を求めることによって被測定対象物の形状が抽出される。これ等の結果を図示しない画面表示器に表示することによってレーダー画像を得ることができる。

【0077】

(4−6)コントローラーの制御動作例

図33は、コントローラー42の動作の概要を説明するフローチャートである。

まず、コントローラー42には、検出装置の各部が動作可能な状態になっているときに、等価時間サンプリングにおける各種パラメーター等(送信パルスの繰り返し周期tp、AD変換器のサンプリング周期tad、送信パルスの送出回数kp、サンプリング周期ts等)が予め設定されている(図31参照)。

【0078】

操作者等によって図示しないインタフェース(スイッチなど)から検出動作が指令されると、コントローラー42(のCPU)は、本ルーチンを実行する。

まず、コントローラー42は検出動作を開始するべくトリガー信号をインタフェースを介して送信系の信号遅延部21及び受信系のサンプリングクロック発生部35に送出する(ステップC12)。

【0079】

信号遅延部21はトリガー信号に応答して遅延信号の出力を開始し(ステップS12)、モノサイクルパルス発生部22は遅延信号に基づいてモノサイクルパルス信号(送信パルス)を形成して出力する(ステップS14)。

【0080】

また、受信系のサンプリングクロック発生部35は上記トリガー信号に応答してAD変換器34にサンプリングクロック(動作クロック)を供給して受信系を活性化させ(ステップR12)。受信信号をサンプリングして送信パルスの反射波を抽出する。サンプリングデータはコントローラー42に供給される(R14)。

【0081】

コントローラー42は、サンプリングされた1つの送信パルスについての受信信号のデータをメモリーに記憶する。この際、他の送信パルスの受信データと区別可能に記憶する(ステップC14)。コントローラー42は、トリガー信号の出力回数(あるいは送信パルスの送出回数)が予め定めた回数kpに達したかどうかを判断する(ステップC16)。

【0082】

所定数に達しない場合には(ステップC15;No)、コントローラー42はステップC12及びC14を繰り返して送信パルスの出力指令と、送信パルスに対応する受信データを取り込みを繰り返す(ステップC12からC14)。送信系において、2回目以降の送信バルスの発射に際しては送信パルスの遅延が行われる。この遅延はトリガー信号の発生タイミングからパルス回数に応じて所定時間ずつ増大される(ステップS12〜S14)。

【0083】

トリガー信号の出力回数が所定数kpを越えると(ステップC18;Yes)、コントローラー42はトリガー信号の送出をやめ、メモリーに取り込んだ各送信パルスに対応する複数の受信データ群(図13参照)の時間軸(位相)を調整する。調整は送信パルスの遅延時間分だけ対応する受信データ群の時間軸の位置を進める(受信波形をずらす)ことによって行われる(ステップC18)。それによって、図14に示すように各受信データ群が担っている潜在的な受信波形の位相が同じになる。コントローラー42はこれ等の波形のデータ群を一つの時間軸上に集めて(各受信波形の合成)、図15に示すような高い時間分解能でサンプリングされた受信信号と等価の受信信号の波形データを形成する(ステップC20)。得られた高時間分解能の受信波形データをメモリーに記憶する(ステップC22)。

【0084】

なお、トリガー信号の繰り返し周期と基準信号発生器41から出力される基準クロック信号CLOCKの周期が同じである場合、基準クロック信号の立ち上がり(あるいは立ち下がり)をトリガー信号として利用することが可能である。

【0085】

更に、図示しない信号処理においてこの受信波形に基づいて送信パルスの往復時間を計算することによってアンテナから被測定対象までの距離が求められる。このようにして、一箇所についての被測定対象物の位置(距離)検出が行われる(ステップC24)。複数の箇所から上述した被測定対象物の位置検出を繰り返してデータを集めることによって被測定対象物の形状を知ることが可能となる。

【0086】

(4−7)送信系30の回路要素

更に、上述した送信系20の要部(信号遅延部、モノサイクルパルス発生部)の具体的な構成例について説明する。

【0087】

図17は、送信系20の信号遅延部21とパルス発生部22に相当する部分を説明するもので、当該部分ではトリガタイミングから所定時間遅延した送信パルス(遅延パルス)を発生させる。

【0088】

信号遅延部21は、複数(奇数)個のインバーターを直列に接続してなるリング発振回路211、ローカル発振器、N分周器、M分周器、位相比較器、ローパスフィルターを備えるPLL回路212、直列に接続された複数(偶数)個のインバーターによって構成される遅延部213等によって構成される。N分周器及びM分周器の分周比はコントローラー42によって設定される。PLL回路212はローカル発振器とリング発振回路211の位相差に基づいて直流電圧を発生し、これをリング発振回路211を構成する各インバーターの電源電圧やMOSトランジスター基板のゲートバイアス電圧としてフィードバックする。それにより、インバーター波形の立ち上がり特性が変化し、リング発振回路211の周波数が調整される。また、PLL回路212の直流電圧は後述の遅延部213を構成するインバーターの電源やMOSトランジスター基板のゲートバイアス電圧としても供給される。これにより、遅延部213の遅延時間が設定される。遅延部213の入力端には基準クロック信号CLOCKが供給され、遅延部213の出力端V1〜V6にそれぞれ所定時間ずつ遅延したクロック信号V1〜V6が得られる。

【0089】

(4−8)リング発振回路

図18は、リング発振回路211を説明する図である。この例では5段のインバーターIV1〜IV5で環状に構成されている。各インバーターIVは同じ動作特性を持っている。各インバーターIVに入力された入力信号は時間tdだけ遅れて出力信号として出力される。インバーターIVの入力レベルと出力レベルをそれぞれVHとVLで表す。例えば、VHは電源電圧(例えば5Vや3.3V)、VLは共通電圧(例えば、0Vやグランド電位)とする。例えば、インバーターIV1の出力電圧がある時間t0で電圧VLから電圧VHに変化した場合、インバーターIV2の出力電圧はt0+td遅延して、電圧VHから電圧VLに変化する。

【0090】

リング発振回路211に電源を投入した当初、インバーターIV1、IV2、IV3、IV4、及びIV5が不定状態(電位が決まらない状態)であるが、何らかの要因(ばらつきなど)で、例えば、インバーターIV1の出力電圧がVLになったとすると、インバーターIV2は時間tdだけ遅れて出力電圧がVHに、インバーターIV3はさらに時間tdだけ遅れて出力電圧がVLとなる。インバーターIV4はさらに時間tdだけ遅れて出力電圧がVH、インバーターIV5はさらに時間tdだけ遅れて出力電圧がVL、インバーターV1はさらに時間tdだけ遅れて電位がVHと変化する。この変化を順次繰り返す。この結果、インバーターIV1〜5の出力電圧はある周期で変化し、この周期はインバーターIVの段数×2tdである。

【0091】

図19は、インバーターIV1〜IV5の出力が遅延時間tdで順次変化する様子を示している。

【0092】

図20は、インバーターIVの出力の順番を図19の状態からインバーターV1、V3、V5、V2、V4と並べ変えると各インバーター出力から2tdだけ遅れた信号が作られることを示している。これにより、各2tdだけ遅延されたクロック信号を作ることができる。

【0093】

(4−9)PLL回路

図18に示したリング発振回路211は温度などの外因の影響で発振周波数が変化しやすい傾向がある。実施例では、図17に示したように、PLL回路212を用いてリング発振回路211の周波数を安定に制御している。また、PLL回路212でリング発振回路211の周波数を制御することによってインバーターIV1〜IV5の遅延時間を調整する。各インバーターIV1〜IV5は、例えば、図示しないインバーターの回路電源の電圧やMOSトランジスターのバックゲート電圧を変えることによって出力波形の立ち上がり・立ち下がり特性が調整可能になされている。この制御電圧をPLL回路212で形成する。

【0094】

上述したように、PLL回路212は、基準発振回路の出力信号の周波数をN分周するN分周器、リング発振回路211の出力信号の周波数をM分周するM分周器、両分周器の出力信号の位相を比較する位相比較器、ローパスフィルター(LPF)を備えている。分周数M,Nはコントローラー42によって設定される。PLL回路212はM分周器の出力信号の位相がN分周器の出力信号の位相と同じになるようにリング発振回路211の周波数をを可変する。位相比較器の出力はローパスフィルターで平滑化されて雑音成分が除去され、リング発振器211及び遅延部213に制御電圧として供給される。

【0095】

(4−10)遅延部

上述したように、PLL回路212は遅延部213を制御する電圧信号を生成する。図17に示すように、遅延部213を構成する遅延素子は、リング発振回路211を構成するインバーターと同じ回路構成のインバーターを使用している。2つのインバーターを一組として一段遅延素子を構成し、これを所要遅延時間に対応して複数段縦列接続して遅延部213を構成している。実施例では遅延素子D1〜D6の六段構成としているが、これに限定されない。遅延素子としてのインバーターはPLL回路212から供給される電圧信号のレベルによって遅延時間tdが設定される。一段の遅延素子Dの遅延時間Δtは2tdとなっている。例えば、遅延素子D1〜D6は、100psecの遅延時間に設定される(インバーター1つ当たりの遅延時間tdが50psec)。遅延部213は一端に入力される基準クロック信号CLOCKを遅延して遅延素子D1〜D6の各出力端にそれぞれ遅延信号V1〜V6を出力する。

【0096】

図21は遅延信号V1〜V6の波形例を示している。遅延信号V1は基準クロック信号CLOCKに対して100psec遅延した信号である。遅延信号V2は基準クロック信号CLOCKに対して200psec遅延した信号である。遅延信号V3はCLOCKに対して300psec遅延した信号である。遅延信号V4は基準クロック信号CLOCKに対して400psec遅延した信号である。遅延信号V5は基準クロック信号CLOCKに対して500psec遅延した信号である。遅延信号V6は基準クロック信号CLOCKに対して600psec遅延した信号である。

【0097】

これら遅延素子D1〜D6の各出力はパルス発生器222〜225に供給される。パルス発生器222は、遅延信号V1〜V3(100psec遅延、200psec遅延、300psec遅延)からモノサイクルパルスPG1を形成する(図21参照)。パルス発生器223は遅延信号V2〜V4(200psec遅延、300psec遅延、400psec遅延)からモノサイクルパルスPG2を形成する。パルス発生器224は、遅延信号V3〜V5(300psec遅延、400psec遅延、500psec遅延)からモノサイクルパルスPG3を形成する。パルス発生器225は、遅延信号V4〜V6(400psec遅延、500psec遅延、600psec遅延)からモノサイクルパルスPG4を形成する。

【0098】

図21に示されるように、基準クロック信号CLOCK(トリガー)から各パルスPG1〜PG4(送信パルスに相当)は100psecずつずれる。パルスPGの幅は遅延素子Dの遅延時間によって設定される。

【0099】

(4−11)パルス発生器

図22はパルス発生回路222を説明する説明図である。パルス発生回路223〜225もパルス発生回路222と同様に構成されるのでその説明は省略する。モノサイクルパルス(短パルス)の形成は、以下に説明するものに限らるものではなく、例えば、特開2007−274681に開示されている短パルス形成の技術を使用することが出来る。

【0100】

図22乃至図27に示すように、パルス発生器222は、3つの電流源I1〜I3、電流源I1〜I3の各電流をそれぞれ制御するスイッチSW1〜SW3、及び電流源I1〜I3の電流が流れる負荷抵抗(例えば、1K[Ω])で構成されている。

電流源I1〜I3は、予め定められた所定の電流値を流す。例えば、電流源I1は1mA、電流源I2は2mA、電流源I3は1mA流すように設定される。電流の向きは、電流源記号内の矢印方向(下向き)である。

【0101】

パルス発生器222のスイッチSW1〜3は、遅延信号V1〜V3(図21の遅延信号V1〜V3参照)で制御されている。遅延信号V1〜V3は、ある一定時間ごとに信号のレベルが反転する。遅延信号V1とV2とV3との間では、遅延信号V2は時間Δt(2td)だけ遅延信号V1より遅れている。遅延信号V3は時間2Δt(4td)だけ遅延信号V1より遅れている。

【0102】

なお、パルス発生器223のスイッチSW1〜3は遅延信号V2〜V4、パルス発生器224のスイッチSW1〜3は遅延信号V3〜V5、パルス発生器225のスイッチSW1〜3は遅延信号V4〜V6で制御されている(図17参照)。

図22〜図27は、パルス発生回路222のスイッチSW1〜SW3の動作態様を示している。

【0103】

図28はスイッチSW1〜3の動作条件を示している。スイッチSW1とSW3は遅延信号V1とV3の電圧レベルがVLのときには、スイッチが非導通状態になり、電流源の電流を負荷抵抗に流さない。また、遅延信号V1とV3のレベルがVHのときにはスイッチSW1とSW3が導通状態となり電流源の電流I1と電流I3を負荷抵抗に流す。スイッチSW2はスイッチSW1及びSW3と逆の特性で、スイッチSW2は遅延信号V2のレベルがVLのときには、スイッチSWが導通状態になり、電流源I2の電流を抵抗に流す。スイッチSW2がVHのときに非導通状態になり、電流源I2の電流を負荷抵抗に流さない。負荷抵抗に発生する電圧V0は、負荷抵抗に流れた電流値×抵抗値の積になる。

【0104】

図29及び図30は、遅延信号V1〜V3がスイッチSW1〜SW3に供給されたときの各スイッチSWの動作と、負荷抵抗に発生する出力電圧V0のパルス波形を示している。図30に示す出力電圧V0の時間軸上の領域A〜FにおけるスイッチSW1〜3の動作が図29に示されている。また、領域A〜FにおけるスイッチSW1〜3の動作が図22〜図27に示されている。

【0105】

図21及び図30に示すように、パルス発生器222は3つの遅延信号V1〜V3に基づいて領域Bで凸状のパルス(正パルス)であり領域Cで凹状のパルス(負パルス)である1サイクルのパルス波形に相当するモノサイクルパルス(出力信号V0)を形成する。パルス発生器222の出力のパルス幅は基準クロック信号の遅延信号(V1,V2,V3,…)の遅延時間で設定されることが判る。

【0106】

パルス発生器223〜225も同様に3つの遅延信号に基づいてモノサイクルパルスを形成する。パルス発生器222〜225は形成したモノサイクルパルスを信号選択器221に供給する。信号選択器221はコントローラー42によって制御され、一連の送信パルスの出力に対応してトリガー信号から所定時間ずつずれた複数のモノサイクルパルスを順次選択する。

【0107】

図12に示すように、選択された複数のモノサイクルパルスは一つの時間軸上に送信パルスとして配置され、周期的な基準時間位置(基準周期、あるいはトリガー位置)から所定時間ずつ遅延した(ずれた)送信パルスの列としてパワーアンプ23に供給される。既述したように、送信パルスは送受信アンテナ11を介して電磁波として被測定対象物に放射され、被測定対象物からの反射波が送受信アンテナ11に戻る。

【0108】

送受信アンテナ11で受信された反射波は受信系30において受信信号(アナログパルス波形)に復調され、サンプリングされる。データのサンプリングは基準周期の間中行っても良いが、例えば、トリガー位置から反射波全体が戻る所定時間以内の時間幅について行うこととしてもよい。それにより、データ量を減らすことができる。

なお、送信パルスの基準時間位置に対するずれとこの送信パルスの受信データの対応が判っていればコントローラー42で時間軸を調整して受信波形の合成ができるので、信号選択器221におけるモノサイクルパルスの選択順序は任意の順序で設定しも良い。

【0109】

(5)実施例の効果

図11及び図31,図32を参照して従来例の等価時間サンプリング方式(一定周期で送信パルスを送信し、受信パルス毎に受信側のサンプリング位置をシフトする形式)と本発明の実施例の等価時間サンプリング方式(送信パルス側の各パルス位置をシフト(パルス位置変調)し、受信側のサンプリング間隔を一定とする形式)との効果の差異について説明する。

【0110】

(5−1)従来の等価時間サンプリング方式の場合

既述したように(図11参照)、パルス発射の繰り返し周期をtp、ADのサンプリング周期をtad、パルスの送出回数をkpとすると、kp=lcm(tp, tad)/tp なる関係がある。ここで、lcm(a,b)はa,bの最小公倍数である。パルスの送出回数は等価時間サンプリング周期が最小となるようにした場合のパルス発射の繰り返し数である。

【0111】

例えば、基準発振器の発振周波数(周期)と同じになるように送信パルス発射の繰り返し周期tpを10000psecとし、AD変換器のサンプリング周期tadを種々に設定してパラメーターを計算すると図11のように特定のパラメーターの組合せになる。もし、パルス発射の繰り返し周期tpを10000psecに限定しないならば、図31に示すようにより多くのパラメーターを選定することが出来る。

【0112】

パルス発射の繰り返し周期tpを10000psecに選定した場合、図11に示すようにAD変換器のサンプリング周期tadが70psec(サンプリング回数kpが7回)及び90psec(サンプリング回数kpが9回)の場合でしかサンプリングの時間分解能10psecを実現できない。すなわち、設計の自由度が少ない。

【0113】

(5−2)本実施例の等価時間サンプリング方式の場合

図32に示すように、実施例ではパルス発射の繰り返し周期tpは10000psecに選定するが、送信パルスの位置(位相)を各送信パルス発射の繰り返し周期tp毎にシフトする。この周期tp内でパルス位置変調(PPM)信号のように送信パルスの位置を移動すると、AD変換器のサンプリング点をシフトした場合と同様の結果を得ることが出来る。

【0114】

例えば、パルス繰り返し周期10000psecでAD変換器のサンプリング周期を40psecに選定した場合、パルス繰り返し周期内での送信パルスの遅延(位相シフト)を50psecに設定し、パルス位置をずらすとパルス送信回数4回で時間分解能10psecが実現できる(図13乃至図15参照)。これは上記(1)の場合(送信回数7回、9回)に比べて送信パルスの送信回数を減らすことが出来る。また、AD変換器の動作性能を発揮させること出来る。

【0115】

また、パルス繰り返し周期10000psecでAD変換器のサンプリング周期が50psecの場合、パルス繰り返し周期内での送信パルスの遅延(位相シフト)を40psecに設定し、この周期内でパルス位置をずらすと送信回数5回で時間分解能10psecのサンプリングを実現できる。これは上記(1)の場合(送信回数7回、9回)に比べて送信パルスの送信回数を減らすことが出来る。また、AD変換器の動作性能を発揮させること出来る。

【0116】

(別途の表現)

また、実施例の発明(検出装置)を別の表現で示せば、検出波を対象物に対して送出する送信手段と当該対象物からの反射波を受信する受信手段と信号処理手段とを備える検出装置において、上記送信手段は、各送信パルスが所定の送信パルス繰り返し周期内に配置されるパルス列信号であって、各送信パルスの位相を当該送信パルス繰り返し周期内において予め段階的にシフトした送信パルス列信号を上記検出波として送出し、上記受信手段は、上記反射波を受信して各受信パルスが同波形で位相が異なる受信パルス列信号を形成し、当該受信パルス列信号のレベルを所定のサンプリング周期のサンプリング信号でサンプリングして複数の受信パルスの波形データを出力し、上記信号処理手段は、上記複数の受信パルスの各波形データの時間軸を上記各送信パルスの位相の段階的シフトに対応して調整し、当該複数の受信パルスの各波形データを時系列的に配置して一つの受信パルスの波形データを形成するもの、であるとも言える。

【0117】

また、実施例の発明(検出装置)を別の表現で示せば、検出波を対象物に対して送信する送信手段と、上記検出波が当該対象物から反射した反射波を受信して受信信号を生成する受信手段と、上記受信信号を処理する信号処理手段と、を備える検出装置であって、上記検出波は、第1の周期のパルス列であって当該周期におけるパルスの位相が互いに異なるようにシフトされた複数の送信パルスを含む送信パルス列信号であり、上記受信手段は、上記反射波を受信して複数のパルスを含む受信パルス列信号を生成し、当該受信パルス列信号を第2の周期でサンプリングして複数の受信パルス信号を形成し、上記信号処理手段は、上記複数の受信パルス信号の各位相を上記複数の送信パルスにおけるパルス位相のシフトに対応して揃えて、当該複数の受信パルス信号を合成して1つの受信パルス信号を形成する、ことを特徴とする検出装置とも言える。

【0118】

また、実施例の発明(方法)を別の表現で示せば、検出波を対象物に対して送出し、当該対象物からの上記検出波の反射波を受信して当該対象物の位置を検出する検出方法において、各送信パルスが所定の送信パルス繰り返し周期内に配置されるパルス列信号であって、各送信パルスの位相を当該送信パルス繰り返し周期内において予め段階的にシフトした送信パルス列信号を上記検出波として送出する過程と、上記反射波を受信して各受信パルスが同波形で位相が異なる受信パルス列信号を形成する過程と、当該受信パルス列信号のレベルを所定のサンプリング周期のサンプリング信号でサンプリングして複数の受信パルスの波形データを出力する過程と、上記複数の受信パルスの各波形データの時間軸を上記各送信パルスの位相の段階的シフトに対応して調整する過程と、当該複数の受信パルスの各波形データを時系列的に配置して一つの受信パルスの波形データを形成する過程と、を含むものであるとも言える。

【0119】

また、実施例の発明(方法)を別の表現で示せば、検出波を対象物に対して送信し、当該対象物から反射した反射波を受信して上記反射波を検出する検出方法であって、第1の周期のパルス列であって当該周期におけるパルスの位相が互いに異なるようにシフトされた複数の送信パルスを含む送信パルス列信号を上記検出波として上記対象物に送信する過程と、上記反射波を受信して受信パルスが繰り返される受信パルス列信号を生成し、当該受信パルス列信号を第2の周期でサンプリングし、複数の受信信号を生成する過程と、上記複数の受信信号の各々の時間軸を前記複数の送信パルスの位相シフトに応じて補正し、1つの時間軸上に合成することにより上記受信パルスの波形データを形成する過程と、を含むものであるとも言える。

【0120】

(6)むすび

以上説明したように、本発明の実施例によれば従来の等価時間サンプリング方式に比べて設計の自由度が増す。また、所要の送信パルスの送信回数を減らすことが出来るので好都合である。

【0121】

前述したように、例えば、乳がん検査器のように被測定対象が送受信アンテナからごく短距離(2cm程度)に存在する場合、探知波の往復時間が数100psec(psec=10-12秒)程度しかない。この場合、AD変換の時間分解能は10〜20psec程度必要とされるが、現状ではAD変換器のサンプリング間隔は40psec程度が限界である。本発明を適用すれば現状のAD変換器(40〜50psec程度)を使用してサンプリングの時間分解能10psecを実現できる。

【0122】

なお、実施例では、センス波(検出波)として電磁波(電波)を使用しているが、これに代えて超音波や光を使用することが可能である。被測定対象の特性に応じて選択することができる。

【0123】

また、上記発明の実施の形態を通じて説明された実施例は、用途に応じて適宜に変更若しくは改良を加えて用いることができ、本発明は上述した実施形態の記載に限定されるものではない。そのような組み合わせ又は変更若しくは改良を加えた形態も本発明の技術的範囲に含まれ得ることが、特許請求の範囲の記載から明らかである。

【0124】

例えば、実施例では送信系と受信系の基準発振器41を共通にしている場合について説明しているが、送信系と受信系とで別々に発振器を備えていても良い。そのような場合に本発明を適用すれば、更に設計の自由度が増して好ましい。また、発振器あるいは発振器の機能をコントローラーに内蔵することが出来る。

【産業上の利用可能性】

【0125】

本発明によれば、等価時間サンプリング方式における設計の自由度を向上することができるので、高い時間分解能を容易に得ることが可能となる。したがって、等価時間サンプリング方式レーダーなどの検出装置の設計の自由度を向上することができる。例えば、乳がんの検査装置のようにアンテナから被測定対象物までの距離が極めて短いために等価時間サンプリング方式におけるパラメーター選定が制約される場合に設計がより容易化されて好ましい。

【符号の説明】

【0126】

10 アンテナ系、11 送受信アンテナ、12 方向性結合器、20 送信系、21 信号遅延部、22 モノサイクルパルス発生部、23 パワー増幅部、30 受信系、31 低雑音増幅器、32 絶対値回路、33 ローパスフィルター、34 AD変換器、40 共通系、41 基準発振器、42 コントローラー

【特許請求の範囲】

【請求項1】

検出波を対象物に対して送信する送信手段と、前記検出波が当該対象物から反射した反射波を受信して受信信号を生成する受信手段と、前記受信信号を処理する信号処理手段と、を備える検出装置であって、

前記検出波は、複数の送信パルスが第1の周期で繰り返される送信パルス列信号であり、

前記受信手段は、前記反射波を受信して複数のパルスを含む受信パルス列信号を生成し、当該受信パルス列信号を第2の周期で前記第2の周期より長い第3の周期の間にサンプリングして複数の受信パルス信号を形成し、

前記信号処理手段は、前記複数の受信パルス信号の各々の時間軸を前記複数の受信パルス信号の各々と前記複数の送信パルスの各々との位相差に応じて補正し、補正された当該複数の受信パルス信号を合成して1つの受信パルス信号を形成する、ことを特徴とする検出装置。

【請求項2】

前記検出装置内部又は外部で前記第3の周期のトリガー信号を生成し、

前記送信手段及び前記受信手段は、前記トリガー信号に応答して動作する、ことを特徴とする請求項1に記載の検出装置。

【請求項3】

前記複数の受信パルス信号の合成は、1つの時間軸上に当該複数の受信パルス信号のデータを時系列的に配置することで行われる、ことを特徴とする請求項1又は2に記載の検出装置。

【請求項4】

前記送信手段は前記複数の送信パルスの位相設定に関わる第1のPLL回路を含み、前記受信手段は前記サンプリングに関わる第2のPLL回路を含み、前記第1及び第2のPLL回路は基準発振器を共通にする、ことを特徴とする請求項1乃至3のいずれかに記載の検出装置。

【請求項5】

前記検出波が、電磁波、音波、及び光波のいずれかである、請求項1乃至4のいずれかに記載の検出装置。

【請求項6】

検出波を対象物に対して送信する送信装置であって、

前記検出波を前記対象物に対して送信する送信手段を含み、

前記検出波は、複数の送信パルスが第1の周期で繰り返される送信パルス列信号であり、

前記対象物から反射した反射波は受信装置に受信され、受信パルスが繰り返される受信パルス列信号が生成され、当該受信パルス列信号は第2の周期で前記第2の周期より長い第3の周期の間にサンプリングされ複数の受信パルス信号が生成され、前記複数の受信パルス信号の各々の時間軸は前記複数の受信パルス信号の各々と前記複数の送信パルスの各々との位相差に応じて補正され、補正された当該複数の受信パルス信号は合成されて1つの受信パルス信号が形成される、ことを特徴とする送信装置。

【請求項7】

送信された検出波が対象物から反射した反射波を受信する受信装置であって、

受信手段と、信号処理手段と、を含み、

前記検出波は、複数の送信パルスが第1の周期で繰り返される送信パルス列信号であり、

前記受信手段は、前記反射波を受信して複数のパルスを含む受信パルス列信号を生成し、当該受信パルス列信号を第2の周期で前記第2の周期より長い第3の周期の間にサンプリングして複数の受信パルス信号を形成し、

前記信号処理手段は、前記複数の受信パルス信号の各々の時間軸を前記複数の受信パルス信号の各々と前記複数の送信パルスの各々との位相差に応じて補正し、補正された当該複数の受信パルス信号を合成して1つの受信パルス信号を形成する、ことを特徴とする受信装置。

【請求項8】

検出波を対象物に対して送信し、当該対象物から反射した反射波を受信して前記反射波を検出する検出方法であって、

複数の送信パルスが第1の周期で繰り返される送信パルス列信号である前記検出波を前記対象物に送信する過程と、

前記反射波を受信して受信パルスが繰り返される受信パルス列信号を生成し、当該受信パルス列信号を第2の周期で前記第2の周期より長い第3の周期の間にサンプリングし、複数の受信パルス信号を生成する過程と、

前記複数の受信パルス信号の各々の時間軸を前記複数の受信パルス信号の各々と前記複数の送信パルスの各々との位相差に応じて補正し、補正された当該複数の受信パルス信号を合成して1つの受信パルス信号を形成する過程と、を含む検出方法。

【請求項9】

供給されるトリガー信号に応答して前記検出波の送信及び前記反射波の受信の動作が開始される、ことを特徴とする請求項8に記載の検出方法。

【請求項1】

検出波を対象物に対して送信する送信手段と、前記検出波が当該対象物から反射した反射波を受信して受信信号を生成する受信手段と、前記受信信号を処理する信号処理手段と、を備える検出装置であって、

前記検出波は、複数の送信パルスが第1の周期で繰り返される送信パルス列信号であり、

前記受信手段は、前記反射波を受信して複数のパルスを含む受信パルス列信号を生成し、当該受信パルス列信号を第2の周期で前記第2の周期より長い第3の周期の間にサンプリングして複数の受信パルス信号を形成し、

前記信号処理手段は、前記複数の受信パルス信号の各々の時間軸を前記複数の受信パルス信号の各々と前記複数の送信パルスの各々との位相差に応じて補正し、補正された当該複数の受信パルス信号を合成して1つの受信パルス信号を形成する、ことを特徴とする検出装置。

【請求項2】

前記検出装置内部又は外部で前記第3の周期のトリガー信号を生成し、

前記送信手段及び前記受信手段は、前記トリガー信号に応答して動作する、ことを特徴とする請求項1に記載の検出装置。

【請求項3】

前記複数の受信パルス信号の合成は、1つの時間軸上に当該複数の受信パルス信号のデータを時系列的に配置することで行われる、ことを特徴とする請求項1又は2に記載の検出装置。

【請求項4】

前記送信手段は前記複数の送信パルスの位相設定に関わる第1のPLL回路を含み、前記受信手段は前記サンプリングに関わる第2のPLL回路を含み、前記第1及び第2のPLL回路は基準発振器を共通にする、ことを特徴とする請求項1乃至3のいずれかに記載の検出装置。

【請求項5】

前記検出波が、電磁波、音波、及び光波のいずれかである、請求項1乃至4のいずれかに記載の検出装置。

【請求項6】

検出波を対象物に対して送信する送信装置であって、

前記検出波を前記対象物に対して送信する送信手段を含み、

前記検出波は、複数の送信パルスが第1の周期で繰り返される送信パルス列信号であり、

前記対象物から反射した反射波は受信装置に受信され、受信パルスが繰り返される受信パルス列信号が生成され、当該受信パルス列信号は第2の周期で前記第2の周期より長い第3の周期の間にサンプリングされ複数の受信パルス信号が生成され、前記複数の受信パルス信号の各々の時間軸は前記複数の受信パルス信号の各々と前記複数の送信パルスの各々との位相差に応じて補正され、補正された当該複数の受信パルス信号は合成されて1つの受信パルス信号が形成される、ことを特徴とする送信装置。

【請求項7】

送信された検出波が対象物から反射した反射波を受信する受信装置であって、

受信手段と、信号処理手段と、を含み、

前記検出波は、複数の送信パルスが第1の周期で繰り返される送信パルス列信号であり、

前記受信手段は、前記反射波を受信して複数のパルスを含む受信パルス列信号を生成し、当該受信パルス列信号を第2の周期で前記第2の周期より長い第3の周期の間にサンプリングして複数の受信パルス信号を形成し、

前記信号処理手段は、前記複数の受信パルス信号の各々の時間軸を前記複数の受信パルス信号の各々と前記複数の送信パルスの各々との位相差に応じて補正し、補正された当該複数の受信パルス信号を合成して1つの受信パルス信号を形成する、ことを特徴とする受信装置。

【請求項8】

検出波を対象物に対して送信し、当該対象物から反射した反射波を受信して前記反射波を検出する検出方法であって、

複数の送信パルスが第1の周期で繰り返される送信パルス列信号である前記検出波を前記対象物に送信する過程と、

前記反射波を受信して受信パルスが繰り返される受信パルス列信号を生成し、当該受信パルス列信号を第2の周期で前記第2の周期より長い第3の周期の間にサンプリングし、複数の受信パルス信号を生成する過程と、

前記複数の受信パルス信号の各々の時間軸を前記複数の受信パルス信号の各々と前記複数の送信パルスの各々との位相差に応じて補正し、補正された当該複数の受信パルス信号を合成して1つの受信パルス信号を形成する過程と、を含む検出方法。

【請求項9】

供給されるトリガー信号に応答して前記検出波の送信及び前記反射波の受信の動作が開始される、ことを特徴とする請求項8に記載の検出方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【公開番号】特開2013−3071(P2013−3071A)

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願番号】特願2011−136985(P2011−136985)

【出願日】平成23年6月21日(2011.6.21)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願日】平成23年6月21日(2011.6.21)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]