機能素子パッケージ体及びその製造方法

【課題】 小型化と薄型化、コスト低減と信頼性の向上を図る。

【解決手段】 各入出力電極32と各素子実装用ランド6との接続部位及び可動子封装空間部21を構成する絶縁樹脂層34の形成部位とを同一箇所に設ける。犠牲層35を残した状態で機能素子体3をパッケージ基板2に実装した後に、犠牲層除去孔11から可動子封装空間部21に犠牲層除去剤を充填して犠牲層35を除去し、犠牲層除去孔11を封止材層13によって封止する。

【解決手段】 各入出力電極32と各素子実装用ランド6との接続部位及び可動子封装空間部21を構成する絶縁樹脂層34の形成部位とを同一箇所に設ける。犠牲層35を残した状態で機能素子体3をパッケージ基板2に実装した後に、犠牲層除去孔11から可動子封装空間部21に犠牲層除去剤を充填して犠牲層35を除去し、犠牲層除去孔11を封止材層13によって封止する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、機能面に可動子や振動子(以下、本明細書では可動子と総称する。)を有する機能素子体、例えば微小電子機械部品(MEMS:Micro Electro Mechanical Systems)や圧電薄膜共振素子(FBAR:Film Bulk Acoustic Resonator)或いは表面弾性波フィルタ素子(SAW:Surface Acoustic Wave Device)、バルク弾性波フィルタ素子(BAW:Bulk Acoustic Wave Device)等の機能素子体を実装してなる機能素子パッケージ体及びその製造方法に関する。

【背景技術】

【0002】

パーソナルコンピュータ、携帯電話機、ビデオ機器、オーディオ機器等の各種モバイル電子機器においては、近年小型軽量化や多機能化、高機能化或いは高速処理化等が図られている。モバイル電子機器等においては、このために微細な配線パターンを有する配線層を多層に形成して高密度配線化を図ったマザーボード等の実装用基板を用い、この実装用基板に小型で多機能化等が図られた集積回路部品や電子部品或いは各種の半導体ディバイス部品等をフリップチップ実装法等の表面実装法によって実装した素子パッケージ体が搭載される。

【0003】

例えば半導体チップを有する半導体ディバイスパッケージ体は、樹脂モールドやセラミックパッケージから突出された端子片を介するチップ実装方法から、非パッケージ状態のいわゆるベアチップをパッケージ基板に直接実装するフリップチップ実装法の採用によりチップサイズ化を図っている。半導体ディバイスパッケージ体は、パッケージ基板に形成した多数個の素子実装用ランド上に予め半田バンプ等の導電バンプを設け、この実装用基板に対して位置決めして組み合わされて実装される。

【0004】

かかる半導体ディバイスパッケージ体等においては、パッケージ基板におけるチップ実装領域をチップサイズとほぼ同等とすることによって実装面積の狭域化や多ピン化の対応を図り、実装用基板に対して各種の電子部品やディバイス等の高密度実装化を可能とし、小型化や多機能化が図られるようにする。また、半導体ディバイスパッケージ体等においては、伝送ロスの発生が小さい配線長の短縮化によって、信号伝達の高速化や高周波化等も実現する。半導体ディバイスパッケージ体等においては、実装用基板に実装した状態で必要に応じてベアチップを絶縁樹脂により封止することによって、他の実装部品との絶縁や機械的保護が図られるようにする。

【0005】

ところで、電極形成面に可動子や多数個の入出力電極が設けられたMEMSやFBAR或いはSAW等の機能素子パッケージ体においては、上述した半導体ディバイスのように実装用基板に対して表面実装法により実装して絶縁樹脂で封止する構造を採用すると、絶縁樹脂によって可動子が固定されて動作不能となり機能することができないといった問題がある。また、機能素子パッケージ体においては、微細な可動子が露出した状態のままで取り扱われることにより、後工程において破損等が生じないように慎重な取り扱いが必要であり、また負荷される温度変化やエッチング液等の影響を受けて特性の変化が生じる虞がある。

【0006】

したがって、機能素子パッケージ体は、従来セラミック基板等のパッケージ基板に素子体をダイボンドした後に素子体の入出力電極とパッケージ基板の主面上に素子体実装領域を囲んで形成したランドとをワイヤボンディング法によって接続し、さらに素子体を被覆するキャップ部材をパッケージ基板上に接合することによってパッケージ化していた。機能素子パッケージ体は、パッケージ基板とキャップ部材とによって気密空間部を構成して素子体を封装するとともに、気密空間部を真空雰囲気或いは不活性ガスを充填した還元ガス雰囲気に保持して可動子に対して環境変化の影響が及ばないように構成される。

【0007】

例えば、特許文献1には、チップのアクティブ面を囲んで接着層を構成する絶縁樹脂枠と接続用バンプとを設け、アクティブ面を対向面としてチップを実装用基板に対してフェイスダウン実装(表面実装)するマイクロパッケージ構造が開示されている。かかるマイクロパッケージ構造においては、チップのアクティブ面と実装用基板の主面との間に絶縁樹脂枠によって囲まれた中空部が構成される。かかるマイクロパッケージ構造によれば、実装用基板に対してアクティブ面を有するチップを、他の電子部品やベアチップ等と同様にフェイスダウン実装することが可能である。したがって、かかるマイクロパッケージ構造によれば、モジュールの薄型化や実装工程の効率が向上されるようになる。

【0008】

特許文献2には、中空部(キャビティ)に実装した機能素子体とモジュール基板の表面層に形成した外部出力端子とをビアで接続するが、キャビティの気密性が保持されるようにした回路基板が開示されている。回路基板においては、ガラス−セラミック成分を含む絶縁層に回路パターンを多層に形成するとともに、めっき液によって溶解されないように金属成分からなる中間層を設けている。回路基板においては、表面配線層を形成するめっき工程により絶縁層のポーラス化が生じても中間層によってキャビティの気密状態が保持されるようにする。

【0009】

【特許文献1】特許第3514349号公報

【特許文献2】特開2003−282763号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

ところで、従来の機能素子パッケージ体においては、セラミック基板に素子体実装領域を囲んで多数個のランドを形成するとともにキャップ部材を接合して素子体を封装することから、素子サイズに対してセラミック基板が大型となるとともに全体の厚みも大きくなってしまう。したがって、この機能素子パッケージ体を実装する回路パッケージ体は、全体の小型化が困難となり、複数個の機能素子体を有するマルチチップモジュールの場合にその傾向が一層顕著となっていた。

【0011】

また、機能素子体は、一般に電極形成面の主面上に酸化膜やシリコン或いは有機膜等からなる犠牲層を介して3次元形状の可動子が形成され、後工程で犠牲層が除去される。機能素子体は、ウエーハ上で多数個が一括して製作された後にダイシング工程を経て1個ずつに切断されるが、犠牲層を除去してむき出し状態にある可動子に冷却水の水圧がかかって変形等を生じさせてしまうことがある。機能素子体は、パッケージ基板上に実装するまで犠牲層を残すことによって、微細な可動子を保護して破損を防止したり静電気の帯電による貼り付きを防止する等が図られるようになる。機能素子体は、この場合にパッケージ基板上に実装した後に犠牲層を除去する対応を図ることが必要となる。

【0012】

一方、上述した特許文献1に開示されるマイクロパッケージにおいては、薄型化では有効であるが、チップに接続バンプを形成する領域と枠状の絶縁樹脂層を形成する領域とを設けることからチップ自体が大型化してしまう。マイクロパッケージにおいては、実装用基板に対して、チップをその外形寸法とほぼ同等の領域に実装することを可能とするが、このチップ自体が大型化するためにモジュール全体の小型化にさほど貢献度し得ないといった問題があった。また、マイクロパッケージにおいては、チップが開放状態で実装されることで、水分や酸化の影響により信頼性が低下するといった問題もある。

【0013】

また、特許文献2に開示される回路基板においては、実装基板のキャビティ内に機能素子を気密状態に実装することで、信頼性の向上が図られるようになる。しかしながら、かかる回路基板においては、ガラス−セラミック成分を含む基板を用いることから、セラミック焼成時に機能素子体がダメージを受けるといった問題がある。また、回路基板においては、基板も高価であるとともに、ビアホールの気密性を保持するためにAu、Ag、Pt、Rh等の貴金属が用いられることでコストが高いといった問題がある。また、回路基板においては、キャビティを閉塞する蓋体が設けられことから、全体として厚みが大きくなり小型化が図れないといった問題もある。

【0014】

したがって、本発明は、簡易な構成と工程とによりパッケージ基板に対して犠牲層を残して可動子を保護した状態で機能素子体を実装するとともに可動子を気密空間部内に封装することで、小型化と薄型化を図り、またコスト低減と信頼性の向上を図る機能素子パッケージ体及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0015】

上述した目的を達成する本発明にかかる機能素子パッケージ体は、パッケージ基板と、機能素子体とを備える。機能素子パッケージ体は、パッケージ基板が、第1主面上に多数個の素子実装用ランドを形成してこれら素子実装用ランドで囲まれた領域を素子体実装領域として構成し、各素子実装用ランドにそれぞれ設けた導電バンプと、素子体実装領域内に位置して第2主面に貫通して形成された貫通孔と、この貫通孔を閉塞する封止材層とを有する。機能素子パッケージ体は、機能素子体が、多数個の入出力電極と可動子とを設けた電極形成面に、可動子を囲む枠状に形成されるとともに各入出力電極をそれぞれ露出させる多数個の開口部が設けられた所定の厚みを有する絶縁樹脂層を形成してなる。機能素子パッケージ体は、機能素子体が、可動子を形成する犠牲層を残した状態で電極形成面を実装面としてパッケージ基板の素子体実装領域に組み付けられ、導電バンプを介して相対する各入出力電極と各素子実装用ランドとがそれぞれ接続されることによって第1主面上に絶縁樹脂層で囲まれて構成された可動子封装空間部内に可動子を封装して実装される。機能素子パッケージ体は、貫通孔が、機能素子体をパッケージ基板に実装した状態で第2主面側から犠牲層を除去する犠牲層除去孔として作用し、犠牲層を除去した後に封止層によって閉塞される。

【0016】

機能素子パッケージ体においては、機能素子体が、犠牲層を残して可動子を保護した状態のままで電極形成面を実装面としてパッケージ基板の素子体実装領域上に組み合わされる。機能素子パッケージ体においては、絶縁樹脂層に形成した各開口部内に相対する各導電バンプをそれぞれ嵌合させるようにして、パッケージ基板に対して機能素子体が位置決めして組み合わされる。機能素子パッケージ体においては、各導電バンプに対して加熱圧着処理や超音波印加処理を施すことによって、各導電バンプを介して相対する各入出力電極と各素子実装用ランドとが機械的かつ電気的に接続される。機能素子パッケージ体においては、機能素子体の可動子が、犠牲層を残したままの状態でパッケージ基板の第1主面上において絶縁樹脂層内に囲まれて構成された可動子封装空間部内に封装される。

【0017】

機能素子パッケージ体においては、可動子封装空間部内にパッケージ基板の第2主面側から貫通孔を介して犠牲層除去剤を充填して犠牲層を溶解し、用済みの犠牲層除去剤を貫通孔から回収する。機能素子パッケージ体においては、可動子を可動子封装空間部内に封装した状態で犠牲層が除去されることで、取り扱いが簡便化されるとともに変形等の発生が抑制される。機能素子パッケージ体においては、各入出力電極と各素子実装用ランドとの接続部位及び可動子封装空間部を構成する絶縁樹脂層の形成部位とが同一箇所に構成されることで、簡易かつ確実な実装が行われるようになるとともに小型化が図られるようになる。機能素子パッケージ体においては、貫通孔内に封止材を充填することによって、可動子を封装した可動子封装空間部を密閉空間部として構成する。機能素子パッケージ体においては、可動子封装空間部内において可動子が安定した動作を行い、また経時変化の発生も抑制される。

【0018】

また、上述した目的を達成する本発明にかかる機能素子パッケージ体の製造方法は、第1主面上に多数個の素子実装用ランドを形成してこれら素子実装用ランドによって囲まれた領域を素子体実装領域として構成してなるパッケージ基板を製作するパッケージ基板製作工程と、電極形成面に可動子と多数個の入出力電極とを設けた機能素子体を製作する機能素子体製作工程と、パッケージ基板に対してその素子実装領域に電極形成面を実装面として機能素子体を実装する機能素子体実装工程とを有して機能素子パッケージ体を製造する。機能素子パッケージ体の製造方法は、パッケージ基板の製作工程が、素子体実装領域内に位置して第1主面と第2主面とに貫通する貫通孔を形成する貫通孔形成工程と、各素子実装用ランド上にそれぞれ導電バンプを設ける導電バンプ形成工程とを有する。機能素子パッケージ体の製造方法は、機能素子体の製作工程が、素子基板の第1主面を電極形成面として多数個の入出力電極と犠牲層を残した可動子とを形成する素子形成工程と、各入出力電極を跨り可動子を囲む所定の厚みを有する枠状の絶縁樹脂層を形成する絶縁樹脂層形成工程と、絶縁樹脂層に対して各入出力電極をそれぞれ露出させる多数個の開口部を形成する開口部形成工程とを有する。機能素子パッケージ体の製造方法は、パッケージ基板に対する機能素子体の実装工程が、電極形成面を実装面として、各開口部内にそれぞれ相対する各導電バンプを嵌合させて各導電バンプと各入出力電極とを接触させるように位置決めして組み合わせることによって絶縁樹脂層に囲まれて構成された可動子封装空間部内に可動子を臨ませる機能素子体組合せ実装工程と、各導電バンプを介して相対する各入出力電極と素子実装用ランドとを電気的かつ機械的に接続する入出力電極接続工程と、パッケージ基板の第2主面側から貫通孔を介して犠牲層除去剤を充填して犠牲層を除去する犠牲層除去工程と、貫通孔内に封止材を充填して貫通孔を閉塞する貫通孔封止工程とを有する。

【0019】

機能素子パッケージ体の製造方法においては、パッケージ基板に対して機能素子体が、犠牲層を残して可動子を保護した状態のままで電極形成面を実装面として組み合わされることから、取り扱いが簡便となるとともに外部負荷によって微細な可動子の破損等の発生が防止されて生産性や歩留りを向上してコスト低減を図って機能素子パッケージ体を製造する。機能素子パッケージ体の製造方法においては、パッケージ基板に対して機能素子体が、絶縁樹脂層に形成した各開口部内に相対する各導電バンプをそれぞれ嵌合させるように位置決めして組み合わせた状態で、各導電バンプに対して加熱圧着処理や超音波印加処理を施して各導電バンプを介して相対する各入出力電極と各素子実装用ランドとが機械的かつ電気的に接続されるようにする。機能素子パッケージ体の製造方法においては、各入出力電極と各素子実装用ランドとの接続部位及び可動子封装空間部を構成する絶縁樹脂層の形成部位とを同一箇所に設けることで、小型化を図った機能素子パッケージ体を製造する。機能素子パッケージ体の製造方法においては、可動子を気密空間部内に封装して外部環境等の影響を受けることなく安定した動作が行われるようにするとともに、気密空間部を構成するためのキャップ部材を不要とすることで高精度でかつ構造の簡易化を図った機能素子パッケージ体を製造する。

【発明の効果】

【0020】

本発明によれば、枠状の絶縁樹脂層によって各入出力電極と各素子実装用ランドとの接続部位を固定するとともに可動子を封装する気密状態の可動子封装空間部を構成することから、可動子の安定動作化による信頼性の向上と、構造の簡易化及び小型化を図ることが可能となる。本発明によれば、可動子を可動子封装空間部内に封装した状態で犠牲層を除去することから、工程の簡易化や歩留りの向上を図ることが可能となる。

【発明を実施するための最良の形態】

【0021】

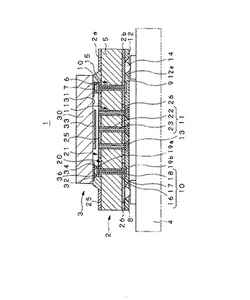

以下、本発明の実施の形態として示す機能素子パッケージ体1及びその製造方法について図面を参照して詳細に説明する。実施の形態として図面に示した機能素子パッケージ体1は、各種の電子機器、例えば携帯電話機やパーソナルコンピュータ等に搭載される高周波機能素子パッケージ体であり、図1に示すようにパッケージ基板2と、このパッケージ基板2の第1主面2a上に実装される機能素子体3とから構成され、パッケージ基板2の第2主面2bを実装面として、詳細を省略する実装用基板4に実装される。機能素子パッケージ体1は、パッケージ基板2が実装用基板4と接続されて機能素子体3と入出力信号を授受する入出力回路部等を構成する。

【0022】

機能素子パッケージ体1においては、詳細を後述するようにパッケージ基板2に機能素子体3を実装することにより、機能素子体3に設けた可動子33が気密状態に保持される可動子封装空間部21内に封装される。機能素子パッケージ体1においては、パッケージ基板2に機能素子体3が、3次元形状の可動子33を形成する犠牲層35を残したままの状態で実装した後に、犠牲層35が除去される。機能素子パッケージ体1においては、パッケージ基板2と機能素子体3との電気的接続部位と可動子封装空間部21を構成する絶縁樹脂層34の形成部位とが同一箇所に設けられる。

【0023】

パッケージ基板2は、例えば配線基板として一般的に用いられる銅貼りガラスエポキシ樹脂基板等の絶縁基板5を基材として詳細を後述する工程を経て製作される。なお、パッケージ基板2は、耐熱性や耐薬品性或いは加工性に優れた基板材、例えば液晶ポリマー、ガラスエポキシ、ポリイミド、ポリフェニレンエーテル、ビスマレイトトリアジン、ポリテトラフルオロエチレン或いは高周波対応を図るブタジエン樹脂等の有機絶縁基板を基材としてもよい。パッケージ基板2には、第1主面2aを構成する絶縁基板5の一方主面に多数個の素子実装用ランド6が形成されるとともに、これら素子実装用ランド6に導電バンプ7が設けられる。パッケージ基板2には、第2主面2bを構成する絶縁基板5の他方主面に、所定の配線パターン8や実装用ランド9が形成されている。

【0024】

パッケージ基板2には、絶縁基板5を貫通して第1主面2a側の素子実装用ランド6と相対する第2主面2b側の配線パターン8或いは実装用ランド9とをそれぞれ層間接続する多数個のビア10が形成されている。パッケージ基板2には、詳細を後述するように所定の箇所に位置して第1主面2aと第2主面2bとに貫通する貫通孔からなる複数個の犠牲層除去孔11が形成されている。パッケージ基板2には、第2主面2b側に全面に亘って配線パターン8を被覆するとともに開口部12aを介して実装用ランド9を露出させるソルダレジスト層12が形成されている。

【0025】

パッケージ基板2には、第2主面2b側において、各犠牲層除去孔11の開口部をそれぞれ閉塞する封止材層13が形成されている。パッケージ基板2には、ソルダレジスト層12に形成した各開口部12aに臨ませられて露出される各実装用ランド9に、それぞれ導電バンプ14が設けられる。パッケージ基板2には、第1主面2aに機能素子体3の接合状態を補強する補強樹脂層15が形成されている。なお、パッケージ基板2は、両面に配線パターンが形成された両面配線基板を示したが、多数層の配線層を有する多層配線基板であってもよいことは勿論である。

【0026】

パッケージ基板2は、第1主面2a上に各素子実装用ランド6を、互いに絶縁されて絶縁基板5の各辺に沿って枠状に配列して形成する。各素子実装用ランド6は、詳細には前工程で形成された各ビア10と一体化して形成される。ビア10は、絶縁基板5を貫通して形成されたスルーホール16と、このスルーホール16の内壁に全域に亘って形成されためっき層17と、導電性樹脂或いは非導電性樹脂を充填してスルーホール16内に形成された充填樹脂層18と、スルーホール16の上下開口部をそれぞれ閉塞して形成される蓋めっき層19a、19bからなる。各素子実装用ランド6は、スルーホール16の第1主面2a側の開口部に形成された蓋めっき層19aと一体化して形成される。なお、パッケージ基板2は、多層配線基板によって構成される場合に、各ビア10が内層の各配線層を適宜層間接続するように形成される。

【0027】

パッケージ基板2は、第1主面2aの各素子実装用ランド6によって囲まれた矩形の領域が、機能素子体3を実装する素子体実装領域20として構成される。パッケージ基板2は、後述するように素子体実装領域20上に機能素子体3を実装した状態において、この素子体実装領域20と機能素子体3の電極形成面31と後述する絶縁樹脂層34とによって機能素子体3の可動子33を封装する可動子封装空間部21を構成する。

【0028】

導電バンプ7は、各素子実装用ランド6に設けられた導電性を有する突起体であり、周知のようにめっき法、印刷法或いはボールボンディング法等によって形成される。導電バンプ7は、機能素子体3と接続する接続子として作用する。同様に、第2主面2b側の実装用ランド9に設けられた導電バンプ14も、導電性を有する突起体であり、機能素子パッケージ体1を実装用基板4に実装する際の接続子として作用する。導電バンプ14は、機能素子体3を接続するための導電バンプ7よりも大型に形成することが可能であることから、例えば半田ボール等の金属ボールを搭載してリフロー処理を施すことによって形成される。なお、導電バンプ14は、導電バンプ7と同様にめっき法、印刷法或いはボールボンディング法等によって形成してもよいことは勿論である。

【0029】

パッケージ基板2は、例えば絶縁基板5に貼り付けた銅箔に対してパターニング処理を施して、第2主面2bに配線パターン8と実装用ランド9とを形成する。パッケージ基板2は、配線パターン8や実装用ランド9が上述した各ビア10の蓋めっき層19bと適宜接続されて形成される。パッケージ基板2は、配線パターン8や実装用ランド9を被覆して第2主面2bの全面にソルダレジスト層12が形成され、このソルダレジスト層12に適宜のパターニング処理を施して導電バンプ14の外径寸法よりもやや大きな開口寸法となる開口部12aを形成する。

【0030】

パッケージ基板2は、各犠牲層除去孔11が、絶縁基板5を貫通して可動子封装空間部20に連通して形成され、後述するようにパッケージ基板2に機能素子体3を実装した状態で可動子33を保護するために残された犠牲層35を除去するために用いられる。各犠牲層除去孔11は、上述した各ビア10と同一工程で形成され、スルーホール22と、このスルーホール22の内壁に全域に亘って形成されためっき層23とから構成される。各犠牲層除去孔11には、スルーホール22の開口部を閉塞する蓋めっき層が形成されていない。

【0031】

各犠牲層除去孔11は、第2主面2b側から犠牲層除去剤を可動子封装空間部20内に充填して犠牲層35を除去した後に、可動子封装空間部20内に還元ガスを注入するために用いられる。各犠牲層除去孔11は、犠牲層35の除去工程を経た後に、封止材層13によって第2主面2b側の開口部を閉塞される。各犠牲層除去孔11は、スルーホール22内のめっき層23を特に必要としないが、これらが各ビア10と同一工程で形成されることで工程数が増えることは無く、可動子封装空間部20の気密性を向上させるために有効である。また、各犠牲層除去孔11は、機能素子体3から発生して可動子封装空間部20内に籠もる熱を効率的に放熱するサーマルビアホールとしても機能する。

【0032】

ところで、パッケージ基板2は、微小な機能素子体3を高精度に実装するために、第1主面2aや第2主面2bが比較的平坦化されて形成されることが好ましい。したがって、パッケージ基板2は、第1主面2aに各素子実装用ランド6や各ビア10の蓋めっき層19の厚みによって生じる段差を埋める第1平坦化樹脂層25が形成される。第1平坦化樹脂層25は、素子実装用ランド6や蓋めっき層19を埋設する厚みで第1主面2aの全面に亘って絶縁樹脂層を形成し、この絶縁樹脂層に対して素子実装用ランド6を露出させる機械研磨や化学研磨或いは機械−化学研磨を施して形成される。

【0033】

パッケージ基板2は、同様にして第2主面2bにも配線パターン8や各実装用ランド9或いは各ビア10の蓋めっき層19bの厚みによって生じる段差を埋める第2平坦化樹脂層26が形成される。第2平坦化樹脂層26も、配線パターン8や各実装用ランド9或いは各ビア10の蓋めっき層19bを埋設する厚みで第2主面2bの全面に亘って絶縁樹脂層を形成し、この絶縁層に対して各実装用ランド9を露出させる機械研磨や化学研磨或いは機械−化学研磨を施して形成される。

【0034】

機能素子体3は、SAW素子(表面弾性波素子)やBAW素子(バルク弾性波素子)或いはMEMS(微小電子機械部品)やFBAR素子(圧電薄膜共振素子)等のマイクロディバイスであり、シリコン基板やガラス基板を母材とする基板30と、この基板30の第1主面を電極形成面31として多数個の入出力電極32と、詳細を省略する可動子33を形成してなる。機能素子体3は、図示を省略するが基板30に可動子33を駆動する電極や、これら電極と入出力電極32とを接続する微細配線パターン等が形成されている。機能素子体3には、電極形成面31に詳細を後述する絶縁樹脂層34が形成され、電極形成面31を実装面として上述したパッケージ基板2の素子体実装領域20に実装される。

【0035】

機能素子体3は、基板30上に適宜の形状で犠牲層29を形成し、この犠牲層29を利用して3次元形状の可動子33を形成する。機能素子体3は、犠牲層29が酸化膜やシリコン或いは有機膜等によって形成され、この犠牲層29を残した状態で供給されて上述したパッケージ基板2に実装される。機能素子体3は、一般にはウエーハ上で多数個が形成され、それぞれの犠牲層29を除去した後にダイシング工程によって1個ずつに切断されて供給される。機能素子体3は、犠牲層29を残して可動子33を保護した状態で用いることから、微細な可動子33がダイシング工程に際しの水圧による変形或いは外部環境の影響による特性変化等を防止されるとともにハンドリング性の向上が図られる。

【0036】

機能素子体3は、入出力電極32が、電極形成面31上に可動子33を囲んで絶縁基板5の各辺に沿って枠状に配列して形成される。各入出力電極32は、パッケージ基板2に機能素子体3を実装した状態で、各素子実装用ランド6とそれぞれ相対するようにして形成されている。機能素子体3は、パッケージ基板2側から供給される入力信号によって可動子33が動作し、この可動子33の動作による出力信号をパッケージ基板2側へと出力する。

【0037】

機能素子体3には、絶縁樹脂層34が、電極形成面31に各入出力電極32上に跨って可動子33を囲む枠状に形成される。絶縁樹脂層34は、図1において上下方向に動作する可動子33の動作領域よりもやや大きな厚みと各入出力電極32の外形寸法よりもやや大きな幅とを有して形成される。絶縁樹脂層34は、詳細を後述するようにエポキシ樹脂やフェノール樹脂或いはベンゾシクロブテン樹脂(BCB)等の感光性絶縁樹脂層を電極形成面31上に全面に亘って形成し、この絶縁樹脂層にパターニング処理を施して形成する。

【0038】

絶縁樹脂層34には、上述したパターニング処理を施す際に、各入出力電極32に対応する位置にそれぞれ開口部36も形成される。各開口部36は、パッケージ基板2側に設けた上述した導電バンプ7の外形寸法よりもやや大きな開口寸法を以って形成され、それぞれの底部に相対する各入出力電極32の表面を露出させる。絶縁樹脂層34は、半硬化状態で電極形成面31上に形成されることによって導電バンプ7が相対する各開口部36の内壁に密着するようにし、パッケージ基板2に機能素子体3を実装した状態で硬化処理が行われる。

【0039】

機能素子体3は、上述したように犠牲層35を残すことによって可動子33を保護した状態で、電極形成面31を実装面としてパッケージ基板2の素子実装領域20上に実装される。機能素子体3は、絶縁樹脂層34の各開口部36に相対する導電バンプ7がそれぞれ嵌合して入出力電極32と接触するように位置決めされてパッケージ基板2に組み合わされる。機能素子体3は、電極形成面31の対向面側からパッケージ基板2に押し付けられた状態で加熱処理が施されることによって各導電バンプ7を介して入出力電極32がパッケージ基板2側の各素子実装用ランド6と電気的かつ機械的に接続されて機能素子パッケージ体1を完成する。

【0040】

機能素子パッケージ体1は、補強樹脂層15を外周面の全周に亘って形成することにより絶縁樹脂層34が補強される。補強樹脂層15は、例えば流動性とチクソ性(thixotropy)を有するフィラー入り液状エポキシ系樹脂材によって形成され、パッケージ基板2に対する機能素子体3の実装状態を補強するとともに、絶縁樹脂層34によって保持された各導電バンプ7を介する各素子実装用ランド6と入出力電極32との接合状態を補強する。補強樹脂層15は、絶縁樹脂層34によって構成される可動子封装空間部21の気密性を補強する。

【0041】

機能素子パッケージ体1においては、硬化処理が施された絶縁樹脂層34が、導電バンプ7を介した入出力電極32と各素子実装用ランド6との接合状態を保持するとともに機能素子体3の電極形成面31とパッケージ基板2の第1主面2aとの間において可動子封装空間部21を構成する。機能素子パッケージ体1においては、犠牲層35が除去された可動子33が、還元ガス雰囲気の可動子封装空間部21内において外部環境変化や静電気の帯電等から隔離されて安定した状態で動作するとともに経時変化の発生も抑制される。機能素子パッケージ体1においては、絶縁樹脂層34が、同一箇所において各入出力電極32と各素子実装用ランド6との接続部位を保持するとともに可動子封装空間部21を構成することで、小型化が図られる。

【0042】

上述した機能素子パッケージ体1は、パッケージ基板製作工程と、機能素子体製作工程と、機能素子体実装工程とを経て製造される。パッケージ基板製作工程には、図2に示す表裏主面(第1主面2a及び第2主面2b)にそれぞれ銅箔層40a、40bが設けられた絶縁基板5が供給される。絶縁基板5は、セラミック基板やガラス基板と比較して廉価であり、スルーホールの加工性にも優れている。なお、絶縁基板5については、上述したようにかかる銅貼積層基板に限定されず、回路基板用に用いられる各種の基板材を用いてもよいことは勿論である。

【0043】

パッケージ基板製作工程は、絶縁基板5に対して、図3に示すようにビア10を構成するスルーホール16や犠牲層除去孔11を構成するスルーホール22を形成する貫通孔形成工程が施される。貫通孔形成工程は、レーザ照射やプラズマ照射或いはこれらを同時に照射するいわゆるドライエッチング加工やドリル加工によって絶縁基板5を貫通する多数個のスルーホール16、22を所定位置にそれぞれ穿孔する。

【0044】

パッケージ基板製作工程は、図4に示すように、各スルーホール16に対してめっき処理を施してその内壁に全域に亘ってめっき層17形成して、表裏主面2a、2bの銅箔層40a、40bを導通させてビア10を構成する。なお、犠牲層除去孔11を構成するスルーホール22にも、上述したように可動子封装空間部21の気密性を高めるとともに封止材層13を形成するためにめっき層23が同時に形成される。

【0045】

パッケージ基板製作工程は、同図に示すように、各ビア10内に導電性或いは非導電性の樹脂を充填して充填樹脂層18を形成する。充填樹脂層18は、例えばエポキシ系樹脂にグリコール系溶剤や芳香族系溶剤を混合してなる樹脂材が用いられ、この樹脂材を各ビア10内に充填した後に紫外線の照射や加熱処理を施して硬化させることによって形成される。パッケージ基板製作工程は、スルーホール22が犠牲層除去孔11を構成して犠牲層除去孔剤を可動子封装空間部21内に充填することから、内部に充填樹脂層は形成されない。

【0046】

パッケージ基板製作工程は、図5に示すように、ビア10の表裏開口部に蓋めっき処理を施してそれぞれ蓋めっき層19a、19bを形成する。蓋めっき処理は、蓋めっき層19a、19bが、それぞれ素子実装用ランド6や配線パターン8の一部を構成することから、銅めっき或いはアルミめっきによって行われる。パッケージ基板製作工程は、上述した工程を経て、図6に示した第1中間基板50を得る。第1中間基板50は、第1主面2aを構成する主面上に、各ビア10の開口部を閉塞して銅箔層40a上に多数個の蓋めっき層19aが形成されるとともに、各蓋めっき層19aに囲まれた矩形領域内に犠牲層除去孔11を構成する多数個のスルーホール22が開口される。

【0047】

パッケージ基板製作工程は、絶縁基板5の銅箔層40a、40bに対してパターニング工程を施し、図7に示すように第1主面2aに素子実装用ランド6を形成するとともに第2主面2bに配線パターン8や実装用ランド9を形成する。パターニング工程は、いわゆるフォトリソグラフ技術により、銅箔層40a、40b上に全面に亘ってエッチングレジスト層を形成する工程と、エッチングレジスト層に所定の開口部を形成する工程と、開口部の銅箔を除去して素子実装用ランド6や配線パターン8及び実装用ランド9を形成するエッチング工程と、エッチングレジスト層を除去する工程等からなる。

【0048】

パターニング工程は、エッチングレジスト層形成工程において、例えば液状の感光性レジストをスピンコート法或いはロールコート法等によって銅箔層40a、40b上に塗布してエッチングレジスト層を形成する。また、エッチングレジスト層形成工程は、例えばフィルム状の感光性レジスト材を用いてラミネート法等によって銅箔層40a、40b上に被覆してエッチングレジスト層を形成する。なお、エッチングレジスト層については、非感光性レジストを用いて形成するようにしてもよいことは勿論である。

【0049】

パターニング工程は、開口部形成工程が、素子実装用ランド6や配線パターン8及び実装用ランド9に対応する部位を開口したマスクをエッチングレジスト層上に接合する工程と、各開口部を介してエッチングレジスト層に露光処理と現像処理とを施して当該部位のエッチングレジスト層を除去する工程とからなる。エッチング工程は、マスクを取り外した状態で硫酸と硝酸と酢酸との混合酸や塩化第二鉄等のエッチャント(エッチング材)を用いて、エッチングレジスト層の各開口部に露出した銅箔層を除去する。

【0050】

パターニング工程は、エッチングレジスト層除去工程において、エッチングレジストの種類に応じて適宜選択された除去材、例えばアセトン等の有機溶剤やレジスト剥離液、水酸化ナトリウム溶液等を用いて第1主面2aや第2主面2bに残ったエッチングレジスト層を除去することにより、第1主面2aと第2主面2b上に必要な銅箔層のみを残して素子実装用ランド6や配線パターン8及び実装用ランド9を形成する。なお、パターニング工程は、非感光性レジストによってエッチングレジスト層を形成した場合には、反応性イオンエッチング法やレーザ照射等によって開口部が形成される。

【0051】

パターニング工程においては、上述した各工程を経て、第1主面2a上に枠状に配列された各素子実装用ランド6を形成するとともに第2主面2b上にも枠状に配列された各実装用ランド9を形成する。パターニング工程においては、図7に示すように各素子実装用ランド6によって囲まれた領域、すなわち素子体実装領域20内の銅箔層40aをそのまま残すことによって第1主面2aに第1遮蔽金属層41を形成する。パターニング工程においては、同様にして各実装用ランド9によって囲まれた領域内の銅箔層40bをそのまま残すことによって第2主面2b上に第2遮蔽金属層42を形成する。なお、第2遮蔽金属層42については、第2主面2bの当該部位に配線パターン8が形成される場合には、特に設ける必要は無い。

【0052】

第1遮蔽金属層41及び第2遮蔽金属層42は、可動子封装空間部21の底面部を構成する部位であるが、金属層で覆うことによって絶縁基板5の気密性を向上させる。また、第1遮蔽金属層41及び第2遮蔽金属層42は、可動子封装空間部21を磁気的シールド空間部として構成して可動子33が安定して動作が行われるようにする。

【0053】

パッケージ基板製作工程は、第1主面2a上に微細で精密な機能素子体3を実装することから、パッケージ基板2が第1主面2aと第2主面2bとを高面精度に形成されていることが好ましい。パッケージ基板2は、上述したように第1主面2a側に多数個の素子実装用ランド6を形成するとともに第2主面2b側に配線パターン8や実装用ランド9を形成することで、それらの厚みによる段差が生じている。パッケージ基板製作工程は、第1主面2aと第2主面2bとに第1平坦化樹脂層25と第2平坦化樹脂層26の形成工程が施される。なお、以下に第1平坦化樹脂層25の形成工程について代表して説明する。

【0054】

平坦化樹脂層形成工程は、熱膨張による変形等を防止するために絶縁樹脂層34と同一樹脂材を用いることが好ましく、例えばエポキシ樹脂、フェノール樹脂、BCB樹脂等の絶縁樹脂材が用いられる。平坦化樹脂層形成工程は、第1主面2a上に絶縁樹脂材を各素子実装用ランド6を被覆して全面に亘って塗布し、絶縁樹脂材を硬化させた状態で機械研磨、化学研磨或いは機械−化学研磨処理によって素子実装用ランド6の表面を露出させるまで研磨する。なお、研磨処理については、第1主面2a側の第1平坦化樹脂層25と第2主面2b側の第2平坦化樹脂層26とを同時に研磨することが可能である。平坦化樹脂層形成工程については、機能素子体3が直接実装される第1主面2a側にのみ施すようにしてもよい。

【0055】

パッケージ基板製作工程は、図8に示すように第2主面2b側に、配線パターン8を被覆してこれを保護するとともに絶縁を保持するとともに実装用ランド9を露出させるソルダレジスト層12を形成する。ソルダレジスト層形成工程は、第2主面2b上に例えば感光性ソルダレジストをスピンコート法や印刷法等によって所定の厚みで塗布してソルダレジスト層を形成する。ソルダレジスト層形成工程は、ソルダレジスト層に対して実装用ランド9に対応する部位に開口部を設けたマスクを接合してソルダレジスト層に露光処理と現像処理とを施す。ソルダレジスト層形成工程は、マスクを取り外してマスクの開口部に対応するソルダレジスト層を除去して底部に各実装用ランド9をそれぞれ露出させた多数個の開口部12aを形成する。ソルダレジスト層形成工程においては、ソルダレジストを硬化させることによって、第2主面2bにソルダレジスト層12を形成する。

【0056】

ソルダレジスト層形成工程においては、同図に示すように各犠牲層除去孔11の第2主面2b側の開口部位についても、同時に開口部43を形成する。なお、ソルダレジスト層形成工程は、非感光性のソルダレジスト材を用いる場合には、第2主面2b上にソルダレジスト材を塗布した後に硬化させてソルダレジスト層12を形成し、このソルダレジスト層12に反応性イオンエッチングやレーザ加工等を施して各実装用ランド9を露出させる開口部12aや各犠牲層除去孔11の開口部位を露出させる開口部41を形成する。

【0057】

パッケージ基板製作工程は、図9に示すように平坦化された第1主面2aに露出された各素子実装用ランド6上にそれぞれ導電バンプ7を形成する。導電バンプ形成工程は、具体的には各素子実装用ランド6上に一体化された蓋めっき層19aに、例えばめっき法、印刷法或いはボールボンディング法等によって所定の外径寸法を有する半球形突起物からなる導電バンプ7を形成する。

【0058】

パッケージ基板製作工程は、上述した各工程を経て図10に示したパッケージ基板2を得る。パッケージ基板2は、上述したように第2主面2a上に、全面に亘って形成された第1平坦化樹脂層25に、略同一面を構成してそれぞれ蓋めっき層19aを一体化してなる多数個の素子実装用ランド6が枠状に配列されて形成される。パッケージ基板2は、各素子実装用ランド6に囲まれた領域内に第1遮蔽金属層41が形成されるとともに、多数個の犠牲層除去孔11が開口される。

【0059】

パッケージ基板製作工程においては、第2主面2b側において、ソルダレジスト層12に形成された開口部12aを介して実装用ランド8がそれぞれ露出されており、これら実装用ランド8に導電バンプ14を設ける導電バンプ形成工程も施される。導電バンプ形成工程は、第2主面2bがパッケージ基板2上に機能素子体3を精密に実装する際の受け面を構成するために平坦性が要求されることから、補強樹脂層15の形成工程と同様に機能素子体3を実装した後工程で行われる。

【0060】

機能素子体製作工程は、大判のウエーハ上で多数個の機能素子体3を一括して製作し、ウエーハを切断して1個ずつに切り離されるが、説明の便宜上、基板30に個別に形成する工程により説明する。機能素子体製作工程においては、シリコン基板やガラス基板からなる基板30が工程に供給され、この基板30の第1主面を電極形成面31として図11に示すように多数個の入出力電極32や図示しない配線パターン或いは可動子33とが形成される。

【0061】

機能素子体製作工程は、詳細を省略するが基板30上にスパッタ法等によって金属薄膜層を形成し、この金属薄膜層に対して所定のパターニング処理を施して各入出力電極32や微細な配線パターンを形成する。機能素子体製作工程は、上述したパッケージ基板2の各素子実装用ランド6に対応して枠状に配列して形成された各入出力電極32に囲まれた領域内に可動子33を形成する。機能素子体製作工程は、3次元形状の可動子33を形成するために基板30上に、例えば酸化膜やシリコン或いは有機膜等によって所定の形状を有する犠牲層35を形成し、後述するパッケージ基板2の実装工程を経て犠牲層35を除去する。

【0062】

機能素子体製作工程は、犠牲層35を残した状態のままで、基板30の主面上に絶縁樹脂基層44を形成する工程と、絶縁樹脂基層44に所定のパターニング処理を施す工程とを有する。絶縁樹脂基層形成工程は、感光性を有する絶縁樹脂、例えばエポキシ樹脂、フェノール樹或いはBCBをスピンコート法等によって各入出力電極32や可動子33を形成した電極形成面31上に所定の厚みで塗布することによって、図12に示すように絶縁樹脂基層44を形成する。絶縁樹脂基層44は、パターニング処理を施こされて絶縁樹脂層34を形成するため、上述したように可動子33の動作領域を確保するに足る均一な厚みを有して形成される。

【0063】

パターニング工程は、絶縁樹脂基層44にフォトグラフ処理を施して上述した形状の絶縁樹脂層34を形成する工程であり、絶縁樹脂層34に対応する部位に開口部を設けたマスクを接合して絶縁樹脂基層44に露光処理と現像処理とを施す。パターニング工程は、マスクを取り外してマスクの開口部に対応する絶縁樹脂を除去して、各入出力電極32上に跨りかつ可動子33を囲む枠状の絶縁樹脂層34を形成する。パターニング工程は、絶縁樹脂基層44から、半硬化状態であり、各入出力電極32を被覆するに足る幅寸法を有する絶縁樹脂層34を形成する。

【0064】

パターニング工程は、図13に示すように絶縁樹脂層34を形成するとともに各入出力電極32に対応する位置にそれぞれ開口部36も形成する。パターニング工程は、絶縁樹脂層34内に、パッケージ基板2側に設けた導電バンプ7の外形寸法よりもやや大きな開口寸法を有してそれぞれの底部に相対する各入出力電極32の表面を露出させる開口部36を形成する。

【0065】

機能素子パッケージ体1の製造工程は、上述したパッケージ基板製作工程によって製作されたパッケージ基板2の素子体実装領域20上に上述した機能素子体製作工程によって製作された機能素子体3を実装する。機能素子体実装工程は、機能素子体3を電極形成面31を実装面としてパッケージ基板2に対して位置決めして組み合わせる機能素子体組合せ工程と、各導電バンプ7を介して相対する各入出力電極32と各素子実装用ランド6とを電気的かつ機械的に接合する入出力電極接続工程と、絶縁樹脂層34を硬化させる絶縁樹脂層硬化工程と、絶縁樹脂層34を補強する補強樹脂層15を形成する補強樹脂層形成工程と、犠牲層35を除去する犠牲層除去工程と、犠牲層除去孔11を封止する犠牲層除去孔封止工程とを有する。

【0066】

機能素子体組合せ工程は、図14に示すように、機能素子体3の絶縁樹脂層34に形成した各開口部36内にそれぞれ相対する各導電バンプ7を嵌合させ、各導電バンプ7と各開口部36の底部に露出された各入出力電極32とを接触させて機能素子体3をパッケージ基板2の素子体実装領域20上に組み合わせる。機能素子体組合せ工程においては、絶縁樹脂層34が半硬化状態で形成されることにより、導電バンプ7が開口部36を押し広げて入出力電極32と確実に接触されるようにする。

【0067】

入出力電極接続工程は、加熱加圧装置を用い、機能素子体3を電極形成面31の対向面からパッケージ基板2に押し付けた状態で、入出力電極32の対応部位を加熱して導電バンプ7を接合させる。入出力電極接続工程は、機能素子体3の特性が損なわれないように比較的低温領域で行うことが好ましい。入出力電極接続工程は、加熱加圧装置ばかりでなく超音波ホーンを用いて各入出力電極32と各導電バンプ7の接触部位に超音波を印加することで、より低温領域でかつ処理時間を短縮化して接合処理を行うことを可能とする。なお、入出力電極接続工程は、超音波ホーンのみを用いて各入出力電極32と各導電バンプ7の接合処理を行うようにしてもよい。

【0068】

絶縁樹脂層硬化工程は、半硬化状態の絶縁樹脂層34に対して加熱処理を施すことにより硬化させることによって、図14に示すようにパッケージ基板2側の素子体実装領域20と機能素子体3側の電極形成面31との間に外周部を絶縁樹脂層34によって閉塞して可動子33を封装する可動子封装空間部21を形成する。

【0069】

補強樹脂層形成工程は、図15に示すように硬化処理を施された絶縁樹脂層34の外周面を全週に亘って被覆する補強樹脂層15を形成する。補強樹脂層形成工程は、上述したように流動性とチクソ性を有するフィラー入り液状エポキシ系樹脂材をディスペンサ等によってパッケージ基板2の第1主面2aと機能素子体3の基板30との間に充填し、加熱処理や紫外線照射処理を行って硬化させることにより、パッケージ基板2に対する機能素子体3の実装状態を補強し、絶縁樹脂層34によって保持された各導電バンプ7を介する各素子実装用ランド6と入出力電極32との接合状態を補強し、絶縁樹脂層34によって構成される可動子封装空間部21の気密性を補強する補強樹脂層15を形成する。

【0070】

機能素子パッケージ体1の製造工程においては、上述したように犠牲層35を残して可動子33を保護した状態で機能素子体3を実装することから、犠牲層除去工程によって機能素子体3から犠牲層35の除去処理が施される。犠牲層除去工程は、パッケージ基板2の第2主面2bに開口された各犠牲層除去孔11から、可動子封装空間部21内に犠牲層除去剤を充填する。犠牲層除去工程は、犠牲層除去剤として犠牲層35の材料に適合したフッ酸系溶剤、アルカリ系溶剤、有機溶剤或いはフッ酸系ガス、フッ素を含有するガス、酸素を含むガスが選択して用いられる。犠牲層除去工程は、各犠牲層除去孔11から可動子封装空間部21内に充填した犠牲層除去剤によって犠牲層35を溶解するとともに、各犠牲層除去孔11から排出する。

【0071】

機能素子パッケージ体1の製造工程においては、機能素子体3を最終工程に近い犠牲層除去工程まで犠牲層35を残した状態のままで取り扱うことから、微細な可動子33が損傷することが防止されるようになるとともに加熱処理やエッチング処理による影響も回避されるようになる。機能素子体3は、可動子33が可動子封装空間部21内において犠牲層35を除去されることで、電極形成面31上で動作が可能な状態となる。

【0072】

犠牲層除去孔封止工程は、犠牲層35を除去した各犠牲層除去孔11内に例えば半田や金属ペースト或いは絶縁樹脂等の封止材を充填することによって、図16に示すように封止材層13を形成する。犠牲層除去孔封止工程は、図示しないチャンバー内を真空或いはアルゴン等の還元ガス雰囲気に保持した状態で行うことによって可動子封装空間部21内を真空雰囲気や還元ガス雰囲気とする。可動子33は、還元ガス雰囲気の可動子封装空間部21内に封装されることによって、外部環境変化や静電気の帯電等から隔離されて安定した状態で動作するとともに錆の発生も防止される。

【0073】

機能素子パッケージ体1の製造工程においては、上述したようにパッケージ基板2の第2主面2b側に形成されたソルダレジスト層12の開口部12aに導電バンプ14を設ける導電バンプ形成工程が施される。導電バンプ形成工程は、犠牲層除去孔封止工程の前工程又は後工程で実施され、例えば各開口部12a内に半田等の金属ボールをそれぞれ装填した後にリフロー処理を施すことによって各開口部12aの底部に露出された実装用ランド9に接合された導電バンプ14を形成する。なお、導電バンプ形成工程は、導電バンプ14を例えば導電ペーストや半田ペーストを用いて印刷法によって形成したり、めっき法やボールボンディング法によって形成するようにしてもよい。

【0074】

機能素子パッケージ体1の製造工程においては、上述した各工程を経て、可動子33が製造工程中において破損や温度変化或いはエッチング液やめっき液の影響、静電気による貼り付き等が防止され、歩留りの向上を図って図1に示した機能素子パッケージ体1を製造する。機能素子パッケージ体1の製造工程においては、キャップ部材等を用いることなくパッケージ基板2と機能素子体3とによって可動子33を封装する気密性の高い可動子封装空間部21を構成し、可動部子33の酸化や劣化等を抑制して長寿命化が図られた機能素子パッケージ体1を製造する。機能素子パッケージ体1の製造工程においては、各入出力電極32と各素子実装用ランド6との接続部位及び可動子封装空間部21を構成する絶縁樹脂層34の形成部位とを同一箇所に設けることで、小型化を図った機能素子パッケージ体1を製造する。

【図面の簡単な説明】

【0075】

【図1】実施の形態として示す機能素子パッケージ体の縦断面図である。

【図2】パッケージ基板製作工程に用いられる両面基板の断面図である。

【図3】スルーホールを形成した両面基板の断面図である。

【図4】ビア形成を行った両面基板の断面図である。

【図5】各ビアに蓋めっき層を形成した両面基板の断面図である。

【図6】同両面基板の平面図である。

【図7】平坦化処理を施した両面基板の断面図である。

【図8】第2主面側にソルダレジスト層を形成した両面基板の断面図である。

【図9】導電バンプを形成した両面基板の断面図である。

【図10】パッケージ基板の平面図である。

【図11】機能素子体の断面図である。

【図12】絶縁樹脂基層を形成した機能素子体の断面図である。

【図13】開口部を有する絶縁樹脂層を形成した機能素子体の断面図である。

【図14】パッケージ基板に対する機能素子体の実装工程図であり、パッケージ基板に機能素子体を組み合せた中間体の断面図である。

【図15】同補強樹脂層を形成した中間体の断面図である。

【図16】同封止材層を形成した中間体の断面図である。

【符号の説明】

【0076】

1 機能素子パッケージ体、2 パッケージ基板、3 機能素子体、4 実装用基板、5 絶縁基板、6 素子実装用ランド、7 導電バンプ、8 配線パターン、9 実装用ランド、10 ビア、11 犠牲層除去孔、12 ソルダレジスト層、13 封止材層、14 導電バンプ、15 補強樹脂層、19 蓋めっき層、20 素子体実装領域、21 可動子封装空間部、25 第1平坦化樹脂層、26 第2平坦化樹脂層、30 基板、31 電極形成面、32 入出力電極、33 可動子、35 犠牲層、36 開口部

【技術分野】

【0001】

本発明は、機能面に可動子や振動子(以下、本明細書では可動子と総称する。)を有する機能素子体、例えば微小電子機械部品(MEMS:Micro Electro Mechanical Systems)や圧電薄膜共振素子(FBAR:Film Bulk Acoustic Resonator)或いは表面弾性波フィルタ素子(SAW:Surface Acoustic Wave Device)、バルク弾性波フィルタ素子(BAW:Bulk Acoustic Wave Device)等の機能素子体を実装してなる機能素子パッケージ体及びその製造方法に関する。

【背景技術】

【0002】

パーソナルコンピュータ、携帯電話機、ビデオ機器、オーディオ機器等の各種モバイル電子機器においては、近年小型軽量化や多機能化、高機能化或いは高速処理化等が図られている。モバイル電子機器等においては、このために微細な配線パターンを有する配線層を多層に形成して高密度配線化を図ったマザーボード等の実装用基板を用い、この実装用基板に小型で多機能化等が図られた集積回路部品や電子部品或いは各種の半導体ディバイス部品等をフリップチップ実装法等の表面実装法によって実装した素子パッケージ体が搭載される。

【0003】

例えば半導体チップを有する半導体ディバイスパッケージ体は、樹脂モールドやセラミックパッケージから突出された端子片を介するチップ実装方法から、非パッケージ状態のいわゆるベアチップをパッケージ基板に直接実装するフリップチップ実装法の採用によりチップサイズ化を図っている。半導体ディバイスパッケージ体は、パッケージ基板に形成した多数個の素子実装用ランド上に予め半田バンプ等の導電バンプを設け、この実装用基板に対して位置決めして組み合わされて実装される。

【0004】

かかる半導体ディバイスパッケージ体等においては、パッケージ基板におけるチップ実装領域をチップサイズとほぼ同等とすることによって実装面積の狭域化や多ピン化の対応を図り、実装用基板に対して各種の電子部品やディバイス等の高密度実装化を可能とし、小型化や多機能化が図られるようにする。また、半導体ディバイスパッケージ体等においては、伝送ロスの発生が小さい配線長の短縮化によって、信号伝達の高速化や高周波化等も実現する。半導体ディバイスパッケージ体等においては、実装用基板に実装した状態で必要に応じてベアチップを絶縁樹脂により封止することによって、他の実装部品との絶縁や機械的保護が図られるようにする。

【0005】

ところで、電極形成面に可動子や多数個の入出力電極が設けられたMEMSやFBAR或いはSAW等の機能素子パッケージ体においては、上述した半導体ディバイスのように実装用基板に対して表面実装法により実装して絶縁樹脂で封止する構造を採用すると、絶縁樹脂によって可動子が固定されて動作不能となり機能することができないといった問題がある。また、機能素子パッケージ体においては、微細な可動子が露出した状態のままで取り扱われることにより、後工程において破損等が生じないように慎重な取り扱いが必要であり、また負荷される温度変化やエッチング液等の影響を受けて特性の変化が生じる虞がある。

【0006】

したがって、機能素子パッケージ体は、従来セラミック基板等のパッケージ基板に素子体をダイボンドした後に素子体の入出力電極とパッケージ基板の主面上に素子体実装領域を囲んで形成したランドとをワイヤボンディング法によって接続し、さらに素子体を被覆するキャップ部材をパッケージ基板上に接合することによってパッケージ化していた。機能素子パッケージ体は、パッケージ基板とキャップ部材とによって気密空間部を構成して素子体を封装するとともに、気密空間部を真空雰囲気或いは不活性ガスを充填した還元ガス雰囲気に保持して可動子に対して環境変化の影響が及ばないように構成される。

【0007】

例えば、特許文献1には、チップのアクティブ面を囲んで接着層を構成する絶縁樹脂枠と接続用バンプとを設け、アクティブ面を対向面としてチップを実装用基板に対してフェイスダウン実装(表面実装)するマイクロパッケージ構造が開示されている。かかるマイクロパッケージ構造においては、チップのアクティブ面と実装用基板の主面との間に絶縁樹脂枠によって囲まれた中空部が構成される。かかるマイクロパッケージ構造によれば、実装用基板に対してアクティブ面を有するチップを、他の電子部品やベアチップ等と同様にフェイスダウン実装することが可能である。したがって、かかるマイクロパッケージ構造によれば、モジュールの薄型化や実装工程の効率が向上されるようになる。

【0008】

特許文献2には、中空部(キャビティ)に実装した機能素子体とモジュール基板の表面層に形成した外部出力端子とをビアで接続するが、キャビティの気密性が保持されるようにした回路基板が開示されている。回路基板においては、ガラス−セラミック成分を含む絶縁層に回路パターンを多層に形成するとともに、めっき液によって溶解されないように金属成分からなる中間層を設けている。回路基板においては、表面配線層を形成するめっき工程により絶縁層のポーラス化が生じても中間層によってキャビティの気密状態が保持されるようにする。

【0009】

【特許文献1】特許第3514349号公報

【特許文献2】特開2003−282763号公報

【発明の開示】

【発明が解決しようとする課題】

【0010】

ところで、従来の機能素子パッケージ体においては、セラミック基板に素子体実装領域を囲んで多数個のランドを形成するとともにキャップ部材を接合して素子体を封装することから、素子サイズに対してセラミック基板が大型となるとともに全体の厚みも大きくなってしまう。したがって、この機能素子パッケージ体を実装する回路パッケージ体は、全体の小型化が困難となり、複数個の機能素子体を有するマルチチップモジュールの場合にその傾向が一層顕著となっていた。

【0011】

また、機能素子体は、一般に電極形成面の主面上に酸化膜やシリコン或いは有機膜等からなる犠牲層を介して3次元形状の可動子が形成され、後工程で犠牲層が除去される。機能素子体は、ウエーハ上で多数個が一括して製作された後にダイシング工程を経て1個ずつに切断されるが、犠牲層を除去してむき出し状態にある可動子に冷却水の水圧がかかって変形等を生じさせてしまうことがある。機能素子体は、パッケージ基板上に実装するまで犠牲層を残すことによって、微細な可動子を保護して破損を防止したり静電気の帯電による貼り付きを防止する等が図られるようになる。機能素子体は、この場合にパッケージ基板上に実装した後に犠牲層を除去する対応を図ることが必要となる。

【0012】

一方、上述した特許文献1に開示されるマイクロパッケージにおいては、薄型化では有効であるが、チップに接続バンプを形成する領域と枠状の絶縁樹脂層を形成する領域とを設けることからチップ自体が大型化してしまう。マイクロパッケージにおいては、実装用基板に対して、チップをその外形寸法とほぼ同等の領域に実装することを可能とするが、このチップ自体が大型化するためにモジュール全体の小型化にさほど貢献度し得ないといった問題があった。また、マイクロパッケージにおいては、チップが開放状態で実装されることで、水分や酸化の影響により信頼性が低下するといった問題もある。

【0013】

また、特許文献2に開示される回路基板においては、実装基板のキャビティ内に機能素子を気密状態に実装することで、信頼性の向上が図られるようになる。しかしながら、かかる回路基板においては、ガラス−セラミック成分を含む基板を用いることから、セラミック焼成時に機能素子体がダメージを受けるといった問題がある。また、回路基板においては、基板も高価であるとともに、ビアホールの気密性を保持するためにAu、Ag、Pt、Rh等の貴金属が用いられることでコストが高いといった問題がある。また、回路基板においては、キャビティを閉塞する蓋体が設けられことから、全体として厚みが大きくなり小型化が図れないといった問題もある。

【0014】

したがって、本発明は、簡易な構成と工程とによりパッケージ基板に対して犠牲層を残して可動子を保護した状態で機能素子体を実装するとともに可動子を気密空間部内に封装することで、小型化と薄型化を図り、またコスト低減と信頼性の向上を図る機能素子パッケージ体及びその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0015】

上述した目的を達成する本発明にかかる機能素子パッケージ体は、パッケージ基板と、機能素子体とを備える。機能素子パッケージ体は、パッケージ基板が、第1主面上に多数個の素子実装用ランドを形成してこれら素子実装用ランドで囲まれた領域を素子体実装領域として構成し、各素子実装用ランドにそれぞれ設けた導電バンプと、素子体実装領域内に位置して第2主面に貫通して形成された貫通孔と、この貫通孔を閉塞する封止材層とを有する。機能素子パッケージ体は、機能素子体が、多数個の入出力電極と可動子とを設けた電極形成面に、可動子を囲む枠状に形成されるとともに各入出力電極をそれぞれ露出させる多数個の開口部が設けられた所定の厚みを有する絶縁樹脂層を形成してなる。機能素子パッケージ体は、機能素子体が、可動子を形成する犠牲層を残した状態で電極形成面を実装面としてパッケージ基板の素子体実装領域に組み付けられ、導電バンプを介して相対する各入出力電極と各素子実装用ランドとがそれぞれ接続されることによって第1主面上に絶縁樹脂層で囲まれて構成された可動子封装空間部内に可動子を封装して実装される。機能素子パッケージ体は、貫通孔が、機能素子体をパッケージ基板に実装した状態で第2主面側から犠牲層を除去する犠牲層除去孔として作用し、犠牲層を除去した後に封止層によって閉塞される。

【0016】

機能素子パッケージ体においては、機能素子体が、犠牲層を残して可動子を保護した状態のままで電極形成面を実装面としてパッケージ基板の素子体実装領域上に組み合わされる。機能素子パッケージ体においては、絶縁樹脂層に形成した各開口部内に相対する各導電バンプをそれぞれ嵌合させるようにして、パッケージ基板に対して機能素子体が位置決めして組み合わされる。機能素子パッケージ体においては、各導電バンプに対して加熱圧着処理や超音波印加処理を施すことによって、各導電バンプを介して相対する各入出力電極と各素子実装用ランドとが機械的かつ電気的に接続される。機能素子パッケージ体においては、機能素子体の可動子が、犠牲層を残したままの状態でパッケージ基板の第1主面上において絶縁樹脂層内に囲まれて構成された可動子封装空間部内に封装される。

【0017】

機能素子パッケージ体においては、可動子封装空間部内にパッケージ基板の第2主面側から貫通孔を介して犠牲層除去剤を充填して犠牲層を溶解し、用済みの犠牲層除去剤を貫通孔から回収する。機能素子パッケージ体においては、可動子を可動子封装空間部内に封装した状態で犠牲層が除去されることで、取り扱いが簡便化されるとともに変形等の発生が抑制される。機能素子パッケージ体においては、各入出力電極と各素子実装用ランドとの接続部位及び可動子封装空間部を構成する絶縁樹脂層の形成部位とが同一箇所に構成されることで、簡易かつ確実な実装が行われるようになるとともに小型化が図られるようになる。機能素子パッケージ体においては、貫通孔内に封止材を充填することによって、可動子を封装した可動子封装空間部を密閉空間部として構成する。機能素子パッケージ体においては、可動子封装空間部内において可動子が安定した動作を行い、また経時変化の発生も抑制される。

【0018】

また、上述した目的を達成する本発明にかかる機能素子パッケージ体の製造方法は、第1主面上に多数個の素子実装用ランドを形成してこれら素子実装用ランドによって囲まれた領域を素子体実装領域として構成してなるパッケージ基板を製作するパッケージ基板製作工程と、電極形成面に可動子と多数個の入出力電極とを設けた機能素子体を製作する機能素子体製作工程と、パッケージ基板に対してその素子実装領域に電極形成面を実装面として機能素子体を実装する機能素子体実装工程とを有して機能素子パッケージ体を製造する。機能素子パッケージ体の製造方法は、パッケージ基板の製作工程が、素子体実装領域内に位置して第1主面と第2主面とに貫通する貫通孔を形成する貫通孔形成工程と、各素子実装用ランド上にそれぞれ導電バンプを設ける導電バンプ形成工程とを有する。機能素子パッケージ体の製造方法は、機能素子体の製作工程が、素子基板の第1主面を電極形成面として多数個の入出力電極と犠牲層を残した可動子とを形成する素子形成工程と、各入出力電極を跨り可動子を囲む所定の厚みを有する枠状の絶縁樹脂層を形成する絶縁樹脂層形成工程と、絶縁樹脂層に対して各入出力電極をそれぞれ露出させる多数個の開口部を形成する開口部形成工程とを有する。機能素子パッケージ体の製造方法は、パッケージ基板に対する機能素子体の実装工程が、電極形成面を実装面として、各開口部内にそれぞれ相対する各導電バンプを嵌合させて各導電バンプと各入出力電極とを接触させるように位置決めして組み合わせることによって絶縁樹脂層に囲まれて構成された可動子封装空間部内に可動子を臨ませる機能素子体組合せ実装工程と、各導電バンプを介して相対する各入出力電極と素子実装用ランドとを電気的かつ機械的に接続する入出力電極接続工程と、パッケージ基板の第2主面側から貫通孔を介して犠牲層除去剤を充填して犠牲層を除去する犠牲層除去工程と、貫通孔内に封止材を充填して貫通孔を閉塞する貫通孔封止工程とを有する。

【0019】

機能素子パッケージ体の製造方法においては、パッケージ基板に対して機能素子体が、犠牲層を残して可動子を保護した状態のままで電極形成面を実装面として組み合わされることから、取り扱いが簡便となるとともに外部負荷によって微細な可動子の破損等の発生が防止されて生産性や歩留りを向上してコスト低減を図って機能素子パッケージ体を製造する。機能素子パッケージ体の製造方法においては、パッケージ基板に対して機能素子体が、絶縁樹脂層に形成した各開口部内に相対する各導電バンプをそれぞれ嵌合させるように位置決めして組み合わせた状態で、各導電バンプに対して加熱圧着処理や超音波印加処理を施して各導電バンプを介して相対する各入出力電極と各素子実装用ランドとが機械的かつ電気的に接続されるようにする。機能素子パッケージ体の製造方法においては、各入出力電極と各素子実装用ランドとの接続部位及び可動子封装空間部を構成する絶縁樹脂層の形成部位とを同一箇所に設けることで、小型化を図った機能素子パッケージ体を製造する。機能素子パッケージ体の製造方法においては、可動子を気密空間部内に封装して外部環境等の影響を受けることなく安定した動作が行われるようにするとともに、気密空間部を構成するためのキャップ部材を不要とすることで高精度でかつ構造の簡易化を図った機能素子パッケージ体を製造する。

【発明の効果】

【0020】

本発明によれば、枠状の絶縁樹脂層によって各入出力電極と各素子実装用ランドとの接続部位を固定するとともに可動子を封装する気密状態の可動子封装空間部を構成することから、可動子の安定動作化による信頼性の向上と、構造の簡易化及び小型化を図ることが可能となる。本発明によれば、可動子を可動子封装空間部内に封装した状態で犠牲層を除去することから、工程の簡易化や歩留りの向上を図ることが可能となる。

【発明を実施するための最良の形態】

【0021】

以下、本発明の実施の形態として示す機能素子パッケージ体1及びその製造方法について図面を参照して詳細に説明する。実施の形態として図面に示した機能素子パッケージ体1は、各種の電子機器、例えば携帯電話機やパーソナルコンピュータ等に搭載される高周波機能素子パッケージ体であり、図1に示すようにパッケージ基板2と、このパッケージ基板2の第1主面2a上に実装される機能素子体3とから構成され、パッケージ基板2の第2主面2bを実装面として、詳細を省略する実装用基板4に実装される。機能素子パッケージ体1は、パッケージ基板2が実装用基板4と接続されて機能素子体3と入出力信号を授受する入出力回路部等を構成する。

【0022】

機能素子パッケージ体1においては、詳細を後述するようにパッケージ基板2に機能素子体3を実装することにより、機能素子体3に設けた可動子33が気密状態に保持される可動子封装空間部21内に封装される。機能素子パッケージ体1においては、パッケージ基板2に機能素子体3が、3次元形状の可動子33を形成する犠牲層35を残したままの状態で実装した後に、犠牲層35が除去される。機能素子パッケージ体1においては、パッケージ基板2と機能素子体3との電気的接続部位と可動子封装空間部21を構成する絶縁樹脂層34の形成部位とが同一箇所に設けられる。

【0023】

パッケージ基板2は、例えば配線基板として一般的に用いられる銅貼りガラスエポキシ樹脂基板等の絶縁基板5を基材として詳細を後述する工程を経て製作される。なお、パッケージ基板2は、耐熱性や耐薬品性或いは加工性に優れた基板材、例えば液晶ポリマー、ガラスエポキシ、ポリイミド、ポリフェニレンエーテル、ビスマレイトトリアジン、ポリテトラフルオロエチレン或いは高周波対応を図るブタジエン樹脂等の有機絶縁基板を基材としてもよい。パッケージ基板2には、第1主面2aを構成する絶縁基板5の一方主面に多数個の素子実装用ランド6が形成されるとともに、これら素子実装用ランド6に導電バンプ7が設けられる。パッケージ基板2には、第2主面2bを構成する絶縁基板5の他方主面に、所定の配線パターン8や実装用ランド9が形成されている。

【0024】

パッケージ基板2には、絶縁基板5を貫通して第1主面2a側の素子実装用ランド6と相対する第2主面2b側の配線パターン8或いは実装用ランド9とをそれぞれ層間接続する多数個のビア10が形成されている。パッケージ基板2には、詳細を後述するように所定の箇所に位置して第1主面2aと第2主面2bとに貫通する貫通孔からなる複数個の犠牲層除去孔11が形成されている。パッケージ基板2には、第2主面2b側に全面に亘って配線パターン8を被覆するとともに開口部12aを介して実装用ランド9を露出させるソルダレジスト層12が形成されている。

【0025】

パッケージ基板2には、第2主面2b側において、各犠牲層除去孔11の開口部をそれぞれ閉塞する封止材層13が形成されている。パッケージ基板2には、ソルダレジスト層12に形成した各開口部12aに臨ませられて露出される各実装用ランド9に、それぞれ導電バンプ14が設けられる。パッケージ基板2には、第1主面2aに機能素子体3の接合状態を補強する補強樹脂層15が形成されている。なお、パッケージ基板2は、両面に配線パターンが形成された両面配線基板を示したが、多数層の配線層を有する多層配線基板であってもよいことは勿論である。

【0026】

パッケージ基板2は、第1主面2a上に各素子実装用ランド6を、互いに絶縁されて絶縁基板5の各辺に沿って枠状に配列して形成する。各素子実装用ランド6は、詳細には前工程で形成された各ビア10と一体化して形成される。ビア10は、絶縁基板5を貫通して形成されたスルーホール16と、このスルーホール16の内壁に全域に亘って形成されためっき層17と、導電性樹脂或いは非導電性樹脂を充填してスルーホール16内に形成された充填樹脂層18と、スルーホール16の上下開口部をそれぞれ閉塞して形成される蓋めっき層19a、19bからなる。各素子実装用ランド6は、スルーホール16の第1主面2a側の開口部に形成された蓋めっき層19aと一体化して形成される。なお、パッケージ基板2は、多層配線基板によって構成される場合に、各ビア10が内層の各配線層を適宜層間接続するように形成される。

【0027】

パッケージ基板2は、第1主面2aの各素子実装用ランド6によって囲まれた矩形の領域が、機能素子体3を実装する素子体実装領域20として構成される。パッケージ基板2は、後述するように素子体実装領域20上に機能素子体3を実装した状態において、この素子体実装領域20と機能素子体3の電極形成面31と後述する絶縁樹脂層34とによって機能素子体3の可動子33を封装する可動子封装空間部21を構成する。

【0028】

導電バンプ7は、各素子実装用ランド6に設けられた導電性を有する突起体であり、周知のようにめっき法、印刷法或いはボールボンディング法等によって形成される。導電バンプ7は、機能素子体3と接続する接続子として作用する。同様に、第2主面2b側の実装用ランド9に設けられた導電バンプ14も、導電性を有する突起体であり、機能素子パッケージ体1を実装用基板4に実装する際の接続子として作用する。導電バンプ14は、機能素子体3を接続するための導電バンプ7よりも大型に形成することが可能であることから、例えば半田ボール等の金属ボールを搭載してリフロー処理を施すことによって形成される。なお、導電バンプ14は、導電バンプ7と同様にめっき法、印刷法或いはボールボンディング法等によって形成してもよいことは勿論である。

【0029】

パッケージ基板2は、例えば絶縁基板5に貼り付けた銅箔に対してパターニング処理を施して、第2主面2bに配線パターン8と実装用ランド9とを形成する。パッケージ基板2は、配線パターン8や実装用ランド9が上述した各ビア10の蓋めっき層19bと適宜接続されて形成される。パッケージ基板2は、配線パターン8や実装用ランド9を被覆して第2主面2bの全面にソルダレジスト層12が形成され、このソルダレジスト層12に適宜のパターニング処理を施して導電バンプ14の外径寸法よりもやや大きな開口寸法となる開口部12aを形成する。

【0030】

パッケージ基板2は、各犠牲層除去孔11が、絶縁基板5を貫通して可動子封装空間部20に連通して形成され、後述するようにパッケージ基板2に機能素子体3を実装した状態で可動子33を保護するために残された犠牲層35を除去するために用いられる。各犠牲層除去孔11は、上述した各ビア10と同一工程で形成され、スルーホール22と、このスルーホール22の内壁に全域に亘って形成されためっき層23とから構成される。各犠牲層除去孔11には、スルーホール22の開口部を閉塞する蓋めっき層が形成されていない。

【0031】

各犠牲層除去孔11は、第2主面2b側から犠牲層除去剤を可動子封装空間部20内に充填して犠牲層35を除去した後に、可動子封装空間部20内に還元ガスを注入するために用いられる。各犠牲層除去孔11は、犠牲層35の除去工程を経た後に、封止材層13によって第2主面2b側の開口部を閉塞される。各犠牲層除去孔11は、スルーホール22内のめっき層23を特に必要としないが、これらが各ビア10と同一工程で形成されることで工程数が増えることは無く、可動子封装空間部20の気密性を向上させるために有効である。また、各犠牲層除去孔11は、機能素子体3から発生して可動子封装空間部20内に籠もる熱を効率的に放熱するサーマルビアホールとしても機能する。

【0032】

ところで、パッケージ基板2は、微小な機能素子体3を高精度に実装するために、第1主面2aや第2主面2bが比較的平坦化されて形成されることが好ましい。したがって、パッケージ基板2は、第1主面2aに各素子実装用ランド6や各ビア10の蓋めっき層19の厚みによって生じる段差を埋める第1平坦化樹脂層25が形成される。第1平坦化樹脂層25は、素子実装用ランド6や蓋めっき層19を埋設する厚みで第1主面2aの全面に亘って絶縁樹脂層を形成し、この絶縁樹脂層に対して素子実装用ランド6を露出させる機械研磨や化学研磨或いは機械−化学研磨を施して形成される。

【0033】

パッケージ基板2は、同様にして第2主面2bにも配線パターン8や各実装用ランド9或いは各ビア10の蓋めっき層19bの厚みによって生じる段差を埋める第2平坦化樹脂層26が形成される。第2平坦化樹脂層26も、配線パターン8や各実装用ランド9或いは各ビア10の蓋めっき層19bを埋設する厚みで第2主面2bの全面に亘って絶縁樹脂層を形成し、この絶縁層に対して各実装用ランド9を露出させる機械研磨や化学研磨或いは機械−化学研磨を施して形成される。

【0034】

機能素子体3は、SAW素子(表面弾性波素子)やBAW素子(バルク弾性波素子)或いはMEMS(微小電子機械部品)やFBAR素子(圧電薄膜共振素子)等のマイクロディバイスであり、シリコン基板やガラス基板を母材とする基板30と、この基板30の第1主面を電極形成面31として多数個の入出力電極32と、詳細を省略する可動子33を形成してなる。機能素子体3は、図示を省略するが基板30に可動子33を駆動する電極や、これら電極と入出力電極32とを接続する微細配線パターン等が形成されている。機能素子体3には、電極形成面31に詳細を後述する絶縁樹脂層34が形成され、電極形成面31を実装面として上述したパッケージ基板2の素子体実装領域20に実装される。

【0035】

機能素子体3は、基板30上に適宜の形状で犠牲層29を形成し、この犠牲層29を利用して3次元形状の可動子33を形成する。機能素子体3は、犠牲層29が酸化膜やシリコン或いは有機膜等によって形成され、この犠牲層29を残した状態で供給されて上述したパッケージ基板2に実装される。機能素子体3は、一般にはウエーハ上で多数個が形成され、それぞれの犠牲層29を除去した後にダイシング工程によって1個ずつに切断されて供給される。機能素子体3は、犠牲層29を残して可動子33を保護した状態で用いることから、微細な可動子33がダイシング工程に際しの水圧による変形或いは外部環境の影響による特性変化等を防止されるとともにハンドリング性の向上が図られる。

【0036】

機能素子体3は、入出力電極32が、電極形成面31上に可動子33を囲んで絶縁基板5の各辺に沿って枠状に配列して形成される。各入出力電極32は、パッケージ基板2に機能素子体3を実装した状態で、各素子実装用ランド6とそれぞれ相対するようにして形成されている。機能素子体3は、パッケージ基板2側から供給される入力信号によって可動子33が動作し、この可動子33の動作による出力信号をパッケージ基板2側へと出力する。

【0037】

機能素子体3には、絶縁樹脂層34が、電極形成面31に各入出力電極32上に跨って可動子33を囲む枠状に形成される。絶縁樹脂層34は、図1において上下方向に動作する可動子33の動作領域よりもやや大きな厚みと各入出力電極32の外形寸法よりもやや大きな幅とを有して形成される。絶縁樹脂層34は、詳細を後述するようにエポキシ樹脂やフェノール樹脂或いはベンゾシクロブテン樹脂(BCB)等の感光性絶縁樹脂層を電極形成面31上に全面に亘って形成し、この絶縁樹脂層にパターニング処理を施して形成する。

【0038】

絶縁樹脂層34には、上述したパターニング処理を施す際に、各入出力電極32に対応する位置にそれぞれ開口部36も形成される。各開口部36は、パッケージ基板2側に設けた上述した導電バンプ7の外形寸法よりもやや大きな開口寸法を以って形成され、それぞれの底部に相対する各入出力電極32の表面を露出させる。絶縁樹脂層34は、半硬化状態で電極形成面31上に形成されることによって導電バンプ7が相対する各開口部36の内壁に密着するようにし、パッケージ基板2に機能素子体3を実装した状態で硬化処理が行われる。

【0039】

機能素子体3は、上述したように犠牲層35を残すことによって可動子33を保護した状態で、電極形成面31を実装面としてパッケージ基板2の素子実装領域20上に実装される。機能素子体3は、絶縁樹脂層34の各開口部36に相対する導電バンプ7がそれぞれ嵌合して入出力電極32と接触するように位置決めされてパッケージ基板2に組み合わされる。機能素子体3は、電極形成面31の対向面側からパッケージ基板2に押し付けられた状態で加熱処理が施されることによって各導電バンプ7を介して入出力電極32がパッケージ基板2側の各素子実装用ランド6と電気的かつ機械的に接続されて機能素子パッケージ体1を完成する。

【0040】

機能素子パッケージ体1は、補強樹脂層15を外周面の全周に亘って形成することにより絶縁樹脂層34が補強される。補強樹脂層15は、例えば流動性とチクソ性(thixotropy)を有するフィラー入り液状エポキシ系樹脂材によって形成され、パッケージ基板2に対する機能素子体3の実装状態を補強するとともに、絶縁樹脂層34によって保持された各導電バンプ7を介する各素子実装用ランド6と入出力電極32との接合状態を補強する。補強樹脂層15は、絶縁樹脂層34によって構成される可動子封装空間部21の気密性を補強する。

【0041】

機能素子パッケージ体1においては、硬化処理が施された絶縁樹脂層34が、導電バンプ7を介した入出力電極32と各素子実装用ランド6との接合状態を保持するとともに機能素子体3の電極形成面31とパッケージ基板2の第1主面2aとの間において可動子封装空間部21を構成する。機能素子パッケージ体1においては、犠牲層35が除去された可動子33が、還元ガス雰囲気の可動子封装空間部21内において外部環境変化や静電気の帯電等から隔離されて安定した状態で動作するとともに経時変化の発生も抑制される。機能素子パッケージ体1においては、絶縁樹脂層34が、同一箇所において各入出力電極32と各素子実装用ランド6との接続部位を保持するとともに可動子封装空間部21を構成することで、小型化が図られる。

【0042】

上述した機能素子パッケージ体1は、パッケージ基板製作工程と、機能素子体製作工程と、機能素子体実装工程とを経て製造される。パッケージ基板製作工程には、図2に示す表裏主面(第1主面2a及び第2主面2b)にそれぞれ銅箔層40a、40bが設けられた絶縁基板5が供給される。絶縁基板5は、セラミック基板やガラス基板と比較して廉価であり、スルーホールの加工性にも優れている。なお、絶縁基板5については、上述したようにかかる銅貼積層基板に限定されず、回路基板用に用いられる各種の基板材を用いてもよいことは勿論である。

【0043】

パッケージ基板製作工程は、絶縁基板5に対して、図3に示すようにビア10を構成するスルーホール16や犠牲層除去孔11を構成するスルーホール22を形成する貫通孔形成工程が施される。貫通孔形成工程は、レーザ照射やプラズマ照射或いはこれらを同時に照射するいわゆるドライエッチング加工やドリル加工によって絶縁基板5を貫通する多数個のスルーホール16、22を所定位置にそれぞれ穿孔する。

【0044】

パッケージ基板製作工程は、図4に示すように、各スルーホール16に対してめっき処理を施してその内壁に全域に亘ってめっき層17形成して、表裏主面2a、2bの銅箔層40a、40bを導通させてビア10を構成する。なお、犠牲層除去孔11を構成するスルーホール22にも、上述したように可動子封装空間部21の気密性を高めるとともに封止材層13を形成するためにめっき層23が同時に形成される。

【0045】

パッケージ基板製作工程は、同図に示すように、各ビア10内に導電性或いは非導電性の樹脂を充填して充填樹脂層18を形成する。充填樹脂層18は、例えばエポキシ系樹脂にグリコール系溶剤や芳香族系溶剤を混合してなる樹脂材が用いられ、この樹脂材を各ビア10内に充填した後に紫外線の照射や加熱処理を施して硬化させることによって形成される。パッケージ基板製作工程は、スルーホール22が犠牲層除去孔11を構成して犠牲層除去孔剤を可動子封装空間部21内に充填することから、内部に充填樹脂層は形成されない。

【0046】

パッケージ基板製作工程は、図5に示すように、ビア10の表裏開口部に蓋めっき処理を施してそれぞれ蓋めっき層19a、19bを形成する。蓋めっき処理は、蓋めっき層19a、19bが、それぞれ素子実装用ランド6や配線パターン8の一部を構成することから、銅めっき或いはアルミめっきによって行われる。パッケージ基板製作工程は、上述した工程を経て、図6に示した第1中間基板50を得る。第1中間基板50は、第1主面2aを構成する主面上に、各ビア10の開口部を閉塞して銅箔層40a上に多数個の蓋めっき層19aが形成されるとともに、各蓋めっき層19aに囲まれた矩形領域内に犠牲層除去孔11を構成する多数個のスルーホール22が開口される。

【0047】

パッケージ基板製作工程は、絶縁基板5の銅箔層40a、40bに対してパターニング工程を施し、図7に示すように第1主面2aに素子実装用ランド6を形成するとともに第2主面2bに配線パターン8や実装用ランド9を形成する。パターニング工程は、いわゆるフォトリソグラフ技術により、銅箔層40a、40b上に全面に亘ってエッチングレジスト層を形成する工程と、エッチングレジスト層に所定の開口部を形成する工程と、開口部の銅箔を除去して素子実装用ランド6や配線パターン8及び実装用ランド9を形成するエッチング工程と、エッチングレジスト層を除去する工程等からなる。

【0048】

パターニング工程は、エッチングレジスト層形成工程において、例えば液状の感光性レジストをスピンコート法或いはロールコート法等によって銅箔層40a、40b上に塗布してエッチングレジスト層を形成する。また、エッチングレジスト層形成工程は、例えばフィルム状の感光性レジスト材を用いてラミネート法等によって銅箔層40a、40b上に被覆してエッチングレジスト層を形成する。なお、エッチングレジスト層については、非感光性レジストを用いて形成するようにしてもよいことは勿論である。

【0049】

パターニング工程は、開口部形成工程が、素子実装用ランド6や配線パターン8及び実装用ランド9に対応する部位を開口したマスクをエッチングレジスト層上に接合する工程と、各開口部を介してエッチングレジスト層に露光処理と現像処理とを施して当該部位のエッチングレジスト層を除去する工程とからなる。エッチング工程は、マスクを取り外した状態で硫酸と硝酸と酢酸との混合酸や塩化第二鉄等のエッチャント(エッチング材)を用いて、エッチングレジスト層の各開口部に露出した銅箔層を除去する。

【0050】

パターニング工程は、エッチングレジスト層除去工程において、エッチングレジストの種類に応じて適宜選択された除去材、例えばアセトン等の有機溶剤やレジスト剥離液、水酸化ナトリウム溶液等を用いて第1主面2aや第2主面2bに残ったエッチングレジスト層を除去することにより、第1主面2aと第2主面2b上に必要な銅箔層のみを残して素子実装用ランド6や配線パターン8及び実装用ランド9を形成する。なお、パターニング工程は、非感光性レジストによってエッチングレジスト層を形成した場合には、反応性イオンエッチング法やレーザ照射等によって開口部が形成される。

【0051】

パターニング工程においては、上述した各工程を経て、第1主面2a上に枠状に配列された各素子実装用ランド6を形成するとともに第2主面2b上にも枠状に配列された各実装用ランド9を形成する。パターニング工程においては、図7に示すように各素子実装用ランド6によって囲まれた領域、すなわち素子体実装領域20内の銅箔層40aをそのまま残すことによって第1主面2aに第1遮蔽金属層41を形成する。パターニング工程においては、同様にして各実装用ランド9によって囲まれた領域内の銅箔層40bをそのまま残すことによって第2主面2b上に第2遮蔽金属層42を形成する。なお、第2遮蔽金属層42については、第2主面2bの当該部位に配線パターン8が形成される場合には、特に設ける必要は無い。

【0052】

第1遮蔽金属層41及び第2遮蔽金属層42は、可動子封装空間部21の底面部を構成する部位であるが、金属層で覆うことによって絶縁基板5の気密性を向上させる。また、第1遮蔽金属層41及び第2遮蔽金属層42は、可動子封装空間部21を磁気的シールド空間部として構成して可動子33が安定して動作が行われるようにする。

【0053】

パッケージ基板製作工程は、第1主面2a上に微細で精密な機能素子体3を実装することから、パッケージ基板2が第1主面2aと第2主面2bとを高面精度に形成されていることが好ましい。パッケージ基板2は、上述したように第1主面2a側に多数個の素子実装用ランド6を形成するとともに第2主面2b側に配線パターン8や実装用ランド9を形成することで、それらの厚みによる段差が生じている。パッケージ基板製作工程は、第1主面2aと第2主面2bとに第1平坦化樹脂層25と第2平坦化樹脂層26の形成工程が施される。なお、以下に第1平坦化樹脂層25の形成工程について代表して説明する。

【0054】

平坦化樹脂層形成工程は、熱膨張による変形等を防止するために絶縁樹脂層34と同一樹脂材を用いることが好ましく、例えばエポキシ樹脂、フェノール樹脂、BCB樹脂等の絶縁樹脂材が用いられる。平坦化樹脂層形成工程は、第1主面2a上に絶縁樹脂材を各素子実装用ランド6を被覆して全面に亘って塗布し、絶縁樹脂材を硬化させた状態で機械研磨、化学研磨或いは機械−化学研磨処理によって素子実装用ランド6の表面を露出させるまで研磨する。なお、研磨処理については、第1主面2a側の第1平坦化樹脂層25と第2主面2b側の第2平坦化樹脂層26とを同時に研磨することが可能である。平坦化樹脂層形成工程については、機能素子体3が直接実装される第1主面2a側にのみ施すようにしてもよい。

【0055】

パッケージ基板製作工程は、図8に示すように第2主面2b側に、配線パターン8を被覆してこれを保護するとともに絶縁を保持するとともに実装用ランド9を露出させるソルダレジスト層12を形成する。ソルダレジスト層形成工程は、第2主面2b上に例えば感光性ソルダレジストをスピンコート法や印刷法等によって所定の厚みで塗布してソルダレジスト層を形成する。ソルダレジスト層形成工程は、ソルダレジスト層に対して実装用ランド9に対応する部位に開口部を設けたマスクを接合してソルダレジスト層に露光処理と現像処理とを施す。ソルダレジスト層形成工程は、マスクを取り外してマスクの開口部に対応するソルダレジスト層を除去して底部に各実装用ランド9をそれぞれ露出させた多数個の開口部12aを形成する。ソルダレジスト層形成工程においては、ソルダレジストを硬化させることによって、第2主面2bにソルダレジスト層12を形成する。

【0056】

ソルダレジスト層形成工程においては、同図に示すように各犠牲層除去孔11の第2主面2b側の開口部位についても、同時に開口部43を形成する。なお、ソルダレジスト層形成工程は、非感光性のソルダレジスト材を用いる場合には、第2主面2b上にソルダレジスト材を塗布した後に硬化させてソルダレジスト層12を形成し、このソルダレジスト層12に反応性イオンエッチングやレーザ加工等を施して各実装用ランド9を露出させる開口部12aや各犠牲層除去孔11の開口部位を露出させる開口部41を形成する。

【0057】

パッケージ基板製作工程は、図9に示すように平坦化された第1主面2aに露出された各素子実装用ランド6上にそれぞれ導電バンプ7を形成する。導電バンプ形成工程は、具体的には各素子実装用ランド6上に一体化された蓋めっき層19aに、例えばめっき法、印刷法或いはボールボンディング法等によって所定の外径寸法を有する半球形突起物からなる導電バンプ7を形成する。

【0058】

パッケージ基板製作工程は、上述した各工程を経て図10に示したパッケージ基板2を得る。パッケージ基板2は、上述したように第2主面2a上に、全面に亘って形成された第1平坦化樹脂層25に、略同一面を構成してそれぞれ蓋めっき層19aを一体化してなる多数個の素子実装用ランド6が枠状に配列されて形成される。パッケージ基板2は、各素子実装用ランド6に囲まれた領域内に第1遮蔽金属層41が形成されるとともに、多数個の犠牲層除去孔11が開口される。

【0059】

パッケージ基板製作工程においては、第2主面2b側において、ソルダレジスト層12に形成された開口部12aを介して実装用ランド8がそれぞれ露出されており、これら実装用ランド8に導電バンプ14を設ける導電バンプ形成工程も施される。導電バンプ形成工程は、第2主面2bがパッケージ基板2上に機能素子体3を精密に実装する際の受け面を構成するために平坦性が要求されることから、補強樹脂層15の形成工程と同様に機能素子体3を実装した後工程で行われる。

【0060】

機能素子体製作工程は、大判のウエーハ上で多数個の機能素子体3を一括して製作し、ウエーハを切断して1個ずつに切り離されるが、説明の便宜上、基板30に個別に形成する工程により説明する。機能素子体製作工程においては、シリコン基板やガラス基板からなる基板30が工程に供給され、この基板30の第1主面を電極形成面31として図11に示すように多数個の入出力電極32や図示しない配線パターン或いは可動子33とが形成される。

【0061】

機能素子体製作工程は、詳細を省略するが基板30上にスパッタ法等によって金属薄膜層を形成し、この金属薄膜層に対して所定のパターニング処理を施して各入出力電極32や微細な配線パターンを形成する。機能素子体製作工程は、上述したパッケージ基板2の各素子実装用ランド6に対応して枠状に配列して形成された各入出力電極32に囲まれた領域内に可動子33を形成する。機能素子体製作工程は、3次元形状の可動子33を形成するために基板30上に、例えば酸化膜やシリコン或いは有機膜等によって所定の形状を有する犠牲層35を形成し、後述するパッケージ基板2の実装工程を経て犠牲層35を除去する。

【0062】

機能素子体製作工程は、犠牲層35を残した状態のままで、基板30の主面上に絶縁樹脂基層44を形成する工程と、絶縁樹脂基層44に所定のパターニング処理を施す工程とを有する。絶縁樹脂基層形成工程は、感光性を有する絶縁樹脂、例えばエポキシ樹脂、フェノール樹或いはBCBをスピンコート法等によって各入出力電極32や可動子33を形成した電極形成面31上に所定の厚みで塗布することによって、図12に示すように絶縁樹脂基層44を形成する。絶縁樹脂基層44は、パターニング処理を施こされて絶縁樹脂層34を形成するため、上述したように可動子33の動作領域を確保するに足る均一な厚みを有して形成される。

【0063】

パターニング工程は、絶縁樹脂基層44にフォトグラフ処理を施して上述した形状の絶縁樹脂層34を形成する工程であり、絶縁樹脂層34に対応する部位に開口部を設けたマスクを接合して絶縁樹脂基層44に露光処理と現像処理とを施す。パターニング工程は、マスクを取り外してマスクの開口部に対応する絶縁樹脂を除去して、各入出力電極32上に跨りかつ可動子33を囲む枠状の絶縁樹脂層34を形成する。パターニング工程は、絶縁樹脂基層44から、半硬化状態であり、各入出力電極32を被覆するに足る幅寸法を有する絶縁樹脂層34を形成する。

【0064】

パターニング工程は、図13に示すように絶縁樹脂層34を形成するとともに各入出力電極32に対応する位置にそれぞれ開口部36も形成する。パターニング工程は、絶縁樹脂層34内に、パッケージ基板2側に設けた導電バンプ7の外形寸法よりもやや大きな開口寸法を有してそれぞれの底部に相対する各入出力電極32の表面を露出させる開口部36を形成する。

【0065】

機能素子パッケージ体1の製造工程は、上述したパッケージ基板製作工程によって製作されたパッケージ基板2の素子体実装領域20上に上述した機能素子体製作工程によって製作された機能素子体3を実装する。機能素子体実装工程は、機能素子体3を電極形成面31を実装面としてパッケージ基板2に対して位置決めして組み合わせる機能素子体組合せ工程と、各導電バンプ7を介して相対する各入出力電極32と各素子実装用ランド6とを電気的かつ機械的に接合する入出力電極接続工程と、絶縁樹脂層34を硬化させる絶縁樹脂層硬化工程と、絶縁樹脂層34を補強する補強樹脂層15を形成する補強樹脂層形成工程と、犠牲層35を除去する犠牲層除去工程と、犠牲層除去孔11を封止する犠牲層除去孔封止工程とを有する。

【0066】

機能素子体組合せ工程は、図14に示すように、機能素子体3の絶縁樹脂層34に形成した各開口部36内にそれぞれ相対する各導電バンプ7を嵌合させ、各導電バンプ7と各開口部36の底部に露出された各入出力電極32とを接触させて機能素子体3をパッケージ基板2の素子体実装領域20上に組み合わせる。機能素子体組合せ工程においては、絶縁樹脂層34が半硬化状態で形成されることにより、導電バンプ7が開口部36を押し広げて入出力電極32と確実に接触されるようにする。

【0067】

入出力電極接続工程は、加熱加圧装置を用い、機能素子体3を電極形成面31の対向面からパッケージ基板2に押し付けた状態で、入出力電極32の対応部位を加熱して導電バンプ7を接合させる。入出力電極接続工程は、機能素子体3の特性が損なわれないように比較的低温領域で行うことが好ましい。入出力電極接続工程は、加熱加圧装置ばかりでなく超音波ホーンを用いて各入出力電極32と各導電バンプ7の接触部位に超音波を印加することで、より低温領域でかつ処理時間を短縮化して接合処理を行うことを可能とする。なお、入出力電極接続工程は、超音波ホーンのみを用いて各入出力電極32と各導電バンプ7の接合処理を行うようにしてもよい。

【0068】

絶縁樹脂層硬化工程は、半硬化状態の絶縁樹脂層34に対して加熱処理を施すことにより硬化させることによって、図14に示すようにパッケージ基板2側の素子体実装領域20と機能素子体3側の電極形成面31との間に外周部を絶縁樹脂層34によって閉塞して可動子33を封装する可動子封装空間部21を形成する。

【0069】

補強樹脂層形成工程は、図15に示すように硬化処理を施された絶縁樹脂層34の外周面を全週に亘って被覆する補強樹脂層15を形成する。補強樹脂層形成工程は、上述したように流動性とチクソ性を有するフィラー入り液状エポキシ系樹脂材をディスペンサ等によってパッケージ基板2の第1主面2aと機能素子体3の基板30との間に充填し、加熱処理や紫外線照射処理を行って硬化させることにより、パッケージ基板2に対する機能素子体3の実装状態を補強し、絶縁樹脂層34によって保持された各導電バンプ7を介する各素子実装用ランド6と入出力電極32との接合状態を補強し、絶縁樹脂層34によって構成される可動子封装空間部21の気密性を補強する補強樹脂層15を形成する。

【0070】

機能素子パッケージ体1の製造工程においては、上述したように犠牲層35を残して可動子33を保護した状態で機能素子体3を実装することから、犠牲層除去工程によって機能素子体3から犠牲層35の除去処理が施される。犠牲層除去工程は、パッケージ基板2の第2主面2bに開口された各犠牲層除去孔11から、可動子封装空間部21内に犠牲層除去剤を充填する。犠牲層除去工程は、犠牲層除去剤として犠牲層35の材料に適合したフッ酸系溶剤、アルカリ系溶剤、有機溶剤或いはフッ酸系ガス、フッ素を含有するガス、酸素を含むガスが選択して用いられる。犠牲層除去工程は、各犠牲層除去孔11から可動子封装空間部21内に充填した犠牲層除去剤によって犠牲層35を溶解するとともに、各犠牲層除去孔11から排出する。

【0071】

機能素子パッケージ体1の製造工程においては、機能素子体3を最終工程に近い犠牲層除去工程まで犠牲層35を残した状態のままで取り扱うことから、微細な可動子33が損傷することが防止されるようになるとともに加熱処理やエッチング処理による影響も回避されるようになる。機能素子体3は、可動子33が可動子封装空間部21内において犠牲層35を除去されることで、電極形成面31上で動作が可能な状態となる。

【0072】

犠牲層除去孔封止工程は、犠牲層35を除去した各犠牲層除去孔11内に例えば半田や金属ペースト或いは絶縁樹脂等の封止材を充填することによって、図16に示すように封止材層13を形成する。犠牲層除去孔封止工程は、図示しないチャンバー内を真空或いはアルゴン等の還元ガス雰囲気に保持した状態で行うことによって可動子封装空間部21内を真空雰囲気や還元ガス雰囲気とする。可動子33は、還元ガス雰囲気の可動子封装空間部21内に封装されることによって、外部環境変化や静電気の帯電等から隔離されて安定した状態で動作するとともに錆の発生も防止される。

【0073】

機能素子パッケージ体1の製造工程においては、上述したようにパッケージ基板2の第2主面2b側に形成されたソルダレジスト層12の開口部12aに導電バンプ14を設ける導電バンプ形成工程が施される。導電バンプ形成工程は、犠牲層除去孔封止工程の前工程又は後工程で実施され、例えば各開口部12a内に半田等の金属ボールをそれぞれ装填した後にリフロー処理を施すことによって各開口部12aの底部に露出された実装用ランド9に接合された導電バンプ14を形成する。なお、導電バンプ形成工程は、導電バンプ14を例えば導電ペーストや半田ペーストを用いて印刷法によって形成したり、めっき法やボールボンディング法によって形成するようにしてもよい。

【0074】

機能素子パッケージ体1の製造工程においては、上述した各工程を経て、可動子33が製造工程中において破損や温度変化或いはエッチング液やめっき液の影響、静電気による貼り付き等が防止され、歩留りの向上を図って図1に示した機能素子パッケージ体1を製造する。機能素子パッケージ体1の製造工程においては、キャップ部材等を用いることなくパッケージ基板2と機能素子体3とによって可動子33を封装する気密性の高い可動子封装空間部21を構成し、可動部子33の酸化や劣化等を抑制して長寿命化が図られた機能素子パッケージ体1を製造する。機能素子パッケージ体1の製造工程においては、各入出力電極32と各素子実装用ランド6との接続部位及び可動子封装空間部21を構成する絶縁樹脂層34の形成部位とを同一箇所に設けることで、小型化を図った機能素子パッケージ体1を製造する。

【図面の簡単な説明】

【0075】

【図1】実施の形態として示す機能素子パッケージ体の縦断面図である。

【図2】パッケージ基板製作工程に用いられる両面基板の断面図である。

【図3】スルーホールを形成した両面基板の断面図である。

【図4】ビア形成を行った両面基板の断面図である。

【図5】各ビアに蓋めっき層を形成した両面基板の断面図である。

【図6】同両面基板の平面図である。

【図7】平坦化処理を施した両面基板の断面図である。

【図8】第2主面側にソルダレジスト層を形成した両面基板の断面図である。

【図9】導電バンプを形成した両面基板の断面図である。

【図10】パッケージ基板の平面図である。

【図11】機能素子体の断面図である。

【図12】絶縁樹脂基層を形成した機能素子体の断面図である。

【図13】開口部を有する絶縁樹脂層を形成した機能素子体の断面図である。

【図14】パッケージ基板に対する機能素子体の実装工程図であり、パッケージ基板に機能素子体を組み合せた中間体の断面図である。

【図15】同補強樹脂層を形成した中間体の断面図である。

【図16】同封止材層を形成した中間体の断面図である。

【符号の説明】

【0076】

1 機能素子パッケージ体、2 パッケージ基板、3 機能素子体、4 実装用基板、5 絶縁基板、6 素子実装用ランド、7 導電バンプ、8 配線パターン、9 実装用ランド、10 ビア、11 犠牲層除去孔、12 ソルダレジスト層、13 封止材層、14 導電バンプ、15 補強樹脂層、19 蓋めっき層、20 素子体実装領域、21 可動子封装空間部、25 第1平坦化樹脂層、26 第2平坦化樹脂層、30 基板、31 電極形成面、32 入出力電極、33 可動子、35 犠牲層、36 開口部

【特許請求の範囲】

【請求項1】

第1主面上に多数個の素子実装用ランドを形成してこれら素子実装用ランドで囲まれた領域を素子体実装領域として構成し、上記各素子実装用ランドにそれぞれ設けた導電バンプと、上記素子体実装領域内に位置して第2主面に貫通して形成された貫通孔と、この貫通孔を閉塞する封止材層とを有するパッケージ基板と、

多数個の入出力電極と可動子とを設けた電極形成面に上記可動子を囲む枠状に形成されるとともに底部に上記各入出力電極をそれぞれ露出させる多数個の開口部が設けられた所定の厚みを有する絶縁樹脂層を形成した機能素子体とを備え、

上記機能素子体が、上記可動子を形成する犠牲層を残した状態で上記電極形成面を実装面として上記パッケージ基板の上記素子体実装領域に組み付けられ、上記導電バンプを介して相対する上記各入出力電極と上記各素子実装用ランドとがそれぞれ接続されることによって上記第1主面上に上記絶縁樹脂層で囲まれて構成された可動子封装空間部内に上記可動子を封装して実装され、

上記貫通孔が、上記機能素子体を上記パッケージ基板に実装した状態で上記第2主面側から上記犠牲層を除去する犠牲層除去孔として作用し、上記犠牲層を除去した後に上記封止材層によって閉塞されることを特徴とする機能素子パッケージ体。

【請求項2】

上記機能素子体が、微小電子機械部品(MEMS)や圧電薄膜共振素子或いは表面弾性波フィルタ素子やバルク弾性波フィルタ素子であることを特徴とする請求項1に記載の機能素子パッケージ体。

【請求項3】

上記パッケージ基板が、上記第1主面に上記各素子実装用ランドや所定の配線パターンを形成するとともに上記第2主面にビアを介して接続された多数個の実装用ランドや所定の配線パターンを形成し、

上記各実装用端子にそれぞれ導電バンプを設けた上記第2主面を実装面として実装用基板に実装されることを特徴とする請求項1に記載の機能素子パッケージ体。

【請求項4】

第1主面上に多数個の素子実装用ランドを形成してこれら素子実装用ランドによって囲まれた領域を素子体実装領域として構成してなるパッケージ基板に、可動子と多数個の入出力電極とを設けた電極形成面を実装面として機能素子体を上記素子体実装領域上に実装してなる機能素子パッケージ体の製造方法であり、

上記パッケージ基板の製作工程が、上記素子体実装領域内に位置して第1主面と第2主面とに貫通する貫通孔を形成する貫通孔形成工程と、上記各素子実装用ランド上にそれぞれ導電バンプを設ける導電バンプ形成工程とを有し、

上記機能素子体の製作工程が、素子基板の第1主面を電極形成面として多数個の入出力電極と犠牲層を残した可動子とを形成する素子形成工程と、上記各入出力電極を跨り上記可動子を囲む所定の厚みを有する枠状の絶縁樹脂層を形成する絶縁樹脂層形成工程と、上記絶縁樹脂層に対して底部に上記各入出力電極をそれぞれ露出させる多数個の開口部を形成する開口部形成工程とを有し、

上記パッケージ基板に対する上記機能素子体の実装工程が、上記電極形成面を実装面として、上記各開口部内にそれぞれ相対する上記各導電バンプを嵌合させて上記各導電バンプと上記各入出力電極とを接触させるように位置決めして組み合わせることによって上記絶縁樹脂層に囲まれて構成された可動子封装空間部内に上記可動子を臨ませる機能素子体組合せ実装工程と、上記各導電バンプを介して相対する上記各入出力電極と上記素子実装用ランドとを電気的かつ機械的に接続する入出力電極接続工程と、上記パッケージ基板の第2主面側から上記貫通孔を介して犠牲層除去剤を充填して上記犠牲層を除去する犠牲層除去工程と、上記貫通孔内に封止材を充填して上記貫通孔を閉塞する貫通孔封止工程とを有する

ことを特徴とする機能素子パッケージ体の製造方法。

【請求項5】

上記機能素子体が、微小電子機械部品(MEMS)や圧電薄膜共振素子或いは表面弾性波フィルタ素子やバルク弾性波フィルタ素子であることを特徴とする請求項4に記載の機能素子パッケージ体の製造方法。

【請求項6】

上記パッケージ基板の製作工程が、上記第1主面に上記各素子実装用ランドを形成する素子実装用ランド形成工程と、上記第2主面に多数個の実装用端子や所定の配線パターンを形成する実装用端子形成工程と、上記各素子実装用ランドと相対する上記各実装用端子或いは上記配線パターンとを層間接続するビアを形成するビア形成工程と、上記各実装用端子に導電バンプを設ける導電バンプ形成工程とを有し、

上記機能素子体の実装工程を経て、上記第2主面を実装面として実装用基板に実装されることを特徴とする請求項4に記載の機能素子パッケージ体の製造方法。

【請求項7】

上記パッケージ基板の製作工程が、上記素子実装用ランド形成工程の後工程として、少なくとも上記第1主面を平坦化する第1主面平坦化工程が施されることを特徴とする請求項6に記載の機能素子パッケージ体の製造方法。

【請求項8】

上記第1主面平坦化工程が、上記第1主面上に上記素子実装用ランドを被覆する厚みを有して段差を埋める平坦化樹脂層を全面に亘って形成する平坦化樹脂層形成工程と、上記平坦化樹脂層を研磨して上記各素子実装用ランドを露出させる研磨工程とが施されることを特徴とする請求項7に記載の機能素子パッケージ体の製造方法。

【請求項9】

上記絶縁樹脂層形成工程と上記開口部形成工程とが、感光性絶縁樹脂材を用いて上記電極形成面上に全面に亘って下地絶縁樹脂層を形成する工程と、上記下地絶縁樹脂層にリソグラフ処理を施して上記各入出力電極に跨り上記可動子を囲む枠状の絶縁樹脂層を形成するとともに上記各入出力電極をそれぞれ露出させる多数個の開口部を形成するリソグラフ工程とからなることを特徴とする請求項4に記載の機能素子パッケージ体の製造方法。

【請求項10】

上記絶縁樹脂層が、上記絶縁樹脂層形成工程において半硬化状態で形成され、上記入出力電極接続工程の後工程として施される絶縁樹脂層硬化工程によって、上記各入出力電極と上記素子実装用ランドとの接合部を包み込んで硬化されることを特徴とする請求項4に記載の機能素子パッケージ体の製造方法。

【請求項11】

上記機能素子体の実装工程が、真空雰囲気或いは還元ガス雰囲気で行われることによって、上記可動子封装空間部を真空雰囲気或いは還元ガス雰囲気に保持することを特徴とする請求項4に記載の機能素子パッケージ体の製造方法。

【請求項12】

上記機能素子体の実装工程が、上記入出力電極接続工程の後工程として、上記機能素子体の上記電極形成面と上記パッケージ基板の第1主面との間で上記絶縁樹脂層の外周部位に全周に亘って形成されて上記各入出力電極と上記素子実装用ランドとの接合部を補強する補強樹脂層を形成する補強樹脂層形成工程を有することを特徴とする請求項4に記載の機能素子パッケージ体の製造方法。

【請求項1】

第1主面上に多数個の素子実装用ランドを形成してこれら素子実装用ランドで囲まれた領域を素子体実装領域として構成し、上記各素子実装用ランドにそれぞれ設けた導電バンプと、上記素子体実装領域内に位置して第2主面に貫通して形成された貫通孔と、この貫通孔を閉塞する封止材層とを有するパッケージ基板と、

多数個の入出力電極と可動子とを設けた電極形成面に上記可動子を囲む枠状に形成されるとともに底部に上記各入出力電極をそれぞれ露出させる多数個の開口部が設けられた所定の厚みを有する絶縁樹脂層を形成した機能素子体とを備え、

上記機能素子体が、上記可動子を形成する犠牲層を残した状態で上記電極形成面を実装面として上記パッケージ基板の上記素子体実装領域に組み付けられ、上記導電バンプを介して相対する上記各入出力電極と上記各素子実装用ランドとがそれぞれ接続されることによって上記第1主面上に上記絶縁樹脂層で囲まれて構成された可動子封装空間部内に上記可動子を封装して実装され、

上記貫通孔が、上記機能素子体を上記パッケージ基板に実装した状態で上記第2主面側から上記犠牲層を除去する犠牲層除去孔として作用し、上記犠牲層を除去した後に上記封止材層によって閉塞されることを特徴とする機能素子パッケージ体。

【請求項2】

上記機能素子体が、微小電子機械部品(MEMS)や圧電薄膜共振素子或いは表面弾性波フィルタ素子やバルク弾性波フィルタ素子であることを特徴とする請求項1に記載の機能素子パッケージ体。

【請求項3】

上記パッケージ基板が、上記第1主面に上記各素子実装用ランドや所定の配線パターンを形成するとともに上記第2主面にビアを介して接続された多数個の実装用ランドや所定の配線パターンを形成し、

上記各実装用端子にそれぞれ導電バンプを設けた上記第2主面を実装面として実装用基板に実装されることを特徴とする請求項1に記載の機能素子パッケージ体。

【請求項4】

第1主面上に多数個の素子実装用ランドを形成してこれら素子実装用ランドによって囲まれた領域を素子体実装領域として構成してなるパッケージ基板に、可動子と多数個の入出力電極とを設けた電極形成面を実装面として機能素子体を上記素子体実装領域上に実装してなる機能素子パッケージ体の製造方法であり、

上記パッケージ基板の製作工程が、上記素子体実装領域内に位置して第1主面と第2主面とに貫通する貫通孔を形成する貫通孔形成工程と、上記各素子実装用ランド上にそれぞれ導電バンプを設ける導電バンプ形成工程とを有し、

上記機能素子体の製作工程が、素子基板の第1主面を電極形成面として多数個の入出力電極と犠牲層を残した可動子とを形成する素子形成工程と、上記各入出力電極を跨り上記可動子を囲む所定の厚みを有する枠状の絶縁樹脂層を形成する絶縁樹脂層形成工程と、上記絶縁樹脂層に対して底部に上記各入出力電極をそれぞれ露出させる多数個の開口部を形成する開口部形成工程とを有し、

上記パッケージ基板に対する上記機能素子体の実装工程が、上記電極形成面を実装面として、上記各開口部内にそれぞれ相対する上記各導電バンプを嵌合させて上記各導電バンプと上記各入出力電極とを接触させるように位置決めして組み合わせることによって上記絶縁樹脂層に囲まれて構成された可動子封装空間部内に上記可動子を臨ませる機能素子体組合せ実装工程と、上記各導電バンプを介して相対する上記各入出力電極と上記素子実装用ランドとを電気的かつ機械的に接続する入出力電極接続工程と、上記パッケージ基板の第2主面側から上記貫通孔を介して犠牲層除去剤を充填して上記犠牲層を除去する犠牲層除去工程と、上記貫通孔内に封止材を充填して上記貫通孔を閉塞する貫通孔封止工程とを有する

ことを特徴とする機能素子パッケージ体の製造方法。

【請求項5】

上記機能素子体が、微小電子機械部品(MEMS)や圧電薄膜共振素子或いは表面弾性波フィルタ素子やバルク弾性波フィルタ素子であることを特徴とする請求項4に記載の機能素子パッケージ体の製造方法。

【請求項6】

上記パッケージ基板の製作工程が、上記第1主面に上記各素子実装用ランドを形成する素子実装用ランド形成工程と、上記第2主面に多数個の実装用端子や所定の配線パターンを形成する実装用端子形成工程と、上記各素子実装用ランドと相対する上記各実装用端子或いは上記配線パターンとを層間接続するビアを形成するビア形成工程と、上記各実装用端子に導電バンプを設ける導電バンプ形成工程とを有し、

上記機能素子体の実装工程を経て、上記第2主面を実装面として実装用基板に実装されることを特徴とする請求項4に記載の機能素子パッケージ体の製造方法。

【請求項7】

上記パッケージ基板の製作工程が、上記素子実装用ランド形成工程の後工程として、少なくとも上記第1主面を平坦化する第1主面平坦化工程が施されることを特徴とする請求項6に記載の機能素子パッケージ体の製造方法。

【請求項8】

上記第1主面平坦化工程が、上記第1主面上に上記素子実装用ランドを被覆する厚みを有して段差を埋める平坦化樹脂層を全面に亘って形成する平坦化樹脂層形成工程と、上記平坦化樹脂層を研磨して上記各素子実装用ランドを露出させる研磨工程とが施されることを特徴とする請求項7に記載の機能素子パッケージ体の製造方法。

【請求項9】

上記絶縁樹脂層形成工程と上記開口部形成工程とが、感光性絶縁樹脂材を用いて上記電極形成面上に全面に亘って下地絶縁樹脂層を形成する工程と、上記下地絶縁樹脂層にリソグラフ処理を施して上記各入出力電極に跨り上記可動子を囲む枠状の絶縁樹脂層を形成するとともに上記各入出力電極をそれぞれ露出させる多数個の開口部を形成するリソグラフ工程とからなることを特徴とする請求項4に記載の機能素子パッケージ体の製造方法。

【請求項10】

上記絶縁樹脂層が、上記絶縁樹脂層形成工程において半硬化状態で形成され、上記入出力電極接続工程の後工程として施される絶縁樹脂層硬化工程によって、上記各入出力電極と上記素子実装用ランドとの接合部を包み込んで硬化されることを特徴とする請求項4に記載の機能素子パッケージ体の製造方法。

【請求項11】

上記機能素子体の実装工程が、真空雰囲気或いは還元ガス雰囲気で行われることによって、上記可動子封装空間部を真空雰囲気或いは還元ガス雰囲気に保持することを特徴とする請求項4に記載の機能素子パッケージ体の製造方法。

【請求項12】

上記機能素子体の実装工程が、上記入出力電極接続工程の後工程として、上記機能素子体の上記電極形成面と上記パッケージ基板の第1主面との間で上記絶縁樹脂層の外周部位に全周に亘って形成されて上記各入出力電極と上記素子実装用ランドとの接合部を補強する補強樹脂層を形成する補強樹脂層形成工程を有することを特徴とする請求項4に記載の機能素子パッケージ体の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2006−202918(P2006−202918A)

【公開日】平成18年8月3日(2006.8.3)

【国際特許分類】

【出願番号】特願2005−12024(P2005−12024)

【出願日】平成17年1月19日(2005.1.19)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成18年8月3日(2006.8.3)

【国際特許分類】

【出願日】平成17年1月19日(2005.1.19)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]