機能素子搭載方法及び機能素子搭載基板

【課題】Biを含有するはんだ接続部の放熱性を向上させ、Biが接続部の外部へ拡散し接続部にカーケンダルボイドが形成されることを防止して光素子等の機能素子の特性を向上させる。

【解決手段】機能素子1が搭載される基板2の主面側の、機能素子1が搭載される領域の少なくとも一部に第1の導体層5を形成し、第1の導体層5の少なくとも一部に第2の導体層6を形成する導体層形成工程と、第2の導体層6の少なくとも一部に凹凸形状状の第3の導体層8を形成し、第3の導体層8の少なくとも一部にはんだ9を形成し、第2の基板17を挟持し、はんだ9を溶融させて機能素子1を接続して搭載し、はんだ9が第3の凹凸状の導体層8により堰き止められて第1の導体層5に接しない接続工程を備えた機能素子搭載方法とする。

【解決手段】機能素子1が搭載される基板2の主面側の、機能素子1が搭載される領域の少なくとも一部に第1の導体層5を形成し、第1の導体層5の少なくとも一部に第2の導体層6を形成する導体層形成工程と、第2の導体層6の少なくとも一部に凹凸形状状の第3の導体層8を形成し、第3の導体層8の少なくとも一部にはんだ9を形成し、第2の基板17を挟持し、はんだ9を溶融させて機能素子1を接続して搭載し、はんだ9が第3の凹凸状の導体層8により堰き止められて第1の導体層5に接しない接続工程を備えた機能素子搭載方法とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子等の機能素子を導電層上にはんだが形成されたフレキシブル基板に接続して搭載する機能素子搭載方法および機能素子を搭載した機能素子搭載基板に関する。

【背景技術】

【0002】

従来の機能素子搭載方法としては、特許文献1及び特許文献2に記載の技術が知られている。特許文献1には、基板とこの基板上に形成され、半導体素子のパッドとバンプで接続される領域に凹凸部が形成された導電層とを備え、半導体素子は前記バンプが前記導電層の接続領域に接続されるように前記フリップチップ実装基板にマウント・ボンディングする半導体装置が記載されている。

【0003】

また、特許文献2には、半導体基板上に設けられた配線層と、前記配線層上に設けられた検査用電極パッドとを備え、前記検査用電極パッドは、バリアメタル層およびコンタクト層が積層した構造を有し、前記検査用電極パッドの表面に凹凸が設けられた半導体装置が記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2003−109987号公報

【特許文献2】特開2003−179112号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

近年、光素子等の機能素子を導電層及び、はんだが形成されたフレキシブル基板に実装する要求がある。フレキシブル基板とはプリント配線板の一種で、薄くて屈曲性がある。絶縁体には柔軟性の高いポリイミドや高周波特性の良い液晶ポリマを用い、片面、両面、多層のものがある。また、光導波路用のフレキシブル基板には導波路層が形成されており、マルチモードの前記導波路層の耐熱温度は160℃〜200℃程度である。この場合の課題としては、前記導波路層の耐熱温度が低いことから低融点の接続材料で接続する必要がある。また、機能素子から出る熱が大きくなることから、接続部の高い放熱性を確保する必要がある。

【0006】

本発明の目的は、上記課題を解決すべく、はんだ接続部において、はんだの良好な濡れ性を確保して放熱性を向上し、Biの接続部以外の導体層への拡散を防止することで光素子等の機能素子の特性を向上させた機能素子搭載方法および機能素子搭載基板搭載構造体を提供することにある。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本発明の機能素子搭載方法は、機能素子を、導体層を有する基板にはんだを用いて接続して搭載する機能素子搭載方法であって、前記機能素子が搭載される前記基板の主面側の、前記機能素子が搭載される領域の少なくとも一部に第1の導体層を形成する導体層形成工程と、前記第1の導体層の少なくとも一部に第2の導体層を形成する導体層形成工程と、前記第2の導体層の少なくとも一部に凹凸形状の第3の導体層を形成する導体層形成工程と、前記第3の導体層で、前記機能素子が接続される領域の最も外側に形成された凸部の最も高い箇所よりも、前記機能素子が接続される領域の内側の少なくとも一部にはんだを形成するはんだ形成工程と、前記はんだを溶融させて前記機能素子を前記基板の主面側の前記第3の導体層に接続して搭載する接続工程と、溶融させた前記はんだが前記第3の導体層により堰き止められて前記第1の導体層に接しない接続部を形成する接続工程と、を備え、前記接続部が前記第1の導体層に接しないことを特徴とする。

【0008】

また、本発明は、前記機能素子搭載方法において、前記機能素子の主面側の少なくとも一部に、前記接続工程において前記はんだと接続される第4の導体層を有することを特徴とする。

【0009】

また、本発明は、凹凸形状の前記第3の導体層を形成する導体層形成工程において、形成する凹凸形状の高さが、最も低い箇所では、第3の導体層が形成される基板や、導体層1および導体層2の表面粗さより明らかに高い2μm以上とし、最も高い箇所では、はんだの高さで最も高い10μmと同じ10μm以下とし、接続に関与するはんだの体積を十分確保することを特徴とする。

【0010】

また、本発明は、前記接続工程において、前記機能素子に予め形成されたAu層若しくはAuバンプを溶融した前記はんだに押し付けてAuとはんだ成分との反応により前記接続部を形成することを特徴とする。

【0011】

また、本発明は、凹凸形状の前記第3の導体層形成工程において、形成する凹凸形状の前記第3の導体層を構成する導体層7および導体層8が金属材料であることを特徴とする。

【0012】

また、本発明は、凹凸形状の前記第3の導体層形成工程において、前記第3の導体層を構成する材料がCuまたはCu合金、AlまたはAl合金、NiまたはNi合金の金属、またはAuまたはAu合金であることを特徴とする。

【0013】

また、本発明は、前記はんだ形成工程において、形成される前記はんだが、Bi−Sn、Sn−Ag−Bi、Sn−Zn−Bi、Sn―Ag―In―Bi、In−Bi等、Biが含まれるはんだであることを特徴とする。

【0014】

また、本発明は、前記はんだ形成工程において、形成される前記はんだが、Bi−SnはんだまたはSn−Ag−Biはんだであって、Biの濃度が21%以上99.9%以下であることを特徴とする。

【0015】

また、本発明は、前記はんだ形成工程において、形成されるBi−Sn、Sn−Ag−Bi、Sn−Zn−Bi、Sn―Ag―In―Bi、In−Bi等、Biが含まれるはんだ表面に、Ag、Au若しくはAgとAuを積層して構成される膜が形成されていることを特徴とする。

【0016】

また、本発明は、前記はんだ形成工程において、前記はんだの表面に、前記Ag、Au若しくはAgとAuを積層して構成される膜が蒸着、スパッタまたはめっきにより形成されることを特徴とする。

【0017】

また、本発明の方法に用いる基板は、前記機能素子をはんだにより接続される基板が耐熱温度200℃以下の有機材料を有するフレキシブル基板であることを特徴とする。

【0018】

また、本発明は、前記接続工程において接続された前記はんだが前記第3の導体層と接していないことを特徴とする。

【0019】

また、本発明の機能素子搭載方法では、前記機能素子と前記基板の間に第2の基板を挟持することを特徴とする。

【0020】

また、本発明の機能素子搭載基板は、導体層を有する基板にはんだを用いて機能素子を接続して搭載した機能素子搭載基板であって、前記機能素子が搭載される前記基板の主面側の、前記機能素子が搭載される領域の少なくとも一部に形成された第1の導体層と、前記第1の導体層の少なくとも一部に形成された第2の導体層と、前記第2の導体層の少なくとも一部に形成された凹凸形状の第3の導体層と、前記第3の導体層で、前記機能素子が接続される領域の最も外側に形成された凸部の最も高い箇所よりも、前記機能素子が接続される領域の内側の少なくとも一部に形成されたはんだと、前記はんだを溶融させ、前記機能素子が前記基板の主面側の前記第3の導体層に接続して搭載され、溶融させた前記はんだが前記第3の導体層により堰き止められて前記第1の導体層に接しない接続部と、を備え、前記接続部が前記第1の導体層に接しないことを特徴とする。

【0021】

また、本発明の機能素子搭載基板は、接続された前記はんだが前記第3の導体層と接していないことを特徴とする。

【0022】

また、本発明の機能素子搭載基板は、前記機能素子と前記基板の間に挟持された第2の基板を備えていることを特徴とする。

【0023】

また、本発明の機能素子搭載基板は、前記第2の基板の機能素子を搭載する面および前記基板と接する面の少なくとも一部に第4の導体層が形成されており、前記第4の導体層の少なくとも一部にはんだが形成されていることを特徴とする。

【0024】

また、本発明の機能素子搭載基板は、前記第2の基板の機能素子が接続される側に形成されているはんだの方が、機能素子を接続しない側に形成されているはんだより熱伝導率が高いことを特徴とする。

【0025】

また、本発明の機能素子搭載基板は、前記第2の基板の一部に貫通穴が開いていることを特徴とする。

【発明の効果】

【0026】

本発明によれば、比較的接続温度が低く、比較的熱伝導率が小さいSn−Biはんだ等を用いて機能素子と基板を接続した接続部の放熱性を向上することが可能となる。

【0027】

また、本発明によれば、機能素子と基板をSn−Biはんだ等を用いて接続後、接続部と基板上に形成され、接続部以外の領域まで続いて形成されている導電層が接することのないようにすることで、Biの導電層への拡散による接続部に形成されるカーケンダルボイドの形成を抑止することが可能となる。

【0028】

また、本発明によれば、基板上の凹凸形状の導電層により、機能素子との接続時にはんだ表面に形成されていた酸化膜を破り濡れの良い良好な接続を実現できる。

【0029】

また、本発明によれば、第2の基板を挟持することにより、機能素子と基板を接続した接続部の放熱性の向上と熱膨張率の違いを緩和することができる。

【0030】

また、本発明によれば、第2の基板に貫通穴を設けることにより、光素子等の機能素子からの光を第2の基板を通過させて第1の基板の導波路層に導くことができる。

【図面の簡単な説明】

【0031】

【図1】図1は本発明に係わる基本構造である機能素子1を基板2上に実装する前の状態を示す断面図である。

【図2】図2は本発明に係わる基本構造である機能素子1を基板2上に実装した状態を示す断面図である。

【図3】図3は本発明に係わる基本構造である機能素子1を基板2上に実装後、接続部とその周囲の領域にアンダーフィルを注入した状態を示す断面図である。

【図4】図4は本発明に係わる基本構造である機能素子1を基板2上に実装する前の状態の半分を拡大した断面図である。

【図5】図5は本発明に係わる基本構造である機能素子1を基板2上に実装する前の状態の半分を拡大した断面図である。

【図6】図6は本発明に係わる基本構造である機能素子1を基板2上に実装後の状態の半分を拡大した断面図である。

【図7】図7は本発明に係わる基本構造である機能素子1を基板2上に実装後の状態の半分を拡大した断面図である。

【図8】図8は本発明に係わる接続前の基板2側を平面的に上方より見た図である。

【図9】図9は本発明に係わる接続前の基板2側を平面的に上方より見た図である。

【図10】図10は本発明に係わるBi−Snはんだの組成範囲を説明するための二元平衡状態図である。

【図11】図11は本発明の実施例2について示す図である。

【図12】図12は本発明の実施例2について示す図である。

【図13】図13は本発明の実施例3について示す図である。

【図14】図14は本発明の実施例4について示す図である。

【図15】図15は本発明の実施例4について示す図である。

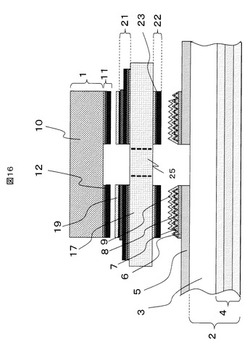

【図16】図16は本発明の実施例6の基板2上に基板17を接続し、基板17上に機能素子1を実装する前の断面図である。

【図17】図17は本発明の実施例6の機能素子1と基板2の間に挟持される基板17および基板17の主面に形成される導体層21、導体層22を斜方向から見た立体図である。

【図18】図18は本発明の実施例6の基板2上に基板17を接続し、基板17上に機能素子1を実装後に金属ワイヤーを形成した後の断面図である。

【図19】図19は本発明の実施例7ついて示す図である。

【図20】図20は本発明の実施例7ついて示す図である。

【図21】図21は本発明の実施例7ついて示す図である。

【発明を実施するための形態】

【0032】

以下、本発明に係わる機能素子搭載方法及び機能素子を基板に搭載した機能素子基板搭載構造体の実施の形態について、図1乃至図21を参照しながら説明する。

【実施例1】

【0033】

本発明に係わる第1の実施の形態である高出力でサイズの大きな光素子などの半導体チップ搭載用のフレキシブル基板について、図1乃至図10を用いて説明する。図1は、光素子などの機能素子1を基板2上に実装する前の断面図である。図2は光素子などの機能素子1を基板2上に実装した後の断面図である。図3は光素子などの機能素子1を基板2に実装後、アンダーフィルを接続部の周囲に流し込んだ図である。図4および図5は、図1の光素子などの機能素子1を基板2に接続する前の拡大図である。図6および図7は、図1の光素子などの機能素子1を基板2に接続した後の拡大図であり、図4と図6、図5と図7がそれぞれ対応する。図8および図9は、接続前の基板2側を平面的に上方より見た図である。

【0034】

機能素子1に例えばGaAsが主成分の面発光タイプの光素子(半導体レーザ)を用いた場合、基板2を構成する基材3にはポリイミドや液晶ポリマなどの樹脂を用い、導波路層4には、光導波路モードがマルチモード対応の場合UVエポキシ樹脂などの樹脂を用いるが、低光損失、高速光信号が伝送可能、良好な屈曲特性をもち、好適である。

【0035】

なお、光素子としてはGaAsに限定されるものではなく、GaNやInGaNなどにも適用可能である。そして、機能素子である光素子が搭載(実装)される基板2の主面側に外部から光素子へ送電すること、および光素子から発生する熱を放熱するために導体層5としてCuやAuおよびCuやAuで構成される金属で形成する。

【0036】

前記導体層5の主面に、機能素子である光素子が搭載される少なくとも一部に前記導体層5の主面の酸化防止のための導体層6が形成される。導体層6にはAuおよびNiと導体層5の主面側から順にNi,Au(以降Ni/Auと表記)の金属を用いることで酸化防止ができる。

【0037】

前記導体層6上に、機能素子である光素子が搭載される少なくとも一部に接続後の接続部の放熱性向上およびSn−Biはんだ等のBiが導体層5との接触を防止することを目的に、凹凸形状の導体層7としてCuおよびCu合金が形成される。

【0038】

凹凸形状の導体層7がCuで形成される場合、形成する凹凸形状の高さが、最も低い箇所では、基板3や、導体層5および導体層6の表面粗さより明らかに高い2μm以上とし、最も高い箇所では、はんだの高さで最も高い10μmと同じ10μm以下とすることで、接続に関与するはんだの体積を十分確保できる。

【0039】

ただし、導体層の種類はAlやAuおよびAgの金属でもよい。また、凹凸形状は四角形でも良いし、三角形でも良いし、2〜10μm程度の厚さである凹凸が形成されていればその断面形状によらず同様の効果を奏することができる。導体層7の少なくとも一部に、導体層7の主面の酸化防止を目的に導体層7の主面側から順にNi/Auなどの導体層8が形成される。

【0040】

導体層8がNi/Auで形成される場合、Niは0・05〜5μm程度、Auは0・05〜5μm程度の厚さとすることができる。ただし、導体層の種類、層の数はこれに限定されるものではない。さらに、導体層8の少なくとも一部にはんだ9が形成される。該はんだ9は薄膜はんだであることが必須である。

【0041】

その理由は、機能素子1が光素子の場合、(1)はんだが厚いと接続後のはんだの体積膨張や、接続後の原子の拡散が原因で接続部に体積移動が起こるため、光素子の位置ずれ量が大きくなり、光軸がずれてしまうこと、(2)溶融中に接続部外部へのはんだの流出量が増えることにより光素子の側面にはんだが付着し、光素子の特性が劣化してしまうこと、(3)熱伝導率が比較的低いはんだを薄くすることで高放熱性を得ることが挙げられる。なお、薄膜はんだ9の厚さは1μm〜10μm程度が好適である。

【0042】

なお、薄膜はんだ9の組成としては、後述するように例えばBi−Snはんだ(融点139℃)、またはSn−Ag−Biはんだ(融点138℃)、またはSn−Zn−Biはんだ(融点197℃)、またはSn―Ag―In―Biはんだ(融点205〜214)、またはIn−Bi−Snはんだ(融点60℃)等の共晶組成が好適であるが、必ずしも共晶組成に限定されるものではなく、共晶組成から多少ずれていても、望ましい接続状態が得られれば良い。

【0043】

機能素子1を構成する基板10の主面上に、主面側から順に密着層/拡散防止層/電極層としてのTi,Pt,Au(以降、Ti/Pt/Auと表記)やTi/Ni/Au、およびCr/Ni/Auなどの半導体チップ側導体層11が形成される。

【0044】

機能素子側導体層11がTi/Pt/Auで形成される場合、Tiは0.1μm程度、Ptは0.2μm程度、Auは0.05μm〜5μm程度の厚さとすることができる。ただし、導体層の種類、層の数、厚さはこれに限定されるものではなく、また機能素子側導体層11とは同じである必要はない。光素子を形成する基板10の主面上の導体層11の一部にAu層12が形成されている。このAu層8の厚さははんだ9との濡れ性を良好にするために、0.05μm〜5μm程度が好適である。

【0045】

ところで、図4および図5に示すように、接続前の、導体層8の主面の少なくとも一部に形成されているはんだ9は、凹凸形状の導体層7の中で機能素子1が接続される領域の最外部に形成された凸部より外側には形成しない。この様にはんだ9を形成することで図6および7に示すように、接続後の、接続部に存在するはんだ9の成分であるBiと導体層5が接することはない。

【0046】

接続部のはんだ9の成分であるBiと導体層5が接すると、はんだ9の成分であるBiが導体層5に拡散することで接続部のBiが存在する領域にカーケンダルボイドが形成され、接続部の接続強度や放熱性が低下する。

【0047】

接続部のはんだ9の成分であるBiと導体層5が接しないようにするために図8および図9のように基板2の主面側に形成された凹凸形状の導体層7および導体層8形成領域の、機能素子接続領域13に形成された凸部14のみ、導体層5側に面するように凹凸形状の向きが決められる。機能素子接続領域13に接する導体層5以外の領域は基板2を構成する基材3である。ここでの基材3は金属以外の屈曲性のよい材料であればよい。

【0048】

次に、本発明に係る基板2の主面側に形成される導電層形成プロセスの概略について説明する。まず、基板2を構成する基材3の主面に、電極となる基板側導体層5および6をフォトリソグラフィー技術を用いた半導体プロセスにより形成する。

【0049】

次に凹凸形状の導体層7の形成に移る。導体層7および導電層8の形成は、まず導体層5および6と同様にフォトリソグラフィー技術を用いた半導体プロセスにより導体層7および導電層8の凹凸形状を有していない状態を形成し、転写技術やナノインプリント技術や溶液を使ったウェットエッチングを適用することで凹凸形状を形成する。

【0050】

次に、はんだ9の形成に移る。はんだ9の形成は、蒸着、スパッタ、あるいはめっきなどを用いるが、大きく分けて二つのプロセスが適用できる。一つ目のプロセスはマスクパターンを形成した後に、はんだ部の形成を行い、余分なはんだ部を取り除くプロセスである。レジストパターンを用いたリフトオフや、メタルマスクを用いての成膜などが当てはまる。

【0051】

二つ目のプロセスは、先に蒸着、スパッタなどを用いてはんだ膜を成膜して、その上にマスクパターンを形成し、余分なはんだ膜をエッチングで除去するプロセスである。該除去プロセスとしては、ミリングなどのドライのエッチングや、溶液を使ったウェットエッチングを適用することができる。また、その他のプロセスとしては基板側導電層8上に、めっき法によりはんだ9を形成することも考えられる。

【0052】

本技術は、Biが混入した比較的低融点のはんだ(融点が200℃を超えないはんだ)に対し効果的である。比較的低融点のはんだを代表してSn−Bi薄膜はんだについて説明する。Sn−Biは接続温度が160℃〜200℃程度であり、融点の低い有機物を有する材料の接続に好適である。使用するSn−Biはんだは、共晶が含まれる組成範囲、すなわち、Bi濃度21wt%以上99.9wt%以下と規定する。

【0053】

図10は、Bi−Snの二元平衡状態図である。まず、Bi濃度21wt%以上とすることで、139℃で液相が生成することがわかる。次に、図10より139℃で溶融するBi−Sn共晶は、Biが99.9wt%まで存在することがわかる。接続温度は、融点の20℃〜40℃程度、多少高めならば50℃程度高い温度を選択するのが一般的である。

【0054】

したがって、139℃で溶融するBi−Snはんだならば、例えば160℃〜180℃、多少高めで200℃などが典型的な接続温度と言え、はんだの接続温度としては比較的低い。その結果、融点が低い有機材料を有する基板2の上に機能素子を接続することが可能となる。

【0055】

本発明は、接続後、図3に示すように接続部全体が樹脂15でモールドされていてもよいが、樹脂15でモールドすることが必須ではない。以上、機能素子が光素子で構成される場合について説明したが、光素子以外としてホトダイオードなどの機能素子全般に適用可能である。

【実施例2】

【0056】

次に本発明に係わる第2の実施の形態について図11および図12を用いて説明する。第2の実施の形態において、第1の実施形態と相違する点は、はんだ9を基板2側に形成せず、機能素子1を構成する基板10の主面上に形成にされた導体層11上に形成された場合である。導体層11の種類、層の数は第1の実施例で説明した通りである。このようにはんだ9を形成することで、接続時において、はんだ9の表面に酸化膜が形成されている場合、凹凸形状の導体層7および8により該酸化膜の少なくとも一部を突き破ることではんだ9の濡れ性が向上し、濡れの良い良好な接続部を得ることができる。また、このような第2の実施の形態においても、接続後、図12に示す通り接続部が導体層5と接することはない。

【実施例3】

【0057】

次に本発明に係わる第3の実施の形態について図13および図14を用いて説明する。第3の実施の形態において、第1の実施形態と相違する点は、基板2側に凹凸形状の導体層を形成せず、機能素子1側に形成された場合である。この場合、凹凸形状の導体層7および8は、導体層11上に形成され、はんだ9は導体層8上に形成される。これらの導体層の膜厚、層の数は第1の実施例で説明した通りである。

【0058】

接続時において、はんだ9の表面に酸化膜が形成されている場合、凹凸形状の導体層7および8により該酸化膜の少なくとも一部を突き破ることではんだ9の濡れ性が向上し、濡れの良い良好な接続部を得ることができる。また、このような第2の実施の形態においても、図14に示す通り、接続後、接続部が導体層5と接することはない。

【実施例4】

【0059】

次に本発明に係わる第4の実施の形態について図15を用いて説明する。第4の実施の形態において、第1乃至第3の実施形態と相違する点は、はんだ9を用いて接続する代わりに、バンプ形状のはんだまたは金属16を用いて接続する場合である。このような第4の実施の形態においても、接続時において、凹凸形状の導体層7および8により該酸化膜の少なくとも一部を突き破ることではんだ9の濡れ性が向上し、濡れの良い良好な接続部を得ることができる。また、接続後、接続部が導体層5と接することはない。

【実施例5】

【0060】

次に本発明に係わる第5の実施の形態について説明する。第5の実施の形態は、第1乃至4の実施の形態で説明したはんだ9の表面に、さらにAg膜あるいはAu膜が形成されており、Ag膜を形成する場合は、さらにAg膜の表面にAu膜が形成され、はんだ表面の酸化を防止している。Ag膜は0・1μm程度の厚さで、酸化防止能力を発揮し、特にノンフラックスの接続プロセスに有効な技術である。ただし、Ag膜あるいはAu膜の形成は必須ではない。例えば、フラックスが使える場合や、はんだ表面の酸化防止をしなくても良好な接続ができる場合など、Ag膜あるいはAu膜の形成が必要ないこともある。

【0061】

以上説明したように、第5の実施の形態によれば、はんだの濡れ性を向上させるはたらきのあるフラックスをはんだに塗布することもフラックスを洗浄することも必要ないため、フラックスによる光素子などの機能素子が特性劣化を起こす懸念も、フラックス残渣によって配線部を腐食させて電子部品が故障することも防止することが可能となる。

【実施例6】

【0062】

次に本発明に係わる第6の実施の形態について、図16乃至図18を用いて説明する。図16は、基板2上に基板17を接続し、基板17上に機能素子1を実装する前の断面図である。

【0063】

図17は、機能素子1と基板2の間に挟持される基板17および基板17の主面に形成される導体層21、導体層22を斜方向から見た立体図である。

【0064】

図18は、基板2上に基板17を接続し、基板17上に機能素子1を実装後に金属ワイヤーを形成した後の断面図である。第6の実施の形態において、第1乃至4の実施の形態と相違する点は、機能素子1と基板2の間に基板17を挟持し、基板17の片面に機能素子1を接続し、基板17の面のうち、機能素子1を接続する面と反対向きの面に基板2を接続する場合である。

【0065】

基板17の機能素子1と接続する側の主面の一部に導体層21を形成し、導体層21の少なくとも一部にはんだ19を形成する。基板17の基板2を接続する側の主面の一部に導体層22を形成する。

【0066】

基板17の機能素子を接続する側の主面には、主面側から順に密着層/拡散防止層/電極層/拡散防止層/電極層としてのTi/Pt/Au/Pt/AuやTi/Ni/Au/Pt/Au、Ti/Ni/Au/Ni/Au、Cr/Ni/Au/Pt/Au、Cr/Ni/Au/Ni/Auなどの半導体チップ側導体層21が形成される。

【0067】

機能素子側導体層21がTi/Pt/Au/Pt/Auで形成される場合、Tiは0.1μm程度、Ptは0.2μm〜0.4μm程度、Auは0.05μm〜5μm程度の厚さとすることができる。ただし、導体層の種類、層の数、厚さはこれに限定されるものではない。基板2側導体層22は、実施例1の導体層11と同じ種類、層である。導体層21の主面に形成されるはんだ19には、熱伝導率がはんだ9以上のはんだを使う。導体層5、6、7、8、および11、はんだ9の種類、層の数は第1の実施例で説明した通りである。

【0068】

図17に示すように、第6の実施の形態では、機能素子1と基板2の間に挟持する基板17の一部に貫通穴25が施されている。

【0069】

図18に示すように基板2上に基板17を接続し、基板17上に機能素子1を接続後に金属ワイヤー24で基板2の主面に形成された導体層5と基板17の主面に形成された導体層21の導通を確保する。金属ワイヤーにはAuを用いるが、Au以外にAlやCuを使ってもよい。

【0070】

本発明に係わる第6の実施の形態では、第2の基板を挟持することにより、機能素子と基板を接続した接続部の放熱性の向上と熱膨張率の違いの緩和を図ることができる。

【0071】

また、本発明に係わる第6の実施の形態では、第2の基板17に貫通穴25を設けることにより、光素子等の機能素子1からの光を第2の基板17を通過させて第1の基板2の導波路層4に導くことができる。

【実施例7】

【0072】

次に本発明に係わる第7の実施の形態について、図19乃至21を用いて説明する。図19は、基板2上に基板17を接続し、基板17上に機能素子1を実装する前の断面図である。

【0073】

図20は、機能素子1と基板2の間に挟持され、貫通穴を施された基板17および基板17の主面に形成される導体層18を斜方向から見た立体図である。

【0074】

図21は、基板2上に基板17を接続し、基板17上に機能素子1を実装後の断面図である。第7の実施の形態においては、第6の実施の形態と同様に、機能素子1と基板2の間に挟持する基板17の一部に貫通穴25が施されており、第6の実施の形態と相違する点は、基板17の主面に形成される導体層18が基板17の機能素子1を接続する面から側面まで連続し、さらに側面から基板2を接続する面に連続することである。

【0075】

導体層18は、実施例1の導体層11と同じ種類、層である。導体層21の主面に形成されるはんだ19には、熱伝導率がはんだ9以上のはんだを使う。導体層5、6、7、8、および11、はんだ9の種類、層の数は第1の実施例で説明した通りである。基板17の一部に施される貫通穴25の形状は円状でも三角形でも四角形等の多角形でもよく、その大きさに制限はなく、基板17の面内に収まればよい。

【0076】

本発明に係わる第7の実施の形態では、第2の基板17を挟持することにより、機能素子1と基板2を接続した接続部の放熱性の向上と熱膨張率の違いの緩和を図ることができる。

【0077】

また、本発明に係わる第7の実施の形態では、第2の基板17に貫通穴25を設けることにより、光素子等の機能素子1からの光を第2の基板17を通過させて第1の基板2の導波路層4に導くことができる。

【産業上の利用可能性】

【0078】

本発明は、比較的接続温度が低く、比較的熱伝導率が小さいSn−Biはんだ等を用いて機能素子と基板を接続した接続部の放熱性を向上することが可能となる。

【0079】

また、本発明によれば、機能素子と基板をSn−Biはんだ等を用いて接続後、接続部と基板上に形成され、接続部以外の領域まで続いて形成されている導電層が接することのないようにすることで、Biの導電層への拡散による接続部に形成されるカーケンダルボイドの形成を抑止することが可能となる。

【0080】

また、本発明によれば、基板上の凹凸形状の導電層により、機能素子との接続時にはんだ表面に形成されていた酸化膜を破り濡れの良い良好な接続を実現するものである。本発明は、特に以下の分野に適用できる可能性がある。

【0081】

融点が低い有機材料を含む基板の上に機能素子を接続する場合、Au−Snなどのはんだなどの接続温度が300℃程度のはんだは、有機材料が劣化してしまうため使えない。

【0082】

そこで候補となる実施例が、比較的接続温度の低いSn−Biはんだである。Sn−Biは、Au−Snはんだに比べ放熱性が悪い。また、Sn−Biはんだで接続する場合、接続部がCuやAuの金属と接していると、接続部のBiが接続部の外へ拡散してしまい、Biが存在していた領域にカーケンダルボイドが形成されてしまう。

【0083】

そこで、Sn−Biはんだより放熱性のよい凹凸形状の導体層を形成し、接続部に占めるSn−Biはんだの割合を減らすことで放熱性を向上させ、凹凸形状の導体層により接続部とCuやAuの金属が接することのないようにすることで、放熱性が良く、良好な接続部を得ることができる。この様に、比較的低温で接続する必要があるときに必要になる技術である。

【符号の説明】

【0084】

1 機能素子

2 基板

3 基板2を構成する基材

4 導波路層

5 第1の導体層(基板2側)

6 第2の導体層(基板2側)

7 凹凸形状の第3の導体層(1)

8 凹凸形状の第3の導体層(2)

9 はんだ

10 基板(機能素子側)

11 導体層(機能素子側)

12 Au層

13 機能素子接続領域

14 第1の導体層と唯一接する凸部

15 樹脂

16 バンプ

17 第二の基板

18 導体層

19 はんだ

21 導体層(機能素子側)

22 導体層(基板2側)

23 Au層

24 金属ワイヤー

25 貫通穴

201 Bi−Sn共存領域

202 Sn/液相共存領域

203 Bi/液相共存領域

【技術分野】

【0001】

本発明は、半導体素子等の機能素子を導電層上にはんだが形成されたフレキシブル基板に接続して搭載する機能素子搭載方法および機能素子を搭載した機能素子搭載基板に関する。

【背景技術】

【0002】

従来の機能素子搭載方法としては、特許文献1及び特許文献2に記載の技術が知られている。特許文献1には、基板とこの基板上に形成され、半導体素子のパッドとバンプで接続される領域に凹凸部が形成された導電層とを備え、半導体素子は前記バンプが前記導電層の接続領域に接続されるように前記フリップチップ実装基板にマウント・ボンディングする半導体装置が記載されている。

【0003】

また、特許文献2には、半導体基板上に設けられた配線層と、前記配線層上に設けられた検査用電極パッドとを備え、前記検査用電極パッドは、バリアメタル層およびコンタクト層が積層した構造を有し、前記検査用電極パッドの表面に凹凸が設けられた半導体装置が記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2003−109987号公報

【特許文献2】特開2003−179112号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

近年、光素子等の機能素子を導電層及び、はんだが形成されたフレキシブル基板に実装する要求がある。フレキシブル基板とはプリント配線板の一種で、薄くて屈曲性がある。絶縁体には柔軟性の高いポリイミドや高周波特性の良い液晶ポリマを用い、片面、両面、多層のものがある。また、光導波路用のフレキシブル基板には導波路層が形成されており、マルチモードの前記導波路層の耐熱温度は160℃〜200℃程度である。この場合の課題としては、前記導波路層の耐熱温度が低いことから低融点の接続材料で接続する必要がある。また、機能素子から出る熱が大きくなることから、接続部の高い放熱性を確保する必要がある。

【0006】

本発明の目的は、上記課題を解決すべく、はんだ接続部において、はんだの良好な濡れ性を確保して放熱性を向上し、Biの接続部以外の導体層への拡散を防止することで光素子等の機能素子の特性を向上させた機能素子搭載方法および機能素子搭載基板搭載構造体を提供することにある。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本発明の機能素子搭載方法は、機能素子を、導体層を有する基板にはんだを用いて接続して搭載する機能素子搭載方法であって、前記機能素子が搭載される前記基板の主面側の、前記機能素子が搭載される領域の少なくとも一部に第1の導体層を形成する導体層形成工程と、前記第1の導体層の少なくとも一部に第2の導体層を形成する導体層形成工程と、前記第2の導体層の少なくとも一部に凹凸形状の第3の導体層を形成する導体層形成工程と、前記第3の導体層で、前記機能素子が接続される領域の最も外側に形成された凸部の最も高い箇所よりも、前記機能素子が接続される領域の内側の少なくとも一部にはんだを形成するはんだ形成工程と、前記はんだを溶融させて前記機能素子を前記基板の主面側の前記第3の導体層に接続して搭載する接続工程と、溶融させた前記はんだが前記第3の導体層により堰き止められて前記第1の導体層に接しない接続部を形成する接続工程と、を備え、前記接続部が前記第1の導体層に接しないことを特徴とする。

【0008】

また、本発明は、前記機能素子搭載方法において、前記機能素子の主面側の少なくとも一部に、前記接続工程において前記はんだと接続される第4の導体層を有することを特徴とする。

【0009】

また、本発明は、凹凸形状の前記第3の導体層を形成する導体層形成工程において、形成する凹凸形状の高さが、最も低い箇所では、第3の導体層が形成される基板や、導体層1および導体層2の表面粗さより明らかに高い2μm以上とし、最も高い箇所では、はんだの高さで最も高い10μmと同じ10μm以下とし、接続に関与するはんだの体積を十分確保することを特徴とする。

【0010】

また、本発明は、前記接続工程において、前記機能素子に予め形成されたAu層若しくはAuバンプを溶融した前記はんだに押し付けてAuとはんだ成分との反応により前記接続部を形成することを特徴とする。

【0011】

また、本発明は、凹凸形状の前記第3の導体層形成工程において、形成する凹凸形状の前記第3の導体層を構成する導体層7および導体層8が金属材料であることを特徴とする。

【0012】

また、本発明は、凹凸形状の前記第3の導体層形成工程において、前記第3の導体層を構成する材料がCuまたはCu合金、AlまたはAl合金、NiまたはNi合金の金属、またはAuまたはAu合金であることを特徴とする。

【0013】

また、本発明は、前記はんだ形成工程において、形成される前記はんだが、Bi−Sn、Sn−Ag−Bi、Sn−Zn−Bi、Sn―Ag―In―Bi、In−Bi等、Biが含まれるはんだであることを特徴とする。

【0014】

また、本発明は、前記はんだ形成工程において、形成される前記はんだが、Bi−SnはんだまたはSn−Ag−Biはんだであって、Biの濃度が21%以上99.9%以下であることを特徴とする。

【0015】

また、本発明は、前記はんだ形成工程において、形成されるBi−Sn、Sn−Ag−Bi、Sn−Zn−Bi、Sn―Ag―In―Bi、In−Bi等、Biが含まれるはんだ表面に、Ag、Au若しくはAgとAuを積層して構成される膜が形成されていることを特徴とする。

【0016】

また、本発明は、前記はんだ形成工程において、前記はんだの表面に、前記Ag、Au若しくはAgとAuを積層して構成される膜が蒸着、スパッタまたはめっきにより形成されることを特徴とする。

【0017】

また、本発明の方法に用いる基板は、前記機能素子をはんだにより接続される基板が耐熱温度200℃以下の有機材料を有するフレキシブル基板であることを特徴とする。

【0018】

また、本発明は、前記接続工程において接続された前記はんだが前記第3の導体層と接していないことを特徴とする。

【0019】

また、本発明の機能素子搭載方法では、前記機能素子と前記基板の間に第2の基板を挟持することを特徴とする。

【0020】

また、本発明の機能素子搭載基板は、導体層を有する基板にはんだを用いて機能素子を接続して搭載した機能素子搭載基板であって、前記機能素子が搭載される前記基板の主面側の、前記機能素子が搭載される領域の少なくとも一部に形成された第1の導体層と、前記第1の導体層の少なくとも一部に形成された第2の導体層と、前記第2の導体層の少なくとも一部に形成された凹凸形状の第3の導体層と、前記第3の導体層で、前記機能素子が接続される領域の最も外側に形成された凸部の最も高い箇所よりも、前記機能素子が接続される領域の内側の少なくとも一部に形成されたはんだと、前記はんだを溶融させ、前記機能素子が前記基板の主面側の前記第3の導体層に接続して搭載され、溶融させた前記はんだが前記第3の導体層により堰き止められて前記第1の導体層に接しない接続部と、を備え、前記接続部が前記第1の導体層に接しないことを特徴とする。

【0021】

また、本発明の機能素子搭載基板は、接続された前記はんだが前記第3の導体層と接していないことを特徴とする。

【0022】

また、本発明の機能素子搭載基板は、前記機能素子と前記基板の間に挟持された第2の基板を備えていることを特徴とする。

【0023】

また、本発明の機能素子搭載基板は、前記第2の基板の機能素子を搭載する面および前記基板と接する面の少なくとも一部に第4の導体層が形成されており、前記第4の導体層の少なくとも一部にはんだが形成されていることを特徴とする。

【0024】

また、本発明の機能素子搭載基板は、前記第2の基板の機能素子が接続される側に形成されているはんだの方が、機能素子を接続しない側に形成されているはんだより熱伝導率が高いことを特徴とする。

【0025】

また、本発明の機能素子搭載基板は、前記第2の基板の一部に貫通穴が開いていることを特徴とする。

【発明の効果】

【0026】

本発明によれば、比較的接続温度が低く、比較的熱伝導率が小さいSn−Biはんだ等を用いて機能素子と基板を接続した接続部の放熱性を向上することが可能となる。

【0027】

また、本発明によれば、機能素子と基板をSn−Biはんだ等を用いて接続後、接続部と基板上に形成され、接続部以外の領域まで続いて形成されている導電層が接することのないようにすることで、Biの導電層への拡散による接続部に形成されるカーケンダルボイドの形成を抑止することが可能となる。

【0028】

また、本発明によれば、基板上の凹凸形状の導電層により、機能素子との接続時にはんだ表面に形成されていた酸化膜を破り濡れの良い良好な接続を実現できる。

【0029】

また、本発明によれば、第2の基板を挟持することにより、機能素子と基板を接続した接続部の放熱性の向上と熱膨張率の違いを緩和することができる。

【0030】

また、本発明によれば、第2の基板に貫通穴を設けることにより、光素子等の機能素子からの光を第2の基板を通過させて第1の基板の導波路層に導くことができる。

【図面の簡単な説明】

【0031】

【図1】図1は本発明に係わる基本構造である機能素子1を基板2上に実装する前の状態を示す断面図である。

【図2】図2は本発明に係わる基本構造である機能素子1を基板2上に実装した状態を示す断面図である。

【図3】図3は本発明に係わる基本構造である機能素子1を基板2上に実装後、接続部とその周囲の領域にアンダーフィルを注入した状態を示す断面図である。

【図4】図4は本発明に係わる基本構造である機能素子1を基板2上に実装する前の状態の半分を拡大した断面図である。

【図5】図5は本発明に係わる基本構造である機能素子1を基板2上に実装する前の状態の半分を拡大した断面図である。

【図6】図6は本発明に係わる基本構造である機能素子1を基板2上に実装後の状態の半分を拡大した断面図である。

【図7】図7は本発明に係わる基本構造である機能素子1を基板2上に実装後の状態の半分を拡大した断面図である。

【図8】図8は本発明に係わる接続前の基板2側を平面的に上方より見た図である。

【図9】図9は本発明に係わる接続前の基板2側を平面的に上方より見た図である。

【図10】図10は本発明に係わるBi−Snはんだの組成範囲を説明するための二元平衡状態図である。

【図11】図11は本発明の実施例2について示す図である。

【図12】図12は本発明の実施例2について示す図である。

【図13】図13は本発明の実施例3について示す図である。

【図14】図14は本発明の実施例4について示す図である。

【図15】図15は本発明の実施例4について示す図である。

【図16】図16は本発明の実施例6の基板2上に基板17を接続し、基板17上に機能素子1を実装する前の断面図である。

【図17】図17は本発明の実施例6の機能素子1と基板2の間に挟持される基板17および基板17の主面に形成される導体層21、導体層22を斜方向から見た立体図である。

【図18】図18は本発明の実施例6の基板2上に基板17を接続し、基板17上に機能素子1を実装後に金属ワイヤーを形成した後の断面図である。

【図19】図19は本発明の実施例7ついて示す図である。

【図20】図20は本発明の実施例7ついて示す図である。

【図21】図21は本発明の実施例7ついて示す図である。

【発明を実施するための形態】

【0032】

以下、本発明に係わる機能素子搭載方法及び機能素子を基板に搭載した機能素子基板搭載構造体の実施の形態について、図1乃至図21を参照しながら説明する。

【実施例1】

【0033】

本発明に係わる第1の実施の形態である高出力でサイズの大きな光素子などの半導体チップ搭載用のフレキシブル基板について、図1乃至図10を用いて説明する。図1は、光素子などの機能素子1を基板2上に実装する前の断面図である。図2は光素子などの機能素子1を基板2上に実装した後の断面図である。図3は光素子などの機能素子1を基板2に実装後、アンダーフィルを接続部の周囲に流し込んだ図である。図4および図5は、図1の光素子などの機能素子1を基板2に接続する前の拡大図である。図6および図7は、図1の光素子などの機能素子1を基板2に接続した後の拡大図であり、図4と図6、図5と図7がそれぞれ対応する。図8および図9は、接続前の基板2側を平面的に上方より見た図である。

【0034】

機能素子1に例えばGaAsが主成分の面発光タイプの光素子(半導体レーザ)を用いた場合、基板2を構成する基材3にはポリイミドや液晶ポリマなどの樹脂を用い、導波路層4には、光導波路モードがマルチモード対応の場合UVエポキシ樹脂などの樹脂を用いるが、低光損失、高速光信号が伝送可能、良好な屈曲特性をもち、好適である。

【0035】

なお、光素子としてはGaAsに限定されるものではなく、GaNやInGaNなどにも適用可能である。そして、機能素子である光素子が搭載(実装)される基板2の主面側に外部から光素子へ送電すること、および光素子から発生する熱を放熱するために導体層5としてCuやAuおよびCuやAuで構成される金属で形成する。

【0036】

前記導体層5の主面に、機能素子である光素子が搭載される少なくとも一部に前記導体層5の主面の酸化防止のための導体層6が形成される。導体層6にはAuおよびNiと導体層5の主面側から順にNi,Au(以降Ni/Auと表記)の金属を用いることで酸化防止ができる。

【0037】

前記導体層6上に、機能素子である光素子が搭載される少なくとも一部に接続後の接続部の放熱性向上およびSn−Biはんだ等のBiが導体層5との接触を防止することを目的に、凹凸形状の導体層7としてCuおよびCu合金が形成される。

【0038】

凹凸形状の導体層7がCuで形成される場合、形成する凹凸形状の高さが、最も低い箇所では、基板3や、導体層5および導体層6の表面粗さより明らかに高い2μm以上とし、最も高い箇所では、はんだの高さで最も高い10μmと同じ10μm以下とすることで、接続に関与するはんだの体積を十分確保できる。

【0039】

ただし、導体層の種類はAlやAuおよびAgの金属でもよい。また、凹凸形状は四角形でも良いし、三角形でも良いし、2〜10μm程度の厚さである凹凸が形成されていればその断面形状によらず同様の効果を奏することができる。導体層7の少なくとも一部に、導体層7の主面の酸化防止を目的に導体層7の主面側から順にNi/Auなどの導体層8が形成される。

【0040】

導体層8がNi/Auで形成される場合、Niは0・05〜5μm程度、Auは0・05〜5μm程度の厚さとすることができる。ただし、導体層の種類、層の数はこれに限定されるものではない。さらに、導体層8の少なくとも一部にはんだ9が形成される。該はんだ9は薄膜はんだであることが必須である。

【0041】

その理由は、機能素子1が光素子の場合、(1)はんだが厚いと接続後のはんだの体積膨張や、接続後の原子の拡散が原因で接続部に体積移動が起こるため、光素子の位置ずれ量が大きくなり、光軸がずれてしまうこと、(2)溶融中に接続部外部へのはんだの流出量が増えることにより光素子の側面にはんだが付着し、光素子の特性が劣化してしまうこと、(3)熱伝導率が比較的低いはんだを薄くすることで高放熱性を得ることが挙げられる。なお、薄膜はんだ9の厚さは1μm〜10μm程度が好適である。

【0042】

なお、薄膜はんだ9の組成としては、後述するように例えばBi−Snはんだ(融点139℃)、またはSn−Ag−Biはんだ(融点138℃)、またはSn−Zn−Biはんだ(融点197℃)、またはSn―Ag―In―Biはんだ(融点205〜214)、またはIn−Bi−Snはんだ(融点60℃)等の共晶組成が好適であるが、必ずしも共晶組成に限定されるものではなく、共晶組成から多少ずれていても、望ましい接続状態が得られれば良い。

【0043】

機能素子1を構成する基板10の主面上に、主面側から順に密着層/拡散防止層/電極層としてのTi,Pt,Au(以降、Ti/Pt/Auと表記)やTi/Ni/Au、およびCr/Ni/Auなどの半導体チップ側導体層11が形成される。

【0044】

機能素子側導体層11がTi/Pt/Auで形成される場合、Tiは0.1μm程度、Ptは0.2μm程度、Auは0.05μm〜5μm程度の厚さとすることができる。ただし、導体層の種類、層の数、厚さはこれに限定されるものではなく、また機能素子側導体層11とは同じである必要はない。光素子を形成する基板10の主面上の導体層11の一部にAu層12が形成されている。このAu層8の厚さははんだ9との濡れ性を良好にするために、0.05μm〜5μm程度が好適である。

【0045】

ところで、図4および図5に示すように、接続前の、導体層8の主面の少なくとも一部に形成されているはんだ9は、凹凸形状の導体層7の中で機能素子1が接続される領域の最外部に形成された凸部より外側には形成しない。この様にはんだ9を形成することで図6および7に示すように、接続後の、接続部に存在するはんだ9の成分であるBiと導体層5が接することはない。

【0046】

接続部のはんだ9の成分であるBiと導体層5が接すると、はんだ9の成分であるBiが導体層5に拡散することで接続部のBiが存在する領域にカーケンダルボイドが形成され、接続部の接続強度や放熱性が低下する。

【0047】

接続部のはんだ9の成分であるBiと導体層5が接しないようにするために図8および図9のように基板2の主面側に形成された凹凸形状の導体層7および導体層8形成領域の、機能素子接続領域13に形成された凸部14のみ、導体層5側に面するように凹凸形状の向きが決められる。機能素子接続領域13に接する導体層5以外の領域は基板2を構成する基材3である。ここでの基材3は金属以外の屈曲性のよい材料であればよい。

【0048】

次に、本発明に係る基板2の主面側に形成される導電層形成プロセスの概略について説明する。まず、基板2を構成する基材3の主面に、電極となる基板側導体層5および6をフォトリソグラフィー技術を用いた半導体プロセスにより形成する。

【0049】

次に凹凸形状の導体層7の形成に移る。導体層7および導電層8の形成は、まず導体層5および6と同様にフォトリソグラフィー技術を用いた半導体プロセスにより導体層7および導電層8の凹凸形状を有していない状態を形成し、転写技術やナノインプリント技術や溶液を使ったウェットエッチングを適用することで凹凸形状を形成する。

【0050】

次に、はんだ9の形成に移る。はんだ9の形成は、蒸着、スパッタ、あるいはめっきなどを用いるが、大きく分けて二つのプロセスが適用できる。一つ目のプロセスはマスクパターンを形成した後に、はんだ部の形成を行い、余分なはんだ部を取り除くプロセスである。レジストパターンを用いたリフトオフや、メタルマスクを用いての成膜などが当てはまる。

【0051】

二つ目のプロセスは、先に蒸着、スパッタなどを用いてはんだ膜を成膜して、その上にマスクパターンを形成し、余分なはんだ膜をエッチングで除去するプロセスである。該除去プロセスとしては、ミリングなどのドライのエッチングや、溶液を使ったウェットエッチングを適用することができる。また、その他のプロセスとしては基板側導電層8上に、めっき法によりはんだ9を形成することも考えられる。

【0052】

本技術は、Biが混入した比較的低融点のはんだ(融点が200℃を超えないはんだ)に対し効果的である。比較的低融点のはんだを代表してSn−Bi薄膜はんだについて説明する。Sn−Biは接続温度が160℃〜200℃程度であり、融点の低い有機物を有する材料の接続に好適である。使用するSn−Biはんだは、共晶が含まれる組成範囲、すなわち、Bi濃度21wt%以上99.9wt%以下と規定する。

【0053】

図10は、Bi−Snの二元平衡状態図である。まず、Bi濃度21wt%以上とすることで、139℃で液相が生成することがわかる。次に、図10より139℃で溶融するBi−Sn共晶は、Biが99.9wt%まで存在することがわかる。接続温度は、融点の20℃〜40℃程度、多少高めならば50℃程度高い温度を選択するのが一般的である。

【0054】

したがって、139℃で溶融するBi−Snはんだならば、例えば160℃〜180℃、多少高めで200℃などが典型的な接続温度と言え、はんだの接続温度としては比較的低い。その結果、融点が低い有機材料を有する基板2の上に機能素子を接続することが可能となる。

【0055】

本発明は、接続後、図3に示すように接続部全体が樹脂15でモールドされていてもよいが、樹脂15でモールドすることが必須ではない。以上、機能素子が光素子で構成される場合について説明したが、光素子以外としてホトダイオードなどの機能素子全般に適用可能である。

【実施例2】

【0056】

次に本発明に係わる第2の実施の形態について図11および図12を用いて説明する。第2の実施の形態において、第1の実施形態と相違する点は、はんだ9を基板2側に形成せず、機能素子1を構成する基板10の主面上に形成にされた導体層11上に形成された場合である。導体層11の種類、層の数は第1の実施例で説明した通りである。このようにはんだ9を形成することで、接続時において、はんだ9の表面に酸化膜が形成されている場合、凹凸形状の導体層7および8により該酸化膜の少なくとも一部を突き破ることではんだ9の濡れ性が向上し、濡れの良い良好な接続部を得ることができる。また、このような第2の実施の形態においても、接続後、図12に示す通り接続部が導体層5と接することはない。

【実施例3】

【0057】

次に本発明に係わる第3の実施の形態について図13および図14を用いて説明する。第3の実施の形態において、第1の実施形態と相違する点は、基板2側に凹凸形状の導体層を形成せず、機能素子1側に形成された場合である。この場合、凹凸形状の導体層7および8は、導体層11上に形成され、はんだ9は導体層8上に形成される。これらの導体層の膜厚、層の数は第1の実施例で説明した通りである。

【0058】

接続時において、はんだ9の表面に酸化膜が形成されている場合、凹凸形状の導体層7および8により該酸化膜の少なくとも一部を突き破ることではんだ9の濡れ性が向上し、濡れの良い良好な接続部を得ることができる。また、このような第2の実施の形態においても、図14に示す通り、接続後、接続部が導体層5と接することはない。

【実施例4】

【0059】

次に本発明に係わる第4の実施の形態について図15を用いて説明する。第4の実施の形態において、第1乃至第3の実施形態と相違する点は、はんだ9を用いて接続する代わりに、バンプ形状のはんだまたは金属16を用いて接続する場合である。このような第4の実施の形態においても、接続時において、凹凸形状の導体層7および8により該酸化膜の少なくとも一部を突き破ることではんだ9の濡れ性が向上し、濡れの良い良好な接続部を得ることができる。また、接続後、接続部が導体層5と接することはない。

【実施例5】

【0060】

次に本発明に係わる第5の実施の形態について説明する。第5の実施の形態は、第1乃至4の実施の形態で説明したはんだ9の表面に、さらにAg膜あるいはAu膜が形成されており、Ag膜を形成する場合は、さらにAg膜の表面にAu膜が形成され、はんだ表面の酸化を防止している。Ag膜は0・1μm程度の厚さで、酸化防止能力を発揮し、特にノンフラックスの接続プロセスに有効な技術である。ただし、Ag膜あるいはAu膜の形成は必須ではない。例えば、フラックスが使える場合や、はんだ表面の酸化防止をしなくても良好な接続ができる場合など、Ag膜あるいはAu膜の形成が必要ないこともある。

【0061】

以上説明したように、第5の実施の形態によれば、はんだの濡れ性を向上させるはたらきのあるフラックスをはんだに塗布することもフラックスを洗浄することも必要ないため、フラックスによる光素子などの機能素子が特性劣化を起こす懸念も、フラックス残渣によって配線部を腐食させて電子部品が故障することも防止することが可能となる。

【実施例6】

【0062】

次に本発明に係わる第6の実施の形態について、図16乃至図18を用いて説明する。図16は、基板2上に基板17を接続し、基板17上に機能素子1を実装する前の断面図である。

【0063】

図17は、機能素子1と基板2の間に挟持される基板17および基板17の主面に形成される導体層21、導体層22を斜方向から見た立体図である。

【0064】

図18は、基板2上に基板17を接続し、基板17上に機能素子1を実装後に金属ワイヤーを形成した後の断面図である。第6の実施の形態において、第1乃至4の実施の形態と相違する点は、機能素子1と基板2の間に基板17を挟持し、基板17の片面に機能素子1を接続し、基板17の面のうち、機能素子1を接続する面と反対向きの面に基板2を接続する場合である。

【0065】

基板17の機能素子1と接続する側の主面の一部に導体層21を形成し、導体層21の少なくとも一部にはんだ19を形成する。基板17の基板2を接続する側の主面の一部に導体層22を形成する。

【0066】

基板17の機能素子を接続する側の主面には、主面側から順に密着層/拡散防止層/電極層/拡散防止層/電極層としてのTi/Pt/Au/Pt/AuやTi/Ni/Au/Pt/Au、Ti/Ni/Au/Ni/Au、Cr/Ni/Au/Pt/Au、Cr/Ni/Au/Ni/Auなどの半導体チップ側導体層21が形成される。

【0067】

機能素子側導体層21がTi/Pt/Au/Pt/Auで形成される場合、Tiは0.1μm程度、Ptは0.2μm〜0.4μm程度、Auは0.05μm〜5μm程度の厚さとすることができる。ただし、導体層の種類、層の数、厚さはこれに限定されるものではない。基板2側導体層22は、実施例1の導体層11と同じ種類、層である。導体層21の主面に形成されるはんだ19には、熱伝導率がはんだ9以上のはんだを使う。導体層5、6、7、8、および11、はんだ9の種類、層の数は第1の実施例で説明した通りである。

【0068】

図17に示すように、第6の実施の形態では、機能素子1と基板2の間に挟持する基板17の一部に貫通穴25が施されている。

【0069】

図18に示すように基板2上に基板17を接続し、基板17上に機能素子1を接続後に金属ワイヤー24で基板2の主面に形成された導体層5と基板17の主面に形成された導体層21の導通を確保する。金属ワイヤーにはAuを用いるが、Au以外にAlやCuを使ってもよい。

【0070】

本発明に係わる第6の実施の形態では、第2の基板を挟持することにより、機能素子と基板を接続した接続部の放熱性の向上と熱膨張率の違いの緩和を図ることができる。

【0071】

また、本発明に係わる第6の実施の形態では、第2の基板17に貫通穴25を設けることにより、光素子等の機能素子1からの光を第2の基板17を通過させて第1の基板2の導波路層4に導くことができる。

【実施例7】

【0072】

次に本発明に係わる第7の実施の形態について、図19乃至21を用いて説明する。図19は、基板2上に基板17を接続し、基板17上に機能素子1を実装する前の断面図である。

【0073】

図20は、機能素子1と基板2の間に挟持され、貫通穴を施された基板17および基板17の主面に形成される導体層18を斜方向から見た立体図である。

【0074】

図21は、基板2上に基板17を接続し、基板17上に機能素子1を実装後の断面図である。第7の実施の形態においては、第6の実施の形態と同様に、機能素子1と基板2の間に挟持する基板17の一部に貫通穴25が施されており、第6の実施の形態と相違する点は、基板17の主面に形成される導体層18が基板17の機能素子1を接続する面から側面まで連続し、さらに側面から基板2を接続する面に連続することである。

【0075】

導体層18は、実施例1の導体層11と同じ種類、層である。導体層21の主面に形成されるはんだ19には、熱伝導率がはんだ9以上のはんだを使う。導体層5、6、7、8、および11、はんだ9の種類、層の数は第1の実施例で説明した通りである。基板17の一部に施される貫通穴25の形状は円状でも三角形でも四角形等の多角形でもよく、その大きさに制限はなく、基板17の面内に収まればよい。

【0076】

本発明に係わる第7の実施の形態では、第2の基板17を挟持することにより、機能素子1と基板2を接続した接続部の放熱性の向上と熱膨張率の違いの緩和を図ることができる。

【0077】

また、本発明に係わる第7の実施の形態では、第2の基板17に貫通穴25を設けることにより、光素子等の機能素子1からの光を第2の基板17を通過させて第1の基板2の導波路層4に導くことができる。

【産業上の利用可能性】

【0078】

本発明は、比較的接続温度が低く、比較的熱伝導率が小さいSn−Biはんだ等を用いて機能素子と基板を接続した接続部の放熱性を向上することが可能となる。

【0079】

また、本発明によれば、機能素子と基板をSn−Biはんだ等を用いて接続後、接続部と基板上に形成され、接続部以外の領域まで続いて形成されている導電層が接することのないようにすることで、Biの導電層への拡散による接続部に形成されるカーケンダルボイドの形成を抑止することが可能となる。

【0080】

また、本発明によれば、基板上の凹凸形状の導電層により、機能素子との接続時にはんだ表面に形成されていた酸化膜を破り濡れの良い良好な接続を実現するものである。本発明は、特に以下の分野に適用できる可能性がある。

【0081】

融点が低い有機材料を含む基板の上に機能素子を接続する場合、Au−Snなどのはんだなどの接続温度が300℃程度のはんだは、有機材料が劣化してしまうため使えない。

【0082】

そこで候補となる実施例が、比較的接続温度の低いSn−Biはんだである。Sn−Biは、Au−Snはんだに比べ放熱性が悪い。また、Sn−Biはんだで接続する場合、接続部がCuやAuの金属と接していると、接続部のBiが接続部の外へ拡散してしまい、Biが存在していた領域にカーケンダルボイドが形成されてしまう。

【0083】

そこで、Sn−Biはんだより放熱性のよい凹凸形状の導体層を形成し、接続部に占めるSn−Biはんだの割合を減らすことで放熱性を向上させ、凹凸形状の導体層により接続部とCuやAuの金属が接することのないようにすることで、放熱性が良く、良好な接続部を得ることができる。この様に、比較的低温で接続する必要があるときに必要になる技術である。

【符号の説明】

【0084】

1 機能素子

2 基板

3 基板2を構成する基材

4 導波路層

5 第1の導体層(基板2側)

6 第2の導体層(基板2側)

7 凹凸形状の第3の導体層(1)

8 凹凸形状の第3の導体層(2)

9 はんだ

10 基板(機能素子側)

11 導体層(機能素子側)

12 Au層

13 機能素子接続領域

14 第1の導体層と唯一接する凸部

15 樹脂

16 バンプ

17 第二の基板

18 導体層

19 はんだ

21 導体層(機能素子側)

22 導体層(基板2側)

23 Au層

24 金属ワイヤー

25 貫通穴

201 Bi−Sn共存領域

202 Sn/液相共存領域

203 Bi/液相共存領域

【特許請求の範囲】

【請求項1】

機能素子を、導体層を有する基板にはんだを用いて接続して搭載する機能素子搭載方法であって、

前記機能素子が搭載される前記基板の主面側の、前記機能素子が搭載される領域の少なくとも一部に第1の導体層を形成する導体層形成工程と、

前記第1の導体層の少なくとも一部に第2の導体層を形成する導体層形成工程と、

前記第2の導体層の少なくとも一部に凹凸形状の第3の導体層を形成する導体層形成工程と、

前記第3の導体層で、前記機能素子が接続される領域の最も外側に形成された凸部の最も高い箇所よりも、前記機能素子が接続される領域の内側の少なくとも一部にはんだを形成するはんだ形成工程と、

前記はんだを溶融させて前記機能素子を前記基板の主面側の前記第3の導体層に接続して搭載する接続工程と、

溶融させた前記はんだが前記第3の導体層により堰き止められて前記第1の導体層に接しない接続部を形成する接続工程と、を備え、

前記接続部が前記第1の導体層に接しないことを特徴とする機能素子搭載方法。

【請求項2】

前記機能素子の主面側の少なくとも一部に、前記接続工程において前記はんだと接続される第4の導体層を有することを特徴とする請求項1に記載の機能素子搭載方法。

【請求項3】

凹凸形状の前記第3の導体層を形成する導体層形成工程において、形成する凹凸形状の高さが、最も高い箇所で2μm〜10μmであることを特徴とする請求項1または2に記載の機能素子搭載方法。

【請求項4】

前記接続工程において、前記機能素子に予め形成されたAu層若しくはAuバンプを溶融した前記はんだに押し付けてAuとはんだ成分との反応により前記接続部を形成することを特徴とする請求項1乃至3の何れかの一つに記載の機能素子搭載方法。

【請求項5】

凹凸形状の前記第3の導体層を形成する導体層形成工程において、形成する凹凸形状の前記第3の導体層を構成する複数の導体層が金属材料であることを特徴とする請求項1乃至3の何れか一つに記載の機能素子搭載方法。

【請求項6】

凹凸形状の前記第3の導体層を形成する導体層形成工程において、前記第3の導体層を構成する材料がCuまたはCu合金、AlまたはAl合金、NiまたはNi合金の金属、またはAuまたはAu合金であることを特徴とする請求項1乃至3の何れかの一つに記載の機能素子搭載方法。

【請求項7】

前記はんだ形成工程において、形成される前記はんだが、Bi−Sn、Sn−Ag−Bi、Sn−Zn−Bi、Sn―Ag―In―Bi、In−Bi等、Biが含まれるはんだであることを特徴とする請求項1乃至3のいずれか一つに記載の機能素子搭載方法。

【請求項8】

前記はんだ形成工程において、形成される前記はんだが、Bi−SnはんだまたはSn−Ag−Biはんだであって、Biの濃度が21%以上99.9%以下であることを特徴とする請求項1乃至3の何れか一つに記載の機能素搭載方法。

【請求項9】

前記はんだ形成工程において、形成されるBi−Sn、Sn−Ag−Bi、Sn−Zn−Bi、Sn―Ag―In―Bi、In−Bi等、Biが含まれるはんだ表面に、Ag、Au若しくはAgとAuを積層して構成される膜が形成されていることを特徴とする請求項1乃至3の何れか一つに記載の機能素子搭載方法。

【請求項10】

前記はんだ形成工程において、前記はんだの表面に、前記Ag、Au若しくはAgとAuを積層して構成される膜が蒸着、スパッタまたはめっきにより形成されることを特徴とする請求項9に記載の機能素子搭載方法。

【請求項11】

請求項1乃至10の何れか一つに記載の機能素子搭載方法において、前記機能素子が前記はんだにより接続される前記基板が耐熱温度200℃以下の有機材料を有するフレキシブル基板であることを特徴とする機能素子搭載方法。

【請求項12】

請求項1乃至10の何れか一つに記載の機能素子搭載方法において、前記機能素子と前記基板の間に第2の基板を挟持することを特徴とする機能素子搭載方法。

【請求項13】

導体層を有する基板にはんだを用いて機能素子を接続して搭載した機能素子搭載基板であって、

前記機能素子が搭載される前記基板の主面側の、前記機能素子が搭載される領域の少なくとも一部に形成された第1の導体層と、

前記第1の導体層の少なくとも一部に形成された第2の導体層と、

前記第2の導体層の少なくとも一部に形成された凹凸形状の第3の導体層と、

前記第3の導体層で、前記機能素子が接続される領域の最も外側に形成された凸部の最も高い箇所よりも、前記機能素子が接続される領域の内側の少なくとも一部に形成されたはんだと、

前記はんだを溶融させ、前記機能素子が前記基板の主面側の前記第3の導体層に接続して搭載され、溶融させた前記はんだが前記第3の導体層により堰き止められて前記第1の導体層に接しない接続部と、を備え、

前記接続部が前記第1の導体層に接しないことを特徴とする機能素子搭載基板。

【請求項14】

請求項13に記載の機能素子搭載基板において、接続された前記はんだが前記第3の導体層と接していないことを特徴とする機能素子搭載基板。

【請求項15】

請求項13または14に記載の機能素子搭載基板において、前記機能素子と前記基板の間に挟持された第2の基板を備えていることを特徴とする機能素子搭載基板。

【請求項16】

請求項13乃至15のいずれか一つに記載の機能素子搭載基板において、前記第2の基板の機能素子を搭載する面および前記基板と接する面の少なくとも一部に第4の導体層が形成されており、前記第4の導体層の少なくとも一部にはんだが形成されていることを特徴とする機能素子搭載基板。

【請求項17】

請求項13乃至16のいずれか一つに記載の機能素子搭載基板において、前記第2の基板の機能素子が接続される側に形成されているはんだの方が、機能素子を接続しない側に形成されているはんだより熱伝導率が高いことを特徴とする機能素子搭載基板。

【請求項18】

請求項13乃至17のいずれか一つに記載の機能素子搭載基板において、前記第2の基板の一部に貫通穴が開いていることを特徴とする機能素子搭載基板。

【請求項1】

機能素子を、導体層を有する基板にはんだを用いて接続して搭載する機能素子搭載方法であって、

前記機能素子が搭載される前記基板の主面側の、前記機能素子が搭載される領域の少なくとも一部に第1の導体層を形成する導体層形成工程と、

前記第1の導体層の少なくとも一部に第2の導体層を形成する導体層形成工程と、

前記第2の導体層の少なくとも一部に凹凸形状の第3の導体層を形成する導体層形成工程と、

前記第3の導体層で、前記機能素子が接続される領域の最も外側に形成された凸部の最も高い箇所よりも、前記機能素子が接続される領域の内側の少なくとも一部にはんだを形成するはんだ形成工程と、

前記はんだを溶融させて前記機能素子を前記基板の主面側の前記第3の導体層に接続して搭載する接続工程と、

溶融させた前記はんだが前記第3の導体層により堰き止められて前記第1の導体層に接しない接続部を形成する接続工程と、を備え、

前記接続部が前記第1の導体層に接しないことを特徴とする機能素子搭載方法。

【請求項2】

前記機能素子の主面側の少なくとも一部に、前記接続工程において前記はんだと接続される第4の導体層を有することを特徴とする請求項1に記載の機能素子搭載方法。

【請求項3】

凹凸形状の前記第3の導体層を形成する導体層形成工程において、形成する凹凸形状の高さが、最も高い箇所で2μm〜10μmであることを特徴とする請求項1または2に記載の機能素子搭載方法。

【請求項4】

前記接続工程において、前記機能素子に予め形成されたAu層若しくはAuバンプを溶融した前記はんだに押し付けてAuとはんだ成分との反応により前記接続部を形成することを特徴とする請求項1乃至3の何れかの一つに記載の機能素子搭載方法。

【請求項5】

凹凸形状の前記第3の導体層を形成する導体層形成工程において、形成する凹凸形状の前記第3の導体層を構成する複数の導体層が金属材料であることを特徴とする請求項1乃至3の何れか一つに記載の機能素子搭載方法。

【請求項6】

凹凸形状の前記第3の導体層を形成する導体層形成工程において、前記第3の導体層を構成する材料がCuまたはCu合金、AlまたはAl合金、NiまたはNi合金の金属、またはAuまたはAu合金であることを特徴とする請求項1乃至3の何れかの一つに記載の機能素子搭載方法。

【請求項7】

前記はんだ形成工程において、形成される前記はんだが、Bi−Sn、Sn−Ag−Bi、Sn−Zn−Bi、Sn―Ag―In―Bi、In−Bi等、Biが含まれるはんだであることを特徴とする請求項1乃至3のいずれか一つに記載の機能素子搭載方法。

【請求項8】

前記はんだ形成工程において、形成される前記はんだが、Bi−SnはんだまたはSn−Ag−Biはんだであって、Biの濃度が21%以上99.9%以下であることを特徴とする請求項1乃至3の何れか一つに記載の機能素搭載方法。

【請求項9】

前記はんだ形成工程において、形成されるBi−Sn、Sn−Ag−Bi、Sn−Zn−Bi、Sn―Ag―In―Bi、In−Bi等、Biが含まれるはんだ表面に、Ag、Au若しくはAgとAuを積層して構成される膜が形成されていることを特徴とする請求項1乃至3の何れか一つに記載の機能素子搭載方法。

【請求項10】

前記はんだ形成工程において、前記はんだの表面に、前記Ag、Au若しくはAgとAuを積層して構成される膜が蒸着、スパッタまたはめっきにより形成されることを特徴とする請求項9に記載の機能素子搭載方法。

【請求項11】

請求項1乃至10の何れか一つに記載の機能素子搭載方法において、前記機能素子が前記はんだにより接続される前記基板が耐熱温度200℃以下の有機材料を有するフレキシブル基板であることを特徴とする機能素子搭載方法。

【請求項12】

請求項1乃至10の何れか一つに記載の機能素子搭載方法において、前記機能素子と前記基板の間に第2の基板を挟持することを特徴とする機能素子搭載方法。

【請求項13】

導体層を有する基板にはんだを用いて機能素子を接続して搭載した機能素子搭載基板であって、

前記機能素子が搭載される前記基板の主面側の、前記機能素子が搭載される領域の少なくとも一部に形成された第1の導体層と、

前記第1の導体層の少なくとも一部に形成された第2の導体層と、

前記第2の導体層の少なくとも一部に形成された凹凸形状の第3の導体層と、

前記第3の導体層で、前記機能素子が接続される領域の最も外側に形成された凸部の最も高い箇所よりも、前記機能素子が接続される領域の内側の少なくとも一部に形成されたはんだと、

前記はんだを溶融させ、前記機能素子が前記基板の主面側の前記第3の導体層に接続して搭載され、溶融させた前記はんだが前記第3の導体層により堰き止められて前記第1の導体層に接しない接続部と、を備え、

前記接続部が前記第1の導体層に接しないことを特徴とする機能素子搭載基板。

【請求項14】

請求項13に記載の機能素子搭載基板において、接続された前記はんだが前記第3の導体層と接していないことを特徴とする機能素子搭載基板。

【請求項15】

請求項13または14に記載の機能素子搭載基板において、前記機能素子と前記基板の間に挟持された第2の基板を備えていることを特徴とする機能素子搭載基板。

【請求項16】

請求項13乃至15のいずれか一つに記載の機能素子搭載基板において、前記第2の基板の機能素子を搭載する面および前記基板と接する面の少なくとも一部に第4の導体層が形成されており、前記第4の導体層の少なくとも一部にはんだが形成されていることを特徴とする機能素子搭載基板。

【請求項17】

請求項13乃至16のいずれか一つに記載の機能素子搭載基板において、前記第2の基板の機能素子が接続される側に形成されているはんだの方が、機能素子を接続しない側に形成されているはんだより熱伝導率が高いことを特徴とする機能素子搭載基板。

【請求項18】

請求項13乃至17のいずれか一つに記載の機能素子搭載基板において、前記第2の基板の一部に貫通穴が開いていることを特徴とする機能素子搭載基板。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2010−212646(P2010−212646A)

【公開日】平成22年9月24日(2010.9.24)

【国際特許分類】

【出願番号】特願2009−141860(P2009−141860)

【出願日】平成21年6月15日(2009.6.15)

【出願人】(000233228)日立協和エンジニアリング株式会社 (35)

【Fターム(参考)】

【公開日】平成22年9月24日(2010.9.24)

【国際特許分類】

【出願日】平成21年6月15日(2009.6.15)

【出願人】(000233228)日立協和エンジニアリング株式会社 (35)

【Fターム(参考)】

[ Back to top ]