歪検知装置及びその製造方法

【課題】微小領域で歪を高感度に検知することができる歪検知装置及びその製造方法を提供する。

【解決手段】実施形態によれば、半導体回路部と、半導体回路部の上に設けられた検知部と、を含む歪検知装置が提供される。半導体回路部は、半導体基板上に設けられたトランジスタを有する。検知部は、トランジスタの上方に設けられた空洞部と、空洞部と並置された非空洞部と、を有する。検知部は、可動梁、歪検知素子部、第1、第2埋め込み配線を含む。可動梁は、固定部分及び可動部分を有し、第1、第2配線層を含む。固定部分は非空洞部に固定される。可動部分は、固定部分から空洞部に延びトランジスタと離間する。歪検知素子部は、可動部分に固定され、第1、第2配線層と電気的に接続され、第1磁性層を含む。第1、第2埋め込み配線は、非空洞部に設けられ、第1、第2配線層と半導体回路部とを電気的に接続する。

【解決手段】実施形態によれば、半導体回路部と、半導体回路部の上に設けられた検知部と、を含む歪検知装置が提供される。半導体回路部は、半導体基板上に設けられたトランジスタを有する。検知部は、トランジスタの上方に設けられた空洞部と、空洞部と並置された非空洞部と、を有する。検知部は、可動梁、歪検知素子部、第1、第2埋め込み配線を含む。可動梁は、固定部分及び可動部分を有し、第1、第2配線層を含む。固定部分は非空洞部に固定される。可動部分は、固定部分から空洞部に延びトランジスタと離間する。歪検知素子部は、可動部分に固定され、第1、第2配線層と電気的に接続され、第1磁性層を含む。第1、第2埋め込み配線は、非空洞部に設けられ、第1、第2配線層と半導体回路部とを電気的に接続する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、歪検知装置及びその製造方法に関する。

【背景技術】

【0002】

微小領域でも高感度に歪を測定することができる歪センサが必要とされている。例えば、圧力変動を振動により検出する音響検出部を有する半導体センサチップと制御回路チップとをボンディングワイヤで電気的に接続する構成がある。しかしながら、この構成においては、装置の小型化が困難であり、微小領域で歪を高感度に測定することが困難である。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−5077号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の実施形態は、微小領域で歪を高感度に検知することができる歪検知装置及びその製造方法を提供する。

【課題を解決するための手段】

【0005】

本発明の実施形態によれば、半導体回路部と、検知部と、を含む歪検知装置が提供される。前記半導体回路部は、半導体基板と、前記半導体基板の主面上に設けられたトランジスタと、を有する。前記検知部は、前記半導体回路部の上に設けられる。前記検知部は、前記トランジスタの上方に設けられた空洞部と、前記主面に対して平行な平面内で前記空洞部と並置された非空洞部と、を有する。前記検知部は、可動梁と、歪検知素子部と、第1埋め込み配線と、第2埋め込み配線と、を含む。前記可動梁は、固定部分と、可動部分と、を有する。前記可動梁は、第1配線層と、第2配線層と、を含む。前記固定部分は、前記非空洞部に固定される。前記可動部分は、前記固定部分から前記空洞部に延び前記トランジスタと離間し前記トランジスタと間の距離が可変である。前記第1配線層と前記第2配線層とは、前記固定部分から前記可動部分に向けて延びる。前記歪検知素子部は、前記可動部分に固定される。前記歪検知素子部の一端は前記第1配線層と電気的に接続される。前記歪検知素子部の他端は、前記第2配線層と電気的に接続される。前記歪検知素子部は、第1磁性層を含む。前記第1埋め込み配線は、前記非空洞部に設けられ、前記第1配線層と前記半導体回路部とを電気的に接続する。前記第2埋め込み配線は、前記非空洞部に設けられ、前記第2配線層と前記半導体回路部とを電気的に接続する。

【図面の簡単な説明】

【0006】

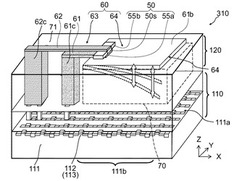

【図1】第1の実施形態に係る歪検知装置を示す模式的斜視図である。

【図2】第1の実施形態に係る歪検知装置の一部を示す模式的斜視図である。

【図3】図3(a)〜図3(c)は、第1の実施形態に係る歪検知装置の動作を示す模式的斜視図である。

【図4】第1の実施形態に係る歪検知装置の一部を示す模式的斜視図である。

【図5】第1の実施形態に係る歪検知装置の一部を示す模式的斜視図である。

【図6】図6(a)〜図6(c)は、第1の実施形態に係る歪検知装置の一部を示す模式図である。

【図7】図7(a)〜図7(c)は、第1の実施形態に係る歪検知装置の一部を示す模式図である。

【図8】図8(a)〜図8(c)は、第1の実施形態に係る歪検知装置の一部を示す模式図である。

【図9】第1の実施形態に係る別の歪検知装置を示す模式的斜視図である。

【図10】第1の実施形態に係る別の歪検知装置の一部を示す模式的斜視図である。

【図11】第1の実施形態に係る別の歪検知装置の一部を示す模式的斜視図である。

【図12】図12(a)〜図12(c)は、第1の実施形態に係る別の歪検知装置及び電子機器を示す模式図である。

【図13】図13(a)及び図13(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図14】図14(a)及び図14(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図15】図15(a)及び図15(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図16】図16(a)及び図16(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図17】図17(a)及び図17(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図18】図18(a)及び図18(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図19】図19(a)及び図19(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図20】図20(a)及び図20(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図21】図21(a)及び図21(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図22】図22(a)及び図22(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図23】図23(a)及び図23(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図24】図24(a)及び図24(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図25】図25(a)〜図25(c)は、第1の実施形態に係る歪検知装置の一部を示す模式図である。

【図26】図26(a)及び図26(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図27】図27(a)及び図27(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図28】図28(a)及び図28(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図29】図29(a)及び図29(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図30】図30(a)及び図30(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図31】図31(a)及び図31(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図32】図32(a)及び図32(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図33】図33(a)及び図33(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図34】第1の実施形態に係る別の歪検知装置を示す模式的斜視図である。

【図35】第2の実施形態に係る歪検知装置の製造方法を示すフローチャート図である。

【発明を実施するための形態】

【0007】

以下に、各実施の形態について図面を参照しつつ説明する。

なお、図面は模式的または概念的なものであり、部分間の大きさの比率などは、必ずしも現実のものと同一とは限らない。また、同じ部分を表す場合であっても、図面により互いの寸法や比率が異なって表される場合もある。

なお、本願明細書と各図において、既出の図に関して前述したものと同様の要素には同一の符号を付して詳細な説明は適宜省略する。

【0008】

(第1の実施形態)

図1は、第1の実施形態に係る歪検知装置の構成を例示する模式的斜視図である。

図1では、図を見やすくするために、絶縁部分を省略し、導電部分が主に描かれている。

【0009】

図1に表したように、本実施形態に係る歪検知装置310は、半導体回路部110と、検知部120と、を含む。

【0010】

半導体回路部110は、半導体基板111と、トランジスタ112と、を有する。

半導体基板111は、半導体基板111の主面111aを有する。半導体基板111は、主面111aに設けられた素子領域111bを有する。トランジスタ112は、素子領域111bに設けられる。

【0011】

半導体回路部110は、処理回路113を含んでも良い。処理回路113は、素子領域111bに設けられても良く、それ以外の領域に設けられても良い。処理回路113は半導体回路部110の任意の場所に設けられる。処理回路113は、素子領域111bに設けられるトランジスタ112を含んでも良い。

【0012】

検知部120は、半導体回路部110の上に設けられる。

【0013】

検知部120は、空洞部70と、非空洞部71と、を有する。空洞部70は、トランジスタ112の上方に設けられる。空洞部70は、少なくとも、素子領域111bの上に設けられる。非空洞部71は、主面111aに対して平行な平面内で空洞部70と並置される。

【0014】

空洞部70は、非空洞部71を形成する材料が設けられていない部分である。空洞部70内は、真空(1気圧よりも低い低圧状態)でも良く、空洞部70内に、空気や不活性ガスなどの気体が充填されていても良い。また、空洞部70内に、液体が充填されていても良い。空洞部70内には、後述する可動部分が動けるように、変形可能な物質が配置されていても良い。

【0015】

ここで、主面111aに対して平行な面をX−Y平面とする。X−Y平面に対して垂直な方向をZ軸方向とする。検知部120は、半導体回路部110とZ軸方向に沿って積層されている。

【0016】

非空洞部71は、空洞部70を取り囲んでも良い。

【0017】

検知部120は、可動梁60と、歪検知素子部50と、第1埋め込み配線61cと、第2埋め込み配線62cと、を含む。

【0018】

可動梁60は、固定部分63と、可動部分64と、を有する。可動梁60は、第1配線層61と、第2配線層62と、を含む。

【0019】

固定部分63は、非空洞部71に固定される。可動部分64は、固定部分63から空洞部70に延びる。可動部分64は、トランジスタ112と離間している。可動部分64とトランジスタ112との間の距離が可変である。第1配線層61及び第2配線層62は、固定部分63から可動部分64に向けて延びる。

【0020】

この例では、可動梁60は、X軸方向(X−Y平面内の1つの方向)に沿って延びる。すなわち、固定部分63から可動部分64に向かう方向は、X軸方向に沿っている。X軸方向に対して垂直でZ軸方向に対して垂直な軸をY軸方向とする。

【0021】

歪検知素子部50は、可動部分64に固定されている。歪検知素子部50の一端は、第1配線層61と電気的に接続されている。歪検知素子部50の他端は、第2配線層62と電気的に接続されている。歪検知素子部50は、後述する第1磁性層を含む。

【0022】

第1埋め込み配線61cは、非空洞部71に設けられる。第1埋め込み配線61cは、第1配線層61の固定部分63側の端と半導体回路部110とを電気的に接続する。

【0023】

第2埋め込み配線62cは、非空洞部71に設けられる。第2埋め込み配線62cは、第2配線層62の固定部分63側の端と半導体回路部110とを電気的に接続する。

【0024】

例えば、第1埋め込み配線61cと第2埋め込み配線62cとは、Z軸方向に沿う部分を有する。

【0025】

本実施形態に係る歪検知装置310においては、可動部分64とトランジスタ112との間の距離が変化可能である。この距離の変化に応じて、歪検知素子部50に加わる歪の量が変化し、その歪量の変化に応じて、第1磁性層の磁化方向が変化する。この磁化方向の変化に伴って、歪検知素子部50の一端と他端との間の電気抵抗が変化する。この電気抵抗の変化は、例えばMR効果に基づく。これにより、微小領域で歪を高感度に検知することができる。

【0026】

この例では、可動部分64は、第1配線層61と積層されたダイアフラム部61bを有している。この例では、ダイアフラム部61bの一部の上に第1配線層61が延びている。

【0027】

本願明細書において、積層されている状態は、直接重ねられる状態に加え、間に別の要素が挿入された状態で重ねられる状態を含む。また、上に設けられている状態は、接して上に配置される状態に加え、間に別の要素が挿入されて上に配置される状態を含む。

【0028】

ダイアフラム部61bの面積は、第1配線層61の面積よりも大きい。ダイアフラム部61bを設けることで、外部からの外力が効率よく歪検知素子部50に伝わる。これにより、歪検知の感度が高くなる。また、ダイアフラム部61bを設けることで、形状が規定された構造物の上での歪検知が可能になるので、外力と歪との関係が一定となる。例えば、歪量から外力への換算が一意となり、使い易くなる。

【0029】

また、この例では、歪検知素子部50に、歪抵抗変化部50sと、バイアス磁界を歪抵抗変化部50sに印加するバイアス層55a及び55b(例えばハードバイアス層)と、が設けられている。バイアス層55a及び55bは、必要に応じて設けられ、場合によっては省略できる。バイアス層55a及び55bについては後述する。以下、歪抵抗変化部50sについて説明する。

【0030】

図2は、第1の実施形態に係る歪検知装置の一部の構成を例示する模式的斜視図である。

図2に表したように、歪抵抗変化部50s(歪検知素子部50)は、例えば、第1磁性層10と、第2磁性層20と、第1磁性層10と第2磁性層20との間に設けられた中間層30と、を含む。中間層30は、非磁性層である。

【0031】

この例では、第1磁性層10は、磁化自由層である。第2磁性層20は、例えば、磁化固定層または磁化自由層である。

【0032】

以下では、歪検知素子部50の動作の例について、第2磁性層20が磁化固定層であり、第1磁性層10が磁化自由層である場合について説明する。歪検知素子部50においては、強磁性体が有する「逆磁歪効果」と、歪抵抗変化部50sで発現する「MR効果」と、が利用される。

【0033】

「MR効果」は、磁性体を有する積層膜において、外部磁界が印加されたときに、磁性体の磁化の変化によって積層膜の電気抵抗の値が変化する現象である。GMR(Giant magnetoresistance)効果、TMR(Tunneling magnetoresistance)効果などがある。歪抵抗変化部50sに電流を流すことで、磁化の向きの相対角度の変化を電気抵抗変化として読み取ることで、MR効果は発現する。例えば、歪検知素子部50に加わる応力に基づいて、歪抵抗変化部50sに引っ張り応力が加わる。第1磁性層10(磁化自由層)の磁化の向きと、第2磁性層20に加わる引っ張り応力の方向と、が異なるときに、逆磁歪効果によりMR効果が発現する。低抵抗状態の抵抗をRとし、MR効果によって変化する電気抵抗の変化量をΔRとしたときに、ΔR/Rを「MR変化率」という。

【0034】

図3(a)〜図3(c)は、第1の実施形態に係る歪検知装置の動作を例示する模式的斜視図である。

これらの図は、歪検知素子部50の状態を例示している。これらの図は、歪検知素子部50における磁化の方向と、引っ張り応力の方向と、の関係を例示している。

【0035】

図3(a)は、引っ張り応力が印加されていない状態を示す。このとき、この例では、第2磁性層20(磁化固定層)の磁化の向きは、第1磁性層10(磁化自由層)の磁化の向きと、同じである。

【0036】

図3(b)は、引っ張り応力が印加された状態を示している。この例では、X軸方向に沿って引っ張り応力が印加されている。例えば、可動部分64の変形により、例えばX軸方向に沿った引っ張り応力が印加される。すなわち、引っ張り応力は、第2磁性層20(磁化固定層)及び第1磁性層10(磁化自由層)の磁化の向き(この例では、Y軸方向)に対して直交方向に印加される。このとき、引っ張り応力の方向と同じ方向になるように、第1磁性層10(磁化自由層)の磁化が回転する。これを「逆磁歪効果」という。このとき、第2磁性層20(磁化固定層)の磁化は固定されている。よって、第1磁性層10(磁化自由層)の磁化が回転することで、第2磁性層20(磁化固定層)の磁化の向きと、第1磁性層10(磁化自由層)の磁化の向きと、の相対角度が変化する。

【0037】

この図には、第2磁性層20(磁化固定層)の磁化の方向が一例として図示されており、磁化の方向は、この図に示した方向でなくても良い。

【0038】

逆磁歪効果においては、強磁性体の磁歪定数の符号によって磁化の容易軸が変化する。大きな逆磁歪効果を示す多くの材料は、磁歪定数が正の符号を持つ。磁歪定数が正の符号である場合には、上述のように引っ張り応力が加わる方向が磁化容易軸となる。このときには、上記のように、第1磁性層10(磁化自由層)の磁化は、磁化容易軸の方向に回転する。

【0039】

例えば、第1磁性層10(磁化自由層)の磁歪定数が正である場合には、第1磁性層10(磁化自由層)の磁化の方向は、引っ張り応力が加わる方向とは異なる方向に設定する。

【0040】

一方、磁歪定数が負である場合には、引っ張り応力が加わる方向に垂直な方向が磁化容易軸となる。

図3(c)は、磁歪定数が負である場合の状態を例示している。この場合には、第1磁性層10(磁化自由層)の磁化の方向は、引っ張り応力が加わる方向(この例ではX軸方向)に対して垂直な方向とは異なる方向に設定する。

この図には、第2磁性層20(磁化固定層)の磁化の方向が一例として図示されており、磁化の方向は、この図に示した方向でなくても良い。

【0041】

第1磁性層10の磁化と第2磁性層20の磁化との間の角度に応じて、歪検知素子部50(歪抵抗変化部50s)の電気抵抗が、例えば、MR効果によって変化する。

【0042】

磁歪定数(λs)は、外部磁界を印加して強磁性層をある方向に飽和磁化させたときの形状変化の大きさを示す。外部磁界がない状態で長さLであるときに、外部磁界が印加されたときにΔLだけ変化したとすると、磁歪定数λsは、ΔL/Lで表される。この変化量は磁界の大きさによって変わるが、磁歪定数λsは十分な磁界が印加され、磁化が飽和された状態のΔL/Lとしてあらわす。

【0043】

例えば、第2磁性層20が磁化固定層である場合、第2磁性層20には、例えば、CoFe合金、CoFeB合金及びNiFe合金等を用いることができる。第2磁性層20の厚さは、例えば2ナノメートル(nm)以上6nm以下である。

【0044】

中間層30には、金属または絶縁体を用いることができる。金属としては、例えば、Cu、Au及びAg等を用いることができる。金属の場合、中間層30の厚さは、例えば1nm以上7nm以下である。絶縁体としては、例えば、マグネシウム酸化物(MgO等)、アルミ酸化物(Al2O3等)、チタン酸化物(TiO等)、及び、亜鉛酸化物(ZnO等)を用いることができる。絶縁体の場合、中間層30の厚さは、例えば0.6nm以上2.5nm以下である。

【0045】

第1磁性層10が磁化自由層である場合、第1磁性層10には、例えば、FeCo合金、及び、NiFe合金等を用いることができる。この他、第1磁性層10には、Fe−Co−Si−B合金、λs>100ppmを示すTb−M−Fe合金(Mは、Sm、Eu、Gd、Dy、Ho、Er)、Tb−M1−Fe−M2合金(M1は、Sm、Eu、Gd、Dy、Ho、Er、M2は、Ti,Cr,Mn,Co,Cu,Nb,Mo,W,Ta)、Fe−M3−M4−B合金(M3は、Ti,Cr,Mn,Co,Cu,Nb,Mo,W,Ta、M4は、Ce,Pr,Nd,Sm,Tb,Dy,Er)、Ni、Al−Feやフェライト(Fe3O4、(FeCo)3O4)など)等を用いることができる。第1磁性層10の厚さは、例えば2nm以上である。

【0046】

第1磁性層10は、2層構造を有することができる。この場合、第1磁性層10は、FeCo合金の層と、FeCo合金の層と積層された以下の層と、を含むことができる。FeCo合金の層と積層されるのは、Fe−Co−Si−B合金、λs>100ppmを示すTb−M−Fe合金(Mは、Sm、Eu、Gd、Dy、Ho、Er)、Tb−M1−Fe−M2合金(M1は、Sm、Eu、Gd、Dy、Ho、Er、M2は、Ti,Cr,Mn,Co,Cu,Nb,Mo,W,Ta)、Fe−M3−M4−B合金(M3は、Ti,Cr,Mn,Co,Cu,Nb,Mo,W,Ta、M4は、Ce,Pr,Nd,Sm,Tb,Dy,Er)、Ni、Al−Feやフェライト(Fe3O4、(FeCo)3O4)など)等から選択される材料の層である。

【0047】

例えば、中間層30が金属の場合は、GMR(Giant Magnetoresistance)効果が発現する。中間層30が絶縁体の場合は、TMR(Tunneling Magnetoresistance)効果が発現する。例えば、歪検知素子部50においては、例えば、歪抵抗変化部50sの積層方向に沿って電流を流すCPP(Current Perpendicular to Plane)−GMR効果が用いられる。

【0048】

また、中間層30として、絶縁層の一部に1nm以上5nm程度の幅(例えば径)の金属電流パスが膜厚方向に貫通して複数形成された、CCP(Current-Confined-Path)スペーサー層を用いることができる。この場合も、CCP−GMR効果が用いられる。

【0049】

このように、本実施形態においては、歪検知素子部50における逆磁歪現象が用いられる。これにより、高感度な検知が可能になる。逆磁歪効果を用いる場合、例えば、外部から加えられる歪に対して、第1磁性層10及び第2磁性層20の少なくともいずれかの磁性層の磁化方向が変化させられる。外部から加えられる歪(有無及びその程度など)によって、2つの磁性層の磁化の相対的な角度が変わる。外部から加えられる歪によって電気抵抗が変わるため、歪検知素子部50は、歪センサとして機能する。

【0050】

図4は、第1の実施形態に係る歪検知装置の一部の構成を例示する模式的斜視図である。

図4に表したように、歪検知素子部50は、例えば、第1電極51と、第2電極52と、を含む。第1電極51と第2電極52との間に歪抵抗変化部50sが設けられている。この例では、歪抵抗変化部50sにおいては、第1電極51の側から第2電極52に向けて、バッファ層41(兼シード層、厚さ数nm)、反強磁性層42(厚さ数nm)、磁性層43(厚さ数nm)、Ru層44、第2磁性層20(厚さ数nm)、中間層30(厚さ数nm)、第1磁性層10及びキャップ層45(厚さ数nm)が、この順で設けられている。

【0051】

第2磁性層20には、例えば、磁性積層膜が用いられる。第1磁性層10は、磁性積層膜10a(厚さ約1nm)と、磁性積層膜10aとキャップ層45との間に設けられた高磁歪磁性膜10b(厚さ数nm)と、を含む。

【0052】

第1電極51及び第2電極52には、例えば、非磁性体であるAu、Cu、Ta、Al等を用いることができる。第1電極51及び第2電極52として、軟磁性体の材料を用いることで、歪抵抗変化部50sに影響を及ぼす外部からの磁気ノイズを低減することができる。軟磁性体の材料としては、例えば、パーマロイ(NiFe合金)や珪素鋼(FeSi合金)を用いることができる。歪検知素子部50は、アルミ酸化物(例えばAl2O3)やシリコン酸化物(例えばSiO2)等の絶縁体で覆われる。

【0053】

第1磁性層10及び第2磁性層20の少なくともいずれかの磁性層の磁化方向は、応力に応じて変化する。少なくともいずれかの磁性層(応力に応じて磁化方向が変化する磁性層)の磁歪定数の絶対値は、例えば、10−5以上に設定する。これにより、逆磁歪効果によって、外部から加えられる歪みに応じて磁化の方向が変化する。例えば、第1磁性層10及び第2磁性層20の少なくともいずれかには、Fe、Co及びNiなどのような金属または、それらを含む合金などが用いられる。用いる元素や添加元素などによって、磁歪定数は大きく設定される。

【0054】

例えば、中間層30としてMgOのような酸化物が用いられる。MgO層上の磁性層は、一般的にプラスの磁歪定数を有する。例えば、中間層30の上に第1磁性層10を形成する場合、第1磁性層10として、CoFeB/CoFe/NiFeの積層構成の磁化自由層を用いる。最上層のNiFe層をNiリッチにすると、NiFe層の磁歪定数はマイナスでその絶対値が大きくなる。酸化物層上のプラスの磁歪が打ち消されることを抑制するために、最上層のNiFe層のNi組成は、一般的に用いられるNi81Fe19のパーマロイ組成と比較して、Niリッチにしない。具体的には、最上層のNiFe層におけるNiの比率は、80原子パーセント(atomic%)未満とすることが好ましい。第1磁性層10を磁化自由層とする場合には、第1磁性層10の厚さは、例えば、1nm以上20nm以下が好ましい。

【0055】

第1磁性層10が磁化自由層である場合において、第2磁性層20は、磁化固定層でも磁化自由層でも良い。第2磁性層20が磁化固定層である場合、外部から歪が加えられても第2磁性層20の磁化の方向は実質的に変化しない。そして、第1磁性層10と第2磁性層20との間での相対的な磁化の角度によって電気抵抗が変化する。電気抵抗の違いによって歪の有無が検知される。

【0056】

第1磁性層10及び第2磁性層20の両方が磁化自由層である場合には、例えば、第1磁性層10の磁歪定数は、第2磁性層20の磁歪定数とは異なるように設定される。

【0057】

第2磁性層20が磁化固定層である場合も磁化自由層である場合も、第2磁性層20の厚さは、例えば1nm以上20nm以下が好ましい。

【0058】

例えば、第2磁性層20が磁化固定層である場合、例えば、第2磁性層20には、反磁性層/磁性層/Ru層/磁性層の積層構造を用いたシンセティックAF構造などを用いることができる。反磁性層には、例えばIrMnなどが用いられる。また、後述するように、ハードバイアス層を設けても良い。

【0059】

歪検知素子部50では、磁性層のスピンが用いられる。歪検知素子部50に必要な面積は、極めて小さいサイズで十分である。歪検知素子部50の面積は、例えば、10nm×10nm〜20nm×20nm以下程度で十分である。

【0060】

例えば、歪検知素子部50のX軸方向(固定部分63から可動部分64に向かう第1方向)に沿った長さは、20nm以上10μm以下である。歪検知素子部50のX軸方向に沿った長さは、100nm以上3μm以下であることが好ましい。

【0061】

例えば、歪検知素子部50のY軸方向(X軸方向に対して垂直で、X−Y平面に対して平行な方向)に沿った長さは、20nm以上10μm以下である。歪検知素子部50のY軸方向に沿った長さは、100nm以上3μm以下であることが好ましい。

【0062】

例えば、歪検知素子部50のZ軸方向(X−Y平面に対して垂直な方向)に沿った長さは、20nm以上100nm以下である。

【0063】

歪検知素子部50のX軸方向に沿った長さは、歪検知素子部50のY軸方向に沿った長さと同じでも良く、異なっても良い。歪検知素子部50のX軸方向に沿った長さが、歪検知素子部50のY軸方向に沿った長さと異なるときに、形状磁気異方性が生じる。これにより、ハードバイアス層で得られる作用と同様の作用を得ることもできる。

【0064】

歪検知素子部50において流される電流の向きは、第1磁性層10から第2磁性層20に向かう方向でも良く、第2磁性層20から第1磁性層10に向かう方向でも良い。

【0065】

図5は、第1の実施形態に係る歪検知装置の一部の構成を例示する模式的斜視図である。

図5に表したように、この例では、歪検知素子部50は、バイアス層55a及び55b(ハードバイアス層)をさらに含む。バイアス層55a及び55bは、歪抵抗変化部50sに対向して設けられる。

【0066】

この例では、第2磁性層20が磁化固定層である。バイアス層55a及び55bは、第2磁性層20に並置される。バイアス層55a及び55bの間に、歪抵抗変化部50sが配置される。バイアス層55aと歪抵抗変化部50sとの間に絶縁層54aが設けられる。バイアス層55bと歪抵抗変化部50sとの間に絶縁層54bが設けられる。

【0067】

バイアス層55a及び55bは、第1磁性層10にバイアス磁界を印加する。これにより、第1磁性層10の磁化方向を適正な位置にバイアスすることが可能になるとともに、単一磁区化することが可能となる。

【0068】

バイアス層55a及び55bのそれぞれの大きさ(この例ではY軸方向に沿った長さ)は、例えば、100nm以上10μm以下である。

【0069】

絶縁層54a及び54bのそれぞれの大きさ(この例ではY軸方向に沿った長さ)は、例えば、1nm以上5nm以下である。

【0070】

本実施形態に係る歪検知装置310においては、トランジスタ112が形成された基板の上方に、歪検知素子部50が形成されている。トランジスタ112と、歪検知素子部50とは、実装工程で用いられるようなワイヤではなく、ウェーハ製造工程で一貫して形成される配線層で接続されている。これにより、歪検知装置の小型化が可能になり、微小領域で歪を高感度に検知することができる。

【0071】

トランジスタと歪検知素子部とを共通の基板上に形成することで、例えば、演算回路、増幅回路及び通信回路などの、センサで得られた情報を処理する回路(処理回路113など)を歪検知素子部50と同じ基板上に形成することができる。高感度なセンサを演算回路と一体として形成することで、システム全体としてみたときに、小型化が実現できる。また、低消費電力化を実現することができる。

【0072】

本実施形態においては、例えば、高感度のセンサを用い、さらに、そのセンサで得られた信号を演算処理する回路が、共通の基板上にシステムオンチップとして実現される。

【0073】

トランジスタ112の上方に可動部分64(ダイアフラム部61b)を設ける場合、現実的に得られる可動範囲(Z軸方向に沿った距離)は、10μm以下である。実際には、さらに小さい可動範囲のほうが形成しやすい。このような小さい可動範囲の場合でも歪を正確に測定するためには、歪センサとして非常に高感度なものが必要となる。また、微小点接触状態においても圧力を正確に測定するために、ダイアフラムの面積も小さいことが望ましい。ダイアフラムが小さくなると、ダイアフラムの膜厚を薄くしなければ、たわみ量も小さくなってしまい、感度良く測定することができない。外部環境で壊れにくい状態で圧力センサとして使用するためには、ダイアフラムの膜厚もあまり薄くすることはできないため、ダイアフラム径が小さくなると、圧力センサの感度も悪くなってしまう。

【0074】

以上のように、ダイアフラムの上下可動範囲が小さいこと、および、ダイアフラムの直径が小さい状態で使うこと、の2つの状況を実現しようとすると、歪センサとしては感度が高いものが望まれる。実施形態に係る歪検知素子部50は、この要求を満たすため、このようなことが可能になる。

【0075】

実施形態に係る歪検知素子部50においては、実質的に素子サイズの大きさに依存せず、小さい素子面積でも高い歪感度αを実現することができる。歪感度αは、例えば、α=(ΔR/Rmin)/εで表される。Rminは、低い状態の抵抗であり、ΔRは、抵抗変化量である。εは、歪であり、Δl/lで表される。ここで、lは初期の長さであり、Δlは変位量である。

【0076】

例えば、Siを用いたピエゾ抵抗型歪センサの場合には、歪感度αは用いる材料で決まり、例えば歪感度αは、約130である。また、Siを用いたピエゾ抵抗型歪センサの場合には、一辺が100μm程度の素子の面積が必要である。単位面積あたりの歪感度αは、例えば130/100μm2であり、約1010となる。

【0077】

一方、本実施形態に係る歪検知素子部50(スピン歪センサ)の場合には、歪感度αに上限はなく、1000程度のものは容易に実現できる。この歪感度αを実現するために必要な素子面積は、一辺が20nm程度である。このため、例えば、単位面積あたりの歪感度αは、約1017となる。このように、実施形態においては、従来のSiを用いたMEMS構造(Si−MEMS:Micro Electro Mechanical Systems)の圧力センサの場合と比較して、約7桁の単位面積あたりの感度向上が可能になる。

【0078】

本実施形態によれば、スピン歪センサ技術を用いることで、高い歪感度が得られ、例えば、演算回路を混載した歪・圧力センサの実現が可能となる。

【0079】

図6(a)〜図6(c)は、第1の実施形態に係る歪検知装置の一部の構成を例示する模式図である。

これらの図は、検知部120の1つの例である検知部121の構成を示している。図6(a)は斜視図である。図6(b)は、平面図である。図6(c)は、図6(a)のA1−A2線断面図である。

【0080】

図6(a)に表したように、可動部分64は、空洞部70の中において、Z軸方向に沿って動く。検知部121(検知部120)の厚さLz(Z軸方向に沿った長さ)は、例えば、1μm以上10μm以下である。この例では、ダイアフラム部61bが設けられている。可動部分64のサイズは、ダイアフラム部61bのサイズとなる。

【0081】

図6(b)に表したように、可動部分64は、ダイアフラム部61bを含む。ダイアフラム部61bのY軸方向(固定部分63から可動部分64に向かうX軸方向に対して垂直で主面111aに対して平行な方向)に沿った幅は、第1配線層61及び第2配線層62のY軸方向に沿った幅よりも広い。

【0082】

X軸方向に沿った可動部分64の長さLx(ダイアフラム部61bのX軸方向に沿った長さに相当)は、10μm以上500μm以下である。長さLxは、50μm以上200μm以下であることが好ましい。また、Y軸方向に沿った可動部分64の長さLy(ダイアフラム部61bのY軸方向に沿った長さに相当)は、10μm以上500μm以下である。長さLyは、50μm以上200μm以下であることが好ましい。

【0083】

長さLxは、長さLy以上であることが好ましい。例えば、長さLxは、長さLyの1.5倍以上5倍以下である。

【0084】

ダイアフラム部61bの一部は、固定部分63として、非空洞部71に固定されていても良い。ダイアフラム部61bのうちで非空洞部71に固定されている部分の幅L1(X軸方向に沿った幅)は、例えば、長さLxの1/10以上1/3以下である。

【0085】

図6(c)に表したように、可動部分64(ダイアフラム部61b)はZ軸方向に沿って撓む。空洞部70のZ軸方向に沿う高さLz70は、例えば、1μm以上10μm以下である。可動部分64は、空洞部70の中で動く。可動部分64(ダイアフラム部61b)の先端のZ軸方向に沿う移動の距離(Z軸方向に沿う距離)は、例えば、1μm以上10μm以下である。可動部分64とトランジスタ112(半導体回路部110)との間の距離は、例えば、1μm以上10μm以下の範囲で変化する。

【0086】

可動部分64(ダイアフラム部61b)の動きに応じて、歪検知素子部50に応力が加わる。この応力に応じて、歪検知素子部50の電気抵抗が変化する。

【0087】

第1埋め込み配線61c、第2埋め込み配線62c、第1配線層61及び第2配線層62を介して、歪検知素子部50に電流が流され、電気抵抗が検知される。これにより、可動部分64(ダイアフラム部61b)に加えられる応力が検知される。すなわち、歪検知装置310に加わる歪みが検知される。

【0088】

第1埋め込み配線61c、第2埋め込み配線62c、第1配線層61及び第2配線層62には、例えば、Cu及びAlなどの金属が用いられる。

【0089】

ダイアフラム部61bには、例えば、SiO2、アモルファスSi、各種酸化物、及び、各種窒化物の単層膜または積層膜などが用いられる。なお、後述するように、第1配線層61(第1配線層61層及び第2配線層62の少なくともいずれか)が、ダイアフラム部61bの機能を果たすこともできる。この場合には、ダイアフラム部61b(第1配線層61)には、Cu及びAlなどの金属が用いられる。このように、実施形態においては、トランジスタ112と混載されたダイアフラムの構成が採用される。

【0090】

一方、従来のSi−MEMSではSOI(Silicon on insulator)基板が用いられる。この場合には、SOIが設けられる基板(Si単結晶基板)の裏面が選択的に除去され、SOIの酸化膜がダイアフラムとなり、SOIのシリコン膜が能動部となる。従来の構成においては、SOI基板を用いる発想であるため、使用できる膜の材料が、酸化膜と、その上に形成されたシリコン膜に限定される。これは、RIE(Reactive Ion Etching)プロセスなどでエッチングすることが、単結晶Siを歪センサとして用いるためには必要であるためである。基板裏面からエッチングするプロセスとなるため、必然的に基板上に形成するトランジスタの上に、ダイアフラムを形成するということが極めて困難というのが従来の発想である。また、このように単結晶Siを歪センサとして用いる場合には、ダイアフラムの材料は、必然的に上述のような極めて限定された材料となってしまう。

【0091】

これに対して、実施形態においては、トランジスタ112上に、後述する犠牲層が形成され、犠牲層の上に可動部分64が形成される。例えば、トランジスタ112上に形成された犠牲層の上に成膜された膜が、ダイアフラム部61bとして用いられる。そのため、ダイアフラム部61bとして任意の材料を用いることが可能である。これにより、材料を適切に選択することで、ダイアフラム特性が向上でき、さらに、例えば、ダイアフラム部61bの応力を実質的にゼロにすることができる。また、SOI基板以外の基体の上に形成したダイアフラム上に単結晶Siを形成することは極めて困難だが、スピン歪センサならば形成することが可能となる。

【0092】

実施形態においては、犠牲層の上に可動部分64を形成し、犠牲層を犠牲層の上面から除去する構成を採用する。この場合、犠牲層を厚くすることが困難であるため、可動部分64の可動範囲は、SOI基板を用いたSi−MEMSに比べて限定的になる。すなわち、ダイアフラムの可動量が小さく、歪変化量が小さくなる。スピン歪センサにおいては高い歪感度が実現可能なため、ダイアフラムの可動量が小さい場合においても、センサとして十分機能することが可能であると、本願発明者は考えた。

【0093】

ダイアフラム部61bの厚さは、例えば、50nm以上1μm以下である。100nm以上500nm以下であることが好ましい。

【0094】

図6(c)に表したように、第1配線層61と第2配線層62との間には、絶縁層65(例えばSiO2層など)が設けられる。また、第1配線層61の可動部分64側の端部と、第2配線層62の可動部分64側の端部とに接して絶縁層66(例えばSiO2層など)が設けられる。

【0095】

このような構成を有する検知部120(検知部121)を用いることで、微小領域で歪を高感度に検知することができる。

【0096】

この例では、可動部分64(例えばダイアフラム部61b)、及び、空洞部70のZ軸方向に沿ってみた時の形状は、実質的に長方形であるが、実施形態はこれに限らない。これらの形状は任意である。

【0097】

図7(a)〜図7(c)は、第1の実施形態に係る歪検知装置の一部の構成を例示する模式図である。

これらの図は、検知部120の1つの例である検知部122の構成を示している。図7(a)は斜視図である。図7(b)は、平面図である。図7(c)は、図7(a)のA1−A2線断面図である。

【0098】

図7(a)〜図7(c)に表したように、この例では、可動部分64(例えばダイアフラム部61b)のZ軸方向に沿ってみたときの形状は、略円形(扁平円も含む)である。そして、空洞部70のZ軸方向に沿ってみた時の形状も、略円形(扁平円も含む)である。

この場合も、微小領域で歪を高感度に検知することができる。

【0099】

図8(a)〜図8(c)は、第1の実施形態に係る歪検知装置の一部の構成を例示する模式図である。

これらの図は、検知部120の1つの例である検知部123の構成を示している。図8(a)は斜視図である。図8(b)は、平面図である。図8(c)は、図8(a)のA1−A2線断面図である。

【0100】

図8(a)〜図8(c)に表したように、この例では、可動部分64の端は固定部分63に接続されており、可動部分64の他の端(この例では、3つの端)が、固定部67a、67b及び67cで、非空洞部71に固定されている。可動部分64は、固定部分63と、3つの固定部とによって、4箇所で支持されている。固定部67a、67b及び67cには、例えば、SiO2などの絶縁層が用いられる。

【0101】

この構成においては、図8(c)に表したように、可動部分64の中央部がZ軸方向に沿って動く。

【0102】

この例では、可動部分64は、4箇所で支持されているが、可動部分64に、可動部分64を貫通する孔64hが設けられていると見なすこともできる。

【0103】

このように、可動部分64は、複数の箇所によって支持されても良い。この場合も、微小領域で歪を高感度に検知することができる。

【0104】

本実施形態に係る歪検知装置310においては、外部から何らかの作用が可動部分64(例えばダイアフラム部61b)に与えられ、可動部分64(例えばダイアフラム部61b)の形状が変化する。この形状の変化に伴って歪検知素子部50に歪みが発生し、この歪みを電気抵抗の変化として検知する。歪検知装置310は、例えば圧力センサとして用いることができる。さらに、歪検知装置310は、加速センサとして用いることができる。さらに、歪検知装置310は、温度センサとして用いることができる。温度センサとして用いる場合には、温度に応じて可動部分64(例えばダイアフラム部61b)は伸縮し、これによる歪が検知される。例えば、温度膨張係数が大きい材料を可動部分64(例えばダイアフラム部61b)として用いることで、高感度の温度センサを提供することができる。

【0105】

図9は、第1の実施形態に係る別の歪検知装置の構成を例示する模式的斜視図である。 図9に表したように、本実施形態に係る歪検知装置320は、検知部120の上に設けられた圧力トランスデュース部130をさらに含む。

【0106】

圧力トランスデュース部130は、センサ保護部132と、圧力トランスデュース空洞部131と、を有する。圧力トランスデュース空洞部131は、例えば、センサ保護部132を形成する材料が設けられていない部分である。

【0107】

図10は、第1の実施形態に係る別の歪検知装置の一部の構成を例示する模式的斜視図である。

図10は、圧力トランスデュース部130の構成の1つの例を示している。

センサ保護部132には、例えば、Al2O3、及び、SiO2などの絶縁材料が用いられる。圧力トランスデュース空洞部131のZ軸方向にみたときの形状は、例えば、検知部120の空洞部70のZ軸方向にみたときの形状に沿う。但し、圧力トランスデュース空洞部131の形状は任意である。圧力トランスデュース空洞部131の内部には、例えば、空気が充填されている。圧力トランスデュース空洞部131は、例えば、空気の振動を歪検知素子部50に伝える。

【0108】

この構成を応用すると、音を検知するマイクロフォンを作製することも可能である。このように、実施形態に係る歪検知装置320は、音などの、任意の媒体における振動を検知する検知装置に応用できる。

【0109】

圧力トランスデュース部130を設けることにより、外部の圧力の変化をより効率的に歪検知素子部50に伝えることができる。これにより、より高精度でより安定した検知が可能になる。

【0110】

この例では、圧力トランスデュース空洞部131のZ軸方向にみたときの形状は、円形(扁平円も含む)であり、その直径131wは、例えば、1μm以上500nm以下である。センサ保護部132の厚さt130は、例えば300nm以上100μm以下である。ただし、実施形態はこれには限らない。これらの形状及び大きさは任意である。

【0111】

図11は、第1の実施形態に係る別の歪検知装置の一部の構成を例示する模式的斜視図である。

図11は、圧力トランスデュース部130の構成の別の例を示している。

この例では、圧力トランスデュース空洞部131の内部には、例えば、圧力トランスデュース材料133が配置されている。圧力トランスデュース材料133には、例えば、ジェル又は液体の例えばシリコーンなどが用いられる。

【0112】

この構成を用いる場合には、例えば、歪検知装置の製造の実装工程で、圧力トランスデュース部130と外部との間で圧力が伝達されるような実装が行われる。

【0113】

図1に関して説明した処理回路113は、例えば、歪検知素子部50で得られた信号の増幅処理や、センサ信号のA/D変換処理などを行うことができる。このように、半導体回路部110は、歪検知素子部50に流れる電流に基づく信号を処理する。処理回路113は、さらに、センサ信号のデータを他の電子機器に送信するための処理を行うことができる。さらに、処理回路113は、センサ信号から有意義な情報を引き出すためのデータマイニング処理(例えばノイズ除去処理など)を行うこともできる。

【0114】

図12(a)〜図12(c)は、第1の実施形態に係る別の歪検知装置及び電子機器の構成を例示する模式図である。

図12(a)は、本実施形態に係る別の歪検知装置311の構成を例示する模式的斜視図である。図12(b)は、歪検知装置311に設けられる送信回路117の例を示している。図12(c)は、歪検知装置311と組み合わせて用いられる電子機器118dの例を示している。

【0115】

図12(a)に表したように、歪検知装置311は、半導体回路部110及び検知部120に加え、アンテナ115と、電気配線116と、をさらに含む。アンテナ115は、電気配線116を介して、半導体回路部110と接続される。

【0116】

図12(b)に表したように、送信回路117が歪検知装置311に設けられる。送信回路117は、歪検知素子部50に流れる電気信号に基づくデータを無線で送信する。送信回路117の少なくとも一部は、半導体回路部110に設けることができる。半導体回路部110は、歪検知素子部50に流れる電気信号に基づくデータを無線で送信する送信回路117を含むことができる。

【0117】

図12(c)に表したように、歪検知装置311と組み合わせて用いられる電子機器118dには、受信部118が設けられる。電子機器118dとして、例えば、携帯端末などの電子装置が用いられる。

【0118】

例えば、送信回路117を含む歪検知装置311と、受信部118を含む電子機器118dと、を組み合わせて用いることで、より便利になる。

【0119】

この例では、図12(b)に表したように、歪検知装置311には、電子機器118dからの制御信号を受信する受信回路117rが設けられている。例えば、受信回路117rの少なくとも一部は、半導体回路部110に設けることができる。受信回路117rを設けることにより、例えば、電子機器118dを操作することで、歪検知装置311の動作を制御することができる。

【0120】

図12(b)に表したように、この例では、歪検知装置311には、送信回路117として、例えば、歪検知素子部50に接続されたADコンバータ117aと、マンチェスター符号化部117bと、が設けられる。さらに、切替部117cが設けられ、送信と受信を切り替える。タイミングコントローラ117dによりこの切り替えが制御される。そして、受信回路117rとして、データ訂正部117eと、同期部117fと、判定部117gと、が設けられる。さらに、電圧制御発振器117h(VCO)が設けられている。

【0121】

一方、図12(c)に表したように、電子機器118dには、マンチェスター符号化部117b、切替部117c、タイミングコントローラ117d、データ訂正部117e、同期部117f、判定部117g及び電圧制御発振器117hが設けられ、さらに記憶部118a及び中央演算部118b(CPU)が設けられている。

【0122】

以下、本実施形態に係る歪検知装置310の製造方法の例として、図6(a)〜図6(c)に例示した検知部121のように四角形のダイアフラム部61bを有する歪検知装置の製造方法の例について説明する。

【0123】

図13(a)、図13(b)、図14(a)、図14(b)、図15(a)、図15(b)、図16(a)、図16(b)、図17(a)、図17(b)、図18(a)、図18(b)、図19(a)、図19(b)、図20(a)、図20(b)、図21(a)、図21(b)、図22(a)、図22(b)、図23(a)、図23(b)、図24(a)及び図24(b)は、第1の実施形態に係る歪検知装置の製造方法を例示する模式図である。

図13(a)〜図24(a)は、模式的平面図であり、図13(b)〜図24(b)は、模式的断面図である。

【0124】

図13(a)及び図13(b)に表したように、半導体基板111の表面部分に半導体層112Mが設けられている。半導体層112Mの上面に素子分離絶縁層112Iを形成する。半導体層112Mの上に、図示しない絶縁層を介して、ゲート112Gを形成する。ゲート112Gの両側に、ソース112Sとドレイン112Dとを形成し、トランジスタ112が形成される。この上に層間絶縁膜114aを形成し、さらに層間絶縁膜114bを形成する。

【0125】

非空洞部71となる領域において、層間絶縁膜114a及び114bの一部に、トレンチ及び孔を形成する。孔に導電材料を埋め込んで、接続ピラー114c〜114eを形成する。この例では、接続ピラー114cは、1つのトランジスタのソース112Sに接続され、接続ピラー114dはドレイン112Dに接続されている。接続ピラー114eは、別のトランジスタのソース112Sに接続されている。トレンチに導電材料を埋め込んで、配線部114f及び配線部114gを形成する。配線部114fは、接続ピラー114c及び接続ピラー114dに接続される。配線部114gは、接続ピラー114eに接続される。層間絶縁膜114bの上に、層間絶縁膜114hを形成する。

【0126】

図14(a)及び図14(b)に表したように、層間絶縁膜114hの上に層間絶縁膜114iとなるSiO2を例えばCVDで形成する。層間絶縁膜114iの所定の位置に孔を形成し、導電材料(金属材料)を埋め込み、上面をCMPで平坦化する。これにより、配線部114fに接続された接続ピラー114jと、配線部114gに接続された接続ピラー114kと、が形成される。

【0127】

図15(a)及び図15(b)に表したように、層間絶縁膜114iの空洞部70となる領域に溝を形成し、その溝に犠牲層114lを埋め込む。犠牲層114lには、例えば、SiGeなどが用いられる。犠牲層114lには、低温で成膜できる材料が用いられる。

【0128】

図16(a)及び図16(b)に表したように、層間絶縁膜114i及び犠牲層114lの上に、ダイアフラム部61bとなる絶縁膜61bf(SiO2など)を形成する。絶縁膜61bfに孔を設け、その孔に導電材料(金属)を埋め込み、接続ピラー61fa及び接続ピラー62faを形成する。接続ピラー61faは接続ピラー114kと接続され、接続ピラー62faは接続ピラー114jと接続されている。

【0129】

図17(a)及び図17(b)に表したように、絶縁膜61bf、接続ピラー61fa及び接続ピラー62faの上に、第1配線層61となる導電層61fを形成する。

【0130】

図18(a)及び図18(b)に表したように、導電層61fの上に、歪検知素子部50となる積層膜50fを形成する。

【0131】

図19(a)及び図19(b)に表したように、積層膜50fを所定の形状に加工し、その上に、絶縁層65となる絶縁膜65f(SiO2など)を形成する。

【0132】

図20(a)及び図20(b)に表したように、絶縁膜65fの一部を除去し、導電層61fを所定の形状に加工する。これにより、第1配線層61の形状が形成される。このとき、導電層61fの一部は、接続ピラー62faに接続された接続ピラー62fbとなる。さらに、この上に、絶縁層66となる絶縁膜66fを形成する。

【0133】

図21(a)及び図21(b)に表したように、絶縁膜66fに開口部66pを形成する。これにより、接続ピラー62fbが露出する。

【0134】

図22(a)及び図22(b)に表したように、この上に、第2配線層62となる導電層62fを形成する。導電層62fの一部は、接続ピラー62fbと接続される。

【0135】

図23(a)及び図23(b)に表したように、導電層62fを所定の形状に加工する。これにより、第2配線層62が形成される。第2配線層62は、接続ピラー62fbに接続されている。

【0136】

図24(a)及び図24(b)に表したように、絶縁膜66fに所定の形状の開口部66oを形成する。開口部66oを介して、絶縁膜61bfを加工し、さらに、犠牲層114lを除去する。これにより、空洞部70が形成される。犠牲層114lの除去においては、例えば、犠牲層114lの上面(犠牲層114lの半導体基板111とは反対側の面)から犠牲層114lを除去(例えばエッチング)する。

これにより、本実施形態に係る歪検知装置310が形成できる。

【0137】

図25(a)〜図25(c)は、第1の実施形態に係る歪検知装置の一部の構成を例示する模式図である。

これらの図は、検知部120の1つの例である検知部124の構成を示している。図25(a)は斜視図である。図25(b)は、平面図である。図25(c)は、図25(a)のA1−A2線断面図である。

【0138】

図25(a)に表したように、この例では、ダイアフラム部61bが設けられず、ダイアフラム部61bの機能を第1配線層61が果たす。

【0139】

第1配線層61は、第2配線層62よりも下側に設けられている。すなわち、第1配線層61は、第2配線層62と半導体回路部110(図25(a)では図示していない)との間に設けられている。

【0140】

第1配線層61の可動部分64におけるY軸方向(固定部分63から可動部分64に向かうX軸方向に対して垂直で主面111aに対して平行な方向)に沿った幅は、第2配線層62の可動部分64におけるY軸方向に沿った幅よりも広い。

【0141】

ダイアフラム部61bが設けられない場合は、可動部分64のY軸方向の長さLyは、第1配線層61のうちの可動部分64におけるY軸方向の長さに相当する。可動部分64のX軸方向の長さLxは、第1配線層61のうちの可動部分64におけるX軸方向の長さに相当する。

【0142】

ダイアフラム部61bの機能を第1配線層61が果たすことで、構成が簡単になり、製造工程も簡単になる。このような検知部124においても、微小領域で歪を高感度に検知することができる。

【0143】

以下、図25(a)〜図25(c)に例示した検知部124を有する歪検知装置の製造方法の例について説明する。

【0144】

図26(a)、図26(b)、図27(a)、図27(b)、図28(a)、図28(b)、図29(a)、図29(b)、図30(a)、図30(b)、図31(a)、図31(b)、図32(a)、図32(b)、図33(a)及び図33(b)は、第1の実施形態に係る歪検知装置の製造方法を例示する模式図である。

図26(a)〜図33(a)は、模式的平面図であり、図26(b)〜図33(b)は、模式的断面図である。以下では、図13(a)〜図15(b)に関して説明したのと同様の工程の後の工程について説明する。

【0145】

図26(a)及び図26(b)に表したように、接続ピラー114j、接続ピラー114k、層間絶縁膜114i及び犠牲層114lの上に、第1配線層61となる導電層61fを形成する。

【0146】

図27(a)及び図27(b)に表したように、導電層61fの上に、歪検知素子部50となる積層膜50fを形成する。

【0147】

図28(a)及び図28(b)に表したように、積層膜50fを所定の形状に加工し、その上に、絶縁層65となる絶縁膜65f(SiO2など)を形成する。

【0148】

図29(a)及び図29(b)に表したように、絶縁膜65fの一部を除去し、導電層61fを所定の形状に加工する。これにより、第1配線層61の形状が形成される。第1配線層61は、接続ピラー114kと接続される。このとき、導電層61fの一部は、接続ピラー114jに接続された接続ピラー62fbとなる。さらに、この上に、絶縁層66となる絶縁膜66fを形成する。

【0149】

図30(a)及び図30(b)に表したように、絶縁膜66fに開口部66pを形成する。これにより、接続ピラー62fbが露出する。

【0150】

図31(a)及び図31(b)に表したように、この上に、第2配線層62となる導電層62fを形成する。導電層62fの一部は、接続ピラー62fbと接続される。

【0151】

図32(a)及び図32(b)に表したように、導電層62fを所定の形状に加工する。これにより、第2配線層62が形成される。第2配線層62は、接続ピラー62fbに接続されている。

【0152】

図33(a)及び図33(b)に表したように、絶縁膜66fに所定の形状の開口部66oを形成する。開口部66oを介して、犠牲層114lを除去する。これにより、空洞部70が形成される。

これにより、検知部124を有する歪検知装置が形成できる。この構成においては、ダイアフラム部61bの機能を第1配線層61が果たし、構成が簡単であるため、製造も簡単になる。

【0153】

図34は、第1の実施形態に係る別の歪検知装置の構成を例示する模式的斜視図である。

図34に表したように、本実施形態に係る別の歪検知装置330においては、検知部120の第1埋め込み配線61c及び第2埋め込み配線62cは、空洞部70の下方に設けられたトランジスタ112と電気的に接続されている。

【0154】

この例では、歪検知素子部50に流れる電流は、第1配線層61、第2配線層62、第1埋め込み配線61c及び第2埋め込み配線62cを介して、空洞部70の下に設けられたトランジスタ112に流れる。

【0155】

歪検知素子部50の下に設けられたトランジスタ112が、歪検知素子部50の抵抗変化を検知する構成により、例えば、チップ面積がより小さくできる。

【0156】

(第2の実施形態)

本実施形態は、歪検知装置の製造方法に係る。

図35は、第2の実施形態に係る歪検知装置の製造方法を例示するフローチャート図である。

図35に表したように、本実施形態に係る歪検知装置の製造方法においては、半導体基板111の上にトランジスタ112を形成する(ステップS110)。例えば、図13(a)及び図13(b)に関して説明した処理を行う。

【0157】

本製造方法においては、半導体基板111の上に層間絶縁層を形成し、トランジスタ112の上に犠牲層114lを形成する(ステップS120)。例えば、図14(a)〜図15(b)に関して説明した処理を行う。この層間絶縁層は、例えば、層間絶縁膜114iを含む。

【0158】

層間絶縁層(例えば層間絶縁膜114i)と犠牲層114lとの上に、第1配線層61となる第1導電層(導電層61f)を形成する(ステップS130)。例えば、図17(a)及び図17(b)に関して説明した処理を行う。なお、この前に、ダイアフラム部61bを形成しても良い。

【0159】

犠牲層114lの上の第1導電層(導電層61f)の上に、第1磁性層10を含む歪検知素子部50を形成する(ステップS140)。例えば、図18(a)〜図19(b)に関して説明した処理を行う。

【0160】

歪検知素子部50の上に第2配線層62となる第2導電層(導電層62f)を形成する(ステップS150)。例えば、図22(a)〜図23(b)に関して説明した処理を行う。

【0161】

層間絶縁層の中に、第1導電層(導電層61f)を半導体基板111と電気的に接続する第1埋め込み配線61cと、第2導電層(導電層62f)を半導体基板111と電気的に接続する第2埋め込み配線62cと、を形成する(ステップS160)。例えば、図13(a)、図13(b)、図14(a)、図14(b)、図16(a)、図16(b)、図20(a)及び図20(b)に関して説明した処理を行う。ステップS160は、例えば、上記のステップS110〜ステップS150の間、及び、ステップS150の後、の少なくともいずれかの工程において、1回、または、複数の処理により実施される。

【0162】

そして、犠牲層114lを除去する(ステップS170)。例えば、図24(a)及び図24(b)に関して説明した処理を行う。

【0163】

これにより、微小領域で歪を高感度に検知することができる歪検知装置の製造方法を提供できる。

【0164】

上記の犠牲層114lを除去する工程(ステップS170)は、例えば、犠牲層114lの上面(犠牲層114lの半導体基板111とは反対側の面)から犠牲層114lを除去(例えばエッチング)することを含む。

【0165】

実施形態によれば、微小領域で歪を高感度に検知することができる歪検知装置及びその製造方法が提供される。

【0166】

以上、具体例を参照しつつ、本発明の実施の形態について説明した。しかし、本発明の実施形態は、これらの具体例に限定されるものではない。例えば、歪検知装置に含まれる半導体回路部、半導体基板、トランジスタ、歪検知部、固定部分、可動部分、歪検知素子部、第1磁性層、第2磁性層、中間層、第1配線層、第2配線層、ダイアフラム部、第1埋め込み配線、第2埋め込み配線、及びトランスデューサ部などの各要素の具体的な構成に関しては、当業者が公知の範囲から適宜選択することにより本発明を同様に実施し、同様の効果を得ることができる限り、本発明の範囲に包含される。

【0167】

また、各具体例のいずれか2つ以上の要素を技術的に可能な範囲で組み合わせたものも、本発明の要旨を包含する限り本発明の範囲に含まれる。

【0168】

その他、本発明の実施の形態として上述した歪検知装置及びその製造方法を基にして、当業者が適宜設計変更して実施し得る全ての歪検知装置及びその製造方法も、本発明の要旨を包含する限り、本発明の範囲に属する。

【0169】

その他、本発明の思想の範疇において、当業者であれば、各種の変更例及び修正例に想到し得るものであり、それら変更例及び修正例についても本発明の範囲に属するものと了解される。

【0170】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0171】

10…第1磁性層、 10a…磁性積層膜、 10b…高磁歪磁性膜、 20…第2磁性層、 30…中間層、 41…バッファ層、 42…反強磁性層、 43…磁性層、 44…Ru層、 45…キャップ層、 50…歪検知素子部、 50f…積層膜、 50s…歪抵抗変化部、 51…第1電極、 52…第2電極、 54a、54b…絶縁層、 55a、55b…バイアス層、 60…可動梁、 61…第1配線層、 61b…ダイアフラム部、 61bf…絶縁膜、 61c…第1埋め込み配線、 61f…導電層、 61fa…接続ピラー、 62…第2配線層、 62c…第2埋め込み配線、 62f…導電層、 62fa、62fb…接続ピラー、 63…固定部分、 64…可動部分、 64h…孔、 65…絶縁層、 65f…絶縁膜、 66…絶縁層、 66f…絶縁膜、 66o、66p…開口部、 67a〜67c…固定部、 70…空洞部、 71…非空洞部、 110…半導体回路部、 111…半導体基板、 111a…主面、 111b…素子領域、 112…トランジスタ、 112D…ドレイン、 112G…ゲート、 112I…素子分離絶縁層、 112M…半導体層、 112S…ソース、 113…処理回路、 114a、114b…層間絶縁膜、 114c〜114e…接続ピラー、 114f、114g…配線部、 114h、114i…層間絶縁膜、 114j、114k…接続ピラー、 114l…犠牲層、 115…アンテナ、 116…電気配線、 117…送信回路、 117a…ADコンバータ、 117b…マンチェスター符号化部、117c…切替部、 117d…タイミングコントローラ、 117e…データ訂正部、 117f…同期部、 117g…判定部、 117h…電圧制御発振器、 117r…受信回路、 118…受信部、 118a…記憶部、 118b…中央演算部、 118d…電子機器、 120〜124…検知部、 130…圧力トランスデュース部、 131…圧力トランスデュース空洞部、 131w…直径、 132…センサ保護部、 133…圧力トランスデュース材料、 310、311、320、330…歪検知装置、L1…幅、 Lx、Ly…長さ、 Lz…厚さ、 Lz70…高さ、 t130…厚さ

【技術分野】

【0001】

本発明の実施形態は、歪検知装置及びその製造方法に関する。

【背景技術】

【0002】

微小領域でも高感度に歪を測定することができる歪センサが必要とされている。例えば、圧力変動を振動により検出する音響検出部を有する半導体センサチップと制御回路チップとをボンディングワイヤで電気的に接続する構成がある。しかしながら、この構成においては、装置の小型化が困難であり、微小領域で歪を高感度に測定することが困難である。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−5077号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

本発明の実施形態は、微小領域で歪を高感度に検知することができる歪検知装置及びその製造方法を提供する。

【課題を解決するための手段】

【0005】

本発明の実施形態によれば、半導体回路部と、検知部と、を含む歪検知装置が提供される。前記半導体回路部は、半導体基板と、前記半導体基板の主面上に設けられたトランジスタと、を有する。前記検知部は、前記半導体回路部の上に設けられる。前記検知部は、前記トランジスタの上方に設けられた空洞部と、前記主面に対して平行な平面内で前記空洞部と並置された非空洞部と、を有する。前記検知部は、可動梁と、歪検知素子部と、第1埋め込み配線と、第2埋め込み配線と、を含む。前記可動梁は、固定部分と、可動部分と、を有する。前記可動梁は、第1配線層と、第2配線層と、を含む。前記固定部分は、前記非空洞部に固定される。前記可動部分は、前記固定部分から前記空洞部に延び前記トランジスタと離間し前記トランジスタと間の距離が可変である。前記第1配線層と前記第2配線層とは、前記固定部分から前記可動部分に向けて延びる。前記歪検知素子部は、前記可動部分に固定される。前記歪検知素子部の一端は前記第1配線層と電気的に接続される。前記歪検知素子部の他端は、前記第2配線層と電気的に接続される。前記歪検知素子部は、第1磁性層を含む。前記第1埋め込み配線は、前記非空洞部に設けられ、前記第1配線層と前記半導体回路部とを電気的に接続する。前記第2埋め込み配線は、前記非空洞部に設けられ、前記第2配線層と前記半導体回路部とを電気的に接続する。

【図面の簡単な説明】

【0006】

【図1】第1の実施形態に係る歪検知装置を示す模式的斜視図である。

【図2】第1の実施形態に係る歪検知装置の一部を示す模式的斜視図である。

【図3】図3(a)〜図3(c)は、第1の実施形態に係る歪検知装置の動作を示す模式的斜視図である。

【図4】第1の実施形態に係る歪検知装置の一部を示す模式的斜視図である。

【図5】第1の実施形態に係る歪検知装置の一部を示す模式的斜視図である。

【図6】図6(a)〜図6(c)は、第1の実施形態に係る歪検知装置の一部を示す模式図である。

【図7】図7(a)〜図7(c)は、第1の実施形態に係る歪検知装置の一部を示す模式図である。

【図8】図8(a)〜図8(c)は、第1の実施形態に係る歪検知装置の一部を示す模式図である。

【図9】第1の実施形態に係る別の歪検知装置を示す模式的斜視図である。

【図10】第1の実施形態に係る別の歪検知装置の一部を示す模式的斜視図である。

【図11】第1の実施形態に係る別の歪検知装置の一部を示す模式的斜視図である。

【図12】図12(a)〜図12(c)は、第1の実施形態に係る別の歪検知装置及び電子機器を示す模式図である。

【図13】図13(a)及び図13(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図14】図14(a)及び図14(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図15】図15(a)及び図15(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図16】図16(a)及び図16(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図17】図17(a)及び図17(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図18】図18(a)及び図18(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図19】図19(a)及び図19(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図20】図20(a)及び図20(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図21】図21(a)及び図21(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図22】図22(a)及び図22(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図23】図23(a)及び図23(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図24】図24(a)及び図24(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図25】図25(a)〜図25(c)は、第1の実施形態に係る歪検知装置の一部を示す模式図である。

【図26】図26(a)及び図26(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図27】図27(a)及び図27(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図28】図28(a)及び図28(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図29】図29(a)及び図29(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図30】図30(a)及び図30(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図31】図31(a)及び図31(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図32】図32(a)及び図32(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図33】図33(a)及び図33(b)は、第1の実施形態に係る歪検知装置の製造方法を示す模式図である。

【図34】第1の実施形態に係る別の歪検知装置を示す模式的斜視図である。

【図35】第2の実施形態に係る歪検知装置の製造方法を示すフローチャート図である。

【発明を実施するための形態】

【0007】

以下に、各実施の形態について図面を参照しつつ説明する。

なお、図面は模式的または概念的なものであり、部分間の大きさの比率などは、必ずしも現実のものと同一とは限らない。また、同じ部分を表す場合であっても、図面により互いの寸法や比率が異なって表される場合もある。

なお、本願明細書と各図において、既出の図に関して前述したものと同様の要素には同一の符号を付して詳細な説明は適宜省略する。

【0008】

(第1の実施形態)

図1は、第1の実施形態に係る歪検知装置の構成を例示する模式的斜視図である。

図1では、図を見やすくするために、絶縁部分を省略し、導電部分が主に描かれている。

【0009】

図1に表したように、本実施形態に係る歪検知装置310は、半導体回路部110と、検知部120と、を含む。

【0010】

半導体回路部110は、半導体基板111と、トランジスタ112と、を有する。

半導体基板111は、半導体基板111の主面111aを有する。半導体基板111は、主面111aに設けられた素子領域111bを有する。トランジスタ112は、素子領域111bに設けられる。

【0011】

半導体回路部110は、処理回路113を含んでも良い。処理回路113は、素子領域111bに設けられても良く、それ以外の領域に設けられても良い。処理回路113は半導体回路部110の任意の場所に設けられる。処理回路113は、素子領域111bに設けられるトランジスタ112を含んでも良い。

【0012】

検知部120は、半導体回路部110の上に設けられる。

【0013】

検知部120は、空洞部70と、非空洞部71と、を有する。空洞部70は、トランジスタ112の上方に設けられる。空洞部70は、少なくとも、素子領域111bの上に設けられる。非空洞部71は、主面111aに対して平行な平面内で空洞部70と並置される。

【0014】

空洞部70は、非空洞部71を形成する材料が設けられていない部分である。空洞部70内は、真空(1気圧よりも低い低圧状態)でも良く、空洞部70内に、空気や不活性ガスなどの気体が充填されていても良い。また、空洞部70内に、液体が充填されていても良い。空洞部70内には、後述する可動部分が動けるように、変形可能な物質が配置されていても良い。

【0015】

ここで、主面111aに対して平行な面をX−Y平面とする。X−Y平面に対して垂直な方向をZ軸方向とする。検知部120は、半導体回路部110とZ軸方向に沿って積層されている。

【0016】

非空洞部71は、空洞部70を取り囲んでも良い。

【0017】

検知部120は、可動梁60と、歪検知素子部50と、第1埋め込み配線61cと、第2埋め込み配線62cと、を含む。

【0018】

可動梁60は、固定部分63と、可動部分64と、を有する。可動梁60は、第1配線層61と、第2配線層62と、を含む。

【0019】

固定部分63は、非空洞部71に固定される。可動部分64は、固定部分63から空洞部70に延びる。可動部分64は、トランジスタ112と離間している。可動部分64とトランジスタ112との間の距離が可変である。第1配線層61及び第2配線層62は、固定部分63から可動部分64に向けて延びる。

【0020】

この例では、可動梁60は、X軸方向(X−Y平面内の1つの方向)に沿って延びる。すなわち、固定部分63から可動部分64に向かう方向は、X軸方向に沿っている。X軸方向に対して垂直でZ軸方向に対して垂直な軸をY軸方向とする。

【0021】

歪検知素子部50は、可動部分64に固定されている。歪検知素子部50の一端は、第1配線層61と電気的に接続されている。歪検知素子部50の他端は、第2配線層62と電気的に接続されている。歪検知素子部50は、後述する第1磁性層を含む。

【0022】

第1埋め込み配線61cは、非空洞部71に設けられる。第1埋め込み配線61cは、第1配線層61の固定部分63側の端と半導体回路部110とを電気的に接続する。

【0023】

第2埋め込み配線62cは、非空洞部71に設けられる。第2埋め込み配線62cは、第2配線層62の固定部分63側の端と半導体回路部110とを電気的に接続する。

【0024】

例えば、第1埋め込み配線61cと第2埋め込み配線62cとは、Z軸方向に沿う部分を有する。

【0025】

本実施形態に係る歪検知装置310においては、可動部分64とトランジスタ112との間の距離が変化可能である。この距離の変化に応じて、歪検知素子部50に加わる歪の量が変化し、その歪量の変化に応じて、第1磁性層の磁化方向が変化する。この磁化方向の変化に伴って、歪検知素子部50の一端と他端との間の電気抵抗が変化する。この電気抵抗の変化は、例えばMR効果に基づく。これにより、微小領域で歪を高感度に検知することができる。

【0026】

この例では、可動部分64は、第1配線層61と積層されたダイアフラム部61bを有している。この例では、ダイアフラム部61bの一部の上に第1配線層61が延びている。

【0027】

本願明細書において、積層されている状態は、直接重ねられる状態に加え、間に別の要素が挿入された状態で重ねられる状態を含む。また、上に設けられている状態は、接して上に配置される状態に加え、間に別の要素が挿入されて上に配置される状態を含む。

【0028】

ダイアフラム部61bの面積は、第1配線層61の面積よりも大きい。ダイアフラム部61bを設けることで、外部からの外力が効率よく歪検知素子部50に伝わる。これにより、歪検知の感度が高くなる。また、ダイアフラム部61bを設けることで、形状が規定された構造物の上での歪検知が可能になるので、外力と歪との関係が一定となる。例えば、歪量から外力への換算が一意となり、使い易くなる。

【0029】

また、この例では、歪検知素子部50に、歪抵抗変化部50sと、バイアス磁界を歪抵抗変化部50sに印加するバイアス層55a及び55b(例えばハードバイアス層)と、が設けられている。バイアス層55a及び55bは、必要に応じて設けられ、場合によっては省略できる。バイアス層55a及び55bについては後述する。以下、歪抵抗変化部50sについて説明する。

【0030】

図2は、第1の実施形態に係る歪検知装置の一部の構成を例示する模式的斜視図である。

図2に表したように、歪抵抗変化部50s(歪検知素子部50)は、例えば、第1磁性層10と、第2磁性層20と、第1磁性層10と第2磁性層20との間に設けられた中間層30と、を含む。中間層30は、非磁性層である。

【0031】

この例では、第1磁性層10は、磁化自由層である。第2磁性層20は、例えば、磁化固定層または磁化自由層である。

【0032】

以下では、歪検知素子部50の動作の例について、第2磁性層20が磁化固定層であり、第1磁性層10が磁化自由層である場合について説明する。歪検知素子部50においては、強磁性体が有する「逆磁歪効果」と、歪抵抗変化部50sで発現する「MR効果」と、が利用される。

【0033】

「MR効果」は、磁性体を有する積層膜において、外部磁界が印加されたときに、磁性体の磁化の変化によって積層膜の電気抵抗の値が変化する現象である。GMR(Giant magnetoresistance)効果、TMR(Tunneling magnetoresistance)効果などがある。歪抵抗変化部50sに電流を流すことで、磁化の向きの相対角度の変化を電気抵抗変化として読み取ることで、MR効果は発現する。例えば、歪検知素子部50に加わる応力に基づいて、歪抵抗変化部50sに引っ張り応力が加わる。第1磁性層10(磁化自由層)の磁化の向きと、第2磁性層20に加わる引っ張り応力の方向と、が異なるときに、逆磁歪効果によりMR効果が発現する。低抵抗状態の抵抗をRとし、MR効果によって変化する電気抵抗の変化量をΔRとしたときに、ΔR/Rを「MR変化率」という。

【0034】

図3(a)〜図3(c)は、第1の実施形態に係る歪検知装置の動作を例示する模式的斜視図である。

これらの図は、歪検知素子部50の状態を例示している。これらの図は、歪検知素子部50における磁化の方向と、引っ張り応力の方向と、の関係を例示している。

【0035】

図3(a)は、引っ張り応力が印加されていない状態を示す。このとき、この例では、第2磁性層20(磁化固定層)の磁化の向きは、第1磁性層10(磁化自由層)の磁化の向きと、同じである。

【0036】

図3(b)は、引っ張り応力が印加された状態を示している。この例では、X軸方向に沿って引っ張り応力が印加されている。例えば、可動部分64の変形により、例えばX軸方向に沿った引っ張り応力が印加される。すなわち、引っ張り応力は、第2磁性層20(磁化固定層)及び第1磁性層10(磁化自由層)の磁化の向き(この例では、Y軸方向)に対して直交方向に印加される。このとき、引っ張り応力の方向と同じ方向になるように、第1磁性層10(磁化自由層)の磁化が回転する。これを「逆磁歪効果」という。このとき、第2磁性層20(磁化固定層)の磁化は固定されている。よって、第1磁性層10(磁化自由層)の磁化が回転することで、第2磁性層20(磁化固定層)の磁化の向きと、第1磁性層10(磁化自由層)の磁化の向きと、の相対角度が変化する。

【0037】

この図には、第2磁性層20(磁化固定層)の磁化の方向が一例として図示されており、磁化の方向は、この図に示した方向でなくても良い。

【0038】

逆磁歪効果においては、強磁性体の磁歪定数の符号によって磁化の容易軸が変化する。大きな逆磁歪効果を示す多くの材料は、磁歪定数が正の符号を持つ。磁歪定数が正の符号である場合には、上述のように引っ張り応力が加わる方向が磁化容易軸となる。このときには、上記のように、第1磁性層10(磁化自由層)の磁化は、磁化容易軸の方向に回転する。

【0039】

例えば、第1磁性層10(磁化自由層)の磁歪定数が正である場合には、第1磁性層10(磁化自由層)の磁化の方向は、引っ張り応力が加わる方向とは異なる方向に設定する。

【0040】

一方、磁歪定数が負である場合には、引っ張り応力が加わる方向に垂直な方向が磁化容易軸となる。

図3(c)は、磁歪定数が負である場合の状態を例示している。この場合には、第1磁性層10(磁化自由層)の磁化の方向は、引っ張り応力が加わる方向(この例ではX軸方向)に対して垂直な方向とは異なる方向に設定する。

この図には、第2磁性層20(磁化固定層)の磁化の方向が一例として図示されており、磁化の方向は、この図に示した方向でなくても良い。

【0041】

第1磁性層10の磁化と第2磁性層20の磁化との間の角度に応じて、歪検知素子部50(歪抵抗変化部50s)の電気抵抗が、例えば、MR効果によって変化する。

【0042】

磁歪定数(λs)は、外部磁界を印加して強磁性層をある方向に飽和磁化させたときの形状変化の大きさを示す。外部磁界がない状態で長さLであるときに、外部磁界が印加されたときにΔLだけ変化したとすると、磁歪定数λsは、ΔL/Lで表される。この変化量は磁界の大きさによって変わるが、磁歪定数λsは十分な磁界が印加され、磁化が飽和された状態のΔL/Lとしてあらわす。

【0043】

例えば、第2磁性層20が磁化固定層である場合、第2磁性層20には、例えば、CoFe合金、CoFeB合金及びNiFe合金等を用いることができる。第2磁性層20の厚さは、例えば2ナノメートル(nm)以上6nm以下である。

【0044】

中間層30には、金属または絶縁体を用いることができる。金属としては、例えば、Cu、Au及びAg等を用いることができる。金属の場合、中間層30の厚さは、例えば1nm以上7nm以下である。絶縁体としては、例えば、マグネシウム酸化物(MgO等)、アルミ酸化物(Al2O3等)、チタン酸化物(TiO等)、及び、亜鉛酸化物(ZnO等)を用いることができる。絶縁体の場合、中間層30の厚さは、例えば0.6nm以上2.5nm以下である。

【0045】

第1磁性層10が磁化自由層である場合、第1磁性層10には、例えば、FeCo合金、及び、NiFe合金等を用いることができる。この他、第1磁性層10には、Fe−Co−Si−B合金、λs>100ppmを示すTb−M−Fe合金(Mは、Sm、Eu、Gd、Dy、Ho、Er)、Tb−M1−Fe−M2合金(M1は、Sm、Eu、Gd、Dy、Ho、Er、M2は、Ti,Cr,Mn,Co,Cu,Nb,Mo,W,Ta)、Fe−M3−M4−B合金(M3は、Ti,Cr,Mn,Co,Cu,Nb,Mo,W,Ta、M4は、Ce,Pr,Nd,Sm,Tb,Dy,Er)、Ni、Al−Feやフェライト(Fe3O4、(FeCo)3O4)など)等を用いることができる。第1磁性層10の厚さは、例えば2nm以上である。

【0046】

第1磁性層10は、2層構造を有することができる。この場合、第1磁性層10は、FeCo合金の層と、FeCo合金の層と積層された以下の層と、を含むことができる。FeCo合金の層と積層されるのは、Fe−Co−Si−B合金、λs>100ppmを示すTb−M−Fe合金(Mは、Sm、Eu、Gd、Dy、Ho、Er)、Tb−M1−Fe−M2合金(M1は、Sm、Eu、Gd、Dy、Ho、Er、M2は、Ti,Cr,Mn,Co,Cu,Nb,Mo,W,Ta)、Fe−M3−M4−B合金(M3は、Ti,Cr,Mn,Co,Cu,Nb,Mo,W,Ta、M4は、Ce,Pr,Nd,Sm,Tb,Dy,Er)、Ni、Al−Feやフェライト(Fe3O4、(FeCo)3O4)など)等から選択される材料の層である。

【0047】

例えば、中間層30が金属の場合は、GMR(Giant Magnetoresistance)効果が発現する。中間層30が絶縁体の場合は、TMR(Tunneling Magnetoresistance)効果が発現する。例えば、歪検知素子部50においては、例えば、歪抵抗変化部50sの積層方向に沿って電流を流すCPP(Current Perpendicular to Plane)−GMR効果が用いられる。

【0048】

また、中間層30として、絶縁層の一部に1nm以上5nm程度の幅(例えば径)の金属電流パスが膜厚方向に貫通して複数形成された、CCP(Current-Confined-Path)スペーサー層を用いることができる。この場合も、CCP−GMR効果が用いられる。

【0049】

このように、本実施形態においては、歪検知素子部50における逆磁歪現象が用いられる。これにより、高感度な検知が可能になる。逆磁歪効果を用いる場合、例えば、外部から加えられる歪に対して、第1磁性層10及び第2磁性層20の少なくともいずれかの磁性層の磁化方向が変化させられる。外部から加えられる歪(有無及びその程度など)によって、2つの磁性層の磁化の相対的な角度が変わる。外部から加えられる歪によって電気抵抗が変わるため、歪検知素子部50は、歪センサとして機能する。

【0050】

図4は、第1の実施形態に係る歪検知装置の一部の構成を例示する模式的斜視図である。

図4に表したように、歪検知素子部50は、例えば、第1電極51と、第2電極52と、を含む。第1電極51と第2電極52との間に歪抵抗変化部50sが設けられている。この例では、歪抵抗変化部50sにおいては、第1電極51の側から第2電極52に向けて、バッファ層41(兼シード層、厚さ数nm)、反強磁性層42(厚さ数nm)、磁性層43(厚さ数nm)、Ru層44、第2磁性層20(厚さ数nm)、中間層30(厚さ数nm)、第1磁性層10及びキャップ層45(厚さ数nm)が、この順で設けられている。

【0051】

第2磁性層20には、例えば、磁性積層膜が用いられる。第1磁性層10は、磁性積層膜10a(厚さ約1nm)と、磁性積層膜10aとキャップ層45との間に設けられた高磁歪磁性膜10b(厚さ数nm)と、を含む。

【0052】

第1電極51及び第2電極52には、例えば、非磁性体であるAu、Cu、Ta、Al等を用いることができる。第1電極51及び第2電極52として、軟磁性体の材料を用いることで、歪抵抗変化部50sに影響を及ぼす外部からの磁気ノイズを低減することができる。軟磁性体の材料としては、例えば、パーマロイ(NiFe合金)や珪素鋼(FeSi合金)を用いることができる。歪検知素子部50は、アルミ酸化物(例えばAl2O3)やシリコン酸化物(例えばSiO2)等の絶縁体で覆われる。

【0053】

第1磁性層10及び第2磁性層20の少なくともいずれかの磁性層の磁化方向は、応力に応じて変化する。少なくともいずれかの磁性層(応力に応じて磁化方向が変化する磁性層)の磁歪定数の絶対値は、例えば、10−5以上に設定する。これにより、逆磁歪効果によって、外部から加えられる歪みに応じて磁化の方向が変化する。例えば、第1磁性層10及び第2磁性層20の少なくともいずれかには、Fe、Co及びNiなどのような金属または、それらを含む合金などが用いられる。用いる元素や添加元素などによって、磁歪定数は大きく設定される。

【0054】

例えば、中間層30としてMgOのような酸化物が用いられる。MgO層上の磁性層は、一般的にプラスの磁歪定数を有する。例えば、中間層30の上に第1磁性層10を形成する場合、第1磁性層10として、CoFeB/CoFe/NiFeの積層構成の磁化自由層を用いる。最上層のNiFe層をNiリッチにすると、NiFe層の磁歪定数はマイナスでその絶対値が大きくなる。酸化物層上のプラスの磁歪が打ち消されることを抑制するために、最上層のNiFe層のNi組成は、一般的に用いられるNi81Fe19のパーマロイ組成と比較して、Niリッチにしない。具体的には、最上層のNiFe層におけるNiの比率は、80原子パーセント(atomic%)未満とすることが好ましい。第1磁性層10を磁化自由層とする場合には、第1磁性層10の厚さは、例えば、1nm以上20nm以下が好ましい。

【0055】

第1磁性層10が磁化自由層である場合において、第2磁性層20は、磁化固定層でも磁化自由層でも良い。第2磁性層20が磁化固定層である場合、外部から歪が加えられても第2磁性層20の磁化の方向は実質的に変化しない。そして、第1磁性層10と第2磁性層20との間での相対的な磁化の角度によって電気抵抗が変化する。電気抵抗の違いによって歪の有無が検知される。

【0056】

第1磁性層10及び第2磁性層20の両方が磁化自由層である場合には、例えば、第1磁性層10の磁歪定数は、第2磁性層20の磁歪定数とは異なるように設定される。

【0057】

第2磁性層20が磁化固定層である場合も磁化自由層である場合も、第2磁性層20の厚さは、例えば1nm以上20nm以下が好ましい。

【0058】

例えば、第2磁性層20が磁化固定層である場合、例えば、第2磁性層20には、反磁性層/磁性層/Ru層/磁性層の積層構造を用いたシンセティックAF構造などを用いることができる。反磁性層には、例えばIrMnなどが用いられる。また、後述するように、ハードバイアス層を設けても良い。

【0059】

歪検知素子部50では、磁性層のスピンが用いられる。歪検知素子部50に必要な面積は、極めて小さいサイズで十分である。歪検知素子部50の面積は、例えば、10nm×10nm〜20nm×20nm以下程度で十分である。

【0060】

例えば、歪検知素子部50のX軸方向(固定部分63から可動部分64に向かう第1方向)に沿った長さは、20nm以上10μm以下である。歪検知素子部50のX軸方向に沿った長さは、100nm以上3μm以下であることが好ましい。

【0061】

例えば、歪検知素子部50のY軸方向(X軸方向に対して垂直で、X−Y平面に対して平行な方向)に沿った長さは、20nm以上10μm以下である。歪検知素子部50のY軸方向に沿った長さは、100nm以上3μm以下であることが好ましい。

【0062】

例えば、歪検知素子部50のZ軸方向(X−Y平面に対して垂直な方向)に沿った長さは、20nm以上100nm以下である。

【0063】

歪検知素子部50のX軸方向に沿った長さは、歪検知素子部50のY軸方向に沿った長さと同じでも良く、異なっても良い。歪検知素子部50のX軸方向に沿った長さが、歪検知素子部50のY軸方向に沿った長さと異なるときに、形状磁気異方性が生じる。これにより、ハードバイアス層で得られる作用と同様の作用を得ることもできる。

【0064】

歪検知素子部50において流される電流の向きは、第1磁性層10から第2磁性層20に向かう方向でも良く、第2磁性層20から第1磁性層10に向かう方向でも良い。

【0065】

図5は、第1の実施形態に係る歪検知装置の一部の構成を例示する模式的斜視図である。

図5に表したように、この例では、歪検知素子部50は、バイアス層55a及び55b(ハードバイアス層)をさらに含む。バイアス層55a及び55bは、歪抵抗変化部50sに対向して設けられる。

【0066】

この例では、第2磁性層20が磁化固定層である。バイアス層55a及び55bは、第2磁性層20に並置される。バイアス層55a及び55bの間に、歪抵抗変化部50sが配置される。バイアス層55aと歪抵抗変化部50sとの間に絶縁層54aが設けられる。バイアス層55bと歪抵抗変化部50sとの間に絶縁層54bが設けられる。

【0067】

バイアス層55a及び55bは、第1磁性層10にバイアス磁界を印加する。これにより、第1磁性層10の磁化方向を適正な位置にバイアスすることが可能になるとともに、単一磁区化することが可能となる。

【0068】

バイアス層55a及び55bのそれぞれの大きさ(この例ではY軸方向に沿った長さ)は、例えば、100nm以上10μm以下である。

【0069】

絶縁層54a及び54bのそれぞれの大きさ(この例ではY軸方向に沿った長さ)は、例えば、1nm以上5nm以下である。

【0070】

本実施形態に係る歪検知装置310においては、トランジスタ112が形成された基板の上方に、歪検知素子部50が形成されている。トランジスタ112と、歪検知素子部50とは、実装工程で用いられるようなワイヤではなく、ウェーハ製造工程で一貫して形成される配線層で接続されている。これにより、歪検知装置の小型化が可能になり、微小領域で歪を高感度に検知することができる。

【0071】

トランジスタと歪検知素子部とを共通の基板上に形成することで、例えば、演算回路、増幅回路及び通信回路などの、センサで得られた情報を処理する回路(処理回路113など)を歪検知素子部50と同じ基板上に形成することができる。高感度なセンサを演算回路と一体として形成することで、システム全体としてみたときに、小型化が実現できる。また、低消費電力化を実現することができる。

【0072】

本実施形態においては、例えば、高感度のセンサを用い、さらに、そのセンサで得られた信号を演算処理する回路が、共通の基板上にシステムオンチップとして実現される。

【0073】

トランジスタ112の上方に可動部分64(ダイアフラム部61b)を設ける場合、現実的に得られる可動範囲(Z軸方向に沿った距離)は、10μm以下である。実際には、さらに小さい可動範囲のほうが形成しやすい。このような小さい可動範囲の場合でも歪を正確に測定するためには、歪センサとして非常に高感度なものが必要となる。また、微小点接触状態においても圧力を正確に測定するために、ダイアフラムの面積も小さいことが望ましい。ダイアフラムが小さくなると、ダイアフラムの膜厚を薄くしなければ、たわみ量も小さくなってしまい、感度良く測定することができない。外部環境で壊れにくい状態で圧力センサとして使用するためには、ダイアフラムの膜厚もあまり薄くすることはできないため、ダイアフラム径が小さくなると、圧力センサの感度も悪くなってしまう。

【0074】

以上のように、ダイアフラムの上下可動範囲が小さいこと、および、ダイアフラムの直径が小さい状態で使うこと、の2つの状況を実現しようとすると、歪センサとしては感度が高いものが望まれる。実施形態に係る歪検知素子部50は、この要求を満たすため、このようなことが可能になる。

【0075】

実施形態に係る歪検知素子部50においては、実質的に素子サイズの大きさに依存せず、小さい素子面積でも高い歪感度αを実現することができる。歪感度αは、例えば、α=(ΔR/Rmin)/εで表される。Rminは、低い状態の抵抗であり、ΔRは、抵抗変化量である。εは、歪であり、Δl/lで表される。ここで、lは初期の長さであり、Δlは変位量である。

【0076】

例えば、Siを用いたピエゾ抵抗型歪センサの場合には、歪感度αは用いる材料で決まり、例えば歪感度αは、約130である。また、Siを用いたピエゾ抵抗型歪センサの場合には、一辺が100μm程度の素子の面積が必要である。単位面積あたりの歪感度αは、例えば130/100μm2であり、約1010となる。

【0077】

一方、本実施形態に係る歪検知素子部50(スピン歪センサ)の場合には、歪感度αに上限はなく、1000程度のものは容易に実現できる。この歪感度αを実現するために必要な素子面積は、一辺が20nm程度である。このため、例えば、単位面積あたりの歪感度αは、約1017となる。このように、実施形態においては、従来のSiを用いたMEMS構造(Si−MEMS:Micro Electro Mechanical Systems)の圧力センサの場合と比較して、約7桁の単位面積あたりの感度向上が可能になる。

【0078】

本実施形態によれば、スピン歪センサ技術を用いることで、高い歪感度が得られ、例えば、演算回路を混載した歪・圧力センサの実現が可能となる。

【0079】

図6(a)〜図6(c)は、第1の実施形態に係る歪検知装置の一部の構成を例示する模式図である。

これらの図は、検知部120の1つの例である検知部121の構成を示している。図6(a)は斜視図である。図6(b)は、平面図である。図6(c)は、図6(a)のA1−A2線断面図である。

【0080】

図6(a)に表したように、可動部分64は、空洞部70の中において、Z軸方向に沿って動く。検知部121(検知部120)の厚さLz(Z軸方向に沿った長さ)は、例えば、1μm以上10μm以下である。この例では、ダイアフラム部61bが設けられている。可動部分64のサイズは、ダイアフラム部61bのサイズとなる。

【0081】

図6(b)に表したように、可動部分64は、ダイアフラム部61bを含む。ダイアフラム部61bのY軸方向(固定部分63から可動部分64に向かうX軸方向に対して垂直で主面111aに対して平行な方向)に沿った幅は、第1配線層61及び第2配線層62のY軸方向に沿った幅よりも広い。

【0082】

X軸方向に沿った可動部分64の長さLx(ダイアフラム部61bのX軸方向に沿った長さに相当)は、10μm以上500μm以下である。長さLxは、50μm以上200μm以下であることが好ましい。また、Y軸方向に沿った可動部分64の長さLy(ダイアフラム部61bのY軸方向に沿った長さに相当)は、10μm以上500μm以下である。長さLyは、50μm以上200μm以下であることが好ましい。

【0083】

長さLxは、長さLy以上であることが好ましい。例えば、長さLxは、長さLyの1.5倍以上5倍以下である。

【0084】

ダイアフラム部61bの一部は、固定部分63として、非空洞部71に固定されていても良い。ダイアフラム部61bのうちで非空洞部71に固定されている部分の幅L1(X軸方向に沿った幅)は、例えば、長さLxの1/10以上1/3以下である。

【0085】

図6(c)に表したように、可動部分64(ダイアフラム部61b)はZ軸方向に沿って撓む。空洞部70のZ軸方向に沿う高さLz70は、例えば、1μm以上10μm以下である。可動部分64は、空洞部70の中で動く。可動部分64(ダイアフラム部61b)の先端のZ軸方向に沿う移動の距離(Z軸方向に沿う距離)は、例えば、1μm以上10μm以下である。可動部分64とトランジスタ112(半導体回路部110)との間の距離は、例えば、1μm以上10μm以下の範囲で変化する。

【0086】

可動部分64(ダイアフラム部61b)の動きに応じて、歪検知素子部50に応力が加わる。この応力に応じて、歪検知素子部50の電気抵抗が変化する。

【0087】

第1埋め込み配線61c、第2埋め込み配線62c、第1配線層61及び第2配線層62を介して、歪検知素子部50に電流が流され、電気抵抗が検知される。これにより、可動部分64(ダイアフラム部61b)に加えられる応力が検知される。すなわち、歪検知装置310に加わる歪みが検知される。

【0088】

第1埋め込み配線61c、第2埋め込み配線62c、第1配線層61及び第2配線層62には、例えば、Cu及びAlなどの金属が用いられる。

【0089】

ダイアフラム部61bには、例えば、SiO2、アモルファスSi、各種酸化物、及び、各種窒化物の単層膜または積層膜などが用いられる。なお、後述するように、第1配線層61(第1配線層61層及び第2配線層62の少なくともいずれか)が、ダイアフラム部61bの機能を果たすこともできる。この場合には、ダイアフラム部61b(第1配線層61)には、Cu及びAlなどの金属が用いられる。このように、実施形態においては、トランジスタ112と混載されたダイアフラムの構成が採用される。

【0090】

一方、従来のSi−MEMSではSOI(Silicon on insulator)基板が用いられる。この場合には、SOIが設けられる基板(Si単結晶基板)の裏面が選択的に除去され、SOIの酸化膜がダイアフラムとなり、SOIのシリコン膜が能動部となる。従来の構成においては、SOI基板を用いる発想であるため、使用できる膜の材料が、酸化膜と、その上に形成されたシリコン膜に限定される。これは、RIE(Reactive Ion Etching)プロセスなどでエッチングすることが、単結晶Siを歪センサとして用いるためには必要であるためである。基板裏面からエッチングするプロセスとなるため、必然的に基板上に形成するトランジスタの上に、ダイアフラムを形成するということが極めて困難というのが従来の発想である。また、このように単結晶Siを歪センサとして用いる場合には、ダイアフラムの材料は、必然的に上述のような極めて限定された材料となってしまう。

【0091】

これに対して、実施形態においては、トランジスタ112上に、後述する犠牲層が形成され、犠牲層の上に可動部分64が形成される。例えば、トランジスタ112上に形成された犠牲層の上に成膜された膜が、ダイアフラム部61bとして用いられる。そのため、ダイアフラム部61bとして任意の材料を用いることが可能である。これにより、材料を適切に選択することで、ダイアフラム特性が向上でき、さらに、例えば、ダイアフラム部61bの応力を実質的にゼロにすることができる。また、SOI基板以外の基体の上に形成したダイアフラム上に単結晶Siを形成することは極めて困難だが、スピン歪センサならば形成することが可能となる。

【0092】

実施形態においては、犠牲層の上に可動部分64を形成し、犠牲層を犠牲層の上面から除去する構成を採用する。この場合、犠牲層を厚くすることが困難であるため、可動部分64の可動範囲は、SOI基板を用いたSi−MEMSに比べて限定的になる。すなわち、ダイアフラムの可動量が小さく、歪変化量が小さくなる。スピン歪センサにおいては高い歪感度が実現可能なため、ダイアフラムの可動量が小さい場合においても、センサとして十分機能することが可能であると、本願発明者は考えた。

【0093】

ダイアフラム部61bの厚さは、例えば、50nm以上1μm以下である。100nm以上500nm以下であることが好ましい。

【0094】

図6(c)に表したように、第1配線層61と第2配線層62との間には、絶縁層65(例えばSiO2層など)が設けられる。また、第1配線層61の可動部分64側の端部と、第2配線層62の可動部分64側の端部とに接して絶縁層66(例えばSiO2層など)が設けられる。

【0095】

このような構成を有する検知部120(検知部121)を用いることで、微小領域で歪を高感度に検知することができる。

【0096】

この例では、可動部分64(例えばダイアフラム部61b)、及び、空洞部70のZ軸方向に沿ってみた時の形状は、実質的に長方形であるが、実施形態はこれに限らない。これらの形状は任意である。

【0097】

図7(a)〜図7(c)は、第1の実施形態に係る歪検知装置の一部の構成を例示する模式図である。

これらの図は、検知部120の1つの例である検知部122の構成を示している。図7(a)は斜視図である。図7(b)は、平面図である。図7(c)は、図7(a)のA1−A2線断面図である。

【0098】

図7(a)〜図7(c)に表したように、この例では、可動部分64(例えばダイアフラム部61b)のZ軸方向に沿ってみたときの形状は、略円形(扁平円も含む)である。そして、空洞部70のZ軸方向に沿ってみた時の形状も、略円形(扁平円も含む)である。

この場合も、微小領域で歪を高感度に検知することができる。

【0099】

図8(a)〜図8(c)は、第1の実施形態に係る歪検知装置の一部の構成を例示する模式図である。

これらの図は、検知部120の1つの例である検知部123の構成を示している。図8(a)は斜視図である。図8(b)は、平面図である。図8(c)は、図8(a)のA1−A2線断面図である。

【0100】

図8(a)〜図8(c)に表したように、この例では、可動部分64の端は固定部分63に接続されており、可動部分64の他の端(この例では、3つの端)が、固定部67a、67b及び67cで、非空洞部71に固定されている。可動部分64は、固定部分63と、3つの固定部とによって、4箇所で支持されている。固定部67a、67b及び67cには、例えば、SiO2などの絶縁層が用いられる。

【0101】

この構成においては、図8(c)に表したように、可動部分64の中央部がZ軸方向に沿って動く。

【0102】

この例では、可動部分64は、4箇所で支持されているが、可動部分64に、可動部分64を貫通する孔64hが設けられていると見なすこともできる。

【0103】

このように、可動部分64は、複数の箇所によって支持されても良い。この場合も、微小領域で歪を高感度に検知することができる。

【0104】

本実施形態に係る歪検知装置310においては、外部から何らかの作用が可動部分64(例えばダイアフラム部61b)に与えられ、可動部分64(例えばダイアフラム部61b)の形状が変化する。この形状の変化に伴って歪検知素子部50に歪みが発生し、この歪みを電気抵抗の変化として検知する。歪検知装置310は、例えば圧力センサとして用いることができる。さらに、歪検知装置310は、加速センサとして用いることができる。さらに、歪検知装置310は、温度センサとして用いることができる。温度センサとして用いる場合には、温度に応じて可動部分64(例えばダイアフラム部61b)は伸縮し、これによる歪が検知される。例えば、温度膨張係数が大きい材料を可動部分64(例えばダイアフラム部61b)として用いることで、高感度の温度センサを提供することができる。

【0105】

図9は、第1の実施形態に係る別の歪検知装置の構成を例示する模式的斜視図である。 図9に表したように、本実施形態に係る歪検知装置320は、検知部120の上に設けられた圧力トランスデュース部130をさらに含む。

【0106】

圧力トランスデュース部130は、センサ保護部132と、圧力トランスデュース空洞部131と、を有する。圧力トランスデュース空洞部131は、例えば、センサ保護部132を形成する材料が設けられていない部分である。

【0107】

図10は、第1の実施形態に係る別の歪検知装置の一部の構成を例示する模式的斜視図である。

図10は、圧力トランスデュース部130の構成の1つの例を示している。

センサ保護部132には、例えば、Al2O3、及び、SiO2などの絶縁材料が用いられる。圧力トランスデュース空洞部131のZ軸方向にみたときの形状は、例えば、検知部120の空洞部70のZ軸方向にみたときの形状に沿う。但し、圧力トランスデュース空洞部131の形状は任意である。圧力トランスデュース空洞部131の内部には、例えば、空気が充填されている。圧力トランスデュース空洞部131は、例えば、空気の振動を歪検知素子部50に伝える。

【0108】

この構成を応用すると、音を検知するマイクロフォンを作製することも可能である。このように、実施形態に係る歪検知装置320は、音などの、任意の媒体における振動を検知する検知装置に応用できる。

【0109】

圧力トランスデュース部130を設けることにより、外部の圧力の変化をより効率的に歪検知素子部50に伝えることができる。これにより、より高精度でより安定した検知が可能になる。

【0110】

この例では、圧力トランスデュース空洞部131のZ軸方向にみたときの形状は、円形(扁平円も含む)であり、その直径131wは、例えば、1μm以上500nm以下である。センサ保護部132の厚さt130は、例えば300nm以上100μm以下である。ただし、実施形態はこれには限らない。これらの形状及び大きさは任意である。

【0111】

図11は、第1の実施形態に係る別の歪検知装置の一部の構成を例示する模式的斜視図である。

図11は、圧力トランスデュース部130の構成の別の例を示している。

この例では、圧力トランスデュース空洞部131の内部には、例えば、圧力トランスデュース材料133が配置されている。圧力トランスデュース材料133には、例えば、ジェル又は液体の例えばシリコーンなどが用いられる。

【0112】

この構成を用いる場合には、例えば、歪検知装置の製造の実装工程で、圧力トランスデュース部130と外部との間で圧力が伝達されるような実装が行われる。

【0113】

図1に関して説明した処理回路113は、例えば、歪検知素子部50で得られた信号の増幅処理や、センサ信号のA/D変換処理などを行うことができる。このように、半導体回路部110は、歪検知素子部50に流れる電流に基づく信号を処理する。処理回路113は、さらに、センサ信号のデータを他の電子機器に送信するための処理を行うことができる。さらに、処理回路113は、センサ信号から有意義な情報を引き出すためのデータマイニング処理(例えばノイズ除去処理など)を行うこともできる。

【0114】

図12(a)〜図12(c)は、第1の実施形態に係る別の歪検知装置及び電子機器の構成を例示する模式図である。

図12(a)は、本実施形態に係る別の歪検知装置311の構成を例示する模式的斜視図である。図12(b)は、歪検知装置311に設けられる送信回路117の例を示している。図12(c)は、歪検知装置311と組み合わせて用いられる電子機器118dの例を示している。

【0115】

図12(a)に表したように、歪検知装置311は、半導体回路部110及び検知部120に加え、アンテナ115と、電気配線116と、をさらに含む。アンテナ115は、電気配線116を介して、半導体回路部110と接続される。

【0116】

図12(b)に表したように、送信回路117が歪検知装置311に設けられる。送信回路117は、歪検知素子部50に流れる電気信号に基づくデータを無線で送信する。送信回路117の少なくとも一部は、半導体回路部110に設けることができる。半導体回路部110は、歪検知素子部50に流れる電気信号に基づくデータを無線で送信する送信回路117を含むことができる。

【0117】

図12(c)に表したように、歪検知装置311と組み合わせて用いられる電子機器118dには、受信部118が設けられる。電子機器118dとして、例えば、携帯端末などの電子装置が用いられる。

【0118】

例えば、送信回路117を含む歪検知装置311と、受信部118を含む電子機器118dと、を組み合わせて用いることで、より便利になる。

【0119】

この例では、図12(b)に表したように、歪検知装置311には、電子機器118dからの制御信号を受信する受信回路117rが設けられている。例えば、受信回路117rの少なくとも一部は、半導体回路部110に設けることができる。受信回路117rを設けることにより、例えば、電子機器118dを操作することで、歪検知装置311の動作を制御することができる。

【0120】

図12(b)に表したように、この例では、歪検知装置311には、送信回路117として、例えば、歪検知素子部50に接続されたADコンバータ117aと、マンチェスター符号化部117bと、が設けられる。さらに、切替部117cが設けられ、送信と受信を切り替える。タイミングコントローラ117dによりこの切り替えが制御される。そして、受信回路117rとして、データ訂正部117eと、同期部117fと、判定部117gと、が設けられる。さらに、電圧制御発振器117h(VCO)が設けられている。

【0121】

一方、図12(c)に表したように、電子機器118dには、マンチェスター符号化部117b、切替部117c、タイミングコントローラ117d、データ訂正部117e、同期部117f、判定部117g及び電圧制御発振器117hが設けられ、さらに記憶部118a及び中央演算部118b(CPU)が設けられている。

【0122】

以下、本実施形態に係る歪検知装置310の製造方法の例として、図6(a)〜図6(c)に例示した検知部121のように四角形のダイアフラム部61bを有する歪検知装置の製造方法の例について説明する。

【0123】

図13(a)、図13(b)、図14(a)、図14(b)、図15(a)、図15(b)、図16(a)、図16(b)、図17(a)、図17(b)、図18(a)、図18(b)、図19(a)、図19(b)、図20(a)、図20(b)、図21(a)、図21(b)、図22(a)、図22(b)、図23(a)、図23(b)、図24(a)及び図24(b)は、第1の実施形態に係る歪検知装置の製造方法を例示する模式図である。

図13(a)〜図24(a)は、模式的平面図であり、図13(b)〜図24(b)は、模式的断面図である。

【0124】

図13(a)及び図13(b)に表したように、半導体基板111の表面部分に半導体層112Mが設けられている。半導体層112Mの上面に素子分離絶縁層112Iを形成する。半導体層112Mの上に、図示しない絶縁層を介して、ゲート112Gを形成する。ゲート112Gの両側に、ソース112Sとドレイン112Dとを形成し、トランジスタ112が形成される。この上に層間絶縁膜114aを形成し、さらに層間絶縁膜114bを形成する。

【0125】

非空洞部71となる領域において、層間絶縁膜114a及び114bの一部に、トレンチ及び孔を形成する。孔に導電材料を埋め込んで、接続ピラー114c〜114eを形成する。この例では、接続ピラー114cは、1つのトランジスタのソース112Sに接続され、接続ピラー114dはドレイン112Dに接続されている。接続ピラー114eは、別のトランジスタのソース112Sに接続されている。トレンチに導電材料を埋め込んで、配線部114f及び配線部114gを形成する。配線部114fは、接続ピラー114c及び接続ピラー114dに接続される。配線部114gは、接続ピラー114eに接続される。層間絶縁膜114bの上に、層間絶縁膜114hを形成する。

【0126】

図14(a)及び図14(b)に表したように、層間絶縁膜114hの上に層間絶縁膜114iとなるSiO2を例えばCVDで形成する。層間絶縁膜114iの所定の位置に孔を形成し、導電材料(金属材料)を埋め込み、上面をCMPで平坦化する。これにより、配線部114fに接続された接続ピラー114jと、配線部114gに接続された接続ピラー114kと、が形成される。

【0127】

図15(a)及び図15(b)に表したように、層間絶縁膜114iの空洞部70となる領域に溝を形成し、その溝に犠牲層114lを埋め込む。犠牲層114lには、例えば、SiGeなどが用いられる。犠牲層114lには、低温で成膜できる材料が用いられる。

【0128】

図16(a)及び図16(b)に表したように、層間絶縁膜114i及び犠牲層114lの上に、ダイアフラム部61bとなる絶縁膜61bf(SiO2など)を形成する。絶縁膜61bfに孔を設け、その孔に導電材料(金属)を埋め込み、接続ピラー61fa及び接続ピラー62faを形成する。接続ピラー61faは接続ピラー114kと接続され、接続ピラー62faは接続ピラー114jと接続されている。

【0129】

図17(a)及び図17(b)に表したように、絶縁膜61bf、接続ピラー61fa及び接続ピラー62faの上に、第1配線層61となる導電層61fを形成する。

【0130】

図18(a)及び図18(b)に表したように、導電層61fの上に、歪検知素子部50となる積層膜50fを形成する。

【0131】

図19(a)及び図19(b)に表したように、積層膜50fを所定の形状に加工し、その上に、絶縁層65となる絶縁膜65f(SiO2など)を形成する。

【0132】

図20(a)及び図20(b)に表したように、絶縁膜65fの一部を除去し、導電層61fを所定の形状に加工する。これにより、第1配線層61の形状が形成される。このとき、導電層61fの一部は、接続ピラー62faに接続された接続ピラー62fbとなる。さらに、この上に、絶縁層66となる絶縁膜66fを形成する。

【0133】

図21(a)及び図21(b)に表したように、絶縁膜66fに開口部66pを形成する。これにより、接続ピラー62fbが露出する。

【0134】

図22(a)及び図22(b)に表したように、この上に、第2配線層62となる導電層62fを形成する。導電層62fの一部は、接続ピラー62fbと接続される。

【0135】

図23(a)及び図23(b)に表したように、導電層62fを所定の形状に加工する。これにより、第2配線層62が形成される。第2配線層62は、接続ピラー62fbに接続されている。

【0136】

図24(a)及び図24(b)に表したように、絶縁膜66fに所定の形状の開口部66oを形成する。開口部66oを介して、絶縁膜61bfを加工し、さらに、犠牲層114lを除去する。これにより、空洞部70が形成される。犠牲層114lの除去においては、例えば、犠牲層114lの上面(犠牲層114lの半導体基板111とは反対側の面)から犠牲層114lを除去(例えばエッチング)する。

これにより、本実施形態に係る歪検知装置310が形成できる。

【0137】

図25(a)〜図25(c)は、第1の実施形態に係る歪検知装置の一部の構成を例示する模式図である。

これらの図は、検知部120の1つの例である検知部124の構成を示している。図25(a)は斜視図である。図25(b)は、平面図である。図25(c)は、図25(a)のA1−A2線断面図である。

【0138】

図25(a)に表したように、この例では、ダイアフラム部61bが設けられず、ダイアフラム部61bの機能を第1配線層61が果たす。

【0139】

第1配線層61は、第2配線層62よりも下側に設けられている。すなわち、第1配線層61は、第2配線層62と半導体回路部110(図25(a)では図示していない)との間に設けられている。

【0140】

第1配線層61の可動部分64におけるY軸方向(固定部分63から可動部分64に向かうX軸方向に対して垂直で主面111aに対して平行な方向)に沿った幅は、第2配線層62の可動部分64におけるY軸方向に沿った幅よりも広い。

【0141】

ダイアフラム部61bが設けられない場合は、可動部分64のY軸方向の長さLyは、第1配線層61のうちの可動部分64におけるY軸方向の長さに相当する。可動部分64のX軸方向の長さLxは、第1配線層61のうちの可動部分64におけるX軸方向の長さに相当する。

【0142】

ダイアフラム部61bの機能を第1配線層61が果たすことで、構成が簡単になり、製造工程も簡単になる。このような検知部124においても、微小領域で歪を高感度に検知することができる。

【0143】

以下、図25(a)〜図25(c)に例示した検知部124を有する歪検知装置の製造方法の例について説明する。

【0144】

図26(a)、図26(b)、図27(a)、図27(b)、図28(a)、図28(b)、図29(a)、図29(b)、図30(a)、図30(b)、図31(a)、図31(b)、図32(a)、図32(b)、図33(a)及び図33(b)は、第1の実施形態に係る歪検知装置の製造方法を例示する模式図である。

図26(a)〜図33(a)は、模式的平面図であり、図26(b)〜図33(b)は、模式的断面図である。以下では、図13(a)〜図15(b)に関して説明したのと同様の工程の後の工程について説明する。

【0145】

図26(a)及び図26(b)に表したように、接続ピラー114j、接続ピラー114k、層間絶縁膜114i及び犠牲層114lの上に、第1配線層61となる導電層61fを形成する。

【0146】

図27(a)及び図27(b)に表したように、導電層61fの上に、歪検知素子部50となる積層膜50fを形成する。

【0147】

図28(a)及び図28(b)に表したように、積層膜50fを所定の形状に加工し、その上に、絶縁層65となる絶縁膜65f(SiO2など)を形成する。

【0148】

図29(a)及び図29(b)に表したように、絶縁膜65fの一部を除去し、導電層61fを所定の形状に加工する。これにより、第1配線層61の形状が形成される。第1配線層61は、接続ピラー114kと接続される。このとき、導電層61fの一部は、接続ピラー114jに接続された接続ピラー62fbとなる。さらに、この上に、絶縁層66となる絶縁膜66fを形成する。

【0149】

図30(a)及び図30(b)に表したように、絶縁膜66fに開口部66pを形成する。これにより、接続ピラー62fbが露出する。

【0150】

図31(a)及び図31(b)に表したように、この上に、第2配線層62となる導電層62fを形成する。導電層62fの一部は、接続ピラー62fbと接続される。

【0151】

図32(a)及び図32(b)に表したように、導電層62fを所定の形状に加工する。これにより、第2配線層62が形成される。第2配線層62は、接続ピラー62fbに接続されている。

【0152】

図33(a)及び図33(b)に表したように、絶縁膜66fに所定の形状の開口部66oを形成する。開口部66oを介して、犠牲層114lを除去する。これにより、空洞部70が形成される。

これにより、検知部124を有する歪検知装置が形成できる。この構成においては、ダイアフラム部61bの機能を第1配線層61が果たし、構成が簡単であるため、製造も簡単になる。

【0153】

図34は、第1の実施形態に係る別の歪検知装置の構成を例示する模式的斜視図である。

図34に表したように、本実施形態に係る別の歪検知装置330においては、検知部120の第1埋め込み配線61c及び第2埋め込み配線62cは、空洞部70の下方に設けられたトランジスタ112と電気的に接続されている。

【0154】

この例では、歪検知素子部50に流れる電流は、第1配線層61、第2配線層62、第1埋め込み配線61c及び第2埋め込み配線62cを介して、空洞部70の下に設けられたトランジスタ112に流れる。

【0155】

歪検知素子部50の下に設けられたトランジスタ112が、歪検知素子部50の抵抗変化を検知する構成により、例えば、チップ面積がより小さくできる。

【0156】

(第2の実施形態)

本実施形態は、歪検知装置の製造方法に係る。

図35は、第2の実施形態に係る歪検知装置の製造方法を例示するフローチャート図である。

図35に表したように、本実施形態に係る歪検知装置の製造方法においては、半導体基板111の上にトランジスタ112を形成する(ステップS110)。例えば、図13(a)及び図13(b)に関して説明した処理を行う。

【0157】

本製造方法においては、半導体基板111の上に層間絶縁層を形成し、トランジスタ112の上に犠牲層114lを形成する(ステップS120)。例えば、図14(a)〜図15(b)に関して説明した処理を行う。この層間絶縁層は、例えば、層間絶縁膜114iを含む。

【0158】

層間絶縁層(例えば層間絶縁膜114i)と犠牲層114lとの上に、第1配線層61となる第1導電層(導電層61f)を形成する(ステップS130)。例えば、図17(a)及び図17(b)に関して説明した処理を行う。なお、この前に、ダイアフラム部61bを形成しても良い。

【0159】

犠牲層114lの上の第1導電層(導電層61f)の上に、第1磁性層10を含む歪検知素子部50を形成する(ステップS140)。例えば、図18(a)〜図19(b)に関して説明した処理を行う。

【0160】

歪検知素子部50の上に第2配線層62となる第2導電層(導電層62f)を形成する(ステップS150)。例えば、図22(a)〜図23(b)に関して説明した処理を行う。

【0161】

層間絶縁層の中に、第1導電層(導電層61f)を半導体基板111と電気的に接続する第1埋め込み配線61cと、第2導電層(導電層62f)を半導体基板111と電気的に接続する第2埋め込み配線62cと、を形成する(ステップS160)。例えば、図13(a)、図13(b)、図14(a)、図14(b)、図16(a)、図16(b)、図20(a)及び図20(b)に関して説明した処理を行う。ステップS160は、例えば、上記のステップS110〜ステップS150の間、及び、ステップS150の後、の少なくともいずれかの工程において、1回、または、複数の処理により実施される。

【0162】

そして、犠牲層114lを除去する(ステップS170)。例えば、図24(a)及び図24(b)に関して説明した処理を行う。

【0163】

これにより、微小領域で歪を高感度に検知することができる歪検知装置の製造方法を提供できる。

【0164】

上記の犠牲層114lを除去する工程(ステップS170)は、例えば、犠牲層114lの上面(犠牲層114lの半導体基板111とは反対側の面)から犠牲層114lを除去(例えばエッチング)することを含む。

【0165】

実施形態によれば、微小領域で歪を高感度に検知することができる歪検知装置及びその製造方法が提供される。

【0166】

以上、具体例を参照しつつ、本発明の実施の形態について説明した。しかし、本発明の実施形態は、これらの具体例に限定されるものではない。例えば、歪検知装置に含まれる半導体回路部、半導体基板、トランジスタ、歪検知部、固定部分、可動部分、歪検知素子部、第1磁性層、第2磁性層、中間層、第1配線層、第2配線層、ダイアフラム部、第1埋め込み配線、第2埋め込み配線、及びトランスデューサ部などの各要素の具体的な構成に関しては、当業者が公知の範囲から適宜選択することにより本発明を同様に実施し、同様の効果を得ることができる限り、本発明の範囲に包含される。

【0167】

また、各具体例のいずれか2つ以上の要素を技術的に可能な範囲で組み合わせたものも、本発明の要旨を包含する限り本発明の範囲に含まれる。

【0168】

その他、本発明の実施の形態として上述した歪検知装置及びその製造方法を基にして、当業者が適宜設計変更して実施し得る全ての歪検知装置及びその製造方法も、本発明の要旨を包含する限り、本発明の範囲に属する。

【0169】

その他、本発明の思想の範疇において、当業者であれば、各種の変更例及び修正例に想到し得るものであり、それら変更例及び修正例についても本発明の範囲に属するものと了解される。

【0170】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0171】

10…第1磁性層、 10a…磁性積層膜、 10b…高磁歪磁性膜、 20…第2磁性層、 30…中間層、 41…バッファ層、 42…反強磁性層、 43…磁性層、 44…Ru層、 45…キャップ層、 50…歪検知素子部、 50f…積層膜、 50s…歪抵抗変化部、 51…第1電極、 52…第2電極、 54a、54b…絶縁層、 55a、55b…バイアス層、 60…可動梁、 61…第1配線層、 61b…ダイアフラム部、 61bf…絶縁膜、 61c…第1埋め込み配線、 61f…導電層、 61fa…接続ピラー、 62…第2配線層、 62c…第2埋め込み配線、 62f…導電層、 62fa、62fb…接続ピラー、 63…固定部分、 64…可動部分、 64h…孔、 65…絶縁層、 65f…絶縁膜、 66…絶縁層、 66f…絶縁膜、 66o、66p…開口部、 67a〜67c…固定部、 70…空洞部、 71…非空洞部、 110…半導体回路部、 111…半導体基板、 111a…主面、 111b…素子領域、 112…トランジスタ、 112D…ドレイン、 112G…ゲート、 112I…素子分離絶縁層、 112M…半導体層、 112S…ソース、 113…処理回路、 114a、114b…層間絶縁膜、 114c〜114e…接続ピラー、 114f、114g…配線部、 114h、114i…層間絶縁膜、 114j、114k…接続ピラー、 114l…犠牲層、 115…アンテナ、 116…電気配線、 117…送信回路、 117a…ADコンバータ、 117b…マンチェスター符号化部、117c…切替部、 117d…タイミングコントローラ、 117e…データ訂正部、 117f…同期部、 117g…判定部、 117h…電圧制御発振器、 117r…受信回路、 118…受信部、 118a…記憶部、 118b…中央演算部、 118d…電子機器、 120〜124…検知部、 130…圧力トランスデュース部、 131…圧力トランスデュース空洞部、 131w…直径、 132…センサ保護部、 133…圧力トランスデュース材料、 310、311、320、330…歪検知装置、L1…幅、 Lx、Ly…長さ、 Lz…厚さ、 Lz70…高さ、 t130…厚さ

【特許請求の範囲】

【請求項1】

半導体基板と、前記半導体基板の主面上に設けられたトランジスタと、を有する半導体回路部と、

前記半導体回路部の上に設けられた検知部であって、

前記検知部は、前記トランジスタの上方に設けられた空洞部と、前記主面に対して平行な平面内で前記空洞部と並置された非空洞部と、を有し、

前記検知部は、

前記非空洞部に固定された固定部分と、

前記固定部分から前記空洞部に延び前記トランジスタと離間し前記トランジスタとの間の距離が可変の可動部分と、

を有する可動梁であって、前記固定部分から前記可動部分に向けて延びる第1配線層と第2配線層とを含む、可動梁と、

前記可動部分に固定され、一端が前記第1配線層と電気的に接続され、他端が前記第2配線層と電気的に接続され、第1磁性層を含む歪検知素子部と、

前記非空洞部に設けられ、前記第1配線層と前記半導体回路部とを電気的に接続する第1埋め込み配線と、

前記非空洞部に設けられ、前記第2配線層と前記半導体回路部とを電気的に接続する第2埋め込み配線と、

を含む、前記検知部と

を備えた歪検知装置。

【請求項2】

前記可動部分は、

前記固定部分から前記可動部分に向かう第1方向に対して垂直で前記主面に対して平行な第2方向に沿った幅が、前記第1配線層及び前記第2配線層の前記第2方向に沿った幅よりも広いダイアフラム部をさらに含む請求項1記載の歪検知装置。

【請求項3】

前記第1配線層は、前記第2配線層と前記半導体回路部との間に設けられ、

前記第1配線層の前記可動部分における、前記固定部分から前記可動部分に向かう第1方向に対して垂直で前記主面に対して平行な第2方向に沿った幅は、前記第2配線層の前記可動部分における前記第2方向に沿った幅よりも広い請求項1記載の歪検知装置。

【請求項4】

前記可動部分の前記トランジスタとの前記距離の変化に応じて、前記第1磁性層の磁化方向が変化し、前記磁化方向の変化に伴って前記一端と前記他端との間の電気抵抗が変化する請求項1〜3のいずれか1つに記載の歪検知装置。

【請求項5】

前記歪検知素子部は、

前記第2磁性層と、

前記第1磁性層と前記第2磁性層との間に設けられた非磁性の中間層と、

をさらに含む請求項1〜4のいずれか1つに記載の歪検知装置。

【請求項6】

前記歪検知素子部は、前記第1磁性層に並置され、前記第1磁性層にバイアス磁界を印加するバイアス層をさらに含む請求項1〜5のいずれか1つに記載の歪検知装置。

【請求項7】

前記第1磁性層の磁歪定数は、10−5以上である請求項1〜6のいずれか1つに記載の歪検知装置。

【請求項8】

前記可動部分は、前記可動部分を貫通する孔を有する請求項1〜7のいずれか1つに記載の歪検知装置。

【請求項9】

前記可動部分と前記トランジスタと間の距離は、1マイクロメートル以上10マイクロメートル以下の範囲で変化する請求項1〜8のいずれか1つに記載の歪検知装置。

【請求項10】

前記固定部分から前記可動部分に向かう第1方向に沿った前記可動部分の長さは、10マイクロメートル以上500マイクロメートル以下である請求項1〜9のいずれか1つに記載の歪検知装置。

【請求項11】

前記半導体回路部は、歪検知素子部に流れる電流に基づく信号を処理する処理回路を含む請求項1〜10のいずれか1つに記載の歪検知装置。

【請求項12】

前記半導体回路部は、歪検知素子部に流れる電気信号に基づくデータを無線で送信する送信回路を含む請求項1〜11のいずれか1つに記載の歪検知装置。

【請求項13】

半導体基板の上にトランジスタを形成する工程と、

前記半導体基板の上に層間絶縁層を形成し、前記トランジスタの上に犠牲層を形成する工程と、

前記層間絶縁層と前記犠牲層との上に第1配線層となる第1導電層を形成する工程と、

前記犠牲層の上の前記第1導電層の上に、第1磁性層を含む歪検知素子部を形成する工程と、

前記歪検知素子部の上に第2配線層となる第2導電層を形成する工程と、

前記層間絶縁層の中に、前記第1導電層を前記半導体基板と電気的に接続する第1埋め込み配線と、前記第2導電層を前記半導体基板と電気的に接続する第2埋め込み配線と、を形成する工程と、

前記犠牲層を除去する工程と、

を備えた歪検知装置の製造方法。

【請求項14】

前記犠牲層を除去する前記工程は、前記犠牲層の上面から前記犠牲層を除去することを含む請求項13記載の歪検知装置の製造方法。

【請求項1】

半導体基板と、前記半導体基板の主面上に設けられたトランジスタと、を有する半導体回路部と、

前記半導体回路部の上に設けられた検知部であって、

前記検知部は、前記トランジスタの上方に設けられた空洞部と、前記主面に対して平行な平面内で前記空洞部と並置された非空洞部と、を有し、

前記検知部は、

前記非空洞部に固定された固定部分と、

前記固定部分から前記空洞部に延び前記トランジスタと離間し前記トランジスタとの間の距離が可変の可動部分と、

を有する可動梁であって、前記固定部分から前記可動部分に向けて延びる第1配線層と第2配線層とを含む、可動梁と、

前記可動部分に固定され、一端が前記第1配線層と電気的に接続され、他端が前記第2配線層と電気的に接続され、第1磁性層を含む歪検知素子部と、

前記非空洞部に設けられ、前記第1配線層と前記半導体回路部とを電気的に接続する第1埋め込み配線と、

前記非空洞部に設けられ、前記第2配線層と前記半導体回路部とを電気的に接続する第2埋め込み配線と、

を含む、前記検知部と

を備えた歪検知装置。

【請求項2】

前記可動部分は、

前記固定部分から前記可動部分に向かう第1方向に対して垂直で前記主面に対して平行な第2方向に沿った幅が、前記第1配線層及び前記第2配線層の前記第2方向に沿った幅よりも広いダイアフラム部をさらに含む請求項1記載の歪検知装置。

【請求項3】

前記第1配線層は、前記第2配線層と前記半導体回路部との間に設けられ、

前記第1配線層の前記可動部分における、前記固定部分から前記可動部分に向かう第1方向に対して垂直で前記主面に対して平行な第2方向に沿った幅は、前記第2配線層の前記可動部分における前記第2方向に沿った幅よりも広い請求項1記載の歪検知装置。

【請求項4】

前記可動部分の前記トランジスタとの前記距離の変化に応じて、前記第1磁性層の磁化方向が変化し、前記磁化方向の変化に伴って前記一端と前記他端との間の電気抵抗が変化する請求項1〜3のいずれか1つに記載の歪検知装置。

【請求項5】

前記歪検知素子部は、

前記第2磁性層と、

前記第1磁性層と前記第2磁性層との間に設けられた非磁性の中間層と、

をさらに含む請求項1〜4のいずれか1つに記載の歪検知装置。

【請求項6】

前記歪検知素子部は、前記第1磁性層に並置され、前記第1磁性層にバイアス磁界を印加するバイアス層をさらに含む請求項1〜5のいずれか1つに記載の歪検知装置。

【請求項7】

前記第1磁性層の磁歪定数は、10−5以上である請求項1〜6のいずれか1つに記載の歪検知装置。

【請求項8】

前記可動部分は、前記可動部分を貫通する孔を有する請求項1〜7のいずれか1つに記載の歪検知装置。

【請求項9】

前記可動部分と前記トランジスタと間の距離は、1マイクロメートル以上10マイクロメートル以下の範囲で変化する請求項1〜8のいずれか1つに記載の歪検知装置。

【請求項10】

前記固定部分から前記可動部分に向かう第1方向に沿った前記可動部分の長さは、10マイクロメートル以上500マイクロメートル以下である請求項1〜9のいずれか1つに記載の歪検知装置。

【請求項11】

前記半導体回路部は、歪検知素子部に流れる電流に基づく信号を処理する処理回路を含む請求項1〜10のいずれか1つに記載の歪検知装置。

【請求項12】

前記半導体回路部は、歪検知素子部に流れる電気信号に基づくデータを無線で送信する送信回路を含む請求項1〜11のいずれか1つに記載の歪検知装置。

【請求項13】

半導体基板の上にトランジスタを形成する工程と、

前記半導体基板の上に層間絶縁層を形成し、前記トランジスタの上に犠牲層を形成する工程と、

前記層間絶縁層と前記犠牲層との上に第1配線層となる第1導電層を形成する工程と、

前記犠牲層の上の前記第1導電層の上に、第1磁性層を含む歪検知素子部を形成する工程と、

前記歪検知素子部の上に第2配線層となる第2導電層を形成する工程と、

前記層間絶縁層の中に、前記第1導電層を前記半導体基板と電気的に接続する第1埋め込み配線と、前記第2導電層を前記半導体基板と電気的に接続する第2埋め込み配線と、を形成する工程と、

前記犠牲層を除去する工程と、

を備えた歪検知装置の製造方法。

【請求項14】

前記犠牲層を除去する前記工程は、前記犠牲層の上面から前記犠牲層を除去することを含む請求項13記載の歪検知装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【公開番号】特開2013−72712(P2013−72712A)

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願番号】特願2011−211212(P2011−211212)

【出願日】平成23年9月27日(2011.9.27)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願日】平成23年9月27日(2011.9.27)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]