比較回路及びアナログデジタル変換回路

【課題】動作電圧に対して入力電圧範囲を拡大し、低消費電力化を図ること。

【解決手段】比較回路10の電圧制御部12は、キャパシタC11の第1端子に、クロック信号CKに応答して高電位電圧AVDと低電位電圧(グランドGND)を供給する。キャパシタC11の第2端子に接続されたトランジスタT23は、反転クロック信号XCKに応答してオンオフする。入力トランジスタT11,T12のしきい値電圧と等しく設定されたトランジスタT23は、グランドGNDの電圧とノードN21の電圧に応じて反転状態となり、比較部11に供給する制御電圧VCM(ノードN21の電圧)をグランドGNDからトランジスタT23のしきい値電圧低い電圧に安定させる。

【解決手段】比較回路10の電圧制御部12は、キャパシタC11の第1端子に、クロック信号CKに応答して高電位電圧AVDと低電位電圧(グランドGND)を供給する。キャパシタC11の第2端子に接続されたトランジスタT23は、反転クロック信号XCKに応答してオンオフする。入力トランジスタT11,T12のしきい値電圧と等しく設定されたトランジスタT23は、グランドGNDの電圧とノードN21の電圧に応じて反転状態となり、比較部11に供給する制御電圧VCM(ノードN21の電圧)をグランドGNDからトランジスタT23のしきい値電圧低い電圧に安定させる。

【発明の詳細な説明】

【技術分野】

【0001】

比較回路及びアナログデジタル変換回路に関する。

【背景技術】

【0002】

比較回路は、2つの入力電圧を大小比較した結果に応じて高電位電源レベル(Hレベル)又は低電位電源レベル(Lレベル)の信号を出力する。

比較回路は、入力電圧を受けるトランジスタの型に応じて、動作範囲に制限を受ける。例えば、入力電圧をNチャネルMOSトランジスタで受ける比較回路は、低電位電源に近い入力電圧の比較を行うことができない。また、入力電圧をPチャネルMOSトランジスタで受ける比較回路は、高電位電源に近い入力電圧の比較を行うことができない。

【0003】

このため、電源電圧をチャージポンプ回路で昇圧した電源電圧を比較回路に供給することで、動作範囲を拡大する方法が提案されている(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平7−104014号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、比較回路は、電源電圧の低電圧化とともに、低消費電力化が望まれている。

【課題を解決するための手段】

【0006】

本発明の一観点によれば、クロック信号に応答してキャパシタの第1端子に第1の電圧と第2の電圧とを交互に供給するインバータ回路と、前記キャパシタの第2端子に第1端子が接続され、ゲートに反転クロック信号が供給され、第2端子に前記第2の電圧が供給されるトランジスタとを含み、前記キャパシタと前記トランジスタとの間のノードに前記第2の電圧と前記キャパシタの蓄積電荷に応じた制御電圧を生成する電圧制御部と、第1の入力電圧をゲートに受ける第1のトランジスタと、第2の入力電圧をゲートに受ける第2のトランジスタと、前記クロック信号がゲートに供給され、ソースに前記制御電圧が供給され、ドレインが前記第1のトランジスタのソースと前記第2のトランジスタのソースにそれぞれ接続された第3のトランジスタを含み、クロック信号に応答して、前記第1の入力電圧と前記第2の入力電圧との比較結果に応じた出力信号を生成する比較動作と、前記第1の電圧に応じたレベルの前記出力信号を生成するリセット動作とを交互に行う比較部と、を有する。

【発明の効果】

【0007】

本発明の一観点によれば、動作電圧に対して入力電圧範囲を拡大し、低消費電力化を図ることができる。

【図面の簡単な説明】

【0008】

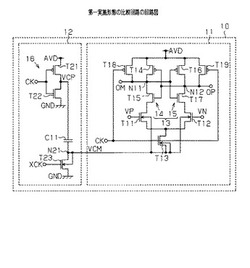

【図1】第一実施形態の比較回路の回路図である。

【図2】図1の比較回路の動作波形図である。

【図3】アナログデジタル変換回路のブロック回路図である。

【図4】第二実施形態の比較回路の回路図である。

【図5】トランジスタの概略構成図である。

【図6】トランジスタの概略構成図である。

【図7】第三実施形態の比較回路の回路図である。

【図8】図7の比較回路の動作波形図である。

【図9】第四実施形態の比較回路の回路図である。

【図10】図9の比較回路の動作波形図である。

【図11】第五実施形態の比較回路の回路図である。

【図12】図11の比較回路の動作波形図である。

【図13】電圧制御部の回路図である。

【図14】図13の電圧制御部の動作波形図である。

【図15】電圧制御部の回路図である。

【図16】図15の電圧制御部の動作波形図である。

【図17】比較例の比較回路の回路図である。

【図18】比較例の比較回路の回路図である。

【発明を実施するための形態】

【0009】

(第一実施形態)

以下、第一実施形態を説明する。

図1に示すように、比較回路10は、入力電圧VP,VNを比較して出力信号OP,OMを生成する比較部11と、比較部11の動作電圧を制御する電圧制御部12を備えている。

【0010】

入力電圧VP,VNは、比較部11の入力トランジスタT11,T12に入力される。入力トランジスタT11,T12はNチャネルMOSトランジスタである。入力電圧VP(第1の入力電圧)は入力トランジスタT11のゲートに入力され、入力電圧VN(第2の入力電圧)は入力トランジスタT12のゲートに入力される。両入力トランジスタT11,T12のソースは互いに接続され、その接続点はスイッチングトランジスタT13に接続されている。

【0011】

スイッチングトランジスタT13は入力トランジスタT12,T12と同じ導電型のNチャネルMOSトランジスタである。スイッチングトランジスタT13のドレインは両入力トランジスタT11,T12に接続され、ゲートにはクロック信号CKが供給される。トランジスタT13のソース及びバックゲートと、入力トランジスタT11,T12のバックゲートは互いに接続され、その接続点は電圧制御部12に接続されている。

【0012】

入力トランジスタT11,T12のドレインは、ラッチ部13に接続されている。

ラッチ部13は、互いに入力端子と出力端子がクロスカップル接続された一対のインバータ回路14,15を備える。インバータ回路14は、PチャネルMOSトランジスタT14と、NチャネルMOSトランジスタT15を備えている。インバータ回路15は、PチャネルMOSトランジスタT16と、NチャネルMOSトランジスタT17を備えている。

【0013】

トランジスタT14のソースには高電位電圧AVD(第1の電圧)が供給され、トランジスタT14のドレインはトランジスタT15のドレインと接続され、トランジスタT15のソースは入力トランジスタT11のドレインと接続されている。トランジスタT16のソースには高電位電圧AVDが供給され、トランジスタT16のドレインはトランジスタT17のドレインと接続され、トランジスタT17のソースは入力トランジスタT12のドレインと接続されている。

【0014】

トランジスタT14のドレインとトランジスタT15のドレインとの間のノードN11はトランジスタT16,T17のゲートに接続されている。トランジスタT16のドレインとトランジスタT17のドレインとの間のノードN12は、トランジスタT14,T15のゲートに接続されている。

【0015】

ノードN11にはリセットトランジスタT18が接続されている。リセットトランジスタT18はPチャネルMOSトランジスタであり、ドレインがノードN11に接続され、ソースに高電位電圧AVDが供給され、ゲートにクロック信号CKが供給される。ノードN12にはリセットトランジスタT19が接続されている。リセットトランジスタT19はPチャネルMOSトランジスタであり、ドレインがノードN12に接続され、ソースに高電位電圧AVDが供給され、ゲートにクロック信号CKが供給される。そして、ノードN11から出力信号OMが出力され、ノードN12から出力信号OPが出力される。

【0016】

電圧制御部12は、PチャネルMOSトランジスタT21、NチャネルMOSトランジスタT22,T23、キャパシタC11を備えている。トランジスタT21のソースには高電位電圧AVDが供給され、トランジスタT21のドレインはトランジスタT22のドレインに接続され、トランジスタT22のソースは低電位電圧(第2の電圧)を供給する配線(以下、グランドGND)と接続される。両トランジスタT21,T22のゲートにはクロック信号CKが供給される。トランジスタT21とトランジスタT22はインバータ回路16に含まれる。

【0017】

トランジスタT21のドレインとトランジスタT22のドレインとの間の接続点は、キャパシタC11の第1端子に接続され、キャパシタC11の第2端子は降圧用トランジスタT23のドレインに接続されている。トランジスタT23のソースはグランドGNDに接続されている。トランジスタT23のゲートにはクロック信号XCKが供給される。降圧用トランジスタT23の電気的特性(しきい値電圧)は、入力トランジスタT11,T12のしきい値電圧と等しい値に設定されている。例えば、トランジスタT23のゲート長(L)及びゲート幅(W)と、入力トランジスタT11,T12のゲート長(L)及びライト長(W)とを等しく設定することにより、各トランジスタT11,T12,T23のしきい値電圧が互いに等しくなる。

【0018】

クロック信号XCKは、クロック信号CKに対して相補的に変化する反転クロック信号である。なお、この反転クロック信号XCKのエッジは、クロック信号CKのエッジと同期した、又は進んだタイミングとなるのが好ましい。トランジスタT23のバックゲートはトランジスタT23のドレインとキャパシタC11の第2端子との間のノードN21に接続されている。そして、このノードN21は、比較部11に含まれるトランジスタT13のソース及びトランジスタT11,T12,T13のバックゲートに接続されている。

【0019】

次に、比較回路10の作用を説明する。

[電圧制御部]

クロック信号CKがLレベルのとき、トランジスタT21はクロック信号CKに応答してオンし、トランジスタT22はクロック信号CKに応答してオフし、インバータ回路16は高電位電圧AVDをキャパシタC11の第1端子に供給する。クロック信号CKがLレベルのとき、反転クロック信号XCKはHレベルである。トランジスタT23は、Hレベルの反転クロック信号XCKに応答してオンし、キャパシタC11の第2端子が接続されたノードN21をグランドGNDに接続する。従って、クロック信号CKがLレベルのとき、ノードN21の電位はグランドGNDレベル(=0V)となる。キャパシタC11は、供給される電圧に応じた電荷を蓄積する。この状態を[蓄積状態]という。

【0020】

次いで、反転クロック信号XCKがHレベルからLレベルに立ち下がる(図2の時刻t0)と、Lレベルの反転クロック信号XCKに応答してトランジスタT23がオフし、ノードN21がフローティング状態となる。

【0021】

次いで、クロック信号CKがLレベルからHレベルに立ち上がる(図2の時刻t1)と、インバータ回路16は、Hレベルのクロック信号CKに応答して、キャパシタC11の第1端子をグランドGNDに接続する。すると、図2に示すように、キャパシタC11の第2端子が接続されたノードN21の電位は、キャパシタC11に蓄積された電荷により、負の電圧[−ADV]まで低下する。

【0022】

トランジスタT23は、ゲート及びソースの電位がグランドGNDレベルとなり、ドレイン及びバックゲートの電位がノードN21の電位(−AVD)となる。すると、NチャネルMOSトランジスタT23は、ソース及びバックゲートがノードN21に接続され、そのノードN21の電位より高電位側のグランドGNDにゲート及びドレインが接続される。つまり、トランジスタT23は、ソースとドレインが互いに反転した反転状態となってオンし、グランドGNDからノードN21に向って電流を流す。その結果、ノードN21の電位は、グランドGNDの電位(0V)からトランジスタT23のしきい値電圧Vthn低い電圧[−Vthn]にて安定する。この状態を[降圧状態]という。

【0023】

次いで、反転クロック信号XCKがLレベルからHレベルに立ち上がる(図2の時刻t2)と、Hレベルの反転クロック信号XCKに応答してトランジスタT23がオンし、ノードN21をグランドGNDに接続する。次いで、クロック信号CKがHレベルからLレベルに立ち下がる(図2の時刻t3)と、インバータ回路15はキャパシタC11に高電位電圧AVDを供給する。これにより、キャパシタC11の充電が開始される。

【0024】

このように、電圧制御部12は、クロック信号CKと反転クロック信号XCKに応答して、充電状態と降圧状態とを交互に繰り返し、それぞれの状態に応じた制御電圧VCMを、ノードN21から出力する。

【0025】

[比較部]

クロック信号CKがLレベルのとき、NチャネルMOSトランジスタT13はオフし、PチャネルMOSトランジスタT18,T19はオンする。入力トランジスタT11,T12のソースは、オフしたトランジスタT13によりフローティング状態となる。オンしたトランジスタT18,T19は、ノードN11,N12の電位をHレベルとする。この結果、出力信号OP,OMはHレベルとなる。この時の状態をリセット状態という。そして、クロック信号CKがLレベルである期間をリセット期間という。

【0026】

クロック信号CKがLレベルからHレベルへと変化する(図2の時刻t1)。スイッチングトランジスタT13は、Hレベルのクロック信号CKに応答してオンする。また、リセットトランジスタT18,T19は、Hレベルのクロック信号CKに応答してオフする。

【0027】

トランジスタT13がオンすると、入力トランジスタT11,T12のソースにはノードN21の電位に応じた制御電圧VCM(=−Vthn)が供給される。また、入力トランジスタT11,T12のバックゲートには、制御電圧VCMが供給される。従って、比較部11は、高電位電圧AVDと制御電圧VCM(=−Vthn)とを動作電圧として動作する。そして、トランジスタT14,T15,T11,T13による第1の電流経路を介して電流が流れ、トランジスタT16,T17,T12,T13による第2の電流経路を介して電流が流れる。

【0028】

入力電圧VP,VNの電圧差、つまり入力トランジスタT11,T12のソース−ゲート間電圧Vgsに電圧差は、ノードN11,N12に流れる電流量に差を生じさせ、ノードN11,N12に電位差を生じさせる。ノードN11,N12の電位差は、インバータ回路14,15の正帰還により増幅され、ノードN11,N12のレベルが確定する。そして、ノードN11,N12のレベルに応じてトランジスタT14〜T17がオンオフする。

【0029】

例えば、入力電圧VPが入力電圧VNよりも高い場合、ノードN11の電位がノードN12の電位よりも低くなる。この電位差が増幅され、トランジスタT16がオンし、トランジスタT17がオフし、ノードN12がHレベル(高電位電圧AVDレベル)となる。一方、トランジスタT14がオフし、トランジスタT15がオンし、ノードN11の電位は、トランジスタT15のソース電圧、即ち入力トランジスタT11のソースに供給される制御電圧VCMと等しく、グランドGNDよりしきい値電圧VTHn低い電圧(=−Vthn)で安定する(図2の時刻tc1)。

【0030】

次いで、反転クロック信号XCKがLレベルからHレベルに立ち上がる(図2の時刻t2)と、図1に示すスイッチングトランジスタT13のソースにグランドGNDレベルの制御電圧VCMが供給され、ノードN11の電圧、即ち出力信号OMはグランドGNDレベルへと変化する。次いで、クロック信号CKがHレベルからLレベルに立ち下がる(図2の時刻t3)と、図1に示すスイッチングトランジスタT13がオフし、リセットトランジスタT18,T19がオンする。このオンしたトランジスタT18,T19は、ノードN11,N12のレベルをHレベルにクリップする。

【0031】

次いで、反転クロック信号XCKがHレベルからLレベルに立ち下がる(図2の時刻t4)と、Lレベルの反転クロック信号XCKに応答してトランジスタT23がオフし、ノードN21がフローティング状態となる。つまり、比較回路10は、上記の動作(図2の時刻t0から時刻t3)を繰り返し実行し(例えば、図2の時刻t4から時刻t7)、入力電圧VP,VNの電位差に応じたレベルの信号OM,OPを出力する。

【0032】

上記の比較状態において、入力トランジスタT11,T12のソース及びバックゲートには、グランドGNDよりも降圧用トランジスタT23のしきい値電圧低い制御電圧VCM(=−Vthn)が供給されている。従って、入力電圧VP,VNの電圧範囲は、トランジスタT13のソース電圧と、トランジスタT13のソース−ドレイン間電圧と、入力トランジスタT11,T12のソース−ゲート間電圧の和から、高電位電圧AVDまでの範囲となる。

【0033】

トランジスタT13のソース電圧は、そのトランジスタT13のソースが接続されたノードN21の電圧であり、制御電圧VCMである。トランジスタT13のゲート電圧はクロック信号CKのHレベル、即ち高電位電圧AVDレベルであるため、「0」となる。従って、入力トランジスタT11,T12のしきい値電圧をVthn2とすると、入力電圧VP,VNの範囲は、

(VCM+Vthn2)<VP<AVD

(VCM+Vthn2)<VN<AVD

となる。制御電圧VCMは、グランドGND(=0V)からトランジスタT21のしきい値電圧Vth低い電圧である。そして、降圧用トランジスタT23のしきい値電圧Vthは、入力トランジスタT11,T12のしきい値電圧Vthn2と等しい。従って、入力電圧VP,VNの範囲は、

0(V)<VP<AVD

0(V)<VN<AVD

となる。

【0034】

例えば、図17に示すように、トランジスタT13のソースをグランドGND(=0V)に接続した比較回路80の場合、入力電圧VPの範囲は、

(0+Vthn2)<VP<AVD

となる。従って、比較回路80における入力電圧VP,VNの範囲は、グランドGNDから入力トランジスタT11,T12のしきい値電圧Vthn2高い電圧を低電位側とし、高電位電圧AVDを高電位側とする範囲となる。

【0035】

従って、図1に示す比較回路10は、図17に示す比較回路80と比べ、入力電圧VP,VNの範囲を拡大することができる。

また、図1に示す比較回路10は、駆動電圧の低電圧化に対して有利である。例えば、高電位電圧AVDを3.0(V)とし、入力トランジスタT11,T12のしきい値電圧を1(V)とする。この場合、図17に示す比較回路80における入力電圧VP(VN)の範囲は、

1.0(V)<VP<3.0(V)

となる。従って、一方の入力電圧(例えば、VN)を高電位電圧AVDの2分の1(=1/2)として入力電圧VP,VNを比較するような用途に、図17に示す比較回路80を用いることができる。

【0036】

しかし、低電圧化により高電位電圧AVDが例えば1.8(V)になると、入力電圧VP(VN)の範囲は、

1.0(V)<VP<1.8(V)

となる。従って、一方の入力電圧(例えば、VN)を高電位電圧AVDの2分の1(=1/2)として入力電圧VP,VNを比較するような用途に、図17に示す比較回路80を用いることができない。

【0037】

これに対し、図1に示す比較回路10は、入力電圧VP,VNの範囲が、

0(V)<VP<AVD

0(V)<VN<AVD

である。従って、比較回路10は、一方の入力電圧(例えば、VN)を高電位電圧AVDの2分の1(=1/2)として入力電圧VP,VNを比較するような用途に用いることができる。

【0038】

また、図1に示すトランジスタT13は、Hレベルのクロック信号CKに応答してオンし、入力トランジスタT11,T12のソースに、ノードN21の電圧、即ちグランドGNDよりトランジスタT23のしきい値電圧低い電圧(=−Vthn)を供給する。従って、入力電圧VP,VNがグランドGNDレベルに近づいても、図17に示す回路構成と比べ、入力トランジスタT11,T12のオン抵抗値が増加が少なく、比較速度の低下を抑制することができる。

【0039】

キャパシタC11の容量値は、比較部11の動作と、降圧用トランジスタT23のしきい値電圧Vthnに応じて設定される。比較部11は、Hレベルのクロック信号CKに応答して比較動作を開始し(図2の時刻t1)、入力電圧VP,VNに応じてインバータ回路14,15の出力信号レベルが確定して比較動作を終了する(図2の時刻tc1)。この比較動作の間、高電位電圧AVDが供給される配線からノードN21に向って電流が流れる。キャパシタC11の容量値は、ノードN21の電位が、グランドGNDからトランジスタT23のしきい値電圧Vthn低い電圧以下を保つように設定される。例えば、キャパシタC11の容量値は、比較動作を行う期間(図2の時刻t1から時刻tc1)と、比較部11に流れる電流量の積により得られる電荷Q1と、トランジスタT23のしきい値電圧Vthnとに基づいて、

C11≫Q1/Vthn

となるように設定される。

【0040】

[適用例]

図1に示す比較回路10は、例えば、図3に示すように、逐次変換型のアナログデジタル変換回路(Analog to Digital Converter:ADC)20に用いられる。アナログデジタル変換回路20は、ホールド回路21と、比較回路10と、逐次変換レジスタ(SAR:successive approximation register)回路22と、デジタルアナログ変換回路(Digital to Analog Converter:DAC)23を有している。

【0041】

ホールド回路21は,アナログ入力信号Vinをサンプルクロックに同期してサンプルホールドし、ホールドした電圧Vaを出力する。比較回路10は、クロック信号CKに同期して、ホールド回路21から出力される電圧Va(VP)と判定電圧Vc(VN)とを比較し、入力電圧Vaが判定電圧Vcより大きいか小さいかの判定結果を示す判定信号Vq(OP)を生成する。逐次変換レジスタ回路22は、判定信号Vqを逐次保存するレジスタと,デジタル入力信号DIを生成する論理回路とを有する。SAR回路22は、クロック信号CKに同期して、判定信号Vqを逐次保存しデジタル出力信号Doutとして出力する。また、SAR回路22は、判定信号Vqに応じてデジタル入力信号DIを出力する。デジタルアナログ変換回路(DAC)23は、デジタル入力信号DIをアナログの判定電圧Vcに変換する。

【0042】

このように、電源電圧範囲を入力電圧範囲とする比較回路10を用いることで、アナログ入力信号Vinに対して電源電圧の制約を受けないアナログデジタル変換回路を提供することができる。

【0043】

以上記述したように、本実施形態によれば、以下の効果を奏する。

(1)比較回路10は、入力電圧VP,VNを比較して出力信号OP,OMを生成する比較部11と、比較部11の動作電圧を制御する電圧制御部12を備える。比較部11は、入力電圧VP,VNを受けるPチャネルMOSトランジスタT11,T12と、両トランジスタT11,T12のソースに接続され、ドレインに制御電圧VCMが供給され、クロック信号CKに応答してオンオフするスイッチングトランジスタT13を備える。比較部11は、Hレベルのクロック信号CKに応答して比較状態となり、入力電圧VP,VNの電位差に応じた出力信号OP,OMを出力する。

【0044】

電圧制御部12のインバータ回路16は、キャパシタC11の第1端子に、クロック信号CKに応答して高電位電圧AVDと低電位電圧(グランドGND)を供給する。キャパシタC11の第2端子に接続されたトランジスタT23は、反転クロック信号XCKに応答してオンオフする。トランジスタT23がオフすると、キャパシタC11とトランジスタT23との間のノードN21の電位は、キャパシタC11に蓄積された電荷に応じてグランドGNDから低下する。トランジスタT23のしきい値電圧は入力トランジスタT11,T12のしきい値電圧と等しく設定される。トランジスタT23は、グランドGNDの電圧とノードN21の電圧に応じて反転状態となり、ノードN21の電圧をグランドGNDからトランジスタT23のしきい値電圧低い電圧に安定させる。ノードN21の電圧が制御電圧VCMとして比較部11に供給される。

【0045】

比較部11は、グランドGNDより低い制御電圧VCMと高電位電圧AVDを動作電圧として比較動作する。従って、入力電圧VP,VNの範囲は、高電位電圧AVDからグランドGNDまでの範囲となり、入力範囲を拡大することができる。

【0046】

(2)電圧制御部12は、キャパシタC11に接続されたトランジスタT23の反転動作により、キャパシタC11とトランジスタT23の間ノードN21の電圧を、グランドGNDよりトランジスタT23のしきい値電圧Vthn低い電圧にて安定化させる。従って、チャージポンプ回路などのように、大きな回路を必要とせず、素子数が少なく、占有面積の小さな比較回路を提供することができる。

【0047】

(3)電圧制御部12のキャパシタC11は、グランドGND(0V)よりトランジスタT23のしきい値電圧Vthn低い電圧(制御電圧VCM)を安定的に保持することができればよく、容量の小さなキャパシタC11を用いることができる。このようなキャパシタC11は、配線間容量でも実現可能である。このため、大きな回路を必要とせず、占有面積の小さな比較回路を提供することができる。

【0048】

(4)電圧制御部12のトランジスタT23のしきい値電圧Vthnは、比較部11の入力トランジスタT11,T12のしきい値電圧と等しく設定されている。従って、プロセス条件や動作条件(温度、電源電圧)によって入力トランジスタT11,T12のしきい値電圧が変化しても、トランジスタT23のしきい値電圧Vthnも同様に変化するため、入力電圧VP,VNの範囲が変化するのを抑制することができる。

【0049】

(5)比較部11は、Hレベルのクロック信号CKに応答して比較状態となり、Lレベルのクロック信号CKに応答してリセット状態となる。このリセット状態において、入力トランジスタT11,T12のソースが接続されたスイッチングトランジスタT13は、Lレベルのクロック信号CKに応答してオフする。従って、常に電流が流れる比較回路と比べ、消費電力を低減することができる。

【0050】

(6)入力トランジスタT11,T12のドレインには、クロスカップル接続されたインバータ回路14,15を含むラッチ部13が接続されている。インバータ回路14,15は、PチャネルMOSトランジスタ又はNチャネルMOSトランジスタがオフして出力信号OP,OMのレベルを確定する。従って、比較状態において、出力信号OP,OMのレベルが確定した後は、インバータ回路14,15を介して貫通電力が流れなくなるため、消費連力を低減することができる。

【0051】

(第二実施形態)

以下、第二実施形態を説明する。

なお、第一実施形態と同じ部材については同じ符号を付し、その部材に対する全て又は一部の説明を省略する。

【0052】

図4に示すように、比較回路10aは、入力電圧VP,VNを比較して出力信号OP,OMを生成する比較部11aと、比較部11aの動作電圧を制御する電圧制御部12aを備えている。

【0053】

入力電圧VP,VNは、比較部11aの入力トランジスタT11,T12に入力される。入力トランジスタT11,T12のソースは互いに接続され、その接続点はスイッチングトランジスタT13aに接続されている。

【0054】

スイッチングトランジスタT13aは入力トランジスタT12,T12と同じ導電型であるNチャネルMOSトランジスタである。スイッチングトランジスタT13aのドレインは両入力トランジスタT11,T12に接続され、ゲートにはクロック信号CKが供給される。トランジスタT13aのソースは、電圧制御部12aのノードN21に接続され、そのノードN21の制御電圧VCMが供給される。トランジスタT13aのバックゲートと、入力トランジスタT11,T12のバックゲートはグランドGNDに接続されている。

【0055】

電圧制御部12aのトランジスタT23aのソース及びバックゲートはグランドGNDに接続されている。このトランジスタT23aは、バックゲートとソース、もしくはバックゲートとドレインの間に形成される寄生ダイオードを有している。電圧制御部12aのトランジスタT22がHレベルのクロック信号CKに応答してオンするとき(降圧動作)、グランドGNDからトランジスタT23の寄生ダイオードを介してキャパシタC11に向って電流が流れる。この電流を流す寄生ダイオードの順方向電圧VFは、トランジスタT23のしきい値電圧Vthnより高い。従って、キャパシタC11の第2端子が接続されたノードN21の電位は、グランドGNDよりトランジスタT23の寄生ダイオードにおける順方向電圧だけ低い電圧(=−VF)となる。そして、このノードN21とグランドGNDとの間の電位差は、入力トランジスタT11,T12のしきい値電圧Vthnより大きい。従って、入力トランジスタT11,T12のソースは、両トランジスタT11,T12のしきい値電圧Vthnより低い電圧(=−VF)となる。このため、入力トランジスタT11,T12及びスイッチングトランジスタT13aのバックゲートをグランドGNDに接続することができる。

【0056】

この場合、比較部11aに含まれるトランジスタのうち、少なくともスイッチングトランジスタT13aは、図5に示すように構成される。P型半導体基板100には、N+型拡散層101とN+型拡散層102とP−型領域103が形成され、両拡散層101,102の間において、基板100上に絶縁層(例えば、酸化膜)104及び導電層105が形成されている。これらN+型拡散層101、N+型拡散層102、導電層105、P−領域103は、それぞれトランジスタT13aのドレイン、ソース、ゲート、バックゲートとなる。

【0057】

比較例として、図1に示すスイッチングトランジスタT13の概略構成を図6に示す。P型半導体基板110には、ディープN型ウェル(Deep Nwell)111とP−型領域112が形成され、ウェル111にP型ウェル(Pwell)113とN−型領域114が形成されている。P型ウェル113には、N+型拡散層115,116とP−型領域117が形成されている。N+型拡散層115,116の間において、P型ウェル113の表面には絶縁層(酸化膜)118及び導電層119が形成されている。これらN+型拡散層115、N+型拡散層116、導電層119、P−型領域117は、それぞれトランジスタT13のドレイン、ソース、ゲート、バックゲートとなる。N−型領域114には高電位電圧AVDが供給され、P−型領域112はグランドGNDに接続される。

【0058】

このように、図4,図5に示すトランジスタT13aは、図1,図6に示すトランジスタT13と比べ、占有面積が少なく、比較回路10aを含む半導体チップの面積の縮小を図ることができる。また、図5に示すトランジスタT13aは、図6に示すトランジスタT13と比べ、構造が簡単で製造工数が少ない。

【0059】

この実施形態における比較回路10aは、図1に示す比較回路10と同様に、図3に示す逐次比較型のアナログデジタル変換回路に用いることができる。

以上記述したように、本実施形態によれば、第一実施形態の効果に加え、以下の効果を奏する。

【0060】

(7)寄生ダイオードの順方向電圧VFがしきい値電圧Vthnより大きなトランジスタT23aを用いて制御電圧VCMを生成することで、比較部11aのトランジスタT13aの構造を簡略化することができ、占有面積を低減することができる。

【0061】

(第三実施形態)

以下、第三実施形態を説明する。

なお、上記各実施形態と同じ部材については同じ符号を付し、その部材に対する一部又は全ての説明を省略する。

【0062】

図7に示すように、比較回路30は、比較部11と電圧制御部12とラッチ部31を備えている。ラッチ部31は、2つのナンド回路32,33を備えている。ナンド回路32の1つの入力端子は比較部11のノードN11に接続され、信号OMを入力する。ナンド回路32の他の1つの入力端子はナンド回路33の出力端子に接続され、ナンド回路32は信号OP2を出力する。ナンド回路33の1つの入力端子は比較部11のノードN12に接続され、信号OPを入力する。ナンド回路33の他の1つの入力端子はナンド回路32の出力端子に接続されている。ナンド回路33は、信号OM2を出力する。

【0063】

ナンド回路32,33は、2つの入力信号のうちの少なくとも一方の信号がLレベルのときにHレベルの信号を出力し、2つの入力信号がともにHレベルのときにLレベルの信号を出力する。

【0064】

比較部11は、Hレベルのクロック信号CKに応答して比較状態となり、入力電圧VP,VNの電位差に応じたレベルの信号OP,OMを出力する。

例えば、入力電圧VPが入力電圧VNより高いとき、比較部11は、Lレベルの信号OMと、Hレベルの信号OPを出力する。Lレベルの信号OMを受けるナンド回路32はHレベルの信号OP2を出力する。ナンド回路33は、Hレベルの信号OPとHレベルの信号OP2に基づいてLレベルの信号OM2を出力する。ナンド回路32は、Lレベルの信号OMと、Lレベルの信号OM2を受ける。

【0065】

また、入力電圧VPが入力電圧VNより低いとき、比較部11は、Hレベルの信号OMと、Lレベルの信号OPを出力する。Lレベルの信号OPを受けるナンド回路33はHレベルの信号OM2を出力する。ナンド回路32は、Hレベルの信号OMとHレベルの信号OM2に基づいてLレベルの信号OP2を出力する。ナンド回路33は、Lレベルの信号OPと、Lレベルの信号OP2を受ける。つまり、ラッチ部31は、比較部11の比較動作によって出力される信号OP,OMとそれぞれ等しいレベルの信号OP2,OM2を出力する。

【0066】

比較部11は、Lレベルのクロック信号CKに応答してリセット状態となり、ノードN11,N12を高電位電圧AVDレベル(Hレベル)にリセットする。つまり、リセット状態の比較部11は、Hレベルの信号OP,OMを出力する。

【0067】

比較状態において、2つのナンド回路32,33のうちの何れか一方は2つのLレベルの信号を受け、2つのナンド回路32,33のうちの何れか他方は2つのHレベルの信号を受ける。2つのLレベルの信号を受けるナンド回路は、Hレベルの信号を受けても、出力信号のレベルを変更しない。また、2つのHレベルの信号を受けるナンド回路は、Hレベルの信号を受ける、つまり入力信号のレベルが変化しないため、出力信号のレベルを変更しない。

【0068】

つまり、ラッチ部31は、比較状態(図8の時刻t1から時刻tc1の間)の比較部11が出力する信号OP,OMのレベルを保持し、保持したレベルに応じた信号OP2,OM2を出力する。また、ラッチ部31は、出力信号OP2,OM2のレベルを、次の比較によってノードN11,N12のレベルが確定するまで(例えば、図8の時刻t2から時刻tc2までの間)出力する。

【0069】

この実施形態における比較回路30は、図1に示す比較回路10と同様に、図3に示す逐次比較型のアナログデジタル変換回路に用いることができる。

以上記述したように、本実施形態によれば、以下の効果を奏する。

【0070】

(1)ラッチ部31は、一対のナンド回路32,33を備える。ラッチ部31は、比較状態の比較部11から出力される信号OP,OMをラッチし、信号OP,OMに応じたレベルの信号OP2,OM2を出力する。また、ラッチ部31は、リセット状態の比較部11から出力されるHレベルの信号OP,OMに応答して出力信号OP2,OM2のレベルを保持する。従って、この比較回路30は、クロック信号CKに同期して動作し、クロック信号CKの1周期の間、入力電圧VP,VNの電位差に応じた出力信号OP2,OM2を出力することができる。

【0071】

(第四実施形態)

以下、第四実施形態を説明する。

図9に示すように、比較回路40は、入力電圧VP,VNを比較して出力信号OP,OMを生成する比較部41と、比較部41の動作電圧を制御する電圧制御部42を備えている。

【0072】

入力電圧VP,VNは、比較部41の入力トランジスタT31,T32に入力される。入力トランジスタT31,T32はPチャネルMOSトランジスタである。入力電圧VPは入力トランジスタT31のゲートに入力され、入力電圧VNは入力トランジスタT32のゲートに入力される。両入力トランジスタT31,T32のソースは互いに接続され、その接続点はスイッチングトランジスタT33に接続されている。

【0073】

スイッチングトランジスタT33は入力トランジスタT32,T32と同じ導電型のPチャネルMOSトランジスタである。スイッチングトランジスタT33のドレインは両入力トランジスタT31,T32に接続され、ゲートにはクロック信号CKが供給される。トランジスタT33のソース及びバックゲートと、入力トランジスタT31,T32のバックゲートは互いに接続され、その接続点は電圧制御部42に接続されている。

【0074】

入力トランジスタT31,T32のドレインは、ラッチ部43に接続されている。

ラッチ部43は、互いに入力端子と出力端子がクロスカップル接続された一対のインバータ回路44,45を備える。インバータ回路44は、PチャネルMOSトランジスタT34と、NチャネルMOSトランジスタT35を備えている。インバータ回路45は、PチャネルMOSトランジスタT36と、NチャネルMOSトランジスタT37を備えている。

【0075】

トランジスタT34のソースは入力トランジスタT31のドレインに接続され、トランジスタT34のドレインはトランジスタT35のドレインと接続され、トランジスタT35のソースはグランドGNDに接続されている。トランジスタT36のソースは入力トランジスタT32のドレインに接続され、トランジスタT36のドレインはトランジスタT37のドレインと接続され、トランジスタT37のソースはグランドGNDと接続されている。

【0076】

トランジスタT34のドレインとトランジスタT35のドレインとの間のノードN31はトランジスタT36,T37のゲートに接続されている。トランジスタT36のドレインとトランジスタT37のドレインとの間のノードN32は、トランジスタT34,T35のゲートに接続されている。

【0077】

ノードN31にはリセットトランジスタT38が接続されている。リセットトランジスタT38はNチャネルMOSトランジスタであり、ドレインがノードN31に接続され、ソースはグランドGNDに接続され、ゲートにクロック信号CKが供給される。ノードN32にはリセットトランジスタT39が接続されている。リセットトランジスタT39はNチャネルMOSトランジスタであり、ドレインがノードN32に接続され、ソースはグランドGNDに接続され、ゲートにクロック信号CKが供給される。そして、ノードN31から出力信号OMが出力され、ノードN32から出力信号OPが出力される。

【0078】

電圧制御部42は、PチャネルMOSトランジスタT41,T42、NチャネルMOSトランジスタT43、キャパシタC21を備えている。トランジスタT41のソースには高電位電圧AVD(第2の電圧)が供給され、トランジスタT41のドレインはキャパシタC21の第1端子に接続されている。トランジスタT41のゲートには反転クロック信号XCKが供給され、トランジスタT41のバックゲートはトランジスタT41のドレインと接続されている。トランジスタT41のドレインとキャパシタC21の第1端子との間のノードN41は、比較部41に含まれるトランジスタT33のソース及びトランジスタT31,T32,T33のバックゲートに接続されている。

【0079】

キャパシタC21の第2端子は、トランジスタT42のドレインとトランジスタT43のドレインとの間の接続点に接続されている。トランジスタT42のソースには高電位電圧AVDが供給され、トランジスタT43のソースは低電位電圧(第1の電圧)を供給する配線(以下、グランドGND)と接続される。両トランジスタT42,T43のゲートは互いに接続され、クロック信号CKが供給される。トランジスタT42とトランジスタT43はインバータ回路46に含まれる。

【0080】

次に、比較回路40の作用を説明する。

[電圧制御部]

反転クロック信号XCKがLレベルのとき、トランジスタT41は、Lレベルの反転クロック信号XCKに応答してオンし、キャパシタC21の第1端子に高電位電圧AVDを供給する。クロック信号CKがHレベルのとき、トランジスタT42はHレベルのクロック信号CKに応答してオフし、トランジスタT43はHレベルのクロック信号CKに応答してオンし、インバータ回路46はキャパシタC11の第2端子をグランドに接続する。従って、クロック信号CKがLレベルのとき、ノードN41の電位は高電位電圧AVDレベルとなる。キャパシタC11は、供給される電圧に応じた電荷を蓄積する。この状態を[蓄積状態]という。

【0081】

次いで、反転クロック信号XCKがLレベルからHレベルに立ち上がる(図10の時刻t0)と、Hレベルの反転クロック信号XCKに応答してトランジスタT41がオフし、ノードN41がフローティング状態となる。

【0082】

次いで、クロック信号CKがHレベルからLレベルに立ち下がる(図10の時刻t1)と、インバータ回路46は、Lレベルのクロック信号CKに応答して、キャパシタC11の第2端子に高電位電圧AVDを供給する。すると、図10に示すように、キャパシタC11の第2端子が接続されたノードN41の電位は、キャパシタC11に蓄積された電荷により、正の電圧[=ADV×2]まで上昇する。

【0083】

トランジスタT41は、ゲート及びソースの電位が高電位電圧AVDレベルであり、ドレイン及びバックゲートの電位がノードN41の電位(AVD×2)となる。すると、PチャネルMOSトランジスタT41は、ソース及びバックゲートがノードN41に接続され、そのノードN41の電位より低電位側の電圧AVDがゲート及びドレインに供給される。つまり、トランジスタT41は、ソースとドレインが互いに反転した反転状態となってオンし、キャパシタC21から高電位電圧AVDに向って電流を流す。その結果、ノードN41の電位は、高電位電圧AVDからトランジスタT41のしきい値電圧Vthp高い電圧[=AVD+Vthp]にて安定する。この状態を[昇圧状態]という。

【0084】

次いで、反転クロック信号XCKがHレベルからLレベルに立ち下がる(図10の時刻t2)と、Lレベルの反転クロック信号XCKに応答してトランジスタT41がオンし、キャパシタC21の第1端子に高電位電圧AVDを供給する。次いで、クロック信号CKがLレベルからHレベルに立ち上がる(図10の時刻t3)と、インバータ回路46は、キャパシタC21の第2端子をグランドGNDに接続する。これにより、キャパシタC21の充電が開始される。

【0085】

このように、電圧制御部42は、クロック信号CKと反転クロック信号XCKに応答して、充電状態と昇圧状態とを交互に繰り返し、それぞれの状態に応じた制御電圧VCP1を、ノードN41から出力する。

【0086】

[比較部]

クロック信号CKがHレベルのとき、PチャネルMOSトランジスタT33はオフし、NチャネルMOSトランジスタT38,T39はオンする。入力トランジスタT31,T32のソースは、オフしたトランジスタT33によりフローティング状態となる。オンしたトランジスタT38,T39は、ノードN31,N32の電位をLレベルとする。この結果、出力信号OP,OMはLレベルとなる。この時の状態をリセット状態という。そして、クロック信号CKがHレベルである期間をリセット期間という。

【0087】

クロック信号CKがHレベルからLレベルへと変化する(図10の時刻t1)。スイッチングトランジスタT33は、Lレベルのクロック信号CKに応答してオンする。また、リセットトランジスタT38,T39は、Lレベルのクロック信号CKに応答してオフする。

【0088】

トランジスタT33がオンすると、入力トランジスタT31,T32のソースにはノードN41の電位に応じた制御電圧VCP1(=AVD+Vthp)が供給される。また、入力トランジスタT31,T32のバックゲートには、制御電圧VCP1が供給される。従って、比較部41は、制御電圧VCP1(=AVD+Vthp)とグランドGNDの電圧(=0V)を動作電圧として動作する。そして、トランジスタT33,T31,T34,T35による第1の電流経路を介して電流が流れ、トランジスタT33,T32,T36,T37による第2の電流経路を介して電流が流れる。

【0089】

入力電圧VP,VNの電圧差、つまり入力トランジスタT31,T32のソース−ゲート間電圧Vgsに電圧差は、ノードN31,N32に流れる電流量に差を生じさせ、ノードN31,N32に電位差を生じさせる。ノードN31,N32の電位差は、インバータ回路44,45の正帰還により増幅され、ノードN31,N32のレベルが確定する。そして、ノードN31,N32のレベルに応じてトランジスタT34〜T37がオンオフする。

【0090】

例えば、入力電圧VPが入力電圧VNよりも高い場合、ノードN31の電位がノードN32の電位よりも低くなる。この電位差が増幅され、トランジスタT36がオンし、トランジスタT37がオフし、ノードN32がHレベル(制御電圧VCP1のレベル)となる。一方、トランジスタT34がオフし、トランジスタT35がオンし、ノードN31の電位は、Lレベル(グランドGNDレベル)で安定する(図10の時刻tc1)。

【0091】

次いで、反転クロック信号XCKがHレベルからLレベルに立ち下がる(図10の時刻t2)と、図9に示すスイッチングトランジスタT33のソースに高電位電圧AVDレベルの制御電圧VCP1が供給され、ノードN31の電圧、即ち出力信号OMはグランドGNDレベルへと変化する。次いで、クロック信号CKがLレベルからHレベルに立ち上がる(図10の時刻t3)と、図9に示すスイッチングトランジスタT33がオフし、リセットトランジスタT38,T39がオンする。このオンしたトランジスタT38,T39は、ノードN31,N32のレベルをLレベルにクリップする。

【0092】

次いで、反転クロック信号XCKがLレベルからHレベルに立ち上がる(図10の時刻t4)と、Hレベルの反転クロック信号XCKに応答してトランジスタT41がオフし、ノードN41がフローティング状態となる。つまり、比較回路10は、上記の動作(図10の時刻t0から時刻t3)を繰り返し実行し(例えば、図10の時刻t4から時刻t7)、入力電圧VP,VNの電位差に応じたレベルの信号OM,OPを出力する。

【0093】

上記の比較状態において、入力トランジスタT31,T32のソース及びバックゲートには、高電位電圧AVDよりも昇圧用トランジスタT41のしきい値電圧高い制御電圧VCP1(=AVD+Vthp)が供給されている。従って、入力電圧VP,VNの電圧範囲は、トランジスタT33のソース電圧から、トランジスタT33のソース−ドレイン間電圧と、入力トランジスタT31,T32のソース−ゲート間電圧の和から、高電位電圧AVDまでの範囲となる。

【0094】

トランジスタT33のソース電圧は、そのトランジスタT33のソースが接続されたノードN41の電圧であり、制御電圧VCP1である。トランジスタT33のゲート電圧はクロック信号CKのLレベル、即ち高電位電圧AVDレベルであるため、「0」となる。従って、入力トランジスタT31,T32のしきい値電圧をVthp2とすると、入力電圧VP,VNの範囲は、

0(V)<VP<(VCP1−Vthp2)

0(V)<VN<(VCP1−Vthp2)

となる。制御電圧VCP1は、高電位電圧AVDからトランジスタT21のしきい値電圧Vthp高い電圧である。そして、降圧用トランジスタT23のしきい値電圧Vthpは、入力トランジスタT31,T32のしきい値電圧Vthp2と等しい。従って、入力電圧VP,VNの範囲は、

0(V)<VP<AVD

0(V)<VN<AVD

となる。

【0095】

例えば、図18に示すように、トランジスタT33のソースに高電位電圧AVDを供給した比較回路90の場合、入力電圧VPの範囲は、

0(V)<VP<(AVD−Vthp2)

となる。従って、比較回路90における入力電圧VP,VNの範囲は、グランドGNDを低電位側とし、高電位電圧AVDから入力トランジスタT31,T32のしきい値電圧Vthp2低い電圧を高電位側とする範囲となる。

【0096】

従って、図9に示す比較回路10は、図18に示す比較回路90と比べ、入力電圧VP,VNの範囲を拡大することができる。

また、図9に示す比較回路10は、図1に示す比較回路10と同様に、駆動電圧の低電圧化に対して有利である。例えば、高電位電圧AVDを3.0(V)とし、入力トランジスタT31,T32のしきい値電圧を1(V)とする。この場合、図18に示す比較回路90における入力電圧VP(VN)の範囲は、

0(V)<VP<2.0(V)

となる。従って、一方の入力電圧(例えば、VN)を高電位電圧AVDの2分の1(=1/2)として入力電圧VP,VNを比較するような用途に、図18に示す比較回路90を用いることができる。

【0097】

しかし、低電圧化により高電位電圧AVDが例えば1.8(V)になると、入力電圧VP(VN)の範囲は、

0(V)<VP<0.8(V)

となる。従って、一方の入力電圧(例えば、VN)を高電位電圧AVDの2分の1(=1/2)として入力電圧VP,VNを比較するような用途に、図18に示す比較回路90を用いることができない。

【0098】

これに対し、図9に示す比較回路10は、入力電圧VP,VNの範囲が、

0(V)<VP<AVD

0(V)<VN<AVD

である。従って、比較回路10は、一方の入力電圧(例えば、VN)を高電位電圧AVDの2分の1(=1/2)として入力電圧VP,VNを比較するような用途に用いることができる。

【0099】

また、図9に示すトランジスタT33は、Lレベルのクロック信号CKに応答してオンし、入力トランジスタT31,T32のソースに、ノードN41の電圧、即ち高電位電圧AVDよりトランジスタT41のしきい値電圧高い電圧(=AVD+Vthp)を供給する。従って、入力電圧VP,VNが高電位電圧AVDレベルに近づいても、図18に示す回路構成と比べ、入力トランジスタT31,T32のオン抵抗値が増加が少なく、比較速度の低下を抑制することができる。

【0100】

キャパシタC21の容量値は、比較部41の動作と、昇圧用トランジスタT41のしきい値電圧Vthpに応じて設定される。比較部41は、Lレベルのクロック信号CKに応答して比較動作を開始し(図10の時刻t1)、入力電圧VP,VNに応じてインバータ回路14,15の出力信号レベルが確定して比較動作を終了する(図10の時刻tc1)。この比較動作の間、制御電圧VCP1を供給するノードN41からグランドGNDに向って電流が流れる。キャパシタC11の容量値は、ノードN41の電位が、高電位電圧AVDからトランジスタT41のしきい値電圧Vthp高い電圧以上を保つように設定される。例えば、キャパシタC21の容量値は、比較動作を行う期間(図10の時刻t1から時刻tc1)と、比較部41に流れる電流量の積により得られる電荷Q2と、トランジスタT41のしきい値電圧Vthpとに基づいて、

C21≫Q2/Vthp

となるように設定される。

【0101】

この実施形態における比較回路40は、図1に示す比較回路10と同様に、図3に示す逐次比較型のアナログデジタル変換回路に用いることができる。

以上記述したように、本実施形態によれば、第一実施形態と同様の効果をえることができる。

【0102】

(第五実施形態)

以下、第五実施形態を説明する。

なお、上記各実施形態と同じ部材については同じ符号を付し、その部材に対する一部又は全ての説明を省略する。

【0103】

図11に示すように、比較回路50は、比較部41と電圧制御部42とラッチ部51を備えている。ラッチ部51は、2つのノア回路52,53を備えている。ノア回路52の1つの入力端子は比較部41のノードN31に接続され、信号OMを入力する。ノア回路52の他の1つの入力端子はノア回路53の出力端子に接続され、ノア回路52は信号OP2を出力する。ノア回路53の1つの入力端子は比較部41のノードN32に接続され、信号OPを入力する。ノア回路53の他の1つの入力端子はノア回路52の出力端子に接続されている。ノア回路53は、信号OM2を出力する。

【0104】

ノア回路52,53は、2つの入力信号のうちの少なくとも一方の信号がHレベルのときにLレベルの信号を出力し、2つの入力信号がともにLレベルのときにHレベルの信号を出力する。

【0105】

比較部41は、Lレベルのクロック信号CKに応答して比較状態となり、入力電圧VP,VNの電位差に応じたレベルの信号OP,OMを出力する。

例えば、入力電圧VPが入力電圧VNより高いとき、比較部41は、Lレベルの信号OMと、Hレベルの信号OPを出力する。Hレベルの信号OPを受けるノア回路53はLレベルの信号OM2を出力する。ノア回路52は、Lレベルの信号OMとLレベルの信号OM2に基づいてHレベルの信号OP2を出力する。ノア回路53は、Hレベルの信号OPと、Hレベルの信号OP2を受ける。

【0106】

また、入力電圧VPが入力電圧VNより低いとき、比較部41は、Hレベルの信号OMと、Lレベルの信号OPを出力する。Hレベルの信号OMを受けるノア回路52はLレベルの信号OP2を出力する。ノア回路53は、Lレベルの信号OPとLレベルの信号OP2に基づいてHレベルの信号OM2を出力する。ノア回路52は、Hレベルの信号OMと、Hレベルの信号OM2を受ける。つまり、ラッチ部51は、比較部41の比較動作によって出力される信号OP,OMとそれぞれ等しいレベルの信号OP2,OM2を出力する。

【0107】

比較部41は、Hレベルのクロック信号CKに応答してリセット状態となり、ノードN31,N32をグランドGNDレベル(Lレベル)にリセットする。つまり、リセット状態の比較部41は、Lレベルの信号OP,OMを出力する。

【0108】

比較状態において、2つのノア回路52,53のうちの何れか一方は2つのLレベルの信号を受け、2つのノア回路52,53のうちの何れか他方は2つのHレベルの信号を受ける。2つのHレベルの信号を受けるノア回路は、Lレベルの信号を受けても、出力信号のレベルを変更しない。また、2つのLレベルの信号を受けるノア回路は、Lレベルの信号を受ける、つまり入力信号のレベルが変化しないため、出力信号のレベルを変更しない。

【0109】

つまり、ラッチ部51は、比較状態(図12の時刻t1から時刻tc1の間)の比較部41が出力する信号OP,OMのレベルを保持し、保持したレベルに応じた信号OP2,OM2を出力する。また、ラッチ部51は、出力信号OP2,OM2のレベルを、次の比較によってノードN31,N32のレベルが確定するまで(例えば、図12の時刻t2から時刻tc2までの間)出力する。

【0110】

この実施形態における比較回路50は、図1に示す比較回路10と同様に、図3に示す逐次比較型のアナログデジタル変換回路に用いることができる。

以上記述したように、本実施形態によれば、第三実施形態と同様の効果を得ることができる。

【0111】

尚、上記各実施形態は、以下の態様で実施してもよい。

・図9に示す実施形態では、入力トランジスタT31,T32のバックゲートとスイッチングトランジスタT33のバックゲートとを電圧制御部42のノードN41に接続して制御電圧VCP1を供給するようにした。これに対し、各トランジスタT31,T32,T33のバックゲートに高電位電圧AVDを供給するようにしてもよい。

【0112】

・電圧制御部の構成を適宜変更しても良い。

例えば、図13に示す電圧制御部61は、PチャネルMOSトランジスタT61(スイッチ部)、NチャネルMOSトランジスタT62、インダクタL11、キャパシタC31を備える。トランジスタT61は、ソースに高電位電圧AVDが供給され、ゲートにクロック信号CKが供給され、ドレインにインダクタL11の第1端子が接続される。インダクタL11の第2端子はグランドGNDに接続される。トランジスタT61のドレインとインダクタL11の第1端子との間のノードN61はトランジスタT62に接続されている。トランジスタT62は、第1端子(例えばドレイン)がノードN61に接続され、ゲートはグランドGNDに接続され、バックゲートと第2端子(例えばソース)が互いに接続されている。キャパシタC31の第1端子はトランジスタT62の第2端子に接続され、キャパシタC31の第2端子はグランドGNDに接続されている。

【0113】

この電圧制御部61の動作を図14に従って説明する。

クロック信号CKがLレベルのとき、トランジスタT61はオンし、トランジスタT61を介してインダクタL11に電流が流れる。このとき、ノードN61はグランドGNDレベルにある。また、トランジスタT62はオフし、キャパシタC31の第1端子はフローティング状態にある(初期状態)。

【0114】

クロック信号CKがLレベルからHレベルに立ち上がる(図14の時刻t1)と、トランジスタT61がオフする。すると、インダクタL11に流れる電流が減少し、ノードN61の電位がグランドGNDより低くなる。

【0115】

ノードN61の電圧V61は、

V(t)=L11×di(t)/dt

により、di(t)/dtが負であり、V(t)=V61−0(V)であるため、

V61=0(V)−L11|di(t)/dt|

となる。

【0116】

ノードN61の電圧がトランジスタT62のしきい値電圧より低くなるとトランジスタT62がオンし、ノードN61の電圧と等しい制御電圧VCMが比較回路に供給される。

インダクタL11の電流変化が収束し、ノードN61の電圧はグランドGNDの電圧に収束する。このとき、ノードN61の電圧が、設定電圧(グランドGNDよりトランジスタT62のしきい値電圧Vthn低い電圧)より高くなる(図14の時刻t3)と、トランジスタT62がオフし、制御電圧VCMはキャパシタC31により設定電圧(=−Vthn)に保持される。

【0117】

次いで、クロック信号CKがHレベルからLレベルに立ち下がる(図14の時刻t4)と、電圧制御部61の各素子は初期状態に戻る。制御電圧VCMはキャパシタC31により設定電圧(=−Vthn)に保持される。

【0118】

また、図15に示す電圧制御部71は、NチャネルMOSトランジスタT71(スイッチ部)、PチャネルMOSトランジスタT72、インダクタL21、キャパシタC41を備える。インダクタL21の第1端子には高電位電圧AVDが供給され、インダクタL21の第2端子はトランジスタT71のドレインに接続されている。トランジスタT71はゲートにクロック信号CKが供給され、ソースがグランドGNDに接続されている。インダクタL21の第2端子とトランジスタT71のドレインとの間のノードN71はトランジスタT72に接続されている。トランジスタT72は、第1端子(例えばドレイン)がノードN71に接続され、ゲートに高電位電圧AVDが供給され、バックゲートと第2端子(例えばソース)が互いに接続されている。キャパシタC41の第1端子はトランジスタT72の第2端子と接続され、キャパシタC41の第2端子はグランドGNDに接続されている。

【0119】

この電圧制御部71の動作を図16に従って説明する。

クロック信号CKがHレベルのとき、トランジスタT71はオンし、インダクタL21に電流が流れる。このとき、ノードN71はグランドGNDレベルにある。また、トランジスタT72はオフし、キャパシタC41の第1端子はフローティング状態にある(初期状態)。

【0120】

クロック信号CKがHレベルからLレベルに立ち下がる(図16の時刻t1)と、トランジスタT71がオフする。すると、インダクタL21に流れる電流が減少し、ノードN71の電位が高電位電圧AVDより高くなる。

【0121】

ノードN71の電圧V71は、

V(t)=L21×di(t)/dt

により、di(t)/dtが負であり、V(t)=AVD−V71であるため、

V71=AVD+L21|di(t)/dt|

となる。

【0122】

ノードN71の電圧が設定電圧(高電位電圧AVDよりトランジスタT72のしきい値電圧Vthp高い電圧)より高くなるとトランジスタT72がオンし、ノードN71の電圧と等しい制御電圧VCP1が比較回路に供給される。

【0123】

インダクタL21の電流変化が収束し、ノードN71の電圧は高電位電圧AVDに収束する。このとき、ノードN71の電圧V71が、設定電圧(高電位電圧AVDよりトランジスタT72のしきい値電圧Vthp高い電圧)より低くなる(図16の時刻t3)と、トランジスタT72がオフし、制御電圧VCP1はキャパシタC41により設定電圧(=AVD+Vthp)に保持される。

【0124】

次いで、クロック信号CKがLレベルからHレベルに立ち下がる(図16の時刻t4)と、電圧制御部71の各素子は初期状態に戻る。制御電圧VCP1はキャパシタC41により目標電圧(=AVD+Vthp)に保持される。

【0125】

・上記各実施形態において、制御電圧を降圧又は昇圧するタイミングと、比較部が比較動作を開始するタイミングとを適宜変更してもよい。これらのタイミングは、例えば電圧制御部と比較部に互いに異なるクロック信号を供給する、クロック信号に応答する回路の動作速度(応答速度)を変更することで、設定することが可能である。

【0126】

・上記第二実施形態において、しきい値電圧Vthnに対して寄生ダイオードの順方向電圧VFが大きいトランジスタT23aを用いた。寄生ダイオードの順方向電圧VFが入力トランジスタT11,T12のしきい値電圧より大きければよく、トランジスタT23aのしきい値電圧を適宜変更してもよい。

【0127】

上記各実施形態に関し、以下の付記を開示する。

(付記1)

クロック信号に応答してキャパシタの第1端子に第1の電圧と第2の電圧とを交互に供給するインバータ回路と、前記キャパシタの第2端子に第1端子が接続され、ゲートに反転クロック信号が供給され、第2端子に前記第2の電圧が供給されるトランジスタとを含み、前記キャパシタと前記トランジスタとの間のノードに前記第2の電圧と前記キャパシタの蓄積電荷に応じた制御電圧を生成する電圧制御部と、

第1の入力電圧をゲートに受ける第1のトランジスタと、第2の入力電圧をゲートに受ける第2のトランジスタと、前記クロック信号がゲートに供給され、ソースに前記制御電圧が供給され、ドレインが前記第1のトランジスタのソースと前記第2のトランジスタのソースにそれぞれ接続された第3のトランジスタを含み、クロック信号に応答して、前記第1の入力電圧と前記第2の入力電圧との比較結果に応じた出力信号を生成する比較動作と、前記第1の電圧に応じたレベルの前記出力信号を生成するリセット動作とを交互に行う比較部と、

を有する比較回路。

(付記2)

前記電圧制御部の前記トランジスタのバックゲートは前記制御電圧を生成するノードに接続され、

前記比較部の前記第1〜第3のトランジスタのバックゲートには前記制御電圧が供給される、

ことを特徴とする付記1記載の比較回路。

(付記3)

前記電圧制御部の前記トランジスタのバックゲートには前記第1の電圧が供給され、

前記比較部の前記第1〜第3のトランジスタのバックゲートには前記第1の電圧が供給される、

ことを特徴とする付記1記載の比較回路。

(付記4)

一端に第2の電圧が供給されるインダクタの他端に対してクロック信号に応答して第1の電圧の供給と停止を行うスイッチ部と、前記インダクタと前記スイッチ部との間のノードに第1端子が接続され、ゲートに前記第2の電圧が供給され、バックゲートと第2端子が互いに接続されたトランジスタを含み、前記トランジスタの第2端子に制御電圧を生成する電圧制御部と、

第1の入力電圧をゲートに受ける第1のトランジスタと、第2の入力電圧をゲートに受ける第2のトランジスタと、前記クロック信号がゲートに供給され、ソースに前記制御電圧が供給され、ドレインが前記第1のトランジスタのソースと前記第2のトランジスタのソースにそれぞれ接続された第3のトランジスタを含み、クロック信号に応答して、前記第1の入力電圧と前記第2の入力電圧との比較結果に応じた出力信号を生成する比較動作と、前記第1の電圧に応じたレベルの前記出力信号を生成するリセット動作とを交互に行う比較部と、

を有する比較回路。

(付記5)

前記電圧制御部は、前記第2の電圧より低い前記制御電圧を生成するものであり、

前記トランジスタの第2端子に一端が接続され、他端に前記第2の電圧が供給されたキャパシタを含む、ことを特徴とする付記4記載の比較回路。

(付記6)

前記電圧制御部は、前記第2の電圧より高い前記制御電圧を生成するものであり、

前記トランジスタの第2端子に一端が接続され、他端に前記第1の電圧が供給されるキャパシタを含む、ことを特徴とする付記4記載の比較回路。

(付記7)

前記比較部は、

前記第1のトランジスタのドレインと前記第2のトランジスタのドレインにそれぞれ接続され、前記第1の電圧が供給され、互いに入力端子と出力端子がクロスカップル接続された一対のインバータ回路と、

前記一対のインバータ回路の出力端子にドレインがそれぞれ接続され、ゲートに前記クロック信号が供給され、ソースに前記第1の電圧が供給される一対のリセットトランジスタと、

を含むことを特徴とする付記1〜6のうちの何れか一項に記載の比較回路。

(付記8)

前記第2の電圧は前記第1の電圧よりも高い電圧であり、

前記比較部の出力信号がそれぞれ入力され、互いの出力信号が入力される一対のノア回路を含む、ことを特徴とする付記1〜4,6のうちの何れか一項に記載の比較回路。

(付記9)

前記第2の電圧は前記第1の電圧よりも低い電圧であり、

前記比較部の出力信号がそれぞれ入力され、互いの出力信号が入力される一対のナンド回路を含む、ことを特徴とする付記1〜5のうちの何れか一項に記載の比較回路。

(付記10)

アナログ入力信号をサンプルクロックに同期してサンプルホールドし、保持するホールド回路と、

前記ホールド回路から出力される電圧と判定電圧との比較結果に応じた判定信号を出力する付記1〜9のうちの何れか一項に記載の比較回路と、

前記判定信号を逐次変換してデジタル入力信号を生成する逐次変換レジスタ回路と、

前記デジタル入力信号をアナログの前記判定信号に変換するデジタルアナログ変換回路と、

を有するアナログデジタル変換回路。

【符号の説明】

【0128】

11,11a,41 比較部

12,12a,42,61,71 電圧制御部

AVD 高電位電圧

GND グランド(低電位電圧)

C11,C21 キャパシタ

T23,T41 トランジスタ

T11,T31 第1のトランジスタ

T12,T32 第2のトランジスタ

T13,T33 第3のトランジスタ

L11,L21 インダクタ

T62,T72 トランジスタ

CK クロック信号

XCK 反転クロック信号

VP,VN 入力電圧

OP,OM 出力信号

VCM,VCP 制御電圧

VCM1,VCP1 制御電圧

【技術分野】

【0001】

比較回路及びアナログデジタル変換回路に関する。

【背景技術】

【0002】

比較回路は、2つの入力電圧を大小比較した結果に応じて高電位電源レベル(Hレベル)又は低電位電源レベル(Lレベル)の信号を出力する。

比較回路は、入力電圧を受けるトランジスタの型に応じて、動作範囲に制限を受ける。例えば、入力電圧をNチャネルMOSトランジスタで受ける比較回路は、低電位電源に近い入力電圧の比較を行うことができない。また、入力電圧をPチャネルMOSトランジスタで受ける比較回路は、高電位電源に近い入力電圧の比較を行うことができない。

【0003】

このため、電源電圧をチャージポンプ回路で昇圧した電源電圧を比較回路に供給することで、動作範囲を拡大する方法が提案されている(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平7−104014号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、比較回路は、電源電圧の低電圧化とともに、低消費電力化が望まれている。

【課題を解決するための手段】

【0006】

本発明の一観点によれば、クロック信号に応答してキャパシタの第1端子に第1の電圧と第2の電圧とを交互に供給するインバータ回路と、前記キャパシタの第2端子に第1端子が接続され、ゲートに反転クロック信号が供給され、第2端子に前記第2の電圧が供給されるトランジスタとを含み、前記キャパシタと前記トランジスタとの間のノードに前記第2の電圧と前記キャパシタの蓄積電荷に応じた制御電圧を生成する電圧制御部と、第1の入力電圧をゲートに受ける第1のトランジスタと、第2の入力電圧をゲートに受ける第2のトランジスタと、前記クロック信号がゲートに供給され、ソースに前記制御電圧が供給され、ドレインが前記第1のトランジスタのソースと前記第2のトランジスタのソースにそれぞれ接続された第3のトランジスタを含み、クロック信号に応答して、前記第1の入力電圧と前記第2の入力電圧との比較結果に応じた出力信号を生成する比較動作と、前記第1の電圧に応じたレベルの前記出力信号を生成するリセット動作とを交互に行う比較部と、を有する。

【発明の効果】

【0007】

本発明の一観点によれば、動作電圧に対して入力電圧範囲を拡大し、低消費電力化を図ることができる。

【図面の簡単な説明】

【0008】

【図1】第一実施形態の比較回路の回路図である。

【図2】図1の比較回路の動作波形図である。

【図3】アナログデジタル変換回路のブロック回路図である。

【図4】第二実施形態の比較回路の回路図である。

【図5】トランジスタの概略構成図である。

【図6】トランジスタの概略構成図である。

【図7】第三実施形態の比較回路の回路図である。

【図8】図7の比較回路の動作波形図である。

【図9】第四実施形態の比較回路の回路図である。

【図10】図9の比較回路の動作波形図である。

【図11】第五実施形態の比較回路の回路図である。

【図12】図11の比較回路の動作波形図である。

【図13】電圧制御部の回路図である。

【図14】図13の電圧制御部の動作波形図である。

【図15】電圧制御部の回路図である。

【図16】図15の電圧制御部の動作波形図である。

【図17】比較例の比較回路の回路図である。

【図18】比較例の比較回路の回路図である。

【発明を実施するための形態】

【0009】

(第一実施形態)

以下、第一実施形態を説明する。

図1に示すように、比較回路10は、入力電圧VP,VNを比較して出力信号OP,OMを生成する比較部11と、比較部11の動作電圧を制御する電圧制御部12を備えている。

【0010】

入力電圧VP,VNは、比較部11の入力トランジスタT11,T12に入力される。入力トランジスタT11,T12はNチャネルMOSトランジスタである。入力電圧VP(第1の入力電圧)は入力トランジスタT11のゲートに入力され、入力電圧VN(第2の入力電圧)は入力トランジスタT12のゲートに入力される。両入力トランジスタT11,T12のソースは互いに接続され、その接続点はスイッチングトランジスタT13に接続されている。

【0011】

スイッチングトランジスタT13は入力トランジスタT12,T12と同じ導電型のNチャネルMOSトランジスタである。スイッチングトランジスタT13のドレインは両入力トランジスタT11,T12に接続され、ゲートにはクロック信号CKが供給される。トランジスタT13のソース及びバックゲートと、入力トランジスタT11,T12のバックゲートは互いに接続され、その接続点は電圧制御部12に接続されている。

【0012】

入力トランジスタT11,T12のドレインは、ラッチ部13に接続されている。

ラッチ部13は、互いに入力端子と出力端子がクロスカップル接続された一対のインバータ回路14,15を備える。インバータ回路14は、PチャネルMOSトランジスタT14と、NチャネルMOSトランジスタT15を備えている。インバータ回路15は、PチャネルMOSトランジスタT16と、NチャネルMOSトランジスタT17を備えている。

【0013】

トランジスタT14のソースには高電位電圧AVD(第1の電圧)が供給され、トランジスタT14のドレインはトランジスタT15のドレインと接続され、トランジスタT15のソースは入力トランジスタT11のドレインと接続されている。トランジスタT16のソースには高電位電圧AVDが供給され、トランジスタT16のドレインはトランジスタT17のドレインと接続され、トランジスタT17のソースは入力トランジスタT12のドレインと接続されている。

【0014】

トランジスタT14のドレインとトランジスタT15のドレインとの間のノードN11はトランジスタT16,T17のゲートに接続されている。トランジスタT16のドレインとトランジスタT17のドレインとの間のノードN12は、トランジスタT14,T15のゲートに接続されている。

【0015】

ノードN11にはリセットトランジスタT18が接続されている。リセットトランジスタT18はPチャネルMOSトランジスタであり、ドレインがノードN11に接続され、ソースに高電位電圧AVDが供給され、ゲートにクロック信号CKが供給される。ノードN12にはリセットトランジスタT19が接続されている。リセットトランジスタT19はPチャネルMOSトランジスタであり、ドレインがノードN12に接続され、ソースに高電位電圧AVDが供給され、ゲートにクロック信号CKが供給される。そして、ノードN11から出力信号OMが出力され、ノードN12から出力信号OPが出力される。

【0016】

電圧制御部12は、PチャネルMOSトランジスタT21、NチャネルMOSトランジスタT22,T23、キャパシタC11を備えている。トランジスタT21のソースには高電位電圧AVDが供給され、トランジスタT21のドレインはトランジスタT22のドレインに接続され、トランジスタT22のソースは低電位電圧(第2の電圧)を供給する配線(以下、グランドGND)と接続される。両トランジスタT21,T22のゲートにはクロック信号CKが供給される。トランジスタT21とトランジスタT22はインバータ回路16に含まれる。

【0017】

トランジスタT21のドレインとトランジスタT22のドレインとの間の接続点は、キャパシタC11の第1端子に接続され、キャパシタC11の第2端子は降圧用トランジスタT23のドレインに接続されている。トランジスタT23のソースはグランドGNDに接続されている。トランジスタT23のゲートにはクロック信号XCKが供給される。降圧用トランジスタT23の電気的特性(しきい値電圧)は、入力トランジスタT11,T12のしきい値電圧と等しい値に設定されている。例えば、トランジスタT23のゲート長(L)及びゲート幅(W)と、入力トランジスタT11,T12のゲート長(L)及びライト長(W)とを等しく設定することにより、各トランジスタT11,T12,T23のしきい値電圧が互いに等しくなる。

【0018】

クロック信号XCKは、クロック信号CKに対して相補的に変化する反転クロック信号である。なお、この反転クロック信号XCKのエッジは、クロック信号CKのエッジと同期した、又は進んだタイミングとなるのが好ましい。トランジスタT23のバックゲートはトランジスタT23のドレインとキャパシタC11の第2端子との間のノードN21に接続されている。そして、このノードN21は、比較部11に含まれるトランジスタT13のソース及びトランジスタT11,T12,T13のバックゲートに接続されている。

【0019】

次に、比較回路10の作用を説明する。

[電圧制御部]

クロック信号CKがLレベルのとき、トランジスタT21はクロック信号CKに応答してオンし、トランジスタT22はクロック信号CKに応答してオフし、インバータ回路16は高電位電圧AVDをキャパシタC11の第1端子に供給する。クロック信号CKがLレベルのとき、反転クロック信号XCKはHレベルである。トランジスタT23は、Hレベルの反転クロック信号XCKに応答してオンし、キャパシタC11の第2端子が接続されたノードN21をグランドGNDに接続する。従って、クロック信号CKがLレベルのとき、ノードN21の電位はグランドGNDレベル(=0V)となる。キャパシタC11は、供給される電圧に応じた電荷を蓄積する。この状態を[蓄積状態]という。

【0020】

次いで、反転クロック信号XCKがHレベルからLレベルに立ち下がる(図2の時刻t0)と、Lレベルの反転クロック信号XCKに応答してトランジスタT23がオフし、ノードN21がフローティング状態となる。

【0021】

次いで、クロック信号CKがLレベルからHレベルに立ち上がる(図2の時刻t1)と、インバータ回路16は、Hレベルのクロック信号CKに応答して、キャパシタC11の第1端子をグランドGNDに接続する。すると、図2に示すように、キャパシタC11の第2端子が接続されたノードN21の電位は、キャパシタC11に蓄積された電荷により、負の電圧[−ADV]まで低下する。

【0022】

トランジスタT23は、ゲート及びソースの電位がグランドGNDレベルとなり、ドレイン及びバックゲートの電位がノードN21の電位(−AVD)となる。すると、NチャネルMOSトランジスタT23は、ソース及びバックゲートがノードN21に接続され、そのノードN21の電位より高電位側のグランドGNDにゲート及びドレインが接続される。つまり、トランジスタT23は、ソースとドレインが互いに反転した反転状態となってオンし、グランドGNDからノードN21に向って電流を流す。その結果、ノードN21の電位は、グランドGNDの電位(0V)からトランジスタT23のしきい値電圧Vthn低い電圧[−Vthn]にて安定する。この状態を[降圧状態]という。

【0023】

次いで、反転クロック信号XCKがLレベルからHレベルに立ち上がる(図2の時刻t2)と、Hレベルの反転クロック信号XCKに応答してトランジスタT23がオンし、ノードN21をグランドGNDに接続する。次いで、クロック信号CKがHレベルからLレベルに立ち下がる(図2の時刻t3)と、インバータ回路15はキャパシタC11に高電位電圧AVDを供給する。これにより、キャパシタC11の充電が開始される。

【0024】

このように、電圧制御部12は、クロック信号CKと反転クロック信号XCKに応答して、充電状態と降圧状態とを交互に繰り返し、それぞれの状態に応じた制御電圧VCMを、ノードN21から出力する。

【0025】

[比較部]

クロック信号CKがLレベルのとき、NチャネルMOSトランジスタT13はオフし、PチャネルMOSトランジスタT18,T19はオンする。入力トランジスタT11,T12のソースは、オフしたトランジスタT13によりフローティング状態となる。オンしたトランジスタT18,T19は、ノードN11,N12の電位をHレベルとする。この結果、出力信号OP,OMはHレベルとなる。この時の状態をリセット状態という。そして、クロック信号CKがLレベルである期間をリセット期間という。

【0026】

クロック信号CKがLレベルからHレベルへと変化する(図2の時刻t1)。スイッチングトランジスタT13は、Hレベルのクロック信号CKに応答してオンする。また、リセットトランジスタT18,T19は、Hレベルのクロック信号CKに応答してオフする。

【0027】

トランジスタT13がオンすると、入力トランジスタT11,T12のソースにはノードN21の電位に応じた制御電圧VCM(=−Vthn)が供給される。また、入力トランジスタT11,T12のバックゲートには、制御電圧VCMが供給される。従って、比較部11は、高電位電圧AVDと制御電圧VCM(=−Vthn)とを動作電圧として動作する。そして、トランジスタT14,T15,T11,T13による第1の電流経路を介して電流が流れ、トランジスタT16,T17,T12,T13による第2の電流経路を介して電流が流れる。

【0028】

入力電圧VP,VNの電圧差、つまり入力トランジスタT11,T12のソース−ゲート間電圧Vgsに電圧差は、ノードN11,N12に流れる電流量に差を生じさせ、ノードN11,N12に電位差を生じさせる。ノードN11,N12の電位差は、インバータ回路14,15の正帰還により増幅され、ノードN11,N12のレベルが確定する。そして、ノードN11,N12のレベルに応じてトランジスタT14〜T17がオンオフする。

【0029】

例えば、入力電圧VPが入力電圧VNよりも高い場合、ノードN11の電位がノードN12の電位よりも低くなる。この電位差が増幅され、トランジスタT16がオンし、トランジスタT17がオフし、ノードN12がHレベル(高電位電圧AVDレベル)となる。一方、トランジスタT14がオフし、トランジスタT15がオンし、ノードN11の電位は、トランジスタT15のソース電圧、即ち入力トランジスタT11のソースに供給される制御電圧VCMと等しく、グランドGNDよりしきい値電圧VTHn低い電圧(=−Vthn)で安定する(図2の時刻tc1)。

【0030】

次いで、反転クロック信号XCKがLレベルからHレベルに立ち上がる(図2の時刻t2)と、図1に示すスイッチングトランジスタT13のソースにグランドGNDレベルの制御電圧VCMが供給され、ノードN11の電圧、即ち出力信号OMはグランドGNDレベルへと変化する。次いで、クロック信号CKがHレベルからLレベルに立ち下がる(図2の時刻t3)と、図1に示すスイッチングトランジスタT13がオフし、リセットトランジスタT18,T19がオンする。このオンしたトランジスタT18,T19は、ノードN11,N12のレベルをHレベルにクリップする。

【0031】

次いで、反転クロック信号XCKがHレベルからLレベルに立ち下がる(図2の時刻t4)と、Lレベルの反転クロック信号XCKに応答してトランジスタT23がオフし、ノードN21がフローティング状態となる。つまり、比較回路10は、上記の動作(図2の時刻t0から時刻t3)を繰り返し実行し(例えば、図2の時刻t4から時刻t7)、入力電圧VP,VNの電位差に応じたレベルの信号OM,OPを出力する。

【0032】

上記の比較状態において、入力トランジスタT11,T12のソース及びバックゲートには、グランドGNDよりも降圧用トランジスタT23のしきい値電圧低い制御電圧VCM(=−Vthn)が供給されている。従って、入力電圧VP,VNの電圧範囲は、トランジスタT13のソース電圧と、トランジスタT13のソース−ドレイン間電圧と、入力トランジスタT11,T12のソース−ゲート間電圧の和から、高電位電圧AVDまでの範囲となる。

【0033】

トランジスタT13のソース電圧は、そのトランジスタT13のソースが接続されたノードN21の電圧であり、制御電圧VCMである。トランジスタT13のゲート電圧はクロック信号CKのHレベル、即ち高電位電圧AVDレベルであるため、「0」となる。従って、入力トランジスタT11,T12のしきい値電圧をVthn2とすると、入力電圧VP,VNの範囲は、

(VCM+Vthn2)<VP<AVD

(VCM+Vthn2)<VN<AVD

となる。制御電圧VCMは、グランドGND(=0V)からトランジスタT21のしきい値電圧Vth低い電圧である。そして、降圧用トランジスタT23のしきい値電圧Vthは、入力トランジスタT11,T12のしきい値電圧Vthn2と等しい。従って、入力電圧VP,VNの範囲は、

0(V)<VP<AVD

0(V)<VN<AVD

となる。

【0034】

例えば、図17に示すように、トランジスタT13のソースをグランドGND(=0V)に接続した比較回路80の場合、入力電圧VPの範囲は、

(0+Vthn2)<VP<AVD

となる。従って、比較回路80における入力電圧VP,VNの範囲は、グランドGNDから入力トランジスタT11,T12のしきい値電圧Vthn2高い電圧を低電位側とし、高電位電圧AVDを高電位側とする範囲となる。

【0035】

従って、図1に示す比較回路10は、図17に示す比較回路80と比べ、入力電圧VP,VNの範囲を拡大することができる。

また、図1に示す比較回路10は、駆動電圧の低電圧化に対して有利である。例えば、高電位電圧AVDを3.0(V)とし、入力トランジスタT11,T12のしきい値電圧を1(V)とする。この場合、図17に示す比較回路80における入力電圧VP(VN)の範囲は、

1.0(V)<VP<3.0(V)

となる。従って、一方の入力電圧(例えば、VN)を高電位電圧AVDの2分の1(=1/2)として入力電圧VP,VNを比較するような用途に、図17に示す比較回路80を用いることができる。

【0036】

しかし、低電圧化により高電位電圧AVDが例えば1.8(V)になると、入力電圧VP(VN)の範囲は、

1.0(V)<VP<1.8(V)

となる。従って、一方の入力電圧(例えば、VN)を高電位電圧AVDの2分の1(=1/2)として入力電圧VP,VNを比較するような用途に、図17に示す比較回路80を用いることができない。

【0037】

これに対し、図1に示す比較回路10は、入力電圧VP,VNの範囲が、

0(V)<VP<AVD

0(V)<VN<AVD

である。従って、比較回路10は、一方の入力電圧(例えば、VN)を高電位電圧AVDの2分の1(=1/2)として入力電圧VP,VNを比較するような用途に用いることができる。

【0038】

また、図1に示すトランジスタT13は、Hレベルのクロック信号CKに応答してオンし、入力トランジスタT11,T12のソースに、ノードN21の電圧、即ちグランドGNDよりトランジスタT23のしきい値電圧低い電圧(=−Vthn)を供給する。従って、入力電圧VP,VNがグランドGNDレベルに近づいても、図17に示す回路構成と比べ、入力トランジスタT11,T12のオン抵抗値が増加が少なく、比較速度の低下を抑制することができる。

【0039】

キャパシタC11の容量値は、比較部11の動作と、降圧用トランジスタT23のしきい値電圧Vthnに応じて設定される。比較部11は、Hレベルのクロック信号CKに応答して比較動作を開始し(図2の時刻t1)、入力電圧VP,VNに応じてインバータ回路14,15の出力信号レベルが確定して比較動作を終了する(図2の時刻tc1)。この比較動作の間、高電位電圧AVDが供給される配線からノードN21に向って電流が流れる。キャパシタC11の容量値は、ノードN21の電位が、グランドGNDからトランジスタT23のしきい値電圧Vthn低い電圧以下を保つように設定される。例えば、キャパシタC11の容量値は、比較動作を行う期間(図2の時刻t1から時刻tc1)と、比較部11に流れる電流量の積により得られる電荷Q1と、トランジスタT23のしきい値電圧Vthnとに基づいて、

C11≫Q1/Vthn

となるように設定される。

【0040】

[適用例]

図1に示す比較回路10は、例えば、図3に示すように、逐次変換型のアナログデジタル変換回路(Analog to Digital Converter:ADC)20に用いられる。アナログデジタル変換回路20は、ホールド回路21と、比較回路10と、逐次変換レジスタ(SAR:successive approximation register)回路22と、デジタルアナログ変換回路(Digital to Analog Converter:DAC)23を有している。

【0041】

ホールド回路21は,アナログ入力信号Vinをサンプルクロックに同期してサンプルホールドし、ホールドした電圧Vaを出力する。比較回路10は、クロック信号CKに同期して、ホールド回路21から出力される電圧Va(VP)と判定電圧Vc(VN)とを比較し、入力電圧Vaが判定電圧Vcより大きいか小さいかの判定結果を示す判定信号Vq(OP)を生成する。逐次変換レジスタ回路22は、判定信号Vqを逐次保存するレジスタと,デジタル入力信号DIを生成する論理回路とを有する。SAR回路22は、クロック信号CKに同期して、判定信号Vqを逐次保存しデジタル出力信号Doutとして出力する。また、SAR回路22は、判定信号Vqに応じてデジタル入力信号DIを出力する。デジタルアナログ変換回路(DAC)23は、デジタル入力信号DIをアナログの判定電圧Vcに変換する。

【0042】

このように、電源電圧範囲を入力電圧範囲とする比較回路10を用いることで、アナログ入力信号Vinに対して電源電圧の制約を受けないアナログデジタル変換回路を提供することができる。

【0043】

以上記述したように、本実施形態によれば、以下の効果を奏する。

(1)比較回路10は、入力電圧VP,VNを比較して出力信号OP,OMを生成する比較部11と、比較部11の動作電圧を制御する電圧制御部12を備える。比較部11は、入力電圧VP,VNを受けるPチャネルMOSトランジスタT11,T12と、両トランジスタT11,T12のソースに接続され、ドレインに制御電圧VCMが供給され、クロック信号CKに応答してオンオフするスイッチングトランジスタT13を備える。比較部11は、Hレベルのクロック信号CKに応答して比較状態となり、入力電圧VP,VNの電位差に応じた出力信号OP,OMを出力する。

【0044】

電圧制御部12のインバータ回路16は、キャパシタC11の第1端子に、クロック信号CKに応答して高電位電圧AVDと低電位電圧(グランドGND)を供給する。キャパシタC11の第2端子に接続されたトランジスタT23は、反転クロック信号XCKに応答してオンオフする。トランジスタT23がオフすると、キャパシタC11とトランジスタT23との間のノードN21の電位は、キャパシタC11に蓄積された電荷に応じてグランドGNDから低下する。トランジスタT23のしきい値電圧は入力トランジスタT11,T12のしきい値電圧と等しく設定される。トランジスタT23は、グランドGNDの電圧とノードN21の電圧に応じて反転状態となり、ノードN21の電圧をグランドGNDからトランジスタT23のしきい値電圧低い電圧に安定させる。ノードN21の電圧が制御電圧VCMとして比較部11に供給される。

【0045】

比較部11は、グランドGNDより低い制御電圧VCMと高電位電圧AVDを動作電圧として比較動作する。従って、入力電圧VP,VNの範囲は、高電位電圧AVDからグランドGNDまでの範囲となり、入力範囲を拡大することができる。

【0046】

(2)電圧制御部12は、キャパシタC11に接続されたトランジスタT23の反転動作により、キャパシタC11とトランジスタT23の間ノードN21の電圧を、グランドGNDよりトランジスタT23のしきい値電圧Vthn低い電圧にて安定化させる。従って、チャージポンプ回路などのように、大きな回路を必要とせず、素子数が少なく、占有面積の小さな比較回路を提供することができる。

【0047】

(3)電圧制御部12のキャパシタC11は、グランドGND(0V)よりトランジスタT23のしきい値電圧Vthn低い電圧(制御電圧VCM)を安定的に保持することができればよく、容量の小さなキャパシタC11を用いることができる。このようなキャパシタC11は、配線間容量でも実現可能である。このため、大きな回路を必要とせず、占有面積の小さな比較回路を提供することができる。

【0048】

(4)電圧制御部12のトランジスタT23のしきい値電圧Vthnは、比較部11の入力トランジスタT11,T12のしきい値電圧と等しく設定されている。従って、プロセス条件や動作条件(温度、電源電圧)によって入力トランジスタT11,T12のしきい値電圧が変化しても、トランジスタT23のしきい値電圧Vthnも同様に変化するため、入力電圧VP,VNの範囲が変化するのを抑制することができる。

【0049】

(5)比較部11は、Hレベルのクロック信号CKに応答して比較状態となり、Lレベルのクロック信号CKに応答してリセット状態となる。このリセット状態において、入力トランジスタT11,T12のソースが接続されたスイッチングトランジスタT13は、Lレベルのクロック信号CKに応答してオフする。従って、常に電流が流れる比較回路と比べ、消費電力を低減することができる。

【0050】

(6)入力トランジスタT11,T12のドレインには、クロスカップル接続されたインバータ回路14,15を含むラッチ部13が接続されている。インバータ回路14,15は、PチャネルMOSトランジスタ又はNチャネルMOSトランジスタがオフして出力信号OP,OMのレベルを確定する。従って、比較状態において、出力信号OP,OMのレベルが確定した後は、インバータ回路14,15を介して貫通電力が流れなくなるため、消費連力を低減することができる。

【0051】

(第二実施形態)

以下、第二実施形態を説明する。

なお、第一実施形態と同じ部材については同じ符号を付し、その部材に対する全て又は一部の説明を省略する。

【0052】

図4に示すように、比較回路10aは、入力電圧VP,VNを比較して出力信号OP,OMを生成する比較部11aと、比較部11aの動作電圧を制御する電圧制御部12aを備えている。

【0053】

入力電圧VP,VNは、比較部11aの入力トランジスタT11,T12に入力される。入力トランジスタT11,T12のソースは互いに接続され、その接続点はスイッチングトランジスタT13aに接続されている。

【0054】

スイッチングトランジスタT13aは入力トランジスタT12,T12と同じ導電型であるNチャネルMOSトランジスタである。スイッチングトランジスタT13aのドレインは両入力トランジスタT11,T12に接続され、ゲートにはクロック信号CKが供給される。トランジスタT13aのソースは、電圧制御部12aのノードN21に接続され、そのノードN21の制御電圧VCMが供給される。トランジスタT13aのバックゲートと、入力トランジスタT11,T12のバックゲートはグランドGNDに接続されている。

【0055】

電圧制御部12aのトランジスタT23aのソース及びバックゲートはグランドGNDに接続されている。このトランジスタT23aは、バックゲートとソース、もしくはバックゲートとドレインの間に形成される寄生ダイオードを有している。電圧制御部12aのトランジスタT22がHレベルのクロック信号CKに応答してオンするとき(降圧動作)、グランドGNDからトランジスタT23の寄生ダイオードを介してキャパシタC11に向って電流が流れる。この電流を流す寄生ダイオードの順方向電圧VFは、トランジスタT23のしきい値電圧Vthnより高い。従って、キャパシタC11の第2端子が接続されたノードN21の電位は、グランドGNDよりトランジスタT23の寄生ダイオードにおける順方向電圧だけ低い電圧(=−VF)となる。そして、このノードN21とグランドGNDとの間の電位差は、入力トランジスタT11,T12のしきい値電圧Vthnより大きい。従って、入力トランジスタT11,T12のソースは、両トランジスタT11,T12のしきい値電圧Vthnより低い電圧(=−VF)となる。このため、入力トランジスタT11,T12及びスイッチングトランジスタT13aのバックゲートをグランドGNDに接続することができる。

【0056】

この場合、比較部11aに含まれるトランジスタのうち、少なくともスイッチングトランジスタT13aは、図5に示すように構成される。P型半導体基板100には、N+型拡散層101とN+型拡散層102とP−型領域103が形成され、両拡散層101,102の間において、基板100上に絶縁層(例えば、酸化膜)104及び導電層105が形成されている。これらN+型拡散層101、N+型拡散層102、導電層105、P−領域103は、それぞれトランジスタT13aのドレイン、ソース、ゲート、バックゲートとなる。

【0057】

比較例として、図1に示すスイッチングトランジスタT13の概略構成を図6に示す。P型半導体基板110には、ディープN型ウェル(Deep Nwell)111とP−型領域112が形成され、ウェル111にP型ウェル(Pwell)113とN−型領域114が形成されている。P型ウェル113には、N+型拡散層115,116とP−型領域117が形成されている。N+型拡散層115,116の間において、P型ウェル113の表面には絶縁層(酸化膜)118及び導電層119が形成されている。これらN+型拡散層115、N+型拡散層116、導電層119、P−型領域117は、それぞれトランジスタT13のドレイン、ソース、ゲート、バックゲートとなる。N−型領域114には高電位電圧AVDが供給され、P−型領域112はグランドGNDに接続される。

【0058】

このように、図4,図5に示すトランジスタT13aは、図1,図6に示すトランジスタT13と比べ、占有面積が少なく、比較回路10aを含む半導体チップの面積の縮小を図ることができる。また、図5に示すトランジスタT13aは、図6に示すトランジスタT13と比べ、構造が簡単で製造工数が少ない。

【0059】

この実施形態における比較回路10aは、図1に示す比較回路10と同様に、図3に示す逐次比較型のアナログデジタル変換回路に用いることができる。

以上記述したように、本実施形態によれば、第一実施形態の効果に加え、以下の効果を奏する。

【0060】

(7)寄生ダイオードの順方向電圧VFがしきい値電圧Vthnより大きなトランジスタT23aを用いて制御電圧VCMを生成することで、比較部11aのトランジスタT13aの構造を簡略化することができ、占有面積を低減することができる。

【0061】

(第三実施形態)

以下、第三実施形態を説明する。

なお、上記各実施形態と同じ部材については同じ符号を付し、その部材に対する一部又は全ての説明を省略する。

【0062】

図7に示すように、比較回路30は、比較部11と電圧制御部12とラッチ部31を備えている。ラッチ部31は、2つのナンド回路32,33を備えている。ナンド回路32の1つの入力端子は比較部11のノードN11に接続され、信号OMを入力する。ナンド回路32の他の1つの入力端子はナンド回路33の出力端子に接続され、ナンド回路32は信号OP2を出力する。ナンド回路33の1つの入力端子は比較部11のノードN12に接続され、信号OPを入力する。ナンド回路33の他の1つの入力端子はナンド回路32の出力端子に接続されている。ナンド回路33は、信号OM2を出力する。

【0063】

ナンド回路32,33は、2つの入力信号のうちの少なくとも一方の信号がLレベルのときにHレベルの信号を出力し、2つの入力信号がともにHレベルのときにLレベルの信号を出力する。

【0064】

比較部11は、Hレベルのクロック信号CKに応答して比較状態となり、入力電圧VP,VNの電位差に応じたレベルの信号OP,OMを出力する。

例えば、入力電圧VPが入力電圧VNより高いとき、比較部11は、Lレベルの信号OMと、Hレベルの信号OPを出力する。Lレベルの信号OMを受けるナンド回路32はHレベルの信号OP2を出力する。ナンド回路33は、Hレベルの信号OPとHレベルの信号OP2に基づいてLレベルの信号OM2を出力する。ナンド回路32は、Lレベルの信号OMと、Lレベルの信号OM2を受ける。

【0065】

また、入力電圧VPが入力電圧VNより低いとき、比較部11は、Hレベルの信号OMと、Lレベルの信号OPを出力する。Lレベルの信号OPを受けるナンド回路33はHレベルの信号OM2を出力する。ナンド回路32は、Hレベルの信号OMとHレベルの信号OM2に基づいてLレベルの信号OP2を出力する。ナンド回路33は、Lレベルの信号OPと、Lレベルの信号OP2を受ける。つまり、ラッチ部31は、比較部11の比較動作によって出力される信号OP,OMとそれぞれ等しいレベルの信号OP2,OM2を出力する。

【0066】

比較部11は、Lレベルのクロック信号CKに応答してリセット状態となり、ノードN11,N12を高電位電圧AVDレベル(Hレベル)にリセットする。つまり、リセット状態の比較部11は、Hレベルの信号OP,OMを出力する。

【0067】

比較状態において、2つのナンド回路32,33のうちの何れか一方は2つのLレベルの信号を受け、2つのナンド回路32,33のうちの何れか他方は2つのHレベルの信号を受ける。2つのLレベルの信号を受けるナンド回路は、Hレベルの信号を受けても、出力信号のレベルを変更しない。また、2つのHレベルの信号を受けるナンド回路は、Hレベルの信号を受ける、つまり入力信号のレベルが変化しないため、出力信号のレベルを変更しない。

【0068】

つまり、ラッチ部31は、比較状態(図8の時刻t1から時刻tc1の間)の比較部11が出力する信号OP,OMのレベルを保持し、保持したレベルに応じた信号OP2,OM2を出力する。また、ラッチ部31は、出力信号OP2,OM2のレベルを、次の比較によってノードN11,N12のレベルが確定するまで(例えば、図8の時刻t2から時刻tc2までの間)出力する。

【0069】

この実施形態における比較回路30は、図1に示す比較回路10と同様に、図3に示す逐次比較型のアナログデジタル変換回路に用いることができる。

以上記述したように、本実施形態によれば、以下の効果を奏する。

【0070】

(1)ラッチ部31は、一対のナンド回路32,33を備える。ラッチ部31は、比較状態の比較部11から出力される信号OP,OMをラッチし、信号OP,OMに応じたレベルの信号OP2,OM2を出力する。また、ラッチ部31は、リセット状態の比較部11から出力されるHレベルの信号OP,OMに応答して出力信号OP2,OM2のレベルを保持する。従って、この比較回路30は、クロック信号CKに同期して動作し、クロック信号CKの1周期の間、入力電圧VP,VNの電位差に応じた出力信号OP2,OM2を出力することができる。

【0071】

(第四実施形態)

以下、第四実施形態を説明する。

図9に示すように、比較回路40は、入力電圧VP,VNを比較して出力信号OP,OMを生成する比較部41と、比較部41の動作電圧を制御する電圧制御部42を備えている。

【0072】

入力電圧VP,VNは、比較部41の入力トランジスタT31,T32に入力される。入力トランジスタT31,T32はPチャネルMOSトランジスタである。入力電圧VPは入力トランジスタT31のゲートに入力され、入力電圧VNは入力トランジスタT32のゲートに入力される。両入力トランジスタT31,T32のソースは互いに接続され、その接続点はスイッチングトランジスタT33に接続されている。

【0073】

スイッチングトランジスタT33は入力トランジスタT32,T32と同じ導電型のPチャネルMOSトランジスタである。スイッチングトランジスタT33のドレインは両入力トランジスタT31,T32に接続され、ゲートにはクロック信号CKが供給される。トランジスタT33のソース及びバックゲートと、入力トランジスタT31,T32のバックゲートは互いに接続され、その接続点は電圧制御部42に接続されている。

【0074】

入力トランジスタT31,T32のドレインは、ラッチ部43に接続されている。

ラッチ部43は、互いに入力端子と出力端子がクロスカップル接続された一対のインバータ回路44,45を備える。インバータ回路44は、PチャネルMOSトランジスタT34と、NチャネルMOSトランジスタT35を備えている。インバータ回路45は、PチャネルMOSトランジスタT36と、NチャネルMOSトランジスタT37を備えている。

【0075】

トランジスタT34のソースは入力トランジスタT31のドレインに接続され、トランジスタT34のドレインはトランジスタT35のドレインと接続され、トランジスタT35のソースはグランドGNDに接続されている。トランジスタT36のソースは入力トランジスタT32のドレインに接続され、トランジスタT36のドレインはトランジスタT37のドレインと接続され、トランジスタT37のソースはグランドGNDと接続されている。

【0076】

トランジスタT34のドレインとトランジスタT35のドレインとの間のノードN31はトランジスタT36,T37のゲートに接続されている。トランジスタT36のドレインとトランジスタT37のドレインとの間のノードN32は、トランジスタT34,T35のゲートに接続されている。

【0077】

ノードN31にはリセットトランジスタT38が接続されている。リセットトランジスタT38はNチャネルMOSトランジスタであり、ドレインがノードN31に接続され、ソースはグランドGNDに接続され、ゲートにクロック信号CKが供給される。ノードN32にはリセットトランジスタT39が接続されている。リセットトランジスタT39はNチャネルMOSトランジスタであり、ドレインがノードN32に接続され、ソースはグランドGNDに接続され、ゲートにクロック信号CKが供給される。そして、ノードN31から出力信号OMが出力され、ノードN32から出力信号OPが出力される。

【0078】

電圧制御部42は、PチャネルMOSトランジスタT41,T42、NチャネルMOSトランジスタT43、キャパシタC21を備えている。トランジスタT41のソースには高電位電圧AVD(第2の電圧)が供給され、トランジスタT41のドレインはキャパシタC21の第1端子に接続されている。トランジスタT41のゲートには反転クロック信号XCKが供給され、トランジスタT41のバックゲートはトランジスタT41のドレインと接続されている。トランジスタT41のドレインとキャパシタC21の第1端子との間のノードN41は、比較部41に含まれるトランジスタT33のソース及びトランジスタT31,T32,T33のバックゲートに接続されている。

【0079】

キャパシタC21の第2端子は、トランジスタT42のドレインとトランジスタT43のドレインとの間の接続点に接続されている。トランジスタT42のソースには高電位電圧AVDが供給され、トランジスタT43のソースは低電位電圧(第1の電圧)を供給する配線(以下、グランドGND)と接続される。両トランジスタT42,T43のゲートは互いに接続され、クロック信号CKが供給される。トランジスタT42とトランジスタT43はインバータ回路46に含まれる。

【0080】

次に、比較回路40の作用を説明する。

[電圧制御部]

反転クロック信号XCKがLレベルのとき、トランジスタT41は、Lレベルの反転クロック信号XCKに応答してオンし、キャパシタC21の第1端子に高電位電圧AVDを供給する。クロック信号CKがHレベルのとき、トランジスタT42はHレベルのクロック信号CKに応答してオフし、トランジスタT43はHレベルのクロック信号CKに応答してオンし、インバータ回路46はキャパシタC11の第2端子をグランドに接続する。従って、クロック信号CKがLレベルのとき、ノードN41の電位は高電位電圧AVDレベルとなる。キャパシタC11は、供給される電圧に応じた電荷を蓄積する。この状態を[蓄積状態]という。

【0081】

次いで、反転クロック信号XCKがLレベルからHレベルに立ち上がる(図10の時刻t0)と、Hレベルの反転クロック信号XCKに応答してトランジスタT41がオフし、ノードN41がフローティング状態となる。

【0082】

次いで、クロック信号CKがHレベルからLレベルに立ち下がる(図10の時刻t1)と、インバータ回路46は、Lレベルのクロック信号CKに応答して、キャパシタC11の第2端子に高電位電圧AVDを供給する。すると、図10に示すように、キャパシタC11の第2端子が接続されたノードN41の電位は、キャパシタC11に蓄積された電荷により、正の電圧[=ADV×2]まで上昇する。

【0083】

トランジスタT41は、ゲート及びソースの電位が高電位電圧AVDレベルであり、ドレイン及びバックゲートの電位がノードN41の電位(AVD×2)となる。すると、PチャネルMOSトランジスタT41は、ソース及びバックゲートがノードN41に接続され、そのノードN41の電位より低電位側の電圧AVDがゲート及びドレインに供給される。つまり、トランジスタT41は、ソースとドレインが互いに反転した反転状態となってオンし、キャパシタC21から高電位電圧AVDに向って電流を流す。その結果、ノードN41の電位は、高電位電圧AVDからトランジスタT41のしきい値電圧Vthp高い電圧[=AVD+Vthp]にて安定する。この状態を[昇圧状態]という。

【0084】

次いで、反転クロック信号XCKがHレベルからLレベルに立ち下がる(図10の時刻t2)と、Lレベルの反転クロック信号XCKに応答してトランジスタT41がオンし、キャパシタC21の第1端子に高電位電圧AVDを供給する。次いで、クロック信号CKがLレベルからHレベルに立ち上がる(図10の時刻t3)と、インバータ回路46は、キャパシタC21の第2端子をグランドGNDに接続する。これにより、キャパシタC21の充電が開始される。

【0085】

このように、電圧制御部42は、クロック信号CKと反転クロック信号XCKに応答して、充電状態と昇圧状態とを交互に繰り返し、それぞれの状態に応じた制御電圧VCP1を、ノードN41から出力する。

【0086】

[比較部]

クロック信号CKがHレベルのとき、PチャネルMOSトランジスタT33はオフし、NチャネルMOSトランジスタT38,T39はオンする。入力トランジスタT31,T32のソースは、オフしたトランジスタT33によりフローティング状態となる。オンしたトランジスタT38,T39は、ノードN31,N32の電位をLレベルとする。この結果、出力信号OP,OMはLレベルとなる。この時の状態をリセット状態という。そして、クロック信号CKがHレベルである期間をリセット期間という。

【0087】

クロック信号CKがHレベルからLレベルへと変化する(図10の時刻t1)。スイッチングトランジスタT33は、Lレベルのクロック信号CKに応答してオンする。また、リセットトランジスタT38,T39は、Lレベルのクロック信号CKに応答してオフする。

【0088】

トランジスタT33がオンすると、入力トランジスタT31,T32のソースにはノードN41の電位に応じた制御電圧VCP1(=AVD+Vthp)が供給される。また、入力トランジスタT31,T32のバックゲートには、制御電圧VCP1が供給される。従って、比較部41は、制御電圧VCP1(=AVD+Vthp)とグランドGNDの電圧(=0V)を動作電圧として動作する。そして、トランジスタT33,T31,T34,T35による第1の電流経路を介して電流が流れ、トランジスタT33,T32,T36,T37による第2の電流経路を介して電流が流れる。

【0089】

入力電圧VP,VNの電圧差、つまり入力トランジスタT31,T32のソース−ゲート間電圧Vgsに電圧差は、ノードN31,N32に流れる電流量に差を生じさせ、ノードN31,N32に電位差を生じさせる。ノードN31,N32の電位差は、インバータ回路44,45の正帰還により増幅され、ノードN31,N32のレベルが確定する。そして、ノードN31,N32のレベルに応じてトランジスタT34〜T37がオンオフする。

【0090】

例えば、入力電圧VPが入力電圧VNよりも高い場合、ノードN31の電位がノードN32の電位よりも低くなる。この電位差が増幅され、トランジスタT36がオンし、トランジスタT37がオフし、ノードN32がHレベル(制御電圧VCP1のレベル)となる。一方、トランジスタT34がオフし、トランジスタT35がオンし、ノードN31の電位は、Lレベル(グランドGNDレベル)で安定する(図10の時刻tc1)。

【0091】

次いで、反転クロック信号XCKがHレベルからLレベルに立ち下がる(図10の時刻t2)と、図9に示すスイッチングトランジスタT33のソースに高電位電圧AVDレベルの制御電圧VCP1が供給され、ノードN31の電圧、即ち出力信号OMはグランドGNDレベルへと変化する。次いで、クロック信号CKがLレベルからHレベルに立ち上がる(図10の時刻t3)と、図9に示すスイッチングトランジスタT33がオフし、リセットトランジスタT38,T39がオンする。このオンしたトランジスタT38,T39は、ノードN31,N32のレベルをLレベルにクリップする。

【0092】

次いで、反転クロック信号XCKがLレベルからHレベルに立ち上がる(図10の時刻t4)と、Hレベルの反転クロック信号XCKに応答してトランジスタT41がオフし、ノードN41がフローティング状態となる。つまり、比較回路10は、上記の動作(図10の時刻t0から時刻t3)を繰り返し実行し(例えば、図10の時刻t4から時刻t7)、入力電圧VP,VNの電位差に応じたレベルの信号OM,OPを出力する。

【0093】

上記の比較状態において、入力トランジスタT31,T32のソース及びバックゲートには、高電位電圧AVDよりも昇圧用トランジスタT41のしきい値電圧高い制御電圧VCP1(=AVD+Vthp)が供給されている。従って、入力電圧VP,VNの電圧範囲は、トランジスタT33のソース電圧から、トランジスタT33のソース−ドレイン間電圧と、入力トランジスタT31,T32のソース−ゲート間電圧の和から、高電位電圧AVDまでの範囲となる。

【0094】

トランジスタT33のソース電圧は、そのトランジスタT33のソースが接続されたノードN41の電圧であり、制御電圧VCP1である。トランジスタT33のゲート電圧はクロック信号CKのLレベル、即ち高電位電圧AVDレベルであるため、「0」となる。従って、入力トランジスタT31,T32のしきい値電圧をVthp2とすると、入力電圧VP,VNの範囲は、

0(V)<VP<(VCP1−Vthp2)

0(V)<VN<(VCP1−Vthp2)

となる。制御電圧VCP1は、高電位電圧AVDからトランジスタT21のしきい値電圧Vthp高い電圧である。そして、降圧用トランジスタT23のしきい値電圧Vthpは、入力トランジスタT31,T32のしきい値電圧Vthp2と等しい。従って、入力電圧VP,VNの範囲は、

0(V)<VP<AVD

0(V)<VN<AVD

となる。

【0095】

例えば、図18に示すように、トランジスタT33のソースに高電位電圧AVDを供給した比較回路90の場合、入力電圧VPの範囲は、

0(V)<VP<(AVD−Vthp2)

となる。従って、比較回路90における入力電圧VP,VNの範囲は、グランドGNDを低電位側とし、高電位電圧AVDから入力トランジスタT31,T32のしきい値電圧Vthp2低い電圧を高電位側とする範囲となる。

【0096】

従って、図9に示す比較回路10は、図18に示す比較回路90と比べ、入力電圧VP,VNの範囲を拡大することができる。

また、図9に示す比較回路10は、図1に示す比較回路10と同様に、駆動電圧の低電圧化に対して有利である。例えば、高電位電圧AVDを3.0(V)とし、入力トランジスタT31,T32のしきい値電圧を1(V)とする。この場合、図18に示す比較回路90における入力電圧VP(VN)の範囲は、

0(V)<VP<2.0(V)

となる。従って、一方の入力電圧(例えば、VN)を高電位電圧AVDの2分の1(=1/2)として入力電圧VP,VNを比較するような用途に、図18に示す比較回路90を用いることができる。

【0097】

しかし、低電圧化により高電位電圧AVDが例えば1.8(V)になると、入力電圧VP(VN)の範囲は、

0(V)<VP<0.8(V)

となる。従って、一方の入力電圧(例えば、VN)を高電位電圧AVDの2分の1(=1/2)として入力電圧VP,VNを比較するような用途に、図18に示す比較回路90を用いることができない。

【0098】

これに対し、図9に示す比較回路10は、入力電圧VP,VNの範囲が、

0(V)<VP<AVD

0(V)<VN<AVD

である。従って、比較回路10は、一方の入力電圧(例えば、VN)を高電位電圧AVDの2分の1(=1/2)として入力電圧VP,VNを比較するような用途に用いることができる。

【0099】

また、図9に示すトランジスタT33は、Lレベルのクロック信号CKに応答してオンし、入力トランジスタT31,T32のソースに、ノードN41の電圧、即ち高電位電圧AVDよりトランジスタT41のしきい値電圧高い電圧(=AVD+Vthp)を供給する。従って、入力電圧VP,VNが高電位電圧AVDレベルに近づいても、図18に示す回路構成と比べ、入力トランジスタT31,T32のオン抵抗値が増加が少なく、比較速度の低下を抑制することができる。

【0100】

キャパシタC21の容量値は、比較部41の動作と、昇圧用トランジスタT41のしきい値電圧Vthpに応じて設定される。比較部41は、Lレベルのクロック信号CKに応答して比較動作を開始し(図10の時刻t1)、入力電圧VP,VNに応じてインバータ回路14,15の出力信号レベルが確定して比較動作を終了する(図10の時刻tc1)。この比較動作の間、制御電圧VCP1を供給するノードN41からグランドGNDに向って電流が流れる。キャパシタC11の容量値は、ノードN41の電位が、高電位電圧AVDからトランジスタT41のしきい値電圧Vthp高い電圧以上を保つように設定される。例えば、キャパシタC21の容量値は、比較動作を行う期間(図10の時刻t1から時刻tc1)と、比較部41に流れる電流量の積により得られる電荷Q2と、トランジスタT41のしきい値電圧Vthpとに基づいて、

C21≫Q2/Vthp

となるように設定される。

【0101】

この実施形態における比較回路40は、図1に示す比較回路10と同様に、図3に示す逐次比較型のアナログデジタル変換回路に用いることができる。

以上記述したように、本実施形態によれば、第一実施形態と同様の効果をえることができる。

【0102】

(第五実施形態)

以下、第五実施形態を説明する。

なお、上記各実施形態と同じ部材については同じ符号を付し、その部材に対する一部又は全ての説明を省略する。

【0103】

図11に示すように、比較回路50は、比較部41と電圧制御部42とラッチ部51を備えている。ラッチ部51は、2つのノア回路52,53を備えている。ノア回路52の1つの入力端子は比較部41のノードN31に接続され、信号OMを入力する。ノア回路52の他の1つの入力端子はノア回路53の出力端子に接続され、ノア回路52は信号OP2を出力する。ノア回路53の1つの入力端子は比較部41のノードN32に接続され、信号OPを入力する。ノア回路53の他の1つの入力端子はノア回路52の出力端子に接続されている。ノア回路53は、信号OM2を出力する。

【0104】

ノア回路52,53は、2つの入力信号のうちの少なくとも一方の信号がHレベルのときにLレベルの信号を出力し、2つの入力信号がともにLレベルのときにHレベルの信号を出力する。

【0105】

比較部41は、Lレベルのクロック信号CKに応答して比較状態となり、入力電圧VP,VNの電位差に応じたレベルの信号OP,OMを出力する。

例えば、入力電圧VPが入力電圧VNより高いとき、比較部41は、Lレベルの信号OMと、Hレベルの信号OPを出力する。Hレベルの信号OPを受けるノア回路53はLレベルの信号OM2を出力する。ノア回路52は、Lレベルの信号OMとLレベルの信号OM2に基づいてHレベルの信号OP2を出力する。ノア回路53は、Hレベルの信号OPと、Hレベルの信号OP2を受ける。

【0106】

また、入力電圧VPが入力電圧VNより低いとき、比較部41は、Hレベルの信号OMと、Lレベルの信号OPを出力する。Hレベルの信号OMを受けるノア回路52はLレベルの信号OP2を出力する。ノア回路53は、Lレベルの信号OPとLレベルの信号OP2に基づいてHレベルの信号OM2を出力する。ノア回路52は、Hレベルの信号OMと、Hレベルの信号OM2を受ける。つまり、ラッチ部51は、比較部41の比較動作によって出力される信号OP,OMとそれぞれ等しいレベルの信号OP2,OM2を出力する。

【0107】

比較部41は、Hレベルのクロック信号CKに応答してリセット状態となり、ノードN31,N32をグランドGNDレベル(Lレベル)にリセットする。つまり、リセット状態の比較部41は、Lレベルの信号OP,OMを出力する。

【0108】

比較状態において、2つのノア回路52,53のうちの何れか一方は2つのLレベルの信号を受け、2つのノア回路52,53のうちの何れか他方は2つのHレベルの信号を受ける。2つのHレベルの信号を受けるノア回路は、Lレベルの信号を受けても、出力信号のレベルを変更しない。また、2つのLレベルの信号を受けるノア回路は、Lレベルの信号を受ける、つまり入力信号のレベルが変化しないため、出力信号のレベルを変更しない。

【0109】

つまり、ラッチ部51は、比較状態(図12の時刻t1から時刻tc1の間)の比較部41が出力する信号OP,OMのレベルを保持し、保持したレベルに応じた信号OP2,OM2を出力する。また、ラッチ部51は、出力信号OP2,OM2のレベルを、次の比較によってノードN31,N32のレベルが確定するまで(例えば、図12の時刻t2から時刻tc2までの間)出力する。

【0110】

この実施形態における比較回路50は、図1に示す比較回路10と同様に、図3に示す逐次比較型のアナログデジタル変換回路に用いることができる。

以上記述したように、本実施形態によれば、第三実施形態と同様の効果を得ることができる。

【0111】

尚、上記各実施形態は、以下の態様で実施してもよい。

・図9に示す実施形態では、入力トランジスタT31,T32のバックゲートとスイッチングトランジスタT33のバックゲートとを電圧制御部42のノードN41に接続して制御電圧VCP1を供給するようにした。これに対し、各トランジスタT31,T32,T33のバックゲートに高電位電圧AVDを供給するようにしてもよい。

【0112】

・電圧制御部の構成を適宜変更しても良い。

例えば、図13に示す電圧制御部61は、PチャネルMOSトランジスタT61(スイッチ部)、NチャネルMOSトランジスタT62、インダクタL11、キャパシタC31を備える。トランジスタT61は、ソースに高電位電圧AVDが供給され、ゲートにクロック信号CKが供給され、ドレインにインダクタL11の第1端子が接続される。インダクタL11の第2端子はグランドGNDに接続される。トランジスタT61のドレインとインダクタL11の第1端子との間のノードN61はトランジスタT62に接続されている。トランジスタT62は、第1端子(例えばドレイン)がノードN61に接続され、ゲートはグランドGNDに接続され、バックゲートと第2端子(例えばソース)が互いに接続されている。キャパシタC31の第1端子はトランジスタT62の第2端子に接続され、キャパシタC31の第2端子はグランドGNDに接続されている。

【0113】

この電圧制御部61の動作を図14に従って説明する。

クロック信号CKがLレベルのとき、トランジスタT61はオンし、トランジスタT61を介してインダクタL11に電流が流れる。このとき、ノードN61はグランドGNDレベルにある。また、トランジスタT62はオフし、キャパシタC31の第1端子はフローティング状態にある(初期状態)。

【0114】

クロック信号CKがLレベルからHレベルに立ち上がる(図14の時刻t1)と、トランジスタT61がオフする。すると、インダクタL11に流れる電流が減少し、ノードN61の電位がグランドGNDより低くなる。

【0115】

ノードN61の電圧V61は、

V(t)=L11×di(t)/dt

により、di(t)/dtが負であり、V(t)=V61−0(V)であるため、

V61=0(V)−L11|di(t)/dt|

となる。

【0116】

ノードN61の電圧がトランジスタT62のしきい値電圧より低くなるとトランジスタT62がオンし、ノードN61の電圧と等しい制御電圧VCMが比較回路に供給される。

インダクタL11の電流変化が収束し、ノードN61の電圧はグランドGNDの電圧に収束する。このとき、ノードN61の電圧が、設定電圧(グランドGNDよりトランジスタT62のしきい値電圧Vthn低い電圧)より高くなる(図14の時刻t3)と、トランジスタT62がオフし、制御電圧VCMはキャパシタC31により設定電圧(=−Vthn)に保持される。

【0117】

次いで、クロック信号CKがHレベルからLレベルに立ち下がる(図14の時刻t4)と、電圧制御部61の各素子は初期状態に戻る。制御電圧VCMはキャパシタC31により設定電圧(=−Vthn)に保持される。

【0118】

また、図15に示す電圧制御部71は、NチャネルMOSトランジスタT71(スイッチ部)、PチャネルMOSトランジスタT72、インダクタL21、キャパシタC41を備える。インダクタL21の第1端子には高電位電圧AVDが供給され、インダクタL21の第2端子はトランジスタT71のドレインに接続されている。トランジスタT71はゲートにクロック信号CKが供給され、ソースがグランドGNDに接続されている。インダクタL21の第2端子とトランジスタT71のドレインとの間のノードN71はトランジスタT72に接続されている。トランジスタT72は、第1端子(例えばドレイン)がノードN71に接続され、ゲートに高電位電圧AVDが供給され、バックゲートと第2端子(例えばソース)が互いに接続されている。キャパシタC41の第1端子はトランジスタT72の第2端子と接続され、キャパシタC41の第2端子はグランドGNDに接続されている。

【0119】

この電圧制御部71の動作を図16に従って説明する。

クロック信号CKがHレベルのとき、トランジスタT71はオンし、インダクタL21に電流が流れる。このとき、ノードN71はグランドGNDレベルにある。また、トランジスタT72はオフし、キャパシタC41の第1端子はフローティング状態にある(初期状態)。

【0120】

クロック信号CKがHレベルからLレベルに立ち下がる(図16の時刻t1)と、トランジスタT71がオフする。すると、インダクタL21に流れる電流が減少し、ノードN71の電位が高電位電圧AVDより高くなる。

【0121】

ノードN71の電圧V71は、

V(t)=L21×di(t)/dt

により、di(t)/dtが負であり、V(t)=AVD−V71であるため、

V71=AVD+L21|di(t)/dt|

となる。

【0122】

ノードN71の電圧が設定電圧(高電位電圧AVDよりトランジスタT72のしきい値電圧Vthp高い電圧)より高くなるとトランジスタT72がオンし、ノードN71の電圧と等しい制御電圧VCP1が比較回路に供給される。

【0123】

インダクタL21の電流変化が収束し、ノードN71の電圧は高電位電圧AVDに収束する。このとき、ノードN71の電圧V71が、設定電圧(高電位電圧AVDよりトランジスタT72のしきい値電圧Vthp高い電圧)より低くなる(図16の時刻t3)と、トランジスタT72がオフし、制御電圧VCP1はキャパシタC41により設定電圧(=AVD+Vthp)に保持される。

【0124】

次いで、クロック信号CKがLレベルからHレベルに立ち下がる(図16の時刻t4)と、電圧制御部71の各素子は初期状態に戻る。制御電圧VCP1はキャパシタC41により目標電圧(=AVD+Vthp)に保持される。

【0125】

・上記各実施形態において、制御電圧を降圧又は昇圧するタイミングと、比較部が比較動作を開始するタイミングとを適宜変更してもよい。これらのタイミングは、例えば電圧制御部と比較部に互いに異なるクロック信号を供給する、クロック信号に応答する回路の動作速度(応答速度)を変更することで、設定することが可能である。

【0126】

・上記第二実施形態において、しきい値電圧Vthnに対して寄生ダイオードの順方向電圧VFが大きいトランジスタT23aを用いた。寄生ダイオードの順方向電圧VFが入力トランジスタT11,T12のしきい値電圧より大きければよく、トランジスタT23aのしきい値電圧を適宜変更してもよい。

【0127】

上記各実施形態に関し、以下の付記を開示する。

(付記1)

クロック信号に応答してキャパシタの第1端子に第1の電圧と第2の電圧とを交互に供給するインバータ回路と、前記キャパシタの第2端子に第1端子が接続され、ゲートに反転クロック信号が供給され、第2端子に前記第2の電圧が供給されるトランジスタとを含み、前記キャパシタと前記トランジスタとの間のノードに前記第2の電圧と前記キャパシタの蓄積電荷に応じた制御電圧を生成する電圧制御部と、

第1の入力電圧をゲートに受ける第1のトランジスタと、第2の入力電圧をゲートに受ける第2のトランジスタと、前記クロック信号がゲートに供給され、ソースに前記制御電圧が供給され、ドレインが前記第1のトランジスタのソースと前記第2のトランジスタのソースにそれぞれ接続された第3のトランジスタを含み、クロック信号に応答して、前記第1の入力電圧と前記第2の入力電圧との比較結果に応じた出力信号を生成する比較動作と、前記第1の電圧に応じたレベルの前記出力信号を生成するリセット動作とを交互に行う比較部と、

を有する比較回路。

(付記2)

前記電圧制御部の前記トランジスタのバックゲートは前記制御電圧を生成するノードに接続され、

前記比較部の前記第1〜第3のトランジスタのバックゲートには前記制御電圧が供給される、

ことを特徴とする付記1記載の比較回路。

(付記3)

前記電圧制御部の前記トランジスタのバックゲートには前記第1の電圧が供給され、

前記比較部の前記第1〜第3のトランジスタのバックゲートには前記第1の電圧が供給される、

ことを特徴とする付記1記載の比較回路。

(付記4)

一端に第2の電圧が供給されるインダクタの他端に対してクロック信号に応答して第1の電圧の供給と停止を行うスイッチ部と、前記インダクタと前記スイッチ部との間のノードに第1端子が接続され、ゲートに前記第2の電圧が供給され、バックゲートと第2端子が互いに接続されたトランジスタを含み、前記トランジスタの第2端子に制御電圧を生成する電圧制御部と、

第1の入力電圧をゲートに受ける第1のトランジスタと、第2の入力電圧をゲートに受ける第2のトランジスタと、前記クロック信号がゲートに供給され、ソースに前記制御電圧が供給され、ドレインが前記第1のトランジスタのソースと前記第2のトランジスタのソースにそれぞれ接続された第3のトランジスタを含み、クロック信号に応答して、前記第1の入力電圧と前記第2の入力電圧との比較結果に応じた出力信号を生成する比較動作と、前記第1の電圧に応じたレベルの前記出力信号を生成するリセット動作とを交互に行う比較部と、

を有する比較回路。

(付記5)

前記電圧制御部は、前記第2の電圧より低い前記制御電圧を生成するものであり、

前記トランジスタの第2端子に一端が接続され、他端に前記第2の電圧が供給されたキャパシタを含む、ことを特徴とする付記4記載の比較回路。

(付記6)

前記電圧制御部は、前記第2の電圧より高い前記制御電圧を生成するものであり、

前記トランジスタの第2端子に一端が接続され、他端に前記第1の電圧が供給されるキャパシタを含む、ことを特徴とする付記4記載の比較回路。

(付記7)

前記比較部は、

前記第1のトランジスタのドレインと前記第2のトランジスタのドレインにそれぞれ接続され、前記第1の電圧が供給され、互いに入力端子と出力端子がクロスカップル接続された一対のインバータ回路と、

前記一対のインバータ回路の出力端子にドレインがそれぞれ接続され、ゲートに前記クロック信号が供給され、ソースに前記第1の電圧が供給される一対のリセットトランジスタと、

を含むことを特徴とする付記1〜6のうちの何れか一項に記載の比較回路。

(付記8)

前記第2の電圧は前記第1の電圧よりも高い電圧であり、

前記比較部の出力信号がそれぞれ入力され、互いの出力信号が入力される一対のノア回路を含む、ことを特徴とする付記1〜4,6のうちの何れか一項に記載の比較回路。

(付記9)

前記第2の電圧は前記第1の電圧よりも低い電圧であり、

前記比較部の出力信号がそれぞれ入力され、互いの出力信号が入力される一対のナンド回路を含む、ことを特徴とする付記1〜5のうちの何れか一項に記載の比較回路。

(付記10)

アナログ入力信号をサンプルクロックに同期してサンプルホールドし、保持するホールド回路と、

前記ホールド回路から出力される電圧と判定電圧との比較結果に応じた判定信号を出力する付記1〜9のうちの何れか一項に記載の比較回路と、

前記判定信号を逐次変換してデジタル入力信号を生成する逐次変換レジスタ回路と、

前記デジタル入力信号をアナログの前記判定信号に変換するデジタルアナログ変換回路と、

を有するアナログデジタル変換回路。

【符号の説明】

【0128】

11,11a,41 比較部

12,12a,42,61,71 電圧制御部

AVD 高電位電圧

GND グランド(低電位電圧)

C11,C21 キャパシタ

T23,T41 トランジスタ

T11,T31 第1のトランジスタ

T12,T32 第2のトランジスタ

T13,T33 第3のトランジスタ

L11,L21 インダクタ

T62,T72 トランジスタ

CK クロック信号

XCK 反転クロック信号

VP,VN 入力電圧

OP,OM 出力信号

VCM,VCP 制御電圧

VCM1,VCP1 制御電圧

【特許請求の範囲】

【請求項1】

クロック信号に応答してキャパシタの第1端子に第1の電圧と第2の電圧とを交互に供給するインバータ回路と、前記キャパシタの第2端子に第1端子が接続され、ゲートに反転クロック信号が供給され、第2端子に前記第2の電圧が供給されるトランジスタとを含み、前記キャパシタと前記トランジスタとの間のノードに前記第2の電圧と前記キャパシタの蓄積電荷に応じた制御電圧を生成する電圧制御部と、

第1の入力電圧をゲートに受ける第1のトランジスタと、第2の入力電圧をゲートに受ける第2のトランジスタと、前記クロック信号がゲートに供給され、ソースに前記制御電圧が供給され、ドレインが前記第1のトランジスタのソースと前記第2のトランジスタのソースにそれぞれ接続された第3のトランジスタを含み、クロック信号に応答して、前記第1の入力電圧と前記第2の入力電圧との比較結果に応じた出力信号を生成する比較動作と、前記第1の電圧に応じたレベルの前記出力信号を生成するリセット動作とを交互に行う比較部と、

を有する比較回路。

【請求項2】

前記電圧制御部の前記トランジスタのバックゲートは前記制御電圧を生成するノードに接続され、

前記比較部の前記第1〜第3のトランジスタのバックゲートには前記制御電圧が供給される、

ことを特徴とする請求項1記載の比較回路。

【請求項3】

前記電圧制御部の前記トランジスタのバックゲートには前記第1の電圧が供給され、

前記比較部の前記第1〜第3のトランジスタのバックゲートには前記第1の電圧が供給される、

ことを特徴とする請求項1記載の比較回路。

【請求項4】

一端に第2の電圧が供給されるインダクタの他端に対してクロック信号に応答して第1の電圧の供給と停止を行うスイッチ部と、前記インダクタと前記スイッチ部との間のノードに第1端子が接続され、ゲートに前記第2の電圧が供給され、バックゲートと第2端子が互いに接続されたトランジスタを含み、前記トランジスタの第2端子に制御電圧を生成する電圧制御部と、

第1の入力電圧をゲートに受ける第1のトランジスタと、第2の入力電圧をゲートに受ける第2のトランジスタと、前記クロック信号がゲートに供給され、ソースに前記制御電圧が供給され、ドレインが前記第1のトランジスタのソースと前記第2のトランジスタのソースにそれぞれ接続された第3のトランジスタを含み、クロック信号に応答して、前記第1の入力電圧と前記第2の入力電圧との比較結果に応じた出力信号を生成する比較動作と、前記第1の電圧に応じたレベルの前記出力信号を生成するリセット動作とを交互に行う比較部と、

を有する比較回路。

【請求項5】

前記電圧制御部は、前記第2の電圧より低い前記制御電圧を生成するものであり、

前記トランジスタの第2端子に一端が接続され、他端に前記第2の電圧が供給されたキャパシタを含む、ことを特徴とする請求項4記載の比較回路。

【請求項6】

前記電圧制御部は、前記第2の電圧より高い前記制御電圧を生成するものであり、

前記トランジスタの第2端子に一端が接続され、他端に前記第1の電圧が供給されるキャパシタを含む、ことを特徴とする請求項4記載の比較回路。

【請求項7】

アナログ入力信号をサンプルクロックに同期してサンプルホールドし、保持するホールド回路と、

前記ホールド回路から出力される電圧と判定電圧との比較結果に応じた判定信号を出力する請求項1〜6のうちの何れか一項に記載の比較回路と、

前記判定信号を逐次変換してデジタル入力信号を生成する逐次変換レジスタ回路と、

前記デジタル入力信号をアナログの前記判定信号に変換するデジタルアナログ変換回路と、

を有するアナログデジタル変換回路。

【請求項1】

クロック信号に応答してキャパシタの第1端子に第1の電圧と第2の電圧とを交互に供給するインバータ回路と、前記キャパシタの第2端子に第1端子が接続され、ゲートに反転クロック信号が供給され、第2端子に前記第2の電圧が供給されるトランジスタとを含み、前記キャパシタと前記トランジスタとの間のノードに前記第2の電圧と前記キャパシタの蓄積電荷に応じた制御電圧を生成する電圧制御部と、

第1の入力電圧をゲートに受ける第1のトランジスタと、第2の入力電圧をゲートに受ける第2のトランジスタと、前記クロック信号がゲートに供給され、ソースに前記制御電圧が供給され、ドレインが前記第1のトランジスタのソースと前記第2のトランジスタのソースにそれぞれ接続された第3のトランジスタを含み、クロック信号に応答して、前記第1の入力電圧と前記第2の入力電圧との比較結果に応じた出力信号を生成する比較動作と、前記第1の電圧に応じたレベルの前記出力信号を生成するリセット動作とを交互に行う比較部と、

を有する比較回路。

【請求項2】

前記電圧制御部の前記トランジスタのバックゲートは前記制御電圧を生成するノードに接続され、

前記比較部の前記第1〜第3のトランジスタのバックゲートには前記制御電圧が供給される、

ことを特徴とする請求項1記載の比較回路。

【請求項3】

前記電圧制御部の前記トランジスタのバックゲートには前記第1の電圧が供給され、

前記比較部の前記第1〜第3のトランジスタのバックゲートには前記第1の電圧が供給される、

ことを特徴とする請求項1記載の比較回路。

【請求項4】

一端に第2の電圧が供給されるインダクタの他端に対してクロック信号に応答して第1の電圧の供給と停止を行うスイッチ部と、前記インダクタと前記スイッチ部との間のノードに第1端子が接続され、ゲートに前記第2の電圧が供給され、バックゲートと第2端子が互いに接続されたトランジスタを含み、前記トランジスタの第2端子に制御電圧を生成する電圧制御部と、

第1の入力電圧をゲートに受ける第1のトランジスタと、第2の入力電圧をゲートに受ける第2のトランジスタと、前記クロック信号がゲートに供給され、ソースに前記制御電圧が供給され、ドレインが前記第1のトランジスタのソースと前記第2のトランジスタのソースにそれぞれ接続された第3のトランジスタを含み、クロック信号に応答して、前記第1の入力電圧と前記第2の入力電圧との比較結果に応じた出力信号を生成する比較動作と、前記第1の電圧に応じたレベルの前記出力信号を生成するリセット動作とを交互に行う比較部と、

を有する比較回路。

【請求項5】

前記電圧制御部は、前記第2の電圧より低い前記制御電圧を生成するものであり、

前記トランジスタの第2端子に一端が接続され、他端に前記第2の電圧が供給されたキャパシタを含む、ことを特徴とする請求項4記載の比較回路。

【請求項6】

前記電圧制御部は、前記第2の電圧より高い前記制御電圧を生成するものであり、

前記トランジスタの第2端子に一端が接続され、他端に前記第1の電圧が供給されるキャパシタを含む、ことを特徴とする請求項4記載の比較回路。

【請求項7】

アナログ入力信号をサンプルクロックに同期してサンプルホールドし、保持するホールド回路と、

前記ホールド回路から出力される電圧と判定電圧との比較結果に応じた判定信号を出力する請求項1〜6のうちの何れか一項に記載の比較回路と、

前記判定信号を逐次変換してデジタル入力信号を生成する逐次変換レジスタ回路と、

前記デジタル入力信号をアナログの前記判定信号に変換するデジタルアナログ変換回路と、

を有するアナログデジタル変換回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2012−227588(P2012−227588A)

【公開日】平成24年11月15日(2012.11.15)

【国際特許分類】

【出願番号】特願2011−90867(P2011−90867)

【出願日】平成23年4月15日(2011.4.15)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成24年11月15日(2012.11.15)

【国際特許分類】

【出願日】平成23年4月15日(2011.4.15)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]