治具プレート及び該治具プレートを使用した半導体デバイスチップの積層方法

【課題】 半導体デバイスウエーハ上に形成された各半導体デバイスに対応させて複数の半導体デバイスチップを容易に積層可能な治具プレートを提供することである。

【解決手段】 交差する複数の分割予定ラインで区画された各領域に第1半導体デバイスが形成された半導体デバイスウエーハの該各第1半導体デバイス上に、表面に第2半導体デバイスが形成された半導体デバイスチップを積層する際に使用する治具プレートであって、該半導体デバイスウエーハの該分割予定ラインに対応した基準パターンを表面に有していることを特徴とする。

【解決手段】 交差する複数の分割予定ラインで区画された各領域に第1半導体デバイスが形成された半導体デバイスウエーハの該各第1半導体デバイス上に、表面に第2半導体デバイスが形成された半導体デバイスチップを積層する際に使用する治具プレートであって、該半導体デバイスウエーハの該分割予定ラインに対応した基準パターンを表面に有していることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体デバイスウエーハ上に半導体デバイスチップを積層する際に使用する治具プレート及び該治具プレートを使用した半導体デバイスチップの積層方法に関する。

【背景技術】

【0002】

半導体デバイスの製造プロセスにおいては、半導体ウエーハの表面にストリートと呼ばれる分割予定ラインによって区画された各領域にICやLSI等のデバイスが形成される。そして、分割予定ラインに沿って半導体ウエーハをチップに分割することで、個々の半導体デバイスが製造される。このようにして製造された半導体デバイスは各種電気機器に広く利用されている。

【0003】

近年、電気機器の小型化・薄型化に伴い半導体デバイスパッケージも小型化・薄型化が要求され、実装の高密度化が要求されている。複数の半導体デバイスを一つのパッケージに集積する手法の一つに複数の半導体デバイスチップを縦方向に積層して実装する三次元実装がある。

【0004】

従来の三次元実装では、ワイヤボンディングを用いて半導体デバイスチップ間、或いは半導体デバイスチップとインターポーザとを接続していた。ワイヤボンディングによる接続では、その配線長分インダクタンス等が大きくなるので高速での信号のやり取りには向かないという問題があるとともに、ワイヤが半導体デバイスチップ等に触れないようにチップを積層する必要があるため小型化が難しい等の問題がある。

【0005】

近年、新たな三次元実装技術として、ワイヤの代わりにSi貫通電極(Through−Silicon Via:TSV)を用いた実装技術が注目されている。TSV技術を用いると、配線長がワイヤより短いため配線抵抗やインダクタンスが大幅に低減でき、消費電力も大幅に低減できるというメリットがある。

【0006】

一方、半導体デバイスチップの積層方法としては次のような積層技術が開発されつつある。第1の積層方法は、複数の半導体ウエーハ同士を積層し、積層した半導体ウエーハを貫く貫通電極を形成してウエーハ同士を接続する積層方法である(Wafer on Wafer:WOW)。

【0007】

第2の積層方法は、個片化された半導体デバイスチップを半導体ウエーハ上にバンプ等を介してマウントする方法である(Chip on Wafer:COW)。これらの積層方法で積層したウエーハを分割することで、個々の積層デバイスチップが製造される。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2002−261232号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

殆どの半導体ウエーハには、良品デバイスと幾つかの不良デバイスが混在しているため、複数の半導体ウエーハ同士を積層し、積層した半導体ウエーハを貫く貫通電極を形成して半導体ウエーハ同士を接続するWOW技術では歩留まりが悪いという問題がある。

【0010】

一方、COW技術で半導体ウエーハ上に一つずつ半導体デバイスチップを積層して各半導体デバイスチップと半導体ウエーハ上の半導体デバイスとを接続する方法では、時間がかかり生産性が悪いという問題がある。

【0011】

本発明はこのような点に鑑みてなされたものであり、その目的とするところは、半導体デバイスウエーハの各半導体デバイスに対応させて効率良く複数の半導体デバイスチップを積層する際に使用する治具プレート及び該治具プレートを使用した半導体デバイスチップの積層方法を提供することである。

【課題を解決するための手段】

【0012】

請求項1記載の発明によると、交差する複数の分割予定ラインで区画された各領域に第1半導体デバイスが形成された半導体デバイスウエーハの該各第1半導体デバイス上に、表面に第2半導体デバイスが形成された半導体デバイスチップを積層する際に使用する治具プレートであって、該半導体デバイスウエーハの該分割予定ラインに対応した基準パターンを表面に有していることを特徴とする治具プレートが提供される。

【0013】

請求項2記載の発明によると、請求項1記載の治具プレートを使用した半導体デバイスチップの積層方法であって、該治具プレートの該基準パターンを基に、該治具プレート表面に複数の半導体デバイスチップを該半導体デバイスウエーハの該分割予定ラインで区画された各領域に対応させた状態で配設する配設ステップと、該複数の半導体デバイスチップが配設された該治具プレートを反転して、該治具プレートの該半導体デバイスチップと該半導体デバイスウエーハの該第1半導体デバイスとを対面させて貼り合わせる貼り合わせウエーハ形成ステップと、該貼り合わせウエーハから該治具プレートを除去する治具プレート除去ステップと、を具備したことを特徴とする半導体デバイスチップの積層方法が提供される。

【発明の効果】

【0014】

本発明の治具プレートは、半導体デバイスウエーハの分割予定ラインに対して所定の角度及び所定の位置関係を有する基準パターンを有するため、本発明の治具プレートを使用することにより半導体デバイスウエーハの各半導体デバイス上に複数の半導体デバイスチップを容易に配設することができる。

【図面の簡単な説明】

【0015】

【図1】半導体デバイスウエーハの表面側斜視図である。

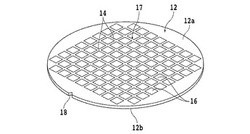

【図2】第1実施形態の治具プレートの表面側斜視図である。

【図3】治具プレート上に基準パターンに基づいて複数の半導体デバイスチップが配設された状態の斜視図である。

【図4】複数の半導体デバイスチップが仮接着された治具プレートを半導体デバイスウエーハに貼り合わせる様子を示す分解斜視図である。

【図5】半導体デバイスウエーハ上に複数の半導体デバイスチップが積層された状態の斜視図である。

【図6】図6(A)は本発明第2実施形態の治具プレートの平面図、図6(B)は第2実施形態の治具プレート上に複数の半導体デバイスチップを配設した状態の平面図である。

【図7】図7(A)は本発明第3実施形態の治具プレートの平面図、図7(B)は第3実施形態の治具プレート上に複数の半導体デバイスチップを配設した状態の平面図である。

【発明を実施するための形態】

【0016】

以下、本発明の実施形態を図面を参照して詳細に説明する。図1を参照すると、シリコンウエーハから形成された半導体デバイスウエーハ2の表面側斜視図が示されている。半導体デバイスウエーハ2の表面2aには、格子状に形成された複数の分割予定ライン(ストリート)4によって区画された各領域にIC、LSI等の半導体デバイス6が形成されている。2bは半導体デバイスウエーハ2の裏面、8はシリコンウエーハの結晶方位を示すマークとしてのノッチである。

【0017】

図2を参照すると、本発明第1実施形態の治具プレート12の表面側斜視図が示されている。好ましくは、治具プレート12はシリコンウエーハから形成され、図1に示した半導体デバイスウエーハ2と同一サイズを有している。

【0018】

治具プレート12の表面12aには半導体デバイスウエーハ2のストリート4に対応して複数のストリート14が格子状に形成されており、ストリート14によって区画された各領域にチップ搭載領域16が形成されている。ストリート14とチップ搭載領域16で基準パターン17を構成する。12bは治具プレート12の裏面、18は半導体デバイスウエーハ2のノッチ8に対応したノッチである。

【0019】

図2に示した治具プレート12はシリコンウエーハから形成されているが、治具プレートはこれに限定されるものではなく、透明な樹脂プレート、ガラスプレート等を採用するようにしてもよい。

【0020】

図3を参照すると、治具プレート12の各チップ搭載領域16上に半導体デバイスチップ20を搭載して仮接着した状態の斜視図が示されている。ここで仮接着とは、後で容易に剥離可能な接着剤で接着された状態をいう。例えば、治具プレート12が透明樹脂から形成されている場合には、紫外線硬化型接着剤で半導体デバイスチップ20を治具プレート12に仮接着する。

【0021】

このように複数の半導体デバイスチップ20を治具プレート12に仮接着した後、図4に示すように、治具プレート12を反転して治具プレート12に仮装着された各半導体デバイスチップ20と半導体デバイスウエーハ2の各半導体デバイス6とを対面させて、治具プレート12を接着剤で半導体デバイスウエーハ2に貼り合わせて貼り合わせウエーハ21を形成する。

【0022】

この時、治具プレート12がシリコンウエーハから形成されている場合には、治具プレート12のノッチ18を半導体デバイスウエーハ2のノッチ8に合わせて、治具プレート12を半導体デバイスウエーハ2に貼り合わせるのが好ましい。

【0023】

或いは、複数のピンを使用する他の位置決め方法を採用するようにしてもよい。治具プレート12を透明プレートから形成した場合には、治具プレート12を透かして半導体デバイスウエーハ2の各半導体デバイス6の形成位置を確認できる。

【0024】

貼り合わせウエーハ21を形成してから、貼り合わせウエーハ21から治具プレート12を剥離すると、図5に示すように、半導体デバイスウエーハ2の各半導体デバイス6上に半導体デバイスチップ20が接着された積層ウエーハ23を得ることができる。

【0025】

治具プレート12として透明樹脂、ガラス等からなる透明プレートを採用し、治具プレート12のチップ搭載領域16上に半導体デバイスチップ20を搭載して紫外線硬化型接着剤で接着した場合には、貼り合わせウエーハ21の透明な治具プレート12側から紫外線を照射して、紫外線硬化型接着剤の接着力を低減してから、治具プレート12を貼り合わせウエーハ21から剥離するようにする。

【0026】

図6(A)を参照すると、本発明第2実施形態の治具プレート22の平面図が示されている。本実施形態の治具プレート22は基準パターンとしての目盛線24がその表面に形成されている。

【0027】

治具プレート22上に複数の半導体デバイスチップ20を搭載するには、例えばチップ搭載ロボットの撮像装置で治具プレート22を撮像し、目盛線24に基づいてチップ搭載ロボットが予め記憶している半導体デバイスウエーハ2の半導体デバイス6に対応する位置に、図6(B)に示すように、半導体デバイスチップ20を搭載して仮接着する。25は半導体デバイスウエーハ2のストリート4に対応する領域である。

【0028】

図7(A)を参照すると、本発明第3実施形態の治具プレート26の平面図が示されている。本実施形態の治具プレート26には、治具プレート26の外周に互いに90度離間した基準パターンとしての4個のアライメントマーク28が形成されている。

【0029】

治具プレート26上に複数の半導体デバイスチップ20を搭載するには、図6に示した第2実施形態と同様に、チップ搭載ロボットの撮像装置で治具プレート26を撮像し、アライメントマーク28に基づいて、予め記憶している半導体デバイスウエーハ2の半導体デバイス6の位置に対応するように、図7(B)に示すように、チップ搭載ロボットが治具プレート26上に複数の半導体デバイスチップ20を搭載し、接着剤で仮接着する。29は半導体デバイスウエーハ2のストリート4に対応する領域である。

【0030】

上述した各実施形態の治具プレート12,22,26は、半導体デバイスウエーハ2の分割予定ライン4に対応して所定の角度及び所定の位置関係を有する基準パターン17,24,28を有するため、半導体デバイスウエーハ2の各半導体デバイス6に対応させて治具プレート上に複数の半導体デバイスチップ20を容易に配設して仮接着することができる。

【符号の説明】

【0031】

2 半導体デバイスウエーハ

4 分割予定ライン(ストリート)

6 半導体デバイス

8 ノッチ

12 治具プレート

16 チップ搭載領域

17 基準パターン

18 ノッチ

20 半導体デバイスチップ

21 貼り合わせウエーハ

22,26 治具プレート

23 積層ウエーハ

24 目盛線

28 アライメントマーク

【技術分野】

【0001】

本発明は、半導体デバイスウエーハ上に半導体デバイスチップを積層する際に使用する治具プレート及び該治具プレートを使用した半導体デバイスチップの積層方法に関する。

【背景技術】

【0002】

半導体デバイスの製造プロセスにおいては、半導体ウエーハの表面にストリートと呼ばれる分割予定ラインによって区画された各領域にICやLSI等のデバイスが形成される。そして、分割予定ラインに沿って半導体ウエーハをチップに分割することで、個々の半導体デバイスが製造される。このようにして製造された半導体デバイスは各種電気機器に広く利用されている。

【0003】

近年、電気機器の小型化・薄型化に伴い半導体デバイスパッケージも小型化・薄型化が要求され、実装の高密度化が要求されている。複数の半導体デバイスを一つのパッケージに集積する手法の一つに複数の半導体デバイスチップを縦方向に積層して実装する三次元実装がある。

【0004】

従来の三次元実装では、ワイヤボンディングを用いて半導体デバイスチップ間、或いは半導体デバイスチップとインターポーザとを接続していた。ワイヤボンディングによる接続では、その配線長分インダクタンス等が大きくなるので高速での信号のやり取りには向かないという問題があるとともに、ワイヤが半導体デバイスチップ等に触れないようにチップを積層する必要があるため小型化が難しい等の問題がある。

【0005】

近年、新たな三次元実装技術として、ワイヤの代わりにSi貫通電極(Through−Silicon Via:TSV)を用いた実装技術が注目されている。TSV技術を用いると、配線長がワイヤより短いため配線抵抗やインダクタンスが大幅に低減でき、消費電力も大幅に低減できるというメリットがある。

【0006】

一方、半導体デバイスチップの積層方法としては次のような積層技術が開発されつつある。第1の積層方法は、複数の半導体ウエーハ同士を積層し、積層した半導体ウエーハを貫く貫通電極を形成してウエーハ同士を接続する積層方法である(Wafer on Wafer:WOW)。

【0007】

第2の積層方法は、個片化された半導体デバイスチップを半導体ウエーハ上にバンプ等を介してマウントする方法である(Chip on Wafer:COW)。これらの積層方法で積層したウエーハを分割することで、個々の積層デバイスチップが製造される。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2002−261232号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

殆どの半導体ウエーハには、良品デバイスと幾つかの不良デバイスが混在しているため、複数の半導体ウエーハ同士を積層し、積層した半導体ウエーハを貫く貫通電極を形成して半導体ウエーハ同士を接続するWOW技術では歩留まりが悪いという問題がある。

【0010】

一方、COW技術で半導体ウエーハ上に一つずつ半導体デバイスチップを積層して各半導体デバイスチップと半導体ウエーハ上の半導体デバイスとを接続する方法では、時間がかかり生産性が悪いという問題がある。

【0011】

本発明はこのような点に鑑みてなされたものであり、その目的とするところは、半導体デバイスウエーハの各半導体デバイスに対応させて効率良く複数の半導体デバイスチップを積層する際に使用する治具プレート及び該治具プレートを使用した半導体デバイスチップの積層方法を提供することである。

【課題を解決するための手段】

【0012】

請求項1記載の発明によると、交差する複数の分割予定ラインで区画された各領域に第1半導体デバイスが形成された半導体デバイスウエーハの該各第1半導体デバイス上に、表面に第2半導体デバイスが形成された半導体デバイスチップを積層する際に使用する治具プレートであって、該半導体デバイスウエーハの該分割予定ラインに対応した基準パターンを表面に有していることを特徴とする治具プレートが提供される。

【0013】

請求項2記載の発明によると、請求項1記載の治具プレートを使用した半導体デバイスチップの積層方法であって、該治具プレートの該基準パターンを基に、該治具プレート表面に複数の半導体デバイスチップを該半導体デバイスウエーハの該分割予定ラインで区画された各領域に対応させた状態で配設する配設ステップと、該複数の半導体デバイスチップが配設された該治具プレートを反転して、該治具プレートの該半導体デバイスチップと該半導体デバイスウエーハの該第1半導体デバイスとを対面させて貼り合わせる貼り合わせウエーハ形成ステップと、該貼り合わせウエーハから該治具プレートを除去する治具プレート除去ステップと、を具備したことを特徴とする半導体デバイスチップの積層方法が提供される。

【発明の効果】

【0014】

本発明の治具プレートは、半導体デバイスウエーハの分割予定ラインに対して所定の角度及び所定の位置関係を有する基準パターンを有するため、本発明の治具プレートを使用することにより半導体デバイスウエーハの各半導体デバイス上に複数の半導体デバイスチップを容易に配設することができる。

【図面の簡単な説明】

【0015】

【図1】半導体デバイスウエーハの表面側斜視図である。

【図2】第1実施形態の治具プレートの表面側斜視図である。

【図3】治具プレート上に基準パターンに基づいて複数の半導体デバイスチップが配設された状態の斜視図である。

【図4】複数の半導体デバイスチップが仮接着された治具プレートを半導体デバイスウエーハに貼り合わせる様子を示す分解斜視図である。

【図5】半導体デバイスウエーハ上に複数の半導体デバイスチップが積層された状態の斜視図である。

【図6】図6(A)は本発明第2実施形態の治具プレートの平面図、図6(B)は第2実施形態の治具プレート上に複数の半導体デバイスチップを配設した状態の平面図である。

【図7】図7(A)は本発明第3実施形態の治具プレートの平面図、図7(B)は第3実施形態の治具プレート上に複数の半導体デバイスチップを配設した状態の平面図である。

【発明を実施するための形態】

【0016】

以下、本発明の実施形態を図面を参照して詳細に説明する。図1を参照すると、シリコンウエーハから形成された半導体デバイスウエーハ2の表面側斜視図が示されている。半導体デバイスウエーハ2の表面2aには、格子状に形成された複数の分割予定ライン(ストリート)4によって区画された各領域にIC、LSI等の半導体デバイス6が形成されている。2bは半導体デバイスウエーハ2の裏面、8はシリコンウエーハの結晶方位を示すマークとしてのノッチである。

【0017】

図2を参照すると、本発明第1実施形態の治具プレート12の表面側斜視図が示されている。好ましくは、治具プレート12はシリコンウエーハから形成され、図1に示した半導体デバイスウエーハ2と同一サイズを有している。

【0018】

治具プレート12の表面12aには半導体デバイスウエーハ2のストリート4に対応して複数のストリート14が格子状に形成されており、ストリート14によって区画された各領域にチップ搭載領域16が形成されている。ストリート14とチップ搭載領域16で基準パターン17を構成する。12bは治具プレート12の裏面、18は半導体デバイスウエーハ2のノッチ8に対応したノッチである。

【0019】

図2に示した治具プレート12はシリコンウエーハから形成されているが、治具プレートはこれに限定されるものではなく、透明な樹脂プレート、ガラスプレート等を採用するようにしてもよい。

【0020】

図3を参照すると、治具プレート12の各チップ搭載領域16上に半導体デバイスチップ20を搭載して仮接着した状態の斜視図が示されている。ここで仮接着とは、後で容易に剥離可能な接着剤で接着された状態をいう。例えば、治具プレート12が透明樹脂から形成されている場合には、紫外線硬化型接着剤で半導体デバイスチップ20を治具プレート12に仮接着する。

【0021】

このように複数の半導体デバイスチップ20を治具プレート12に仮接着した後、図4に示すように、治具プレート12を反転して治具プレート12に仮装着された各半導体デバイスチップ20と半導体デバイスウエーハ2の各半導体デバイス6とを対面させて、治具プレート12を接着剤で半導体デバイスウエーハ2に貼り合わせて貼り合わせウエーハ21を形成する。

【0022】

この時、治具プレート12がシリコンウエーハから形成されている場合には、治具プレート12のノッチ18を半導体デバイスウエーハ2のノッチ8に合わせて、治具プレート12を半導体デバイスウエーハ2に貼り合わせるのが好ましい。

【0023】

或いは、複数のピンを使用する他の位置決め方法を採用するようにしてもよい。治具プレート12を透明プレートから形成した場合には、治具プレート12を透かして半導体デバイスウエーハ2の各半導体デバイス6の形成位置を確認できる。

【0024】

貼り合わせウエーハ21を形成してから、貼り合わせウエーハ21から治具プレート12を剥離すると、図5に示すように、半導体デバイスウエーハ2の各半導体デバイス6上に半導体デバイスチップ20が接着された積層ウエーハ23を得ることができる。

【0025】

治具プレート12として透明樹脂、ガラス等からなる透明プレートを採用し、治具プレート12のチップ搭載領域16上に半導体デバイスチップ20を搭載して紫外線硬化型接着剤で接着した場合には、貼り合わせウエーハ21の透明な治具プレート12側から紫外線を照射して、紫外線硬化型接着剤の接着力を低減してから、治具プレート12を貼り合わせウエーハ21から剥離するようにする。

【0026】

図6(A)を参照すると、本発明第2実施形態の治具プレート22の平面図が示されている。本実施形態の治具プレート22は基準パターンとしての目盛線24がその表面に形成されている。

【0027】

治具プレート22上に複数の半導体デバイスチップ20を搭載するには、例えばチップ搭載ロボットの撮像装置で治具プレート22を撮像し、目盛線24に基づいてチップ搭載ロボットが予め記憶している半導体デバイスウエーハ2の半導体デバイス6に対応する位置に、図6(B)に示すように、半導体デバイスチップ20を搭載して仮接着する。25は半導体デバイスウエーハ2のストリート4に対応する領域である。

【0028】

図7(A)を参照すると、本発明第3実施形態の治具プレート26の平面図が示されている。本実施形態の治具プレート26には、治具プレート26の外周に互いに90度離間した基準パターンとしての4個のアライメントマーク28が形成されている。

【0029】

治具プレート26上に複数の半導体デバイスチップ20を搭載するには、図6に示した第2実施形態と同様に、チップ搭載ロボットの撮像装置で治具プレート26を撮像し、アライメントマーク28に基づいて、予め記憶している半導体デバイスウエーハ2の半導体デバイス6の位置に対応するように、図7(B)に示すように、チップ搭載ロボットが治具プレート26上に複数の半導体デバイスチップ20を搭載し、接着剤で仮接着する。29は半導体デバイスウエーハ2のストリート4に対応する領域である。

【0030】

上述した各実施形態の治具プレート12,22,26は、半導体デバイスウエーハ2の分割予定ライン4に対応して所定の角度及び所定の位置関係を有する基準パターン17,24,28を有するため、半導体デバイスウエーハ2の各半導体デバイス6に対応させて治具プレート上に複数の半導体デバイスチップ20を容易に配設して仮接着することができる。

【符号の説明】

【0031】

2 半導体デバイスウエーハ

4 分割予定ライン(ストリート)

6 半導体デバイス

8 ノッチ

12 治具プレート

16 チップ搭載領域

17 基準パターン

18 ノッチ

20 半導体デバイスチップ

21 貼り合わせウエーハ

22,26 治具プレート

23 積層ウエーハ

24 目盛線

28 アライメントマーク

【特許請求の範囲】

【請求項1】

交差する複数の分割予定ラインで区画された各領域に第1半導体デバイスが形成された半導体デバイスウエーハの該各第1半導体デバイス上に、表面に第2半導体デバイスが形成された半導体デバイスチップを積層する際に使用する治具プレートであって、

該半導体デバイスウエーハの該分割予定ラインに対応した基準パターンを表面に有していることを特徴とする治具プレート。

【請求項2】

請求項1記載の治具プレートを使用した半導体デバイスチップの積層方法であって、

該治具プレートの該基準パターンを基に、該治具プレート表面に複数の半導体デバイスチップを該半導体デバイスウエーハの該分割予定ラインで区画された各領域に対応させた状態で配設する配設ステップと、

該複数の半導体デバイスチップが配設された該治具プレートを反転して、該治具プレートの該半導体デバイスチップと該半導体デバイスウエーハの該第1半導体デバイスとを対面させて貼り合わせる貼り合わせウエーハ形成ステップと、

該貼り合わせウエーハから該治具プレートを除去する治具プレート除去ステップと、

を具備したことを特徴とする半導体デバイスチップの積層方法。

【請求項1】

交差する複数の分割予定ラインで区画された各領域に第1半導体デバイスが形成された半導体デバイスウエーハの該各第1半導体デバイス上に、表面に第2半導体デバイスが形成された半導体デバイスチップを積層する際に使用する治具プレートであって、

該半導体デバイスウエーハの該分割予定ラインに対応した基準パターンを表面に有していることを特徴とする治具プレート。

【請求項2】

請求項1記載の治具プレートを使用した半導体デバイスチップの積層方法であって、

該治具プレートの該基準パターンを基に、該治具プレート表面に複数の半導体デバイスチップを該半導体デバイスウエーハの該分割予定ラインで区画された各領域に対応させた状態で配設する配設ステップと、

該複数の半導体デバイスチップが配設された該治具プレートを反転して、該治具プレートの該半導体デバイスチップと該半導体デバイスウエーハの該第1半導体デバイスとを対面させて貼り合わせる貼り合わせウエーハ形成ステップと、

該貼り合わせウエーハから該治具プレートを除去する治具プレート除去ステップと、

を具備したことを特徴とする半導体デバイスチップの積層方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2012−134233(P2012−134233A)

【公開日】平成24年7月12日(2012.7.12)

【国際特許分類】

【出願番号】特願2010−283283(P2010−283283)

【出願日】平成22年12月20日(2010.12.20)

【出願人】(000134051)株式会社ディスコ (2,397)

【Fターム(参考)】

【公開日】平成24年7月12日(2012.7.12)

【国際特許分類】

【出願日】平成22年12月20日(2010.12.20)

【出願人】(000134051)株式会社ディスコ (2,397)

【Fターム(参考)】

[ Back to top ]