波形制御装置,応答素子モジュール,光スイッチ装置,応答素子および光スイッチ装置の制御方法

【課題】簡易な波形調整によって最適な矩形形状を有するパルスを生成する。

【解決手段】供給される駆動信号に応答素子が応答して得られる出力パルスの波形をモニタするモニタ部3と、モニタ部3でのモニタ結果に基づいて、前記駆動信号の波形を可変する駆動波形可変部4,5と、をそなえた波形制御装置により波形を整形する。

【解決手段】供給される駆動信号に応答素子が応答して得られる出力パルスの波形をモニタするモニタ部3と、モニタ部3でのモニタ結果に基づいて、前記駆動信号の波形を可変する駆動波形可変部4,5と、をそなえた波形制御装置により波形を整形する。

【発明の詳細な説明】

【技術分野】

【0001】

本案件は、波形制御装置,応答素子モジュール,光スイッチ装置,応答素子および光スイッチ装置の制御方法に関する。

【背景技術】

【0002】

光信号処理システムや光通信システムに適用される素子等においては、矩形波形状を有する光パルスを、取り扱われる光波形の理想とするものは少なくない。

たとえば、光半導体増幅器(Semiconductor Optical Amplifier:SOA)のような光素子は、時間軸上においてオンオフが切り替わる電気信号(駆動信号)によって駆動されて、入力光の導通/遮断を切り換えるゲートスイッチとして適用される。駆動信号の導通/遮断の切り換わりによって、SOAからの出力光は時間軸上でオンオフが切り替わる光パルスとなる。SOAから出力される光パルスとしては、真正の(理想的な)矩形波形状に近いことがしばしば求められる。

【0003】

2値のディジタル電気信号を扱う電子機器においても、導通する信号が2値の矩形波信号であることを理想とする内部素子や配線等を含むものがある。例えば、メモリやバッファ、変調機、高速入出力インタフェース機器などの伝送線路機器などがある。このような電子機器においても、信号波形について最適な矩形形状を有するよう簡易に整形できるようにすることがしばしば求められている。

【特許文献1】特開平9−36471号公報

【特許文献2】特開2000−341728号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

そこで、本件は、簡易な波形整形によって目標の矩形度を有するパルスを生成することを目的の一つとするものである。

なお、前記目的に限らず、後述する発明を実施するための最良の形態にかかる各構成又は作用により導かれる効果であって、従来の技術によっては得られない効果を奏することも本案件の他の目的として位置づけることができる。

【課題を解決するための手段】

【0005】

たとえば、以下の手段を用いる。

供給される駆動信号に応答素子が応答して得られる出力パルスの波形をモニタするモニタ部と、該モニタ部でのモニタ結果に基づいて、前記駆動信号の波形を整形する駆動波形整形部と、をそなえた波形制御装置を用いることができる。

【発明の効果】

【0006】

開示の技術によれば、簡易な構成によって目標の矩形度を有するパルスを生成することができる。

【発明を実施するための最良の形態】

【0007】

以下、図面を参照して実施の形態を説明する。但し、以下に説明する実施形態は、あくまでも例示であり、以下に明示しない種々の変形や技術の適用を排除する意図は無い。即ち、本実施形態は、その趣旨に逸脱しない範囲において種々変形して実施することができる。

〔A〕第1実施形態

現在、波長多重(Wavelength Division Multiplexing:WDM)伝送システムが幹線系光通信ネットワークシステムの主流である。しかしながら、今後は、ネットワーク利用効率の向上の観点から、光信号のまま経路を切り替える光パケット・バーストスイッチングネットワークシステムへの進展が期待されている。

【0008】

光パケット・バーストスイッチングネットワークシステムにおいては、回線使用効率を向上させるために、光信号をパケットに分割し、そのパケット単位で光信号のまま交換・方路切り替えの処理を行なう機能が必要となることが見込まれている。

このような機能を担う装置においては、上述のパケット単位での交換や方路切り替えを行なうにあたって、少なくともミリ秒次元よりも小さい時間次元、例えばマイクロ秒〜ナノ秒次元での切り替え処理を行なうことができるようにすることが期待されている。

【0009】

一例として、光半導体増幅器(Semiconductor Optical Amplifier:SOA)のような素子をゲートスイッチとして利用し、それをマトリクス状に複数配置する分配・合流型の光パケットスイッチシステムがある。分配・合流型の光パケットスイッチシステムでは、ポート数Nに対し、N×N以上のスイッチング素子が必要となる。

図1に、8個の入力ポート(♯1〜♯8)および8個の出力ポート(♯1〜♯8)を有する分配・合流ゲートスイッチ型の光パケットスイッチ(光スイッチ装置、インターコネクトシステム)100の例を示す。8ポートから入力される光パケット信号は、入力ポートごとにそなえられた1:8カプラ101でそれぞれ8分配される。8:8光ゲートスイッチ部102は出力先の出力ポートごとにそなえられる。

【0010】

一つの光ゲートスイッチ部102は、8個の入力ポート♯1〜♯8に対応した1:8カプラ101からの分配経路を1本ずつ接続して、それぞれの分配経路ごとに、光ゲートスイッチ102aがそなえられる。光ゲートスイッチ102aは、駆動回路105からの駆動信号に基づいて、入力される光パケット信号についての通過/遮断が制御されるもので、例えばSOAを用いることができるが、電界吸収型光変調器などの他の光素子を用いることもできる。なお、光パケットスイッチ(インターコネクトシステム)100は筐体に収容されてもよい。

【0011】

駆動回路105は、光ゲートスイッチ102aごとにそなえられて、トリガ信号出力部106から入力されるトリガ信号に応じた駆動信号を光ゲートスイッチ102aに供給する。尚、図1中においては、出力ポート♯8に対応する光ゲートスイッチ部102における光ゲートスイッチ102aに対応した駆動回路105に着目して図示している。

トリガ信号出力部106は、各光ゲートスイッチ102aに対する導通/遮断の制御タイミングに応じたトリガ信号を対応する駆動回路105に供給する。又、トリガ信号出力部106から出力される各駆動回路105へのトリガ信号の出力タイミングは同期手段107によって制御することができる。

【0012】

同期部107は、光パケット信号を導通させる制御を行なう対象となる光ゲートスイッチ102aにその光パケット信号が入力されるタイミングおよび通過するタイミングと、当該光ゲートスイッチ102aの導通/遮断の制御を同期させる。例えば、トリガ信号出力部106から出力される光ゲートスイッチ102aの導通/遮断制御のためのトリガ信号が、光パケット信号の入力および通過のタイミングにほぼ同期するように、トリガ信号出力部106を制御する。

【0013】

なお、同期部107は、例えば、光パケットスイッチ100が搭載される箇所に応じた態様でトリガ信号出力部106を制御することができる。

たとえば、ネットワークの中継箇所に適用される場合には、入出力ポート♯1〜♯8にはそれぞれ光伝送路が接続される。そして、各入力ポート♯1〜♯8への光パケット信号の入力を1:8カプラ101よりも上流側箇所で検出する。そして、入力を検出した光パケット信号が導かれるべき出力ポート♯1〜♯8に応じて定められる光ゲートスイッチ102aが、当該光パケット信号が該当の光ゲートスイッチ102aに到達する以前に導通状態となるようにトリガ信号の出力を制御する。又、当該光パケット信号が通過した後は遮断されるようにトリガ信号の出力を制御する。

【0014】

または、光パケット信号を送信する送信器箇所に適用される場合には、各入力ポート♯1〜8には、光パケット信号を生成する光パケット信号源等が接続される。この場合には、該当の光パケット信号源で光パケット信号を生成するためのデータ信号の供給タイミングに関する情報を受け取り、導出先とすべき光ゲートスイッチ102aに対するトリガ信号が当該パケット信号の入力タイミングにほぼ同期させる制御を行なう。

【0015】

なお、光パケットスイッチ100が搭載される箇所がいずれとなる場合においても、光パケット信号の入力を検出する箇所、または光パケット信号が生成される光パケット信号源の搭載箇所から、1:8光カプラ101に至る光経路上に適宜遅延手段を介装できる。これにより、光ゲートスイッチ102aの制御が、当該光ゲートスイッチ102aへの光パケット信号の入力以前に完了させられるようにすることができる。

【0016】

これにより、光ゲートスイッチ102aは、光パケット信号が通過する期間のみオンにし、それ以外はオフにして、クロストークや雑音光の漏出を防ぐ。経路のスイッチングは、例えばスイッチング前の経路に対応する光ゲートスイッチ102aをオフ(遮断制御)するとともに、スイッチング後の経路に対応する光ゲートスイッチ102aをオンすることで行なうことができる。

【0017】

このように、所望の入出力ポート間の光ゲートスイッチ102aおよび対応の下流側SOA104をオン(通過制御)すると、当該入出力ポート間において光パケット信号の経路を設定できる。例えば、入力ポート♯iと出力ポート♯jとの間で光パケット信号を設定する場合には、図中i−jのゲート出力を有するSOA102aとともに、当該SOA102aの下流側のSOA104を通過(オン)する制御を行なう。

【0018】

すなわち、オンとされた光ゲートスイッチ102aを通過した光パケット信号は出力ポートごとに8:1カプラ103で合波され、出力される。尚、SOA104は、8:1カプラ103での光損失を補うために、例えば8:1カプラ103の出力にそなえられたものであるが、適宜省略してもよい。

図1においては、出力ポート毎に損失補償用のSOA104を具備しているため、同一経路上にそなえられる2個のSOA102a,104をほぼ同時または同時にオン又はオフさせる。このとき、オンオフの切り換えに要する時間が短いほど粒度の細かい(パケット長の短い)光パケット信号を処理することが可能となる。更に、オンからオフへの、又はオフからオンへの切り換えが速いほど、光パケット信号間の空き時間(ガードタイム)を短くすることが可能となる。

【0019】

このように、図1に示す光パケットスイッチ100においては、8×8+8=72個のSOA102a,104が用いられている。即ち、ポート数N(=8)とした場合のN×Nよりも多数のスイッチング素子であるSOA102a,104が適用されている。

分配・合流型の光パケットスイッチ100のように、ナノ秒オーダのスイッチングが必要な場合、光ゲートスイッチングを担う複数のSOA102a,104に対して駆動信号を供給するための配線長さがミリ単位で相違すると、スイッチング時間を遅くする等、応答特性に影響を与える。

【0020】

すなわち、SOA102a,104自身が持つキャパシタンス成分(寄生容量)や抵抗成分、駆動回路とSOAとの間の配線のインダクタンスL成分等によって決定される時定数の影響によって、SOA102a,104のスイッチング応答が遅くなることがある。具体的には、SOAに対する光導通/遮断のための駆動波形を理想的な矩形波で入力した場合でも、応答信号である出力光の波形は鈍ってしまい、スイッチング応答が遅くなることがある。

【0021】

各々のSOA102a,104に対し駆動信号を出力する駆動回路が対応するSOA102a,104の直近に配置され、その配線長は互いに等距離となるよう配置することで、SOA102a,104ごとの応答特性を画一的に改善することが期待できる。しかし、図1に例示した場合のように、SOA102a,104とそれらの駆動回路とが数多く存在する場合、各々の配線長を均一な距離に保つことは容易ではない。このため、SOA102a,104ごとの応答特性は、各々の配線長が相違し、寄生容量に個体差を有するため、それぞれ実質的に相違しているといえる。

【0022】

プリエンファシス等の技術は、回路部やCR回路等を用いて、駆動信号における立ち上がりを持ち上げる(立ち上がり応答の高速化)ことで、応答信号の矩形波の立ち上がりの鈍りを鋭くするための技術として知られている。このようなプリエンファシス技術を用いて、上述のSOA102a,104の応答特性を速めることも想定できるが、SOA102a,104の特性を改善させるためには、与えるべきプリエンファシスの量について、それぞれ個別の調整が必要になる。例示した光パケットスイッチ100においては、72個ものスイッチ素子であるSOA102a,104に対して個別調整が必要になる。

【0023】

プリエンファシスの量を調整するには、駆動波形の矩形波エッジを立ち上げる機能を有する回路をなす素子特性について調整する必要がある。又、個別に駆動波形の調整を行なったとしても、スイッチ素子であるSOAの特性が経年変化したり、駆動回路基板の吸湿等によって特性変化を起こしたりすることなども想定すると、その後の調整作業は不可欠になる。メインテナンスや製造プロセスの効率化のためにもこのような個別調整の負担はなるべく軽減させることが望ましい。

【0024】

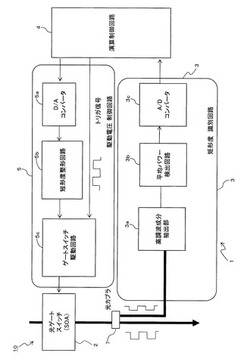

そこで、第1実施形態においては、図2に示す波形制御装置1および応答素子モジュール10を提案する。波形制御装置1においては、応答素子であるSOA2の駆動信号に対する応答出力をなす光パルスの矩形度をモニタし、モニタ結果の矩形度に応じて駆動信号の駆動波形を制御して、光パルスの矩形度を自在に制御する。

すなわち、図2に示す波形制御装置1を上述の図1に示す各々のSOA102a,104の駆動のために適用することで、各々のSOA102a,104の応答出力をなす光パルスの矩形度が目標形状を有するように整形できる。

【0025】

なお、SOA2を図1に示す光パケットスイッチ100の要素(符号102a,104)として適用する場合には、矩形度の制御のためにはSOA2から出力される光パルスの周期が波形制御装置1において既知であることが必要である。このため、光パケットスイッチ100の運用開始前(即ちSOA2への入力光が非入力の状態)において、波形制御装置1による光パルスの矩形度についての整形を行なうことができる。

【0026】

また、応答素子モジュール10は、上述の波形制御装置1および応答素子としての少なくとも1つのSOA2を含む。図2に示す波形制御装置1は、実施形態の一例(以降、一例と呼ぶ。)として矩形度識別回路3と、演算制御回路4と、駆動電圧制御回路5と、をそなえる。演算制御回路4は、上述の図1に示すトリガ信号出力部106の一例となる。即ち、運用にあるSOA2(図1の102a,104参照)に入力光である光パケットが入力されるタイミングに同期して、当該SOA2に入力光を導通させるトリガ信号を、以下のような矩形度の整形が行なわれた駆動電圧制御回路5を介して供給することができる。

【0027】

波形制御装置1においては、出力光パルスの矩形度の整形を行なう場合、非運用時のSOA2について、SOA2を一定周期のトリガ信号で駆動することにより得られる自然放出光(ASE光)を用いる。即ち、入力光が入力されていないSOA2に、演算制御回路4で生成される一定のオンオフ周期の駆動信号が駆動電圧制御回路5を介して供給されると、このSOA2から応答出力として自然放出光(ASE光)を出力する。

【0028】

このとき、ASE光は、駆動信号のオンオフに応じた光パルスの強度変動を有する。即ち、駆動信号をオンさせるとASE光が出力されるので光パルスのオンに該当する一方、駆動信号をオフさせるとASE光の出力光レベルが0となるので光パルスのオフに該当する。

矩形度識別回路3は、後述の駆動電圧制御回路5から供給される駆動信号に応答素子であるSOA2が応答して得られる出力パルスの波形をモニタするモニタ部の一例である。矩形度識別回路3は、SOA2からの出力光パルスの波形の矩形度を、例えば、出力光パルスの波形が真正の(理想的な)矩形形状となっている度合いを数値化することにより識別する。矩形度識別回路3は、一例として、高調波成分抽出部3a,平均パワー検出回路3bおよびアナログ/ディジタル(A/D)コンバータ3cをそなえる。

【0029】

高調波成分抽出部3aは、SOA2からの出力パルス(出力光パルス)に含まれる、駆動信号をなすトリガパルスの周波数(既知)についての偶数次又は奇数次の高調波成分を抽出する。高周波成分抽出部3aをトリガパルスの偶数次の高調波成分を抽出するものとする場合は、一例として、図3(a)に示すように、分岐部11,遅延部12,受光部13,14および合成部15をそなえる。

【0030】

分岐部11は、例えば3dBカプラ等が適用され、SOA2から出力される出力光パルスの一部を、光カプラ等を含む光分岐部7を通じて受けて、受けた出力光パルスについて2分岐する。そして、分岐部11で分岐された一方は受光部13に接続される一方、他方は遅延部12を介して受光部14に接続される。

遅延部12は、例えば分岐部11と受光部14との間に介装される遅延線(光ファイバ)が適用され、受光部14に入力される光に、分岐部11から受光部13に入力される光よりも所定時間だけ遅延させる。この遅延時間としては、例えばSOA2からの出力パルスのパルス周期(又は駆動電圧制御回路5からSOA2に出力される駆動信号をなすパルス信号の周期)の半周期相当の時間である。

【0031】

受光部13,14はともに入力される光について電気信号に変換(光電変換)するもので、例えばフォトダイオード(PD)が適用される。即ち、受光部13,14から出力される電気信号は、SOA2から出力される出力光パルスに相当する振幅変化を有する電気パルス信号である。但し、遅延部12で遅延された光を受光する受光部14からの電気パルス信号は、受光部13からの電気パルス信号に対してそのパルス周期の半周期時間が遅延されている。

【0032】

合成部15は、上述の受光部13,14から出力される電気パルス信号を合成、即ち重ねあわせる。合成部15において、パルス周期の半周期時間分の相対的な遅延時間差を有する電気パルス信号を重ね合わせることで、パルス周期に半波長ずれた奇数次高調波成分については互いにキャンセルされる。その結果、合成部15での合成後の信号には偶数次高調波成分のみが残存することになる。これにより、高調波成分抽出部3aとして、偶数次の高調波成分を出力することができる。

【0033】

ところで、式(1)は、非正弦波交流の時間tでの瞬時値v(t)のフーリエ級数式の一例である。そして、理想的な矩形波v(t)は、一例として、式(1)から式(2)のフーリエ級数展開式のように導出することができる。ここで、式(1),(2)において、Vは振幅、ωは角速度であり、周期をTとすると、ω=2π/Tである。尚、式(2)に示す矩形波v(t)は、−T/4<t<T/4においてv(t)=Vであり、−T/2<t<−T/4,T/4<t<T/2においてv(t)=−Vである。

【0034】

【数1】

【0035】

理想的な矩形波は、パルス信号をなすパルス周期の奇数次の高調波成分の重ね合わせを含む。即ち、この式(2)に示すωtの成分は1次波であり、3ωt,5ωt,7ωtの成分はそれぞれ3,5,7次高調波である。この式(2)に示すように、理想的な矩形波においては、式(1)における偶数次高調波成分(n=2,4,…の成分)は、0になる。

【0036】

したがって、上述の高調波成分抽出部3aにおいて抽出される、偶数次の高調波成分(例えば、式(1)におけるフーリエ級数展開式での2ωt,4ωtの成分)は、パルス信号波形を理想的な矩形波形状から実質的に変形させる要素であるといえる。

図4は、光分岐部7から矩形度識別回路3に入力されるパルス信号に含まれるスペクトラム特性(A)の一例とともに、上述の高調波成分抽出部3aとしての透過特性(B)の一例を示す図である。この図4に例示するように、矩形度識別回路3に入力されるパルス信号には、上述の式(1)で例示されるような奇数次高調波成分A1,A3,A5,…とともに、理想的な矩形波形状を変形させる成分である偶数次高調波成分A2,A4,A6,…が含まれる。尚、図4中、「A」に付される数字は、高調波成分の次数を示す。又、図4中、横軸は周波数であり、縦軸は振幅(瞬時値電圧)を表す。

【0037】

高調波成分抽出部3aは、例えば、図4中、網掛け部Bで示すような透過周波数帯を有する。換言すれば、透過周波数帯(B)と遮断周波数帯とが交互に配列されるコムフィルタ(comb filter)としての特性を有することができる。これにより、上述の偶数次の高調波成分A2,A4,A6,…を透過させる一方、奇数次の高調波成分A1,A3,A5,…については遮断させることができる。

【0038】

図5(a)〜図5(d)は、例えば式(1)における偶数次高調波成分の係数を変化させることで、パルス周期の奇数次高調波成分に対し偶数次高調波成分が含まれる割合を変化させた場合のパルス信号波形のシミュレーション結果の一例である。

ここで、図5(c)は、1〜199次までの高調波成分のうちの、偶数次高調波成分を除く奇数次高調波成分を重ね合わせた場合のシミュレーション結果の一例である。また、図5(a)は、1〜199次までの高調波成分のうちの奇数次高調波成分の重ね合わせと、第1割合の偶数次高調波成分と、を同位相で重ね合わせた場合のシミュレーション結果の一例である。又、図5(b)は奇数次高調波成分の重ね合わせに、第1割合よりも少ない第2割合の偶数次高調波成分を同位相で重ね合わせた場合のシミュレーション結果の一例である。

【0039】

これに対し、図5(d)は、上述の第1割合の偶数次高調波成分を、奇数次高調波成分とは逆位相で、奇数次高調波成分とともに重ね合わせた場合のシミュレーション結果の一例である。又、図5(e)は上述の第2割合の偶数次高調波成分を、奇数次高調波成分とは逆位相で、奇数次高調波成分とともに重ね合わせた場合のシミュレーション結果の一例である。

【0040】

すなわち、パルス信号をなすパルス周期の奇数次の高調波成分の重ね合わせの場合には、図5(c)のシミュレーション結果に示すように、ほぼ理想的な矩形波の形状になる。一方、図5(a),図5(b),図5(d),図5(e)に示すように、偶数次の高調波成分が含まれる割合が増えるに従って、パルス信号波形が理想的な矩形波形状から変形する度合いが大きくなる。

【0041】

矩形度識別回路3の要素である平均パワー検出回路3bは、高調波成分抽出部3aにて抽出された偶数次又は奇数次の高調波成分のパワーをモニタするパワーモニタ部の一例である。第1実施形態における平均パワー検出回路3bにおいては、高調波成分抽出部3aにおいて抽出した偶数次高調波成分のパワー(平均パワー)を検出する。A/Dコンバータ3cにおいては、平均パワー検出回路3bにて検出された平均パワーの値についてアナログ信号からディジタル信号に変換して、演算制御回路4に出力する。

【0042】

これにより、矩形度識別回路3においては、出力光パルスにおける理想的な矩形波形状から変形される要素である偶数次の高調波成分の大きさを、モニタ結果として出力している。この場合には、出力光パルスに含まれる偶数次の高調波成分のパワーが最小となっている場合には、出力光パルスの波形として、ほぼ理想的な矩形波形状を得ることができる。

【0043】

なお、前述の図3(a)においては、分岐部11での光分岐の後段において分岐光をそれぞれ光電変換する受光部13,14がそなえられている。他の例としては、例えば図3(b)に示すように、分岐部11としての機能の前段に受光部19をそなえるようにしてもよい。この場合においては、分岐部11′としては受光部19からの電気パルス信号について2分岐し、遅延部12′においては、分岐部11′からの電気パルス信号について上述の場合と同等の遅延時間差を与える。これにより、合成部15において、図3(a)の場合と同様の偶数次の高調波成分を出力することができる。

【0044】

また、図3(a),図3(b)のごとき遅延時間差を有するパルス信号を合成部15で重ね合わせる場合において、入力される各パルス信号のレベルを整合させるべく合成部15の入力側にアンプ等を適宜介装するようにしてもよい。

さらに、高調波成分抽出部3aとしては、奇数次高調波成分を抽出し、矩形度識別回路3においてはそのパワー情報(ディジタル信号)をモニタ結果として出力するようにしてもよい。この場合には、高調波成分抽出部3aは、前述の図4に示す奇数次高調波成分A1,A3,A5,…を通過させる一方、偶数次の高調波成分A2,A4,…については遮断するコムフィルタとしての特性を有する。奇数次高調波成分は、出力パルスにおける理想的な矩形度形状を形成する要素である。従って、平均パワー検出回路3bにおいて検出する奇数次高調波成分のパワーが最大となれば、出力光パルスの波形として、ほぼ理想的な矩形波形状を得ることができる。

【0045】

図3(c)は、トリガパルスの奇数次の高調波成分を抽出する高調波成分抽出部3aの一例である。この図3(c)に示す高調波成分抽出部3aは、分岐部11,遅延部12,受光部13,14,合成部15,受光部16,位相調整回路17および減算部18をそなえる。

分岐部11は、前述の図3(a)に示すものと異なり、光分岐部7を通じて受けた出力光パルスについてパワーを等分に3分岐し、それぞれ、3つの受光部13,14,16に導く。遅延部12,受光部13,14および合成部15は、前述の図3(a)に示すものと基本的に同様である。即ち、合成部15からは、出力光パルスの偶数次の高調波成分を出力することができる。

【0046】

また、受光部16は、入力される光、即ち、分岐部11で3等分されたうちの一の出力光パルスについて電気信号に変換(光電変換)し、減算部18に出力する。位相調整回路17は、合成部15からの偶数次の高調波成分の信号について位相調整を行ない、減算部18に入力される受光部16からの電気パルス信号に含まれる偶数次の高調波成分と位相を整合させる。

【0047】

さらに、減算部18は、受光部16からの電気パルス信号から、合成部15からの偶数次の高調波成分を減算し、減算した残りの成分である奇数次高調波成分を抽出する。これにより、図3(c)に示す高調波成分抽出部3aは、トリガパルスの奇数次の高調波成分を抽出することができる。

なお、上述の図3(c)に示す分岐部11において3分岐されるものにおいては、4分岐される分岐素子における3本の分岐方路を適用することとしてもよい。又、受光部13,14および16から出力される電気信号の振幅を調整するアンプや減衰器を適宜用いることで、受光部13,14,16から出力される各電気信号の振幅を整合させることもできる。

【0048】

また、演算制御回路4および駆動電圧制御回路5は、互いに協働することで、モニタ部3でのモニタ結果に基づいて、駆動信号の波形を整形する駆動波形整形部の一例に相当する。即ち、駆動波形整形部4,5として、矩形度識別回路3でモニタされたパワーが所定レベル又は所定範囲となるように駆動パルス信号の波形を整形している。

たとえば、平均パワー検出回路3bで 偶数次の高調波成分のパワーをモニタ結果として出力している場合には、モニタされたパワーが最小となることを制御目標に置いて駆動パルス信号の波形を整形する。又、平均パワー検出回路3bで奇数次の高調波成分のパワーをモニタ結果として出力している場合には、モニタされたパワーが最大となることを制御目標に置いて駆動パルス信号の波形を整形する。

【0049】

ここで、演算制御回路4は、例えばディジタル演算素子からなり、駆動電圧制御回路5の要素であるゲートスイッチ駆動回路5cに対し、ゲートオンオフのためのトリガ信号を供給する。又、演算制御回路4は、矩形度識別回路3からディジタル信号として入力されたモニタ結果をもとに、SOA2での光パルスの波形を制御するための制御信号をディジタル信号として出力する。

【0050】

駆動電圧制御回路5は、演算制御回路4からのゲートオンオフのためのパルス信号に基づいて駆動パルス信号を生成し、SOA2に供給する。このとき、駆動電圧制御回路5においては、SOA2で出力する光パルス波形を制御するための制御信号をもとに、出力する駆動パルス信号の波形を整形している。駆動電圧制御回路5は、一例として、図2に示すD/Aコンバータ5a,矩形度整形回路5bおよびゲートスイッチ駆動回路5cをそなえる。

【0051】

D/Aコンバータ5aは、演算制御回路4からディジタル信号として入力される制御信号をアナログ信号に変換する。矩形度整形回路5bは、D/Aコンバータ5aからの制御信号をもとに、ゲートスイッチ駆動回路5cの要素である可変容量素子16a(図6参照)への制御信号を生成する。

ゲートスイッチ駆動回路5cは、演算制御回路4からのゲートオンオフのためのトリガ信号に基づいて駆動パルス信号(駆動信号)を生成するが、ここで生成する駆動パルス信号の波形については矩形度整形回路5bからの制御信号をもとに整形されている。換言すれば、ゲートスイッチ駆動回路5cは、応答素子であるSOA2への駆動信号の波形を制御信号に基づき整形する駆動回路部の一例であり、又、演算制御回路4は、モニタ部3でのモニタ結果に基づき(矩形度整形回路5bを介して)制御信号を駆動回路部5cに出力する制御部の一例である。

【0052】

図6はゲートスイッチ駆動回路5cの一例である。図6に示すスイッチ駆動回路5cにおいては、可変容量素子16aおよび抵抗16b,16cを含む回路部16と、ドライバアンプ(Driver AMP)17とをそなえる。ここでは、演算制御回路4からのトリガ信号は、回路部16を介してドライバアンプ17で増幅され、駆動パルス信号としてSOA2へ出力される。

【0053】

回路部16をなす可変容量素子16aは、矩形度整形回路5bからの制御信号の値により容量が可変される素子である。バリキャップは可変容量素子16aの一例である。この場合、演算制御回路4からの制御信号に応じて、バリキャップ16aへの制御信号として印加すべき電圧(バリキャップ電圧)を可変するバリキャップ電圧制御回路は、矩形度整形回路5bの一例である。

【0054】

矩形度整形回路5bからの制御信号を通じて、可変容量素子16aの容量が可変されると、回路部16の応答時定数が可変するので、ゲートスイッチ駆動回路5cからの駆動パルス信号の立ち上がりおよび立ち下がりの波形が整形される。可変容量素子16aの容量C12、抵抗16b,16cの抵抗値をそれぞれ固定値R21,R23とすると、回路部16の応答時定数τ1は式(3)のようになる。従って、容量C12を大きくすると、応答時定数τ1は大きくなり、容量C12を小さくすると、応答時定数τ1は小さくなる。

【0055】

【数2】

【0056】

バリキャップとしての可変容量素子16aにおいては、例えば、矩形度整形回路5bからの制御電圧信号が小さくなると容量C12が大きくなり、矩形度整形回路5bからの制御電圧信号が大きくなると容量C12が小さくなる関係とすることができる。これにより、ゲートスイッチ駆動回路5cをなす回路部16の応答時定数は、演算制御回路4からの制御信号により生成される制御電圧信号を通じて、可変させることができる。換言すれば、演算制御回路4は、可変容量素子16aの容量を制御することを通じて、回路部16の応答時定数を制御し、これにより、ゲートスイッチ駆動回路5cから出力される駆動パルス信号の波形を制御することができる。

【0057】

図7(a)〜図7(c)は可変容量素子16aの容量の大きさ(又は制御電圧信号(印加電圧)の大きさ)に応じた、駆動パルス信号および光パルスの立ち上がり波形の一例を示す図である。図7の(a)は、制御電圧信号の値を比較的小さくして容量C12を比較的大きくした場合であり、図7の(c)は、制御電圧信号を比較的大きくして容量C12を比較的小さくした場合であり、図7の(b)は、制御電圧信号および容量C12を上述の図7(b)および図7(c)のときの間の値とした場合である。

【0058】

すなわち、図7(a)に示すように、容量C12を大きくすると応答時定数が大きくなる。このため、ゲートスイッチ駆動回路5cからの駆動パルス信号A1は、鋭く立ち上がるとともに、その過渡的な立ち上がり幅W1は大きくなり、且つ一定値に落ち着くまでの時間も比較的長くなる。更に、SOA2は、このように立ち上がり幅が大きくなった駆動パルス信号A1により駆動されるので、出力される光パルスA2の立ち上がり幅も大きくなる。

【0059】

これに対し、図7(c)に示すように、容量C12を小さくすると応答時定数が小さくなる。このため、ゲートスイッチ駆動回路5cからの駆動パルス信号C1は、鈍く立ち上がるとともに、その過渡的な立ち上がり幅W3は小さくなり、且つ一定値に落ち着くまでの時間は比較的短くなる。更に、SOA2は、このように立ち上がりが鈍くなった駆動パルス信号C1により駆動されるので、出力される光パルスC2の立ち上がりも緩くなる。

【0060】

図7(b)は、制御電圧信号および容量C12を上述の図7(a)および図7(c)のときの間の値としている。この場合には、駆動パルス信号B1の立ち上がり特性は、上述のA1,C1の立ち上がり特性の間の鋭さを有し、その過渡的な立ち上がり幅W2はW1,W3の間の値となり、一定値に落ち着くまでの時間も図7(a)および図7(c)のときの間の値となる。尚、この駆動パルス信号B1により駆動されるSOA2からの光パルスは、真正の(理想的な)矩形波形状に近い立ち上がりが得られている。

【0061】

演算制御回路4においては、矩形度識別回路3からの光パルス波形のモニタ結果に基づいて、SOA2から出力される光パルス波形を、矩形度整形回路5bおよびゲートスイッチ駆動回路5cを通じたフィードバック制御により制御している。図8(a)〜図8(c)は、上述の可変容量素子16aへの制御電圧信号(又はそのときの容量C12)の値に応じた、高調波成分抽出部3aで抽出される偶数次高調波成分の信号波形、および、SOA2から出力される光パルスの波形の例である。

【0062】

図8(a)に例示するように、光パルスa1が急峻に立ち上がる場合には、高調波成分抽出部3aで抽出する偶数次高調波成分の信号b1についても比較的大きな振幅となる箇所を含む。又、図8(c)に例示するように、光パルスa3の立ち上がりが鈍っている場合にも、高調波成分抽出部3aで抽出する偶数次高調波成分の信号b3についても比較的大きな振幅となる箇所を含む。このため、図8(a),図8(c)の場合の双方とも、パワー検出回路3bで検出する偶数次高調波成分パワーは比較的大きくなる。

【0063】

これに対し、図8(b)に例示するように、光パルスa2が真正の(理想的な)矩形波形状に近い波形を有している場合には、高調波成分抽出部3aで抽出する偶数次高調波成分b2は、比較的振幅が小さくなる。この場合にパワー検出回路3bで検出する偶数次高調波成分のパワーは、上述の図8(a),図8(c)の場合よりも小さくなる。

したがって、演算制御回路4においては、一例として矩形度識別回路3からのモニタ結果である偶数次の高調波成分のパワーが最小又は一定誤差を含む最小範囲に収まるように、制御信号を矩形度整形回路5bに出力する。これにより、出力光パルスの波形を例えば図7(b)の波形B2を保つようにすることができる。前述したように、出力光パルスに含まれる偶数次の高調波成分が最小となる場合には、光パルスの波形としては、奇数次の高調波成分の重ね合わせである理想的な矩形波形状を、ほぼ有するようになるからである。

【0064】

上述したように、演算制御回路4における、矩形度識別回路3からの偶数次高調波成分パワーに基づく矩形度整形回路5bを介した可変容量素子16aの容量の制御により、SOA2から出力される光パルスの波形が所定の波形を保つようにしている。尚、演算制御回路4においては、所定の波形が保たれるようになったときの制御信号(例えば矩形度整形回路5bへの制御信号)の制御量を記憶しておくことができる。これにより、SOA2をゲートスイッチとして実運用する際にはフィードバック制御を行なわずとも出力光波形を所期の波形にすることができる。

【0065】

また、制御目標となる光パルスの波形については、例示したように真正の矩形波形状としたり、又は、図7(a)のA2のような立ち上がり幅の大きい矩形度の波形としたり、図7(c)のC2のような立ち上がりの鈍った矩形度の波形としたりすることもできる。

図9は図6に示すゲートスイッチ駆動回路5cの変形例であるゲートスイッチ駆動回路5c′を示す図である。ゲートスイッチ駆動回路5c′は、応答素子であるSOA2への駆動信号の波形を、制御信号に基づき整形する駆動回路部の他の例であり、回路部18とともに図6の場合と同様のドライバアンプ17をそなえている。回路部18は、抵抗18a,18bとともに、矩形度整形回路5bからの制御信号によりインダクタンスを可変としうるインダクタ素子18cをそなえる。

【0066】

矩形度整形回路5bからの制御信号を通じて、可変インダクタ素子18cのインダクタンスが可変されると、回路部18の応答時定数が可変する。このため、ゲートスイッチ駆動回路5cから出力される駆動パルス信号の立ち上がりおよび立ち下がりの波形が整形される。可変インダクタ素子18cのインダクタンスをL1、抵抗18a,18bの抵抗値をそれぞれ固定値R11,R13とすると、回路部18の応答時定数τ2は式(4)のようになる。従って、インダクタンスL1を大きくすると、応答時定数τ2は大きくなり、インダクタンスL1を小さくすると、応答時定数τ2は小さくなる。

【0067】

【数3】

【0068】

換言すれば、演算制御回路4は、可変インダクタ素子18cのインダクタンスを、矩形度整形回路5bを介して制御することを通じて、回路部18の応答時定数を制御し、ゲートスイッチ駆動回路5cから出力される駆動パルス信号の波形を制御できる。

つぎに、上述したような波形制御装置1又は応答素子モジュール10の動作例について説明する。

【0069】

たとえば、図1に示す光パケットスイッチ100の運用を開始する前段において、光パケットスイッチ100の要素として適用される応答素子としてのSOA102a,104の調整を行なう際に、波形制御装置1を用いる。又は、SOA102a,104として適用されるSOA2を有する応答素子モジュール10において、SOA2への駆動パルス波形の整形を行なう。

【0070】

駆動電圧制御回路5ではSOA2に対して駆動信号を供給することで、SOA2から出力パルスを出力させる。このとき、SOA2への入力光は非入力であり、駆動電圧制御回路5から供給される駆動信号のオンオフにより、出力/非出力が繰り返されるASE光が、SOA2から出力される出力パルスである。尚、駆動信号のオンオフ周期、即ち駆動パルス信号としてのパルス周期は、演算制御回路4からのトリガ信号の周期に由来しているので、演算制御回路5において既知のものである。

【0071】

そして、矩形度識別回路3では、SOA2から出力された出力パルスの波形をモニタし、その矩形度、又は、立ち上がりエッジの先鋭度について識別する。例えば、高調波成分抽出部3aにおいて、SOA2から出力された出力光パルスの、当該パルス周期における偶数次高調波成分について抽出し、パワー検出回路3bで、抽出した偶数次高調波成分のパワーを検出する。

【0072】

演算制御回路4は、検出した偶数次高調波成分のパワーについてA/Dコンバータ3cを介してディジタル信号として受ける。そして、この演算制御回路4と駆動電圧制御回路5とが協働して、受けた偶数次高調波成分のパワーをもとに、当該パワーが目標値(例えば最小又は所定の誤差を含む最小範囲)に一致するまたは近づくように、SOA2への駆動パルス信号の波形を制御する。

【0073】

具体的には、演算制御回路4において、矩形度整形回路5bを介することにより、ゲートスイッチ駆動回路5cをなす回路部16(図6参照)の可変容量素子16aの容量を可変させることで、SOA2への駆動パルス信号の波形を整形させる。又は、ゲートスイッチ駆動回路5c′をなす回路部18(図9参照)の可変インダクタ素子18cの容量を可変させることで、SOA2への駆動パルス信号の立ち上がりエッジの先鋭度を整形させる。

【0074】

SOA2は、上述の駆動パルス信号により駆動されて出力パルスを出力する。このため、演算制御回路4で、矩形度整形回路5bを介して、ゲートスイッチ駆動回路5cから出力される駆動パルス信号の波形を制御することを通じて、SOA2から出力される出力パルスの波形の矩形度を制御することができるようになる。

上述のごとく制御目標となる駆動パルス信号が得られるようになった場合においては、演算制御回路4においては、そのときの矩形度整形回路5bに対する制御信号の制御量を記憶しておくようにしてもよい。このようにすれば、その後実運用に移行した際において、演算制御回路4において記憶している固定的な制御量で矩形度整形回路5bを介してゲートスイッチ駆動回路5cを制御することができる。

【0075】

実運用時には、演算制御回路4からゲートスイッチ駆動回路5cに対して入力光について導通/遮断すべきタイミングに応じたトリガ信号が入力されるようになるので、トリガ信号の周波数としては一定になるとは限らない。しかしながら、演算制御回路4においては、記憶されている制御量において矩形度整形回路5bを制御することで、SOA2からの出力光の立ち上がり波形を初期の形状とすることができるようになる。尚、実運用後においても、導通/遮断の対象となる入力光が入力されない状態においては、必要に応じて適宜上述のフィードバックを働かせることもできる。

【0076】

このように、第1実施形態によれば、簡易な波形整形によって目標の矩形度を有するパルスを生成できる利点がある。

なお、上述の第1実施形態においては、SOA2から出力されるASE光を含む光パルスをモニタすることにより、光パルスの矩形度を整形している。このほかに、外部からの入力信号、例えば、SOA2を光ゲートスイッチとして適用した場合の導通/遮断の対象となる入力光を用いて整形することとしてもよい。この場合においては、演算制御回路4から出力されるトリガ信号の周波数としては既知の一定周波数としておくことで、矩形度識別回路3をなす高調波成分抽出部3aの周波数抽出特性について、上記一定周波数に基づき定めておくことが可能になる。

【0077】

〔B〕第2実施形態

図10は第2実施形態にかかる波形制御装置1A又は応答素子モジュール10Aを示す図である。第2実施形態においては、前述の第1実施形態と比較して、異なる要素をそなえた矩形度識別回路3Aをそなえるとともに、制御態様の異なる演算制御回路4Aをそなえている。尚、既述の符号はほぼ同様の部分を示す。即ち、波形制御装置1Aは、矩形度識別回路3Aおよび演算制御回路4Aをそなえるとともに、第1実施形態の場合と同様の駆動電圧制御回路5をそなえ、応答素子モジュール10Aは、上述の波形制御装置1Aとしての要素とともにSOA2をそなえる。

【0078】

矩形度識別回路3Aは、応答素子であるSOA2に供給される駆動信号に当該SOA2が応答して得られる出力パルスの波形をモニタするモニタ部の一例であるが、第2実施形態においては受光部3dおよび高速A/Dコンバータ3eをそなえている。受光部3dは、SOA2から出力された光について光カプラ7を介して受けて、光パルスとしての振幅変化に応じた振幅変化を有する電圧信号等の電気信号に変換する。フォトダイオード(PD)およびトランスインピーダンスアンプは、協働して受光部3dの一例に相当する。

【0079】

また、高速A/Dコンバータ3eは、出力パルスの波形をサンプリングするサンプリング部の一例であり、受光部3dからの電気信号を高速サンプリングする。高速A/Dコンバータ3eにおいては、光パルスに応じた振幅変化をサンプリングするために、SOA2をオンオフスイッチングする際の応答波形を複数点サンプリングする必要がある。

このため、高速A/Dコンバータ3eとしては、例えば、SOA2のオンオフスイッチングの速度の5〜10倍程度高速のサンプリング周期を有するものを用いる。例えば、スイッチングを10ナノ秒で行なう性能を持つ光ゲートスイッチを用いる場合、その5〜10倍高速の1〜2ナノ秒のサンプリング周期を有するものを用いる。即ち、高速A/Dコンバータ3eとしては、500Msps〜1Gsps、もしくはそれ以上サンプリング周期を持つものを用いる。

【0080】

演算制御回路4Aは、駆動電圧制御回路5と協働して、サンプリング部3eでのサンプリング結果をもとに、SOA2への駆動信号の波形を整形する駆動波形整形部の一例に相当する。具体的には、演算制御回路4Aは、ゲートスイッチ駆動回路5cに一定周波数のトリガ信号を出力する一方、高速A/Dコンバータ3eからの出力を用いた演算を行ない、その演算結果に基づいて、矩形度整形回路5bへの制御信号を出力する。矩形度整形回路5bへの制御信号は、前述したように、ゲートスイッチ駆動回路5c(5c′)をなす回路部16又は回路部18(図6又は図9参照)の回路時定数を変更するための制御信号である。

【0081】

一例として、演算制御回路4Aにおいては、高速A/Dコンバータ3eにおいて、出力パルスの立ち上がり領域においてサンプリングされた値の変動指標を、例えば分散等の演算により導出し、導出結果に応じた制御信号を矩形度整形回路5bに出力する。例えば、演算制御回路4Aでは、演算された分散が最小となるように矩形度整形回路5bへの制御信号の制御量を制御すると、SOA2から出力される出力パルスの波形は、制御信号が他の制御量である場合に比較して、真正の(理想的な)矩形波形状に最も近くなる。

【0082】

図11は演算制御回路4Aの処理に着目した波形制御装置1Aの動作例について説明するフローチャートである。まず、演算制御回路4Aから矩形度整形回路5bに対して、矩形度整形回路5bでの制御量を初期設定する制御信号を出力する。ゲートスイッチ駆動回路5cの要素に、図6に示すバリキャップとしての可変容量素子16aを有する回路部16を適用する場合には、当該バリキャップ16aへの制御電圧信号を初期値Vk=Vbに設定する制御信号を矩形度整形回路5bに出力する(ステップA1)。

【0083】

ついで、演算制御回路4Aにおいて、SOA2から出力されるASE光のオンオフ制御のためのトリガ信号を生成し、ゲートスイッチ駆動回路5cに供給する。これにより、SOA2では、バリキャップ電圧の初期値に応じた立ち上がり波形を有する出力光パルス(例えばASE光)を出力することができる(ステップA2)。

そして、高速A/Dコンバータ3eから、SOA2から出力される出力光パルスの一定時間についてのサンプリング結果を受ける。一例として、演算制御回路4Aでは、既知であるトリガ信号の1以上の整数倍周期の時間についてのサンプリング結果を高速A/Dコンバータ3eから受けて、たとえば、メモリなどに記憶領域を設けて時系列で保持する(ステップA3)。

【0084】

さらに、上述の記憶領域に保持された上記一定時間のサンプリング結果について、その平均値X(=サンプリング合計値÷サンプリング数)を算出する(ステップA4)。

つぎに、記憶領域に保持された上記一定時間のサンプリング結果のうちで、算出した平均値Xを上回るサンプル点を抽出するとともに、抽出したサンプル点のうちの時系列における先頭のNサンプル標準偏差σを算出する(ステップA5)。先頭のNサンプルとしては、図12に示すように、可変容量素子16aの容量の値に応じて、出力光パルスの立ち上がり波形に変動が現れる時間範囲R1におけるサンプル点の個数の程度とすることができる。

【0085】

上述のごとく算出された標準偏差σについては、設定している電圧信号Vkの値に対応付けて図示しない記憶領域に記憶しておく(ステップA6)。以降、矩形度整形回路5bからの電圧信号について、制御範囲(Vb〜Vend)に亘り単位刻み幅ΔVで変更する(Vk=Vk+ΔV)。そして、その都度のサンプリング結果をもとにして上述のごとく標準偏差を演算する(ステップA7のNoルートからステップA8,ステップA3〜ステップA6)。

【0086】

上述の制御範囲に亘る標準偏差の値の演算が終了すると、即ちステップA7でVk≧Vendとなると(ステップA7のYesルート)、次に、目標点となる標準偏差を有する電圧信号の値を、上述の記憶領域を参照して検索する(ステップA9)。即ち、記憶領域に保持された矩形度整形回路5bでの電圧信号の値に応じた標準偏差の値の関係から、標準偏差σが目標値(例えば最小の標準偏差)となる電圧信号値を検索する。

【0087】

そして、このように検索された電圧信号値を、最適電圧信号値Voptとする。即ち、演算制御回路4Aにおいては、制御信号を出力することにより、矩形度整形回路5bからゲートスイッチ駆動回路5cのバリキャップ16aに供給する電圧信号をVoptとする(ステップA10)。

立ち上がりエッジが最も真正の矩形波形状に近い場合、標準偏差σはばらつきが最も小さくなるため、最小の値をとる。従って、例示したように、矩形度整形回路5bへの制御信号を通じて、算出される標準偏差σを最小となるようパルスの矩形度を制御する。このようにすると、出力光パルスの波形を、他の標準偏差をとる出力光パルスに比べて、最も矩形波形状に近づけることが可能となる。

【0088】

このように、第2実施形態においても、簡易な波形整形によって目標の矩形度を有するパルスを生成できる利点がある。

なお、上述の場合においては出力光パルスの立ち上がり波形における変動が現れる範囲についてのサンプル点について標準偏差を算出しているが、立ち下がり波形におけるにおける変動が現れる範囲についてのサンプル点について標準偏差を算出してもよい。この場合においては、上述のステップA4と同様に平均値Xを算出後、平均値Xを下回るサンプル点の最初のNサンプルに対して標準偏差σを算出すればよい。

【0089】

〔C〕第3実施形態

図13は第2実施形態にかかる波形制御装置1B又は応答素子モジュール10Bを示す図である。第3実施形態においては、前述の第1,第2実施形態と比較して、異なる要素をそなえた矩形度識別回路3Bをそなえるとともに、制御態様の異なる演算制御回路4Bをそなえている。尚、既述の符号はほぼ同様の部分を示す。即ち、波形制御装置1Bは、矩形度識別回路3Bおよび演算制御回路4Bをそなえるとともに、第1,第2実施形態の場合と同様の駆動電圧制御回路5をそなえ、応答素子モジュール10Bは、上述の波形制御装置1Bとしての要素とともにSOA2をそなえる。

【0090】

矩形度識別回路3Bは、応答素子であるSOA2に供給される駆動信号に当該SOA2が応答して得られる出力パルスの波形をモニタするモニタ部の一例である。第3実施形態の矩形度識別回路3Bにおいては、受光部3d,AC結合部3f,レベル調整部3g,エッジ検出回路3h,ピークホールド回路3i,サンプルホールド回路3jおよび2つのA/Dコンバータ3m,3nをそなえている。受光部3dについては第2実施形態におけるものと同様である。

【0091】

AC(Alternating Current)結合部3fは、受光部3dからの電気信号についてAC結合により直流成分をカットして、エッジ検出回路3hに出力する。又、レベル調整部3gは、受光部3dからの電気出力についてレベル調整を行なうアンプをそなえ、ピークホールド回路3iおよびサンプルホールド回路3jにそれぞれ出力する。

エッジ検出回路(エッジ検出部)3hは、電気信号として直流成分が除去された出力パルスをAC結合部3fから受けて、出力パルスの波形における立ち上がりエッジおよび立ち下がりエッジを検出する。

【0092】

また、ピークホールド回路(ピークホールド部)3iは、エッジ検出回路3hでの立ち上がりエッジの検出をもとに、出力パルスの波形における、駆動信号の立ち上がりに応答した立ち上がりピークレベルの値を保持する。具体的には、エッジ検出回路3hにおいて検出される立ち上がりエッジの検出をトリガとして、SOA2のスイッチング時間から立ち上がりピークレベルを検出するに必要とされる時間について、レベル調整部3gからの出力パルスのピーク値(最大値)を保持する。

【0093】

立ち上がりピークレベルを検出するに必要とされる時間は、たとえば図14に示すように定めることができる。即ち、エッジ検出回路3hでの立ち上がりエッジの検出によるトリガ信号を受けて開始して(時点T11)、当該立ち上がりが収束に向かうようになる所定時点T12までの時間T1とすることができる。これにより、ピークホールド回路3iにおいては、図14に示すように、可変容量素子16a(図6参照)の容量に応じて相違する立ち上がり波形W1,W2,W3に応じて、立ち上がりピークレベルP1,P2,P3を得ることができる。

【0094】

なお、ピークホールド回路3iでの上述のピークホールド動作のため、当該ピークホールド回路3iまたはエッジ検出回路3hにおいては、上述のT1についての時間管理機能を持つことができる。

または、ピークホールド回路3iでは、エッジ検出回路3hからの立ち上がりエッジ検出によるトリガ信号を受けてピークホールドを開始する一方、エッジ検出回路3hからの立ち下がりエッジ検出によるトリガ信号を受けるまでピークホールドを継続することとしてもよい。

【0095】

さらに、サンプルホールド回路(サンプルホールド部)3jは、エッジ検出回路3hでの立ち上がりエッジの検出をもとに、駆動信号の立ち下がり前の平坦領域に対応した応答波形レベルである出力パルスのレベルの値をサンプルホールドする。

具体的には、エッジ検出回路3hにおいて検出される立ち上がりエッジの検出から所定時間経過後の、立ち下がり前において出力パルスのレベルが安定する時間においてそのレベル値Sをサンプルホールドする。

【0096】

たとえば図14に示すように、サンプルホールド回路3jは、立ち上がりエッジの検出によるトリガ信号を受けてから(T11)、時間T2が経過した後のレベルが安定する時間(立ち下がり直前の時間)T3において、出力パルスのレベル値をサンプルホールドする。サンプルホールド回路3jでの上述のサンプルホールド動作のため、当該サンプルホールド回路3jまたはエッジ検出回路3hにおいては、上述のT2,T3についての時間管理機能を持つことができる。

【0097】

矩形度識別回路3Bに入力される出力パルスは、演算制御回路4Bから出力されるトリガ信号に対応するオンオフ周期を有している。従って、サンプルホールド回路3jにおいても、出力パルスについての立ち上がりから立ち下がりに至るオン時間が固定されている。このため、サンプルホールド回路3jまたはエッジ検出回路3hにおいては、当該オン時間の値に応じて上述の時間T2,T3を設定することができる。

【0098】

A/Dコンバータ3mは、ピークホールド回路3iからの、立ち上がりピークレベルの値を示すアナログ信号についてディジタル信号に変換して演算制御回路4Bに出力する。又、A/Dコンバータ3nは、サンプルホールド回路3jにおいてサンプルホールドしている値を示すアナログ信号についてディジタル信号に変換して演算制御回路4Bに出力する。

【0099】

演算制御回路4Bは、駆動電圧制御回路5と協働して、ピークホールド回路3iで保持した値およびサンプルホールド回路3jでサンプルホールドした値をモニタ結果として受けて、当該モニタ結果に基づき駆動信号の波形を整形する駆動波形可変部の一例に相当する。

具体的には、演算制御回路4Bは、ゲートスイッチ駆動回路5cに一定周波数のトリガ信号を出力する一方、A/Dコンバータ3m,3nからの各出力を用いた演算を行ない、その演算結果に基づいて、矩形度整形回路5bへの制御信号を出力する。矩形度整形回路5bへの制御信号は、前述したように、図6に示す可変容量素子16aの容量(又は図9に示す可変インダクタ素子18cのインダクタンス)の制御を通じ回路16(又は18)の応答時定数を変更するための制御信号である。

【0100】

一例として、A/Dコンバータ3mからのピークホールド値を立ち上がり振幅値とする一方、A/Dコンバータ3nからのサンプルホールド値を立ち下がり振幅値として、両者の差を演算する。このようにして演算される差の値に応じて上述の矩形度整形回路5bへの制御信号による制御量を制御する。例えば、演算される差の値が最小となるように矩形度整形回路5bへの制御信号による制御量を制御すると、SOA2から出力される出力パルスの波形は、制御信号が他の制御量である場合に比較して、真正の(理想的な)矩形波形状に最も近くなる。

【0101】

図15は演算制御回路4Bの処理に着目した波形制御装置1Bの動作例について説明するフローチャートである。この動作例では、波形制御装置1Bを図1に示す光パケットスイッチ100に適用して、複数のSOA102a,104に対する駆動信号(又は出力光パルス波形)について、理想的な矩形波形状を有するように順次整形している。又、ゲートスイッチ駆動回路5cとして図6に示す回路部16を、更に、可変容量素子16aとしてバリキャップを適用している。

【0102】

まず、演算制御回路4Bから矩形度整形回路5bに対して、矩形度整形回路5bでの制御量を初期設定する制御信号を出力する。ゲートスイッチ駆動回路5cの要素に、図6に示すバリキャップとしての可変容量素子16aを有する回路部16を適用する場合には、当該バリキャップ16aへの制御電圧信号を初期値αに設定する制御信号を出力する(ステップB1)。

【0103】

ついで、演算制御回路4Bにおいて、SOA2から出力されるASE光のオンオフ制御のためのトリガ信号を生成し、ゲートスイッチ駆動回路5cに供給する。これにより、SOA2では、バリキャップ電圧の初期値に応じた立ち上がり波形を有する出力光パルス(例えばASE光)を出力することができる(ステップB2)。

そして、エッジ検出回路3hにおいて、受光部3dからAC結合部3fを介して入力される出力パルスから、出力パルスの立ち上がりおよび立ち下がりエッジを検出する(ステップB3)。この場合において、エッジ検出回路3hでは、エッジ検出するとその旨のトリガ信号をピークホールド回路3iおよびサンプルホールド回路3jに出力する。

【0104】

さらに、ピークホールド回路3iは、エッジ検出回路3hからの立ち上がりエッジに応じたトリガ信号により、出力パルスの立ち上がりタイミングで一定時間起動される。そして、このピークホールド回路3iで、立ち上がり波形のピーク値(最大値)を保持する(ステップB4)。更に、A/Dコンバータ3mにおいては、ピークホールド回路3iで保持するピーク値について読み取り、これを立ち上がり振幅Vrとして演算制御回路4Bに出力する(ステップB5)。

【0105】

また、サンプルホールド回路3jでは、エッジ検出回路3hにおいて検出される立ち上がりエッジの検出から所定時間経過後の、立ち下がり前において出力パルスのレベルが安定する時間においてそのレベル値Sをサンプルホールドする(ステップB6)。更に、A/Dコンバータ3nにおいては、サンプルホールド回路3jで保持するピーク値について読み取り、これを立ち下がり振幅Vfとして演算制御回路4Bに出力する(ステップB7)。

【0106】

演算制御回路4Bでは、A/Dコンバータ3m,3nからの立ち上がり振幅値Vrおよび立ち下がり振幅値Vfを比較する。両者の差が一定値D以上である場合には、当該SOA2から出力される出力パルスの波形は理想的な矩形波形状から崩れているので、理想的な矩形波形状に近づくように、矩形度整形回路5bへの制御信号の制御量を変更する(ステップB8のYesルート)。

【0107】

具体的には、立ち上がり振幅Vrが立ち下がり振幅Vfよりも大きい場合においては(ステップB9のYesルート)、エッジが利きすぎ、即ち、理想的な矩形度からすると立ち上がりが急峻である。このため、演算制御回路4Bから矩形度整形回路5bに対する制御信号を通じて、矩形度整形回路5bからのバリキャップ電圧をΔVだけ上げることにより、立ち上がり波形を鈍らせる(ステップB10)。

【0108】

また、立ち上がり振幅Vrが立ち下がり振幅Vf以下の場合においては(ステップB9のNoルート)、エッジがなまりすぎ、即ち、理想的な矩形度からすると立ち上がりが鈍い。このため、演算制御回路4Bから矩形度整形回路5bに対する制御信号を通じて、矩形度整形回路5bからのバリキャップ電圧をΔVだけ下げることにより、立ち上がり波形を尖らせる(ステップB11)。

【0109】

演算制御回路4Bでは、立ち上がり振幅値Vrおよび立ち下がり振幅値Vfの差がDよりも小さくなるまで、上述したようなバリキャップ電圧を変更する制御を繰り返す(ステップB10,B11からステップB3)。

矩形度整形回路5bからのバリキャップ電圧の制御を通じて、VrとVfとの差が一定値Dよりも小さくなった場合には、駆動信号の調整対象となっている当該SOA2(SOA102a,104)に対する駆動信号の調整は終了する。このようにして、全ての測定対象のSOA102a,104について駆動信号を順次調整していく(ステップB12)。

【0110】

全てのSOAに対する駆動信号の調整が終了すると、装置としての実運用を開始することができる。例えば、図1の光パケットスイッチ100をなす全てのSOA102a,104についての駆動信号の調整が完了すると、光パケットスイッチ100として実運用が可能になる。即ち、SOA102aは、光ゲートスイッチとして入力光の導通/遮断の制御に用いることができ、又は、SOA104は、入力光の導通/遮断のほか増幅のために用いることができる。

【0111】

なお、上述のVrとVfとの差に対する基準値Dとしては、例えばSOA2から出力される出力パルスの波形が目標とする矩形度を得られる許容値に対応するものとすることができる。

なお、上述の動作例においては、SOA2からの出力パルスについて理想的な矩形波形状に近づけるように制御しているが、制御目標としては理想的でない特定の矩形波形状となるようにしてもよい。一例として、演算制御回路4Bにおいては、立ち上がり振幅値と立ち下がり振幅値との差が、誤差範囲を含む特定の(最小ではない)値となるように、矩形波整形回路5bを制御することとしてもよい。

【0112】

このように、第3実施形態においても、簡易な波形整形によって目標の矩形度を有するパルスを生成できる利点がある。

〔D〕実施例

上述の第1〜第3実施形態において例示した波形制御装置1,1A,1B,応答素子モジュール10,10A,10Bは、例えば、光パケットスイッチングを行なう光パケットスイッチに適用することができる。その一例を図16に示す。この図16に示す光パケットスイッチ200においては、図1に示す光パケットスイッチ100と同様、8個の1:8カプラ101,8個の8:8光ゲートスイッチ部102,8個の8:1カプラ103および8個のSOA104をそなえている。尚、図1と同一の符号はほぼ同様の部分を示している。

【0113】

光パケットスイッチ200は、駆動信号に応答して入力光の導通/遮断を切り換える光ゲートスイッチとしてのSOA102a,104を複数有する光スイッチ装置の一例である。光パケットスイッチ200は、光カプラ207a−1〜207a−8,207b,矩形度識別回路203,演算制御回路204および各SOA102a,104に対応した数の駆動電圧制御回路205をそなえる。

【0114】

駆動電圧制御回路205は、8:8光ゲートスイッチ部102をなす64個のSOA102aとともに、8個のSOA104に対応づけて72個がそなえられ、それぞれ、個別のSOA102a,104に対して駆動信号を供給するものである。各駆動電圧制御回路205としては、前述の各実施形態における波形制御装置1,1A,1Bの要素である駆動電圧制御回路5を適用することができる。

【0115】

すなわち、各駆動電圧制御回路205をなすゲートスイッチ駆動回路5c(図2,図10,図13参照)は、縦続して接続される複数個の光ゲートスイッチ102a,104に対応してそなえられ、対応する光ゲートスイッチ102a,104への駆動信号の波形を、制御信号に基づき整形する複数個の駆動回路部の一例である。

演算制御回路204は、各駆動電圧制御回路205をなすゲートスイッチ駆動回路5cに対して、対応するSOA102a,104を駆動するためのトリガ信号を出力するとともに、各駆動電圧制御回路205をなす矩形度整形回路5bへの制御信号を与える。演算制御回路204としては、前述の各実施形態における波形制御装置1,1A,1Bの要素である演算制御回路4,4A,4Bの一態様を、上述の72個の駆動電圧制御回路205を制御するために適用することができる。

【0116】

したがって、各駆動電圧制御回路205をなす矩形度整形回路5b(図2,図10,図13参照)および演算制御回路4,4A,4Bは、協働することにより、モニタ部203でのモニタ結果に基づき制御信号を駆動回路部5cに出力する制御部の一例に相当する。

光カプラ207a−1,207a−8は、出力ポート♯1〜♯8を伝搬する光をそれぞれ分岐する。光カプラ207bは、光カプラ207a−1〜207a−8からの分岐光経路を合流して、矩形度識別回路203の入力とする。

【0117】

矩形度識別回路203は、72個のSOA102a,104から出力される出力光パルス(出力パルス)の波形をモニタするモニタ部の一例であり、出力光パルスの矩形度を識別する。ここで、出力ポート♯j(j=1〜8の整数)に対応する8:8光ゲートスイッチ部102をなすSOA102aおよび対応する下流側のSOA104から出力される光は、光カプラ207a−j,207bを介して矩形度識別回路203に入力される。

【0118】

このとき、各SOA102a,104に対する駆動電圧制御回路205からの駆動信号の供給態様により、一のSOA102a,104から出力される光パルスの矩形度について順次識別することが可能になる。又、矩形度識別回路203としては、前述の各実施形態における波形制御装置1,1A,1Bの要素である矩形度識別回路3,3A,3Bの一態様を適用することができる。

【0119】

このように、駆動電圧制御回路205においては、各SOA102a,104に対応して72個そなえられているが、演算制御回路204および矩形度識別回路203については、各SOA102a,104について共用することができる。即ち、各駆動電圧制御回路205および演算制御回路204は、協働することで、モニタ部203でのモニタ結果に基づいて、当該出力された光波形をモニタした光ゲートスイッチ102a,104への駆動信号の波形を整形する駆動波形整形部に相当する。

【0120】

つぎに、光パケットスイッチ200の運用開始前の各SOA102a,104を駆動する駆動信号の調整動作例を説明する。各SOA102a,104の駆動信号を調整するにあたっては、光パケットスイッチ200をなす下流側のSOA104に対する駆動信号を優先的に調整する。

各出力ポート♯1〜♯8に対応して、一のSOA104が最下流に、8個のSOA102aが上流側にそなえられ、光カプラ207a−1〜207a−8,207bにより各出力ポート♯1〜♯8への出力が取りまとめられて矩形度識別回路203に接続されている。従って、上流側のSOA102aに対する駆動信号の調整のためには、下流側のSOA104を通じた出力光パルスをモニタすることになる。

【0121】

そこで、一の出力ポートに対応付けられた上流側のSOA102aに対する駆動信号を調整するには、当該下流側のSOA104への駆動信号の調整が完了していることが望ましい。これにより、下流側のSOA104への駆動信号が未調整である場合における、上流側のSOA102aに対する駆動信号の調整への影響を、生じさせないようにすることができる。

【0122】

たとえば、一の出力ポート♯jに対応して、最下流のSOA104についての駆動電圧制御回路205からの駆動信号について第1に調整し、第2に、上流側の8個のSOA102aについての駆動電圧制御回路205からの駆動信号について調整する。その後、他の出力ポートについてのSOA104,102aに対する駆動信号について同様に調整する。

【0123】

すなわち、演算制御回路204により、上流側のSOA102aへの駆動信号をオフとする一方、一のSOA104に対応する駆動電圧制御回路205に対して、トリガ信号を供給することを通じ、ASE光を含む出力光パルスを生成させる。この出力光パルスは、光カプラ207a−j,207bを介して矩形度識別回路203に入力される。そして、演算制御回路204および該当の駆動電圧制御回路205が協働することにより、矩形度識別回路203からのモニタ結果をもとにして駆動信号の波形を整形することを実現する。

【0124】

なお、上流側の8個のSOA102aについての駆動信号を整形するにあたっては、調整対象のSOA102aよりも下流側のSOA104についてはオン状態に固定しておく。これにより、上流側SOA102aで生成されるASE光による光パルスは、下流側SOA104および光カプラ207a−j,207bを介して矩形度識別回路203に入力されるので、モニタすることが可能になる。

【0125】

または、各出力ポート♯1〜♯8に対応する下流側SOA104についての駆動信号について順次優先的に調整し、次いで、各出力ポート♯1〜♯8に対応する上流側SOA102aについての駆動信号について調整してもよい。

このようにして、全てのSOA102a,104についての駆動信号の調整動作が完了すると、光パケットスイッチ200として実運用を開始できる。

【0126】

このように、例示した波形制御装置1,1A,1Bを光パケットスイッチ200の要素として適用することにより、多ポート対多ポートの光パケットスイッチシステムを容易に構築できる。即ち、光ゲートスイッチ102a,104ごとの駆動回路を個別に調整する必要がなくなり、組立調整にかかる工数を大幅に削減することが可能となる。また、装置運用開始後においても、各光ゲートスイッチ102a,104についての調整作業が効率化されるので、メインテナンス性やシステム信頼性も向上する。即ち、定期的に各光ゲートスイッチ102a,104についての駆動波形の最適化を行なうことで、長期に渡り装置性能を維持することが可能となる。

【0127】

図17は、上述の第1〜第3実施形態において例示した波形制御装置1,1A,1B,応答素子モジュール10,10A,10Bの他の光パケットスイッチ300への適用例である。この図17に示す光パケットスイッチ300においては、256の入力ポートに対応してそなえられた256個の分配部310−k,256の出力ポートに対応してそなえられた256個の合流部320−kをそなえる(k=1〜256の整数)。

【0128】

なお、図17中においては、一の分配部310−1,320−1をなす要素とともに、一対の入出力ポート♯1間が接続された経路に着目して示している。又、各分配部310−kは互いに同様の構成を有し、各合流部320−kも互いに同様の構成を有するので、以下においては一の分配部310−1および一の合流部320−1に着目して説明する。

分配部310−1は、入力ポート♯1からの光について256分配して、各分配経路を、一の合流部320−kに接続する。このため、分配部310−1は、一例として、上流側から、エルビウムドープファイバ増幅器(EDFA)311,1:16カプラ312,16個のEDFA313,16個の1:16カプラ314および16×16個のEDFA315をそなえる。

【0129】

入力ポート♯1からの光がEDFA311で光増幅され、1:16カプラ312で16分岐される。1:16カプラ312で分岐された16経路の各光は対応のEDFA313で光増幅される。EDFA313で光増幅された16経路の各光は、更に対応の1:16カプラ314で16分岐される。1:16カプラ314で分岐された合計16×16(=256)経路の各光は、対応のEDFA315で光増幅され、対応の合流部320−kに出力される。

【0130】

合流部320−1は、各分配部310−kからの経路が1経路ずつ接続されて、合計256の光経路を合流させて、出力ポート♯1に導く。そして、256の経路のいずれか1経路からの光について選択的に導通させ、他の経路からの光については遮断されるようになっている。このため、合流部320−1は、一例として、上流側から、256個のSOA321,32個の8:1カプラ322,32個のSOA323,32個の4:1カプラ324,8個のSOA325,1個の8:1カプラ326および1個のSOA327をそなえる。

【0131】

SOA321は、各分配部310−kからの光について導通/遮断を切り換える。各8:1カプラ322は、それぞれ8個のSOA321からの光経路を合流させる。各SOA323は、一の8:1カプラ322からの光について導通/遮断を切り換える。各4:1カプラ324は、それぞれ4個のSOA323からの光経路を合流させる。各SOA325は、一の4:1カプラ324からの光について導通/遮断を切り換える。8:1カプラ326は、8個のSOA325からの光経路を合流させる。SOA327は、8:1カプラ326からの光について導通/遮断を切り換える。

【0132】

これにより、合流部320−1においては、縦続接続された各段一つずつの合計4つのSOA321,323,325,327が同時に導通制御されることで、いずれかの分配部310−kからの光について出力ポート♯1に導くことができるようになる。

このような構成を有する光パケットスイッチ300においても、図16に示す光パケットスイッチ200の場合に倣って、矩形度識別回路(符号203参照),演算制御回路(符号204参照)および駆動電圧制御回路(符号205参照)を適用することができる。これにより、(256+32+8+1)×256ものSOAに対して、簡易に駆動信号を調整することができる。

【0133】

なお、この場合においても、矩形度識別回路としては一つで共用することができる。又、一対の入出力ポートを形成する経路単位で、下流側のSOAから上流側のSOAにわたり順次駆動信号を調整していくことで、光パケットスイッチ300全体として効率的かつ高精度での駆動信号の調整を実現できる。

また、一対の入出力ポートを形成する経路において、上流側のSOAについての駆動信号を調整するにあたっては、調整対象のSOAよりも下流側のSOAについては全てオン状態に固定しておく。これにより、上流側SOAで生成されるASE光による光パルスは、下流側SOAを介して矩形度識別回路に入力されるので、モニタすることが可能になる。

【0134】

このように、例示した波形制御装置1,1A,1Bを光パケットスイッチ300の要素として適用することにより、多ポート対多ポートの光パケットスイッチシステムを容易に構築できる。特に、図16の場合よりも光ゲートスイッチの素子数が増大する反面、各光ゲートスイッチの調整の効率化に対する効果はより大きくなる。

〔E〕その他

なお、第1〜第3実施形態における応答素子モジュール10,10A,10Bにおいては、その製造工程において、矩形度調整回路5bへの制御信号の制御量等を記憶しておくようにしてもよい。例えば、応答素子モジュール10,10A,10Bの各要素についての組み立てを行なったのちに、ASE光による光パルスを用いた上述の駆動信号の調整制御を行ない、更にモニタ結果が制御目標となる値となったときの、矩形度調整回路5bへの制御信号の制御量等を記憶しておくようにする。このようにすれば、応答素子モジュール10,10A,10Bの立ち上げ時において、演算制御回路4において記憶された制御量を用いてSOA2を駆動できるので、上述の各実施形態の場合と同様の利点があるほか、立ち上げ時においてのパルス波形の調整制御を省略でき、立ち上げ時間を高速化させるとともに、処理負荷を軽減できる。

【0135】

また、上述の実施形態においては、SOAのごとき光ゲートスイッチ素子に対する駆動信号の調整を通じて、光ゲートスイッチ素子から出力される出力光パルスの波形を整形している。しかしながら、例えば電気素子に対する出力パルスの波形を整形する際に用いることも勿論可能である。即ち、例示する波形制御装置1,1A,1Bは、電気信号を媒介として駆動信号の波形を整形しているので、波形制御装置1,1A,1Bとしてモニタ対象の出力パルスを出力する応答素子としては、電気素子とすることも勿論可能である。

【0136】

この場合は、例示の応答素子モジュール10,10A,10Bをなす応答素子2は電気素子に置き換えられ、矩形度識別回路3,3A,3B中の光を受光する機能については適宜省略できる。このような応答素子モジュールについては、2値のディジタル信号を扱う様々な電子機器に適用でき、実施形態で説明したような作用効果を奏することが可能となる。

【0137】

図18に、応答素子として電気素子を適用した場合の波形制御装置1Cおよび応答素子モジュール10Cの一例を示す。応答素子モジュール10Cは、スイッチ21,アンプ22,スイッチ27および波形制御装置1Cを含み、波形制御装置1Cで、アンプ22から出力される電気信号の波形をモニタして、モニタ結果に基づきアンプ22への駆動信号波形を整形する。これにより、アンプ22から出力される電気信号の矩形度を自在に制御する。

【0138】

スイッチ21は、入力電気信号のアンプ22への導通又は遮断を切り換える。アンプ22は、応答素子の一例であり、スイッチ21から入力される電気信号を、波形制御装置1Cで波形制御された駆動信号の一例である利得制御信号に基づいて増幅する。スイッチ27は、アンプ22から出力される出力電気信号について、応答素子モジュール10Cの出力方路か又は波形制御装置1Cへ入力される方路のいずれか一方を選択的に切り換える。

【0139】

波形制御装置1Cは、図18に例示するように、矩形度識別回路23と、演算制御回路24と、駆動電圧制御回路25と、を含む。演算制御回路24は、スイッチ21,27の切り換え設定を制御できる。例えば、スイッチ21,27を制御することにより、入力電気信号がアンプ22に供給され、アンプ22の出力が応答素子モジュール10Cの出力に導かれるようにする。これにより、応答素子モジュール10Cのアンプ22を経由した電気信号を用いることができる。

【0140】

また、スイッチ21を制御することにより、入力電気信号のアンプ22への供給を遮断できる。更に、スイッチ27を制御することにより、アンプ22の出力を矩形度識別回路23のコムフィルタ3a′に導くことができる。この場合には、例えば、演算制御回路24で生成した電気信号(一例として、擬似信号)を、スイッチ21を通じてアンプ22に出力するようにしてもよい。

【0141】

矩形度識別回路23は、供給される駆動信号に応答素子が応答して得られる出力パルスの波形をモニタするモニタ部の一例であり、コムフィルタ3a′とともに、前述の第1実施形態の場合と同様の平均パワー検出回路3bおよびA/Dコンバータ3cをそなえる。この場合には、演算制御回路24で生成した電気信号がアンプ22で増幅されて、このアンプ22から出力された出力電気信号がスイッチ27を経由して矩形度識別回路23に入力される。

【0142】

コムフィルタ3a′は、高調波成分抽出部の一例であり、アンプ22からの出力電気信号を、スイッチ27を通じて入力され、この出力電気信号に含まれる偶数次又は奇数次の高調波成分を抽出する。これにより、矩形度識別回路23においては、出力電気信号に含まれる偶数次又は奇数次の高調波成分の平均パワー値を演算制御回路24に出力する。

演算制御回路24および駆動波形制御回路25は、互いに協働することで、モニタ部23でのモニタ結果に基づいて、駆動信号の波形を整形する駆動波形整形部の一例に相当する。演算制御回路24においては、矩形度識別回路23からのモニタ結果をもとに、駆動波形制御回路25を介してアンプ22の利得を制御する。

【0143】

たとえば、矩形度識別回路23から偶数次の高調波成分の平均パワー値を受ける場合には、演算制御回路24では当該平均パワー値が最小となるように、駆動波形制御回路25を介してアンプ22の利得を制御する信号を出力する。これに対し、奇数次の高調波成分の平均パワー値を受ける場合には、演算制御回路24では当該平均パワー値が最大となるように、駆動波形制御回路25を介してアンプ22の利得を制御する信号を出力する。

【0144】

また、駆動波形制御回路25は、一例として、前述の第1実施形態の場合と同様のD/Aコンバータ5aおよび矩形度整形回路5bとともに、図6に例示するものと同等の駆動回路5cをそなえる。これにより、第1実施形態の場合と同様、演算制御回路24および駆動波形制御回路25が協働することにより、アンプ22に利得制御信号として供給される駆動信号の立ち上がり波形を整形することができる。結果として、出力電気信号の矩形度を目標の矩形度とすることができる。

【0145】

このように、図18に示す例においても、簡易な波形整形によって目標の矩形度を有する出力電気信号を得ることができる。

〔F〕付記

(付記1)

供給される駆動信号に応答素子が応答して得られる出力パルスの波形をモニタするモニタ部と、

該モニタ部でのモニタ結果に基づいて、前記駆動信号の波形を整形する駆動波形整形部と、をそなえたことを特徴とする、波形制御装置。

【0146】

(付記2)

該駆動波形整形部は、

前記応答素子への前記駆動信号の波形を、制御信号に基づき整形する駆動回路部と、

該モニタ部でのモニタ結果に基づき前記制御信号を該駆動回路部に出力する制御部と、をそなえたことを特徴とする、付記1記載の波形制御装置。

【0147】

(付記3)

該制御部は、前記モニタ結果としての前記出力パルスの波形が所定の波形を保つように前記制御信号を出力することを特徴とする、付記2記載の波形制御装置。

(付記4)

該駆動回路部は、前記制御信号に応じて応答時定数が可変されることを特徴とする、付記2記載の波形制御装置。

【0148】

(付記5)

該駆動回路部は、前記制御信号により容量が可変される可変容量素子を有することを特徴とする、付記4記載の波形制御装置。

(付記6)

該駆動回路部は、前記制御信号によりインダクタンスが可変されるインダクタ素子を有することを特徴とする、付記4記載の波形制御装置。

【0149】

(付記7)

該モニタ部は、

前記駆動信号の周波数の偶数次又は奇数次の高調波成分を前記出力パルスから抽出する高調波成分抽出部と、

該高調波成分抽出部にて抽出された前記偶数次又は奇数次の高調波成分を含む パワーをモニタするパワーモニタ部と、をそなえたことを特徴とする、付記1記載の波形制御装置。

【0150】

(付記8)

該駆動波形整形部は、該パワーモニタ部でモニタされたパワーが所定レベル又は所定範囲となるように前記駆動信号の波形を整形することを特徴とする、付記7記載の波形制御装置。

(付記9)

該モニタ部は、前記出力パルスの波形をサンプリングするサンプリング部をそなえ、

該駆動波形整形部は、該サンプリング部でのサンプリング結果をもとに、前記駆動信号の波形を整形することを特徴とする、付記1記載の波形制御装置。

【0151】

(付記10)

該モニタ部は、

前記出力パルスの波形における立ち上がりエッジおよび立ち下がりエッジを検出するエッジ検出部と、

該エッジ検出部での前記立ち上がりエッジの検出をもとに、前記出力パルスの波形における、前記駆動信号の立ち上がりに応答した立ち上がりピークレベルの値を保持するピークホールド部と、

該エッジ検出部での前記立ち上がりエッジの検出をもとに、前記駆動信号の立ち下がり前の平坦領域に対応した応答波形レベルの値をサンプルホールドするサンプルホールド部と、をそなえ、

該駆動波形整形部は、該ピークホールド部で保持した値および該サンプルホールド部でサンプルホールドした値を前記モニタ結果として受けることを特徴とする、付記1記載の波形制御装置。

【0152】

(付記11)

該駆動波形整形部は、該ピークホールド部で保持した値と、該サンプルホールド部でサンプルホールドした値と、の差が所定値又は所定範囲となるように、前記駆動信号の波形を整形することを特徴とする、付記10記載の波形制御装置。

(付記12)

供給される駆動信号に応答して出力パルスを得る応答素子と、

該応答素子からの前記出力パルスの波形をモニタするモニタ部と、

該モニタ部でのモニタ結果に基づいて、前記駆動信号の波形を整形する駆動波形整形部と、をそなえたことを特徴とする、応答素子モジュール。

【0153】

(付記13)

該応答素子は、前記駆動信号に応答して出力される光パルスを前記出力パルスとして出力する半導体光増幅器であることを特徴とする、付記12記載の応答素子モジュール。

(付記14)

前記光パルスは、自然放出光であることを特徴とする、付記13記載の応答素子モジュール。

【0154】

(付記15)

駆動信号に応答して入力光の導通/遮断を切り換える光ゲートスイッチを複数有する光スイッチ装置であって、

該光ゲートスイッチの一つから出力される光波形をモニタするモニタ部と、

該モニタ部でのモニタ結果に基づいて、当該出力された光波形をモニタした光ゲートスイッチへの前記駆動信号の波形を整形する駆動波形整形部と、をそなえたことを特徴とする、光スイッチ装置。

【0155】

(付記16)

該光ゲートスイッチは複数個が縦続して接続されたことを特徴とする、付記15記載の光スイッチ装置。

(付記17)

該モニタ部は、前記縦続して接続される該複数個の光ゲートスイッチのうちの最下流の光ゲートスイッチの出力端の箇所に設置された受光素子をそなえ、該受光素子の出力から前記光波形をモニタすることを特徴とする、付記16記載の光スイッチ装置。

【0156】

(付記18)

該駆動波形整形部は、

前記縦続して接続される該複数個の光ゲートスイッチに対応してそなえられ、前記対応する光ゲートスイッチへの前記駆動信号の波形を、制御信号に基づき整形する複数個の駆動回路部と、

該モニタ部でのモニタ結果に基づき前記制御信号を、該複数の駆動回路部のうちの該一のゲートスイッチに対応する駆動回路部に出力する制御部と、をそなえたことを特徴とする、付記16記載の波形制御装置。

【0157】

(付記19)

付記1記載の波形制御装置において前記整形された波形を有する駆動信号によって駆動されることを特徴とする、応答素子。

(付記20)

駆動信号に応答して入力光の導通/遮断を切り換える光ゲートスイッチを複数個が縦続して接続された光スイッチ装置の制御方法であって、

前記縦続して接続される該複数個の光ゲートスイッチのうちの一の光ゲートスイッチに対して前記駆動信号を供給するとともに、

前記複数個の光ゲートスイッチのうち最下流の光ゲートスイッチの出力端の箇所に設置された受光素子を用いて、前記一の光ゲートスイッチの一つから出力される光波形をモニタし、

該モニタ部でのモニタ結果に基づいて、当該最下流の光ゲートスイッチへの前記駆動信号の波形を整形する一方、

前記駆動信号の波形を整形する対象の光ゲートスイッチは、前記縦続して接続される複数個の光ゲートスイッチのうちの最下流の光ゲートスイッチから、上流側の光ゲートスイッチに順次変更することを特徴とする、光スイッチ装置の制御方法。

【図面の簡単な説明】

【0158】

【図1】光パケットスイッチの一例を示す図である。

【図2】第1実施形態を示す図である。

【図3】(a)〜(c)はいずれも第1実施形態の高調波成分抽出部を示す図である。

【図4】第1実施形態の高調波成分抽出部の作用機能を説明するための図である。

【図5】第1実施形態の高調波成分抽出部の作用機能を説明するための図である。

【図6】ゲートスイッチ駆動回路の一例を示す図である。

【図7】(a)〜(c)は可変容量素子の容量の大きさに応じた、駆動パルス信号および光パルスの立ち上がり波形の一例を示す図である。

【図8】(a)〜(c)は、可変容量素子への制御電圧信号の値に応じた、偶数次高調波成分の信号波形、および、光パルスの波形の例である。

【図9】ゲートスイッチ駆動回路の一例を示す図である。

【図10】第2実施形態を示す図である。

【図11】第2実施形態の動作例を説明するためのフローチャートである。

【図12】第2実施形態の演算制御回路の作用機能を説明するための図である。

【図13】第3実施形態を示す図である。

【図14】第3実施形態の作用機能を説明するための図である。

【図15】第3実施形態の動作例を説明するためのフローチャートである。

【図16】第1〜第3実施形態の適用例を説明するための図である。

【図17】第1〜第3実施形態の適用例を説明するための図である。

【図18】他の実施形態を示す図である。

【符号の説明】

【0159】

1,1A,1B 波形制御装置

2 SOA(応答素子)

3,3A,3B,203 矩形度識別回路(モニタ部)

3a,3a′ 高調波成分抽出部

3b 平均パワー検出回路

3c A/Dコンバータ

3d 受光部

3e 高速A/Dコンバータ

3f AC結合部

3g レベル調整部

3h エッジ検出回路

3i ピークホールド回路

3j サンプルホールド回路

3m,3n A/Dコンバータ

4,4A,4B,204 演算制御回路(駆動波形整形部)

5,205 駆動電圧制御回路(駆動波形整形部)

5a D/Aコンバータ

5b 矩形度整形回路

5c,5c′ ゲートスイッチ駆動回路

7 光カプラ

10,10A,10B 応答素子モジュール

11,11′ 分岐部

12,12′ 遅延部

13,14 受光部

15 合成部

16,18 回路部

16a 可変容量素子

16b,16c,18a,18b 抵抗

17 ドライバアンプ

18c インダクタ素子

100,200,300 光パケットスイッチ

101 1:8カプラ

102 8:8光ゲートスイッチ部

102a,104 SOA

103 8:1カプラ

207a−1〜207a−8,207b 光カプラ

310−1 分配部

311,313 EDFA

312,314 1:16カプラ

320−1 合流部

321,323,325,327 SOA

322,326 8:1カプラ

324 4:1カプラ

【技術分野】

【0001】

本案件は、波形制御装置,応答素子モジュール,光スイッチ装置,応答素子および光スイッチ装置の制御方法に関する。

【背景技術】

【0002】

光信号処理システムや光通信システムに適用される素子等においては、矩形波形状を有する光パルスを、取り扱われる光波形の理想とするものは少なくない。

たとえば、光半導体増幅器(Semiconductor Optical Amplifier:SOA)のような光素子は、時間軸上においてオンオフが切り替わる電気信号(駆動信号)によって駆動されて、入力光の導通/遮断を切り換えるゲートスイッチとして適用される。駆動信号の導通/遮断の切り換わりによって、SOAからの出力光は時間軸上でオンオフが切り替わる光パルスとなる。SOAから出力される光パルスとしては、真正の(理想的な)矩形波形状に近いことがしばしば求められる。

【0003】

2値のディジタル電気信号を扱う電子機器においても、導通する信号が2値の矩形波信号であることを理想とする内部素子や配線等を含むものがある。例えば、メモリやバッファ、変調機、高速入出力インタフェース機器などの伝送線路機器などがある。このような電子機器においても、信号波形について最適な矩形形状を有するよう簡易に整形できるようにすることがしばしば求められている。

【特許文献1】特開平9−36471号公報

【特許文献2】特開2000−341728号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

そこで、本件は、簡易な波形整形によって目標の矩形度を有するパルスを生成することを目的の一つとするものである。

なお、前記目的に限らず、後述する発明を実施するための最良の形態にかかる各構成又は作用により導かれる効果であって、従来の技術によっては得られない効果を奏することも本案件の他の目的として位置づけることができる。

【課題を解決するための手段】

【0005】

たとえば、以下の手段を用いる。

供給される駆動信号に応答素子が応答して得られる出力パルスの波形をモニタするモニタ部と、該モニタ部でのモニタ結果に基づいて、前記駆動信号の波形を整形する駆動波形整形部と、をそなえた波形制御装置を用いることができる。

【発明の効果】

【0006】

開示の技術によれば、簡易な構成によって目標の矩形度を有するパルスを生成することができる。

【発明を実施するための最良の形態】

【0007】

以下、図面を参照して実施の形態を説明する。但し、以下に説明する実施形態は、あくまでも例示であり、以下に明示しない種々の変形や技術の適用を排除する意図は無い。即ち、本実施形態は、その趣旨に逸脱しない範囲において種々変形して実施することができる。

〔A〕第1実施形態

現在、波長多重(Wavelength Division Multiplexing:WDM)伝送システムが幹線系光通信ネットワークシステムの主流である。しかしながら、今後は、ネットワーク利用効率の向上の観点から、光信号のまま経路を切り替える光パケット・バーストスイッチングネットワークシステムへの進展が期待されている。

【0008】

光パケット・バーストスイッチングネットワークシステムにおいては、回線使用効率を向上させるために、光信号をパケットに分割し、そのパケット単位で光信号のまま交換・方路切り替えの処理を行なう機能が必要となることが見込まれている。

このような機能を担う装置においては、上述のパケット単位での交換や方路切り替えを行なうにあたって、少なくともミリ秒次元よりも小さい時間次元、例えばマイクロ秒〜ナノ秒次元での切り替え処理を行なうことができるようにすることが期待されている。

【0009】

一例として、光半導体増幅器(Semiconductor Optical Amplifier:SOA)のような素子をゲートスイッチとして利用し、それをマトリクス状に複数配置する分配・合流型の光パケットスイッチシステムがある。分配・合流型の光パケットスイッチシステムでは、ポート数Nに対し、N×N以上のスイッチング素子が必要となる。

図1に、8個の入力ポート(♯1〜♯8)および8個の出力ポート(♯1〜♯8)を有する分配・合流ゲートスイッチ型の光パケットスイッチ(光スイッチ装置、インターコネクトシステム)100の例を示す。8ポートから入力される光パケット信号は、入力ポートごとにそなえられた1:8カプラ101でそれぞれ8分配される。8:8光ゲートスイッチ部102は出力先の出力ポートごとにそなえられる。

【0010】

一つの光ゲートスイッチ部102は、8個の入力ポート♯1〜♯8に対応した1:8カプラ101からの分配経路を1本ずつ接続して、それぞれの分配経路ごとに、光ゲートスイッチ102aがそなえられる。光ゲートスイッチ102aは、駆動回路105からの駆動信号に基づいて、入力される光パケット信号についての通過/遮断が制御されるもので、例えばSOAを用いることができるが、電界吸収型光変調器などの他の光素子を用いることもできる。なお、光パケットスイッチ(インターコネクトシステム)100は筐体に収容されてもよい。

【0011】

駆動回路105は、光ゲートスイッチ102aごとにそなえられて、トリガ信号出力部106から入力されるトリガ信号に応じた駆動信号を光ゲートスイッチ102aに供給する。尚、図1中においては、出力ポート♯8に対応する光ゲートスイッチ部102における光ゲートスイッチ102aに対応した駆動回路105に着目して図示している。

トリガ信号出力部106は、各光ゲートスイッチ102aに対する導通/遮断の制御タイミングに応じたトリガ信号を対応する駆動回路105に供給する。又、トリガ信号出力部106から出力される各駆動回路105へのトリガ信号の出力タイミングは同期手段107によって制御することができる。

【0012】

同期部107は、光パケット信号を導通させる制御を行なう対象となる光ゲートスイッチ102aにその光パケット信号が入力されるタイミングおよび通過するタイミングと、当該光ゲートスイッチ102aの導通/遮断の制御を同期させる。例えば、トリガ信号出力部106から出力される光ゲートスイッチ102aの導通/遮断制御のためのトリガ信号が、光パケット信号の入力および通過のタイミングにほぼ同期するように、トリガ信号出力部106を制御する。

【0013】

なお、同期部107は、例えば、光パケットスイッチ100が搭載される箇所に応じた態様でトリガ信号出力部106を制御することができる。

たとえば、ネットワークの中継箇所に適用される場合には、入出力ポート♯1〜♯8にはそれぞれ光伝送路が接続される。そして、各入力ポート♯1〜♯8への光パケット信号の入力を1:8カプラ101よりも上流側箇所で検出する。そして、入力を検出した光パケット信号が導かれるべき出力ポート♯1〜♯8に応じて定められる光ゲートスイッチ102aが、当該光パケット信号が該当の光ゲートスイッチ102aに到達する以前に導通状態となるようにトリガ信号の出力を制御する。又、当該光パケット信号が通過した後は遮断されるようにトリガ信号の出力を制御する。

【0014】

または、光パケット信号を送信する送信器箇所に適用される場合には、各入力ポート♯1〜8には、光パケット信号を生成する光パケット信号源等が接続される。この場合には、該当の光パケット信号源で光パケット信号を生成するためのデータ信号の供給タイミングに関する情報を受け取り、導出先とすべき光ゲートスイッチ102aに対するトリガ信号が当該パケット信号の入力タイミングにほぼ同期させる制御を行なう。

【0015】

なお、光パケットスイッチ100が搭載される箇所がいずれとなる場合においても、光パケット信号の入力を検出する箇所、または光パケット信号が生成される光パケット信号源の搭載箇所から、1:8光カプラ101に至る光経路上に適宜遅延手段を介装できる。これにより、光ゲートスイッチ102aの制御が、当該光ゲートスイッチ102aへの光パケット信号の入力以前に完了させられるようにすることができる。

【0016】

これにより、光ゲートスイッチ102aは、光パケット信号が通過する期間のみオンにし、それ以外はオフにして、クロストークや雑音光の漏出を防ぐ。経路のスイッチングは、例えばスイッチング前の経路に対応する光ゲートスイッチ102aをオフ(遮断制御)するとともに、スイッチング後の経路に対応する光ゲートスイッチ102aをオンすることで行なうことができる。

【0017】

このように、所望の入出力ポート間の光ゲートスイッチ102aおよび対応の下流側SOA104をオン(通過制御)すると、当該入出力ポート間において光パケット信号の経路を設定できる。例えば、入力ポート♯iと出力ポート♯jとの間で光パケット信号を設定する場合には、図中i−jのゲート出力を有するSOA102aとともに、当該SOA102aの下流側のSOA104を通過(オン)する制御を行なう。

【0018】

すなわち、オンとされた光ゲートスイッチ102aを通過した光パケット信号は出力ポートごとに8:1カプラ103で合波され、出力される。尚、SOA104は、8:1カプラ103での光損失を補うために、例えば8:1カプラ103の出力にそなえられたものであるが、適宜省略してもよい。

図1においては、出力ポート毎に損失補償用のSOA104を具備しているため、同一経路上にそなえられる2個のSOA102a,104をほぼ同時または同時にオン又はオフさせる。このとき、オンオフの切り換えに要する時間が短いほど粒度の細かい(パケット長の短い)光パケット信号を処理することが可能となる。更に、オンからオフへの、又はオフからオンへの切り換えが速いほど、光パケット信号間の空き時間(ガードタイム)を短くすることが可能となる。

【0019】

このように、図1に示す光パケットスイッチ100においては、8×8+8=72個のSOA102a,104が用いられている。即ち、ポート数N(=8)とした場合のN×Nよりも多数のスイッチング素子であるSOA102a,104が適用されている。

分配・合流型の光パケットスイッチ100のように、ナノ秒オーダのスイッチングが必要な場合、光ゲートスイッチングを担う複数のSOA102a,104に対して駆動信号を供給するための配線長さがミリ単位で相違すると、スイッチング時間を遅くする等、応答特性に影響を与える。

【0020】

すなわち、SOA102a,104自身が持つキャパシタンス成分(寄生容量)や抵抗成分、駆動回路とSOAとの間の配線のインダクタンスL成分等によって決定される時定数の影響によって、SOA102a,104のスイッチング応答が遅くなることがある。具体的には、SOAに対する光導通/遮断のための駆動波形を理想的な矩形波で入力した場合でも、応答信号である出力光の波形は鈍ってしまい、スイッチング応答が遅くなることがある。

【0021】

各々のSOA102a,104に対し駆動信号を出力する駆動回路が対応するSOA102a,104の直近に配置され、その配線長は互いに等距離となるよう配置することで、SOA102a,104ごとの応答特性を画一的に改善することが期待できる。しかし、図1に例示した場合のように、SOA102a,104とそれらの駆動回路とが数多く存在する場合、各々の配線長を均一な距離に保つことは容易ではない。このため、SOA102a,104ごとの応答特性は、各々の配線長が相違し、寄生容量に個体差を有するため、それぞれ実質的に相違しているといえる。

【0022】

プリエンファシス等の技術は、回路部やCR回路等を用いて、駆動信号における立ち上がりを持ち上げる(立ち上がり応答の高速化)ことで、応答信号の矩形波の立ち上がりの鈍りを鋭くするための技術として知られている。このようなプリエンファシス技術を用いて、上述のSOA102a,104の応答特性を速めることも想定できるが、SOA102a,104の特性を改善させるためには、与えるべきプリエンファシスの量について、それぞれ個別の調整が必要になる。例示した光パケットスイッチ100においては、72個ものスイッチ素子であるSOA102a,104に対して個別調整が必要になる。

【0023】

プリエンファシスの量を調整するには、駆動波形の矩形波エッジを立ち上げる機能を有する回路をなす素子特性について調整する必要がある。又、個別に駆動波形の調整を行なったとしても、スイッチ素子であるSOAの特性が経年変化したり、駆動回路基板の吸湿等によって特性変化を起こしたりすることなども想定すると、その後の調整作業は不可欠になる。メインテナンスや製造プロセスの効率化のためにもこのような個別調整の負担はなるべく軽減させることが望ましい。

【0024】

そこで、第1実施形態においては、図2に示す波形制御装置1および応答素子モジュール10を提案する。波形制御装置1においては、応答素子であるSOA2の駆動信号に対する応答出力をなす光パルスの矩形度をモニタし、モニタ結果の矩形度に応じて駆動信号の駆動波形を制御して、光パルスの矩形度を自在に制御する。

すなわち、図2に示す波形制御装置1を上述の図1に示す各々のSOA102a,104の駆動のために適用することで、各々のSOA102a,104の応答出力をなす光パルスの矩形度が目標形状を有するように整形できる。

【0025】

なお、SOA2を図1に示す光パケットスイッチ100の要素(符号102a,104)として適用する場合には、矩形度の制御のためにはSOA2から出力される光パルスの周期が波形制御装置1において既知であることが必要である。このため、光パケットスイッチ100の運用開始前(即ちSOA2への入力光が非入力の状態)において、波形制御装置1による光パルスの矩形度についての整形を行なうことができる。

【0026】

また、応答素子モジュール10は、上述の波形制御装置1および応答素子としての少なくとも1つのSOA2を含む。図2に示す波形制御装置1は、実施形態の一例(以降、一例と呼ぶ。)として矩形度識別回路3と、演算制御回路4と、駆動電圧制御回路5と、をそなえる。演算制御回路4は、上述の図1に示すトリガ信号出力部106の一例となる。即ち、運用にあるSOA2(図1の102a,104参照)に入力光である光パケットが入力されるタイミングに同期して、当該SOA2に入力光を導通させるトリガ信号を、以下のような矩形度の整形が行なわれた駆動電圧制御回路5を介して供給することができる。

【0027】

波形制御装置1においては、出力光パルスの矩形度の整形を行なう場合、非運用時のSOA2について、SOA2を一定周期のトリガ信号で駆動することにより得られる自然放出光(ASE光)を用いる。即ち、入力光が入力されていないSOA2に、演算制御回路4で生成される一定のオンオフ周期の駆動信号が駆動電圧制御回路5を介して供給されると、このSOA2から応答出力として自然放出光(ASE光)を出力する。

【0028】

このとき、ASE光は、駆動信号のオンオフに応じた光パルスの強度変動を有する。即ち、駆動信号をオンさせるとASE光が出力されるので光パルスのオンに該当する一方、駆動信号をオフさせるとASE光の出力光レベルが0となるので光パルスのオフに該当する。

矩形度識別回路3は、後述の駆動電圧制御回路5から供給される駆動信号に応答素子であるSOA2が応答して得られる出力パルスの波形をモニタするモニタ部の一例である。矩形度識別回路3は、SOA2からの出力光パルスの波形の矩形度を、例えば、出力光パルスの波形が真正の(理想的な)矩形形状となっている度合いを数値化することにより識別する。矩形度識別回路3は、一例として、高調波成分抽出部3a,平均パワー検出回路3bおよびアナログ/ディジタル(A/D)コンバータ3cをそなえる。

【0029】

高調波成分抽出部3aは、SOA2からの出力パルス(出力光パルス)に含まれる、駆動信号をなすトリガパルスの周波数(既知)についての偶数次又は奇数次の高調波成分を抽出する。高周波成分抽出部3aをトリガパルスの偶数次の高調波成分を抽出するものとする場合は、一例として、図3(a)に示すように、分岐部11,遅延部12,受光部13,14および合成部15をそなえる。

【0030】

分岐部11は、例えば3dBカプラ等が適用され、SOA2から出力される出力光パルスの一部を、光カプラ等を含む光分岐部7を通じて受けて、受けた出力光パルスについて2分岐する。そして、分岐部11で分岐された一方は受光部13に接続される一方、他方は遅延部12を介して受光部14に接続される。

遅延部12は、例えば分岐部11と受光部14との間に介装される遅延線(光ファイバ)が適用され、受光部14に入力される光に、分岐部11から受光部13に入力される光よりも所定時間だけ遅延させる。この遅延時間としては、例えばSOA2からの出力パルスのパルス周期(又は駆動電圧制御回路5からSOA2に出力される駆動信号をなすパルス信号の周期)の半周期相当の時間である。

【0031】

受光部13,14はともに入力される光について電気信号に変換(光電変換)するもので、例えばフォトダイオード(PD)が適用される。即ち、受光部13,14から出力される電気信号は、SOA2から出力される出力光パルスに相当する振幅変化を有する電気パルス信号である。但し、遅延部12で遅延された光を受光する受光部14からの電気パルス信号は、受光部13からの電気パルス信号に対してそのパルス周期の半周期時間が遅延されている。

【0032】

合成部15は、上述の受光部13,14から出力される電気パルス信号を合成、即ち重ねあわせる。合成部15において、パルス周期の半周期時間分の相対的な遅延時間差を有する電気パルス信号を重ね合わせることで、パルス周期に半波長ずれた奇数次高調波成分については互いにキャンセルされる。その結果、合成部15での合成後の信号には偶数次高調波成分のみが残存することになる。これにより、高調波成分抽出部3aとして、偶数次の高調波成分を出力することができる。

【0033】

ところで、式(1)は、非正弦波交流の時間tでの瞬時値v(t)のフーリエ級数式の一例である。そして、理想的な矩形波v(t)は、一例として、式(1)から式(2)のフーリエ級数展開式のように導出することができる。ここで、式(1),(2)において、Vは振幅、ωは角速度であり、周期をTとすると、ω=2π/Tである。尚、式(2)に示す矩形波v(t)は、−T/4<t<T/4においてv(t)=Vであり、−T/2<t<−T/4,T/4<t<T/2においてv(t)=−Vである。

【0034】

【数1】

【0035】

理想的な矩形波は、パルス信号をなすパルス周期の奇数次の高調波成分の重ね合わせを含む。即ち、この式(2)に示すωtの成分は1次波であり、3ωt,5ωt,7ωtの成分はそれぞれ3,5,7次高調波である。この式(2)に示すように、理想的な矩形波においては、式(1)における偶数次高調波成分(n=2,4,…の成分)は、0になる。

【0036】

したがって、上述の高調波成分抽出部3aにおいて抽出される、偶数次の高調波成分(例えば、式(1)におけるフーリエ級数展開式での2ωt,4ωtの成分)は、パルス信号波形を理想的な矩形波形状から実質的に変形させる要素であるといえる。

図4は、光分岐部7から矩形度識別回路3に入力されるパルス信号に含まれるスペクトラム特性(A)の一例とともに、上述の高調波成分抽出部3aとしての透過特性(B)の一例を示す図である。この図4に例示するように、矩形度識別回路3に入力されるパルス信号には、上述の式(1)で例示されるような奇数次高調波成分A1,A3,A5,…とともに、理想的な矩形波形状を変形させる成分である偶数次高調波成分A2,A4,A6,…が含まれる。尚、図4中、「A」に付される数字は、高調波成分の次数を示す。又、図4中、横軸は周波数であり、縦軸は振幅(瞬時値電圧)を表す。

【0037】

高調波成分抽出部3aは、例えば、図4中、網掛け部Bで示すような透過周波数帯を有する。換言すれば、透過周波数帯(B)と遮断周波数帯とが交互に配列されるコムフィルタ(comb filter)としての特性を有することができる。これにより、上述の偶数次の高調波成分A2,A4,A6,…を透過させる一方、奇数次の高調波成分A1,A3,A5,…については遮断させることができる。

【0038】

図5(a)〜図5(d)は、例えば式(1)における偶数次高調波成分の係数を変化させることで、パルス周期の奇数次高調波成分に対し偶数次高調波成分が含まれる割合を変化させた場合のパルス信号波形のシミュレーション結果の一例である。

ここで、図5(c)は、1〜199次までの高調波成分のうちの、偶数次高調波成分を除く奇数次高調波成分を重ね合わせた場合のシミュレーション結果の一例である。また、図5(a)は、1〜199次までの高調波成分のうちの奇数次高調波成分の重ね合わせと、第1割合の偶数次高調波成分と、を同位相で重ね合わせた場合のシミュレーション結果の一例である。又、図5(b)は奇数次高調波成分の重ね合わせに、第1割合よりも少ない第2割合の偶数次高調波成分を同位相で重ね合わせた場合のシミュレーション結果の一例である。

【0039】

これに対し、図5(d)は、上述の第1割合の偶数次高調波成分を、奇数次高調波成分とは逆位相で、奇数次高調波成分とともに重ね合わせた場合のシミュレーション結果の一例である。又、図5(e)は上述の第2割合の偶数次高調波成分を、奇数次高調波成分とは逆位相で、奇数次高調波成分とともに重ね合わせた場合のシミュレーション結果の一例である。

【0040】

すなわち、パルス信号をなすパルス周期の奇数次の高調波成分の重ね合わせの場合には、図5(c)のシミュレーション結果に示すように、ほぼ理想的な矩形波の形状になる。一方、図5(a),図5(b),図5(d),図5(e)に示すように、偶数次の高調波成分が含まれる割合が増えるに従って、パルス信号波形が理想的な矩形波形状から変形する度合いが大きくなる。

【0041】

矩形度識別回路3の要素である平均パワー検出回路3bは、高調波成分抽出部3aにて抽出された偶数次又は奇数次の高調波成分のパワーをモニタするパワーモニタ部の一例である。第1実施形態における平均パワー検出回路3bにおいては、高調波成分抽出部3aにおいて抽出した偶数次高調波成分のパワー(平均パワー)を検出する。A/Dコンバータ3cにおいては、平均パワー検出回路3bにて検出された平均パワーの値についてアナログ信号からディジタル信号に変換して、演算制御回路4に出力する。

【0042】

これにより、矩形度識別回路3においては、出力光パルスにおける理想的な矩形波形状から変形される要素である偶数次の高調波成分の大きさを、モニタ結果として出力している。この場合には、出力光パルスに含まれる偶数次の高調波成分のパワーが最小となっている場合には、出力光パルスの波形として、ほぼ理想的な矩形波形状を得ることができる。

【0043】

なお、前述の図3(a)においては、分岐部11での光分岐の後段において分岐光をそれぞれ光電変換する受光部13,14がそなえられている。他の例としては、例えば図3(b)に示すように、分岐部11としての機能の前段に受光部19をそなえるようにしてもよい。この場合においては、分岐部11′としては受光部19からの電気パルス信号について2分岐し、遅延部12′においては、分岐部11′からの電気パルス信号について上述の場合と同等の遅延時間差を与える。これにより、合成部15において、図3(a)の場合と同様の偶数次の高調波成分を出力することができる。

【0044】

また、図3(a),図3(b)のごとき遅延時間差を有するパルス信号を合成部15で重ね合わせる場合において、入力される各パルス信号のレベルを整合させるべく合成部15の入力側にアンプ等を適宜介装するようにしてもよい。

さらに、高調波成分抽出部3aとしては、奇数次高調波成分を抽出し、矩形度識別回路3においてはそのパワー情報(ディジタル信号)をモニタ結果として出力するようにしてもよい。この場合には、高調波成分抽出部3aは、前述の図4に示す奇数次高調波成分A1,A3,A5,…を通過させる一方、偶数次の高調波成分A2,A4,…については遮断するコムフィルタとしての特性を有する。奇数次高調波成分は、出力パルスにおける理想的な矩形度形状を形成する要素である。従って、平均パワー検出回路3bにおいて検出する奇数次高調波成分のパワーが最大となれば、出力光パルスの波形として、ほぼ理想的な矩形波形状を得ることができる。

【0045】

図3(c)は、トリガパルスの奇数次の高調波成分を抽出する高調波成分抽出部3aの一例である。この図3(c)に示す高調波成分抽出部3aは、分岐部11,遅延部12,受光部13,14,合成部15,受光部16,位相調整回路17および減算部18をそなえる。

分岐部11は、前述の図3(a)に示すものと異なり、光分岐部7を通じて受けた出力光パルスについてパワーを等分に3分岐し、それぞれ、3つの受光部13,14,16に導く。遅延部12,受光部13,14および合成部15は、前述の図3(a)に示すものと基本的に同様である。即ち、合成部15からは、出力光パルスの偶数次の高調波成分を出力することができる。

【0046】

また、受光部16は、入力される光、即ち、分岐部11で3等分されたうちの一の出力光パルスについて電気信号に変換(光電変換)し、減算部18に出力する。位相調整回路17は、合成部15からの偶数次の高調波成分の信号について位相調整を行ない、減算部18に入力される受光部16からの電気パルス信号に含まれる偶数次の高調波成分と位相を整合させる。

【0047】

さらに、減算部18は、受光部16からの電気パルス信号から、合成部15からの偶数次の高調波成分を減算し、減算した残りの成分である奇数次高調波成分を抽出する。これにより、図3(c)に示す高調波成分抽出部3aは、トリガパルスの奇数次の高調波成分を抽出することができる。

なお、上述の図3(c)に示す分岐部11において3分岐されるものにおいては、4分岐される分岐素子における3本の分岐方路を適用することとしてもよい。又、受光部13,14および16から出力される電気信号の振幅を調整するアンプや減衰器を適宜用いることで、受光部13,14,16から出力される各電気信号の振幅を整合させることもできる。

【0048】

また、演算制御回路4および駆動電圧制御回路5は、互いに協働することで、モニタ部3でのモニタ結果に基づいて、駆動信号の波形を整形する駆動波形整形部の一例に相当する。即ち、駆動波形整形部4,5として、矩形度識別回路3でモニタされたパワーが所定レベル又は所定範囲となるように駆動パルス信号の波形を整形している。

たとえば、平均パワー検出回路3bで 偶数次の高調波成分のパワーをモニタ結果として出力している場合には、モニタされたパワーが最小となることを制御目標に置いて駆動パルス信号の波形を整形する。又、平均パワー検出回路3bで奇数次の高調波成分のパワーをモニタ結果として出力している場合には、モニタされたパワーが最大となることを制御目標に置いて駆動パルス信号の波形を整形する。

【0049】

ここで、演算制御回路4は、例えばディジタル演算素子からなり、駆動電圧制御回路5の要素であるゲートスイッチ駆動回路5cに対し、ゲートオンオフのためのトリガ信号を供給する。又、演算制御回路4は、矩形度識別回路3からディジタル信号として入力されたモニタ結果をもとに、SOA2での光パルスの波形を制御するための制御信号をディジタル信号として出力する。

【0050】

駆動電圧制御回路5は、演算制御回路4からのゲートオンオフのためのパルス信号に基づいて駆動パルス信号を生成し、SOA2に供給する。このとき、駆動電圧制御回路5においては、SOA2で出力する光パルス波形を制御するための制御信号をもとに、出力する駆動パルス信号の波形を整形している。駆動電圧制御回路5は、一例として、図2に示すD/Aコンバータ5a,矩形度整形回路5bおよびゲートスイッチ駆動回路5cをそなえる。

【0051】

D/Aコンバータ5aは、演算制御回路4からディジタル信号として入力される制御信号をアナログ信号に変換する。矩形度整形回路5bは、D/Aコンバータ5aからの制御信号をもとに、ゲートスイッチ駆動回路5cの要素である可変容量素子16a(図6参照)への制御信号を生成する。

ゲートスイッチ駆動回路5cは、演算制御回路4からのゲートオンオフのためのトリガ信号に基づいて駆動パルス信号(駆動信号)を生成するが、ここで生成する駆動パルス信号の波形については矩形度整形回路5bからの制御信号をもとに整形されている。換言すれば、ゲートスイッチ駆動回路5cは、応答素子であるSOA2への駆動信号の波形を制御信号に基づき整形する駆動回路部の一例であり、又、演算制御回路4は、モニタ部3でのモニタ結果に基づき(矩形度整形回路5bを介して)制御信号を駆動回路部5cに出力する制御部の一例である。

【0052】

図6はゲートスイッチ駆動回路5cの一例である。図6に示すスイッチ駆動回路5cにおいては、可変容量素子16aおよび抵抗16b,16cを含む回路部16と、ドライバアンプ(Driver AMP)17とをそなえる。ここでは、演算制御回路4からのトリガ信号は、回路部16を介してドライバアンプ17で増幅され、駆動パルス信号としてSOA2へ出力される。

【0053】

回路部16をなす可変容量素子16aは、矩形度整形回路5bからの制御信号の値により容量が可変される素子である。バリキャップは可変容量素子16aの一例である。この場合、演算制御回路4からの制御信号に応じて、バリキャップ16aへの制御信号として印加すべき電圧(バリキャップ電圧)を可変するバリキャップ電圧制御回路は、矩形度整形回路5bの一例である。

【0054】

矩形度整形回路5bからの制御信号を通じて、可変容量素子16aの容量が可変されると、回路部16の応答時定数が可変するので、ゲートスイッチ駆動回路5cからの駆動パルス信号の立ち上がりおよび立ち下がりの波形が整形される。可変容量素子16aの容量C12、抵抗16b,16cの抵抗値をそれぞれ固定値R21,R23とすると、回路部16の応答時定数τ1は式(3)のようになる。従って、容量C12を大きくすると、応答時定数τ1は大きくなり、容量C12を小さくすると、応答時定数τ1は小さくなる。

【0055】

【数2】

【0056】

バリキャップとしての可変容量素子16aにおいては、例えば、矩形度整形回路5bからの制御電圧信号が小さくなると容量C12が大きくなり、矩形度整形回路5bからの制御電圧信号が大きくなると容量C12が小さくなる関係とすることができる。これにより、ゲートスイッチ駆動回路5cをなす回路部16の応答時定数は、演算制御回路4からの制御信号により生成される制御電圧信号を通じて、可変させることができる。換言すれば、演算制御回路4は、可変容量素子16aの容量を制御することを通じて、回路部16の応答時定数を制御し、これにより、ゲートスイッチ駆動回路5cから出力される駆動パルス信号の波形を制御することができる。

【0057】

図7(a)〜図7(c)は可変容量素子16aの容量の大きさ(又は制御電圧信号(印加電圧)の大きさ)に応じた、駆動パルス信号および光パルスの立ち上がり波形の一例を示す図である。図7の(a)は、制御電圧信号の値を比較的小さくして容量C12を比較的大きくした場合であり、図7の(c)は、制御電圧信号を比較的大きくして容量C12を比較的小さくした場合であり、図7の(b)は、制御電圧信号および容量C12を上述の図7(b)および図7(c)のときの間の値とした場合である。

【0058】

すなわち、図7(a)に示すように、容量C12を大きくすると応答時定数が大きくなる。このため、ゲートスイッチ駆動回路5cからの駆動パルス信号A1は、鋭く立ち上がるとともに、その過渡的な立ち上がり幅W1は大きくなり、且つ一定値に落ち着くまでの時間も比較的長くなる。更に、SOA2は、このように立ち上がり幅が大きくなった駆動パルス信号A1により駆動されるので、出力される光パルスA2の立ち上がり幅も大きくなる。

【0059】

これに対し、図7(c)に示すように、容量C12を小さくすると応答時定数が小さくなる。このため、ゲートスイッチ駆動回路5cからの駆動パルス信号C1は、鈍く立ち上がるとともに、その過渡的な立ち上がり幅W3は小さくなり、且つ一定値に落ち着くまでの時間は比較的短くなる。更に、SOA2は、このように立ち上がりが鈍くなった駆動パルス信号C1により駆動されるので、出力される光パルスC2の立ち上がりも緩くなる。

【0060】

図7(b)は、制御電圧信号および容量C12を上述の図7(a)および図7(c)のときの間の値としている。この場合には、駆動パルス信号B1の立ち上がり特性は、上述のA1,C1の立ち上がり特性の間の鋭さを有し、その過渡的な立ち上がり幅W2はW1,W3の間の値となり、一定値に落ち着くまでの時間も図7(a)および図7(c)のときの間の値となる。尚、この駆動パルス信号B1により駆動されるSOA2からの光パルスは、真正の(理想的な)矩形波形状に近い立ち上がりが得られている。

【0061】

演算制御回路4においては、矩形度識別回路3からの光パルス波形のモニタ結果に基づいて、SOA2から出力される光パルス波形を、矩形度整形回路5bおよびゲートスイッチ駆動回路5cを通じたフィードバック制御により制御している。図8(a)〜図8(c)は、上述の可変容量素子16aへの制御電圧信号(又はそのときの容量C12)の値に応じた、高調波成分抽出部3aで抽出される偶数次高調波成分の信号波形、および、SOA2から出力される光パルスの波形の例である。

【0062】

図8(a)に例示するように、光パルスa1が急峻に立ち上がる場合には、高調波成分抽出部3aで抽出する偶数次高調波成分の信号b1についても比較的大きな振幅となる箇所を含む。又、図8(c)に例示するように、光パルスa3の立ち上がりが鈍っている場合にも、高調波成分抽出部3aで抽出する偶数次高調波成分の信号b3についても比較的大きな振幅となる箇所を含む。このため、図8(a),図8(c)の場合の双方とも、パワー検出回路3bで検出する偶数次高調波成分パワーは比較的大きくなる。

【0063】

これに対し、図8(b)に例示するように、光パルスa2が真正の(理想的な)矩形波形状に近い波形を有している場合には、高調波成分抽出部3aで抽出する偶数次高調波成分b2は、比較的振幅が小さくなる。この場合にパワー検出回路3bで検出する偶数次高調波成分のパワーは、上述の図8(a),図8(c)の場合よりも小さくなる。

したがって、演算制御回路4においては、一例として矩形度識別回路3からのモニタ結果である偶数次の高調波成分のパワーが最小又は一定誤差を含む最小範囲に収まるように、制御信号を矩形度整形回路5bに出力する。これにより、出力光パルスの波形を例えば図7(b)の波形B2を保つようにすることができる。前述したように、出力光パルスに含まれる偶数次の高調波成分が最小となる場合には、光パルスの波形としては、奇数次の高調波成分の重ね合わせである理想的な矩形波形状を、ほぼ有するようになるからである。

【0064】

上述したように、演算制御回路4における、矩形度識別回路3からの偶数次高調波成分パワーに基づく矩形度整形回路5bを介した可変容量素子16aの容量の制御により、SOA2から出力される光パルスの波形が所定の波形を保つようにしている。尚、演算制御回路4においては、所定の波形が保たれるようになったときの制御信号(例えば矩形度整形回路5bへの制御信号)の制御量を記憶しておくことができる。これにより、SOA2をゲートスイッチとして実運用する際にはフィードバック制御を行なわずとも出力光波形を所期の波形にすることができる。

【0065】

また、制御目標となる光パルスの波形については、例示したように真正の矩形波形状としたり、又は、図7(a)のA2のような立ち上がり幅の大きい矩形度の波形としたり、図7(c)のC2のような立ち上がりの鈍った矩形度の波形としたりすることもできる。

図9は図6に示すゲートスイッチ駆動回路5cの変形例であるゲートスイッチ駆動回路5c′を示す図である。ゲートスイッチ駆動回路5c′は、応答素子であるSOA2への駆動信号の波形を、制御信号に基づき整形する駆動回路部の他の例であり、回路部18とともに図6の場合と同様のドライバアンプ17をそなえている。回路部18は、抵抗18a,18bとともに、矩形度整形回路5bからの制御信号によりインダクタンスを可変としうるインダクタ素子18cをそなえる。

【0066】

矩形度整形回路5bからの制御信号を通じて、可変インダクタ素子18cのインダクタンスが可変されると、回路部18の応答時定数が可変する。このため、ゲートスイッチ駆動回路5cから出力される駆動パルス信号の立ち上がりおよび立ち下がりの波形が整形される。可変インダクタ素子18cのインダクタンスをL1、抵抗18a,18bの抵抗値をそれぞれ固定値R11,R13とすると、回路部18の応答時定数τ2は式(4)のようになる。従って、インダクタンスL1を大きくすると、応答時定数τ2は大きくなり、インダクタンスL1を小さくすると、応答時定数τ2は小さくなる。

【0067】

【数3】

【0068】

換言すれば、演算制御回路4は、可変インダクタ素子18cのインダクタンスを、矩形度整形回路5bを介して制御することを通じて、回路部18の応答時定数を制御し、ゲートスイッチ駆動回路5cから出力される駆動パルス信号の波形を制御できる。

つぎに、上述したような波形制御装置1又は応答素子モジュール10の動作例について説明する。

【0069】

たとえば、図1に示す光パケットスイッチ100の運用を開始する前段において、光パケットスイッチ100の要素として適用される応答素子としてのSOA102a,104の調整を行なう際に、波形制御装置1を用いる。又は、SOA102a,104として適用されるSOA2を有する応答素子モジュール10において、SOA2への駆動パルス波形の整形を行なう。

【0070】

駆動電圧制御回路5ではSOA2に対して駆動信号を供給することで、SOA2から出力パルスを出力させる。このとき、SOA2への入力光は非入力であり、駆動電圧制御回路5から供給される駆動信号のオンオフにより、出力/非出力が繰り返されるASE光が、SOA2から出力される出力パルスである。尚、駆動信号のオンオフ周期、即ち駆動パルス信号としてのパルス周期は、演算制御回路4からのトリガ信号の周期に由来しているので、演算制御回路5において既知のものである。

【0071】

そして、矩形度識別回路3では、SOA2から出力された出力パルスの波形をモニタし、その矩形度、又は、立ち上がりエッジの先鋭度について識別する。例えば、高調波成分抽出部3aにおいて、SOA2から出力された出力光パルスの、当該パルス周期における偶数次高調波成分について抽出し、パワー検出回路3bで、抽出した偶数次高調波成分のパワーを検出する。

【0072】

演算制御回路4は、検出した偶数次高調波成分のパワーについてA/Dコンバータ3cを介してディジタル信号として受ける。そして、この演算制御回路4と駆動電圧制御回路5とが協働して、受けた偶数次高調波成分のパワーをもとに、当該パワーが目標値(例えば最小又は所定の誤差を含む最小範囲)に一致するまたは近づくように、SOA2への駆動パルス信号の波形を制御する。

【0073】

具体的には、演算制御回路4において、矩形度整形回路5bを介することにより、ゲートスイッチ駆動回路5cをなす回路部16(図6参照)の可変容量素子16aの容量を可変させることで、SOA2への駆動パルス信号の波形を整形させる。又は、ゲートスイッチ駆動回路5c′をなす回路部18(図9参照)の可変インダクタ素子18cの容量を可変させることで、SOA2への駆動パルス信号の立ち上がりエッジの先鋭度を整形させる。

【0074】

SOA2は、上述の駆動パルス信号により駆動されて出力パルスを出力する。このため、演算制御回路4で、矩形度整形回路5bを介して、ゲートスイッチ駆動回路5cから出力される駆動パルス信号の波形を制御することを通じて、SOA2から出力される出力パルスの波形の矩形度を制御することができるようになる。

上述のごとく制御目標となる駆動パルス信号が得られるようになった場合においては、演算制御回路4においては、そのときの矩形度整形回路5bに対する制御信号の制御量を記憶しておくようにしてもよい。このようにすれば、その後実運用に移行した際において、演算制御回路4において記憶している固定的な制御量で矩形度整形回路5bを介してゲートスイッチ駆動回路5cを制御することができる。

【0075】

実運用時には、演算制御回路4からゲートスイッチ駆動回路5cに対して入力光について導通/遮断すべきタイミングに応じたトリガ信号が入力されるようになるので、トリガ信号の周波数としては一定になるとは限らない。しかしながら、演算制御回路4においては、記憶されている制御量において矩形度整形回路5bを制御することで、SOA2からの出力光の立ち上がり波形を初期の形状とすることができるようになる。尚、実運用後においても、導通/遮断の対象となる入力光が入力されない状態においては、必要に応じて適宜上述のフィードバックを働かせることもできる。

【0076】

このように、第1実施形態によれば、簡易な波形整形によって目標の矩形度を有するパルスを生成できる利点がある。

なお、上述の第1実施形態においては、SOA2から出力されるASE光を含む光パルスをモニタすることにより、光パルスの矩形度を整形している。このほかに、外部からの入力信号、例えば、SOA2を光ゲートスイッチとして適用した場合の導通/遮断の対象となる入力光を用いて整形することとしてもよい。この場合においては、演算制御回路4から出力されるトリガ信号の周波数としては既知の一定周波数としておくことで、矩形度識別回路3をなす高調波成分抽出部3aの周波数抽出特性について、上記一定周波数に基づき定めておくことが可能になる。

【0077】

〔B〕第2実施形態

図10は第2実施形態にかかる波形制御装置1A又は応答素子モジュール10Aを示す図である。第2実施形態においては、前述の第1実施形態と比較して、異なる要素をそなえた矩形度識別回路3Aをそなえるとともに、制御態様の異なる演算制御回路4Aをそなえている。尚、既述の符号はほぼ同様の部分を示す。即ち、波形制御装置1Aは、矩形度識別回路3Aおよび演算制御回路4Aをそなえるとともに、第1実施形態の場合と同様の駆動電圧制御回路5をそなえ、応答素子モジュール10Aは、上述の波形制御装置1Aとしての要素とともにSOA2をそなえる。

【0078】

矩形度識別回路3Aは、応答素子であるSOA2に供給される駆動信号に当該SOA2が応答して得られる出力パルスの波形をモニタするモニタ部の一例であるが、第2実施形態においては受光部3dおよび高速A/Dコンバータ3eをそなえている。受光部3dは、SOA2から出力された光について光カプラ7を介して受けて、光パルスとしての振幅変化に応じた振幅変化を有する電圧信号等の電気信号に変換する。フォトダイオード(PD)およびトランスインピーダンスアンプは、協働して受光部3dの一例に相当する。

【0079】

また、高速A/Dコンバータ3eは、出力パルスの波形をサンプリングするサンプリング部の一例であり、受光部3dからの電気信号を高速サンプリングする。高速A/Dコンバータ3eにおいては、光パルスに応じた振幅変化をサンプリングするために、SOA2をオンオフスイッチングする際の応答波形を複数点サンプリングする必要がある。

このため、高速A/Dコンバータ3eとしては、例えば、SOA2のオンオフスイッチングの速度の5〜10倍程度高速のサンプリング周期を有するものを用いる。例えば、スイッチングを10ナノ秒で行なう性能を持つ光ゲートスイッチを用いる場合、その5〜10倍高速の1〜2ナノ秒のサンプリング周期を有するものを用いる。即ち、高速A/Dコンバータ3eとしては、500Msps〜1Gsps、もしくはそれ以上サンプリング周期を持つものを用いる。

【0080】

演算制御回路4Aは、駆動電圧制御回路5と協働して、サンプリング部3eでのサンプリング結果をもとに、SOA2への駆動信号の波形を整形する駆動波形整形部の一例に相当する。具体的には、演算制御回路4Aは、ゲートスイッチ駆動回路5cに一定周波数のトリガ信号を出力する一方、高速A/Dコンバータ3eからの出力を用いた演算を行ない、その演算結果に基づいて、矩形度整形回路5bへの制御信号を出力する。矩形度整形回路5bへの制御信号は、前述したように、ゲートスイッチ駆動回路5c(5c′)をなす回路部16又は回路部18(図6又は図9参照)の回路時定数を変更するための制御信号である。

【0081】

一例として、演算制御回路4Aにおいては、高速A/Dコンバータ3eにおいて、出力パルスの立ち上がり領域においてサンプリングされた値の変動指標を、例えば分散等の演算により導出し、導出結果に応じた制御信号を矩形度整形回路5bに出力する。例えば、演算制御回路4Aでは、演算された分散が最小となるように矩形度整形回路5bへの制御信号の制御量を制御すると、SOA2から出力される出力パルスの波形は、制御信号が他の制御量である場合に比較して、真正の(理想的な)矩形波形状に最も近くなる。

【0082】

図11は演算制御回路4Aの処理に着目した波形制御装置1Aの動作例について説明するフローチャートである。まず、演算制御回路4Aから矩形度整形回路5bに対して、矩形度整形回路5bでの制御量を初期設定する制御信号を出力する。ゲートスイッチ駆動回路5cの要素に、図6に示すバリキャップとしての可変容量素子16aを有する回路部16を適用する場合には、当該バリキャップ16aへの制御電圧信号を初期値Vk=Vbに設定する制御信号を矩形度整形回路5bに出力する(ステップA1)。

【0083】

ついで、演算制御回路4Aにおいて、SOA2から出力されるASE光のオンオフ制御のためのトリガ信号を生成し、ゲートスイッチ駆動回路5cに供給する。これにより、SOA2では、バリキャップ電圧の初期値に応じた立ち上がり波形を有する出力光パルス(例えばASE光)を出力することができる(ステップA2)。

そして、高速A/Dコンバータ3eから、SOA2から出力される出力光パルスの一定時間についてのサンプリング結果を受ける。一例として、演算制御回路4Aでは、既知であるトリガ信号の1以上の整数倍周期の時間についてのサンプリング結果を高速A/Dコンバータ3eから受けて、たとえば、メモリなどに記憶領域を設けて時系列で保持する(ステップA3)。

【0084】

さらに、上述の記憶領域に保持された上記一定時間のサンプリング結果について、その平均値X(=サンプリング合計値÷サンプリング数)を算出する(ステップA4)。

つぎに、記憶領域に保持された上記一定時間のサンプリング結果のうちで、算出した平均値Xを上回るサンプル点を抽出するとともに、抽出したサンプル点のうちの時系列における先頭のNサンプル標準偏差σを算出する(ステップA5)。先頭のNサンプルとしては、図12に示すように、可変容量素子16aの容量の値に応じて、出力光パルスの立ち上がり波形に変動が現れる時間範囲R1におけるサンプル点の個数の程度とすることができる。

【0085】

上述のごとく算出された標準偏差σについては、設定している電圧信号Vkの値に対応付けて図示しない記憶領域に記憶しておく(ステップA6)。以降、矩形度整形回路5bからの電圧信号について、制御範囲(Vb〜Vend)に亘り単位刻み幅ΔVで変更する(Vk=Vk+ΔV)。そして、その都度のサンプリング結果をもとにして上述のごとく標準偏差を演算する(ステップA7のNoルートからステップA8,ステップA3〜ステップA6)。

【0086】

上述の制御範囲に亘る標準偏差の値の演算が終了すると、即ちステップA7でVk≧Vendとなると(ステップA7のYesルート)、次に、目標点となる標準偏差を有する電圧信号の値を、上述の記憶領域を参照して検索する(ステップA9)。即ち、記憶領域に保持された矩形度整形回路5bでの電圧信号の値に応じた標準偏差の値の関係から、標準偏差σが目標値(例えば最小の標準偏差)となる電圧信号値を検索する。

【0087】

そして、このように検索された電圧信号値を、最適電圧信号値Voptとする。即ち、演算制御回路4Aにおいては、制御信号を出力することにより、矩形度整形回路5bからゲートスイッチ駆動回路5cのバリキャップ16aに供給する電圧信号をVoptとする(ステップA10)。

立ち上がりエッジが最も真正の矩形波形状に近い場合、標準偏差σはばらつきが最も小さくなるため、最小の値をとる。従って、例示したように、矩形度整形回路5bへの制御信号を通じて、算出される標準偏差σを最小となるようパルスの矩形度を制御する。このようにすると、出力光パルスの波形を、他の標準偏差をとる出力光パルスに比べて、最も矩形波形状に近づけることが可能となる。

【0088】

このように、第2実施形態においても、簡易な波形整形によって目標の矩形度を有するパルスを生成できる利点がある。

なお、上述の場合においては出力光パルスの立ち上がり波形における変動が現れる範囲についてのサンプル点について標準偏差を算出しているが、立ち下がり波形におけるにおける変動が現れる範囲についてのサンプル点について標準偏差を算出してもよい。この場合においては、上述のステップA4と同様に平均値Xを算出後、平均値Xを下回るサンプル点の最初のNサンプルに対して標準偏差σを算出すればよい。

【0089】

〔C〕第3実施形態

図13は第2実施形態にかかる波形制御装置1B又は応答素子モジュール10Bを示す図である。第3実施形態においては、前述の第1,第2実施形態と比較して、異なる要素をそなえた矩形度識別回路3Bをそなえるとともに、制御態様の異なる演算制御回路4Bをそなえている。尚、既述の符号はほぼ同様の部分を示す。即ち、波形制御装置1Bは、矩形度識別回路3Bおよび演算制御回路4Bをそなえるとともに、第1,第2実施形態の場合と同様の駆動電圧制御回路5をそなえ、応答素子モジュール10Bは、上述の波形制御装置1Bとしての要素とともにSOA2をそなえる。

【0090】

矩形度識別回路3Bは、応答素子であるSOA2に供給される駆動信号に当該SOA2が応答して得られる出力パルスの波形をモニタするモニタ部の一例である。第3実施形態の矩形度識別回路3Bにおいては、受光部3d,AC結合部3f,レベル調整部3g,エッジ検出回路3h,ピークホールド回路3i,サンプルホールド回路3jおよび2つのA/Dコンバータ3m,3nをそなえている。受光部3dについては第2実施形態におけるものと同様である。

【0091】

AC(Alternating Current)結合部3fは、受光部3dからの電気信号についてAC結合により直流成分をカットして、エッジ検出回路3hに出力する。又、レベル調整部3gは、受光部3dからの電気出力についてレベル調整を行なうアンプをそなえ、ピークホールド回路3iおよびサンプルホールド回路3jにそれぞれ出力する。

エッジ検出回路(エッジ検出部)3hは、電気信号として直流成分が除去された出力パルスをAC結合部3fから受けて、出力パルスの波形における立ち上がりエッジおよび立ち下がりエッジを検出する。

【0092】

また、ピークホールド回路(ピークホールド部)3iは、エッジ検出回路3hでの立ち上がりエッジの検出をもとに、出力パルスの波形における、駆動信号の立ち上がりに応答した立ち上がりピークレベルの値を保持する。具体的には、エッジ検出回路3hにおいて検出される立ち上がりエッジの検出をトリガとして、SOA2のスイッチング時間から立ち上がりピークレベルを検出するに必要とされる時間について、レベル調整部3gからの出力パルスのピーク値(最大値)を保持する。

【0093】

立ち上がりピークレベルを検出するに必要とされる時間は、たとえば図14に示すように定めることができる。即ち、エッジ検出回路3hでの立ち上がりエッジの検出によるトリガ信号を受けて開始して(時点T11)、当該立ち上がりが収束に向かうようになる所定時点T12までの時間T1とすることができる。これにより、ピークホールド回路3iにおいては、図14に示すように、可変容量素子16a(図6参照)の容量に応じて相違する立ち上がり波形W1,W2,W3に応じて、立ち上がりピークレベルP1,P2,P3を得ることができる。

【0094】

なお、ピークホールド回路3iでの上述のピークホールド動作のため、当該ピークホールド回路3iまたはエッジ検出回路3hにおいては、上述のT1についての時間管理機能を持つことができる。

または、ピークホールド回路3iでは、エッジ検出回路3hからの立ち上がりエッジ検出によるトリガ信号を受けてピークホールドを開始する一方、エッジ検出回路3hからの立ち下がりエッジ検出によるトリガ信号を受けるまでピークホールドを継続することとしてもよい。

【0095】

さらに、サンプルホールド回路(サンプルホールド部)3jは、エッジ検出回路3hでの立ち上がりエッジの検出をもとに、駆動信号の立ち下がり前の平坦領域に対応した応答波形レベルである出力パルスのレベルの値をサンプルホールドする。

具体的には、エッジ検出回路3hにおいて検出される立ち上がりエッジの検出から所定時間経過後の、立ち下がり前において出力パルスのレベルが安定する時間においてそのレベル値Sをサンプルホールドする。

【0096】

たとえば図14に示すように、サンプルホールド回路3jは、立ち上がりエッジの検出によるトリガ信号を受けてから(T11)、時間T2が経過した後のレベルが安定する時間(立ち下がり直前の時間)T3において、出力パルスのレベル値をサンプルホールドする。サンプルホールド回路3jでの上述のサンプルホールド動作のため、当該サンプルホールド回路3jまたはエッジ検出回路3hにおいては、上述のT2,T3についての時間管理機能を持つことができる。

【0097】

矩形度識別回路3Bに入力される出力パルスは、演算制御回路4Bから出力されるトリガ信号に対応するオンオフ周期を有している。従って、サンプルホールド回路3jにおいても、出力パルスについての立ち上がりから立ち下がりに至るオン時間が固定されている。このため、サンプルホールド回路3jまたはエッジ検出回路3hにおいては、当該オン時間の値に応じて上述の時間T2,T3を設定することができる。

【0098】

A/Dコンバータ3mは、ピークホールド回路3iからの、立ち上がりピークレベルの値を示すアナログ信号についてディジタル信号に変換して演算制御回路4Bに出力する。又、A/Dコンバータ3nは、サンプルホールド回路3jにおいてサンプルホールドしている値を示すアナログ信号についてディジタル信号に変換して演算制御回路4Bに出力する。

【0099】

演算制御回路4Bは、駆動電圧制御回路5と協働して、ピークホールド回路3iで保持した値およびサンプルホールド回路3jでサンプルホールドした値をモニタ結果として受けて、当該モニタ結果に基づき駆動信号の波形を整形する駆動波形可変部の一例に相当する。

具体的には、演算制御回路4Bは、ゲートスイッチ駆動回路5cに一定周波数のトリガ信号を出力する一方、A/Dコンバータ3m,3nからの各出力を用いた演算を行ない、その演算結果に基づいて、矩形度整形回路5bへの制御信号を出力する。矩形度整形回路5bへの制御信号は、前述したように、図6に示す可変容量素子16aの容量(又は図9に示す可変インダクタ素子18cのインダクタンス)の制御を通じ回路16(又は18)の応答時定数を変更するための制御信号である。

【0100】

一例として、A/Dコンバータ3mからのピークホールド値を立ち上がり振幅値とする一方、A/Dコンバータ3nからのサンプルホールド値を立ち下がり振幅値として、両者の差を演算する。このようにして演算される差の値に応じて上述の矩形度整形回路5bへの制御信号による制御量を制御する。例えば、演算される差の値が最小となるように矩形度整形回路5bへの制御信号による制御量を制御すると、SOA2から出力される出力パルスの波形は、制御信号が他の制御量である場合に比較して、真正の(理想的な)矩形波形状に最も近くなる。

【0101】

図15は演算制御回路4Bの処理に着目した波形制御装置1Bの動作例について説明するフローチャートである。この動作例では、波形制御装置1Bを図1に示す光パケットスイッチ100に適用して、複数のSOA102a,104に対する駆動信号(又は出力光パルス波形)について、理想的な矩形波形状を有するように順次整形している。又、ゲートスイッチ駆動回路5cとして図6に示す回路部16を、更に、可変容量素子16aとしてバリキャップを適用している。

【0102】

まず、演算制御回路4Bから矩形度整形回路5bに対して、矩形度整形回路5bでの制御量を初期設定する制御信号を出力する。ゲートスイッチ駆動回路5cの要素に、図6に示すバリキャップとしての可変容量素子16aを有する回路部16を適用する場合には、当該バリキャップ16aへの制御電圧信号を初期値αに設定する制御信号を出力する(ステップB1)。

【0103】

ついで、演算制御回路4Bにおいて、SOA2から出力されるASE光のオンオフ制御のためのトリガ信号を生成し、ゲートスイッチ駆動回路5cに供給する。これにより、SOA2では、バリキャップ電圧の初期値に応じた立ち上がり波形を有する出力光パルス(例えばASE光)を出力することができる(ステップB2)。

そして、エッジ検出回路3hにおいて、受光部3dからAC結合部3fを介して入力される出力パルスから、出力パルスの立ち上がりおよび立ち下がりエッジを検出する(ステップB3)。この場合において、エッジ検出回路3hでは、エッジ検出するとその旨のトリガ信号をピークホールド回路3iおよびサンプルホールド回路3jに出力する。

【0104】

さらに、ピークホールド回路3iは、エッジ検出回路3hからの立ち上がりエッジに応じたトリガ信号により、出力パルスの立ち上がりタイミングで一定時間起動される。そして、このピークホールド回路3iで、立ち上がり波形のピーク値(最大値)を保持する(ステップB4)。更に、A/Dコンバータ3mにおいては、ピークホールド回路3iで保持するピーク値について読み取り、これを立ち上がり振幅Vrとして演算制御回路4Bに出力する(ステップB5)。

【0105】

また、サンプルホールド回路3jでは、エッジ検出回路3hにおいて検出される立ち上がりエッジの検出から所定時間経過後の、立ち下がり前において出力パルスのレベルが安定する時間においてそのレベル値Sをサンプルホールドする(ステップB6)。更に、A/Dコンバータ3nにおいては、サンプルホールド回路3jで保持するピーク値について読み取り、これを立ち下がり振幅Vfとして演算制御回路4Bに出力する(ステップB7)。

【0106】

演算制御回路4Bでは、A/Dコンバータ3m,3nからの立ち上がり振幅値Vrおよび立ち下がり振幅値Vfを比較する。両者の差が一定値D以上である場合には、当該SOA2から出力される出力パルスの波形は理想的な矩形波形状から崩れているので、理想的な矩形波形状に近づくように、矩形度整形回路5bへの制御信号の制御量を変更する(ステップB8のYesルート)。

【0107】

具体的には、立ち上がり振幅Vrが立ち下がり振幅Vfよりも大きい場合においては(ステップB9のYesルート)、エッジが利きすぎ、即ち、理想的な矩形度からすると立ち上がりが急峻である。このため、演算制御回路4Bから矩形度整形回路5bに対する制御信号を通じて、矩形度整形回路5bからのバリキャップ電圧をΔVだけ上げることにより、立ち上がり波形を鈍らせる(ステップB10)。

【0108】

また、立ち上がり振幅Vrが立ち下がり振幅Vf以下の場合においては(ステップB9のNoルート)、エッジがなまりすぎ、即ち、理想的な矩形度からすると立ち上がりが鈍い。このため、演算制御回路4Bから矩形度整形回路5bに対する制御信号を通じて、矩形度整形回路5bからのバリキャップ電圧をΔVだけ下げることにより、立ち上がり波形を尖らせる(ステップB11)。

【0109】

演算制御回路4Bでは、立ち上がり振幅値Vrおよび立ち下がり振幅値Vfの差がDよりも小さくなるまで、上述したようなバリキャップ電圧を変更する制御を繰り返す(ステップB10,B11からステップB3)。

矩形度整形回路5bからのバリキャップ電圧の制御を通じて、VrとVfとの差が一定値Dよりも小さくなった場合には、駆動信号の調整対象となっている当該SOA2(SOA102a,104)に対する駆動信号の調整は終了する。このようにして、全ての測定対象のSOA102a,104について駆動信号を順次調整していく(ステップB12)。

【0110】

全てのSOAに対する駆動信号の調整が終了すると、装置としての実運用を開始することができる。例えば、図1の光パケットスイッチ100をなす全てのSOA102a,104についての駆動信号の調整が完了すると、光パケットスイッチ100として実運用が可能になる。即ち、SOA102aは、光ゲートスイッチとして入力光の導通/遮断の制御に用いることができ、又は、SOA104は、入力光の導通/遮断のほか増幅のために用いることができる。

【0111】

なお、上述のVrとVfとの差に対する基準値Dとしては、例えばSOA2から出力される出力パルスの波形が目標とする矩形度を得られる許容値に対応するものとすることができる。

なお、上述の動作例においては、SOA2からの出力パルスについて理想的な矩形波形状に近づけるように制御しているが、制御目標としては理想的でない特定の矩形波形状となるようにしてもよい。一例として、演算制御回路4Bにおいては、立ち上がり振幅値と立ち下がり振幅値との差が、誤差範囲を含む特定の(最小ではない)値となるように、矩形波整形回路5bを制御することとしてもよい。

【0112】

このように、第3実施形態においても、簡易な波形整形によって目標の矩形度を有するパルスを生成できる利点がある。

〔D〕実施例

上述の第1〜第3実施形態において例示した波形制御装置1,1A,1B,応答素子モジュール10,10A,10Bは、例えば、光パケットスイッチングを行なう光パケットスイッチに適用することができる。その一例を図16に示す。この図16に示す光パケットスイッチ200においては、図1に示す光パケットスイッチ100と同様、8個の1:8カプラ101,8個の8:8光ゲートスイッチ部102,8個の8:1カプラ103および8個のSOA104をそなえている。尚、図1と同一の符号はほぼ同様の部分を示している。

【0113】

光パケットスイッチ200は、駆動信号に応答して入力光の導通/遮断を切り換える光ゲートスイッチとしてのSOA102a,104を複数有する光スイッチ装置の一例である。光パケットスイッチ200は、光カプラ207a−1〜207a−8,207b,矩形度識別回路203,演算制御回路204および各SOA102a,104に対応した数の駆動電圧制御回路205をそなえる。

【0114】

駆動電圧制御回路205は、8:8光ゲートスイッチ部102をなす64個のSOA102aとともに、8個のSOA104に対応づけて72個がそなえられ、それぞれ、個別のSOA102a,104に対して駆動信号を供給するものである。各駆動電圧制御回路205としては、前述の各実施形態における波形制御装置1,1A,1Bの要素である駆動電圧制御回路5を適用することができる。

【0115】

すなわち、各駆動電圧制御回路205をなすゲートスイッチ駆動回路5c(図2,図10,図13参照)は、縦続して接続される複数個の光ゲートスイッチ102a,104に対応してそなえられ、対応する光ゲートスイッチ102a,104への駆動信号の波形を、制御信号に基づき整形する複数個の駆動回路部の一例である。

演算制御回路204は、各駆動電圧制御回路205をなすゲートスイッチ駆動回路5cに対して、対応するSOA102a,104を駆動するためのトリガ信号を出力するとともに、各駆動電圧制御回路205をなす矩形度整形回路5bへの制御信号を与える。演算制御回路204としては、前述の各実施形態における波形制御装置1,1A,1Bの要素である演算制御回路4,4A,4Bの一態様を、上述の72個の駆動電圧制御回路205を制御するために適用することができる。

【0116】

したがって、各駆動電圧制御回路205をなす矩形度整形回路5b(図2,図10,図13参照)および演算制御回路4,4A,4Bは、協働することにより、モニタ部203でのモニタ結果に基づき制御信号を駆動回路部5cに出力する制御部の一例に相当する。

光カプラ207a−1,207a−8は、出力ポート♯1〜♯8を伝搬する光をそれぞれ分岐する。光カプラ207bは、光カプラ207a−1〜207a−8からの分岐光経路を合流して、矩形度識別回路203の入力とする。

【0117】

矩形度識別回路203は、72個のSOA102a,104から出力される出力光パルス(出力パルス)の波形をモニタするモニタ部の一例であり、出力光パルスの矩形度を識別する。ここで、出力ポート♯j(j=1〜8の整数)に対応する8:8光ゲートスイッチ部102をなすSOA102aおよび対応する下流側のSOA104から出力される光は、光カプラ207a−j,207bを介して矩形度識別回路203に入力される。

【0118】

このとき、各SOA102a,104に対する駆動電圧制御回路205からの駆動信号の供給態様により、一のSOA102a,104から出力される光パルスの矩形度について順次識別することが可能になる。又、矩形度識別回路203としては、前述の各実施形態における波形制御装置1,1A,1Bの要素である矩形度識別回路3,3A,3Bの一態様を適用することができる。

【0119】

このように、駆動電圧制御回路205においては、各SOA102a,104に対応して72個そなえられているが、演算制御回路204および矩形度識別回路203については、各SOA102a,104について共用することができる。即ち、各駆動電圧制御回路205および演算制御回路204は、協働することで、モニタ部203でのモニタ結果に基づいて、当該出力された光波形をモニタした光ゲートスイッチ102a,104への駆動信号の波形を整形する駆動波形整形部に相当する。

【0120】

つぎに、光パケットスイッチ200の運用開始前の各SOA102a,104を駆動する駆動信号の調整動作例を説明する。各SOA102a,104の駆動信号を調整するにあたっては、光パケットスイッチ200をなす下流側のSOA104に対する駆動信号を優先的に調整する。

各出力ポート♯1〜♯8に対応して、一のSOA104が最下流に、8個のSOA102aが上流側にそなえられ、光カプラ207a−1〜207a−8,207bにより各出力ポート♯1〜♯8への出力が取りまとめられて矩形度識別回路203に接続されている。従って、上流側のSOA102aに対する駆動信号の調整のためには、下流側のSOA104を通じた出力光パルスをモニタすることになる。

【0121】

そこで、一の出力ポートに対応付けられた上流側のSOA102aに対する駆動信号を調整するには、当該下流側のSOA104への駆動信号の調整が完了していることが望ましい。これにより、下流側のSOA104への駆動信号が未調整である場合における、上流側のSOA102aに対する駆動信号の調整への影響を、生じさせないようにすることができる。

【0122】

たとえば、一の出力ポート♯jに対応して、最下流のSOA104についての駆動電圧制御回路205からの駆動信号について第1に調整し、第2に、上流側の8個のSOA102aについての駆動電圧制御回路205からの駆動信号について調整する。その後、他の出力ポートについてのSOA104,102aに対する駆動信号について同様に調整する。

【0123】

すなわち、演算制御回路204により、上流側のSOA102aへの駆動信号をオフとする一方、一のSOA104に対応する駆動電圧制御回路205に対して、トリガ信号を供給することを通じ、ASE光を含む出力光パルスを生成させる。この出力光パルスは、光カプラ207a−j,207bを介して矩形度識別回路203に入力される。そして、演算制御回路204および該当の駆動電圧制御回路205が協働することにより、矩形度識別回路203からのモニタ結果をもとにして駆動信号の波形を整形することを実現する。

【0124】

なお、上流側の8個のSOA102aについての駆動信号を整形するにあたっては、調整対象のSOA102aよりも下流側のSOA104についてはオン状態に固定しておく。これにより、上流側SOA102aで生成されるASE光による光パルスは、下流側SOA104および光カプラ207a−j,207bを介して矩形度識別回路203に入力されるので、モニタすることが可能になる。

【0125】

または、各出力ポート♯1〜♯8に対応する下流側SOA104についての駆動信号について順次優先的に調整し、次いで、各出力ポート♯1〜♯8に対応する上流側SOA102aについての駆動信号について調整してもよい。

このようにして、全てのSOA102a,104についての駆動信号の調整動作が完了すると、光パケットスイッチ200として実運用を開始できる。

【0126】

このように、例示した波形制御装置1,1A,1Bを光パケットスイッチ200の要素として適用することにより、多ポート対多ポートの光パケットスイッチシステムを容易に構築できる。即ち、光ゲートスイッチ102a,104ごとの駆動回路を個別に調整する必要がなくなり、組立調整にかかる工数を大幅に削減することが可能となる。また、装置運用開始後においても、各光ゲートスイッチ102a,104についての調整作業が効率化されるので、メインテナンス性やシステム信頼性も向上する。即ち、定期的に各光ゲートスイッチ102a,104についての駆動波形の最適化を行なうことで、長期に渡り装置性能を維持することが可能となる。

【0127】

図17は、上述の第1〜第3実施形態において例示した波形制御装置1,1A,1B,応答素子モジュール10,10A,10Bの他の光パケットスイッチ300への適用例である。この図17に示す光パケットスイッチ300においては、256の入力ポートに対応してそなえられた256個の分配部310−k,256の出力ポートに対応してそなえられた256個の合流部320−kをそなえる(k=1〜256の整数)。

【0128】

なお、図17中においては、一の分配部310−1,320−1をなす要素とともに、一対の入出力ポート♯1間が接続された経路に着目して示している。又、各分配部310−kは互いに同様の構成を有し、各合流部320−kも互いに同様の構成を有するので、以下においては一の分配部310−1および一の合流部320−1に着目して説明する。

分配部310−1は、入力ポート♯1からの光について256分配して、各分配経路を、一の合流部320−kに接続する。このため、分配部310−1は、一例として、上流側から、エルビウムドープファイバ増幅器(EDFA)311,1:16カプラ312,16個のEDFA313,16個の1:16カプラ314および16×16個のEDFA315をそなえる。

【0129】

入力ポート♯1からの光がEDFA311で光増幅され、1:16カプラ312で16分岐される。1:16カプラ312で分岐された16経路の各光は対応のEDFA313で光増幅される。EDFA313で光増幅された16経路の各光は、更に対応の1:16カプラ314で16分岐される。1:16カプラ314で分岐された合計16×16(=256)経路の各光は、対応のEDFA315で光増幅され、対応の合流部320−kに出力される。

【0130】

合流部320−1は、各分配部310−kからの経路が1経路ずつ接続されて、合計256の光経路を合流させて、出力ポート♯1に導く。そして、256の経路のいずれか1経路からの光について選択的に導通させ、他の経路からの光については遮断されるようになっている。このため、合流部320−1は、一例として、上流側から、256個のSOA321,32個の8:1カプラ322,32個のSOA323,32個の4:1カプラ324,8個のSOA325,1個の8:1カプラ326および1個のSOA327をそなえる。

【0131】

SOA321は、各分配部310−kからの光について導通/遮断を切り換える。各8:1カプラ322は、それぞれ8個のSOA321からの光経路を合流させる。各SOA323は、一の8:1カプラ322からの光について導通/遮断を切り換える。各4:1カプラ324は、それぞれ4個のSOA323からの光経路を合流させる。各SOA325は、一の4:1カプラ324からの光について導通/遮断を切り換える。8:1カプラ326は、8個のSOA325からの光経路を合流させる。SOA327は、8:1カプラ326からの光について導通/遮断を切り換える。

【0132】

これにより、合流部320−1においては、縦続接続された各段一つずつの合計4つのSOA321,323,325,327が同時に導通制御されることで、いずれかの分配部310−kからの光について出力ポート♯1に導くことができるようになる。

このような構成を有する光パケットスイッチ300においても、図16に示す光パケットスイッチ200の場合に倣って、矩形度識別回路(符号203参照),演算制御回路(符号204参照)および駆動電圧制御回路(符号205参照)を適用することができる。これにより、(256+32+8+1)×256ものSOAに対して、簡易に駆動信号を調整することができる。

【0133】

なお、この場合においても、矩形度識別回路としては一つで共用することができる。又、一対の入出力ポートを形成する経路単位で、下流側のSOAから上流側のSOAにわたり順次駆動信号を調整していくことで、光パケットスイッチ300全体として効率的かつ高精度での駆動信号の調整を実現できる。

また、一対の入出力ポートを形成する経路において、上流側のSOAについての駆動信号を調整するにあたっては、調整対象のSOAよりも下流側のSOAについては全てオン状態に固定しておく。これにより、上流側SOAで生成されるASE光による光パルスは、下流側SOAを介して矩形度識別回路に入力されるので、モニタすることが可能になる。

【0134】

このように、例示した波形制御装置1,1A,1Bを光パケットスイッチ300の要素として適用することにより、多ポート対多ポートの光パケットスイッチシステムを容易に構築できる。特に、図16の場合よりも光ゲートスイッチの素子数が増大する反面、各光ゲートスイッチの調整の効率化に対する効果はより大きくなる。

〔E〕その他

なお、第1〜第3実施形態における応答素子モジュール10,10A,10Bにおいては、その製造工程において、矩形度調整回路5bへの制御信号の制御量等を記憶しておくようにしてもよい。例えば、応答素子モジュール10,10A,10Bの各要素についての組み立てを行なったのちに、ASE光による光パルスを用いた上述の駆動信号の調整制御を行ない、更にモニタ結果が制御目標となる値となったときの、矩形度調整回路5bへの制御信号の制御量等を記憶しておくようにする。このようにすれば、応答素子モジュール10,10A,10Bの立ち上げ時において、演算制御回路4において記憶された制御量を用いてSOA2を駆動できるので、上述の各実施形態の場合と同様の利点があるほか、立ち上げ時においてのパルス波形の調整制御を省略でき、立ち上げ時間を高速化させるとともに、処理負荷を軽減できる。

【0135】

また、上述の実施形態においては、SOAのごとき光ゲートスイッチ素子に対する駆動信号の調整を通じて、光ゲートスイッチ素子から出力される出力光パルスの波形を整形している。しかしながら、例えば電気素子に対する出力パルスの波形を整形する際に用いることも勿論可能である。即ち、例示する波形制御装置1,1A,1Bは、電気信号を媒介として駆動信号の波形を整形しているので、波形制御装置1,1A,1Bとしてモニタ対象の出力パルスを出力する応答素子としては、電気素子とすることも勿論可能である。

【0136】

この場合は、例示の応答素子モジュール10,10A,10Bをなす応答素子2は電気素子に置き換えられ、矩形度識別回路3,3A,3B中の光を受光する機能については適宜省略できる。このような応答素子モジュールについては、2値のディジタル信号を扱う様々な電子機器に適用でき、実施形態で説明したような作用効果を奏することが可能となる。

【0137】

図18に、応答素子として電気素子を適用した場合の波形制御装置1Cおよび応答素子モジュール10Cの一例を示す。応答素子モジュール10Cは、スイッチ21,アンプ22,スイッチ27および波形制御装置1Cを含み、波形制御装置1Cで、アンプ22から出力される電気信号の波形をモニタして、モニタ結果に基づきアンプ22への駆動信号波形を整形する。これにより、アンプ22から出力される電気信号の矩形度を自在に制御する。

【0138】

スイッチ21は、入力電気信号のアンプ22への導通又は遮断を切り換える。アンプ22は、応答素子の一例であり、スイッチ21から入力される電気信号を、波形制御装置1Cで波形制御された駆動信号の一例である利得制御信号に基づいて増幅する。スイッチ27は、アンプ22から出力される出力電気信号について、応答素子モジュール10Cの出力方路か又は波形制御装置1Cへ入力される方路のいずれか一方を選択的に切り換える。

【0139】

波形制御装置1Cは、図18に例示するように、矩形度識別回路23と、演算制御回路24と、駆動電圧制御回路25と、を含む。演算制御回路24は、スイッチ21,27の切り換え設定を制御できる。例えば、スイッチ21,27を制御することにより、入力電気信号がアンプ22に供給され、アンプ22の出力が応答素子モジュール10Cの出力に導かれるようにする。これにより、応答素子モジュール10Cのアンプ22を経由した電気信号を用いることができる。

【0140】

また、スイッチ21を制御することにより、入力電気信号のアンプ22への供給を遮断できる。更に、スイッチ27を制御することにより、アンプ22の出力を矩形度識別回路23のコムフィルタ3a′に導くことができる。この場合には、例えば、演算制御回路24で生成した電気信号(一例として、擬似信号)を、スイッチ21を通じてアンプ22に出力するようにしてもよい。

【0141】

矩形度識別回路23は、供給される駆動信号に応答素子が応答して得られる出力パルスの波形をモニタするモニタ部の一例であり、コムフィルタ3a′とともに、前述の第1実施形態の場合と同様の平均パワー検出回路3bおよびA/Dコンバータ3cをそなえる。この場合には、演算制御回路24で生成した電気信号がアンプ22で増幅されて、このアンプ22から出力された出力電気信号がスイッチ27を経由して矩形度識別回路23に入力される。

【0142】

コムフィルタ3a′は、高調波成分抽出部の一例であり、アンプ22からの出力電気信号を、スイッチ27を通じて入力され、この出力電気信号に含まれる偶数次又は奇数次の高調波成分を抽出する。これにより、矩形度識別回路23においては、出力電気信号に含まれる偶数次又は奇数次の高調波成分の平均パワー値を演算制御回路24に出力する。

演算制御回路24および駆動波形制御回路25は、互いに協働することで、モニタ部23でのモニタ結果に基づいて、駆動信号の波形を整形する駆動波形整形部の一例に相当する。演算制御回路24においては、矩形度識別回路23からのモニタ結果をもとに、駆動波形制御回路25を介してアンプ22の利得を制御する。

【0143】

たとえば、矩形度識別回路23から偶数次の高調波成分の平均パワー値を受ける場合には、演算制御回路24では当該平均パワー値が最小となるように、駆動波形制御回路25を介してアンプ22の利得を制御する信号を出力する。これに対し、奇数次の高調波成分の平均パワー値を受ける場合には、演算制御回路24では当該平均パワー値が最大となるように、駆動波形制御回路25を介してアンプ22の利得を制御する信号を出力する。

【0144】

また、駆動波形制御回路25は、一例として、前述の第1実施形態の場合と同様のD/Aコンバータ5aおよび矩形度整形回路5bとともに、図6に例示するものと同等の駆動回路5cをそなえる。これにより、第1実施形態の場合と同様、演算制御回路24および駆動波形制御回路25が協働することにより、アンプ22に利得制御信号として供給される駆動信号の立ち上がり波形を整形することができる。結果として、出力電気信号の矩形度を目標の矩形度とすることができる。

【0145】

このように、図18に示す例においても、簡易な波形整形によって目標の矩形度を有する出力電気信号を得ることができる。

〔F〕付記

(付記1)

供給される駆動信号に応答素子が応答して得られる出力パルスの波形をモニタするモニタ部と、

該モニタ部でのモニタ結果に基づいて、前記駆動信号の波形を整形する駆動波形整形部と、をそなえたことを特徴とする、波形制御装置。

【0146】

(付記2)

該駆動波形整形部は、

前記応答素子への前記駆動信号の波形を、制御信号に基づき整形する駆動回路部と、

該モニタ部でのモニタ結果に基づき前記制御信号を該駆動回路部に出力する制御部と、をそなえたことを特徴とする、付記1記載の波形制御装置。

【0147】

(付記3)

該制御部は、前記モニタ結果としての前記出力パルスの波形が所定の波形を保つように前記制御信号を出力することを特徴とする、付記2記載の波形制御装置。

(付記4)

該駆動回路部は、前記制御信号に応じて応答時定数が可変されることを特徴とする、付記2記載の波形制御装置。

【0148】

(付記5)

該駆動回路部は、前記制御信号により容量が可変される可変容量素子を有することを特徴とする、付記4記載の波形制御装置。

(付記6)

該駆動回路部は、前記制御信号によりインダクタンスが可変されるインダクタ素子を有することを特徴とする、付記4記載の波形制御装置。

【0149】

(付記7)

該モニタ部は、

前記駆動信号の周波数の偶数次又は奇数次の高調波成分を前記出力パルスから抽出する高調波成分抽出部と、

該高調波成分抽出部にて抽出された前記偶数次又は奇数次の高調波成分を含む パワーをモニタするパワーモニタ部と、をそなえたことを特徴とする、付記1記載の波形制御装置。

【0150】

(付記8)

該駆動波形整形部は、該パワーモニタ部でモニタされたパワーが所定レベル又は所定範囲となるように前記駆動信号の波形を整形することを特徴とする、付記7記載の波形制御装置。

(付記9)

該モニタ部は、前記出力パルスの波形をサンプリングするサンプリング部をそなえ、

該駆動波形整形部は、該サンプリング部でのサンプリング結果をもとに、前記駆動信号の波形を整形することを特徴とする、付記1記載の波形制御装置。

【0151】

(付記10)

該モニタ部は、

前記出力パルスの波形における立ち上がりエッジおよび立ち下がりエッジを検出するエッジ検出部と、

該エッジ検出部での前記立ち上がりエッジの検出をもとに、前記出力パルスの波形における、前記駆動信号の立ち上がりに応答した立ち上がりピークレベルの値を保持するピークホールド部と、