波形測定装置

【課題】異なるアクイジションデータ格納領域に取り込まれた波形データを同時に解析してそれらの解析結果を同時に表示できる波形測定装置を実現する。

【解決手段】各データ格納領域に取り込まれた波形データに対する解析完了を確認する複数の解析確認部と、前記各データ格納領域への波形データの取り込みを制御する格納制御部と、次波形取込指示部と、アクイジションステータス監視部とを具備し、前記アクイジションステータス監視部は、前記解析確認部の解析確認出力信号に基づき前記各データ格納領域に取り込まれた波形データに対する解析がそれぞれ完了したことを確認すると前記次波形取込指示部にその旨を通知し、前記次波形取込指示部は前記アクイジションステータス監視部からの通知を確認すると前記各データ格納領域への次の波形データの取り込みを指示する。

【解決手段】各データ格納領域に取り込まれた波形データに対する解析完了を確認する複数の解析確認部と、前記各データ格納領域への波形データの取り込みを制御する格納制御部と、次波形取込指示部と、アクイジションステータス監視部とを具備し、前記アクイジションステータス監視部は、前記解析確認部の解析確認出力信号に基づき前記各データ格納領域に取り込まれた波形データに対する解析がそれぞれ完了したことを確認すると前記次波形取込指示部にその旨を通知し、前記次波形取込指示部は前記アクイジションステータス監視部からの通知を確認すると前記各データ格納領域への次の波形データの取り込みを指示する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、波形測定装置に関し、詳しくは、波形解析機能の改善に関する。

【背景技術】

【0002】

図5は、たとえば自動車に実装されているシリアルバスを流れる電気信号の測定解析などにも用いられる波形測定装置の一例を示す基本ブロック図である。図5において、入力端子1に入力されるシリアルバスを流れる電気信号は、アッテネータ2→プリアンプ3の信号経路を経て適正な振幅に調整された後、たとえば100MS/sで高速サンプリングを行うA/D変換器4に入力されて波形データとしてのデジタル信号に変換される。

【0003】

A/D変換器4の出力データは、メモリ制御部5に入力される。メモリ制御部5には、ACQ(アクイジション)メモリ6、測定処理部7およびCPU8が接続されている。なお、メモリ制御部5には、メインデータ格納制御部5aとサブデータ格納制御部5bと次波形取込制御部5cが設けられている。ACQメモリ6には、メインデータ格納領域6aとサブデータ格納領域6bが設けられている。

【0004】

CPU8には、メインメモリ9および内部バスBが接続されている。内部バスBには、表示処理部10、操作設定部11、サブ側解析部12、メイン側解析部13、解析状態監視部14などの各機能ブロックが接続されている。表示処理部10には表示部15が接続されている。

【0005】

プリアンプ3の出力端子にはトリガ検出部16も接続され、トリガ検出部16の出力端子はメモリ制御部5に接続されている。また、トリガ検出部16にはトリガ設定部17の出力端子も接続され、トリガ設定部17は内部バスBに接続されている。

【0006】

このような構成において、ユーザーは操作設定部11を操作し、メインデータ格納制御部5aにA/D変換器4から高速で変換出力される波形データをたとえば10kS/sの低速サンプリングデータになるように間引いてメインデータ格納領域6aに取り込むための時間軸とサンプリング・レートを設定するとともに、トリガ条件が成立した場合にA/D変換器4から出力される高速変換データを所定期間サブデータ格納制御部5bに取り込むためのプリアンプ3からA/D変換器4に入力される電気信号に対するトリガ条件をトリガ設定部17を介してトリガ検出部16に設定する。

【0007】

これにより、A/D変換器4から高速変換出力される波形データは、メインデータ格納制御部5aの制御にしたがって連続的に低速サンプリングデータに間引きされてメインデータ格納領域6aに取り込まれるとともに、トリガ条件が成立した場合にはサブデータ格納制御部5bの制御にしたがって所定期間の高速変換データがサブデータ格納制御部5bに取り込まれる。

【0008】

これらACQメモリ6のメインデータ格納領域6aに格納されるメイン波形データおよびサブデータ格納領域6bに格納されるサブ波形データは、表示処理部10を介して表示部15に表示される。

【0009】

測定処理部7は、ACQメモリ6のサブデータ格納制御部5bに取り込まれた波形データに基づき、立ち上がり時間や立ち下がり時間、パルス幅、パルス振幅など、測定信号波形に関する各種パラメータの測定を行う。これら各種パラメータの測定値は、たとえば測定処理部7の内部に設けられているメモリに格納される。

【0010】

サブ側解析部12およびメイン側解析部13は、それぞれに適した「時間軸」と「サンプリング・レート」で波形データを取り込むことにより、解析することができる。図6はサブ側解析部12における解析例の表示画面例図であり、2値化された波形データ(0,1)に対し定義されたプロトコルを解析した例を示している。図6において、「Break」は通信開始を表し、続く「0x55」は同期ビットを表し、次の「0xAA」はデータの宛先を表し、次の「0x55」はデータ列を表している。

【0011】

解析状態監視部14は、サブ側解析部12およびメイン側解析部13の波形データ解析状態を監視し、いずれかの解析部の波形解析が終了したことを確認すると、メモリ制御部5の次波形取込指示部5cに波形解析終了を通知する。これにより、次波形取込指示部5cは、メインデータ格納制御部5aまたはサブデータ格納制御部5bに次の波形取込を指示する。

【0012】

図7は、ACQメモリ6のメインデータ格納領域6aおよびサブデータ格納領域6bにそれぞれ異なる2系統の「時間軸」と「サンプリング・レート」で波形データを取り込み表示する表示画面例図である。

【0013】

図7の表示機能を使用することで、画面の上側領域には遅いサンプリング・レート(たとえば10kS/s)でメインデータ格納領域6aに長時間にわたる波形データをたとえば「メイン側」として表示でき、画面下側領域にはトリガが検出された場合に高速のサンプリング・レート(たとえば100MS/s)でサブデータ格納領域6bに取り込まれる所定区間の波形データをたとえば「サブ側」として拡大表示できるとともに、サブ側の波形データについては各種パラメータの測定結果も表示できる。

【0014】

図8は図5における波形データ取込動作の流れを説明するフローチャートであり、サブデータ格納領域6bに波形データ取込中もサブ側解析部12の解析結果を同期させる場合を示している。

【0015】

メモリ制御部5に対し、CPU8を介して波形取込開始が指示されると、メモリ制御部5はメインデータおよびサブデータの波形取込を開始する(ステップS1)。

【0016】

メインデータ格納制御部5aはメインデータ格納領域6aにA/D変換器4の出力データに基づく所定のメイン波形データが格納されるように制御し、サブデータ格納制御部5bはサブデータ格納領域6bに所定期間のA/D変換器4の出力データがサブ波形データとして格納されるように制御する(ステップS2)。

【0017】

これらACQメモリ6のメインデータ格納領域6aに格納されるメイン波形データおよびサブデータ格納領域6bに格納されるサブ波形データは、表示処理部10を介して表示部15に表示される(ステップS3)。

【0018】

サブ側解析部12が有効になると(ステップS4)、解析タスクが始動されて(ステップS11)、サブデータ格納領域6bに格納されるサブ波形データに対する解析が実行され(ステップS12)、解析結果が表示部15の表示画面にGUI表示されて(ステップS13)、解析タスクは終了し(ステップS14)、次の波形を取り込むか否かの判断ステップS5に遷移する。

【0019】

メモリ制御部5は、波形データアクイジションのステータスが「Run」であればステップ1に戻って一連の処理を繰り返して実行し、ステータスが「Run」でなければ波形データ取込を終了する(ステップS5)。

【0020】

特許文献1には、シリアルバスを流れる波形パターン解析を効率よく行える波形測定器の構成が記載されている。

【0021】

非特許文献1には、高速現象と低速現象が混在する波形データの測定に適した波形測定器の構成が記載されている。

【先行技術文献】

【特許文献】

【0022】

【特許文献1】特開2002−311060

【非特許文献】

【0023】

【非特許文献1】中山 悦郎、外3名、「スコープコーダDL750」、横河技報、横河電機株式会社、2003年、Vol.47 No.1(2003) p.27−30

【発明の開示】

【発明が解決しようとする課題】

【0024】

しかし、図5に示す従来の構成によれば、図6に示すように設定された「時間軸」と「サンプリング・レート」で観測された波形に対する異常信号などは解析できるものの、その測定範囲を超えた「時間軸」や「サンプリング・レート」の設定で解析できるたとえば物理層とアプリケーション層などの異なる測定域で発生する異常を同時に観察することはできない。

【0025】

また、図7に示すようにサブ側の表示領域に表示されている波形に対しては解析することができるが、メイン側およびサブ側のそれぞれの表示領域に表示された波形に対して同時に解析することはできず、メイン側とサブ側を同時に解析することで有用となるような解析方法を示すこともできなかった。

【0026】

本発明は、これらの課題を解決するものであり、その目的は、異なるアクイジションデータ格納領域に取り込まれた波形データを同時に解析してそれらの解析結果を同時に表示できる波形測定装置を実現することにある。

【課題を解決するための手段】

【0027】

このような課題を達成するために、本発明のうち請求項1記載の発明は、

同時に異なる「時間軸」と「サンプリング・レート」でアクイジションメモリの異なるデータ格納領域に取り込まれた波形データを同時に解析して、それらの解析結果を共通の表示画面上に同時に表示させる波形測定装置であって、

前記各データ格納領域に取り込まれた波形データに対する解析がそれぞれ完了したことを確認する複数の解析確認部と、

前記アクイジションメモリへの波形データの取り込みを制御するメモリ制御部に設けられ前記各データ格納領域への波形データの取り込みを制御する複数の格納制御部と、次の波形データの取り込みを指示する次波形取込指示部と、前記アクイジションメモリへの波形データの取り込み状態を監視するアクイジションステータス監視部とを具備し、

前記アクイジションステータス監視部は、前記複数の解析確認部の解析確認出力信号に基づき前記各データ格納領域に取り込まれた波形データに対する解析がそれぞれ完了したことを確認すると前記次波形取込指示部にその旨を通知し、前記次波形取込指示部は前記アクイジションステータス監視部からの通知を確認すると前記各データ格納領域への次の波形データの取り込みを指示することを特徴とする。

【0028】

請求項2の発明は、請求項1記載の波形測定装置において、

前記アクイジションメモリには第1の波形データ格納領域と第2の波形データ格納領域が設けられていて、第1の波形データ格納領域には第1の格納制御部で連続的に低速サンプリングデータに間引きされた波形データが取り込まれ、第2の波形データ格納領域には所定のトリガ条件が成立したときに第2の格納制御部の制御にしたがって所定期間の高速変換データが取り込まれることを特徴とする波形測定装置である。

【0029】

請求項3記載の発明は、請求項1または請求項2に記載の波形測定装置において、

自動車に実装されているシリアルバスを流れる電気信号を測定解析することを特徴とする。

【発明の効果】

【0030】

これらの構成により、異なるアクイジションデータ格納領域に取り込まれた波形データを同時に解析してそれらの解析結果を同時に表示でき、異常現象把握の的確性を高めることができる。

【図面の簡単な説明】

【0031】

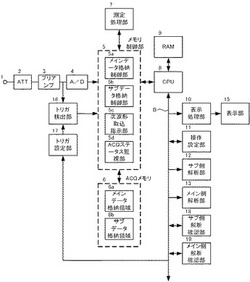

【図1】本発明の一実施例を示すブロック図である。

【図2】本発明に基づく同時解析の表示画面例図である。

【図3】図1における波形データ取込動作の流れを説明するフローチャートである。

【図4】インバータの電力損失を検証するための波形測定解析例図である。

【図5】従来の波形測定装置の一例を示す基本ブロック図である。

【図6】図5のサブ側解析部12における解析例の表示画面例図である。

【図7】異なる2系統の「時間軸」と「サンプリング・レート」で波形データを取り込み表示する表示画面例図である。

【図8】図5における波形データ取込動作の流れを説明するフローチャートである。

【発明を実施するための最良の形態】

【0032】

以下、本発明の実施の形態について、図面を用いて詳細に説明する。図1は本発明の一実施例を示すブロック図であり、図5と共通する部分には同一の符号を付けている。図1において、メモリ制御部5には図5の構成に加えてACQステータス監視部5dが設けられている。そして、バスBには、図5の監視状態監視部14に代えて、サブ側解析確認部18とメイン側解析確認部19が設けられている。

【0033】

メモリ制御部5に新たに設けられるACQステータス監視部5dは、サブ側解析確認部18およびメイン側解析確認部19の確認結果に基づき、ACQメモリ6への波形データの取り込み状態を監視する機能を有するものである。具体的には、サブ側解析確認部18およびメイン側解析確認部19の解析確認出力信号に基づき解析が完了したことを確認すると、次波形取込指示部5cにその旨を通知する。

【0034】

次波形取込指示部5cは、ACQステータス監視部5dからサブ側解析確認部18およびメイン側解析確認部19の解析が完了したことの通知を確認すると、図5の構成と同様に、メインデータ格納制御部5aおよびサブデータ格納制御部5bに対してACQメモリ6のメインデータ格納領域6aおよびサブデータ格納領域6bにそれぞれ異なる2系統の「時間軸」と「サンプリング・レート」で次の波形取込を指示する。

【0035】

図2は、ACQメモリ6のメインデータ格納領域6aおよびサブデータ格納領域6bにそれぞれ異なる2系統の「時間軸」と「サンプリング・レート」で取り込まれた波形データに対する本発明に基づく同時解析の表示画面例図である。

【0036】

図2において、画面の上側領域と下側領域には、それぞれ異なる「時間軸」と「サンプリング・レート」で取り込まれた同じ信号の波形データが表示されている。すなわち、画面の上側領域には遅いサンプリング・レート(たとえば10kS/s)でメインデータ格納領域6aに長時間にわたる波形データがたとえば「メイン側」として表示され、画面下側領域にはトリガが検出された場合に高速のサンプリング・レート(たとえば100MS/s)でサブデータ格納領域6bに取り込まれる所定区間の波形データがたとえば「サブ側」として拡大表示される。

【0037】

「メイン」側では、2値化されたデータ(0,1)に対し、定義されたプロトコルを解析し、さらにユーザーが予め定義した「データ変換テーブル」を通して、解析結果に変換されたデータのトレンド表示や、トレンドに対する測定結果表示を行っている。これらの解析結果をユーザーが参照することで、設計したデータのやり取りが実行されているかどうかを、アプリケーションの動作レベルで検証できる。

【0038】

一方、「サブ」側では、1つのパケットやフレームに着目して、メインの時間軸に比べ短くサンプリング・レートも高速な設定で波形観測を行っている。解析結果には、従来の図6と同様に、この観測波形に対して2値化されたデータ(0,1)と定義されたプロトコルに従ってデコードされたデータが表示されている。この解析結果をユーザが参照することで電気的に正しく通信されているかどうか、ノイズの影響を受けてないか、正しくコンパレータが作動しているかなど、物理レイヤーでの検証を行うことができる。

【0039】

これら2つの異なる測定条件の解析結果を同一の画面上に同時に表示することにより、アプリケーション層で起きている不具合かあるいは物理層で起きた不具合なのかを切り分けることができる。

【0040】

図3は図1における波形データ取込動作の流れを説明するフローチャートであり、ACQメモリ6のメインデータ格納領域6aおよびサブデータ格納領域6bに波形データ取込中もサブ側解析部12およびメイン側解析部13の解析結果を同期させる場合を示している。

【0041】

メモリ制御部5に対し、CPU8を介して波形取込開始が指示されると、メモリ制御部5はメインデータおよびサブデータの波形取込を開始する(ステップS1)。

【0042】

メインデータ格納制御部5aはメインデータ格納領域6aにA/D変換器4の出力データに基づく所定のメイン波形データが格納されるように制御し、サブデータ格納制御部5bはサブデータ格納領域6bに所定期間のA/D変換器4の出力データがサブ波形データとして格納されるように制御する(ステップS2)。

【0043】

これらACQメモリ6のメインデータ格納領域6aに格納されるメイン波形データおよびサブデータ格納領域6bに格納されるサブ波形データは、表示処理部10を介して表示部15に表示される(ステップS3)。

【0044】

メイン側解析部13が有効になると(ステップS4)、解析タスクが始動されて(ステップS11)、メインデータ格納領域6aに格納されるメイン波形データに対する解析が実行され(ステップS12)、解析結果が表示部15の表示画面にGUI表示されて(ステップS13)、解析タスクは終了し(ステップS14)、サブ側解析部12が有効か否かの判断ステップS5に遷移する。

【0045】

サブ側解析部12が有効になると(ステップS5)、再び解析タスクが始動されて(ステップS11)、サブデータ格納領域6bに格納されるサブ波形データに対する解析が実行され(ステップS12)、解析結果が表示部15の表示画面にGUI表示されて(ステップS13)、解析タスクは終了し(ステップS14)、次の波形を取り込むか否かの判断ステップS6に遷移する。

【0046】

メモリ制御部5は、波形データアクイジションのステータスが「Run」であればステップ1に戻って一連の処理を繰り返して実行し、ステータスが「Run」でなければ波形データ取込を終了する(ステップS6)。

【0047】

このように構成される本発明の波形測定装置は、同時に異なる2系統の「時間軸」と「サンプリング・レート」で異なるアクイジションデータ格納領域に取り込まれた波形データを同時に解析して、それらの解析結果を共通の表示画面上に同時に表示させることにより、異常現象を把握する的確性を高めることができる。

【0048】

なお、上記実施例では、シリアルバスを流れる電気信号をメイン側とサブ側で同時に解析し、関連性を有する解析結果を同時に表示させる例について説明したが、本発明はたとえば図4に示すように、インバータの電力損失を検証する場合の波形測定解析にも有効である。

【0049】

図4において、メイン側では階調制御式インバータの各インバータの出力波形を加算すして擬似正弦波を生成し、その生成された波形データに対して解析を実行することにより波形品位や出力特性についての検証を行っている。一方、サブ側では、各インバータのスイッチング時の電圧と電流の変化に着目し、電源ON/OFF区間の切替時に発生するスイッチング損失を解析している。

【0050】

これらにより、サブ側で解析している各インバータのスイッチング時の損失がメイン側で解析しているインバータの出力波形にどのような影響を及ぼしているかを、メイン側とサブ側がそれぞれ異なる設定条件で観測することで的確に検証できる。

【0051】

このように、本発明の波形測定装置は、測定対象となる試験物に対して、異なる2つの事象を観測できる設定条件で波形データを取り込み、それぞれ関連しあう解析結果を表示することができ、異常現象の把握のみならず特性などの品質の解析にも有効である。

【0052】

以上説明したように、本発明によれば、異なるアクイジションデータ格納領域に取り込まれた波形データを同時に解析してそれらの解析結果を同時に表示できる波形測定装置が実現でき、波形データに基づく異常現象の把握や各種電気特性などの品質解析にも好適である。

【符号の説明】

【0053】

1 入力端子

2 アッテネータ

3 プリアンプ

4 A/D変換器

5 メモリ制御部

5a メインデータ格納制御部

5b サブデータ格納制御部

5c 次波形取込制御部

5d ACQステータス監視部

6 ACQ(アクイジション)メモリ

7 測定処理部

8 CPU

9 メインメモリ

10 表示処理部

11 操作設定部

12 サブ側解析部

13 メイン側解析部

14 解析状態監視部

15 表示部

16 トリガ検出部

17 トリガ設定部

18 サブ側解析確認部

19 メイン側解析確認部

B 内部バス

【技術分野】

【0001】

本発明は、波形測定装置に関し、詳しくは、波形解析機能の改善に関する。

【背景技術】

【0002】

図5は、たとえば自動車に実装されているシリアルバスを流れる電気信号の測定解析などにも用いられる波形測定装置の一例を示す基本ブロック図である。図5において、入力端子1に入力されるシリアルバスを流れる電気信号は、アッテネータ2→プリアンプ3の信号経路を経て適正な振幅に調整された後、たとえば100MS/sで高速サンプリングを行うA/D変換器4に入力されて波形データとしてのデジタル信号に変換される。

【0003】

A/D変換器4の出力データは、メモリ制御部5に入力される。メモリ制御部5には、ACQ(アクイジション)メモリ6、測定処理部7およびCPU8が接続されている。なお、メモリ制御部5には、メインデータ格納制御部5aとサブデータ格納制御部5bと次波形取込制御部5cが設けられている。ACQメモリ6には、メインデータ格納領域6aとサブデータ格納領域6bが設けられている。

【0004】

CPU8には、メインメモリ9および内部バスBが接続されている。内部バスBには、表示処理部10、操作設定部11、サブ側解析部12、メイン側解析部13、解析状態監視部14などの各機能ブロックが接続されている。表示処理部10には表示部15が接続されている。

【0005】

プリアンプ3の出力端子にはトリガ検出部16も接続され、トリガ検出部16の出力端子はメモリ制御部5に接続されている。また、トリガ検出部16にはトリガ設定部17の出力端子も接続され、トリガ設定部17は内部バスBに接続されている。

【0006】

このような構成において、ユーザーは操作設定部11を操作し、メインデータ格納制御部5aにA/D変換器4から高速で変換出力される波形データをたとえば10kS/sの低速サンプリングデータになるように間引いてメインデータ格納領域6aに取り込むための時間軸とサンプリング・レートを設定するとともに、トリガ条件が成立した場合にA/D変換器4から出力される高速変換データを所定期間サブデータ格納制御部5bに取り込むためのプリアンプ3からA/D変換器4に入力される電気信号に対するトリガ条件をトリガ設定部17を介してトリガ検出部16に設定する。

【0007】

これにより、A/D変換器4から高速変換出力される波形データは、メインデータ格納制御部5aの制御にしたがって連続的に低速サンプリングデータに間引きされてメインデータ格納領域6aに取り込まれるとともに、トリガ条件が成立した場合にはサブデータ格納制御部5bの制御にしたがって所定期間の高速変換データがサブデータ格納制御部5bに取り込まれる。

【0008】

これらACQメモリ6のメインデータ格納領域6aに格納されるメイン波形データおよびサブデータ格納領域6bに格納されるサブ波形データは、表示処理部10を介して表示部15に表示される。

【0009】

測定処理部7は、ACQメモリ6のサブデータ格納制御部5bに取り込まれた波形データに基づき、立ち上がり時間や立ち下がり時間、パルス幅、パルス振幅など、測定信号波形に関する各種パラメータの測定を行う。これら各種パラメータの測定値は、たとえば測定処理部7の内部に設けられているメモリに格納される。

【0010】

サブ側解析部12およびメイン側解析部13は、それぞれに適した「時間軸」と「サンプリング・レート」で波形データを取り込むことにより、解析することができる。図6はサブ側解析部12における解析例の表示画面例図であり、2値化された波形データ(0,1)に対し定義されたプロトコルを解析した例を示している。図6において、「Break」は通信開始を表し、続く「0x55」は同期ビットを表し、次の「0xAA」はデータの宛先を表し、次の「0x55」はデータ列を表している。

【0011】

解析状態監視部14は、サブ側解析部12およびメイン側解析部13の波形データ解析状態を監視し、いずれかの解析部の波形解析が終了したことを確認すると、メモリ制御部5の次波形取込指示部5cに波形解析終了を通知する。これにより、次波形取込指示部5cは、メインデータ格納制御部5aまたはサブデータ格納制御部5bに次の波形取込を指示する。

【0012】

図7は、ACQメモリ6のメインデータ格納領域6aおよびサブデータ格納領域6bにそれぞれ異なる2系統の「時間軸」と「サンプリング・レート」で波形データを取り込み表示する表示画面例図である。

【0013】

図7の表示機能を使用することで、画面の上側領域には遅いサンプリング・レート(たとえば10kS/s)でメインデータ格納領域6aに長時間にわたる波形データをたとえば「メイン側」として表示でき、画面下側領域にはトリガが検出された場合に高速のサンプリング・レート(たとえば100MS/s)でサブデータ格納領域6bに取り込まれる所定区間の波形データをたとえば「サブ側」として拡大表示できるとともに、サブ側の波形データについては各種パラメータの測定結果も表示できる。

【0014】

図8は図5における波形データ取込動作の流れを説明するフローチャートであり、サブデータ格納領域6bに波形データ取込中もサブ側解析部12の解析結果を同期させる場合を示している。

【0015】

メモリ制御部5に対し、CPU8を介して波形取込開始が指示されると、メモリ制御部5はメインデータおよびサブデータの波形取込を開始する(ステップS1)。

【0016】

メインデータ格納制御部5aはメインデータ格納領域6aにA/D変換器4の出力データに基づく所定のメイン波形データが格納されるように制御し、サブデータ格納制御部5bはサブデータ格納領域6bに所定期間のA/D変換器4の出力データがサブ波形データとして格納されるように制御する(ステップS2)。

【0017】

これらACQメモリ6のメインデータ格納領域6aに格納されるメイン波形データおよびサブデータ格納領域6bに格納されるサブ波形データは、表示処理部10を介して表示部15に表示される(ステップS3)。

【0018】

サブ側解析部12が有効になると(ステップS4)、解析タスクが始動されて(ステップS11)、サブデータ格納領域6bに格納されるサブ波形データに対する解析が実行され(ステップS12)、解析結果が表示部15の表示画面にGUI表示されて(ステップS13)、解析タスクは終了し(ステップS14)、次の波形を取り込むか否かの判断ステップS5に遷移する。

【0019】

メモリ制御部5は、波形データアクイジションのステータスが「Run」であればステップ1に戻って一連の処理を繰り返して実行し、ステータスが「Run」でなければ波形データ取込を終了する(ステップS5)。

【0020】

特許文献1には、シリアルバスを流れる波形パターン解析を効率よく行える波形測定器の構成が記載されている。

【0021】

非特許文献1には、高速現象と低速現象が混在する波形データの測定に適した波形測定器の構成が記載されている。

【先行技術文献】

【特許文献】

【0022】

【特許文献1】特開2002−311060

【非特許文献】

【0023】

【非特許文献1】中山 悦郎、外3名、「スコープコーダDL750」、横河技報、横河電機株式会社、2003年、Vol.47 No.1(2003) p.27−30

【発明の開示】

【発明が解決しようとする課題】

【0024】

しかし、図5に示す従来の構成によれば、図6に示すように設定された「時間軸」と「サンプリング・レート」で観測された波形に対する異常信号などは解析できるものの、その測定範囲を超えた「時間軸」や「サンプリング・レート」の設定で解析できるたとえば物理層とアプリケーション層などの異なる測定域で発生する異常を同時に観察することはできない。

【0025】

また、図7に示すようにサブ側の表示領域に表示されている波形に対しては解析することができるが、メイン側およびサブ側のそれぞれの表示領域に表示された波形に対して同時に解析することはできず、メイン側とサブ側を同時に解析することで有用となるような解析方法を示すこともできなかった。

【0026】

本発明は、これらの課題を解決するものであり、その目的は、異なるアクイジションデータ格納領域に取り込まれた波形データを同時に解析してそれらの解析結果を同時に表示できる波形測定装置を実現することにある。

【課題を解決するための手段】

【0027】

このような課題を達成するために、本発明のうち請求項1記載の発明は、

同時に異なる「時間軸」と「サンプリング・レート」でアクイジションメモリの異なるデータ格納領域に取り込まれた波形データを同時に解析して、それらの解析結果を共通の表示画面上に同時に表示させる波形測定装置であって、

前記各データ格納領域に取り込まれた波形データに対する解析がそれぞれ完了したことを確認する複数の解析確認部と、

前記アクイジションメモリへの波形データの取り込みを制御するメモリ制御部に設けられ前記各データ格納領域への波形データの取り込みを制御する複数の格納制御部と、次の波形データの取り込みを指示する次波形取込指示部と、前記アクイジションメモリへの波形データの取り込み状態を監視するアクイジションステータス監視部とを具備し、

前記アクイジションステータス監視部は、前記複数の解析確認部の解析確認出力信号に基づき前記各データ格納領域に取り込まれた波形データに対する解析がそれぞれ完了したことを確認すると前記次波形取込指示部にその旨を通知し、前記次波形取込指示部は前記アクイジションステータス監視部からの通知を確認すると前記各データ格納領域への次の波形データの取り込みを指示することを特徴とする。

【0028】

請求項2の発明は、請求項1記載の波形測定装置において、

前記アクイジションメモリには第1の波形データ格納領域と第2の波形データ格納領域が設けられていて、第1の波形データ格納領域には第1の格納制御部で連続的に低速サンプリングデータに間引きされた波形データが取り込まれ、第2の波形データ格納領域には所定のトリガ条件が成立したときに第2の格納制御部の制御にしたがって所定期間の高速変換データが取り込まれることを特徴とする波形測定装置である。

【0029】

請求項3記載の発明は、請求項1または請求項2に記載の波形測定装置において、

自動車に実装されているシリアルバスを流れる電気信号を測定解析することを特徴とする。

【発明の効果】

【0030】

これらの構成により、異なるアクイジションデータ格納領域に取り込まれた波形データを同時に解析してそれらの解析結果を同時に表示でき、異常現象把握の的確性を高めることができる。

【図面の簡単な説明】

【0031】

【図1】本発明の一実施例を示すブロック図である。

【図2】本発明に基づく同時解析の表示画面例図である。

【図3】図1における波形データ取込動作の流れを説明するフローチャートである。

【図4】インバータの電力損失を検証するための波形測定解析例図である。

【図5】従来の波形測定装置の一例を示す基本ブロック図である。

【図6】図5のサブ側解析部12における解析例の表示画面例図である。

【図7】異なる2系統の「時間軸」と「サンプリング・レート」で波形データを取り込み表示する表示画面例図である。

【図8】図5における波形データ取込動作の流れを説明するフローチャートである。

【発明を実施するための最良の形態】

【0032】

以下、本発明の実施の形態について、図面を用いて詳細に説明する。図1は本発明の一実施例を示すブロック図であり、図5と共通する部分には同一の符号を付けている。図1において、メモリ制御部5には図5の構成に加えてACQステータス監視部5dが設けられている。そして、バスBには、図5の監視状態監視部14に代えて、サブ側解析確認部18とメイン側解析確認部19が設けられている。

【0033】

メモリ制御部5に新たに設けられるACQステータス監視部5dは、サブ側解析確認部18およびメイン側解析確認部19の確認結果に基づき、ACQメモリ6への波形データの取り込み状態を監視する機能を有するものである。具体的には、サブ側解析確認部18およびメイン側解析確認部19の解析確認出力信号に基づき解析が完了したことを確認すると、次波形取込指示部5cにその旨を通知する。

【0034】

次波形取込指示部5cは、ACQステータス監視部5dからサブ側解析確認部18およびメイン側解析確認部19の解析が完了したことの通知を確認すると、図5の構成と同様に、メインデータ格納制御部5aおよびサブデータ格納制御部5bに対してACQメモリ6のメインデータ格納領域6aおよびサブデータ格納領域6bにそれぞれ異なる2系統の「時間軸」と「サンプリング・レート」で次の波形取込を指示する。

【0035】

図2は、ACQメモリ6のメインデータ格納領域6aおよびサブデータ格納領域6bにそれぞれ異なる2系統の「時間軸」と「サンプリング・レート」で取り込まれた波形データに対する本発明に基づく同時解析の表示画面例図である。

【0036】

図2において、画面の上側領域と下側領域には、それぞれ異なる「時間軸」と「サンプリング・レート」で取り込まれた同じ信号の波形データが表示されている。すなわち、画面の上側領域には遅いサンプリング・レート(たとえば10kS/s)でメインデータ格納領域6aに長時間にわたる波形データがたとえば「メイン側」として表示され、画面下側領域にはトリガが検出された場合に高速のサンプリング・レート(たとえば100MS/s)でサブデータ格納領域6bに取り込まれる所定区間の波形データがたとえば「サブ側」として拡大表示される。

【0037】

「メイン」側では、2値化されたデータ(0,1)に対し、定義されたプロトコルを解析し、さらにユーザーが予め定義した「データ変換テーブル」を通して、解析結果に変換されたデータのトレンド表示や、トレンドに対する測定結果表示を行っている。これらの解析結果をユーザーが参照することで、設計したデータのやり取りが実行されているかどうかを、アプリケーションの動作レベルで検証できる。

【0038】

一方、「サブ」側では、1つのパケットやフレームに着目して、メインの時間軸に比べ短くサンプリング・レートも高速な設定で波形観測を行っている。解析結果には、従来の図6と同様に、この観測波形に対して2値化されたデータ(0,1)と定義されたプロトコルに従ってデコードされたデータが表示されている。この解析結果をユーザが参照することで電気的に正しく通信されているかどうか、ノイズの影響を受けてないか、正しくコンパレータが作動しているかなど、物理レイヤーでの検証を行うことができる。

【0039】

これら2つの異なる測定条件の解析結果を同一の画面上に同時に表示することにより、アプリケーション層で起きている不具合かあるいは物理層で起きた不具合なのかを切り分けることができる。

【0040】

図3は図1における波形データ取込動作の流れを説明するフローチャートであり、ACQメモリ6のメインデータ格納領域6aおよびサブデータ格納領域6bに波形データ取込中もサブ側解析部12およびメイン側解析部13の解析結果を同期させる場合を示している。

【0041】

メモリ制御部5に対し、CPU8を介して波形取込開始が指示されると、メモリ制御部5はメインデータおよびサブデータの波形取込を開始する(ステップS1)。

【0042】

メインデータ格納制御部5aはメインデータ格納領域6aにA/D変換器4の出力データに基づく所定のメイン波形データが格納されるように制御し、サブデータ格納制御部5bはサブデータ格納領域6bに所定期間のA/D変換器4の出力データがサブ波形データとして格納されるように制御する(ステップS2)。

【0043】

これらACQメモリ6のメインデータ格納領域6aに格納されるメイン波形データおよびサブデータ格納領域6bに格納されるサブ波形データは、表示処理部10を介して表示部15に表示される(ステップS3)。

【0044】

メイン側解析部13が有効になると(ステップS4)、解析タスクが始動されて(ステップS11)、メインデータ格納領域6aに格納されるメイン波形データに対する解析が実行され(ステップS12)、解析結果が表示部15の表示画面にGUI表示されて(ステップS13)、解析タスクは終了し(ステップS14)、サブ側解析部12が有効か否かの判断ステップS5に遷移する。

【0045】

サブ側解析部12が有効になると(ステップS5)、再び解析タスクが始動されて(ステップS11)、サブデータ格納領域6bに格納されるサブ波形データに対する解析が実行され(ステップS12)、解析結果が表示部15の表示画面にGUI表示されて(ステップS13)、解析タスクは終了し(ステップS14)、次の波形を取り込むか否かの判断ステップS6に遷移する。

【0046】

メモリ制御部5は、波形データアクイジションのステータスが「Run」であればステップ1に戻って一連の処理を繰り返して実行し、ステータスが「Run」でなければ波形データ取込を終了する(ステップS6)。

【0047】

このように構成される本発明の波形測定装置は、同時に異なる2系統の「時間軸」と「サンプリング・レート」で異なるアクイジションデータ格納領域に取り込まれた波形データを同時に解析して、それらの解析結果を共通の表示画面上に同時に表示させることにより、異常現象を把握する的確性を高めることができる。

【0048】

なお、上記実施例では、シリアルバスを流れる電気信号をメイン側とサブ側で同時に解析し、関連性を有する解析結果を同時に表示させる例について説明したが、本発明はたとえば図4に示すように、インバータの電力損失を検証する場合の波形測定解析にも有効である。

【0049】

図4において、メイン側では階調制御式インバータの各インバータの出力波形を加算すして擬似正弦波を生成し、その生成された波形データに対して解析を実行することにより波形品位や出力特性についての検証を行っている。一方、サブ側では、各インバータのスイッチング時の電圧と電流の変化に着目し、電源ON/OFF区間の切替時に発生するスイッチング損失を解析している。

【0050】

これらにより、サブ側で解析している各インバータのスイッチング時の損失がメイン側で解析しているインバータの出力波形にどのような影響を及ぼしているかを、メイン側とサブ側がそれぞれ異なる設定条件で観測することで的確に検証できる。

【0051】

このように、本発明の波形測定装置は、測定対象となる試験物に対して、異なる2つの事象を観測できる設定条件で波形データを取り込み、それぞれ関連しあう解析結果を表示することができ、異常現象の把握のみならず特性などの品質の解析にも有効である。

【0052】

以上説明したように、本発明によれば、異なるアクイジションデータ格納領域に取り込まれた波形データを同時に解析してそれらの解析結果を同時に表示できる波形測定装置が実現でき、波形データに基づく異常現象の把握や各種電気特性などの品質解析にも好適である。

【符号の説明】

【0053】

1 入力端子

2 アッテネータ

3 プリアンプ

4 A/D変換器

5 メモリ制御部

5a メインデータ格納制御部

5b サブデータ格納制御部

5c 次波形取込制御部

5d ACQステータス監視部

6 ACQ(アクイジション)メモリ

7 測定処理部

8 CPU

9 メインメモリ

10 表示処理部

11 操作設定部

12 サブ側解析部

13 メイン側解析部

14 解析状態監視部

15 表示部

16 トリガ検出部

17 トリガ設定部

18 サブ側解析確認部

19 メイン側解析確認部

B 内部バス

【特許請求の範囲】

【請求項1】

同時に異なる「時間軸」と「サンプリング・レート」でアクイジションメモリの異なるデータ格納領域に取り込まれた波形データを同時に解析して、それらの解析結果を共通の表示画面上に同時に表示させる波形測定装置であって、

前記各データ格納領域に取り込まれた波形データに対する解析がそれぞれ完了したことを確認する複数の解析確認部と、

前記アクイジションメモリへの波形データの取り込みを制御するメモリ制御部に設けられ前記各データ格納領域への波形データの取り込みを制御する複数の格納制御部と、次の波形データの取り込みを指示する次波形取込指示部と、前記アクイジションメモリへの波形データの取り込み状態を監視するアクイジションステータス監視部とを具備し、

前記アクイジションステータス監視部は、前記複数の解析確認部の解析確認出力信号に基づき前記各データ格納領域に取り込まれた波形データに対する解析がそれぞれ完了したことを確認すると前記次波形取込指示部にその旨を通知し、前記次波形取込指示部は前記アクイジションステータス監視部からの通知を確認すると前記各データ格納領域への次の波形データの取り込みを指示することを特徴とする波形測定装置。

【請求項2】

前記アクイジションメモリには第1の波形データ格納領域と第2の波形データ格納領域が設けられていて、第1の波形データ格納領域には第1の格納制御部で連続的に低速サンプリングデータに間引きされた波形データが取り込まれ、第2の波形データ格納領域には所定のトリガ条件が成立したときに第2の格納制御部の制御にしたがって所定期間の高速変換データが取り込まれることを特徴とする請求項1記載の波形測定装置。

【請求項3】

自動車に実装されているシリアルバスを流れる電気信号を測定解析することを特徴とする請求項1または請求項2記載の波形測定装置。

【請求項1】

同時に異なる「時間軸」と「サンプリング・レート」でアクイジションメモリの異なるデータ格納領域に取り込まれた波形データを同時に解析して、それらの解析結果を共通の表示画面上に同時に表示させる波形測定装置であって、

前記各データ格納領域に取り込まれた波形データに対する解析がそれぞれ完了したことを確認する複数の解析確認部と、

前記アクイジションメモリへの波形データの取り込みを制御するメモリ制御部に設けられ前記各データ格納領域への波形データの取り込みを制御する複数の格納制御部と、次の波形データの取り込みを指示する次波形取込指示部と、前記アクイジションメモリへの波形データの取り込み状態を監視するアクイジションステータス監視部とを具備し、

前記アクイジションステータス監視部は、前記複数の解析確認部の解析確認出力信号に基づき前記各データ格納領域に取り込まれた波形データに対する解析がそれぞれ完了したことを確認すると前記次波形取込指示部にその旨を通知し、前記次波形取込指示部は前記アクイジションステータス監視部からの通知を確認すると前記各データ格納領域への次の波形データの取り込みを指示することを特徴とする波形測定装置。

【請求項2】

前記アクイジションメモリには第1の波形データ格納領域と第2の波形データ格納領域が設けられていて、第1の波形データ格納領域には第1の格納制御部で連続的に低速サンプリングデータに間引きされた波形データが取り込まれ、第2の波形データ格納領域には所定のトリガ条件が成立したときに第2の格納制御部の制御にしたがって所定期間の高速変換データが取り込まれることを特徴とする請求項1記載の波形測定装置。

【請求項3】

自動車に実装されているシリアルバスを流れる電気信号を測定解析することを特徴とする請求項1または請求項2記載の波形測定装置。

【図1】

【図2】

【図3】

【図5】

【図6】

【図7】

【図8】

【図4】

【図2】

【図3】

【図5】

【図6】

【図7】

【図8】

【図4】

【公開番号】特開2013−64655(P2013−64655A)

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願番号】特願2011−203880(P2011−203880)

【出願日】平成23年9月17日(2011.9.17)

【出願人】(000006507)横河電機株式会社 (4,443)

【出願人】(596157780)横河メータ&インスツルメンツ株式会社 (43)

【上記1名の代理人】

【識別番号】000006507

【氏名又は名称】横河電機株式会社

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願日】平成23年9月17日(2011.9.17)

【出願人】(000006507)横河電機株式会社 (4,443)

【出願人】(596157780)横河メータ&インスツルメンツ株式会社 (43)

【上記1名の代理人】

【識別番号】000006507

【氏名又は名称】横河電機株式会社

[ Back to top ]