消費電力錯乱型論理回路及び情報記憶媒体

【課題】入力信号の組合せにより充電経路の平均数が異なるため、及び後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減する。

【解決手段】論理回路1は、入力信号X、Yと乱数信号rとに基づいて生成される出力論理状態を出力線Z1に出力する論理演算回路10と、制御信号en1に応じて出力線Z1の出力状態を制御し、論理演算回路10の出力論理状態を無効とする出力無効状態である場合に、出力線Z1から電源線VDDに通じる経路を遮断し、電源線VDDの電位により出力線Z1を充電する出力制御部20と、出力線Z1の出力状態に基づいて出力する状態を無効とするマスク状態に、制御信号en2に応じて切り替える出力段回路30とを備える。

【解決手段】論理回路1は、入力信号X、Yと乱数信号rとに基づいて生成される出力論理状態を出力線Z1に出力する論理演算回路10と、制御信号en1に応じて出力線Z1の出力状態を制御し、論理演算回路10の出力論理状態を無効とする出力無効状態である場合に、出力線Z1から電源線VDDに通じる経路を遮断し、電源線VDDの電位により出力線Z1を充電する出力制御部20と、出力線Z1の出力状態に基づいて出力する状態を無効とするマスク状態に、制御信号en2に応じて切り替える出力段回路30とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、暗号/復号処理の際に電力消費を解析して、秘密鍵を解明する電力解析攻撃を防ぐ消費電力錯乱型論理回路及び情報記憶媒体に関する。

【背景技術】

【0002】

ICカードなどの暗号処理を行う情報記憶媒体の電力消費を解析処理することにより、暗号処理に使用する秘密鍵を解明する電力解析攻撃がある。この攻撃に対して論理回路レベルの対策回路が、開示されている。非特許文献1では、乱数を用いて入力信号及び論理演算の正論理/負論理をランダムに切り替えるRSL(Random Switching Logic)回路を開示している。CMOS(Complementary Metal Oxide Semiconductor:相補型金属酸化膜半導体)集積回路が動作する場合の電力消費は、論理ゲートの出力負荷容量を充放電させる電流による電力が支配的である。そのため、RSL回路は、論理ゲートの出力を乱数によりランダムに遷移させることにより、電力消費の統計値と秘密鍵の相関を無くすことを意図した回路である。

【0003】

図12の(a)は、非特許文献1が開示するRSLによるNAND(否定論理積)ゲート(以下、RSL−NANDという。)を示す。元のNANDゲートの入力信号をa、bとし、出力をc(=a NAND b)とする。RSL−NANDの入力信号X、Yは、乱数rと入力信号a、bとをそれぞれXOR(排他的論理和)演算された値である(X=a XOR r、Y=b XOR r)。また、RSL−NANDの出力Zは、同じく乱数信号rと出力cをXOR演算した値である(Z=c XOR r)。入力信号a、bをXOR演算する乱数と出力cをXOR演算する乱数は同じ値であり、ゲート動作ごとに毎回異なる値にする。

また、RSL−NANDは、制御信号enを備える。制御信号enは、“1”の場合にRSL−NANDの出力を無効状態にし、RSL−NANDの出力を“0”に固定する。また、制御信号enは、“0”の場合にRSL−NANDの出力を有効状態にし、入力信号X、Y、rの値に応じた出力にさせる。入力信号X、Y、rが遷移する期間では、制御信号enは“1”にされ、入力が確定した後に制御信号enは“0”にされ、RSL−NANDの出力を有効にする。これは、入力信号X、Y、rが遷移する際に消費される電力をなくすためである。

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】D.Suzuki et al.,“Random Switching Logic: A New Countermeasure against DPA and Second-Order DPA at the Logic Level”IEICE TRANS.FUNDAMENTALS, VOL.E90-A, NO.1, JANUARY 2007.

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、図12の(a)が示すRSL−NANDでは、制御信号enが“1”から”0”に遷移し、無効状態から有効状態に切り替わる際に電力消費が発生する。この電力消費は、入力信号X、Y、rの状態により電力消費波形が異なる。

図12の(b)は、RSL−NANDの論理と“1”を出力する際の充電パスの数を示す論理表である。乱数rが“0”の場合、充電パスは、入力信号a、bの組合せ(1)において3本のパス、組合せ(2)及び(3)において1本のパスとなる。また、乱数信号rが“1”の場合、充電パスは、組合せ(4)において1本のパスとなる。そして、組合せ(1)から(4)の各場合における平均パス数、すなわち、rが“0”である場合のパス数とrが“1”である場合のパス数との平均は、順に3/2、1/2、1/2、1/2となる。充電のパス数が異なると、充電電流と充電速度に差が生じる。これら2つの差は、情報記憶媒体の外部から観測できる電力消費波形の差を生じさせる。この電力消費波形の差により、入力信号a、bの組合せが特定される可能性がある。すなわち、上述のRSL−NANDでは、入力信号a、bの組合せにより充電経路(パス)の平均数が異なることから電力消費波形の変化が生じるという問題がある。

【0006】

また、充電速度が異なると、RSL−NANDの出力遷移時間の違いとなって、後段のゲートの動作タイミングに影響する。後段のゲートの動作タイミングが異なれば、情報記憶媒体の外部から観測できる電力消費波形の差を生じさせる。すなわち、上述のRSL−NANDでは、後段のゲートの動作タイミングが異なることから電力消費波形に変化が生じるという問題がある。

【0007】

本発明は、上記問題を解決すべくなされたもので、その目的は、入力信号の組合せにより充電経路の平均数が異なるために生じる電力消費波形の変化と、後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減する消費電力錯乱型論理回路、及び情報記憶媒体を提供することにある。

【課題を解決するための手段】

【0008】

上記問題を解決するために、本発明は、第1の電位が第1の供給線から供給され、該第1の電位より低い第2の電位が第2の供給線から供給され、入力される入力信号と乱数信号とに基づいて生成される出力論理状態を出力線に出力する論理演算回路と、入力される第1の制御信号に応じて前記出力線の出力状態を制御し、前記出力論理状態を無効とする出力無効状態である場合に、前記出力線から前記第2の供給線に通じる第1の経路を遮断し、前記第1の電位により前記出力線を充電する出力制御部と、前記論理演算回路の後段に設けられ、前記出力線の出力状態に基づいて出力する状態を無効とするマスク状態に、入力される第2の制御信号に応じて切り替える出力段回路とを備える消費電力錯乱型論理回路である。

【0009】

また、本発明は上記発明において、前記出力制御部は、前記出力無効状態を解除した場合、前記第1の経路を導通させ、前記生成される論理状態に応じて、前記第2の電位により前記出力線を放電することを特徴とする。

【0010】

また、本発明は上記発明において、前記論理演算回路は、前記入力信号と前記乱数信号とに基づいて前記第1の電位により前記出力線を充電するPネット部と、前記入力信号と前記乱数信号とに基づいて前記第2の電位により前記出力線を放電するNネット部とが相補に動作して前記出力論理状態を生成し、前記第1の経路は、前記出力線から前記Nネット部を介して前記第2の供給線に通じる経路であることを特徴とする。

【0011】

また、本発明は上記発明において、前記消費電力錯乱型論理回路は、前記第1の制御信号又は前記第2の制御信号に応じて、前記第1の供給線から前記Pネット部を介して前記出力線に通じる第2の経路を遮断するPネット遮断部を備えることを特徴とする。

【0012】

また、本発明は上記発明において、前記入力信号及び前記乱数信号は、前記出力制御部が前記出力無効状態にあり、前記出力線が前記第1の電位になった後に、変更され、前記出力制御部は、前記入力信号及び前記乱数信号の変更が確定した後に、前記第1の制御信号に基づいて前記出力無効状態を解除し、前記出力段回路は、前記出力無効状態が解除され、前記出力線の出力状態が確定した後に、前記第2の制御信号に基づいて前記マスク状態を解除することを特徴とする。

【0013】

また、本発明は上記発明において、前記入力信号及び前記乱数信号は、前記出力制御部が前記出力無効状態にあり、前記Pネット遮断部が前記第2の経路を遮断した後に変更され、前記出力制御部は、前記入力信号及び前記乱数信号の変更が確定した後に、前記第1の制御信号に基づいて前記出力無効状態を解除し、前記出力段回路は、前記出力無効状態が解除され、前記出力線の出力状態が確定した後に、前記第2の制御信号に基づいて前記マスク状態を解除することを特徴とする。

【0014】

また、本発明は上記発明において、前記論理演算回路は、前記入力信号に基づいて予め定められた論理演算処理に応じた論理状態を生成し、前記乱数信号に基づき、前記入力信号を反転させた前記論理演算処理を行うか否か、及び前記出力論理状態を前記論理状態から反転したものにするか否かを切り替えることを特徴とする。

【0015】

また、本発明は、秘密鍵と情報を記憶する記憶部と、前記乱数信号を生成する乱数生成部と、上記発明のいずれかの消費電力錯乱型論理回路を含み、前記秘密鍵に応じて暗号処理を行う暗号処理部とを備える情報記憶媒体である。

【発明の効果】

【0016】

本発明によれば、論理演算回路が、第1の電位が第1の供給線から供給され、第1の電位より低い第2の電位が第2の供給線から供給され、入力される入力信号と乱数信号とに基づいて生成される出力論理状態を出力線に出力する。出力制御部が、第1の制御信号に応じて論理演算回路の出力線の出力状態を制御し、論理演算回路の出力論理状態を無効とする出力無効状態である場合に、論理演算回路の出力線から第2の供給線に通じる第1の経路を遮断し、第1の電位により前記出力線を充電する。これにより、入力信号の組合せによらず、充電経路の数が同じになる。そのため、消費電力錯乱型論理回路は、充電経路の平均数が異なるために生じる電力消費波形の変化を低減できる。また、論理演算回路の後段に設けられた出力段回路が、論理演算回路の出力線の出力状態に基づいて出力する出力状態を無効とするマスク状態に、入力される第2の制御信号に応じて切り替える。これにより、消費電力錯乱型論理回路は、論理演算回路の出力線の動作タイミングの変化をマスクし、消費電力錯乱型論理回路の後段のゲートの動作タイミングの変化を低減できる。そのため、消費電力錯乱型論理回路は、後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減できる。

【図面の簡単な説明】

【0017】

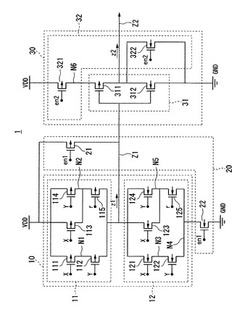

【図1】第1の実施形態による論理回路を示すブロック図である。

【図2】同実施形態における論理回路の論理表を示す図である。

【図3】同実施形態における論理回路のシーケンスを示すタイムチャートである。

【図4】第2の実施形態による論理回路を示すブロック図である。

【図5】同実施形態における論理回路のシーケンスを示すタイムチャートである。

【図6】第3の実施形態による論理回路を示すブロック図である。

【図7】同実施形態における論理回路のシーケンスを示すタイムチャートである。

【図8】第4の実施形態による携帯可能情報記憶媒体を示すブロック図である。

【図9】同実施形態における暗号処理部を示すブロック図である。

【図10】第5の実施形態による論理回路を示すブロック図である。

【図11】同実施形態における論理回路の論理表を示す図である。

【図12】従来技術による論理回路と論理表を示す図である。

【発明を実施するための形態】

【0018】

<第1の実施形態>

以下、本発明の第1の実施形態による論理回路について図面を参照して説明する。

図1は、本実施形態における論理回路を示すブロック図である。

図1に示される消費電力錯乱型論理回路である論理回路1は、論理演算回路10、出力制御部20及び出力段回路30を備える。

論理演算回路10は、電源線VDDと電源線GNDとの間に配置され、Pネット部11とNネット部12を備える。論理演算回路10は、入力信号X、Yと乱数信号rに基づき、Pネット部11とNネット部12とが相補に動作して生成される出力論理状態を出力線Z1に出力する。

Pネット部11は、電源線VDDと出力線Z1との間に配置され、入力信号X、Yと乱数信号rとに基づいて電源線VDDの電位により出力線Z1を充電し、論理レベル“1”を出力する。

Nネット部12は、出力線Z1と電源線GNDとの間に配置され、入力信号X、Yと乱数信号rとに基づいて電源線GNDの電位により出力線Z1を放電し、論理レベル“0”を出力する。

【0019】

Pネット部11は、Pチャネル型金属酸化膜半導体電界効果トランジスタ(P Channel Metal Oxide Semiconductor Field Effect Transistor、以下、PMOSという。)111〜115を備える。PMOS111、112は、電源線VDDと出力線Z1との間に直列に配置される。PMOS111は、ソース端子が電源線VDDに、ドレイン端子がノードN1にそれぞれ接続され、ゲート端子に入力信号Xが供給される。PMOS112は、ソース端子がノードN1、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に入力信号Yが供給される。

また、PMOS113、114は、電源線VDDとノードN2との間に並列に接続される。PMOS113は、ソース端子が電源線VDDに、ドレイン端子がノードN2にそれぞれ接続され、ゲート端子に入力信号Xが供給される。PMOS114は、ソース端子が電源線VDDに、ドレイン端子がノードN2にそれぞれ接続され、ゲート端子に入力信号Yが供給される。

また、PMOS115は、ソース端子がノードN2に、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に乱数信号rが供給される。

【0020】

Nネット部12は、Nチャネル型金属酸化膜半導体電界効果トランジスタ(N Channel Metal Oxide Semiconductor Field Effect Transistor、以下、NMOSという。)121〜125を備える。NMOS121、122は、出力線Z1とノードN4との間に直列に配置される。NMOS121は、ソース端子がノードN3に、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に入力信号Xが供給される。NMOS122は、ソース端子がノードN4、ドレイン端子がノードN3にそれぞれ接続され、ゲート端子に入力信号Yが供給される。

また、NMOS123、124は、出力線Z1とノードN5との間に並列に接続される。NMOS123は、ソース端子がN5に、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に入力信号Xが供給される。NMOS124は、ソース端子がノードN5に、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に入力信号Yが供給される。

また、NMOS125は、ソース端子がノードN4に、ドレイン端子がノードN5にそれぞれ接続され、ゲート端子に乱数信号rが供給される。

【0021】

出力制御部20は、PMOS21とNMOS22とを備え、制御信号en1に応じて出力線Z1の出力状態を制御する。出力制御部20は、PMOS21とNMOS22とにより、制御信号en1に応じて論理演算回路10の出力論理状態を無効にする。

PMOS21は、電源線VDDと出力線Z1との間に、Pネット部11と並列に配置される。PMOS21は、ソース端子が電源線VDDに、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に制御信号en1が供給される。PMOS21は、制御信号en1が“0”の場合(出力無効状態とする場合)に、電源線VDDと出力線Z1との間を導通して、出力線Z1を論理レベル“1”に充電する。これにより、Pネット部11は無効化される。

また、NMOS22は、出力線Z1と電源船GNDとの間に、Nネット部12と直列に配置される。NMOS22は、ソース端子が電源線GNDに、ドレイン端子がノードN4にそれぞれ接続され、ゲート端子に制御信号en1が供給される。NMOS22は、制御信号en1が“0”の場合(出力無効状態とする場合)に、電源線GNDからNネット部12を介して出力線Z1に通じる経路を遮断して、Nネット部12を無効化する。

【0022】

出力段回路30は、論理演算回路10の後段に配置され、インバータ部31と出力段制御部32とを備える。出力段回路30は、論理演算回路10の出力線Z1の出力状態に基づいて、論理回路1の出力線Z2に論理レベル“1”又は“0”を出力する。また、出力段回路30は、制御信号en2に応じて、出力線Z2の出力状態を無効にするマスク状態に切り替わる。

インバータ部31は、PMOS311とNMOS312とを備え、論理演算回路10の出力線Z1に出力される論理状態を反転した論理レベル“1”又は“0”を出力線Z2に出力する。

PMOS311とNMOS312は、ゲート端子が出力線Z1に、ドレイン端子が出力線Z2にそれぞれ接続される。また、PMOS311は、ソース端子がノードN6に接続される。NMOS312は、ソース端子が電源線GNDに接続される。

【0023】

出力段制御部32は、PMOS321とNMOS322とを備え、制御信号en2に応じて、出力線Z2の出力状態を無効にするマスク状態に切り替わる。PMOS321は、電源線VDDとインバータ部31との間に配置される。PMOS321は、ソース端子が電源線VDDに、ドレイン端子がノードN6にそれぞれ接続され、ゲート端子に制御信号en2が供給される。PMOS321は、制御信号en2が“1”の場合(マスク状態とする場合)に、電源線VDDからインバータ部31を遮断して、インバータ部31を無効化する。

NMOS322は、出力線Z2と電源線GNDとの間に、NMOS312と並列に配置される。NMOS322は、ソース端子が電源線GNDに、ドレイン端子が出力線Z2にそれぞれ接続され、ゲート端子に制御信号en2が供給される。NMOS322は、制御信号en2が“1”の場合(マスク状態とする場合)に、電源線GNDと出力線Z2との間を導通して、出力線Z2を論理レベル“0”に放電する。これにより、出力段制御部32は、マスク状態である場合に、出力線Z2に論理レベル“0”を出力する。

【0024】

次に、本実施形態の動作について説明する。

論理回路1は、入力信号a、bをAND(論理積)演算した出力cを得るためのAND回路である。論理回路1の入力信号X、Yは、入力信号a、bと、乱数信号rとをそれぞれXOR(排他的論理和)演算された値である(X=a XOR r、Y=b XOR r)。また、論理回路1の出力線Z2の出力z2は、同じく乱数rと出力cをXOR演算した値である(z2=c XOR r)。入力a、bをXOR演算する乱数信号rと出力cをXOR演算する乱数信号rは同じ値であり、乱数信号rはゲート動作ごとに毎回異なる値にする。

【0025】

また、論理演算回路10は、入力信号a、bをNAND(否定論理積)演算した結果を乱数信号rとXOR演算した出力z1を得るためのNAND/NOR(否定論理和)演算回路である。乱数信号rが“0”の場合、論理演算回路10は、入力信号X、YのNAND演算回路として機能する(z1=X NAND Y)。また、乱数信号rが“1”の場合、論理演算回路10は、入力信号X、YのNOR演算回路として機能する(z1=X NOR Y)。その原理は、式(1)から式(3)に示される。

【0026】

z1=(a NAND b) XOR r ・・・(1)

【0027】

式(1)は、論理演算回路10の論理演算を示す式である。

【0028】

[r=“0”の場合]

X=a XOR r=a、Y=b XOR r=b、

z1=(a NAND b)XOR r=X NAND Y ・・・(2)

【0029】

式(2)は、乱数信号rが“0”の場合における論理演算回路10の論理演算を示す式である。乱数信号rが“0”の場合、入力信号a、bはそれぞれ入力信号X、Yと等しくなる。このため、論理演算回路10の出力線Z1の論理は、入力信号XとYのNAND演算したものになる。

【0030】

[r=“1”の場合]

X=a XOR r=NOT(a)、Y=b XOR r=NOT(b)、

z1=NOT(NOT(X) NAND NOT(Y))=NOT(X OR Y)=X NOR Y ・・・(3)

【0031】

式(3)は、乱数信号rが“1”の場合における論理演算回路10の論理演算を示す式である。乱数信号rが“1”の場合、入力信号a、bはそれぞれ入力信号X、YのNOT(否定)演算した値になる。このため、論理演算回路10の出力線Z1の論理は、入力信号XとYをそれぞれNOT演算したものをNAND演算し、更にその演算結果をNOT演算したものになる。ト゛・モルガンの定理により、(NOT(X) NAND NOT(Y))は、入力信号XとYのOR(論理和)演算(X OR Y)に置き換えられる。これにより、論理演算回路10の出力線Z1の論理は、入力信号XとYのNOR演算したものになる。

【0032】

論理演算回路10は、乱数信号rが“0”の場合、Pネット部11のPMOS115がオンして、電源線VDDに並列接続されたPMOS113、114が有効になる。また、Nネット部12のNMOS125がオフして、出力線Z1に並列接続されたNMOS123、124が無効になる。これにより、出力線Z1は、PMOS113、114と、出力線Z1にノードN3を介して直列接続されたNMOS121、122とで論理演算される出力論理状態が出力される。つまり、論理演算回路10は、入力信号XとYのNAND演算回路として機能する。なお、この場合、PMOS111、112は、出力論理状態を決める際に関係しない。

また、論理演算回路10は、乱数信号rが“1”の場合、Pネット部11のPMOS115がオフして、電源線VDDに並列接続されたPMOS113、114が無効になる。また、Nネット部12のNMOS125がオンして、出力線Z1に並列接続されたNMOS123、124が有効になる。これにより、出力線Z1は、NMOS123、124と、出力線Z1にノードN1を介して直列接続されたPMOS111、112とで論理演算される出力論理状態が出力される。つまり、論理演算回路10は、入力信号XとYのNOR演算回路として機能する。なお、この場合、NMOS121、122は、出力論理状態を決める際に関係しない。

【0033】

論理演算回路10により論理演算された出力z1は、出力線Z1を介して出力段回路30のインバータ部31に供給される。インバータ部31は、PMOS311とNMOS312により、出力z1の出力論理状態を反転して、出力線Z2に出力z2として出力する。

これにより、論理回路1は、乱数信号rに応じて、入力信号XとYのAND演算結果(z2=X AND Y)、又は入力信号XとYのOR演算結果(z2=X OR Y)を出力線Z2に出力する。

【0034】

図2は、本実施形態における論理回路1の論理表を示す図である。

図2において、入力信号X、Yの組合せ4通りと乱数信号rの組合せを合わせた8通りの組合せに応じて、出力線Z2の出力z2の状態を示している。乱数信号rの値に応じて、出力z2が論理反転していることがわかる。乱数信号rはランダムに値が変わるため、入力信号a、bが同じであっても、出力z2がランダムに変動する。

【0035】

次に、タイムチャートを参照して、本実施形態の動作を詳細に説明する。

図3は、同実施形態における論理回路1のシーケンスを示すタイムチャートである。

図3において、入力信号X、Yと乱数信号r、制御信号en1、en2、出力線Z1の出力状態z1、及び出力線Z2の出力状態z2を示している。

まず、制御信号en1が時刻T0Hから時刻T0LでL(ロウ)状態(論理“0”状態)にされると出力制御部20が出力有効状態から出力無効状態に移行する。これにより、NMOS22がオフする。そのため、出力制御部20は、電源線GNDからNネット部12を介して出力線Z1に通じる経路を遮断して、Nネット部12を無効化する。また、PMOS21がオンする。PMOS21は、出力線Z1を電源線VDDによりH(ハイ)状態(論理“1”状態)に充電する。ここで、出力線Z1がH状態に充電されるのは、入力信号X、Yと乱数信号rにより出力論理状態が“0”となる場合である。そのため、Pネット部11の経路は遮断されている。従って、出力線Z1への充電は、Pネット部11を経由することなく、PMOS21よって行われる。また、その場合の電力消費波形は、入力信号a、bの組合せに依存しない一定の波形となる。

【0036】

時刻Taは、出力線Z1の充電が完了する時刻を示す。制御信号en2が出力線Z2の出力を有効にするL状態であるため、出力線Z1の出力z1がH状態になった結果、出力線Z2の出力z2は、L状態になる。この出力線Z2のH状態からL状態への移行は、PMOS21による充電タイミングが一定であるため、論理回路1の後段のゲートの動作タイミングは、一定となる。

【0037】

次に、制御信号en2が時刻T1Lから時刻T1HでH状態(論理“1”状態)にされると出力段回路30が出力有効状態からマスク状態に移行する。これにより、PMOS321がオフし、NMOS322がオンする。そのため、出力段回路30は、PMOS321により電源線VDDから出力線Z2に通じる経路を遮断する。また、出力段回路30は、NMOS322により出力線Z2と電源線GNDとの間を導通してL状態(論理”0”状態)に放電する。これにより、出力段回路30はマスク状態になり、出力線Z1の状態が変化しても、論理回路1の後段のゲートに伝播しない状態となる。マスク状態の場合、出力線Z2は、出力線Z1の状態に係わらず、L状態(論理”0”状態)が保持される。

【0038】

また、入力信号X、Yと乱数信号rは、時刻T2から時刻T3の間に変更される。時刻T2は、出力制御部20が出力無効状態にあり、出力線Z1の充電が完了して、電源線VDDの電位になった時刻Taよりも後の時刻である。これは、時刻Taよりも前に、入力信号X、Yと乱数信号rを変更した場合、電源線VDDからPネット部11を介して出力線Z1に通じる経路が導通して、電力消費波形が入力信号a、bの組合せに依存する可能性があるためである。

【0039】

次に、制御信号en1が時刻T4Lから時刻T4HでH状態(論理“1”状態)にされると出力制御部20が出力無効状態から出力有効状態に移行する。これにより、PMOS21がオフする。PMOS21は、出力線Z1と電源線VDDとの間を遮断する。また、NMOS22がオンする。そのため、出力制御部20は、電源線GNDからNネット部12を介して出力線Z1に通じる経路を導通して、Nネット部12による出力論理状態に応じて信号線Z1をL状態(論理“0”状態)に放電する。出力z1のp0は、論理演算回路10の出力論理状態が“1”である場合である。この場合、出力z1はH状態(論理“1”状態)を保持する。

また、出力z1のp1は、論理演算回路10のNネット部12において電源線GNDに放電する経路(パス)が1本の場合の波形である。この状態は、例えば図2の論理表における(4)の組合せ、且つ乱数信号rが“0”の場合である。この場合、NMOS125がオフとなるため、出力線Z1から電源線GNDに通じる経路は、NMOS121とNMOS122を通る経路の1本となる。放電の経路が1本であるため、出力z1は、p3よりも遅れてL状態に放電される。ここで、p1により、出力線Z1がL状態になる時刻をTbとする。

【0040】

また、出力z1のp3は、論理演算回路10のNネット部12において電源線GNDに放電する経路(パス)が3本の場合の波形である。この状態は、例えば図2の論理表における(1)の組合せ、且つ乱数信号rが“1”の場合である。この場合、NMOS125がオンとなるため、出力線Z1から電源線GNDに通じる経路は、NMOS121とNMOS122を通る経路、NMOS123の経路、及びNMOS124の経路の3本となる。放電の経路が3本であるため、出力z1は、p1よりも早くL状態に放電される。

ここで、出力線Z1の負荷容量を電源線GNDに放電する放電電流が流れる。しかし、出力線Z1の負荷容量が繋がる電源線GNDとNMOS22と接続される電源線GNDが接続され、共通の電源線として論理回路1の外部に出ているものとする。その場合、この放電電流は、論理回路1内で消費されたものとなり、外部からの電力消費として観測されない。また、p1とp3による遷移タイミングの違いは、出力段回路30によりマスクされ、論理回路1の後段のゲートの動作タイミングに影響しない。

【0041】

次に、制御信号en2が時刻T5Hから時刻T5LでL状態(論理“0”状態)にされると出力段回路30がマスク状態から出力有効状態に移行する。これにより、PMOS321がオンし、NMOS322がオフする。そのため、出力線Z1の状態を反転した状態が、出力線Z2に出力される。この際に出力段回路30が消費する電力は、出力線Z2の負荷容量を充電する電流である。そのため、電力消費波形は、出力線Z1の状態により決まり、入力信号a、bの組合せに依存しない。また、出力線Z2の遷移タイミングは、入力信号a、bの組合せに依存しない。そのため、論理回路1の後段のゲートの動作タイミングは、入力信号a、bの組合せに依存しない一定となる。

【0042】

以上のように、出力制御部20が、制御信号en1に応じて論理演算回路10の出力線Z1の出力状態を制御する。出力制御部20は、出力無効状態にある場合に、NMOS22により論理演算回路10の出力線Z1から電源線GNDに通じる経路を遮断し、PMOS21により電源線VDDと出力線Zとを導通して、H状態に充電する。これにより、入力信号の組合せによらず、充電経路の数がPMOS21による1本になる。そのため、論理回路1は、充電経路の平均数が異なるために生じる電力消費波形の変化を低減できる。これにより、入力信号a、bと相関する電力消費波形の統計的結果の変化を低減できる。

また、論理演算回路10の後段に設けられた出力段回路30が、制御信号en2に応じてマスク状態に切り替わる。出力段回路30は、マスク状態にある場合に、出力線Z1の出力状態を無効にして論理回路1の出力線Z2をL状態(論理“0”状態)に保持する。これにより、論理回路1は、論理演算回路10の出力線の動作タイミングの変化をマスクし、論理回路1の後段のゲートの動作タイミングの変化を低減できる。そのため、論理回路1は、後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減できる。これにより、入力信号a、bと相関する電力消費波形の変化を低減できる。

【0043】

<第2の実施形態>

以下、本発明の第2の実施形態による論理回路について図面を参照して説明する。

図4は、本実施形態における論理回路1aを示すブロック図である。

図4において、第1の実施形態の論理回路1に、PMOSで構成されるPネット遮断部40を設けている。その他の構成は、第1の実施形態と同様である。この図において、図1と同じ構成には同一の符号を付す。

Pネット遮断部40は、Pネット部11と出力線Z1の間に配置され、ソース端子がPネット部11の出力であるノードN7に、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に制御信号en2が供給される。Pネット遮断部40は、制御信号en2が“0”になり、出力段回路30がマスク状態にある場合に、Pネット部11と出力線Z1との間を遮断し、Pネット部11を出力線Z1から切り離す。

【0044】

次に、本実施形態の動作について説明する。

論理回路1aは、Pネット遮断部40の動作が加わる以外、第1の実施形態と基本的な動作は同じである。

論理回路1aは、入力信号a、bをAND演算した出力cを得るためのAND回路である。論理回路1aの入力信号X、Yは、入力信号a、bと、乱数信号rとをそれぞれXOR演算された値である(X=a XOR r、Y=b XOR r)。また、論理回路1aの出力線Z2の出力z2は、同じく乱数rと出力cをXOR演算した値である(z2=c XOR r)。入力a、bをXOR演算する乱数信号rと出力cをXOR演算する乱数信号rは同じ値であり、乱数信号rはゲート動作ごとに毎回異なる値にする。

【0045】

図5は、同実施形態における論理回路1aのシーケンスを示すタイムチャートである。

図5において、入力信号X、Yと乱数信号r、制御信号en1、en2、出力線Z1の出力状態z1、及び出力線Z2の出力状態z2を示している。この図において、以下の2つのタイミングが、制御信号en1による時刻T0Hから時刻T0Lの前になる以外、図3におけるシーケンスと同じである。2つのタイミングとは、制御信号en2による時刻T1Lから時刻T1Hと、入力信号X,Yと乱数信号rを変更するための時刻T2から時刻T3である。

【0046】

制御信号en2が時刻T1Lから時刻T1HでH状態(論理“1”状態)にされると出力段回路30が出力有効状態からマスク状態に移行する。また、Pネット遮断部40が、電源線VDDからPネット部11を介して出力線Z1に通じる経路を遮断する。また、制御信号en2が“0”から“1”に遷移する場合の動作は、第1の実施形態と同様である。

次に、入力信号X、Yと乱数信号rは、時刻T2から時刻T3の間に変更される。時刻T2は、Pネット遮断部40がPネット部11を遮断した時刻T1Hよりも後の時刻である。このタイミングにより入力信号X、Yと乱数信号rが変更される場合、Pネット遮断部40がPネット部11を遮断した後であるため、電力消費波形は、電力消費波形が入力信号X、Yと乱数信号rを変更しても影響を受けない。これにより、制御信号en1の状態に係わらず、入力信号X、Yと乱数信号rを変更することができる。そのため、入力信号X、Yと乱数信号rの変更タイミングを早めることができる。

【0047】

次に、制御信号en1が時刻T0Hから時刻T0LでL状態(論理“0”状態)にされると出力制御部20が出力有効状態から出力無効状態に移行する。これにより、NMOS22がオフする。そのため、出力制御部20は、電源線GNDからNネット部12を介して出力線Z1に通じる経路を遮断して、Nネット部12を無効化する。また、PMOS21がオンする。PMOS21は、出力線Z1を電源線VDDによりH状態(論理“1”状態)に充電する。時刻Taは、出力線Z1の充電が完了する時刻を示す。

その後の動作は、制御信号en1が時刻T4Lから時刻T4HでH状態(論理“1”状態)にされると出力制御部20が出力無効状態から出力有効状態に移行する。また、制御信号en2が時刻T5Hから時刻T5LでL状態(論理“0”状態)にされると出力段回路30がマスク状態から出力有効状態に移行する。また、Pネット遮断部40が、電源線VDDからPネット部11を介して出力線Z1に通じる経路を導通する。これにより、論理演算回路10の出力論理状態が“1”である場合、出力線Z1は、H状態(“1”状態)を保持する。また、出力線Z1の状態を反転した状態が、出力線Z2に出力される。

【0048】

以上のように、出力制御部20が、制御信号en1に応じて論理演算回路10の出力線Z1の出力状態を制御する。出力制御部20は、出力無効状態にある場合に、NMOS22により論理演算回路10の出力線Z1から電源線GNDに通じる経路を遮断し、PMOS21により電源線VDDと出力線Zとを導通して、H状態に充電する。これにより、入力信号の組合せによらず、充電経路の数がPMOS21による1本になる。そのため、論理回路1aは、充電経路の平均数が異なるために生じる電力消費波形の変化を低減できる。これにより、入力信号a、bと相関する電力消費波形の統計的結果の変化を低減できる。

また、論理演算回路10の後段に設けられた出力段回路30が、制御信号en2に応じてマスク状態に切り替わる。出力段回路30は、マスク状態にある場合に、出力線Z1の出力状態を無効にして論理回路1aの出力線Z2をL状態に保持する。これにより、論理回路1aは、論理演算回路10の出力線の動作タイミングの変化をマスクし、論理回路1aの後段のゲートの動作タイミングの変化を低減できる。そのため、論理回路1aは、後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減できる。これにより、入力信号a、bと相関する電力消費波形の変化を低減できる。

【0049】

また、Pネット遮断部40が、制御信号en2に応じて、電源線VDDからPネット部11を介して出力線Z1に通じる経路を遮断する。これにより、出力線Z1の充電が完了する時刻Taよりも前に、入力信号X、Yと乱数信号rを変更することができる。時刻Taは、論理回路1aの内部信号である出力線Z1の状態を観測して判断する必要があるが、本実施形態では、入力信号である制御信号en2の状態により、入力信号X、Yと乱数信号rを変更するタイミングを判断できる。そのため、論理回路1aは、入力信号X、Yと乱数信号rを変更するタイミングを容易に決定できる利点がある。

【0050】

<第3の実施形態>

以下、本発明の第3の実施形態による論理回路について図面を参照して説明する。

図6は、本実施形態における論理回路1bを示すブロック図である。

図6において、第2の実施形態と同様にPMOSで構成されるPネット遮断部40aを設けている。その他の構成は、第2の実施形態と同様である。この図において、図4と同じ構成には同一の符号を付す。

Pネット遮断部40aは、Pネット部11と出力線Z1の間に配置され、ソース端子がPネット部11の出力であるノードN7に、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に制御信号en1を論理反転したen1b(=NOT(en1))が供給される。Pネット遮断部40aは、制御信号en1が“0”になり、出力段回路30がマスク状態にある場合に、Pネット部11と出力線Z1との間を遮断し、Pネット部11を出力線Z1から切り離す。

【0051】

次に、本実施形態の動作について説明する。

論理回路1bは、Pネット遮断部40aの制御信号en1bが異なる以外、第2の実施形態と基本的な動作は同じである。

論理回路1bは、入力信号a、bをAND演算した出力cを得るためのAND回路である。論理回路1bの入力信号X、Yは、入力信号a、bと、乱数信号rとをそれぞれXOR演算された値である(X=a XOR r、Y=b XOR r)。また、論理回路1bの出力線Z2の出力z2は、同じく乱数rと出力cをXOR演算した値である(z2=c XOR r)。入力a、bをXOR演算する乱数信号rと出力cをXOR演算する乱数信号rは同じ値であり、乱数信号rはゲート動作ごとに毎回異なる値にする。

【0052】

図7は、同実施形態における論理回路1bのシーケンスを示すタイムチャートである。

図7において、入力信号X、Yと乱数信号r、制御信号en1、en1b、en2、出力線Z1の出力状態z1、及び出力線Z2の出力状態z2を示している。この図において、以下の3つのタイミングの順序が異なる以外、図5におけるシーケンスと同じである。3つのタイミングとは、制御信号en1による時刻T0Hから時刻T0L、制御信号en2による時刻T1Lから時刻T1H、及び入力信号X,Yと乱数信号rを変更するための時刻T2から時刻T3である。

【0053】

まず、制御信号en1が時刻T0Hから時刻T0LでL状態(論理“0”状態)にされると出力制御部20が出力有効状態から出力無効状態に移行する。また、制御信号en1の論理反転した制御信号en1bにより、Pネット遮断部40aが、電源線VDDからPネット部11を介して出力線Z1に通じる経路を遮断する。制御信号en1による出力制御部20の動作は、第1及び第2の実施形態と同様である。なお、時刻Taは、出力線Z1の充電が完了する時刻を示す。

次に、入力信号X、Yと乱数信号rは、時刻T2から時刻T3の間に変更される。時刻T2は、Pネット遮断部40aがPネット部11を遮断した時刻T0Hよりも後の時刻である。このタイミングにより入力信号X、Yと乱数信号rが変更される場合、Pネット遮断部40aがPネット部11を遮断した後であるため、電力消費波形は、電力消費波形が入力信号X、Yと乱数信号rを変更しても影響を受けない。これにより、出力線Z1の充電が完了する時刻Taより前のタイミングにおいて、入力信号X、Yと乱数信号rを変更することができる。そのため、入力信号X、Yと乱数信号rの変更タイミングを早めることができる。

次に、制御信号en2が時刻T1Lから時刻T1HでH状態(論理“1”状態)にされると出力段回路30が出力有効状態からマスク状態に移行する。また、制御信号en2が“0”から“1”に遷移する場合の動作は、第1の実施形態と同様である。

【0054】

その後の動作は、制御信号en1が時刻T4Lから時刻T4HでH状態(論理“1”状態)にされると出力制御部20が出力無効状態から出力有効状態に移行する。また、時刻T4Hにおいて、Pネット遮断部40aが、電源線VDDからPネット部11を介して出力線Z1に通じる経路を導通する。また、制御信号en2が時刻T5Hから時刻T5LでL状態(論理“0”状態)にされると出力段回路30がマスク状態から出力有効状態に移行する。これにより、出力線Z1の状態を反転した状態が、出力線Z2に出力される。

【0055】

以上のように、出力制御部20が、制御信号en1に応じて論理演算回路10の出力線Z1の出力状態を制御する。出力制御部20は、出力無効状態にある場合に、NMOS22により論理演算回路10の出力線Z1から電源線GNDに通じる経路を遮断し、PMOS21により電源線VDDと出力線Zとを導通して、H状態に充電する。これにより、入力信号の組合せによらず、充電経路の数がPMOS21による1本になる。そのため、論理回路1bは、充電経路の平均数が異なるために生じる電力消費波形の変化を低減できる。これにより、入力信号a、bと相関する電力消費波形の統計的結果の変化を低減できる。

また、論理演算回路10の後段に設けられた出力段回路30が、制御信号en2に応じてマスク状態に切り替わる。出力段回路30は、マスク状態にある場合に、出力線Z1の出力状態を無効にして論理回路1bの出力線Z2をL状態に保持する。これにより、論理回路1bは、論理演算回路10の出力線の動作タイミングの変化をマスクし、論理回路1bの後段のゲートの動作タイミングの変化を低減できる。そのため、論理回路1bは、後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減できる。これにより、入力信号a、bと相関する電力消費波形の変化を低減できる。

【0056】

また、Pネット遮断部40aが、制御信号en1b(=NOT(en1))に応じて、電源線VDDからPネット部11を介して出力線Z1に通じる経路を遮断する。これにより、出力線Z1の充電が完了する時刻Taよりも前に、入力信号X、Yと乱数信号rを変更することができる。時刻Taは、論理回路1bの内部信号である出力線Z1の状態を観測して判断する必要があるが、本実施形態では、入力信号である制御信号en1の状態により、入力信号X、Yと乱数信号rを変更するタイミングを判断できる。そのため、論理回路1bは、入力信号X、Yと乱数信号rを変更するタイミングを容易に決定できる利点がある。

【0057】

<第4の実施形態>

以下、本発明の第4の実施形態による情報記憶媒体について図面を参照して説明する。

図8は、本実施形態における情報記憶媒体(ICカード200)を示すブロック図である。

図8において、情報記憶媒体(ICカード200)は、制御部210、RAM(Random Access Memory)220、ROM(Read Only Memory)230、EEPROM(Electrically Erasable Programmable ROM)240、インタフェース部250、暗号処理部260、及び乱数生成部270を備える。ICカード200は、外部装置300とインタフェース部250を通じて接続される。また、制御部210、RAM220、ROM230、EEPROM240、インタフェース部250、暗号処理部260、及び乱数生成部270は、それぞれデータバスB1に接続される。

【0058】

制御部210は、ICカード200全体を制御する。RAM220は、制御部210が制御に使用する一時記憶情報を記憶する。ROM230は、制御部210のための制御プログラム及び定数情報などを記憶する。EEPROM240は、電気的に書き換え可能な不揮発性メモリであり、外部装置300からインタフェース部250を介して供給された情報や暗号処理又は復号処理に使用する秘密鍵などを記憶する。インタフェース部250は、外部装置300との情報の授受を行う。

暗号処理部260は、EEPROM240が記憶する秘密鍵に基づき、情報の暗号処理及び復号処理を行う。乱数生成部270は、乱数Rを生成し、暗号処理部260に供給する。

【0059】

図9は、本実施形態における暗号処理部260を示すブロック図である。

図9において、暗号処理部260は、入力データレジスタ261、暗号キーレジスタ262、制御レジスタ263、暗号復号回路264、及び出力データレジスタ265を備える。入力データレジスタ261は、制御部210によってデータバスB1を通じて供給される情報を記憶し、暗号復号回路264に供給する。制御部210によって供給される情報は、EEPROM240に記憶された情報やインタフェース部250を介して外部装置300から供給された情報などである。また、暗号キーレジスタ262は、制御部210によってデータバスB1を通じて供給される秘密鍵を記憶し、暗号復号回路264に供給する。また、制御レジスタ263は、制御部210によってデータバスB1を通じて供給される制御情報を記憶し、制御信号を暗号復号回路264に供給する。制御信号は、暗号復号回路264の暗号処理、及び復号処理の制御を行う。また、制御レジスタ263は、暗号復号回路264の状態を記憶する。暗号復号回路264の状態は、データバスB1を通じて制御部210によって参照される。

【0060】

暗号復号回路264は、第1の実施形態のAND回路である論理回路1(図1)を含む。暗号復号回路264は、図示は省略するが、論理回路1を含んだ基本論理回路ライブラリを用いて、暗号処理回路、及び復号処理回路が構成される。また、暗号復号回路264は、乱数生成部270から供給される乱数Rを論理回路1に乱数信号rとして供給する。また、論理回路1の制御信号en1及びen2は、暗号復号回路264の図示しないタイミングコントローラにより生成する。

また、暗号復号回路264は、制御レジスタ263から供給される制御信号に応じて、入力データレジスタ261から供給される情報を、暗号キーレジスタ262から供給される秘密鍵に基づき暗号処理又は復号処理する。その結果、暗号情報又は平文情報が生成される。暗号復号回路264は、生成した暗号情報又は平文情報を出力データレジスタ265に記憶させる。ここで、暗号処理又は復号処理する暗号方式は、例えば、DES(Data Encryption Standard)暗号とする。

出力データレジスタ265は、暗号復号回路264が生成した暗号情報又は平文情報を記憶する。暗号情報又は平文情報は、制御部210により、データバスB1を介して読み出され、ICカード200の情報処理に使用される。

【0061】

次に、本実施形態の動作について説明する。

ICカード200は、インタフェース部250を介して外部装置300と様々な情報の授受を行う。その様々な情報を授受する処理の中で、ICカード200は、秘匿情報を扱う場合に、暗号復号処理部260を使用して、暗号処理又は復号処理を行う。例えば、ICカード200と外部装置300の正当性を互いに確認する相互認証処理において、暗号処理又は復号処理を使用する。

暗号処理又は復号処理を行う場合、まず、制御部210が、EEPROM240に記憶された秘密鍵を、データバスB1を通じて暗号キーレジスタ262に記憶させる。また、制御部210は、暗号処理又は復号処理する情報を、データバスB1を通じて入力データレジスタ261に記憶させる。次に、制御部210は、データバスB1を通じて制御レジスタ263に制御コマンドを供給する。これにより、制御信号が暗号復号回路264に供給され、暗号処理又は復号処理が開始される。

【0062】

暗号復号回路264は、制御信号を受けて、入力データレジスタ261が記憶する情報を、暗号キーレジスタ262が記憶する秘密鍵に基づき暗号処理又は復号処理を行う。この暗号処理又は復号処理を行う際に、暗号復号回路264を構成する論理回路1は、乱数信号rに応じて、論理回路1の出力線Z2(図1)の出力をランダムに遷移させる。また、論理回路1の動作は、第1の実施形態で説明した通りである。論理回路1の動作により、暗号復号回路264は、電力消費の統計値と秘密鍵の相関を無くすことができる。

また、暗号復号回路264は、暗号処理又は復号処理が完了した場合、生成した暗号情報又は平文情報を出力データレジスタ265に記憶させる。また、暗号復号回路264は、暗号処理又は復号処理が完了した状態にあることを、制御レジスタ263に記憶させる。制御部210は、制御レジスタ263を参照して、暗号処理又は復号処理が完了したことを検出する。制御部210は、暗号処理又は復号処理の完了を検出した場合、データバスB1を通じて出力データレジスタ265の情報を読み出して、EEPROM240に記憶させる、又はインタフェース部250を介して外部装置300に供給する。

【0063】

以上のように、ICカード200は、制御部210、RAM220、ROM230、EEPROM240、インタフェース部250、暗号処理部260、及び乱数生成部270を備える。また、暗号処理部260は、入力データレジスタ261、暗号キーレジスタ262、制御レジスタ263、暗号復号回路264、及び出力データレジスタ265を備える。暗号復号回路264は、論理回路1を含み、制御レジスタ263から供給される制御信号に応じて、入力データレジスタ261から供給される情報を、暗号キーレジスタ262から供給される秘密鍵に基づき暗号処理又は復号処理する。そのため、ICカード200は、暗号処理又は復号処理において、論理回路1の充電経路の平均数が異なるために生じる電力消費波形の変化、及び論理回路の後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減できる。結果として、ICカード200は、電力消費の統計値と秘密鍵の相関を低減でき、電力解析攻撃を防止する効果が期待できる。

【0064】

<第5の実施形態>

以下、本発明の第5の実施形態による論理回路について図面を参照して説明する。

図10は、本実施形態における論理回路を示すブロック図である。

図10に示される論理回路1cは、図1に示される論理回路1にORAND(論理和論理積)論理演算を行う複合ゲートを適用した一形態である。論理回路1cは、論理演算回路10a、出力制御部20及び出力段回路30を備える。この図において、図1と同じ構成には同一の符号を付す。

論理演算回路10aは、電源線VDDと電源線GNDとの間に配置され、Pネット部11aとNネット部12aを備える。論理演算回路10aは、入力信号X、Y、Wと乱数信号rに基づき、Pネット部11aとNネット部12aとが相補に動作して生成される出力論理状態を出力線Z1に出力する。

Pネット部11aは、電源線VDDと出力線Z1との間に配置され、入力信号X、Y、Wと乱数信号rとに基づいて電源線VDDの電位により出力線Z1を充電し、論理レベル“1”を出力する。

Nネット部12aは、出力線Z1と電源線GNDとの間に配置され、入力信号X、Y、Wと乱数信号rとに基づいて電源線GNDの電位により出力線Z1を放電し、論理レベル“0”を出力する。

【0065】

Pネット部11aは、PMOS111a〜115a、116、117を備える。PMOS111a、112a、115aは、電源線VDDと出力線Z1との間に直列に配置される。PMOS111aは、ソース端子が電源線VDDに、ドレイン端子がノードN1aにそれぞれ接続され、ゲート端子に入力信号Xが供給される。PMOS112aは、ソース端子がノードN1a、ドレイン端子がノードN8にそれぞれ接続され、ゲート端子に入力信号Yが供給される。PMOS115aは、ソース端子がノードN8に、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に乱数信号rが供給される。また、PMOS116は、PMOS111a、112aと並列に配置される。PMOS116は、ソース端子が電源線VDDに、ドレイン端子がノードN8にそれぞれ接続され、ゲート端子に入力信号Wが供給される。

また、PMOS113a、114aは、電源線VDDとノードN2aとの間に並列に接続される。PMOS113aは、ソース端子が電源線VDDに、ドレイン端子がノードN2aにそれぞれ接続され、ゲート端子に入力信号Xが供給される。PMOS114aは、ソース端子が電源線VDDに、ドレイン端子がノードN2aにそれぞれ接続され、ゲート端子に入力信号Yが供給される。

また、PMOS117は、ソース端子がノードN2aに、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に入力信号Wが供給される。

【0066】

Nネット部12aは、NMOS121a〜125a、126、127を備える。NMOS121a、122a、125aは、出力線Z1とノードN4との間に直列に配置される。NMOS121aは、ソース端子がノードN3aに、ドレイン端子がノードN9にそれぞれ接続され、ゲート端子に入力信号Xが供給される。NMOS122aは、ソース端子がノードN4、ドレイン端子がノードN3aにそれぞれ接続され、ゲート端子に入力信号Yが供給される。NMOS125aは、ソース端子がノードN9に、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に乱数信号rが供給される。また、NMOS126は、NMOS121a、122aと並列に配置される。NMOS126は、ソース端子がノードN4に、ドレイン端子がノードN9にそれぞれ接続され、ゲート端子に入力信号Wが供給される。

また、NMOS123a、124aは、ノードN5aとノードN4との間に並列に接続される。NMOS123aは、ソース端子がノードN4に、ドレイン端子がノードN5aにそれぞれ接続され、ゲート端子に入力信号Xが供給される。NMOS124aは、ソース端子がノードN4に、ドレイン端子がノードN5aにそれぞれ接続され、ゲート端子に入力信号Yが供給される。

また、NMOS127は、ソース端子がノードN5aに、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に入力信号Wが供給される。

【0067】

次に、本実施形態の動作について説明する。

論理回路1cは、入力信号a、b、cをORAND(論理和論理積)演算した出力dを得るためのORAND回路である。論理回路1cの入力信号X、Y、Wは、入力信号a、b、cと、乱数信号rとをそれぞれXOR(排他的論理和)演算された値である(X=a XOR r、Y=b XOR r、W=c XOR r)。また、論理回路1cの出力線Z2の出力z2は、同じく乱数rと出力dをXOR演算した値である(z2=d XOR r)。入力a、b、cをXOR演算する乱数信号rと出力dをXOR演算する乱数信号rは同じ値であり、乱数信号rはゲート動作ごとに毎回異なる値にする。

【0068】

また、論理演算回路10aは、入力信号a、b、cをORNAND(論理和否定論理積)演算した結果を乱数信号rとXOR演算した出力z1を得るためのORNAND/ANDNOR(論理積否定論理和)演算回路である。乱数信号rが“0”の場合、論理演算回路10aは、入力信号X、Y、WのORNAND演算回路として機能する(z1=(X OR Y)NAND W)。また、乱数信号rが“1”の場合、論理演算回路10aは、入力信号X、Y、WのANDNOR演算回路として機能する(z1=(X AND Y)NOR W)。その原理は、式(4)から式(6)に示される。

【0069】

z1=((a OR b) NAND c) XOR r ・・・(4)

【0070】

式(4)は、論理演算回路10aの論理演算を示す式である。

【0071】

[r=“0”の場合]

X=a XOR r=a、Y=b XOR r=b、W=c XOR r=c、

z1=((a OR b) NAND c)XOR r=(X OR Y) NAND W ・・・(5)

【0072】

式(5)は、乱数信号rが“0”の場合における論理演算回路10aの論理演算を示す式である。乱数信号rが“0”の場合、入力信号a、b、cはそれぞれ入力信号X、Y、Wと等しくなる。このため、論理演算回路10aの出力線Z1の論理は、入力信号X、Y、WのORNAND演算したものになる。

【0073】

[r=“1”の場合]

X=a XOR r=NOT(a)、Y=b XOR r=NOT(b)、W=c XOR r=NOT(c)、

z1=NOT((NOT(X) OR NOT(Y))NAND NOT(W))=NOT((X AND Y)OR W)=(X AND Y)NOR W ・・・(6)

【0074】

式(6)は、乱数信号rが“1”の場合における論理演算回路10aの論理演算を示す式である。乱数信号rが“1”の場合、入力信号a、b、cはそれぞれ入力信号X、Y、WのNOT演算した値になる。このため、論理演算回路10aの出力線Z1の論理は、入力信号X、Y、WをそれぞれNOT演算したものをORNAND演算し、更にその演算結果をNOT演算したものになる。ト゛・モルガンの定理により、((NOT(X) OR NOT(Y))NAND NOT(W))は、入力信号X、Y、WのANDOR(論理積論理和)演算((X AND Y)OR W)に置き換えられる。これにより、論理演算回路10aの出力線Z1の論理は、入力信号X、Y、WのANDNOR演算したものになる。

【0075】

論理演算回路10aは、乱数信号rが“0”の場合、Pネット部11aのPMOS115aがオンして、PMOS111a、112a、116が有効になる。また、Nネット部12aのNMOS125aがオフして、NMOS121a、122a、126が無効になる。これにより、出力線Z1は、PMOS111a、112a、116と、NMOS123a、124a、127とで論理演算される出力論理状態が出力される。つまり、論理演算回路10aは、入力信号X、Y、WのORNAND演算回路として機能する。なお、この場合、PMOS113a、114a、117は、出力論理状態を決める際に関係しない。

また、論理演算回路10aは、乱数信号rが“1”の場合、Pネット部11aのPMOS115aがオフして、111a、112a、116が無効になる。また、Nネット部12aのNMOS125aがオンして、NMOS121a、122a、126が有効になる。これにより、出力線Z1は、NMOS121a、122a、126と、PMOS113a、114a、117とで論理演算される出力論理状態が出力される。つまり、論理演算回路10aは、入力信号X、Y、WのANDNOR演算回路として機能する。なお、この場合、NMOS123a、124a、127は、出力論理状態を決める際に関係しない。

【0076】

論理演算回路10aにより論理演算された出力z1は、出力線Z1を介して出力段回路30に供給される。出力段回路30は、出力z1の出力論理状態を反転して、出力線Z2に出力z2として出力する。これにより、論理回路1cは、乱数信号rに応じて、入力信号X、Y、WのORAND演算結果(z2=(X OR Y)AND W)、又は入力信号X、Y、WのANDOR演算結果(z2=(X AND Y)OR W)を出力線Z2に出力する。

【0077】

図11は、本実施形態における論理回路1cの論理表を示す図である。

図11において、入力信号X、Y、Wの組合せ8通りと乱数信号rの組合せを合わせた16通りの組合せに応じて、出力線Z2の出力z2の状態を示している。乱数信号rの値に応じて、出力z2が論理反転していることがわかる。乱数信号rはランダムに値が変わるため、入力信号a、b、cが同じであっても、出力z2がランダムに変動する。

【0078】

論理回路1cにおける、入力信号X、Y、W、乱数信号r、及び制御信号en1、en2の制御シーケンスは、図3が示すタイムチャートと同様である。入力信号Wは、入力信号X、Yと同じタイミング(時刻T2から時刻T3)で変更する。

【0079】

以上のように、出力制御部20が、制御信号en1に応じて論理演算回路10aの出力線Z1の出力状態を制御する。出力制御部20は、出力無効状態にある場合に、NMOS22により論理演算回路10aの出力線Z1から電源線GNDに通じる経路を遮断し、PMOS21により電源線VDDと出力線Z1とを導通して、H状態に充電する。これにより、入力信号の組合せによらず、充電経路の数がPMOS21による1本になる。そのため、論理回路1cは、充電経路の平均数が異なるために生じる電力消費波形の変化を低減できる。これにより、入力信号a、b、cと相関する電力消費波形の統計的結果の変化を低減できる。

また、論理演算回路10aの後段に設けられた出力段回路30が、制御信号en2に応じてマスク状態に切り替わる。出力段回路30は、マスク状態にある場合に、出力線Z1の出力状態を無効にして論理回路1cの出力線Z2をL状態に保持する。これにより、論理回路1cは、論理演算回路10aの出力線の動作タイミングの変化をマスクし、論理回路1cの後段のゲートの動作タイミングの変化を低減できる。そのため、論理回路1cは、後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減できる。これにより、入力信号a、b、cと相関する電力消費波形の変化を低減できる。

【0080】

なお、本発明の実施形態によれば、論理回路1(又は1a、1b、1cのいずれか)は、電源線VDDの電位が供給され、電源線VDDの電位より低い電源線GNDの電位が供給され、入力される入力信号X、Y(又はX、Y、W)と乱数信号rとに基づいて生成される出力論理状態を出力線Z1に出力する論理演算回路10(又は10a)と、入力される制御信号en1に応じて出力線Z1の出力状態を制御し、出力論理状態を無効とする出力無効状態である場合に、出力線Z1から電源線GNDに通じる経路を遮断し、電源線VDDの電位により出力線Z1を充電する出力制御部20と、論理演算回路10(又は10a)の後段に設けられ、出力線Z1の出力状態に基づいて出力する状態を無効とするマスク状態に、入力される制御信号en2に応じて切り替える出力段回路30とを備える。

これにより、入力信号X、Y(又はX、Y、W)の組合せによらず、充電経路の数がPMOS21による1本になる。そのため、論理回路1(又は1a、1b、1cのいずれか)は、充電経路の平均数が異なるために生じる電力消費波形の変化を低減できる。

また、論理回路1(又は1a、1b、1cのいずれか)は、出力段回路30により、論理演算回路10(又は10a)の出力線Z1の動作タイミングの変化をマスクし、論理回路1(又は1a、1b、1cのいずれか)の後段のゲートの動作タイミングの変化を低減できる。そのため、論理回路1(又は1a、1b、1cのいずれか)は、後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減できる。

【0081】

また、出力制御部20は、出力無効状態を解除した場合、出力線Z1から電源線GNDに通じる経路を導通させ、生成される論理状態に応じて、電源線GNDの電位により出力線Z1を放電する。

また、論理演算回路10(又は、10a)は、入力信号X、Y(又はX、Y、W)と乱数信号rとに基づいて電源線VDDの電位により出力線Z1を充電するPネット部11(又は11a)と、入力信号X、Y(又はX、Y、W)と乱数信号rとに基づいて電源線GNDの電位により出力線Z1を放電するNネット部12(又は12a)とが相補に動作して出力論理状態を生成する。また、出力線Z1から電源線GNDに通じる経路は、出力線Z1からNネット部12(又は12a)を介して電源線GNDに通じる経路である。

これにより、出力線Z1の負荷容量を電源線GNDに放電することで、論理演算回路10(又は10a)の出力論理状態になる。この放電電流は、論理回路1内で消費されるため、外部からの電力消費として観測されない。論理演算回路10(又は10a)の出力論理状態を決める際に、電力消費波形に影響を与えない。

【0082】

また、論理回路1a(又は1b)は、制御信号en1(en1b)(又は制御信号en2)に応じて、電源線VDDからPネット部11を介して出力線Z1に通じる経路を遮断するPネット遮断部40(又は40a)を備える。

これにより、出力制御部20が電源線VDDの電位により出力線Z1を充電する際に、Pネット部11を出力線Z1から遮断することができる。そのため、出力制御部20は、入力信号X、Yと乱数信号rの状態によらず、PMOS21により1本の経路により出力線Z1を充電することができる。

【0083】

また、入力信号X、Y(又はX、Y、W)及び乱数信号rは、出力制御部20が出力無効状態にあり、出力線Z1が電源線VDDの電位になった後に、変更される。出力制御部20は、入力信号X、Y(又はX、Y、W)及び乱数信号rの変更が確定した後に、制御信号en1に基づいて出力無効状態を解除する。出力段回路30は、出力無効状態が解除され、出力線Z1の出力状態が確定した後に、制御信号en2に基づいてマスク状態を解除する。

これにより、入力信号X、Y(又はX、Y、W)及び乱数信号rが遷移する際に消費される電力を低減し、入力信号X、Y(又はX、Y、W)の組合せによらず確実に、充電経路をPMOS21による1本にできる。そのため、論理回路1(又は1a、1b、1cのいずれか)は、充電経路の平均数が異なるために生じる電力消費波形の変化をより低減できる。また、論理演算回路10(又は10a)の出力線Z1の動作タイミングの変化を確実にマスクできる。そのため、論理回路1(又は1a、1b、1cのいずれか)の後段のゲートの動作タイミングの変化をより低減できる。

【0084】

また、入力信号X、Y及び乱数信号rは、出力制御部20が出力無効状態にあり、Pネット遮断部40(又は40a)が電源線VDDからPネット部11を介して出力線Z1に通じる経路を遮断した後に変更される。出力制御部20は、入力信号X、Y及び乱数信号rの変更が確定した後に、制御信号en1に基づいて出力無効状態を解除する。出力段回路30は、出力無効状態が解除され、出力線Z1の出力状態が確定した後に、制御信号en1に基づいてマスク状態を解除する。

これにより、入力信号X、Y及び乱数信号rの変更タイミングを早めることができる。また、入力信号である制御信号en1(又はen2)の状態により、入力信号X、Yと乱数信号rを変更するタイミングを判断できる。そのため、論理回路1a(又は1b)は、入力信号X、Yと乱数信号rを変更するタイミングを容易に決定できる利点がある。

【0085】

また、論理演算回路10(又は10a)は、入力信号X、Y(又はX、Y、W)に基づいて予め定められた論理演算処理に応じた論理状態を生成し、乱数信号rに基づき、入力信号X、Y(又はX、Y、W)を反転させた論理演算処理を行うか否か、及び出力論理状態を論理状態から反転したものにするか否かを切り替える。

これにより、論理演算回路10(又は10a)は、乱数信号rに基づき、NAND論理演算とNOR論理演算(又はORNAND論理演算とANDNOR論理演算)を切り替えることができる。そのため、論理回路1(又は1a、1b、1cのいずれか)は、出力線Z2の出力z2を乱数rによりランダムに遷移させることができる。

【0086】

また、本発明の実施形態によれば、ICカード200は、秘密鍵と情報を記憶するEEPROM240と、乱数信号Rを生成する乱数生成部270と、論理回路(1、1a、1b、1cの少なくともいずれか)を含み、秘密鍵に応じて暗号処理又は復号処理の少なくともいずれか一方を行う暗号処理部260とを備える。

これにより、ICカード200は、暗号処理又は復号処理において、論理回路1(又は1a、1b、1cのいずれか)の充電経路の平均数が異なるために生じる電力消費波形の変化、及び論理回路の後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減できる。結果として、ICカード200は、電力消費の統計値と秘密鍵の相関を低減でき、電力解析攻撃を防止する効果が期待できる。

【0087】

なお、本発明は、上記の各実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲で変更可能である。Pネット部11、11a、Nネット部12、12aは、各実施形態に限定されるものではなく、例えば、直列接続されたNMOS又はPMOSの接続順序は別の順序で接続された形態でも良い。また、論理演算回路10、10aは、NAND/NOR演算回路とORNAND/ANDNOR演算回路の形態を説明したが、これに限定されるものではなく、他の論理演算を行う形態でも良い。

また、論理演算回路10、10aにおいて、乱数信号rの代わりに乱数信号rの反転信号を使用しても良い。例えば、論理演算回路10に乱数信号rの反転信号を使用した場合、論理演算回路10は、乱数信号rが“0”の場合にNOR論理、乱数信号rが“1”の場合にNAND論理となり、異なる論理演算を行う論理演算回路(NOR/NAND演算回路)に容易に変更することができる。論理演算回路10aに乱数信号rの反転信号を使用した場合、ANDNOR/ORNAND演算回路となる。

また、出力段回路30の出力段制御部32は、マスク状態の場合に出力線Z2を“0”に保持する形態を説明したが、PMOS321とNMOS322の位置を変えて“1”を保持する形態でも良い。ただしこの場合、制御信号en2の論理を反転する必要がある。

【0088】

また、Pネット遮断部40(又は40a)は、Pネット部11と出力線Z1の間に配置する形態を説明したが、電源線VDDとPネット部11の間に配置する形態でも良い。また、NMOS22は、Nネット部12(又は12a)と電源線GNDの間に配置する形態を説明したが、出力線Z1とNネット部12(又は12a)の間に配置する形態でも良い。また、PMOS321も同様に、PMOS311と出力線Z2の間に配置しても良い。

また、論理演算回路10(又は10a)及び出力制御部20に使用する電源線VDDと、出力段回路30に使用する電源線VDDとは、同じ電位の形態を説明したが、異なる電位の電源を使用して、レベルシフタを介して接続しても良い。

また、第1、第3の実施形態において、制御信号en2をH状態にする時刻T1Lは、制御信号en1をL状態にする時刻T0H以前でも良い。また、第2の実施形態において、制御信号en2をH状態にする時刻T1Lは、制御信号en1をL状態にする時刻T0H以降でも良い。

【0089】

また、本発明の情報記憶媒体は、第4の実施形態のICカード200に限定されるものではない。例えば、暗号処理機能を備えたUSB(Universal Serial Bus)メモリやSD(エスディー)メモリカードでも良いし、他の形態の情報記憶媒体でも良い。また、インタフェース部250は、コンタクトによる接触式インタフェースでも良いし、非接触式インタフェースでも良い。また、暗号処理部260が使用する暗号方式は、DES暗号に限定されるものではなく、AES(Advanced Encryption Standard)暗号などの共通鍵暗号や、RSA(アールエスエイ)暗号、楕円曲線暗号などの公開鍵暗号、あるいはSHA−1(Secure Hash Algorithm−1)などのハッシュ関数でも良く、他の暗号方式でも良い。また、第4の実施形態において、ICカード200は、暗号処理と復号処理の両方を行う形態を説明したが、いずれか一方を処理する形態でも良い。

また、ICカード200は、情報を記憶する書き換え可能な不揮発性メモリとしてEEPROM240を備える形態を説明したが、他の書き換え可能な不揮発性メモリを備える形態でも良い。例えば、フラッシュメモリやFeRAM(Ferroelectric Random Access Memory)などのメモリを備える形態でも良い。

また、ICカード200は、暗号復号回路264に論理回路1を含む形態を説明したが、論理回路1a、1b、1cの内のいずれか1つ又は複数を含む形態でも良い。

なお、本発明の消費電力錯乱型論理回路は、論理回路1(又は1a、1b、1cのいずれか)に対応する。

【符号の説明】

【0090】

1、1a、1b、1c 論理回路

10、10a 論理演算回路

11、11a Pネット部

12、12a Nネット部

20 出力制御部

21 PMOS

22 NMOS

30 出力段回路

31 インバータ部

32 出力段制御部

40、40a Pネット遮断部

111、111a、112、112a、113、113a、114、114a、115115a、116、117 PMOS

121、121a、122、122a、123、123a、124、124a、125125a、126、127 NMOS

200 ICカード

210 制御部

220 RAM

230 ROM

240 EEPROM

250 インタフェース部

260 暗号処理部

261 入力データレジスタ

262 暗号キーレジスタ

263 制御レジスタ

264 暗号復号回路

265 出力データレジスタ

270 乱数生成部

300 外部装置

311、321 PMOS

312、322 NMOS

【技術分野】

【0001】

本発明は、暗号/復号処理の際に電力消費を解析して、秘密鍵を解明する電力解析攻撃を防ぐ消費電力錯乱型論理回路及び情報記憶媒体に関する。

【背景技術】

【0002】

ICカードなどの暗号処理を行う情報記憶媒体の電力消費を解析処理することにより、暗号処理に使用する秘密鍵を解明する電力解析攻撃がある。この攻撃に対して論理回路レベルの対策回路が、開示されている。非特許文献1では、乱数を用いて入力信号及び論理演算の正論理/負論理をランダムに切り替えるRSL(Random Switching Logic)回路を開示している。CMOS(Complementary Metal Oxide Semiconductor:相補型金属酸化膜半導体)集積回路が動作する場合の電力消費は、論理ゲートの出力負荷容量を充放電させる電流による電力が支配的である。そのため、RSL回路は、論理ゲートの出力を乱数によりランダムに遷移させることにより、電力消費の統計値と秘密鍵の相関を無くすことを意図した回路である。

【0003】

図12の(a)は、非特許文献1が開示するRSLによるNAND(否定論理積)ゲート(以下、RSL−NANDという。)を示す。元のNANDゲートの入力信号をa、bとし、出力をc(=a NAND b)とする。RSL−NANDの入力信号X、Yは、乱数rと入力信号a、bとをそれぞれXOR(排他的論理和)演算された値である(X=a XOR r、Y=b XOR r)。また、RSL−NANDの出力Zは、同じく乱数信号rと出力cをXOR演算した値である(Z=c XOR r)。入力信号a、bをXOR演算する乱数と出力cをXOR演算する乱数は同じ値であり、ゲート動作ごとに毎回異なる値にする。

また、RSL−NANDは、制御信号enを備える。制御信号enは、“1”の場合にRSL−NANDの出力を無効状態にし、RSL−NANDの出力を“0”に固定する。また、制御信号enは、“0”の場合にRSL−NANDの出力を有効状態にし、入力信号X、Y、rの値に応じた出力にさせる。入力信号X、Y、rが遷移する期間では、制御信号enは“1”にされ、入力が確定した後に制御信号enは“0”にされ、RSL−NANDの出力を有効にする。これは、入力信号X、Y、rが遷移する際に消費される電力をなくすためである。

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】D.Suzuki et al.,“Random Switching Logic: A New Countermeasure against DPA and Second-Order DPA at the Logic Level”IEICE TRANS.FUNDAMENTALS, VOL.E90-A, NO.1, JANUARY 2007.

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、図12の(a)が示すRSL−NANDでは、制御信号enが“1”から”0”に遷移し、無効状態から有効状態に切り替わる際に電力消費が発生する。この電力消費は、入力信号X、Y、rの状態により電力消費波形が異なる。

図12の(b)は、RSL−NANDの論理と“1”を出力する際の充電パスの数を示す論理表である。乱数rが“0”の場合、充電パスは、入力信号a、bの組合せ(1)において3本のパス、組合せ(2)及び(3)において1本のパスとなる。また、乱数信号rが“1”の場合、充電パスは、組合せ(4)において1本のパスとなる。そして、組合せ(1)から(4)の各場合における平均パス数、すなわち、rが“0”である場合のパス数とrが“1”である場合のパス数との平均は、順に3/2、1/2、1/2、1/2となる。充電のパス数が異なると、充電電流と充電速度に差が生じる。これら2つの差は、情報記憶媒体の外部から観測できる電力消費波形の差を生じさせる。この電力消費波形の差により、入力信号a、bの組合せが特定される可能性がある。すなわち、上述のRSL−NANDでは、入力信号a、bの組合せにより充電経路(パス)の平均数が異なることから電力消費波形の変化が生じるという問題がある。

【0006】

また、充電速度が異なると、RSL−NANDの出力遷移時間の違いとなって、後段のゲートの動作タイミングに影響する。後段のゲートの動作タイミングが異なれば、情報記憶媒体の外部から観測できる電力消費波形の差を生じさせる。すなわち、上述のRSL−NANDでは、後段のゲートの動作タイミングが異なることから電力消費波形に変化が生じるという問題がある。

【0007】

本発明は、上記問題を解決すべくなされたもので、その目的は、入力信号の組合せにより充電経路の平均数が異なるために生じる電力消費波形の変化と、後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減する消費電力錯乱型論理回路、及び情報記憶媒体を提供することにある。

【課題を解決するための手段】

【0008】

上記問題を解決するために、本発明は、第1の電位が第1の供給線から供給され、該第1の電位より低い第2の電位が第2の供給線から供給され、入力される入力信号と乱数信号とに基づいて生成される出力論理状態を出力線に出力する論理演算回路と、入力される第1の制御信号に応じて前記出力線の出力状態を制御し、前記出力論理状態を無効とする出力無効状態である場合に、前記出力線から前記第2の供給線に通じる第1の経路を遮断し、前記第1の電位により前記出力線を充電する出力制御部と、前記論理演算回路の後段に設けられ、前記出力線の出力状態に基づいて出力する状態を無効とするマスク状態に、入力される第2の制御信号に応じて切り替える出力段回路とを備える消費電力錯乱型論理回路である。

【0009】

また、本発明は上記発明において、前記出力制御部は、前記出力無効状態を解除した場合、前記第1の経路を導通させ、前記生成される論理状態に応じて、前記第2の電位により前記出力線を放電することを特徴とする。

【0010】

また、本発明は上記発明において、前記論理演算回路は、前記入力信号と前記乱数信号とに基づいて前記第1の電位により前記出力線を充電するPネット部と、前記入力信号と前記乱数信号とに基づいて前記第2の電位により前記出力線を放電するNネット部とが相補に動作して前記出力論理状態を生成し、前記第1の経路は、前記出力線から前記Nネット部を介して前記第2の供給線に通じる経路であることを特徴とする。

【0011】

また、本発明は上記発明において、前記消費電力錯乱型論理回路は、前記第1の制御信号又は前記第2の制御信号に応じて、前記第1の供給線から前記Pネット部を介して前記出力線に通じる第2の経路を遮断するPネット遮断部を備えることを特徴とする。

【0012】

また、本発明は上記発明において、前記入力信号及び前記乱数信号は、前記出力制御部が前記出力無効状態にあり、前記出力線が前記第1の電位になった後に、変更され、前記出力制御部は、前記入力信号及び前記乱数信号の変更が確定した後に、前記第1の制御信号に基づいて前記出力無効状態を解除し、前記出力段回路は、前記出力無効状態が解除され、前記出力線の出力状態が確定した後に、前記第2の制御信号に基づいて前記マスク状態を解除することを特徴とする。

【0013】

また、本発明は上記発明において、前記入力信号及び前記乱数信号は、前記出力制御部が前記出力無効状態にあり、前記Pネット遮断部が前記第2の経路を遮断した後に変更され、前記出力制御部は、前記入力信号及び前記乱数信号の変更が確定した後に、前記第1の制御信号に基づいて前記出力無効状態を解除し、前記出力段回路は、前記出力無効状態が解除され、前記出力線の出力状態が確定した後に、前記第2の制御信号に基づいて前記マスク状態を解除することを特徴とする。

【0014】

また、本発明は上記発明において、前記論理演算回路は、前記入力信号に基づいて予め定められた論理演算処理に応じた論理状態を生成し、前記乱数信号に基づき、前記入力信号を反転させた前記論理演算処理を行うか否か、及び前記出力論理状態を前記論理状態から反転したものにするか否かを切り替えることを特徴とする。

【0015】

また、本発明は、秘密鍵と情報を記憶する記憶部と、前記乱数信号を生成する乱数生成部と、上記発明のいずれかの消費電力錯乱型論理回路を含み、前記秘密鍵に応じて暗号処理を行う暗号処理部とを備える情報記憶媒体である。

【発明の効果】

【0016】

本発明によれば、論理演算回路が、第1の電位が第1の供給線から供給され、第1の電位より低い第2の電位が第2の供給線から供給され、入力される入力信号と乱数信号とに基づいて生成される出力論理状態を出力線に出力する。出力制御部が、第1の制御信号に応じて論理演算回路の出力線の出力状態を制御し、論理演算回路の出力論理状態を無効とする出力無効状態である場合に、論理演算回路の出力線から第2の供給線に通じる第1の経路を遮断し、第1の電位により前記出力線を充電する。これにより、入力信号の組合せによらず、充電経路の数が同じになる。そのため、消費電力錯乱型論理回路は、充電経路の平均数が異なるために生じる電力消費波形の変化を低減できる。また、論理演算回路の後段に設けられた出力段回路が、論理演算回路の出力線の出力状態に基づいて出力する出力状態を無効とするマスク状態に、入力される第2の制御信号に応じて切り替える。これにより、消費電力錯乱型論理回路は、論理演算回路の出力線の動作タイミングの変化をマスクし、消費電力錯乱型論理回路の後段のゲートの動作タイミングの変化を低減できる。そのため、消費電力錯乱型論理回路は、後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減できる。

【図面の簡単な説明】

【0017】

【図1】第1の実施形態による論理回路を示すブロック図である。

【図2】同実施形態における論理回路の論理表を示す図である。

【図3】同実施形態における論理回路のシーケンスを示すタイムチャートである。

【図4】第2の実施形態による論理回路を示すブロック図である。

【図5】同実施形態における論理回路のシーケンスを示すタイムチャートである。

【図6】第3の実施形態による論理回路を示すブロック図である。

【図7】同実施形態における論理回路のシーケンスを示すタイムチャートである。

【図8】第4の実施形態による携帯可能情報記憶媒体を示すブロック図である。

【図9】同実施形態における暗号処理部を示すブロック図である。

【図10】第5の実施形態による論理回路を示すブロック図である。

【図11】同実施形態における論理回路の論理表を示す図である。

【図12】従来技術による論理回路と論理表を示す図である。

【発明を実施するための形態】

【0018】

<第1の実施形態>

以下、本発明の第1の実施形態による論理回路について図面を参照して説明する。

図1は、本実施形態における論理回路を示すブロック図である。

図1に示される消費電力錯乱型論理回路である論理回路1は、論理演算回路10、出力制御部20及び出力段回路30を備える。

論理演算回路10は、電源線VDDと電源線GNDとの間に配置され、Pネット部11とNネット部12を備える。論理演算回路10は、入力信号X、Yと乱数信号rに基づき、Pネット部11とNネット部12とが相補に動作して生成される出力論理状態を出力線Z1に出力する。

Pネット部11は、電源線VDDと出力線Z1との間に配置され、入力信号X、Yと乱数信号rとに基づいて電源線VDDの電位により出力線Z1を充電し、論理レベル“1”を出力する。

Nネット部12は、出力線Z1と電源線GNDとの間に配置され、入力信号X、Yと乱数信号rとに基づいて電源線GNDの電位により出力線Z1を放電し、論理レベル“0”を出力する。

【0019】

Pネット部11は、Pチャネル型金属酸化膜半導体電界効果トランジスタ(P Channel Metal Oxide Semiconductor Field Effect Transistor、以下、PMOSという。)111〜115を備える。PMOS111、112は、電源線VDDと出力線Z1との間に直列に配置される。PMOS111は、ソース端子が電源線VDDに、ドレイン端子がノードN1にそれぞれ接続され、ゲート端子に入力信号Xが供給される。PMOS112は、ソース端子がノードN1、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に入力信号Yが供給される。

また、PMOS113、114は、電源線VDDとノードN2との間に並列に接続される。PMOS113は、ソース端子が電源線VDDに、ドレイン端子がノードN2にそれぞれ接続され、ゲート端子に入力信号Xが供給される。PMOS114は、ソース端子が電源線VDDに、ドレイン端子がノードN2にそれぞれ接続され、ゲート端子に入力信号Yが供給される。

また、PMOS115は、ソース端子がノードN2に、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に乱数信号rが供給される。

【0020】

Nネット部12は、Nチャネル型金属酸化膜半導体電界効果トランジスタ(N Channel Metal Oxide Semiconductor Field Effect Transistor、以下、NMOSという。)121〜125を備える。NMOS121、122は、出力線Z1とノードN4との間に直列に配置される。NMOS121は、ソース端子がノードN3に、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に入力信号Xが供給される。NMOS122は、ソース端子がノードN4、ドレイン端子がノードN3にそれぞれ接続され、ゲート端子に入力信号Yが供給される。

また、NMOS123、124は、出力線Z1とノードN5との間に並列に接続される。NMOS123は、ソース端子がN5に、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に入力信号Xが供給される。NMOS124は、ソース端子がノードN5に、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に入力信号Yが供給される。

また、NMOS125は、ソース端子がノードN4に、ドレイン端子がノードN5にそれぞれ接続され、ゲート端子に乱数信号rが供給される。

【0021】

出力制御部20は、PMOS21とNMOS22とを備え、制御信号en1に応じて出力線Z1の出力状態を制御する。出力制御部20は、PMOS21とNMOS22とにより、制御信号en1に応じて論理演算回路10の出力論理状態を無効にする。

PMOS21は、電源線VDDと出力線Z1との間に、Pネット部11と並列に配置される。PMOS21は、ソース端子が電源線VDDに、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に制御信号en1が供給される。PMOS21は、制御信号en1が“0”の場合(出力無効状態とする場合)に、電源線VDDと出力線Z1との間を導通して、出力線Z1を論理レベル“1”に充電する。これにより、Pネット部11は無効化される。

また、NMOS22は、出力線Z1と電源船GNDとの間に、Nネット部12と直列に配置される。NMOS22は、ソース端子が電源線GNDに、ドレイン端子がノードN4にそれぞれ接続され、ゲート端子に制御信号en1が供給される。NMOS22は、制御信号en1が“0”の場合(出力無効状態とする場合)に、電源線GNDからNネット部12を介して出力線Z1に通じる経路を遮断して、Nネット部12を無効化する。

【0022】

出力段回路30は、論理演算回路10の後段に配置され、インバータ部31と出力段制御部32とを備える。出力段回路30は、論理演算回路10の出力線Z1の出力状態に基づいて、論理回路1の出力線Z2に論理レベル“1”又は“0”を出力する。また、出力段回路30は、制御信号en2に応じて、出力線Z2の出力状態を無効にするマスク状態に切り替わる。

インバータ部31は、PMOS311とNMOS312とを備え、論理演算回路10の出力線Z1に出力される論理状態を反転した論理レベル“1”又は“0”を出力線Z2に出力する。

PMOS311とNMOS312は、ゲート端子が出力線Z1に、ドレイン端子が出力線Z2にそれぞれ接続される。また、PMOS311は、ソース端子がノードN6に接続される。NMOS312は、ソース端子が電源線GNDに接続される。

【0023】

出力段制御部32は、PMOS321とNMOS322とを備え、制御信号en2に応じて、出力線Z2の出力状態を無効にするマスク状態に切り替わる。PMOS321は、電源線VDDとインバータ部31との間に配置される。PMOS321は、ソース端子が電源線VDDに、ドレイン端子がノードN6にそれぞれ接続され、ゲート端子に制御信号en2が供給される。PMOS321は、制御信号en2が“1”の場合(マスク状態とする場合)に、電源線VDDからインバータ部31を遮断して、インバータ部31を無効化する。

NMOS322は、出力線Z2と電源線GNDとの間に、NMOS312と並列に配置される。NMOS322は、ソース端子が電源線GNDに、ドレイン端子が出力線Z2にそれぞれ接続され、ゲート端子に制御信号en2が供給される。NMOS322は、制御信号en2が“1”の場合(マスク状態とする場合)に、電源線GNDと出力線Z2との間を導通して、出力線Z2を論理レベル“0”に放電する。これにより、出力段制御部32は、マスク状態である場合に、出力線Z2に論理レベル“0”を出力する。

【0024】

次に、本実施形態の動作について説明する。

論理回路1は、入力信号a、bをAND(論理積)演算した出力cを得るためのAND回路である。論理回路1の入力信号X、Yは、入力信号a、bと、乱数信号rとをそれぞれXOR(排他的論理和)演算された値である(X=a XOR r、Y=b XOR r)。また、論理回路1の出力線Z2の出力z2は、同じく乱数rと出力cをXOR演算した値である(z2=c XOR r)。入力a、bをXOR演算する乱数信号rと出力cをXOR演算する乱数信号rは同じ値であり、乱数信号rはゲート動作ごとに毎回異なる値にする。

【0025】

また、論理演算回路10は、入力信号a、bをNAND(否定論理積)演算した結果を乱数信号rとXOR演算した出力z1を得るためのNAND/NOR(否定論理和)演算回路である。乱数信号rが“0”の場合、論理演算回路10は、入力信号X、YのNAND演算回路として機能する(z1=X NAND Y)。また、乱数信号rが“1”の場合、論理演算回路10は、入力信号X、YのNOR演算回路として機能する(z1=X NOR Y)。その原理は、式(1)から式(3)に示される。

【0026】

z1=(a NAND b) XOR r ・・・(1)

【0027】

式(1)は、論理演算回路10の論理演算を示す式である。

【0028】

[r=“0”の場合]

X=a XOR r=a、Y=b XOR r=b、

z1=(a NAND b)XOR r=X NAND Y ・・・(2)

【0029】

式(2)は、乱数信号rが“0”の場合における論理演算回路10の論理演算を示す式である。乱数信号rが“0”の場合、入力信号a、bはそれぞれ入力信号X、Yと等しくなる。このため、論理演算回路10の出力線Z1の論理は、入力信号XとYのNAND演算したものになる。

【0030】

[r=“1”の場合]

X=a XOR r=NOT(a)、Y=b XOR r=NOT(b)、

z1=NOT(NOT(X) NAND NOT(Y))=NOT(X OR Y)=X NOR Y ・・・(3)

【0031】

式(3)は、乱数信号rが“1”の場合における論理演算回路10の論理演算を示す式である。乱数信号rが“1”の場合、入力信号a、bはそれぞれ入力信号X、YのNOT(否定)演算した値になる。このため、論理演算回路10の出力線Z1の論理は、入力信号XとYをそれぞれNOT演算したものをNAND演算し、更にその演算結果をNOT演算したものになる。ト゛・モルガンの定理により、(NOT(X) NAND NOT(Y))は、入力信号XとYのOR(論理和)演算(X OR Y)に置き換えられる。これにより、論理演算回路10の出力線Z1の論理は、入力信号XとYのNOR演算したものになる。

【0032】

論理演算回路10は、乱数信号rが“0”の場合、Pネット部11のPMOS115がオンして、電源線VDDに並列接続されたPMOS113、114が有効になる。また、Nネット部12のNMOS125がオフして、出力線Z1に並列接続されたNMOS123、124が無効になる。これにより、出力線Z1は、PMOS113、114と、出力線Z1にノードN3を介して直列接続されたNMOS121、122とで論理演算される出力論理状態が出力される。つまり、論理演算回路10は、入力信号XとYのNAND演算回路として機能する。なお、この場合、PMOS111、112は、出力論理状態を決める際に関係しない。

また、論理演算回路10は、乱数信号rが“1”の場合、Pネット部11のPMOS115がオフして、電源線VDDに並列接続されたPMOS113、114が無効になる。また、Nネット部12のNMOS125がオンして、出力線Z1に並列接続されたNMOS123、124が有効になる。これにより、出力線Z1は、NMOS123、124と、出力線Z1にノードN1を介して直列接続されたPMOS111、112とで論理演算される出力論理状態が出力される。つまり、論理演算回路10は、入力信号XとYのNOR演算回路として機能する。なお、この場合、NMOS121、122は、出力論理状態を決める際に関係しない。

【0033】

論理演算回路10により論理演算された出力z1は、出力線Z1を介して出力段回路30のインバータ部31に供給される。インバータ部31は、PMOS311とNMOS312により、出力z1の出力論理状態を反転して、出力線Z2に出力z2として出力する。

これにより、論理回路1は、乱数信号rに応じて、入力信号XとYのAND演算結果(z2=X AND Y)、又は入力信号XとYのOR演算結果(z2=X OR Y)を出力線Z2に出力する。

【0034】

図2は、本実施形態における論理回路1の論理表を示す図である。

図2において、入力信号X、Yの組合せ4通りと乱数信号rの組合せを合わせた8通りの組合せに応じて、出力線Z2の出力z2の状態を示している。乱数信号rの値に応じて、出力z2が論理反転していることがわかる。乱数信号rはランダムに値が変わるため、入力信号a、bが同じであっても、出力z2がランダムに変動する。

【0035】

次に、タイムチャートを参照して、本実施形態の動作を詳細に説明する。

図3は、同実施形態における論理回路1のシーケンスを示すタイムチャートである。

図3において、入力信号X、Yと乱数信号r、制御信号en1、en2、出力線Z1の出力状態z1、及び出力線Z2の出力状態z2を示している。

まず、制御信号en1が時刻T0Hから時刻T0LでL(ロウ)状態(論理“0”状態)にされると出力制御部20が出力有効状態から出力無効状態に移行する。これにより、NMOS22がオフする。そのため、出力制御部20は、電源線GNDからNネット部12を介して出力線Z1に通じる経路を遮断して、Nネット部12を無効化する。また、PMOS21がオンする。PMOS21は、出力線Z1を電源線VDDによりH(ハイ)状態(論理“1”状態)に充電する。ここで、出力線Z1がH状態に充電されるのは、入力信号X、Yと乱数信号rにより出力論理状態が“0”となる場合である。そのため、Pネット部11の経路は遮断されている。従って、出力線Z1への充電は、Pネット部11を経由することなく、PMOS21よって行われる。また、その場合の電力消費波形は、入力信号a、bの組合せに依存しない一定の波形となる。

【0036】

時刻Taは、出力線Z1の充電が完了する時刻を示す。制御信号en2が出力線Z2の出力を有効にするL状態であるため、出力線Z1の出力z1がH状態になった結果、出力線Z2の出力z2は、L状態になる。この出力線Z2のH状態からL状態への移行は、PMOS21による充電タイミングが一定であるため、論理回路1の後段のゲートの動作タイミングは、一定となる。

【0037】

次に、制御信号en2が時刻T1Lから時刻T1HでH状態(論理“1”状態)にされると出力段回路30が出力有効状態からマスク状態に移行する。これにより、PMOS321がオフし、NMOS322がオンする。そのため、出力段回路30は、PMOS321により電源線VDDから出力線Z2に通じる経路を遮断する。また、出力段回路30は、NMOS322により出力線Z2と電源線GNDとの間を導通してL状態(論理”0”状態)に放電する。これにより、出力段回路30はマスク状態になり、出力線Z1の状態が変化しても、論理回路1の後段のゲートに伝播しない状態となる。マスク状態の場合、出力線Z2は、出力線Z1の状態に係わらず、L状態(論理”0”状態)が保持される。

【0038】

また、入力信号X、Yと乱数信号rは、時刻T2から時刻T3の間に変更される。時刻T2は、出力制御部20が出力無効状態にあり、出力線Z1の充電が完了して、電源線VDDの電位になった時刻Taよりも後の時刻である。これは、時刻Taよりも前に、入力信号X、Yと乱数信号rを変更した場合、電源線VDDからPネット部11を介して出力線Z1に通じる経路が導通して、電力消費波形が入力信号a、bの組合せに依存する可能性があるためである。

【0039】

次に、制御信号en1が時刻T4Lから時刻T4HでH状態(論理“1”状態)にされると出力制御部20が出力無効状態から出力有効状態に移行する。これにより、PMOS21がオフする。PMOS21は、出力線Z1と電源線VDDとの間を遮断する。また、NMOS22がオンする。そのため、出力制御部20は、電源線GNDからNネット部12を介して出力線Z1に通じる経路を導通して、Nネット部12による出力論理状態に応じて信号線Z1をL状態(論理“0”状態)に放電する。出力z1のp0は、論理演算回路10の出力論理状態が“1”である場合である。この場合、出力z1はH状態(論理“1”状態)を保持する。

また、出力z1のp1は、論理演算回路10のNネット部12において電源線GNDに放電する経路(パス)が1本の場合の波形である。この状態は、例えば図2の論理表における(4)の組合せ、且つ乱数信号rが“0”の場合である。この場合、NMOS125がオフとなるため、出力線Z1から電源線GNDに通じる経路は、NMOS121とNMOS122を通る経路の1本となる。放電の経路が1本であるため、出力z1は、p3よりも遅れてL状態に放電される。ここで、p1により、出力線Z1がL状態になる時刻をTbとする。

【0040】

また、出力z1のp3は、論理演算回路10のNネット部12において電源線GNDに放電する経路(パス)が3本の場合の波形である。この状態は、例えば図2の論理表における(1)の組合せ、且つ乱数信号rが“1”の場合である。この場合、NMOS125がオンとなるため、出力線Z1から電源線GNDに通じる経路は、NMOS121とNMOS122を通る経路、NMOS123の経路、及びNMOS124の経路の3本となる。放電の経路が3本であるため、出力z1は、p1よりも早くL状態に放電される。

ここで、出力線Z1の負荷容量を電源線GNDに放電する放電電流が流れる。しかし、出力線Z1の負荷容量が繋がる電源線GNDとNMOS22と接続される電源線GNDが接続され、共通の電源線として論理回路1の外部に出ているものとする。その場合、この放電電流は、論理回路1内で消費されたものとなり、外部からの電力消費として観測されない。また、p1とp3による遷移タイミングの違いは、出力段回路30によりマスクされ、論理回路1の後段のゲートの動作タイミングに影響しない。

【0041】

次に、制御信号en2が時刻T5Hから時刻T5LでL状態(論理“0”状態)にされると出力段回路30がマスク状態から出力有効状態に移行する。これにより、PMOS321がオンし、NMOS322がオフする。そのため、出力線Z1の状態を反転した状態が、出力線Z2に出力される。この際に出力段回路30が消費する電力は、出力線Z2の負荷容量を充電する電流である。そのため、電力消費波形は、出力線Z1の状態により決まり、入力信号a、bの組合せに依存しない。また、出力線Z2の遷移タイミングは、入力信号a、bの組合せに依存しない。そのため、論理回路1の後段のゲートの動作タイミングは、入力信号a、bの組合せに依存しない一定となる。

【0042】

以上のように、出力制御部20が、制御信号en1に応じて論理演算回路10の出力線Z1の出力状態を制御する。出力制御部20は、出力無効状態にある場合に、NMOS22により論理演算回路10の出力線Z1から電源線GNDに通じる経路を遮断し、PMOS21により電源線VDDと出力線Zとを導通して、H状態に充電する。これにより、入力信号の組合せによらず、充電経路の数がPMOS21による1本になる。そのため、論理回路1は、充電経路の平均数が異なるために生じる電力消費波形の変化を低減できる。これにより、入力信号a、bと相関する電力消費波形の統計的結果の変化を低減できる。

また、論理演算回路10の後段に設けられた出力段回路30が、制御信号en2に応じてマスク状態に切り替わる。出力段回路30は、マスク状態にある場合に、出力線Z1の出力状態を無効にして論理回路1の出力線Z2をL状態(論理“0”状態)に保持する。これにより、論理回路1は、論理演算回路10の出力線の動作タイミングの変化をマスクし、論理回路1の後段のゲートの動作タイミングの変化を低減できる。そのため、論理回路1は、後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減できる。これにより、入力信号a、bと相関する電力消費波形の変化を低減できる。

【0043】

<第2の実施形態>

以下、本発明の第2の実施形態による論理回路について図面を参照して説明する。

図4は、本実施形態における論理回路1aを示すブロック図である。

図4において、第1の実施形態の論理回路1に、PMOSで構成されるPネット遮断部40を設けている。その他の構成は、第1の実施形態と同様である。この図において、図1と同じ構成には同一の符号を付す。

Pネット遮断部40は、Pネット部11と出力線Z1の間に配置され、ソース端子がPネット部11の出力であるノードN7に、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に制御信号en2が供給される。Pネット遮断部40は、制御信号en2が“0”になり、出力段回路30がマスク状態にある場合に、Pネット部11と出力線Z1との間を遮断し、Pネット部11を出力線Z1から切り離す。

【0044】

次に、本実施形態の動作について説明する。

論理回路1aは、Pネット遮断部40の動作が加わる以外、第1の実施形態と基本的な動作は同じである。

論理回路1aは、入力信号a、bをAND演算した出力cを得るためのAND回路である。論理回路1aの入力信号X、Yは、入力信号a、bと、乱数信号rとをそれぞれXOR演算された値である(X=a XOR r、Y=b XOR r)。また、論理回路1aの出力線Z2の出力z2は、同じく乱数rと出力cをXOR演算した値である(z2=c XOR r)。入力a、bをXOR演算する乱数信号rと出力cをXOR演算する乱数信号rは同じ値であり、乱数信号rはゲート動作ごとに毎回異なる値にする。

【0045】

図5は、同実施形態における論理回路1aのシーケンスを示すタイムチャートである。

図5において、入力信号X、Yと乱数信号r、制御信号en1、en2、出力線Z1の出力状態z1、及び出力線Z2の出力状態z2を示している。この図において、以下の2つのタイミングが、制御信号en1による時刻T0Hから時刻T0Lの前になる以外、図3におけるシーケンスと同じである。2つのタイミングとは、制御信号en2による時刻T1Lから時刻T1Hと、入力信号X,Yと乱数信号rを変更するための時刻T2から時刻T3である。

【0046】

制御信号en2が時刻T1Lから時刻T1HでH状態(論理“1”状態)にされると出力段回路30が出力有効状態からマスク状態に移行する。また、Pネット遮断部40が、電源線VDDからPネット部11を介して出力線Z1に通じる経路を遮断する。また、制御信号en2が“0”から“1”に遷移する場合の動作は、第1の実施形態と同様である。

次に、入力信号X、Yと乱数信号rは、時刻T2から時刻T3の間に変更される。時刻T2は、Pネット遮断部40がPネット部11を遮断した時刻T1Hよりも後の時刻である。このタイミングにより入力信号X、Yと乱数信号rが変更される場合、Pネット遮断部40がPネット部11を遮断した後であるため、電力消費波形は、電力消費波形が入力信号X、Yと乱数信号rを変更しても影響を受けない。これにより、制御信号en1の状態に係わらず、入力信号X、Yと乱数信号rを変更することができる。そのため、入力信号X、Yと乱数信号rの変更タイミングを早めることができる。

【0047】

次に、制御信号en1が時刻T0Hから時刻T0LでL状態(論理“0”状態)にされると出力制御部20が出力有効状態から出力無効状態に移行する。これにより、NMOS22がオフする。そのため、出力制御部20は、電源線GNDからNネット部12を介して出力線Z1に通じる経路を遮断して、Nネット部12を無効化する。また、PMOS21がオンする。PMOS21は、出力線Z1を電源線VDDによりH状態(論理“1”状態)に充電する。時刻Taは、出力線Z1の充電が完了する時刻を示す。

その後の動作は、制御信号en1が時刻T4Lから時刻T4HでH状態(論理“1”状態)にされると出力制御部20が出力無効状態から出力有効状態に移行する。また、制御信号en2が時刻T5Hから時刻T5LでL状態(論理“0”状態)にされると出力段回路30がマスク状態から出力有効状態に移行する。また、Pネット遮断部40が、電源線VDDからPネット部11を介して出力線Z1に通じる経路を導通する。これにより、論理演算回路10の出力論理状態が“1”である場合、出力線Z1は、H状態(“1”状態)を保持する。また、出力線Z1の状態を反転した状態が、出力線Z2に出力される。

【0048】

以上のように、出力制御部20が、制御信号en1に応じて論理演算回路10の出力線Z1の出力状態を制御する。出力制御部20は、出力無効状態にある場合に、NMOS22により論理演算回路10の出力線Z1から電源線GNDに通じる経路を遮断し、PMOS21により電源線VDDと出力線Zとを導通して、H状態に充電する。これにより、入力信号の組合せによらず、充電経路の数がPMOS21による1本になる。そのため、論理回路1aは、充電経路の平均数が異なるために生じる電力消費波形の変化を低減できる。これにより、入力信号a、bと相関する電力消費波形の統計的結果の変化を低減できる。

また、論理演算回路10の後段に設けられた出力段回路30が、制御信号en2に応じてマスク状態に切り替わる。出力段回路30は、マスク状態にある場合に、出力線Z1の出力状態を無効にして論理回路1aの出力線Z2をL状態に保持する。これにより、論理回路1aは、論理演算回路10の出力線の動作タイミングの変化をマスクし、論理回路1aの後段のゲートの動作タイミングの変化を低減できる。そのため、論理回路1aは、後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減できる。これにより、入力信号a、bと相関する電力消費波形の変化を低減できる。

【0049】

また、Pネット遮断部40が、制御信号en2に応じて、電源線VDDからPネット部11を介して出力線Z1に通じる経路を遮断する。これにより、出力線Z1の充電が完了する時刻Taよりも前に、入力信号X、Yと乱数信号rを変更することができる。時刻Taは、論理回路1aの内部信号である出力線Z1の状態を観測して判断する必要があるが、本実施形態では、入力信号である制御信号en2の状態により、入力信号X、Yと乱数信号rを変更するタイミングを判断できる。そのため、論理回路1aは、入力信号X、Yと乱数信号rを変更するタイミングを容易に決定できる利点がある。

【0050】

<第3の実施形態>

以下、本発明の第3の実施形態による論理回路について図面を参照して説明する。

図6は、本実施形態における論理回路1bを示すブロック図である。

図6において、第2の実施形態と同様にPMOSで構成されるPネット遮断部40aを設けている。その他の構成は、第2の実施形態と同様である。この図において、図4と同じ構成には同一の符号を付す。

Pネット遮断部40aは、Pネット部11と出力線Z1の間に配置され、ソース端子がPネット部11の出力であるノードN7に、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に制御信号en1を論理反転したen1b(=NOT(en1))が供給される。Pネット遮断部40aは、制御信号en1が“0”になり、出力段回路30がマスク状態にある場合に、Pネット部11と出力線Z1との間を遮断し、Pネット部11を出力線Z1から切り離す。

【0051】

次に、本実施形態の動作について説明する。

論理回路1bは、Pネット遮断部40aの制御信号en1bが異なる以外、第2の実施形態と基本的な動作は同じである。

論理回路1bは、入力信号a、bをAND演算した出力cを得るためのAND回路である。論理回路1bの入力信号X、Yは、入力信号a、bと、乱数信号rとをそれぞれXOR演算された値である(X=a XOR r、Y=b XOR r)。また、論理回路1bの出力線Z2の出力z2は、同じく乱数rと出力cをXOR演算した値である(z2=c XOR r)。入力a、bをXOR演算する乱数信号rと出力cをXOR演算する乱数信号rは同じ値であり、乱数信号rはゲート動作ごとに毎回異なる値にする。

【0052】

図7は、同実施形態における論理回路1bのシーケンスを示すタイムチャートである。

図7において、入力信号X、Yと乱数信号r、制御信号en1、en1b、en2、出力線Z1の出力状態z1、及び出力線Z2の出力状態z2を示している。この図において、以下の3つのタイミングの順序が異なる以外、図5におけるシーケンスと同じである。3つのタイミングとは、制御信号en1による時刻T0Hから時刻T0L、制御信号en2による時刻T1Lから時刻T1H、及び入力信号X,Yと乱数信号rを変更するための時刻T2から時刻T3である。

【0053】

まず、制御信号en1が時刻T0Hから時刻T0LでL状態(論理“0”状態)にされると出力制御部20が出力有効状態から出力無効状態に移行する。また、制御信号en1の論理反転した制御信号en1bにより、Pネット遮断部40aが、電源線VDDからPネット部11を介して出力線Z1に通じる経路を遮断する。制御信号en1による出力制御部20の動作は、第1及び第2の実施形態と同様である。なお、時刻Taは、出力線Z1の充電が完了する時刻を示す。

次に、入力信号X、Yと乱数信号rは、時刻T2から時刻T3の間に変更される。時刻T2は、Pネット遮断部40aがPネット部11を遮断した時刻T0Hよりも後の時刻である。このタイミングにより入力信号X、Yと乱数信号rが変更される場合、Pネット遮断部40aがPネット部11を遮断した後であるため、電力消費波形は、電力消費波形が入力信号X、Yと乱数信号rを変更しても影響を受けない。これにより、出力線Z1の充電が完了する時刻Taより前のタイミングにおいて、入力信号X、Yと乱数信号rを変更することができる。そのため、入力信号X、Yと乱数信号rの変更タイミングを早めることができる。

次に、制御信号en2が時刻T1Lから時刻T1HでH状態(論理“1”状態)にされると出力段回路30が出力有効状態からマスク状態に移行する。また、制御信号en2が“0”から“1”に遷移する場合の動作は、第1の実施形態と同様である。

【0054】

その後の動作は、制御信号en1が時刻T4Lから時刻T4HでH状態(論理“1”状態)にされると出力制御部20が出力無効状態から出力有効状態に移行する。また、時刻T4Hにおいて、Pネット遮断部40aが、電源線VDDからPネット部11を介して出力線Z1に通じる経路を導通する。また、制御信号en2が時刻T5Hから時刻T5LでL状態(論理“0”状態)にされると出力段回路30がマスク状態から出力有効状態に移行する。これにより、出力線Z1の状態を反転した状態が、出力線Z2に出力される。

【0055】

以上のように、出力制御部20が、制御信号en1に応じて論理演算回路10の出力線Z1の出力状態を制御する。出力制御部20は、出力無効状態にある場合に、NMOS22により論理演算回路10の出力線Z1から電源線GNDに通じる経路を遮断し、PMOS21により電源線VDDと出力線Zとを導通して、H状態に充電する。これにより、入力信号の組合せによらず、充電経路の数がPMOS21による1本になる。そのため、論理回路1bは、充電経路の平均数が異なるために生じる電力消費波形の変化を低減できる。これにより、入力信号a、bと相関する電力消費波形の統計的結果の変化を低減できる。

また、論理演算回路10の後段に設けられた出力段回路30が、制御信号en2に応じてマスク状態に切り替わる。出力段回路30は、マスク状態にある場合に、出力線Z1の出力状態を無効にして論理回路1bの出力線Z2をL状態に保持する。これにより、論理回路1bは、論理演算回路10の出力線の動作タイミングの変化をマスクし、論理回路1bの後段のゲートの動作タイミングの変化を低減できる。そのため、論理回路1bは、後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減できる。これにより、入力信号a、bと相関する電力消費波形の変化を低減できる。

【0056】

また、Pネット遮断部40aが、制御信号en1b(=NOT(en1))に応じて、電源線VDDからPネット部11を介して出力線Z1に通じる経路を遮断する。これにより、出力線Z1の充電が完了する時刻Taよりも前に、入力信号X、Yと乱数信号rを変更することができる。時刻Taは、論理回路1bの内部信号である出力線Z1の状態を観測して判断する必要があるが、本実施形態では、入力信号である制御信号en1の状態により、入力信号X、Yと乱数信号rを変更するタイミングを判断できる。そのため、論理回路1bは、入力信号X、Yと乱数信号rを変更するタイミングを容易に決定できる利点がある。

【0057】

<第4の実施形態>

以下、本発明の第4の実施形態による情報記憶媒体について図面を参照して説明する。

図8は、本実施形態における情報記憶媒体(ICカード200)を示すブロック図である。

図8において、情報記憶媒体(ICカード200)は、制御部210、RAM(Random Access Memory)220、ROM(Read Only Memory)230、EEPROM(Electrically Erasable Programmable ROM)240、インタフェース部250、暗号処理部260、及び乱数生成部270を備える。ICカード200は、外部装置300とインタフェース部250を通じて接続される。また、制御部210、RAM220、ROM230、EEPROM240、インタフェース部250、暗号処理部260、及び乱数生成部270は、それぞれデータバスB1に接続される。

【0058】

制御部210は、ICカード200全体を制御する。RAM220は、制御部210が制御に使用する一時記憶情報を記憶する。ROM230は、制御部210のための制御プログラム及び定数情報などを記憶する。EEPROM240は、電気的に書き換え可能な不揮発性メモリであり、外部装置300からインタフェース部250を介して供給された情報や暗号処理又は復号処理に使用する秘密鍵などを記憶する。インタフェース部250は、外部装置300との情報の授受を行う。

暗号処理部260は、EEPROM240が記憶する秘密鍵に基づき、情報の暗号処理及び復号処理を行う。乱数生成部270は、乱数Rを生成し、暗号処理部260に供給する。

【0059】

図9は、本実施形態における暗号処理部260を示すブロック図である。

図9において、暗号処理部260は、入力データレジスタ261、暗号キーレジスタ262、制御レジスタ263、暗号復号回路264、及び出力データレジスタ265を備える。入力データレジスタ261は、制御部210によってデータバスB1を通じて供給される情報を記憶し、暗号復号回路264に供給する。制御部210によって供給される情報は、EEPROM240に記憶された情報やインタフェース部250を介して外部装置300から供給された情報などである。また、暗号キーレジスタ262は、制御部210によってデータバスB1を通じて供給される秘密鍵を記憶し、暗号復号回路264に供給する。また、制御レジスタ263は、制御部210によってデータバスB1を通じて供給される制御情報を記憶し、制御信号を暗号復号回路264に供給する。制御信号は、暗号復号回路264の暗号処理、及び復号処理の制御を行う。また、制御レジスタ263は、暗号復号回路264の状態を記憶する。暗号復号回路264の状態は、データバスB1を通じて制御部210によって参照される。

【0060】

暗号復号回路264は、第1の実施形態のAND回路である論理回路1(図1)を含む。暗号復号回路264は、図示は省略するが、論理回路1を含んだ基本論理回路ライブラリを用いて、暗号処理回路、及び復号処理回路が構成される。また、暗号復号回路264は、乱数生成部270から供給される乱数Rを論理回路1に乱数信号rとして供給する。また、論理回路1の制御信号en1及びen2は、暗号復号回路264の図示しないタイミングコントローラにより生成する。

また、暗号復号回路264は、制御レジスタ263から供給される制御信号に応じて、入力データレジスタ261から供給される情報を、暗号キーレジスタ262から供給される秘密鍵に基づき暗号処理又は復号処理する。その結果、暗号情報又は平文情報が生成される。暗号復号回路264は、生成した暗号情報又は平文情報を出力データレジスタ265に記憶させる。ここで、暗号処理又は復号処理する暗号方式は、例えば、DES(Data Encryption Standard)暗号とする。

出力データレジスタ265は、暗号復号回路264が生成した暗号情報又は平文情報を記憶する。暗号情報又は平文情報は、制御部210により、データバスB1を介して読み出され、ICカード200の情報処理に使用される。

【0061】

次に、本実施形態の動作について説明する。

ICカード200は、インタフェース部250を介して外部装置300と様々な情報の授受を行う。その様々な情報を授受する処理の中で、ICカード200は、秘匿情報を扱う場合に、暗号復号処理部260を使用して、暗号処理又は復号処理を行う。例えば、ICカード200と外部装置300の正当性を互いに確認する相互認証処理において、暗号処理又は復号処理を使用する。

暗号処理又は復号処理を行う場合、まず、制御部210が、EEPROM240に記憶された秘密鍵を、データバスB1を通じて暗号キーレジスタ262に記憶させる。また、制御部210は、暗号処理又は復号処理する情報を、データバスB1を通じて入力データレジスタ261に記憶させる。次に、制御部210は、データバスB1を通じて制御レジスタ263に制御コマンドを供給する。これにより、制御信号が暗号復号回路264に供給され、暗号処理又は復号処理が開始される。

【0062】

暗号復号回路264は、制御信号を受けて、入力データレジスタ261が記憶する情報を、暗号キーレジスタ262が記憶する秘密鍵に基づき暗号処理又は復号処理を行う。この暗号処理又は復号処理を行う際に、暗号復号回路264を構成する論理回路1は、乱数信号rに応じて、論理回路1の出力線Z2(図1)の出力をランダムに遷移させる。また、論理回路1の動作は、第1の実施形態で説明した通りである。論理回路1の動作により、暗号復号回路264は、電力消費の統計値と秘密鍵の相関を無くすことができる。

また、暗号復号回路264は、暗号処理又は復号処理が完了した場合、生成した暗号情報又は平文情報を出力データレジスタ265に記憶させる。また、暗号復号回路264は、暗号処理又は復号処理が完了した状態にあることを、制御レジスタ263に記憶させる。制御部210は、制御レジスタ263を参照して、暗号処理又は復号処理が完了したことを検出する。制御部210は、暗号処理又は復号処理の完了を検出した場合、データバスB1を通じて出力データレジスタ265の情報を読み出して、EEPROM240に記憶させる、又はインタフェース部250を介して外部装置300に供給する。

【0063】

以上のように、ICカード200は、制御部210、RAM220、ROM230、EEPROM240、インタフェース部250、暗号処理部260、及び乱数生成部270を備える。また、暗号処理部260は、入力データレジスタ261、暗号キーレジスタ262、制御レジスタ263、暗号復号回路264、及び出力データレジスタ265を備える。暗号復号回路264は、論理回路1を含み、制御レジスタ263から供給される制御信号に応じて、入力データレジスタ261から供給される情報を、暗号キーレジスタ262から供給される秘密鍵に基づき暗号処理又は復号処理する。そのため、ICカード200は、暗号処理又は復号処理において、論理回路1の充電経路の平均数が異なるために生じる電力消費波形の変化、及び論理回路の後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減できる。結果として、ICカード200は、電力消費の統計値と秘密鍵の相関を低減でき、電力解析攻撃を防止する効果が期待できる。

【0064】

<第5の実施形態>

以下、本発明の第5の実施形態による論理回路について図面を参照して説明する。

図10は、本実施形態における論理回路を示すブロック図である。

図10に示される論理回路1cは、図1に示される論理回路1にORAND(論理和論理積)論理演算を行う複合ゲートを適用した一形態である。論理回路1cは、論理演算回路10a、出力制御部20及び出力段回路30を備える。この図において、図1と同じ構成には同一の符号を付す。

論理演算回路10aは、電源線VDDと電源線GNDとの間に配置され、Pネット部11aとNネット部12aを備える。論理演算回路10aは、入力信号X、Y、Wと乱数信号rに基づき、Pネット部11aとNネット部12aとが相補に動作して生成される出力論理状態を出力線Z1に出力する。

Pネット部11aは、電源線VDDと出力線Z1との間に配置され、入力信号X、Y、Wと乱数信号rとに基づいて電源線VDDの電位により出力線Z1を充電し、論理レベル“1”を出力する。

Nネット部12aは、出力線Z1と電源線GNDとの間に配置され、入力信号X、Y、Wと乱数信号rとに基づいて電源線GNDの電位により出力線Z1を放電し、論理レベル“0”を出力する。

【0065】

Pネット部11aは、PMOS111a〜115a、116、117を備える。PMOS111a、112a、115aは、電源線VDDと出力線Z1との間に直列に配置される。PMOS111aは、ソース端子が電源線VDDに、ドレイン端子がノードN1aにそれぞれ接続され、ゲート端子に入力信号Xが供給される。PMOS112aは、ソース端子がノードN1a、ドレイン端子がノードN8にそれぞれ接続され、ゲート端子に入力信号Yが供給される。PMOS115aは、ソース端子がノードN8に、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に乱数信号rが供給される。また、PMOS116は、PMOS111a、112aと並列に配置される。PMOS116は、ソース端子が電源線VDDに、ドレイン端子がノードN8にそれぞれ接続され、ゲート端子に入力信号Wが供給される。

また、PMOS113a、114aは、電源線VDDとノードN2aとの間に並列に接続される。PMOS113aは、ソース端子が電源線VDDに、ドレイン端子がノードN2aにそれぞれ接続され、ゲート端子に入力信号Xが供給される。PMOS114aは、ソース端子が電源線VDDに、ドレイン端子がノードN2aにそれぞれ接続され、ゲート端子に入力信号Yが供給される。

また、PMOS117は、ソース端子がノードN2aに、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に入力信号Wが供給される。

【0066】

Nネット部12aは、NMOS121a〜125a、126、127を備える。NMOS121a、122a、125aは、出力線Z1とノードN4との間に直列に配置される。NMOS121aは、ソース端子がノードN3aに、ドレイン端子がノードN9にそれぞれ接続され、ゲート端子に入力信号Xが供給される。NMOS122aは、ソース端子がノードN4、ドレイン端子がノードN3aにそれぞれ接続され、ゲート端子に入力信号Yが供給される。NMOS125aは、ソース端子がノードN9に、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に乱数信号rが供給される。また、NMOS126は、NMOS121a、122aと並列に配置される。NMOS126は、ソース端子がノードN4に、ドレイン端子がノードN9にそれぞれ接続され、ゲート端子に入力信号Wが供給される。

また、NMOS123a、124aは、ノードN5aとノードN4との間に並列に接続される。NMOS123aは、ソース端子がノードN4に、ドレイン端子がノードN5aにそれぞれ接続され、ゲート端子に入力信号Xが供給される。NMOS124aは、ソース端子がノードN4に、ドレイン端子がノードN5aにそれぞれ接続され、ゲート端子に入力信号Yが供給される。

また、NMOS127は、ソース端子がノードN5aに、ドレイン端子が出力線Z1にそれぞれ接続され、ゲート端子に入力信号Wが供給される。

【0067】

次に、本実施形態の動作について説明する。

論理回路1cは、入力信号a、b、cをORAND(論理和論理積)演算した出力dを得るためのORAND回路である。論理回路1cの入力信号X、Y、Wは、入力信号a、b、cと、乱数信号rとをそれぞれXOR(排他的論理和)演算された値である(X=a XOR r、Y=b XOR r、W=c XOR r)。また、論理回路1cの出力線Z2の出力z2は、同じく乱数rと出力dをXOR演算した値である(z2=d XOR r)。入力a、b、cをXOR演算する乱数信号rと出力dをXOR演算する乱数信号rは同じ値であり、乱数信号rはゲート動作ごとに毎回異なる値にする。

【0068】

また、論理演算回路10aは、入力信号a、b、cをORNAND(論理和否定論理積)演算した結果を乱数信号rとXOR演算した出力z1を得るためのORNAND/ANDNOR(論理積否定論理和)演算回路である。乱数信号rが“0”の場合、論理演算回路10aは、入力信号X、Y、WのORNAND演算回路として機能する(z1=(X OR Y)NAND W)。また、乱数信号rが“1”の場合、論理演算回路10aは、入力信号X、Y、WのANDNOR演算回路として機能する(z1=(X AND Y)NOR W)。その原理は、式(4)から式(6)に示される。

【0069】

z1=((a OR b) NAND c) XOR r ・・・(4)

【0070】

式(4)は、論理演算回路10aの論理演算を示す式である。

【0071】

[r=“0”の場合]

X=a XOR r=a、Y=b XOR r=b、W=c XOR r=c、

z1=((a OR b) NAND c)XOR r=(X OR Y) NAND W ・・・(5)

【0072】

式(5)は、乱数信号rが“0”の場合における論理演算回路10aの論理演算を示す式である。乱数信号rが“0”の場合、入力信号a、b、cはそれぞれ入力信号X、Y、Wと等しくなる。このため、論理演算回路10aの出力線Z1の論理は、入力信号X、Y、WのORNAND演算したものになる。

【0073】

[r=“1”の場合]

X=a XOR r=NOT(a)、Y=b XOR r=NOT(b)、W=c XOR r=NOT(c)、

z1=NOT((NOT(X) OR NOT(Y))NAND NOT(W))=NOT((X AND Y)OR W)=(X AND Y)NOR W ・・・(6)

【0074】

式(6)は、乱数信号rが“1”の場合における論理演算回路10aの論理演算を示す式である。乱数信号rが“1”の場合、入力信号a、b、cはそれぞれ入力信号X、Y、WのNOT演算した値になる。このため、論理演算回路10aの出力線Z1の論理は、入力信号X、Y、WをそれぞれNOT演算したものをORNAND演算し、更にその演算結果をNOT演算したものになる。ト゛・モルガンの定理により、((NOT(X) OR NOT(Y))NAND NOT(W))は、入力信号X、Y、WのANDOR(論理積論理和)演算((X AND Y)OR W)に置き換えられる。これにより、論理演算回路10aの出力線Z1の論理は、入力信号X、Y、WのANDNOR演算したものになる。

【0075】

論理演算回路10aは、乱数信号rが“0”の場合、Pネット部11aのPMOS115aがオンして、PMOS111a、112a、116が有効になる。また、Nネット部12aのNMOS125aがオフして、NMOS121a、122a、126が無効になる。これにより、出力線Z1は、PMOS111a、112a、116と、NMOS123a、124a、127とで論理演算される出力論理状態が出力される。つまり、論理演算回路10aは、入力信号X、Y、WのORNAND演算回路として機能する。なお、この場合、PMOS113a、114a、117は、出力論理状態を決める際に関係しない。

また、論理演算回路10aは、乱数信号rが“1”の場合、Pネット部11aのPMOS115aがオフして、111a、112a、116が無効になる。また、Nネット部12aのNMOS125aがオンして、NMOS121a、122a、126が有効になる。これにより、出力線Z1は、NMOS121a、122a、126と、PMOS113a、114a、117とで論理演算される出力論理状態が出力される。つまり、論理演算回路10aは、入力信号X、Y、WのANDNOR演算回路として機能する。なお、この場合、NMOS123a、124a、127は、出力論理状態を決める際に関係しない。

【0076】

論理演算回路10aにより論理演算された出力z1は、出力線Z1を介して出力段回路30に供給される。出力段回路30は、出力z1の出力論理状態を反転して、出力線Z2に出力z2として出力する。これにより、論理回路1cは、乱数信号rに応じて、入力信号X、Y、WのORAND演算結果(z2=(X OR Y)AND W)、又は入力信号X、Y、WのANDOR演算結果(z2=(X AND Y)OR W)を出力線Z2に出力する。

【0077】

図11は、本実施形態における論理回路1cの論理表を示す図である。

図11において、入力信号X、Y、Wの組合せ8通りと乱数信号rの組合せを合わせた16通りの組合せに応じて、出力線Z2の出力z2の状態を示している。乱数信号rの値に応じて、出力z2が論理反転していることがわかる。乱数信号rはランダムに値が変わるため、入力信号a、b、cが同じであっても、出力z2がランダムに変動する。

【0078】

論理回路1cにおける、入力信号X、Y、W、乱数信号r、及び制御信号en1、en2の制御シーケンスは、図3が示すタイムチャートと同様である。入力信号Wは、入力信号X、Yと同じタイミング(時刻T2から時刻T3)で変更する。

【0079】

以上のように、出力制御部20が、制御信号en1に応じて論理演算回路10aの出力線Z1の出力状態を制御する。出力制御部20は、出力無効状態にある場合に、NMOS22により論理演算回路10aの出力線Z1から電源線GNDに通じる経路を遮断し、PMOS21により電源線VDDと出力線Z1とを導通して、H状態に充電する。これにより、入力信号の組合せによらず、充電経路の数がPMOS21による1本になる。そのため、論理回路1cは、充電経路の平均数が異なるために生じる電力消費波形の変化を低減できる。これにより、入力信号a、b、cと相関する電力消費波形の統計的結果の変化を低減できる。

また、論理演算回路10aの後段に設けられた出力段回路30が、制御信号en2に応じてマスク状態に切り替わる。出力段回路30は、マスク状態にある場合に、出力線Z1の出力状態を無効にして論理回路1cの出力線Z2をL状態に保持する。これにより、論理回路1cは、論理演算回路10aの出力線の動作タイミングの変化をマスクし、論理回路1cの後段のゲートの動作タイミングの変化を低減できる。そのため、論理回路1cは、後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減できる。これにより、入力信号a、b、cと相関する電力消費波形の変化を低減できる。

【0080】

なお、本発明の実施形態によれば、論理回路1(又は1a、1b、1cのいずれか)は、電源線VDDの電位が供給され、電源線VDDの電位より低い電源線GNDの電位が供給され、入力される入力信号X、Y(又はX、Y、W)と乱数信号rとに基づいて生成される出力論理状態を出力線Z1に出力する論理演算回路10(又は10a)と、入力される制御信号en1に応じて出力線Z1の出力状態を制御し、出力論理状態を無効とする出力無効状態である場合に、出力線Z1から電源線GNDに通じる経路を遮断し、電源線VDDの電位により出力線Z1を充電する出力制御部20と、論理演算回路10(又は10a)の後段に設けられ、出力線Z1の出力状態に基づいて出力する状態を無効とするマスク状態に、入力される制御信号en2に応じて切り替える出力段回路30とを備える。

これにより、入力信号X、Y(又はX、Y、W)の組合せによらず、充電経路の数がPMOS21による1本になる。そのため、論理回路1(又は1a、1b、1cのいずれか)は、充電経路の平均数が異なるために生じる電力消費波形の変化を低減できる。

また、論理回路1(又は1a、1b、1cのいずれか)は、出力段回路30により、論理演算回路10(又は10a)の出力線Z1の動作タイミングの変化をマスクし、論理回路1(又は1a、1b、1cのいずれか)の後段のゲートの動作タイミングの変化を低減できる。そのため、論理回路1(又は1a、1b、1cのいずれか)は、後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減できる。

【0081】

また、出力制御部20は、出力無効状態を解除した場合、出力線Z1から電源線GNDに通じる経路を導通させ、生成される論理状態に応じて、電源線GNDの電位により出力線Z1を放電する。

また、論理演算回路10(又は、10a)は、入力信号X、Y(又はX、Y、W)と乱数信号rとに基づいて電源線VDDの電位により出力線Z1を充電するPネット部11(又は11a)と、入力信号X、Y(又はX、Y、W)と乱数信号rとに基づいて電源線GNDの電位により出力線Z1を放電するNネット部12(又は12a)とが相補に動作して出力論理状態を生成する。また、出力線Z1から電源線GNDに通じる経路は、出力線Z1からNネット部12(又は12a)を介して電源線GNDに通じる経路である。

これにより、出力線Z1の負荷容量を電源線GNDに放電することで、論理演算回路10(又は10a)の出力論理状態になる。この放電電流は、論理回路1内で消費されるため、外部からの電力消費として観測されない。論理演算回路10(又は10a)の出力論理状態を決める際に、電力消費波形に影響を与えない。

【0082】

また、論理回路1a(又は1b)は、制御信号en1(en1b)(又は制御信号en2)に応じて、電源線VDDからPネット部11を介して出力線Z1に通じる経路を遮断するPネット遮断部40(又は40a)を備える。

これにより、出力制御部20が電源線VDDの電位により出力線Z1を充電する際に、Pネット部11を出力線Z1から遮断することができる。そのため、出力制御部20は、入力信号X、Yと乱数信号rの状態によらず、PMOS21により1本の経路により出力線Z1を充電することができる。

【0083】

また、入力信号X、Y(又はX、Y、W)及び乱数信号rは、出力制御部20が出力無効状態にあり、出力線Z1が電源線VDDの電位になった後に、変更される。出力制御部20は、入力信号X、Y(又はX、Y、W)及び乱数信号rの変更が確定した後に、制御信号en1に基づいて出力無効状態を解除する。出力段回路30は、出力無効状態が解除され、出力線Z1の出力状態が確定した後に、制御信号en2に基づいてマスク状態を解除する。

これにより、入力信号X、Y(又はX、Y、W)及び乱数信号rが遷移する際に消費される電力を低減し、入力信号X、Y(又はX、Y、W)の組合せによらず確実に、充電経路をPMOS21による1本にできる。そのため、論理回路1(又は1a、1b、1cのいずれか)は、充電経路の平均数が異なるために生じる電力消費波形の変化をより低減できる。また、論理演算回路10(又は10a)の出力線Z1の動作タイミングの変化を確実にマスクできる。そのため、論理回路1(又は1a、1b、1cのいずれか)の後段のゲートの動作タイミングの変化をより低減できる。

【0084】

また、入力信号X、Y及び乱数信号rは、出力制御部20が出力無効状態にあり、Pネット遮断部40(又は40a)が電源線VDDからPネット部11を介して出力線Z1に通じる経路を遮断した後に変更される。出力制御部20は、入力信号X、Y及び乱数信号rの変更が確定した後に、制御信号en1に基づいて出力無効状態を解除する。出力段回路30は、出力無効状態が解除され、出力線Z1の出力状態が確定した後に、制御信号en1に基づいてマスク状態を解除する。

これにより、入力信号X、Y及び乱数信号rの変更タイミングを早めることができる。また、入力信号である制御信号en1(又はen2)の状態により、入力信号X、Yと乱数信号rを変更するタイミングを判断できる。そのため、論理回路1a(又は1b)は、入力信号X、Yと乱数信号rを変更するタイミングを容易に決定できる利点がある。

【0085】

また、論理演算回路10(又は10a)は、入力信号X、Y(又はX、Y、W)に基づいて予め定められた論理演算処理に応じた論理状態を生成し、乱数信号rに基づき、入力信号X、Y(又はX、Y、W)を反転させた論理演算処理を行うか否か、及び出力論理状態を論理状態から反転したものにするか否かを切り替える。

これにより、論理演算回路10(又は10a)は、乱数信号rに基づき、NAND論理演算とNOR論理演算(又はORNAND論理演算とANDNOR論理演算)を切り替えることができる。そのため、論理回路1(又は1a、1b、1cのいずれか)は、出力線Z2の出力z2を乱数rによりランダムに遷移させることができる。

【0086】

また、本発明の実施形態によれば、ICカード200は、秘密鍵と情報を記憶するEEPROM240と、乱数信号Rを生成する乱数生成部270と、論理回路(1、1a、1b、1cの少なくともいずれか)を含み、秘密鍵に応じて暗号処理又は復号処理の少なくともいずれか一方を行う暗号処理部260とを備える。

これにより、ICカード200は、暗号処理又は復号処理において、論理回路1(又は1a、1b、1cのいずれか)の充電経路の平均数が異なるために生じる電力消費波形の変化、及び論理回路の後段のゲートの動作タイミングが異なるために生じる電力消費波形の変化を低減できる。結果として、ICカード200は、電力消費の統計値と秘密鍵の相関を低減でき、電力解析攻撃を防止する効果が期待できる。

【0087】

なお、本発明は、上記の各実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲で変更可能である。Pネット部11、11a、Nネット部12、12aは、各実施形態に限定されるものではなく、例えば、直列接続されたNMOS又はPMOSの接続順序は別の順序で接続された形態でも良い。また、論理演算回路10、10aは、NAND/NOR演算回路とORNAND/ANDNOR演算回路の形態を説明したが、これに限定されるものではなく、他の論理演算を行う形態でも良い。

また、論理演算回路10、10aにおいて、乱数信号rの代わりに乱数信号rの反転信号を使用しても良い。例えば、論理演算回路10に乱数信号rの反転信号を使用した場合、論理演算回路10は、乱数信号rが“0”の場合にNOR論理、乱数信号rが“1”の場合にNAND論理となり、異なる論理演算を行う論理演算回路(NOR/NAND演算回路)に容易に変更することができる。論理演算回路10aに乱数信号rの反転信号を使用した場合、ANDNOR/ORNAND演算回路となる。

また、出力段回路30の出力段制御部32は、マスク状態の場合に出力線Z2を“0”に保持する形態を説明したが、PMOS321とNMOS322の位置を変えて“1”を保持する形態でも良い。ただしこの場合、制御信号en2の論理を反転する必要がある。

【0088】

また、Pネット遮断部40(又は40a)は、Pネット部11と出力線Z1の間に配置する形態を説明したが、電源線VDDとPネット部11の間に配置する形態でも良い。また、NMOS22は、Nネット部12(又は12a)と電源線GNDの間に配置する形態を説明したが、出力線Z1とNネット部12(又は12a)の間に配置する形態でも良い。また、PMOS321も同様に、PMOS311と出力線Z2の間に配置しても良い。

また、論理演算回路10(又は10a)及び出力制御部20に使用する電源線VDDと、出力段回路30に使用する電源線VDDとは、同じ電位の形態を説明したが、異なる電位の電源を使用して、レベルシフタを介して接続しても良い。

また、第1、第3の実施形態において、制御信号en2をH状態にする時刻T1Lは、制御信号en1をL状態にする時刻T0H以前でも良い。また、第2の実施形態において、制御信号en2をH状態にする時刻T1Lは、制御信号en1をL状態にする時刻T0H以降でも良い。

【0089】

また、本発明の情報記憶媒体は、第4の実施形態のICカード200に限定されるものではない。例えば、暗号処理機能を備えたUSB(Universal Serial Bus)メモリやSD(エスディー)メモリカードでも良いし、他の形態の情報記憶媒体でも良い。また、インタフェース部250は、コンタクトによる接触式インタフェースでも良いし、非接触式インタフェースでも良い。また、暗号処理部260が使用する暗号方式は、DES暗号に限定されるものではなく、AES(Advanced Encryption Standard)暗号などの共通鍵暗号や、RSA(アールエスエイ)暗号、楕円曲線暗号などの公開鍵暗号、あるいはSHA−1(Secure Hash Algorithm−1)などのハッシュ関数でも良く、他の暗号方式でも良い。また、第4の実施形態において、ICカード200は、暗号処理と復号処理の両方を行う形態を説明したが、いずれか一方を処理する形態でも良い。

また、ICカード200は、情報を記憶する書き換え可能な不揮発性メモリとしてEEPROM240を備える形態を説明したが、他の書き換え可能な不揮発性メモリを備える形態でも良い。例えば、フラッシュメモリやFeRAM(Ferroelectric Random Access Memory)などのメモリを備える形態でも良い。

また、ICカード200は、暗号復号回路264に論理回路1を含む形態を説明したが、論理回路1a、1b、1cの内のいずれか1つ又は複数を含む形態でも良い。

なお、本発明の消費電力錯乱型論理回路は、論理回路1(又は1a、1b、1cのいずれか)に対応する。

【符号の説明】

【0090】

1、1a、1b、1c 論理回路

10、10a 論理演算回路

11、11a Pネット部

12、12a Nネット部

20 出力制御部

21 PMOS

22 NMOS

30 出力段回路

31 インバータ部

32 出力段制御部

40、40a Pネット遮断部

111、111a、112、112a、113、113a、114、114a、115115a、116、117 PMOS

121、121a、122、122a、123、123a、124、124a、125125a、126、127 NMOS

200 ICカード

210 制御部

220 RAM

230 ROM

240 EEPROM

250 インタフェース部

260 暗号処理部

261 入力データレジスタ

262 暗号キーレジスタ

263 制御レジスタ

264 暗号復号回路

265 出力データレジスタ

270 乱数生成部

300 外部装置

311、321 PMOS

312、322 NMOS

【特許請求の範囲】

【請求項1】

第1の電位が第1の供給線から供給され、該第1の電位より低い第2の電位が第2の供給線から供給され、入力される入力信号と乱数信号とに基づいて生成される出力論理状態を出力線に出力する論理演算回路と、

入力される第1の制御信号に応じて前記出力線の出力状態を制御し、前記出力論理状態を無効とする出力無効状態である場合に、前記出力線から前記第2の供給線に通じる第1の経路を遮断し、前記第1の電位により前記出力線を充電する出力制御部と、

前記論理演算回路の後段に設けられ、前記出力線の出力状態に基づいて出力する状態を無効とするマスク状態に、入力される第2の制御信号に応じて切り替える出力段回路と

を備えることを特徴とする消費電力錯乱型論理回路。

【請求項2】

前記出力制御部は、

前記出力無効状態を解除した場合、前記第1の経路を導通させ、前記生成される論理状態に応じて、前記第2の電位により前記出力線を放電する

ことを特徴とする請求項1に記載の消費電力錯乱型論理回路。

【請求項3】

前記論理演算回路は、

前記入力信号と前記乱数信号とに基づいて前記第1の電位により前記出力線を充電するPネット部と、前記入力信号と前記乱数信号とに基づいて前記第2の電位により前記出力線を放電するNネット部とが相補に動作して前記出力論理状態を生成し、

前記第1の経路は、

前記出力線から前記Nネット部を介して前記第2の供給線に通じる経路である

ことを特徴とする請求項1又は2項に記載の消費電力錯乱型論理回路。

【請求項4】

前記第1の制御信号又は前記第2の制御信号に応じて、前記第1の供給線から前記Pネット部を介して前記出力線に通じる第2の経路を遮断するPネット遮断部

を備える

ことを特徴とする請求項3に記載の消費電力錯乱型論理回路。

【請求項5】

前記入力信号及び前記乱数信号は、

前記出力制御部が前記出力無効状態にあり、前記出力線が前記第1の電位になった後に、変更され、

前記出力制御部は、

前記入力信号及び前記乱数信号の変更が確定した後に、前記第1の制御信号に基づいて前記出力無効状態を解除し、

前記出力段回路は、

前記出力無効状態が解除され、前記出力線の出力状態が確定した後に、前記第2の制御信号に基づいて前記マスク状態を解除する

ことを特徴とする請求項1から請求項4のいずれかに記載の消費電力錯乱型論理回路。

【請求項6】

前記入力信号及び前記乱数信号は、

前記出力制御部が前記出力無効状態にあり、前記Pネット遮断部が前記第2の経路を遮断した後に変更され、

前記出力制御部は、

前記入力信号及び前記乱数信号の変更が確定した後に、前記第1の制御信号に基づいて前記出力無効状態を解除し、

前記出力段回路は、

前記出力無効状態が解除され、前記出力線の出力状態が確定した後に、前記第2の制御信号に基づいて前記マスク状態を解除する

ことを特徴とする請求項4に記載の消費電力錯乱型論理回路。

【請求項7】

前記論理演算回路は、

前記入力信号に基づいて予め定められた論理演算処理に応じた論理状態を生成し、前記乱数信号に基づき、前記入力信号を反転させた前記論理演算処理を行うか否か、及び前記出力論理状態を前記論理状態から反転したものにするか否かを切り替える

ことを特徴とする請求項1から請求項6のいずれかに記載の消費電力錯乱型論理回路。

【請求項8】

秘密鍵と情報を記憶する記憶部と、

前記乱数信号を生成する乱数生成部と、

請求項1から請求項7のいずれかに記載の消費電力錯乱型論理回路を含み、前記秘密鍵に応じて暗号処理を行う暗号処理部と

を備えることを特徴とする情報記憶媒体。

【請求項1】

第1の電位が第1の供給線から供給され、該第1の電位より低い第2の電位が第2の供給線から供給され、入力される入力信号と乱数信号とに基づいて生成される出力論理状態を出力線に出力する論理演算回路と、

入力される第1の制御信号に応じて前記出力線の出力状態を制御し、前記出力論理状態を無効とする出力無効状態である場合に、前記出力線から前記第2の供給線に通じる第1の経路を遮断し、前記第1の電位により前記出力線を充電する出力制御部と、

前記論理演算回路の後段に設けられ、前記出力線の出力状態に基づいて出力する状態を無効とするマスク状態に、入力される第2の制御信号に応じて切り替える出力段回路と

を備えることを特徴とする消費電力錯乱型論理回路。

【請求項2】

前記出力制御部は、

前記出力無効状態を解除した場合、前記第1の経路を導通させ、前記生成される論理状態に応じて、前記第2の電位により前記出力線を放電する

ことを特徴とする請求項1に記載の消費電力錯乱型論理回路。

【請求項3】

前記論理演算回路は、

前記入力信号と前記乱数信号とに基づいて前記第1の電位により前記出力線を充電するPネット部と、前記入力信号と前記乱数信号とに基づいて前記第2の電位により前記出力線を放電するNネット部とが相補に動作して前記出力論理状態を生成し、

前記第1の経路は、

前記出力線から前記Nネット部を介して前記第2の供給線に通じる経路である

ことを特徴とする請求項1又は2項に記載の消費電力錯乱型論理回路。

【請求項4】

前記第1の制御信号又は前記第2の制御信号に応じて、前記第1の供給線から前記Pネット部を介して前記出力線に通じる第2の経路を遮断するPネット遮断部

を備える

ことを特徴とする請求項3に記載の消費電力錯乱型論理回路。

【請求項5】

前記入力信号及び前記乱数信号は、

前記出力制御部が前記出力無効状態にあり、前記出力線が前記第1の電位になった後に、変更され、

前記出力制御部は、

前記入力信号及び前記乱数信号の変更が確定した後に、前記第1の制御信号に基づいて前記出力無効状態を解除し、

前記出力段回路は、

前記出力無効状態が解除され、前記出力線の出力状態が確定した後に、前記第2の制御信号に基づいて前記マスク状態を解除する

ことを特徴とする請求項1から請求項4のいずれかに記載の消費電力錯乱型論理回路。

【請求項6】

前記入力信号及び前記乱数信号は、

前記出力制御部が前記出力無効状態にあり、前記Pネット遮断部が前記第2の経路を遮断した後に変更され、

前記出力制御部は、

前記入力信号及び前記乱数信号の変更が確定した後に、前記第1の制御信号に基づいて前記出力無効状態を解除し、

前記出力段回路は、

前記出力無効状態が解除され、前記出力線の出力状態が確定した後に、前記第2の制御信号に基づいて前記マスク状態を解除する

ことを特徴とする請求項4に記載の消費電力錯乱型論理回路。

【請求項7】

前記論理演算回路は、

前記入力信号に基づいて予め定められた論理演算処理に応じた論理状態を生成し、前記乱数信号に基づき、前記入力信号を反転させた前記論理演算処理を行うか否か、及び前記出力論理状態を前記論理状態から反転したものにするか否かを切り替える

ことを特徴とする請求項1から請求項6のいずれかに記載の消費電力錯乱型論理回路。

【請求項8】

秘密鍵と情報を記憶する記憶部と、

前記乱数信号を生成する乱数生成部と、

請求項1から請求項7のいずれかに記載の消費電力錯乱型論理回路を含み、前記秘密鍵に応じて暗号処理を行う暗号処理部と

を備えることを特徴とする情報記憶媒体。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2011−188009(P2011−188009A)

【公開日】平成23年9月22日(2011.9.22)

【国際特許分類】

【出願番号】特願2010−47810(P2010−47810)

【出願日】平成22年3月4日(2010.3.4)

【出願人】(000102728)株式会社エヌ・ティ・ティ・データ (438)

【Fターム(参考)】

【公開日】平成23年9月22日(2011.9.22)

【国際特許分類】

【出願日】平成22年3月4日(2010.3.4)

【出願人】(000102728)株式会社エヌ・ティ・ティ・データ (438)

【Fターム(参考)】

[ Back to top ]