液晶制御回路,液晶表示装置

【課題】アナログ回路を削減した液晶制御回路を提供する。

【解決手段】パルス信号生成部21は,第1の周期を分周した第2の周期において相互に異なるデューティー比を有し第1のレベル,第2のレベルに対応する複数のパルス信号を生成する。第1の出力部24は,複数のパルス信号SIG_0〜SIG_3の何れかのパルス信号を選択し選択した第1のパルス信号を液晶表示素子のコモン電極に第1の周期の間出力する。第2の出力部26は,複数のパルス信号SIG_0〜SIG_3の何れかのパルス信号を映像フレームの映像データに応じて選択し選択した第2のパルス信号を液晶表示素子のセグメント電極に第1の周期の間出力する。

【解決手段】パルス信号生成部21は,第1の周期を分周した第2の周期において相互に異なるデューティー比を有し第1のレベル,第2のレベルに対応する複数のパルス信号を生成する。第1の出力部24は,複数のパルス信号SIG_0〜SIG_3の何れかのパルス信号を選択し選択した第1のパルス信号を液晶表示素子のコモン電極に第1の周期の間出力する。第2の出力部26は,複数のパルス信号SIG_0〜SIG_3の何れかのパルス信号を映像フレームの映像データに応じて選択し選択した第2のパルス信号を液晶表示素子のセグメント電極に第1の周期の間出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は,液晶制御回路,液晶制御回路を有する液晶表示装置に関する。

【背景技術】

【0002】

液晶制御回路は,液晶表示素子のコモン電極とこの液晶表示素子のセグメント電極との間に電圧を発生させることで,この液晶表示素子のオン(点灯とも言う),オフ(消灯とも言う)を制御する。すなわち,液晶制御回路は,液晶表示素子のコモン電極とこの液晶表示素子のセグメント電極との間に閾値以上の電圧を発生させることで,この液晶表示素子をオンする。

【0003】

液晶制御回路は,この電圧を発生させるため,相互に異なる3つ以上の電圧を生成する電圧生成回路を有する。電圧生成回路は,例えば電源とグランドとの間に直列接続された複数の分圧抵抗を有する分圧抵抗回路を有する。電圧生成回路は,この分圧抵抗回路により,前記した3つ以上の電圧を生成するアナログ回路である。

【0004】

液晶制御回路は,3つ以上の電圧の中から基準電圧となる電圧を選択し選択した電圧を有するコモン電極駆動信号を生成しコモン電極に出力する。同時に,液晶制御回路は,液晶表示素子のオンまたはオフを指示する映像データに応じて,3つ以上の電圧の中から液晶表示素子をオンまたはオフする電圧を選択し選択した電圧を有するセグメント電極駆動信号を生成しセグメント電極に出力する。このようにして,液晶制御回路は,液晶表示素子に前記した電圧を発生させる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平08-286171号公報

【特許文献2】特開平10-133630号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

液晶制御回路は,3つ以上の電圧レベルを有するアナログ信号を取り扱う必要があるため,主にアナログ回路により構成する必要がある。しかし,例えば開発工程を削減するため,アナログ回路を削減しデジタル回路に置き換えることが望ましい。

【0007】

そこで,本発明の目的は,アナログ回路を削減した液晶制御回路を提供することにある。

【課題を解決するための手段】

【0008】

液晶制御回路の第1の側面は,映像フレームの表示周期を分周した第1の周期の開始タイミングを生成するタイミング制御部と,

前記第1の周期を分周した第2の周期において相互に異なるデューティー比を有し第1のレベル,第2のレベルに対応する複数のパルス信号を生成するパルス信号生成部と,

前記複数のパルス信号の何れかのパルス信号を選択し選択した第1のパルス信号を液晶表示素子のコモン電極に前記第1の周期の間出力する第1の出力部と,

前記複数のパルス信号の何れかのパルス信号を前記映像フレームの映像データに応じて選択し選択した第2のパルス信号を前記液晶表示素子のセグメント電極に前記第1の周期の間出力する第2の出力部とを有する。

【発明の効果】

【0009】

第1の側面によれば,コモン電極駆動信号,セグメント電極駆動信号をデジタル信号である位相変調信号により生成するのでアナログ回路を削減することができる。

【図面の簡単な説明】

【0010】

【図1】液晶表示素子を有する液晶表示部を示す図である。

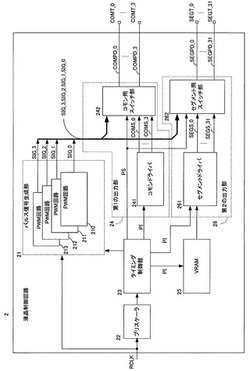

【図2】本実施の形態に関連する液晶制御回路の機能ブロック図である。

【図3】本実施の形態に関連する液晶制御回路の動作を説明する図である。

【図4】VRAMに格納されている映像データを模式的に示した図である。

【図5】本実施の形態の液晶制御回路の機能ブロック図である。

【図6】PWM信号の信号波形図の一例を示す。

【図7】本実施の形態の液晶制御回路の動作を説明する図である。

【図8】PWM回路の機能ブロック図である。

【図9】図8のPWM回路の動作を説明する図である。

【図10】コモン用スイッチ部を説明する図である。

【図11】出力タイミング制御を説明する図である。

【図12】セグメント用スイッチ部を説明する図である。

【図13】本実施の形態に関連する液晶制御回路,デジタル論理回路を搭載する半導体チップの機能ブロック図である。

【図14】液晶制御回路と液晶表示部とを有する液晶表示装置を示した図である。

【発明を実施するための形態】

【0011】

図1は,液晶表示素子を有する液晶表示部を示す図である。液晶表示部Dは,セグメント方式の液晶表示パネルであり,例えば液晶表示素子LCD0〜LCD7を有する。液晶表示素子は,液晶セルとも呼ばれる。

【0012】

一般に,液晶表示パネルは,コモン電極が形成された第1の透明基板とセグメント電極が形成された第2の透明基板とをギャップコントロール材を介して重ね合わせ,その間に液晶が封入されたものである。なお,透明基板とは,例えばガラス基板である。

【0013】

図1に示す例では,第1の透明基板において,液晶表示素子LCD0,LCD2,LCD5の透明基板部にコモン電極COM_0が形成され,液晶表示素子LCD1,LCD3,LCD6の透明基板部にコモン電極COM_1が形成され,液晶表示素子LCD4,LCD7の透明基板部にコモン電極COM_2が形成されている。

【0014】

また,第2の透明基板において,液晶表示素子LCD0,LCD1の透明基板部にセグメント電極SEG_nが形成され,液晶表示素子LCD2,LCD3,LCD4の透明基板部にセグメント電極SEG_n+1が形成され,液晶表示素子LCD5,LCD6,LCD7の透明基板部にセグメント電極SEG_n+2が形成されている。以下,nは"0"として説明する。

【0015】

図2は,本実施の形態に関連する液晶制御回路の機能ブロック図である。液晶制御回路1は,コモン端子COMT_0〜COMT_3のそれぞれに接続されたコモン電極にコモン電極駆動信号COMVD_0〜COMVD_3を出力する。また,液晶制御回路1は,セグメント端子SEGT_0〜SEGT_31のそれぞれに接続されたセグメント電極にセグメント電極駆動信号SEGVD_0〜SEGVD_31を出力する。

【0016】

液晶制御回路1は,コモン電極駆動信号COMVD_0〜COMVD_3,セグメント電極駆動信号SEGVD_0〜SEGVD_31により,コモン端子COMT_0〜COMT_3,セグメント端子SEGT_0〜SEGT_31に接続された液晶表示部の液晶表示素子のオン,オフを制御する。

【0017】

図1の液晶表示部Dにおいて,例えば,図2のコモン端子COMT_0〜COMT_2がそれぞれコモン電極COM_0〜COM_2に接続され,セグメント端子SEGT_0〜SEGT_2がそれぞれセグメント電極SEG_0〜SEG_2に接続される。

【0018】

図3は,液晶制御回路1の動作を説明する図である。

【0019】

時間T0〜T1は,1映像フレームの表示周期FPに相当する。この表示周期は,映像フレーム周期とも言われる。時間T1〜T2,時間T2〜T3,時間T3〜T4,時間T4〜T5も,1映像フレームの表示周期に相当する。

【0020】

表示周期FPは,所定数で分周される。表示周期が所定数で分周されることは,表示周期が所定数で時分割されることと同意である。この所定数は,図1で説明したコモン電極の数に対応する。図1の例では,コモン電極の数は3つ(コモン電極COM_0〜COM_2)なので,所定数"3"で時分割される。例えば,時間T1〜T2の表示周期FPにおいて,表示周期FPは,時分割周期TDP_0〜TPD_2の3つに時分割されている。

【0021】

図3(A)〜図3(C)は,コモン電極駆動信号COMVD_0〜COMVD_2の信号波形の一例を示す。図3(D)は,セグメント電極駆動信号SEGVD_1の信号波形の一例を示す。図3(A)〜図3(D)において,縦軸は電圧を示し,横軸は時間を示す。縦軸の電圧V0〜V3は,図2の電圧生成回路11が生成する電圧である。

【0022】

図3(E)〜図3(G)は,図3(A)〜図3(D)に示した駆動信号により電圧差が生じる液晶表示素子LCD2〜LCD4のオン状態,オフ状態を示す図である。

【0023】

液晶表示素子のコモン電極に出力されたコモン電極駆動信号の電圧とこの液晶表示素子のセグメント電極に出力されたセグメント電極駆動信号の電圧との電圧差が所定の閾値Vth以上の時分割周期において,この液晶表示素子はオンする。一方,この電圧差が所定の閾値Vth未満の時分割周期においては,この液晶表示素子はオフする。所定の閾値Vthは,例えば,電圧V3-電圧V0である。

【0024】

例えば,時間T1〜T2の表示周期FPにおける先頭の時分割周期TDP_0において,コモン電極駆動信号COMVD_0の電圧V0とセグメント電極駆動信号SEGVD_1の電圧V3との電圧差は,所定の閾値Vth以上である(符号P1,P2参照)。従って,時分割周期TDP_0において,電圧V0を有するコモン電極駆動信号COMVD_0と電圧V3を有するセグメント電極駆動信号SEGVD_1とが入力される液晶表示素子LCD2は,オンする(符号P3参照)。

【0025】

一方,時分割周期TDP_1,TDP_2において,コモン電極駆動信号COMVD_0の電圧V2とセグメント電極駆動信号SEGVD_1の電圧V1または電圧V3の電圧差は,所定の閾値Vth未満である(符号P1,P2参照)。従って,液晶表示素子LCD2は,オフする(符号P3参照)。

【0026】

なお,図3(F)に示すように,液晶表示素子LCD3についても,液晶表示素子LCD3のコモン電極COM_1に出力されるコモン電極駆動信号COMVD_1の電圧と液晶表示素子LCD3のセグメント電極SEG_1に出力されるセグメント電極駆動信号SEGVD_1の電圧との電圧差に基づき,液晶表示素子LCD3のオン,オフが制御される。同じく,図3(G)に示すように,液晶表示素子LCD4についても,液晶表示素子LCD4のコモン電極COM_2に出力されるコモン電極駆動信号COMVD_2の電圧と液晶表示素子LCD4のセグメント電極SEG_1に出力されるセグメント電極駆動信号SEGVD_1の電圧との電圧差に基づき,液晶表示素子LCD4のオン,オフが制御される。

【0027】

図3に例示したコモン電極駆動信号,セグメント電極駆動信号を生成する液晶制御回路1について説明する。

【0028】

図2の電圧生成回路11は,電圧V3〜V0を生成し,電圧V3〜V0をコモン用スイッチ部14,セグメント用スイッチ部15に出力する。電圧生成回路11は,高電源VCCとグランドGNDとの間に,直列接続された分圧抵抗Ra,Rb,Rcを有し,この分圧抵抗Ra,Rb,Rcにより電圧V3〜V0を生成する。

【0029】

プリスケーラ12は,基準クロックRCLKを所定の分周比で分周し,タイミング制御部13に出力する。

【0030】

タイミング制御部13は,プリスケーラ12から入力された基準クロックRCLKの分周クロックに基づき,映像フレームの表示処理に必要な各種制御を実行する。例えば,タイミング制御部13は,映像フレームの表示周期FPの開始タイミングを生成する。また,タイミング制御部13は,映像フレームの表示周期FPを時分割した時分割周期TDPの開始タイミングを生成する。そして,タイミング制御部13は,時分割周期TDPの開始タイミングを開始タイミング情報PSとしてコモン用スイッチ部14,セグメント用スイッチ部15に出力する。

【0031】

さらに,タイミング制御部13は,各表示周期FPにおいて先頭からTN番目の時分割周期TDP_TNの開始タイミングを生成すると,TN番目の時分割周期TDP_TNの開始タイミングを生成したことを示すフェーズ情報PIを生成する。図3の例では,TNは0〜2である。ここで,0番目の時分割周期TDP_0の開始タイミングは表示周期FPの開始タイミングであり,表示周期FPにおいて最初に生成された時分割周期の開始タイミングである。そして,タイミング制御部13は,生成したフェーズ情報PIを,コモンドライバ16,VRAM17,セグメントドライバ18に出力する。

【0032】

コモン用スイッチ部14は,コモンドライバ16から入力されたコモン用選択信号COMS_0〜COMS_3に基づき,電圧生成回路11が生成する電圧V0〜V3の中の何れかの電圧を選択する。すなわち,コモン用スイッチ部14は,コモン端子COMT_CN(CNは0〜3)に対応して設けられたスイッチを有する。このスイッチは,コモンドライバ16から入力されたコモン用選択信号COMS_CNに基づき,電圧V0〜V3の中の何れか1つの電圧を選択する。

【0033】

そして,コモン用スイッチ部14は,選択した電圧をコモン端子COMT_CNにタイミング制御部13から入力された開始タイミング情報PSに応答して出力する。

【0034】

セグメント用スイッチ部15は,セグメントドライバ18から入力された選択信号SEGS_0〜SEGS_31に基づき,電圧生成回路11が生成する電圧V0〜V3の中の何れかの電圧を選択する。すなわち,セグメント用スイッチ部15は,セグメント端子SEGT_SN(SNは0〜31)に対応して設けられたスイッチを有する。このスイッチは,セグメントドライバ18から入力された選択信号SEGS_SNに基づき,電圧V0〜V3の中の何れか1つの電圧を選択する。

【0035】

そして,セグメント用スイッチ部15は,選択した電圧をセグメント端子SEGT_SNにタイミング制御部13から入力された開始タイミング情報PSに応答して出力する。

【0036】

コモンドライバ16は,タイミング制御部13から入力されたフェーズ情報PIに基づき,コモン用選択信号COMS_0〜COMS_3を生成し,コモンドライバ16に出力する。

【0037】

VRAM17は,1映像フレームの映像データが格納されるメモリである。映像データは,1フレーム毎に例えば外部CPUにより新たに格納(更新)される。VRAM17は,タイミング制御部13から入力されたフェーズ情報PIに基づき,VRAM17に格納されている映像データを選択し,選択した映像データVRをセグメントドライバ18に出力する。

【0038】

図4は,VRAM17に格納されている映像データを模式的に示した図である。図4に示すように,コモン端子COMT_0〜COMT_3,セグメント端子SEGT_0,SEGT_1…に対応する液晶表示素子のオン,オフを指示する映像データbit0,bit1…が格納されている。例えば,コモン端子COMT_0,セグメント端子SEGT_1に対応する液晶表示素子LCD2のオン,オフを指示する映像データbit4が格納されている。なお,映像データのビットが"1"の場合,液晶表示素子をオン,映像データが"0"の場合,液晶表示素子をオフにする。

【0039】

セグメントドライバ18は,タイミング制御部13から入力されたフェーズ情報PI,VRAM17から入力された映像データVRに応じて,選択信号SEGS_0〜SEGS_31を生成し,セグメント用スイッチ15に出力する。

【0040】

ここで,液晶制御回路1の動作を詳細に説明する。タイミング制御部13は,例えば,図3に示した時間T1〜T2の表示周期FPの開始タイミングを生成する。また,タイミング制御部13は,表示周期FPにおいて先頭からTN番目(TNは0〜2)の時分割周期TDP_TNの開始タイミングを生成すると,TN番目の時分割周期TDP_TNの開始タイミングを生成したことを示すフェーズ情報PIを生成する。

【0041】

コモンドライバ16は,表示周期FPにおいて先頭からTN番目の開始タイミングを生成したことを示すフェーズ情報PIが入力されると,連続する表示周期FPにおいて一定の波形パターンを有するコモン電極駆動信号COMVD_TNが生成されるように最大電圧V3または最小電圧V0の何れかを決定する。そして,コモンドライバ16は,決定した電圧を選択するようにコモン用スイッチ部14に指示するコモン用選択信号COMS_TNを生成する。

【0042】

一方,コモン用選択信号COMS_0〜COMS_3のうちコモン用選択信号COMS_TN以外のコモン用選択信号については,コモンドライバ16は,連続する表示周期FPにおいて一定の波形パターンを有するコモン電極駆動信号が生成されるように,中間電圧V1またはV2の何れか1つを決定する。そして,コモンドライバ16は,決定した電圧を選択するようにコモン用スイッチ部14に指示するコモン用選択信号を生成する。なお,中間電圧は,中間電位とも言う。

【0043】

VRAM17は,タイミング制御部13からフェーズ情報PIが入力されると表示周期FPにおいて先頭からTN番目の時分割周期TDP_TNに対応するコモン端子COMT_TNの列に格納された映像データを選択し,選択した映像データVRをセグメントドライバ18に出力する。

【0044】

セグメントドライバ18は,VRAM17から入力された映像データによりオンが指定される液晶表示素子のコモン電極とこの液晶表示素子のセグメント電極との間の電圧が所定の閾値Vth以上になる電圧を電圧V3〜V0の中から決定する。または,VRAM17から入力された映像データによりオフが指定される液晶表示素子のコモン電極とこの液晶表示素子のセグメント電極との間の電圧が所定の閾値Vth未満になる電圧を電圧V3〜V0の中から決定する。そして,この決定した電圧を選択するようにセグメント用スイッチ部15に指示するセグメント用選択信号SEGS_0〜SEGS_31を生成する。

【0045】

さらに,タイミング制御部13は,生成した時分割周期TDP_TNの開始タイミングを開始タイミング情報PSとして,コモン用スイッチ部14,セグメント用スイッチ部15に出力する。なお,この場合, 時分割周期TDP_0の開始タイミング情報PSは,時間T1に対応する。

【0046】

コモン用スイッチ部14は,コモン用選択信号COMS_0〜COMS_3に基づき,電圧V3〜V0を選択し,開始タイミング情報PSに応答して,コモン端子COMT_0〜COMT_3に出力する。

【0047】

同じく,セグメント用スイッチ部15は,セグメント用選択信号SEGS_0〜SEGS_31に基づき,電圧V3〜V0を選択し,開始タイミング情報PSに応答して,セグメント端子SEGT_0〜SEGT_31に出力する。その結果,コモン電極駆動信号COMVD_0〜COMVD_3,セグメント電極駆動信号SEGVD_0〜SEGVD_31が生成される。

【0048】

液晶制御回路1は,このようにして,コモン電極駆動信号,セグメント電極駆動信号を生成して,液晶表示素子のコモン電極,セグメント電極に出力することで,液晶表示素子のオン,オフを制御する。

【0049】

ところで,電圧生成回路11は,複数の抵抗を有するアナログ回路である。また,コモン用スイッチ部14,セグメント用スイッチ部15,コモンドライバ16,セグメントドライバ18は,3つ以上の電圧を有するアナログ信号を取り扱う必要があるためアナログ回路で構成する必要がある。例えば,コモン用スイッチ部14,セグメント用スイッチ部15は,スイッチ素子として,CMOSトランスファゲートを利用する。しかし,例えば開発工程を削減するため,アナログ回路を削減しデジタル回路に置き換えることが望ましい。

【0050】

(本実施の形態)

本実施の形態において,液晶表示素子の液晶は,容量(キャパシタ)として機能する,すなわち容量成分(浮遊容量)であることに着目する。

【0051】

ここで,液晶表示素子のコモン電極とセグメント電極とにパルス幅変調信号(以下,PWM信号と略記する)を出力するとする。液晶表示素子の液晶は容量成分であるので,このPWM信号は,液晶表示素子の液晶内部において,PWM信号のデューティー比(Hレベル幅)に対応する電圧に変換される。また,PWM信号のデューティー比を変化させることにより,コモン電極とセグメント電極との間に様々な電圧を発生させることができる。そのため,この電圧差により液晶表示素子のオン,オフを制御することができる。

【0052】

PWM信号は,2つの電圧レベル(Hレベル,Lレベル)を有するデジタル信号であるので,PWM信号を扱う回路をデジタル化することができる。その結果,開発工程が削減され,開発費用,開発時間が少なくなる。

【0053】

図5は,本実施の形態の液晶制御回路2の機能ブロック図である。パルス信号生成部21は,4つのPWM回路(パルス幅変調回路)210〜PWM回路213を有する。

【0054】

図6は,PWM信号の信号波形図の一例を示す。図6(A)〜図6(D)は,PWM信号SIG_0〜SIG_3の信号波形図の一例である。符号PWMPはPWM信号の周期を示し,縦軸はPWM信号の電圧(HレベルまたはLレベル),横軸は時間を示す。PWM信号SIG_0〜SIG_3は,それぞれ電圧V0〜V3に対応する。

【0055】

ここで,時間T10〜T14が時分割周期TDPであり,この時分割周期TDPを例えば3つに分周してそれぞれをPWM信号のPWM周期PWMPとしている。時分割周期が第1の周期であり,PWM周期が第2の周期である。このように,時分割周期TDPを分周して,PWM周期とする理由については,後述する。

【0056】

PWM回路210は,図6(A)に示すように,PWM周期PWMPにおいて,デューティー比が0%のPWM信号SIG_0を生成する。PWM回路211は,図6(B)に示すように,PWM周期PWMPにおいて,デューティー比が33%のPWM信号SIG_1を生成する。PWM回路212は,図6(C)に示すように,PWM周期PWMPにおいて,デューティー比が66%のPWM信号SIG_2を生成する。PWM回路213は,図6(D)に示すように,PWM周期PWMPにおいて,デューティー比が100%のPWM信号SIG_3を生成する。

【0057】

液晶制御回路2は,PWM信号SIG_0〜SIG_3の何れか1を選択しコモン電極駆動信号として液晶表示素子のコモン電極に出力する。同時に,液晶制御回路2は,PWM信号SIG_0〜SIG_3の何れか1を選択しセグメント電極駆動信号としてこの液晶表示素子のセグメント電極に出力する。そして,液晶制御回路2は,この駆動信号の出力によりコモン電極とセグメント電極との間に電圧差を発生させ,この電圧差により液晶表示素子のオン,オフを制御する。

【0058】

図7は,本実施の形態の液晶制御回路2の動作を説明する図である。

【0059】

図7(A)は,図3の符号P1に示す部分のコモン電極駆動信号COMVD_0の信号波形を示す。図7(A')は,コモン電極駆動信号COMVD_0の電圧に相当する電圧をPWM信号により生成するコモン電極駆動信号COMPD_0を示す。

【0060】

時間T1〜T110の時分割周期TPD_0において,液晶制御回路2は,コモン電極駆動信号COMVD_0の電圧V0に相当する電圧を,図7(A')に示すように,デューティー比0%のPWM信号SIG_0により生成する。

【0061】

また,時間T110〜T120の時分割周期TPD_1,時間T120〜T2の時分割周期TDP_2において,液晶制御回路2は,コモン電極駆動信号COMVD_0の電圧V2に相当する電圧を,図7(A')に示すように,デューティー比66%のPWM信号SIG_2により生成する。

【0062】

図7(B)は,図3の符号P2に示す部分のセグメント電極駆動信号SEGVD_1の信号波形を示す。図7(B')は,セグメント電極駆動信号SEGVD_1の電圧に相当する電圧をPWM信号により生成するセグメント電極駆動信号SEGPD_1を示す。

【0063】

時分割周期TPD_0において,液晶制御回路2は,セグメント電極駆動信号SEGVD_1の電圧V3に相当する電圧を,図7(B')に示すように,デューティー比100%のPWM信号SIG_3により生成する。

【0064】

時分割周期TPD_1において,液晶制御回路2は,セグメント電極駆動信号SEGVD_1の電圧V1に相当する電圧を,図7(B')に示すように,デューティー比33%のPWM信号SIG_1により生成する。

【0065】

また,時分割周期TPD_2において,液晶制御回路2は,セグメント電極駆動信号SEGVD_1の電圧V3に相当する電圧を,図7(B')に示すように,デューティー比100%のPWM信号SIG_3により生成する。

【0066】

ここで,時分割周期TDPを複数のPWM周期に分周する理由を説明する。前述したように,液晶制御回路2が出力するコモン電極駆動信号,セグメント電極駆動信号により,液晶表示素子のコモン電極とセグメント電極との間の電圧差が変化する。そして,変化後の電圧差が閾値Vth以上になると,この液晶表示素子がオンし,この変化後の電圧差が閾値Vth未満になるとオフする。

【0067】

ところで,液晶表示素子は,この電圧変化に応答して,オンオフ,オフオンするまでに所定の時間(タイムラグ)を要する。この時間が短いほど,液晶表示素子の電圧変化に対する応答性(追随性)は高い。そして,この応答性は,液晶表示素子に封入された液晶の種類毎に異なる。

【0068】

液晶制御回路2が,PWM周期が長いPWM信号により,応答性が高い液晶表示素子のオン,オフを制御すると,液晶画面がちらつくことがある。これは,PWM信号の電圧レベル変化(PWM信号の立ち上がり,立ち下がり)に対して液晶表示素子が素早く応答して,高速にオン,オフするからである。

【0069】

このちらつきを防止するため,液晶制御回路2は,応答性が高い液晶表示素子のオンオフを制御する場合,PWM周期が短いPWM信号により,この液晶表示素子のオン,オフ制御を行う必要がある。すなわち,液晶表示素子の応答性に応じて,最適なPWM周期を調整する必要がある。

【0070】

そこで,液晶制御回路2のパルス信号生成部21は,PWM信号のPWM周期を調整可能なPWM回路210〜PWM回路213を有する。

【0071】

図8は,PWM回路21xの機能ブロック図である。PWM回路21xは,PWM回路210〜PWM回路213に相当するものであり,PWM回路210〜PWM回路213は,PWM回路21xと同様の機能ブロックを有する。

【0072】

PWM回路21xは,PWM周期を設定する周期設定レジスタ211xと,PWM信号のデューティー比を設定するデューティー比設定レジスタ212xとを有し,周期設定レジスタ211xの設定値PV(第1の設定値),および,デューティー比設定レジスタ212xの設定値DV(第2の設定値)を有するパルス信号であるPWM信号SIG_xを生成する。このようなPWM回路は,PPG(Programmable Pulse Generator)とも呼ばれる。この設定値PV,設定値DVは,後述するように,分周クロックDRCLKのクロック数に対応する。

【0073】

周期設定レジスタ211xの設定値PVは,外部,例えばタイミング制御部23から設定可能である。周期設定レジスタ211xは,設定値PVがタイミング制御部23から設定されると,設定された設定値PVをバッファ213xに出力する。

【0074】

デューティー比設定レジスタ212xの設定値DVは,外部,例えばタイミング制御部23から設定可能である。デューティー比設定レジスタ212xは,設定値DVがタイミング制御部23から設定されると設定値DVをバッファ214xに出力する。また,設定値DVがタイミング制御部23から新たに設定(更新)されると,ボロー信号Brの入力に応答して,新たに設定された設定値DVをバッファ214xに出力する。

【0075】

バッファ213xは,周期設定レジスタ211xの設定値PVを一時的に格納(バッファリング)するバッファである。バッファ213xは,PWM信号生成開始指示がPWM信号生成部21から入力された場合や,ボロー信号Brがダウンカウンタ216xから入力された場合,設定値PVをダウンカウンタ216xに出力する。

【0076】

バッファ214xは,デューティー比設定レジスタ212xの設定値DVをバッファリングするバッファである。バッファ214xは,設定値DVを比較器217xの非反転入力端子(+端子)に出力する。

【0077】

プリスケーラ215xは,基準クロックRCLKを所定の分周比で分周し,分周した分周クロックDRCLKをダウンカウンタ216xに出力する。

【0078】

ダウンカウンタ216xは,入力された分周クロックDRCLKに基づき,バッファ213xから入力されたPWM周期の設定値PVをダウンカウントして,カウント結果CNTを比較器217xの反転入力端子(-端子)に出力する。また,カウント結果CNTが0になるとボロー信号(桁下がり信号)Brをデューティー比設定レジスタ212x,バッファ213x,出力レベル部218xに出力する。

【0079】

比較器217xは,デューティー比の設定値DVとカウント結果CNTとを比較し,比較信号CMPを出力レベル部218xに出力する。すなわち,カウント結果CNTがデューティー比の設定値DVよりも大きい間は,ローレベルの比較信号CMPを出力レベル部218xに出力する。一方,カウント結果CNTがデューティー比の設定値DVよりも小さくなると,以後ハイレベルの比較信号CMPを出力レベル部218xに出力する。

【0080】

出力レベル部218xは,比較器217xから入力された比較信号CMPをラッチしPWM信号SIG_xとして出力する。このとき,ハイレベルの比較信号CMPが入力されると,比較信号CMPのレベルをより高レベルにシフトしてもよい。これは,液晶表示素子のコモン電極とセグメント電極との間に所定の閾値Vth 以上の電圧を発生させ,液晶表示素子をオンさせるためである。また,ボロー信号Brが入力されると,ハイレベルの比較信号CMPを立ち下げる。

【0081】

図9は,図8のPWM回路21xの動作を説明する図である。図9(A)は,カウント結果CNTの変化を示す図で,縦軸がカウント結果CNTの値を示し,横軸が時間を示す。図9(B)は,PWM信号SIG_xの信号波形図で,縦軸がレベルを示し,横軸が時間を示す。図9(B)の符号PWMPは,PWM信号SIG_xのPWM周期を示す。また,符号DTYは,PWM信号SIG_xのハイレベルの幅(デューティー比)を示す。

【0082】

ここで,既に,周期設定レジスタ211xにはPWM周期の設定値PVが設定され,デューティー比設定レジスタ212xにはデューティー比の設定値DVが設定されている。このとき,分周クロックDRCLKの1周期をTa[ms]とすると,Ta×(PV+1)[ms]がPWM周期PWMPである。すなわち,PWM周期の設定値PV,プリスケーラ215xの分周比を変更すれば,PWM周期PWMPを変更することができる。また,Ta×(DV+1)[ms]がデューティー比DTYである。すなわち,デューティー比の設定値DV,プリスケーラ215xの分周比を変更すれば,デューティー比DTYを変更することができる。

【0083】

さて,図9の時間T10において,PWM信号生成部21からのPWM信号生成開始指示に応答して,バッファ213xがダウンカウンタ216xに設定値PVを出力する。また,バッファ214xは比較器217xの非反転入力端子に設定値DVを出力する。ダウンカウンタ216xは,入力される分周クロックDRCLKに基づき入力された設定値PVをダウンカウントし,カウント結果CNTが0になるまでダウンカウントを継続する。このダウンカウンタ216xによるダウンカウントの開始タイミングがPWM信号SIG_xのPWM周期の開始タイミングである。この開始タイミングは,図9の例では,時間T10,時間T11である。

【0084】

時間T10〜Tdにおいて,カウント結果CNTはデューティー比の設定値DVよりも大きいので,比較器217xは,ローレベルの比較信号CMPを出力する。その結果,出力レベル部218xは,ローレベルのPWM信号SIG_xを出力する。

【0085】

時間Tdにおいて,カウント結果CNTがデューティー比の設定値DVよりも小さくなると,比較器217xは,ハイレベルの比較信号CMPを出力する。その結果,出力レベル部218xは,ハイレベルのPWM信号SIG_xを出力する。

【0086】

時間Tdから,カウント結果CNTが0になる時間T11に至るまで間,カウント結果CNTは,デューティー比の設定値DVよりも小さいので,比較器217xは,ハイレベルの比較信号CMPの出力を継続する。そのため,出力レベル部218xは,ハイレベルのPWM信号SIG_xの出力を継続する。

【0087】

カウント結果CNTが0になると,ダウンカウンタ216xはボロー信号Brをデューティー比設定レジスタ212x,バッファ213x,出力レベル部218xに出力する。すると,出力レベル部218xは,ハイレベルのPWM信号SIG_xをローレベルに立ち下げる。また,バッファ213xは,設定値PVをダウンカウンタ216xに出力する。そして,ダウンカウンタ216xは,ダウンカウントを開始する。

【0088】

なお,デューティー比設定レジスタ212xに新たに設定値DVが設定された場合には,ボロー信号Brの入力に応答して,デューティー比設定レジスタ212xは,バッファ214xに設定値DVを出力する。

【0089】

以後,PWM回路21xは,上記で説明した処理を繰り返す。

【0090】

図5の説明に戻る。プリスケーラ22は,基準クロックRCLKを所定の分周比で分周し,タイミング制御部23に出力する。

【0091】

タイミング制御部23は,プリスケーラ22から入力された基準クロックRCLKの分周クロックに基づき,映像フレームの表示処理に必要な各種制御を実行する。例えば,タイミング制御部23は,映像フレームの表示周期FPの開始タイミングを生成する。

【0092】

また,タイミング制御部23は,映像フレームの表示周期FPを時分割(分周)した時分割周期TDP(第1の周期)の開始タイミングを生成する。そして,タイミング制御部23は,時分割周期TDPの開始タイミングを開始タイミング情報PSとしてコモン用スイッチ部242,セグメント用スイッチ部262に出力する。タイミング制御部23が,開始タイミング情報PSをコモン用スイッチ部242,セグメント用スイッチ部262に出力する理由については,図11で説明する。

【0093】

また,タイミング制御部23は,各表示周期FPにおいて先頭からTN番目の時分割周期TDP_TNの開始タイミングを生成すると,TN番目の時分割周期TDP_TNの開始タイミングを生成したことを示すフェーズ情報PIを生成する。図3の例では,TNは0〜2である。ここで,0番目の時分割周期TDP_0の開始タイミングは表示周期FPの開始タイミングであり,表示周期FPにおいて最初に生成された時分割周期の開始タイミングである。そして,タイミング制御部23は,フェーズ情報PIをコモンドライバ241,VRAM25,セグメントドライバ261に出力する。

【0094】

また,液晶制御回路2の起動時などにおいて,タイミング制御部23は,PWM周期PWMPに対応する図8に示した分周クロックDRCLKのクロック数をPWM回路210〜213の周期設定レジスタに設定する。例えば,時分割周期TDPを3つのPWM周期PWMPに分周し,時分割周期TDPに対応する分周クロックDRCLKのクロック数がTDPNUMとする。この場合,タイミング制御部23は,"クロック数TDPNUM×(1/3)"を設定値PVとしてPWM回路210〜213の周期設定レジスタに設定する。

【0095】

そして,タイミング制御部23は,"0"をPWM回路210のデューティー比レジスタに設定し,"設定値PV×(1/3)"をPWM回路211のデューティー比レジスタに設定し,"設定値PV×(2/3)"をPWM回路212のデューティー比レジスタに設定し,"設定値PV"をPWM回路213のデューティー比レジスタに設定する。

【0096】

その結果,複数のPWM回路210〜PWM回路213の周期設定レジスタ毎にPWM周期PWMP(第2の周期)が設定され,複数のPWM回路210〜PWM回路213のデューティー比設定レジスタ毎に相互に異なるデューティー比が設定される。

【0097】

また,タイミング制御部23は,表示周期FPの最初の開始タイミングの生成に合わせて,パルス信号生成部21にPWM信号生成開始を指示する。なお,タイミング制御部23は,表示周期FPの開始タイミングの生成時や,時分割周期TDPの開始タイミングの生成時に適宜,この指示を実行してもよい。例えば,タイミング制御部23は,一定時間の経過毎に,時分割周期TDPの開始タイミングの生成時にこの指示を行ってもよい。

【0098】

パルス信号生成部21は,この指示に応答して,PWM回路210〜PWM回路213の周期設定レジスタ(211x)のバッファ(213x)に設定された設定値PVをダウンカウンタ(216x)に出力するようにPWM生成回路210〜PWM生成回路213に指示し,PWM信号の生成を開始させる。

【0099】

前記の設定により,パルス信号生成部21は,時分割周期TDPを分周したPWM周期PWMPにおいて相互に異なるデューティー比を有しローレベル(第1のレベル),ハイレベル(第2のレベル)に対応する複数のPWM信号(パルス信号)SIG_0〜SIG_3を生成する。そして,前記の指示により,時分割周期TDPの開始タイミングとPWM信号のPWM周期の開始タイミングとが図6,図7に示したように同期する。

【0100】

第1の出力部24は,複数のPWM信号SIG_0〜SIG_3の何れかのPWM信号を選択し選択した第1のPWM信号を液晶表示素子のコモン電極に接続するコモン端子に時分割周期TDPの間出力する。

【0101】

VRAM25は,図2のVRAM17と同様の機能を有し,映像フレームの映像データを格納する。

【0102】

第2の出力部26は,複数のPWM信号SIG_0〜SIG_3の何れかのPWM信号をVRAM25に格納された映像フレームの映像データに応じて選択し選択した第2のPWM信号を液晶表示素子のセグメント電極に接続するセグメント端子にPWM周期の間出力する。

【0103】

タイミング制御部23は,時分割周期TDPの開始タイミングと,第1,第2のPWM信号のPWM周期(第2の周期)の開始タイミングとを同期させるため,前記のように,パルス信号生成部21にPWM信号生成開始を指示する。

【0104】

前述したように,タイミング制御部23は,映像フレームの表示周期FPを時分割した時分割周期TDPの開始タイミングを生成する。また,タイミング制御部23は,表示周期FPにおいて先頭からTN番目の時分割周期TDP_TNの開始タイミングを生成したことを示すフェーズ情報PIを生成する。図3の例では,TNは0〜2である。

【0105】

第1の出力部24のコモンドライバ241は,連続する表示周期FPにおいて一定の波形パターンを有するコモン電極駆動信号が生成されるために必要となるPWM信号の決定パターンが記録されたパターン情報を有する。そして,このパターン情報,フェーズ情報PIに基づき,PWM信号の決定を行う。

【0106】

すなわち,コモンドライバ241は,タイミング制御部23からフェーズ情報PIが入力されると,連続する表示周期FPにおいて一定の波形パターンを有するコモン電極駆動信号COMPD_TNが生成されるようにPWM信号SIG_3またはPWM信号SIG_0の何れか1つを決定する。そして,コモンドライバ241は,決定したPWM信号を選択するようにコモン用スイッチ部242に指示するコモン用選択信号COMS_TNを生成する。

【0107】

コモン用選択信号COMS_0〜COMS_3のうちコモン用選択信号COMS_TN以外のコモン用選択信号について説明する。コモンドライバ241は,コモン電極駆動信号COMPD_TN以外のコモン電極駆動信号が一定の波形パターンを有するように,PWM信号SIG_1またはPWM信号SIG_2の何れか1つを決定する。そして,コモンドライバ241は,決定したPWM信号を選択するようにコモン用スイッチ部242に指示するコモン用選択信号を生成する。

【0108】

コモン用スイッチ部242は,コモンドライバ241から入力されたコモン用選択信号COMS_0〜COMS_3に基づき,PWM信号SIG_0〜SIG_3の中の何れかのPWM信号を選択する。そして,コモン用スイッチ部242は,選択したPWM信号をコモン端子COMT_0〜COMT_3に,タイミング制御部23から入力された時分割周期TDPの開始タイミングを示す開始タイミング情報PSに応答して出力する。

【0109】

図10は,コモン用スイッチ部を説明する図である。図10(A)は,コモン用スイッチ部242の機能ブロック図,図10(B)は,コモン用スイッチ部242のセレクタ(SEL)242_0の機能ブロック図である。

【0110】

コモン用スイッチ部242は,コモン端子COMT_0〜COMT_3に対応して設けられたセレクタ(SEL)242_0〜セレクタ242_3を有する。図10(B)では,セレクタ242_0について示しているが,セレクタ242_1〜242_3についても同様の構成を有する。

【0111】

セレクタ242_CN(CNは0〜3)は,SIG_PN(PNは0〜3)を選択するように指示するコモン用選択信号COMS_CNに基づき,PWM信号SIG_0〜SIG_3の中の何れかのPWM信号を選択する。そして,開始タイミング情報PSに応答して,選択した信号をコモン端子COMT_CNに出力する。そのため,セレクタ242_CNは,開始タイミング情報PSが次に入力されるまでの間(時分割周期TDPの間),選択したPWM信号を出力する。

【0112】

図11は,PWM信号の出力タイミング制御を説明する図である。タイミング制御部23が,開始タイミング情報PSをコモン用スイッチ部242,セグメント用スイッチ部262に出力する理由について説明する。

【0113】

図11(A)は,図7(A)に対応する。図11(A’),図11(A”)は,コモン電極駆動信号COMPD_0の出力タイミングを示す。ここで,コモン用スイッチ部242は,時分割周期TDP_1において,デューティー比66%のPWM信号SIG_2を選択する。この選択されたPWM信号SIG_2は,出力対象のPWM信号である。

【0114】

このとき,タイミング制御部23は,図11(A’)の矢印TMG0に示すように,時分割周期TDP_1の開始タイミング(時間T110)と選択されたPWM信号SIG_2の出力タイミングを同期させる必要がある。すなわち,タイミング制御部23は,時分割周期TDPの開始タイミングと,選択されたPWM信号の出力タイミングを同期させる必要がある。

【0115】

その理由を説明する。例えば,図11(A”)の矢印TMG1に示すように,選択されたPWM信号SIG_2の出力タイミングがずれてしまうと,時分割周期TDP_1におけるPWM信号SIG_2のハイレベル幅の時間が短くなる。その結果,時分割周期TDP_1において,このPWM信号SIG_2を有するコモン電極駆動信号COMPD_0がコモン電極COMT_0に入力されることによりこの電極に生じる電圧が,小さくなる。そのため,コモン電極COM_0と,このコモン電極に対応するセグメント電極との間に所望の電圧が発生しなくなり,コモン電極COM_0と前記したセグメント電極とを有する液晶表示素子のオン,オフ制御を適切に行うことができなくなることがある。

【0116】

以上の理由により,タイミング制御部23は,開始タイミング情報PSをコモン用スイッチ部242に出力する。また,タイミング制御部23が,開始タイミング情報PSをセグメント用スイッチ部262に出力する理由も同様である。

【0117】

図5の説明に戻る。VRAM25は,図2のVRAM17と同様の機能を有する。すなわち,VRAM25は,表示周期FPにおいて先頭からTN番目の時分割周期TDP_TNの開始タイミングを生成したことを示すフェーズ情報PIが入力されると,時分割周期TDP_TNに対応するコモン端子COMT_TNの列に格納された映像データを選択し,選択した映像データVRをセグメントドライバ261に出力する。

【0118】

セグメントドライバ261は,VRAM25から入力された映像データによりオンが指定される液晶表示素子のコモン電極とこの液晶表示素子のセグメント電極との間の電圧が所定の閾値Vth以上になるPWM信号をPWM信号SIG_0〜SIG_3の中から決定する。

【0119】

または,セグメントドライバ261は,VRAM25から入力された映像データによりオフが指定される液晶表示素子のコモン電極とこの液晶表示素子のセグメント電極との間の電圧が所定の閾値Vth未満になるPWM信号をPWM信号SIG_0〜SIG_3の中から決定する。この決定されたPWM信号は,前記のセグメント電極に出力される信号である。

【0120】

なお,前述したように,コモンドライバ241は,パターン情報,フェーズ情報PIに基づき,PWM信号の決定を行う。セグメントドライバ261は,このパターン情報にアクセス可能である。従って,セグメントドライバ261は,パターン情報,フェーズ情報PIに基づき,VRAM25から入力された映像データによりオン,オフが指定される液晶表示素子のコモン電極にPWM信号SIG_0〜SIG_4の中の何れかが出力されるかを認識できるので,前記したPWM信号の決定が可能である。

【0121】

セグメントドライバ261は,前記決定したPWM信号を選択するようにセグメント用スイッチ部262に指示するセグメント用選択信号SEGS_0〜SEGS_31を生成する。

【0122】

セグメント用スイッチ部262は,セグメントドライバ261から入力されたセグメント用選択信号SEGS_0〜SEGS_31に基づき,PWM信号SIG_0〜SIG_3の中の何れかのPWM信号を選択する。そして,セグメント用スイッチ部262は,タイミング制御部23から入力された時分割周期TDP_TNの開始タイミングを示す開始タイミング情報PSに応答して,選択したPWM信号をセグメント端子SEGT_0〜SEGT_31に出力する。

【0123】

なお,タイミング制御部23が,開始タイミング情報PSをセグメント用スイッチ部262に出力する理由は,図11で説明したとおりである。

【0124】

図12は,セグメント用スイッチ部を説明する図である。図12(A)は,セグメント用スイッチ部262の機能ブロック図,図12(B)は,セグメント用スイッチ部262のセレクタ(SEL)262_0の機能ブロック図である。

【0125】

セグメント用スイッチ部262は,セグメント端子SEGT_0〜SEGT_31に対応して設けられたセレクタ(SEL)262_0〜262_31を有する。図12(B)では,セレクタ262_0について示しているが,セレクタ262_1〜262_31についても同様の構成を有する。

【0126】

セレクタ262_SN(SNは0〜31)は,SIG_PN(PNは0〜3)を選択するように指示するセグメント用選択信号SEGS_SNに基づき,PWM信号SIG_0〜SIG_3の中の何れかのPWM信号を選択する。そして,開始タイミング情報PSに応答して,選択した信号をセグメント端子SEGT_SNに出力する。そのため,セレクタ262_SNは,開始タイミング情報PSが次に入力されるまでの間(時分割周期TDPの間),選択したPWM信号を出力する。

【0127】

ここで,例えば,液晶制御回路2が,図7に示す時間T1〜T120において,コモン電極駆動信号COMPD_0(図7(A’)参照),セグメント電極駆動信号SEGPD_1(図7(B’)参照)を生成する場合を例示して,液晶制御回路2の動作を説明する。なお,既に,パルス信号生成部21のPWM回路210〜PWM回路213は,タイミング制御部23からのPWM信号生成開始指示に応答して,PWM信号SIG_0〜SIG3の生成を開始している。

【0128】

時間T1において,タイミング制御部23は,映像フレームの表示周期FPを時分割した時分割周期TDPの開始タイミングを生成する。そして,映像フレームの表示周期FPにおいて先頭から0番目の時分割周期TDP_0の開始タイミングを生成したことを示すフェーズ情報PIを生成する。

【0129】

コモンドライバ241は,タイミング制御部23から0番目の時分割周期TDP_0の開始タイミングを生成したことを示すフェーズ情報PIが入力されると,PWM信号SIG_0を選択するようにコモン用スイッチ部242に指示するコモン用選択信号COMS_0を生成する。なお,コモン用選択信号COMS_0以外のコモン用選択信号については,コモンドライバ241は,PWM信号SIG_1またはPWM信号SIG_2の何れか1つを決定し,決定したPWM信号を選択するようにコモン用スイッチ部242に指示するコモン用選択信号を生成する。

【0130】

VRAM25は,タイミング制御部23からフェーズ情報PIが入力されると0番目の時分割周期TDP_0に対応するコモン端子COMT_0の列に格納された映像データを選択し,選択した映像データVRをセグメントドライバ261に出力する。この場合,図4に示すbit4("1")などを有する映像データVRが出力される。

【0131】

セグメントドライバ261は,VRAM25から入力された映像データVRによりオンが指定された液晶表示素子LCD2のコモン電極COM_0と液晶表示素子LCD2のセグメント電極SEG_1との間の電圧が閾値Vth以上になるPWM信号SIG_3を選択するようにセグメント用スイッチ部262に指示するセグメント用選択信号SEGS_1を生成する。

【0132】

コモン用スイッチ部242のセレクタ242_0は,PWM信号SIG_0を選択するようにコモン用スイッチ部242に指示するコモン用選択信号COMS_0に基づいてPWM信号SIG_0を選択する。そして,セレクタ242_0は,時分割周期TDP_0の開始タイミングを示す開始タイミング情報PSの入力に応答してPWM信号SIG_0をコモン端子COMT_0に出力する。

【0133】

セグメント用スイッチ部262のセレクタ262_1は,PWM信号SIG_3を選択するようにセグメント用スイッチ部262に指示するセグメント用選択信号SEGS_1に基づいて,PWM信号SIG_3を選択する。そして,セレクタ262_1は,時分割周期TDP_0の開始タイミングを示す開始タイミング情報PSの入力に応答してPWM信号SIG_3をセグメント端子SEGT_1に出力する。

【0134】

コモン用スイッチ部242のセレクタ242_0,セグメント用スイッチ部262のセレクタ262_1は,次に,タイミング制御部23から開始タイミング情報PSが入力されるまでの間,選択したPWM信号を出力する。

【0135】

時間T110において,タイミング制御部23は,映像フレームの表示周期FPを時分割した時分割周期TDPの開始タイミングを生成する。そして,映像フレームの表示周期FPにおいて先頭から1番目の時分割周期TDP_1の開始タイミングを生成したことを示すフェーズ情報PIを生成する。

【0136】

コモンドライバ241は,タイミング制御部23から1番目の時分割周期TDP_1の開始タイミングを生成したことを示すフェーズ情報PIが入力されると,PWM信号SIG_2を選択するようにコモン用スイッチ部242に指示するコモン用選択信号COMS_0を生成する。

【0137】

VRAM25は,タイミング制御部23からフェーズ情報PIが入力されると1番目の時分割周期TDP_1に対応するコモン端子COMT_1の列に格納された映像データを選択し,選択した映像データVRをセグメントドライバ261に出力する。この場合,図4に示すbit5("0")などを有する映像データVRが出力される。

【0138】

セグメントドライバ261は,VRAM25から入力された映像データVRによりオフが指定された液晶表示素子LCD2のコモン電極COM_0と液晶表示素子LCD2のセグメント電極SEG_1との間の電圧が閾値Vth未満になるPWM信号SIG_1を選択するようにセグメント用スイッチ部262に指示するセグメント用選択信号SEGS_1を生成する。

【0139】

コモン用スイッチ部242のセレクタ242_0は,PWM信号SIG_2を選択するようにコモン用スイッチ部242に指示するコモン用選択信号COMS_0に基づいてPWM信号SIG_2を選択する。そして,セレクタ242_0は,時分割周期の開始タイミングを示す開始タイミング情報PSの入力に応答してPWM信号SIG_2をコモン端子COMT_0に出力する。

【0140】

セグメント用スイッチ部262のセレクタ262_1は,PWM信号SIG_1を選択するようにセグメント用スイッチ部262に指示するセグメント用選択信号SEGS_1に基づいて,PWM信号SIG_1を選択する。そして,セレクタ262_1は,時分割周期の開始タイミングを示す開始タイミング情報PSの入力に応答してPWM信号SIG_1をセグメント端子SEGT_1に出力する。

【0141】

以上,本実施の形態の液晶制御回路2によれば,デジタル信号であるPWM信号により液晶表示素子のオン,オフ制御を実現できる。そのため,第1の出力部24のコモンドライバ241,コモン用スイッチ部242,第2の出力部26のセグメントドライバ261,セグメント用スイッチ部262をデジタル化することができる。そして,電圧生成部の替わりに,デジタル回路であるパルス信号生成部21を使用している。そのため,アナログ回路を削減することができる。その結果,開発工程が削減され,開発費用,開発時間が少なくなる。さらに,回路面積を減らすことができる。

【0142】

また,電圧生成部を利用する場合,液晶表示素子の輝度調整を行うため,最大電圧V3を可変抵抗により調整することがある。この調整は,外部の調整用回路により行うため,部品コストの増大となる。しかし,本実施の形態の液晶制御回路2によれば,最大電圧V3に対応する電圧をPWM信号SIG_3のデューティー比を変更することにより,すなわちPWM回路213のデューティー比レジスタの設定値を変更することにより,調整することができる。そのため,前記した外部の調整用回路が不要になり,部品コストの増大を抑制できる。

【0143】

図13は,本実施の形態に関連する液晶制御回路1,デジタル論理回路を搭載する半導体チップの機能ブロック図である。

【0144】

液晶制御回路1を搭載する半導体チップCは,半導体チップC上に各種処理を実行するデジタル論理回路3を搭載することがある。デジタル論理回路3は,液晶制御回路1のコモン端子COMT_0〜COMT_3,セグメント端子SEGT_0〜SEGT_31をデジタル論理回路3の入出力端子として兼用することがある。

【0145】

図13では,一例として,デジタル論理回路3が,液晶制御回路1のコモン端子COMT_0をデジタル論理回路3の入出力端子として兼用する場合を示している。

【0146】

アナログ信号であるコモン電極駆動信号COMVD_0が,デジタル論理回路3内に設けられた例えばインバータ回路,バッファ回路に入力されると,この回路に貫通電流が流れることがある。このように貫通電流が流れる理由は,この回路内に設けられたCMOSトランジスタの閾値電圧に対応する電圧レベルを有するコモン電極駆動信号COMVD_0がこの回路に入力されるからである。

【0147】

そこで,液晶制御回路1が,コモン電極駆動信号COMVD_0を出力する間,このコモン電極駆動信号COMVD_0がデジタル論理回路3に入力されないように遮断する遮断回路4を液晶制御回路1とデジタル論理回路3との間に設けている。

【0148】

なお,この遮断回路4は,ポート機能設定レジスタ5の設定値により動作する。例えば,液晶制御回路の動作実行を示す"1"がポート機能設定レジスタに設定されている場合,遮断回路4が動作して,アナログ信号であるコモン電極駆動信号COMVD_0がデジタル論理回路3に入力しないように遮断する。

【0149】

本実施の形態の液晶制御回路2は,デジタル信号であるコモン電極駆動信号,セグメント電極駆動信号を出力する。従って,本実施の形態の液晶制御回路2を搭載する半導体チップは,アナログ信号の入力に起因するデジタル論理回路3の貫通電流を阻止する遮断回路4を搭載する必要がなくなる。その結果,半導体チップの面積を削減することができ,さらに,半導体チップのコストをも削減することができる。

【0150】

図14は,本実施の形態の液晶制御回路2と,液晶表示素子を有する液晶表示部Dとを有する液晶表示装置を示した図である。図14に示すように,液晶表示装置DPは,コモン端子COMT_0〜COMT_3,セグメント端子SEG_0〜SEG_31とを介して接続した液晶制御回路2と液晶表示部Dとを有する。

【0151】

このように,液晶制御回路2と液晶表示部Dとを接続することにより,液晶制御回路2は,液晶表示部Dの表示制御を実行できる。

【0152】

以上の実施の形態をまとめると,次の付記のとおりである。

【0153】

(付記1)

映像フレームの表示周期を分周した第1の周期の開始タイミングを生成するタイミング制御部と,

前記第1の周期を分周した第2の周期において相互に異なるデューティー比を有し第1のレベル,第2のレベルに対応する複数のパルス信号を生成するパルス信号生成部と,

前記複数のパルス信号の何れかのパルス信号を選択し選択した第1のパルス信号を液晶表示素子のコモン電極に前記第1の周期の間出力する第1の出力部と,

前記複数のパルス信号の何れかのパルス信号を前記映像フレームの映像データに応じて選択し選択した第2のパルス信号を前記液晶表示素子のセグメント電極に前記第1の周期の間出力する第2の出力部とを有する液晶制御回路。

【0154】

(付記2)

付記1において,

前記パルス信号生成部は,前記第2の周期を設定する周期設定レジスタと,前記デューティー比を設定するデューティー比設定レジスタとを有し,前記周期設定レジスタの第1の設定値および前記デューティー比設定レジスタの第2の設定値を有するパルス信号を生成する複数のバルス幅変調回路を有し,

前記第1の設定値は外部から前記周期設定レジスタに設定可能であり,前記第2の設定値は外部から前記デューティー比設定レジスタに設定可能であって,

前記複数のバルス幅変調回路の前記周期設定レジスタ毎に前記第2の周期が設定され,前記複数のバルス幅変調回路の前記デューティー比設定レジスタ毎に相互に異なるデューティー比が設定される液晶制御回路。

【0155】

(付記3)

付記2において,

4つの前記バルス幅変調回路を有する液晶制御回路。

【0156】

(付記4)

付記2の液晶制御回路と,

前記液晶表示素子を有する液晶表示部と,

を有する液晶表示装置。

【符号の説明】

【0157】

D…液晶表示部,LCD0〜LCD7…液晶表示素子,COM_0〜COM_3…コモン電極,SEG_0〜SEG_31…セグメント電極,1,2…液晶制御回路,11…電圧生成回路,12…プリスケーラ,13…タイミング制御部,14…コモン用スイッチ部,15…セグメント用スイッチ部,16…コモンドライバ,17…VRAM,18…セグメントドライバ,21…パルス信号生成部,210〜213,21x…PWM回路,211x…周期設定レジスタ,212x…デューティー比設定レジスタ,213x,214x…バッファ,215x…プリスケーラ,216x…ダウンカウンタ,217x…比較器,218x…出力レベル部,22…プリスケーラ,23…タイミング制御部,24…第1の出力部,241…コモンドライバ,242…コモン用スイッチ部,242_0〜242_3…セレクタ(SEL),25…VRAM,26…第2の出力部,261…セグメントドライバ,262…セグメント用スイッチ部,262_0〜262_31…セレクタ(SEL),C…半導体チップ,3…デジタル論理回路,4…遮断回路,5…ポート機能レジスタ,DP…液晶表示装置。

【技術分野】

【0001】

本発明は,液晶制御回路,液晶制御回路を有する液晶表示装置に関する。

【背景技術】

【0002】

液晶制御回路は,液晶表示素子のコモン電極とこの液晶表示素子のセグメント電極との間に電圧を発生させることで,この液晶表示素子のオン(点灯とも言う),オフ(消灯とも言う)を制御する。すなわち,液晶制御回路は,液晶表示素子のコモン電極とこの液晶表示素子のセグメント電極との間に閾値以上の電圧を発生させることで,この液晶表示素子をオンする。

【0003】

液晶制御回路は,この電圧を発生させるため,相互に異なる3つ以上の電圧を生成する電圧生成回路を有する。電圧生成回路は,例えば電源とグランドとの間に直列接続された複数の分圧抵抗を有する分圧抵抗回路を有する。電圧生成回路は,この分圧抵抗回路により,前記した3つ以上の電圧を生成するアナログ回路である。

【0004】

液晶制御回路は,3つ以上の電圧の中から基準電圧となる電圧を選択し選択した電圧を有するコモン電極駆動信号を生成しコモン電極に出力する。同時に,液晶制御回路は,液晶表示素子のオンまたはオフを指示する映像データに応じて,3つ以上の電圧の中から液晶表示素子をオンまたはオフする電圧を選択し選択した電圧を有するセグメント電極駆動信号を生成しセグメント電極に出力する。このようにして,液晶制御回路は,液晶表示素子に前記した電圧を発生させる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平08-286171号公報

【特許文献2】特開平10-133630号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

液晶制御回路は,3つ以上の電圧レベルを有するアナログ信号を取り扱う必要があるため,主にアナログ回路により構成する必要がある。しかし,例えば開発工程を削減するため,アナログ回路を削減しデジタル回路に置き換えることが望ましい。

【0007】

そこで,本発明の目的は,アナログ回路を削減した液晶制御回路を提供することにある。

【課題を解決するための手段】

【0008】

液晶制御回路の第1の側面は,映像フレームの表示周期を分周した第1の周期の開始タイミングを生成するタイミング制御部と,

前記第1の周期を分周した第2の周期において相互に異なるデューティー比を有し第1のレベル,第2のレベルに対応する複数のパルス信号を生成するパルス信号生成部と,

前記複数のパルス信号の何れかのパルス信号を選択し選択した第1のパルス信号を液晶表示素子のコモン電極に前記第1の周期の間出力する第1の出力部と,

前記複数のパルス信号の何れかのパルス信号を前記映像フレームの映像データに応じて選択し選択した第2のパルス信号を前記液晶表示素子のセグメント電極に前記第1の周期の間出力する第2の出力部とを有する。

【発明の効果】

【0009】

第1の側面によれば,コモン電極駆動信号,セグメント電極駆動信号をデジタル信号である位相変調信号により生成するのでアナログ回路を削減することができる。

【図面の簡単な説明】

【0010】

【図1】液晶表示素子を有する液晶表示部を示す図である。

【図2】本実施の形態に関連する液晶制御回路の機能ブロック図である。

【図3】本実施の形態に関連する液晶制御回路の動作を説明する図である。

【図4】VRAMに格納されている映像データを模式的に示した図である。

【図5】本実施の形態の液晶制御回路の機能ブロック図である。

【図6】PWM信号の信号波形図の一例を示す。

【図7】本実施の形態の液晶制御回路の動作を説明する図である。

【図8】PWM回路の機能ブロック図である。

【図9】図8のPWM回路の動作を説明する図である。

【図10】コモン用スイッチ部を説明する図である。

【図11】出力タイミング制御を説明する図である。

【図12】セグメント用スイッチ部を説明する図である。

【図13】本実施の形態に関連する液晶制御回路,デジタル論理回路を搭載する半導体チップの機能ブロック図である。

【図14】液晶制御回路と液晶表示部とを有する液晶表示装置を示した図である。

【発明を実施するための形態】

【0011】

図1は,液晶表示素子を有する液晶表示部を示す図である。液晶表示部Dは,セグメント方式の液晶表示パネルであり,例えば液晶表示素子LCD0〜LCD7を有する。液晶表示素子は,液晶セルとも呼ばれる。

【0012】

一般に,液晶表示パネルは,コモン電極が形成された第1の透明基板とセグメント電極が形成された第2の透明基板とをギャップコントロール材を介して重ね合わせ,その間に液晶が封入されたものである。なお,透明基板とは,例えばガラス基板である。

【0013】

図1に示す例では,第1の透明基板において,液晶表示素子LCD0,LCD2,LCD5の透明基板部にコモン電極COM_0が形成され,液晶表示素子LCD1,LCD3,LCD6の透明基板部にコモン電極COM_1が形成され,液晶表示素子LCD4,LCD7の透明基板部にコモン電極COM_2が形成されている。

【0014】

また,第2の透明基板において,液晶表示素子LCD0,LCD1の透明基板部にセグメント電極SEG_nが形成され,液晶表示素子LCD2,LCD3,LCD4の透明基板部にセグメント電極SEG_n+1が形成され,液晶表示素子LCD5,LCD6,LCD7の透明基板部にセグメント電極SEG_n+2が形成されている。以下,nは"0"として説明する。

【0015】

図2は,本実施の形態に関連する液晶制御回路の機能ブロック図である。液晶制御回路1は,コモン端子COMT_0〜COMT_3のそれぞれに接続されたコモン電極にコモン電極駆動信号COMVD_0〜COMVD_3を出力する。また,液晶制御回路1は,セグメント端子SEGT_0〜SEGT_31のそれぞれに接続されたセグメント電極にセグメント電極駆動信号SEGVD_0〜SEGVD_31を出力する。

【0016】

液晶制御回路1は,コモン電極駆動信号COMVD_0〜COMVD_3,セグメント電極駆動信号SEGVD_0〜SEGVD_31により,コモン端子COMT_0〜COMT_3,セグメント端子SEGT_0〜SEGT_31に接続された液晶表示部の液晶表示素子のオン,オフを制御する。

【0017】

図1の液晶表示部Dにおいて,例えば,図2のコモン端子COMT_0〜COMT_2がそれぞれコモン電極COM_0〜COM_2に接続され,セグメント端子SEGT_0〜SEGT_2がそれぞれセグメント電極SEG_0〜SEG_2に接続される。

【0018】

図3は,液晶制御回路1の動作を説明する図である。

【0019】

時間T0〜T1は,1映像フレームの表示周期FPに相当する。この表示周期は,映像フレーム周期とも言われる。時間T1〜T2,時間T2〜T3,時間T3〜T4,時間T4〜T5も,1映像フレームの表示周期に相当する。

【0020】

表示周期FPは,所定数で分周される。表示周期が所定数で分周されることは,表示周期が所定数で時分割されることと同意である。この所定数は,図1で説明したコモン電極の数に対応する。図1の例では,コモン電極の数は3つ(コモン電極COM_0〜COM_2)なので,所定数"3"で時分割される。例えば,時間T1〜T2の表示周期FPにおいて,表示周期FPは,時分割周期TDP_0〜TPD_2の3つに時分割されている。

【0021】

図3(A)〜図3(C)は,コモン電極駆動信号COMVD_0〜COMVD_2の信号波形の一例を示す。図3(D)は,セグメント電極駆動信号SEGVD_1の信号波形の一例を示す。図3(A)〜図3(D)において,縦軸は電圧を示し,横軸は時間を示す。縦軸の電圧V0〜V3は,図2の電圧生成回路11が生成する電圧である。

【0022】

図3(E)〜図3(G)は,図3(A)〜図3(D)に示した駆動信号により電圧差が生じる液晶表示素子LCD2〜LCD4のオン状態,オフ状態を示す図である。

【0023】

液晶表示素子のコモン電極に出力されたコモン電極駆動信号の電圧とこの液晶表示素子のセグメント電極に出力されたセグメント電極駆動信号の電圧との電圧差が所定の閾値Vth以上の時分割周期において,この液晶表示素子はオンする。一方,この電圧差が所定の閾値Vth未満の時分割周期においては,この液晶表示素子はオフする。所定の閾値Vthは,例えば,電圧V3-電圧V0である。

【0024】

例えば,時間T1〜T2の表示周期FPにおける先頭の時分割周期TDP_0において,コモン電極駆動信号COMVD_0の電圧V0とセグメント電極駆動信号SEGVD_1の電圧V3との電圧差は,所定の閾値Vth以上である(符号P1,P2参照)。従って,時分割周期TDP_0において,電圧V0を有するコモン電極駆動信号COMVD_0と電圧V3を有するセグメント電極駆動信号SEGVD_1とが入力される液晶表示素子LCD2は,オンする(符号P3参照)。

【0025】

一方,時分割周期TDP_1,TDP_2において,コモン電極駆動信号COMVD_0の電圧V2とセグメント電極駆動信号SEGVD_1の電圧V1または電圧V3の電圧差は,所定の閾値Vth未満である(符号P1,P2参照)。従って,液晶表示素子LCD2は,オフする(符号P3参照)。

【0026】

なお,図3(F)に示すように,液晶表示素子LCD3についても,液晶表示素子LCD3のコモン電極COM_1に出力されるコモン電極駆動信号COMVD_1の電圧と液晶表示素子LCD3のセグメント電極SEG_1に出力されるセグメント電極駆動信号SEGVD_1の電圧との電圧差に基づき,液晶表示素子LCD3のオン,オフが制御される。同じく,図3(G)に示すように,液晶表示素子LCD4についても,液晶表示素子LCD4のコモン電極COM_2に出力されるコモン電極駆動信号COMVD_2の電圧と液晶表示素子LCD4のセグメント電極SEG_1に出力されるセグメント電極駆動信号SEGVD_1の電圧との電圧差に基づき,液晶表示素子LCD4のオン,オフが制御される。

【0027】

図3に例示したコモン電極駆動信号,セグメント電極駆動信号を生成する液晶制御回路1について説明する。

【0028】

図2の電圧生成回路11は,電圧V3〜V0を生成し,電圧V3〜V0をコモン用スイッチ部14,セグメント用スイッチ部15に出力する。電圧生成回路11は,高電源VCCとグランドGNDとの間に,直列接続された分圧抵抗Ra,Rb,Rcを有し,この分圧抵抗Ra,Rb,Rcにより電圧V3〜V0を生成する。

【0029】

プリスケーラ12は,基準クロックRCLKを所定の分周比で分周し,タイミング制御部13に出力する。

【0030】

タイミング制御部13は,プリスケーラ12から入力された基準クロックRCLKの分周クロックに基づき,映像フレームの表示処理に必要な各種制御を実行する。例えば,タイミング制御部13は,映像フレームの表示周期FPの開始タイミングを生成する。また,タイミング制御部13は,映像フレームの表示周期FPを時分割した時分割周期TDPの開始タイミングを生成する。そして,タイミング制御部13は,時分割周期TDPの開始タイミングを開始タイミング情報PSとしてコモン用スイッチ部14,セグメント用スイッチ部15に出力する。

【0031】

さらに,タイミング制御部13は,各表示周期FPにおいて先頭からTN番目の時分割周期TDP_TNの開始タイミングを生成すると,TN番目の時分割周期TDP_TNの開始タイミングを生成したことを示すフェーズ情報PIを生成する。図3の例では,TNは0〜2である。ここで,0番目の時分割周期TDP_0の開始タイミングは表示周期FPの開始タイミングであり,表示周期FPにおいて最初に生成された時分割周期の開始タイミングである。そして,タイミング制御部13は,生成したフェーズ情報PIを,コモンドライバ16,VRAM17,セグメントドライバ18に出力する。

【0032】

コモン用スイッチ部14は,コモンドライバ16から入力されたコモン用選択信号COMS_0〜COMS_3に基づき,電圧生成回路11が生成する電圧V0〜V3の中の何れかの電圧を選択する。すなわち,コモン用スイッチ部14は,コモン端子COMT_CN(CNは0〜3)に対応して設けられたスイッチを有する。このスイッチは,コモンドライバ16から入力されたコモン用選択信号COMS_CNに基づき,電圧V0〜V3の中の何れか1つの電圧を選択する。

【0033】

そして,コモン用スイッチ部14は,選択した電圧をコモン端子COMT_CNにタイミング制御部13から入力された開始タイミング情報PSに応答して出力する。

【0034】

セグメント用スイッチ部15は,セグメントドライバ18から入力された選択信号SEGS_0〜SEGS_31に基づき,電圧生成回路11が生成する電圧V0〜V3の中の何れかの電圧を選択する。すなわち,セグメント用スイッチ部15は,セグメント端子SEGT_SN(SNは0〜31)に対応して設けられたスイッチを有する。このスイッチは,セグメントドライバ18から入力された選択信号SEGS_SNに基づき,電圧V0〜V3の中の何れか1つの電圧を選択する。

【0035】

そして,セグメント用スイッチ部15は,選択した電圧をセグメント端子SEGT_SNにタイミング制御部13から入力された開始タイミング情報PSに応答して出力する。

【0036】

コモンドライバ16は,タイミング制御部13から入力されたフェーズ情報PIに基づき,コモン用選択信号COMS_0〜COMS_3を生成し,コモンドライバ16に出力する。

【0037】

VRAM17は,1映像フレームの映像データが格納されるメモリである。映像データは,1フレーム毎に例えば外部CPUにより新たに格納(更新)される。VRAM17は,タイミング制御部13から入力されたフェーズ情報PIに基づき,VRAM17に格納されている映像データを選択し,選択した映像データVRをセグメントドライバ18に出力する。

【0038】

図4は,VRAM17に格納されている映像データを模式的に示した図である。図4に示すように,コモン端子COMT_0〜COMT_3,セグメント端子SEGT_0,SEGT_1…に対応する液晶表示素子のオン,オフを指示する映像データbit0,bit1…が格納されている。例えば,コモン端子COMT_0,セグメント端子SEGT_1に対応する液晶表示素子LCD2のオン,オフを指示する映像データbit4が格納されている。なお,映像データのビットが"1"の場合,液晶表示素子をオン,映像データが"0"の場合,液晶表示素子をオフにする。

【0039】

セグメントドライバ18は,タイミング制御部13から入力されたフェーズ情報PI,VRAM17から入力された映像データVRに応じて,選択信号SEGS_0〜SEGS_31を生成し,セグメント用スイッチ15に出力する。

【0040】

ここで,液晶制御回路1の動作を詳細に説明する。タイミング制御部13は,例えば,図3に示した時間T1〜T2の表示周期FPの開始タイミングを生成する。また,タイミング制御部13は,表示周期FPにおいて先頭からTN番目(TNは0〜2)の時分割周期TDP_TNの開始タイミングを生成すると,TN番目の時分割周期TDP_TNの開始タイミングを生成したことを示すフェーズ情報PIを生成する。

【0041】

コモンドライバ16は,表示周期FPにおいて先頭からTN番目の開始タイミングを生成したことを示すフェーズ情報PIが入力されると,連続する表示周期FPにおいて一定の波形パターンを有するコモン電極駆動信号COMVD_TNが生成されるように最大電圧V3または最小電圧V0の何れかを決定する。そして,コモンドライバ16は,決定した電圧を選択するようにコモン用スイッチ部14に指示するコモン用選択信号COMS_TNを生成する。

【0042】

一方,コモン用選択信号COMS_0〜COMS_3のうちコモン用選択信号COMS_TN以外のコモン用選択信号については,コモンドライバ16は,連続する表示周期FPにおいて一定の波形パターンを有するコモン電極駆動信号が生成されるように,中間電圧V1またはV2の何れか1つを決定する。そして,コモンドライバ16は,決定した電圧を選択するようにコモン用スイッチ部14に指示するコモン用選択信号を生成する。なお,中間電圧は,中間電位とも言う。

【0043】

VRAM17は,タイミング制御部13からフェーズ情報PIが入力されると表示周期FPにおいて先頭からTN番目の時分割周期TDP_TNに対応するコモン端子COMT_TNの列に格納された映像データを選択し,選択した映像データVRをセグメントドライバ18に出力する。

【0044】

セグメントドライバ18は,VRAM17から入力された映像データによりオンが指定される液晶表示素子のコモン電極とこの液晶表示素子のセグメント電極との間の電圧が所定の閾値Vth以上になる電圧を電圧V3〜V0の中から決定する。または,VRAM17から入力された映像データによりオフが指定される液晶表示素子のコモン電極とこの液晶表示素子のセグメント電極との間の電圧が所定の閾値Vth未満になる電圧を電圧V3〜V0の中から決定する。そして,この決定した電圧を選択するようにセグメント用スイッチ部15に指示するセグメント用選択信号SEGS_0〜SEGS_31を生成する。

【0045】

さらに,タイミング制御部13は,生成した時分割周期TDP_TNの開始タイミングを開始タイミング情報PSとして,コモン用スイッチ部14,セグメント用スイッチ部15に出力する。なお,この場合, 時分割周期TDP_0の開始タイミング情報PSは,時間T1に対応する。

【0046】

コモン用スイッチ部14は,コモン用選択信号COMS_0〜COMS_3に基づき,電圧V3〜V0を選択し,開始タイミング情報PSに応答して,コモン端子COMT_0〜COMT_3に出力する。

【0047】

同じく,セグメント用スイッチ部15は,セグメント用選択信号SEGS_0〜SEGS_31に基づき,電圧V3〜V0を選択し,開始タイミング情報PSに応答して,セグメント端子SEGT_0〜SEGT_31に出力する。その結果,コモン電極駆動信号COMVD_0〜COMVD_3,セグメント電極駆動信号SEGVD_0〜SEGVD_31が生成される。

【0048】

液晶制御回路1は,このようにして,コモン電極駆動信号,セグメント電極駆動信号を生成して,液晶表示素子のコモン電極,セグメント電極に出力することで,液晶表示素子のオン,オフを制御する。

【0049】

ところで,電圧生成回路11は,複数の抵抗を有するアナログ回路である。また,コモン用スイッチ部14,セグメント用スイッチ部15,コモンドライバ16,セグメントドライバ18は,3つ以上の電圧を有するアナログ信号を取り扱う必要があるためアナログ回路で構成する必要がある。例えば,コモン用スイッチ部14,セグメント用スイッチ部15は,スイッチ素子として,CMOSトランスファゲートを利用する。しかし,例えば開発工程を削減するため,アナログ回路を削減しデジタル回路に置き換えることが望ましい。

【0050】

(本実施の形態)

本実施の形態において,液晶表示素子の液晶は,容量(キャパシタ)として機能する,すなわち容量成分(浮遊容量)であることに着目する。

【0051】

ここで,液晶表示素子のコモン電極とセグメント電極とにパルス幅変調信号(以下,PWM信号と略記する)を出力するとする。液晶表示素子の液晶は容量成分であるので,このPWM信号は,液晶表示素子の液晶内部において,PWM信号のデューティー比(Hレベル幅)に対応する電圧に変換される。また,PWM信号のデューティー比を変化させることにより,コモン電極とセグメント電極との間に様々な電圧を発生させることができる。そのため,この電圧差により液晶表示素子のオン,オフを制御することができる。

【0052】

PWM信号は,2つの電圧レベル(Hレベル,Lレベル)を有するデジタル信号であるので,PWM信号を扱う回路をデジタル化することができる。その結果,開発工程が削減され,開発費用,開発時間が少なくなる。

【0053】

図5は,本実施の形態の液晶制御回路2の機能ブロック図である。パルス信号生成部21は,4つのPWM回路(パルス幅変調回路)210〜PWM回路213を有する。

【0054】

図6は,PWM信号の信号波形図の一例を示す。図6(A)〜図6(D)は,PWM信号SIG_0〜SIG_3の信号波形図の一例である。符号PWMPはPWM信号の周期を示し,縦軸はPWM信号の電圧(HレベルまたはLレベル),横軸は時間を示す。PWM信号SIG_0〜SIG_3は,それぞれ電圧V0〜V3に対応する。

【0055】

ここで,時間T10〜T14が時分割周期TDPであり,この時分割周期TDPを例えば3つに分周してそれぞれをPWM信号のPWM周期PWMPとしている。時分割周期が第1の周期であり,PWM周期が第2の周期である。このように,時分割周期TDPを分周して,PWM周期とする理由については,後述する。

【0056】

PWM回路210は,図6(A)に示すように,PWM周期PWMPにおいて,デューティー比が0%のPWM信号SIG_0を生成する。PWM回路211は,図6(B)に示すように,PWM周期PWMPにおいて,デューティー比が33%のPWM信号SIG_1を生成する。PWM回路212は,図6(C)に示すように,PWM周期PWMPにおいて,デューティー比が66%のPWM信号SIG_2を生成する。PWM回路213は,図6(D)に示すように,PWM周期PWMPにおいて,デューティー比が100%のPWM信号SIG_3を生成する。

【0057】

液晶制御回路2は,PWM信号SIG_0〜SIG_3の何れか1を選択しコモン電極駆動信号として液晶表示素子のコモン電極に出力する。同時に,液晶制御回路2は,PWM信号SIG_0〜SIG_3の何れか1を選択しセグメント電極駆動信号としてこの液晶表示素子のセグメント電極に出力する。そして,液晶制御回路2は,この駆動信号の出力によりコモン電極とセグメント電極との間に電圧差を発生させ,この電圧差により液晶表示素子のオン,オフを制御する。

【0058】

図7は,本実施の形態の液晶制御回路2の動作を説明する図である。

【0059】

図7(A)は,図3の符号P1に示す部分のコモン電極駆動信号COMVD_0の信号波形を示す。図7(A')は,コモン電極駆動信号COMVD_0の電圧に相当する電圧をPWM信号により生成するコモン電極駆動信号COMPD_0を示す。

【0060】

時間T1〜T110の時分割周期TPD_0において,液晶制御回路2は,コモン電極駆動信号COMVD_0の電圧V0に相当する電圧を,図7(A')に示すように,デューティー比0%のPWM信号SIG_0により生成する。

【0061】

また,時間T110〜T120の時分割周期TPD_1,時間T120〜T2の時分割周期TDP_2において,液晶制御回路2は,コモン電極駆動信号COMVD_0の電圧V2に相当する電圧を,図7(A')に示すように,デューティー比66%のPWM信号SIG_2により生成する。

【0062】

図7(B)は,図3の符号P2に示す部分のセグメント電極駆動信号SEGVD_1の信号波形を示す。図7(B')は,セグメント電極駆動信号SEGVD_1の電圧に相当する電圧をPWM信号により生成するセグメント電極駆動信号SEGPD_1を示す。

【0063】

時分割周期TPD_0において,液晶制御回路2は,セグメント電極駆動信号SEGVD_1の電圧V3に相当する電圧を,図7(B')に示すように,デューティー比100%のPWM信号SIG_3により生成する。

【0064】

時分割周期TPD_1において,液晶制御回路2は,セグメント電極駆動信号SEGVD_1の電圧V1に相当する電圧を,図7(B')に示すように,デューティー比33%のPWM信号SIG_1により生成する。

【0065】

また,時分割周期TPD_2において,液晶制御回路2は,セグメント電極駆動信号SEGVD_1の電圧V3に相当する電圧を,図7(B')に示すように,デューティー比100%のPWM信号SIG_3により生成する。

【0066】

ここで,時分割周期TDPを複数のPWM周期に分周する理由を説明する。前述したように,液晶制御回路2が出力するコモン電極駆動信号,セグメント電極駆動信号により,液晶表示素子のコモン電極とセグメント電極との間の電圧差が変化する。そして,変化後の電圧差が閾値Vth以上になると,この液晶表示素子がオンし,この変化後の電圧差が閾値Vth未満になるとオフする。

【0067】

ところで,液晶表示素子は,この電圧変化に応答して,オンオフ,オフオンするまでに所定の時間(タイムラグ)を要する。この時間が短いほど,液晶表示素子の電圧変化に対する応答性(追随性)は高い。そして,この応答性は,液晶表示素子に封入された液晶の種類毎に異なる。

【0068】

液晶制御回路2が,PWM周期が長いPWM信号により,応答性が高い液晶表示素子のオン,オフを制御すると,液晶画面がちらつくことがある。これは,PWM信号の電圧レベル変化(PWM信号の立ち上がり,立ち下がり)に対して液晶表示素子が素早く応答して,高速にオン,オフするからである。

【0069】

このちらつきを防止するため,液晶制御回路2は,応答性が高い液晶表示素子のオンオフを制御する場合,PWM周期が短いPWM信号により,この液晶表示素子のオン,オフ制御を行う必要がある。すなわち,液晶表示素子の応答性に応じて,最適なPWM周期を調整する必要がある。

【0070】

そこで,液晶制御回路2のパルス信号生成部21は,PWM信号のPWM周期を調整可能なPWM回路210〜PWM回路213を有する。

【0071】

図8は,PWM回路21xの機能ブロック図である。PWM回路21xは,PWM回路210〜PWM回路213に相当するものであり,PWM回路210〜PWM回路213は,PWM回路21xと同様の機能ブロックを有する。

【0072】

PWM回路21xは,PWM周期を設定する周期設定レジスタ211xと,PWM信号のデューティー比を設定するデューティー比設定レジスタ212xとを有し,周期設定レジスタ211xの設定値PV(第1の設定値),および,デューティー比設定レジスタ212xの設定値DV(第2の設定値)を有するパルス信号であるPWM信号SIG_xを生成する。このようなPWM回路は,PPG(Programmable Pulse Generator)とも呼ばれる。この設定値PV,設定値DVは,後述するように,分周クロックDRCLKのクロック数に対応する。

【0073】

周期設定レジスタ211xの設定値PVは,外部,例えばタイミング制御部23から設定可能である。周期設定レジスタ211xは,設定値PVがタイミング制御部23から設定されると,設定された設定値PVをバッファ213xに出力する。

【0074】

デューティー比設定レジスタ212xの設定値DVは,外部,例えばタイミング制御部23から設定可能である。デューティー比設定レジスタ212xは,設定値DVがタイミング制御部23から設定されると設定値DVをバッファ214xに出力する。また,設定値DVがタイミング制御部23から新たに設定(更新)されると,ボロー信号Brの入力に応答して,新たに設定された設定値DVをバッファ214xに出力する。

【0075】

バッファ213xは,周期設定レジスタ211xの設定値PVを一時的に格納(バッファリング)するバッファである。バッファ213xは,PWM信号生成開始指示がPWM信号生成部21から入力された場合や,ボロー信号Brがダウンカウンタ216xから入力された場合,設定値PVをダウンカウンタ216xに出力する。

【0076】

バッファ214xは,デューティー比設定レジスタ212xの設定値DVをバッファリングするバッファである。バッファ214xは,設定値DVを比較器217xの非反転入力端子(+端子)に出力する。

【0077】

プリスケーラ215xは,基準クロックRCLKを所定の分周比で分周し,分周した分周クロックDRCLKをダウンカウンタ216xに出力する。

【0078】

ダウンカウンタ216xは,入力された分周クロックDRCLKに基づき,バッファ213xから入力されたPWM周期の設定値PVをダウンカウントして,カウント結果CNTを比較器217xの反転入力端子(-端子)に出力する。また,カウント結果CNTが0になるとボロー信号(桁下がり信号)Brをデューティー比設定レジスタ212x,バッファ213x,出力レベル部218xに出力する。

【0079】

比較器217xは,デューティー比の設定値DVとカウント結果CNTとを比較し,比較信号CMPを出力レベル部218xに出力する。すなわち,カウント結果CNTがデューティー比の設定値DVよりも大きい間は,ローレベルの比較信号CMPを出力レベル部218xに出力する。一方,カウント結果CNTがデューティー比の設定値DVよりも小さくなると,以後ハイレベルの比較信号CMPを出力レベル部218xに出力する。

【0080】

出力レベル部218xは,比較器217xから入力された比較信号CMPをラッチしPWM信号SIG_xとして出力する。このとき,ハイレベルの比較信号CMPが入力されると,比較信号CMPのレベルをより高レベルにシフトしてもよい。これは,液晶表示素子のコモン電極とセグメント電極との間に所定の閾値Vth 以上の電圧を発生させ,液晶表示素子をオンさせるためである。また,ボロー信号Brが入力されると,ハイレベルの比較信号CMPを立ち下げる。

【0081】

図9は,図8のPWM回路21xの動作を説明する図である。図9(A)は,カウント結果CNTの変化を示す図で,縦軸がカウント結果CNTの値を示し,横軸が時間を示す。図9(B)は,PWM信号SIG_xの信号波形図で,縦軸がレベルを示し,横軸が時間を示す。図9(B)の符号PWMPは,PWM信号SIG_xのPWM周期を示す。また,符号DTYは,PWM信号SIG_xのハイレベルの幅(デューティー比)を示す。

【0082】

ここで,既に,周期設定レジスタ211xにはPWM周期の設定値PVが設定され,デューティー比設定レジスタ212xにはデューティー比の設定値DVが設定されている。このとき,分周クロックDRCLKの1周期をTa[ms]とすると,Ta×(PV+1)[ms]がPWM周期PWMPである。すなわち,PWM周期の設定値PV,プリスケーラ215xの分周比を変更すれば,PWM周期PWMPを変更することができる。また,Ta×(DV+1)[ms]がデューティー比DTYである。すなわち,デューティー比の設定値DV,プリスケーラ215xの分周比を変更すれば,デューティー比DTYを変更することができる。

【0083】

さて,図9の時間T10において,PWM信号生成部21からのPWM信号生成開始指示に応答して,バッファ213xがダウンカウンタ216xに設定値PVを出力する。また,バッファ214xは比較器217xの非反転入力端子に設定値DVを出力する。ダウンカウンタ216xは,入力される分周クロックDRCLKに基づき入力された設定値PVをダウンカウントし,カウント結果CNTが0になるまでダウンカウントを継続する。このダウンカウンタ216xによるダウンカウントの開始タイミングがPWM信号SIG_xのPWM周期の開始タイミングである。この開始タイミングは,図9の例では,時間T10,時間T11である。

【0084】

時間T10〜Tdにおいて,カウント結果CNTはデューティー比の設定値DVよりも大きいので,比較器217xは,ローレベルの比較信号CMPを出力する。その結果,出力レベル部218xは,ローレベルのPWM信号SIG_xを出力する。

【0085】

時間Tdにおいて,カウント結果CNTがデューティー比の設定値DVよりも小さくなると,比較器217xは,ハイレベルの比較信号CMPを出力する。その結果,出力レベル部218xは,ハイレベルのPWM信号SIG_xを出力する。

【0086】

時間Tdから,カウント結果CNTが0になる時間T11に至るまで間,カウント結果CNTは,デューティー比の設定値DVよりも小さいので,比較器217xは,ハイレベルの比較信号CMPの出力を継続する。そのため,出力レベル部218xは,ハイレベルのPWM信号SIG_xの出力を継続する。

【0087】

カウント結果CNTが0になると,ダウンカウンタ216xはボロー信号Brをデューティー比設定レジスタ212x,バッファ213x,出力レベル部218xに出力する。すると,出力レベル部218xは,ハイレベルのPWM信号SIG_xをローレベルに立ち下げる。また,バッファ213xは,設定値PVをダウンカウンタ216xに出力する。そして,ダウンカウンタ216xは,ダウンカウントを開始する。

【0088】

なお,デューティー比設定レジスタ212xに新たに設定値DVが設定された場合には,ボロー信号Brの入力に応答して,デューティー比設定レジスタ212xは,バッファ214xに設定値DVを出力する。

【0089】

以後,PWM回路21xは,上記で説明した処理を繰り返す。

【0090】

図5の説明に戻る。プリスケーラ22は,基準クロックRCLKを所定の分周比で分周し,タイミング制御部23に出力する。

【0091】

タイミング制御部23は,プリスケーラ22から入力された基準クロックRCLKの分周クロックに基づき,映像フレームの表示処理に必要な各種制御を実行する。例えば,タイミング制御部23は,映像フレームの表示周期FPの開始タイミングを生成する。

【0092】

また,タイミング制御部23は,映像フレームの表示周期FPを時分割(分周)した時分割周期TDP(第1の周期)の開始タイミングを生成する。そして,タイミング制御部23は,時分割周期TDPの開始タイミングを開始タイミング情報PSとしてコモン用スイッチ部242,セグメント用スイッチ部262に出力する。タイミング制御部23が,開始タイミング情報PSをコモン用スイッチ部242,セグメント用スイッチ部262に出力する理由については,図11で説明する。

【0093】

また,タイミング制御部23は,各表示周期FPにおいて先頭からTN番目の時分割周期TDP_TNの開始タイミングを生成すると,TN番目の時分割周期TDP_TNの開始タイミングを生成したことを示すフェーズ情報PIを生成する。図3の例では,TNは0〜2である。ここで,0番目の時分割周期TDP_0の開始タイミングは表示周期FPの開始タイミングであり,表示周期FPにおいて最初に生成された時分割周期の開始タイミングである。そして,タイミング制御部23は,フェーズ情報PIをコモンドライバ241,VRAM25,セグメントドライバ261に出力する。

【0094】

また,液晶制御回路2の起動時などにおいて,タイミング制御部23は,PWM周期PWMPに対応する図8に示した分周クロックDRCLKのクロック数をPWM回路210〜213の周期設定レジスタに設定する。例えば,時分割周期TDPを3つのPWM周期PWMPに分周し,時分割周期TDPに対応する分周クロックDRCLKのクロック数がTDPNUMとする。この場合,タイミング制御部23は,"クロック数TDPNUM×(1/3)"を設定値PVとしてPWM回路210〜213の周期設定レジスタに設定する。

【0095】

そして,タイミング制御部23は,"0"をPWM回路210のデューティー比レジスタに設定し,"設定値PV×(1/3)"をPWM回路211のデューティー比レジスタに設定し,"設定値PV×(2/3)"をPWM回路212のデューティー比レジスタに設定し,"設定値PV"をPWM回路213のデューティー比レジスタに設定する。

【0096】

その結果,複数のPWM回路210〜PWM回路213の周期設定レジスタ毎にPWM周期PWMP(第2の周期)が設定され,複数のPWM回路210〜PWM回路213のデューティー比設定レジスタ毎に相互に異なるデューティー比が設定される。

【0097】

また,タイミング制御部23は,表示周期FPの最初の開始タイミングの生成に合わせて,パルス信号生成部21にPWM信号生成開始を指示する。なお,タイミング制御部23は,表示周期FPの開始タイミングの生成時や,時分割周期TDPの開始タイミングの生成時に適宜,この指示を実行してもよい。例えば,タイミング制御部23は,一定時間の経過毎に,時分割周期TDPの開始タイミングの生成時にこの指示を行ってもよい。

【0098】

パルス信号生成部21は,この指示に応答して,PWM回路210〜PWM回路213の周期設定レジスタ(211x)のバッファ(213x)に設定された設定値PVをダウンカウンタ(216x)に出力するようにPWM生成回路210〜PWM生成回路213に指示し,PWM信号の生成を開始させる。

【0099】

前記の設定により,パルス信号生成部21は,時分割周期TDPを分周したPWM周期PWMPにおいて相互に異なるデューティー比を有しローレベル(第1のレベル),ハイレベル(第2のレベル)に対応する複数のPWM信号(パルス信号)SIG_0〜SIG_3を生成する。そして,前記の指示により,時分割周期TDPの開始タイミングとPWM信号のPWM周期の開始タイミングとが図6,図7に示したように同期する。

【0100】

第1の出力部24は,複数のPWM信号SIG_0〜SIG_3の何れかのPWM信号を選択し選択した第1のPWM信号を液晶表示素子のコモン電極に接続するコモン端子に時分割周期TDPの間出力する。

【0101】

VRAM25は,図2のVRAM17と同様の機能を有し,映像フレームの映像データを格納する。

【0102】

第2の出力部26は,複数のPWM信号SIG_0〜SIG_3の何れかのPWM信号をVRAM25に格納された映像フレームの映像データに応じて選択し選択した第2のPWM信号を液晶表示素子のセグメント電極に接続するセグメント端子にPWM周期の間出力する。

【0103】

タイミング制御部23は,時分割周期TDPの開始タイミングと,第1,第2のPWM信号のPWM周期(第2の周期)の開始タイミングとを同期させるため,前記のように,パルス信号生成部21にPWM信号生成開始を指示する。

【0104】

前述したように,タイミング制御部23は,映像フレームの表示周期FPを時分割した時分割周期TDPの開始タイミングを生成する。また,タイミング制御部23は,表示周期FPにおいて先頭からTN番目の時分割周期TDP_TNの開始タイミングを生成したことを示すフェーズ情報PIを生成する。図3の例では,TNは0〜2である。

【0105】

第1の出力部24のコモンドライバ241は,連続する表示周期FPにおいて一定の波形パターンを有するコモン電極駆動信号が生成されるために必要となるPWM信号の決定パターンが記録されたパターン情報を有する。そして,このパターン情報,フェーズ情報PIに基づき,PWM信号の決定を行う。

【0106】

すなわち,コモンドライバ241は,タイミング制御部23からフェーズ情報PIが入力されると,連続する表示周期FPにおいて一定の波形パターンを有するコモン電極駆動信号COMPD_TNが生成されるようにPWM信号SIG_3またはPWM信号SIG_0の何れか1つを決定する。そして,コモンドライバ241は,決定したPWM信号を選択するようにコモン用スイッチ部242に指示するコモン用選択信号COMS_TNを生成する。

【0107】

コモン用選択信号COMS_0〜COMS_3のうちコモン用選択信号COMS_TN以外のコモン用選択信号について説明する。コモンドライバ241は,コモン電極駆動信号COMPD_TN以外のコモン電極駆動信号が一定の波形パターンを有するように,PWM信号SIG_1またはPWM信号SIG_2の何れか1つを決定する。そして,コモンドライバ241は,決定したPWM信号を選択するようにコモン用スイッチ部242に指示するコモン用選択信号を生成する。

【0108】

コモン用スイッチ部242は,コモンドライバ241から入力されたコモン用選択信号COMS_0〜COMS_3に基づき,PWM信号SIG_0〜SIG_3の中の何れかのPWM信号を選択する。そして,コモン用スイッチ部242は,選択したPWM信号をコモン端子COMT_0〜COMT_3に,タイミング制御部23から入力された時分割周期TDPの開始タイミングを示す開始タイミング情報PSに応答して出力する。

【0109】

図10は,コモン用スイッチ部を説明する図である。図10(A)は,コモン用スイッチ部242の機能ブロック図,図10(B)は,コモン用スイッチ部242のセレクタ(SEL)242_0の機能ブロック図である。

【0110】

コモン用スイッチ部242は,コモン端子COMT_0〜COMT_3に対応して設けられたセレクタ(SEL)242_0〜セレクタ242_3を有する。図10(B)では,セレクタ242_0について示しているが,セレクタ242_1〜242_3についても同様の構成を有する。

【0111】

セレクタ242_CN(CNは0〜3)は,SIG_PN(PNは0〜3)を選択するように指示するコモン用選択信号COMS_CNに基づき,PWM信号SIG_0〜SIG_3の中の何れかのPWM信号を選択する。そして,開始タイミング情報PSに応答して,選択した信号をコモン端子COMT_CNに出力する。そのため,セレクタ242_CNは,開始タイミング情報PSが次に入力されるまでの間(時分割周期TDPの間),選択したPWM信号を出力する。

【0112】

図11は,PWM信号の出力タイミング制御を説明する図である。タイミング制御部23が,開始タイミング情報PSをコモン用スイッチ部242,セグメント用スイッチ部262に出力する理由について説明する。

【0113】

図11(A)は,図7(A)に対応する。図11(A’),図11(A”)は,コモン電極駆動信号COMPD_0の出力タイミングを示す。ここで,コモン用スイッチ部242は,時分割周期TDP_1において,デューティー比66%のPWM信号SIG_2を選択する。この選択されたPWM信号SIG_2は,出力対象のPWM信号である。

【0114】

このとき,タイミング制御部23は,図11(A’)の矢印TMG0に示すように,時分割周期TDP_1の開始タイミング(時間T110)と選択されたPWM信号SIG_2の出力タイミングを同期させる必要がある。すなわち,タイミング制御部23は,時分割周期TDPの開始タイミングと,選択されたPWM信号の出力タイミングを同期させる必要がある。

【0115】

その理由を説明する。例えば,図11(A”)の矢印TMG1に示すように,選択されたPWM信号SIG_2の出力タイミングがずれてしまうと,時分割周期TDP_1におけるPWM信号SIG_2のハイレベル幅の時間が短くなる。その結果,時分割周期TDP_1において,このPWM信号SIG_2を有するコモン電極駆動信号COMPD_0がコモン電極COMT_0に入力されることによりこの電極に生じる電圧が,小さくなる。そのため,コモン電極COM_0と,このコモン電極に対応するセグメント電極との間に所望の電圧が発生しなくなり,コモン電極COM_0と前記したセグメント電極とを有する液晶表示素子のオン,オフ制御を適切に行うことができなくなることがある。

【0116】

以上の理由により,タイミング制御部23は,開始タイミング情報PSをコモン用スイッチ部242に出力する。また,タイミング制御部23が,開始タイミング情報PSをセグメント用スイッチ部262に出力する理由も同様である。

【0117】

図5の説明に戻る。VRAM25は,図2のVRAM17と同様の機能を有する。すなわち,VRAM25は,表示周期FPにおいて先頭からTN番目の時分割周期TDP_TNの開始タイミングを生成したことを示すフェーズ情報PIが入力されると,時分割周期TDP_TNに対応するコモン端子COMT_TNの列に格納された映像データを選択し,選択した映像データVRをセグメントドライバ261に出力する。

【0118】

セグメントドライバ261は,VRAM25から入力された映像データによりオンが指定される液晶表示素子のコモン電極とこの液晶表示素子のセグメント電極との間の電圧が所定の閾値Vth以上になるPWM信号をPWM信号SIG_0〜SIG_3の中から決定する。

【0119】

または,セグメントドライバ261は,VRAM25から入力された映像データによりオフが指定される液晶表示素子のコモン電極とこの液晶表示素子のセグメント電極との間の電圧が所定の閾値Vth未満になるPWM信号をPWM信号SIG_0〜SIG_3の中から決定する。この決定されたPWM信号は,前記のセグメント電極に出力される信号である。

【0120】

なお,前述したように,コモンドライバ241は,パターン情報,フェーズ情報PIに基づき,PWM信号の決定を行う。セグメントドライバ261は,このパターン情報にアクセス可能である。従って,セグメントドライバ261は,パターン情報,フェーズ情報PIに基づき,VRAM25から入力された映像データによりオン,オフが指定される液晶表示素子のコモン電極にPWM信号SIG_0〜SIG_4の中の何れかが出力されるかを認識できるので,前記したPWM信号の決定が可能である。

【0121】

セグメントドライバ261は,前記決定したPWM信号を選択するようにセグメント用スイッチ部262に指示するセグメント用選択信号SEGS_0〜SEGS_31を生成する。

【0122】

セグメント用スイッチ部262は,セグメントドライバ261から入力されたセグメント用選択信号SEGS_0〜SEGS_31に基づき,PWM信号SIG_0〜SIG_3の中の何れかのPWM信号を選択する。そして,セグメント用スイッチ部262は,タイミング制御部23から入力された時分割周期TDP_TNの開始タイミングを示す開始タイミング情報PSに応答して,選択したPWM信号をセグメント端子SEGT_0〜SEGT_31に出力する。

【0123】

なお,タイミング制御部23が,開始タイミング情報PSをセグメント用スイッチ部262に出力する理由は,図11で説明したとおりである。

【0124】

図12は,セグメント用スイッチ部を説明する図である。図12(A)は,セグメント用スイッチ部262の機能ブロック図,図12(B)は,セグメント用スイッチ部262のセレクタ(SEL)262_0の機能ブロック図である。

【0125】

セグメント用スイッチ部262は,セグメント端子SEGT_0〜SEGT_31に対応して設けられたセレクタ(SEL)262_0〜262_31を有する。図12(B)では,セレクタ262_0について示しているが,セレクタ262_1〜262_31についても同様の構成を有する。

【0126】

セレクタ262_SN(SNは0〜31)は,SIG_PN(PNは0〜3)を選択するように指示するセグメント用選択信号SEGS_SNに基づき,PWM信号SIG_0〜SIG_3の中の何れかのPWM信号を選択する。そして,開始タイミング情報PSに応答して,選択した信号をセグメント端子SEGT_SNに出力する。そのため,セレクタ262_SNは,開始タイミング情報PSが次に入力されるまでの間(時分割周期TDPの間),選択したPWM信号を出力する。

【0127】

ここで,例えば,液晶制御回路2が,図7に示す時間T1〜T120において,コモン電極駆動信号COMPD_0(図7(A’)参照),セグメント電極駆動信号SEGPD_1(図7(B’)参照)を生成する場合を例示して,液晶制御回路2の動作を説明する。なお,既に,パルス信号生成部21のPWM回路210〜PWM回路213は,タイミング制御部23からのPWM信号生成開始指示に応答して,PWM信号SIG_0〜SIG3の生成を開始している。

【0128】

時間T1において,タイミング制御部23は,映像フレームの表示周期FPを時分割した時分割周期TDPの開始タイミングを生成する。そして,映像フレームの表示周期FPにおいて先頭から0番目の時分割周期TDP_0の開始タイミングを生成したことを示すフェーズ情報PIを生成する。

【0129】

コモンドライバ241は,タイミング制御部23から0番目の時分割周期TDP_0の開始タイミングを生成したことを示すフェーズ情報PIが入力されると,PWM信号SIG_0を選択するようにコモン用スイッチ部242に指示するコモン用選択信号COMS_0を生成する。なお,コモン用選択信号COMS_0以外のコモン用選択信号については,コモンドライバ241は,PWM信号SIG_1またはPWM信号SIG_2の何れか1つを決定し,決定したPWM信号を選択するようにコモン用スイッチ部242に指示するコモン用選択信号を生成する。

【0130】

VRAM25は,タイミング制御部23からフェーズ情報PIが入力されると0番目の時分割周期TDP_0に対応するコモン端子COMT_0の列に格納された映像データを選択し,選択した映像データVRをセグメントドライバ261に出力する。この場合,図4に示すbit4("1")などを有する映像データVRが出力される。

【0131】

セグメントドライバ261は,VRAM25から入力された映像データVRによりオンが指定された液晶表示素子LCD2のコモン電極COM_0と液晶表示素子LCD2のセグメント電極SEG_1との間の電圧が閾値Vth以上になるPWM信号SIG_3を選択するようにセグメント用スイッチ部262に指示するセグメント用選択信号SEGS_1を生成する。

【0132】

コモン用スイッチ部242のセレクタ242_0は,PWM信号SIG_0を選択するようにコモン用スイッチ部242に指示するコモン用選択信号COMS_0に基づいてPWM信号SIG_0を選択する。そして,セレクタ242_0は,時分割周期TDP_0の開始タイミングを示す開始タイミング情報PSの入力に応答してPWM信号SIG_0をコモン端子COMT_0に出力する。

【0133】

セグメント用スイッチ部262のセレクタ262_1は,PWM信号SIG_3を選択するようにセグメント用スイッチ部262に指示するセグメント用選択信号SEGS_1に基づいて,PWM信号SIG_3を選択する。そして,セレクタ262_1は,時分割周期TDP_0の開始タイミングを示す開始タイミング情報PSの入力に応答してPWM信号SIG_3をセグメント端子SEGT_1に出力する。

【0134】

コモン用スイッチ部242のセレクタ242_0,セグメント用スイッチ部262のセレクタ262_1は,次に,タイミング制御部23から開始タイミング情報PSが入力されるまでの間,選択したPWM信号を出力する。

【0135】

時間T110において,タイミング制御部23は,映像フレームの表示周期FPを時分割した時分割周期TDPの開始タイミングを生成する。そして,映像フレームの表示周期FPにおいて先頭から1番目の時分割周期TDP_1の開始タイミングを生成したことを示すフェーズ情報PIを生成する。

【0136】

コモンドライバ241は,タイミング制御部23から1番目の時分割周期TDP_1の開始タイミングを生成したことを示すフェーズ情報PIが入力されると,PWM信号SIG_2を選択するようにコモン用スイッチ部242に指示するコモン用選択信号COMS_0を生成する。

【0137】

VRAM25は,タイミング制御部23からフェーズ情報PIが入力されると1番目の時分割周期TDP_1に対応するコモン端子COMT_1の列に格納された映像データを選択し,選択した映像データVRをセグメントドライバ261に出力する。この場合,図4に示すbit5("0")などを有する映像データVRが出力される。

【0138】

セグメントドライバ261は,VRAM25から入力された映像データVRによりオフが指定された液晶表示素子LCD2のコモン電極COM_0と液晶表示素子LCD2のセグメント電極SEG_1との間の電圧が閾値Vth未満になるPWM信号SIG_1を選択するようにセグメント用スイッチ部262に指示するセグメント用選択信号SEGS_1を生成する。

【0139】

コモン用スイッチ部242のセレクタ242_0は,PWM信号SIG_2を選択するようにコモン用スイッチ部242に指示するコモン用選択信号COMS_0に基づいてPWM信号SIG_2を選択する。そして,セレクタ242_0は,時分割周期の開始タイミングを示す開始タイミング情報PSの入力に応答してPWM信号SIG_2をコモン端子COMT_0に出力する。

【0140】

セグメント用スイッチ部262のセレクタ262_1は,PWM信号SIG_1を選択するようにセグメント用スイッチ部262に指示するセグメント用選択信号SEGS_1に基づいて,PWM信号SIG_1を選択する。そして,セレクタ262_1は,時分割周期の開始タイミングを示す開始タイミング情報PSの入力に応答してPWM信号SIG_1をセグメント端子SEGT_1に出力する。

【0141】

以上,本実施の形態の液晶制御回路2によれば,デジタル信号であるPWM信号により液晶表示素子のオン,オフ制御を実現できる。そのため,第1の出力部24のコモンドライバ241,コモン用スイッチ部242,第2の出力部26のセグメントドライバ261,セグメント用スイッチ部262をデジタル化することができる。そして,電圧生成部の替わりに,デジタル回路であるパルス信号生成部21を使用している。そのため,アナログ回路を削減することができる。その結果,開発工程が削減され,開発費用,開発時間が少なくなる。さらに,回路面積を減らすことができる。

【0142】

また,電圧生成部を利用する場合,液晶表示素子の輝度調整を行うため,最大電圧V3を可変抵抗により調整することがある。この調整は,外部の調整用回路により行うため,部品コストの増大となる。しかし,本実施の形態の液晶制御回路2によれば,最大電圧V3に対応する電圧をPWM信号SIG_3のデューティー比を変更することにより,すなわちPWM回路213のデューティー比レジスタの設定値を変更することにより,調整することができる。そのため,前記した外部の調整用回路が不要になり,部品コストの増大を抑制できる。

【0143】

図13は,本実施の形態に関連する液晶制御回路1,デジタル論理回路を搭載する半導体チップの機能ブロック図である。

【0144】

液晶制御回路1を搭載する半導体チップCは,半導体チップC上に各種処理を実行するデジタル論理回路3を搭載することがある。デジタル論理回路3は,液晶制御回路1のコモン端子COMT_0〜COMT_3,セグメント端子SEGT_0〜SEGT_31をデジタル論理回路3の入出力端子として兼用することがある。

【0145】

図13では,一例として,デジタル論理回路3が,液晶制御回路1のコモン端子COMT_0をデジタル論理回路3の入出力端子として兼用する場合を示している。

【0146】

アナログ信号であるコモン電極駆動信号COMVD_0が,デジタル論理回路3内に設けられた例えばインバータ回路,バッファ回路に入力されると,この回路に貫通電流が流れることがある。このように貫通電流が流れる理由は,この回路内に設けられたCMOSトランジスタの閾値電圧に対応する電圧レベルを有するコモン電極駆動信号COMVD_0がこの回路に入力されるからである。

【0147】

そこで,液晶制御回路1が,コモン電極駆動信号COMVD_0を出力する間,このコモン電極駆動信号COMVD_0がデジタル論理回路3に入力されないように遮断する遮断回路4を液晶制御回路1とデジタル論理回路3との間に設けている。

【0148】

なお,この遮断回路4は,ポート機能設定レジスタ5の設定値により動作する。例えば,液晶制御回路の動作実行を示す"1"がポート機能設定レジスタに設定されている場合,遮断回路4が動作して,アナログ信号であるコモン電極駆動信号COMVD_0がデジタル論理回路3に入力しないように遮断する。

【0149】

本実施の形態の液晶制御回路2は,デジタル信号であるコモン電極駆動信号,セグメント電極駆動信号を出力する。従って,本実施の形態の液晶制御回路2を搭載する半導体チップは,アナログ信号の入力に起因するデジタル論理回路3の貫通電流を阻止する遮断回路4を搭載する必要がなくなる。その結果,半導体チップの面積を削減することができ,さらに,半導体チップのコストをも削減することができる。

【0150】

図14は,本実施の形態の液晶制御回路2と,液晶表示素子を有する液晶表示部Dとを有する液晶表示装置を示した図である。図14に示すように,液晶表示装置DPは,コモン端子COMT_0〜COMT_3,セグメント端子SEG_0〜SEG_31とを介して接続した液晶制御回路2と液晶表示部Dとを有する。

【0151】

このように,液晶制御回路2と液晶表示部Dとを接続することにより,液晶制御回路2は,液晶表示部Dの表示制御を実行できる。

【0152】

以上の実施の形態をまとめると,次の付記のとおりである。

【0153】

(付記1)

映像フレームの表示周期を分周した第1の周期の開始タイミングを生成するタイミング制御部と,

前記第1の周期を分周した第2の周期において相互に異なるデューティー比を有し第1のレベル,第2のレベルに対応する複数のパルス信号を生成するパルス信号生成部と,

前記複数のパルス信号の何れかのパルス信号を選択し選択した第1のパルス信号を液晶表示素子のコモン電極に前記第1の周期の間出力する第1の出力部と,

前記複数のパルス信号の何れかのパルス信号を前記映像フレームの映像データに応じて選択し選択した第2のパルス信号を前記液晶表示素子のセグメント電極に前記第1の周期の間出力する第2の出力部とを有する液晶制御回路。

【0154】

(付記2)

付記1において,

前記パルス信号生成部は,前記第2の周期を設定する周期設定レジスタと,前記デューティー比を設定するデューティー比設定レジスタとを有し,前記周期設定レジスタの第1の設定値および前記デューティー比設定レジスタの第2の設定値を有するパルス信号を生成する複数のバルス幅変調回路を有し,

前記第1の設定値は外部から前記周期設定レジスタに設定可能であり,前記第2の設定値は外部から前記デューティー比設定レジスタに設定可能であって,

前記複数のバルス幅変調回路の前記周期設定レジスタ毎に前記第2の周期が設定され,前記複数のバルス幅変調回路の前記デューティー比設定レジスタ毎に相互に異なるデューティー比が設定される液晶制御回路。

【0155】

(付記3)

付記2において,

4つの前記バルス幅変調回路を有する液晶制御回路。

【0156】

(付記4)

付記2の液晶制御回路と,

前記液晶表示素子を有する液晶表示部と,

を有する液晶表示装置。

【符号の説明】

【0157】

D…液晶表示部,LCD0〜LCD7…液晶表示素子,COM_0〜COM_3…コモン電極,SEG_0〜SEG_31…セグメント電極,1,2…液晶制御回路,11…電圧生成回路,12…プリスケーラ,13…タイミング制御部,14…コモン用スイッチ部,15…セグメント用スイッチ部,16…コモンドライバ,17…VRAM,18…セグメントドライバ,21…パルス信号生成部,210〜213,21x…PWM回路,211x…周期設定レジスタ,212x…デューティー比設定レジスタ,213x,214x…バッファ,215x…プリスケーラ,216x…ダウンカウンタ,217x…比較器,218x…出力レベル部,22…プリスケーラ,23…タイミング制御部,24…第1の出力部,241…コモンドライバ,242…コモン用スイッチ部,242_0〜242_3…セレクタ(SEL),25…VRAM,26…第2の出力部,261…セグメントドライバ,262…セグメント用スイッチ部,262_0〜262_31…セレクタ(SEL),C…半導体チップ,3…デジタル論理回路,4…遮断回路,5…ポート機能レジスタ,DP…液晶表示装置。

【特許請求の範囲】

【請求項1】

映像フレームの表示周期を分周した第1の周期の開始タイミングを生成するタイミング制御部と,

前記第1の周期を分周した第2の周期において相互に異なるデューティー比を有し第1のレベル,第2のレベルに対応する複数のパルス信号を生成するパルス信号生成部と,

前記複数のパルス信号の何れかのパルス信号を選択し選択した第1のパルス信号を液晶表示素子のコモン電極に前記第1の周期の間出力する第1の出力部と,

前記複数のパルス信号の何れかのパルス信号を前記映像フレームの映像データに応じて選択し選択した第2のパルス信号を前記液晶表示素子のセグメント電極に前記第1の周期の間出力する第2の出力部とを有する液晶制御回路。

【請求項2】

請求項1において,

前記パルス信号生成部は,前記第2の周期を設定する周期設定レジスタと,前記デューティー比を設定するデューティー比設定レジスタとを有し,前記周期設定レジスタの第1の設定値および前記デューティー比設定レジスタの第2の設定値を有するパルス信号を生成する複数のバルス幅変調回路を有し,

前記第1の設定値は外部から前記周期設定レジスタに設定可能であり,前記第2の設定値は外部から前記デューティー比設定レジスタに設定可能であって,

前記複数のバルス幅変調回路の前記周期設定レジスタ毎に前記第2の周期が設定され,前記複数のバルス幅変調回路の前記デューティー比設定レジスタ毎に相互に異なるデューティー比が設定される液晶制御回路。

【請求項3】

請求項2の液晶制御回路と,

前記液晶表示素子を有する液晶表示部と,

を有する液晶表示装置。

【請求項1】

映像フレームの表示周期を分周した第1の周期の開始タイミングを生成するタイミング制御部と,

前記第1の周期を分周した第2の周期において相互に異なるデューティー比を有し第1のレベル,第2のレベルに対応する複数のパルス信号を生成するパルス信号生成部と,

前記複数のパルス信号の何れかのパルス信号を選択し選択した第1のパルス信号を液晶表示素子のコモン電極に前記第1の周期の間出力する第1の出力部と,

前記複数のパルス信号の何れかのパルス信号を前記映像フレームの映像データに応じて選択し選択した第2のパルス信号を前記液晶表示素子のセグメント電極に前記第1の周期の間出力する第2の出力部とを有する液晶制御回路。

【請求項2】

請求項1において,

前記パルス信号生成部は,前記第2の周期を設定する周期設定レジスタと,前記デューティー比を設定するデューティー比設定レジスタとを有し,前記周期設定レジスタの第1の設定値および前記デューティー比設定レジスタの第2の設定値を有するパルス信号を生成する複数のバルス幅変調回路を有し,

前記第1の設定値は外部から前記周期設定レジスタに設定可能であり,前記第2の設定値は外部から前記デューティー比設定レジスタに設定可能であって,

前記複数のバルス幅変調回路の前記周期設定レジスタ毎に前記第2の周期が設定され,前記複数のバルス幅変調回路の前記デューティー比設定レジスタ毎に相互に異なるデューティー比が設定される液晶制御回路。

【請求項3】

請求項2の液晶制御回路と,

前記液晶表示素子を有する液晶表示部と,

を有する液晶表示装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2013−57905(P2013−57905A)

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願番号】特願2011−197548(P2011−197548)

【出願日】平成23年9月9日(2011.9.9)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願日】平成23年9月9日(2011.9.9)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]