液晶表示装置、液晶表示装置の駆動方法および電子機器

【課題】焼き付きやフリッカーが発生しないようにする。

【解決手段】画素110の周辺には、ダミー画素111が設けられる。ダミー画素111が供える液晶素子120dの画素電極118dには、基準電圧より高位の第1電圧と低位の第2電圧とが時間をずらして印加される。画像を表示する画素110が備える液晶素子120に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比を、第1電圧が印加された時に第2対向電極109に流れた電流と第2電圧が印加された時に第2対向電極109に流れた電流とに基づいて変更する。

【解決手段】画素110の周辺には、ダミー画素111が設けられる。ダミー画素111が供える液晶素子120dの画素電極118dには、基準電圧より高位の第1電圧と低位の第2電圧とが時間をずらして印加される。画像を表示する画素110が備える液晶素子120に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比を、第1電圧が印加された時に第2対向電極109に流れた電流と第2電圧が印加された時に第2対向電極109に流れた電流とに基づいて変更する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、焼き付きやフリッカーが発生するのを抑える技術に関する。

【背景技術】

【0002】

液晶表示装置では、液晶素子を交流駆動するのが一般的である。ただし、交流駆動するだけでは、液晶に直流成分が印加される場合がある。具体的には、液晶表示装置においては、液晶層を挟む画素電極基板と対向電極基板は物理的な構造が異なっており、対向電極から見て高位である正極性電圧が画素電極基板に印加された場合と、対向電極から見て低位である負極性電圧が画素電極基板に印加された場合とで、電極と配向膜との界面や配向膜と液晶層などの界面における抵抗値が異なってしまう。これにより液晶表示装置においては、正極性電圧の印加時と負極性電圧の印加時とで液晶層への実効電圧が等しくても電流量が異なることとなり、電荷の移動量に非対象性が生じる。また、この電流量の非対称性により、液晶内部の電荷に偏りが生じ、電荷の偏りによって内部電界が発生する。この内部電界の影響により、実際に液晶層に印加される電圧は駆動電圧の極性によって非対称となり、液晶層に直流電圧成分が印加される。

【0003】

液晶層にこの直流電圧成分が印加されるとフリッカーが生じることとなるため、フリッカーを抑えるために対向電極の電圧を調整する技術がある。例えば特許文献1に開示されている調整回路は、液晶素子に正極性電圧を印加した時の輝度と負極性電圧を印加した時の輝度とを光センサーで測定し、正極性電圧を印加した時の輝度と負極性電圧を印加した時の輝度と差に基づいて対向電極の電圧を調整する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平8−286169号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、特許文献1の調整回路でフリッカーが最小となるように調整しても、経年変化によって液晶素子へ直流電圧成分が印加され、焼き付きという問題が発生してしまう。この場合、オペレータが再度調整回路を操作して調整回路に対向電極の電圧調整を行わせることとなり、手間がかかる。

本発明は、上述した事情に鑑みてなされたものであり、その目的の1つは、焼き付きやフリッカーが発生しないようにすることにある。

【課題を解決するための手段】

【0006】

上記目的を達成するために、本発明に係る液晶表示装置は、第1電極とコモン電極とにより液晶を挟持した表示画素と、所定の基準電圧よりも高位側で前記表示画素の階調に応じた正極性電圧と、所定の基準電圧よりも低位側で前記階調に応じた負極性電圧とを時間的に交互に前記第1電極へ印加し、前記コモン電極に所定の電圧を印加する駆動回路と、第2電極と前記コモン電極により液晶を挟持したダミー画素と、前記基準電圧よりも高位側の第1電圧と低位側の第2電圧とを時間的にずらして印加する測定信号を前記第2電極へ供給する測定信号回路と、前記第2電極に前記第1電圧が印加された後に前記コモン電極に流れる電流のうち当該第1電圧の印加による瞬時電流を除いた第1電流と、前記第2電極に前記第2電圧が印加された後に前記コモン電極に流れる電流のうち当該第2電圧の印加による瞬時電流を除いた第2電流とに基づいて、前記駆動回路により前記第1電極に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比を変更する制御回路とを有する。

【0007】

本発明によれば、測定信号回路から第2電極に第1電圧が印加された後にコモン電極に流れる電流のうち当該第1電圧の印加による瞬時電流を除いた第1電流と、第2電極に第2電圧が印加された後にコモン電極に流れる電流のうち当該第2電圧の印加による瞬時電流を除いた第2電流とに基づいて、表示画素の第1電極に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比が変更するため、液晶に直流電圧成分が印加されるのを抑え、液晶表示装置において、焼き付きやフリッカーが発生しないようにすることができる。

【0008】

本発明においては、前記制御回路は、前記第1電流と前記第2電流との差が予め定められた閾値未満となるように、前記第1電極に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比を変更する構成としてもよい。

この構成によれば、ダミー画素の液晶に第1電圧を印加した時に流れた第1電流と第2電圧を印加した時に流れた第2電流との差に基づいて、第1電極に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比が変更され、焼き付きやフリッカーが発生しないようにすることができる。

【0009】

また、本発明においては、前記制御回路は、前記第1電流と前記第2電流との差が予め定められた閾値未満となるように、前記第1電極に印加する正極性電圧の印加時間と負極性電圧の印加時間を変更する構成としてもよい。

この構成によれば、正極性電圧の実効電圧と、負極性電圧の実効電圧とが変更され、焼き付きやフリッカーが発生しないようにすることができる。

【0010】

また、本発明においては、前記制御回路は、前記第1電流と前記第2電流との差が予め定められた閾値未満となるように、前記第1電極に印加する正極性電圧と負極性電圧の電圧比を変更する構成としてもよい。

この構成によれば、正極性電圧と負極性電圧の比を変更することにより、正極性電圧の実効電圧と、負極性電圧の実効電圧とが変更され、焼き付きやフリッカーが発生しないようにすることができる。

【0011】

また、本発明においては、前記測定信号は、前記第1電圧を印加する期間と前記第2電圧を印加する期間との間に前記第2コモン電極と同じ第3電圧を前記第2電極へ印加する信号である構成としてもよい。

この構成によれば、第1電圧を印加した時と第2電圧を印加した時に液晶の光学応答が遅くなるので、第1電流と第2電流を得易くなる。

【0012】

また、本発明においては、前記コモン電極は、前記第1電極との間に前記液晶を挟持する第1コモン電極と、前記第2電極との間に前記液晶を挟持する第2コモン電極とで構成され、前記第1コモン電極と前記第2コモン電極は互いに絶縁されており、前記制御回路は、前記第2電極に前記第1電圧が印加された後に前記第2コモン電極に流れる電流のうち当該第1電圧の印加による瞬時電流を除いた電流と、前記第2電極に前記第2電圧が印加された後に前記第2コモン電極に流れる電流のうち当該第2電圧の印加による瞬時電流を除いた電流とに基づいて、前記駆動回路により前記第1電極に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比を変更する構成としてもよい。

この構成によれば、表示画素とは別にダミー画素の液晶に流れる電流を測定することができる。

【0013】

また、本発明においては、前記測定信号により前記第1電圧が前記第2電極へ印加される期間は、前記第1電極へ前記正極性電圧が印加される期間より長く、前記測定信号により前記第2電圧が前記第2電極へ印加される期間は、前記第1電極へ前記負極性電圧が印加される期間より長い構成としてもよい。

この構成によれば、第1電流と第2電流を得る時間を確保し、第1電流と第2電流を得易くなる。

【0014】

また、本発明においては、前記ダミー画素は、予め定められた期間においては前記測定信号回路から前記測定信号が前記第2電極へ供給され、当該期間外においては、当該ダミー画素に隣り合う前記表示画素に印加される正極性電圧と負極性電圧とが時間的に交互に前記駆動回路から前記第2電極へ印加される構成としてもよい。

この構成によれば、ダミー画素を隣り合う表示画素と同じ階調にし、ダミー画素を目立たないようにすることができる。

【0015】

なお、本発明は、電気光学装置のみならず、液晶表示装置の駆動方法としても、当該液晶表示装置を有する電子機器としても概念することが可能である。

【図面の簡単な説明】

【0016】

【図1】電気光学装置1の構成を示したブロック図。

【図2】表示パネル100の構成を示した図。

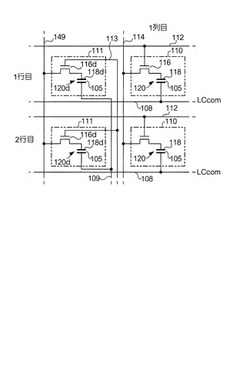

【図3】画素110とダミー画素111の構成を示した図。

【図4】測定信号Meの波形、検出回路61で測定される電圧の波形及び液晶の透過率の変化を示した図。

【図5】走査線駆動回路130の動作を示す図。

【図6】データ信号の波形例を示した図。

【図7】データ信号の波形例を示した図。

【図8】表示領域A1における画素の書き込みの推移を示す図。

【図9】走査線駆動回路130の動作を示す図。

【図10】表示領域A1における画素の書き込みの推移を示す図。

【図11】走査線駆動回路130の動作を示す図。

【図12】表示領域A1における画素の書き込みの推移を示す図。

【図13】表示パネル100の特性を示した図。

【図14】走査制御回路52の処理の流れを示したフローチャート。

【図15】実施形態に係る電気光学装置1を用いたプロジェクターの構成を示す図。

【図16】変形例に係る走査制御回路52の処理の流れを示したフローチャート。

【図17】変形例に係る画素110とダミー画素111の構成を示した図。

【図18】変形例に係る電気光学装置1Aの構成を示した図。

【発明を実施するための形態】

【0017】

[実施形態]

まず、この発明の一実施形態の概略について説明する。画素電極と対向電極(コモン電極)とで液晶を挟時した液晶素子は、焼き付きや劣化を防止するために、基準電圧よりも高位側の正極性電圧と、低位側の負極性電圧とを画素電極に交互に印加する一方、対向電極に所定電圧を印加して、交流で駆動する。このとき、正極性で電圧を印加・保持する期間と、負極性で電圧を印加・保持する期間とにおいて、液晶素子の透過率(または反射率)が異なっていると、フリッカー(ちらつき、明滅)として知覚される。

【0018】

液晶分子は、画素電極および対向電極の間で生じる電界によって、その傾きが変化し、これによって、液晶素子を通過する光の偏光状態が規定されて、液晶素子の透過率(または反射率)が変化する。液晶は、誘電異方性を有するので、正極性電圧の保持期間と負極性電圧の保持期間とにおいて、液晶素子の透過率が異なっているということは、液晶分子の傾きが異なっているということであり、これは、液晶素子の容量が異なっているということにほかならない。

したがって、液晶素子の容量を正極性電圧の保持期間と負極性電圧の保持期間との各々について検出するとともに、その差が小さくなるように、液晶素子への印加電圧を制御すれば、フリッカーを低減することができるはずである。ただし、液晶素子の容量を直接的に検出するのは困難である。このため、本実施形態では、後述するように当該液晶素子の容量に対応して当該液晶素子に流れる電流を測定し、測定した電流に基づいて液晶素子への印加電圧を制御する構成とした。本実施形態は、これを具現化したものであり、以下、その詳細について説明する。

【0019】

図1は、本発明の一実施形態に係る電気光学装置1(液晶表示装置)の構成を示したブロック図である。図1に示したように、電気光学装置1は、表示パネル100と制御回路50に大別される。このうち、表示パネル100の動作等を制御する制御回路50は、走査制御回路52、データ信号生成回路54、A/D変換回路56、検出回路61及び抵抗素子Rを含み、例えばFPC(flexible printed circuit)基板によって表示パネル100に接続される。

【0020】

制御回路50は、外部上位回路(図示省略)から供給される垂直同期信号Vs、水平同期信号Hsおよびクロック信号Clkにしたがって表示パネル100の各部を制御する。また、制御回路50は、外部上位回路から供給されるデジタルの画像データVdをアナログのデータ信号Vidに変換し、データ信号Vidを表示パネル100へ供給する。なお、制御回路50の詳細については後述する。

【0021】

図2は、表示パネル100の構成を示した図である。表示パネル100は、液晶を用いて画像の表示を行うものであり、画像の表示を行う表示領域A1と、表示領域A1の周辺に設けられたダミー画素領域A2を備え、ダミー画素領域A2の周辺に走査線駆動回路130およびデータ線駆動回路140が配置された周辺回路内蔵型となっている。

表示領域A1には、480行の走査線112が図において横方向(X方向)に設けられる一方、640列のデータ線114が縦方向(Y方向)に設けられている。そして、これらの走査線112とデータ線114との交差の各々に対応するように画素110(表示画素)がそれぞれ設けられている。なお、本実施形態では、表示領域A1において画素110が縦480行×横640列でマトリクス状に配列されることになるが、本発明をこの配列に限定する趣旨ではない。

また、ダミー画素領域A2には、表示領域A1を囲むようにして複数のダミー画素111が配置されており、各画素111には表示領域A1を囲むように設けられた走査線113と測定信号線149が接続されている。具体的には、本実施形態においては、ダミー画素111は、1行目の画素110の隣に1行×640列で設けられ、480行目の画素110の隣に1行×640列で設けられている。またダミー画素111は、1列目の画素110の隣に1列×480行で設けられ、640列目の画素110の隣に1列×480行で設けられている。

【0022】

走査線駆動回路130は、制御回路50により制御され、垂直走査期間にわたって走査信号G1、G2、G3、・・・、G480を、それぞれ1、2、3、・・・480行目の走査線112に供給するものである。走査線駆動回路130は、走査線112を予め定められた順番で水平走査期間毎に選択し、選択した走査線112へ供給する走査信号を電圧Vddに相当するHレベル(選択電圧)とする。

また、走査線駆動回路130は、制御回路50により制御され、走査線113へ走査信号Gdを供給する。走査線駆動回路130は、液晶に流れる電流を測定する際には走査信号Gdを電圧Vddに相当するHレベルにする。

【0023】

データ線駆動回路140は、サンプリング信号出力回路142と、各データ線114に対応して設けられるnチャネル型の薄膜トランジスタ(thin film transistor、以下「TFT」と称する)146とを備えている。サンプリング信号出力回路142は、制御回路50により制御され、各TFT146に対応してサンプリング信号S1、S2、S3、・・・、S640を出力するものである。サンプリング信号出力回路142は、図6,7に示したように水平走査期間(H)に供給されるスタートパルスDxを、クロック信号Clxのレベルが遷移する毎に順次シフトし、サンプリング信号S1、S2、S3、・・・、S640として出力する。

【0024】

TFT146は、1〜640列のデータ線114の各々に設けられ、それぞれサンプリングスイッチとして機能するものであり、そのドレイン電極は、データ線114の一端に接続されている。TFT146のソース電極は、画像信号線148に接続される。また、TFT146のゲート電極には、サンプリング信号出力回路142からのサンプリング信号が供給される。例えば、左から数えて2番目のTFT146は、2列目のデータ線114に対応するので、このデータ線114に対応するTFT146のゲート電極には、サンプリング信号S2が供給される。サンプリング信号S2がHレベルになると、TFT146がソース・ドレイン電極間で導通(オン)状態となるので、データ線114は、画像信号線148に接続されることになる。

【0025】

次に、画素110とダミー画素111について説明する。図3は、画素110とダミー画素111の構成を示した図であり、1行1列目の画素110、2行1列目の画素110、1行1列目の画素110に隣り合うダミー画素111、2行1列目の画素110に隣り合うダミー画素111の構成を示した図である。

各画素110は互いに同一構成であり、nチャネル型のTFT116と液晶素子120とを有する。i行j列目の画素110においては、TFT116のゲート電極はi行目の走査線112に接続される一方、そのソース電極はj列目のデータ線114に接続され、ドレイン電極は、液晶素子120の一端である画素電極118(第1電極)に接続されている。また、液晶素子120の他端は、第1対向電極108(第1コモン電極)に接続されている。この第1対向電極108は、全ての画素110にわたって共通であって、時間的に一定の電圧LCcomが印加されている。なお、iは、画素110が配列する行を一般的に示す場合の記号であって、本実施形態では、それぞれ1以上480以下を満たす整数である。また、jは、画素110が配列する列を一般的に示す場合の記号であって、本実施形態では、それぞれ1以上640以下を満たす整数である。例えば、1行1列目の画素110において、TFT116のゲート電極は1行目の走査線112に接続される一方、そのソース電極は1列目のデータ線114に接続され、そのドレイン電極は液晶素子120の一端である画素電極118に接続されている。

【0026】

また、各ダミー画素111は各々同一構成であり、nチャネル型のTFT116dと液晶素子120dとを有する。TFT116dのゲート電極は走査線113に接続される一方、そのソース電極は測定信号線149に接続され、そのドレイン電極は液晶素子120dの一端である画素電極118d(第2電極)に接続されている。また、液晶素子120dの他端は、第2対向電極109(第2コモン電極)に接続されている。この第2対向電極109は、全てのダミー画素111にわたって共通であり、信号線107により制御回路50の抵抗素子Rに接続されている。また、第2対向電極109は、第1対向電極108とは絶縁されている。

【0027】

なお、この表示パネル100は、特に図示しないが、素子基板と対向基板との一対の基板が一定の間隙を保って貼り合わせられるとともに、この間隙に液晶が封止された構成となっている。このうち、素子基板には、走査線112,113、データ線114、TFT116,116d,146、画素電極118,118d及び測定信号線149が走査線駆動回路130やデータ線駆動回路140とともに形成される。一方、対向基板には第1対向電極108と第2対向電極109が形成されており、これらの電極形成面が互いに対向するように一定の間隙を保って貼り合わせられている。なお、画素110に対しては第1対向電極108が対向し、ダミー画素111に対しては第2対向電極109が対向する。このため、本実施形態において液晶素子120は、画素電極118と第1対向電極108とが液晶105を挟持することによって構成され、液晶素子120dは、画素電極118dと第2対向電極109とが液晶105を挟持することによって構成されることになる。

【0028】

本実施形態では、液晶素子120,120dにおいて保持される電圧の実効値がゼロ(またはゼロ近傍)に近ければ、液晶素子120,120を通過する光の透過率が最小となって黒色表示になる一方、保持される電圧の実効値が大きくなるにつれて透過する光量が増大して、ついには透過率が最大の白色表示になるノーマリーブラックモードに設定されている。

【0029】

この構成において、走査線112に走査信号を供給し、TFT116をオン(導通)させるとともに、データ線114およびオン状態のTFT116を介して、画素電極118に階調(明るさ)に応じた電圧のデータ信号Vidを供給すると、走査信号が供給された走査線112とデータ信号が供給されたデータ線114との交差に対応する液晶素子120に、階調に応じた実効電圧を保持させることができる。したがって、液晶素子120を透過する光は、画素毎に異ならせることが可能であり、これにより、表示領域A1において画像が形成される。なお、形成された画像は、使用者に直視され、または、後述するプロジェクターのように拡大投射されて視認される。

また、この構成において、走査線113に走査信号Gdを供給し、TFT116dをオン(導通)させるとともに、測定信号線149およびオン状態のTFT116dを介して、画素電極118dに電圧を印加すると、液晶素子120dに、測定信号線149に供給された測定信号に応じた実効電圧を保持させることができる。なお、表示パネル100においては、ダミー画素111が視認されないようにするため、表示領域A1より外側に外側にダミー画素111を透過した光を遮光する遮光層を設けるようにしてもよい。

【0030】

続いて、制御回路50について説明する。図1に示したように、制御回路50においては、垂直同期信号Vs、水平同期信号Hsおよびクロック信号Clkが走査制御回路52に供給され、画像データVdがデータ信号生成回路54に供給される。

画像データVdは、図示省略した外部上位回路から、垂直走査信号Vs、水平走査信号Hsおよびクロック信号Clkに同期して供給される。画像データVdは、縦480行×横640列の画素110の階調を例えば8ビットで指定するデジタルデータであり、特に図示しないが、垂直同期信号Vsで規定される垂直走査期間にわたって、1行1列〜1行640列、2行1列〜2行640列、3行1列〜3行640列、・・・、480行1列〜480行640列という画素の順番で供給される。この供給の際に、水平同期信号Hsで規定される水平走査期間において1行分の画像データVdが供給され、さらに、クロック信号Clkの1周期で1画素分の画像データVdが供給される。なお、画像データVdは、周期16.7ミリ秒(周波数60Hz)で1フレーム分(表示パネル100の全画素分)が供給される。

【0031】

走査制御回路52は、極性指定信号Polをデータ信号生成回路54へ出力する。極性指定信号Polは、液晶素子120に対する電圧の書込極性を指定する信号であり、例えばHレベルであれば正極性を指定し、Lレベルであれば負極性を指定する。ここで、正極性書込とは、階調に応じた電圧を液晶素子120に保持させる際に、画素電極118が第1対向電極108よりも高位側となる場合をいい、反対に、負極性書込とは、画素電極118が第1対向電極108よりも低位側となる場合をいう。

【0032】

データ信号生成回路54は、外部上位装置から供給される画像データVdを、一旦内部メモリ(図示省略)に記憶した後、表示パネル100の駆動に同期して読み出すものである。データ信号生成回路54は、表示パネル100のある行の走査線を選択するとき、当該行の画像データVdを読み出し、読み出した画像データVdをアナログの信号に変換してデータ信号Vidを生成する。

なお、データ信号生成回路54は、極性指定信号Polによって正極性書込が指定されている場合、データ信号Vidを、第1対向電極108への印加電圧LCcomよりもやや高位側に設定された基準電圧Vc(基準電位)に対して高位側の電圧であって、階調に応じた電圧とする。また、データ信号生成回路54は、極性指定信号Polによって負極性書込が指定されている場合、データ信号Vidを、基準電圧Vcに対して低位側の電圧であって、階調に応じた電圧とする。なお、極性を切り替える理由は、直流成分の印加によって液晶が劣化するのを防止するためである。

【0033】

また、走査制御回路52は、測定信号Meと電圧設定信号Vsetを出力する。測定信号Meは、ダミー画素111の液晶に流れる電流を測定するために出力される信号であり、測定信号線149に供給される。測定信号Meは、図4の(a)に示したように基準電圧Vc(第3電圧)、基準電圧Vcに対して高位側の電圧V1(第1電圧)、基準電圧Vcに対して低位側の電圧V2(第2電圧)という順番で繰り返し電圧が変化する。

電圧設定信号Vsetは、第2対向電極109の電位を規定する信号であり、第2対向電極109に供給される。電圧設定信号Vsetが第2対向電極109に供給されると、第2対向電極109には基準電圧Vcが印加される。

【0034】

また、走査制御回路52は、垂直同期信号Vs、水平同期信号Hsおよびクロック信号Clkに同期して、スタートパルスDx、Dya,Dybおよびクロック信号Clx、Clyを出力する。

詳細には、走査制御回路52は、1行目の画像データVdに対応したデータ信号Vidが供給される水平走査期間に1行目の走査線112が選択されるようにスタートパルスDya,Dybおよびクロック信号Clyを出力し、2、3、4、・・・、480行の画像データVdに対応したデータ信号Vidが供給される水平走査期間にそれぞれ2、3、4、・・・、480行目の走査線112が選択されるようにクロック信号Clyを出力して走査線駆動回路130を制御する。

また、走査制御回路52は、1列目の画素に対応するデータ信号Vidを出力するときにサンプリング信号S1をHレベルとし、以下2列目、3列目、・・・、640列目の画素に対応するデータ信号Vidを出力するときにサンプリング信号S2、S3、・・・、S640がHレベルとなるように、スタートパルスDxおよびクロック信号Clxを出力してサンプリング信号出力回路142を制御する。

【0035】

図5は、走査線駆動回路130により出力される走査信号G1〜G480を、スタートパルスDya、Dybとクロック信号Clyとの関係において示すタイミングチャートである。この図に示したように、本実施形態では、1フレームの期間において走査線112は、それぞれ2回選択される。ここで、フレームとは、1枚の画像を表示パネル100に表示させるのに要する期間をいうが、画像データVdは、周期16.7ミリ秒(周波数60Hz)で供給されるので、1フレームとは、この周期の16.7ミリ秒と一致する。

走査制御回路52は、デューティ比が50%のクロック信号Clyを、1フレームの期間にわたって走査線数に等しい480周期分出力する。なお、図5においては、クロック信号Clyの1周期の期間をHと表記している。また、走査制御回路52は、クロック信号Clyの1周期分のパルス幅を有するスタートパルスDya、Dybを、それぞれクロック信号ClyがHレベルの立ち上がり時において、それぞれ次のように出力する。すなわち、走査制御回路52は、スタートパルスDyaを1フレームの期間の最初(すなわち第1フィールドの最初)に出力する一方、スタートパルスDybを、スタートパルスDybを出力してからクロック信号Clyの240周期分を出力した(すなわち、1フレームの半分期間が経過した)タイミングTで出力する。ただし、走査制御回路52は、後述するように、スタートパルスDybをタイミングTに対し、クロック信号Clyの周期を単位とした分だけ時間的に前方側または後方側に出力する場合がある。

【0036】

なお、本実施形態では、1フレームの期間のうち、スタートパルスDyaが出力されてからスタートパルスDybが出力されるまでの期間を第1フィールドとし、スタートパルスDybが出力されてから次のスタートパルスDyaが出力されるまでの期間を第2フィールドとしている。ここで、スタートパルスDya、Dybは交互に出力され、このうち、スタートパルスDyaは、1フレームの開始タイミング、すなわち16.7ミリ秒毎に出力される。このため、スタートパルスDyaを特定すると、必然的にスタートパルスDybも特定できるので、図1、図2等においては、特に両者を区別することなく、スタートパルスDyとして表記している。

【0037】

走査線駆動回路130は、このようなスタートパルスDya、Dybおよびクロック信号Clyから、図5に示される走査信号G1〜G480を出力する。すなわち、走査線駆動回路130は、走査信号G1〜G480について、スタートパルスDyaが供給されると、クロック信号ClyがLレベルの期間において順次Hレベルとさせる一方、スタートパルスDybが供給されると、クロック信号ClyがHレベルの期間において順次Hレベルとさせる。

このため、走査線112は、スタートパルスDyaの供給によって、あるフレームの第1フィールドから第2フィールドまでにわたって画面下方向にむかって1、2、3、4、・・・、480行目の順番で、クロック信号Clyの半周期の期間をおいて選択される。一方、走査線112は、スタートパルスDybの供給によって、あるフレームの第2フィールドから次フレームの第1フィールドまでにわたって画面下方向にむかって1、2、3、4、・・・、480行目の順番で、スタートパルスDyaの供給を契機とする選択の合間にて選択されることになる。なお、走査信号がHレベルとなる期間は、実際には図5,6に示されるように、クロック信号Clyの半分周期の期間よりも狭められている。

【0038】

次にスタートパルスDybの出力タイミングについて説明する。走査制御回路52は、スタートパルスDybの出力タイミングを制御する。具体的には、走査制御回路52は、スタートパルスDybの出力タイミングを指定するための設定値として、予め定められた第1設定値と第2設定値を記憶している。なお、本実施形態においては、第1設定値は、マイナスの整数の値であり、第2設定値は、プラスの整数の値である。また、走査制御回路52は、スタートパルスDybの出力タイミングを指定するための値を格納するレジスターを有している。走査制御回路52は、レジスターに格納された値に応じてスタートパルスDybの出力タイミングを変更する。

【0039】

具体的には、まず走査制御回路52は、外部上位装置から供給される画像データVdを、データ信号生成回路54の内部メモリに記憶させた後、表示パネル100においてある行の走査線112を選択するとき、当該行の画像データVdを記憶速度の倍の速度で読み出すとともに、画像データVdの読み出しに合わせて、サンプリング信号S1〜S640が順番にHレベルとなるように、サンプリング信号出力回路142を制御する。なお、読み出された画像データVdは、アナログのデータ信号Vidに変換される。

【0040】

ここで、走査制御回路52は、レジスターに格納されている値が「0」であると、タイミングTにおいてスタートパルスDybを供給する。走査制御回路52がタイミングTにおいてスタートパルスDybを供給する場合、第1フィールドにおいては、走査線112が241、1、242、2、243、3、・・・、480、240行目という順番で選択される。

このため、走査制御回路52は、はじめに241行目の走査線112が選択されるように、走査線駆動回路130を制御する。また、走査制御回路52は、データ信号生成回路54に対し、メモリに記憶された241行目に相当する画像データVdを倍速で読み出させ、極性指定信号Polに応じて、負極性のデータ信号Vidに変換するように制御するとともに、この読み出しに合わせて、サンプリング信号S1〜S640がこの順番で排他的にHレベルとなるようにサンプリング信号出力回路142を制御する。サンプリング信号S1〜S640が順番にHレベルになると、TFT146が1列目から640列目まで順番にオンとなり、画像信号線148に供給されたデータ信号Vidが1〜640列目のデータ線114に順番にサンプリングされる。

一方、241行目の走査線112が選択されて走査信号G241がHレベルになると、241行目に位置する画素110におけるTFT116がすべてオンする。このため、データ線114にサンプリングされたデータ信号Vidの負極性電圧がそのまま画素電極118に印加される。このため、241行目であって1、2、3、4、・・・、639、640列の画素における液晶素子120には、画像データVdで指定された階調に応じた負極性電圧が書き込まれて、保持されることになる。

【0041】

次に、走査制御回路52は、1行目の走査線112が選択されるように、走査線駆動回路130を制御する。また、走査制御回路52は、データ信号生成回路54に対し、メモリに記憶された1行目に相当する画像データVdを倍速で読み出させ、極性指定信号Polに応じて、正極性のデータ信号Vidに変換するように制御するとともに、この読み出しに合わせて、サンプリング信号S1〜S640がこの順番で排他的にHレベルとなるようにサンプリング信号出力回路142を制御する。

1行目の走査線112が選択されて走査信号G1がHレベルになると、1行目に位置する画素110におけるTFT116がすべてオンし、これにより、データ線114にサンプリングされたデータ信号Vidの電圧が画素電極118に印加される。このため、1行目であって1〜640列の画素における液晶素子120には、画像データVdで指定された階調に応じた正極性電圧が書き込まれて、保持されることになる。

【0042】

以下、第1フィールドにおいては、同様な電圧書込の動作が、242、2、243、3、・・・、480、240行目という順番で実行される。これにより、1〜240行目の画素に対しては階調に応じた正極性電圧が書き込まれ、241〜480行目の画素に対しては階調に応じた負極性電圧が書き込まれて、それぞれ保持されることになる。

なお、タイミングTにおいてスタートパルスDybが供給される場合であれば、第2フィールドにおいて、走査線112が1、241、2、242、3、243、4、244、・・・、240、480行目という順番で選択されるともに、同一行における書込極性が反転される。このため、1〜240行目の画素に対しては階調に応じた負極性電圧が書き込まれ、241〜480行目の画素に対しては階調に応じた正極性電圧が書き込まれて、それぞれ保持されることになる。

【0043】

図6には、第1フィールドにおける(i+240)行目の走査線とi行目の走査線とが選択される期間におけるデータ信号Vidの電圧波形の一例が示されている。この図において、電圧Vw(+)、Vw(−)は、それぞれ最高階調の白色に相当する正極性、負極性電圧であり、基準電圧Vcを中心に対称の関係にある。基準電圧Vcは、データ信号Vidの振幅中心であり、電圧Vw(+)、Vw(−)の中間の電圧である。なお、本実施形態においては、特に説明のない限り、接地電位Gndを電圧の基準としている。画像データVdで指定される階調値の十進値が「0」のときに最低階調の黒色を指定し、以後当該十進値が大きくなるにつれて明るい階調を指定する場合、本実施形態はノーマリーブラックモードであるから、データ信号Vidの電圧は、正極性に変換する場合であれば、階調値が大きくなるにつれて基準電圧Vcから高位側(Vw(+)側)に振られた電圧となり、負極性に変換する場合であれば、基準電圧Vcから低位側(Vw(−)側)に振られた電圧となる。

【0044】

第1フィールドでは、i行目よりも先に(i+240)行目の走査線が選択されるので、走査信号G(i+240)がHレベルになる期間のうち、例えばサンプリング信号S1がHレベルになる期間に、データ信号Vidは、(i+240)行1列の画素の階調に応じた負極性電圧となり、以降、サンプリング信号の変化に合わせて、2、3、4、・・・、640列目の画素の階調に応じた負極性電圧に変化する。続いて選択されるi行目では、正極性書込が指定されるので、走査信号GiがHレベルになる期間のうち、例えばサンプリング信号S1がHレベルになる期間に、データ信号Vidは、i行1列の画素の階調に応じた正極性電圧となり、以降、サンプリング信号の変化に合わせて、2、3、4、・・・、640列の画素の階調に応じた正極性電圧に変化する。なお、第2フィールドでは、i行目よりも後に(i+240)行目の走査線が選択されるので、走査信号Giが先にHレベルになるとともに、書込極性が反転するので、データ信号Vidの電圧波形は図7に示される通りとなる。

なお、図6および図7においてデータ信号Vidの電圧を示す縦スケールは、便宜的に他の信号における縦スケールよりも拡大してある。また、データ信号Vidは、サンプリング信号S640がLレベルに変化してからサンプリング信号S1がHレベルに変化するまでの期間にわたって黒色に相当する電圧となっているが、その理由は、タイミングずれなどの理由により誤って画素に書き込まれても、表示に寄与させないためである。

【0045】

次に図8は、スタートパルスDybがタイミングTで供給される場合において、各行の書込状態を連続するフレームにわたった時間経過とともに示す図である。この図に示されるように、本実施形態では、第1フィールドにおいて241、242、243、・・・、480行目の画素では負極性の書き込みがなされ、1、2、3、・・・、240行目の画素では正極性の書き込みがなされて、次の書き込みまで保持される。一方、第2フィールドにおいて1、2、3、・・・、240行目の画素では負極性の書き込みがなされ、241、242、243、・・・、480行目の画素では正極性の書き込みがなされて、同様に次の書き込みまで保持される。

レジスターの値が「0」であり、スタートパルスDybがタイミングTで供給される場合、第1および第2フィールドの期間は、クロック信号Clyの240周期分であるから、各画素において液晶素子120に正極性電圧が保持される期間と負極性電圧が保持される期間とは半分ずつとなる。

【0046】

次に、レジスターに格納されている値が0以外の値である場合について説明する。例えば、レジスターに格納された値が「−1」である場合、走査制御回路52は、図9に示したように、スタートパルスDybを、タイミングTよりもクロック信号Clyの1周期分だけ早いタイミングT(−1)に変更して出力する。すると、第1フィールドの期間はクロック信号Clyの239周期分となるのに対し、第2フィールドの期間はクロック信号Clyの241周期分となる。これにより、図10に示されるように、スタートパルスDybの供給を契機とする選択により書き込まれる負極性電圧の保持期間は、スタートパルスDyaの供給を契機とする選択により書き込まれる正極性電圧の保持期間よりも長くなる。したがって、画素においては、負極性電圧で保持された実効電圧が高められ、正極性電圧で保持された実効電圧が低められる。

【0047】

負極性電圧で保持された実効電圧が正極性電圧で保持された実効電圧より高くなると、画素は、負極性電圧を保持した時に明るくなり、正極性電圧を保持した時の暗くなる方向に変化する。なお、レジスターに格納した値が「−2」であれば、走査制御回路52は、スタートパルスDybを、タイミングTよりもクロック信号Clyの2周期分だけ早いタイミングに変更して出力する。すると、画素は、レジスターに格納した値が「−1」の場合より、負極性電圧で保持された実効電圧がさらに高められ、正極性電圧で保持された実効電圧がさらに低められる。

【0048】

一方、レジスターに格納した値が「+1」である場合、走査制御回路52は、図11に示したように、スタートパルスDybを、タイミングTよりもクロック信号Clyの1周期分だけ遅いタイミングT(+1)に変更して出力する。すると、第1フィールドの期間はクロック信号Clyの241周期分となるのに対し、第2フィールドの期間はクロック信号Clyの239周期分となる。これにより、図12に示されるように、スタートパルスDybの供給を契機とする選択により書き込まれる負極性電圧の保持期間は、スタートパルスDyaの供給を契機とする選択により書き込まれる正極性電圧の保持期間よりも短くなる。したがって、画素においては、正極性電圧で保持された実効電圧が高められ、負極性電圧で保持された実効電圧が低められる。

【0049】

正極性電圧で保持された実効電圧が負極性電圧で保持された実効電圧より高くなると、画素は、正極性電圧を保持した時に明るくなり、負極性電圧を保持した時に暗くなる方向に変化する。なお、レジスターに格納した値が「+2」であれば、走査制御回路52は、スタートパルスDybを、タイミングTよりもクロック信号Clyの2周期分だけ遅いタイミングに変更して出力する。すると、画素は、レジスターに格納した値が「+1」の場合より、正極性で保持された実効電圧がさらに高められ、負極性で保持された実効電圧がさらに低められる。

このように、走査制御回路52においてレジスターの値を変更することにより、正極性で保持された実効電圧と、負極性で保持された実効電圧との比が変更されるため、走査制御回路52は、正極性で保持された実効電圧と、負極性で保持された実効電圧との比を変更する実効電圧変更回路として機能している。

【0050】

ところで、第1対向電極108に印加される電圧LCcomは、図6に示されるように、工場出荷時において、基準電圧Vcよりも低位側に設定される。これは、画素電極をTFTで駆動するアクティブマトリクス型の電気光学装置では、いわゆるブッシュダウンが発生することや、液晶素子のリークが正極性の電圧を保持する場合と負極性の電圧を保持する場合とで異なることなどによる。仮に電圧LCcomを基準電圧Vcと一致させた場合、負極性書込による液晶素子120の実効電圧が、正極性書込による実効電圧よりも若干大きくなってしまう(TFT116がnチャネルの場合)ので、この差が相殺されるような最適値に、電圧LCcomを基準電圧Vcよりも低位側にオフセットして設定しているのである。

【0051】

本実施形態において、スタートパルスDybがタイミングTで供給される場合、第1および第2フィールドの期間は互いに等しく、各画素において液晶素子120に書き込まれた正極性電圧の保持期間と負極性電圧の保持期間とは同じとなるので、液晶素子120には直流成分が印加されないはずである。しかしながら、経年変化などによりTFTのプッシュダウン量や、液晶素子におけるリーク量が工場出荷時から変化したとき、電圧LCcomは、もはや最適値ではなくなり、液晶素子120に直流成分が印加される。すると、正極性電圧を保持している期間と負極性電圧を保持している期間とで画素110の明るさに差が生じることになる。

また、表示パネル100は、個々に特性が異なり、一定時間が経過すると、正極性電圧を保持している期間と負極性電圧を保持している期間とで画素110の明るさの差を抑えるために電圧LCcomを増やす必要がある特性のパネルと、画素110の明るさの差を抑えるために電圧LCcomを減らす必要がある特性のパネルとがある。この場合、レジスターの値を0にしても、画素110においては明るさの差が発生することになる。

【0052】

ここで図13は、表示パネル100の特性を説明するための図である。この図において横軸はレジスターの値を表し、レジスターの値が正の場合には正極性電圧の保持期間が長く、レジスターの値が負の場合には負極性電圧の保持期間が長いことを示している。また、縦軸は、一定時間経過した後に、第1対向電極108の電圧をどれだけ電圧LCcomから変更するとフリッカーが最小になるかを表している。

図13の(1)の特性のパネルは、レジスターの値が0の時において時間が経過すると液晶素子120に直流成分が印加され、フリッカーを最小にするためには第1対向電極108へ印加する電圧を電圧LCcomより大きくする必要が生じる特性のパネルである。また、図13の(2)の特性のパネルは、レジスターの値が0の時において時間が経過すると液晶素子120に直流成分が印加され、フリッカーを最小にするためには第1対向電極108に印加する電圧を電圧LCcomより小さくする必要が生じる特性のパネルである。

なお、スタートパルスDybの出力タイミングを指定するための設定値である上述した第2設定値は、図13に示した第2設定値であり、図13の(1)の特性のパネルと(2)の特性のパネルの両方について、一定時間経過後にフリッカーを最小にするには、電圧LCcomを減らす必要が生じる値である。また、スタートパルスDybの出力タイミングを指定するための設定値である上述した第1設定値は、図13に示した第1設定値であり、(1)と(2)のパネルの両方について、一定時間経過後にフリッカーを最小にするには、電圧LCComを増やす必要が生じる値である。

【0053】

電気光学装置1を備える電子機器の出荷時には、レジスターの値を0にし(即ち、正極性電圧の保持時間と負極性電圧の保持時間を同じとし)、フリッカーが知覚されないように第1対向電極108の電圧を電圧LCcomに調整する。しかし、経年変化によって液晶素子120に直流成分が印加されると、正極性電圧の保持期間と負極性電圧の保持期間との間で実効電圧の差が大きくなり、フリッカーが知覚される。

【0054】

図13の(1)の特性のパネルの場合、時間が経過して液晶素子120に直流成分が印加されると、フリッカーが最小となる最適な第1対向電極108の電圧は、電圧LCcomより大きな電圧となる。

一方、図13の(2)の特性のパネルの場合、時間が経過して液晶素子120に直流成分が印加されると、フリッカーが最小となる最適な第1対向電極108の電圧は、電圧LCcomより小さな電圧となる。

【0055】

表示パネル100を駆動した場合、レジスターの値を0にして正極性電圧の保持期間と負極性電圧の保持期間とを同じとした状態で液晶素子120に直流成分が印加されなければ、フリッカーや焼き付きが発生しない。しかし、表示パネル100の特性には、ばらつきがあり、駆動を続けると液晶素子120に直流成分が印加され、正極性電圧の保持期間と負極性電圧の保持期間とで実効電圧に差が生じる。この差が大きくなるとフリッカーが発生し、この差が大きくなった状態が続くと焼き付きが発生する。

なお、フリッカーが発生するということは、正極性の電圧を保持している状態と負極性の電圧を保持している状態とで、液晶素子の透過率が異なっているということであり、これは、冒頭で説明したように液晶素子の容量が異なっているということになる。したがって、液晶素子120について、正極性電圧の保持期間と負極性電圧の保持期間とで容量の差が小さくなるように制御すれば、正極性で保持された実効電圧と負極性で保持された実効電圧に差が小さくなり、フリッカーや焼き付きが発生しないこととなる。

なお、この制御を行うためには、液晶素子120の容量を測定する必要があるが、液晶素子の容量を直接的に検出するのは困難であるため、本実施形態では、液晶素子の容量に対応して当該液晶素子に流れる電流を測定し、測定した電流に基づいて液晶素子への印加電圧を制御する構成とした。以下、この制御を行うための構成について説明する。

【0056】

図1に示した抵抗素子R、検出回路61及びA/D変換回路56は、液晶素子120dに流れる電流を測定するためのものである。抵抗素子Rは、一端が走査制御回路52に接続され、他端が信号線107に接続されている。このため、抵抗素子Rの両端には、第2対向電極109に流れる電流に比例した電圧が現れる。検出回路61は、抵抗素子Rの両端電圧を検出して増幅するものである。A/D変換回路56は、検出回路61によって検出・増幅された電圧を、デジタルデータに変換して走査制御回路52に出力するものである。A/D変換回路56によるサンプリングレート(標本化周波数)は、検出回路61によって検出・増幅される電圧の変化に対して十分に高く設定されている。なお、デジタルデータで示される電圧を、抵抗素子Rの抵抗値、および、検出回路61による電圧増幅率でそれぞれ除算すると、第2対向電極109に流れた電流値を算出することができる。

【0057】

走査線駆動回路130は、液晶素子に流れる電流を測定するため、走査線113に供給する走査信号Gdを常時Hレベルとする。これにより、ダミー画素111のTFT116dは常時オンとなる。また、走査線駆動回路130は、抵抗素子Rを介して信号線107に基準電圧Vcを印加する。また、走査制御回路52は、測定信号線149へ図4の(a)に示した測定信号Meを供給する。

測定信号Meは、電圧V1→基準電圧Vc→電圧V2→基準電圧Vcという順番で電圧が切り替えられ、この電圧の切り替えが繰り返される。なお、電圧V1は、電圧Vw(+)と基準電圧Vcとの間の正極性の電圧であり、電圧V2は、電圧Vw(−)と基準電圧Vcとの間の負極性の電圧である。なお、測定信号Meにおいて電圧の切り替えが早いと電流の測定が困難となるため、測定信号Meの周波数は、1フレームの周波数より低い周波数(例えば10Hz〜20Hz)であるのが好ましい。つまり、測定信号Meの電圧V1(第1電圧)が画素電極118d(第2電極)に印加される期間は、画素電極118(第1電極)に正極性電圧が印加される期間より長く、測定信号Meの電圧V2(第2電圧)が画素電極118d(第2電極)に印加される期間は、画素電極118(第1電極)に負極性電圧が印加される期間より長いのが好ましい。

【0058】

表示パネル100においては、全てのダミー画素111のTFT116dがオン状態にあるため、全ての画素電極118dには、測定信号Meが供給されることになる。測定信号Meは、図4の(a)に示したように電圧が切り替わるので、この電圧の切り替えに伴って、液晶素子120dに電流が流れる。このとき、第2対向電極109と抵抗素子Rを接続する信号線107には、各液晶素子120dにそれぞれ流れた電流を総和した電流が流れる。信号線107に流れる総和電流は抵抗素子Rによって電圧に変換され、当該電圧は、走査制御回路52によって測定される。このときに測定される電圧波形(電流波形)は、図4の(b)に示されるようなものとなっていると考えられる。その理由について以下詳述する。

【0059】

まず、画素電極118dに印加される電圧が、基準電圧Vcから電圧V1に切り替わったとき、液晶素子120dの印加電圧(当該画素電極に印加された電圧と第2対向電極109に印加された電圧との差)は、当該切り替わりに対し瞬時に変化するのに対し、光学応答である透過率は、図4の(c)に示されるように、駆動電圧の変化に対して、かなり遅く変化する。すなわち、黒色に相当する透過率Tbから中間階調に相当する透過率Tgまで積分的に変化する。次に、液晶素子120dの容量は、画素電極118dと第2対向電極109との間に介在する誘電体としての液晶の分子配列状態(傾き)によって変化し、この傾きによって、透過率が決まる。このため、液晶素子120dの容量は、透過率とほぼ同様な特性で変化すると考えられる。

【0060】

液晶素子120dの容量が、図4の(c)で示される透過率と同様な特性で変化するのであれば、液晶素子120に流れる電流波形には、図4の(b)に示されるように、電圧V1の開始タイミングにおいて過渡的に流れる瞬時電流、すなわち、第2対向電極109からみて画素電極118dの電位が高くなる方向に切り替わることに伴う微分波形の第1ピークApと、電圧V1の開始タイミングからの液晶素子の容量変化(透過率変化とほぼ同特性と考えられる)に伴う第2ピークBpとが現れる。同様に、電圧V2の開始タイミングにおいて、電流波形には、第2対向電極109からみて画素電極118dの電位が低くなる方向に切り替わることに伴う微分波形の第1ピークAmと、電圧V2の開始タイミングからの液晶素子の容量変化に伴う第2ピークBmとが現れる。

【0061】

なお、液晶素子120dに流れる電流波形には、電圧V1から基準電圧Vcに切り替わったタイミングにおいては、第1ピークAmのみが現れる。同様に、電圧V2から基準電圧Vcに切り替わったタイミングにおいては、第1ピークApのみが現れる。これは、実施形態において液晶105として、印加電圧が絶対値でみて大きい方向(オン方向)に変化するときの光学応答が、小さい方向(オフ方向)へ変化するときの光学応答よりも遅く、かつ、オフ方向への光学応答は十分に速い性質を持つものを想定しているので、第2ピークBp、Bmは、オフ方向への変化であるこれらのタイミングにおいて現れない(現れにくい)からである。

【0062】

ここで、電圧V1(V2)が印加される期間において、第1ピークAP(Am)を除いた電流波形成分、すなわち図4の(b)においてハッチングで示した成分は、液晶素子120dの容量変化によって生じた成分である。液晶素子120dの容量変化は、透過率の変化であるから、第1ピークAp(Am)を除いた電流波形成分は、透過率の変化を反映したものとなる。したがって、電圧V1の印加期間において第1ピークApを除いた電流波形成分と、電圧V2の印加期間において第1ピークAmを除いた電流波形成分との差が小さくなるような制御を行えば、透過率の差が小さくなり、フリッカーが発生しないこととなる。

【0063】

この制御の一例としては、正極性で保持された実効電圧と負極性で保持された実効電圧との比を変更する制御があり、本実施形態では、正極性電圧の印加時間と負極性電圧の印加時間の比を変更する方法を採用した。また、電圧V1(V2)の印加期間において第1ピークAp(Am)を除いた電流波形成分は、第2ピークBp(Bm)の波高値として反映される。このため、本実施形態では、電圧V1(V2)の印加期間において第1ピークAp(Am)を除いた電流波形成分を、第2ピークBp(Bm)の波高値で特定する構成とした。

【0064】

なお、図4の(b)における電流波形(電圧波形)では、ゼロ点が重要となる。ここで、測定信号Meの電圧および第2対向電極109の電圧がそれぞれ時間的に一定であれば、信号線107に流れる電流はゼロのはずである。このため、測定信号Meの電圧および第2対向電極109の電圧をそれぞれ所定期間だけ一定として、この一定状態における検出回路61の出力値を電流のゼロ点として用いればよい。

【0065】

また、測定信号Meの電圧がV1である期間において第1ピークApを除いた電流波形成分(または波高値)と、測定信号Meの電圧がV2の期間において第1ピークAmを除いた電流波形成分(または波高値)とを比較するためには、液晶素子120dに電圧を印加する前の条件を揃えた状態が望ましい。このため、本実施形態では、画素電極118dに、正極性の電圧V1を印加する前の期間、および、負極性の電圧V2を印加する前の期間において、それぞれリセット電圧として、第2対向電極109と等しい基準電圧Vcを画素電極118dに印加して、液晶素子120dの駆動電圧をゼロに揃えることにした。

【0066】

なお、例えばリセット電圧として、ノーマリーブラックモードの白色に相当する電圧Vw(+)、Vw(−)を画素電極118dに印加して、液晶素子120dの印加電圧を高い状態で揃えてしまうと、変化方向は、光学応答が十分に速いオフ方向になるので、第2ピークが現れにくくなる。換言すれば、リセット電圧として、液晶素子120dの印加電圧を小さい状態で揃える電圧を画素電極118dに印加すると、オン方向への変化となるので、第2ピークが特定しやすくなるのである。この意味において、リセット電圧としては、画素電極118に黒色に相当する電圧Vb(+)、Vb(−)としてもよい。

【0067】

次に走査制御回路52の動作について説明する。図14は、走査制御回路52が行う処理の流れを示したフローチャートである。まず走査制御回路52は、表示パネル100の駆動を開始するとスタートパルスDybの出力タイミングを指定するためにレジスターの値を「0」にする(ステップSA1)。走査制御回路52は、外部上位装置から垂直同期信号Vs、水平同期信号Hs及びクロック信号Clkが走査制御回路52に供給され、画像データVdがデータ信号生成回路54に供給されると、供給された各信号に基づいて表示パネル100を駆動する。走査制御回路52は、レジスターに格納されている値が「0」であるため、スタートパルスDybをタイミングTで出力する。また、走査制御回路52は、走査信号Gdと測定信号Meを出力する(ステップSA2)。

【0068】

次に、走査制御回路52は、A/D変換回路56によって変換されたデジタルデータを処理し、第2ピークBpの波高値と第2ピークBmの波高値を取得する(ステップSA3)。具体的には、走査制御回路52は、測定信号Meにおいて電圧V1の印加開始タイミングから2番目に現れる第2ピークBpの波高値(第2ピーク値)、すなわち図4の(b)に示した+Iaに相当する値を取得する。また、走査制御回路52は、測定信号Meにおいて電圧V2の印加開始タイミングから2番目に現れる第2ピークBmの波高値(第2ピーク値)、すなわち図4の(b)に示した−Icに相当する値を取得する。次に走査制御回路52は、第2ピークBpの波高値と第2ピークBmの波高値の差を算出し、算出した値を電流差Aとする(ステップSA4)。

【0069】

次に走査制御回路52は、予め定められた一定時間が経過したか否か判断する(ステップSA5)。なお、本実施形態では、この一定時間は10分とするが、10分に限定されうるものではなく、10分を超える時間や10分未満の時間であってもよい。走査制御回路52は、一定時間が経過していない場合(ステップSA5でNO)、一定時間が経過するのを待つ。走査制御回路52は、一定時間が経過したと判断すると(ステップSA5でYES)、A/D変換回路56によって変換されたデジタルデータを処理し、第2ピークBpの波高値と第2ピークBmの波高値を取得する(ステップSA6)。走査制御回路52は、ステップSA6の処理を終えると、第2ピークBpの波高値と第2ピークBmの波高値の差を算出し、算出した値を電流差Bとする(ステップSA7)。そして、走査制御回路52は、ΔI=|電流差A−電流差B|の演算を行い、電流差Aと電流差Bの差を表すΔIを算出する(ステップSA8)。

【0070】

次に走査制御回路52は、ステップSA8で算出したΔIが予め定められた閾値以上であるか否か判断する。なお、この閾値は、本実施形態においてはフリッカーが知覚される時の値より小さい値に設定されている。走査制御回路52は、ΔIの値が閾値未満である場合(ステップSA9でNO)、フリッカーが発生していないと判断し、処理の流れをステップSA5へ戻す。

また、走査制御回路52は、ΔIの値が閾値以上である場合(ステップSA9でYES)、ステップSA6で取得した第2ピークBpの波高値と第2ピークBmの波高値に基づいて、前述のレジスターの値を設定する。

【0071】

ここで、例えば表示パネル100が図13の(2)の特性の表示パネルである場合、第2ピークBpの波高値が第2ピークBmの波高値より大きくなっている。つまり、正極性電圧で保持された実効電圧が負極性電圧で保持された実効電圧より高くなっている。

このため、走査制御回路52は、ステップSA6で取得した波高値が、第2ピークBpの波高値>第2ピークBmの波高値の関係にある場合(ステップSA10でYES)、レジスターの値を第1設定値にする(ステップSA11)。レジスターに第1設定値が格納されると、正極性電圧の印加時間が短くなり、負極性電圧の印加時間が長くなる。これにより、画素110においては、負極性電圧で保持された実効電圧が高くなり、正極性電圧で保持された実効電圧が低くなるため、時間の経過と共に第2ピークBmの波高値が第2ピークBpの波高値より大きくなる方向へ変化していくこととなる。

【0072】

走査制御回路52は、ステップSA11の処理が終了すると処理の流れをステップSA5へ戻し、再び一定時間が経過するのを待つ。走査制御回路52は、ステップSA5でYESと判断すると、ステップSA6からステップSA8の処理を行う。次に走査制御回路52は、ステップSA9の処理を行う。レジスターに第1設定値が格納され、時間が経過して第2ピークBmの波高値が増大し、ΔIが閾値以上である場合(ステップSA9でYES)、ステップSA6で取得した第2ピークBpの波高値と第2ピークBmの波高値に基づいて、前述のレジスターの値を設定する。

ここでは、前述のように、負極性電圧で保持された実効電圧が高くなり、正極性電圧で保持された実効電圧が低くなっているため、ステップSA6で取得した波高値は、第2ピークBpの波高値<第2ピークBmの波高値の関係にある。この場合、走査制御回路52は、ステップSA10でNOと判断し、レジスターの値を第2設定値にする(ステップSA12)。レジスターに第2設定値が格納されると、負極性電圧の印加時間が短くなり、正極性電圧の印加時間が長くなる。これにより、画素110においては、正極性電圧で保持された実効電圧が高くなり、負極性電圧で保持された実効電圧が低くなるため、時間の経過と共に第2ピークBpの波高値が第2ピークBmの波高値より大きくなる方向へ変化していくこととなる。走査制御回路52は、ステップSA10の処理が終了すると処理の流れをステップSA3へ戻し、上述した処理を繰り返す。

【0073】

なお、表示パネル100が、図12の(1)の特性のパネル、つまり、レジスターの値を0にした場合に負極性電圧で保持された実効電圧が高くなり、正極性電圧で保持された実効電圧が低くなるパネルである場合、レジスターを0にして表示パネル100を駆動すると、時間が経過すると第2ピークBmの波高値が第2ピークBpの波高値より大きくなる方向へ変化していくこととなる。

この場合、走査制御回路52は、ステップSA6で取得した波高値が、第2ピークBpの波高値<第2ピークBmの波高値の関係にあると(ステップSA10でNO)、レジスターの値を第2設定値にする(ステップSA12)。レジスターに第2設定値が格納されると、負極性電圧の印加時間が短くなり、正極性電圧の印加時間が長くなる。これにより、画素110においては、正極性電圧で保持された実効電圧が高くなり、負極性電圧で保持された実効電圧が低くなるため、時間の経過と共に第2ピークBpの波高値が第2ピークBmの波高値より大きくなる方向へ変化していくこととなる。

【0074】

走査制御回路52は、ステップSA12の処理が終了すると処理の流れをステップSA5へ戻し、再び一定時間が経過するのを待つ。走査制御回路52は、ステップSA5でYESと判断すると、ステップSA6からステップSA8の処理を行う。

次に走査制御回路52は、ステップSA9の処理を行う。レジスターに第2設定値が格納され、時間が経過して第2ピークBpの波高値が増大し、ΔIが閾値以上である場合(ステップSA9でYES)、ステップSA6で取得した第2ピークBpの波高値と第2ピークBmの波高値に基づいて、前述のレジスターの値を設定する。ここでは、前述のように正極性電圧で保持された実効電圧が高くなり、負極性電圧で保持された実効電圧が低くなっているため、ステップSA6で取得した波高値が、第2ピークBpの波高値>第2ピークBmの波高値の関係にある。この場合、走査制御回路52は、ステップSA10でYESと判断し、レジスターの値を第1設定値にする(ステップSA11)。レジスターに第1設定値が格納されると、正極性電圧の印加時間が短くなり、負極性電圧の印加時間が長くなる。これにより、画素110においては、負極性電圧で保持された実効電圧が高くなり、正極性電圧で保持された実効電圧が低くなるため、時間の経過と共に第2ピークBmの波高値が第2ピークBpの波高値より大きくなる方向へ変化していくこととなる。

走査制御回路52は、ステップSA11の処理が終了すると処理の流れをステップSA3へ戻し、上述した処理を繰り返す。

【0075】

本実施形態によれば、液晶素子120に直流成分が印加されることにより正極性の電圧を印加した時と負極性の電圧を印加した時とで実効電圧に差が生じても、実効電圧の差が少なくなるように正極性電圧の印加時間と負極性電圧の印加時間が制御されるので、フリッカーや焼き付きの発生を抑えることができる。

【0076】

[電子機器]

次に、上述した実施形態に係る電気光学装置を用いた電子機器の例について説明する。図15は、上述した電気光学装置1の表示パネル100をライトバルブとして用いた3板式プロジェクターの構成を示す平面図である。プロジェクター2100の内部には、ハロゲンランプ等の白色光源を備えたランプユニット2102が設けられている。このプロジェクター2100において、ランプユニット2102から射出された光は、内部に配置された3枚のミラー2106および2枚のダイクロイックミラー2108によってR(赤)、G(緑)、B(青)の3原色に分離されて、各原色に対応するライトバルブ100R、100Gおよび100Bにそれぞれ導かれる。なお、B色の光は、他のR色やG色と比較すると、光路が長いので、その損失を防ぐために、入射レンズ2122、リレーレンズ2123および出射レンズ2124からなるリレーレンズ系2121を介して導かれる。

【0077】

ここで、ライトバルブ100R、100Gおよび100Bの構成は、上述した実施形態における表示パネル100と同様であり、外部上位装置(図示省略)から供給されるR、G、Bの各色に対応する画像データVdでそれぞれ駆動されるものである。ライトバルブ100R、100G、100Bによってそれぞれ変調された光は、ダイクロイックプリズム2112に3方向から入射する。そして、このダイクロイックプリズム2112において、R色およびB色の光は90度に屈折する一方、G色の光は直進する。したがって、各色の画像が合成された後、レンズユニット2114によって正転拡大投影されるので、スクリーン2120には、カラー画像が表示されることとなる。

【0078】

なお、ライトバルブ100R、100Bの透過像は、ダイクロイックプリズム2112により反射した後に投射されるのに対し、ライトバルブ100Gの透過像はそのまま投射されるので、ライトバルブ100R、100Bにより形成される画像と、ライトバルブ100Gにより形成される画像とは左右反転の関係にある。

【0079】

また、電子機器としては、図15を参照して説明した他にも、リアプロジェクション型のテレビジョンや、直視型、例えば携帯電話や、パーソナルコンピューター、ビデオカメラのモニター、カーナビゲーション装置、ページャー、電子手帳、電卓、ワードプロセッサー、ワークステーション、テレビ電話、POS端末、ディジタルスチルカメラ、タッチパネルを備えた機器等などが挙げられる。そして、これらの各種の電子機器に対して、本発明に係る電気光学装置が適用可能なのは言うまでもない。

【0080】

[変形例]

以上、本発明の実施形態について説明したが、本発明は上述した実施形態に限定されることなく、他の様々な形態で実施可能である。例えば、上述の実施形態を以下のように変形して本発明を実施してもよい。なお、上述した実施形態および以下の変形例は、各々を組み合わせてもよい。

【0081】

(変形例1)

上述した実施形態では、液晶素子120において保持される電圧の実効値がゼロ(またはゼロ近傍)に近ければ、黒色を表示するノーマリーブラックモードとしたが、液晶素子120において保持される電圧の実効値がゼロ(またはゼロ近傍)に近ければ白色を表示するノーマリーホワイトモードとしても良い。

【0082】

(変形例2)

上述した実施形態においては、走査線113は常時Hレベルであり、測定信号Meが常時出力されているが、ステップSA3とステップSA6で波高値を取得する期間には、走査線113をHレベルとし、測定信号Meを出力するようにし、波高値を取得する期間以外においては走査線113をLレベルとし、測定信号Meを出力しないようにしてもよい。

【0083】

(変形例3)

上述した実施形態においては、電圧V1は電圧Vw(+)と基準電圧Vcとの間の正極性の電圧であり、電圧V2は、電圧Vw(−)と基準電圧Vcとの間の負極性の電圧であるが、上述したプロジェクター2100のように表示パネル100を透過型とする場合、電圧V1を電圧Vw(+)にし、電圧V2をVw(−)としてもよい。また、表示パネル100を反射型とする場合、電圧V1を電圧Vb(+)にし、電圧V2をVb(−)としてもよい。

【0084】

(変形例4)

上述した実施形態においては、正極性電圧の保持時間と負極性電圧の保持時間との比を変更することにより、正極性電圧で保持された実効電圧と正極性電圧で保持された実効電圧との比を変更し、ΔIが一定の範囲内に収まるようにしているが、ΔIを一定の範囲内に収める方法は、上述した実施形態の方法に限定されるものではない。

例えば、走査制御回路52は、表示パネル100の駆動を開始すると、階調が同じであれば正極性のデータ信号Vidと負極性のデータ信号Vidを基準電圧Vcを中心に対象の関係にする。また、走査制御回路52は、ステップSA11においては、正極性電圧の印加時間と負極性電圧の印加時間を変更する処理に替えて、正極性電圧と負極性電圧の電圧比を変更する。具体的には、走査制御回路52は、階調値が同じであれば、基準電圧Vcからのデータ信号Vidの振幅を正極性側を小さく、負極性側を大きくする。また、走査制御回路52は、ステップSA12においては、例えば階調値が同じであれば、基準電圧Vcからのデータ信号Vidの振幅を、正極性側を大きく、負極性側を小さくする。この変形例においても、正極性電圧の実効電圧と負極性電圧の実効電圧との比を変更することができる。

【0085】

(変形例5)

上述した実施形態では、ダミー画素111は、表示領域A1を囲むように表示領域A1の周辺に設けられているが、ダミー画素111の配置位置は、上述した実施形態の配置に限定されるものではない。例えば、1行1列目〜1行640列目の各画素110に隣り合うように1行目の画素に沿ってダミー画素111を設け、480行1列目〜480行640列目の各画素110と隣り合うように480行目の画素に沿ってダミー画素111を設けるようにしてもよい。また、1行1列目〜480行1列目の各画素110に隣り合うように1列目の画素に沿ってダミー画素111を設け、1行640列目〜480行640列目の各画素110に隣り合うように640列目の画素に沿ってダミー画素111を設けるようにしてもよい。要するに、ダミー画素111の配置位置及び数は図2に示した配置位置及び数に限定されず、表示領域A1の周辺にダミー画素111が設けられていればよい。なお、ダミー画素111の配置は、表示領域A1の一辺にのみ沿って配置する構成であってもよいが、表示領域A1の二辺以上に沿ってダミー画素111を配置するのが好ましく、さらに表示領域A1の4つの辺に沿ってダミー画素111を配置するのがより好ましい。ダミー画素111を二辺以上に沿って配置した場合、表示領域A1の一辺にのみ沿って配置した構成と比較すると、電流の測定に係るダミー画素111の数が増えるため、ダミー画素111毎の特性の違いの影響が少なくなる(異なる場所の画素の特性が得られる)。

【0086】

(変形例6)

上述した実施形態においては、ステップSA8でΔIを算出し、ΔIが閾値以上であった場合、正極性電圧を保持した時の実効電圧と負極性電圧を保持した時の実効電圧の差が少なくなるように正極性電圧の印加時間と負極性電圧の印加時間を変更しているが、印加時間を制御する処理の流れは図14に示したものに限定されるものではなく、例えば、図16に示した処理の流れとしてもよい。図16の処理は、電流差A、B及びΔIを算出するのではなく、第2ピークBpの波高値と第2ピークBmの波高値の差を求め、この波高値の差に基づいてレジスターの値を変更する点が前述の実施形態と異なる。

具体的には、ステップSB1〜SB2の処理は、ステップSA1〜SA2の処理と同じである。また、ステップSB3〜SB4の処理は、ステップSA5〜SA6の処理と同じである。本変形例においては、ステップSB4で取得した第2ピークBpの波高値と第2ピークBmの波高値の差が予め定められた閾値以上である場合(ステップSB5でYES)、レジスターの値を変更する処理を行う。なお、ステップSB6〜SB8の処理は、ステップSA10〜SA12の処理と同じである。

【0087】

(変形例7)

上述した実施形態においては、ダミー画素111には測定信号Meが供給されているが、第2ピークBpの波高値と第2ピークBmの波高値を取得する期間以外については、ダミー画素111の階調を隣り合う画素110の階調と同じ階調としてもよい。

図17は、本変形例に係るダミー画素111と画素110の構成を示した図である。本変形例においては、ダミー画素111は、スイッチSW1〜SW3を備えている。スイッチSW1の入力端の一方は、1行目の走査線112から分岐した走査線112aに接続されており、他方の入力端は、走査線113に接続され、出力端はTFT116dのゲート電極に接続されている。また、スイッチSW2の入力端の一方は、1列目のデータ線114に接続され、他方の入力端は、測定信号線149に接続され、出力端は、TFT116dのソース電極に接続されている。また、スイッチSW3の入力端の一方は、第1対向電極108に接続され、他方の入力端は、第2対向電極109に接続され、出力端は、TFT116dのドレイン電極に接続されている。

【0088】

この構成においては、ステップSA3とステップSA6で波高値を取得する際には、予め定められた期間、SW1の出力端は、走査線113に接続され、SW2の出力端は、測定信号線149に接続され、SW3の出力端は、第2対向電極109に接続される。これにより、ステップSA3とステップSA6で第2ピークBpの波高値と第2ピークBmの波高値を取得する期間には、ダミー画素111には測定信号Meが供給される。

一方、第2ピークBpの波高値と第2ピークBmの波高値を取得する期間ではない場合、SW1の出力端は、走査線112aに接続され、SW2の出力端は、データ線114に接続され、SW3の出力端は、第1対向電極108に接続される。これにより、第2ピークBpの波高値と第2ピークBmの波高値を取得する期間ではない場合、1行目の画素110に隣り合うダミー画素111には画素110と同じデータ信号Vidが供給され、1行目の画素110と、1行目の画素110に隣り合うダミー画素111の階調は、同じ階調になる。

【0089】

(変形例8)

上述した実施形態においては、第1対向電極108と第2対向電極109とが絶縁されているが、第1対向電極108と第2対向電極109とを電気的に接続し、一つのコモン電極としてもよい。この構成においては、第1対向電極108には電圧LCcomが印加される。本変形例によれば、表示パネル100と制御回路50を接続する配線の数を上述した実施形態より減らすことができる。

【0090】

(変形例9)

上述した実施形態においては、測定信号Meと電圧設定信号Vsetは走査制御回路52から出力されているが、測定信号Meと電圧設定信号Vsetを出力する構成は、この構成に限定されるものではなく、例えば、図18に示した構成としてもよい。

図18は、本発明の変形例に係る電気光学装置1Aの構成を示した図である。電気光学装置1Aは、測定信号回路62と、対向電極駆動回路63を備えている。測定信号回路62は、測定信号Meを出力する回路であり、測定信号線149に接続されている。測定信号回路62は、走査制御回路52により制御されて測定信号Meを出力する。また、対向電極駆動回路63は、第2対向電極109に接続されている。対向電極駆動回路63は、走査制御回路52により制御されて電圧設定信号Vsetを出力する。

本変形例においても、測定信号線149に測定信号を供給し、第2対向電極109に電圧Vsetを印加することができる。なお、測定信号線149をデータ線駆動回路140に接続し、データ線駆動回路140から測定信号Meを測定信号線149に供給する構成としてもよい。

【符号の説明】

【0091】

1,1A…電気光学装置、50…制御回路、52…走査制御回路、54…データ信号生成回路、56…A/D変換回路、61…検出回路、62…測定信号回路、63…対向電極駆動回路、100…表示パネル、105…液晶、107…信号線、108…第1対向電極、109…第2対向電極、110…画素、111…ダミー画素、112…走査線、114…データ線、116,116d…TFT、118,118d…画素電極、120,120d…液晶素子、130…走査線駆動回路、140…データ線駆動回路、142…サンプリング信号出力回路、146…TFT、148…画像信号線、149…測定信号線、2100…プロジェクター、2102…ランプユニット、2106…ミラー、2108…ダイクロイックミラー、2112…ダイクロイックプリズム、2114…レンズユニット、2120…スクリーン、2121…リレーレンズ系、2122…入射レンズ、2123…リレーレンズ、2124…出射レンズ、SW1〜SW3…スイッチ

【技術分野】

【0001】

本発明は、焼き付きやフリッカーが発生するのを抑える技術に関する。

【背景技術】

【0002】

液晶表示装置では、液晶素子を交流駆動するのが一般的である。ただし、交流駆動するだけでは、液晶に直流成分が印加される場合がある。具体的には、液晶表示装置においては、液晶層を挟む画素電極基板と対向電極基板は物理的な構造が異なっており、対向電極から見て高位である正極性電圧が画素電極基板に印加された場合と、対向電極から見て低位である負極性電圧が画素電極基板に印加された場合とで、電極と配向膜との界面や配向膜と液晶層などの界面における抵抗値が異なってしまう。これにより液晶表示装置においては、正極性電圧の印加時と負極性電圧の印加時とで液晶層への実効電圧が等しくても電流量が異なることとなり、電荷の移動量に非対象性が生じる。また、この電流量の非対称性により、液晶内部の電荷に偏りが生じ、電荷の偏りによって内部電界が発生する。この内部電界の影響により、実際に液晶層に印加される電圧は駆動電圧の極性によって非対称となり、液晶層に直流電圧成分が印加される。

【0003】

液晶層にこの直流電圧成分が印加されるとフリッカーが生じることとなるため、フリッカーを抑えるために対向電極の電圧を調整する技術がある。例えば特許文献1に開示されている調整回路は、液晶素子に正極性電圧を印加した時の輝度と負極性電圧を印加した時の輝度とを光センサーで測定し、正極性電圧を印加した時の輝度と負極性電圧を印加した時の輝度と差に基づいて対向電極の電圧を調整する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平8−286169号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

ところで、特許文献1の調整回路でフリッカーが最小となるように調整しても、経年変化によって液晶素子へ直流電圧成分が印加され、焼き付きという問題が発生してしまう。この場合、オペレータが再度調整回路を操作して調整回路に対向電極の電圧調整を行わせることとなり、手間がかかる。

本発明は、上述した事情に鑑みてなされたものであり、その目的の1つは、焼き付きやフリッカーが発生しないようにすることにある。

【課題を解決するための手段】

【0006】

上記目的を達成するために、本発明に係る液晶表示装置は、第1電極とコモン電極とにより液晶を挟持した表示画素と、所定の基準電圧よりも高位側で前記表示画素の階調に応じた正極性電圧と、所定の基準電圧よりも低位側で前記階調に応じた負極性電圧とを時間的に交互に前記第1電極へ印加し、前記コモン電極に所定の電圧を印加する駆動回路と、第2電極と前記コモン電極により液晶を挟持したダミー画素と、前記基準電圧よりも高位側の第1電圧と低位側の第2電圧とを時間的にずらして印加する測定信号を前記第2電極へ供給する測定信号回路と、前記第2電極に前記第1電圧が印加された後に前記コモン電極に流れる電流のうち当該第1電圧の印加による瞬時電流を除いた第1電流と、前記第2電極に前記第2電圧が印加された後に前記コモン電極に流れる電流のうち当該第2電圧の印加による瞬時電流を除いた第2電流とに基づいて、前記駆動回路により前記第1電極に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比を変更する制御回路とを有する。

【0007】

本発明によれば、測定信号回路から第2電極に第1電圧が印加された後にコモン電極に流れる電流のうち当該第1電圧の印加による瞬時電流を除いた第1電流と、第2電極に第2電圧が印加された後にコモン電極に流れる電流のうち当該第2電圧の印加による瞬時電流を除いた第2電流とに基づいて、表示画素の第1電極に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比が変更するため、液晶に直流電圧成分が印加されるのを抑え、液晶表示装置において、焼き付きやフリッカーが発生しないようにすることができる。

【0008】

本発明においては、前記制御回路は、前記第1電流と前記第2電流との差が予め定められた閾値未満となるように、前記第1電極に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比を変更する構成としてもよい。

この構成によれば、ダミー画素の液晶に第1電圧を印加した時に流れた第1電流と第2電圧を印加した時に流れた第2電流との差に基づいて、第1電極に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比が変更され、焼き付きやフリッカーが発生しないようにすることができる。

【0009】

また、本発明においては、前記制御回路は、前記第1電流と前記第2電流との差が予め定められた閾値未満となるように、前記第1電極に印加する正極性電圧の印加時間と負極性電圧の印加時間を変更する構成としてもよい。

この構成によれば、正極性電圧の実効電圧と、負極性電圧の実効電圧とが変更され、焼き付きやフリッカーが発生しないようにすることができる。

【0010】

また、本発明においては、前記制御回路は、前記第1電流と前記第2電流との差が予め定められた閾値未満となるように、前記第1電極に印加する正極性電圧と負極性電圧の電圧比を変更する構成としてもよい。

この構成によれば、正極性電圧と負極性電圧の比を変更することにより、正極性電圧の実効電圧と、負極性電圧の実効電圧とが変更され、焼き付きやフリッカーが発生しないようにすることができる。

【0011】

また、本発明においては、前記測定信号は、前記第1電圧を印加する期間と前記第2電圧を印加する期間との間に前記第2コモン電極と同じ第3電圧を前記第2電極へ印加する信号である構成としてもよい。

この構成によれば、第1電圧を印加した時と第2電圧を印加した時に液晶の光学応答が遅くなるので、第1電流と第2電流を得易くなる。

【0012】

また、本発明においては、前記コモン電極は、前記第1電極との間に前記液晶を挟持する第1コモン電極と、前記第2電極との間に前記液晶を挟持する第2コモン電極とで構成され、前記第1コモン電極と前記第2コモン電極は互いに絶縁されており、前記制御回路は、前記第2電極に前記第1電圧が印加された後に前記第2コモン電極に流れる電流のうち当該第1電圧の印加による瞬時電流を除いた電流と、前記第2電極に前記第2電圧が印加された後に前記第2コモン電極に流れる電流のうち当該第2電圧の印加による瞬時電流を除いた電流とに基づいて、前記駆動回路により前記第1電極に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比を変更する構成としてもよい。

この構成によれば、表示画素とは別にダミー画素の液晶に流れる電流を測定することができる。

【0013】

また、本発明においては、前記測定信号により前記第1電圧が前記第2電極へ印加される期間は、前記第1電極へ前記正極性電圧が印加される期間より長く、前記測定信号により前記第2電圧が前記第2電極へ印加される期間は、前記第1電極へ前記負極性電圧が印加される期間より長い構成としてもよい。

この構成によれば、第1電流と第2電流を得る時間を確保し、第1電流と第2電流を得易くなる。

【0014】

また、本発明においては、前記ダミー画素は、予め定められた期間においては前記測定信号回路から前記測定信号が前記第2電極へ供給され、当該期間外においては、当該ダミー画素に隣り合う前記表示画素に印加される正極性電圧と負極性電圧とが時間的に交互に前記駆動回路から前記第2電極へ印加される構成としてもよい。

この構成によれば、ダミー画素を隣り合う表示画素と同じ階調にし、ダミー画素を目立たないようにすることができる。

【0015】

なお、本発明は、電気光学装置のみならず、液晶表示装置の駆動方法としても、当該液晶表示装置を有する電子機器としても概念することが可能である。

【図面の簡単な説明】

【0016】

【図1】電気光学装置1の構成を示したブロック図。

【図2】表示パネル100の構成を示した図。

【図3】画素110とダミー画素111の構成を示した図。

【図4】測定信号Meの波形、検出回路61で測定される電圧の波形及び液晶の透過率の変化を示した図。

【図5】走査線駆動回路130の動作を示す図。

【図6】データ信号の波形例を示した図。

【図7】データ信号の波形例を示した図。

【図8】表示領域A1における画素の書き込みの推移を示す図。

【図9】走査線駆動回路130の動作を示す図。

【図10】表示領域A1における画素の書き込みの推移を示す図。

【図11】走査線駆動回路130の動作を示す図。

【図12】表示領域A1における画素の書き込みの推移を示す図。

【図13】表示パネル100の特性を示した図。

【図14】走査制御回路52の処理の流れを示したフローチャート。

【図15】実施形態に係る電気光学装置1を用いたプロジェクターの構成を示す図。

【図16】変形例に係る走査制御回路52の処理の流れを示したフローチャート。

【図17】変形例に係る画素110とダミー画素111の構成を示した図。

【図18】変形例に係る電気光学装置1Aの構成を示した図。

【発明を実施するための形態】

【0017】

[実施形態]

まず、この発明の一実施形態の概略について説明する。画素電極と対向電極(コモン電極)とで液晶を挟時した液晶素子は、焼き付きや劣化を防止するために、基準電圧よりも高位側の正極性電圧と、低位側の負極性電圧とを画素電極に交互に印加する一方、対向電極に所定電圧を印加して、交流で駆動する。このとき、正極性で電圧を印加・保持する期間と、負極性で電圧を印加・保持する期間とにおいて、液晶素子の透過率(または反射率)が異なっていると、フリッカー(ちらつき、明滅)として知覚される。

【0018】

液晶分子は、画素電極および対向電極の間で生じる電界によって、その傾きが変化し、これによって、液晶素子を通過する光の偏光状態が規定されて、液晶素子の透過率(または反射率)が変化する。液晶は、誘電異方性を有するので、正極性電圧の保持期間と負極性電圧の保持期間とにおいて、液晶素子の透過率が異なっているということは、液晶分子の傾きが異なっているということであり、これは、液晶素子の容量が異なっているということにほかならない。

したがって、液晶素子の容量を正極性電圧の保持期間と負極性電圧の保持期間との各々について検出するとともに、その差が小さくなるように、液晶素子への印加電圧を制御すれば、フリッカーを低減することができるはずである。ただし、液晶素子の容量を直接的に検出するのは困難である。このため、本実施形態では、後述するように当該液晶素子の容量に対応して当該液晶素子に流れる電流を測定し、測定した電流に基づいて液晶素子への印加電圧を制御する構成とした。本実施形態は、これを具現化したものであり、以下、その詳細について説明する。

【0019】

図1は、本発明の一実施形態に係る電気光学装置1(液晶表示装置)の構成を示したブロック図である。図1に示したように、電気光学装置1は、表示パネル100と制御回路50に大別される。このうち、表示パネル100の動作等を制御する制御回路50は、走査制御回路52、データ信号生成回路54、A/D変換回路56、検出回路61及び抵抗素子Rを含み、例えばFPC(flexible printed circuit)基板によって表示パネル100に接続される。

【0020】

制御回路50は、外部上位回路(図示省略)から供給される垂直同期信号Vs、水平同期信号Hsおよびクロック信号Clkにしたがって表示パネル100の各部を制御する。また、制御回路50は、外部上位回路から供給されるデジタルの画像データVdをアナログのデータ信号Vidに変換し、データ信号Vidを表示パネル100へ供給する。なお、制御回路50の詳細については後述する。

【0021】

図2は、表示パネル100の構成を示した図である。表示パネル100は、液晶を用いて画像の表示を行うものであり、画像の表示を行う表示領域A1と、表示領域A1の周辺に設けられたダミー画素領域A2を備え、ダミー画素領域A2の周辺に走査線駆動回路130およびデータ線駆動回路140が配置された周辺回路内蔵型となっている。

表示領域A1には、480行の走査線112が図において横方向(X方向)に設けられる一方、640列のデータ線114が縦方向(Y方向)に設けられている。そして、これらの走査線112とデータ線114との交差の各々に対応するように画素110(表示画素)がそれぞれ設けられている。なお、本実施形態では、表示領域A1において画素110が縦480行×横640列でマトリクス状に配列されることになるが、本発明をこの配列に限定する趣旨ではない。

また、ダミー画素領域A2には、表示領域A1を囲むようにして複数のダミー画素111が配置されており、各画素111には表示領域A1を囲むように設けられた走査線113と測定信号線149が接続されている。具体的には、本実施形態においては、ダミー画素111は、1行目の画素110の隣に1行×640列で設けられ、480行目の画素110の隣に1行×640列で設けられている。またダミー画素111は、1列目の画素110の隣に1列×480行で設けられ、640列目の画素110の隣に1列×480行で設けられている。

【0022】

走査線駆動回路130は、制御回路50により制御され、垂直走査期間にわたって走査信号G1、G2、G3、・・・、G480を、それぞれ1、2、3、・・・480行目の走査線112に供給するものである。走査線駆動回路130は、走査線112を予め定められた順番で水平走査期間毎に選択し、選択した走査線112へ供給する走査信号を電圧Vddに相当するHレベル(選択電圧)とする。

また、走査線駆動回路130は、制御回路50により制御され、走査線113へ走査信号Gdを供給する。走査線駆動回路130は、液晶に流れる電流を測定する際には走査信号Gdを電圧Vddに相当するHレベルにする。

【0023】

データ線駆動回路140は、サンプリング信号出力回路142と、各データ線114に対応して設けられるnチャネル型の薄膜トランジスタ(thin film transistor、以下「TFT」と称する)146とを備えている。サンプリング信号出力回路142は、制御回路50により制御され、各TFT146に対応してサンプリング信号S1、S2、S3、・・・、S640を出力するものである。サンプリング信号出力回路142は、図6,7に示したように水平走査期間(H)に供給されるスタートパルスDxを、クロック信号Clxのレベルが遷移する毎に順次シフトし、サンプリング信号S1、S2、S3、・・・、S640として出力する。

【0024】

TFT146は、1〜640列のデータ線114の各々に設けられ、それぞれサンプリングスイッチとして機能するものであり、そのドレイン電極は、データ線114の一端に接続されている。TFT146のソース電極は、画像信号線148に接続される。また、TFT146のゲート電極には、サンプリング信号出力回路142からのサンプリング信号が供給される。例えば、左から数えて2番目のTFT146は、2列目のデータ線114に対応するので、このデータ線114に対応するTFT146のゲート電極には、サンプリング信号S2が供給される。サンプリング信号S2がHレベルになると、TFT146がソース・ドレイン電極間で導通(オン)状態となるので、データ線114は、画像信号線148に接続されることになる。

【0025】

次に、画素110とダミー画素111について説明する。図3は、画素110とダミー画素111の構成を示した図であり、1行1列目の画素110、2行1列目の画素110、1行1列目の画素110に隣り合うダミー画素111、2行1列目の画素110に隣り合うダミー画素111の構成を示した図である。

各画素110は互いに同一構成であり、nチャネル型のTFT116と液晶素子120とを有する。i行j列目の画素110においては、TFT116のゲート電極はi行目の走査線112に接続される一方、そのソース電極はj列目のデータ線114に接続され、ドレイン電極は、液晶素子120の一端である画素電極118(第1電極)に接続されている。また、液晶素子120の他端は、第1対向電極108(第1コモン電極)に接続されている。この第1対向電極108は、全ての画素110にわたって共通であって、時間的に一定の電圧LCcomが印加されている。なお、iは、画素110が配列する行を一般的に示す場合の記号であって、本実施形態では、それぞれ1以上480以下を満たす整数である。また、jは、画素110が配列する列を一般的に示す場合の記号であって、本実施形態では、それぞれ1以上640以下を満たす整数である。例えば、1行1列目の画素110において、TFT116のゲート電極は1行目の走査線112に接続される一方、そのソース電極は1列目のデータ線114に接続され、そのドレイン電極は液晶素子120の一端である画素電極118に接続されている。

【0026】

また、各ダミー画素111は各々同一構成であり、nチャネル型のTFT116dと液晶素子120dとを有する。TFT116dのゲート電極は走査線113に接続される一方、そのソース電極は測定信号線149に接続され、そのドレイン電極は液晶素子120dの一端である画素電極118d(第2電極)に接続されている。また、液晶素子120dの他端は、第2対向電極109(第2コモン電極)に接続されている。この第2対向電極109は、全てのダミー画素111にわたって共通であり、信号線107により制御回路50の抵抗素子Rに接続されている。また、第2対向電極109は、第1対向電極108とは絶縁されている。

【0027】

なお、この表示パネル100は、特に図示しないが、素子基板と対向基板との一対の基板が一定の間隙を保って貼り合わせられるとともに、この間隙に液晶が封止された構成となっている。このうち、素子基板には、走査線112,113、データ線114、TFT116,116d,146、画素電極118,118d及び測定信号線149が走査線駆動回路130やデータ線駆動回路140とともに形成される。一方、対向基板には第1対向電極108と第2対向電極109が形成されており、これらの電極形成面が互いに対向するように一定の間隙を保って貼り合わせられている。なお、画素110に対しては第1対向電極108が対向し、ダミー画素111に対しては第2対向電極109が対向する。このため、本実施形態において液晶素子120は、画素電極118と第1対向電極108とが液晶105を挟持することによって構成され、液晶素子120dは、画素電極118dと第2対向電極109とが液晶105を挟持することによって構成されることになる。

【0028】

本実施形態では、液晶素子120,120dにおいて保持される電圧の実効値がゼロ(またはゼロ近傍)に近ければ、液晶素子120,120を通過する光の透過率が最小となって黒色表示になる一方、保持される電圧の実効値が大きくなるにつれて透過する光量が増大して、ついには透過率が最大の白色表示になるノーマリーブラックモードに設定されている。

【0029】

この構成において、走査線112に走査信号を供給し、TFT116をオン(導通)させるとともに、データ線114およびオン状態のTFT116を介して、画素電極118に階調(明るさ)に応じた電圧のデータ信号Vidを供給すると、走査信号が供給された走査線112とデータ信号が供給されたデータ線114との交差に対応する液晶素子120に、階調に応じた実効電圧を保持させることができる。したがって、液晶素子120を透過する光は、画素毎に異ならせることが可能であり、これにより、表示領域A1において画像が形成される。なお、形成された画像は、使用者に直視され、または、後述するプロジェクターのように拡大投射されて視認される。

また、この構成において、走査線113に走査信号Gdを供給し、TFT116dをオン(導通)させるとともに、測定信号線149およびオン状態のTFT116dを介して、画素電極118dに電圧を印加すると、液晶素子120dに、測定信号線149に供給された測定信号に応じた実効電圧を保持させることができる。なお、表示パネル100においては、ダミー画素111が視認されないようにするため、表示領域A1より外側に外側にダミー画素111を透過した光を遮光する遮光層を設けるようにしてもよい。

【0030】

続いて、制御回路50について説明する。図1に示したように、制御回路50においては、垂直同期信号Vs、水平同期信号Hsおよびクロック信号Clkが走査制御回路52に供給され、画像データVdがデータ信号生成回路54に供給される。

画像データVdは、図示省略した外部上位回路から、垂直走査信号Vs、水平走査信号Hsおよびクロック信号Clkに同期して供給される。画像データVdは、縦480行×横640列の画素110の階調を例えば8ビットで指定するデジタルデータであり、特に図示しないが、垂直同期信号Vsで規定される垂直走査期間にわたって、1行1列〜1行640列、2行1列〜2行640列、3行1列〜3行640列、・・・、480行1列〜480行640列という画素の順番で供給される。この供給の際に、水平同期信号Hsで規定される水平走査期間において1行分の画像データVdが供給され、さらに、クロック信号Clkの1周期で1画素分の画像データVdが供給される。なお、画像データVdは、周期16.7ミリ秒(周波数60Hz)で1フレーム分(表示パネル100の全画素分)が供給される。

【0031】

走査制御回路52は、極性指定信号Polをデータ信号生成回路54へ出力する。極性指定信号Polは、液晶素子120に対する電圧の書込極性を指定する信号であり、例えばHレベルであれば正極性を指定し、Lレベルであれば負極性を指定する。ここで、正極性書込とは、階調に応じた電圧を液晶素子120に保持させる際に、画素電極118が第1対向電極108よりも高位側となる場合をいい、反対に、負極性書込とは、画素電極118が第1対向電極108よりも低位側となる場合をいう。

【0032】

データ信号生成回路54は、外部上位装置から供給される画像データVdを、一旦内部メモリ(図示省略)に記憶した後、表示パネル100の駆動に同期して読み出すものである。データ信号生成回路54は、表示パネル100のある行の走査線を選択するとき、当該行の画像データVdを読み出し、読み出した画像データVdをアナログの信号に変換してデータ信号Vidを生成する。

なお、データ信号生成回路54は、極性指定信号Polによって正極性書込が指定されている場合、データ信号Vidを、第1対向電極108への印加電圧LCcomよりもやや高位側に設定された基準電圧Vc(基準電位)に対して高位側の電圧であって、階調に応じた電圧とする。また、データ信号生成回路54は、極性指定信号Polによって負極性書込が指定されている場合、データ信号Vidを、基準電圧Vcに対して低位側の電圧であって、階調に応じた電圧とする。なお、極性を切り替える理由は、直流成分の印加によって液晶が劣化するのを防止するためである。

【0033】

また、走査制御回路52は、測定信号Meと電圧設定信号Vsetを出力する。測定信号Meは、ダミー画素111の液晶に流れる電流を測定するために出力される信号であり、測定信号線149に供給される。測定信号Meは、図4の(a)に示したように基準電圧Vc(第3電圧)、基準電圧Vcに対して高位側の電圧V1(第1電圧)、基準電圧Vcに対して低位側の電圧V2(第2電圧)という順番で繰り返し電圧が変化する。

電圧設定信号Vsetは、第2対向電極109の電位を規定する信号であり、第2対向電極109に供給される。電圧設定信号Vsetが第2対向電極109に供給されると、第2対向電極109には基準電圧Vcが印加される。

【0034】

また、走査制御回路52は、垂直同期信号Vs、水平同期信号Hsおよびクロック信号Clkに同期して、スタートパルスDx、Dya,Dybおよびクロック信号Clx、Clyを出力する。

詳細には、走査制御回路52は、1行目の画像データVdに対応したデータ信号Vidが供給される水平走査期間に1行目の走査線112が選択されるようにスタートパルスDya,Dybおよびクロック信号Clyを出力し、2、3、4、・・・、480行の画像データVdに対応したデータ信号Vidが供給される水平走査期間にそれぞれ2、3、4、・・・、480行目の走査線112が選択されるようにクロック信号Clyを出力して走査線駆動回路130を制御する。

また、走査制御回路52は、1列目の画素に対応するデータ信号Vidを出力するときにサンプリング信号S1をHレベルとし、以下2列目、3列目、・・・、640列目の画素に対応するデータ信号Vidを出力するときにサンプリング信号S2、S3、・・・、S640がHレベルとなるように、スタートパルスDxおよびクロック信号Clxを出力してサンプリング信号出力回路142を制御する。

【0035】

図5は、走査線駆動回路130により出力される走査信号G1〜G480を、スタートパルスDya、Dybとクロック信号Clyとの関係において示すタイミングチャートである。この図に示したように、本実施形態では、1フレームの期間において走査線112は、それぞれ2回選択される。ここで、フレームとは、1枚の画像を表示パネル100に表示させるのに要する期間をいうが、画像データVdは、周期16.7ミリ秒(周波数60Hz)で供給されるので、1フレームとは、この周期の16.7ミリ秒と一致する。

走査制御回路52は、デューティ比が50%のクロック信号Clyを、1フレームの期間にわたって走査線数に等しい480周期分出力する。なお、図5においては、クロック信号Clyの1周期の期間をHと表記している。また、走査制御回路52は、クロック信号Clyの1周期分のパルス幅を有するスタートパルスDya、Dybを、それぞれクロック信号ClyがHレベルの立ち上がり時において、それぞれ次のように出力する。すなわち、走査制御回路52は、スタートパルスDyaを1フレームの期間の最初(すなわち第1フィールドの最初)に出力する一方、スタートパルスDybを、スタートパルスDybを出力してからクロック信号Clyの240周期分を出力した(すなわち、1フレームの半分期間が経過した)タイミングTで出力する。ただし、走査制御回路52は、後述するように、スタートパルスDybをタイミングTに対し、クロック信号Clyの周期を単位とした分だけ時間的に前方側または後方側に出力する場合がある。

【0036】

なお、本実施形態では、1フレームの期間のうち、スタートパルスDyaが出力されてからスタートパルスDybが出力されるまでの期間を第1フィールドとし、スタートパルスDybが出力されてから次のスタートパルスDyaが出力されるまでの期間を第2フィールドとしている。ここで、スタートパルスDya、Dybは交互に出力され、このうち、スタートパルスDyaは、1フレームの開始タイミング、すなわち16.7ミリ秒毎に出力される。このため、スタートパルスDyaを特定すると、必然的にスタートパルスDybも特定できるので、図1、図2等においては、特に両者を区別することなく、スタートパルスDyとして表記している。

【0037】

走査線駆動回路130は、このようなスタートパルスDya、Dybおよびクロック信号Clyから、図5に示される走査信号G1〜G480を出力する。すなわち、走査線駆動回路130は、走査信号G1〜G480について、スタートパルスDyaが供給されると、クロック信号ClyがLレベルの期間において順次Hレベルとさせる一方、スタートパルスDybが供給されると、クロック信号ClyがHレベルの期間において順次Hレベルとさせる。

このため、走査線112は、スタートパルスDyaの供給によって、あるフレームの第1フィールドから第2フィールドまでにわたって画面下方向にむかって1、2、3、4、・・・、480行目の順番で、クロック信号Clyの半周期の期間をおいて選択される。一方、走査線112は、スタートパルスDybの供給によって、あるフレームの第2フィールドから次フレームの第1フィールドまでにわたって画面下方向にむかって1、2、3、4、・・・、480行目の順番で、スタートパルスDyaの供給を契機とする選択の合間にて選択されることになる。なお、走査信号がHレベルとなる期間は、実際には図5,6に示されるように、クロック信号Clyの半分周期の期間よりも狭められている。

【0038】

次にスタートパルスDybの出力タイミングについて説明する。走査制御回路52は、スタートパルスDybの出力タイミングを制御する。具体的には、走査制御回路52は、スタートパルスDybの出力タイミングを指定するための設定値として、予め定められた第1設定値と第2設定値を記憶している。なお、本実施形態においては、第1設定値は、マイナスの整数の値であり、第2設定値は、プラスの整数の値である。また、走査制御回路52は、スタートパルスDybの出力タイミングを指定するための値を格納するレジスターを有している。走査制御回路52は、レジスターに格納された値に応じてスタートパルスDybの出力タイミングを変更する。

【0039】

具体的には、まず走査制御回路52は、外部上位装置から供給される画像データVdを、データ信号生成回路54の内部メモリに記憶させた後、表示パネル100においてある行の走査線112を選択するとき、当該行の画像データVdを記憶速度の倍の速度で読み出すとともに、画像データVdの読み出しに合わせて、サンプリング信号S1〜S640が順番にHレベルとなるように、サンプリング信号出力回路142を制御する。なお、読み出された画像データVdは、アナログのデータ信号Vidに変換される。

【0040】

ここで、走査制御回路52は、レジスターに格納されている値が「0」であると、タイミングTにおいてスタートパルスDybを供給する。走査制御回路52がタイミングTにおいてスタートパルスDybを供給する場合、第1フィールドにおいては、走査線112が241、1、242、2、243、3、・・・、480、240行目という順番で選択される。

このため、走査制御回路52は、はじめに241行目の走査線112が選択されるように、走査線駆動回路130を制御する。また、走査制御回路52は、データ信号生成回路54に対し、メモリに記憶された241行目に相当する画像データVdを倍速で読み出させ、極性指定信号Polに応じて、負極性のデータ信号Vidに変換するように制御するとともに、この読み出しに合わせて、サンプリング信号S1〜S640がこの順番で排他的にHレベルとなるようにサンプリング信号出力回路142を制御する。サンプリング信号S1〜S640が順番にHレベルになると、TFT146が1列目から640列目まで順番にオンとなり、画像信号線148に供給されたデータ信号Vidが1〜640列目のデータ線114に順番にサンプリングされる。

一方、241行目の走査線112が選択されて走査信号G241がHレベルになると、241行目に位置する画素110におけるTFT116がすべてオンする。このため、データ線114にサンプリングされたデータ信号Vidの負極性電圧がそのまま画素電極118に印加される。このため、241行目であって1、2、3、4、・・・、639、640列の画素における液晶素子120には、画像データVdで指定された階調に応じた負極性電圧が書き込まれて、保持されることになる。

【0041】

次に、走査制御回路52は、1行目の走査線112が選択されるように、走査線駆動回路130を制御する。また、走査制御回路52は、データ信号生成回路54に対し、メモリに記憶された1行目に相当する画像データVdを倍速で読み出させ、極性指定信号Polに応じて、正極性のデータ信号Vidに変換するように制御するとともに、この読み出しに合わせて、サンプリング信号S1〜S640がこの順番で排他的にHレベルとなるようにサンプリング信号出力回路142を制御する。

1行目の走査線112が選択されて走査信号G1がHレベルになると、1行目に位置する画素110におけるTFT116がすべてオンし、これにより、データ線114にサンプリングされたデータ信号Vidの電圧が画素電極118に印加される。このため、1行目であって1〜640列の画素における液晶素子120には、画像データVdで指定された階調に応じた正極性電圧が書き込まれて、保持されることになる。

【0042】

以下、第1フィールドにおいては、同様な電圧書込の動作が、242、2、243、3、・・・、480、240行目という順番で実行される。これにより、1〜240行目の画素に対しては階調に応じた正極性電圧が書き込まれ、241〜480行目の画素に対しては階調に応じた負極性電圧が書き込まれて、それぞれ保持されることになる。

なお、タイミングTにおいてスタートパルスDybが供給される場合であれば、第2フィールドにおいて、走査線112が1、241、2、242、3、243、4、244、・・・、240、480行目という順番で選択されるともに、同一行における書込極性が反転される。このため、1〜240行目の画素に対しては階調に応じた負極性電圧が書き込まれ、241〜480行目の画素に対しては階調に応じた正極性電圧が書き込まれて、それぞれ保持されることになる。

【0043】

図6には、第1フィールドにおける(i+240)行目の走査線とi行目の走査線とが選択される期間におけるデータ信号Vidの電圧波形の一例が示されている。この図において、電圧Vw(+)、Vw(−)は、それぞれ最高階調の白色に相当する正極性、負極性電圧であり、基準電圧Vcを中心に対称の関係にある。基準電圧Vcは、データ信号Vidの振幅中心であり、電圧Vw(+)、Vw(−)の中間の電圧である。なお、本実施形態においては、特に説明のない限り、接地電位Gndを電圧の基準としている。画像データVdで指定される階調値の十進値が「0」のときに最低階調の黒色を指定し、以後当該十進値が大きくなるにつれて明るい階調を指定する場合、本実施形態はノーマリーブラックモードであるから、データ信号Vidの電圧は、正極性に変換する場合であれば、階調値が大きくなるにつれて基準電圧Vcから高位側(Vw(+)側)に振られた電圧となり、負極性に変換する場合であれば、基準電圧Vcから低位側(Vw(−)側)に振られた電圧となる。

【0044】

第1フィールドでは、i行目よりも先に(i+240)行目の走査線が選択されるので、走査信号G(i+240)がHレベルになる期間のうち、例えばサンプリング信号S1がHレベルになる期間に、データ信号Vidは、(i+240)行1列の画素の階調に応じた負極性電圧となり、以降、サンプリング信号の変化に合わせて、2、3、4、・・・、640列目の画素の階調に応じた負極性電圧に変化する。続いて選択されるi行目では、正極性書込が指定されるので、走査信号GiがHレベルになる期間のうち、例えばサンプリング信号S1がHレベルになる期間に、データ信号Vidは、i行1列の画素の階調に応じた正極性電圧となり、以降、サンプリング信号の変化に合わせて、2、3、4、・・・、640列の画素の階調に応じた正極性電圧に変化する。なお、第2フィールドでは、i行目よりも後に(i+240)行目の走査線が選択されるので、走査信号Giが先にHレベルになるとともに、書込極性が反転するので、データ信号Vidの電圧波形は図7に示される通りとなる。

なお、図6および図7においてデータ信号Vidの電圧を示す縦スケールは、便宜的に他の信号における縦スケールよりも拡大してある。また、データ信号Vidは、サンプリング信号S640がLレベルに変化してからサンプリング信号S1がHレベルに変化するまでの期間にわたって黒色に相当する電圧となっているが、その理由は、タイミングずれなどの理由により誤って画素に書き込まれても、表示に寄与させないためである。

【0045】

次に図8は、スタートパルスDybがタイミングTで供給される場合において、各行の書込状態を連続するフレームにわたった時間経過とともに示す図である。この図に示されるように、本実施形態では、第1フィールドにおいて241、242、243、・・・、480行目の画素では負極性の書き込みがなされ、1、2、3、・・・、240行目の画素では正極性の書き込みがなされて、次の書き込みまで保持される。一方、第2フィールドにおいて1、2、3、・・・、240行目の画素では負極性の書き込みがなされ、241、242、243、・・・、480行目の画素では正極性の書き込みがなされて、同様に次の書き込みまで保持される。

レジスターの値が「0」であり、スタートパルスDybがタイミングTで供給される場合、第1および第2フィールドの期間は、クロック信号Clyの240周期分であるから、各画素において液晶素子120に正極性電圧が保持される期間と負極性電圧が保持される期間とは半分ずつとなる。

【0046】

次に、レジスターに格納されている値が0以外の値である場合について説明する。例えば、レジスターに格納された値が「−1」である場合、走査制御回路52は、図9に示したように、スタートパルスDybを、タイミングTよりもクロック信号Clyの1周期分だけ早いタイミングT(−1)に変更して出力する。すると、第1フィールドの期間はクロック信号Clyの239周期分となるのに対し、第2フィールドの期間はクロック信号Clyの241周期分となる。これにより、図10に示されるように、スタートパルスDybの供給を契機とする選択により書き込まれる負極性電圧の保持期間は、スタートパルスDyaの供給を契機とする選択により書き込まれる正極性電圧の保持期間よりも長くなる。したがって、画素においては、負極性電圧で保持された実効電圧が高められ、正極性電圧で保持された実効電圧が低められる。

【0047】

負極性電圧で保持された実効電圧が正極性電圧で保持された実効電圧より高くなると、画素は、負極性電圧を保持した時に明るくなり、正極性電圧を保持した時の暗くなる方向に変化する。なお、レジスターに格納した値が「−2」であれば、走査制御回路52は、スタートパルスDybを、タイミングTよりもクロック信号Clyの2周期分だけ早いタイミングに変更して出力する。すると、画素は、レジスターに格納した値が「−1」の場合より、負極性電圧で保持された実効電圧がさらに高められ、正極性電圧で保持された実効電圧がさらに低められる。

【0048】

一方、レジスターに格納した値が「+1」である場合、走査制御回路52は、図11に示したように、スタートパルスDybを、タイミングTよりもクロック信号Clyの1周期分だけ遅いタイミングT(+1)に変更して出力する。すると、第1フィールドの期間はクロック信号Clyの241周期分となるのに対し、第2フィールドの期間はクロック信号Clyの239周期分となる。これにより、図12に示されるように、スタートパルスDybの供給を契機とする選択により書き込まれる負極性電圧の保持期間は、スタートパルスDyaの供給を契機とする選択により書き込まれる正極性電圧の保持期間よりも短くなる。したがって、画素においては、正極性電圧で保持された実効電圧が高められ、負極性電圧で保持された実効電圧が低められる。

【0049】

正極性電圧で保持された実効電圧が負極性電圧で保持された実効電圧より高くなると、画素は、正極性電圧を保持した時に明るくなり、負極性電圧を保持した時に暗くなる方向に変化する。なお、レジスターに格納した値が「+2」であれば、走査制御回路52は、スタートパルスDybを、タイミングTよりもクロック信号Clyの2周期分だけ遅いタイミングに変更して出力する。すると、画素は、レジスターに格納した値が「+1」の場合より、正極性で保持された実効電圧がさらに高められ、負極性で保持された実効電圧がさらに低められる。

このように、走査制御回路52においてレジスターの値を変更することにより、正極性で保持された実効電圧と、負極性で保持された実効電圧との比が変更されるため、走査制御回路52は、正極性で保持された実効電圧と、負極性で保持された実効電圧との比を変更する実効電圧変更回路として機能している。

【0050】

ところで、第1対向電極108に印加される電圧LCcomは、図6に示されるように、工場出荷時において、基準電圧Vcよりも低位側に設定される。これは、画素電極をTFTで駆動するアクティブマトリクス型の電気光学装置では、いわゆるブッシュダウンが発生することや、液晶素子のリークが正極性の電圧を保持する場合と負極性の電圧を保持する場合とで異なることなどによる。仮に電圧LCcomを基準電圧Vcと一致させた場合、負極性書込による液晶素子120の実効電圧が、正極性書込による実効電圧よりも若干大きくなってしまう(TFT116がnチャネルの場合)ので、この差が相殺されるような最適値に、電圧LCcomを基準電圧Vcよりも低位側にオフセットして設定しているのである。

【0051】

本実施形態において、スタートパルスDybがタイミングTで供給される場合、第1および第2フィールドの期間は互いに等しく、各画素において液晶素子120に書き込まれた正極性電圧の保持期間と負極性電圧の保持期間とは同じとなるので、液晶素子120には直流成分が印加されないはずである。しかしながら、経年変化などによりTFTのプッシュダウン量や、液晶素子におけるリーク量が工場出荷時から変化したとき、電圧LCcomは、もはや最適値ではなくなり、液晶素子120に直流成分が印加される。すると、正極性電圧を保持している期間と負極性電圧を保持している期間とで画素110の明るさに差が生じることになる。

また、表示パネル100は、個々に特性が異なり、一定時間が経過すると、正極性電圧を保持している期間と負極性電圧を保持している期間とで画素110の明るさの差を抑えるために電圧LCcomを増やす必要がある特性のパネルと、画素110の明るさの差を抑えるために電圧LCcomを減らす必要がある特性のパネルとがある。この場合、レジスターの値を0にしても、画素110においては明るさの差が発生することになる。

【0052】

ここで図13は、表示パネル100の特性を説明するための図である。この図において横軸はレジスターの値を表し、レジスターの値が正の場合には正極性電圧の保持期間が長く、レジスターの値が負の場合には負極性電圧の保持期間が長いことを示している。また、縦軸は、一定時間経過した後に、第1対向電極108の電圧をどれだけ電圧LCcomから変更するとフリッカーが最小になるかを表している。

図13の(1)の特性のパネルは、レジスターの値が0の時において時間が経過すると液晶素子120に直流成分が印加され、フリッカーを最小にするためには第1対向電極108へ印加する電圧を電圧LCcomより大きくする必要が生じる特性のパネルである。また、図13の(2)の特性のパネルは、レジスターの値が0の時において時間が経過すると液晶素子120に直流成分が印加され、フリッカーを最小にするためには第1対向電極108に印加する電圧を電圧LCcomより小さくする必要が生じる特性のパネルである。

なお、スタートパルスDybの出力タイミングを指定するための設定値である上述した第2設定値は、図13に示した第2設定値であり、図13の(1)の特性のパネルと(2)の特性のパネルの両方について、一定時間経過後にフリッカーを最小にするには、電圧LCcomを減らす必要が生じる値である。また、スタートパルスDybの出力タイミングを指定するための設定値である上述した第1設定値は、図13に示した第1設定値であり、(1)と(2)のパネルの両方について、一定時間経過後にフリッカーを最小にするには、電圧LCComを増やす必要が生じる値である。

【0053】

電気光学装置1を備える電子機器の出荷時には、レジスターの値を0にし(即ち、正極性電圧の保持時間と負極性電圧の保持時間を同じとし)、フリッカーが知覚されないように第1対向電極108の電圧を電圧LCcomに調整する。しかし、経年変化によって液晶素子120に直流成分が印加されると、正極性電圧の保持期間と負極性電圧の保持期間との間で実効電圧の差が大きくなり、フリッカーが知覚される。

【0054】

図13の(1)の特性のパネルの場合、時間が経過して液晶素子120に直流成分が印加されると、フリッカーが最小となる最適な第1対向電極108の電圧は、電圧LCcomより大きな電圧となる。

一方、図13の(2)の特性のパネルの場合、時間が経過して液晶素子120に直流成分が印加されると、フリッカーが最小となる最適な第1対向電極108の電圧は、電圧LCcomより小さな電圧となる。

【0055】

表示パネル100を駆動した場合、レジスターの値を0にして正極性電圧の保持期間と負極性電圧の保持期間とを同じとした状態で液晶素子120に直流成分が印加されなければ、フリッカーや焼き付きが発生しない。しかし、表示パネル100の特性には、ばらつきがあり、駆動を続けると液晶素子120に直流成分が印加され、正極性電圧の保持期間と負極性電圧の保持期間とで実効電圧に差が生じる。この差が大きくなるとフリッカーが発生し、この差が大きくなった状態が続くと焼き付きが発生する。

なお、フリッカーが発生するということは、正極性の電圧を保持している状態と負極性の電圧を保持している状態とで、液晶素子の透過率が異なっているということであり、これは、冒頭で説明したように液晶素子の容量が異なっているということになる。したがって、液晶素子120について、正極性電圧の保持期間と負極性電圧の保持期間とで容量の差が小さくなるように制御すれば、正極性で保持された実効電圧と負極性で保持された実効電圧に差が小さくなり、フリッカーや焼き付きが発生しないこととなる。

なお、この制御を行うためには、液晶素子120の容量を測定する必要があるが、液晶素子の容量を直接的に検出するのは困難であるため、本実施形態では、液晶素子の容量に対応して当該液晶素子に流れる電流を測定し、測定した電流に基づいて液晶素子への印加電圧を制御する構成とした。以下、この制御を行うための構成について説明する。

【0056】

図1に示した抵抗素子R、検出回路61及びA/D変換回路56は、液晶素子120dに流れる電流を測定するためのものである。抵抗素子Rは、一端が走査制御回路52に接続され、他端が信号線107に接続されている。このため、抵抗素子Rの両端には、第2対向電極109に流れる電流に比例した電圧が現れる。検出回路61は、抵抗素子Rの両端電圧を検出して増幅するものである。A/D変換回路56は、検出回路61によって検出・増幅された電圧を、デジタルデータに変換して走査制御回路52に出力するものである。A/D変換回路56によるサンプリングレート(標本化周波数)は、検出回路61によって検出・増幅される電圧の変化に対して十分に高く設定されている。なお、デジタルデータで示される電圧を、抵抗素子Rの抵抗値、および、検出回路61による電圧増幅率でそれぞれ除算すると、第2対向電極109に流れた電流値を算出することができる。

【0057】

走査線駆動回路130は、液晶素子に流れる電流を測定するため、走査線113に供給する走査信号Gdを常時Hレベルとする。これにより、ダミー画素111のTFT116dは常時オンとなる。また、走査線駆動回路130は、抵抗素子Rを介して信号線107に基準電圧Vcを印加する。また、走査制御回路52は、測定信号線149へ図4の(a)に示した測定信号Meを供給する。

測定信号Meは、電圧V1→基準電圧Vc→電圧V2→基準電圧Vcという順番で電圧が切り替えられ、この電圧の切り替えが繰り返される。なお、電圧V1は、電圧Vw(+)と基準電圧Vcとの間の正極性の電圧であり、電圧V2は、電圧Vw(−)と基準電圧Vcとの間の負極性の電圧である。なお、測定信号Meにおいて電圧の切り替えが早いと電流の測定が困難となるため、測定信号Meの周波数は、1フレームの周波数より低い周波数(例えば10Hz〜20Hz)であるのが好ましい。つまり、測定信号Meの電圧V1(第1電圧)が画素電極118d(第2電極)に印加される期間は、画素電極118(第1電極)に正極性電圧が印加される期間より長く、測定信号Meの電圧V2(第2電圧)が画素電極118d(第2電極)に印加される期間は、画素電極118(第1電極)に負極性電圧が印加される期間より長いのが好ましい。

【0058】

表示パネル100においては、全てのダミー画素111のTFT116dがオン状態にあるため、全ての画素電極118dには、測定信号Meが供給されることになる。測定信号Meは、図4の(a)に示したように電圧が切り替わるので、この電圧の切り替えに伴って、液晶素子120dに電流が流れる。このとき、第2対向電極109と抵抗素子Rを接続する信号線107には、各液晶素子120dにそれぞれ流れた電流を総和した電流が流れる。信号線107に流れる総和電流は抵抗素子Rによって電圧に変換され、当該電圧は、走査制御回路52によって測定される。このときに測定される電圧波形(電流波形)は、図4の(b)に示されるようなものとなっていると考えられる。その理由について以下詳述する。

【0059】

まず、画素電極118dに印加される電圧が、基準電圧Vcから電圧V1に切り替わったとき、液晶素子120dの印加電圧(当該画素電極に印加された電圧と第2対向電極109に印加された電圧との差)は、当該切り替わりに対し瞬時に変化するのに対し、光学応答である透過率は、図4の(c)に示されるように、駆動電圧の変化に対して、かなり遅く変化する。すなわち、黒色に相当する透過率Tbから中間階調に相当する透過率Tgまで積分的に変化する。次に、液晶素子120dの容量は、画素電極118dと第2対向電極109との間に介在する誘電体としての液晶の分子配列状態(傾き)によって変化し、この傾きによって、透過率が決まる。このため、液晶素子120dの容量は、透過率とほぼ同様な特性で変化すると考えられる。

【0060】

液晶素子120dの容量が、図4の(c)で示される透過率と同様な特性で変化するのであれば、液晶素子120に流れる電流波形には、図4の(b)に示されるように、電圧V1の開始タイミングにおいて過渡的に流れる瞬時電流、すなわち、第2対向電極109からみて画素電極118dの電位が高くなる方向に切り替わることに伴う微分波形の第1ピークApと、電圧V1の開始タイミングからの液晶素子の容量変化(透過率変化とほぼ同特性と考えられる)に伴う第2ピークBpとが現れる。同様に、電圧V2の開始タイミングにおいて、電流波形には、第2対向電極109からみて画素電極118dの電位が低くなる方向に切り替わることに伴う微分波形の第1ピークAmと、電圧V2の開始タイミングからの液晶素子の容量変化に伴う第2ピークBmとが現れる。

【0061】

なお、液晶素子120dに流れる電流波形には、電圧V1から基準電圧Vcに切り替わったタイミングにおいては、第1ピークAmのみが現れる。同様に、電圧V2から基準電圧Vcに切り替わったタイミングにおいては、第1ピークApのみが現れる。これは、実施形態において液晶105として、印加電圧が絶対値でみて大きい方向(オン方向)に変化するときの光学応答が、小さい方向(オフ方向)へ変化するときの光学応答よりも遅く、かつ、オフ方向への光学応答は十分に速い性質を持つものを想定しているので、第2ピークBp、Bmは、オフ方向への変化であるこれらのタイミングにおいて現れない(現れにくい)からである。

【0062】

ここで、電圧V1(V2)が印加される期間において、第1ピークAP(Am)を除いた電流波形成分、すなわち図4の(b)においてハッチングで示した成分は、液晶素子120dの容量変化によって生じた成分である。液晶素子120dの容量変化は、透過率の変化であるから、第1ピークAp(Am)を除いた電流波形成分は、透過率の変化を反映したものとなる。したがって、電圧V1の印加期間において第1ピークApを除いた電流波形成分と、電圧V2の印加期間において第1ピークAmを除いた電流波形成分との差が小さくなるような制御を行えば、透過率の差が小さくなり、フリッカーが発生しないこととなる。

【0063】

この制御の一例としては、正極性で保持された実効電圧と負極性で保持された実効電圧との比を変更する制御があり、本実施形態では、正極性電圧の印加時間と負極性電圧の印加時間の比を変更する方法を採用した。また、電圧V1(V2)の印加期間において第1ピークAp(Am)を除いた電流波形成分は、第2ピークBp(Bm)の波高値として反映される。このため、本実施形態では、電圧V1(V2)の印加期間において第1ピークAp(Am)を除いた電流波形成分を、第2ピークBp(Bm)の波高値で特定する構成とした。

【0064】

なお、図4の(b)における電流波形(電圧波形)では、ゼロ点が重要となる。ここで、測定信号Meの電圧および第2対向電極109の電圧がそれぞれ時間的に一定であれば、信号線107に流れる電流はゼロのはずである。このため、測定信号Meの電圧および第2対向電極109の電圧をそれぞれ所定期間だけ一定として、この一定状態における検出回路61の出力値を電流のゼロ点として用いればよい。

【0065】

また、測定信号Meの電圧がV1である期間において第1ピークApを除いた電流波形成分(または波高値)と、測定信号Meの電圧がV2の期間において第1ピークAmを除いた電流波形成分(または波高値)とを比較するためには、液晶素子120dに電圧を印加する前の条件を揃えた状態が望ましい。このため、本実施形態では、画素電極118dに、正極性の電圧V1を印加する前の期間、および、負極性の電圧V2を印加する前の期間において、それぞれリセット電圧として、第2対向電極109と等しい基準電圧Vcを画素電極118dに印加して、液晶素子120dの駆動電圧をゼロに揃えることにした。

【0066】

なお、例えばリセット電圧として、ノーマリーブラックモードの白色に相当する電圧Vw(+)、Vw(−)を画素電極118dに印加して、液晶素子120dの印加電圧を高い状態で揃えてしまうと、変化方向は、光学応答が十分に速いオフ方向になるので、第2ピークが現れにくくなる。換言すれば、リセット電圧として、液晶素子120dの印加電圧を小さい状態で揃える電圧を画素電極118dに印加すると、オン方向への変化となるので、第2ピークが特定しやすくなるのである。この意味において、リセット電圧としては、画素電極118に黒色に相当する電圧Vb(+)、Vb(−)としてもよい。

【0067】

次に走査制御回路52の動作について説明する。図14は、走査制御回路52が行う処理の流れを示したフローチャートである。まず走査制御回路52は、表示パネル100の駆動を開始するとスタートパルスDybの出力タイミングを指定するためにレジスターの値を「0」にする(ステップSA1)。走査制御回路52は、外部上位装置から垂直同期信号Vs、水平同期信号Hs及びクロック信号Clkが走査制御回路52に供給され、画像データVdがデータ信号生成回路54に供給されると、供給された各信号に基づいて表示パネル100を駆動する。走査制御回路52は、レジスターに格納されている値が「0」であるため、スタートパルスDybをタイミングTで出力する。また、走査制御回路52は、走査信号Gdと測定信号Meを出力する(ステップSA2)。

【0068】

次に、走査制御回路52は、A/D変換回路56によって変換されたデジタルデータを処理し、第2ピークBpの波高値と第2ピークBmの波高値を取得する(ステップSA3)。具体的には、走査制御回路52は、測定信号Meにおいて電圧V1の印加開始タイミングから2番目に現れる第2ピークBpの波高値(第2ピーク値)、すなわち図4の(b)に示した+Iaに相当する値を取得する。また、走査制御回路52は、測定信号Meにおいて電圧V2の印加開始タイミングから2番目に現れる第2ピークBmの波高値(第2ピーク値)、すなわち図4の(b)に示した−Icに相当する値を取得する。次に走査制御回路52は、第2ピークBpの波高値と第2ピークBmの波高値の差を算出し、算出した値を電流差Aとする(ステップSA4)。

【0069】

次に走査制御回路52は、予め定められた一定時間が経過したか否か判断する(ステップSA5)。なお、本実施形態では、この一定時間は10分とするが、10分に限定されうるものではなく、10分を超える時間や10分未満の時間であってもよい。走査制御回路52は、一定時間が経過していない場合(ステップSA5でNO)、一定時間が経過するのを待つ。走査制御回路52は、一定時間が経過したと判断すると(ステップSA5でYES)、A/D変換回路56によって変換されたデジタルデータを処理し、第2ピークBpの波高値と第2ピークBmの波高値を取得する(ステップSA6)。走査制御回路52は、ステップSA6の処理を終えると、第2ピークBpの波高値と第2ピークBmの波高値の差を算出し、算出した値を電流差Bとする(ステップSA7)。そして、走査制御回路52は、ΔI=|電流差A−電流差B|の演算を行い、電流差Aと電流差Bの差を表すΔIを算出する(ステップSA8)。

【0070】

次に走査制御回路52は、ステップSA8で算出したΔIが予め定められた閾値以上であるか否か判断する。なお、この閾値は、本実施形態においてはフリッカーが知覚される時の値より小さい値に設定されている。走査制御回路52は、ΔIの値が閾値未満である場合(ステップSA9でNO)、フリッカーが発生していないと判断し、処理の流れをステップSA5へ戻す。

また、走査制御回路52は、ΔIの値が閾値以上である場合(ステップSA9でYES)、ステップSA6で取得した第2ピークBpの波高値と第2ピークBmの波高値に基づいて、前述のレジスターの値を設定する。

【0071】

ここで、例えば表示パネル100が図13の(2)の特性の表示パネルである場合、第2ピークBpの波高値が第2ピークBmの波高値より大きくなっている。つまり、正極性電圧で保持された実効電圧が負極性電圧で保持された実効電圧より高くなっている。

このため、走査制御回路52は、ステップSA6で取得した波高値が、第2ピークBpの波高値>第2ピークBmの波高値の関係にある場合(ステップSA10でYES)、レジスターの値を第1設定値にする(ステップSA11)。レジスターに第1設定値が格納されると、正極性電圧の印加時間が短くなり、負極性電圧の印加時間が長くなる。これにより、画素110においては、負極性電圧で保持された実効電圧が高くなり、正極性電圧で保持された実効電圧が低くなるため、時間の経過と共に第2ピークBmの波高値が第2ピークBpの波高値より大きくなる方向へ変化していくこととなる。

【0072】

走査制御回路52は、ステップSA11の処理が終了すると処理の流れをステップSA5へ戻し、再び一定時間が経過するのを待つ。走査制御回路52は、ステップSA5でYESと判断すると、ステップSA6からステップSA8の処理を行う。次に走査制御回路52は、ステップSA9の処理を行う。レジスターに第1設定値が格納され、時間が経過して第2ピークBmの波高値が増大し、ΔIが閾値以上である場合(ステップSA9でYES)、ステップSA6で取得した第2ピークBpの波高値と第2ピークBmの波高値に基づいて、前述のレジスターの値を設定する。

ここでは、前述のように、負極性電圧で保持された実効電圧が高くなり、正極性電圧で保持された実効電圧が低くなっているため、ステップSA6で取得した波高値は、第2ピークBpの波高値<第2ピークBmの波高値の関係にある。この場合、走査制御回路52は、ステップSA10でNOと判断し、レジスターの値を第2設定値にする(ステップSA12)。レジスターに第2設定値が格納されると、負極性電圧の印加時間が短くなり、正極性電圧の印加時間が長くなる。これにより、画素110においては、正極性電圧で保持された実効電圧が高くなり、負極性電圧で保持された実効電圧が低くなるため、時間の経過と共に第2ピークBpの波高値が第2ピークBmの波高値より大きくなる方向へ変化していくこととなる。走査制御回路52は、ステップSA10の処理が終了すると処理の流れをステップSA3へ戻し、上述した処理を繰り返す。

【0073】

なお、表示パネル100が、図12の(1)の特性のパネル、つまり、レジスターの値を0にした場合に負極性電圧で保持された実効電圧が高くなり、正極性電圧で保持された実効電圧が低くなるパネルである場合、レジスターを0にして表示パネル100を駆動すると、時間が経過すると第2ピークBmの波高値が第2ピークBpの波高値より大きくなる方向へ変化していくこととなる。

この場合、走査制御回路52は、ステップSA6で取得した波高値が、第2ピークBpの波高値<第2ピークBmの波高値の関係にあると(ステップSA10でNO)、レジスターの値を第2設定値にする(ステップSA12)。レジスターに第2設定値が格納されると、負極性電圧の印加時間が短くなり、正極性電圧の印加時間が長くなる。これにより、画素110においては、正極性電圧で保持された実効電圧が高くなり、負極性電圧で保持された実効電圧が低くなるため、時間の経過と共に第2ピークBpの波高値が第2ピークBmの波高値より大きくなる方向へ変化していくこととなる。

【0074】

走査制御回路52は、ステップSA12の処理が終了すると処理の流れをステップSA5へ戻し、再び一定時間が経過するのを待つ。走査制御回路52は、ステップSA5でYESと判断すると、ステップSA6からステップSA8の処理を行う。

次に走査制御回路52は、ステップSA9の処理を行う。レジスターに第2設定値が格納され、時間が経過して第2ピークBpの波高値が増大し、ΔIが閾値以上である場合(ステップSA9でYES)、ステップSA6で取得した第2ピークBpの波高値と第2ピークBmの波高値に基づいて、前述のレジスターの値を設定する。ここでは、前述のように正極性電圧で保持された実効電圧が高くなり、負極性電圧で保持された実効電圧が低くなっているため、ステップSA6で取得した波高値が、第2ピークBpの波高値>第2ピークBmの波高値の関係にある。この場合、走査制御回路52は、ステップSA10でYESと判断し、レジスターの値を第1設定値にする(ステップSA11)。レジスターに第1設定値が格納されると、正極性電圧の印加時間が短くなり、負極性電圧の印加時間が長くなる。これにより、画素110においては、負極性電圧で保持された実効電圧が高くなり、正極性電圧で保持された実効電圧が低くなるため、時間の経過と共に第2ピークBmの波高値が第2ピークBpの波高値より大きくなる方向へ変化していくこととなる。

走査制御回路52は、ステップSA11の処理が終了すると処理の流れをステップSA3へ戻し、上述した処理を繰り返す。

【0075】

本実施形態によれば、液晶素子120に直流成分が印加されることにより正極性の電圧を印加した時と負極性の電圧を印加した時とで実効電圧に差が生じても、実効電圧の差が少なくなるように正極性電圧の印加時間と負極性電圧の印加時間が制御されるので、フリッカーや焼き付きの発生を抑えることができる。

【0076】

[電子機器]

次に、上述した実施形態に係る電気光学装置を用いた電子機器の例について説明する。図15は、上述した電気光学装置1の表示パネル100をライトバルブとして用いた3板式プロジェクターの構成を示す平面図である。プロジェクター2100の内部には、ハロゲンランプ等の白色光源を備えたランプユニット2102が設けられている。このプロジェクター2100において、ランプユニット2102から射出された光は、内部に配置された3枚のミラー2106および2枚のダイクロイックミラー2108によってR(赤)、G(緑)、B(青)の3原色に分離されて、各原色に対応するライトバルブ100R、100Gおよび100Bにそれぞれ導かれる。なお、B色の光は、他のR色やG色と比較すると、光路が長いので、その損失を防ぐために、入射レンズ2122、リレーレンズ2123および出射レンズ2124からなるリレーレンズ系2121を介して導かれる。

【0077】

ここで、ライトバルブ100R、100Gおよび100Bの構成は、上述した実施形態における表示パネル100と同様であり、外部上位装置(図示省略)から供給されるR、G、Bの各色に対応する画像データVdでそれぞれ駆動されるものである。ライトバルブ100R、100G、100Bによってそれぞれ変調された光は、ダイクロイックプリズム2112に3方向から入射する。そして、このダイクロイックプリズム2112において、R色およびB色の光は90度に屈折する一方、G色の光は直進する。したがって、各色の画像が合成された後、レンズユニット2114によって正転拡大投影されるので、スクリーン2120には、カラー画像が表示されることとなる。

【0078】

なお、ライトバルブ100R、100Bの透過像は、ダイクロイックプリズム2112により反射した後に投射されるのに対し、ライトバルブ100Gの透過像はそのまま投射されるので、ライトバルブ100R、100Bにより形成される画像と、ライトバルブ100Gにより形成される画像とは左右反転の関係にある。

【0079】

また、電子機器としては、図15を参照して説明した他にも、リアプロジェクション型のテレビジョンや、直視型、例えば携帯電話や、パーソナルコンピューター、ビデオカメラのモニター、カーナビゲーション装置、ページャー、電子手帳、電卓、ワードプロセッサー、ワークステーション、テレビ電話、POS端末、ディジタルスチルカメラ、タッチパネルを備えた機器等などが挙げられる。そして、これらの各種の電子機器に対して、本発明に係る電気光学装置が適用可能なのは言うまでもない。

【0080】

[変形例]

以上、本発明の実施形態について説明したが、本発明は上述した実施形態に限定されることなく、他の様々な形態で実施可能である。例えば、上述の実施形態を以下のように変形して本発明を実施してもよい。なお、上述した実施形態および以下の変形例は、各々を組み合わせてもよい。

【0081】

(変形例1)

上述した実施形態では、液晶素子120において保持される電圧の実効値がゼロ(またはゼロ近傍)に近ければ、黒色を表示するノーマリーブラックモードとしたが、液晶素子120において保持される電圧の実効値がゼロ(またはゼロ近傍)に近ければ白色を表示するノーマリーホワイトモードとしても良い。

【0082】

(変形例2)

上述した実施形態においては、走査線113は常時Hレベルであり、測定信号Meが常時出力されているが、ステップSA3とステップSA6で波高値を取得する期間には、走査線113をHレベルとし、測定信号Meを出力するようにし、波高値を取得する期間以外においては走査線113をLレベルとし、測定信号Meを出力しないようにしてもよい。

【0083】

(変形例3)

上述した実施形態においては、電圧V1は電圧Vw(+)と基準電圧Vcとの間の正極性の電圧であり、電圧V2は、電圧Vw(−)と基準電圧Vcとの間の負極性の電圧であるが、上述したプロジェクター2100のように表示パネル100を透過型とする場合、電圧V1を電圧Vw(+)にし、電圧V2をVw(−)としてもよい。また、表示パネル100を反射型とする場合、電圧V1を電圧Vb(+)にし、電圧V2をVb(−)としてもよい。

【0084】

(変形例4)

上述した実施形態においては、正極性電圧の保持時間と負極性電圧の保持時間との比を変更することにより、正極性電圧で保持された実効電圧と正極性電圧で保持された実効電圧との比を変更し、ΔIが一定の範囲内に収まるようにしているが、ΔIを一定の範囲内に収める方法は、上述した実施形態の方法に限定されるものではない。

例えば、走査制御回路52は、表示パネル100の駆動を開始すると、階調が同じであれば正極性のデータ信号Vidと負極性のデータ信号Vidを基準電圧Vcを中心に対象の関係にする。また、走査制御回路52は、ステップSA11においては、正極性電圧の印加時間と負極性電圧の印加時間を変更する処理に替えて、正極性電圧と負極性電圧の電圧比を変更する。具体的には、走査制御回路52は、階調値が同じであれば、基準電圧Vcからのデータ信号Vidの振幅を正極性側を小さく、負極性側を大きくする。また、走査制御回路52は、ステップSA12においては、例えば階調値が同じであれば、基準電圧Vcからのデータ信号Vidの振幅を、正極性側を大きく、負極性側を小さくする。この変形例においても、正極性電圧の実効電圧と負極性電圧の実効電圧との比を変更することができる。

【0085】

(変形例5)

上述した実施形態では、ダミー画素111は、表示領域A1を囲むように表示領域A1の周辺に設けられているが、ダミー画素111の配置位置は、上述した実施形態の配置に限定されるものではない。例えば、1行1列目〜1行640列目の各画素110に隣り合うように1行目の画素に沿ってダミー画素111を設け、480行1列目〜480行640列目の各画素110と隣り合うように480行目の画素に沿ってダミー画素111を設けるようにしてもよい。また、1行1列目〜480行1列目の各画素110に隣り合うように1列目の画素に沿ってダミー画素111を設け、1行640列目〜480行640列目の各画素110に隣り合うように640列目の画素に沿ってダミー画素111を設けるようにしてもよい。要するに、ダミー画素111の配置位置及び数は図2に示した配置位置及び数に限定されず、表示領域A1の周辺にダミー画素111が設けられていればよい。なお、ダミー画素111の配置は、表示領域A1の一辺にのみ沿って配置する構成であってもよいが、表示領域A1の二辺以上に沿ってダミー画素111を配置するのが好ましく、さらに表示領域A1の4つの辺に沿ってダミー画素111を配置するのがより好ましい。ダミー画素111を二辺以上に沿って配置した場合、表示領域A1の一辺にのみ沿って配置した構成と比較すると、電流の測定に係るダミー画素111の数が増えるため、ダミー画素111毎の特性の違いの影響が少なくなる(異なる場所の画素の特性が得られる)。

【0086】

(変形例6)

上述した実施形態においては、ステップSA8でΔIを算出し、ΔIが閾値以上であった場合、正極性電圧を保持した時の実効電圧と負極性電圧を保持した時の実効電圧の差が少なくなるように正極性電圧の印加時間と負極性電圧の印加時間を変更しているが、印加時間を制御する処理の流れは図14に示したものに限定されるものではなく、例えば、図16に示した処理の流れとしてもよい。図16の処理は、電流差A、B及びΔIを算出するのではなく、第2ピークBpの波高値と第2ピークBmの波高値の差を求め、この波高値の差に基づいてレジスターの値を変更する点が前述の実施形態と異なる。

具体的には、ステップSB1〜SB2の処理は、ステップSA1〜SA2の処理と同じである。また、ステップSB3〜SB4の処理は、ステップSA5〜SA6の処理と同じである。本変形例においては、ステップSB4で取得した第2ピークBpの波高値と第2ピークBmの波高値の差が予め定められた閾値以上である場合(ステップSB5でYES)、レジスターの値を変更する処理を行う。なお、ステップSB6〜SB8の処理は、ステップSA10〜SA12の処理と同じである。

【0087】

(変形例7)

上述した実施形態においては、ダミー画素111には測定信号Meが供給されているが、第2ピークBpの波高値と第2ピークBmの波高値を取得する期間以外については、ダミー画素111の階調を隣り合う画素110の階調と同じ階調としてもよい。

図17は、本変形例に係るダミー画素111と画素110の構成を示した図である。本変形例においては、ダミー画素111は、スイッチSW1〜SW3を備えている。スイッチSW1の入力端の一方は、1行目の走査線112から分岐した走査線112aに接続されており、他方の入力端は、走査線113に接続され、出力端はTFT116dのゲート電極に接続されている。また、スイッチSW2の入力端の一方は、1列目のデータ線114に接続され、他方の入力端は、測定信号線149に接続され、出力端は、TFT116dのソース電極に接続されている。また、スイッチSW3の入力端の一方は、第1対向電極108に接続され、他方の入力端は、第2対向電極109に接続され、出力端は、TFT116dのドレイン電極に接続されている。

【0088】

この構成においては、ステップSA3とステップSA6で波高値を取得する際には、予め定められた期間、SW1の出力端は、走査線113に接続され、SW2の出力端は、測定信号線149に接続され、SW3の出力端は、第2対向電極109に接続される。これにより、ステップSA3とステップSA6で第2ピークBpの波高値と第2ピークBmの波高値を取得する期間には、ダミー画素111には測定信号Meが供給される。

一方、第2ピークBpの波高値と第2ピークBmの波高値を取得する期間ではない場合、SW1の出力端は、走査線112aに接続され、SW2の出力端は、データ線114に接続され、SW3の出力端は、第1対向電極108に接続される。これにより、第2ピークBpの波高値と第2ピークBmの波高値を取得する期間ではない場合、1行目の画素110に隣り合うダミー画素111には画素110と同じデータ信号Vidが供給され、1行目の画素110と、1行目の画素110に隣り合うダミー画素111の階調は、同じ階調になる。

【0089】

(変形例8)

上述した実施形態においては、第1対向電極108と第2対向電極109とが絶縁されているが、第1対向電極108と第2対向電極109とを電気的に接続し、一つのコモン電極としてもよい。この構成においては、第1対向電極108には電圧LCcomが印加される。本変形例によれば、表示パネル100と制御回路50を接続する配線の数を上述した実施形態より減らすことができる。

【0090】

(変形例9)

上述した実施形態においては、測定信号Meと電圧設定信号Vsetは走査制御回路52から出力されているが、測定信号Meと電圧設定信号Vsetを出力する構成は、この構成に限定されるものではなく、例えば、図18に示した構成としてもよい。

図18は、本発明の変形例に係る電気光学装置1Aの構成を示した図である。電気光学装置1Aは、測定信号回路62と、対向電極駆動回路63を備えている。測定信号回路62は、測定信号Meを出力する回路であり、測定信号線149に接続されている。測定信号回路62は、走査制御回路52により制御されて測定信号Meを出力する。また、対向電極駆動回路63は、第2対向電極109に接続されている。対向電極駆動回路63は、走査制御回路52により制御されて電圧設定信号Vsetを出力する。

本変形例においても、測定信号線149に測定信号を供給し、第2対向電極109に電圧Vsetを印加することができる。なお、測定信号線149をデータ線駆動回路140に接続し、データ線駆動回路140から測定信号Meを測定信号線149に供給する構成としてもよい。

【符号の説明】

【0091】

1,1A…電気光学装置、50…制御回路、52…走査制御回路、54…データ信号生成回路、56…A/D変換回路、61…検出回路、62…測定信号回路、63…対向電極駆動回路、100…表示パネル、105…液晶、107…信号線、108…第1対向電極、109…第2対向電極、110…画素、111…ダミー画素、112…走査線、114…データ線、116,116d…TFT、118,118d…画素電極、120,120d…液晶素子、130…走査線駆動回路、140…データ線駆動回路、142…サンプリング信号出力回路、146…TFT、148…画像信号線、149…測定信号線、2100…プロジェクター、2102…ランプユニット、2106…ミラー、2108…ダイクロイックミラー、2112…ダイクロイックプリズム、2114…レンズユニット、2120…スクリーン、2121…リレーレンズ系、2122…入射レンズ、2123…リレーレンズ、2124…出射レンズ、SW1〜SW3…スイッチ

【特許請求の範囲】

【請求項1】

第1電極とコモン電極とにより液晶を挟持した表示画素と、

所定の基準電圧よりも高位側で前記表示画素の階調に応じた正極性電圧と、所定の基準電圧よりも低位側で前記階調に応じた負極性電圧とを時間的に交互に前記第1電極へ印加し、前記コモン電極に所定の電圧を印加する駆動回路と、

第2電極と前記コモン電極により液晶を挟持したダミー画素と、

前記基準電圧よりも高位側の第1電圧と低位側の第2電圧とを時間的にずらして印加する測定信号を前記第2電極へ供給する測定信号回路と、

前記第2電極に前記第1電圧が印加された後に前記コモン電極に流れる電流のうち当該第1電圧の印加による瞬時電流を除いた第1電流と、前記第2電極に前記第2電圧が印加された後に前記コモン電極に流れる電流のうち当該第2電圧の印加による瞬時電流を除いた第2電流とに基づいて、前記駆動回路により前記第1電極に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比を変更する制御回路と

を有する液晶表示装置。

【請求項2】

前記制御回路は、前記第1電流と前記第2電流との差が予め定められた閾値未満となるように、前記第1電極に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比を変更すること

を特徴とする請求項1に記載の液晶表示装置。

【請求項3】

前記制御回路は、前記第1電流と前記第2電流との差が予め定められた閾値未満となるように、前記第1電極に印加する正極性電圧の印加時間と負極性電圧の印加時間を変更することを特徴とする請求項1または請求項2に記載の液晶表示装置。

【請求項4】

前記制御回路は、前記第1電流と前記第2電流との差が予め定められた閾値未満となるように、前記第1電極に印加する正極性電圧と負極性電圧の電圧比を変更することを特徴とする請求項1乃至3のいずれかに記載の液晶表示装置。

【請求項5】

前記測定信号は、前記第1電圧を印加する期間と前記第2電圧を印加する期間との間に前記コモン電極と同じ第3電圧を前記第2電極へ印加する信号であること

を特徴とする請求項1乃至請求項4のいずれかに記載の液晶表示装置。

【請求項6】

前記コモン電極は、前記第1電極との間に前記液晶を挟持する第1コモン電極と、前記第2電極との間に前記液晶を挟持する第2コモン電極とで構成され、前記第1コモン電極と前記第2コモン電極は互いに絶縁されており、

前記制御回路は、前記第2電極に前記第1電圧が印加された後に前記第2コモン電極に流れる電流のうち当該第1電圧の印加による瞬時電流を除いた電流と、前記第2電極に前記第2電圧が印加された後に前記第2コモン電極に流れる電流のうち当該第2電圧の印加による瞬時電流を除いた電流とに基づいて、前記駆動回路により前記第1電極に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比を変更すること

を特徴とする請求項1乃至請求項5のいずれかに記載の液晶表示装置。

【請求項7】

前記測定信号により前記第1電圧が前記第2電極へ印加される期間は、前記第1電極へ前記正極性電圧が印加される期間より長く、前記測定信号により前記第2電圧が前記第2電極へ印加される期間は、前記第1電極へ前記負極性電圧が印加される期間より長いこと

を特徴とする請求項1乃至請求項6のいずれかに記載の液晶表示装置。

【請求項8】

前記ダミー画素は、予め定められた期間においては前記測定信号回路から前記測定信号が前記第2電極へ供給され、当該期間外においては、当該ダミー画素に隣り合う前記表示画素に印加される正極性電圧と負極性電圧とが時間的に交互に前記駆動回路から前記第2電極へ印加されること

を特徴とする請求項1乃至請求項7のいずれかに記載の液晶表示装置。

【請求項9】

第1電極とコモン電極とにより液晶を挟持した表示画素と、第2電極と前記コモン電極により液晶を挟持したダミー画素とを備える液晶表示装置の駆動方法であって、

所定の基準電圧よりも高位側で前記表示画素の階調に応じた正極性電圧と、所定の基準電圧よりも低位側で前記階調に応じた負極性電圧とを時間的に交互に前記第1電極へ印加し、前記コモン電極に所定の電圧を印加し、

前記基準電圧よりも高位側の第1電圧と低位側の第2電圧とを時間的にずらして印加する測定信号を前記第2電極へ供給し、

前記第2電極に前記第1電圧が印加された後に前記コモン電極に流れる電流のうち当該第1電圧の印加による瞬時電流を除いた第1電流と、前記第2電極に前記第2電圧が印加された後に前記コモン電極に流れる電流のうち当該第2電圧の印加による瞬時電流を除いた第2電流とに基づいて、前記第1電極に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比を変更すること

を特徴とする液晶表示装置の駆動方法。

【請求項10】

請求項1乃至請求項8のいずれかに記載の液晶表示装置を有することを特徴とする電子機器。

【請求項1】

第1電極とコモン電極とにより液晶を挟持した表示画素と、

所定の基準電圧よりも高位側で前記表示画素の階調に応じた正極性電圧と、所定の基準電圧よりも低位側で前記階調に応じた負極性電圧とを時間的に交互に前記第1電極へ印加し、前記コモン電極に所定の電圧を印加する駆動回路と、

第2電極と前記コモン電極により液晶を挟持したダミー画素と、

前記基準電圧よりも高位側の第1電圧と低位側の第2電圧とを時間的にずらして印加する測定信号を前記第2電極へ供給する測定信号回路と、

前記第2電極に前記第1電圧が印加された後に前記コモン電極に流れる電流のうち当該第1電圧の印加による瞬時電流を除いた第1電流と、前記第2電極に前記第2電圧が印加された後に前記コモン電極に流れる電流のうち当該第2電圧の印加による瞬時電流を除いた第2電流とに基づいて、前記駆動回路により前記第1電極に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比を変更する制御回路と

を有する液晶表示装置。

【請求項2】

前記制御回路は、前記第1電流と前記第2電流との差が予め定められた閾値未満となるように、前記第1電極に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比を変更すること

を特徴とする請求項1に記載の液晶表示装置。

【請求項3】

前記制御回路は、前記第1電流と前記第2電流との差が予め定められた閾値未満となるように、前記第1電極に印加する正極性電圧の印加時間と負極性電圧の印加時間を変更することを特徴とする請求項1または請求項2に記載の液晶表示装置。

【請求項4】

前記制御回路は、前記第1電流と前記第2電流との差が予め定められた閾値未満となるように、前記第1電極に印加する正極性電圧と負極性電圧の電圧比を変更することを特徴とする請求項1乃至3のいずれかに記載の液晶表示装置。

【請求項5】

前記測定信号は、前記第1電圧を印加する期間と前記第2電圧を印加する期間との間に前記コモン電極と同じ第3電圧を前記第2電極へ印加する信号であること

を特徴とする請求項1乃至請求項4のいずれかに記載の液晶表示装置。

【請求項6】

前記コモン電極は、前記第1電極との間に前記液晶を挟持する第1コモン電極と、前記第2電極との間に前記液晶を挟持する第2コモン電極とで構成され、前記第1コモン電極と前記第2コモン電極は互いに絶縁されており、

前記制御回路は、前記第2電極に前記第1電圧が印加された後に前記第2コモン電極に流れる電流のうち当該第1電圧の印加による瞬時電流を除いた電流と、前記第2電極に前記第2電圧が印加された後に前記第2コモン電極に流れる電流のうち当該第2電圧の印加による瞬時電流を除いた電流とに基づいて、前記駆動回路により前記第1電極に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比を変更すること

を特徴とする請求項1乃至請求項5のいずれかに記載の液晶表示装置。

【請求項7】

前記測定信号により前記第1電圧が前記第2電極へ印加される期間は、前記第1電極へ前記正極性電圧が印加される期間より長く、前記測定信号により前記第2電圧が前記第2電極へ印加される期間は、前記第1電極へ前記負極性電圧が印加される期間より長いこと

を特徴とする請求項1乃至請求項6のいずれかに記載の液晶表示装置。

【請求項8】

前記ダミー画素は、予め定められた期間においては前記測定信号回路から前記測定信号が前記第2電極へ供給され、当該期間外においては、当該ダミー画素に隣り合う前記表示画素に印加される正極性電圧と負極性電圧とが時間的に交互に前記駆動回路から前記第2電極へ印加されること

を特徴とする請求項1乃至請求項7のいずれかに記載の液晶表示装置。

【請求項9】

第1電極とコモン電極とにより液晶を挟持した表示画素と、第2電極と前記コモン電極により液晶を挟持したダミー画素とを備える液晶表示装置の駆動方法であって、

所定の基準電圧よりも高位側で前記表示画素の階調に応じた正極性電圧と、所定の基準電圧よりも低位側で前記階調に応じた負極性電圧とを時間的に交互に前記第1電極へ印加し、前記コモン電極に所定の電圧を印加し、

前記基準電圧よりも高位側の第1電圧と低位側の第2電圧とを時間的にずらして印加する測定信号を前記第2電極へ供給し、

前記第2電極に前記第1電圧が印加された後に前記コモン電極に流れる電流のうち当該第1電圧の印加による瞬時電流を除いた第1電流と、前記第2電極に前記第2電圧が印加された後に前記コモン電極に流れる電流のうち当該第2電圧の印加による瞬時電流を除いた第2電流とに基づいて、前記第1電極に印加される正極性電圧の実効電圧と負極性電圧の実効電圧との比を変更すること

を特徴とする液晶表示装置の駆動方法。

【請求項10】

請求項1乃至請求項8のいずれかに記載の液晶表示装置を有することを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2013−64792(P2013−64792A)

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願番号】特願2011−202251(P2011−202251)

【出願日】平成23年9月15日(2011.9.15)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成25年4月11日(2013.4.11)

【国際特許分類】

【出願日】平成23年9月15日(2011.9.15)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]