液晶表示装置およびその製造方法

【課題】 個々の液晶表示パネルにおける残像を低減するとともに、複数枚の液晶表示パネル間における残像のレベルを均一化する。

【解決手段】 あらかじめ用意されたレイアウトデータに基づいて複数の走査信号線、複数の映像信号線、複数のTFT素子、および複数の画素電極を形成する工程を有する液晶表示装置の製造方法であって、前記走査信号線を形成する工程は、前記レイアウトデータに基づいて作成される描画データによる数値制御で露光パターンを生成する空間光変調素子を有する露光装置を用いて感光性材料膜を露光する工程を有し、前記描画データは、前記レイアウトデータにおける前記走査信号線のうちの、前記ソース電極と重畳させる部分の形状が、前記走査信号線と前記ソース電極との間に介在する絶縁層の膜厚の分布に応じた面積になるように補正して作成する液晶表示装置の製造方法。

【解決手段】 あらかじめ用意されたレイアウトデータに基づいて複数の走査信号線、複数の映像信号線、複数のTFT素子、および複数の画素電極を形成する工程を有する液晶表示装置の製造方法であって、前記走査信号線を形成する工程は、前記レイアウトデータに基づいて作成される描画データによる数値制御で露光パターンを生成する空間光変調素子を有する露光装置を用いて感光性材料膜を露光する工程を有し、前記描画データは、前記レイアウトデータにおける前記走査信号線のうちの、前記ソース電極と重畳させる部分の形状が、前記走査信号線と前記ソース電極との間に介在する絶縁層の膜厚の分布に応じた面積になるように補正して作成する液晶表示装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶表示装置およびその製造方法に関し、特に、多面取りで液晶表示パネルを製造する方法に適用して有効な技術に関するものである。

【背景技術】

【0002】

アクティブマトリクス型のTFT液晶表示装置(以下、単に液晶表示装置という。)は、たとえば、液晶テレビ、パーソナルコンピュータ用の液晶ディスプレイ、携帯電話端末などの携帯型電子機器の液晶ディスプレイとして広く用いられている。

【0003】

液晶表示装置は、一対の基板の間に液晶材料を封入した液晶表示パネルを有し、当該液晶表示パネルの表示領域は、TFT素子、画素電極、共通電極、および液晶層(液晶材料)を有する画素の集合でなる。また、アクティブマトリクス型の場合、液晶表示パネルは、複数の走査信号線および複数の映像信号線を有する。

【0004】

このとき、各画素のTFT素子は、ソースが画素電極と接続しており、ドレインが複数の映像信号線のうちの1本と接続している。また、各画素のTFT素子は、ゲート電極が複数の走査信号線のうちの1本と接続している。

【0005】

液晶表示装置では、画素電極と共通電極との電位差によって各画素における光の透過量または反射量あるいはその両方を制御して映像や画像を表示する。このとき、液晶表示装置では、複数の走査信号線のうちの1本の走査信号線にゲート電極が接続している複数のTFT素子をオンにし、各映像信号線に加えられている映像信号(階調電圧)を当該TFT素子を介して画素電極に書き込む、という動作が繰り返し行われる。

【0006】

またこのとき、液晶表示装置では、あらかじめ定められたフレーム期間毎に各画素の極性、言い換えると画素電極の電位と共通電極の電位との高低の関係を反転させながら、映像や画像を表示する。

【0007】

ところで、従来の液晶表示装置では、たとえば、走査信号線に加えた走査信号の波形に生じる歪み(なまり)に起因する残像が発生しやすい。この走査信号の波形の歪みによる残像は、一般に、走査信号線の信号入力端から遠い部分で発生しやすいことが知られている。このような走査信号の波形の歪みによる残像を低減する方法としては、たとえば、走査信号線の信号入力端から遠ざかるにつれて、TFT素子のゲート電極とソース電極との間に形成される寄生容量Cgsを大きくする方法が提案されている(たとえば、特許文献1を参照。)。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2004−093821号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

液晶表示パネルを製造するときには、通常、一組のマザーガラスを用いて複数枚の液晶表示パネルを一括して製造する多面取りと呼ばれる方法をとることが多い。

【0010】

一組のマザーガラスを用いて4枚の液晶表示パネルを製造する、いわゆる4面取りの場合は、一方のマザーガラスに設定された4つの領域のそれぞれに、複数の走査信号線、複数の映像信号線、複数のTFT素子、および複数の画素電極などを有する回路(薄膜積層体)を形成する。

【0011】

このとき、前記回路は、導電膜または半導体膜をエッチングする工程と、絶縁膜を形成する工程とを、所定の順序で行って形成する。

【0012】

またこのとき、絶縁膜は、通常、CVD法などの成膜法を用いて、マザーガラスの回路形成面全体に形成する。そのため、マザーガラス上に形成された絶縁膜の膜厚は、当該マザーガラスの中央部分が最も厚く、中心から遠ざかるにつれて同心円的に薄くなっていくような分布になる。

【0013】

4面取りの場合、マザーガラスの前記4つの領域に形成される回路は、通常、並進対称性を有する。したがって、一組のマザーガラスから得られる4枚の液晶表示パネルは、絶縁膜の膜厚分布が異なる。

【0014】

ところで、走査信号線は、回路的に見ると、複数の配線抵抗と複数の配線容量とを有する。走査信号線の配線容量には、たとえば、TFT素子のソース電極や画素電極との間で形成される寄生容量Cgsや、映像信号線との間で形成される寄生容量などがある。これらの寄生容量は、たとえば、走査信号線と他の導電層との間に介在する絶縁層の厚さによって変化する。そのため、1枚の液晶表示パネルにおいて寄生容量に関わる絶縁層の膜厚に分布(傾斜)があると、各走査信号線の配線容量の大きさには、絶縁層の膜厚分布に応じた違いが生じる。このように、各走査信号線の配線容量の大きさに違いが生じると、各走査信号線の時定数に違いが生じる。その結果、1枚の液晶表示パネルに形成された各走査信号線における走査信号の波形の歪み方(信号遅延)が異なってしまう。

【0015】

したがって、各画素の寄生容量Cgsの大きさを調整することで走査信号の波形の歪みによる残像を防ぐ場合は、絶縁膜の膜厚分布を考慮して、たとえば、各TFT素子におけるゲート電極(走査信号線)とソース電極との重畳面積や、ゲート電極(走査信号線)と画素電極との平面距離などを補正することが望まれる。

【0016】

また、一組のマザーガラスから得られる複数枚の液晶表示パネルは、前述のように、絶縁膜の膜厚分布が異なる。そのため、一組のマザーガラスから得られる複数枚の液晶表示パネルでは、各走査信号線における走査信号の波形の歪み方に違いが生じる。

【0017】

したがって、液晶表示パネルを多面取りで製造する場合、一組のマザーガラスから得られる個々の液晶表示パネルにおける残像を低減するとともに、複数枚の液晶表示パネル間における残像のレベル(強さの度合い)を均一化するには、面付け位置(回路を形成する領域)毎に、異なる補正をすることが望まれる。

【0018】

また、CVD法などの成膜法で絶縁膜を形成する場合は、使用するCVD装置によって、たとえば、マザーガラスの中心からの距離と膜厚の減少率との関係が異なることが多い。したがって、ある1組のレイアウトデータに基づき、異なる製造ラインで製造された複数枚の液晶表示パネル間における残像のレベルを均一化するには、使用するCVD装置における膜厚分布を考慮し、たとえば、製造ライン毎に異なる補正をすることが望まれる。

【0019】

しかしながら、寄生容量Cgsの大きさと関わりがある走査信号線やソース電極は、通常、導電膜をエッチングして形成する。導電膜をエッチングするときには、当該導電膜の上に形成した感光性材料膜を露光、現像して、所定のパターンのレジスト(エッチングレジスト)を形成する。このとき、従来の液晶表示パネルの製造方法では、導電膜の上に形成した感光性材料膜を、通常、フォトマスクを有する露光装置で露光する。

【0020】

フォトマスクを有する露光装置で、導電膜の上に形成した感光性材料膜を露光する場合、絶縁膜の膜厚分布に応じて、ゲート電極(走査信号線)とソース電極との重畳面積や、ゲート電極(走査信号線)と画素電極との平面距離などを補正すると、たとえば、面付け位置毎、製造ライン毎に露光パターンが異なるフォトマスクを作成する必要がある。そのため、従来の多面取りの液晶表示パネルの製造方法では、個々の液晶表示パネルにおける残像を低減するとともに、複数枚の液晶表示パネル間における残像の度合いを均一化することが難しく、製造効率が悪くなるという問題があった。

【0021】

本発明の目的は、個々の液晶表示パネルにおける残像を低減するとともに、複数枚の液晶表示パネル間における残像のレベルを均一化することが容易な液晶表示パネルの製造方法を提供することにある。

【0022】

本発明の他の目的は、絶縁膜の膜厚分布によらず、走査信号の波形の歪みに起因する残像が低減されている液晶表示パネルを提供することにある。

【0023】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面によって明らかになるであろう。

【課題を解決するための手段】

【0024】

本願において開示される発明のうち、代表的なものの概略を説明すれば、以下の通りである。

【0025】

(1)TFT基板と対向基板との間に液晶材料が封入された液晶表示パネルを有し、前記TFT基板は、複数の走査信号線、複数の映像信号線、複数のTFT素子、および複数の画素電極を有し、前記複数のTFT素子は、ゲート電極が前記複数の走査信号線のうちの1本の走査信号線に接続し、ドレイン電極が前記複数の映像信号線のうちの1本の映像信号線に接続しており、かつ、TFT素子毎に、前記ゲート電極が接続している前記走査信号線と前記ドレイン電極が接続している前記映像信号線との組み合わせが異なる液晶表示装置であって、前記TFT素子のソース電極は、走査信号線と重畳している部分としていない部分とを有し、1本の前記走査信号線に接続している複数のTFT素子は、当該走査信号線の信号入力端からの距離と前記ソース電極と前記走査信号線との重畳領域の面積との関係が、単調減少の関係である液晶表示装置。

【0026】

(2)前記(1)の液晶表示装置において、1本の前記映像信号線に接続している複数のTFT素子は、当該映像信号線の信号入力端からの距離と前記ソース電極と前記走査信号線との重畳領域の面積との関係が、単調減少の関係である液晶表示装置。

【0027】

(3)TFT基板を形成する工程と、対向基板を形成する工程と、前記TFT基板と前記対向基板とを貼り合わせるとともに液晶材料を封入して液晶表示パネルを形成する工程とを有し、前記TFT基板を形成する工程は、あらかじめ用意されたレイアウトデータに基づいて複数の走査信号線、複数の映像信号線、複数のTFT素子、および複数の画素電極を形成する液晶表示装置の製造方法であって、前記複数のTFT素子のソース電極は、前記画素電極と接続し、かつ、前記走査信号線と重畳させる部分とさせない部分とを有し、前記TFT基板を形成する工程は、前記複数の走査信号線を形成する第1の工程と、前記第1の工程の後、第1の絶縁層を形成する第2の工程と、前記第1の絶縁層の上に、前記TFT素子の半導体層、前記複数の映像信号線、および前記TFT素子のソース電極を形成する第3の工程を有し、前記第1の工程は、導電膜を形成する工程と、前記導電膜の上に感光性材料膜を形成する工程と、前記感光性材料膜を露光、現像する工程と、現像した前記感光性材料膜をマスクにして前記導電膜の不要な部分を除去する工程を有し、前記感光性材料膜の露光は、前記レイアウトデータに基づいて作成される描画データによる数値制御で露光パターンを生成する空間光変調素子を有する露光装置を用いて行い、前記描画データは、前記レイアウトデータにおける前記走査信号線のうちの、前記ソース電極と重畳させる部分の形状が、前記第2の工程で形成される前記第1の絶縁層の膜厚の分布に応じた面積になるように補正して作成する液晶表示装置の製造方法。

【0028】

(4)前記(3)の液晶表示装置の製造方法において、前記TFT基板を形成する工程は、1枚のマザー基板を用いて複数枚のTFT基板を一括して形成し、前記第1の工程で行う前記感光性材料膜の露光は、前記マザー基板上における前記TFT基板の位置毎に、異なる前記描画データを用いて行う液晶表示装置の製造方法。

【発明の効果】

【0029】

本発明の液晶表示装置の製造方法によれば、個々の液晶表示パネルにおける残像を低減するとともに、複数枚の液晶表示パネル間における残像のレベルを均一化することが容易である。

【0030】

また、本発明の液晶表示装置によれば、液晶表示パネルの絶縁膜の膜厚分布によらず、走査信号の波形の歪みに起因する残像が低減される。

【図面の簡単な説明】

【0031】

【図1】液晶表示装置の概略構成の一例を示す模式ブロック図である。

【図2】TFT基板における画素の平面構成の一例を示す模式平面図である。

【図3】図2のA−A’線における液晶表示パネルの断面構成の一例を示す模式断面図である。

【図4】図2および図3に示した画素の模式等価回路図である。

【図5】走査信号線の模式等価回路図である。

【図6】走査信号線の信号入力端からの距離が異なる2つの画素における画素電極の電位の変動の様子の一例を示す模式図である。

【図7】4面取りの場合のTFT基板として切り出す領域と絶縁層の膜厚分布との関係の一例を示す模式平面図である。

【図8】図7の領域AR1に形成された走査信号線および領域AR2に形成された走査信号線における走査信号の遅延量の一例を示す模式図である。

【図9】図7の領域AR1のTFT基板を有する液晶表示パネルおよび領域AR2のTFT基板を有する液晶表示パネルにおける最適なVcom値の分布の一例を示す模式図である。

【図10】図7の領域AR1のTFT基板を有する液晶表示パネルおよび領域AR2のTFT基板を有する液晶表示パネルにおける残像の傾向を示す模式図である。

【図11】信号入力端からの距離と寄生容量Cgsの大きさとの関係を示す模式図である。

【図12】寄生容量Cgsの調整方法の一例を示す模式図である。

【図13】領域AR1に形成されたTFT基板における信号入力端の位置と絶縁層の膜厚分布との関係を示す模式平面図である。

【図14】領域AR1に形成されたTFT基板における絶縁層の膜厚の変動量の一例を示す模式図である。

【図15】図13に示した3本の走査信号線に接続している画素の寄生容量Cgsの補正量の一例を示す模式図である。

【図16】補正後のレイアウトデータにおける4隅の画素の補正パターンの一例を示す模式図である。

【図17】領域AR2に形成されたTFT基板における信号入力端の位置と絶縁層の膜厚分布との関係を示す模式平面図である。

【図18】図17に示した映像信号線に接続している画素の寄生容量Cgsの補正量の一例を示す模式図である。

【図19】補正後のレイアウトデータにおける4隅の画素の補正パターンの一例を示す模式図である。

【図20】本実施例の製造方法の作用効果の一例を示す模式図である。

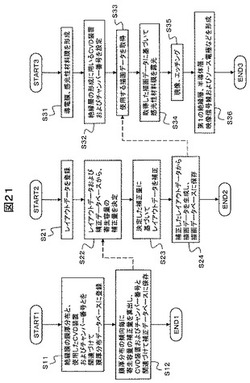

【図21】本実施例の液晶表示パネルの製造方法の主要部を説明するための模式フロー図である。

【発明を実施するための形態】

【0032】

以下、本発明について、図面を参照して実施の形態(実施例)とともに詳細に説明する。

なお、実施例を説明するための全図において、同一機能を有するものは、同一符号を付け、その繰り返しの説明は省略する。

【0033】

図1乃至図3は、本発明に関わる液晶表示装置の概略構成の一例を説明するための模式図である。

図1は、液晶表示装置の概略構成の一例を示す模式ブロック図である。図2は、TFT基板における画素の平面構成の一例を示す模式平面図である。図3は、図2のA−A’線における液晶表示パネルの断面構成の一例を示す模式断面図である。

【0034】

本発明に関わる液晶表示装置は、たとえば、図1に示すように、液晶表示パネル1、第1の駆動回路2、第2の駆動回路3、および制御回路4を有する。また、本発明に関わる液晶表示装置は、そのほかに、たとえば、バックライトユニットなどを有する。

【0035】

液晶表示パネル1は、TFT基板5と対向基板6との間に液晶材料が封入された表示パネルである。また、液晶表示パネル1は、アクティブマトリクス型であり、TFT基板5は、複数の走査信号線GLおよび複数の映像信号線DLを有する。また、液晶表示パネル1の表示領域は、TFT素子、画素電極、共通電極、および液晶層(液晶材料)を有する画素の集合でなる。

【0036】

TFT基板5は、たとえば、図2および図3に示すように、ガラス基板などの第1の絶縁基板501、第1の絶縁基板501の液晶層7と対向する面に形成された第1の薄膜積層体、および第1の偏光板8を有する。

【0037】

第1の薄膜積層体は、走査信号線GL、保持容量線502、第1の絶縁層503、TFT素子の半導体層504、映像信号線DL、TFT素子のソース電極505、第2の絶縁層506、画素電極PX、および第1の配向膜507などを有する。

【0038】

一方、対向基板6は、たとえば、図3に示すように、ガラス基板などの第2の絶縁基板601、第2の絶縁基板601の液晶層7と対向する面に形成された第2の薄膜積層体、および第2の偏光板9を有する。

【0039】

第2の薄膜積層体は、ブラックマトリクス602、カラーフィルタ603、平坦化層604、共通電極CT、および第2の配向膜605などを有する。

【0040】

第1の駆動回路2は、各画素の画素電極PXに加える階調電圧を生成し、各映像信号線DLに出力する回路であり、一般に、データドライバなどと呼ばれている。また、第2の駆動回路3は、第1の駆動回路2から各映像信号線DLに加えられた階調電圧を書き込む画素(画素電極PX)を選択するための走査信号を生成し、各走査信号線GLに出力する回路であり、一般に、ゲートドライバ、走査ドライバなどと呼ばれている。また、制御回路4は、第1の駆動回路2の動作、第2の駆動回路3の動作、および共通電極CTに加える電圧などの制御をする回路であり、一般に、TFTコントローラ、T−CONなどと呼ばれている。

【0041】

本発明に関わる液晶表示装置の動作は、基本的には、従来の液晶表示装置と同じでよい。そのため、第1の駆動回路2、第2の駆動回路3、および制御回路4の具体的な構成や、液晶表示装置の動作に関する説明は省略する。

【0042】

図4乃至図6は、従来の液晶表示装置における残像の発生要因の一例を説明するための模式図である。

図4は、図2および図3に示した画素の模式等価回路図である。図5は、走査信号線の模式等価回路図である。図6は、走査信号線の信号入力端からの距離が異なる2つの画素における画素電極の電位の変動の様子の一例を示す模式図である。

【0043】

図2および図3に示した画素の等価回路は、たとえば、図4のように表すことができ、TFT素子10、画素容量CLC、および保持容量CSTGを有する。

【0044】

TFT素子10は、ゲート電極が走査信号線GLに接続しており、ドレイン電極が映像信号線DLに接続している。また、TFT素子10のソース電極505は、画素電極PXに接続している。このとき、TFT素子10のソースとドレインとは、映像信号線DLの電位と画素電極PXの電位との高低の関係によって決まるが、本明細書では、映像信号線DLに接続しているほうをドレインと呼び、画素電極PXに接続しているほうをソースと呼ぶ。

【0045】

画素容量CLCは、画素電極PX、共通電極CT、および液晶層7により形成される容量であり、液晶容量などと呼ぶこともある。画素容量CLCは、画素電極PXと共通電極CTとの電位差に応じて液晶層7の配向状態が変化する。これにより、バックライトユニットからの光の透過光量が制御される。

【0046】

保持容量CSTGは、画素電極PX、保持容量線502、および介在する絶縁層(第1の絶縁層503および第2の絶縁層506)により形成される容量であり、補助容量、蓄積容量などと呼ぶこともある。保持容量CSTGは、TFT素子10がオフの期間の画素電極PXの電位を保持するための容量である。なお、保持容量CSTGの形成方法には、種々の方法がある。

【0047】

また、図2および図3に示したような構成の画素は、画素容量CLCおよび保持容量CSTGの他に、たとえば、寄生容量Cgsを有する。寄生容量Cgsは、TFT素子10のゲート電極(走査信号線GL)とソース電極505との間で形成される容量である。また、図2および図3に示したような構成の画素は、そのほかにも、たとえば、TFT素子10のゲート電極(走査信号線GL)とドレイン電極(映像信号線DL)との間に形成される寄生容量なども有する。

【0048】

寄生容量は、画素容量CLCおよび保持容量CSTGとは異なり、画素の動作(透過光量の制御)には不要な容量である。しかしながら、TFT基板5の構成上、これらの寄生容量が形成されることは避けられない。

【0049】

このように、アクティブマトリクス型の液晶表示装置では、走査信号線GLを一方の電極とする寄生容量Cgsなどが形成される。また、走査信号線GLは、たとえば、アルミニウムなどの金属で形成されており、電気抵抗を有する。

【0050】

したがって、1本の走査信号線GLは、回路的に見ると、たとえば、図5に示すように、複数の配線抵抗Rm(m=1,2,3,…,M)と複数の配線容量(寄生容量)Cpmとを有する。そのため、第2の駆動回路3から走査信号線GLに加えた走査信号の波形には、配線抵抗Rmおよび配線容量Cpmによる歪みが生じる。また、この走査信号の波形の歪みは、走査信号線GLの信号入力端から遠くなるほど大きくなる。なお、図5において、1つの配線抵抗Rmは、1画素分の配線抵抗であり、1つの配線容量Cpmは1画素分の寄生容量の合成容量である。

【0051】

バックライトユニットを有する液晶表示装置では、各画素における光の透過光量を制御することで、バックライトユニットからの光(面状光線)を変調し、映像や画像を表示する。このとき、光の透過光量は、画素電極PXと共通電極CTとの電位差によって制御する。またこのとき、一般的な液晶表示装置では、画素電極PXに加える階調電圧の極性、すなわち画素電極PXの電位と共通電極CTの電位との高低の関係を、あらかじめ定められたフレーム期間毎(たとえば、1フレーム期間毎)に反転させることで、フリッカや残像などの発生を抑えている。

【0052】

しかしながら、従来の液晶表示装置では、たとえば、上記の走査信号の波形の歪みや寄生容量Cgsなどの影響による残像が発生する。

【0053】

図2および図3に示したような構成の画素を有する従来の液晶表示装置において、走査信号線GLの信号入力端からの距離が異なる2つの画素の画素電極PXに同じ電位VKの階調電圧を書き込む場合、ゲート電極の電位および画素電極PXの電位は、それぞれ、たとえば、図6に示すような時間変化をする。

【0054】

なお、図6において、左側のVG1、VDL1、およびVPX1は、それぞれ、信号入力端から近い位置にある第1の画素U1のゲート電極の電位、ドレイン電極(映像信号線DL)の電位、および画素電極PXの電位の時間変化を示す波形である。また、図6において、右側のVG2、VDL2、およびVPX2は、それぞれ、信号入力端から遠い位置にある第2の画素U2のゲート電極の電位、ドレイン電極(映像信号線)の電位、および画素電極PXの電位の時間変化を示す波形である。また、図6において、Vcom1およびVcom2は、それぞれ、第1の画素PX1および第2の画素PX2における最適コモン電圧である。なお、最適コモン電圧とは、画素電極PXと共通電極CTの電位差が設計段階で定められた所定の値ΔVになるようにするためのコモン電圧のことである。

【0055】

アクティブマトリクス型の液晶表示装置において、画素の透過光量を制御するときには、TFT素子10をオンにする期間と同期させてドレイン電極に階調電圧を加え、当該階調電圧を画素電極PXに書き込む。

【0056】

第2の駆動回路3から走査信号線GLに加わる走査信号の波形は、たとえば、図6に点線で示したような矩形である。しかしながら、走査信号線GLに加えられた走査信号には、前述のように、信号入力端からの距離に応じた歪み(遅延)が生じる。このとき、第1の画素U1のゲート電極および第2の画素U2のゲート電極の電位は、それぞれ、波形VG1および波形VG2のような時間変化をする。すなわち、第2の画素U2のゲート電極に加わる走査信号の波形VG2は、第1の画素U1のゲート電極に加わる走査信号の波形VG1よりも歪みが大きくなる。

【0057】

また、第1の画素U1のドレイン電極に加わる階調電圧の電位および第2の画素U2のドレイン電極に加わる階調電圧の電位は、それぞれ、波形VDL1および波形VDL2のような時間変化をする。すなわち、第1の画素U1のドレイン電極の電位および第2の画素U2のドレイン電極の電位は、それぞれ、ゲート電極の電位が上昇するタイミングと同期して、所定の電位VKに変化する。

【0058】

このとき、第1の画素U1の画素電極PXの電位および第2の画素U2の画素電極PXの電位は、それぞれ、波形VPX1および波形VPX2のような時間変化をする。すなわち、第1の画素U1の画素電極PXの電位および第2の画素U2の画素電極PXの電位は、それぞれ、TFT素子10がオンからオフに切り替わる時点、言い換えるとゲート電極の電位の下降が始まる時点で、それぞれ、ドレイン電極(階調電圧)の電位VKと概ね同じ電位になる。

【0059】

また、液晶表示パネル1における画素の構成が、図2および図3に示したような構成である場合は、TFT素子10がオンからオフに切り替わるときに、たとえば、上記の寄生容量Cgsを介した飛び込み電圧の影響により、画素電極PXの電位に変動が生じる。このTFT素子10がオンからオフに切り替わるときに生じる画素電極PXの電位の変動量は、一般に、フィードスルー電圧と呼ばれる。

【0060】

フィードスルー電圧の大きさは、通常、走査信号線GLの信号入力端から遠い画素ほど小さくなる。そのため、第2の画素U2におけるフィードスルー電圧VFT2は、第1の画素U1におけるフィードスルー電圧VFT1よりも小さくなる。

【0061】

したがって、第1の画素U1と第2の画素U2とでは、画素電極PXと共通電極CTとの電位差を所定の値ΔVにするためのコモン電圧(最適コモン電圧Vcom1,Vcom2)の電位が異なる。また、1本の走査信号線GLには、多数の画素のTFT素子10が接続しており、それらの画素におけるフィードスルー電圧の大きさは、走査信号線GLの信号入力端からの距離によって異なる。そのため、これらの画素の画素電極PXに電位VKの階調電圧を書き込む場合、各画素における最適コモン電圧の電位は、走査信号線GLの信号入力端からの距離によって異なる。

【0062】

しかしながら、共通電極CTに加えるコモン電圧Vcomは、ある所定の電位である。そのため、複数の画素に電位VKの階調電圧を書き込む場合、各画素における最適コモン電圧と、共通電極CTに加わっているコモン電圧Vcomとの電位差に違いが生じ、ある領域では電位差が小さくなり、別の部分では電位差が大きくなる。そして、従来の液晶表示装置では、この最適コモン電圧と共通電極CTに加わっているコモン電圧Vcomとの電位差に相当する電圧が直流成分となり、残像が発生する。

【0063】

なお、液晶表示装置における残像の発生要因には、上記の直流成分以外にも種々の要因があるが、以下の説明における残像は、上記の直流成分により生じる残像のこととする。

【0064】

このような残像を低減する方法としては、従来、たとえば、前述の直流成分をキャンセルする電圧(DCオフセット電圧)を階調電圧に付加する方法や、各画素におけるフィードスルー電圧の差が小さくなるように寄生容量Cgsの大きさを調整する方法が知られている。

【0065】

ところで、液晶表示パネル1を製造するときには、通常、1組のマザーガラスを用いて複数枚の液晶表示パネル1を一括製造する多面取りと呼ばれる方法がとられる。

【0066】

液晶表示パネル1を多面取りで製造する場合は、1組のマザーガラスのうちの一方のマザーガラスに設定された複数の領域のそれぞれに、たとえば、走査信号線GL、映像信号線DL、TFT素子10、および画素電極PXなどを有する回路(第1の薄膜積層体)を形成する。

【0067】

このとき、1枚のマザーガラス11に設定されたそれぞれの領域に、たとえば、ある1つのレイアウトデータに基づいて第1の薄膜積層体を形成すると、当該マザーガラス11から切り出されたTFT基板5を有する複数枚の液晶表示パネル1は、同じ条件で駆動させたときに生じる残像の傾向が概ね等しくなると考えられる。しかしながら、従来の多面取りの製造方法では、1組のマザーガラスから切り出された複数枚の液晶表示パネル1を同じ条件で駆動させたときに、それぞれの液晶表示パネル1における残像の傾向に違いが生じる。なお、残像の傾向というのは、走査信号線GLや映像信号線DLの信号入力端の位置と残像が強く出る位置との関係や、残像のレベル(強さの度合い)のことである。

【0068】

したがって、上記のようにDCオフセット電圧を階調電圧を付加したり、寄生容量Cgsの大きさを調節したりして残像を抑制する場合は、液晶表示パネル1毎に異なる残像の傾向を考慮する必要がある。

【0069】

液晶表示パネル1を4面取りで製造する場合、1組のマザーガラスから得られる4枚の液晶表示パネル1における残像の傾向には、以下のような関係がある。

【0070】

図7乃至図10は、多面取りで製造した複数枚の液晶表示パネルに生じる残像の傾向とレベルの違いを説明するための模式図である。

図7は、4面取りの場合のTFT基板として切り出す領域と絶縁層の膜厚分布との関係の一例を示す模式平面図である。図8は、図7の領域AR1に形成された走査信号線および領域AR2に形成された走査信号線における走査信号の遅延量の一例を示す模式図である。図9は、図7の領域AR1のTFT基板を有する液晶表示パネルおよび領域AR2のTFT基板を有する液晶表示パネルにおける最適なVcom値の分布の一例を示す模式図である。図10は、図7の領域AR1のTFT基板を有する液晶表示パネルおよび領域AR2のTFT基板を有する液晶表示パネルにおける残像の傾向を示す模式図である。

【0071】

液晶表示パネル1を4面取りで製造する場合は、たとえば、図7に示すように、1組のマザーガラスのうちの一方のマザーガラス11に4つの領域AR1,AR2,AR3,AR4が設定され、当該4つの領域AR1,AR2,AR3,AR4のそれぞれに、たとえば、走査信号線GL、映像信号線DL、TFT素子10、および画素電極PXなどを有する回路(第1の薄膜積層体)が形成される。

【0072】

また、ある1つのレイアウトデータに基づいて4つの領域AR1,AR2,AR3,AR4のそれぞれに第1の薄膜積層体を形成したときには、通常、当該4つの領域AR1,AR2,AR3,AR4に形成される回路が並進対称性を有する。

【0073】

しかしながら、多面取りの製造方法において第1の絶縁層503などの絶縁層を形成するときには、通常、CVD法などの成膜法でマザーガラス11の表面全体に形成する。このとき、マザーガラス11に形成(成膜)される絶縁層の膜厚は、図7に二点差線で示したような、マザーガラス11の中心部分が最も厚くなり、中心から遠ざかるにつれて同心円状に徐々に薄くなっていく同心円状の分布になる。そのため、4つの領域AR1,AR2,AR3,AR4のそれぞれに形成された第1の薄膜積層体は、走査信号線GLの信号入力端および映像信号線DLの信号入力端の位置と、絶縁層の膜厚分布との関係に違いがある。

【0074】

液晶表示パネル1を製造するときに使用するレイアウトデータでは、通常、各画素におけるソース電極505の寸法や、走査信号線GLとソース電極505との重畳領域の面積などが同じ値である。そのため、1枚のTFT基板5における絶縁層の膜厚に二次元的な分布があると、各画素の寄生容量Cgsの大きさには、絶縁層の膜厚分布を反映する違いが生じる。

【0075】

また、領域AR1に形成された走査信号線GLと領域AR2に形成された走査信号線GLとでは、信号入力端から他端に向かって見たときの配線容量の大きさの組み合わせ、すなわち時定数が異なる。したがって、領域AR1に形成された走査信号線GLと領域AR2に形成された走査信号線GLとでは、たとえば、図8に示すように、信号入力端からの距離と走査信号の遅延量との関係に違いが生じる。なお、図8は、横軸が信号入力端からの距離の相対値、縦軸が走査信号の遅延量のグラフである。また、図8のグラフの縦軸は、上にいくほど遅延量が大きくなる。また、図8の曲線F1および曲線F2は、それぞれ、領域AR1に形成された走査信号線GLにおける走査信号の遅延量、および領域AR2に形成された走査信号線GLにおける走査信号の遅延量を示している。また、図8の区間DAxは、走査信号線GLのうちの表示領域を通る部分である。

【0076】

またさらに、1枚のTFT基板5に形成された絶縁層の膜厚に二次元的な分布があると、それぞれの走査信号線における信号入力端からの距離と走査信号の遅延量との関係にも違いが生じる。

【0077】

液晶表示パネル1の残像と関係があるフィードスルー電圧の大きさは、主として、寄生容量Cgsの大きさと、寄生容量Cgsの大きさによる走査信号の遅延量(ゲート電極の電位の波形の歪み)によって決まる。また、寄生容量Cgsの大きさは、絶縁層の厚さによって変化する。

【0078】

したがって、ある1つのレイアウトデータに基づいて4面取りで製造した4枚の液晶表示パネル1を同じ条件で駆動させると、残像の傾向に違いが生じる。このとき、4枚の液晶表示パネル1の残像にどのような傾向があるかについては、後述する。

【0079】

液晶表示パネル1を駆動させたときに生じる残像のレベルは、たとえば、最低階調(たとえば、黒)で表示するときの最適コモン電圧VcomBと、最高階調(たとえば、白)で表示するときの最適コモン電圧VcomWとの差で定義される。

【0080】

ところで、絶縁層の膜厚に二次元的な分布があるTFT基板5の液晶表示パネル1は、走査信号の遅延量と寄生容量Cgsの大きさとの組み合わせが画素毎に異なる。そのため、1枚の液晶表示パネル1における最適コモン電圧VcomB,VcomWは、画素毎に異なる。

【0081】

そこで、本願発明者らは、まず、液晶表示パネル1毎に、最低階調で表示するときの最適コモン電圧VcomBの面内分布と、最高階調で表示するときの最適コモン電圧VcomWの面内分布とを調べた。

【0082】

このとき、領域AR1に形成された回路(TFT基板5)を有する第1の液晶表示パネル1と、領域AR2に形成された回路(TFT基板5)を有する第2の液晶表示パネル1とでは、最適コモン電圧VcomB,VcomWの面内分布に、たとえば、図9に示したような違いが生じる。

【0083】

なお、図9の縦軸は、1枚の液晶表示パネル1における共通電極PXの電位の最適値の最大値と最小値との差である。また、図9の点P1および点P2は、それぞれ、第1の液晶表示パネル1の各画素における最適コモン電圧VcomBの最大値と最小値の差および最適コモン電圧VcomWの最大値と最小値の差である。また、図9の点P3および点P4は、それぞれ、第2の液晶表示パネル1の各画素における最適コモン電圧VcomBの最大値と最小値の差および最適コモン電圧VcomWの最大値と最小値の差である。また、図9の点P5および点P6は、それぞれ、4枚の液晶表示パネル1における最適コモン電圧VcomBの最大値と最小値の差の平均値および最適コモン電圧VcomWの最大値と最小値の差の平均値である。

【0084】

液晶表示パネル1を駆動させたときに生じる残像のレベルは、たとえば、図9に示した最適コモン電圧VcomBの差と最適コモン電圧VcomWの差との差ΔSに相当する。そのため、第1の液晶表示パネル1と、第2の液晶表示パネル1とでは、第1の液晶表示パネル1のほうが残像のレベルが大きくなる。

【0085】

また、第1の液晶表示パネル1および第2の液晶表示パネル1について、走査信号線GLの延伸方向に並んでいる各画素における走査信号線GLの信号入力端からの距離と、最適コモン電圧VcomB,VcomBの差との関係を調べると、たとえば、図10に示すような関係になる。

【0086】

なお、図10は、横軸が画素の識別子m、縦軸が最適コモン電圧VcomB,VcomWの差を示すグラフであり、縦軸は上に行くほど値が大きくなる。また、図10の横軸の識別子mは、1本の走査信号線GLに接続しているM個の画素(TFT素子10)を区別する整数値であり、走査信号線GLの信号入力端に最も近い画素から順に、1,2,3,・・・,Mとしている。

【0087】

また、図10の曲線F3は、第1の液晶表示パネル1における走査信号線GLの信号入力端からの距離と、最適コモン電圧VcomB,VcomWの差との関係を示す分布曲線である。また、図10の曲線F4は、第2の液晶表示パネル1における走査信号線GLの信号入力端からの距離と、最適コモン電圧VcomB,VcomWの差との関係を示す分布曲線である。また、図10の曲線F5は、絶縁層の膜厚が面内で均一な液晶表示パネル(以下、レイアウトデータ通りの液晶表示パネルという)における走査信号線GLの信号入力端からの距離と、最適コモン電圧VcomB,VcomWの差との関係を示す分布曲線である。また、図10では、曲線F3、曲線F4、および曲線F5の関係をわかりやすくするために上下方向にずらして示している。

【0088】

また、図10に示した曲線F3、曲線F4、および曲線F5は、それぞれ、第1の液晶表示パネル1、第2の液晶表示パネル1、およびレイアウトデータ通りの液晶表示パネルを同じ条件で駆動させたときの分布曲線である。

【0089】

図10を見ると、第1の液晶表示パネル1および第2の液晶表示パネル1は、同じ条件で駆動したときに、走査信号線GLの信号入力端から遠い画素ほど最適コモン電圧VcomB,VcomWの差が小さくなる。そのため、第1の液晶表示パネル1および第2の液晶表示パネル1は、走査信号線GLの信号入力端から遠い画素ほど残像のレベルが弱くなる。したがって、第1の液晶表示パネル1と第2の液晶表示パネル1とでは、走査信号線GLの延伸方向で見た残像の傾向が同じ傾向である。

【0090】

しかしながら、第1の液晶表示パネル1は、信号入力端から最も近い位置にある画素の最適コモン電圧の差と最も遠い位置にある画素の最適コモン電圧の差との差ΔS3が、レイアウトデータ通りの液晶表示パネルにおける差ΔS5よりも大きくなる。すなわち、第1の液晶表示パネル1は、走査信号線GLの延伸方向で見た残像のレベルが、レイアウトデータ通りの液晶表示パネルよりも強くなる。

【0091】

これに対し、第2の液晶表示パネル1は、信号入力端から最も近い位置にある画素の最適コモン電圧の差と最も遠い位置にある画素の最適コモン電圧の差との差ΔS4が、レイアウトデータ通りの液晶表示パネルにおける差Δ5よりも小さくなる。すなわち、第2の液晶表示パネル1は、走査信号線GLの延伸方向で見た残像のレベルが、レイアウトデータ通りの液晶表示パネルよりも弱くなる。

【0092】

また、図を用いた詳細な説明は省略するが、第1の液晶表示パネル1および第2の液晶表示パネル2は、映像信号線DLの延伸方向でみたときの残像のレベルが、レイアウトデータ通りの液晶表示パネルとは異なる。

【0093】

また、図を用いた詳細な説明は省略するが、領域AR3に形成された回路を有する第3の液晶表示パネル1および領域AR4に形成された回路を有する第4の液晶表示パネル1についても同様のことが言え、走査信号線GLの延在方向で見たときの残像のレベルや、映像信号線DLの延伸方向でみたときの残像のレベルが、レイアウトデータ通りの液晶表示パネルとは異なる。

【0094】

以上の結果をまとめると、4面取りで製造された4枚の液晶表示パネル1における残像の傾向は、たとえば、下記の表1のようになる。

【0095】

【表1】

【0096】

なお、表1において、SPECxは走査信号線GLの延在方向で見たときの残像のレベルであり、SPECyは映像信号線DLの延在方向で見たときの残像のレベルである。また、表1において、丸印はレイアウトデータ通りの液晶表示パネルよりも残像のレベルが弱いことを意味し、×印はレイアウトデータ通りの液晶表示パネルよりも残像のレベルが強いことを意味する。

【0097】

このように、4面取りで製造された4枚の液晶表示パネル1は、同じ条件で駆動させたときに生じる残像の傾向が異なる。

【0098】

DCオフセット電圧を階調電圧に付加して残像を抑制する場合は、たとえば、液晶表示パネル1に生じる残像の傾向に合わせて、第1の駆動回路2の階調電圧生成回路を調整する。そのため、4面取りで製造された液晶表示パネル1を有する液晶表示装置の残像を傾向を均一化するには、第1の駆動回路2の調整方法が4通り必要になる。

【0099】

一方、寄生容量Cgsの大きさを調整して残像を抑制する場合は、たとえば、液晶表示パネル1に生じる残像の傾向にあわせて、走査信号線GLとソース電極505との重畳領域の面積や、走査信号線GLと画素電極PXとの平面距離などを補正する。そのため、4面取りで製造された液晶表示パネル1を有する液晶表示装置の残像を傾向を均一化するには、1つのレイアウトデータに対して4通りの補正が必要になる。

【0100】

また、従来の液晶表示パネル1の製造方法において、走査信号線GL、ソース電極505、および画素電極PXなどの導体パターンは、通常、エッチングで形成している。エッチングで導体パターンを形成するときには、マザーガラス11の表面全体に形成(成膜)された導電膜の上にレジストパターンを形成する。このとき、レジストパターンは、フォトリソグラフィー、すなわち導電膜上に形成した感光性材料膜を露光、現像して形成する。またこのとき、感光性材料膜は、通常、フォトマスクを有する露光装置で露光する。そのため、従来の液晶表示パネル1の製造方法では、レイアウトデータを補正した場合、補正後のレイアウトデータに基づいてフォトマスクを作製する必要がある。したがって、4面取りの製造方法において領域毎に個別に露光する場合は、露光パターンが異なる4枚のフォトマスクを作製する必要がある。また、4面取りの製造方法において4つの領域を一括で露光する場合は、1枚のフォトマスクの4つの領域に、異なる露光パターンを形成する必要がある。

【0101】

また、絶縁層をCVD法などの成膜法で形成する場合、膜厚の分布、すなわちマザーガラス11の中心からの距離と膜厚の変動量との関係は、たとえば、使用するCVD装置やチャンバーによって変化する。

【0102】

そのため、従来の多面取りの液晶表示パネルの製造方法に、従来の残像の抑制方法を適用すると、絶縁層の膜厚に生じるに二次元的な分布が異なる液晶表示パネルを有する液晶表示装置における残像の傾向を均一化させることが難しく、液晶表示装置の製造効率の低下や製造コストの上昇が懸念される。

【0103】

本発明の液晶表示パネルの製造方法は、上記のような懸念を鑑みてなされたものであり、絶縁層の膜厚に生じるに二次元的な分布が異なる液晶表示パネルを有する液晶表示装置間の残像の傾向を均一化させることが容易であり、液晶表示装置の製造効率の低下や製造コストの上昇を抑えることができる。

【実施例】

【0104】

図11および図12は、本発明による一実施例の液晶表示パネルの製造方法の原理を説明するための模式図である。

図11は、信号入力端からの距離と寄生容量Cgsの大きさとの関係を示す模式図である。図12は、寄生容量Cgsの調整方法の一例を示す模式図である。

【0105】

本実施例では、図7に示したような4面取りの液晶表示パネルの製造方法を挙げ、一組のマザーガラスから得られる4枚の液晶表示パネルにおける残像のレベルを均一化する方法について説明する。また、4枚の液晶表示パネル1には、それぞれ、図2および図3に示したような構成の画素を形成する。

【0106】

4面取りで製造された液晶表示パネルのうちの、領域AR1に形成された回路(TFT基板5)を有する第1の液晶表示パネル1、および領域AR2に形成された回路(TFT基板5)を有する第2の液晶表示パネル1は、それぞれ、走査信号線GLの延在方向でみた各画素の寄生容量Cgsの大きさに、たとえば、図11に示すような変動がある。

【0107】

なお、図11は、横軸が画素の識別子m、縦軸が寄生容量Cgsの大きさを示すグラフであり、縦軸は上に行くほど値が大きくなる。また、図11の横軸の識別子mは、1本の走査信号線GLに接続しているM個の画素(TFT素子10)を区別する整数値であり、走査信号線GLの信号入力端に最も近い画素から順に、1,2,3,・・・,Mとしている。

【0108】

また、図11の直線F6は、絶縁層の膜厚が面内で均一な液晶表示パネル(レイアウトデータ通りの液晶表示パネル)における走査信号線GLの信号入力端からの距離と寄生容量Cgsとの関係を示す分布曲線である。また、図11の曲線F7は、第1の液晶表示パネル1における走査信号線GLの信号入力端からの距離と寄生容量Cgsとの関係を示す分布曲線である。また、図11の曲線F8は、第2の液晶表示パネル1における走査信号線の信号入力端からの距離と寄生容量Cgsとの関係を示す分布曲線である。また、図11の曲線F9は、残像の発生を抑えるのに最適な、走査信号線GLの信号入力端からの距離と寄生容量Cgsとの関係の一例を示す分布曲線である。

【0109】

レイアウトデータを作製するときには、通常、絶縁膜の膜厚が面内で均一であるとしている。そのため、レイアウトデータ通りに製造された液晶表示パネル1は、走査信号線GLの延伸方向で見たときの、走査信号線の信号入力端からの距離と寄生容量Cgsとの関係が、図11に示した直線F6のように、一定の関係になる。

【0110】

これに対し、第1の液晶表示パネル1は、走査信号線GLの延伸方向に沿った膜厚が、信号入力端から遠ざかるにつれて薄くなる。そのため、上記のレイアウトデータに基づいて第1の薄膜積層体を形成した場合、第1の液晶表示パネル1における走査信号線GLの信号入力端からの距離と寄生容量Cgsとの関係は、図11に示した曲線F7のように、信号入力端からの距離が遠くなるにつれて寄生容量Cgsが大きくなる関係になる。

【0111】

また、第2の液晶表示パネル1は、走査信号線GLの延伸方向に沿った膜厚が、信号入力端から遠ざかるにつれて厚くなる。そのため、上記のレイアウトデータに基づいて第1の薄膜積層体を形成した場合、第2の液晶表示パネル1における走査信号線GLの信号入力端からの距離と寄生容量Cgsとの関係は、図11に示した曲線F8のように、信号入力端からの距離が遠くなるにつれて寄生容量Cgsが小さくなる関係になる。

【0112】

また、特許文献1などによると、走査信号の遅延による残像を低減するためには、走査信号線GLの延伸方向に沿って並んだ画素における寄生容量Cgsの関係が、たとえば、図11に示した曲線F9のような関係になるようにすることが望ましいとされている。

【0113】

したがって、第1の液晶表示パネル1および第2の液晶表示パネル1における走査信号線の延伸方向に沿った残像のレベルを低減するには、それぞれ、曲線F7および曲線F8が、曲線F9になるようにすればよい。

【0114】

第1の絶縁層503などの絶縁層は、CVD法などの成膜法で形成するので、膜厚を面内で均一にすることが難しい。そのため、本実施例の液晶表示パネルの製造方法では、絶縁層の膜厚分布を考慮して、各画素の寄生容量Cgsの電極面積を調整し、信号入力端からの距離と寄生容量Cgsの大きさとの関係を曲線F9のような関係にする。

【0115】

また、本実施例の液晶表示パネル1では、たとえば、図12に示すように、走査信号線GLのうちの、ソース電極505との重畳領域に補正パターンRPを設けて、各画素の寄生容量Cgsの大きさを調整する。

【0116】

図13乃至図16は、領域AR1に形成される画素の寄生容量Cgsの補正方法の一例を示す模式図である。

図13は、領域AR1に形成されたTFT基板における信号入力端の位置と絶縁層の膜厚分布との関係を示す模式平面図である。図14は、領域AR1に形成されたTFT基板における絶縁層の膜厚の変動量の一例を示す模式図である。図15は、図13に示した3本の走査信号線に接続している画素の寄生容量Cgsの補正量の一例を示す模式図である。図16は、補正後のレイアウトデータにおける4隅の画素の補正パターンの一例を示す模式図である。

【0117】

領域AR1に形成される絶縁層は、たとえば、図13に示すように、走査信号線GLの信号入力端GINから遠ざかるにつれて薄くなり、かつ、映像信号線DLの信号入力端DINから遠ざかるにつれて薄くなる。このとき、絶縁層の膜厚が最も薄くなる画素は、走査信号線の信号入力端GINから最も遠く、かつ、映像信号線の信号入力端DINから最も遠い位置にある画素U6である。すなわち、各画素における走査信号線GLとソース電極505との重畳領域の面積が等しい場合、寄生容量Cgsが最も大きくなるのは、画素U6である。

【0118】

したがって、図12に示したような補正パターンを付加することで各画素の寄生容量Cgsを調整する場合は、画素U6における寄生容量Cgsの大きさを基準にして調整する。

【0119】

領域AR1において、画素U6における絶縁層の厚さを基準膜厚にした場合、基準膜厚と、表示領域内にある各画素U1,U2,U3,U4,U5,U6における絶縁層の厚さとの差の関係は、たとえば、図14に示すような関係になる。なお、図14の縦軸は、絶縁膜の厚さの差である。

【0120】

このとき、映像信号線DLの信号入力端DINから最も遠い位置にある走査信号線GLNに接続されている画素の寄生容量Cgsの分布を、図11に示した曲線F9のようにするには、たとえば、画素U6における寄生容量Cgsを基準にし、当該走査信号線GLNに接続されている各画素の寄生容量Cgsを決める。走査信号線GLNの上における絶縁層の膜厚は、図14に示した点線ような変化をしている。そのため、領域AR1では、映像信号線DLの信号入力端DINから最も遠い位置にある走査信号線GLNに接続されている画素の寄生容量Cgsの分布を、たとえば、図15に示した曲線F10Nのような分布にする。

【0121】

また、映像信号線DLの信号入力端DINから最も近い位置にある走査信号線GL1に接続されている画素の寄生容量Cgsの分布を、図11に示した曲線F9のようにするには、たとえば、画素U3における寄生容量Cgsを基準にし、当該走査信号線GL1に接続されている各画素の寄生容量Cgsを決める。走査信号線GL1の上における絶縁層の膜厚は、図14に示した実線のような変化をしており、走査信号線GL1の信号入力端GINから最も遠い位置にある画素U3における絶縁層の膜厚は、画素U6における膜厚よりも厚くなっている。そのため、領域AR1では、映像信号線DLの信号入力端DINから最も近い位置にある走査信号線GL1に接続されている画素の寄生容量Cgsの分布を、たとえば、図15に示した曲線F101のような分布にする。

【0122】

また、そのほかの走査信号線GLiに接続されている画素の寄生容量Cgsの分布についても、同様の手順で決めればよい。このとき、領域AR1では、走査信号線GLiに接続されている画素の寄生容量Cgsの分布は、たとえば、図15に示した曲線F10iのような分布になる。

【0123】

このとき、各画素における補正パターンの寸法が上記の分布にしたがうようにレイアウトデータを補正し、領域AR1に回路(第1の薄膜積層体)を形成すると、表示領域の4隅に位置する4つの画素U1,U3,U4,U6における走査信号線GLとソース電極505との重畳領域の関係は、たとえば、図15に示すようになる。

【0124】

このようにすると、各走査信号線GLnの配線容量の組み合わせ(時定数)が概ね等しくなり、信号入力端からの距離と遅延量の関係が概ね等しくなる。またこのとき、各走査信号線GLにおける信号入力端からの距離と寄生容量Cgsの大きさの変動量との関係が概ね等しくなる。したがって、領域AR1に形成された回路を有する液晶表示パネル1は、たとえば、DCオフセット電圧が十分小さくても、残像を抑制することができる。

【0125】

図17乃至図19は、領域AR2に形成される画素の寄生容量Cgsの補正方法の一例を示す模式図である。

図17は、領域AR2に形成されたTFT基板における信号入力端の位置と絶縁層の膜厚分布との関係を示す模式平面図である。図18は、図17に示した映像信号線に接続している画素の寄生容量Cgsの補正量の一例を示す模式図である。図19は、補正後のレイアウトデータにおける4隅の画素の補正パターンの一例を示す模式図である。

【0126】

領域AR2に形成される絶縁層の膜厚は、たとえば、図17に示すように、走査信号線GLの信号入力端GINから遠ざかるにつれて厚くなり、かつ、映像信号線DLの信号入力端DINから遠ざかるにつれて薄くなる。

【0127】

領域AR2では、たとえば、図10に示したように、DCオフセット電圧を領域AR1に形成された液晶表示パネル1より小さく入力しても、走査信号線GLの延伸方向でみた残像のレベルが、レイアウトデータ通りの場合に比べて小さくなる。しかしながら、残像のレベルは補正後の領域AR1より大きい。したがって、領域AR2に形成する回路についても、領域AR1と同様に補正し1本の走査信号線に接続されている画素の寄生容量Cgsの分布は、たとえば、図18に示した曲線F11のようになる。

【0128】

このとき、各画素における補正パターンの寸法が上記の分布にしたがうようにレイアウトデータを補正し、領域AR2に回路(第1の薄膜積層体)を形成すると、表示領域の4隅に位置する4つの画素U1,U3,U4,U6における走査信号線GLとソース電極505との重畳領域の関係は、たとえば、図19に示すようになる。

【0129】

このようにすると、各走査信号線GLnの配線容量の組み合わせ(時定数)が概ね等しくなり、信号入力端からの距離と遅延量の関係が概ね等しくなる。またこのとき、各走査信号線における信号入力端からの距離と寄生容量Cgsの大きさの変動量との関係が概ね等しくなる。したがって、領域AR2に形成された回路を有する液晶表示パネル1の残像を抑制することができる。

【0130】

図20は、本実施例の製造方法の作用効果の一例を示す模式図である。

【0131】

本実施例の液晶表示パネルの製造方法では、上記のように、4面取りで製造された第1の液晶表示パネル1と第2の液晶表示パネル1とを比較すると、各画素における走査信号線GLとソース電極505との重畳領域の面積の関係に違いが生じる。

【0132】

しかしながら、第1の液晶表示パネル1および第2の液晶表示パネル1は、それぞれ、第1の絶縁層503の膜厚分布に基づいて、各画素における寄生容量Cgsの大きさを調整している。そのため、第1の液晶表示パネル1と第2の液晶表示パネル2を同じ条件で駆動すると、たとえば、図20に示すように、それぞれの液晶表示パネル1における走査信号線の延在方向で見た残像のレベルΔS3’,ΔS4’が、補正前の液晶表示パネル1の残像のレベルΔS3,ΔS4よりも小さくなり、かつ、概ね等しくなる。

【0133】

また、詳細な説明は省略するが、領域AR3および領域AR4に形成する回路(第1の薄膜積層体)についても、領域AR1および領域AR2の場合と同様の考え方で、各画素における寄生容量Cgsの大きさを決めてやれば、領域AR3に形成された回路を有する第3の液晶表示パネル1および領域AR4に形成された回路を有する第4の液晶表示パネル1も、走査信号線GLの延伸方向で見た残像のレベルを小さくすることができる。

【0134】

したがって、本実施例の液晶表示パネルの製造方法では、一組のマザーガラスから得られる4枚の液晶表示パネル1を駆動するときにDCオフセット電圧を液晶表示パネル毎に変更しなくても、それぞれの液晶表示パネル1における残像を抑制することができ、かつ、4枚の液晶表示パネル1間の残像の傾向を均一化することができる。

【0135】

さて、このように絶縁層の膜厚分布に応じて走査信号線GLとソース電極505との重畳領域の面積を変える場合、従来の液晶表示パネル1の製造方法だと、たとえば、走査信号線GLに関するレイアウトデータを4通りに補正し、走査信号線GLを形成する工程で使用するフォトマスクを4通りに作り分ける必要がある。

【0136】

また、絶縁層の膜厚分布は、使用するCVD装置やチャンバーによって異なることがある。そのため、絶縁層の膜厚分布に応じてレイアウトデータを補正し、フォトマスクを作り分けるのは効率が悪い。

【0137】

したがって、本実施例の液晶表示パネルの製造方法では、走査信号線GLを形成する工程で行う感光性材料膜の露光を、直描露光方式またはダイレクト露光方式と呼ばれる露光装置で行う。

【0138】

直描露光方式の露光装置は、フォトマスクの代わりに、数値制御により露光パターンを生成する空間光変調素子を用いる。このとき、空間光変調素子は、レイアウトデータを所定の条件で変換して得られる描画データ(数値データ)に基づいて制御する。そのため、直描露光方式の露光装置で感光性材料膜を露光するときには、レイアウトデータの数値を変えるだけで露光パターンを変えることができる。

【0139】

図21は、本実施例の液晶表示パネルの製造方法の主要部を説明するための模式フロー図である。

【0140】

実施例1の液晶表示パネルの製造方法は、たとえば、CVD装置と寄生容量Cgsの補正量との関係を登録する工程、レイアウトデータを描画データに変換する工程、液晶表示パネル1を製造する工程の3つの工程を有する。

【0141】

CVD装置と寄生容量Cgsの補正量との関係を登録する工程は、たとえば、図21に示したSTART1からEND1までのような処理を行う。まず、液晶表示パネルの製造に使用するCVD装置と絶縁層の膜厚分布との関係を、たとえば、所定のデータサーバの膜厚分布データベースに登録しておく(ステップS11)。

【0142】

このとき、CVD装置と絶縁層の膜厚分布との関係は、たとえば、CVD装置の号機毎、チャンバー毎に計測する。そして、膜厚分布データベースには、たとえば、CVD装置の号機番号、チャンバー番号、マザーガラス上の面付け位置(領域)、および絶縁膜の膜厚分布の傾向を関連づけたデータを登録する。

【0143】

次に、データサーバにおいて、膜厚分布データベースに登録された上記の関係毎に、たとえば、図15に示したような寄生容量Cgsの補正量を算出し、補正データベースに登録する(ステップS12)。

【0144】

このとき、補正データベースには、たとえば、CVD装置の号機番号、チャンバー番号、マザーガラス上の面付け位置(領域)、および絶縁膜の膜厚分布の傾向と、寄生容量Cgsの補正量とを関連づけたデータを登録する。

【0145】

またこのとき、CVD装置と寄生容量Cgsの補正量との関係を登録する工程は、たとえば、ステップS11とステップS12の処理を定期的に行う。

【0146】

また、レイアウトデータを描画データに変換する工程は、たとえば、図21に示したSTART2からEND2までのような処理を行う。まず、CADなどで作製されたレイアウトデータを、データサーバに登録する(ステップS21)。

【0147】

このとき、データサーバでは、登録されたレイアウトデータと、データベースに登録された寄生容量Cgsの補正量に基づいて、走査信号線とソース電極の重畳領域の面積の補正量を決定(ステップS22)し、決定された補正量に基づいてレイアウトデータを補正する(S23)。

【0148】

次に、データサーバでは、補正されたレイアウトデータから描画データを生成し、描画データベースに登録する(ステップS24)。

【0149】

このとき、描画データベースには、CVD装置の号機番号、チャンバー番号、マザーガラス上の面付け位置(領域)、および描画データを関連づけて登録する。

【0150】

またこのとき、CVD装置と寄生容量Cgsの補正量との関係が変更されたら、描画データも変更する。

【0151】

また、液晶表示パネル1を製造する工程は、基本的には、従来と同じ手順であり、TFT基板5を形成する工程、対向基板6を形成する工程、TFT基板5と対向基板6を貼り合わせるとともに液晶材料(液晶層7)を封入する工程を有する。このとき、TFT基板5を形成する工程は、たとえば、図21に示したSTART3からEND3までのような処理を行う。まず、マザーガラス上に、走査信号線GLを形成するための導電膜を形成(成膜)し、当該導電膜の上に感光性材料膜を形成(成膜)する(ステップS31)。

【0152】

導電膜の上に形成された感光性材料膜の露光は、上記のように直描露光方式の露光装置で行う。直描露光方式の露光装置で感光性材料膜を露光するときには、まず、露光装置に、たとえば、第1の絶縁層503を形成するときに使用するCVD装置の号機番号およびチャンバー番号を設定(ステップS32)し、描画データベースに登録されている描画データを取得する(ステップS33)。

【0153】

このとき、露光装置には、たとえば、CVD装置の号機番号およびチャンバー番号に基づいて、面付け位置(マザーガラスに設定された4つの領域)のそれぞれと対応する、4通りの描画データが登録される。

【0154】

露光装置は、4通りの描画データを取得したら、当該描画データを用いて、マザーガラスに設定された4つの領域の露光を行う(ステップS34)。

【0155】

次に、感光性材料膜を現像し、導電膜をエッチングすると、マザーガラスの4つの領域には、取得した描画データを反映した平面形状の走査信号線GLが形成される(ステップS35)。

【0156】

その後、感光性材料膜を露光する時に指定したCVD装置で第1の絶縁層503を形成し、続けてTFT素子10の半導体層504の形成、映像信号線DLおよびソース電極10などの形成を行い、各領域に所定の回路(第1の薄膜積層体)を形成する(ステップS36)。

【0157】

また、図示は省略するが、これと並行して別のマザーガラスに対向基板6を形成し、これら2枚のマザーガラスを貼り合わせるとともに液晶材料(液晶層7)を封入する。そして、各領域を切り出すと、4枚の液晶表示パネル1が得られる。

【0158】

こうして得られた4枚の液晶表示パネル1は、上記のように、同じ条件で駆動させたときに、1枚の液晶表示パネル内における残像が抑制されており、かつ、4枚の液晶表示パネル1の間の残像のレベルが同程度になる。

【0159】

また、液晶表示パネル1を上記の手順で製造する場合、第1の絶縁層503を形成するときに使用するCVD装置やチャンバーが異なっても、残像のレベルを同程度にすることができる。

【0160】

また、本実施例の製造方法の場合、たとえば、あるCVD装置における膜厚分布が途中で変動しても、寄生容量Cgsの大きさの変更が容易である。

【0161】

以上説明したように、本実施例の液晶表示装置の製造方法によれば、1枚の液晶表示パネルにおける残像の抑制、および複数枚の液晶表示パネル間の残像のレベルの均一化が容易になる。

【0162】

以上、本発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において、種々変更可能であることはもちろんである。

【0163】

たとえば、前記実施例では、4面取りで液晶表示パネルを製造する場合を例に挙げているが、本発明の製造方法は、4面取りに限らず、一組のマザーガラスを用いて任意のn枚の液晶表示パネルを一括製造するn面取りの製造方法に適用できることはもちろんである。

【0164】

また、前記実施例では、たとえば、図2および図3に示したような構成の画素を有する液晶表示パネルを製造する場合を例に挙げている。しかしながら、本発明の製造方法は、これに限らず、各画素のTFT素子のソース電極が、ゲート電極(走査信号線)と重畳している部分としていない部分とを有する構造であり、かつ、レイアウトデータ通りに製造したときに残像が生じる液晶表示パネルであれば適用可能である。すなわち、本発明の製造方法は、たとえば、IPS方式のように共通電極がTFT基板側に形成されている液晶表示パネルの製造方法などにも適用できる。

【0165】

また、前記実施例の製造方法で製造された液晶表示パネルを駆動すると、たとえば、図20に示したように、残像のレベルが低減するものの、完全にゼロにならないこともある。そのため、前記実施例の製造方法で製造された液晶表示パネルを駆動するときには、たとえば、DCオフセット電圧を階調電圧に付加して駆動させてもよい。このようにすることで、残像のレベルをさらに低減することができる。またこのとき、一組のマザーガラスから得られる複数枚の液晶表示パネルは、絶縁層の膜厚分布によらず、残像のレベルが概ね等しい。そのため、DCオフセット電圧を階調電圧に付加して当該複数枚の液晶表示パネルを駆動させる場合、第1の駆動回路の調整が容易になる。

【符号の説明】

【0166】

1 液晶表示パネル

2 第1の駆動回路

3 第2の駆動回路

4 制御回路

5 TFT基板

6 対向基板

GL 走査信号線

DL 映像信号線

PX 画素電極

CT 共通電極

501 第1の絶縁基板

502 保持容量線

503 第1の絶縁層

504 半導体層

505 ソース電極

506 第2の絶縁層

507 第1の配向膜

601 第2の絶縁基板

602 ブラックマトリクス

603 カラーフィルタ

604 平坦化層

605第2の配向膜

7 液晶層

8 第1の偏光板

9 第2の偏光板

10 TFT素子

11 マザーガラス

【技術分野】

【0001】

本発明は、液晶表示装置およびその製造方法に関し、特に、多面取りで液晶表示パネルを製造する方法に適用して有効な技術に関するものである。

【背景技術】

【0002】

アクティブマトリクス型のTFT液晶表示装置(以下、単に液晶表示装置という。)は、たとえば、液晶テレビ、パーソナルコンピュータ用の液晶ディスプレイ、携帯電話端末などの携帯型電子機器の液晶ディスプレイとして広く用いられている。

【0003】

液晶表示装置は、一対の基板の間に液晶材料を封入した液晶表示パネルを有し、当該液晶表示パネルの表示領域は、TFT素子、画素電極、共通電極、および液晶層(液晶材料)を有する画素の集合でなる。また、アクティブマトリクス型の場合、液晶表示パネルは、複数の走査信号線および複数の映像信号線を有する。

【0004】

このとき、各画素のTFT素子は、ソースが画素電極と接続しており、ドレインが複数の映像信号線のうちの1本と接続している。また、各画素のTFT素子は、ゲート電極が複数の走査信号線のうちの1本と接続している。

【0005】

液晶表示装置では、画素電極と共通電極との電位差によって各画素における光の透過量または反射量あるいはその両方を制御して映像や画像を表示する。このとき、液晶表示装置では、複数の走査信号線のうちの1本の走査信号線にゲート電極が接続している複数のTFT素子をオンにし、各映像信号線に加えられている映像信号(階調電圧)を当該TFT素子を介して画素電極に書き込む、という動作が繰り返し行われる。

【0006】

またこのとき、液晶表示装置では、あらかじめ定められたフレーム期間毎に各画素の極性、言い換えると画素電極の電位と共通電極の電位との高低の関係を反転させながら、映像や画像を表示する。

【0007】

ところで、従来の液晶表示装置では、たとえば、走査信号線に加えた走査信号の波形に生じる歪み(なまり)に起因する残像が発生しやすい。この走査信号の波形の歪みによる残像は、一般に、走査信号線の信号入力端から遠い部分で発生しやすいことが知られている。このような走査信号の波形の歪みによる残像を低減する方法としては、たとえば、走査信号線の信号入力端から遠ざかるにつれて、TFT素子のゲート電極とソース電極との間に形成される寄生容量Cgsを大きくする方法が提案されている(たとえば、特許文献1を参照。)。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2004−093821号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

液晶表示パネルを製造するときには、通常、一組のマザーガラスを用いて複数枚の液晶表示パネルを一括して製造する多面取りと呼ばれる方法をとることが多い。

【0010】

一組のマザーガラスを用いて4枚の液晶表示パネルを製造する、いわゆる4面取りの場合は、一方のマザーガラスに設定された4つの領域のそれぞれに、複数の走査信号線、複数の映像信号線、複数のTFT素子、および複数の画素電極などを有する回路(薄膜積層体)を形成する。

【0011】

このとき、前記回路は、導電膜または半導体膜をエッチングする工程と、絶縁膜を形成する工程とを、所定の順序で行って形成する。

【0012】

またこのとき、絶縁膜は、通常、CVD法などの成膜法を用いて、マザーガラスの回路形成面全体に形成する。そのため、マザーガラス上に形成された絶縁膜の膜厚は、当該マザーガラスの中央部分が最も厚く、中心から遠ざかるにつれて同心円的に薄くなっていくような分布になる。

【0013】

4面取りの場合、マザーガラスの前記4つの領域に形成される回路は、通常、並進対称性を有する。したがって、一組のマザーガラスから得られる4枚の液晶表示パネルは、絶縁膜の膜厚分布が異なる。

【0014】

ところで、走査信号線は、回路的に見ると、複数の配線抵抗と複数の配線容量とを有する。走査信号線の配線容量には、たとえば、TFT素子のソース電極や画素電極との間で形成される寄生容量Cgsや、映像信号線との間で形成される寄生容量などがある。これらの寄生容量は、たとえば、走査信号線と他の導電層との間に介在する絶縁層の厚さによって変化する。そのため、1枚の液晶表示パネルにおいて寄生容量に関わる絶縁層の膜厚に分布(傾斜)があると、各走査信号線の配線容量の大きさには、絶縁層の膜厚分布に応じた違いが生じる。このように、各走査信号線の配線容量の大きさに違いが生じると、各走査信号線の時定数に違いが生じる。その結果、1枚の液晶表示パネルに形成された各走査信号線における走査信号の波形の歪み方(信号遅延)が異なってしまう。

【0015】

したがって、各画素の寄生容量Cgsの大きさを調整することで走査信号の波形の歪みによる残像を防ぐ場合は、絶縁膜の膜厚分布を考慮して、たとえば、各TFT素子におけるゲート電極(走査信号線)とソース電極との重畳面積や、ゲート電極(走査信号線)と画素電極との平面距離などを補正することが望まれる。

【0016】

また、一組のマザーガラスから得られる複数枚の液晶表示パネルは、前述のように、絶縁膜の膜厚分布が異なる。そのため、一組のマザーガラスから得られる複数枚の液晶表示パネルでは、各走査信号線における走査信号の波形の歪み方に違いが生じる。

【0017】

したがって、液晶表示パネルを多面取りで製造する場合、一組のマザーガラスから得られる個々の液晶表示パネルにおける残像を低減するとともに、複数枚の液晶表示パネル間における残像のレベル(強さの度合い)を均一化するには、面付け位置(回路を形成する領域)毎に、異なる補正をすることが望まれる。

【0018】

また、CVD法などの成膜法で絶縁膜を形成する場合は、使用するCVD装置によって、たとえば、マザーガラスの中心からの距離と膜厚の減少率との関係が異なることが多い。したがって、ある1組のレイアウトデータに基づき、異なる製造ラインで製造された複数枚の液晶表示パネル間における残像のレベルを均一化するには、使用するCVD装置における膜厚分布を考慮し、たとえば、製造ライン毎に異なる補正をすることが望まれる。

【0019】

しかしながら、寄生容量Cgsの大きさと関わりがある走査信号線やソース電極は、通常、導電膜をエッチングして形成する。導電膜をエッチングするときには、当該導電膜の上に形成した感光性材料膜を露光、現像して、所定のパターンのレジスト(エッチングレジスト)を形成する。このとき、従来の液晶表示パネルの製造方法では、導電膜の上に形成した感光性材料膜を、通常、フォトマスクを有する露光装置で露光する。

【0020】

フォトマスクを有する露光装置で、導電膜の上に形成した感光性材料膜を露光する場合、絶縁膜の膜厚分布に応じて、ゲート電極(走査信号線)とソース電極との重畳面積や、ゲート電極(走査信号線)と画素電極との平面距離などを補正すると、たとえば、面付け位置毎、製造ライン毎に露光パターンが異なるフォトマスクを作成する必要がある。そのため、従来の多面取りの液晶表示パネルの製造方法では、個々の液晶表示パネルにおける残像を低減するとともに、複数枚の液晶表示パネル間における残像の度合いを均一化することが難しく、製造効率が悪くなるという問題があった。

【0021】

本発明の目的は、個々の液晶表示パネルにおける残像を低減するとともに、複数枚の液晶表示パネル間における残像のレベルを均一化することが容易な液晶表示パネルの製造方法を提供することにある。

【0022】

本発明の他の目的は、絶縁膜の膜厚分布によらず、走査信号の波形の歪みに起因する残像が低減されている液晶表示パネルを提供することにある。

【0023】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面によって明らかになるであろう。

【課題を解決するための手段】

【0024】

本願において開示される発明のうち、代表的なものの概略を説明すれば、以下の通りである。

【0025】

(1)TFT基板と対向基板との間に液晶材料が封入された液晶表示パネルを有し、前記TFT基板は、複数の走査信号線、複数の映像信号線、複数のTFT素子、および複数の画素電極を有し、前記複数のTFT素子は、ゲート電極が前記複数の走査信号線のうちの1本の走査信号線に接続し、ドレイン電極が前記複数の映像信号線のうちの1本の映像信号線に接続しており、かつ、TFT素子毎に、前記ゲート電極が接続している前記走査信号線と前記ドレイン電極が接続している前記映像信号線との組み合わせが異なる液晶表示装置であって、前記TFT素子のソース電極は、走査信号線と重畳している部分としていない部分とを有し、1本の前記走査信号線に接続している複数のTFT素子は、当該走査信号線の信号入力端からの距離と前記ソース電極と前記走査信号線との重畳領域の面積との関係が、単調減少の関係である液晶表示装置。

【0026】

(2)前記(1)の液晶表示装置において、1本の前記映像信号線に接続している複数のTFT素子は、当該映像信号線の信号入力端からの距離と前記ソース電極と前記走査信号線との重畳領域の面積との関係が、単調減少の関係である液晶表示装置。

【0027】

(3)TFT基板を形成する工程と、対向基板を形成する工程と、前記TFT基板と前記対向基板とを貼り合わせるとともに液晶材料を封入して液晶表示パネルを形成する工程とを有し、前記TFT基板を形成する工程は、あらかじめ用意されたレイアウトデータに基づいて複数の走査信号線、複数の映像信号線、複数のTFT素子、および複数の画素電極を形成する液晶表示装置の製造方法であって、前記複数のTFT素子のソース電極は、前記画素電極と接続し、かつ、前記走査信号線と重畳させる部分とさせない部分とを有し、前記TFT基板を形成する工程は、前記複数の走査信号線を形成する第1の工程と、前記第1の工程の後、第1の絶縁層を形成する第2の工程と、前記第1の絶縁層の上に、前記TFT素子の半導体層、前記複数の映像信号線、および前記TFT素子のソース電極を形成する第3の工程を有し、前記第1の工程は、導電膜を形成する工程と、前記導電膜の上に感光性材料膜を形成する工程と、前記感光性材料膜を露光、現像する工程と、現像した前記感光性材料膜をマスクにして前記導電膜の不要な部分を除去する工程を有し、前記感光性材料膜の露光は、前記レイアウトデータに基づいて作成される描画データによる数値制御で露光パターンを生成する空間光変調素子を有する露光装置を用いて行い、前記描画データは、前記レイアウトデータにおける前記走査信号線のうちの、前記ソース電極と重畳させる部分の形状が、前記第2の工程で形成される前記第1の絶縁層の膜厚の分布に応じた面積になるように補正して作成する液晶表示装置の製造方法。

【0028】

(4)前記(3)の液晶表示装置の製造方法において、前記TFT基板を形成する工程は、1枚のマザー基板を用いて複数枚のTFT基板を一括して形成し、前記第1の工程で行う前記感光性材料膜の露光は、前記マザー基板上における前記TFT基板の位置毎に、異なる前記描画データを用いて行う液晶表示装置の製造方法。

【発明の効果】

【0029】

本発明の液晶表示装置の製造方法によれば、個々の液晶表示パネルにおける残像を低減するとともに、複数枚の液晶表示パネル間における残像のレベルを均一化することが容易である。

【0030】

また、本発明の液晶表示装置によれば、液晶表示パネルの絶縁膜の膜厚分布によらず、走査信号の波形の歪みに起因する残像が低減される。

【図面の簡単な説明】

【0031】

【図1】液晶表示装置の概略構成の一例を示す模式ブロック図である。

【図2】TFT基板における画素の平面構成の一例を示す模式平面図である。

【図3】図2のA−A’線における液晶表示パネルの断面構成の一例を示す模式断面図である。

【図4】図2および図3に示した画素の模式等価回路図である。

【図5】走査信号線の模式等価回路図である。

【図6】走査信号線の信号入力端からの距離が異なる2つの画素における画素電極の電位の変動の様子の一例を示す模式図である。

【図7】4面取りの場合のTFT基板として切り出す領域と絶縁層の膜厚分布との関係の一例を示す模式平面図である。

【図8】図7の領域AR1に形成された走査信号線および領域AR2に形成された走査信号線における走査信号の遅延量の一例を示す模式図である。

【図9】図7の領域AR1のTFT基板を有する液晶表示パネルおよび領域AR2のTFT基板を有する液晶表示パネルにおける最適なVcom値の分布の一例を示す模式図である。

【図10】図7の領域AR1のTFT基板を有する液晶表示パネルおよび領域AR2のTFT基板を有する液晶表示パネルにおける残像の傾向を示す模式図である。

【図11】信号入力端からの距離と寄生容量Cgsの大きさとの関係を示す模式図である。

【図12】寄生容量Cgsの調整方法の一例を示す模式図である。

【図13】領域AR1に形成されたTFT基板における信号入力端の位置と絶縁層の膜厚分布との関係を示す模式平面図である。

【図14】領域AR1に形成されたTFT基板における絶縁層の膜厚の変動量の一例を示す模式図である。

【図15】図13に示した3本の走査信号線に接続している画素の寄生容量Cgsの補正量の一例を示す模式図である。

【図16】補正後のレイアウトデータにおける4隅の画素の補正パターンの一例を示す模式図である。

【図17】領域AR2に形成されたTFT基板における信号入力端の位置と絶縁層の膜厚分布との関係を示す模式平面図である。

【図18】図17に示した映像信号線に接続している画素の寄生容量Cgsの補正量の一例を示す模式図である。

【図19】補正後のレイアウトデータにおける4隅の画素の補正パターンの一例を示す模式図である。

【図20】本実施例の製造方法の作用効果の一例を示す模式図である。

【図21】本実施例の液晶表示パネルの製造方法の主要部を説明するための模式フロー図である。

【発明を実施するための形態】

【0032】

以下、本発明について、図面を参照して実施の形態(実施例)とともに詳細に説明する。

なお、実施例を説明するための全図において、同一機能を有するものは、同一符号を付け、その繰り返しの説明は省略する。

【0033】

図1乃至図3は、本発明に関わる液晶表示装置の概略構成の一例を説明するための模式図である。

図1は、液晶表示装置の概略構成の一例を示す模式ブロック図である。図2は、TFT基板における画素の平面構成の一例を示す模式平面図である。図3は、図2のA−A’線における液晶表示パネルの断面構成の一例を示す模式断面図である。

【0034】

本発明に関わる液晶表示装置は、たとえば、図1に示すように、液晶表示パネル1、第1の駆動回路2、第2の駆動回路3、および制御回路4を有する。また、本発明に関わる液晶表示装置は、そのほかに、たとえば、バックライトユニットなどを有する。

【0035】

液晶表示パネル1は、TFT基板5と対向基板6との間に液晶材料が封入された表示パネルである。また、液晶表示パネル1は、アクティブマトリクス型であり、TFT基板5は、複数の走査信号線GLおよび複数の映像信号線DLを有する。また、液晶表示パネル1の表示領域は、TFT素子、画素電極、共通電極、および液晶層(液晶材料)を有する画素の集合でなる。

【0036】

TFT基板5は、たとえば、図2および図3に示すように、ガラス基板などの第1の絶縁基板501、第1の絶縁基板501の液晶層7と対向する面に形成された第1の薄膜積層体、および第1の偏光板8を有する。

【0037】

第1の薄膜積層体は、走査信号線GL、保持容量線502、第1の絶縁層503、TFT素子の半導体層504、映像信号線DL、TFT素子のソース電極505、第2の絶縁層506、画素電極PX、および第1の配向膜507などを有する。

【0038】

一方、対向基板6は、たとえば、図3に示すように、ガラス基板などの第2の絶縁基板601、第2の絶縁基板601の液晶層7と対向する面に形成された第2の薄膜積層体、および第2の偏光板9を有する。

【0039】

第2の薄膜積層体は、ブラックマトリクス602、カラーフィルタ603、平坦化層604、共通電極CT、および第2の配向膜605などを有する。

【0040】

第1の駆動回路2は、各画素の画素電極PXに加える階調電圧を生成し、各映像信号線DLに出力する回路であり、一般に、データドライバなどと呼ばれている。また、第2の駆動回路3は、第1の駆動回路2から各映像信号線DLに加えられた階調電圧を書き込む画素(画素電極PX)を選択するための走査信号を生成し、各走査信号線GLに出力する回路であり、一般に、ゲートドライバ、走査ドライバなどと呼ばれている。また、制御回路4は、第1の駆動回路2の動作、第2の駆動回路3の動作、および共通電極CTに加える電圧などの制御をする回路であり、一般に、TFTコントローラ、T−CONなどと呼ばれている。

【0041】

本発明に関わる液晶表示装置の動作は、基本的には、従来の液晶表示装置と同じでよい。そのため、第1の駆動回路2、第2の駆動回路3、および制御回路4の具体的な構成や、液晶表示装置の動作に関する説明は省略する。

【0042】

図4乃至図6は、従来の液晶表示装置における残像の発生要因の一例を説明するための模式図である。

図4は、図2および図3に示した画素の模式等価回路図である。図5は、走査信号線の模式等価回路図である。図6は、走査信号線の信号入力端からの距離が異なる2つの画素における画素電極の電位の変動の様子の一例を示す模式図である。

【0043】

図2および図3に示した画素の等価回路は、たとえば、図4のように表すことができ、TFT素子10、画素容量CLC、および保持容量CSTGを有する。

【0044】

TFT素子10は、ゲート電極が走査信号線GLに接続しており、ドレイン電極が映像信号線DLに接続している。また、TFT素子10のソース電極505は、画素電極PXに接続している。このとき、TFT素子10のソースとドレインとは、映像信号線DLの電位と画素電極PXの電位との高低の関係によって決まるが、本明細書では、映像信号線DLに接続しているほうをドレインと呼び、画素電極PXに接続しているほうをソースと呼ぶ。

【0045】

画素容量CLCは、画素電極PX、共通電極CT、および液晶層7により形成される容量であり、液晶容量などと呼ぶこともある。画素容量CLCは、画素電極PXと共通電極CTとの電位差に応じて液晶層7の配向状態が変化する。これにより、バックライトユニットからの光の透過光量が制御される。

【0046】

保持容量CSTGは、画素電極PX、保持容量線502、および介在する絶縁層(第1の絶縁層503および第2の絶縁層506)により形成される容量であり、補助容量、蓄積容量などと呼ぶこともある。保持容量CSTGは、TFT素子10がオフの期間の画素電極PXの電位を保持するための容量である。なお、保持容量CSTGの形成方法には、種々の方法がある。

【0047】

また、図2および図3に示したような構成の画素は、画素容量CLCおよび保持容量CSTGの他に、たとえば、寄生容量Cgsを有する。寄生容量Cgsは、TFT素子10のゲート電極(走査信号線GL)とソース電極505との間で形成される容量である。また、図2および図3に示したような構成の画素は、そのほかにも、たとえば、TFT素子10のゲート電極(走査信号線GL)とドレイン電極(映像信号線DL)との間に形成される寄生容量なども有する。

【0048】

寄生容量は、画素容量CLCおよび保持容量CSTGとは異なり、画素の動作(透過光量の制御)には不要な容量である。しかしながら、TFT基板5の構成上、これらの寄生容量が形成されることは避けられない。

【0049】

このように、アクティブマトリクス型の液晶表示装置では、走査信号線GLを一方の電極とする寄生容量Cgsなどが形成される。また、走査信号線GLは、たとえば、アルミニウムなどの金属で形成されており、電気抵抗を有する。

【0050】

したがって、1本の走査信号線GLは、回路的に見ると、たとえば、図5に示すように、複数の配線抵抗Rm(m=1,2,3,…,M)と複数の配線容量(寄生容量)Cpmとを有する。そのため、第2の駆動回路3から走査信号線GLに加えた走査信号の波形には、配線抵抗Rmおよび配線容量Cpmによる歪みが生じる。また、この走査信号の波形の歪みは、走査信号線GLの信号入力端から遠くなるほど大きくなる。なお、図5において、1つの配線抵抗Rmは、1画素分の配線抵抗であり、1つの配線容量Cpmは1画素分の寄生容量の合成容量である。

【0051】

バックライトユニットを有する液晶表示装置では、各画素における光の透過光量を制御することで、バックライトユニットからの光(面状光線)を変調し、映像や画像を表示する。このとき、光の透過光量は、画素電極PXと共通電極CTとの電位差によって制御する。またこのとき、一般的な液晶表示装置では、画素電極PXに加える階調電圧の極性、すなわち画素電極PXの電位と共通電極CTの電位との高低の関係を、あらかじめ定められたフレーム期間毎(たとえば、1フレーム期間毎)に反転させることで、フリッカや残像などの発生を抑えている。

【0052】

しかしながら、従来の液晶表示装置では、たとえば、上記の走査信号の波形の歪みや寄生容量Cgsなどの影響による残像が発生する。

【0053】

図2および図3に示したような構成の画素を有する従来の液晶表示装置において、走査信号線GLの信号入力端からの距離が異なる2つの画素の画素電極PXに同じ電位VKの階調電圧を書き込む場合、ゲート電極の電位および画素電極PXの電位は、それぞれ、たとえば、図6に示すような時間変化をする。

【0054】

なお、図6において、左側のVG1、VDL1、およびVPX1は、それぞれ、信号入力端から近い位置にある第1の画素U1のゲート電極の電位、ドレイン電極(映像信号線DL)の電位、および画素電極PXの電位の時間変化を示す波形である。また、図6において、右側のVG2、VDL2、およびVPX2は、それぞれ、信号入力端から遠い位置にある第2の画素U2のゲート電極の電位、ドレイン電極(映像信号線)の電位、および画素電極PXの電位の時間変化を示す波形である。また、図6において、Vcom1およびVcom2は、それぞれ、第1の画素PX1および第2の画素PX2における最適コモン電圧である。なお、最適コモン電圧とは、画素電極PXと共通電極CTの電位差が設計段階で定められた所定の値ΔVになるようにするためのコモン電圧のことである。

【0055】

アクティブマトリクス型の液晶表示装置において、画素の透過光量を制御するときには、TFT素子10をオンにする期間と同期させてドレイン電極に階調電圧を加え、当該階調電圧を画素電極PXに書き込む。

【0056】

第2の駆動回路3から走査信号線GLに加わる走査信号の波形は、たとえば、図6に点線で示したような矩形である。しかしながら、走査信号線GLに加えられた走査信号には、前述のように、信号入力端からの距離に応じた歪み(遅延)が生じる。このとき、第1の画素U1のゲート電極および第2の画素U2のゲート電極の電位は、それぞれ、波形VG1および波形VG2のような時間変化をする。すなわち、第2の画素U2のゲート電極に加わる走査信号の波形VG2は、第1の画素U1のゲート電極に加わる走査信号の波形VG1よりも歪みが大きくなる。

【0057】

また、第1の画素U1のドレイン電極に加わる階調電圧の電位および第2の画素U2のドレイン電極に加わる階調電圧の電位は、それぞれ、波形VDL1および波形VDL2のような時間変化をする。すなわち、第1の画素U1のドレイン電極の電位および第2の画素U2のドレイン電極の電位は、それぞれ、ゲート電極の電位が上昇するタイミングと同期して、所定の電位VKに変化する。

【0058】

このとき、第1の画素U1の画素電極PXの電位および第2の画素U2の画素電極PXの電位は、それぞれ、波形VPX1および波形VPX2のような時間変化をする。すなわち、第1の画素U1の画素電極PXの電位および第2の画素U2の画素電極PXの電位は、それぞれ、TFT素子10がオンからオフに切り替わる時点、言い換えるとゲート電極の電位の下降が始まる時点で、それぞれ、ドレイン電極(階調電圧)の電位VKと概ね同じ電位になる。

【0059】

また、液晶表示パネル1における画素の構成が、図2および図3に示したような構成である場合は、TFT素子10がオンからオフに切り替わるときに、たとえば、上記の寄生容量Cgsを介した飛び込み電圧の影響により、画素電極PXの電位に変動が生じる。このTFT素子10がオンからオフに切り替わるときに生じる画素電極PXの電位の変動量は、一般に、フィードスルー電圧と呼ばれる。

【0060】

フィードスルー電圧の大きさは、通常、走査信号線GLの信号入力端から遠い画素ほど小さくなる。そのため、第2の画素U2におけるフィードスルー電圧VFT2は、第1の画素U1におけるフィードスルー電圧VFT1よりも小さくなる。

【0061】

したがって、第1の画素U1と第2の画素U2とでは、画素電極PXと共通電極CTとの電位差を所定の値ΔVにするためのコモン電圧(最適コモン電圧Vcom1,Vcom2)の電位が異なる。また、1本の走査信号線GLには、多数の画素のTFT素子10が接続しており、それらの画素におけるフィードスルー電圧の大きさは、走査信号線GLの信号入力端からの距離によって異なる。そのため、これらの画素の画素電極PXに電位VKの階調電圧を書き込む場合、各画素における最適コモン電圧の電位は、走査信号線GLの信号入力端からの距離によって異なる。

【0062】

しかしながら、共通電極CTに加えるコモン電圧Vcomは、ある所定の電位である。そのため、複数の画素に電位VKの階調電圧を書き込む場合、各画素における最適コモン電圧と、共通電極CTに加わっているコモン電圧Vcomとの電位差に違いが生じ、ある領域では電位差が小さくなり、別の部分では電位差が大きくなる。そして、従来の液晶表示装置では、この最適コモン電圧と共通電極CTに加わっているコモン電圧Vcomとの電位差に相当する電圧が直流成分となり、残像が発生する。

【0063】

なお、液晶表示装置における残像の発生要因には、上記の直流成分以外にも種々の要因があるが、以下の説明における残像は、上記の直流成分により生じる残像のこととする。

【0064】

このような残像を低減する方法としては、従来、たとえば、前述の直流成分をキャンセルする電圧(DCオフセット電圧)を階調電圧に付加する方法や、各画素におけるフィードスルー電圧の差が小さくなるように寄生容量Cgsの大きさを調整する方法が知られている。

【0065】

ところで、液晶表示パネル1を製造するときには、通常、1組のマザーガラスを用いて複数枚の液晶表示パネル1を一括製造する多面取りと呼ばれる方法がとられる。

【0066】

液晶表示パネル1を多面取りで製造する場合は、1組のマザーガラスのうちの一方のマザーガラスに設定された複数の領域のそれぞれに、たとえば、走査信号線GL、映像信号線DL、TFT素子10、および画素電極PXなどを有する回路(第1の薄膜積層体)を形成する。

【0067】

このとき、1枚のマザーガラス11に設定されたそれぞれの領域に、たとえば、ある1つのレイアウトデータに基づいて第1の薄膜積層体を形成すると、当該マザーガラス11から切り出されたTFT基板5を有する複数枚の液晶表示パネル1は、同じ条件で駆動させたときに生じる残像の傾向が概ね等しくなると考えられる。しかしながら、従来の多面取りの製造方法では、1組のマザーガラスから切り出された複数枚の液晶表示パネル1を同じ条件で駆動させたときに、それぞれの液晶表示パネル1における残像の傾向に違いが生じる。なお、残像の傾向というのは、走査信号線GLや映像信号線DLの信号入力端の位置と残像が強く出る位置との関係や、残像のレベル(強さの度合い)のことである。

【0068】

したがって、上記のようにDCオフセット電圧を階調電圧を付加したり、寄生容量Cgsの大きさを調節したりして残像を抑制する場合は、液晶表示パネル1毎に異なる残像の傾向を考慮する必要がある。

【0069】

液晶表示パネル1を4面取りで製造する場合、1組のマザーガラスから得られる4枚の液晶表示パネル1における残像の傾向には、以下のような関係がある。

【0070】

図7乃至図10は、多面取りで製造した複数枚の液晶表示パネルに生じる残像の傾向とレベルの違いを説明するための模式図である。

図7は、4面取りの場合のTFT基板として切り出す領域と絶縁層の膜厚分布との関係の一例を示す模式平面図である。図8は、図7の領域AR1に形成された走査信号線および領域AR2に形成された走査信号線における走査信号の遅延量の一例を示す模式図である。図9は、図7の領域AR1のTFT基板を有する液晶表示パネルおよび領域AR2のTFT基板を有する液晶表示パネルにおける最適なVcom値の分布の一例を示す模式図である。図10は、図7の領域AR1のTFT基板を有する液晶表示パネルおよび領域AR2のTFT基板を有する液晶表示パネルにおける残像の傾向を示す模式図である。

【0071】

液晶表示パネル1を4面取りで製造する場合は、たとえば、図7に示すように、1組のマザーガラスのうちの一方のマザーガラス11に4つの領域AR1,AR2,AR3,AR4が設定され、当該4つの領域AR1,AR2,AR3,AR4のそれぞれに、たとえば、走査信号線GL、映像信号線DL、TFT素子10、および画素電極PXなどを有する回路(第1の薄膜積層体)が形成される。

【0072】

また、ある1つのレイアウトデータに基づいて4つの領域AR1,AR2,AR3,AR4のそれぞれに第1の薄膜積層体を形成したときには、通常、当該4つの領域AR1,AR2,AR3,AR4に形成される回路が並進対称性を有する。

【0073】

しかしながら、多面取りの製造方法において第1の絶縁層503などの絶縁層を形成するときには、通常、CVD法などの成膜法でマザーガラス11の表面全体に形成する。このとき、マザーガラス11に形成(成膜)される絶縁層の膜厚は、図7に二点差線で示したような、マザーガラス11の中心部分が最も厚くなり、中心から遠ざかるにつれて同心円状に徐々に薄くなっていく同心円状の分布になる。そのため、4つの領域AR1,AR2,AR3,AR4のそれぞれに形成された第1の薄膜積層体は、走査信号線GLの信号入力端および映像信号線DLの信号入力端の位置と、絶縁層の膜厚分布との関係に違いがある。

【0074】

液晶表示パネル1を製造するときに使用するレイアウトデータでは、通常、各画素におけるソース電極505の寸法や、走査信号線GLとソース電極505との重畳領域の面積などが同じ値である。そのため、1枚のTFT基板5における絶縁層の膜厚に二次元的な分布があると、各画素の寄生容量Cgsの大きさには、絶縁層の膜厚分布を反映する違いが生じる。

【0075】

また、領域AR1に形成された走査信号線GLと領域AR2に形成された走査信号線GLとでは、信号入力端から他端に向かって見たときの配線容量の大きさの組み合わせ、すなわち時定数が異なる。したがって、領域AR1に形成された走査信号線GLと領域AR2に形成された走査信号線GLとでは、たとえば、図8に示すように、信号入力端からの距離と走査信号の遅延量との関係に違いが生じる。なお、図8は、横軸が信号入力端からの距離の相対値、縦軸が走査信号の遅延量のグラフである。また、図8のグラフの縦軸は、上にいくほど遅延量が大きくなる。また、図8の曲線F1および曲線F2は、それぞれ、領域AR1に形成された走査信号線GLにおける走査信号の遅延量、および領域AR2に形成された走査信号線GLにおける走査信号の遅延量を示している。また、図8の区間DAxは、走査信号線GLのうちの表示領域を通る部分である。

【0076】

またさらに、1枚のTFT基板5に形成された絶縁層の膜厚に二次元的な分布があると、それぞれの走査信号線における信号入力端からの距離と走査信号の遅延量との関係にも違いが生じる。

【0077】

液晶表示パネル1の残像と関係があるフィードスルー電圧の大きさは、主として、寄生容量Cgsの大きさと、寄生容量Cgsの大きさによる走査信号の遅延量(ゲート電極の電位の波形の歪み)によって決まる。また、寄生容量Cgsの大きさは、絶縁層の厚さによって変化する。

【0078】

したがって、ある1つのレイアウトデータに基づいて4面取りで製造した4枚の液晶表示パネル1を同じ条件で駆動させると、残像の傾向に違いが生じる。このとき、4枚の液晶表示パネル1の残像にどのような傾向があるかについては、後述する。

【0079】

液晶表示パネル1を駆動させたときに生じる残像のレベルは、たとえば、最低階調(たとえば、黒)で表示するときの最適コモン電圧VcomBと、最高階調(たとえば、白)で表示するときの最適コモン電圧VcomWとの差で定義される。

【0080】

ところで、絶縁層の膜厚に二次元的な分布があるTFT基板5の液晶表示パネル1は、走査信号の遅延量と寄生容量Cgsの大きさとの組み合わせが画素毎に異なる。そのため、1枚の液晶表示パネル1における最適コモン電圧VcomB,VcomWは、画素毎に異なる。

【0081】

そこで、本願発明者らは、まず、液晶表示パネル1毎に、最低階調で表示するときの最適コモン電圧VcomBの面内分布と、最高階調で表示するときの最適コモン電圧VcomWの面内分布とを調べた。

【0082】

このとき、領域AR1に形成された回路(TFT基板5)を有する第1の液晶表示パネル1と、領域AR2に形成された回路(TFT基板5)を有する第2の液晶表示パネル1とでは、最適コモン電圧VcomB,VcomWの面内分布に、たとえば、図9に示したような違いが生じる。

【0083】

なお、図9の縦軸は、1枚の液晶表示パネル1における共通電極PXの電位の最適値の最大値と最小値との差である。また、図9の点P1および点P2は、それぞれ、第1の液晶表示パネル1の各画素における最適コモン電圧VcomBの最大値と最小値の差および最適コモン電圧VcomWの最大値と最小値の差である。また、図9の点P3および点P4は、それぞれ、第2の液晶表示パネル1の各画素における最適コモン電圧VcomBの最大値と最小値の差および最適コモン電圧VcomWの最大値と最小値の差である。また、図9の点P5および点P6は、それぞれ、4枚の液晶表示パネル1における最適コモン電圧VcomBの最大値と最小値の差の平均値および最適コモン電圧VcomWの最大値と最小値の差の平均値である。

【0084】

液晶表示パネル1を駆動させたときに生じる残像のレベルは、たとえば、図9に示した最適コモン電圧VcomBの差と最適コモン電圧VcomWの差との差ΔSに相当する。そのため、第1の液晶表示パネル1と、第2の液晶表示パネル1とでは、第1の液晶表示パネル1のほうが残像のレベルが大きくなる。

【0085】

また、第1の液晶表示パネル1および第2の液晶表示パネル1について、走査信号線GLの延伸方向に並んでいる各画素における走査信号線GLの信号入力端からの距離と、最適コモン電圧VcomB,VcomBの差との関係を調べると、たとえば、図10に示すような関係になる。

【0086】

なお、図10は、横軸が画素の識別子m、縦軸が最適コモン電圧VcomB,VcomWの差を示すグラフであり、縦軸は上に行くほど値が大きくなる。また、図10の横軸の識別子mは、1本の走査信号線GLに接続しているM個の画素(TFT素子10)を区別する整数値であり、走査信号線GLの信号入力端に最も近い画素から順に、1,2,3,・・・,Mとしている。

【0087】

また、図10の曲線F3は、第1の液晶表示パネル1における走査信号線GLの信号入力端からの距離と、最適コモン電圧VcomB,VcomWの差との関係を示す分布曲線である。また、図10の曲線F4は、第2の液晶表示パネル1における走査信号線GLの信号入力端からの距離と、最適コモン電圧VcomB,VcomWの差との関係を示す分布曲線である。また、図10の曲線F5は、絶縁層の膜厚が面内で均一な液晶表示パネル(以下、レイアウトデータ通りの液晶表示パネルという)における走査信号線GLの信号入力端からの距離と、最適コモン電圧VcomB,VcomWの差との関係を示す分布曲線である。また、図10では、曲線F3、曲線F4、および曲線F5の関係をわかりやすくするために上下方向にずらして示している。

【0088】

また、図10に示した曲線F3、曲線F4、および曲線F5は、それぞれ、第1の液晶表示パネル1、第2の液晶表示パネル1、およびレイアウトデータ通りの液晶表示パネルを同じ条件で駆動させたときの分布曲線である。

【0089】

図10を見ると、第1の液晶表示パネル1および第2の液晶表示パネル1は、同じ条件で駆動したときに、走査信号線GLの信号入力端から遠い画素ほど最適コモン電圧VcomB,VcomWの差が小さくなる。そのため、第1の液晶表示パネル1および第2の液晶表示パネル1は、走査信号線GLの信号入力端から遠い画素ほど残像のレベルが弱くなる。したがって、第1の液晶表示パネル1と第2の液晶表示パネル1とでは、走査信号線GLの延伸方向で見た残像の傾向が同じ傾向である。

【0090】

しかしながら、第1の液晶表示パネル1は、信号入力端から最も近い位置にある画素の最適コモン電圧の差と最も遠い位置にある画素の最適コモン電圧の差との差ΔS3が、レイアウトデータ通りの液晶表示パネルにおける差ΔS5よりも大きくなる。すなわち、第1の液晶表示パネル1は、走査信号線GLの延伸方向で見た残像のレベルが、レイアウトデータ通りの液晶表示パネルよりも強くなる。

【0091】

これに対し、第2の液晶表示パネル1は、信号入力端から最も近い位置にある画素の最適コモン電圧の差と最も遠い位置にある画素の最適コモン電圧の差との差ΔS4が、レイアウトデータ通りの液晶表示パネルにおける差Δ5よりも小さくなる。すなわち、第2の液晶表示パネル1は、走査信号線GLの延伸方向で見た残像のレベルが、レイアウトデータ通りの液晶表示パネルよりも弱くなる。

【0092】

また、図を用いた詳細な説明は省略するが、第1の液晶表示パネル1および第2の液晶表示パネル2は、映像信号線DLの延伸方向でみたときの残像のレベルが、レイアウトデータ通りの液晶表示パネルとは異なる。

【0093】

また、図を用いた詳細な説明は省略するが、領域AR3に形成された回路を有する第3の液晶表示パネル1および領域AR4に形成された回路を有する第4の液晶表示パネル1についても同様のことが言え、走査信号線GLの延在方向で見たときの残像のレベルや、映像信号線DLの延伸方向でみたときの残像のレベルが、レイアウトデータ通りの液晶表示パネルとは異なる。

【0094】

以上の結果をまとめると、4面取りで製造された4枚の液晶表示パネル1における残像の傾向は、たとえば、下記の表1のようになる。

【0095】

【表1】

【0096】

なお、表1において、SPECxは走査信号線GLの延在方向で見たときの残像のレベルであり、SPECyは映像信号線DLの延在方向で見たときの残像のレベルである。また、表1において、丸印はレイアウトデータ通りの液晶表示パネルよりも残像のレベルが弱いことを意味し、×印はレイアウトデータ通りの液晶表示パネルよりも残像のレベルが強いことを意味する。

【0097】

このように、4面取りで製造された4枚の液晶表示パネル1は、同じ条件で駆動させたときに生じる残像の傾向が異なる。

【0098】

DCオフセット電圧を階調電圧に付加して残像を抑制する場合は、たとえば、液晶表示パネル1に生じる残像の傾向に合わせて、第1の駆動回路2の階調電圧生成回路を調整する。そのため、4面取りで製造された液晶表示パネル1を有する液晶表示装置の残像を傾向を均一化するには、第1の駆動回路2の調整方法が4通り必要になる。

【0099】

一方、寄生容量Cgsの大きさを調整して残像を抑制する場合は、たとえば、液晶表示パネル1に生じる残像の傾向にあわせて、走査信号線GLとソース電極505との重畳領域の面積や、走査信号線GLと画素電極PXとの平面距離などを補正する。そのため、4面取りで製造された液晶表示パネル1を有する液晶表示装置の残像を傾向を均一化するには、1つのレイアウトデータに対して4通りの補正が必要になる。

【0100】

また、従来の液晶表示パネル1の製造方法において、走査信号線GL、ソース電極505、および画素電極PXなどの導体パターンは、通常、エッチングで形成している。エッチングで導体パターンを形成するときには、マザーガラス11の表面全体に形成(成膜)された導電膜の上にレジストパターンを形成する。このとき、レジストパターンは、フォトリソグラフィー、すなわち導電膜上に形成した感光性材料膜を露光、現像して形成する。またこのとき、感光性材料膜は、通常、フォトマスクを有する露光装置で露光する。そのため、従来の液晶表示パネル1の製造方法では、レイアウトデータを補正した場合、補正後のレイアウトデータに基づいてフォトマスクを作製する必要がある。したがって、4面取りの製造方法において領域毎に個別に露光する場合は、露光パターンが異なる4枚のフォトマスクを作製する必要がある。また、4面取りの製造方法において4つの領域を一括で露光する場合は、1枚のフォトマスクの4つの領域に、異なる露光パターンを形成する必要がある。

【0101】

また、絶縁層をCVD法などの成膜法で形成する場合、膜厚の分布、すなわちマザーガラス11の中心からの距離と膜厚の変動量との関係は、たとえば、使用するCVD装置やチャンバーによって変化する。

【0102】

そのため、従来の多面取りの液晶表示パネルの製造方法に、従来の残像の抑制方法を適用すると、絶縁層の膜厚に生じるに二次元的な分布が異なる液晶表示パネルを有する液晶表示装置における残像の傾向を均一化させることが難しく、液晶表示装置の製造効率の低下や製造コストの上昇が懸念される。

【0103】

本発明の液晶表示パネルの製造方法は、上記のような懸念を鑑みてなされたものであり、絶縁層の膜厚に生じるに二次元的な分布が異なる液晶表示パネルを有する液晶表示装置間の残像の傾向を均一化させることが容易であり、液晶表示装置の製造効率の低下や製造コストの上昇を抑えることができる。

【実施例】

【0104】

図11および図12は、本発明による一実施例の液晶表示パネルの製造方法の原理を説明するための模式図である。

図11は、信号入力端からの距離と寄生容量Cgsの大きさとの関係を示す模式図である。図12は、寄生容量Cgsの調整方法の一例を示す模式図である。

【0105】

本実施例では、図7に示したような4面取りの液晶表示パネルの製造方法を挙げ、一組のマザーガラスから得られる4枚の液晶表示パネルにおける残像のレベルを均一化する方法について説明する。また、4枚の液晶表示パネル1には、それぞれ、図2および図3に示したような構成の画素を形成する。

【0106】

4面取りで製造された液晶表示パネルのうちの、領域AR1に形成された回路(TFT基板5)を有する第1の液晶表示パネル1、および領域AR2に形成された回路(TFT基板5)を有する第2の液晶表示パネル1は、それぞれ、走査信号線GLの延在方向でみた各画素の寄生容量Cgsの大きさに、たとえば、図11に示すような変動がある。

【0107】

なお、図11は、横軸が画素の識別子m、縦軸が寄生容量Cgsの大きさを示すグラフであり、縦軸は上に行くほど値が大きくなる。また、図11の横軸の識別子mは、1本の走査信号線GLに接続しているM個の画素(TFT素子10)を区別する整数値であり、走査信号線GLの信号入力端に最も近い画素から順に、1,2,3,・・・,Mとしている。

【0108】

また、図11の直線F6は、絶縁層の膜厚が面内で均一な液晶表示パネル(レイアウトデータ通りの液晶表示パネル)における走査信号線GLの信号入力端からの距離と寄生容量Cgsとの関係を示す分布曲線である。また、図11の曲線F7は、第1の液晶表示パネル1における走査信号線GLの信号入力端からの距離と寄生容量Cgsとの関係を示す分布曲線である。また、図11の曲線F8は、第2の液晶表示パネル1における走査信号線の信号入力端からの距離と寄生容量Cgsとの関係を示す分布曲線である。また、図11の曲線F9は、残像の発生を抑えるのに最適な、走査信号線GLの信号入力端からの距離と寄生容量Cgsとの関係の一例を示す分布曲線である。

【0109】

レイアウトデータを作製するときには、通常、絶縁膜の膜厚が面内で均一であるとしている。そのため、レイアウトデータ通りに製造された液晶表示パネル1は、走査信号線GLの延伸方向で見たときの、走査信号線の信号入力端からの距離と寄生容量Cgsとの関係が、図11に示した直線F6のように、一定の関係になる。

【0110】

これに対し、第1の液晶表示パネル1は、走査信号線GLの延伸方向に沿った膜厚が、信号入力端から遠ざかるにつれて薄くなる。そのため、上記のレイアウトデータに基づいて第1の薄膜積層体を形成した場合、第1の液晶表示パネル1における走査信号線GLの信号入力端からの距離と寄生容量Cgsとの関係は、図11に示した曲線F7のように、信号入力端からの距離が遠くなるにつれて寄生容量Cgsが大きくなる関係になる。

【0111】

また、第2の液晶表示パネル1は、走査信号線GLの延伸方向に沿った膜厚が、信号入力端から遠ざかるにつれて厚くなる。そのため、上記のレイアウトデータに基づいて第1の薄膜積層体を形成した場合、第2の液晶表示パネル1における走査信号線GLの信号入力端からの距離と寄生容量Cgsとの関係は、図11に示した曲線F8のように、信号入力端からの距離が遠くなるにつれて寄生容量Cgsが小さくなる関係になる。

【0112】

また、特許文献1などによると、走査信号の遅延による残像を低減するためには、走査信号線GLの延伸方向に沿って並んだ画素における寄生容量Cgsの関係が、たとえば、図11に示した曲線F9のような関係になるようにすることが望ましいとされている。

【0113】

したがって、第1の液晶表示パネル1および第2の液晶表示パネル1における走査信号線の延伸方向に沿った残像のレベルを低減するには、それぞれ、曲線F7および曲線F8が、曲線F9になるようにすればよい。

【0114】

第1の絶縁層503などの絶縁層は、CVD法などの成膜法で形成するので、膜厚を面内で均一にすることが難しい。そのため、本実施例の液晶表示パネルの製造方法では、絶縁層の膜厚分布を考慮して、各画素の寄生容量Cgsの電極面積を調整し、信号入力端からの距離と寄生容量Cgsの大きさとの関係を曲線F9のような関係にする。

【0115】

また、本実施例の液晶表示パネル1では、たとえば、図12に示すように、走査信号線GLのうちの、ソース電極505との重畳領域に補正パターンRPを設けて、各画素の寄生容量Cgsの大きさを調整する。

【0116】

図13乃至図16は、領域AR1に形成される画素の寄生容量Cgsの補正方法の一例を示す模式図である。

図13は、領域AR1に形成されたTFT基板における信号入力端の位置と絶縁層の膜厚分布との関係を示す模式平面図である。図14は、領域AR1に形成されたTFT基板における絶縁層の膜厚の変動量の一例を示す模式図である。図15は、図13に示した3本の走査信号線に接続している画素の寄生容量Cgsの補正量の一例を示す模式図である。図16は、補正後のレイアウトデータにおける4隅の画素の補正パターンの一例を示す模式図である。

【0117】

領域AR1に形成される絶縁層は、たとえば、図13に示すように、走査信号線GLの信号入力端GINから遠ざかるにつれて薄くなり、かつ、映像信号線DLの信号入力端DINから遠ざかるにつれて薄くなる。このとき、絶縁層の膜厚が最も薄くなる画素は、走査信号線の信号入力端GINから最も遠く、かつ、映像信号線の信号入力端DINから最も遠い位置にある画素U6である。すなわち、各画素における走査信号線GLとソース電極505との重畳領域の面積が等しい場合、寄生容量Cgsが最も大きくなるのは、画素U6である。

【0118】

したがって、図12に示したような補正パターンを付加することで各画素の寄生容量Cgsを調整する場合は、画素U6における寄生容量Cgsの大きさを基準にして調整する。

【0119】

領域AR1において、画素U6における絶縁層の厚さを基準膜厚にした場合、基準膜厚と、表示領域内にある各画素U1,U2,U3,U4,U5,U6における絶縁層の厚さとの差の関係は、たとえば、図14に示すような関係になる。なお、図14の縦軸は、絶縁膜の厚さの差である。

【0120】

このとき、映像信号線DLの信号入力端DINから最も遠い位置にある走査信号線GLNに接続されている画素の寄生容量Cgsの分布を、図11に示した曲線F9のようにするには、たとえば、画素U6における寄生容量Cgsを基準にし、当該走査信号線GLNに接続されている各画素の寄生容量Cgsを決める。走査信号線GLNの上における絶縁層の膜厚は、図14に示した点線ような変化をしている。そのため、領域AR1では、映像信号線DLの信号入力端DINから最も遠い位置にある走査信号線GLNに接続されている画素の寄生容量Cgsの分布を、たとえば、図15に示した曲線F10Nのような分布にする。

【0121】

また、映像信号線DLの信号入力端DINから最も近い位置にある走査信号線GL1に接続されている画素の寄生容量Cgsの分布を、図11に示した曲線F9のようにするには、たとえば、画素U3における寄生容量Cgsを基準にし、当該走査信号線GL1に接続されている各画素の寄生容量Cgsを決める。走査信号線GL1の上における絶縁層の膜厚は、図14に示した実線のような変化をしており、走査信号線GL1の信号入力端GINから最も遠い位置にある画素U3における絶縁層の膜厚は、画素U6における膜厚よりも厚くなっている。そのため、領域AR1では、映像信号線DLの信号入力端DINから最も近い位置にある走査信号線GL1に接続されている画素の寄生容量Cgsの分布を、たとえば、図15に示した曲線F101のような分布にする。

【0122】

また、そのほかの走査信号線GLiに接続されている画素の寄生容量Cgsの分布についても、同様の手順で決めればよい。このとき、領域AR1では、走査信号線GLiに接続されている画素の寄生容量Cgsの分布は、たとえば、図15に示した曲線F10iのような分布になる。

【0123】

このとき、各画素における補正パターンの寸法が上記の分布にしたがうようにレイアウトデータを補正し、領域AR1に回路(第1の薄膜積層体)を形成すると、表示領域の4隅に位置する4つの画素U1,U3,U4,U6における走査信号線GLとソース電極505との重畳領域の関係は、たとえば、図15に示すようになる。

【0124】

このようにすると、各走査信号線GLnの配線容量の組み合わせ(時定数)が概ね等しくなり、信号入力端からの距離と遅延量の関係が概ね等しくなる。またこのとき、各走査信号線GLにおける信号入力端からの距離と寄生容量Cgsの大きさの変動量との関係が概ね等しくなる。したがって、領域AR1に形成された回路を有する液晶表示パネル1は、たとえば、DCオフセット電圧が十分小さくても、残像を抑制することができる。

【0125】

図17乃至図19は、領域AR2に形成される画素の寄生容量Cgsの補正方法の一例を示す模式図である。

図17は、領域AR2に形成されたTFT基板における信号入力端の位置と絶縁層の膜厚分布との関係を示す模式平面図である。図18は、図17に示した映像信号線に接続している画素の寄生容量Cgsの補正量の一例を示す模式図である。図19は、補正後のレイアウトデータにおける4隅の画素の補正パターンの一例を示す模式図である。

【0126】

領域AR2に形成される絶縁層の膜厚は、たとえば、図17に示すように、走査信号線GLの信号入力端GINから遠ざかるにつれて厚くなり、かつ、映像信号線DLの信号入力端DINから遠ざかるにつれて薄くなる。

【0127】

領域AR2では、たとえば、図10に示したように、DCオフセット電圧を領域AR1に形成された液晶表示パネル1より小さく入力しても、走査信号線GLの延伸方向でみた残像のレベルが、レイアウトデータ通りの場合に比べて小さくなる。しかしながら、残像のレベルは補正後の領域AR1より大きい。したがって、領域AR2に形成する回路についても、領域AR1と同様に補正し1本の走査信号線に接続されている画素の寄生容量Cgsの分布は、たとえば、図18に示した曲線F11のようになる。

【0128】

このとき、各画素における補正パターンの寸法が上記の分布にしたがうようにレイアウトデータを補正し、領域AR2に回路(第1の薄膜積層体)を形成すると、表示領域の4隅に位置する4つの画素U1,U3,U4,U6における走査信号線GLとソース電極505との重畳領域の関係は、たとえば、図19に示すようになる。

【0129】

このようにすると、各走査信号線GLnの配線容量の組み合わせ(時定数)が概ね等しくなり、信号入力端からの距離と遅延量の関係が概ね等しくなる。またこのとき、各走査信号線における信号入力端からの距離と寄生容量Cgsの大きさの変動量との関係が概ね等しくなる。したがって、領域AR2に形成された回路を有する液晶表示パネル1の残像を抑制することができる。

【0130】

図20は、本実施例の製造方法の作用効果の一例を示す模式図である。

【0131】

本実施例の液晶表示パネルの製造方法では、上記のように、4面取りで製造された第1の液晶表示パネル1と第2の液晶表示パネル1とを比較すると、各画素における走査信号線GLとソース電極505との重畳領域の面積の関係に違いが生じる。

【0132】

しかしながら、第1の液晶表示パネル1および第2の液晶表示パネル1は、それぞれ、第1の絶縁層503の膜厚分布に基づいて、各画素における寄生容量Cgsの大きさを調整している。そのため、第1の液晶表示パネル1と第2の液晶表示パネル2を同じ条件で駆動すると、たとえば、図20に示すように、それぞれの液晶表示パネル1における走査信号線の延在方向で見た残像のレベルΔS3’,ΔS4’が、補正前の液晶表示パネル1の残像のレベルΔS3,ΔS4よりも小さくなり、かつ、概ね等しくなる。

【0133】

また、詳細な説明は省略するが、領域AR3および領域AR4に形成する回路(第1の薄膜積層体)についても、領域AR1および領域AR2の場合と同様の考え方で、各画素における寄生容量Cgsの大きさを決めてやれば、領域AR3に形成された回路を有する第3の液晶表示パネル1および領域AR4に形成された回路を有する第4の液晶表示パネル1も、走査信号線GLの延伸方向で見た残像のレベルを小さくすることができる。

【0134】

したがって、本実施例の液晶表示パネルの製造方法では、一組のマザーガラスから得られる4枚の液晶表示パネル1を駆動するときにDCオフセット電圧を液晶表示パネル毎に変更しなくても、それぞれの液晶表示パネル1における残像を抑制することができ、かつ、4枚の液晶表示パネル1間の残像の傾向を均一化することができる。

【0135】

さて、このように絶縁層の膜厚分布に応じて走査信号線GLとソース電極505との重畳領域の面積を変える場合、従来の液晶表示パネル1の製造方法だと、たとえば、走査信号線GLに関するレイアウトデータを4通りに補正し、走査信号線GLを形成する工程で使用するフォトマスクを4通りに作り分ける必要がある。

【0136】

また、絶縁層の膜厚分布は、使用するCVD装置やチャンバーによって異なることがある。そのため、絶縁層の膜厚分布に応じてレイアウトデータを補正し、フォトマスクを作り分けるのは効率が悪い。

【0137】

したがって、本実施例の液晶表示パネルの製造方法では、走査信号線GLを形成する工程で行う感光性材料膜の露光を、直描露光方式またはダイレクト露光方式と呼ばれる露光装置で行う。

【0138】

直描露光方式の露光装置は、フォトマスクの代わりに、数値制御により露光パターンを生成する空間光変調素子を用いる。このとき、空間光変調素子は、レイアウトデータを所定の条件で変換して得られる描画データ(数値データ)に基づいて制御する。そのため、直描露光方式の露光装置で感光性材料膜を露光するときには、レイアウトデータの数値を変えるだけで露光パターンを変えることができる。

【0139】

図21は、本実施例の液晶表示パネルの製造方法の主要部を説明するための模式フロー図である。

【0140】

実施例1の液晶表示パネルの製造方法は、たとえば、CVD装置と寄生容量Cgsの補正量との関係を登録する工程、レイアウトデータを描画データに変換する工程、液晶表示パネル1を製造する工程の3つの工程を有する。

【0141】

CVD装置と寄生容量Cgsの補正量との関係を登録する工程は、たとえば、図21に示したSTART1からEND1までのような処理を行う。まず、液晶表示パネルの製造に使用するCVD装置と絶縁層の膜厚分布との関係を、たとえば、所定のデータサーバの膜厚分布データベースに登録しておく(ステップS11)。

【0142】

このとき、CVD装置と絶縁層の膜厚分布との関係は、たとえば、CVD装置の号機毎、チャンバー毎に計測する。そして、膜厚分布データベースには、たとえば、CVD装置の号機番号、チャンバー番号、マザーガラス上の面付け位置(領域)、および絶縁膜の膜厚分布の傾向を関連づけたデータを登録する。

【0143】

次に、データサーバにおいて、膜厚分布データベースに登録された上記の関係毎に、たとえば、図15に示したような寄生容量Cgsの補正量を算出し、補正データベースに登録する(ステップS12)。

【0144】

このとき、補正データベースには、たとえば、CVD装置の号機番号、チャンバー番号、マザーガラス上の面付け位置(領域)、および絶縁膜の膜厚分布の傾向と、寄生容量Cgsの補正量とを関連づけたデータを登録する。

【0145】

またこのとき、CVD装置と寄生容量Cgsの補正量との関係を登録する工程は、たとえば、ステップS11とステップS12の処理を定期的に行う。

【0146】

また、レイアウトデータを描画データに変換する工程は、たとえば、図21に示したSTART2からEND2までのような処理を行う。まず、CADなどで作製されたレイアウトデータを、データサーバに登録する(ステップS21)。

【0147】

このとき、データサーバでは、登録されたレイアウトデータと、データベースに登録された寄生容量Cgsの補正量に基づいて、走査信号線とソース電極の重畳領域の面積の補正量を決定(ステップS22)し、決定された補正量に基づいてレイアウトデータを補正する(S23)。

【0148】

次に、データサーバでは、補正されたレイアウトデータから描画データを生成し、描画データベースに登録する(ステップS24)。

【0149】

このとき、描画データベースには、CVD装置の号機番号、チャンバー番号、マザーガラス上の面付け位置(領域)、および描画データを関連づけて登録する。

【0150】

またこのとき、CVD装置と寄生容量Cgsの補正量との関係が変更されたら、描画データも変更する。

【0151】

また、液晶表示パネル1を製造する工程は、基本的には、従来と同じ手順であり、TFT基板5を形成する工程、対向基板6を形成する工程、TFT基板5と対向基板6を貼り合わせるとともに液晶材料(液晶層7)を封入する工程を有する。このとき、TFT基板5を形成する工程は、たとえば、図21に示したSTART3からEND3までのような処理を行う。まず、マザーガラス上に、走査信号線GLを形成するための導電膜を形成(成膜)し、当該導電膜の上に感光性材料膜を形成(成膜)する(ステップS31)。

【0152】

導電膜の上に形成された感光性材料膜の露光は、上記のように直描露光方式の露光装置で行う。直描露光方式の露光装置で感光性材料膜を露光するときには、まず、露光装置に、たとえば、第1の絶縁層503を形成するときに使用するCVD装置の号機番号およびチャンバー番号を設定(ステップS32)し、描画データベースに登録されている描画データを取得する(ステップS33)。

【0153】

このとき、露光装置には、たとえば、CVD装置の号機番号およびチャンバー番号に基づいて、面付け位置(マザーガラスに設定された4つの領域)のそれぞれと対応する、4通りの描画データが登録される。

【0154】

露光装置は、4通りの描画データを取得したら、当該描画データを用いて、マザーガラスに設定された4つの領域の露光を行う(ステップS34)。

【0155】

次に、感光性材料膜を現像し、導電膜をエッチングすると、マザーガラスの4つの領域には、取得した描画データを反映した平面形状の走査信号線GLが形成される(ステップS35)。

【0156】

その後、感光性材料膜を露光する時に指定したCVD装置で第1の絶縁層503を形成し、続けてTFT素子10の半導体層504の形成、映像信号線DLおよびソース電極10などの形成を行い、各領域に所定の回路(第1の薄膜積層体)を形成する(ステップS36)。

【0157】

また、図示は省略するが、これと並行して別のマザーガラスに対向基板6を形成し、これら2枚のマザーガラスを貼り合わせるとともに液晶材料(液晶層7)を封入する。そして、各領域を切り出すと、4枚の液晶表示パネル1が得られる。

【0158】

こうして得られた4枚の液晶表示パネル1は、上記のように、同じ条件で駆動させたときに、1枚の液晶表示パネル内における残像が抑制されており、かつ、4枚の液晶表示パネル1の間の残像のレベルが同程度になる。

【0159】

また、液晶表示パネル1を上記の手順で製造する場合、第1の絶縁層503を形成するときに使用するCVD装置やチャンバーが異なっても、残像のレベルを同程度にすることができる。

【0160】

また、本実施例の製造方法の場合、たとえば、あるCVD装置における膜厚分布が途中で変動しても、寄生容量Cgsの大きさの変更が容易である。

【0161】

以上説明したように、本実施例の液晶表示装置の製造方法によれば、1枚の液晶表示パネルにおける残像の抑制、および複数枚の液晶表示パネル間の残像のレベルの均一化が容易になる。

【0162】

以上、本発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において、種々変更可能であることはもちろんである。

【0163】

たとえば、前記実施例では、4面取りで液晶表示パネルを製造する場合を例に挙げているが、本発明の製造方法は、4面取りに限らず、一組のマザーガラスを用いて任意のn枚の液晶表示パネルを一括製造するn面取りの製造方法に適用できることはもちろんである。

【0164】

また、前記実施例では、たとえば、図2および図3に示したような構成の画素を有する液晶表示パネルを製造する場合を例に挙げている。しかしながら、本発明の製造方法は、これに限らず、各画素のTFT素子のソース電極が、ゲート電極(走査信号線)と重畳している部分としていない部分とを有する構造であり、かつ、レイアウトデータ通りに製造したときに残像が生じる液晶表示パネルであれば適用可能である。すなわち、本発明の製造方法は、たとえば、IPS方式のように共通電極がTFT基板側に形成されている液晶表示パネルの製造方法などにも適用できる。

【0165】

また、前記実施例の製造方法で製造された液晶表示パネルを駆動すると、たとえば、図20に示したように、残像のレベルが低減するものの、完全にゼロにならないこともある。そのため、前記実施例の製造方法で製造された液晶表示パネルを駆動するときには、たとえば、DCオフセット電圧を階調電圧に付加して駆動させてもよい。このようにすることで、残像のレベルをさらに低減することができる。またこのとき、一組のマザーガラスから得られる複数枚の液晶表示パネルは、絶縁層の膜厚分布によらず、残像のレベルが概ね等しい。そのため、DCオフセット電圧を階調電圧に付加して当該複数枚の液晶表示パネルを駆動させる場合、第1の駆動回路の調整が容易になる。

【符号の説明】

【0166】

1 液晶表示パネル

2 第1の駆動回路

3 第2の駆動回路

4 制御回路

5 TFT基板

6 対向基板

GL 走査信号線

DL 映像信号線

PX 画素電極

CT 共通電極

501 第1の絶縁基板

502 保持容量線

503 第1の絶縁層

504 半導体層

505 ソース電極

506 第2の絶縁層

507 第1の配向膜

601 第2の絶縁基板

602 ブラックマトリクス

603 カラーフィルタ

604 平坦化層

605第2の配向膜

7 液晶層

8 第1の偏光板

9 第2の偏光板

10 TFT素子

11 マザーガラス

【特許請求の範囲】

【請求項1】

TFT基板と対向基板との間に液晶材料が封入された液晶表示パネルを有し、

前記TFT基板は、複数の走査信号線、複数の映像信号線、複数のTFT素子、および複数の画素電極を有し、

前記複数のTFT素子は、ゲート電極が前記複数の走査信号線のうちの1本の走査信号線に接続し、ドレイン電極が前記複数の映像信号線のうちの1本の映像信号線に接続しており、かつ、TFT素子毎に、前記ゲート電極が接続している前記走査信号線と前記ドレイン電極が接続している前記映像信号線との組み合わせが異なる液晶表示装置であって、

前記TFT素子のソース電極は、走査信号線と重畳している部分としていない部分とを有し、

1本の前記走査信号線に接続している複数のTFT素子は、当該走査信号線の信号入力端からの距離と前記ソース電極と前記走査信号線との重畳領域の面積との関係が、単調減少の関係であることを特徴とする液晶表示装置。

【請求項2】

1本の前記映像信号線に接続している複数のTFT素子は、当該映像信号線の信号入力端からの距離と前記ソース電極と前記走査信号線との重畳領域の面積との関係が、単調減少の関係であることを特徴とする請求項1に記載の液晶表示装置。

【請求項3】

TFT基板を形成する工程と、対向基板を形成する工程と、前記TFT基板と前記対向基板とを貼り合わせるとともに液晶材料を封入して液晶表示パネルを形成する工程とを有し、

前記TFT基板を形成する工程は、あらかじめ用意されたレイアウトデータに基づいて複数の走査信号線、複数の映像信号線、複数のTFT素子、および複数の画素電極を形成する液晶表示装置の製造方法であって、

前記複数のTFT素子のソース電極は、前記画素電極と接続し、かつ、前記走査信号線と重畳させる部分とさせない部分とを有し、

前記TFT基板を形成する工程は、前記複数の走査信号線を形成する第1の工程と、

前記第1の工程の後、第1の絶縁層を形成する第2の工程と、

前記第1の絶縁層の上に、前記TFT素子の半導体層、前記複数の映像信号線、および前記TFT素子のソース電極を形成する第3の工程を有し、

前記第1の工程は、導電膜を形成する工程と、

前記導電膜の上に感光性材料膜を形成する工程と、

前記感光性材料膜を露光、現像する工程と、

現像した前記感光性材料膜をマスクにして前記導電膜の不要な部分を除去する工程を有し、

前記感光性材料膜の露光は、前記レイアウトデータに基づいて作成される描画データによる数値制御で露光パターンを生成する空間光変調素子を有する露光装置を用いて行い、

前記描画データは、前記レイアウトデータにおける前記走査信号線のうちの、前記ソース電極と重畳させる部分の形状が、前記第2の工程で形成される前記第1の絶縁層の膜厚の分布に応じた面積になるように補正して作成することを特徴とする液晶表示装置の製造方法。

【請求項4】

前記TFT基板を形成する工程は、1枚のマザー基板を用いて複数枚のTFT基板を一括して形成し、

前記第1の工程で行う前記感光性材料膜の露光は、前記マザー基板上における前記TFT基板の位置毎に、異なる前記描画データを用いて行うことを特徴とする請求項3に記載の液晶表示装置の製造方法。

【請求項1】

TFT基板と対向基板との間に液晶材料が封入された液晶表示パネルを有し、

前記TFT基板は、複数の走査信号線、複数の映像信号線、複数のTFT素子、および複数の画素電極を有し、

前記複数のTFT素子は、ゲート電極が前記複数の走査信号線のうちの1本の走査信号線に接続し、ドレイン電極が前記複数の映像信号線のうちの1本の映像信号線に接続しており、かつ、TFT素子毎に、前記ゲート電極が接続している前記走査信号線と前記ドレイン電極が接続している前記映像信号線との組み合わせが異なる液晶表示装置であって、

前記TFT素子のソース電極は、走査信号線と重畳している部分としていない部分とを有し、

1本の前記走査信号線に接続している複数のTFT素子は、当該走査信号線の信号入力端からの距離と前記ソース電極と前記走査信号線との重畳領域の面積との関係が、単調減少の関係であることを特徴とする液晶表示装置。

【請求項2】

1本の前記映像信号線に接続している複数のTFT素子は、当該映像信号線の信号入力端からの距離と前記ソース電極と前記走査信号線との重畳領域の面積との関係が、単調減少の関係であることを特徴とする請求項1に記載の液晶表示装置。

【請求項3】

TFT基板を形成する工程と、対向基板を形成する工程と、前記TFT基板と前記対向基板とを貼り合わせるとともに液晶材料を封入して液晶表示パネルを形成する工程とを有し、

前記TFT基板を形成する工程は、あらかじめ用意されたレイアウトデータに基づいて複数の走査信号線、複数の映像信号線、複数のTFT素子、および複数の画素電極を形成する液晶表示装置の製造方法であって、

前記複数のTFT素子のソース電極は、前記画素電極と接続し、かつ、前記走査信号線と重畳させる部分とさせない部分とを有し、

前記TFT基板を形成する工程は、前記複数の走査信号線を形成する第1の工程と、

前記第1の工程の後、第1の絶縁層を形成する第2の工程と、

前記第1の絶縁層の上に、前記TFT素子の半導体層、前記複数の映像信号線、および前記TFT素子のソース電極を形成する第3の工程を有し、

前記第1の工程は、導電膜を形成する工程と、

前記導電膜の上に感光性材料膜を形成する工程と、

前記感光性材料膜を露光、現像する工程と、

現像した前記感光性材料膜をマスクにして前記導電膜の不要な部分を除去する工程を有し、

前記感光性材料膜の露光は、前記レイアウトデータに基づいて作成される描画データによる数値制御で露光パターンを生成する空間光変調素子を有する露光装置を用いて行い、

前記描画データは、前記レイアウトデータにおける前記走査信号線のうちの、前記ソース電極と重畳させる部分の形状が、前記第2の工程で形成される前記第1の絶縁層の膜厚の分布に応じた面積になるように補正して作成することを特徴とする液晶表示装置の製造方法。

【請求項4】

前記TFT基板を形成する工程は、1枚のマザー基板を用いて複数枚のTFT基板を一括して形成し、

前記第1の工程で行う前記感光性材料膜の露光は、前記マザー基板上における前記TFT基板の位置毎に、異なる前記描画データを用いて行うことを特徴とする請求項3に記載の液晶表示装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2011−53383(P2011−53383A)

【公開日】平成23年3月17日(2011.3.17)

【国際特許分類】

【出願番号】特願2009−201240(P2009−201240)

【出願日】平成21年9月1日(2009.9.1)

【出願人】(502356528)株式会社 日立ディスプレイズ (2,552)

【Fターム(参考)】

【公開日】平成23年3月17日(2011.3.17)

【国際特許分類】

【出願日】平成21年9月1日(2009.9.1)

【出願人】(502356528)株式会社 日立ディスプレイズ (2,552)

【Fターム(参考)】

[ Back to top ]