液晶表示装置および液晶表示装置の駆動方法

【課題】上下反転表示を実現するとともに表示品位の良好な液晶表示装置およびその駆動方法を提供する。

【解決手段】画素電極PEが配列した行に沿って延びたゲート線Gおよび補助容量線Csと、画素電極PEが配列した列に沿って延びた信号線Sと、ゲート線G、信号線S、および、補助容量線Csを駆動する駆動回路XD、YDと、を備えたアレイ基板ARと、アレイ基板ARと対向して配置された対向基板CTと、上下方向に並ぶゲート線Gを順次駆動する第1走査と、下上方向に並ぶゲート線Gを順次駆動する第2走査とを切替える走査方向制御信号UDと、補助容量線Csに供給する信号SCsの極性を制御する極性制御信号FRと、を供給し、第1走査を行う場合と第2走査を行う場合との極性制御信号FRが同じであるフレーム期間において、信号線Sへ供給する信号の極性を水平期間H単位で位相が異なるように駆動回路XD、YDを制御可能な制御回路と、を備える。

【解決手段】画素電極PEが配列した行に沿って延びたゲート線Gおよび補助容量線Csと、画素電極PEが配列した列に沿って延びた信号線Sと、ゲート線G、信号線S、および、補助容量線Csを駆動する駆動回路XD、YDと、を備えたアレイ基板ARと、アレイ基板ARと対向して配置された対向基板CTと、上下方向に並ぶゲート線Gを順次駆動する第1走査と、下上方向に並ぶゲート線Gを順次駆動する第2走査とを切替える走査方向制御信号UDと、補助容量線Csに供給する信号SCsの極性を制御する極性制御信号FRと、を供給し、第1走査を行う場合と第2走査を行う場合との極性制御信号FRが同じであるフレーム期間において、信号線Sへ供給する信号の極性を水平期間H単位で位相が異なるように駆動回路XD、YDを制御可能な制御回路と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、液晶表示装置および液晶表示装置の駆動方法に関する。

【背景技術】

【0002】

液晶表示装置は、一対の基板と、この一対の基板間に挟持された液晶層と、複数の表示画素からなる表示領域とを備えている。

【0003】

液晶表示装置では交番電界駆動を実施しており、フリッカ対策のため1又は複数の走査ライン毎に液晶印加電圧の極性を反転させている。走査線毎の極性反転、または、信号線毎の極性反転のいずれか一方だけでは、走査線が延びる方向または信号線が延びる方向に沿ってフリッカが見えることがあり、高画質液晶表示装置では、走査線毎と信号線毎との両方で極性反転するドット反転駆動を採用することがある。

【0004】

一方、信号電圧振幅を低減する方法として、容量結合駆動(CC(capacitively-coupled)駆動)が提案されている。容量結合駆動では、補助容量を通して、補助容量信号を画素電極に重畳することで所定の電圧に到達させる。容量結合駆動を採用すると、補助容量と画素容量とを略等しくする場合、信号電圧振幅を概略半減できる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−271484号公報

【特許文献2】特開平9−190163号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

携帯電話やスマートフォン等の電子機器に搭載される液晶表示装置の仕様として、画面表示が上下反転表示に対応していることが要求されている。そのため液晶表示装置は、少なくとも、走査方向が上から下へ進む方向の走査(上下走査)と、下から上へ進む方向の走査(下上走査)とのいずれであっても正常に表示できることが要求される。

【0007】

なお、以下の説明において、液晶表示装置使用時の置き方(縦置き又は横置き)とは関係なく、信号線の延びる方向を上下方向とし、一方側を「上」、その反対側を「下」として説明する。

【0008】

本実施形態は、上下反転表示を実現するとともに表示品位の良好な液晶表示装置および液晶表示装置の駆動方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

実施形態によれば、マトリクス状に配置された画素電極と、前記画素電極が配列した行に沿って延びたゲート線と、前記画素電極が配列した列に沿って延びた信号線と、前記ゲート線と略平行に延びた補助容量線と、前記ゲート線、前記信号線、および、前記補助容量線を駆動する駆動回路と、を備えたアレイ基板と、前記アレイ基板と対向して配置された対向基板と、前記アレイ基板と前記対向基板との間に挟持された液晶層と、前記信号線が延びる方向と略平行な方向に並ぶ前記ゲート線を第1方向に順次駆動する第1走査と、前記第1方向と逆方向の第2方向に前記ゲート線を順次駆動する第2走査とを切替える走査方向制御信号と、前記補助容量線に供給する信号の極性を制御する極性制御信号と、を供給し、前記駆動回路の動作を制御する制御回路と、を備え、前記制御回路は、前記第1走査を行う場合と前記第2走査を行う場合との前記極性制御信号が同じであるフレーム期間において、前記信号線へ供給する信号の極性を水平期間単位で位相が異なるように前記駆動回路を制御可能である液晶表示装置が提供される。

【図面の簡単な説明】

【0010】

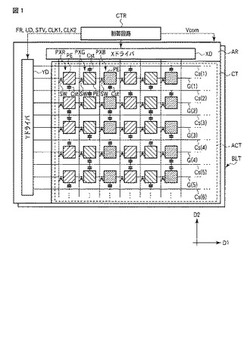

【図1】図1は、一実施形態に係る液晶表示装置の一構成例を概略的に示す図である。

【図2】図2は、図1に示す液晶表示装置のYドライバの回路ブロックの一例を示す図である。

【図3A】図3Aは、一実施形態の液晶表示装置において上下走査を行う際の駆動方法の一例を説明するためのタイミングチャートである。

【図3B】図3Bは、一実施形態の液晶表示装置において下上走査を行う際の駆動方法の一例を説明するためのタイミングチャートである。

【図4A】図4Aは、1H1V−CCDI駆動を行う液晶表示装置において上下走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図4B】図4Bは、1H1V−CCDI駆動を行う液晶表示装置において上下走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図4C】図4Cは、1H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図4D】図4Dは、1H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5A】図5Aは、2H1V−CCDI駆動を行う液晶表示装置において上下走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5B】図5Bは、2H1V−CCDI駆動を行う液晶表示装置において上下走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5C】図5Cは、2H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5D】図5Dは、2H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5E】図5Eは、2H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5F】図5Fは、2H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5G】図5Gは、2H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5H】図5Hは、2H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5I】図5Iは、2H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5J】図5Jは、2H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図6A】図6Aは、CCカラム反転駆動を行う液晶表示装置において上下走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図6B】図6Bは、CCカラム反転駆動を行う液晶表示装置において上下走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図6C】図6Cは、CCカラム反転駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図6D】図6Dは、CCカラム反転駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図6E】図6Eは、CCカラム反転駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図6F】図6Fは、CCカラム反転駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【発明を実施するための形態】

【0011】

以下、一実施形態に係る液晶表示装置について、図面を参照して詳細に説明する。

図1は、一実施形態に係る液晶表示装置の一構成例を概略的に示す図である。図1に示すように、本実施形態に係る液晶表示装置は複数の表示画素PXからなる表示領域ACTを備えた液晶表示パネルLPNと、液晶表示パネルの表示領域ACTを照明するように配置されたバックライトBLTと、液晶表示パネルLPNとバックライトBLTとを制御する制御回路CTRと、を備えている。

【0012】

液晶表示パネルLPNは一対の基板、すなわち、アレイ基板ARおよび対向基板CTと、アレイ基板ARおよび対向基板CT間に挟持された液晶層(図示せず)と、を有している。本実施形態に係る液晶表示装置では、画素配列として正方配列を採用している。複数の表示画素PXはマトリクス状に配置されている。

【0013】

本実施形態に係る液晶表示装置はカラー表示タイプの液晶表示装置であって、複数の表示画素PXは、複数の色表示画素を含んでいる。図1に示す液晶表示装置は、赤色を表示する赤色表示画素PXR、緑色を表示する緑色表示画素PXG、および、青色を表示する青色表示画素PXBを含む。

【0014】

アレイ基板ARは、例えばガラス等の透明絶縁基板(図示せず)を有している。この透明絶縁基板上には、各表示画素PXに対応する複数の画素電極PEが配置されている。さらに、アレイ基板ARは、複数の画素電極PEが配列する行に沿って第1方向D1に延びた複数のゲート線G(G(1)〜G(M))、複数の画素電極PEが配列する列に沿って第2方向D2に延びた複数の信号線S(S(1)〜S(N))、ゲート線Gと略平行に延びる補助容量線Cs(Cs(1)〜Cs(M+1))および、これらゲート線Gおよび信号線Sの交差位置近傍に配置された複数の画素スイッチSWを有している。

【0015】

各画素スイッチSWは、例えば、スイッチング素子として薄膜トランジスタ(TFT)を含む。画素スイッチSWのゲートがゲート線Gと電気的に接続され(あるいは一体に形成され)、ソースが信号線Sと電気的に接続され(あるいは一体に形成され)、ドレインが画素電極PEと電気的に接続され(あるいは一体に形成され)ている。各画素スイッチSWは、各々対応ゲート線Gを介して駆動されたときに対応信号線Sおよび対応画素電極PE間で導通する。

【0016】

液晶表示パネルLPNは、駆動回路として、さらに複数の画素スイッチSWを行単位に導通させるように複数のゲート線G(1)〜G(M)を順次駆動するとともに、複数の補助容量線Cs(1)〜Cs(M+1)を駆動するYドライバYD、および、各行の画素スイッチSWが対応ゲート線Gの駆動によって導通する期間において映像信号あるいは逆転移防止信号を複数の信号線S(1)〜S(N)にそれぞれ出力するXドライバXDを備えている。

【0017】

YドライバYDおよびXドライバXDは、外付けのICとして搭載してもよく、アレイ基板AR上に内蔵回路として造りこんでもよい。本実施形態に係る液晶表示装置では、YドライバYDおよびXドライバXDは表示領域ACTの周囲に配置され、制御回路CTRによりその動作を制御される。

【0018】

なお図1ではYドライバYDが表示領域ACTの左側に配置されているが、場合によっては右側に配置されてもよい。あるいは同一の機能をもつ2つのYドライバYDが左右両側に対称な形で配置されてもよい。あるいは、YドライバYDを、ゲート線Gを駆動する機能と補助容量線Csを駆動する機能とに分離してそれぞれ左右に分けて配置されてもよい。

【0019】

対向基板CTは、例えば、ガラス等の透明絶縁基板(図示せず)上に配置された赤、緑、青の着色層からなるカラーフィルタ(図示せず)、および複数の画素電極PEに対向してカラーフィルタ上に配置された対向電極(図示せず)等を有している。

【0020】

各画素電極PEおよび対向電極は、例えばITO(Indium Tin Oxide)等の透明電極材料からなるとともに、互いに平行な方向に配向処理(例えば、ラビング処理や光配向処理)される配向膜(図示せず)でそれぞれ覆われている。各画素電極PEおよび対向電極は、画素電極PEおよび対向電極からの電界に対応した液晶分子配列に制御される液晶層の一部である画素領域(図示せず)と共に表示画素PXを構成する。

【0021】

複数の色表示画素は、それぞれに配置されたカラーフィルタの着色層の色に応じて分類される。赤色表示画素PXRは赤の着色層を含む。緑色表示画素PXGは緑の着色層を含む。青色表示画素PXBは青の着色層を含む。カラーフィルタはアレイ基板ARと対向基板CTとの一方において、透明絶縁基板の液晶層側あるいは液晶層と反対側に配置される。

【0022】

複数の表示画素PXは各々画素電極PEおよび対向電極間に保持される液晶層によって構成される液晶容量(図示せず)を有する。液晶容量は、液晶材料の比誘電率、画素電極面積、液晶セルギャップによって決まる。

【0023】

XドライバXDによって信号線Sに印加された電圧(以下、ソース電圧という)は、対応する画素スイッチSWを介して選択行の表示画素PXの画素電極PEに印加される。画素電極PEに印加された電圧(画素電位)と対向電極に印加された対向電圧Vcomとの電位差が液晶容量に保持される。

【0024】

また、例えば絶縁膜を介して積層される画素電極PEの一部と補助容量線Cs(Cs(1)〜Cs(M+1))とによって、補助容量Cstが構成される。画素電極PEへの信号書き込み後の保持期間において、補助容量Cstは液晶容量に結合される。補助容量Cstは絶縁膜を介して積層されるスイッチSWのドレインと補助容量線Csとの間に形成されてもよく、絶縁膜を介して積層されるスイッチ素子SWの半導体層と補助容量線Csとの間に形成されてもよい。

【0025】

制御回路CTRは、外部信号源から入力される同期信号に基づいて発生される制御信号をYドライバYDに出力し、外部信号源から入力される同期信号に基づいて発生される制御信号、および外部信号源から入力される映像信号または黒挿入用の逆転移防止信号をXドライバXDに出力する。さらに、制御回路CTRは、対向電極に印加される対向電圧Vcomを対向基板CTの対向電極に対して出力する。

【0026】

制御回路CTRからYドライバYDに対して出力される制御信号には、上下走査(第1走査)と下上走査(第2走査)とを切り替えるための走査方向制御信号UD、容量結合カップリングによる重畳電圧の極性を制御するためのCs極性制御信号FR、およびシフトレジスタ(図2に示す)の動作を制御するためのスタートパルス信号STV、クロック信号CLK1、CLK2などが含まれる。

【0027】

XドライバXDは、並列的に複数の映像信号あるいは逆転移防止信号を信号線Sへ出力する。

【0028】

本実施形態の液晶表示装置では、CCDI駆動を採用している。CCDI駆動は信号線Sから画素に書き込みを行った後に、補助容量線からCstを介して画素電位に容量結合カップリングによる重畳電圧を与えて振幅増大効果を得るものである。CCDI駆動によれば、XドライバXDから信号線Sに与える信号電圧のレンジ(映像信号振幅)よりも大きな画素保持電圧振幅を得ることができる。これにより電圧振幅の小さなXドライバXDを用いることができ、ドライバコスト削減、および消費電力の低減というメリットが得られる。

【0029】

以下、CCDI駆動におけるゲート線Gおよび補助容量線Csの動作について、図2に示すYドライバYDの回路ブロック図、および図3に示す駆動波形のタイミングチャートを用いて説明する。

【0030】

図2は、図1に示す液晶表示装置のYドライバYDの回路ブロックの一例を示す図である。入力信号はUD、STV、CLK1、CLK2、およびFRであり、これらは高電圧状態(以下、Hと表わす)または低電圧状態(以下、Lと表わす)のいずれかの論理値をとるものとする。

【0031】

ここで、UDは上下走査と下上走査とを切り替えるための走査方向制御信号、/UDは走査方向制御信号を反転した信号、STVは後述するシフトレジスタの動作を制御するためのスタートパルス信号、CLK1およびCLK2はクロック信号、FRは容量結合カップリングによる重畳電圧の極性を制御するためのCs極性制御信号と呼ばれる。

【0032】

YドライバYDからの出力信号は、表示領域の対応するゲート線(G(1)〜G(M))に対して出力されるゲート信号(SG(1)〜SG(M))、および、表示領域の対応する補助容量線(Cs(1)〜Cs(M+1))に対して出力されるCs信号(SCs(1)〜SCs(M+1))である。

【0033】

ここでMは表示領域ACTに配置されたゲート線Gの数であるが、本図においては偶数とする。なお、表示領域ACTではゲート線Gの上下に補助容量線Csが配置される構造になっているため、補助容量線Csはゲート線Gより1本多く、総数は(M+1)本となっている。なお、図2に示す回路図上ではゲート信号SG(1)〜SG(M)およびCs信号SCs(1)〜SCs(M+1)はロジック信号として扱っているが、実際はレベルシフタ等を通して電圧変換した上で表示領域ACTへと出力されることもある。電圧変換に関しては本実施形態を説明する上では本質的な構成要素ではないので、説明は省略する。

【0034】

図2において、スイッチ記号で表わされた素子(例えばSWYで示した素子)は、矢印で示された制御端子(走査方向制御信号UDまたは反転した走査方向制御信号/UD)がHレベルのときは導通、Lレベルのときは非導通の状態をとるスイッチ素子である。

【0035】

スイッチ素子SWYは、1つのレジスタP(k)の入力側において、上側のレジスタP(k−1)の出力端との接続を切替えるスイッチ素子SWYと、下側のレジスタP(k+1)の出力端との接続を切替えるスイッチ素子SWYとが配置されている。最も上側のレジスタP(−1)の入力側には、スタートパルス信号STVの入力端との接続を切替えるスイッチ素子SWYと、下側のレジスタP(0)の出力端との接続を切替えるスイッチ素子SWYとが配置されている。最も下側のレジスタP(M+2)の入力側には上側のレジスタP(M+1)の出力端との接続を切替えるスイッチ素子SWYと、スタートパルス信号STVの入力端との接続を切替えるスイッチ素子SWYとが配置されている。

【0036】

P(k)(k=−1,0,1,2,…,M+2)はレジスタであり、矢印で示した制御端子(クロック信号CLK1あるいはクロック信号CLK2)からHレベルが入力されたときには入力側(図にて左側)の値を取り込んでメモリし、その後制御端子信号がLレベルになっても、再びHレベルになるまでは取り込まれた値を保持し続ける機能を持っている。レジスタP(k)の出力側(図にて右側)には、保持された値が常時出力される。

【0037】

以上により、例えば走査方向制御信号UDがHレベル(すなわち反転した走査方向制御信号/UDがLレベル)の場合には、スタートパルス信号STVがP(−1)、P(0)、(1)…、P(M+1)、P(M+2)の順にクロック信号CLK1、クロック信号CLK2に同期して連鎖的にメモリされ、上から下へ(第1方向へ)と走査するシフトレジスタとして機能する。

【0038】

また、走査方向制御信号UDがLレベル(すなわち反転した走査方向制御信号/UDがHレベル)の場合にはスタートパルス信号STVがP(M+2)、P(M+1)、P(M)…、P(0)、P(−1)の順にクロック信号CLK1、CLK2に同期して連鎖的にメモリされ、下から上へ(第2方向へ)と走査するシフトレジスタとして機能する。

【0039】

レジスタP(k)の出力はクロック信号CLK1またはクロック信号CLK2との論理積がとられた後にゲート信号SG(k)として表示領域ACTのゲート線G(1)〜G(M)へ出力される。但し、ゲート信号SG(−1),SG(0),SG(M+1),SG(M+2)は表示領域ACTへは出力されない。

【0040】

ここで、レジスタP(k)の出力信号と、クロック信号CLK1またはクロック信号CLK2との論理積をとるのは、クロック信号CLK1またはクロック信号CLK2を用いてパルス整形(水平期間(H)内でのゲート信号の立ち上がり/立ち下がりタイミングの調整)を行うためである。

【0041】

レジスタQ(j)(j=1,2,…,M+1)はCs信号を生成するためのレジスタであり、機能的にはP(k)と同様である。すなわち、レジスタQ(j)はG(j−2)またはG(j+1)がHレベルになるタイミングで走査方向制御信号FRを取り込み、このときの出力がCs信号SCs(j)として表示領域の補助容量線Cs(j)に出力される(j=1,2,…,M+1)。それ以外のタイミングではレジスタQ(j)の状態は変化せずに保持される。

【0042】

図3Aおよび図3Bは、本実施形態の液晶表示装置の駆動方法の一例を説明するためのタイミングチャートである。

【0043】

以上を踏まえて走査方向制御信号UDがHレベルの場合のゲート信号SGおよびCs信号SCsの動作を図3Aおよび図3Bを用いて説明する。ここで、液晶表示装置は一般に交流化駆動を行っており、1フレーム毎(あるいは2フレーム毎、3フレーム毎などの場合もある)に各画素PXの表示極性を反転させて動作させるため、2種類の極性パターンが存在する。以下の説明では、極性パターンの一方を正フレーム、他方を負フレームと呼んで区別する。

【0044】

まず正フレームにて、図示したようなスタートパルス信号STV、クロック信号CLK1、クロック信号CLK2、およびCs極性制御信号FRの信号が入力されたとする。Cs極性制御信号FRはHレベルとLレベルとが同じ期間(1水平期間(1H))となるように一定のタイミングで立ち上がりおよび立ち下がりを繰り返す。クロック信号CLK1はCs極性制御信号FRがHレベルの期間において所定期間Hレベルとなる。クロック信号CLK2はCs極性制御信号FRがLレベルの期間において所定期間Lレベルとなる。スタートパルス信号STVは、クロック信号CLK2が立ち上がるタイミングで立ち上がり、次にクロック信号CLK1が立ち上がるタイミングで立ち下がる。

【0045】

ここでレジスタP(−1)に着目すると、スタートパルス信号STVがHレベルにある期間中にクロック信号CLK2がHレベルになること(図中で示したパルスa)でレジスタP(−1)にHレベルが取り込まれる。その後クロック信号CLK2がLレベルになってもレジスタP(−1)はHレベルを保ち、再びクロック信号CLK2がHレベル(図中cで示したパルス)となってLレベルのスタートパルスが取り込まれるまでHレベルが保持される。従って、パルスaの立ち上がりからパルスcの立ち上がりまでの期間TAにおいて、レジスタP(−1)にHレベルの信号がメモリされる。レジスタP(−1)がHレベルの期間中にCLK1がHレベル(になること図中で示したパルスb)で、両者の論理積としてパルスbの形状がそのままゲート信号SG(−1)として出力される。

【0046】

次に、レジスタP(0)に着目すると、レジスタP(0)の入力側はレジスタP(−1)の出力端と接続されている。従って、レジスタP(0)の入力はレジスタP(−1)の出力(すなわちP(−1)の状態)であるから、これがHレベルである期間にクロック信号CLK1がHレベルとなること(図中のパルスb)で、レジスタP(0)にHレベルが取り込まれてHレベルとなる。

【0047】

この状態は、クロック信号CLK1の次にHレベルとなること(図中のパルスd)でLレベルが取り込まれるまで保持される。レジスタP(0)がHレベルの期間中にクロック信号CLK2がHレベルとなること(図中のパルスc)で、両者の論理積としてパルスcの形状がそのままゲート信号SG(0)として出力される。以下SG(1)、SG(2)、…についても同様に考えることができ、1水平期間(1H)毎に順次ゲート信号SGのHレベルパルスがシフトしていくことが理解できる。

【0048】

Cs信号SCsに関しては、ゲート信号SG(k)を基準として考えることができる。すなわち、ゲート信号SG(k)がHレベルになったときにレジスタQ(k−1)およびレジスタQ(k+2)においてCs極性制御信号FRが取り込まれ、それぞれCs信号SCs(k−1)およびCs信号SCs(k+2)に出力される。

【0049】

例えばゲート信号SG(2)がHレベルになっている水平期間(1H)ではCs極性制御信号FRがHレベルであるから、ゲート信号SG(2)がHレベルになるのと同じタイミングで、Cs信号SCs(1)およびCs信号SCs(4)がHレベルに遷移する。

【0050】

なおCs信号SCs(4)に関しては、ゲート信号SG(2)がHレベルになる前の状態がHレベル(実線)およびLレベル(破線)のいずれであろうと、ゲート信号SG(2)がHレベルになった時点で、Hレベルに固定されることを示している。ゲート信号SG(2)以外のゲート信号に対しても上記と同様に考えれば、各Cs信号SCsの動きが図3Aに示したとおりのものになる。

【0051】

なお各Cs信号SCsの波形に着目した場合、その上下のゲート信号が相次いでHレベルになる前に1回、後に1回Cs極性制御信号FRを取り込んでいることになる。このうち1回目のCs極性制御信号FR取り込みにおいては、上述のようにそれまでのCs信号SCsの状態にかかわりなく、HレベルまたはLレベルのうち何れか一方の状態に固定される(すなわちそれまでの状態がリセットされてCs極性制御信号FRで規定される状態に遷移する)。

【0052】

そして2回目のCs極性制御信号FR取り込みにおいて、Cs信号SCsが1回目とは逆の状態に遷移する。すなわち、1回目のCs極性制御信号FR取り込みと、2回目のCs極性制御信号FR取り込みとは水平期間(H)の奇数倍の時間差があるため、必ず逆の状態への遷移となる。この2回目のCs極性制御信号FR取り込みにおける遷移動作が、CCDI駆動の本質である画素電位への重畳電圧印加を行うことになる。

【0053】

ここでCs信号SCsがLレベルからHレベルへ遷移する場合を「正極性」、HレベルからLレベルへ遷移する場合を「負極性」と呼び、それぞれのCs信号SCsに「正極性」を示す“+”および「負極性」を示す“−”の記号を付してある。

【0054】

負フレームについては、入力信号においてCs極性制御信号FRのHレベルとLレベルとを正フレームに対して逆転させた駆動を行う。それ以外のスタートパルス信号STVやクロック信号CLK1、および、クロック信号CLK2は、正フレームと全く同じ波形である。

【0055】

この場合、ゲート信号SGは正フレームと全く同じとなり、Cs信号SCsは正フレームに対してHレベルとLレベルとが反転したものとなる。これにより、各Cs信号SCsの「正極性」と「負極性」とが逆転することになる。

【0056】

ここで、1回目のCs極性制御信号FR取り込みの作用について少し補足しておく。先にも述べたが、正フレームと負フレームとは1フレーム毎に交互に動作させる(すなわち1フレーム毎に反転させる)ケースだけでなく、2フレーム以上毎に反転させるケースもある。

【0057】

例えばOCB(Optically Compensated Bend)モードの液晶表示装置において黒挿入駆動を行う場合には、逆転移防止信号(正極性)、映像信号(正極性)、逆転移防止信号(負極性)、映像信号(負極性)、逆転移防止信号(正極性)、…の順に画素PXの表示極性が反転し、実質的に2フレーム毎に極性反転することがある。

【0058】

また、時分割3D(3次元)表示を行う場合などに、表示極性の偏りを防ぐため、左映像信号(正極性)、右映像信号(正極性)、左映像信号(負極性)、右映像信号(負極性)、左映像信号(正極性)、…の順に画素PXの表示極性が反転する場合があり、やはり2フレーム毎の極性反転が採用されることがある。

【0059】

あるいはさらに、OCBモードの液晶表示装置で時分割3D表示を行う場合には、逆転移防止信号(正極性)、左映像信号(正極性)、逆転移防止信号(正極性)、右映像信号(正極性)、逆転移防止信号(負極性)、左映像信号(負極性)、逆転移防止信号(負極性)、右映像信号(負極性)、逆転移防止信号(正極性)、…の順に画素PXの表示極性が反転する場合があり、実質的に4フレーム毎の極性反転となることがある。

【0060】

これらの場合、あるフレームに対してその前のフレームが同極性である場合と逆極性である場合とが混在する。これは例えば図3Aに示すCs信号SCsにおいて、1回目のCs極性制御信号FR取り込みの前の状態が破線で表わされる場合と実線で表される場合とが混在することを意味する。1回目のCs極性制御信号FR取り込みにおいてこの混在をリセットして何れか一方の状態に遷移させておくことで、2回目のCs極性制御信号FR取り込みによるCs信号SCsの遷移を常に正しく実施することが可能となる。

【0061】

次に、下上走査を行う場合(走査方向制御信号UDがLレベルの場合)のゲート信号SGおよびCs信号SCsの動作について図3Bを参照して説明する。この場合、ゲート線Gの走査方向は下から上となる。すなわち、図2に示すレジスタP(k)の入力側において、下側に接続されたスイッチ素子SWYが導通し、レジスタP(M+1)、レジスタP(M)…、レジスタP(0)、レジスタP(−1)の順に、クロック信号CLK1、CLK2に同期して連鎖的にスタートパルス信号STVがメモリされ、下から上へと走査するシフトレジスタとして機能する。

【0062】

レジスタP(k)の動作に連動して、レジスタQ(j)にもレジスタQ(M+1)、レジスタQ(M)…、レジスタQ(2)、レジスタQ(1)の順に、連鎖的にCs極性制御信号FRがメモリされる。

【0063】

すなわち、図3Aに示す上下走査の場合と、図3Bに示す下上走査の場合とを比較すると、走査方向制御信号UDが反転し、クロック信号CLK1とクロック信号CLK2とがそれぞれ反転している。また、上下走査におけるシフトレジスタP(k)は、下上走査におけるシフトレジスタP(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査におけるシフトレジスタQ(j)は、下上走査におけるシフトレジスタQ(j+2−k)(j=1,2,…,M+1)に対応する。

【0064】

その結果、走査方向が上下反転し、上下走査におけるゲート線G(k)は、下上走査におけるゲート線G(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査における補助容量線Cs(j)は、下上走査における補助容量線Cs(M+2−j)(j=1,2,…,M+1)に対応することになる。

【0065】

なお、図3Bでは、クロック信号CLK1とクロック信号CLK2とのタイミングが、図3Aと反転しているが、これは行毎に交互にクロック信号CLK1とクロック信号CLK2との接続パターンが入れ替わり、かつ、本実施形態ではMが偶数の場合を説明しているからである。Mが奇数の場合には、走査方向が上から下への向きのときと下から上への向きのときとでクロック信号CLK1とクロック信号CLK2とは同じ波形となる。

【0066】

図4Aおよび図4Bは、1H1V−CCDI駆動を行う液晶表示装置において上下走査を行う駆動方法の一例について説明するためのタイミングチャートである。

【0067】

上述のゲート信号SGおよびCs信号SCsの波形をもとにして、表示領域ACTにおける画素PXでの、CCDI駆動による重畳電圧の極性と、信号線Sに出力される信号(ソース出力)の極性との関係について説明する。

【0068】

まず、CCDI駆動の中で最も基本的な1H1V−CCDI駆動について、図4Aおよび図4Bを用いて説明する。1H1Vとは、画素PXの表示極性の配列が1列毎に極性反転し、かつ、1行毎に極性反転する方式、すなわち、表示極性が正極性の画素PXと負極性の画素PXとが市松状に配列する駆動方法である。

【0069】

1H1V反転の利点として、各行書き込み時に正負極性が混在することになり、例えば信号線Sから対向電極へのカップリングが正負極性で相殺されるため、横クロストークが改善できるということが挙げられる。また、ライン反転駆動やカラム反転駆動では対向電極電位がずれた場合などにラインフリッカが見えることがあるが、ドット反転では対向電極電位がずれてもラインフリッカが見えにくいというメリットもある。

【0070】

1H1V反転駆動においては、図4Aに示す正フレームにおける画素配置図で示したように、各画素PXの補助容量Cstは、紙面に向かって画素電極PEの上側、あるいは下側の補助容量線Csのいずれかに接続されるが、1列ごとに接続先の補助容量線Csが上側と下側との交互になっている。すなわち、例えば奇数番目の列(図中のODD列)に属する画素PXの補助容量Cstは画素電極PEの上側の補助容量線Csに接続され、偶数番目の列(図中のEVEN列)に属する画素PXの補助容量Cstは画素電極PEの下側の補助容量線Csに接続される。

【0071】

ここで、図4Aおよび図4Bには正フレームと負フレームとのそれぞれについて、画素配置図の右側に、各ゲート線Gと補助容量線Csに対応させて、上下走査時(走査方向制御信号UDがHレベルのとき)のゲート信号SG波形およびCs信号SCs波形、Cs極性制御信号FR波形、および各Cs信号SCsの極性を示している。図4Aに示す信号波形は、図3Aに示す上下走査時の正フレームでのゲート信号SG波形およびCs信号SCs波形、Cs極性制御信号FR波形、および各Cs信号SCsの極性と同様である。

【0072】

例えばゲート線G1の行に注目すると、ゲート信号SG1がHレベルになった次の水平期間(1H)で、上側の補助容量線Cs1のCs信号SCs1がLレベルからHレベルへ遷移し(Cs信号SCs1は「正極性」)、さらに、その次の水平期間(1H)では下側の補助容量線Cs2のCs信号SCs2がHレベルからLレベルへ遷移している(Cs信号SCs2は「負極性」)。

【0073】

これは、補助容量Cstが画素電極PEの上側の補助容量線Cs1に接続される画素PX(O1)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる正の重畳電圧が加えられ、補助容量Cstが画素電極PEの下側の補助容量線Cs2に接続される画素PX(E1)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる負の重畳電圧が加えられることを意味している。

【0074】

画素電位に正しい極性の重畳電圧を与えるためには、XドライバXDが出力する映像信号あるいは逆転移防止信号(例えば黒表示に対応した信号)等のソース出力の極性と、重畳電圧の極性とが一致している必要がある。この条件が満たされないと表示の白黒が反転する等の不具合が生じる。従って、ゲート信号SG1がHレベルになっている水平期間では、奇数(ODD)列の信号線Sへのソース出力は正極性に、偶数(EVEN)列の信号線Sへのソース出力は負極性にする必要がある。

【0075】

以下、順次ゲート線G2、G3、…の行に注目して同様の考え方を適用すれば、各行の画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。各画素PXには、このようにして決まった重畳電圧の極性を示してある。また、Cs極性制御信号FR波形の上にはこのようにして決定したソース出力の極性を示してある。各画素PXの極性は確かに、1H1V反転パターンで市松状に分布していることが確認される。

【0076】

図4Bの負フレームにおいては、正フレームと同じ画素配置図を描き、それに対応させて図3Aの負フレームと同様のゲート信号およびCs信号波形、FR信号波形、および各Cs信号の極性を記載している。

【0077】

ここでは、Cs信号SCsの極性が正フレームに対して正負逆転したものとなっている。従って、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性も正フレームに対して反転したものとなり、図4Aに示したとおりの画素極性パターンおよびソース出力極性パターンが得られる。

【0078】

図4Cおよび図4Dは、1H1V−CCDI駆動を行う液晶表示装置において下上走査を行う駆動方法の一例について説明するためのタイミングチャートである。

【0079】

次に、図4Cおよび図4Dにて下上走査の場合(走査方向制御信号UDがLレベルの場合)を説明する。なお、本実施形態ではMが800の場合について説明する。図4Cおよび図4Dでは、ゲート配線G800、G799、G798、…の順に上から並び、図4Aおよび図4Bと上下が反転した画素配置図を示している。従って、画素PXの補助容量Cst配置の接続先の補助容量線Csも上下反転する。すなわち、図4Cおよび図4Dにおける上側は図4Aおよび図4Bにおける下側に相当し、図4Cおよび図4Dにおける下側は図4Aおよび図4Bにおける上側に相当する。

【0080】

図4Aおよび図4Bでは、画素PXの奇数(ODD)列において画素電極PEの図の上側の補助容量線Csに対して補助容量Cstが接続され、画素PXの偶数(EVEN)列において画素電極PEの図の下側の補助容量線Csに対して補助容量Cstが接続されていたが、図4Cおよび図4Dでは奇数(ODD)列において画素電極PEの図の下側の補助容量線Csに対して補助容量Cstが接続され、偶数(EVEN)列において画素電極PEの図の上側の補助容量線Csに対して補助容量Cstが接続されることになる。

【0081】

これは図4Aおよび図4Bと比較して、接続先の補助容量線Csが偶数(EVEN)列と奇数(ODD)列とが上下入れ替わったことに相当する。よって、図4Aおよび図4Bのときと同じ考え方で決められる、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性も、偶数(EVEN)列と奇数(ODD)列とが入れ替わったものになり、結果的にソース出力の極性は図4Aに示す上下走査の場合に対して正負反転したものとなる。

【0082】

この場合、ゲート信号SG波形およびCs信号SCs波形に関しては、図4Aおよび図4Bにおけるゲート信号SG1、SG2、…をゲート信号SG800、SG799、…と置き換え、Cs信号SCs1、SCs2、…をCs信号SCs801、SCs800、…と置き換えたものである。

【0083】

なお上記ではMが800の場合を一例として説明したが、Mが800以外の場合でも同様であることは自明である。

【0084】

以上の図4A乃至図4Dの結果を総合すると、1H1V−CCDI駆動にて正常表示を行うために必要な条件は、上下走査と下上走査にて、Cs極性制御信号FR(各画素に与える容量結合重畳電圧の極性を決める制御信号)が同じ極性のフレームでのソース出力の極性を比較したときに、互いに逆になっていることであるといえる。すなわち、上下走査のときの正フレームと下上走査のときの正フレームとでは、ソース出力の極性が逆になっている。同様に上下走査のときの負フレームと下上走査のときの負フレームとでは、ソース出力の極性が逆になっている。

【0085】

以上より制御回路CTRは、上下走査と下上走査とにおいて、Cs極性制御信号FRが同じ極性フレームでのソース出力の極性の位相が逆になるように(言い換えれば水平期間単位での位相が異なるように)出力するものである。

【0086】

上記のように、本実施形態の液晶表示装置によれば、上下反転表示を実現するとともに表示品位の良好な液晶表示装置および液晶表示装置の駆動方法を提供することができる。

【0087】

次に、第2実施形態の液晶表示装置およびその駆動方法について、図5A乃至図5Jを参照して説明する。本実施形態の液晶表示装置では、上述の1H1V−CCDI駆動を改良した駆動方法を採用している。本実施形態では、画素PXが並ぶ列方向に関して画素極性の配列が1列毎に極性反転している点は上述の1H1V−CCDIと同様であるが、行方向に関して2行毎に極性が反転する2H1V−CCDI駆動を採用している。

【0088】

2H1V−CCDI駆動の利点は、1H1V−CCDI駆動よりもさらに低電力を実現できることである。すなわち、1H1V反転の場合は各信号線Sに供給される映像信号(あるいは逆転移防止信号)の極性が1水平期間(1H)毎に反転していたが、2H1V反転の場合は2水平期間(2H)毎の反転となるため、信号線充放電の周波数が半分になり、消費電力が低減される。

【0089】

最初に、2H1V−CCDI駆動における補助容量Cst配置について説明する。1H1V−CCDI駆動においては奇数(ODD)列と偶数(EVEN)列とで補助容量Cst配置の上下が分かれていたが、2H1V−CCDI駆動においては、画素PXの極性パターンがまず与えられたものとし、そこからあるべき補助容量Cst配置を求める。

【0090】

図5Aの上下走査時(走査方向制御信号UDがHレベルのとき)の正フレームの図に基づいて説明する。まず、図3Aの正フレームに相当する駆動が行われるものとして、図3Aと同様のゲート信号SG波形、Cs信号SCs波形、Cs極性制御信号FR波形、および各Cs信号SCsの極性を記載している。すなわち、図5Aの正フレームの波形は、図4Aに示す正フレームの波形と同一である。

【0091】

この場合、Cs信号SCs1、Cs信号SCs2、Cs信号SCs3、Cs信号SCs4、Cs信号SCs5、Cs信号SCs6、…の極性はそれぞれ正、負、正、負、正、負、…である。

【0092】

いま、図5Aの左の画素配置図にあるように、たとえば奇数(ODD)列において画素PX(O1)、PX(O2)、PX(O3)、PX(O4)、PX(O5)、…の表示極性がそれぞれ正、正、負、負、正、…で、奇数(EVEN)列において画素PX(E1)、PX(E2)、PX(E3)、PX(E4)、PX(E5)、…の表示極性がそれぞれ負、負、正、正、負、…極性というような、2H1V反転の極性パターンでCs信号からの重畳電圧を与えるものとする。

【0093】

まず、ゲート線G1の行に注目すると、画素PX(O1)に正、画素PX(E1)に負の重畳電圧を与えるのであるから、画素PX(O1)は上側の補助容量線Cs1(正極性)、画素PX(E1)は下側の補助容量線Cs2(負極性)との間に補助容量Cstを形成すればよい。

【0094】

次にゲート線G2の行に注目すると、画素PX(O2)に正、画素PX(E2)に負の重畳電圧を与えるのであるから、画素PX(O2)は下側の補助容量線Cs3(正極性)、画素PX(E2)は上側の補助容量線Cs2(負極性)との間に補助容量Cstを形成すればよい。

【0095】

次にゲート線G3の行に注目すると、画素PX(O3)に負、画素PX(E3)に正の重畳電圧を与えるのであるから、画素PX(O3)は下側の補助容量線Cs4(負極性)、画素PX(E3)は上側の補助容量線Cs3(正極性)との間に補助容量Cstを形成すればよい。

【0096】

次にゲート線G4の行に注目すると、画素PX(O4)に負、画素PX(E4)に正の重畳電圧を与えるのであるから、画素PX(O4)は上側の補助容量線Cs4(負極性)、画素PX(E4)は下側の補助容量線Cs5(正極性)との間に補助容量Cstを形成すればよい。

【0097】

次にゲート線G5の行に注目すると、画素PX(O5)に正、画素PX(E5)に負の重畳電圧を与えるのであるから、画素PX(O5)は上側の補助容量線Cs5(正極性)、画素PX(E5)は下側の補助容量線Cs6(負極性)との間に補助容量Cstを形成すればよい。

【0098】

以下、ゲート線G6の行、ゲート線G7の行、…と全く同じようにして補助容量Cst配置を決定することができる。このようにして得られた補助容量Cst配置は、画素極性パターンに対応して4行周期の繰り返しパターンになる。

【0099】

ソース出力の極性パターンも併せて、Cs極性制御信号FR波形の上に示す。これは画素PXの重畳電圧極性パターンに一致するように極性を決めればよく、図に示したように4水平期間周期のパターンとなる。

【0100】

図5Bの負フレームにおいては、上記のようにして決めた補助容量Cst配置に対して、Cs信号SCsの極性が逆になるような駆動を行うことになる。従って、画素PXの表示極性とソース出力の極性とも、正フレームに対して反転したものになる。

【0101】

図5Cおよび図5Jは、下上走査を行う場合(走査方向制御信号UDがLレベルの場合)の補助容量Cst配置図およびタイミングチャートである。

【0102】

次に、図5Cおよび図5Dにて下上走査の場合(走査方向制御信号UDがLレベルの場合)の一例について説明する。ここでは、例としてMが800の場合について説明する。基本的な考え方は1H1V−CCDI駆動の場合と同様であり、ゲート信号SGおよびCs信号SCs波形に関しては図5Aおよび図5Bに対して以下の変更を行ったものである。

【0103】

すなわち、図5Aおよび図5Bに示す上下走査の場合と、図5Cおよび図5Dに示す下上走査の場合とを比較すると、走査方向制御信号UDが反転し、クロック信号CLK1とクロック信号CLK2とがそれぞれ反転している。また、上下走査におけるシフトレジスタP(k)は、下上走査におけるシフトレジスタP(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査におけるシフトレジスタQ(j)は、下上走査におけるシフトレジスタQ(j+2−k)(j=1,2,…,M+1)に対応する。

【0104】

その結果、走査方向が上下反転し、上下走査におけるゲート線G(k)は、下上走査におけるゲート線G(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査における補助容量線Cs(j)は、下上走査における補助容量線Cs(M+2−j)(j=1,2,…,M+1)に対応することになる。

【0105】

補助容量Cst配置に関しては、2H1V−CCDI駆動では補助容量Cst配置が4行を1周期とする繰り返しパターンを持っていることに注意する必要がある。すなわち、例えばゲート線G797の行、ゲート線G798の行、ゲート線G799の行、およびゲート線G800の行の補助容量Cst配置は、それぞれゲート線G1の行、ゲート線G2の行、ゲート線G3の行、およびゲート線G4の行の補助容量Cst配置と同じになる。すなわち、行番号を4で割ったときの余り(1、2、3、および0)が同じ画素PXの行同士では補助容量Cst配置が同じである。

【0106】

なお、1H1V−CCDI駆動の図4Cおよび図4Dにて説明したのと同様に、図5Cおよび図5Dの画素配置は図面上では上下反転して描いている。1H1V−CCDI駆動の図4Aおよび図4Bのところで説明したのと同じ手順で、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。

【0107】

正フレームにおいて、例えばゲート線G800の行に注目すると、ゲート信号SG800がHレベルになった次の水平期間(1H)で、下側(図の上側)の補助容量線Cs801のCs信号SCs801がLレベルからHレベルへ遷移し(Cs信号SCs801は「正極性」)、さらに、その次の水平期間(1H)では上側(図の下側)の補助容量線Cs800のCs信号SCs800がHレベルからLレベルへ遷移している(Cs信号SCs800は「負極性」)。

【0108】

これは、補助容量Cstが画素電極PEの下側の補助容量線Cs801に接続される画素PX(E800)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる正の重畳電圧が加えられ、補助容量Cstが画素電極PEの上側の補助容量線Cs800に接続される画素PX(O800)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる負の重畳電圧が加えられることを意味している。

【0109】

従って、ゲート信号SG800がHレベルになっている水平期間(1H)では、奇数(ODD)列の信号線Sへのソース出力は負極性に、偶数(EVEN)列の信号線Sへのソース出力は正極性にする必要がある。

【0110】

以下、順次ゲート線G799、ゲート線G798…の行に注目して同様の考え方を適用すれば、各行の画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。各画素PXには、このようにして決まった重畳電圧の極性を示してある。また、Cs極性制御信号FR波形の上にこのようにして決定したソース出力の極性を示す。

【0111】

また、負フレームでは、Cs信号SCsの極性が正フレームに対して正負逆転したものとなっている。従って、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性も正フレームに対して反転したものとなる。

【0112】

2H1V−CCDI駆動においては、上述したように補助容量Cst配置が4行周期の繰り返しパターンを持っていることに起因して、表示領域ACTの行数Mを4で割ったときの余りに応じて、下上走査時の重畳電圧の極性とそれに対応して与えるべきソース出力の極性とが異なってくる。図5Cおよび図5Dの場合と同様の結果が得られるのは、Mが4の倍数の場合(pを整数としてM=4pで表される場合)に限られる。

【0113】

図5Eおよび図5Fに、M=4p+1(例えばM=801)である場合における下上駆動の際の駆動波形図、および補助容量Cst配置図を示す。ゲート信号SGおよびCs信号SCs波形に関しては図5Aおよび図5Bに対して以下の変更を行ったものである。

【0114】

すなわち、図5Aおよび図5Bにおける上下走査の場合と図5Eおよび図5Fにおける下上走査の場合とを比較すると、走査方向制御信号UDが反転し、クロック信号CLK1とクロック信号CLK2とがそれぞれ反転している。また、上下走査におけるシフトレジスタP(k)は、下上走査におけるシフトレジスタP(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査におけるシフトレジスタQ(j)は、下上走査におけるシフトレジスタQ(j+2−k)(j=1,2,…,M+1)に対応する。

【0115】

その結果、走査方向が上下反転し、上下走査におけるゲート線G(k)は、下上走査におけるゲート線G(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査における補助容量線Cs(j)は、下上走査における補助容量線Cs(M+2−j)(j=1,2,…,M+1)に対応することになる。

【0116】

補助容量Cst配置に関しては、ゲート線G801の行の補助容量Cst配置がゲート線G1行のそれと同じである。ゲート線G800の行、ゲート線G799の行、ゲート線G798の行、…、ゲート線G1の行は図5Cおよび図5Dと同じ補助容量Cst配置になる。

【0117】

なお、図5Eおよび図5Fではゲート配線G801、G800、G799、…の順に上から並び、図5Aおよび図5Bと上下が反転した画素配置図を示している。従って、画素PXの補助容量Cst配置の接続先の補助容量線Csも上下反転する。

【0118】

1H1V−CCDI駆動の図4Aおよび図4Bのところで説明したのと同じ手順で、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。

【0119】

正フレームにおいて、例えばゲート線G801の行に注目すると、ゲート信号SG801がHレベルになった次の水平期間(1H)で、下側(図の上側)の補助容量線Cs802のCs信号SCs802がLレベルからHレベルへ遷移し(Cs信号SCs802は「正極性」)、さらに、その次の水平期間(1H)では上側(図の下側)の補助容量線Cs801のCs信号SCs801がHレベルからLレベルへ遷移している(Cs信号SCs801は「負極性」)。

【0120】

これは、補助容量Cstが画素電極PEの下側の補助容量線Cs802に接続される画素PX(E801)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる正の重畳電圧が加えられ、補助容量Cstが画素電極PEの上側の補助容量線Cs801に接続される画素PX(O801)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる負の重畳電圧が加えられることを意味している。

【0121】

従って、ゲート信号SG801がHレベルになっている水平期間(1H)では、奇数(ODD)列の信号線Sへのソース出力は負極性に、偶数(EVEN)列の信号線Sへのソース出力は正極性にする必要がある。

【0122】

以下、順次ゲート線G800、ゲート線G799、…の行に注目して同様の考え方を適用すれば、各行の画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。各画素PXには、このようにして決まった重畳電圧の極性を示してある。また、Cs極性制御信号FR波形の上にこのようにして決定したソース出力の極性を示す。

【0123】

また、負フレームでは、Cs信号SCsの極性が正フレームに対して正負逆転したものとなっている。従って、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性も正フレームに対して反転したものとなる。

【0124】

図5Gおよび図5HにM=4p+2(例としてM=802)の場合における下上走査の際の駆動波形図、および画素Cst配置図を示す。ゲート信号SGおよびCs信号SCs波形に関しては図5Aおよび図5Bに対して以下の変更を行ったものである。

【0125】

すなわち、図5Aおよび図5Bにおける上下走査の場合と図5Gおよび図5Hにおける下上走査の場合とを比較すると、走査方向制御信号UDが反転し、クロック信号CLK1とクロック信号CLK2とがそれぞれ反転している。また、上下走査におけるシフトレジスタP(k)は、下上走査におけるシフトレジスタP(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査におけるシフトレジスタQ(j)は、下上走査におけるシフトレジスタQ(j+2−k)(j=1,2,…,M+1)に対応する。

【0126】

その結果、走査方向が上下反転し、上下走査におけるゲート線G(k)は、下上走査におけるゲート線G(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査における補助容量線Cs(j)は、下上走査における補助容量線Cs(M+2−j)(j=1,2,…,M+1)に対応することになる。

【0127】

補助容量Cst配置に関しては、ゲート線G802の行の補助容量Cst配置がゲート線G2行のそれと同じである。ゲート線G802の行、ゲート線G801の行、ゲート線G800の行、…、ゲート線G1の行は図5Eおよび図5Fと同じ補助容量Cst配置になる。

【0128】

なお、図5Gおよび図5Hではゲート配線G802、G801、G800、…の順に上から並び、図5Aおよび図5Bと上下が反転した画素配置図を示している。従って、画素PXの補助容量Cst配置の接続先の補助容量線Csも上下反転する。

【0129】

1H1V−CCDI駆動の図4Aおよび図4Bのところで説明したのと同じ手順で、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。

【0130】

正フレームにおいて、例えばゲート線G802の行に注目すると、ゲート信号SG802がHレベルになった次の水平期間(1H)で、下側(図の上側)の補助容量線Cs803のCs信号SCs803がLレベルからHレベルへ遷移し(Cs信号SCs803は「正極性」)、さらに、その次の水平期間(1H)では上側(図の下側)の補助容量線Cs802のCs信号SCs802がHレベルからLレベルへ遷移している(Cs信号SCs802は「負極性」)。

【0131】

これは、補助容量Cstが画素電極PEの下側の補助容量線Cs803に接続される画素PX(O802)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる正の重畳電圧が加えられ、補助容量Cstが画素電極PEの上側の補助容量線Cs802に接続される画素PX(E802)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる負の重畳電圧が加えられることを意味している。

【0132】

従って、ゲート信号SG802がHレベルになっている水平期間(1H)では、奇数(ODD)列の信号線Sへのソース出力は正極性に、偶数(EVEN)列の信号線Sへのソース出力は負極性にする必要がある。

【0133】

以下、順次ゲート線G801、ゲート線G800、…の行に注目して同様の考え方を適用すれば、各行の画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。各画素PXには、このようにして決まった重畳電圧の極性を示してある。また、Cs極性制御信号FR波形の上にこのようにして決定したソース出力の極性を示す。

【0134】

また、負フレームでは、Cs信号SCsの極性が正フレームに対して正負逆転したものとなっている。従って、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性も正フレームに対して反転したものとなる。

【0135】

図5Iおよび図5Jに、M=4p+3(例としてM=803)の場合における下上駆動の際の駆動波形図、および画素Cst配置図を示す。ゲート信号SGおよびCs信号SCs波形に関しては図5Aおよび図5Bに対して以下の変更を行ったものである。

【0136】

すなわち、図5Aおよび図5Bにおける上下走査の場合と図5Iおよび図5Jにおける下上走査の場合とを比較すると、走査方向制御信号UDが反転し、クロック信号CLK1とクロック信号CLK2とがそれぞれ反転している。また、上下走査におけるシフトレジスタP(k)は、下上走査におけるシフトレジスタP(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査におけるシフトレジスタQ(j)は、下上走査におけるシフトレジスタQ(j+2−k)(j=1,2,…,M+1)に対応する。

【0137】

その結果、走査方向が上下反転し、上下走査におけるゲート線G(k)は、下上走査におけるゲート線G(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査における補助容量線Cs(j)は、下上走査における補助容量線Cs(M+2−j)(j=1,2,…,M+1)に対応することになる。

【0138】

補助容量Cst配置に関しては、ゲート線G803の行の補助容量Cst配置がゲート線G3行のそれと同じである。ゲート線G803の行、ゲート線G802の行、ゲート線G801の行、…、ゲート線G1の行は当然ながら図5Dと同じ補助容量Cst配置になる。

【0139】

なお、図5Iおよび図5Jではゲート配線G802、G801、G800、…の順に上から並び、図5Aおよび図5Bと上下が反転した画素配置図を示している。従って、画素PXの補助容量Cst配置の接続先の補助容量線Csも上下反転する。

【0140】

1H1V−CCDI駆動の図4Aおよび図4Bのところで説明したのと同じ手順で、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。

【0141】

正フレームにおいて、例えばゲート線G803の行に注目すると、ゲート信号SG803がHレベルになった次の水平期間(1H)で、下側(図の上側)の補助容量線Cs804のCs信号SCs804がLレベルからHレベルへ遷移し(Cs信号SCs804は「正極性」)、さらに、その次の水平期間(1H)では上側(図の下側)の補助容量線Cs803のCs信号SCs803がHレベルからLレベルへ遷移している(Cs信号SCs803は「負極性」)。

【0142】

これは、補助容量Cstが画素電極PEの下側の補助容量線Cs804に接続される画素PX(O803)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる正の重畳電圧が加えられ、補助容量Cstが画素電極PEの上側の補助容量線Cs803に接続される画素PX(E803)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる負の重畳電圧が加えられることを意味している。

【0143】

従って、ゲート信号SG802がHレベルになっている水平期間(1H)では、奇数(ODD)列の信号線Sへのソース出力は正極性に、偶数(EVEN)列の信号線Sへのソース出力は負極性にする必要がある。

【0144】

以下、順次ゲート線G801、ゲート線G800、…の行に注目して同様の考え方を適用すれば、各行の画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。各画素PXには、このようにして決まった重畳電圧の極性を示してある。また、Cs極性制御信号FR波形の上にこのようにして決定したソース出力の極性を示す。

【0145】

また、負フレームでは、Cs信号SCsの極性が正フレームに対して正負逆転したものとなっている。従って、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性も正フレームに対して反転したものとなる。

【0146】

以上の図5A乃至図5Jの結果を総合すると、2H1V−CCDI駆動にて表示品位の良好な表示を行うために必要な条件は下記である。

【0147】

上下走査と下上走査との、Cs極性制御信号FR(各画素に与える容量結合重畳電圧の極性を決める制御信号)が同じフレーム(正フレーム同士あるいは負フレーム同士)でのソース出力の極性を比較したときに、

(1) M=4pの場合:下上走査では上下走査に比べて位相が2H早い(或いは2H遅い)こと

(2) M=4p+1の場合:下上走査では上下走査に比べて位相が3H早い(或いは1H遅い)こと

(3) M=4p+2の場合:下上走査では上下走査に比べて位相が同じであること

(4) M=4p+3の場合:下上走査では上下走査に比べて位相が1H早い(或いは3H遅い)こと

になる(ここでHは水平期間の意である)。

【0148】

上記(3)(M=4p+2)の場合以外においては上下走査と下上走査で位相を異ならせる必要がある。従って制御回路CTRは、上下走査と下上走査との切替えの際に、Cs極性制御信号FRが同じフレームでのソース出力の極性のH単位での位相を、上記(1)、(2)、(4)の規則に対応させて、異なるように出力するものである。

【0149】

上記のように、本実施形態の液晶表示装置によれば、上下反転表示を実現するとともに表示品位の良好な液晶表示装置および液晶表示装置の駆動方法を提供することができる。

【0150】

また制御回路CTRは、上下走査と下上走査とにおいて、Cs極性制御信号FRが同じフレームでのソース出力の極性の位相関係を、2種類以上に設定可能で、その中から一つを選択できるものであることが望ましい。

【0151】

こうすると、上記(1)〜(4)のうちの特定の1つのケースだけでなく、複数のケースに対応できるようになるため、制御回路CTRとしての汎用性が高くなる。表示領域ACTの行数が異なる複数の機種に対して制御回路CTRを共用化できるため、制御回路CTRを含めた表示装置の開発コストや製造コストが低減されるというメリットが得られる。

【0152】

なお、液晶表示装置の行数は偶数であることが多い。従って、制御回路CTRはソース出力の極性を少なくとも上記(1)と(3)との2種類の位相関係に設定可能であれば、汎用性としては十分に高いといえる。

【0153】

例えば携帯電話やスマートフォンなどの液晶表示装置を搭載した電子機器においては、画面解像度が480(列)×800(行)(800行はM=4pに相当)または480(列)×854(行)(854行はM=4p+2に相当)が主流であり、これらの両者に共通の制御回路CTRを用いられることのメリットは大きい。

【0154】

以上、図5A乃至図5Jを参照して2H1V−CCDI駆動について述べてきたが、同様の考え方はnH1V−CCDI駆動(nは3以上の整数)に対しても適用可能である。

【0155】

映像信号の極性反転をn水平期間毎にすることで、信号線充放電の消費電力を1/nに比例して低減できるというメリットが得られる。ただし、あまりnが大きすぎるとn行ピッチの横帯やラインフリッカが目立ちやすくなるというデメリットも顕在化してくるため、実際の表示装置においては画質や消費電力の要求仕様を鑑みて最適なnの値を選択すればよい。

【0156】

これらの場合も2H1V−CCDI駆動と同様の考え方を適用すれば、表示領域の行数に応じて、上下走査と下上走査で、ソース出力の極性の位相を異ならせる必要があると結論される(因みに補助容量Cst配置の繰返し周期は、nが偶数の場合2n行周期、nが奇数の場合n行周期となる)。従って制御回路CTRは2H1V−CCDI駆動の場合と同様の特徴を持った構成であることが望ましい。

【0157】

次に、第3実施形態の液晶表示装置および液晶表示装置の駆動方法について図面を参照して以下に説明する。

【0158】

nをさらに大きくしてnを画素PXの全行数に一致させると、1列内の全画素の極性が同一になり、CCカラム反転方式に帰着する。CCカラム反転方式も、広い意味でCCDI駆動に含まれるものとみなすことができる。

【0159】

CCカラム反転方式は電力も小さく、横帯やラインフリッカも発生しないという長所があるが、一方で縦クロストークが発生しやすいという課題もある。これらの長所および課題点を勘案の上で、CCカラム反転方式を採用することも可能である。CCカラム反転方式でも、これまでの説明と全く同様の考え方が適用可能である。

【0160】

図6A乃至図6Fは、CCカラム反転方式を採用した液晶表示装置について補助容量Cst配置および駆動波形を示す。これは図5A乃至図5Dでの説明と全く同じ考え方を適用して描いたものである。図6Aおよび図6Bは上下走査時(走査方向制御信号UDがHレベルのとき)に対応するものであり、図3Aに示すゲート信号SGおよびCs信号SCs波形と、カラム反転の画素極性パターン(例えば正フレームにおいて奇数(ODD)列が正、偶数(EVEN)列が負)から、あるべき補助容量Cst配置パターンを求めている。

【0161】

図6Aの上下走査時(走査方向制御信号UDがHレベルのとき)の正フレームの図に基づいて説明する。まず、図3Aの正フレームに相当する駆動が行われるものとして、図3Aと同様のゲート信号SG波形、Cs信号SCs波形、Cs極性制御信号FR波形、および各Cs信号SCsの極性を記載している。すなわち、図6Aの正フレームの波形は、図4Aに示す正フレームの波形と同一である。

【0162】

この場合、Cs信号SCs1、Cs信号SCs2、Cs信号SCs3、Cs信号SCs4、Cs信号SCs5、Cs信号SCs6、…の極性はそれぞれ正、負、正、負、正、負、…である。

【0163】

いま、図6Aの左の画素配置図にあるように、たとえば奇数(ODD)列において画素PX(O1)、PX(O2)、PX(O3)、PX(O4)、PX(O5)、…の表示極性が正極性で、奇数(EVEN)列において画素PX(E1)、PX(E2)、PX(E3)、PX(E4)、PX(E5)、…の表示極性が負極性というような極性パターンでCs信号SCsからの重畳電圧を与えるものとする。

【0164】

まず、ゲート線G1の行に注目すると、画素PX(O1)に正、画素PX(E1)に負の重畳電圧を与えるのであるから、画素PX(O1)は上側の補助容量線Cs1(正極性)、画素PX(E1)は下側の補助容量線Cs2(負極性)との間に補助容量Cstを形成すればよい。

【0165】

次にゲート線G2の行に注目すると、画素PX(O2)に正、画素PX(E2)に負の重畳電圧を与えるのであるから、画素PX(O2)は下側の補助容量線Cs3(正極性)、画素PX(E2)は上側の補助容量線Cs2(負極性)との間に補助容量Cstを形成すればよい。

【0166】

次にゲート線G3の行に注目すると、画素PX(O3)に負、画素PX(E3)に正の重畳電圧を与えるのであるから、画素PX(O3)は上側の補助容量線Cs4(負極性)、画素PX(E3)は下側の補助容量線Cs3(正極性)との間に補助容量Cstを形成すればよい。

【0167】

次にゲート線G4の行に注目すると、画素PX(O4)に負、画素PX(E4)に正の重畳電圧を与えるのであるから、画素PX(O4)は下側の補助容量線Cs4(負極性)、画素PX(E4)は上側の補助容量線Cs5(正極性)との間に補助容量Cstを形成すればよい。

【0168】

以下、ゲート線G5の行、ゲート線G6の行、…と全く同じようにして補助容量Cst配置を決定することができる。このようにして得られた補助容量Cst配置は、列方向において2行周期の繰り返しパターンになる(ソース出力極性がH単位の周期を持たないので、補助容量線の極性反転周期(2行)が補助容量Cst配置の周期に反映される)。同じ行に配置された奇数(ODD)列と偶数(EVEN)列との画素PXの補助容量Cstは互いに異なる補助容量線Csに接続され、同じ列に配置された奇数行と偶数行との画素PXの補助容量Cstは、異なる側の補助容量線Csに接続されている。正極性の補助容量線Csと負極性の補助容量線Csとが行方向に交互に配置されることになる。

【0169】

図6Aおよび図6Bに示す場合、ソース出力の極性は正フレームにおいて奇数(ODD)列の信号線Sが負極性となり、偶数(EVEV)列の信号線Sが負極性となる。ソース出力の極性は負フレームにおいて奇数(ODD)列の信号線Sが正極性となり、偶数(EVEN)列の信号線Sが正極性となる。

【0170】

図6C乃至図6Fは、下上走査(走査方向制御信号UDがLレベルのとき)に対応する図である。補助容量Cst配置が2行周期の繰り返しパターンを持っていることを考慮して、図6Cおよび図6DにはMが偶数の場合(pを整数としてM=2pの場合)を示し、図6Eおよび図6FにはMが奇数の場合(pを整数としてM=2p+1の場合)を示している。なお、図6C乃至図6Fは上下反転して記載されている。

【0171】

図5Cおよび図5Dと同様の考え方を適用することで、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。

【0172】

図6Cに示す正フレームにおいて、例えばゲート線G800の行に注目すると、ゲート信号SG800がHレベルになった次の水平期間(1H)で、下側(図の上側)の補助容量線Cs801のCs信号SCs801がLレベルからHレベルへ遷移し(Cs信号SCs801は「正極性」)、さらに、その次の水平期間(1H)では上側(図の下側)の補助容量線Cs800のCs信号SCs800がHレベルからLレベルへ遷移している(Cs信号SCs800は「負極性」)。

【0173】

これは、補助容量Cstが画素電極PEの下側の補助容量線Cs801に接続される画素PX(O800)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる正の重畳電圧が加えられ、補助容量Cstが画素電極PEの上側の補助容量線Cs800に接続される画素PX(E800)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる負の重畳電圧が加えられることを意味している。

【0174】

従って、ゲート信号SG800がHレベルになっている水平期間(1H)では、奇数(ODD)列の信号線Sへのソース出力は正極性に、偶数(EVEN)列の信号線Sへのソース出力は負極性にする必要がある。

【0175】

以下、順次ゲート線G799、ゲート線G798、…の行に注目して同様の考え方を適用すれば、各行の画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。各画素PXには、このようにして決まった重畳電圧の極性を示してある。また、Cs極性制御信号FR波形の上にこのようにして決定したソース出力の極性を示す。

【0176】

また、図6Dに示す負フレームでは、Cs信号SCsの極性が正フレームに対して正負逆転したものとなっている。従って、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性も正フレームに対して反転したものとなる。

【0177】

図6Eに示す正フレームにおいて、例えばゲート線G801の行に注目すると、ゲート信号SG801がHレベルになった次の水平期間(1H)で、下側(図の上側)の補助容量線Cs802のCs信号SCs802がLレベルからHレベルへ遷移し(Cs信号SCs802は「正極性」)、さらに、その次の水平期間(1H)では上側(図の下側)の補助容量線Cs801のCs信号SCs801がHレベルからLレベルへ遷移している(Cs信号SCs801は「負極性」)。

【0178】

これは、補助容量Cstが画素電極PEの下側の補助容量線Cs802に接続される画素PX(E801)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる正の重畳電圧が加えられ、補助容量Cstが画素電極PEの上側の補助容量線Cs801に接続される画素PX(O801)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる負の重畳電圧が加えられることを意味している。

【0179】

従って、ゲート信号SG801がHレベルになっている水平期間(1H)では、奇数(ODD)列の信号線Sへのソース出力は正極性に、偶数(EVEN)列の信号線Sへのソース出力は負極性にする必要がある。

【0180】

以下、順次ゲート線G800、ゲート線G799、…の行に注目して同様の考え方を適用すれば、各行の画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。各画素PXには、このようにして決まった重畳電圧の極性を示してある。また、Cs極性制御信号FR波形の上にこのようにして決定したソース出力の極性を示す。

【0181】

また、負フレームでは、Cs信号SCsの極性が正フレームに対して正負逆転したものとなっている。従って、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性も正フレームに対して反転したものとなる。

【0182】

以上の図6A乃至図6Fの結果を総合すると、CCカラム反転駆動にて正常表示を行うために必要な条件は、「上下走査と下上走査にて、Cs極性制御信号FR(各画素に与える容量結合重畳電圧の極性を決める制御信号)が同じフレームでのソース出力の極性を比較したときに、

(5) M=2pの場合:下上走査では上下走査に比べて位相が同じであること

(6) M=2p+1の場合:下上走査では上下走査に比べて位相が反転していること

となる。

【0183】

上記(6)の場合においては上下走査と下上走査で位相を異ならせる必要がある。従って制御回路は、上下走査と下上走査において、FRが同じフレームでのソース出力の極性のH単位での位相を、異なるように出力するものであることが望ましい。

【0184】

また制御回路は、上下走査と下上走査において、FRが同じフレームでのソース出力の極性の位相関係を、(5)と(6)との2種類に設定可能で、その中から一つを選択できるものであることが望ましい。こうすると、(5)および(6)のうちの特定の1つのケースだけでなく、両方のケースに対応できるようになるため、制御回路としての汎用性が高くなる。表示領域の行数が異なる複数の機種に対して制御回路を共用化できるため、制御回路を含めた表示装置の開発コストや製造コストが低減されるというメリットが得られる。

【0185】

なお、第2実施形態における(3)M=4p+2の場合、あるいは第3実施形態における(1)M=2pの場合などは、正常表示を行うために必要な条件が、下上走査と上下走査にて、Cs極性制御信号FRが同じフレームでのソース出力の極性の位相が同じであることとなる。これらの共通点は、補助容量Cst配置が表示領域ACT内で上下反転に関して対称であること、すなわちより具体的にはk=1,2,…,M−1,Mに対して行kと行(M+1−k)とで補助容量Cst配置が上下逆であることである。

【0186】

表示領域ACTの補助容量Cst配置にこのような特徴を持たせておく場合に限り、制御回路CTRは、上下走査と下上走査において、Cs極性制御信号FRが同じフレームでのソース出力の極性のH単位での位相が同じになるように出力することで、正常表示が行える。

【0187】

なお第1実施形態乃至第3実施形態において、奇数(ODD)列と偶数(EVEN)列とで極性が反転する場合(1V反転)の例を説明したが、2列周期で反転する場合(nH2V−CCDI駆動)、3列周期で反転する場合(nH3V−CCDI駆動)等であっても適用可能である。

【0188】

なお上記実施形態では高速応答が可能なOCBモードの液晶表示装置について説明したが、他のモード(IPS、TN、FFS、VAなど)の液晶表示装置であっても適用可能である。

【0189】

本実施形態によれば、低消費電力を実現でき、かつ、上下反転表示を実現するとともに表示品位の良好な液晶表示装置および液晶表示装置の駆動方法を提供することができる。

【0190】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0191】

PX…画素、ACT…表示領域、CTR…制御回路、AR…アレイ基板、CT…対向基板、PE…画素電極、G…ゲート線、S…信号線、YD…Yドライバ、XD…Xドライバ、Cs…補助容量線、Cst…補助容量、H…水平期間、UD…走査方向制御信号、FR…Cs極性制御信号。

【技術分野】

【0001】

本発明の実施形態は、液晶表示装置および液晶表示装置の駆動方法に関する。

【背景技術】

【0002】

液晶表示装置は、一対の基板と、この一対の基板間に挟持された液晶層と、複数の表示画素からなる表示領域とを備えている。

【0003】

液晶表示装置では交番電界駆動を実施しており、フリッカ対策のため1又は複数の走査ライン毎に液晶印加電圧の極性を反転させている。走査線毎の極性反転、または、信号線毎の極性反転のいずれか一方だけでは、走査線が延びる方向または信号線が延びる方向に沿ってフリッカが見えることがあり、高画質液晶表示装置では、走査線毎と信号線毎との両方で極性反転するドット反転駆動を採用することがある。

【0004】

一方、信号電圧振幅を低減する方法として、容量結合駆動(CC(capacitively-coupled)駆動)が提案されている。容量結合駆動では、補助容量を通して、補助容量信号を画素電極に重畳することで所定の電圧に到達させる。容量結合駆動を採用すると、補助容量と画素容量とを略等しくする場合、信号電圧振幅を概略半減できる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2010−271484号公報

【特許文献2】特開平9−190163号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

携帯電話やスマートフォン等の電子機器に搭載される液晶表示装置の仕様として、画面表示が上下反転表示に対応していることが要求されている。そのため液晶表示装置は、少なくとも、走査方向が上から下へ進む方向の走査(上下走査)と、下から上へ進む方向の走査(下上走査)とのいずれであっても正常に表示できることが要求される。

【0007】

なお、以下の説明において、液晶表示装置使用時の置き方(縦置き又は横置き)とは関係なく、信号線の延びる方向を上下方向とし、一方側を「上」、その反対側を「下」として説明する。

【0008】

本実施形態は、上下反転表示を実現するとともに表示品位の良好な液晶表示装置および液晶表示装置の駆動方法を提供することを目的とする。

【課題を解決するための手段】

【0009】

実施形態によれば、マトリクス状に配置された画素電極と、前記画素電極が配列した行に沿って延びたゲート線と、前記画素電極が配列した列に沿って延びた信号線と、前記ゲート線と略平行に延びた補助容量線と、前記ゲート線、前記信号線、および、前記補助容量線を駆動する駆動回路と、を備えたアレイ基板と、前記アレイ基板と対向して配置された対向基板と、前記アレイ基板と前記対向基板との間に挟持された液晶層と、前記信号線が延びる方向と略平行な方向に並ぶ前記ゲート線を第1方向に順次駆動する第1走査と、前記第1方向と逆方向の第2方向に前記ゲート線を順次駆動する第2走査とを切替える走査方向制御信号と、前記補助容量線に供給する信号の極性を制御する極性制御信号と、を供給し、前記駆動回路の動作を制御する制御回路と、を備え、前記制御回路は、前記第1走査を行う場合と前記第2走査を行う場合との前記極性制御信号が同じであるフレーム期間において、前記信号線へ供給する信号の極性を水平期間単位で位相が異なるように前記駆動回路を制御可能である液晶表示装置が提供される。

【図面の簡単な説明】

【0010】

【図1】図1は、一実施形態に係る液晶表示装置の一構成例を概略的に示す図である。

【図2】図2は、図1に示す液晶表示装置のYドライバの回路ブロックの一例を示す図である。

【図3A】図3Aは、一実施形態の液晶表示装置において上下走査を行う際の駆動方法の一例を説明するためのタイミングチャートである。

【図3B】図3Bは、一実施形態の液晶表示装置において下上走査を行う際の駆動方法の一例を説明するためのタイミングチャートである。

【図4A】図4Aは、1H1V−CCDI駆動を行う液晶表示装置において上下走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図4B】図4Bは、1H1V−CCDI駆動を行う液晶表示装置において上下走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図4C】図4Cは、1H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図4D】図4Dは、1H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5A】図5Aは、2H1V−CCDI駆動を行う液晶表示装置において上下走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5B】図5Bは、2H1V−CCDI駆動を行う液晶表示装置において上下走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5C】図5Cは、2H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5D】図5Dは、2H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5E】図5Eは、2H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5F】図5Fは、2H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5G】図5Gは、2H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5H】図5Hは、2H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5I】図5Iは、2H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図5J】図5Jは、2H1V−CCDI駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図6A】図6Aは、CCカラム反転駆動を行う液晶表示装置において上下走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図6B】図6Bは、CCカラム反転駆動を行う液晶表示装置において上下走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図6C】図6Cは、CCカラム反転駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図6D】図6Dは、CCカラム反転駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図6E】図6Eは、CCカラム反転駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【図6F】図6Fは、CCカラム反転駆動を行う液晶表示装置において下上走査を行う際の駆動方法の一例について説明するためのタイミングチャートである。

【発明を実施するための形態】

【0011】

以下、一実施形態に係る液晶表示装置について、図面を参照して詳細に説明する。

図1は、一実施形態に係る液晶表示装置の一構成例を概略的に示す図である。図1に示すように、本実施形態に係る液晶表示装置は複数の表示画素PXからなる表示領域ACTを備えた液晶表示パネルLPNと、液晶表示パネルの表示領域ACTを照明するように配置されたバックライトBLTと、液晶表示パネルLPNとバックライトBLTとを制御する制御回路CTRと、を備えている。

【0012】

液晶表示パネルLPNは一対の基板、すなわち、アレイ基板ARおよび対向基板CTと、アレイ基板ARおよび対向基板CT間に挟持された液晶層(図示せず)と、を有している。本実施形態に係る液晶表示装置では、画素配列として正方配列を採用している。複数の表示画素PXはマトリクス状に配置されている。

【0013】

本実施形態に係る液晶表示装置はカラー表示タイプの液晶表示装置であって、複数の表示画素PXは、複数の色表示画素を含んでいる。図1に示す液晶表示装置は、赤色を表示する赤色表示画素PXR、緑色を表示する緑色表示画素PXG、および、青色を表示する青色表示画素PXBを含む。

【0014】

アレイ基板ARは、例えばガラス等の透明絶縁基板(図示せず)を有している。この透明絶縁基板上には、各表示画素PXに対応する複数の画素電極PEが配置されている。さらに、アレイ基板ARは、複数の画素電極PEが配列する行に沿って第1方向D1に延びた複数のゲート線G(G(1)〜G(M))、複数の画素電極PEが配列する列に沿って第2方向D2に延びた複数の信号線S(S(1)〜S(N))、ゲート線Gと略平行に延びる補助容量線Cs(Cs(1)〜Cs(M+1))および、これらゲート線Gおよび信号線Sの交差位置近傍に配置された複数の画素スイッチSWを有している。

【0015】

各画素スイッチSWは、例えば、スイッチング素子として薄膜トランジスタ(TFT)を含む。画素スイッチSWのゲートがゲート線Gと電気的に接続され(あるいは一体に形成され)、ソースが信号線Sと電気的に接続され(あるいは一体に形成され)、ドレインが画素電極PEと電気的に接続され(あるいは一体に形成され)ている。各画素スイッチSWは、各々対応ゲート線Gを介して駆動されたときに対応信号線Sおよび対応画素電極PE間で導通する。

【0016】

液晶表示パネルLPNは、駆動回路として、さらに複数の画素スイッチSWを行単位に導通させるように複数のゲート線G(1)〜G(M)を順次駆動するとともに、複数の補助容量線Cs(1)〜Cs(M+1)を駆動するYドライバYD、および、各行の画素スイッチSWが対応ゲート線Gの駆動によって導通する期間において映像信号あるいは逆転移防止信号を複数の信号線S(1)〜S(N)にそれぞれ出力するXドライバXDを備えている。

【0017】

YドライバYDおよびXドライバXDは、外付けのICとして搭載してもよく、アレイ基板AR上に内蔵回路として造りこんでもよい。本実施形態に係る液晶表示装置では、YドライバYDおよびXドライバXDは表示領域ACTの周囲に配置され、制御回路CTRによりその動作を制御される。

【0018】

なお図1ではYドライバYDが表示領域ACTの左側に配置されているが、場合によっては右側に配置されてもよい。あるいは同一の機能をもつ2つのYドライバYDが左右両側に対称な形で配置されてもよい。あるいは、YドライバYDを、ゲート線Gを駆動する機能と補助容量線Csを駆動する機能とに分離してそれぞれ左右に分けて配置されてもよい。

【0019】

対向基板CTは、例えば、ガラス等の透明絶縁基板(図示せず)上に配置された赤、緑、青の着色層からなるカラーフィルタ(図示せず)、および複数の画素電極PEに対向してカラーフィルタ上に配置された対向電極(図示せず)等を有している。

【0020】

各画素電極PEおよび対向電極は、例えばITO(Indium Tin Oxide)等の透明電極材料からなるとともに、互いに平行な方向に配向処理(例えば、ラビング処理や光配向処理)される配向膜(図示せず)でそれぞれ覆われている。各画素電極PEおよび対向電極は、画素電極PEおよび対向電極からの電界に対応した液晶分子配列に制御される液晶層の一部である画素領域(図示せず)と共に表示画素PXを構成する。

【0021】

複数の色表示画素は、それぞれに配置されたカラーフィルタの着色層の色に応じて分類される。赤色表示画素PXRは赤の着色層を含む。緑色表示画素PXGは緑の着色層を含む。青色表示画素PXBは青の着色層を含む。カラーフィルタはアレイ基板ARと対向基板CTとの一方において、透明絶縁基板の液晶層側あるいは液晶層と反対側に配置される。

【0022】

複数の表示画素PXは各々画素電極PEおよび対向電極間に保持される液晶層によって構成される液晶容量(図示せず)を有する。液晶容量は、液晶材料の比誘電率、画素電極面積、液晶セルギャップによって決まる。

【0023】

XドライバXDによって信号線Sに印加された電圧(以下、ソース電圧という)は、対応する画素スイッチSWを介して選択行の表示画素PXの画素電極PEに印加される。画素電極PEに印加された電圧(画素電位)と対向電極に印加された対向電圧Vcomとの電位差が液晶容量に保持される。

【0024】

また、例えば絶縁膜を介して積層される画素電極PEの一部と補助容量線Cs(Cs(1)〜Cs(M+1))とによって、補助容量Cstが構成される。画素電極PEへの信号書き込み後の保持期間において、補助容量Cstは液晶容量に結合される。補助容量Cstは絶縁膜を介して積層されるスイッチSWのドレインと補助容量線Csとの間に形成されてもよく、絶縁膜を介して積層されるスイッチ素子SWの半導体層と補助容量線Csとの間に形成されてもよい。

【0025】

制御回路CTRは、外部信号源から入力される同期信号に基づいて発生される制御信号をYドライバYDに出力し、外部信号源から入力される同期信号に基づいて発生される制御信号、および外部信号源から入力される映像信号または黒挿入用の逆転移防止信号をXドライバXDに出力する。さらに、制御回路CTRは、対向電極に印加される対向電圧Vcomを対向基板CTの対向電極に対して出力する。

【0026】

制御回路CTRからYドライバYDに対して出力される制御信号には、上下走査(第1走査)と下上走査(第2走査)とを切り替えるための走査方向制御信号UD、容量結合カップリングによる重畳電圧の極性を制御するためのCs極性制御信号FR、およびシフトレジスタ(図2に示す)の動作を制御するためのスタートパルス信号STV、クロック信号CLK1、CLK2などが含まれる。

【0027】

XドライバXDは、並列的に複数の映像信号あるいは逆転移防止信号を信号線Sへ出力する。

【0028】

本実施形態の液晶表示装置では、CCDI駆動を採用している。CCDI駆動は信号線Sから画素に書き込みを行った後に、補助容量線からCstを介して画素電位に容量結合カップリングによる重畳電圧を与えて振幅増大効果を得るものである。CCDI駆動によれば、XドライバXDから信号線Sに与える信号電圧のレンジ(映像信号振幅)よりも大きな画素保持電圧振幅を得ることができる。これにより電圧振幅の小さなXドライバXDを用いることができ、ドライバコスト削減、および消費電力の低減というメリットが得られる。

【0029】

以下、CCDI駆動におけるゲート線Gおよび補助容量線Csの動作について、図2に示すYドライバYDの回路ブロック図、および図3に示す駆動波形のタイミングチャートを用いて説明する。

【0030】

図2は、図1に示す液晶表示装置のYドライバYDの回路ブロックの一例を示す図である。入力信号はUD、STV、CLK1、CLK2、およびFRであり、これらは高電圧状態(以下、Hと表わす)または低電圧状態(以下、Lと表わす)のいずれかの論理値をとるものとする。

【0031】

ここで、UDは上下走査と下上走査とを切り替えるための走査方向制御信号、/UDは走査方向制御信号を反転した信号、STVは後述するシフトレジスタの動作を制御するためのスタートパルス信号、CLK1およびCLK2はクロック信号、FRは容量結合カップリングによる重畳電圧の極性を制御するためのCs極性制御信号と呼ばれる。

【0032】

YドライバYDからの出力信号は、表示領域の対応するゲート線(G(1)〜G(M))に対して出力されるゲート信号(SG(1)〜SG(M))、および、表示領域の対応する補助容量線(Cs(1)〜Cs(M+1))に対して出力されるCs信号(SCs(1)〜SCs(M+1))である。

【0033】

ここでMは表示領域ACTに配置されたゲート線Gの数であるが、本図においては偶数とする。なお、表示領域ACTではゲート線Gの上下に補助容量線Csが配置される構造になっているため、補助容量線Csはゲート線Gより1本多く、総数は(M+1)本となっている。なお、図2に示す回路図上ではゲート信号SG(1)〜SG(M)およびCs信号SCs(1)〜SCs(M+1)はロジック信号として扱っているが、実際はレベルシフタ等を通して電圧変換した上で表示領域ACTへと出力されることもある。電圧変換に関しては本実施形態を説明する上では本質的な構成要素ではないので、説明は省略する。

【0034】

図2において、スイッチ記号で表わされた素子(例えばSWYで示した素子)は、矢印で示された制御端子(走査方向制御信号UDまたは反転した走査方向制御信号/UD)がHレベルのときは導通、Lレベルのときは非導通の状態をとるスイッチ素子である。

【0035】

スイッチ素子SWYは、1つのレジスタP(k)の入力側において、上側のレジスタP(k−1)の出力端との接続を切替えるスイッチ素子SWYと、下側のレジスタP(k+1)の出力端との接続を切替えるスイッチ素子SWYとが配置されている。最も上側のレジスタP(−1)の入力側には、スタートパルス信号STVの入力端との接続を切替えるスイッチ素子SWYと、下側のレジスタP(0)の出力端との接続を切替えるスイッチ素子SWYとが配置されている。最も下側のレジスタP(M+2)の入力側には上側のレジスタP(M+1)の出力端との接続を切替えるスイッチ素子SWYと、スタートパルス信号STVの入力端との接続を切替えるスイッチ素子SWYとが配置されている。

【0036】

P(k)(k=−1,0,1,2,…,M+2)はレジスタであり、矢印で示した制御端子(クロック信号CLK1あるいはクロック信号CLK2)からHレベルが入力されたときには入力側(図にて左側)の値を取り込んでメモリし、その後制御端子信号がLレベルになっても、再びHレベルになるまでは取り込まれた値を保持し続ける機能を持っている。レジスタP(k)の出力側(図にて右側)には、保持された値が常時出力される。

【0037】

以上により、例えば走査方向制御信号UDがHレベル(すなわち反転した走査方向制御信号/UDがLレベル)の場合には、スタートパルス信号STVがP(−1)、P(0)、(1)…、P(M+1)、P(M+2)の順にクロック信号CLK1、クロック信号CLK2に同期して連鎖的にメモリされ、上から下へ(第1方向へ)と走査するシフトレジスタとして機能する。

【0038】

また、走査方向制御信号UDがLレベル(すなわち反転した走査方向制御信号/UDがHレベル)の場合にはスタートパルス信号STVがP(M+2)、P(M+1)、P(M)…、P(0)、P(−1)の順にクロック信号CLK1、CLK2に同期して連鎖的にメモリされ、下から上へ(第2方向へ)と走査するシフトレジスタとして機能する。

【0039】

レジスタP(k)の出力はクロック信号CLK1またはクロック信号CLK2との論理積がとられた後にゲート信号SG(k)として表示領域ACTのゲート線G(1)〜G(M)へ出力される。但し、ゲート信号SG(−1),SG(0),SG(M+1),SG(M+2)は表示領域ACTへは出力されない。

【0040】

ここで、レジスタP(k)の出力信号と、クロック信号CLK1またはクロック信号CLK2との論理積をとるのは、クロック信号CLK1またはクロック信号CLK2を用いてパルス整形(水平期間(H)内でのゲート信号の立ち上がり/立ち下がりタイミングの調整)を行うためである。

【0041】

レジスタQ(j)(j=1,2,…,M+1)はCs信号を生成するためのレジスタであり、機能的にはP(k)と同様である。すなわち、レジスタQ(j)はG(j−2)またはG(j+1)がHレベルになるタイミングで走査方向制御信号FRを取り込み、このときの出力がCs信号SCs(j)として表示領域の補助容量線Cs(j)に出力される(j=1,2,…,M+1)。それ以外のタイミングではレジスタQ(j)の状態は変化せずに保持される。

【0042】

図3Aおよび図3Bは、本実施形態の液晶表示装置の駆動方法の一例を説明するためのタイミングチャートである。

【0043】

以上を踏まえて走査方向制御信号UDがHレベルの場合のゲート信号SGおよびCs信号SCsの動作を図3Aおよび図3Bを用いて説明する。ここで、液晶表示装置は一般に交流化駆動を行っており、1フレーム毎(あるいは2フレーム毎、3フレーム毎などの場合もある)に各画素PXの表示極性を反転させて動作させるため、2種類の極性パターンが存在する。以下の説明では、極性パターンの一方を正フレーム、他方を負フレームと呼んで区別する。

【0044】

まず正フレームにて、図示したようなスタートパルス信号STV、クロック信号CLK1、クロック信号CLK2、およびCs極性制御信号FRの信号が入力されたとする。Cs極性制御信号FRはHレベルとLレベルとが同じ期間(1水平期間(1H))となるように一定のタイミングで立ち上がりおよび立ち下がりを繰り返す。クロック信号CLK1はCs極性制御信号FRがHレベルの期間において所定期間Hレベルとなる。クロック信号CLK2はCs極性制御信号FRがLレベルの期間において所定期間Lレベルとなる。スタートパルス信号STVは、クロック信号CLK2が立ち上がるタイミングで立ち上がり、次にクロック信号CLK1が立ち上がるタイミングで立ち下がる。

【0045】

ここでレジスタP(−1)に着目すると、スタートパルス信号STVがHレベルにある期間中にクロック信号CLK2がHレベルになること(図中で示したパルスa)でレジスタP(−1)にHレベルが取り込まれる。その後クロック信号CLK2がLレベルになってもレジスタP(−1)はHレベルを保ち、再びクロック信号CLK2がHレベル(図中cで示したパルス)となってLレベルのスタートパルスが取り込まれるまでHレベルが保持される。従って、パルスaの立ち上がりからパルスcの立ち上がりまでの期間TAにおいて、レジスタP(−1)にHレベルの信号がメモリされる。レジスタP(−1)がHレベルの期間中にCLK1がHレベル(になること図中で示したパルスb)で、両者の論理積としてパルスbの形状がそのままゲート信号SG(−1)として出力される。

【0046】

次に、レジスタP(0)に着目すると、レジスタP(0)の入力側はレジスタP(−1)の出力端と接続されている。従って、レジスタP(0)の入力はレジスタP(−1)の出力(すなわちP(−1)の状態)であるから、これがHレベルである期間にクロック信号CLK1がHレベルとなること(図中のパルスb)で、レジスタP(0)にHレベルが取り込まれてHレベルとなる。

【0047】

この状態は、クロック信号CLK1の次にHレベルとなること(図中のパルスd)でLレベルが取り込まれるまで保持される。レジスタP(0)がHレベルの期間中にクロック信号CLK2がHレベルとなること(図中のパルスc)で、両者の論理積としてパルスcの形状がそのままゲート信号SG(0)として出力される。以下SG(1)、SG(2)、…についても同様に考えることができ、1水平期間(1H)毎に順次ゲート信号SGのHレベルパルスがシフトしていくことが理解できる。

【0048】

Cs信号SCsに関しては、ゲート信号SG(k)を基準として考えることができる。すなわち、ゲート信号SG(k)がHレベルになったときにレジスタQ(k−1)およびレジスタQ(k+2)においてCs極性制御信号FRが取り込まれ、それぞれCs信号SCs(k−1)およびCs信号SCs(k+2)に出力される。

【0049】

例えばゲート信号SG(2)がHレベルになっている水平期間(1H)ではCs極性制御信号FRがHレベルであるから、ゲート信号SG(2)がHレベルになるのと同じタイミングで、Cs信号SCs(1)およびCs信号SCs(4)がHレベルに遷移する。

【0050】

なおCs信号SCs(4)に関しては、ゲート信号SG(2)がHレベルになる前の状態がHレベル(実線)およびLレベル(破線)のいずれであろうと、ゲート信号SG(2)がHレベルになった時点で、Hレベルに固定されることを示している。ゲート信号SG(2)以外のゲート信号に対しても上記と同様に考えれば、各Cs信号SCsの動きが図3Aに示したとおりのものになる。

【0051】

なお各Cs信号SCsの波形に着目した場合、その上下のゲート信号が相次いでHレベルになる前に1回、後に1回Cs極性制御信号FRを取り込んでいることになる。このうち1回目のCs極性制御信号FR取り込みにおいては、上述のようにそれまでのCs信号SCsの状態にかかわりなく、HレベルまたはLレベルのうち何れか一方の状態に固定される(すなわちそれまでの状態がリセットされてCs極性制御信号FRで規定される状態に遷移する)。

【0052】

そして2回目のCs極性制御信号FR取り込みにおいて、Cs信号SCsが1回目とは逆の状態に遷移する。すなわち、1回目のCs極性制御信号FR取り込みと、2回目のCs極性制御信号FR取り込みとは水平期間(H)の奇数倍の時間差があるため、必ず逆の状態への遷移となる。この2回目のCs極性制御信号FR取り込みにおける遷移動作が、CCDI駆動の本質である画素電位への重畳電圧印加を行うことになる。

【0053】

ここでCs信号SCsがLレベルからHレベルへ遷移する場合を「正極性」、HレベルからLレベルへ遷移する場合を「負極性」と呼び、それぞれのCs信号SCsに「正極性」を示す“+”および「負極性」を示す“−”の記号を付してある。

【0054】

負フレームについては、入力信号においてCs極性制御信号FRのHレベルとLレベルとを正フレームに対して逆転させた駆動を行う。それ以外のスタートパルス信号STVやクロック信号CLK1、および、クロック信号CLK2は、正フレームと全く同じ波形である。

【0055】

この場合、ゲート信号SGは正フレームと全く同じとなり、Cs信号SCsは正フレームに対してHレベルとLレベルとが反転したものとなる。これにより、各Cs信号SCsの「正極性」と「負極性」とが逆転することになる。

【0056】

ここで、1回目のCs極性制御信号FR取り込みの作用について少し補足しておく。先にも述べたが、正フレームと負フレームとは1フレーム毎に交互に動作させる(すなわち1フレーム毎に反転させる)ケースだけでなく、2フレーム以上毎に反転させるケースもある。

【0057】

例えばOCB(Optically Compensated Bend)モードの液晶表示装置において黒挿入駆動を行う場合には、逆転移防止信号(正極性)、映像信号(正極性)、逆転移防止信号(負極性)、映像信号(負極性)、逆転移防止信号(正極性)、…の順に画素PXの表示極性が反転し、実質的に2フレーム毎に極性反転することがある。

【0058】

また、時分割3D(3次元)表示を行う場合などに、表示極性の偏りを防ぐため、左映像信号(正極性)、右映像信号(正極性)、左映像信号(負極性)、右映像信号(負極性)、左映像信号(正極性)、…の順に画素PXの表示極性が反転する場合があり、やはり2フレーム毎の極性反転が採用されることがある。

【0059】

あるいはさらに、OCBモードの液晶表示装置で時分割3D表示を行う場合には、逆転移防止信号(正極性)、左映像信号(正極性)、逆転移防止信号(正極性)、右映像信号(正極性)、逆転移防止信号(負極性)、左映像信号(負極性)、逆転移防止信号(負極性)、右映像信号(負極性)、逆転移防止信号(正極性)、…の順に画素PXの表示極性が反転する場合があり、実質的に4フレーム毎の極性反転となることがある。

【0060】

これらの場合、あるフレームに対してその前のフレームが同極性である場合と逆極性である場合とが混在する。これは例えば図3Aに示すCs信号SCsにおいて、1回目のCs極性制御信号FR取り込みの前の状態が破線で表わされる場合と実線で表される場合とが混在することを意味する。1回目のCs極性制御信号FR取り込みにおいてこの混在をリセットして何れか一方の状態に遷移させておくことで、2回目のCs極性制御信号FR取り込みによるCs信号SCsの遷移を常に正しく実施することが可能となる。

【0061】

次に、下上走査を行う場合(走査方向制御信号UDがLレベルの場合)のゲート信号SGおよびCs信号SCsの動作について図3Bを参照して説明する。この場合、ゲート線Gの走査方向は下から上となる。すなわち、図2に示すレジスタP(k)の入力側において、下側に接続されたスイッチ素子SWYが導通し、レジスタP(M+1)、レジスタP(M)…、レジスタP(0)、レジスタP(−1)の順に、クロック信号CLK1、CLK2に同期して連鎖的にスタートパルス信号STVがメモリされ、下から上へと走査するシフトレジスタとして機能する。

【0062】

レジスタP(k)の動作に連動して、レジスタQ(j)にもレジスタQ(M+1)、レジスタQ(M)…、レジスタQ(2)、レジスタQ(1)の順に、連鎖的にCs極性制御信号FRがメモリされる。

【0063】

すなわち、図3Aに示す上下走査の場合と、図3Bに示す下上走査の場合とを比較すると、走査方向制御信号UDが反転し、クロック信号CLK1とクロック信号CLK2とがそれぞれ反転している。また、上下走査におけるシフトレジスタP(k)は、下上走査におけるシフトレジスタP(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査におけるシフトレジスタQ(j)は、下上走査におけるシフトレジスタQ(j+2−k)(j=1,2,…,M+1)に対応する。

【0064】

その結果、走査方向が上下反転し、上下走査におけるゲート線G(k)は、下上走査におけるゲート線G(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査における補助容量線Cs(j)は、下上走査における補助容量線Cs(M+2−j)(j=1,2,…,M+1)に対応することになる。

【0065】

なお、図3Bでは、クロック信号CLK1とクロック信号CLK2とのタイミングが、図3Aと反転しているが、これは行毎に交互にクロック信号CLK1とクロック信号CLK2との接続パターンが入れ替わり、かつ、本実施形態ではMが偶数の場合を説明しているからである。Mが奇数の場合には、走査方向が上から下への向きのときと下から上への向きのときとでクロック信号CLK1とクロック信号CLK2とは同じ波形となる。

【0066】

図4Aおよび図4Bは、1H1V−CCDI駆動を行う液晶表示装置において上下走査を行う駆動方法の一例について説明するためのタイミングチャートである。

【0067】

上述のゲート信号SGおよびCs信号SCsの波形をもとにして、表示領域ACTにおける画素PXでの、CCDI駆動による重畳電圧の極性と、信号線Sに出力される信号(ソース出力)の極性との関係について説明する。

【0068】

まず、CCDI駆動の中で最も基本的な1H1V−CCDI駆動について、図4Aおよび図4Bを用いて説明する。1H1Vとは、画素PXの表示極性の配列が1列毎に極性反転し、かつ、1行毎に極性反転する方式、すなわち、表示極性が正極性の画素PXと負極性の画素PXとが市松状に配列する駆動方法である。

【0069】

1H1V反転の利点として、各行書き込み時に正負極性が混在することになり、例えば信号線Sから対向電極へのカップリングが正負極性で相殺されるため、横クロストークが改善できるということが挙げられる。また、ライン反転駆動やカラム反転駆動では対向電極電位がずれた場合などにラインフリッカが見えることがあるが、ドット反転では対向電極電位がずれてもラインフリッカが見えにくいというメリットもある。

【0070】

1H1V反転駆動においては、図4Aに示す正フレームにおける画素配置図で示したように、各画素PXの補助容量Cstは、紙面に向かって画素電極PEの上側、あるいは下側の補助容量線Csのいずれかに接続されるが、1列ごとに接続先の補助容量線Csが上側と下側との交互になっている。すなわち、例えば奇数番目の列(図中のODD列)に属する画素PXの補助容量Cstは画素電極PEの上側の補助容量線Csに接続され、偶数番目の列(図中のEVEN列)に属する画素PXの補助容量Cstは画素電極PEの下側の補助容量線Csに接続される。

【0071】

ここで、図4Aおよび図4Bには正フレームと負フレームとのそれぞれについて、画素配置図の右側に、各ゲート線Gと補助容量線Csに対応させて、上下走査時(走査方向制御信号UDがHレベルのとき)のゲート信号SG波形およびCs信号SCs波形、Cs極性制御信号FR波形、および各Cs信号SCsの極性を示している。図4Aに示す信号波形は、図3Aに示す上下走査時の正フレームでのゲート信号SG波形およびCs信号SCs波形、Cs極性制御信号FR波形、および各Cs信号SCsの極性と同様である。

【0072】

例えばゲート線G1の行に注目すると、ゲート信号SG1がHレベルになった次の水平期間(1H)で、上側の補助容量線Cs1のCs信号SCs1がLレベルからHレベルへ遷移し(Cs信号SCs1は「正極性」)、さらに、その次の水平期間(1H)では下側の補助容量線Cs2のCs信号SCs2がHレベルからLレベルへ遷移している(Cs信号SCs2は「負極性」)。

【0073】

これは、補助容量Cstが画素電極PEの上側の補助容量線Cs1に接続される画素PX(O1)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる正の重畳電圧が加えられ、補助容量Cstが画素電極PEの下側の補助容量線Cs2に接続される画素PX(E1)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる負の重畳電圧が加えられることを意味している。

【0074】

画素電位に正しい極性の重畳電圧を与えるためには、XドライバXDが出力する映像信号あるいは逆転移防止信号(例えば黒表示に対応した信号)等のソース出力の極性と、重畳電圧の極性とが一致している必要がある。この条件が満たされないと表示の白黒が反転する等の不具合が生じる。従って、ゲート信号SG1がHレベルになっている水平期間では、奇数(ODD)列の信号線Sへのソース出力は正極性に、偶数(EVEN)列の信号線Sへのソース出力は負極性にする必要がある。

【0075】

以下、順次ゲート線G2、G3、…の行に注目して同様の考え方を適用すれば、各行の画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。各画素PXには、このようにして決まった重畳電圧の極性を示してある。また、Cs極性制御信号FR波形の上にはこのようにして決定したソース出力の極性を示してある。各画素PXの極性は確かに、1H1V反転パターンで市松状に分布していることが確認される。

【0076】

図4Bの負フレームにおいては、正フレームと同じ画素配置図を描き、それに対応させて図3Aの負フレームと同様のゲート信号およびCs信号波形、FR信号波形、および各Cs信号の極性を記載している。

【0077】

ここでは、Cs信号SCsの極性が正フレームに対して正負逆転したものとなっている。従って、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性も正フレームに対して反転したものとなり、図4Aに示したとおりの画素極性パターンおよびソース出力極性パターンが得られる。

【0078】

図4Cおよび図4Dは、1H1V−CCDI駆動を行う液晶表示装置において下上走査を行う駆動方法の一例について説明するためのタイミングチャートである。

【0079】

次に、図4Cおよび図4Dにて下上走査の場合(走査方向制御信号UDがLレベルの場合)を説明する。なお、本実施形態ではMが800の場合について説明する。図4Cおよび図4Dでは、ゲート配線G800、G799、G798、…の順に上から並び、図4Aおよび図4Bと上下が反転した画素配置図を示している。従って、画素PXの補助容量Cst配置の接続先の補助容量線Csも上下反転する。すなわち、図4Cおよび図4Dにおける上側は図4Aおよび図4Bにおける下側に相当し、図4Cおよび図4Dにおける下側は図4Aおよび図4Bにおける上側に相当する。

【0080】

図4Aおよび図4Bでは、画素PXの奇数(ODD)列において画素電極PEの図の上側の補助容量線Csに対して補助容量Cstが接続され、画素PXの偶数(EVEN)列において画素電極PEの図の下側の補助容量線Csに対して補助容量Cstが接続されていたが、図4Cおよび図4Dでは奇数(ODD)列において画素電極PEの図の下側の補助容量線Csに対して補助容量Cstが接続され、偶数(EVEN)列において画素電極PEの図の上側の補助容量線Csに対して補助容量Cstが接続されることになる。

【0081】

これは図4Aおよび図4Bと比較して、接続先の補助容量線Csが偶数(EVEN)列と奇数(ODD)列とが上下入れ替わったことに相当する。よって、図4Aおよび図4Bのときと同じ考え方で決められる、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性も、偶数(EVEN)列と奇数(ODD)列とが入れ替わったものになり、結果的にソース出力の極性は図4Aに示す上下走査の場合に対して正負反転したものとなる。

【0082】

この場合、ゲート信号SG波形およびCs信号SCs波形に関しては、図4Aおよび図4Bにおけるゲート信号SG1、SG2、…をゲート信号SG800、SG799、…と置き換え、Cs信号SCs1、SCs2、…をCs信号SCs801、SCs800、…と置き換えたものである。

【0083】

なお上記ではMが800の場合を一例として説明したが、Mが800以外の場合でも同様であることは自明である。

【0084】

以上の図4A乃至図4Dの結果を総合すると、1H1V−CCDI駆動にて正常表示を行うために必要な条件は、上下走査と下上走査にて、Cs極性制御信号FR(各画素に与える容量結合重畳電圧の極性を決める制御信号)が同じ極性のフレームでのソース出力の極性を比較したときに、互いに逆になっていることであるといえる。すなわち、上下走査のときの正フレームと下上走査のときの正フレームとでは、ソース出力の極性が逆になっている。同様に上下走査のときの負フレームと下上走査のときの負フレームとでは、ソース出力の極性が逆になっている。

【0085】

以上より制御回路CTRは、上下走査と下上走査とにおいて、Cs極性制御信号FRが同じ極性フレームでのソース出力の極性の位相が逆になるように(言い換えれば水平期間単位での位相が異なるように)出力するものである。

【0086】

上記のように、本実施形態の液晶表示装置によれば、上下反転表示を実現するとともに表示品位の良好な液晶表示装置および液晶表示装置の駆動方法を提供することができる。

【0087】

次に、第2実施形態の液晶表示装置およびその駆動方法について、図5A乃至図5Jを参照して説明する。本実施形態の液晶表示装置では、上述の1H1V−CCDI駆動を改良した駆動方法を採用している。本実施形態では、画素PXが並ぶ列方向に関して画素極性の配列が1列毎に極性反転している点は上述の1H1V−CCDIと同様であるが、行方向に関して2行毎に極性が反転する2H1V−CCDI駆動を採用している。

【0088】

2H1V−CCDI駆動の利点は、1H1V−CCDI駆動よりもさらに低電力を実現できることである。すなわち、1H1V反転の場合は各信号線Sに供給される映像信号(あるいは逆転移防止信号)の極性が1水平期間(1H)毎に反転していたが、2H1V反転の場合は2水平期間(2H)毎の反転となるため、信号線充放電の周波数が半分になり、消費電力が低減される。

【0089】

最初に、2H1V−CCDI駆動における補助容量Cst配置について説明する。1H1V−CCDI駆動においては奇数(ODD)列と偶数(EVEN)列とで補助容量Cst配置の上下が分かれていたが、2H1V−CCDI駆動においては、画素PXの極性パターンがまず与えられたものとし、そこからあるべき補助容量Cst配置を求める。

【0090】

図5Aの上下走査時(走査方向制御信号UDがHレベルのとき)の正フレームの図に基づいて説明する。まず、図3Aの正フレームに相当する駆動が行われるものとして、図3Aと同様のゲート信号SG波形、Cs信号SCs波形、Cs極性制御信号FR波形、および各Cs信号SCsの極性を記載している。すなわち、図5Aの正フレームの波形は、図4Aに示す正フレームの波形と同一である。

【0091】

この場合、Cs信号SCs1、Cs信号SCs2、Cs信号SCs3、Cs信号SCs4、Cs信号SCs5、Cs信号SCs6、…の極性はそれぞれ正、負、正、負、正、負、…である。

【0092】

いま、図5Aの左の画素配置図にあるように、たとえば奇数(ODD)列において画素PX(O1)、PX(O2)、PX(O3)、PX(O4)、PX(O5)、…の表示極性がそれぞれ正、正、負、負、正、…で、奇数(EVEN)列において画素PX(E1)、PX(E2)、PX(E3)、PX(E4)、PX(E5)、…の表示極性がそれぞれ負、負、正、正、負、…極性というような、2H1V反転の極性パターンでCs信号からの重畳電圧を与えるものとする。

【0093】

まず、ゲート線G1の行に注目すると、画素PX(O1)に正、画素PX(E1)に負の重畳電圧を与えるのであるから、画素PX(O1)は上側の補助容量線Cs1(正極性)、画素PX(E1)は下側の補助容量線Cs2(負極性)との間に補助容量Cstを形成すればよい。

【0094】

次にゲート線G2の行に注目すると、画素PX(O2)に正、画素PX(E2)に負の重畳電圧を与えるのであるから、画素PX(O2)は下側の補助容量線Cs3(正極性)、画素PX(E2)は上側の補助容量線Cs2(負極性)との間に補助容量Cstを形成すればよい。

【0095】

次にゲート線G3の行に注目すると、画素PX(O3)に負、画素PX(E3)に正の重畳電圧を与えるのであるから、画素PX(O3)は下側の補助容量線Cs4(負極性)、画素PX(E3)は上側の補助容量線Cs3(正極性)との間に補助容量Cstを形成すればよい。

【0096】

次にゲート線G4の行に注目すると、画素PX(O4)に負、画素PX(E4)に正の重畳電圧を与えるのであるから、画素PX(O4)は上側の補助容量線Cs4(負極性)、画素PX(E4)は下側の補助容量線Cs5(正極性)との間に補助容量Cstを形成すればよい。

【0097】

次にゲート線G5の行に注目すると、画素PX(O5)に正、画素PX(E5)に負の重畳電圧を与えるのであるから、画素PX(O5)は上側の補助容量線Cs5(正極性)、画素PX(E5)は下側の補助容量線Cs6(負極性)との間に補助容量Cstを形成すればよい。

【0098】

以下、ゲート線G6の行、ゲート線G7の行、…と全く同じようにして補助容量Cst配置を決定することができる。このようにして得られた補助容量Cst配置は、画素極性パターンに対応して4行周期の繰り返しパターンになる。

【0099】

ソース出力の極性パターンも併せて、Cs極性制御信号FR波形の上に示す。これは画素PXの重畳電圧極性パターンに一致するように極性を決めればよく、図に示したように4水平期間周期のパターンとなる。

【0100】

図5Bの負フレームにおいては、上記のようにして決めた補助容量Cst配置に対して、Cs信号SCsの極性が逆になるような駆動を行うことになる。従って、画素PXの表示極性とソース出力の極性とも、正フレームに対して反転したものになる。

【0101】

図5Cおよび図5Jは、下上走査を行う場合(走査方向制御信号UDがLレベルの場合)の補助容量Cst配置図およびタイミングチャートである。

【0102】

次に、図5Cおよび図5Dにて下上走査の場合(走査方向制御信号UDがLレベルの場合)の一例について説明する。ここでは、例としてMが800の場合について説明する。基本的な考え方は1H1V−CCDI駆動の場合と同様であり、ゲート信号SGおよびCs信号SCs波形に関しては図5Aおよび図5Bに対して以下の変更を行ったものである。

【0103】

すなわち、図5Aおよび図5Bに示す上下走査の場合と、図5Cおよび図5Dに示す下上走査の場合とを比較すると、走査方向制御信号UDが反転し、クロック信号CLK1とクロック信号CLK2とがそれぞれ反転している。また、上下走査におけるシフトレジスタP(k)は、下上走査におけるシフトレジスタP(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査におけるシフトレジスタQ(j)は、下上走査におけるシフトレジスタQ(j+2−k)(j=1,2,…,M+1)に対応する。

【0104】

その結果、走査方向が上下反転し、上下走査におけるゲート線G(k)は、下上走査におけるゲート線G(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査における補助容量線Cs(j)は、下上走査における補助容量線Cs(M+2−j)(j=1,2,…,M+1)に対応することになる。

【0105】

補助容量Cst配置に関しては、2H1V−CCDI駆動では補助容量Cst配置が4行を1周期とする繰り返しパターンを持っていることに注意する必要がある。すなわち、例えばゲート線G797の行、ゲート線G798の行、ゲート線G799の行、およびゲート線G800の行の補助容量Cst配置は、それぞれゲート線G1の行、ゲート線G2の行、ゲート線G3の行、およびゲート線G4の行の補助容量Cst配置と同じになる。すなわち、行番号を4で割ったときの余り(1、2、3、および0)が同じ画素PXの行同士では補助容量Cst配置が同じである。

【0106】

なお、1H1V−CCDI駆動の図4Cおよび図4Dにて説明したのと同様に、図5Cおよび図5Dの画素配置は図面上では上下反転して描いている。1H1V−CCDI駆動の図4Aおよび図4Bのところで説明したのと同じ手順で、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。

【0107】

正フレームにおいて、例えばゲート線G800の行に注目すると、ゲート信号SG800がHレベルになった次の水平期間(1H)で、下側(図の上側)の補助容量線Cs801のCs信号SCs801がLレベルからHレベルへ遷移し(Cs信号SCs801は「正極性」)、さらに、その次の水平期間(1H)では上側(図の下側)の補助容量線Cs800のCs信号SCs800がHレベルからLレベルへ遷移している(Cs信号SCs800は「負極性」)。

【0108】

これは、補助容量Cstが画素電極PEの下側の補助容量線Cs801に接続される画素PX(E800)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる正の重畳電圧が加えられ、補助容量Cstが画素電極PEの上側の補助容量線Cs800に接続される画素PX(O800)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる負の重畳電圧が加えられることを意味している。

【0109】

従って、ゲート信号SG800がHレベルになっている水平期間(1H)では、奇数(ODD)列の信号線Sへのソース出力は負極性に、偶数(EVEN)列の信号線Sへのソース出力は正極性にする必要がある。

【0110】

以下、順次ゲート線G799、ゲート線G798…の行に注目して同様の考え方を適用すれば、各行の画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。各画素PXには、このようにして決まった重畳電圧の極性を示してある。また、Cs極性制御信号FR波形の上にこのようにして決定したソース出力の極性を示す。

【0111】

また、負フレームでは、Cs信号SCsの極性が正フレームに対して正負逆転したものとなっている。従って、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性も正フレームに対して反転したものとなる。

【0112】

2H1V−CCDI駆動においては、上述したように補助容量Cst配置が4行周期の繰り返しパターンを持っていることに起因して、表示領域ACTの行数Mを4で割ったときの余りに応じて、下上走査時の重畳電圧の極性とそれに対応して与えるべきソース出力の極性とが異なってくる。図5Cおよび図5Dの場合と同様の結果が得られるのは、Mが4の倍数の場合(pを整数としてM=4pで表される場合)に限られる。

【0113】

図5Eおよび図5Fに、M=4p+1(例えばM=801)である場合における下上駆動の際の駆動波形図、および補助容量Cst配置図を示す。ゲート信号SGおよびCs信号SCs波形に関しては図5Aおよび図5Bに対して以下の変更を行ったものである。

【0114】

すなわち、図5Aおよび図5Bにおける上下走査の場合と図5Eおよび図5Fにおける下上走査の場合とを比較すると、走査方向制御信号UDが反転し、クロック信号CLK1とクロック信号CLK2とがそれぞれ反転している。また、上下走査におけるシフトレジスタP(k)は、下上走査におけるシフトレジスタP(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査におけるシフトレジスタQ(j)は、下上走査におけるシフトレジスタQ(j+2−k)(j=1,2,…,M+1)に対応する。

【0115】

その結果、走査方向が上下反転し、上下走査におけるゲート線G(k)は、下上走査におけるゲート線G(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査における補助容量線Cs(j)は、下上走査における補助容量線Cs(M+2−j)(j=1,2,…,M+1)に対応することになる。

【0116】

補助容量Cst配置に関しては、ゲート線G801の行の補助容量Cst配置がゲート線G1行のそれと同じである。ゲート線G800の行、ゲート線G799の行、ゲート線G798の行、…、ゲート線G1の行は図5Cおよび図5Dと同じ補助容量Cst配置になる。

【0117】

なお、図5Eおよび図5Fではゲート配線G801、G800、G799、…の順に上から並び、図5Aおよび図5Bと上下が反転した画素配置図を示している。従って、画素PXの補助容量Cst配置の接続先の補助容量線Csも上下反転する。

【0118】

1H1V−CCDI駆動の図4Aおよび図4Bのところで説明したのと同じ手順で、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。

【0119】

正フレームにおいて、例えばゲート線G801の行に注目すると、ゲート信号SG801がHレベルになった次の水平期間(1H)で、下側(図の上側)の補助容量線Cs802のCs信号SCs802がLレベルからHレベルへ遷移し(Cs信号SCs802は「正極性」)、さらに、その次の水平期間(1H)では上側(図の下側)の補助容量線Cs801のCs信号SCs801がHレベルからLレベルへ遷移している(Cs信号SCs801は「負極性」)。

【0120】

これは、補助容量Cstが画素電極PEの下側の補助容量線Cs802に接続される画素PX(E801)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる正の重畳電圧が加えられ、補助容量Cstが画素電極PEの上側の補助容量線Cs801に接続される画素PX(O801)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる負の重畳電圧が加えられることを意味している。

【0121】

従って、ゲート信号SG801がHレベルになっている水平期間(1H)では、奇数(ODD)列の信号線Sへのソース出力は負極性に、偶数(EVEN)列の信号線Sへのソース出力は正極性にする必要がある。

【0122】

以下、順次ゲート線G800、ゲート線G799、…の行に注目して同様の考え方を適用すれば、各行の画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。各画素PXには、このようにして決まった重畳電圧の極性を示してある。また、Cs極性制御信号FR波形の上にこのようにして決定したソース出力の極性を示す。

【0123】

また、負フレームでは、Cs信号SCsの極性が正フレームに対して正負逆転したものとなっている。従って、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性も正フレームに対して反転したものとなる。

【0124】

図5Gおよび図5HにM=4p+2(例としてM=802)の場合における下上走査の際の駆動波形図、および画素Cst配置図を示す。ゲート信号SGおよびCs信号SCs波形に関しては図5Aおよび図5Bに対して以下の変更を行ったものである。

【0125】

すなわち、図5Aおよび図5Bにおける上下走査の場合と図5Gおよび図5Hにおける下上走査の場合とを比較すると、走査方向制御信号UDが反転し、クロック信号CLK1とクロック信号CLK2とがそれぞれ反転している。また、上下走査におけるシフトレジスタP(k)は、下上走査におけるシフトレジスタP(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査におけるシフトレジスタQ(j)は、下上走査におけるシフトレジスタQ(j+2−k)(j=1,2,…,M+1)に対応する。

【0126】

その結果、走査方向が上下反転し、上下走査におけるゲート線G(k)は、下上走査におけるゲート線G(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査における補助容量線Cs(j)は、下上走査における補助容量線Cs(M+2−j)(j=1,2,…,M+1)に対応することになる。

【0127】

補助容量Cst配置に関しては、ゲート線G802の行の補助容量Cst配置がゲート線G2行のそれと同じである。ゲート線G802の行、ゲート線G801の行、ゲート線G800の行、…、ゲート線G1の行は図5Eおよび図5Fと同じ補助容量Cst配置になる。

【0128】

なお、図5Gおよび図5Hではゲート配線G802、G801、G800、…の順に上から並び、図5Aおよび図5Bと上下が反転した画素配置図を示している。従って、画素PXの補助容量Cst配置の接続先の補助容量線Csも上下反転する。

【0129】

1H1V−CCDI駆動の図4Aおよび図4Bのところで説明したのと同じ手順で、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。

【0130】

正フレームにおいて、例えばゲート線G802の行に注目すると、ゲート信号SG802がHレベルになった次の水平期間(1H)で、下側(図の上側)の補助容量線Cs803のCs信号SCs803がLレベルからHレベルへ遷移し(Cs信号SCs803は「正極性」)、さらに、その次の水平期間(1H)では上側(図の下側)の補助容量線Cs802のCs信号SCs802がHレベルからLレベルへ遷移している(Cs信号SCs802は「負極性」)。

【0131】

これは、補助容量Cstが画素電極PEの下側の補助容量線Cs803に接続される画素PX(O802)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる正の重畳電圧が加えられ、補助容量Cstが画素電極PEの上側の補助容量線Cs802に接続される画素PX(E802)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる負の重畳電圧が加えられることを意味している。

【0132】

従って、ゲート信号SG802がHレベルになっている水平期間(1H)では、奇数(ODD)列の信号線Sへのソース出力は正極性に、偶数(EVEN)列の信号線Sへのソース出力は負極性にする必要がある。

【0133】

以下、順次ゲート線G801、ゲート線G800、…の行に注目して同様の考え方を適用すれば、各行の画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。各画素PXには、このようにして決まった重畳電圧の極性を示してある。また、Cs極性制御信号FR波形の上にこのようにして決定したソース出力の極性を示す。

【0134】

また、負フレームでは、Cs信号SCsの極性が正フレームに対して正負逆転したものとなっている。従って、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性も正フレームに対して反転したものとなる。

【0135】

図5Iおよび図5Jに、M=4p+3(例としてM=803)の場合における下上駆動の際の駆動波形図、および画素Cst配置図を示す。ゲート信号SGおよびCs信号SCs波形に関しては図5Aおよび図5Bに対して以下の変更を行ったものである。

【0136】

すなわち、図5Aおよび図5Bにおける上下走査の場合と図5Iおよび図5Jにおける下上走査の場合とを比較すると、走査方向制御信号UDが反転し、クロック信号CLK1とクロック信号CLK2とがそれぞれ反転している。また、上下走査におけるシフトレジスタP(k)は、下上走査におけるシフトレジスタP(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査におけるシフトレジスタQ(j)は、下上走査におけるシフトレジスタQ(j+2−k)(j=1,2,…,M+1)に対応する。

【0137】

その結果、走査方向が上下反転し、上下走査におけるゲート線G(k)は、下上走査におけるゲート線G(M+1−k)(k=−1,0,1,…,M+2)に対応し、上下走査における補助容量線Cs(j)は、下上走査における補助容量線Cs(M+2−j)(j=1,2,…,M+1)に対応することになる。

【0138】

補助容量Cst配置に関しては、ゲート線G803の行の補助容量Cst配置がゲート線G3行のそれと同じである。ゲート線G803の行、ゲート線G802の行、ゲート線G801の行、…、ゲート線G1の行は当然ながら図5Dと同じ補助容量Cst配置になる。

【0139】

なお、図5Iおよび図5Jではゲート配線G802、G801、G800、…の順に上から並び、図5Aおよび図5Bと上下が反転した画素配置図を示している。従って、画素PXの補助容量Cst配置の接続先の補助容量線Csも上下反転する。

【0140】

1H1V−CCDI駆動の図4Aおよび図4Bのところで説明したのと同じ手順で、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。

【0141】

正フレームにおいて、例えばゲート線G803の行に注目すると、ゲート信号SG803がHレベルになった次の水平期間(1H)で、下側(図の上側)の補助容量線Cs804のCs信号SCs804がLレベルからHレベルへ遷移し(Cs信号SCs804は「正極性」)、さらに、その次の水平期間(1H)では上側(図の下側)の補助容量線Cs803のCs信号SCs803がHレベルからLレベルへ遷移している(Cs信号SCs803は「負極性」)。

【0142】

これは、補助容量Cstが画素電極PEの下側の補助容量線Cs804に接続される画素PX(O803)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる正の重畳電圧が加えられ、補助容量Cstが画素電極PEの上側の補助容量線Cs803に接続される画素PX(E803)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる負の重畳電圧が加えられることを意味している。

【0143】

従って、ゲート信号SG802がHレベルになっている水平期間(1H)では、奇数(ODD)列の信号線Sへのソース出力は正極性に、偶数(EVEN)列の信号線Sへのソース出力は負極性にする必要がある。

【0144】

以下、順次ゲート線G801、ゲート線G800、…の行に注目して同様の考え方を適用すれば、各行の画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。各画素PXには、このようにして決まった重畳電圧の極性を示してある。また、Cs極性制御信号FR波形の上にこのようにして決定したソース出力の極性を示す。

【0145】

また、負フレームでは、Cs信号SCsの極性が正フレームに対して正負逆転したものとなっている。従って、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性も正フレームに対して反転したものとなる。

【0146】

以上の図5A乃至図5Jの結果を総合すると、2H1V−CCDI駆動にて表示品位の良好な表示を行うために必要な条件は下記である。

【0147】

上下走査と下上走査との、Cs極性制御信号FR(各画素に与える容量結合重畳電圧の極性を決める制御信号)が同じフレーム(正フレーム同士あるいは負フレーム同士)でのソース出力の極性を比較したときに、

(1) M=4pの場合:下上走査では上下走査に比べて位相が2H早い(或いは2H遅い)こと

(2) M=4p+1の場合:下上走査では上下走査に比べて位相が3H早い(或いは1H遅い)こと

(3) M=4p+2の場合:下上走査では上下走査に比べて位相が同じであること

(4) M=4p+3の場合:下上走査では上下走査に比べて位相が1H早い(或いは3H遅い)こと

になる(ここでHは水平期間の意である)。

【0148】

上記(3)(M=4p+2)の場合以外においては上下走査と下上走査で位相を異ならせる必要がある。従って制御回路CTRは、上下走査と下上走査との切替えの際に、Cs極性制御信号FRが同じフレームでのソース出力の極性のH単位での位相を、上記(1)、(2)、(4)の規則に対応させて、異なるように出力するものである。

【0149】

上記のように、本実施形態の液晶表示装置によれば、上下反転表示を実現するとともに表示品位の良好な液晶表示装置および液晶表示装置の駆動方法を提供することができる。

【0150】

また制御回路CTRは、上下走査と下上走査とにおいて、Cs極性制御信号FRが同じフレームでのソース出力の極性の位相関係を、2種類以上に設定可能で、その中から一つを選択できるものであることが望ましい。

【0151】

こうすると、上記(1)〜(4)のうちの特定の1つのケースだけでなく、複数のケースに対応できるようになるため、制御回路CTRとしての汎用性が高くなる。表示領域ACTの行数が異なる複数の機種に対して制御回路CTRを共用化できるため、制御回路CTRを含めた表示装置の開発コストや製造コストが低減されるというメリットが得られる。

【0152】

なお、液晶表示装置の行数は偶数であることが多い。従って、制御回路CTRはソース出力の極性を少なくとも上記(1)と(3)との2種類の位相関係に設定可能であれば、汎用性としては十分に高いといえる。

【0153】

例えば携帯電話やスマートフォンなどの液晶表示装置を搭載した電子機器においては、画面解像度が480(列)×800(行)(800行はM=4pに相当)または480(列)×854(行)(854行はM=4p+2に相当)が主流であり、これらの両者に共通の制御回路CTRを用いられることのメリットは大きい。

【0154】

以上、図5A乃至図5Jを参照して2H1V−CCDI駆動について述べてきたが、同様の考え方はnH1V−CCDI駆動(nは3以上の整数)に対しても適用可能である。

【0155】

映像信号の極性反転をn水平期間毎にすることで、信号線充放電の消費電力を1/nに比例して低減できるというメリットが得られる。ただし、あまりnが大きすぎるとn行ピッチの横帯やラインフリッカが目立ちやすくなるというデメリットも顕在化してくるため、実際の表示装置においては画質や消費電力の要求仕様を鑑みて最適なnの値を選択すればよい。

【0156】

これらの場合も2H1V−CCDI駆動と同様の考え方を適用すれば、表示領域の行数に応じて、上下走査と下上走査で、ソース出力の極性の位相を異ならせる必要があると結論される(因みに補助容量Cst配置の繰返し周期は、nが偶数の場合2n行周期、nが奇数の場合n行周期となる)。従って制御回路CTRは2H1V−CCDI駆動の場合と同様の特徴を持った構成であることが望ましい。

【0157】

次に、第3実施形態の液晶表示装置および液晶表示装置の駆動方法について図面を参照して以下に説明する。

【0158】

nをさらに大きくしてnを画素PXの全行数に一致させると、1列内の全画素の極性が同一になり、CCカラム反転方式に帰着する。CCカラム反転方式も、広い意味でCCDI駆動に含まれるものとみなすことができる。

【0159】

CCカラム反転方式は電力も小さく、横帯やラインフリッカも発生しないという長所があるが、一方で縦クロストークが発生しやすいという課題もある。これらの長所および課題点を勘案の上で、CCカラム反転方式を採用することも可能である。CCカラム反転方式でも、これまでの説明と全く同様の考え方が適用可能である。

【0160】

図6A乃至図6Fは、CCカラム反転方式を採用した液晶表示装置について補助容量Cst配置および駆動波形を示す。これは図5A乃至図5Dでの説明と全く同じ考え方を適用して描いたものである。図6Aおよび図6Bは上下走査時(走査方向制御信号UDがHレベルのとき)に対応するものであり、図3Aに示すゲート信号SGおよびCs信号SCs波形と、カラム反転の画素極性パターン(例えば正フレームにおいて奇数(ODD)列が正、偶数(EVEN)列が負)から、あるべき補助容量Cst配置パターンを求めている。

【0161】

図6Aの上下走査時(走査方向制御信号UDがHレベルのとき)の正フレームの図に基づいて説明する。まず、図3Aの正フレームに相当する駆動が行われるものとして、図3Aと同様のゲート信号SG波形、Cs信号SCs波形、Cs極性制御信号FR波形、および各Cs信号SCsの極性を記載している。すなわち、図6Aの正フレームの波形は、図4Aに示す正フレームの波形と同一である。

【0162】

この場合、Cs信号SCs1、Cs信号SCs2、Cs信号SCs3、Cs信号SCs4、Cs信号SCs5、Cs信号SCs6、…の極性はそれぞれ正、負、正、負、正、負、…である。

【0163】

いま、図6Aの左の画素配置図にあるように、たとえば奇数(ODD)列において画素PX(O1)、PX(O2)、PX(O3)、PX(O4)、PX(O5)、…の表示極性が正極性で、奇数(EVEN)列において画素PX(E1)、PX(E2)、PX(E3)、PX(E4)、PX(E5)、…の表示極性が負極性というような極性パターンでCs信号SCsからの重畳電圧を与えるものとする。

【0164】

まず、ゲート線G1の行に注目すると、画素PX(O1)に正、画素PX(E1)に負の重畳電圧を与えるのであるから、画素PX(O1)は上側の補助容量線Cs1(正極性)、画素PX(E1)は下側の補助容量線Cs2(負極性)との間に補助容量Cstを形成すればよい。

【0165】

次にゲート線G2の行に注目すると、画素PX(O2)に正、画素PX(E2)に負の重畳電圧を与えるのであるから、画素PX(O2)は下側の補助容量線Cs3(正極性)、画素PX(E2)は上側の補助容量線Cs2(負極性)との間に補助容量Cstを形成すればよい。

【0166】

次にゲート線G3の行に注目すると、画素PX(O3)に負、画素PX(E3)に正の重畳電圧を与えるのであるから、画素PX(O3)は上側の補助容量線Cs4(負極性)、画素PX(E3)は下側の補助容量線Cs3(正極性)との間に補助容量Cstを形成すればよい。

【0167】

次にゲート線G4の行に注目すると、画素PX(O4)に負、画素PX(E4)に正の重畳電圧を与えるのであるから、画素PX(O4)は下側の補助容量線Cs4(負極性)、画素PX(E4)は上側の補助容量線Cs5(正極性)との間に補助容量Cstを形成すればよい。

【0168】

以下、ゲート線G5の行、ゲート線G6の行、…と全く同じようにして補助容量Cst配置を決定することができる。このようにして得られた補助容量Cst配置は、列方向において2行周期の繰り返しパターンになる(ソース出力極性がH単位の周期を持たないので、補助容量線の極性反転周期(2行)が補助容量Cst配置の周期に反映される)。同じ行に配置された奇数(ODD)列と偶数(EVEN)列との画素PXの補助容量Cstは互いに異なる補助容量線Csに接続され、同じ列に配置された奇数行と偶数行との画素PXの補助容量Cstは、異なる側の補助容量線Csに接続されている。正極性の補助容量線Csと負極性の補助容量線Csとが行方向に交互に配置されることになる。

【0169】

図6Aおよび図6Bに示す場合、ソース出力の極性は正フレームにおいて奇数(ODD)列の信号線Sが負極性となり、偶数(EVEV)列の信号線Sが負極性となる。ソース出力の極性は負フレームにおいて奇数(ODD)列の信号線Sが正極性となり、偶数(EVEN)列の信号線Sが正極性となる。

【0170】

図6C乃至図6Fは、下上走査(走査方向制御信号UDがLレベルのとき)に対応する図である。補助容量Cst配置が2行周期の繰り返しパターンを持っていることを考慮して、図6Cおよび図6DにはMが偶数の場合(pを整数としてM=2pの場合)を示し、図6Eおよび図6FにはMが奇数の場合(pを整数としてM=2p+1の場合)を示している。なお、図6C乃至図6Fは上下反転して記載されている。

【0171】

図5Cおよび図5Dと同様の考え方を適用することで、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。

【0172】

図6Cに示す正フレームにおいて、例えばゲート線G800の行に注目すると、ゲート信号SG800がHレベルになった次の水平期間(1H)で、下側(図の上側)の補助容量線Cs801のCs信号SCs801がLレベルからHレベルへ遷移し(Cs信号SCs801は「正極性」)、さらに、その次の水平期間(1H)では上側(図の下側)の補助容量線Cs800のCs信号SCs800がHレベルからLレベルへ遷移している(Cs信号SCs800は「負極性」)。

【0173】

これは、補助容量Cstが画素電極PEの下側の補助容量線Cs801に接続される画素PX(O800)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる正の重畳電圧が加えられ、補助容量Cstが画素電極PEの上側の補助容量線Cs800に接続される画素PX(E800)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる負の重畳電圧が加えられることを意味している。

【0174】

従って、ゲート信号SG800がHレベルになっている水平期間(1H)では、奇数(ODD)列の信号線Sへのソース出力は正極性に、偶数(EVEN)列の信号線Sへのソース出力は負極性にする必要がある。

【0175】

以下、順次ゲート線G799、ゲート線G798、…の行に注目して同様の考え方を適用すれば、各行の画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。各画素PXには、このようにして決まった重畳電圧の極性を示してある。また、Cs極性制御信号FR波形の上にこのようにして決定したソース出力の極性を示す。

【0176】

また、図6Dに示す負フレームでは、Cs信号SCsの極性が正フレームに対して正負逆転したものとなっている。従って、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性も正フレームに対して反転したものとなる。

【0177】

図6Eに示す正フレームにおいて、例えばゲート線G801の行に注目すると、ゲート信号SG801がHレベルになった次の水平期間(1H)で、下側(図の上側)の補助容量線Cs802のCs信号SCs802がLレベルからHレベルへ遷移し(Cs信号SCs802は「正極性」)、さらに、その次の水平期間(1H)では上側(図の下側)の補助容量線Cs801のCs信号SCs801がHレベルからLレベルへ遷移している(Cs信号SCs801は「負極性」)。

【0178】

これは、補助容量Cstが画素電極PEの下側の補助容量線Cs802に接続される画素PX(E801)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる正の重畳電圧が加えられ、補助容量Cstが画素電極PEの上側の補助容量線Cs801に接続される画素PX(O801)では画素電極PEへの信号書き込み後に補助容量Cstを介して画素電位に容量結合カップリングによる負の重畳電圧が加えられることを意味している。

【0179】

従って、ゲート信号SG801がHレベルになっている水平期間(1H)では、奇数(ODD)列の信号線Sへのソース出力は正極性に、偶数(EVEN)列の信号線Sへのソース出力は負極性にする必要がある。

【0180】

以下、順次ゲート線G800、ゲート線G799、…の行に注目して同様の考え方を適用すれば、各行の画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性を決定することができる。各画素PXには、このようにして決まった重畳電圧の極性を示してある。また、Cs極性制御信号FR波形の上にこのようにして決定したソース出力の極性を示す。

【0181】

また、負フレームでは、Cs信号SCsの極性が正フレームに対して正負逆転したものとなっている。従って、各画素電極PEに与えられる重畳電圧の極性とそれに対応して与えるべきソース出力の極性も正フレームに対して反転したものとなる。

【0182】

以上の図6A乃至図6Fの結果を総合すると、CCカラム反転駆動にて正常表示を行うために必要な条件は、「上下走査と下上走査にて、Cs極性制御信号FR(各画素に与える容量結合重畳電圧の極性を決める制御信号)が同じフレームでのソース出力の極性を比較したときに、

(5) M=2pの場合:下上走査では上下走査に比べて位相が同じであること

(6) M=2p+1の場合:下上走査では上下走査に比べて位相が反転していること

となる。

【0183】

上記(6)の場合においては上下走査と下上走査で位相を異ならせる必要がある。従って制御回路は、上下走査と下上走査において、FRが同じフレームでのソース出力の極性のH単位での位相を、異なるように出力するものであることが望ましい。

【0184】

また制御回路は、上下走査と下上走査において、FRが同じフレームでのソース出力の極性の位相関係を、(5)と(6)との2種類に設定可能で、その中から一つを選択できるものであることが望ましい。こうすると、(5)および(6)のうちの特定の1つのケースだけでなく、両方のケースに対応できるようになるため、制御回路としての汎用性が高くなる。表示領域の行数が異なる複数の機種に対して制御回路を共用化できるため、制御回路を含めた表示装置の開発コストや製造コストが低減されるというメリットが得られる。

【0185】

なお、第2実施形態における(3)M=4p+2の場合、あるいは第3実施形態における(1)M=2pの場合などは、正常表示を行うために必要な条件が、下上走査と上下走査にて、Cs極性制御信号FRが同じフレームでのソース出力の極性の位相が同じであることとなる。これらの共通点は、補助容量Cst配置が表示領域ACT内で上下反転に関して対称であること、すなわちより具体的にはk=1,2,…,M−1,Mに対して行kと行(M+1−k)とで補助容量Cst配置が上下逆であることである。

【0186】

表示領域ACTの補助容量Cst配置にこのような特徴を持たせておく場合に限り、制御回路CTRは、上下走査と下上走査において、Cs極性制御信号FRが同じフレームでのソース出力の極性のH単位での位相が同じになるように出力することで、正常表示が行える。

【0187】

なお第1実施形態乃至第3実施形態において、奇数(ODD)列と偶数(EVEN)列とで極性が反転する場合(1V反転)の例を説明したが、2列周期で反転する場合(nH2V−CCDI駆動)、3列周期で反転する場合(nH3V−CCDI駆動)等であっても適用可能である。

【0188】

なお上記実施形態では高速応答が可能なOCBモードの液晶表示装置について説明したが、他のモード(IPS、TN、FFS、VAなど)の液晶表示装置であっても適用可能である。

【0189】

本実施形態によれば、低消費電力を実現でき、かつ、上下反転表示を実現するとともに表示品位の良好な液晶表示装置および液晶表示装置の駆動方法を提供することができる。

【0190】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれるとともに、特許請求の範囲に記載された発明とその均等の範囲に含まれる。

【符号の説明】

【0191】

PX…画素、ACT…表示領域、CTR…制御回路、AR…アレイ基板、CT…対向基板、PE…画素電極、G…ゲート線、S…信号線、YD…Yドライバ、XD…Xドライバ、Cs…補助容量線、Cst…補助容量、H…水平期間、UD…走査方向制御信号、FR…Cs極性制御信号。

【特許請求の範囲】

【請求項1】

マトリクス状に配置された画素電極と、前記画素電極が配列した行に沿って延びたゲート線および補助容量線と、前記画素電極が配列した列に沿って延びた信号線と、前記ゲート線、前記信号線、および、前記補助容量線を駆動する駆動回路と、を備えたアレイ基板と、

前記アレイ基板と対向して配置された対向基板と、

前記アレイ基板と前記対向基板との間に挟持された液晶層と、

前記信号線が延びる方向と略平行な方向に並ぶ前記ゲート線を第1方向に順次駆動する第1走査と、前記第1方向と逆方向の第2方向に前記ゲート線を順次駆動する第2走査とを切替える走査方向制御信号と、前記補助容量線に供給する信号の極性を制御する極性制御信号と、を供給し、前記第1走査を行う場合と前記第2走査を行う場合との前記極性制御信号が同じであるフレーム期間において、前記信号線へ供給する信号の極性を水平期間単位で位相が異なるように前記駆動回路を制御可能である制御回路と、を備えた液晶表示装置。

【請求項2】

前記信号線から前記画素電極に供給される信号の極性パターンはnHmV反転であって、前記nおよび前記mは一以上の整数であって、前記nは前記画素電極が配列する行数以下である請求項1記載の液晶表示装置。

【請求項3】

画素電位へ重畳電圧を印加する補助容量の配置が前記ゲート線の延びる方向に対して対称である場合、前記制御回路は前記第1走査を行う場合と前記第2走査を行う場合との前記極性制御信号が同じであるフレーム期間において、前記信号線へ供給する信号の極性を水平期間単位で位相が同じになるように前記駆動回路を制御する請求項1又は請求項2記載の液晶表示装置。

【請求項4】

前記制御回路は、前記制御回路は前記第1走査を行う場合と前記第2走査を行う場合との前記極性制御信号が同じであるフレーム期間において、前記信号線へ供給する信号の極性の水平期間単位での位相関係を2種類以上から選択可能である請求項1乃至請求項3のいずれか1項記載の液晶表示装置。

【請求項5】

前記液晶層はOCBモードの液晶を含む請求項1乃至請求項4のいずれか1項記載の液晶表示装置。

【請求項6】

マトリクス状に配置された画素電極と、前記画素電極が配列した行に沿って延びたゲート線および補助容量線と、前記画素電極が配列した列に沿って延びた信号線と、前記ゲート線、前記信号線、および、前記補助容量線を駆動する駆動回路と、を備えたアレイ基板と、

前記アレイ基板と対向して配置された対向基板と、

前記アレイ基板と前記対向基板との間に挟持された液晶層と、

前記駆動回路を制御する制御回路と、を備えた液晶表示装置の駆動方法であって、

前記制御回路は、前記信号線が延びる方向と略平行な方向に並ぶ前記ゲート線を第1方向に順次駆動する第1走査と、前記第1方向と逆方向の第2方向に前記ゲート線を順次駆動する第2走査とを切替える走査方向制御信号と、前記補助容量線に供給する信号の極性を制御する極性制御信号と、を供給し、

前記第1走査を行う場合と前記第2走査を行う場合との前記極性制御信号が同じであるフレーム期間において、前記信号線へ供給する信号の極性の水平期間単位での位相を異ならせることができる、液晶表示装置の駆動方法。

【請求項7】

画素電位へ重畳電圧を印加する補助容量の配置が前記ゲート線の延びる方向に対して対称である場合、

前記制御回路は前記第1走査を行う場合と前記第2走査を行う場合との前記極性制御信号が同じであるフレーム期間において、前記信号線へ供給する信号の極性を水平期間単位で位相が同じになるように前記駆動回路を制御する請求項6記載の液晶表示装置の駆動方法。

【請求項1】

マトリクス状に配置された画素電極と、前記画素電極が配列した行に沿って延びたゲート線および補助容量線と、前記画素電極が配列した列に沿って延びた信号線と、前記ゲート線、前記信号線、および、前記補助容量線を駆動する駆動回路と、を備えたアレイ基板と、

前記アレイ基板と対向して配置された対向基板と、

前記アレイ基板と前記対向基板との間に挟持された液晶層と、

前記信号線が延びる方向と略平行な方向に並ぶ前記ゲート線を第1方向に順次駆動する第1走査と、前記第1方向と逆方向の第2方向に前記ゲート線を順次駆動する第2走査とを切替える走査方向制御信号と、前記補助容量線に供給する信号の極性を制御する極性制御信号と、を供給し、前記第1走査を行う場合と前記第2走査を行う場合との前記極性制御信号が同じであるフレーム期間において、前記信号線へ供給する信号の極性を水平期間単位で位相が異なるように前記駆動回路を制御可能である制御回路と、を備えた液晶表示装置。

【請求項2】

前記信号線から前記画素電極に供給される信号の極性パターンはnHmV反転であって、前記nおよび前記mは一以上の整数であって、前記nは前記画素電極が配列する行数以下である請求項1記載の液晶表示装置。

【請求項3】

画素電位へ重畳電圧を印加する補助容量の配置が前記ゲート線の延びる方向に対して対称である場合、前記制御回路は前記第1走査を行う場合と前記第2走査を行う場合との前記極性制御信号が同じであるフレーム期間において、前記信号線へ供給する信号の極性を水平期間単位で位相が同じになるように前記駆動回路を制御する請求項1又は請求項2記載の液晶表示装置。

【請求項4】

前記制御回路は、前記制御回路は前記第1走査を行う場合と前記第2走査を行う場合との前記極性制御信号が同じであるフレーム期間において、前記信号線へ供給する信号の極性の水平期間単位での位相関係を2種類以上から選択可能である請求項1乃至請求項3のいずれか1項記載の液晶表示装置。

【請求項5】

前記液晶層はOCBモードの液晶を含む請求項1乃至請求項4のいずれか1項記載の液晶表示装置。

【請求項6】

マトリクス状に配置された画素電極と、前記画素電極が配列した行に沿って延びたゲート線および補助容量線と、前記画素電極が配列した列に沿って延びた信号線と、前記ゲート線、前記信号線、および、前記補助容量線を駆動する駆動回路と、を備えたアレイ基板と、

前記アレイ基板と対向して配置された対向基板と、

前記アレイ基板と前記対向基板との間に挟持された液晶層と、

前記駆動回路を制御する制御回路と、を備えた液晶表示装置の駆動方法であって、

前記制御回路は、前記信号線が延びる方向と略平行な方向に並ぶ前記ゲート線を第1方向に順次駆動する第1走査と、前記第1方向と逆方向の第2方向に前記ゲート線を順次駆動する第2走査とを切替える走査方向制御信号と、前記補助容量線に供給する信号の極性を制御する極性制御信号と、を供給し、

前記第1走査を行う場合と前記第2走査を行う場合との前記極性制御信号が同じであるフレーム期間において、前記信号線へ供給する信号の極性の水平期間単位での位相を異ならせることができる、液晶表示装置の駆動方法。

【請求項7】

画素電位へ重畳電圧を印加する補助容量の配置が前記ゲート線の延びる方向に対して対称である場合、

前記制御回路は前記第1走査を行う場合と前記第2走査を行う場合との前記極性制御信号が同じであるフレーム期間において、前記信号線へ供給する信号の極性を水平期間単位で位相が同じになるように前記駆動回路を制御する請求項6記載の液晶表示装置の駆動方法。

【図1】

【図2】

【図3A】

【図3B】

【図4A】

【図4B】

【図4C】

【図4D】

【図5A】

【図5B】

【図5C】

【図5D】

【図5E】

【図5F】

【図5G】

【図5H】

【図5I】

【図5J】

【図6A】

【図6B】

【図6C】

【図6D】

【図6E】

【図6F】

【図2】

【図3A】

【図3B】

【図4A】

【図4B】

【図4C】

【図4D】

【図5A】

【図5B】

【図5C】

【図5D】

【図5E】

【図5F】

【図5G】

【図5H】

【図5I】

【図5J】

【図6A】

【図6B】

【図6C】

【図6D】

【図6E】

【図6F】

【公開番号】特開2013−101182(P2013−101182A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2011−243647(P2011−243647)

【出願日】平成23年11月7日(2011.11.7)

【出願人】(302020207)株式会社ジャパンディスプレイセントラル (2,170)

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願日】平成23年11月7日(2011.11.7)

【出願人】(302020207)株式会社ジャパンディスプレイセントラル (2,170)

【Fターム(参考)】

[ Back to top ]