液晶表示装置

【課題】ジグザグパターンを採用する場合に、製品開発・製造における迅速化および低コスト化に貢献し且つ違和感の無い画像表示を実現する。

【解決手段】液晶セルと、ゲートドライバと、ソースドライバと、ゲートドライバおよびソースドライバによる出力を制御することにより画像表示を実現させる制御部とを備え、第1方向を向く画素列を構成する各画素が、所定画素数毎に、当該画素列を挟む両側のソースラインへ交互に接続する配線パターンを有する液晶表示装置であって、液晶セルにおけるソースラインの総数がソースドライバの出力ラインの総数よりも1本多く、液晶セルにおける最外側のソースラインは近隣のソースラインが接続するソースドライバの出力ラインに対して接続され、上記制御部は上記最も外側のソースラインおよび上記近隣のソースラインが接続する画素列を含む領域に黒表示を実行させる。

【解決手段】液晶セルと、ゲートドライバと、ソースドライバと、ゲートドライバおよびソースドライバによる出力を制御することにより画像表示を実現させる制御部とを備え、第1方向を向く画素列を構成する各画素が、所定画素数毎に、当該画素列を挟む両側のソースラインへ交互に接続する配線パターンを有する液晶表示装置であって、液晶セルにおけるソースラインの総数がソースドライバの出力ラインの総数よりも1本多く、液晶セルにおける最外側のソースラインは近隣のソースラインが接続するソースドライバの出力ラインに対して接続され、上記制御部は上記最も外側のソースラインおよび上記近隣のソースラインが接続する画素列を含む領域に黒表示を実行させる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶表示装置に関する。

【背景技術】

【0002】

画面内の画素列を構成する各画素のソース電極に対して、1本のソースラインから駆動電圧を供給するのではなく、当該画素列を挟む両側のソースラインから交互に、当該画素列を構成する各画素へ駆動電圧を供給する配線パターン(以下では、適宜“ジグザグパターン”と呼ぶ。)を採用した液晶セルが存在する。

【0003】

例として、フルHD(Full High Definition)に対応した表示パネルであって、1920×1080個の画素を有し(各画素は赤(R)、緑(G)、青(B)に対応した3個のサブピクセルを有する)、5760(1920×3)本のデータライン(ソースライン)が垂直表示線として必要とされ、さらに追加の5761本目のデータラインを有することで、フレーム反転表示パネルを実現する構成が知られている(特許文献1参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009‐122679号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

液晶セルのソースラインに対しては、各画素が備えるTFT(Thin Film Transistor)等のアクティブ素子のソース電極を駆動するための電圧を供給するソースドライバが接続される。ここで、一つあたりのソースドライバが備える出力ライン(出力チャンネル)数は一定数(例えば720本)であり、このようなソースドライバを液晶表示装置において複数枚(例えば8枚)搭載することで、所定数(例えば5760本)のソースラインを備える液晶セルを駆動させることができる。しかしながら、上述したようなジグザグパターンを採用する液晶セルにおいては、ジグザグパターンを採用しない場合と比較して、ソースラインが多くなる。そのため、これまで液晶表示装置に搭載されていたソースドライバの出力ラインの総数では、当該ジグザグパターンを採用する液晶セルにおけるソースライン数に満たない。

【0006】

このような場合、複数枚あるソースドライバのうち一枚については、上記一定数の他に、上記一定数よりも多い数のソースラインにも対応できるように出力チャンネル数を切替可能な機能を持たせることで、対処しなければならなかった。しかし、製品に搭載する一枚のソースドライバについてそのような切替機能を持たせるには、多くの開発期間と費用を要し、製品開発・製造における迅速化および低コスト化という要求に応え難い。

【0007】

本発明は上記課題を解決するためになされたものであり、ジグザグパターンを採用する場合に、製品開発・製造における迅速化および低コスト化に貢献し、かつユーザにとって違和感の無い画像表示を実現することが可能な液晶表示装置を提供する。

【課題を解決するための手段】

【0008】

本発明の態様の一つは、第1方向を向いて当該第1方向に直交する第2方向に沿って並ぶ複数のソースラインと、第2方向を向いて第1方向に沿って並ぶ複数のゲートラインと、第1方向および第2方向に配列され各々がソースラインおよびゲートラインに接続する複数の画素とを有する液晶セルと、一定数の出力ラインを有し、各出力ラインをゲートラインと接続して各画素に電圧を出力するゲートドライバと、一定数の出力ラインを有し、各出力ラインをソースラインと接続して各画素に電圧を出力するソースドライバと、ゲートドライバおよびソースドライバによる出力を制御することにより画像表示を実現させる制御部とを備え、第1方向を向く画素列を構成する各画素が、所定画素数毎に、当該画素列を挟む両側のソースラインへ交互に接続する配線パターン(ジグザグパターンの一種)を有する液晶表示装置であって、液晶セルにおけるソースラインの総数が、ソースドライバの出力ラインの総数よりも1本多く構成されており、液晶セルにおける最も外側のソースラインは、近隣のソースラインが接続するソースドライバの出力ラインに対して接続され、上記制御部は、上記最も外側のソースラインおよび上記近隣のソースラインが接続する画素列を含む領域に黒表示を実行させる構成としてある。

【0009】

当該構成によれば、ソースドライバの出力ライン総数を超える1本のソースライン(最も外側のソースライン)については、敢えて独自にコントロールしようとするのではなく、近隣のソースラインとともに共通の出力ラインに接続させ、当該近隣のソースラインに与えられる電位と同じ電位に保つ。そして、上記最も外側のソースラインおよび上記近隣のソースラインが接続する画素列を含む領域を黒表示することで、ユーザにとっては違和感の無い(全ての画素列を非黒表示した場合と比べて殆ど違いが判らない)画像を提供することができる。

【図面の簡単な説明】

【0010】

【図1】液晶表示装置の概略構成を示すブロック図である。

【図2】液晶セルにおける画素や配線パターンの配置態様を簡易的に示す図である。

【図3】最も外側のソースラインに関する結線態様を示す図である。

【図4】最端画素領域が黒表示される様子を説明する図である。

【発明を実施するための形態】

【0011】

本発明の他の実施形態として、上記画素列は、各々が複数の要素色のいずれかの表示に対応しており、上記黒表示は、上記最も外側のソースラインが接続する画素列を含み、対応する要素色が異なる複数の画素列が連続して形成された単位領域において実行され、上記最も外側のソースラインは、上記黒表示が実行される単位領域を構成する画素列のいずれかに接続する他のソースラインが接続するソースドライバの出力ラインに、接続される構成としてもよい。

また、本発明の他の実施形態として、上記液晶セルの画素は、各々がアクティブ素子のソース電極をソースラインに接続し且つアクティブ素子のゲート電極をゲートラインに接続し、各々がRGBの要素色のいずれかの表示に対応したサブピクセルであり、上記ゲートドライバは、各出力ラインをゲートラインと接続して各サブピクセルのアクティブ素子のゲート電極に電圧を出力し、上記ソースドライバは、各出力ラインをソースラインと接続して各サブピクセルのアクティブ素子のソース電極に電圧を出力し、第1方向を向きRGBのいずれか一つの要素色に対応したサブピクセルの列を構成する各サブピクセルが1つずつ、当該列を挟む両側のソースラインへ交互に接続する配線パターンを有し、液晶セルにおける最も外側のソースラインは、隣のソースラインが接続するソースドライバの出力ラインに対して接続され、上記制御部は、上記最も外側のソースラインおよび上記隣のソースラインが接続するサブピクセルの列と、当該列と第2方向において連続し且つ当該列が対応する要素色を除くRGBにおける2色に対応するサブピクセルの2列からなる領域に、黒表示を実行させる構成としてもよい。

【0012】

以下、図面を参照しながら本発明の実施形態を説明する。

図1は、本実施形態にかかる液晶表示装置10の概略構成をブロック図により示している。液晶表示装置10は、放送信号の受信機能(チューナ)を備えたテレビジョンであってもよいし、それ自体では受信機能を持たない液晶モニタであってもよい。あるいは、液晶表示装置10は、ある電気製品の一部として組み込まれたものであってもよい。液晶表示装置10は、システムオンチップ(SoC)11、タイミングコントローラ(T‐CON)12、ソースドライバ13、ゲートドライバ14、液晶セル15等を備える。

【0013】

SoC11は、液晶表示装置10全体を制御するためのワンチップ化された集積回路であり、CPUや各種メモリー(ROMやRAM等)を搭載する。SoC11は制御部の一例に該当する。SoC11は、不図示のチューナや外部入力端子を介して放送信号や映像信号を入力し、放送信号に対してデコードを行い映像信号を抽出したり、入力あるいは抽出した映像信号に対して所定の補正や画質調整を実行し、映像信号をT‐CON12へ出力する。T‐CON12は、入力した映像信号をフレームメモリ(図示せず)に一時的に保存しつつ、当該保存した信号に基づいて所定のタイミングでソースドライバ13およびゲートドライバ14を制御する。T‐CON12も、制御部の一例に該当する。SoC11からT‐CON12への信号の伝達は、例えば、LVDS(Low Voltage Differencial Signaling)の通信規格によりなされ、T‐CON12からソースドライバ13、ゲートドライバ14への信号の伝達は、例えば、Mini‐LVDS(Low Voltage Differencial Signaling)の通信規格によりなされる。

【0014】

液晶セル15は、一般的に知られているように、2枚のガラスの間に液晶を挟み、液晶を挟んで対向する電極(画素電極‐共通電極)間に電圧を印加して、背面に配置されたバックライトからの光の透過率を変え、その光をRGBのカラーフィルタに通すことにより色の表現を行うアクティブマトリクス方式の装置である。一方のガラス上には、ソースラインとゲートライン(走査線)を格子状に配置するとともに、画素毎にアクティブ素子としてのTFTを搭載している。

【0015】

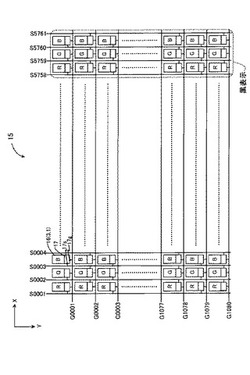

図2は、液晶セル15における画素や配線パターンの配置態様を簡易的に示した図である。液晶セル15は、一例として、互いに直交するX,Y方向で定義される平面において、Y方向を向いてX方向に並ぶ複数のソースラインS0001〜S5761(計5761本)と、X方向を向いてY方向に並ぶ複数のゲートラインG0001〜G1080(計1080本)とを備える。Y方向は第1方向に該当し、X方向は第2方向に該当する。また、液晶セル15は、5760×1080(X方向×Y方向)個の画素を有し、各画素は複数の要素色(ここではRGB)のいずれか一色の表示に対応している。なお、要素色は、RGBの3色に限られず、例えばイエロー(Y)を加えたRGBYの4色であってもよい。以下では、このような画素をサブピクセル(副画素)と呼ぶ。また、X方向に並ぶ要素色数分のサブピクセル(要素色がRGBであれば、Rのサブピクセル、Gのサブピクセル、Bのサブピクセル)を併せた領域を一つの画素と呼んでもよい。

【0016】

一つ一つのサブピクセルにおいては、TFT17および画素電極16が配設されている。TFT17は、ドレイン電極を介して画素電極16と接続し、ゲート電極17gを介していずれかのゲートラインに接続し、ソース電極17sを介していずれかのソースラインと接続している。液晶表示装置10は、図1に示すように複数枚のゲートドライバ14を備えており、各ゲートドライバ14は、一定数の出力ラインを有する。各ゲートドライバ14は、出力ラインと液晶セル15側のゲートラインG0001〜G1080とを一対一で接続している。また、液晶表示装置10は、図1に示すように複数枚のソースドライバ13を備えており、各ソースドライバ13は、一定数の出力ライン13aを有する。各ソースドライバ13は、出力ライン13aと液晶セル15側のソースラインS0001〜S5760とを一対一で接続している。ここで、液晶表示装置10においては、個々のソースドライバ13は720本の出力ライン13aを有しており、計8枚のソースドライバ13(出力ライン総数が720×8=5760)を用いて、液晶セル15側のソースラインS0001〜S5760と接続している。

【0017】

各ゲートドライバ14は、T‐CON12によって制御され、各サブピクセルのTFT17をオンさせるために、ゲートラインG0001〜G1080の順にパルス状の電圧を各ゲートラインに出力する。各ソースドライバ13は、T‐CON12からサブピクセル毎の色データ(6ビットのデジタルデータ)を受け取り、オン状態となったTFT17を通じて画素電極16に供給するための印加電圧を生成し、各ソースラインに出力する。この印加電圧のレベルは、上記色データの階調値(64階調)に応じた値となり、各サブピクセルにおける光の透過率は、この印加電圧に応じて変わる。このような構成により液晶セル15の各サブピクセルが駆動されて、液晶表示装置10による画像表示が実現される。むろん上述した構成以外にも、液晶表示装置10は、電源回路や音声回路等、液晶テレビジョンや液晶モニタとして備え得る、公知の構成を適宜備えることができる。

【0018】

図2から判るように、液晶セル15は、Y方向を向く画素列(サブピクセルの列)を構成する各画素(サブピクセル)が、所定数(1以上の整数)毎に、当該列を挟む両側のソースラインへ交互に接続する配線パターン(ジグザグパターン)を採用している。ここで、(X,Y)平面における画素電極16の座標位置が(3,1)で特定されるBのサブピクセル(図2参照)を含む、Y方向を向くBのサブピクセルの列を例に説明をする。当該Bのサブピクセルの列において一番上の座標位置(3,1)のサブピクセルのTFT17のソース電極17sは、当該列を挟むソースラインS0003,S0004のうちソースラインS0003に接続し、上から2番目の座標位置(3,2)のサブピクセルのTFT17のソース電極はソースラインS0004に接続し、上から3番目の座標位置(3,3)のサブピクセルのTFT17のソース電極はソースラインS0003に接続し…、というように、サブピクセルの位置がY方向において一つ変化する毎に、接続先のソースラインが左右で交互に変る。このようなジグザグパターンによるサブピクセルとソースラインとの接続態様は、Y方向を向くサブピクセルの列の全てにおいて採用されている。

【0019】

上記ジグザグパターンを採用した結果として、液晶セル15におけるソースラインの数は、液晶セル15が有するX方向のサブピクセル数(5760)よりも1つ多い5761本となる。また、液晶セル15におけるソースラインの数は、上述した8枚のソースドライバ13による出力ライン13aの総数(5760)よりも1つ多くなる。そのため、上述した8枚のソースドライバ13と液晶セル15の各ソースラインとを単純に接続しただけでは、液晶セル15における最も外側(X方向の両端のうちの所定の一方の側)のソースラインS5761が余ってしまう(接続する出力ライン13aが存在しない)。このような状況において本実施形態は、図3(および図1)に示すように、ソースラインS5761は、隣のソースラインS5760が接続するソースドライバ13の出力ライン13aに対して接続される。ソースラインS5760が接続するソースドライバ13とは、ソースラインS5041〜S5760と接続する最も外側のソースドライバ13‐8であり(図1参照)、このソースドライバ13‐8が有する最も外側の出力ライン13a(ソースラインS5760が接続する出力ライン13a)に、ソースラインS5761を結線Lにより接続(ショート)する。

【0020】

このように結線LにてソースラインS5760およびS5761を同じ出力ライン13aに接続した状況において、本実施形態では、液晶セル15への画像表示時に、ソースラインS5760およびS5761が接続するサブピクセルの列(液晶セル15において最も外側のBのサブピクセルの列)を含み、対応する要素色が異なる複数のサブピクセルの列が連続して形成された単位領域に黒表示を実行させる。より具体的には、上記最も外側のBのサブピクセルの列と、当該サブピクセルの列とX方向において連続し且つ当該サブピクセルの列が対応する色(B)を除くRGBにおける2色(R,G)に対応するサブピクセルの2列(上記最も外側のBのサブピクセルの列の隣に位置するY方向を向くGのサブピクセルの列と、このGのサブピクセルの列の隣に位置するY方向を向くRのサブピクセルの列)からなる単位領域(便宜上、最端画素領域と呼ぶ。)に、黒表示を実行させる。

【0021】

具体的には、SoC11は、T‐CON12へ出力する映像信号に対して、最端画素領域の色を強制的に黒に変換する処理を実行した上で、映像信号を出力する。つまり、SoC11が、黒表示を実現させるための制御部として機能する。あるいは、T‐CON12がSoC11から入力した映像信号に対して、最端画素領域の色を強制的に黒に変換して映像信号を加工し、当該加工後の映像に基づいて ソースドライバ13およびゲートドライバ14を制御する。つまり、T‐CON12が、黒表示を実現させるための制御部として機能するとしてもよい。

【0022】

図4は、最端画素領域が黒表示される様子を説明する図である。図4において鎖線で囲った範囲が最端画素領域である。上記制御部による処理の結果、ソースドライバ13(13‐8)は、その一部の出力ライン13aを介して、最端画素領域を構成するサブピクセルに対し最小階調(黒)を実現するための印加電圧を生成して出力する。その結果、最端画素領域を構成する全てのサブピクセルにおいてバックライトの光を透過しない状態、すなわち黒表示が実現される。なお、ソースラインS5761は本来対応する出力ライン13aがソースドライバ13(13‐8)側に無いが、上述したように結線Lにて同じ出力ライン13aにソースラインS5760およびS5761が並列接続されているため、ソースラインS5761に接続された各サブピクセルは、ソースラインS5760に接続された各サブピクセルと同電位となり、共に無透過となる。最端画素領域は、液晶セル15のX方向における最縁の、Y方向を向くサブピクセル列3つ分に過ぎない非常に細い領域であるため、この領域が黒表示されていても、ユーザとしては、この領域が黒表示されていない場合との違いを殆ど認識しない。つまり、ユーザに違和感を与えることは無い。むろん、最端画素領域以外の液晶セル15の表示領域においては、映像信号に基づく通常の表示を行なう。

【0023】

なお、ソースラインS5761が結線Lにより接続される先は必ずしも隣のソースラインS5760が接続するソースドライバ13の出力ライン13aに限る必要はなく、“近隣”のソースラインが接続するソースドライバ13の出力ライン13aであってもよい。ただしその場合でも、ソースラインS5761は、上記黒表示が実行される単位領域(最端画素領域)を構成するサブピクセルの列のいずれかに接続する他のソースライン(ソースラインS5758,S5759,S5760)のいずれか一つが接続するソースドライバ13(13‐8)の出力ライン13aに、結線Lにより接続される。つまり、ソースラインS5761の近隣のソースラインと言った場合、ソースラインS5758,S5759,S5760が含まれる。ただし、ソースラインS5758は最端画素領域ではないサブピクセルの列とも接続しているため、より好ましくは、ソースラインS5761の近隣のソースラインとは、ソースラインS5759,S5760を意味する。

【0024】

このように本実施形態によれば、ジグザグパターンを採用した結果、ソースドライバ13の出力ライン13aの総数よりも液晶セル15におけるソースラインが1本多い構成において、最も外側のソースラインS5761については、敢えて独自にコントロールしようとするのではなく、近隣のソースラインとともに共通の出力ライン13aに接続させ、上記最も外側のソースラインS5761および上記近隣のソースラインが接続するサブピクセル列を含む領域を黒表示する。そのため、異なるソースライン数にも対応できるように出力チャンネル数を切替可能なソースドライバをわざわざ開発して一枚搭載する必要もなく、迅速に且つより低いコストにて、ユーザにとって違和感の無い画像表示を実現する液晶表示装置10を製造し提供することが可能となった。

【符号の説明】

【0025】

10…液晶表示装置、11…SoC、12…T‐CON、13,13‐8…ソースドライバ、13a…出力ライン、14…ゲートドライバ、15…液晶セル、16…画素電極、17…TFT、17s…ソース電極、17g…ゲート電極

【技術分野】

【0001】

本発明は、液晶表示装置に関する。

【背景技術】

【0002】

画面内の画素列を構成する各画素のソース電極に対して、1本のソースラインから駆動電圧を供給するのではなく、当該画素列を挟む両側のソースラインから交互に、当該画素列を構成する各画素へ駆動電圧を供給する配線パターン(以下では、適宜“ジグザグパターン”と呼ぶ。)を採用した液晶セルが存在する。

【0003】

例として、フルHD(Full High Definition)に対応した表示パネルであって、1920×1080個の画素を有し(各画素は赤(R)、緑(G)、青(B)に対応した3個のサブピクセルを有する)、5760(1920×3)本のデータライン(ソースライン)が垂直表示線として必要とされ、さらに追加の5761本目のデータラインを有することで、フレーム反転表示パネルを実現する構成が知られている(特許文献1参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2009‐122679号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

液晶セルのソースラインに対しては、各画素が備えるTFT(Thin Film Transistor)等のアクティブ素子のソース電極を駆動するための電圧を供給するソースドライバが接続される。ここで、一つあたりのソースドライバが備える出力ライン(出力チャンネル)数は一定数(例えば720本)であり、このようなソースドライバを液晶表示装置において複数枚(例えば8枚)搭載することで、所定数(例えば5760本)のソースラインを備える液晶セルを駆動させることができる。しかしながら、上述したようなジグザグパターンを採用する液晶セルにおいては、ジグザグパターンを採用しない場合と比較して、ソースラインが多くなる。そのため、これまで液晶表示装置に搭載されていたソースドライバの出力ラインの総数では、当該ジグザグパターンを採用する液晶セルにおけるソースライン数に満たない。

【0006】

このような場合、複数枚あるソースドライバのうち一枚については、上記一定数の他に、上記一定数よりも多い数のソースラインにも対応できるように出力チャンネル数を切替可能な機能を持たせることで、対処しなければならなかった。しかし、製品に搭載する一枚のソースドライバについてそのような切替機能を持たせるには、多くの開発期間と費用を要し、製品開発・製造における迅速化および低コスト化という要求に応え難い。

【0007】

本発明は上記課題を解決するためになされたものであり、ジグザグパターンを採用する場合に、製品開発・製造における迅速化および低コスト化に貢献し、かつユーザにとって違和感の無い画像表示を実現することが可能な液晶表示装置を提供する。

【課題を解決するための手段】

【0008】

本発明の態様の一つは、第1方向を向いて当該第1方向に直交する第2方向に沿って並ぶ複数のソースラインと、第2方向を向いて第1方向に沿って並ぶ複数のゲートラインと、第1方向および第2方向に配列され各々がソースラインおよびゲートラインに接続する複数の画素とを有する液晶セルと、一定数の出力ラインを有し、各出力ラインをゲートラインと接続して各画素に電圧を出力するゲートドライバと、一定数の出力ラインを有し、各出力ラインをソースラインと接続して各画素に電圧を出力するソースドライバと、ゲートドライバおよびソースドライバによる出力を制御することにより画像表示を実現させる制御部とを備え、第1方向を向く画素列を構成する各画素が、所定画素数毎に、当該画素列を挟む両側のソースラインへ交互に接続する配線パターン(ジグザグパターンの一種)を有する液晶表示装置であって、液晶セルにおけるソースラインの総数が、ソースドライバの出力ラインの総数よりも1本多く構成されており、液晶セルにおける最も外側のソースラインは、近隣のソースラインが接続するソースドライバの出力ラインに対して接続され、上記制御部は、上記最も外側のソースラインおよび上記近隣のソースラインが接続する画素列を含む領域に黒表示を実行させる構成としてある。

【0009】

当該構成によれば、ソースドライバの出力ライン総数を超える1本のソースライン(最も外側のソースライン)については、敢えて独自にコントロールしようとするのではなく、近隣のソースラインとともに共通の出力ラインに接続させ、当該近隣のソースラインに与えられる電位と同じ電位に保つ。そして、上記最も外側のソースラインおよび上記近隣のソースラインが接続する画素列を含む領域を黒表示することで、ユーザにとっては違和感の無い(全ての画素列を非黒表示した場合と比べて殆ど違いが判らない)画像を提供することができる。

【図面の簡単な説明】

【0010】

【図1】液晶表示装置の概略構成を示すブロック図である。

【図2】液晶セルにおける画素や配線パターンの配置態様を簡易的に示す図である。

【図3】最も外側のソースラインに関する結線態様を示す図である。

【図4】最端画素領域が黒表示される様子を説明する図である。

【発明を実施するための形態】

【0011】

本発明の他の実施形態として、上記画素列は、各々が複数の要素色のいずれかの表示に対応しており、上記黒表示は、上記最も外側のソースラインが接続する画素列を含み、対応する要素色が異なる複数の画素列が連続して形成された単位領域において実行され、上記最も外側のソースラインは、上記黒表示が実行される単位領域を構成する画素列のいずれかに接続する他のソースラインが接続するソースドライバの出力ラインに、接続される構成としてもよい。

また、本発明の他の実施形態として、上記液晶セルの画素は、各々がアクティブ素子のソース電極をソースラインに接続し且つアクティブ素子のゲート電極をゲートラインに接続し、各々がRGBの要素色のいずれかの表示に対応したサブピクセルであり、上記ゲートドライバは、各出力ラインをゲートラインと接続して各サブピクセルのアクティブ素子のゲート電極に電圧を出力し、上記ソースドライバは、各出力ラインをソースラインと接続して各サブピクセルのアクティブ素子のソース電極に電圧を出力し、第1方向を向きRGBのいずれか一つの要素色に対応したサブピクセルの列を構成する各サブピクセルが1つずつ、当該列を挟む両側のソースラインへ交互に接続する配線パターンを有し、液晶セルにおける最も外側のソースラインは、隣のソースラインが接続するソースドライバの出力ラインに対して接続され、上記制御部は、上記最も外側のソースラインおよび上記隣のソースラインが接続するサブピクセルの列と、当該列と第2方向において連続し且つ当該列が対応する要素色を除くRGBにおける2色に対応するサブピクセルの2列からなる領域に、黒表示を実行させる構成としてもよい。

【0012】

以下、図面を参照しながら本発明の実施形態を説明する。

図1は、本実施形態にかかる液晶表示装置10の概略構成をブロック図により示している。液晶表示装置10は、放送信号の受信機能(チューナ)を備えたテレビジョンであってもよいし、それ自体では受信機能を持たない液晶モニタであってもよい。あるいは、液晶表示装置10は、ある電気製品の一部として組み込まれたものであってもよい。液晶表示装置10は、システムオンチップ(SoC)11、タイミングコントローラ(T‐CON)12、ソースドライバ13、ゲートドライバ14、液晶セル15等を備える。

【0013】

SoC11は、液晶表示装置10全体を制御するためのワンチップ化された集積回路であり、CPUや各種メモリー(ROMやRAM等)を搭載する。SoC11は制御部の一例に該当する。SoC11は、不図示のチューナや外部入力端子を介して放送信号や映像信号を入力し、放送信号に対してデコードを行い映像信号を抽出したり、入力あるいは抽出した映像信号に対して所定の補正や画質調整を実行し、映像信号をT‐CON12へ出力する。T‐CON12は、入力した映像信号をフレームメモリ(図示せず)に一時的に保存しつつ、当該保存した信号に基づいて所定のタイミングでソースドライバ13およびゲートドライバ14を制御する。T‐CON12も、制御部の一例に該当する。SoC11からT‐CON12への信号の伝達は、例えば、LVDS(Low Voltage Differencial Signaling)の通信規格によりなされ、T‐CON12からソースドライバ13、ゲートドライバ14への信号の伝達は、例えば、Mini‐LVDS(Low Voltage Differencial Signaling)の通信規格によりなされる。

【0014】

液晶セル15は、一般的に知られているように、2枚のガラスの間に液晶を挟み、液晶を挟んで対向する電極(画素電極‐共通電極)間に電圧を印加して、背面に配置されたバックライトからの光の透過率を変え、その光をRGBのカラーフィルタに通すことにより色の表現を行うアクティブマトリクス方式の装置である。一方のガラス上には、ソースラインとゲートライン(走査線)を格子状に配置するとともに、画素毎にアクティブ素子としてのTFTを搭載している。

【0015】

図2は、液晶セル15における画素や配線パターンの配置態様を簡易的に示した図である。液晶セル15は、一例として、互いに直交するX,Y方向で定義される平面において、Y方向を向いてX方向に並ぶ複数のソースラインS0001〜S5761(計5761本)と、X方向を向いてY方向に並ぶ複数のゲートラインG0001〜G1080(計1080本)とを備える。Y方向は第1方向に該当し、X方向は第2方向に該当する。また、液晶セル15は、5760×1080(X方向×Y方向)個の画素を有し、各画素は複数の要素色(ここではRGB)のいずれか一色の表示に対応している。なお、要素色は、RGBの3色に限られず、例えばイエロー(Y)を加えたRGBYの4色であってもよい。以下では、このような画素をサブピクセル(副画素)と呼ぶ。また、X方向に並ぶ要素色数分のサブピクセル(要素色がRGBであれば、Rのサブピクセル、Gのサブピクセル、Bのサブピクセル)を併せた領域を一つの画素と呼んでもよい。

【0016】

一つ一つのサブピクセルにおいては、TFT17および画素電極16が配設されている。TFT17は、ドレイン電極を介して画素電極16と接続し、ゲート電極17gを介していずれかのゲートラインに接続し、ソース電極17sを介していずれかのソースラインと接続している。液晶表示装置10は、図1に示すように複数枚のゲートドライバ14を備えており、各ゲートドライバ14は、一定数の出力ラインを有する。各ゲートドライバ14は、出力ラインと液晶セル15側のゲートラインG0001〜G1080とを一対一で接続している。また、液晶表示装置10は、図1に示すように複数枚のソースドライバ13を備えており、各ソースドライバ13は、一定数の出力ライン13aを有する。各ソースドライバ13は、出力ライン13aと液晶セル15側のソースラインS0001〜S5760とを一対一で接続している。ここで、液晶表示装置10においては、個々のソースドライバ13は720本の出力ライン13aを有しており、計8枚のソースドライバ13(出力ライン総数が720×8=5760)を用いて、液晶セル15側のソースラインS0001〜S5760と接続している。

【0017】

各ゲートドライバ14は、T‐CON12によって制御され、各サブピクセルのTFT17をオンさせるために、ゲートラインG0001〜G1080の順にパルス状の電圧を各ゲートラインに出力する。各ソースドライバ13は、T‐CON12からサブピクセル毎の色データ(6ビットのデジタルデータ)を受け取り、オン状態となったTFT17を通じて画素電極16に供給するための印加電圧を生成し、各ソースラインに出力する。この印加電圧のレベルは、上記色データの階調値(64階調)に応じた値となり、各サブピクセルにおける光の透過率は、この印加電圧に応じて変わる。このような構成により液晶セル15の各サブピクセルが駆動されて、液晶表示装置10による画像表示が実現される。むろん上述した構成以外にも、液晶表示装置10は、電源回路や音声回路等、液晶テレビジョンや液晶モニタとして備え得る、公知の構成を適宜備えることができる。

【0018】

図2から判るように、液晶セル15は、Y方向を向く画素列(サブピクセルの列)を構成する各画素(サブピクセル)が、所定数(1以上の整数)毎に、当該列を挟む両側のソースラインへ交互に接続する配線パターン(ジグザグパターン)を採用している。ここで、(X,Y)平面における画素電極16の座標位置が(3,1)で特定されるBのサブピクセル(図2参照)を含む、Y方向を向くBのサブピクセルの列を例に説明をする。当該Bのサブピクセルの列において一番上の座標位置(3,1)のサブピクセルのTFT17のソース電極17sは、当該列を挟むソースラインS0003,S0004のうちソースラインS0003に接続し、上から2番目の座標位置(3,2)のサブピクセルのTFT17のソース電極はソースラインS0004に接続し、上から3番目の座標位置(3,3)のサブピクセルのTFT17のソース電極はソースラインS0003に接続し…、というように、サブピクセルの位置がY方向において一つ変化する毎に、接続先のソースラインが左右で交互に変る。このようなジグザグパターンによるサブピクセルとソースラインとの接続態様は、Y方向を向くサブピクセルの列の全てにおいて採用されている。

【0019】

上記ジグザグパターンを採用した結果として、液晶セル15におけるソースラインの数は、液晶セル15が有するX方向のサブピクセル数(5760)よりも1つ多い5761本となる。また、液晶セル15におけるソースラインの数は、上述した8枚のソースドライバ13による出力ライン13aの総数(5760)よりも1つ多くなる。そのため、上述した8枚のソースドライバ13と液晶セル15の各ソースラインとを単純に接続しただけでは、液晶セル15における最も外側(X方向の両端のうちの所定の一方の側)のソースラインS5761が余ってしまう(接続する出力ライン13aが存在しない)。このような状況において本実施形態は、図3(および図1)に示すように、ソースラインS5761は、隣のソースラインS5760が接続するソースドライバ13の出力ライン13aに対して接続される。ソースラインS5760が接続するソースドライバ13とは、ソースラインS5041〜S5760と接続する最も外側のソースドライバ13‐8であり(図1参照)、このソースドライバ13‐8が有する最も外側の出力ライン13a(ソースラインS5760が接続する出力ライン13a)に、ソースラインS5761を結線Lにより接続(ショート)する。

【0020】

このように結線LにてソースラインS5760およびS5761を同じ出力ライン13aに接続した状況において、本実施形態では、液晶セル15への画像表示時に、ソースラインS5760およびS5761が接続するサブピクセルの列(液晶セル15において最も外側のBのサブピクセルの列)を含み、対応する要素色が異なる複数のサブピクセルの列が連続して形成された単位領域に黒表示を実行させる。より具体的には、上記最も外側のBのサブピクセルの列と、当該サブピクセルの列とX方向において連続し且つ当該サブピクセルの列が対応する色(B)を除くRGBにおける2色(R,G)に対応するサブピクセルの2列(上記最も外側のBのサブピクセルの列の隣に位置するY方向を向くGのサブピクセルの列と、このGのサブピクセルの列の隣に位置するY方向を向くRのサブピクセルの列)からなる単位領域(便宜上、最端画素領域と呼ぶ。)に、黒表示を実行させる。

【0021】

具体的には、SoC11は、T‐CON12へ出力する映像信号に対して、最端画素領域の色を強制的に黒に変換する処理を実行した上で、映像信号を出力する。つまり、SoC11が、黒表示を実現させるための制御部として機能する。あるいは、T‐CON12がSoC11から入力した映像信号に対して、最端画素領域の色を強制的に黒に変換して映像信号を加工し、当該加工後の映像に基づいて ソースドライバ13およびゲートドライバ14を制御する。つまり、T‐CON12が、黒表示を実現させるための制御部として機能するとしてもよい。

【0022】

図4は、最端画素領域が黒表示される様子を説明する図である。図4において鎖線で囲った範囲が最端画素領域である。上記制御部による処理の結果、ソースドライバ13(13‐8)は、その一部の出力ライン13aを介して、最端画素領域を構成するサブピクセルに対し最小階調(黒)を実現するための印加電圧を生成して出力する。その結果、最端画素領域を構成する全てのサブピクセルにおいてバックライトの光を透過しない状態、すなわち黒表示が実現される。なお、ソースラインS5761は本来対応する出力ライン13aがソースドライバ13(13‐8)側に無いが、上述したように結線Lにて同じ出力ライン13aにソースラインS5760およびS5761が並列接続されているため、ソースラインS5761に接続された各サブピクセルは、ソースラインS5760に接続された各サブピクセルと同電位となり、共に無透過となる。最端画素領域は、液晶セル15のX方向における最縁の、Y方向を向くサブピクセル列3つ分に過ぎない非常に細い領域であるため、この領域が黒表示されていても、ユーザとしては、この領域が黒表示されていない場合との違いを殆ど認識しない。つまり、ユーザに違和感を与えることは無い。むろん、最端画素領域以外の液晶セル15の表示領域においては、映像信号に基づく通常の表示を行なう。

【0023】

なお、ソースラインS5761が結線Lにより接続される先は必ずしも隣のソースラインS5760が接続するソースドライバ13の出力ライン13aに限る必要はなく、“近隣”のソースラインが接続するソースドライバ13の出力ライン13aであってもよい。ただしその場合でも、ソースラインS5761は、上記黒表示が実行される単位領域(最端画素領域)を構成するサブピクセルの列のいずれかに接続する他のソースライン(ソースラインS5758,S5759,S5760)のいずれか一つが接続するソースドライバ13(13‐8)の出力ライン13aに、結線Lにより接続される。つまり、ソースラインS5761の近隣のソースラインと言った場合、ソースラインS5758,S5759,S5760が含まれる。ただし、ソースラインS5758は最端画素領域ではないサブピクセルの列とも接続しているため、より好ましくは、ソースラインS5761の近隣のソースラインとは、ソースラインS5759,S5760を意味する。

【0024】

このように本実施形態によれば、ジグザグパターンを採用した結果、ソースドライバ13の出力ライン13aの総数よりも液晶セル15におけるソースラインが1本多い構成において、最も外側のソースラインS5761については、敢えて独自にコントロールしようとするのではなく、近隣のソースラインとともに共通の出力ライン13aに接続させ、上記最も外側のソースラインS5761および上記近隣のソースラインが接続するサブピクセル列を含む領域を黒表示する。そのため、異なるソースライン数にも対応できるように出力チャンネル数を切替可能なソースドライバをわざわざ開発して一枚搭載する必要もなく、迅速に且つより低いコストにて、ユーザにとって違和感の無い画像表示を実現する液晶表示装置10を製造し提供することが可能となった。

【符号の説明】

【0025】

10…液晶表示装置、11…SoC、12…T‐CON、13,13‐8…ソースドライバ、13a…出力ライン、14…ゲートドライバ、15…液晶セル、16…画素電極、17…TFT、17s…ソース電極、17g…ゲート電極

【特許請求の範囲】

【請求項1】

第1方向を向いて当該第1方向に直交する第2方向に沿って並ぶ複数のソースラインと、第2方向を向いて第1方向に沿って並ぶ複数のゲートラインと、第1方向および第2方向に配列され各々がソースラインおよびゲートラインに接続する複数の画素とを有する液晶セルと、

一定数の出力ラインを有し、各出力ラインをゲートラインと接続して各画素に電圧を出力するゲートドライバと、

一定数の出力ラインを有し、各出力ラインをソースラインと接続して各画素に電圧を出力するソースドライバと、

ゲートドライバおよびソースドライバによる出力を制御することにより画像表示を実現させる制御部と、を備え、

第1方向を向く画素列を構成する各画素が、所定画素数毎に、当該画素列を挟む両側のソースラインへ交互に接続する配線パターンを有する液晶表示装置であって、

液晶セルにおけるソースラインの総数が、ソースドライバの出力ラインの総数よりも1本多く構成されており、液晶セルにおける最も外側のソースラインは、近隣のソースラインが接続するソースドライバの出力ラインに対して接続され、

上記制御部は、上記最も外側のソースラインおよび上記近隣のソースラインが接続する画素列を含む領域に黒表示を実行させることを特徴とする液晶表示装置。

【請求項2】

上記画素列は、各々が複数の要素色のいずれかの表示に対応しており、

上記黒表示は、上記最も外側のソースラインが接続する画素列を含み、対応する要素色が異なる複数の画素列が連続して形成された単位領域において実行され、

上記最も外側のソースラインは、上記黒表示が実行される単位領域を構成する画素列のいずれかに接続する他のソースラインが接続するソースドライバの出力ラインに、接続されることを特徴とする請求項1に記載の液晶表示装置。

【請求項3】

上記液晶セルの画素は、各々がアクティブ素子のソース電極をソースラインに接続し且つアクティブ素子のゲート電極をゲートラインに接続し、各々が赤、緑、青の要素色のいずれかの表示に対応したサブピクセルであり、

上記ゲートドライバは、各出力ラインをゲートラインと接続して各サブピクセルのアクティブ素子のゲート電極に電圧を出力し、

上記ソースドライバは、各出力ラインをソースラインと接続して各サブピクセルのアクティブ素子のソース電極に電圧を出力し、

第1方向を向き赤、緑、青のいずれか一つの要素色に対応したサブピクセルの列を構成する各サブピクセルが1つずつ、当該列を挟む両側のソースラインへ交互に接続する配線パターンを有し、

液晶セルにおける最も外側のソースラインは、隣のソースラインが接続するソースドライバの出力ラインに対して接続され、

上記制御部は、上記最も外側のソースラインおよび上記隣のソースラインが接続するサブピクセルの列と、当該列と第2方向において連続し且つ当該列が対応する要素色を除く赤、緑、青における2色に対応するサブピクセルの2列からなる領域に、黒表示を実行させることを特徴とする請求項1または請求項2に記載の液晶表示装置。

【請求項1】

第1方向を向いて当該第1方向に直交する第2方向に沿って並ぶ複数のソースラインと、第2方向を向いて第1方向に沿って並ぶ複数のゲートラインと、第1方向および第2方向に配列され各々がソースラインおよびゲートラインに接続する複数の画素とを有する液晶セルと、

一定数の出力ラインを有し、各出力ラインをゲートラインと接続して各画素に電圧を出力するゲートドライバと、

一定数の出力ラインを有し、各出力ラインをソースラインと接続して各画素に電圧を出力するソースドライバと、

ゲートドライバおよびソースドライバによる出力を制御することにより画像表示を実現させる制御部と、を備え、

第1方向を向く画素列を構成する各画素が、所定画素数毎に、当該画素列を挟む両側のソースラインへ交互に接続する配線パターンを有する液晶表示装置であって、

液晶セルにおけるソースラインの総数が、ソースドライバの出力ラインの総数よりも1本多く構成されており、液晶セルにおける最も外側のソースラインは、近隣のソースラインが接続するソースドライバの出力ラインに対して接続され、

上記制御部は、上記最も外側のソースラインおよび上記近隣のソースラインが接続する画素列を含む領域に黒表示を実行させることを特徴とする液晶表示装置。

【請求項2】

上記画素列は、各々が複数の要素色のいずれかの表示に対応しており、

上記黒表示は、上記最も外側のソースラインが接続する画素列を含み、対応する要素色が異なる複数の画素列が連続して形成された単位領域において実行され、

上記最も外側のソースラインは、上記黒表示が実行される単位領域を構成する画素列のいずれかに接続する他のソースラインが接続するソースドライバの出力ラインに、接続されることを特徴とする請求項1に記載の液晶表示装置。

【請求項3】

上記液晶セルの画素は、各々がアクティブ素子のソース電極をソースラインに接続し且つアクティブ素子のゲート電極をゲートラインに接続し、各々が赤、緑、青の要素色のいずれかの表示に対応したサブピクセルであり、

上記ゲートドライバは、各出力ラインをゲートラインと接続して各サブピクセルのアクティブ素子のゲート電極に電圧を出力し、

上記ソースドライバは、各出力ラインをソースラインと接続して各サブピクセルのアクティブ素子のソース電極に電圧を出力し、

第1方向を向き赤、緑、青のいずれか一つの要素色に対応したサブピクセルの列を構成する各サブピクセルが1つずつ、当該列を挟む両側のソースラインへ交互に接続する配線パターンを有し、

液晶セルにおける最も外側のソースラインは、隣のソースラインが接続するソースドライバの出力ラインに対して接続され、

上記制御部は、上記最も外側のソースラインおよび上記隣のソースラインが接続するサブピクセルの列と、当該列と第2方向において連続し且つ当該列が対応する要素色を除く赤、緑、青における2色に対応するサブピクセルの2列からなる領域に、黒表示を実行させることを特徴とする請求項1または請求項2に記載の液晶表示装置。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2013−104988(P2013−104988A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2011−248261(P2011−248261)

【出願日】平成23年11月14日(2011.11.14)

【出願人】(000201113)船井電機株式会社 (7,855)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成23年11月14日(2011.11.14)

【出願人】(000201113)船井電機株式会社 (7,855)

【Fターム(参考)】

[ Back to top ]