液晶表示装置

【課題】小型携帯機器に用いられる液晶表示装置において、回路規模の増大に対応し高品質な表示を可能とする。

【解決手段】液晶表示パネル上には、駆動回路から出力する映像信号を液晶表示パネル上の複数の映像信号線に出力する分配回路を有し、前記分配回路は、前記駆動回路から出力する制御信号により制御され、前記駆動回路は、高耐圧出力アンプと低耐圧出力アンプからの映像信号が交互に、隣合う2本の映像信号出力端子から出力し、前記分割回路は、前記映像信号線毎にスイッチング素子を有し、前記スイッチング素子は、前記高耐圧出力アンプからの映像信号と、前記低耐圧出力アンプからの映像信号とが入力する入力端子と、前記映像信号線に前記映像信号を出力する出力端子と、前記制御信号が入力する制御端子とを有し、前記分割回路は、前記高耐圧出力アンプからの映像信号と、前記低耐圧出力アンプからの映像信号とを同じ前記スイッチング素子を介して前記映像信号線に出力する。

【解決手段】液晶表示パネル上には、駆動回路から出力する映像信号を液晶表示パネル上の複数の映像信号線に出力する分配回路を有し、前記分配回路は、前記駆動回路から出力する制御信号により制御され、前記駆動回路は、高耐圧出力アンプと低耐圧出力アンプからの映像信号が交互に、隣合う2本の映像信号出力端子から出力し、前記分割回路は、前記映像信号線毎にスイッチング素子を有し、前記スイッチング素子は、前記高耐圧出力アンプからの映像信号と、前記低耐圧出力アンプからの映像信号とが入力する入力端子と、前記映像信号線に前記映像信号を出力する出力端子と、前記制御信号が入力する制御端子とを有し、前記分割回路は、前記高耐圧出力アンプからの映像信号と、前記低耐圧出力アンプからの映像信号とを同じ前記スイッチング素子を介して前記映像信号線に出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、液晶表示装置に係わり、特に、携帯型装置の表示部に用いられる液晶表示装置の駆動回路に適用して有効な技術に関する。

【背景技術】

【0002】

TFT(Thin Film Transistor)方式の液晶表示装置は、パソコン、TV等の表示装置として広く使用されている。これらの液晶表示装置は、液晶表示パネルと、液晶表示パネルを駆動する駆動回路とを備えている。

そして、このような液晶表示装置において小型のものが、携帯電話機等の携帯機器の表示装置として広く利用されている。さらに近年、液晶表示装置を携帯用コンピュータの表示装置として用いることが望まれている。

下記「特許文献1」には、液晶表示パネルで基板上に分配回路を形成し、分配回路を用いて駆動回路から出力する映像信号を複数の映像信号線に分配することで、駆動回路の出力数を減少させて回路規模を抑える開示がある。

しかしながら、「特許文献1」にはさらに高精細な表示装置に分配回路を用いる場合の問題点について記載あるものではない。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2003−270660号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

携帯用コンピュータに用いられる表示装置においても、高精細多階調表示が可能なものが望まれている。そのため、より高精細で表示品質の優れた表示装置が携帯機器においても用いられている。

しかしながら、限られた表示領域を有する携帯用の液晶表示装置で高精細多階調の表示を行うには、駆動回路の回路規模が増大し、液晶表示パネル上に駆動装置を実装することが困難になってきていた。

そのため、携帯機器用液晶表示装置において、液晶表示パネル上に分配回路を形成し、駆動回路からの出力を複数の映像信号線に分配することで、駆動回路の回路規模を抑える方法が用いられてきた。しかしながら、分配回路を用いる方法でも、液晶表示パネルに実装する駆動回路の規模の増大に対応困難となっており、さらに、表示品質の向上のために、ドット反転駆動の要求も高まっている。

本発明は、前記従来技術の問題点を解決するためになされたものであり、本発明の目的は、携帯機器用の液晶表示装置において、回路規模の増大に対応し高品質な表示が可能な液晶表示装置を提供することにある。

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述及び添付図面によって明らかにする。

【課題を解決するための手段】

【0005】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、下記の通りである。

本発明の液晶表示装置は、2枚の基板と、2枚の基板の間に挟まれた液晶組成物と、基板に設けられた複数の画素と、画素に設けられた画素電極と、前記画素電極に対向する対向電極と、画素電極に設けられたスイッチング素子と、スイッチング素子に映像信号を供給する映像信号線と、スイッチング素子のオン・オフを制御する走査信号を供給する走査信号線と、映像信号線に映像信号を出力し、走査信号線に走査信号を出力する駆動回路とを備える。

画素が形成された基板上には、駆動回路の出力を複数の映像信号線に分配する分配回路が形成される。駆動回路からは分配回路を制御する制御信号が分配回路の両端から供給される。

分配回路と駆動回路とは2分割され、駆動回路にはマスタ回路とスレーブ回路との機能が形成され、駆動回路は外部からの制御信号によりマスタ回路とスレーブ回路とに設定可能である。

【発明の効果】

【0006】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記の通りである。

本発明によれば、分配回路の両端から、分配回路を制御する制御信号を供給することで、分配回路の回路規模が増大したことによる制御信号の波形なまりを減少させることが可能である。

また、分配回路と駆動回路とを複数設けることで、高精細で映像信号線数の増加した液晶表示装置に対応が可能となり、さらには駆動回路にマスタ回路とスレーブ回路の機能を持たせることで、複数の回路構成にも対応可能である。

【図面の簡単な説明】

【0007】

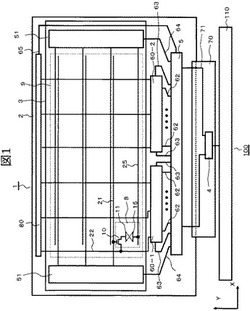

【図1】本発明の実施例の液晶表示装置を示す概略ブロック図である。

【図2】本発明の実施例の液晶表示装置を示す概略ブロック図である。

【図3】本発明の実施例の液晶表示装置に用いられる駆動回路の端子部を示す概略平面図である。

【図4】本発明の実施例の液晶表示装置の分配回路を示す概略ブロック図である。

【図5】本発明の実施例の液晶表示装置の分配回路の駆動方法を示すタイミングチャートである。

【図6】本発明の実施例の液晶表示装置の駆動回路の出力部を示す概略ブロック図である。

【図7】本発明の実施例の液晶表示装置の分配回路を示す概略ブロック図である。

【図8】本発明の実施例の液晶表示装置の分配回路を示す概略ブロック図である。

【図9】本発明の実施例の液晶表示装置の分配回路を示す概略ブロック図である。

【図10】本発明の実施例の液晶表示装置の分配回路を示す概略ブロック図である。

【図11】本発明の実施例の液晶表示装置の分配回路を示す概略ブロック図である。

【図12】本発明の実施例の液晶表示装置のイコライズ回路を示す概略ブロック図である。

【図13】本発明の実施例の液晶表示装置のイコライズ回路を示す概略ブロック図である。

【発明を実施するための形態】

【0008】

以下、図面を参照して本発明の実施例を詳細に説明する。

なお、実施例を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。また、以下の実施例は、本発明の特許請求の範囲の解釈を限定するためのものではない。

図1は、本発明の実施例の液晶表示装置の基本構成を示すブロック図である。同図に示すように、本実施例の液晶表示装置100は、液晶表示パネル1と、駆動回路5と、フレキシブル基板70と、バックライト110と、収納ケース(図示せず)とから構成される。

液晶表示パネル1は、薄膜トランジスタ10、画素電極11、対向電極15等が形成されるTFT基板2と、カラーフィルタ等が形成されるカラーフィルタ基板3とを、所定の間隙を隔てて重ね合わせ、該両基板間の周縁部近傍に枠状に設けたシール材(図示せず)により、両基板を貼り合わせると共に、シール材の内側に液晶組成物を封入、封止し、さらに、両基板の外側に偏光板を貼り付けて構成される。

なお、本実施例は対向電極15がTFT基板2に設けられる所謂横電界方式の液晶表示パネルにも、対向電極15がカラーフィルタ基板3に設けられる所謂縦電界方式の液晶表示パネルにも同様に適用される。

TFT基板2には、図中x方向に延在しy方向に並設される走査信号線(ゲート線とも呼ぶ)21と、y方向に延在しx方向に並設される映像信号線(ドレイン信号線とも呼ぶ)22とが設けられており、走査信号線21と映像信号線22とで囲まれる領域に画素部8が形成されている。

【0009】

なお、液晶表示パネル1は多数の画素部8をマトリクス状に備えているが、図を解り易くするため、図1では画素部8を1つだけ示している。マトリクス状に配置された画素部8は表示領域9を形成し、各画素部8が表示画像の画素の役割をはたし、表示領域9に画像を表示する。

各画素部8の薄膜トランジスタ10はソースが画素電極11に接続され、ドレインが映像信号線22に接続され、ゲートが走査信号線21に接続される。この薄膜トランジスタ10は、画素電極11に表示電圧(階調電圧)を供給するためのスイッチとして機能する。なお、ソース、ドレインの呼び方は、バイアスの関係で逆になることもあるが、ここでは、映像信号線22に接続される方をドレインと称する。

駆動回路5は、TFT基板2を構成する透明な絶縁基板(ガラス基板、樹脂基板等)に配置される。駆動回路5は分配回路60と中継信号線62で接続しており、駆動回路5からは多数の中継信号線62を介して映像信号が分配回路に出力する。さらに、駆動回路5からは分配回路60に制御信号線63が接続している。

図1では、分配回路60は分配回路60−1と60−2とに分割されて形成され、各分配回路60−1と60−2とには外側から制御信号線63に加えて、2つの分配回路の間である内側からも制御信号線63が接続している。分配回路60の両端部から制御信号線63を介して制御信号を供給することで、分配回路60内の制御信号線の長さが長くなることで、制御信号の波形がなまる問題を減少させることが可能である。

また、駆動回路5と走査信号線駆動回路51とは信号線64を介して接続され、駆動回路5とイコライズ回路80とは信号線65を介して電気的に接続している。なお、図1では、一方の走査信号線駆動回路51が走査信号線21に走査信号を供給し、他方の走査信号線駆動回路51が対向電極(コモン電極)25にコモン電圧を供給している。

【0010】

TFT基板2の長辺側には、フレキシブル基板70が接続されている。フレキシブル基板70にはコネクタ4が設けられている。コネクタ4は外部信号線と接続され外部からの信号が入力する。コネクタ4と駆動回路5の間には配線71が設けられており、外部からの信号は配線71を介して駆動回路5に入力する。

液晶表示パネル1は非発光素子であるため、光源を必要とするが、液晶表示装置100にはバックライト110が設けられており、バックライト110は液晶表示パネル1に光を照射する。液晶表示パネル1は照射された光の透過・反射量を制御して表示を行う。なお、バックライト110は液晶表示パネル1の背面または前面に設けられるが、図1では図をわかり易くするために液晶表示パネル1と並べて示した。

液晶表示装置100の外部に設けられた制御装置(図示せず)から送出された制御信号、および外部電源回路(図示せず)から供給される電源電圧が、コネクタ4、配線71を介して駆動回路5に入力する。

【0011】

外部から駆動回路5に入力する信号は、クロック信号、ディスプレイタイミング信号、水平同期信号、垂直同期信号等の各制御信号および表示用デ−タ(R・G・B)、表示モード制御コマンドであり、入力した信号を基に駆動回路5は液晶表示パネル1を駆動する。

駆動回路5は、走査信号線21を駆動するために制御信号を制御信号線64を介して走査信号線駆動回路51に供給する。走査信号線駆動回路51は内部で発生させる基準クロックに基づき、1水平走査期間毎に、走査信号線21に“High”レベル(以後ハイ信号とも呼ぶ)の選択電圧(走査信号)を供給する。これにより、液晶表示パネル1の各走査信号線21に接続された複数の薄膜トランジスタ10が、1水平走査期間の間、映像信号線22と画素電極11との間を電気的に導通させる。

また、駆動回路5は画素が表示すべき階調に対応する階調電圧(映像信号)を中継信号線62に出力する。分配回路60を介して映像信号線22に階調電圧が供給されると、オン状態(導通)の薄膜トランジスタ10を介して、映像信号線22から階調電圧が画素電極11に供給される。その後、薄膜トランジスタ10がオフ状態となることで画素が表示すべき映像に基づく階調電圧が画素電極11に保持される。なお、分配回路60の詳細については後述する。

【0012】

次に図2に、駆動回路5の配置を走査信号線駆動回路51と並列とした場合を示す。図2に示すように、駆動回路5を短辺側に設けることで、フレキシブル基板70を液晶表示パネル1の短辺側から引き出すことが可能となる。

図2に示す短辺側に駆動回路5を搭載した場合でも、駆動回路5と分配回路60−1、60−2とは制御信号線63で接続され、制御信号線63は分配回路60−1と60−2の両端部から入力している。

図2では、分配回路60は2分割されて、液晶表示パネル1の上下に配置されている。また、分配回路60−1では駆動回路5からの距離が図1の場合に比べて長くなっており分配回路60の両端から制御信号線63を入力させることが波形なまりの対策に有効である。なお、イコライズ回路80も2分割されている。

次に図3に駆動回路5の出力端子の配置を示す。図3は分配回路60の両端に制御信号線63を供給するための出力端子の配置となっている。図1、図2に示すように、多数の信号線が駆動回路5と接続している。その中で、映像信号が出力される中継信号線62が駆動回路5と分配回路60との間で多数接続されており、駆動回路5には、中継信号線62に接続する出力端子30が多数形成されている。

出力端子30の両端には制御信号線63に接続する接続端子563が形成されている。特に分配回路60の両端に制御信号を供給するためには、出力端子30の両端に隣接して出力端子563を設けることが有効である。また、2つの出力端子30の間で駆動回路5の中央部に出力端子563を設けることで、分配回路60が分割した場合にも対応可能となっている。

駆動回路5の中央部では、図2に示す短辺側配置に対応して、イコライズ回路80に接続する出力端子565の内側に走査信号線駆動回路51に接続する出力端子564が設けられている。

また、駆動回路5の端部では、図1に示す駆動回路5の配置に対応して、信号線64の外側に信号線65が配置可能なように、走査信号線駆動回路51に接続する出力端子564の外側には、イコライズ回路80に接続する出力端子565が設けられている。なお、符号571は入力端子である。

【0013】

次に図4に分配回路60を示す。分配回路60には駆動回路5から映像信号が中継信号線62を介して供給されている。分配回路60には映像信号線22に接続するスイッチング素子61が設けられている。

図5に分配回路60の駆動方法を説明するタイミングチャートを示す。符号VSIGは中継信号線62に駆動回路5から出力する映像信号である。符号BLは制御信号線63に出力する制御信号を示す。制御信号BL1は制御信号線63−1に、制御信号BL2は制御信号線63−2に、制御信号BL3は制御信号線63−3に出力する。なお、BL11、BL12、BL13は波形なまりが生じた制御信号を示している。

図5に示すように、各中継信号線62には、走査信号がハイ信号である1水平走査期間(1H)に、複数の映像信号線に供給する映像信号VSIGが出力する。映像信号VSIGは各画素に表示される階調に応じて最大VDHから最小VDLの電圧が出力している。

図4に示す分配回路60は3本の映像信号線22に映像信号VSIGを分配する構成であり、3つの制御信号BLは3つのスイッチング素子61をオン状態とするように、順番にハイ信号を出力している。

まず制御信号BL1が制御信号線63−1に出力すると、スイッチング素子61−1がオン状態となり、映像信号線22−1に映像信号が供給される。その後順番に、制御信号BL2が制御信号線63−2を介してスイッチング素子61−2をオン状態として映像信号を映像信号線22−2に供給し、制御信号BL3によって映像信号が映像信号線22−3に供給される。

分配回路60の駆動においては、制御信号線63の引き回し距離が長くなると、制御信号線63の端部では波形なまりが制御信号BL11、BL12、BL13で示すように生じる。そのため、図1、図2で示したように、分配回路60の両端部から制御信号を供給することが有効である。

【0014】

次に図6を用いて、正極性と負極性の映像信号を交互に出力し、かつ駆動回路5から図5に示すように分割して映像信号を供給する構成について説明する。図6は駆動回路5の隣合う2つの出力端子30−1と30−2の出力部について示している。29−1は高耐圧出力アンプで、29−2は低耐圧出力アンプである。対向電極の電圧(以下、コモン電圧と呼ぶ)を一定とする場合の交流化駆動では、コモン電圧に対して正極性の映像信号(以下階調電圧とも呼ぶ)と負極性の階調電圧が画素電極11に印加される。図6に示す回路では、正極性の階調電圧を高耐圧出力アンプ29−1から出力し、負極性の階調電圧を低耐圧出力アンプ29−2から出力する。

図6においては、切換スイッチ36を用いて高耐圧出力アンプ29−1と低耐圧出力アンプ29−2の出力を切り替えている。いま、出力端子30−1から正極性の階調電圧を出力しようとすると、切換スイッチ36は高耐圧出力アンプ29−1と出力端子30−1とを接続する。他方の出力端子30−2は低耐圧出力アンプ29−2に接続され負極性の階調電圧を出力する。

他方、表示データも順番を変更可能となっており、切換スイッチ37はデータ線選択回路125の出力を切り替えてレベルシフタ回路27に接続する。切換スイッチ37によりデータ線選択回路125−1はレベルシフタ回路27−1と27−2の両方に接続可能である。

よって、切換スイッチ37はセレクタ回路24の出力する表示データを正極性の階調電圧を出力する場合は、レベルシフタ回路27−1に供給し、負極性の階調電圧を出力する場合は、セレクタ24の出力をレベルシフタ回路27−2に供給する。

セレクタ回路24は表示データを時分割してデコーダ回路28に出力する。セレクタ回路24はデータ線選択回路125を有しており、分配回路60に供給する制御信号に同期して、時分割制御信号がセレクタ回路24に伝えられている。時分割信号発生回路26では時分割制御信号から時分割信号を作成し、時分割信号線19に出力する。

時分割信号線19は各データ線選択回路125に接続している。データ線選択回路125に入力した時分割信号はデータ線選択回路125を制御する。データ線選択回路125は時分割信号に従いラインラッチ回路23の出力する表示データを選択して、次段のレベルシフタ回路27に出力する。すなわち、ラインラッチ回路23は1水平走査期間(1H)の間表示データを出力するが、セレクタ回路24により1走査期間を複数の期間に分割し、分割した期間毎に異なる表示データがレベルシフタ回路27に伝えられる。

【0015】

次に図7を用いて、信号線62が奇数となった場合の問題点を説明する。

一般に液晶表示パネル1の映像信号線22の数は偶数で、またRGB3本で一組となっているので、中継信号線62の数も一般には偶数であるが、図1に示すように分配回路60を2個設けた場合には、各分配回路60に入力する中継信号線62の数は奇数となる。

中継信号線62が奇数の場合には、駆動回路5の出力が図6で示すように、正極性と負極性の階調電圧を交互に出力するようになっているため、最端部の出力部で、出力アンプが余る問題が生じる。

そのため、図7に示すように、最後の切換スイッチ36−(2n+1)の出力は両方共に信号線62−(2n+1)に接続している。そのため、信号線62−(2n+1)に接続する高耐圧出力アンプ29−1と低耐圧出力アンプ29−2では、例えば高耐圧出力アンプ29−1が信号線62−(2n+1)に階調電圧を出力している場合には、低耐圧出力アンプ29−2は信号線62−(2n+1)に接続されていない状態となる。

【0016】

図8に奇数出力の駆動回路5を2つ並べて配置する場合の問題点を示す。前述したように、駆動回路5−1と5−2共に、最後の切換スイッチ36−(2n+1)の出力は両方共に信号線62−(2n+1)に接続している。

前述したように、正極性の階調電圧と負極性の階調電圧とが交互に出力されているために、3×(2n+1)本目の映像信号線22−3(2n+1)が、例えば正極性の場合には、3×(2n+1)+1本目の映像信号線22−3(2n+1)+1には負極性の階調電圧が供給されている。

そのため、駆動回路5−1が、最初の映像信号線22−1に正極性の階調電圧を出力しているタイミングで、駆動回路5−2は映像信号線22−3(2n+1)+1に負極性の階調電圧を出力することになる。

すなわち、同じ駆動回路5でも正極性の階調電圧から出力開始するものと、負極性の階調電圧から出力開始するものとに分けられることになる。そこで、駆動回路5にマスタ機能とスレーブ機能を持たせ、マスタ機能に設定された駆動回路5は正極性の階調電圧から出力開始し、スレーブ機能に設定された駆動回路5は負極性の階調電圧から出力開始することとした。

なお、配線66はマスタ機能の駆動回路5−1から駆動回路5−2をスレーブ機能に設定するための制御信号線である。

【0017】

次に、図9を用いて2分割した分配回路60−1と分配回路60−2とで、中継信号線62の数を異ならせる場合を示す。駆動回路5−1は出力数が2n本で、駆動回路5−2は出力数を2n−2本として、どちらも偶数本出力とする。この時、駆動回路5−1はマスタ機能に設定され、駆動回路5−2は制御信号線66によりスレーブ機能に設定される。

次に図10に、奇数本出力と双方向シフトに対応した駆動回路5を示す。図中出力アンプ29−1、29−3、29−5、29−7を低耐圧出力アンプとし、出力アンプ29−2、29−4,29−6を高耐圧出力アンプとする。

制御信号線94にハイ信号が出力してアナログスイッチ91がオン状態となると、高耐圧出力アンプ29−2の出力電圧が信号線62−1に供給される。同じく、アナログスイッチ91がオン状態となることで、低耐圧出力アンプ29−3の出力電圧が信号線62−2に供給される。

次に、制御信号線95にハイ信号を出力すると、アナログスイッチ92がオン状態となることで、低耐圧出力アンプ29−1の出力電圧が信号線62−1に供給され、高耐圧出力アンプ29−2の出力電圧が信号線62−2に供給される。

次に、制御信号線96にハイ信号が出力すると、アナログスイッチ93がオン状態となることで、低耐圧出力アンプ29−3の出力電圧が信号線62−1に出力する。

【0018】

図10に示す駆動回路5では、中継信号線62−1に高耐圧出力アンプ29−2から出力する正極性の階調電圧を出力し、中継信号線62−2に低耐圧出力アンプ29−3から出力する負極性の階調電圧を出力する場合には、制御信号94をハイ信号とし、次に、中継信号線62−1に低耐圧出力アンプ29−1から出力する負極性の階調電圧を出力し、中継信号線62−2に高耐圧出力アンプ29−2から出力する正極性の階調電圧を出力する場合には、制御信号95をハイ信号とすることで対応可能である。

また、中継信号線62−1に高耐圧出力アンプ29−2から出力する正極性の階調電圧を出力し、中継信号線62−2に低耐圧出力アンプ29−3から出力する負極性の階調電圧を出力する場合には、制御信号94をハイ信号とし、次に、中継信号線62−1に低耐圧出力アンプ29−3から出力する負極性の階調電圧を出力し、中継信号線62−2に高耐圧出力アンプ29−4から出力する正極性の階調電圧を出力する場合には、制御信号96をハイ信号とすることで対応可能である。

このように、駆動回路5にアナログスイッチ91、92、93を形成することで、低耐圧出力アンプ29−1から高耐圧出力アンプ29−2の順番で、表示データがセレクトされる場合と、低耐圧出力アンプ29−7から高耐圧出力アンプ29−6の順番で、表示データがセレクトされる場合とに対応可能となっている。

【0019】

次に、図11に分配回路60で6本の映像信号線22に映像信号を分配する構成を示す。駆動回路5からは高耐圧出力アンプ29−2と低耐圧出力アンプ29−1からの信号が交互に出力しているため、偶数の映像信号線に分配することは不可能である。そのため、高耐圧出力アンプ29−2と低耐圧出力アンプ29−1の出力を交互に分配回路60に入力している。

図11に示す回路では、中継信号線62−1と中継信号線62−2とがTFT基板2上で交差することになり、絶縁膜を介して2層の導電膜から形成されることになる。

次に、図12に高耐圧出力アンプ29−2と低耐圧出力アンプ29−1の出力をアナログスイッチ85で短絡させて、出力アンプの出力電圧をイコライズする構成を示す。

帰線期間に画素部8のスイッチング素子10をオフ状態として、制御信号線86を用いてアナログスイッチ85により、中継信号線62−1と62−2とを短絡させる。中継信号線62−1と62−2は逆極性であるため、双方に電荷が移動して省電力化に有効である。

次に、図13に高耐圧出力アンプ29−2と低耐圧出力アンプ29−1の出力をアナログスイッチ85で接地電位線87に短絡させて、映像信号線22の電位をGND電位にイコライズする構成を示す。

帰線期間に画素部8のスイッチング素子10をオフ状態として、アナログスイッチ85により、中継信号線62−1と62−2とを接地電位線87に短絡させる。中継信号線62−1と62−2を接地電位とすることで、図12に示す場合に比べて、高耐圧出力アンプ29−2と低耐圧出力アンプ29−1の耐圧を小さくすることが可能である。また、中継信号線62−1と62−2とは逆極性であるため、電荷を接地電位線87を介して供給可能なことから省電力化に有効である。

なお、図1、図2に示すイコライズ回路80も同様に極性の異なる映像信号線22を短絡するものである。

以上、本発明者によってなされた発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは勿論である。

【符号の説明】

【0020】

1 液晶表示パネル

2 TFT基板

5 駆動回路

8 画素部

9 表示領域

10 スイッチング素子

11 画素電極

21 走査信号線

22 映像信号線

60 分配回路

70 フレキシブル基板

80 イコライズ回路

91 アナログスイッチ

100 液晶表示装置

【技術分野】

【0001】

本発明は、液晶表示装置に係わり、特に、携帯型装置の表示部に用いられる液晶表示装置の駆動回路に適用して有効な技術に関する。

【背景技術】

【0002】

TFT(Thin Film Transistor)方式の液晶表示装置は、パソコン、TV等の表示装置として広く使用されている。これらの液晶表示装置は、液晶表示パネルと、液晶表示パネルを駆動する駆動回路とを備えている。

そして、このような液晶表示装置において小型のものが、携帯電話機等の携帯機器の表示装置として広く利用されている。さらに近年、液晶表示装置を携帯用コンピュータの表示装置として用いることが望まれている。

下記「特許文献1」には、液晶表示パネルで基板上に分配回路を形成し、分配回路を用いて駆動回路から出力する映像信号を複数の映像信号線に分配することで、駆動回路の出力数を減少させて回路規模を抑える開示がある。

しかしながら、「特許文献1」にはさらに高精細な表示装置に分配回路を用いる場合の問題点について記載あるものではない。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2003−270660号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

携帯用コンピュータに用いられる表示装置においても、高精細多階調表示が可能なものが望まれている。そのため、より高精細で表示品質の優れた表示装置が携帯機器においても用いられている。

しかしながら、限られた表示領域を有する携帯用の液晶表示装置で高精細多階調の表示を行うには、駆動回路の回路規模が増大し、液晶表示パネル上に駆動装置を実装することが困難になってきていた。

そのため、携帯機器用液晶表示装置において、液晶表示パネル上に分配回路を形成し、駆動回路からの出力を複数の映像信号線に分配することで、駆動回路の回路規模を抑える方法が用いられてきた。しかしながら、分配回路を用いる方法でも、液晶表示パネルに実装する駆動回路の規模の増大に対応困難となっており、さらに、表示品質の向上のために、ドット反転駆動の要求も高まっている。

本発明は、前記従来技術の問題点を解決するためになされたものであり、本発明の目的は、携帯機器用の液晶表示装置において、回路規模の増大に対応し高品質な表示が可能な液晶表示装置を提供することにある。

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述及び添付図面によって明らかにする。

【課題を解決するための手段】

【0005】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、下記の通りである。

本発明の液晶表示装置は、2枚の基板と、2枚の基板の間に挟まれた液晶組成物と、基板に設けられた複数の画素と、画素に設けられた画素電極と、前記画素電極に対向する対向電極と、画素電極に設けられたスイッチング素子と、スイッチング素子に映像信号を供給する映像信号線と、スイッチング素子のオン・オフを制御する走査信号を供給する走査信号線と、映像信号線に映像信号を出力し、走査信号線に走査信号を出力する駆動回路とを備える。

画素が形成された基板上には、駆動回路の出力を複数の映像信号線に分配する分配回路が形成される。駆動回路からは分配回路を制御する制御信号が分配回路の両端から供給される。

分配回路と駆動回路とは2分割され、駆動回路にはマスタ回路とスレーブ回路との機能が形成され、駆動回路は外部からの制御信号によりマスタ回路とスレーブ回路とに設定可能である。

【発明の効果】

【0006】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記の通りである。

本発明によれば、分配回路の両端から、分配回路を制御する制御信号を供給することで、分配回路の回路規模が増大したことによる制御信号の波形なまりを減少させることが可能である。

また、分配回路と駆動回路とを複数設けることで、高精細で映像信号線数の増加した液晶表示装置に対応が可能となり、さらには駆動回路にマスタ回路とスレーブ回路の機能を持たせることで、複数の回路構成にも対応可能である。

【図面の簡単な説明】

【0007】

【図1】本発明の実施例の液晶表示装置を示す概略ブロック図である。

【図2】本発明の実施例の液晶表示装置を示す概略ブロック図である。

【図3】本発明の実施例の液晶表示装置に用いられる駆動回路の端子部を示す概略平面図である。

【図4】本発明の実施例の液晶表示装置の分配回路を示す概略ブロック図である。

【図5】本発明の実施例の液晶表示装置の分配回路の駆動方法を示すタイミングチャートである。

【図6】本発明の実施例の液晶表示装置の駆動回路の出力部を示す概略ブロック図である。

【図7】本発明の実施例の液晶表示装置の分配回路を示す概略ブロック図である。

【図8】本発明の実施例の液晶表示装置の分配回路を示す概略ブロック図である。

【図9】本発明の実施例の液晶表示装置の分配回路を示す概略ブロック図である。

【図10】本発明の実施例の液晶表示装置の分配回路を示す概略ブロック図である。

【図11】本発明の実施例の液晶表示装置の分配回路を示す概略ブロック図である。

【図12】本発明の実施例の液晶表示装置のイコライズ回路を示す概略ブロック図である。

【図13】本発明の実施例の液晶表示装置のイコライズ回路を示す概略ブロック図である。

【発明を実施するための形態】

【0008】

以下、図面を参照して本発明の実施例を詳細に説明する。

なお、実施例を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。また、以下の実施例は、本発明の特許請求の範囲の解釈を限定するためのものではない。

図1は、本発明の実施例の液晶表示装置の基本構成を示すブロック図である。同図に示すように、本実施例の液晶表示装置100は、液晶表示パネル1と、駆動回路5と、フレキシブル基板70と、バックライト110と、収納ケース(図示せず)とから構成される。

液晶表示パネル1は、薄膜トランジスタ10、画素電極11、対向電極15等が形成されるTFT基板2と、カラーフィルタ等が形成されるカラーフィルタ基板3とを、所定の間隙を隔てて重ね合わせ、該両基板間の周縁部近傍に枠状に設けたシール材(図示せず)により、両基板を貼り合わせると共に、シール材の内側に液晶組成物を封入、封止し、さらに、両基板の外側に偏光板を貼り付けて構成される。

なお、本実施例は対向電極15がTFT基板2に設けられる所謂横電界方式の液晶表示パネルにも、対向電極15がカラーフィルタ基板3に設けられる所謂縦電界方式の液晶表示パネルにも同様に適用される。

TFT基板2には、図中x方向に延在しy方向に並設される走査信号線(ゲート線とも呼ぶ)21と、y方向に延在しx方向に並設される映像信号線(ドレイン信号線とも呼ぶ)22とが設けられており、走査信号線21と映像信号線22とで囲まれる領域に画素部8が形成されている。

【0009】

なお、液晶表示パネル1は多数の画素部8をマトリクス状に備えているが、図を解り易くするため、図1では画素部8を1つだけ示している。マトリクス状に配置された画素部8は表示領域9を形成し、各画素部8が表示画像の画素の役割をはたし、表示領域9に画像を表示する。

各画素部8の薄膜トランジスタ10はソースが画素電極11に接続され、ドレインが映像信号線22に接続され、ゲートが走査信号線21に接続される。この薄膜トランジスタ10は、画素電極11に表示電圧(階調電圧)を供給するためのスイッチとして機能する。なお、ソース、ドレインの呼び方は、バイアスの関係で逆になることもあるが、ここでは、映像信号線22に接続される方をドレインと称する。

駆動回路5は、TFT基板2を構成する透明な絶縁基板(ガラス基板、樹脂基板等)に配置される。駆動回路5は分配回路60と中継信号線62で接続しており、駆動回路5からは多数の中継信号線62を介して映像信号が分配回路に出力する。さらに、駆動回路5からは分配回路60に制御信号線63が接続している。

図1では、分配回路60は分配回路60−1と60−2とに分割されて形成され、各分配回路60−1と60−2とには外側から制御信号線63に加えて、2つの分配回路の間である内側からも制御信号線63が接続している。分配回路60の両端部から制御信号線63を介して制御信号を供給することで、分配回路60内の制御信号線の長さが長くなることで、制御信号の波形がなまる問題を減少させることが可能である。

また、駆動回路5と走査信号線駆動回路51とは信号線64を介して接続され、駆動回路5とイコライズ回路80とは信号線65を介して電気的に接続している。なお、図1では、一方の走査信号線駆動回路51が走査信号線21に走査信号を供給し、他方の走査信号線駆動回路51が対向電極(コモン電極)25にコモン電圧を供給している。

【0010】

TFT基板2の長辺側には、フレキシブル基板70が接続されている。フレキシブル基板70にはコネクタ4が設けられている。コネクタ4は外部信号線と接続され外部からの信号が入力する。コネクタ4と駆動回路5の間には配線71が設けられており、外部からの信号は配線71を介して駆動回路5に入力する。

液晶表示パネル1は非発光素子であるため、光源を必要とするが、液晶表示装置100にはバックライト110が設けられており、バックライト110は液晶表示パネル1に光を照射する。液晶表示パネル1は照射された光の透過・反射量を制御して表示を行う。なお、バックライト110は液晶表示パネル1の背面または前面に設けられるが、図1では図をわかり易くするために液晶表示パネル1と並べて示した。

液晶表示装置100の外部に設けられた制御装置(図示せず)から送出された制御信号、および外部電源回路(図示せず)から供給される電源電圧が、コネクタ4、配線71を介して駆動回路5に入力する。

【0011】

外部から駆動回路5に入力する信号は、クロック信号、ディスプレイタイミング信号、水平同期信号、垂直同期信号等の各制御信号および表示用デ−タ(R・G・B)、表示モード制御コマンドであり、入力した信号を基に駆動回路5は液晶表示パネル1を駆動する。

駆動回路5は、走査信号線21を駆動するために制御信号を制御信号線64を介して走査信号線駆動回路51に供給する。走査信号線駆動回路51は内部で発生させる基準クロックに基づき、1水平走査期間毎に、走査信号線21に“High”レベル(以後ハイ信号とも呼ぶ)の選択電圧(走査信号)を供給する。これにより、液晶表示パネル1の各走査信号線21に接続された複数の薄膜トランジスタ10が、1水平走査期間の間、映像信号線22と画素電極11との間を電気的に導通させる。

また、駆動回路5は画素が表示すべき階調に対応する階調電圧(映像信号)を中継信号線62に出力する。分配回路60を介して映像信号線22に階調電圧が供給されると、オン状態(導通)の薄膜トランジスタ10を介して、映像信号線22から階調電圧が画素電極11に供給される。その後、薄膜トランジスタ10がオフ状態となることで画素が表示すべき映像に基づく階調電圧が画素電極11に保持される。なお、分配回路60の詳細については後述する。

【0012】

次に図2に、駆動回路5の配置を走査信号線駆動回路51と並列とした場合を示す。図2に示すように、駆動回路5を短辺側に設けることで、フレキシブル基板70を液晶表示パネル1の短辺側から引き出すことが可能となる。

図2に示す短辺側に駆動回路5を搭載した場合でも、駆動回路5と分配回路60−1、60−2とは制御信号線63で接続され、制御信号線63は分配回路60−1と60−2の両端部から入力している。

図2では、分配回路60は2分割されて、液晶表示パネル1の上下に配置されている。また、分配回路60−1では駆動回路5からの距離が図1の場合に比べて長くなっており分配回路60の両端から制御信号線63を入力させることが波形なまりの対策に有効である。なお、イコライズ回路80も2分割されている。

次に図3に駆動回路5の出力端子の配置を示す。図3は分配回路60の両端に制御信号線63を供給するための出力端子の配置となっている。図1、図2に示すように、多数の信号線が駆動回路5と接続している。その中で、映像信号が出力される中継信号線62が駆動回路5と分配回路60との間で多数接続されており、駆動回路5には、中継信号線62に接続する出力端子30が多数形成されている。

出力端子30の両端には制御信号線63に接続する接続端子563が形成されている。特に分配回路60の両端に制御信号を供給するためには、出力端子30の両端に隣接して出力端子563を設けることが有効である。また、2つの出力端子30の間で駆動回路5の中央部に出力端子563を設けることで、分配回路60が分割した場合にも対応可能となっている。

駆動回路5の中央部では、図2に示す短辺側配置に対応して、イコライズ回路80に接続する出力端子565の内側に走査信号線駆動回路51に接続する出力端子564が設けられている。

また、駆動回路5の端部では、図1に示す駆動回路5の配置に対応して、信号線64の外側に信号線65が配置可能なように、走査信号線駆動回路51に接続する出力端子564の外側には、イコライズ回路80に接続する出力端子565が設けられている。なお、符号571は入力端子である。

【0013】

次に図4に分配回路60を示す。分配回路60には駆動回路5から映像信号が中継信号線62を介して供給されている。分配回路60には映像信号線22に接続するスイッチング素子61が設けられている。

図5に分配回路60の駆動方法を説明するタイミングチャートを示す。符号VSIGは中継信号線62に駆動回路5から出力する映像信号である。符号BLは制御信号線63に出力する制御信号を示す。制御信号BL1は制御信号線63−1に、制御信号BL2は制御信号線63−2に、制御信号BL3は制御信号線63−3に出力する。なお、BL11、BL12、BL13は波形なまりが生じた制御信号を示している。

図5に示すように、各中継信号線62には、走査信号がハイ信号である1水平走査期間(1H)に、複数の映像信号線に供給する映像信号VSIGが出力する。映像信号VSIGは各画素に表示される階調に応じて最大VDHから最小VDLの電圧が出力している。

図4に示す分配回路60は3本の映像信号線22に映像信号VSIGを分配する構成であり、3つの制御信号BLは3つのスイッチング素子61をオン状態とするように、順番にハイ信号を出力している。

まず制御信号BL1が制御信号線63−1に出力すると、スイッチング素子61−1がオン状態となり、映像信号線22−1に映像信号が供給される。その後順番に、制御信号BL2が制御信号線63−2を介してスイッチング素子61−2をオン状態として映像信号を映像信号線22−2に供給し、制御信号BL3によって映像信号が映像信号線22−3に供給される。

分配回路60の駆動においては、制御信号線63の引き回し距離が長くなると、制御信号線63の端部では波形なまりが制御信号BL11、BL12、BL13で示すように生じる。そのため、図1、図2で示したように、分配回路60の両端部から制御信号を供給することが有効である。

【0014】

次に図6を用いて、正極性と負極性の映像信号を交互に出力し、かつ駆動回路5から図5に示すように分割して映像信号を供給する構成について説明する。図6は駆動回路5の隣合う2つの出力端子30−1と30−2の出力部について示している。29−1は高耐圧出力アンプで、29−2は低耐圧出力アンプである。対向電極の電圧(以下、コモン電圧と呼ぶ)を一定とする場合の交流化駆動では、コモン電圧に対して正極性の映像信号(以下階調電圧とも呼ぶ)と負極性の階調電圧が画素電極11に印加される。図6に示す回路では、正極性の階調電圧を高耐圧出力アンプ29−1から出力し、負極性の階調電圧を低耐圧出力アンプ29−2から出力する。

図6においては、切換スイッチ36を用いて高耐圧出力アンプ29−1と低耐圧出力アンプ29−2の出力を切り替えている。いま、出力端子30−1から正極性の階調電圧を出力しようとすると、切換スイッチ36は高耐圧出力アンプ29−1と出力端子30−1とを接続する。他方の出力端子30−2は低耐圧出力アンプ29−2に接続され負極性の階調電圧を出力する。

他方、表示データも順番を変更可能となっており、切換スイッチ37はデータ線選択回路125の出力を切り替えてレベルシフタ回路27に接続する。切換スイッチ37によりデータ線選択回路125−1はレベルシフタ回路27−1と27−2の両方に接続可能である。

よって、切換スイッチ37はセレクタ回路24の出力する表示データを正極性の階調電圧を出力する場合は、レベルシフタ回路27−1に供給し、負極性の階調電圧を出力する場合は、セレクタ24の出力をレベルシフタ回路27−2に供給する。

セレクタ回路24は表示データを時分割してデコーダ回路28に出力する。セレクタ回路24はデータ線選択回路125を有しており、分配回路60に供給する制御信号に同期して、時分割制御信号がセレクタ回路24に伝えられている。時分割信号発生回路26では時分割制御信号から時分割信号を作成し、時分割信号線19に出力する。

時分割信号線19は各データ線選択回路125に接続している。データ線選択回路125に入力した時分割信号はデータ線選択回路125を制御する。データ線選択回路125は時分割信号に従いラインラッチ回路23の出力する表示データを選択して、次段のレベルシフタ回路27に出力する。すなわち、ラインラッチ回路23は1水平走査期間(1H)の間表示データを出力するが、セレクタ回路24により1走査期間を複数の期間に分割し、分割した期間毎に異なる表示データがレベルシフタ回路27に伝えられる。

【0015】

次に図7を用いて、信号線62が奇数となった場合の問題点を説明する。

一般に液晶表示パネル1の映像信号線22の数は偶数で、またRGB3本で一組となっているので、中継信号線62の数も一般には偶数であるが、図1に示すように分配回路60を2個設けた場合には、各分配回路60に入力する中継信号線62の数は奇数となる。

中継信号線62が奇数の場合には、駆動回路5の出力が図6で示すように、正極性と負極性の階調電圧を交互に出力するようになっているため、最端部の出力部で、出力アンプが余る問題が生じる。

そのため、図7に示すように、最後の切換スイッチ36−(2n+1)の出力は両方共に信号線62−(2n+1)に接続している。そのため、信号線62−(2n+1)に接続する高耐圧出力アンプ29−1と低耐圧出力アンプ29−2では、例えば高耐圧出力アンプ29−1が信号線62−(2n+1)に階調電圧を出力している場合には、低耐圧出力アンプ29−2は信号線62−(2n+1)に接続されていない状態となる。

【0016】

図8に奇数出力の駆動回路5を2つ並べて配置する場合の問題点を示す。前述したように、駆動回路5−1と5−2共に、最後の切換スイッチ36−(2n+1)の出力は両方共に信号線62−(2n+1)に接続している。

前述したように、正極性の階調電圧と負極性の階調電圧とが交互に出力されているために、3×(2n+1)本目の映像信号線22−3(2n+1)が、例えば正極性の場合には、3×(2n+1)+1本目の映像信号線22−3(2n+1)+1には負極性の階調電圧が供給されている。

そのため、駆動回路5−1が、最初の映像信号線22−1に正極性の階調電圧を出力しているタイミングで、駆動回路5−2は映像信号線22−3(2n+1)+1に負極性の階調電圧を出力することになる。

すなわち、同じ駆動回路5でも正極性の階調電圧から出力開始するものと、負極性の階調電圧から出力開始するものとに分けられることになる。そこで、駆動回路5にマスタ機能とスレーブ機能を持たせ、マスタ機能に設定された駆動回路5は正極性の階調電圧から出力開始し、スレーブ機能に設定された駆動回路5は負極性の階調電圧から出力開始することとした。

なお、配線66はマスタ機能の駆動回路5−1から駆動回路5−2をスレーブ機能に設定するための制御信号線である。

【0017】

次に、図9を用いて2分割した分配回路60−1と分配回路60−2とで、中継信号線62の数を異ならせる場合を示す。駆動回路5−1は出力数が2n本で、駆動回路5−2は出力数を2n−2本として、どちらも偶数本出力とする。この時、駆動回路5−1はマスタ機能に設定され、駆動回路5−2は制御信号線66によりスレーブ機能に設定される。

次に図10に、奇数本出力と双方向シフトに対応した駆動回路5を示す。図中出力アンプ29−1、29−3、29−5、29−7を低耐圧出力アンプとし、出力アンプ29−2、29−4,29−6を高耐圧出力アンプとする。

制御信号線94にハイ信号が出力してアナログスイッチ91がオン状態となると、高耐圧出力アンプ29−2の出力電圧が信号線62−1に供給される。同じく、アナログスイッチ91がオン状態となることで、低耐圧出力アンプ29−3の出力電圧が信号線62−2に供給される。

次に、制御信号線95にハイ信号を出力すると、アナログスイッチ92がオン状態となることで、低耐圧出力アンプ29−1の出力電圧が信号線62−1に供給され、高耐圧出力アンプ29−2の出力電圧が信号線62−2に供給される。

次に、制御信号線96にハイ信号が出力すると、アナログスイッチ93がオン状態となることで、低耐圧出力アンプ29−3の出力電圧が信号線62−1に出力する。

【0018】

図10に示す駆動回路5では、中継信号線62−1に高耐圧出力アンプ29−2から出力する正極性の階調電圧を出力し、中継信号線62−2に低耐圧出力アンプ29−3から出力する負極性の階調電圧を出力する場合には、制御信号94をハイ信号とし、次に、中継信号線62−1に低耐圧出力アンプ29−1から出力する負極性の階調電圧を出力し、中継信号線62−2に高耐圧出力アンプ29−2から出力する正極性の階調電圧を出力する場合には、制御信号95をハイ信号とすることで対応可能である。

また、中継信号線62−1に高耐圧出力アンプ29−2から出力する正極性の階調電圧を出力し、中継信号線62−2に低耐圧出力アンプ29−3から出力する負極性の階調電圧を出力する場合には、制御信号94をハイ信号とし、次に、中継信号線62−1に低耐圧出力アンプ29−3から出力する負極性の階調電圧を出力し、中継信号線62−2に高耐圧出力アンプ29−4から出力する正極性の階調電圧を出力する場合には、制御信号96をハイ信号とすることで対応可能である。

このように、駆動回路5にアナログスイッチ91、92、93を形成することで、低耐圧出力アンプ29−1から高耐圧出力アンプ29−2の順番で、表示データがセレクトされる場合と、低耐圧出力アンプ29−7から高耐圧出力アンプ29−6の順番で、表示データがセレクトされる場合とに対応可能となっている。

【0019】

次に、図11に分配回路60で6本の映像信号線22に映像信号を分配する構成を示す。駆動回路5からは高耐圧出力アンプ29−2と低耐圧出力アンプ29−1からの信号が交互に出力しているため、偶数の映像信号線に分配することは不可能である。そのため、高耐圧出力アンプ29−2と低耐圧出力アンプ29−1の出力を交互に分配回路60に入力している。

図11に示す回路では、中継信号線62−1と中継信号線62−2とがTFT基板2上で交差することになり、絶縁膜を介して2層の導電膜から形成されることになる。

次に、図12に高耐圧出力アンプ29−2と低耐圧出力アンプ29−1の出力をアナログスイッチ85で短絡させて、出力アンプの出力電圧をイコライズする構成を示す。

帰線期間に画素部8のスイッチング素子10をオフ状態として、制御信号線86を用いてアナログスイッチ85により、中継信号線62−1と62−2とを短絡させる。中継信号線62−1と62−2は逆極性であるため、双方に電荷が移動して省電力化に有効である。

次に、図13に高耐圧出力アンプ29−2と低耐圧出力アンプ29−1の出力をアナログスイッチ85で接地電位線87に短絡させて、映像信号線22の電位をGND電位にイコライズする構成を示す。

帰線期間に画素部8のスイッチング素子10をオフ状態として、アナログスイッチ85により、中継信号線62−1と62−2とを接地電位線87に短絡させる。中継信号線62−1と62−2を接地電位とすることで、図12に示す場合に比べて、高耐圧出力アンプ29−2と低耐圧出力アンプ29−1の耐圧を小さくすることが可能である。また、中継信号線62−1と62−2とは逆極性であるため、電荷を接地電位線87を介して供給可能なことから省電力化に有効である。

なお、図1、図2に示すイコライズ回路80も同様に極性の異なる映像信号線22を短絡するものである。

以上、本発明者によってなされた発明を、前記実施例に基づき具体的に説明したが、本発明は、前記実施例に限定されるものではなく、その要旨を逸脱しない範囲において種々変更可能であることは勿論である。

【符号の説明】

【0020】

1 液晶表示パネル

2 TFT基板

5 駆動回路

8 画素部

9 表示領域

10 スイッチング素子

11 画素電極

21 走査信号線

22 映像信号線

60 分配回路

70 フレキシブル基板

80 イコライズ回路

91 アナログスイッチ

100 液晶表示装置

【特許請求の範囲】

【請求項1】

液晶表示パネルと、

該液晶表示パネルを駆動する駆動回路とを有する液晶表示装置において、

前記液晶表示パネル上には、前記駆動回路から出力する映像信号を液晶表示パネル上の複数の映像信号線に出力する分配回路を有し、

前記分配回路は、前記駆動回路から出力する制御信号により制御され、

前記駆動回路は、高耐圧出力アンプと低耐圧出力アンプからの映像信号が交互に、隣合う2本の映像信号出力端子から出力し、

前記分割回路は、前記映像信号線毎にスイッチング素子を有し、

前記スイッチング素子は、前記高耐圧出力アンプからの映像信号と、前記低耐圧出力アンプからの映像信号とが入力する入力端子と、前記映像信号線に前記映像信号を出力する出力端子と、前記制御信号が入力する制御端子とを有し、

前記分割回路は、前記高耐圧出力アンプからの映像信号と、前記低耐圧出力アンプからの映像信号とを同じ前記スイッチング素子を介して前記映像信号線に出力することを特徴とする液晶表示装置。

【請求項2】

前記液晶表示パネル上には走査信号出力回路が形成され、前記駆動回路には前記制御信号出力端子の外側に走査信号線出力回路に接続された走査信号出力端子を有することを特徴とする請求項1に記載の液晶表示装置。

【請求項3】

前記高耐圧出力アンプからの映像信号と、前記低耐圧出力アンプからの映像信号とは交互に前記映像信号線に出力されることを特徴とする請求項1に記載の液晶表示装置。

【請求項4】

隣合う2本の前記映像信号出力端子からは極性が反転した映像信号が出力することを特徴とする請求項1に記載の液晶表示装置。

【請求項5】

第1の基板と、

第2の基板と、

前記第1の基板と第2の基板とに挟まれた液晶組成物と、

前記第1の基板に形成された画素電極と、

前記画素電極に映像信号を供給する映像信号線と、

前記第1の基板に搭載され、前記映像信号を出力する駆動回路と、

前記第1の基板に形成され、前記駆動回路から出力する映像信号を液晶表示パネル上の複数の映像信号線に出力する分配回路を有し、

前記分配回路は、前記駆動回路から出力する制御信号により制御され、

前記駆動回路と前記分配回路とは、複数の中継信号線で接続され、

前記駆動回路の高耐圧出力アンプと低耐圧出力アンプからの映像信号は交互に、隣合う2本の前記中継信号線に入力し、

前記分割回路は、前記映像信号線毎にスイッチング素子を有し、

前記スイッチング素子の入力端子は、前記高耐圧出力アンプと、前記低耐圧出力アンプとに前記中継信号線を介して接続し、

前記スイッチング素子の出力端子は、前記高耐圧出力アンプからの映像信号と、前記低耐圧出力アンプからの映像信号とを前記映像信号線に出力し、

前記中継信号線は、偶数で、隣合う2本の中継信号線を共通に接続することで、前記分配回路に入力する前記中継信号線は奇数であることを特徴とする液晶表示装置。

【請求項6】

前記中継信号線に接続する接続端子の外側に、前記制御信号が出力する接続端子が設けられることを特徴とする請求項5に記載の液晶表示装置。

【請求項7】

前記中継信号線に接続する接続端子の外側に、前記制御信号が出力する接続端子が設けられ、

前記液晶表示パネル上には走査信号出力回路が形成され、

前記駆動回路は、前記制御信号が出力する接続端子の外側に走査信号線出力回路に接続された走査信号出力端子を有することを特徴とする請求項5に記載の液晶表示装置。

【請求項8】

隣合う2本の前記中継信号線には極性が反転した映像信号が出力することを特徴とする請求項5に記載の液晶表示装置。

【請求項1】

液晶表示パネルと、

該液晶表示パネルを駆動する駆動回路とを有する液晶表示装置において、

前記液晶表示パネル上には、前記駆動回路から出力する映像信号を液晶表示パネル上の複数の映像信号線に出力する分配回路を有し、

前記分配回路は、前記駆動回路から出力する制御信号により制御され、

前記駆動回路は、高耐圧出力アンプと低耐圧出力アンプからの映像信号が交互に、隣合う2本の映像信号出力端子から出力し、

前記分割回路は、前記映像信号線毎にスイッチング素子を有し、

前記スイッチング素子は、前記高耐圧出力アンプからの映像信号と、前記低耐圧出力アンプからの映像信号とが入力する入力端子と、前記映像信号線に前記映像信号を出力する出力端子と、前記制御信号が入力する制御端子とを有し、

前記分割回路は、前記高耐圧出力アンプからの映像信号と、前記低耐圧出力アンプからの映像信号とを同じ前記スイッチング素子を介して前記映像信号線に出力することを特徴とする液晶表示装置。

【請求項2】

前記液晶表示パネル上には走査信号出力回路が形成され、前記駆動回路には前記制御信号出力端子の外側に走査信号線出力回路に接続された走査信号出力端子を有することを特徴とする請求項1に記載の液晶表示装置。

【請求項3】

前記高耐圧出力アンプからの映像信号と、前記低耐圧出力アンプからの映像信号とは交互に前記映像信号線に出力されることを特徴とする請求項1に記載の液晶表示装置。

【請求項4】

隣合う2本の前記映像信号出力端子からは極性が反転した映像信号が出力することを特徴とする請求項1に記載の液晶表示装置。

【請求項5】

第1の基板と、

第2の基板と、

前記第1の基板と第2の基板とに挟まれた液晶組成物と、

前記第1の基板に形成された画素電極と、

前記画素電極に映像信号を供給する映像信号線と、

前記第1の基板に搭載され、前記映像信号を出力する駆動回路と、

前記第1の基板に形成され、前記駆動回路から出力する映像信号を液晶表示パネル上の複数の映像信号線に出力する分配回路を有し、

前記分配回路は、前記駆動回路から出力する制御信号により制御され、

前記駆動回路と前記分配回路とは、複数の中継信号線で接続され、

前記駆動回路の高耐圧出力アンプと低耐圧出力アンプからの映像信号は交互に、隣合う2本の前記中継信号線に入力し、

前記分割回路は、前記映像信号線毎にスイッチング素子を有し、

前記スイッチング素子の入力端子は、前記高耐圧出力アンプと、前記低耐圧出力アンプとに前記中継信号線を介して接続し、

前記スイッチング素子の出力端子は、前記高耐圧出力アンプからの映像信号と、前記低耐圧出力アンプからの映像信号とを前記映像信号線に出力し、

前記中継信号線は、偶数で、隣合う2本の中継信号線を共通に接続することで、前記分配回路に入力する前記中継信号線は奇数であることを特徴とする液晶表示装置。

【請求項6】

前記中継信号線に接続する接続端子の外側に、前記制御信号が出力する接続端子が設けられることを特徴とする請求項5に記載の液晶表示装置。

【請求項7】

前記中継信号線に接続する接続端子の外側に、前記制御信号が出力する接続端子が設けられ、

前記液晶表示パネル上には走査信号出力回路が形成され、

前記駆動回路は、前記制御信号が出力する接続端子の外側に走査信号線出力回路に接続された走査信号出力端子を有することを特徴とする請求項5に記載の液晶表示装置。

【請求項8】

隣合う2本の前記中継信号線には極性が反転した映像信号が出力することを特徴とする請求項5に記載の液晶表示装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2013−33284(P2013−33284A)

【公開日】平成25年2月14日(2013.2.14)

【国際特許分類】

【出願番号】特願2012−239987(P2012−239987)

【出願日】平成24年10月31日(2012.10.31)

【分割の表示】特願2008−60947(P2008−60947)の分割

【原出願日】平成20年3月11日(2008.3.11)

【出願人】(502356528)株式会社ジャパンディスプレイイースト (2,552)

【出願人】(506087819)パナソニック液晶ディスプレイ株式会社 (443)

【Fターム(参考)】

【公開日】平成25年2月14日(2013.2.14)

【国際特許分類】

【出願日】平成24年10月31日(2012.10.31)

【分割の表示】特願2008−60947(P2008−60947)の分割

【原出願日】平成20年3月11日(2008.3.11)

【出願人】(502356528)株式会社ジャパンディスプレイイースト (2,552)

【出願人】(506087819)パナソニック液晶ディスプレイ株式会社 (443)

【Fターム(参考)】

[ Back to top ]