液滴堆積ウェルの形成方法、有機電子デバイス、有機電子デバイスの形成方法

【課題】改良された有機電子デバイスおよびその製造技術を提供すること。

【解決手段】本発明は、有機電子デバイスの液滴堆積ベースの製造のための構造における液滴堆積ウェルの形成方法を提供する。前記方法は、基板上に親水性材料層を堆積させる工程、前記親水性材料層の上にバンク材料層を堆積させる工程、前記バンク材料層をパターニングして1または2以上の前記液滴堆積ウェルを形成するバンクを規定する工程、前記パターニングされたバンク材料層をレジストとして使用して自己整合プロセス中において前記親水性材料層をエッチングする工程を含む。

【解決手段】本発明は、有機電子デバイスの液滴堆積ベースの製造のための構造における液滴堆積ウェルの形成方法を提供する。前記方法は、基板上に親水性材料層を堆積させる工程、前記親水性材料層の上にバンク材料層を堆積させる工程、前記バンク材料層をパターニングして1または2以上の前記液滴堆積ウェルを形成するバンクを規定する工程、前記パターニングされたバンク材料層をレジストとして使用して自己整合プロセス中において前記親水性材料層をエッチングする工程を含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、有機電子デバイス、特に、有機発光ダイオード(OLEDs)の構造および製造方法に関するものである。

【背景技術】

【0002】

本発明の理解を助けるために、先ず、OLEDディスプレイのいくつかの特徴およびその製造におけるいくつかの問題点を説明する。しかしながら、本発明の実施態様はOLEDディスプレイを特に引用して記載されるが、この技術は有機電子デバイスの製造一般に適用できることは明らかである。

【0003】

有機発光ダイオード(OLED)は電気光ディスプレイの特に有利な型である。これは、明るく、カラフルで、立ち上がりが早く、広い視野角を提供し、多様な基板上に安く簡単に製造することができる。有機(本明細書では、有機金属を含む)LEDは、使用される材料に応じて、多色(またはマルチカラーディスプレイ)の範囲で、ポリマーまたは低分子を使用して製造され得る。典型的なOLEDデバイスは2つの有機材料層を有し、その1つは発光ポリマー(LEP)、オリゴマーまたは発光低分子量材料のような発光材料の層であり、他はポリチオフェン誘導体またはポリアニリン誘導体のような正孔輸送材料の層である。

【0004】

有機LEDは、単色または多色画素ディスプレイを形成するために、画素のマトリックス中の基板上に堆積され得る。多色ディスプレイは、赤、緑、青色発光画素のグループを使用して形成される。いわゆるアクティブマトリックスディスプレイは、記憶素子、通常、各画素に連結された蓄積容量およびトランジスタを有し、他方、パッシブマトリックスディスプレイはそのようなメモリ素子を有さず、その代わり、固定した画像の印象を与えるために繰返しスキャンされる。

【0005】

図1はOLEDデバイス100の例の垂直断面図を示す。アクティブマトリックスディスプレイにおいては、画素の一部領域は連結された駆動回路(図1には図示しない)によって占められている。このデバイスの構造は、例示のために簡略化されている。

【0006】

OLED100は、通常は0.7mmまたは1.1mmのガラス、任意に透明なプラスチックの基板102を有し、その上にアノード層106が堆積される。アノード層は、通常約150nmの厚さのITO(インジウム錫酸化物)を含み、その上に、通常約500nmのアルミニウムの金属接続層が提供され、しばしばアノード金属と呼ばれる。ITOで被覆されたガラス基板および接続金属は、Corning,USAから購入することができる。接続金属(および任意にITO)は、ディスプレイを覆い隠さないように、従来のフォトリソグラフィーとこれに続くエッチングプロセスにより望まれるようにパターニングされる。

【0007】

実質的に透明な正孔輸送層108aはアノード金属上に供給され、続いて電子発光層108bが供給される。バンク112は、例えばポジ型またはネガ型フォトレジスト材料から基板上に形成することができ、ウェル114を規定し、この中には、例えば、液滴堆積またはインクジェット印刷技術によって、これらの活性有機層が選択的に堆積され得る。したがって、ウェルは発光領域またはディスプレイの画素を規定する。

【0008】

次いで、カソード層110が、例えば、物理的気相蒸着によって適用される。カソード層は、通常、厚いアルミニウムのキャップ層で覆われたカルシウムまたはバリウムのような低仕事関数の金属を有し、任意に、例えば、電子エネルギーレベルの適合(matching)を改良するために、電子発光層に隣接してフッ化リチウムの層などの追加の層を有する。カソード線の相互の電気的絶縁はカソードセパレータ(図3bの要素302)を使用して達成され得る。通常、多数のディスプレイが単一基板上に形成され、形成プロセスの最後で基板はスクライブされ、ディスプレイが互いに分離された後、酸化および湿気の浸入を防止するためにカプセル缶が個別に付着される。

【0009】

この通常のタイプの有機LEDは、変化する駆動電圧および効率において波長範囲に渡って発光するために、ポリマー、デンドリマーおよびいわゆる低分子を含む材料の範囲を使用して製造され得る。ポリマーベースのOLED材料の例は、WO90/13148、WO95/06400およびWO99/48160に記載されており、デンドリマーベースの材料の例はWO99/21935およびWO02/067343に記載されており、低分子OLED材料の例はUS4,539,507に記載されている。前述のポリマー、デンドリマーおよび低分子は1重項励起子の放射性崩壊によって発光(蛍光)する。しかしながら、励起子の75%までは、通常、非放射性崩壊を行う3重項励起子である。3重項励起子の放射性崩壊による電子発光(燐光)は、例えば、“Very high−efficiency green organic light−emitting devices based on electrophosphorescence”M.A.Baldo,S.Lamansky,P.E.Burrows,M.E.Thompson,and S.R.Forrest Applied Physics Letters,Vol.75(1)pp.4−6,July5,1999に開示されている。ポリマーベースのOLEDの場合、層108は、正孔輸送層108aおよび発光ポリマー(LEP)電子発光層108bを有する。電子発光層は、例えば、約70nm(乾燥)の厚さのPPV(ポリ(p−フェニレンビニレン))を有することができ、正孔輸送層は、アノード層と電子発光層の正孔エネルギーレベルの適合(match)を促進し、例えば、PEDOT:PSS(ポリスチレン−スルフォネート−ドープ−ポリエチレン−ジオキシチオフェン)の約50〜200nmの厚さ、好ましくは、約150nm(乾燥)の厚さを有することができる。

【0010】

図2は、一つの活性カラー層の堆積後の3色アクティブマトリックス画素が形成されたOLEDディスプレイ200の一部を上方から(基板を通さずに)見た図である。同図は、ディスプレイの画素を画定するバンク112およびウェル114のアレイを示す。

【0011】

図3aは、パッシブマトリックスOLEDディスプレイをインクジェット印刷するための基板300を上方から見た図である。図3bは、図3aで線Y−Y’に沿って基板を通して見た横断面図である。

【0012】

図3aおよび図3bを参照すると、隣接するカソード線(領域304に堆積される)を分離するための複数のカソードアンダーカットセパレータ302が基板に供給される。複数のウェル308がバンク310によって規定され、各ウェル308の周囲にそって形成され、アノード層306をウェルの底に露出させる。バンクの端部または面は図示されるように、通常10〜40°の角度で基板の表面に向かって先細になる。バンクは、堆積される有機材料の溶液で濡れないように疎水性の表面を提供し、堆積される材料がウェル内におさまるのを助ける(極性または非極性溶媒が使用され得るが、通常使用される溶媒は極性を有する)。これは、EP0989778に開示されるようにO2/CF4プラズマによりポリイミドのようなバンク材料を処理することによって達成される。あるいは、WO03/083960に開示されるように、フッ素化ポリイミドのような弗化材料の使用によってプラズマ処理工程は回避され得る。

【0013】

前述したように、バンクおよびセパレータ構造はレジスト材料、例えば、バンクのためにポジ型(またはネガ型)レジストが、セパレータのためにネガ型(またはポジ型)レジストを使用して、レジスト材料から形成され得る。これらのレジストは、ポリイミドベースであり得、基板上にスピンコートされるか、またはフッ素化またはフッ素系フォトレジストが使用され得る。示される例においては、カソードセパレータは約5μmの高さおよび約20μmの幅である。バンクは一般には20μm〜100μmの幅であり、示された例は、(バンクが約1μmの高さとなるように)各端部において4μmのテーパーを有する。図3aの画素は約300μm平方であるが、後述するように、画素の大きさは、意図する用途に応じてかなり変化し得る。

【0014】

インクジェット印刷技術を用いた有機発光ダイオード(OLED)の材料の堆積技術は、多くの文献に記載されており、例えば、T.R.Hebner,C.C.Wu,D.Marcy,M.H.Lu and J.C.Sturm,“Ink−jet Printing of doped Polymers for Organic Light Emitting Devices”,Applied Physics Letters,Vol.72,No.5,pp.519−521,1998;Y.Yang,“Review of Recent Progress on Polymer Electroluminescent Devices,”SPIE Photonics West:Optoelectronics ’98,Conf.3279,San Jose,Jan.,1998;EPO 880303;および“Ink−Jet Printing of Polymer Light−Emitting Devices”,Paul C. Duineveld,Margreet M.de Kok,Michael Buechel,Aad H.Sempel,Kees A.H.Mutsaers,Peter van de Weijer,Ivo G.J.Camps,Ton J.M.van den Biggelaar,Jan−Eric J.M.Rubingh and Eliav I.Haskal,Organic Light−Emitting Materials and Devices V.Zakya H.Kafafi,Editor,Proceedings of SPIE Vol.4464(2002)に開示されている。インクジェット技術は、低分子およびポリマーLEDの両者の材料を堆積させるために使用され得る。

【0015】

有機電子材料を堆積させるために、0.5%〜4%の溶媒に溶解した材料を有する揮発性の溶媒が一般的に使用される。これは、乾燥するのに数秒から数分かかることがあり、最初の「インク」容量に比較して相対的に薄い膜をもたらす。しばしば、乾燥材料の十分な厚さを提供するためには、好ましくは乾燥が始まる前に、複数の液滴が堆積される。使用され得る溶媒としては、シクロヘキシルベンゼンおよびアルキル化ベンゼン、特に、トルエンまたはキシレンが使用される。他は、WO00/59267、WO01/16251およびWO02/18513に記載されている。これらの混合の溶媒も使用することができる。Litrex Corporation of California,USAの装置のような正確なインクジェットプリンターが使用される。適切なプリントヘッドは、NH,USAのXaar of Cambridge,UK and Spectra,Inc.から入手できる。いくつかの特に有利な印刷手法は、本出願人の出願である2002年11月28日出願UK特許出願0227778.8(および対応するPCT公開WO2004/049466)に記載されている。

【0016】

インクジェット印刷は、有機電子デバイスの材料の堆積に多くの利点を有するが、この技術に関連する欠点もいくつか存在する。しかしながら、浅い端部を有するウェル内に堆積された溶解した有機電子材料は、乾燥して比較的薄い端部を有する薄膜を形成することがわかっている。図4aおよび4bはこのプロセスを図示している。

【0017】

図4aは、溶解した材料402で満たされた壁308の簡略断面400を示し、図4bは、材料が乾燥して固体薄膜404を形成した後の同じウェルを示す。この実施例において、バンクの角度は約15°であり、バンクの高さは約1.5μmである。見られるように、ウェルは通常、ふちまでいっぱいになるまで満たされる。溶液402はプラズマ処理されたバンク材料に対する接触角θcとして典型的には30°〜40°、例えば約35°を有する。これは、溶解した材料402の表面が接触する(バンク)材料と、例えば、図4aにおける402aの角度を作る。溶媒が蒸発するにつれて、溶液はより濃縮され、溶液の表面は基板に向かってバンクの傾き面を下方に移動し、乾燥端部の留まりが基板上の最初に付着した濡れ端部とバンクの足(ウェルの底)の間の点で生じ得る。図4bに示されるように、この結果、乾燥材料404の薄膜は非常に薄くなり得、バンク面に接する領域404aにおいて、例えば、10nm以下のオーダーの厚さとなる。

【0018】

出願人は、WO2005/076386として公開された2004年2月5日出願のUK特許出願0402559.9において、ウェルの端部に向かって溶液を押す効果を有するアンダーカットバンクの使用により、より均一な充填を得るのを助けることを記載した。しかしながら、このようなバンクは製造するのが容易ではなく、一般的に、高価でありプロセスの条件に敏感なネガ型フォトレジストを使用する。したがって、ポジ型フォトレジストの使用により適した改良された技術の必要性が存在する。

【0019】

他の問題点は、画素(ウェル)の大型化(例えば300μmの画素ピッチを形成するために使用される240μm〜260μmの開口を備えたウェル)に伴い生じる。インク液滴の容量は液滴の特徴的な長さの3乗に比例し、表面の保護範囲は画素の寸法の2乗に比例し、このための任意のインクの薄め方においては、多くの材料が大きな画素に堆積され、そのためより薄いインクが必要とされるようになる。例えば、大きな画素および80nmの望まれるPEDOT薄膜の厚さにおいては、約1%のインクの濃度が導入され得るが、1パーセントのインクを広げて、濡らし大きな画素を満たすのは困難である。これは、いわば、満杯であふれるばかりの画素は120nmの厚さの薄膜をもたらすため、500μm四方を超える画素の製造は困難となる。さらに、製造プロセスにおいて、インクの希釈を変えることは高価である。

【0020】

一般的に、画素ウェルの底部はITOを含み、これは、通常、10度未満(例えば、5〜7度)の低接触角を有し、相対的に良好な濡れ性(親水性)を提供する。しかしながら、特に、大きな画素を有すると、円形を有する堆積された液滴ほど濡れ性は完全ではなく、溶媒はウェルの底内の点で留まる傾向にあるため、堆積された液滴は通常、よりでこぼこの端部を有する。上述したように、バンク上の溶媒の接触角は相対的に高いので、より多くの溶媒をウェルに加えるほど、溶媒がバンクを上るより液滴の高さは高くなる傾向があり、乾燥すると表面エネルギーによって溶液はウェルの端部から離れる傾向がある。これは、PEDOT堆積について特に問題であり、この薄い端部はカソード(ITO)と覆う発光ポリマー(LEP)との直接接触をもたらし、結果、不完全または効率の低い画素となり得る。EP0993235においては、セイコーエプソンは、画素ウェルの底の内部端部のアノードを覆う誘電体層を堆積させることによりこの問題の解決を狙っているが、これは、配置の許容誤差の必要性を考慮すると有効な画素面積を20%まで減らす欠点がある。

【先行技術文献】

【特許文献】

【0021】

【特許文献1】国際公開2005/076386号パンフレット

【特許文献2】欧州特許0993235号明細書

【発明の概要】

【発明が解決しようとする課題】

【0022】

したがって、これらの問題を解決する改良された有機電子デバイス構造および製造技術、特に、有機電子材料を溶媒ベースの堆積プロセスに広げるのを助ける必要性がある。

【課題を解決するための手段】

【0023】

したがって、本発明は、有機電子デバイスの液滴堆積ベースの製造のための構造における液滴堆積ウェルの形成方法を提供する。前記方法は、基板上に親水性材料層を堆積させる工程、前記親水性材料層の上にバンク材料層を堆積させる工程、前記バンク材料層をパターニングして1または2以上の前記液滴堆積ウェルを形成するバンクを規定する工程、前記パターニングされたバンク材料層をレジストとして使用して自己整合プロセス中において前記親水性材料層をエッチングする工程を含む。

【0024】

実施態様において、この方法は、1つはバンク材料について、もう1つは親水性(またはスペーサー)層についての2つの独立したマスク工程の必要性を省く。当業者は、一般的に、この方法が適用される基板は、ITOのような最初の透明導電体の下層を有するものが購入または用意されてきたことを理解する。本方法のいくつかの好ましい実施態様において、バンク材料は、レジスト、好ましくは、ポジ型レジストを含む。好ましくは、バンクはバンク材料の一層のみ(これは好ましくは疎水性である)および親水性材料(酸化物のような)の1層のみを有する。

【0025】

本発明の方法の好ましい実施態様において、親水性材料は、誘電体材料、特にSiO2を有する。ただし、窒化シリコンおよびシリコン酸窒化物のような他の誘電体材料またはレジストも適用できる。他の実施態様において、親水性材料は、アルミニウム、クロムまたはモリクロムのような親水性金属を含む。このような実施態様において、例えば、前記金属は、アノードトラック抵抗を減らすためにITO上に形成されたアノード金属であってもよい。この方法を用いて製造されたOLEDデバイスの実施態様において、前記金属は有機電子材料に、特にPEDOTに向けられることができ、その後ウェル中に堆積される。しかしながら、前記金属が関係する材料(PEDOT)のための不良な電子注入体(高い仕事関数を有する)である場合、これは、実質的に絶縁層として機能するのでこの接触はデバイスの十分な作動とならない。

【0026】

自己整合エッチング工程においては、バンクレジストはマスクとして働くか、等方性または非等方性であり得る。好ましい実施態様において、エッチングはプラズマエッチングを含む。等方性エッチングは親水性層の下を切り取る(したがって、基板および上部バンク層の間のスペーサーとして働く)。非等方性エッチングは、バンクの端部(これは通常先細である)が終了する親水性層の端部をほぼ垂直下方に切除する。等方性エッチングの場合、ドライエッチング、特にプラズマガスエッチングが採用されることができ、これは下方切除内で自己整合し、下方切除の深さが制御される。あるいは、溶液エッチングを導入することができ、これによりエッチング液がある限りエッチングが続いて行われる。非等方性エッチングについては、ドライプラズマエッチングが好ましい。

【0027】

前記デバイス構造のアンダーカットの実施態様については、親水性(スペーサー)層の幅は500nm未満、例えば、50nmと200nmの間、およびいくつかの実施態様において約100nmであり得る。他の実施態様において、親水性層は(効果的な)絶縁を提供しバンク端部の底部での短絡を減らすのに役立つ場合(堆積された有機電子材料が溶媒乾燥効果のため、より薄くなる傾向にある場合)、親水性層はより薄くすることができ、例えば、100nm、50nm、10nmまたは5nm未満である。限界の厚さは、連続的な絶縁膜を形成する要望によって決まり、例えば、SiO2では約2nmである。非等方性エッチングは、下方切除を実質的に防止し、棚を残すために切り取られるバンク材料の量を減らすので、ウェルの底部で絶縁性の棚を形成する方法の実施態様として好ましい。

【0028】

いくつかの特に好ましい実施態様においては、レジストストリッピング法、好ましくはO2プラズマアッシングのようなプラズマアッシング法がエッチングの後に行われる。これは、最も薄くなっている(先細り)バンクの底部の一部、すなわち、ウェルの底部に隣接する部分を取り除き(同時にバンクの全体の厚みを減らす)、ウェルの底部に隣接する親水性材料を露出させる。これは、バンク材料の穴を親水性層中のものより大きくなるように拡大させる。親水性材料層の露出部分は、前述したように、絶縁性のスペーサーとして働き、ウェルの底部の端部の短絡を防止するのに役立つ。特に、これは親水性PEDOT溶液を引きつけ、これはこの材料の露出部分に効果的に付着し、このような堆積された材料の液滴の端部を留める。さらに、PEDOT溶液はこのように閉じ込められるので、バンク材料の層の表面エネルギー特性は、発光ポリマー(LEP)層のような後の材料の堆積層のために望まれる特性に向けて独立して調整され得る。バンクレジストの場合、例えば、これは、LEPの良好な閉じ込めのために、バンク材料をCF4プラズマで処理して疎水性にすることによって行われ得る。(この「調整」は、わずかな「汚染効果」があるだけで、下層酸化物の親水性にほとんど影響を与えない。)あるいは、「テフロン(登録商標)化」またはフッ素化レジストが疎水性のバンク特性を達成するために導入され得る。したがって、この方法のこれらの実施態様は、大まかに言って、いわゆるPEDOTおよびLEPの溶液堆積の結合を切り離すための異なる望まれる表面エネルギー処理(親水性及び疎水性)を許容する。さらに、水中のいわゆるPEDOT溶液の高いバンク接触角は例えば90〜110°であり、PEDOTをバンクから離れさせ、したがってこの材料を閉じ込めることを助ける。

【0029】

したがって、他の側面において、本発明は、有機電子デバイスの液滴堆積ベースの製造のための構造における液滴堆積ウェルを形成する方法を提供し、この方法は、基板上に親水性材料の層を堆積させる工程、前記親水性材料の層の上にレジスト材料の層を堆積させる工程、前記レジスト材料の層をパターニングして前記液滴堆積ウェルの1または2以上を形成するバンクを規定する工程、前記親水性材料の層をパターニングして、前記1または2以上の液滴堆積ウェルの底部領域の少なくとも一部から前記親水性材料を除く工程、およびレジストストリッピング法を使用して前記液滴堆積ウェルの1または2以上を形成する前記バンクの底部に隣接する親水性材料の前記パターンニングされた層の上部表面の一部を露出する工程を含む。

【0030】

実施態様において、バンクを超えて突き出し、下層ITOと同様の表面エネルギーを有する低部層の供給はコストおよび開口率に大きな影響を与えずに生産性と均一性を助けることが可能である。レジストストリッピング(アッシング)がなされるこの構造は自己整合プロセスで形成される必要はなく、例えば、2マスクプロセスを使用して形成されることができたはずである。

【0031】

関連する側面において、本発明は上記の方法を使用して形成される有機電子デバイスを提供する。特に、このようなデバイスは、有機電子材料で満たされた複数の液滴堆積ウェルの下の親水性材料のパターニングされた層を有する基板を含み、前記液滴堆積ウェルの1または2以上を形成する前記バンクの底部に隣接する親水性材料の前記パターニング層の上部表面の一部は前記有機電子材料にさらされる。

【0032】

さらに他の側面において、本発明は有機電子デバイス構造を提供し、前記構造は、基板、および前記基板により支持され、有機電子材料の溶媒ベースの堆積のためのウェルを規定するバンク層を含み、前記構造は、さらに、前記ウェルの内部端部および前記ウェルの底部にある平縁を規定するためにパターニングされる平縁層を含む。

【0033】

好ましくは、前記平縁は、シリコンの酸化物および/または窒化物のような親水性材料を有する。前記平縁層は、前記デバイスの一部を形成するまたは前記装置に連結される薄膜トランジスタの酸化物層のような有機電子デバイスのいくつかの他の部分も形成する層を好都合に含むことができる。

【0034】

1つの実施態様において、前記平縁は基板に向かって先細りする前記バンクの一部に横たわっている。他の実施態様において、1または2以上の層はパターニングされて前記ウェルの内側端部において階段を規定し、前記平縁は前記階段に隣接する。例えば、好ましい実施態様において、前記ウェルは、アノードまたはITO層のような底部層を有し、また、階段層(これも、前記デバイスの既存の層を「再使用」して供給され得る)は、前記ウェルの内部端部に隣接する前記底部層において高さの階段的変化を提供するように前記底部層と前記基板の間に供給される。この場合、前記平縁は前記底部層におけるこの階段に接する。いくつかの実施態様において、2段は、2つ(またはそれ以上)の下側「階段」層を使用して前記底部層に規定され、前記ITOの下により高いスペーサー積層、したがって前記ウェルの端部での改良された溶媒の留めのための広い平縁領域を提供する。実施態様において、1または2以上の階段層は、1または2以上の金属層、ドープされていないシリコン層、ドープされたシリコン層および第2金属層を有し得る。これらの層は、例えば、OLEDディスプレイデバイスの画素に連結された薄膜トランジスタのための既存の製造プロセスの一部として既に存在し得る。好ましくは、このようなデバイスにおいて、前記バンク層は、ポジ型フォトレジストを含み、従来どおり基板に向かって先細る。この場合の有機電子材料の堆積層は、導電性(正孔輸送)層およびこれを覆う発光層を有することができる。

【0035】

他の側面において、本発明は、有機電子材料の溶媒ベースの堆積のための少なくとも1つのウェルを有する基板上の有機電子デバイスの形成方法を提供し、前記方法は、前記デバイスを形成するための前記有機電子材料の溶媒ベースの堆積の前に前記ウェルの内部端部の平縁を規定するために前記平縁層を堆積させ、非等方的にエッチングする工程を含む。

【0036】

好ましくは、前記平縁材料は、有機電子材料を堆積させるために使用される単一の溶媒または溶媒の混合物で濡れるように選択または処理される。好ましくは、このような濡れは、前記平縁と前記溶媒または溶媒混合物との間の接触角として15°未満、より好ましくは10°未満を提供する。

【0037】

本発明は、さらに、本発明の1つの側面の方法によって製造された有機電子デバイス、特に、アクティブまたはパッシブOLEDディスプレイデバイスを提供する。本発明のこれらおよび他の側面を、添付の図面を参照して単に例示としてさらに説明する。

【0038】

図5を参照すると、これは、アクティブマトリックスOLEDディスプレイの画素のウェル502のための第1構造500の垂直断面図および上面図を示す。ウェル502は基板506に向けて先細るバンク504によって規定され、その上を、前記画素のアノードを提供するITO層508が覆う。ウェル502内には、PEDOT層510が堆積され、その上を発光ポリマー(LEP)層512が覆う。図5は、PEDOTおよびLEP層の堆積の前の構造の断面図も示す。

【0039】

酸化物スペーサー層514はITO層518の上、バンク層504の下に供給される。これは、前記ポジ型バンクフォトレジストのパターニングの後、従来の溶液またはドライ等方性エッチング法を使用してエッチングされる。このエッチングプロセスは、ウェル502の低い内部端部周辺の上に突き出る棚516(上面図における破線によって示される)をもたらし、堆積工程において溶解したPEDOTを有する溶媒が流れ込むことができるくぼみを提供する。前記PEDOT溶液は毛細管現象により前記くぼみに自然に流れ込むが、前記酸化物スペーサー514は親水性であるため、前記溶媒は前記棚516の下の層514の露出された内部端部にも付着する。実施態様におけるこれら2つの効果の結合が信頼性のあるPEDOT端部の厚さプロフィールを提供する。

【0040】

PEDOTは、乾燥時に、このへこんだ端部に付着し続けるが、(疎水性の)バンクには残らない。PEDOT溶液は親水性層514の露出された端部および/または前記くぼみの毛細管現象によって効果的に留まるので、バンクは、例えば、CF4により処理されることができ、PEDOT溶液の要求から大きく独立したLEPの堆積に特に適した表面(必要な程度まで疎水性にされる)を提供する。

【0041】

単純な例の製造過程において、ITOで被覆された基板は任意の供給者から購入され、パターニングされ、次いで、二酸化シリコン、一酸化シリコンまたはシリコン酸窒化物のようなブランケット酸化物で被覆され、親水性層を提供する。このブランケット酸化物は、例えば、スピンオンガラスを含むことができる。次いで、ポジ型フォトレジスト層504がスピンコートされ、フォトリソグラフィーによってパターニングされる(露光、現像および洗浄)。次いで、追加のマスクを必要とせずに、くぼみが酸化物スペーサー層514の等方性エッチングバックによって形成される。このプロセスは、バンクが有効に前記酸化物層のエッチングマスクを供給するので、自己整合プロセスである。

【0042】

図6は、図5の画素構造500と一緒に、および/または後述する本発明の第1および第2の側面の他の実施態様と一緒に製造され得る底面ゲート型TFT構造600の垂直断面図を示す。図6において、図5と同じ番号は同じ構成要素を示す。この例において、基板はこの時点でITOによってパターニングされていないか、代わりに、第1の相対的に厚い金属層602はガラス基板506上に堆積され、パターニングされてTFTのゲート金属を提供する。例えば、シリコン窒化物からなるゲート誘電体層604は、ゲート金属602上に堆積され、ドープされていないアモルファスシリコン層606およびドープされたアモルファスシリコン層608の堆積およびパターニングが続き、それぞれ、TFTのチャネルおよびドレイン/ソース領域を形成する。次いで、第2の金属層610が堆積され、パターニングされて、トランジスタおよび絶縁層612のためのソースおよびドレイン導電体を提供し、次いで、例えば、シリコン窒化物が前記構造上に堆積され、ソースおよびドレイン接続孔612aがエッチングされる。次いで、ITO層508が堆積されて前記ソースおよびドレイン電極への接続が形成され、これらを1または2以上の隣接する画素に結合する。従来の工程においては、このITO層が、バンクフォトレジスト層504が堆積される前の最後の層であるが、このTFT構造が、例えば、図5の改良されたウェル構造と関連して使用されるとき前記バンク層504の堆積およびパターニング前に、前記ITO層の上に追加の酸化物層(図6に示さない)が堆積される。

【0043】

次に、図7を参照すると、これは、図5で例示した原理を採用するより典型的な「リアルライフ」ウェル構造を示す。

【0044】

図7および続く図において、図5および図6の同じ番号は同じ構成要素を示す。

【0045】

図7に示されたウェル構造700の実施態様において、2つの下層シリコン窒化層(誘電体層604および絶縁体層612)が示されている。

【0046】

図8は、棚が絶縁層612と第2金属層610の結合によって供給されるウェル構造800の追加の実施態様を示す。前の2つの実施態様と異なり、この実施態様は単に部分的自己整合であり、さらに、いずれかのシリコン層の前にITO層508の堆積を含む。これは、TFT構造はただ画素のアクティブ領域に使用されるため、アクティブマトリックスディスプレイにおいて可能である。しかしながら、この実施態様において層の連続は異なるが、同じ一般的な原理が採用される。

【0047】

概要において、シリコン606,608、金属610および窒化物612層はバンク端部内に配列され、次いで、前記金属端部の下にある前記シリコン層の等方性エッチングバックが導入されてこの構造を生成する(前記金属は、前記シリコン端部によって攻撃されないので)。金属および/または窒化物層は同時にパターニングされる。

【0048】

ウェル構造800において、前記棚の下のスペースは前の実施態様のそれより潜在的に深く、実施態様において(示されるように)、この深さはPEDOT層によって完全に満たされない可能性がある。このような場合も、電子発光層は棚の下に伸びる。PEDOT層および電子発光層は、例えば、示されるドープされたおよびドープされないシリコン(共に親水性)のようなそれぞれ異なるスペーサー層に連結されていることが可能である。有機材料層の厚さは最大500nmであり得、ただし、厚さは、一般的により薄く、例えば、50nm〜200nmであり、図8の実施態様において、棚の下のくぼみの全体高さは最大500nm(またはこれ以上)であり得る。

【0049】

次に、図9を参照すると、これは、シリコン堆積の前のITO堆積と共に部分的自己整合エッチング工程を使用するウェル構造900の他の実施態様を示す。概要において、シリコンおよび窒化物層がバンク端部に配列されて、次いで、シリコン層が窒化物端部の下で等方的にエッチングバックされる。これは、ドープされおよびドープされないシリコン層が異なる段階でエッチングされるため、TFTを組み込む構造において可能である。

【0050】

図10は、酸化物スペーサー層514がITO層508の後に、ただし(シリコン窒化物)絶縁層612の前に堆積されるウェル構造1000の他の実施態様を示す。この構造の形成は、くぼみが前記酸化物層の等方性エッチングバックによって形成されるので、部分的に自己整合される。PEDOT溶液がくぼみに入り、親水性および/または毛細管現象によってウェルの端部に留まり、信頼性のあるPEDOT端部厚みプロフィールを提供するのを助ける。

【0051】

次に、図11を参照すると、これは、本発明の第2の側面のウェル構造1100の第1の実施態様の垂直断面図(溶媒ベースの有機材料堆積の前および後)および上面図を示す。

【0052】

再び、この実施態様およびこれに続くものにおいて、上記の層と同様の層は同じ番号によって示される。

【0053】

図11において、第1の金属層602がパターニングされて、その内側端部のすぐ外側のウェルの周囲に「画像フレーム」を提供する。これは、上に覆うITO508における階段を形成する。次いで、ブランケット酸化物層が堆積されて、当業者に周知な態様で等方的に(垂直に)エッチングされ、垂直端部上の材料の平縁1102、1102aを生成する。これら酸化物平縁は親水性材料を有し、および前記ウェルの端部にPEDOT含有溶媒を留めるのに役立つ(ただし、この溶媒は疎水性のバンク端部に乗り上げない傾向にある)。この疎水性のCF4表面処理は、PEDOT溶媒がバンク上に、たとえ上るとしてもほんの短い距離だけ上るので、PEDOT堆積から大きく独立したLEP溶媒によって適用されることができる。バンク材料、処理および/またはLEP溶媒は、したがって、例えば、LEP溶媒がバンクをある程度濡らし、示されるようにバンクを上るLEPの尾を残すように調整され得る。図11はバンク端部と平縁の正確な配置を示すが、実際にはこれはなくてもよいにしても、この構造は、バンク端部の配置において小さなばらつき(これは、特に先細りされたバンク端部で生じ得る)を許容することが理解されよう。

【0054】

図12は、本発明の第2の側面によるウェル構造1200の第1の代替の実施態様を示す。図11に示される実施態様のように、これはある程度理想化された構造を表す。再び、平縁1102が形成されるが、この場合、金属階段はITO層508の下ではなく上を覆う。前と同様、平縁1102はウェル502の底部における内部端部の周辺の「画像フレーム」を提供する。図12の実施態様における注意すべき特徴は、金属602とLEP層512の直接接触である。この配列は、仕事関数の相違のために金属とLEPの間の直接接触領域から光が放射されないかまたはほとんどされないので、バンク配列に対する改良された頑丈さを提供する。金属602は、PEDOTのような正孔輸送層(存在する場合)と接触しないことでアノードとしてのその効果を減らすことがないものとし、および/または金属602およびLEP層の間の接触領域中で発光された光が見えないように実質的に不透明であるように十分厚いものとし、および/または低い仕事関数を有するものとする。不透明性のために、金属602は好ましくは30nmを超える厚さを有する(不透明性のために必要とされる正確な厚さは材料によって異なる)。

【0055】

図13は、平縁1102がウェルバンク層504の傾斜面を上るウェル構造1300の第3の(理想的な)例を示す。構造1300は、例えば、ポジ型バンクフォトレジスト層504がスピンコートされフォトリソグラフィーによりパターニングされた後に、スピンオンガラスのブランケット堆積により製造され得る。次いで、スピンオンガラスは、平縁を残してスピンオンガラスを除去する非等方性、好ましくはドライエッチングプロセスを使用して、ブランケット(マスク無し)エッチングされ得る。より一般的には、他の低温またはスピンオン材料が堆積され、続いて非等方性エッチングバックによりバンクレジスト端部の内部の親水性スペースを形成することができる。図13の実施態様はより高い平縁の利点を有し、これによって改良された溶媒留めを潜在的に提供する。

【0056】

図14は、ウェル構造1400の他の代替の実施態様であり、階段層は、この実施例では、シリコン窒化物絶縁層612の下、およびITO層508の下に、ドープされないおよびドープされたアモルファスシリコン層606,608および第2金属層610を有する。ITO層508の下にスペーサー堆積層を伴うこの構造は、潜在的により高い階段端部およびこれによってより広い平縁表面積および改良されたPEDOT−バンク分離を提供することができる。

【0057】

図15は、ウェル構造1500の他の代替の実施態様であり、図14に示されるものに似ているが、シリコン窒化物誘電体層604の下に、第1金属層602により供給された他の階段の追加を伴う、図14に示された実施態様の層の同じ組合せにより形成される2段を有する。これは、ITO層508の下により高いスペーサー堆積層およびこれによって平縁1102の潜在的により大きな表面積を提供する。

【0058】

図16は、ウェル構造1600のさらに他の代替的な実施態様を示し、この構造において先細りバンク504端部の2つの代替的な相対的配置を示しており、配置の許容範囲の広さを示している。

【0059】

図16の構造において、ITO層508が金属層の1つの上に堆積され、例示において、第1金属層602および次いで自己整合スペーサー平縁1102が(パターニングされた)ITO層508の端部周辺に形成される。先細りバンク層504の端部は下部金属層に配置されるが、ITO層508に正確に配置される必要がない。なぜなら、下層金属層602が露出されても、仕事関数の不適合により、形成されるダイオードは発光効率がよくないからである。したがって、図16の構造1600の画素の発光は本質的にITO508の面積によって決まり、配置の許容範囲の広い構造を提供する。それにもかかわらず、前のように、平縁はPEDOT含有溶媒をウェルの側面の底部に向けて引っ張る効果を有する(および、これがITOを覆うので、濡れまたは、他の点ではバンク端部の程度は本質的に重要ではない。というのは、バンク端部の直近では実効的なデバイスは存在しないからである。)。

【0060】

この原理は、いくつかの点で図12の実施態様に類似している。ただし、この実施態様では、画素領域(の周囲)のいくつかは配置の許容範囲を広げるために実効的に費やされている。例示されるように、図16における第1の実施態様において、金属は透明であるが、PEDOTと接触せず、したがって高仕事関数金属であり得る。図16の第2の実施態様において、金属は透明で、バンクの配置ミスのためPEDOTと接触されることがあり、これは、この実施態様における金属層は好ましくは低仕事関数を有し、PEDOTとの不適合を提供することを意味する。

【0061】

図17を参照すると、「インク液滴」堆積ウェルの底部の親水性材料の短く突き出た棚を有するデバイスを製造するために示されるように、これはOLEDデバイスの製造方法の実施態様を示す。この方法も、アンダーカットバンクを有するデバイスを製造するために、種々に有益である。

【0062】

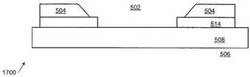

より詳細には、図17a〜17cはウェル構造1700の製造における連続的な工程を示し、ここでは、前に採用した参照番号を使用し、OLEDディスプレイの画素のためのウェル502は基板上のバンク504によって規定される。基板506はITO508層を有し、画素のためのアノード接続を提供し、その上に酸化物スペーサー層514および次いでバンク材料(好ましくは従来の形でパターン形成されたポジ型フォトレジストなどの有機材料で形成される)が堆積されて、図17aに示されるように基板に対して傾くバンク504を形成する。

【0063】

図17bにおいて、SiO2層514の非等方性ドライ(プラズマガス)エッチングはバンク504をマスクとして使用して行われ、自己整合エッチングマスク法を提供する。これは、図17cに示されるように、前方に出た階段の製造の用意である。これは、バンク材料で規定されるものと実質的に同じ開口を生成する。あるいは、溶液(または、ドライ、プラズマ)等方性エッチングが行われ、酸化物層514の下部を切除し、図17bに示される真直ぐな垂直な端部ではなく、図5に示されるような一般的なタイプの構造を製造することができる。他の代替において、溶液(またはドライ、プラズマ)等方性エッチングが行われ、次の工程で十分なバンク材料が除去されて、図17cに示される突き出た階段を残すことができる。

【0064】

図17cはO2プラズマアッシングレジストストリップ工程後の構造を示し、この工程は、画素端部において薄くなることで短絡を生じないように、バンク504の厚さを減らして開口を広げ、示されるようにSiO2層514の端部を露出する。この工程は、酸化物および下層ITOを清浄化して十分濡れるようにし、PEDOT溶液の堆積、これに続くLEP堆積の準備をする。

【0065】

この方法の実施態様は、レジストバンク画素ウェルの端部における親水性作用を提供し、この作用を酸化物層に対する独立したマスクを使用しないで自己整合または部分的自己整合によって行うことを可能にする。さらに、もし端部(突き出た階段または下部切除)構造が、アルミニウムのような層の側面に形成されると、アノード接続が低仕事関数金属(通常、アノードはITOのような高仕事関数金属である)で形成されるときこのダイオード構造は非効率であるから、この層はアクティブ画素の自然な規定も提供することができる。この方法の実施態様は、標準のポジ型レジストが(画素バンク端部を横切るカソード金属化のための良好な階段被覆を維持するために)使用されるのを可能にする。したがって、LEPインクは、PEDT濡れおよびLEP濡れプロセスを分断しながら、表面エネルギー改変処理プロセス(例えば、前述したように、CF4プラズマ処理)に基づいて(場合によって)閉じ込められ得る。これは、表面調整工程がLEPのために調整され(画素レジスト内における良好な閉じ込めを潜在的に可能にし)、一方、PEDT濡れは、自己整合された画素端部(突き出した階段または下層切除)構造の親水性または毛細管現象により強くまたは実質的に完全に頼るので、レジスト上のPEDT接触角には敏感ではないことがある。

【0066】

本発明の実施態様は、ポジ型バンクレジストの使用を可能にし、前述した構造上の利点、特に、画素端部にわたって不連続部なしに良好な金属カソード接続を形成すること、およびPEDOTの分離された段階およびLEP(または他の発光材料)堆積のための構造(例えば、表面調整)の採用を容易化するためにPEDOTおよびLEP濡れ工程を実質的に分離することを提供する。さらに、例えば、追加のマスク/パターニング工程の必要なく前述した構造の実施態様は自己整合または部分的自己整合工程を使用して製造されることができる。他の実施態様は、前記アノード接続が、例えば、4電子ボルト未満および/または介在する正孔輸送層なしの低仕事関数金属により形成されるとき、発光ダイオード構造の固有の非効率性の利点をとり配置の許容範囲の広さを達成する。大まかに言って、本発明の実施態様は、前記材料が堆積されるウェルの側面においてPEDOT(およびLEP)溶媒の濡れ/留めを容易化するための表面エネルギー関連技術に頼る。

【0067】

上述したウェル構造は、溶液堆積有機電子デバイスの広い範囲に採用され得る。これらは、アクティブまたはパッシブマトリックス電子発光ディスプレイデバイス、または、例えば、いわゆるバンク層および/または有機電子材料の堆積のために準備されるデバイスのためのTFTベースのアクティブマトリックス背板に組み込まれ得る。

言うまでもなく、当業者は他の効果的な代替例を思いつくであろう。本発明は上記の実施態様に限定されることはなく、添付の特許請求の範囲の精神と範囲内にある技術において当業者には自明な変更を含んでいることを理解されたい。

【図面の簡単な説明】

【0068】

【図1】OLEDデバイスの例の垂直断面図を示す。

【図2】3色画素OLEDディスプレイの一部の上面図を示す。

【図3a】パッシブマトリックスOLEDデバイスの上面図を示す。

【図3b】パッシブマトリックスOLEDデバイスの断面図を示す。

【図4a】溶解した材料で満たされたOLEDディスプレイ基板のウェルの簡略断面図を示す。

【図4b】乾燥した材料で満たされたOLEDディスプレイのウェルの簡略断面図を示す。

【図5】本発明の第1の側面の第1の実施態様の有機電子デバイス構造を示す。

【図6】本発明の側面を実施する製造並行構造に適した底面ゲート型薄膜トランジスタ(TFT)構造を示す。

【図7】本発明の第1の側面の第2の実施態様の有機電子デバイス構造を示す。

【図8】本発明の第1の側面の第3の実施態様の有機電子デバイス構造を示す。

【図9】本発明の第1の側面の第4の実施態様の有機電子デバイス構造を示す。

【図10】本発明の第1の側面の第5の実施態様の有機電子デバイス構造を示す。

【図11】本発明の第2の側面の第1の実施態様の有機電子デバイス構造を示す。

【図12】本発明の第2の側面の第2の実施態様の有機電子デバイス構造を示す。

【図13】本発明の第2の側面の第3の実施態様の有機電子デバイス構造を示す。

【図14】本発明の第2の側面の第4の実施態様の有機電子デバイス構造を示す。

【図15】本発明の第2の側面の第5の実施態様の有機電子デバイス構造を示す。

【図16】本発明の第2の側面の第6の実施態様の有機電子デバイス構造を示す。

【図17a】本発明の側面の実施態様の有機電子デバイスの製造を示す。

【図17b】本発明の側面の実施態様の有機電子デバイスの製造を示す。

【図17c】本発明の側面の実施態様の有機電子デバイスの製造を示す。

【符号の説明】

【0069】

100 OLED

102 基板

106 アノード層

108 正孔輸送層

110 カソード層

112 バンク

114 ウェル

200 アクティブマトリックス画素OLEDディスプレイ

300 基板

302 カソード下層分離体

304 領域

306 アノード層

308 ウェル

310 バンク

400 断面図

402 溶解した材料

404 固体薄膜

500 第1構造

502 ウェル

504 バンク

506 基板

508 ITO層

510 PEDOT層

512 LEP層

514 スペーサー

516 棚

518 ITO層

600 底面ゲート型TFT

602 金属材料層

604 誘電体層

606 ドープされないアモルファスシリコン層

608 ドープされたアモルファスシリコン層

610 第2金属層

1102 平縁

1200 ウェル構造

1300 ウェル構造

【技術分野】

【0001】

本発明は、有機電子デバイス、特に、有機発光ダイオード(OLEDs)の構造および製造方法に関するものである。

【背景技術】

【0002】

本発明の理解を助けるために、先ず、OLEDディスプレイのいくつかの特徴およびその製造におけるいくつかの問題点を説明する。しかしながら、本発明の実施態様はOLEDディスプレイを特に引用して記載されるが、この技術は有機電子デバイスの製造一般に適用できることは明らかである。

【0003】

有機発光ダイオード(OLED)は電気光ディスプレイの特に有利な型である。これは、明るく、カラフルで、立ち上がりが早く、広い視野角を提供し、多様な基板上に安く簡単に製造することができる。有機(本明細書では、有機金属を含む)LEDは、使用される材料に応じて、多色(またはマルチカラーディスプレイ)の範囲で、ポリマーまたは低分子を使用して製造され得る。典型的なOLEDデバイスは2つの有機材料層を有し、その1つは発光ポリマー(LEP)、オリゴマーまたは発光低分子量材料のような発光材料の層であり、他はポリチオフェン誘導体またはポリアニリン誘導体のような正孔輸送材料の層である。

【0004】

有機LEDは、単色または多色画素ディスプレイを形成するために、画素のマトリックス中の基板上に堆積され得る。多色ディスプレイは、赤、緑、青色発光画素のグループを使用して形成される。いわゆるアクティブマトリックスディスプレイは、記憶素子、通常、各画素に連結された蓄積容量およびトランジスタを有し、他方、パッシブマトリックスディスプレイはそのようなメモリ素子を有さず、その代わり、固定した画像の印象を与えるために繰返しスキャンされる。

【0005】

図1はOLEDデバイス100の例の垂直断面図を示す。アクティブマトリックスディスプレイにおいては、画素の一部領域は連結された駆動回路(図1には図示しない)によって占められている。このデバイスの構造は、例示のために簡略化されている。

【0006】

OLED100は、通常は0.7mmまたは1.1mmのガラス、任意に透明なプラスチックの基板102を有し、その上にアノード層106が堆積される。アノード層は、通常約150nmの厚さのITO(インジウム錫酸化物)を含み、その上に、通常約500nmのアルミニウムの金属接続層が提供され、しばしばアノード金属と呼ばれる。ITOで被覆されたガラス基板および接続金属は、Corning,USAから購入することができる。接続金属(および任意にITO)は、ディスプレイを覆い隠さないように、従来のフォトリソグラフィーとこれに続くエッチングプロセスにより望まれるようにパターニングされる。

【0007】

実質的に透明な正孔輸送層108aはアノード金属上に供給され、続いて電子発光層108bが供給される。バンク112は、例えばポジ型またはネガ型フォトレジスト材料から基板上に形成することができ、ウェル114を規定し、この中には、例えば、液滴堆積またはインクジェット印刷技術によって、これらの活性有機層が選択的に堆積され得る。したがって、ウェルは発光領域またはディスプレイの画素を規定する。

【0008】

次いで、カソード層110が、例えば、物理的気相蒸着によって適用される。カソード層は、通常、厚いアルミニウムのキャップ層で覆われたカルシウムまたはバリウムのような低仕事関数の金属を有し、任意に、例えば、電子エネルギーレベルの適合(matching)を改良するために、電子発光層に隣接してフッ化リチウムの層などの追加の層を有する。カソード線の相互の電気的絶縁はカソードセパレータ(図3bの要素302)を使用して達成され得る。通常、多数のディスプレイが単一基板上に形成され、形成プロセスの最後で基板はスクライブされ、ディスプレイが互いに分離された後、酸化および湿気の浸入を防止するためにカプセル缶が個別に付着される。

【0009】

この通常のタイプの有機LEDは、変化する駆動電圧および効率において波長範囲に渡って発光するために、ポリマー、デンドリマーおよびいわゆる低分子を含む材料の範囲を使用して製造され得る。ポリマーベースのOLED材料の例は、WO90/13148、WO95/06400およびWO99/48160に記載されており、デンドリマーベースの材料の例はWO99/21935およびWO02/067343に記載されており、低分子OLED材料の例はUS4,539,507に記載されている。前述のポリマー、デンドリマーおよび低分子は1重項励起子の放射性崩壊によって発光(蛍光)する。しかしながら、励起子の75%までは、通常、非放射性崩壊を行う3重項励起子である。3重項励起子の放射性崩壊による電子発光(燐光)は、例えば、“Very high−efficiency green organic light−emitting devices based on electrophosphorescence”M.A.Baldo,S.Lamansky,P.E.Burrows,M.E.Thompson,and S.R.Forrest Applied Physics Letters,Vol.75(1)pp.4−6,July5,1999に開示されている。ポリマーベースのOLEDの場合、層108は、正孔輸送層108aおよび発光ポリマー(LEP)電子発光層108bを有する。電子発光層は、例えば、約70nm(乾燥)の厚さのPPV(ポリ(p−フェニレンビニレン))を有することができ、正孔輸送層は、アノード層と電子発光層の正孔エネルギーレベルの適合(match)を促進し、例えば、PEDOT:PSS(ポリスチレン−スルフォネート−ドープ−ポリエチレン−ジオキシチオフェン)の約50〜200nmの厚さ、好ましくは、約150nm(乾燥)の厚さを有することができる。

【0010】

図2は、一つの活性カラー層の堆積後の3色アクティブマトリックス画素が形成されたOLEDディスプレイ200の一部を上方から(基板を通さずに)見た図である。同図は、ディスプレイの画素を画定するバンク112およびウェル114のアレイを示す。

【0011】

図3aは、パッシブマトリックスOLEDディスプレイをインクジェット印刷するための基板300を上方から見た図である。図3bは、図3aで線Y−Y’に沿って基板を通して見た横断面図である。

【0012】

図3aおよび図3bを参照すると、隣接するカソード線(領域304に堆積される)を分離するための複数のカソードアンダーカットセパレータ302が基板に供給される。複数のウェル308がバンク310によって規定され、各ウェル308の周囲にそって形成され、アノード層306をウェルの底に露出させる。バンクの端部または面は図示されるように、通常10〜40°の角度で基板の表面に向かって先細になる。バンクは、堆積される有機材料の溶液で濡れないように疎水性の表面を提供し、堆積される材料がウェル内におさまるのを助ける(極性または非極性溶媒が使用され得るが、通常使用される溶媒は極性を有する)。これは、EP0989778に開示されるようにO2/CF4プラズマによりポリイミドのようなバンク材料を処理することによって達成される。あるいは、WO03/083960に開示されるように、フッ素化ポリイミドのような弗化材料の使用によってプラズマ処理工程は回避され得る。

【0013】

前述したように、バンクおよびセパレータ構造はレジスト材料、例えば、バンクのためにポジ型(またはネガ型)レジストが、セパレータのためにネガ型(またはポジ型)レジストを使用して、レジスト材料から形成され得る。これらのレジストは、ポリイミドベースであり得、基板上にスピンコートされるか、またはフッ素化またはフッ素系フォトレジストが使用され得る。示される例においては、カソードセパレータは約5μmの高さおよび約20μmの幅である。バンクは一般には20μm〜100μmの幅であり、示された例は、(バンクが約1μmの高さとなるように)各端部において4μmのテーパーを有する。図3aの画素は約300μm平方であるが、後述するように、画素の大きさは、意図する用途に応じてかなり変化し得る。

【0014】

インクジェット印刷技術を用いた有機発光ダイオード(OLED)の材料の堆積技術は、多くの文献に記載されており、例えば、T.R.Hebner,C.C.Wu,D.Marcy,M.H.Lu and J.C.Sturm,“Ink−jet Printing of doped Polymers for Organic Light Emitting Devices”,Applied Physics Letters,Vol.72,No.5,pp.519−521,1998;Y.Yang,“Review of Recent Progress on Polymer Electroluminescent Devices,”SPIE Photonics West:Optoelectronics ’98,Conf.3279,San Jose,Jan.,1998;EPO 880303;および“Ink−Jet Printing of Polymer Light−Emitting Devices”,Paul C. Duineveld,Margreet M.de Kok,Michael Buechel,Aad H.Sempel,Kees A.H.Mutsaers,Peter van de Weijer,Ivo G.J.Camps,Ton J.M.van den Biggelaar,Jan−Eric J.M.Rubingh and Eliav I.Haskal,Organic Light−Emitting Materials and Devices V.Zakya H.Kafafi,Editor,Proceedings of SPIE Vol.4464(2002)に開示されている。インクジェット技術は、低分子およびポリマーLEDの両者の材料を堆積させるために使用され得る。

【0015】

有機電子材料を堆積させるために、0.5%〜4%の溶媒に溶解した材料を有する揮発性の溶媒が一般的に使用される。これは、乾燥するのに数秒から数分かかることがあり、最初の「インク」容量に比較して相対的に薄い膜をもたらす。しばしば、乾燥材料の十分な厚さを提供するためには、好ましくは乾燥が始まる前に、複数の液滴が堆積される。使用され得る溶媒としては、シクロヘキシルベンゼンおよびアルキル化ベンゼン、特に、トルエンまたはキシレンが使用される。他は、WO00/59267、WO01/16251およびWO02/18513に記載されている。これらの混合の溶媒も使用することができる。Litrex Corporation of California,USAの装置のような正確なインクジェットプリンターが使用される。適切なプリントヘッドは、NH,USAのXaar of Cambridge,UK and Spectra,Inc.から入手できる。いくつかの特に有利な印刷手法は、本出願人の出願である2002年11月28日出願UK特許出願0227778.8(および対応するPCT公開WO2004/049466)に記載されている。

【0016】

インクジェット印刷は、有機電子デバイスの材料の堆積に多くの利点を有するが、この技術に関連する欠点もいくつか存在する。しかしながら、浅い端部を有するウェル内に堆積された溶解した有機電子材料は、乾燥して比較的薄い端部を有する薄膜を形成することがわかっている。図4aおよび4bはこのプロセスを図示している。

【0017】

図4aは、溶解した材料402で満たされた壁308の簡略断面400を示し、図4bは、材料が乾燥して固体薄膜404を形成した後の同じウェルを示す。この実施例において、バンクの角度は約15°であり、バンクの高さは約1.5μmである。見られるように、ウェルは通常、ふちまでいっぱいになるまで満たされる。溶液402はプラズマ処理されたバンク材料に対する接触角θcとして典型的には30°〜40°、例えば約35°を有する。これは、溶解した材料402の表面が接触する(バンク)材料と、例えば、図4aにおける402aの角度を作る。溶媒が蒸発するにつれて、溶液はより濃縮され、溶液の表面は基板に向かってバンクの傾き面を下方に移動し、乾燥端部の留まりが基板上の最初に付着した濡れ端部とバンクの足(ウェルの底)の間の点で生じ得る。図4bに示されるように、この結果、乾燥材料404の薄膜は非常に薄くなり得、バンク面に接する領域404aにおいて、例えば、10nm以下のオーダーの厚さとなる。

【0018】

出願人は、WO2005/076386として公開された2004年2月5日出願のUK特許出願0402559.9において、ウェルの端部に向かって溶液を押す効果を有するアンダーカットバンクの使用により、より均一な充填を得るのを助けることを記載した。しかしながら、このようなバンクは製造するのが容易ではなく、一般的に、高価でありプロセスの条件に敏感なネガ型フォトレジストを使用する。したがって、ポジ型フォトレジストの使用により適した改良された技術の必要性が存在する。

【0019】

他の問題点は、画素(ウェル)の大型化(例えば300μmの画素ピッチを形成するために使用される240μm〜260μmの開口を備えたウェル)に伴い生じる。インク液滴の容量は液滴の特徴的な長さの3乗に比例し、表面の保護範囲は画素の寸法の2乗に比例し、このための任意のインクの薄め方においては、多くの材料が大きな画素に堆積され、そのためより薄いインクが必要とされるようになる。例えば、大きな画素および80nmの望まれるPEDOT薄膜の厚さにおいては、約1%のインクの濃度が導入され得るが、1パーセントのインクを広げて、濡らし大きな画素を満たすのは困難である。これは、いわば、満杯であふれるばかりの画素は120nmの厚さの薄膜をもたらすため、500μm四方を超える画素の製造は困難となる。さらに、製造プロセスにおいて、インクの希釈を変えることは高価である。

【0020】

一般的に、画素ウェルの底部はITOを含み、これは、通常、10度未満(例えば、5〜7度)の低接触角を有し、相対的に良好な濡れ性(親水性)を提供する。しかしながら、特に、大きな画素を有すると、円形を有する堆積された液滴ほど濡れ性は完全ではなく、溶媒はウェルの底内の点で留まる傾向にあるため、堆積された液滴は通常、よりでこぼこの端部を有する。上述したように、バンク上の溶媒の接触角は相対的に高いので、より多くの溶媒をウェルに加えるほど、溶媒がバンクを上るより液滴の高さは高くなる傾向があり、乾燥すると表面エネルギーによって溶液はウェルの端部から離れる傾向がある。これは、PEDOT堆積について特に問題であり、この薄い端部はカソード(ITO)と覆う発光ポリマー(LEP)との直接接触をもたらし、結果、不完全または効率の低い画素となり得る。EP0993235においては、セイコーエプソンは、画素ウェルの底の内部端部のアノードを覆う誘電体層を堆積させることによりこの問題の解決を狙っているが、これは、配置の許容誤差の必要性を考慮すると有効な画素面積を20%まで減らす欠点がある。

【先行技術文献】

【特許文献】

【0021】

【特許文献1】国際公開2005/076386号パンフレット

【特許文献2】欧州特許0993235号明細書

【発明の概要】

【発明が解決しようとする課題】

【0022】

したがって、これらの問題を解決する改良された有機電子デバイス構造および製造技術、特に、有機電子材料を溶媒ベースの堆積プロセスに広げるのを助ける必要性がある。

【課題を解決するための手段】

【0023】

したがって、本発明は、有機電子デバイスの液滴堆積ベースの製造のための構造における液滴堆積ウェルの形成方法を提供する。前記方法は、基板上に親水性材料層を堆積させる工程、前記親水性材料層の上にバンク材料層を堆積させる工程、前記バンク材料層をパターニングして1または2以上の前記液滴堆積ウェルを形成するバンクを規定する工程、前記パターニングされたバンク材料層をレジストとして使用して自己整合プロセス中において前記親水性材料層をエッチングする工程を含む。

【0024】

実施態様において、この方法は、1つはバンク材料について、もう1つは親水性(またはスペーサー)層についての2つの独立したマスク工程の必要性を省く。当業者は、一般的に、この方法が適用される基板は、ITOのような最初の透明導電体の下層を有するものが購入または用意されてきたことを理解する。本方法のいくつかの好ましい実施態様において、バンク材料は、レジスト、好ましくは、ポジ型レジストを含む。好ましくは、バンクはバンク材料の一層のみ(これは好ましくは疎水性である)および親水性材料(酸化物のような)の1層のみを有する。

【0025】

本発明の方法の好ましい実施態様において、親水性材料は、誘電体材料、特にSiO2を有する。ただし、窒化シリコンおよびシリコン酸窒化物のような他の誘電体材料またはレジストも適用できる。他の実施態様において、親水性材料は、アルミニウム、クロムまたはモリクロムのような親水性金属を含む。このような実施態様において、例えば、前記金属は、アノードトラック抵抗を減らすためにITO上に形成されたアノード金属であってもよい。この方法を用いて製造されたOLEDデバイスの実施態様において、前記金属は有機電子材料に、特にPEDOTに向けられることができ、その後ウェル中に堆積される。しかしながら、前記金属が関係する材料(PEDOT)のための不良な電子注入体(高い仕事関数を有する)である場合、これは、実質的に絶縁層として機能するのでこの接触はデバイスの十分な作動とならない。

【0026】

自己整合エッチング工程においては、バンクレジストはマスクとして働くか、等方性または非等方性であり得る。好ましい実施態様において、エッチングはプラズマエッチングを含む。等方性エッチングは親水性層の下を切り取る(したがって、基板および上部バンク層の間のスペーサーとして働く)。非等方性エッチングは、バンクの端部(これは通常先細である)が終了する親水性層の端部をほぼ垂直下方に切除する。等方性エッチングの場合、ドライエッチング、特にプラズマガスエッチングが採用されることができ、これは下方切除内で自己整合し、下方切除の深さが制御される。あるいは、溶液エッチングを導入することができ、これによりエッチング液がある限りエッチングが続いて行われる。非等方性エッチングについては、ドライプラズマエッチングが好ましい。

【0027】

前記デバイス構造のアンダーカットの実施態様については、親水性(スペーサー)層の幅は500nm未満、例えば、50nmと200nmの間、およびいくつかの実施態様において約100nmであり得る。他の実施態様において、親水性層は(効果的な)絶縁を提供しバンク端部の底部での短絡を減らすのに役立つ場合(堆積された有機電子材料が溶媒乾燥効果のため、より薄くなる傾向にある場合)、親水性層はより薄くすることができ、例えば、100nm、50nm、10nmまたは5nm未満である。限界の厚さは、連続的な絶縁膜を形成する要望によって決まり、例えば、SiO2では約2nmである。非等方性エッチングは、下方切除を実質的に防止し、棚を残すために切り取られるバンク材料の量を減らすので、ウェルの底部で絶縁性の棚を形成する方法の実施態様として好ましい。

【0028】

いくつかの特に好ましい実施態様においては、レジストストリッピング法、好ましくはO2プラズマアッシングのようなプラズマアッシング法がエッチングの後に行われる。これは、最も薄くなっている(先細り)バンクの底部の一部、すなわち、ウェルの底部に隣接する部分を取り除き(同時にバンクの全体の厚みを減らす)、ウェルの底部に隣接する親水性材料を露出させる。これは、バンク材料の穴を親水性層中のものより大きくなるように拡大させる。親水性材料層の露出部分は、前述したように、絶縁性のスペーサーとして働き、ウェルの底部の端部の短絡を防止するのに役立つ。特に、これは親水性PEDOT溶液を引きつけ、これはこの材料の露出部分に効果的に付着し、このような堆積された材料の液滴の端部を留める。さらに、PEDOT溶液はこのように閉じ込められるので、バンク材料の層の表面エネルギー特性は、発光ポリマー(LEP)層のような後の材料の堆積層のために望まれる特性に向けて独立して調整され得る。バンクレジストの場合、例えば、これは、LEPの良好な閉じ込めのために、バンク材料をCF4プラズマで処理して疎水性にすることによって行われ得る。(この「調整」は、わずかな「汚染効果」があるだけで、下層酸化物の親水性にほとんど影響を与えない。)あるいは、「テフロン(登録商標)化」またはフッ素化レジストが疎水性のバンク特性を達成するために導入され得る。したがって、この方法のこれらの実施態様は、大まかに言って、いわゆるPEDOTおよびLEPの溶液堆積の結合を切り離すための異なる望まれる表面エネルギー処理(親水性及び疎水性)を許容する。さらに、水中のいわゆるPEDOT溶液の高いバンク接触角は例えば90〜110°であり、PEDOTをバンクから離れさせ、したがってこの材料を閉じ込めることを助ける。

【0029】

したがって、他の側面において、本発明は、有機電子デバイスの液滴堆積ベースの製造のための構造における液滴堆積ウェルを形成する方法を提供し、この方法は、基板上に親水性材料の層を堆積させる工程、前記親水性材料の層の上にレジスト材料の層を堆積させる工程、前記レジスト材料の層をパターニングして前記液滴堆積ウェルの1または2以上を形成するバンクを規定する工程、前記親水性材料の層をパターニングして、前記1または2以上の液滴堆積ウェルの底部領域の少なくとも一部から前記親水性材料を除く工程、およびレジストストリッピング法を使用して前記液滴堆積ウェルの1または2以上を形成する前記バンクの底部に隣接する親水性材料の前記パターンニングされた層の上部表面の一部を露出する工程を含む。

【0030】

実施態様において、バンクを超えて突き出し、下層ITOと同様の表面エネルギーを有する低部層の供給はコストおよび開口率に大きな影響を与えずに生産性と均一性を助けることが可能である。レジストストリッピング(アッシング)がなされるこの構造は自己整合プロセスで形成される必要はなく、例えば、2マスクプロセスを使用して形成されることができたはずである。

【0031】

関連する側面において、本発明は上記の方法を使用して形成される有機電子デバイスを提供する。特に、このようなデバイスは、有機電子材料で満たされた複数の液滴堆積ウェルの下の親水性材料のパターニングされた層を有する基板を含み、前記液滴堆積ウェルの1または2以上を形成する前記バンクの底部に隣接する親水性材料の前記パターニング層の上部表面の一部は前記有機電子材料にさらされる。

【0032】

さらに他の側面において、本発明は有機電子デバイス構造を提供し、前記構造は、基板、および前記基板により支持され、有機電子材料の溶媒ベースの堆積のためのウェルを規定するバンク層を含み、前記構造は、さらに、前記ウェルの内部端部および前記ウェルの底部にある平縁を規定するためにパターニングされる平縁層を含む。

【0033】

好ましくは、前記平縁は、シリコンの酸化物および/または窒化物のような親水性材料を有する。前記平縁層は、前記デバイスの一部を形成するまたは前記装置に連結される薄膜トランジスタの酸化物層のような有機電子デバイスのいくつかの他の部分も形成する層を好都合に含むことができる。

【0034】

1つの実施態様において、前記平縁は基板に向かって先細りする前記バンクの一部に横たわっている。他の実施態様において、1または2以上の層はパターニングされて前記ウェルの内側端部において階段を規定し、前記平縁は前記階段に隣接する。例えば、好ましい実施態様において、前記ウェルは、アノードまたはITO層のような底部層を有し、また、階段層(これも、前記デバイスの既存の層を「再使用」して供給され得る)は、前記ウェルの内部端部に隣接する前記底部層において高さの階段的変化を提供するように前記底部層と前記基板の間に供給される。この場合、前記平縁は前記底部層におけるこの階段に接する。いくつかの実施態様において、2段は、2つ(またはそれ以上)の下側「階段」層を使用して前記底部層に規定され、前記ITOの下により高いスペーサー積層、したがって前記ウェルの端部での改良された溶媒の留めのための広い平縁領域を提供する。実施態様において、1または2以上の階段層は、1または2以上の金属層、ドープされていないシリコン層、ドープされたシリコン層および第2金属層を有し得る。これらの層は、例えば、OLEDディスプレイデバイスの画素に連結された薄膜トランジスタのための既存の製造プロセスの一部として既に存在し得る。好ましくは、このようなデバイスにおいて、前記バンク層は、ポジ型フォトレジストを含み、従来どおり基板に向かって先細る。この場合の有機電子材料の堆積層は、導電性(正孔輸送)層およびこれを覆う発光層を有することができる。

【0035】

他の側面において、本発明は、有機電子材料の溶媒ベースの堆積のための少なくとも1つのウェルを有する基板上の有機電子デバイスの形成方法を提供し、前記方法は、前記デバイスを形成するための前記有機電子材料の溶媒ベースの堆積の前に前記ウェルの内部端部の平縁を規定するために前記平縁層を堆積させ、非等方的にエッチングする工程を含む。

【0036】

好ましくは、前記平縁材料は、有機電子材料を堆積させるために使用される単一の溶媒または溶媒の混合物で濡れるように選択または処理される。好ましくは、このような濡れは、前記平縁と前記溶媒または溶媒混合物との間の接触角として15°未満、より好ましくは10°未満を提供する。

【0037】

本発明は、さらに、本発明の1つの側面の方法によって製造された有機電子デバイス、特に、アクティブまたはパッシブOLEDディスプレイデバイスを提供する。本発明のこれらおよび他の側面を、添付の図面を参照して単に例示としてさらに説明する。

【0038】

図5を参照すると、これは、アクティブマトリックスOLEDディスプレイの画素のウェル502のための第1構造500の垂直断面図および上面図を示す。ウェル502は基板506に向けて先細るバンク504によって規定され、その上を、前記画素のアノードを提供するITO層508が覆う。ウェル502内には、PEDOT層510が堆積され、その上を発光ポリマー(LEP)層512が覆う。図5は、PEDOTおよびLEP層の堆積の前の構造の断面図も示す。

【0039】

酸化物スペーサー層514はITO層518の上、バンク層504の下に供給される。これは、前記ポジ型バンクフォトレジストのパターニングの後、従来の溶液またはドライ等方性エッチング法を使用してエッチングされる。このエッチングプロセスは、ウェル502の低い内部端部周辺の上に突き出る棚516(上面図における破線によって示される)をもたらし、堆積工程において溶解したPEDOTを有する溶媒が流れ込むことができるくぼみを提供する。前記PEDOT溶液は毛細管現象により前記くぼみに自然に流れ込むが、前記酸化物スペーサー514は親水性であるため、前記溶媒は前記棚516の下の層514の露出された内部端部にも付着する。実施態様におけるこれら2つの効果の結合が信頼性のあるPEDOT端部の厚さプロフィールを提供する。

【0040】

PEDOTは、乾燥時に、このへこんだ端部に付着し続けるが、(疎水性の)バンクには残らない。PEDOT溶液は親水性層514の露出された端部および/または前記くぼみの毛細管現象によって効果的に留まるので、バンクは、例えば、CF4により処理されることができ、PEDOT溶液の要求から大きく独立したLEPの堆積に特に適した表面(必要な程度まで疎水性にされる)を提供する。

【0041】

単純な例の製造過程において、ITOで被覆された基板は任意の供給者から購入され、パターニングされ、次いで、二酸化シリコン、一酸化シリコンまたはシリコン酸窒化物のようなブランケット酸化物で被覆され、親水性層を提供する。このブランケット酸化物は、例えば、スピンオンガラスを含むことができる。次いで、ポジ型フォトレジスト層504がスピンコートされ、フォトリソグラフィーによってパターニングされる(露光、現像および洗浄)。次いで、追加のマスクを必要とせずに、くぼみが酸化物スペーサー層514の等方性エッチングバックによって形成される。このプロセスは、バンクが有効に前記酸化物層のエッチングマスクを供給するので、自己整合プロセスである。

【0042】

図6は、図5の画素構造500と一緒に、および/または後述する本発明の第1および第2の側面の他の実施態様と一緒に製造され得る底面ゲート型TFT構造600の垂直断面図を示す。図6において、図5と同じ番号は同じ構成要素を示す。この例において、基板はこの時点でITOによってパターニングされていないか、代わりに、第1の相対的に厚い金属層602はガラス基板506上に堆積され、パターニングされてTFTのゲート金属を提供する。例えば、シリコン窒化物からなるゲート誘電体層604は、ゲート金属602上に堆積され、ドープされていないアモルファスシリコン層606およびドープされたアモルファスシリコン層608の堆積およびパターニングが続き、それぞれ、TFTのチャネルおよびドレイン/ソース領域を形成する。次いで、第2の金属層610が堆積され、パターニングされて、トランジスタおよび絶縁層612のためのソースおよびドレイン導電体を提供し、次いで、例えば、シリコン窒化物が前記構造上に堆積され、ソースおよびドレイン接続孔612aがエッチングされる。次いで、ITO層508が堆積されて前記ソースおよびドレイン電極への接続が形成され、これらを1または2以上の隣接する画素に結合する。従来の工程においては、このITO層が、バンクフォトレジスト層504が堆積される前の最後の層であるが、このTFT構造が、例えば、図5の改良されたウェル構造と関連して使用されるとき前記バンク層504の堆積およびパターニング前に、前記ITO層の上に追加の酸化物層(図6に示さない)が堆積される。

【0043】

次に、図7を参照すると、これは、図5で例示した原理を採用するより典型的な「リアルライフ」ウェル構造を示す。

【0044】

図7および続く図において、図5および図6の同じ番号は同じ構成要素を示す。

【0045】

図7に示されたウェル構造700の実施態様において、2つの下層シリコン窒化層(誘電体層604および絶縁体層612)が示されている。

【0046】

図8は、棚が絶縁層612と第2金属層610の結合によって供給されるウェル構造800の追加の実施態様を示す。前の2つの実施態様と異なり、この実施態様は単に部分的自己整合であり、さらに、いずれかのシリコン層の前にITO層508の堆積を含む。これは、TFT構造はただ画素のアクティブ領域に使用されるため、アクティブマトリックスディスプレイにおいて可能である。しかしながら、この実施態様において層の連続は異なるが、同じ一般的な原理が採用される。

【0047】

概要において、シリコン606,608、金属610および窒化物612層はバンク端部内に配列され、次いで、前記金属端部の下にある前記シリコン層の等方性エッチングバックが導入されてこの構造を生成する(前記金属は、前記シリコン端部によって攻撃されないので)。金属および/または窒化物層は同時にパターニングされる。

【0048】

ウェル構造800において、前記棚の下のスペースは前の実施態様のそれより潜在的に深く、実施態様において(示されるように)、この深さはPEDOT層によって完全に満たされない可能性がある。このような場合も、電子発光層は棚の下に伸びる。PEDOT層および電子発光層は、例えば、示されるドープされたおよびドープされないシリコン(共に親水性)のようなそれぞれ異なるスペーサー層に連結されていることが可能である。有機材料層の厚さは最大500nmであり得、ただし、厚さは、一般的により薄く、例えば、50nm〜200nmであり、図8の実施態様において、棚の下のくぼみの全体高さは最大500nm(またはこれ以上)であり得る。

【0049】

次に、図9を参照すると、これは、シリコン堆積の前のITO堆積と共に部分的自己整合エッチング工程を使用するウェル構造900の他の実施態様を示す。概要において、シリコンおよび窒化物層がバンク端部に配列されて、次いで、シリコン層が窒化物端部の下で等方的にエッチングバックされる。これは、ドープされおよびドープされないシリコン層が異なる段階でエッチングされるため、TFTを組み込む構造において可能である。

【0050】

図10は、酸化物スペーサー層514がITO層508の後に、ただし(シリコン窒化物)絶縁層612の前に堆積されるウェル構造1000の他の実施態様を示す。この構造の形成は、くぼみが前記酸化物層の等方性エッチングバックによって形成されるので、部分的に自己整合される。PEDOT溶液がくぼみに入り、親水性および/または毛細管現象によってウェルの端部に留まり、信頼性のあるPEDOT端部厚みプロフィールを提供するのを助ける。

【0051】

次に、図11を参照すると、これは、本発明の第2の側面のウェル構造1100の第1の実施態様の垂直断面図(溶媒ベースの有機材料堆積の前および後)および上面図を示す。

【0052】

再び、この実施態様およびこれに続くものにおいて、上記の層と同様の層は同じ番号によって示される。

【0053】

図11において、第1の金属層602がパターニングされて、その内側端部のすぐ外側のウェルの周囲に「画像フレーム」を提供する。これは、上に覆うITO508における階段を形成する。次いで、ブランケット酸化物層が堆積されて、当業者に周知な態様で等方的に(垂直に)エッチングされ、垂直端部上の材料の平縁1102、1102aを生成する。これら酸化物平縁は親水性材料を有し、および前記ウェルの端部にPEDOT含有溶媒を留めるのに役立つ(ただし、この溶媒は疎水性のバンク端部に乗り上げない傾向にある)。この疎水性のCF4表面処理は、PEDOT溶媒がバンク上に、たとえ上るとしてもほんの短い距離だけ上るので、PEDOT堆積から大きく独立したLEP溶媒によって適用されることができる。バンク材料、処理および/またはLEP溶媒は、したがって、例えば、LEP溶媒がバンクをある程度濡らし、示されるようにバンクを上るLEPの尾を残すように調整され得る。図11はバンク端部と平縁の正確な配置を示すが、実際にはこれはなくてもよいにしても、この構造は、バンク端部の配置において小さなばらつき(これは、特に先細りされたバンク端部で生じ得る)を許容することが理解されよう。

【0054】

図12は、本発明の第2の側面によるウェル構造1200の第1の代替の実施態様を示す。図11に示される実施態様のように、これはある程度理想化された構造を表す。再び、平縁1102が形成されるが、この場合、金属階段はITO層508の下ではなく上を覆う。前と同様、平縁1102はウェル502の底部における内部端部の周辺の「画像フレーム」を提供する。図12の実施態様における注意すべき特徴は、金属602とLEP層512の直接接触である。この配列は、仕事関数の相違のために金属とLEPの間の直接接触領域から光が放射されないかまたはほとんどされないので、バンク配列に対する改良された頑丈さを提供する。金属602は、PEDOTのような正孔輸送層(存在する場合)と接触しないことでアノードとしてのその効果を減らすことがないものとし、および/または金属602およびLEP層の間の接触領域中で発光された光が見えないように実質的に不透明であるように十分厚いものとし、および/または低い仕事関数を有するものとする。不透明性のために、金属602は好ましくは30nmを超える厚さを有する(不透明性のために必要とされる正確な厚さは材料によって異なる)。

【0055】

図13は、平縁1102がウェルバンク層504の傾斜面を上るウェル構造1300の第3の(理想的な)例を示す。構造1300は、例えば、ポジ型バンクフォトレジスト層504がスピンコートされフォトリソグラフィーによりパターニングされた後に、スピンオンガラスのブランケット堆積により製造され得る。次いで、スピンオンガラスは、平縁を残してスピンオンガラスを除去する非等方性、好ましくはドライエッチングプロセスを使用して、ブランケット(マスク無し)エッチングされ得る。より一般的には、他の低温またはスピンオン材料が堆積され、続いて非等方性エッチングバックによりバンクレジスト端部の内部の親水性スペースを形成することができる。図13の実施態様はより高い平縁の利点を有し、これによって改良された溶媒留めを潜在的に提供する。

【0056】

図14は、ウェル構造1400の他の代替の実施態様であり、階段層は、この実施例では、シリコン窒化物絶縁層612の下、およびITO層508の下に、ドープされないおよびドープされたアモルファスシリコン層606,608および第2金属層610を有する。ITO層508の下にスペーサー堆積層を伴うこの構造は、潜在的により高い階段端部およびこれによってより広い平縁表面積および改良されたPEDOT−バンク分離を提供することができる。

【0057】

図15は、ウェル構造1500の他の代替の実施態様であり、図14に示されるものに似ているが、シリコン窒化物誘電体層604の下に、第1金属層602により供給された他の階段の追加を伴う、図14に示された実施態様の層の同じ組合せにより形成される2段を有する。これは、ITO層508の下により高いスペーサー堆積層およびこれによって平縁1102の潜在的により大きな表面積を提供する。

【0058】

図16は、ウェル構造1600のさらに他の代替的な実施態様を示し、この構造において先細りバンク504端部の2つの代替的な相対的配置を示しており、配置の許容範囲の広さを示している。

【0059】

図16の構造において、ITO層508が金属層の1つの上に堆積され、例示において、第1金属層602および次いで自己整合スペーサー平縁1102が(パターニングされた)ITO層508の端部周辺に形成される。先細りバンク層504の端部は下部金属層に配置されるが、ITO層508に正確に配置される必要がない。なぜなら、下層金属層602が露出されても、仕事関数の不適合により、形成されるダイオードは発光効率がよくないからである。したがって、図16の構造1600の画素の発光は本質的にITO508の面積によって決まり、配置の許容範囲の広い構造を提供する。それにもかかわらず、前のように、平縁はPEDOT含有溶媒をウェルの側面の底部に向けて引っ張る効果を有する(および、これがITOを覆うので、濡れまたは、他の点ではバンク端部の程度は本質的に重要ではない。というのは、バンク端部の直近では実効的なデバイスは存在しないからである。)。

【0060】

この原理は、いくつかの点で図12の実施態様に類似している。ただし、この実施態様では、画素領域(の周囲)のいくつかは配置の許容範囲を広げるために実効的に費やされている。例示されるように、図16における第1の実施態様において、金属は透明であるが、PEDOTと接触せず、したがって高仕事関数金属であり得る。図16の第2の実施態様において、金属は透明で、バンクの配置ミスのためPEDOTと接触されることがあり、これは、この実施態様における金属層は好ましくは低仕事関数を有し、PEDOTとの不適合を提供することを意味する。

【0061】

図17を参照すると、「インク液滴」堆積ウェルの底部の親水性材料の短く突き出た棚を有するデバイスを製造するために示されるように、これはOLEDデバイスの製造方法の実施態様を示す。この方法も、アンダーカットバンクを有するデバイスを製造するために、種々に有益である。

【0062】

より詳細には、図17a〜17cはウェル構造1700の製造における連続的な工程を示し、ここでは、前に採用した参照番号を使用し、OLEDディスプレイの画素のためのウェル502は基板上のバンク504によって規定される。基板506はITO508層を有し、画素のためのアノード接続を提供し、その上に酸化物スペーサー層514および次いでバンク材料(好ましくは従来の形でパターン形成されたポジ型フォトレジストなどの有機材料で形成される)が堆積されて、図17aに示されるように基板に対して傾くバンク504を形成する。

【0063】

図17bにおいて、SiO2層514の非等方性ドライ(プラズマガス)エッチングはバンク504をマスクとして使用して行われ、自己整合エッチングマスク法を提供する。これは、図17cに示されるように、前方に出た階段の製造の用意である。これは、バンク材料で規定されるものと実質的に同じ開口を生成する。あるいは、溶液(または、ドライ、プラズマ)等方性エッチングが行われ、酸化物層514の下部を切除し、図17bに示される真直ぐな垂直な端部ではなく、図5に示されるような一般的なタイプの構造を製造することができる。他の代替において、溶液(またはドライ、プラズマ)等方性エッチングが行われ、次の工程で十分なバンク材料が除去されて、図17cに示される突き出た階段を残すことができる。

【0064】

図17cはO2プラズマアッシングレジストストリップ工程後の構造を示し、この工程は、画素端部において薄くなることで短絡を生じないように、バンク504の厚さを減らして開口を広げ、示されるようにSiO2層514の端部を露出する。この工程は、酸化物および下層ITOを清浄化して十分濡れるようにし、PEDOT溶液の堆積、これに続くLEP堆積の準備をする。

【0065】

この方法の実施態様は、レジストバンク画素ウェルの端部における親水性作用を提供し、この作用を酸化物層に対する独立したマスクを使用しないで自己整合または部分的自己整合によって行うことを可能にする。さらに、もし端部(突き出た階段または下部切除)構造が、アルミニウムのような層の側面に形成されると、アノード接続が低仕事関数金属(通常、アノードはITOのような高仕事関数金属である)で形成されるときこのダイオード構造は非効率であるから、この層はアクティブ画素の自然な規定も提供することができる。この方法の実施態様は、標準のポジ型レジストが(画素バンク端部を横切るカソード金属化のための良好な階段被覆を維持するために)使用されるのを可能にする。したがって、LEPインクは、PEDT濡れおよびLEP濡れプロセスを分断しながら、表面エネルギー改変処理プロセス(例えば、前述したように、CF4プラズマ処理)に基づいて(場合によって)閉じ込められ得る。これは、表面調整工程がLEPのために調整され(画素レジスト内における良好な閉じ込めを潜在的に可能にし)、一方、PEDT濡れは、自己整合された画素端部(突き出した階段または下層切除)構造の親水性または毛細管現象により強くまたは実質的に完全に頼るので、レジスト上のPEDT接触角には敏感ではないことがある。

【0066】

本発明の実施態様は、ポジ型バンクレジストの使用を可能にし、前述した構造上の利点、特に、画素端部にわたって不連続部なしに良好な金属カソード接続を形成すること、およびPEDOTの分離された段階およびLEP(または他の発光材料)堆積のための構造(例えば、表面調整)の採用を容易化するためにPEDOTおよびLEP濡れ工程を実質的に分離することを提供する。さらに、例えば、追加のマスク/パターニング工程の必要なく前述した構造の実施態様は自己整合または部分的自己整合工程を使用して製造されることができる。他の実施態様は、前記アノード接続が、例えば、4電子ボルト未満および/または介在する正孔輸送層なしの低仕事関数金属により形成されるとき、発光ダイオード構造の固有の非効率性の利点をとり配置の許容範囲の広さを達成する。大まかに言って、本発明の実施態様は、前記材料が堆積されるウェルの側面においてPEDOT(およびLEP)溶媒の濡れ/留めを容易化するための表面エネルギー関連技術に頼る。

【0067】

上述したウェル構造は、溶液堆積有機電子デバイスの広い範囲に採用され得る。これらは、アクティブまたはパッシブマトリックス電子発光ディスプレイデバイス、または、例えば、いわゆるバンク層および/または有機電子材料の堆積のために準備されるデバイスのためのTFTベースのアクティブマトリックス背板に組み込まれ得る。

言うまでもなく、当業者は他の効果的な代替例を思いつくであろう。本発明は上記の実施態様に限定されることはなく、添付の特許請求の範囲の精神と範囲内にある技術において当業者には自明な変更を含んでいることを理解されたい。

【図面の簡単な説明】

【0068】

【図1】OLEDデバイスの例の垂直断面図を示す。

【図2】3色画素OLEDディスプレイの一部の上面図を示す。

【図3a】パッシブマトリックスOLEDデバイスの上面図を示す。

【図3b】パッシブマトリックスOLEDデバイスの断面図を示す。

【図4a】溶解した材料で満たされたOLEDディスプレイ基板のウェルの簡略断面図を示す。

【図4b】乾燥した材料で満たされたOLEDディスプレイのウェルの簡略断面図を示す。

【図5】本発明の第1の側面の第1の実施態様の有機電子デバイス構造を示す。

【図6】本発明の側面を実施する製造並行構造に適した底面ゲート型薄膜トランジスタ(TFT)構造を示す。

【図7】本発明の第1の側面の第2の実施態様の有機電子デバイス構造を示す。

【図8】本発明の第1の側面の第3の実施態様の有機電子デバイス構造を示す。

【図9】本発明の第1の側面の第4の実施態様の有機電子デバイス構造を示す。

【図10】本発明の第1の側面の第5の実施態様の有機電子デバイス構造を示す。

【図11】本発明の第2の側面の第1の実施態様の有機電子デバイス構造を示す。

【図12】本発明の第2の側面の第2の実施態様の有機電子デバイス構造を示す。

【図13】本発明の第2の側面の第3の実施態様の有機電子デバイス構造を示す。

【図14】本発明の第2の側面の第4の実施態様の有機電子デバイス構造を示す。

【図15】本発明の第2の側面の第5の実施態様の有機電子デバイス構造を示す。

【図16】本発明の第2の側面の第6の実施態様の有機電子デバイス構造を示す。

【図17a】本発明の側面の実施態様の有機電子デバイスの製造を示す。

【図17b】本発明の側面の実施態様の有機電子デバイスの製造を示す。

【図17c】本発明の側面の実施態様の有機電子デバイスの製造を示す。

【符号の説明】

【0069】

100 OLED

102 基板

106 アノード層

108 正孔輸送層

110 カソード層

112 バンク

114 ウェル

200 アクティブマトリックス画素OLEDディスプレイ

300 基板

302 カソード下層分離体

304 領域

306 アノード層

308 ウェル

310 バンク

400 断面図

402 溶解した材料

404 固体薄膜

500 第1構造

502 ウェル

504 バンク

506 基板

508 ITO層

510 PEDOT層

512 LEP層

514 スペーサー

516 棚

518 ITO層

600 底面ゲート型TFT

602 金属材料層

604 誘電体層

606 ドープされないアモルファスシリコン層

608 ドープされたアモルファスシリコン層

610 第2金属層

1102 平縁

1200 ウェル構造

1300 ウェル構造

【特許請求の範囲】

【請求項1】

有機電子デバイスの液滴堆積ベースの製造のための構造における液滴堆積ウェルの形成方法であって、

基板上に、親水性材料層を堆積させる工程、

前記親水性材料層の上にバンク材料層を堆積させる工程、

前記バンク材料層をパターニングして前記液滴堆積ウェルの1または2以上を形成するバンクを規定する工程、および

前記バンク材料のパターニング層をマスクとして使用して、自己整合(self−aligned)プロセスにおいて、前記親水性材料層をエッチングする工程を含む形成方法。

【請求項2】

前記エッチング工程は、前記バンクの端部において、前記親水性層における下層切除を規定するための等方性エッチング工程を含む請求項1に記載の形成方法。

【請求項3】

前記エッチング工程は、非等方性エッチング工程を含む請求項1に記載の形成方法。

【請求項4】

前記バンクは、前記バンク材料の単一層および前記親水性材料の単一層によって規定される請求項1ないし3のいずれかに記載の形成方法。

【請求項5】

前記親水性材料は誘電体材料を含む請求項1ないし4のいずれかに記載の形成方法。

【請求項6】

前記親水性材料は金属を含む請求項1ないし4のいずれかに記載の形成方法。

【請求項7】

前記バンク材料はレジスト材料を含み、前記方法は、前記液滴堆積ウェルの1または2以上を形成する前記バンクの底部に隣接する親水性材料の前記エッチングされた層の上部表面の一部を露出するために、前記エッチング工程の後にレジストのストリッピング法を行う工程をさらに含む請求項1ないし6のいずれかに記載の形成方法。

【請求項8】

有機電子デバイスの液滴堆積ベースの製造のための構造における液滴堆積ウェルの形成方法であって、

基板上に、親水性材料層を堆積させる工程、

前記親水性材料層の上にレジスト材料層を堆積させる工程、

前記レジスト材料層をパターニングして前記液滴堆積ウェルの1または2以上を形成するバンクを規定する工程、

前記親水性材料層をパターニングして、前記液滴堆積ウェルの1または2以上の底部領域の少なくとも1部から前記親水性材料を除去する工程、および

レジストストリッピング法を使用して、前記液滴堆積ウェルの1または2以上を形成する前記バンクの底部に隣接する親水性材料の前記パターニングされた層の上部表面の一部を露出する工程を含む方法。

【請求項9】

前記レジストストリッピング法はプラズマアッシングを含む請求項7または8に記載の方法。

【請求項10】

前記液滴堆積ウェル中に液滴堆積プロセスを使用して溶解した有機電子材料を堆積させることにより、前記有機電子デバイスを形成する工程をさらに含む請求項1ないし9のいずれかに記載の方法。

【請求項11】

前記有機電子デバイスはOLEDデバイスを含み、前記溶解した有機電子材料はPEDOTの親水性溶液を含む請求項10に記載の方法。

【請求項12】

有機電子材料で満たされた複数の液滴堆積ウェルの下の親水性材料のパターニングされた層を有する基板を含む有機電子デバイスであって、前記液滴堆積ウェルの1または2以上を形成する前記バンクの底部に隣接する親水性材料の前記パターニングされた層の上部表面の一部が前記有機電子材料に露出される有機電子デバイス。

【請求項13】

有機電子デバイス構造であって、

基板、および

前記基板によって支持され、有機電子材料の溶媒ベースの堆積のためのウェルを規定するバンク層を含み、

前記構造は、さらに前記ウェルの内部端部および前記ウェルの底部にある平縁を規定するようにパターニングされた平縁層を含む有機電子デバイス構造。

【請求項14】

前記平縁は親水性材料を含む請求項13に記載の有機電子デバイス構造。

【請求項15】

前記平縁はシリコンの酸化物および/または窒化物を含む請求項13に記載の有機電子デバイス構造。

【請求項16】

前記バンク層の厚さは前記ウェルの側面が近づくにつれ前記基板に向けて薄くなり、前記平縁は前記バンク層の前記薄くなった部分に乗り上げることを特徴とする請求項13ないし15のいずれかに記載の有機電子デバイス構造。

【請求項17】

前記ウェルの前記内部端部における段部を規定するようにパターニングされる1または2以上の段部層をさらに含み、前記平縁が前記段部に接することを特徴とする請求項13ないし15のいずれかに記載の有機電子デバイス構造。

【請求項18】

前記基板によって支持され、前記ウェルの前記底部を規定する底部層をさらに含み、前記段部層は前記底部層と前記基板の間にあり、前記段部は前記基板から前記底部層までの間隔で段階的変化を有し、前記平縁は前記底部層に接することを特徴とする請求項17に記載の有機電子デバイス構造。

【請求項19】

前記平縁のための前記ウェルの前記内部端部における2段を規定するようにパターニングされた少なくとも2つの前記段部層を有する請求項18に記載の有機電子デバイス構造。

【請求項20】

前記バンク層の厚さは前記ウェルの側面が近づくにつれ前記基板に向けて薄くなり、前記底部層の位置と前記ウェルの内部端部周辺の前記有機電子材料の接触を可能にすること特徴とする請求項18または19に記載の有機電子デバイス構造。

【請求項21】

前記1または2以上の段部層は、前記有機電子デバイスの活性部分のための金属および/またはシリコン層を有する請求項13ないし20のいずれかに記載の有機電子デバイス構造。

【請求項22】

前記バンク層は、ポジ型フォトレジストを含み、前記有機電子材料は導電性材料の第1層と発光材料の第2層を含む請求項13ないし21のいずれかに記載の有機電子デバイス構造を含むOLEDディスプレイデバイス。

【請求項23】

有機電子材料の溶媒ベースの堆積のための少なくとも1つのウェルを有する基板上への有機電子デバイスの形成方法であって、前記方法は、前記デバイスの形成のための前記有機電子材料の溶媒ベースの堆積の前に、平縁層を堆積させて前記平縁層を非等方的にエッチングして、前記ウェルの内部端部において平縁を規定する工程を含むことを特徴とする方法。

【請求項1】

有機電子デバイスの液滴堆積ベースの製造のための構造における液滴堆積ウェルの形成方法であって、

基板上に、親水性材料層を堆積させる工程、

前記親水性材料層の上にバンク材料層を堆積させる工程、

前記バンク材料層をパターニングして前記液滴堆積ウェルの1または2以上を形成するバンクを規定する工程、および

前記バンク材料のパターニング層をマスクとして使用して、自己整合(self−aligned)プロセスにおいて、前記親水性材料層をエッチングする工程を含む形成方法。

【請求項2】

前記エッチング工程は、前記バンクの端部において、前記親水性層における下層切除を規定するための等方性エッチング工程を含む請求項1に記載の形成方法。

【請求項3】

前記エッチング工程は、非等方性エッチング工程を含む請求項1に記載の形成方法。

【請求項4】

前記バンクは、前記バンク材料の単一層および前記親水性材料の単一層によって規定される請求項1ないし3のいずれかに記載の形成方法。

【請求項5】

前記親水性材料は誘電体材料を含む請求項1ないし4のいずれかに記載の形成方法。

【請求項6】

前記親水性材料は金属を含む請求項1ないし4のいずれかに記載の形成方法。

【請求項7】

前記バンク材料はレジスト材料を含み、前記方法は、前記液滴堆積ウェルの1または2以上を形成する前記バンクの底部に隣接する親水性材料の前記エッチングされた層の上部表面の一部を露出するために、前記エッチング工程の後にレジストのストリッピング法を行う工程をさらに含む請求項1ないし6のいずれかに記載の形成方法。

【請求項8】

有機電子デバイスの液滴堆積ベースの製造のための構造における液滴堆積ウェルの形成方法であって、

基板上に、親水性材料層を堆積させる工程、

前記親水性材料層の上にレジスト材料層を堆積させる工程、

前記レジスト材料層をパターニングして前記液滴堆積ウェルの1または2以上を形成するバンクを規定する工程、

前記親水性材料層をパターニングして、前記液滴堆積ウェルの1または2以上の底部領域の少なくとも1部から前記親水性材料を除去する工程、および

レジストストリッピング法を使用して、前記液滴堆積ウェルの1または2以上を形成する前記バンクの底部に隣接する親水性材料の前記パターニングされた層の上部表面の一部を露出する工程を含む方法。

【請求項9】

前記レジストストリッピング法はプラズマアッシングを含む請求項7または8に記載の方法。

【請求項10】

前記液滴堆積ウェル中に液滴堆積プロセスを使用して溶解した有機電子材料を堆積させることにより、前記有機電子デバイスを形成する工程をさらに含む請求項1ないし9のいずれかに記載の方法。

【請求項11】

前記有機電子デバイスはOLEDデバイスを含み、前記溶解した有機電子材料はPEDOTの親水性溶液を含む請求項10に記載の方法。

【請求項12】

有機電子材料で満たされた複数の液滴堆積ウェルの下の親水性材料のパターニングされた層を有する基板を含む有機電子デバイスであって、前記液滴堆積ウェルの1または2以上を形成する前記バンクの底部に隣接する親水性材料の前記パターニングされた層の上部表面の一部が前記有機電子材料に露出される有機電子デバイス。

【請求項13】

有機電子デバイス構造であって、

基板、および

前記基板によって支持され、有機電子材料の溶媒ベースの堆積のためのウェルを規定するバンク層を含み、

前記構造は、さらに前記ウェルの内部端部および前記ウェルの底部にある平縁を規定するようにパターニングされた平縁層を含む有機電子デバイス構造。

【請求項14】

前記平縁は親水性材料を含む請求項13に記載の有機電子デバイス構造。

【請求項15】

前記平縁はシリコンの酸化物および/または窒化物を含む請求項13に記載の有機電子デバイス構造。

【請求項16】

前記バンク層の厚さは前記ウェルの側面が近づくにつれ前記基板に向けて薄くなり、前記平縁は前記バンク層の前記薄くなった部分に乗り上げることを特徴とする請求項13ないし15のいずれかに記載の有機電子デバイス構造。

【請求項17】

前記ウェルの前記内部端部における段部を規定するようにパターニングされる1または2以上の段部層をさらに含み、前記平縁が前記段部に接することを特徴とする請求項13ないし15のいずれかに記載の有機電子デバイス構造。

【請求項18】

前記基板によって支持され、前記ウェルの前記底部を規定する底部層をさらに含み、前記段部層は前記底部層と前記基板の間にあり、前記段部は前記基板から前記底部層までの間隔で段階的変化を有し、前記平縁は前記底部層に接することを特徴とする請求項17に記載の有機電子デバイス構造。

【請求項19】

前記平縁のための前記ウェルの前記内部端部における2段を規定するようにパターニングされた少なくとも2つの前記段部層を有する請求項18に記載の有機電子デバイス構造。

【請求項20】

前記バンク層の厚さは前記ウェルの側面が近づくにつれ前記基板に向けて薄くなり、前記底部層の位置と前記ウェルの内部端部周辺の前記有機電子材料の接触を可能にすること特徴とする請求項18または19に記載の有機電子デバイス構造。

【請求項21】

前記1または2以上の段部層は、前記有機電子デバイスの活性部分のための金属および/またはシリコン層を有する請求項13ないし20のいずれかに記載の有機電子デバイス構造。

【請求項22】

前記バンク層は、ポジ型フォトレジストを含み、前記有機電子材料は導電性材料の第1層と発光材料の第2層を含む請求項13ないし21のいずれかに記載の有機電子デバイス構造を含むOLEDディスプレイデバイス。

【請求項23】

有機電子材料の溶媒ベースの堆積のための少なくとも1つのウェルを有する基板上への有機電子デバイスの形成方法であって、前記方法は、前記デバイスの形成のための前記有機電子材料の溶媒ベースの堆積の前に、平縁層を堆積させて前記平縁層を非等方的にエッチングして、前記ウェルの内部端部において平縁を規定する工程を含むことを特徴とする方法。

【図1】

【図2】

【図3a】

【図3b】

【図4a】

【図4b】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17a】

【図17b】

【図17c】

【図2】

【図3a】

【図3b】

【図4a】

【図4b】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17a】

【図17b】

【図17c】

【公開番号】特開2012−43813(P2012−43813A)

【公開日】平成24年3月1日(2012.3.1)

【国際特許分類】

【出願番号】特願2011−258870(P2011−258870)

【出願日】平成23年11月28日(2011.11.28)

【分割の表示】特願2008−527504(P2008−527504)の分割

【原出願日】平成18年8月22日(2006.8.22)

【出願人】(597063048)ケンブリッジ ディスプレイ テクノロジー リミテッド (152)

【Fターム(参考)】

【公開日】平成24年3月1日(2012.3.1)

【国際特許分類】

【出願日】平成23年11月28日(2011.11.28)

【分割の表示】特願2008−527504(P2008−527504)の分割

【原出願日】平成18年8月22日(2006.8.22)

【出願人】(597063048)ケンブリッジ ディスプレイ テクノロジー リミテッド (152)

【Fターム(参考)】

[ Back to top ]