温度センサ

【課題】量子井戸型の温度センサにおいて、高い障壁高さを実現できる量子障壁層と量子井戸層とを、フェルミ準位の上昇およびトンネル効果が生じにくい膜厚を持って形成する。

【解決手段】この量子井戸型温度センサは、基体の表面上に量子井戸構造体を備え、量子井戸構造体は、基体に隣接して形成された第1電極層と、第1電極層上に形成されたサーミスタ層と、サーミスタ層上に形成された第2電極層とを有している。サーミスタ層は、量子井戸層を少なくとも一層含み、複数の量子障壁層を有するとともに、第1電極層、サーミスタ層、第2電極層の積層方向に沿って量子井戸層と量子障壁層とが交互に配置されてなる。

そして、量子井戸層および量子障壁層は、これらの層により形成される量子井戸の障壁高さが0.34eVより大きい材料からなり、第1電極層の結晶格子に対する格子不整合率が、それぞれ、4%以下および0.9%以下の材料からなる。

【解決手段】この量子井戸型温度センサは、基体の表面上に量子井戸構造体を備え、量子井戸構造体は、基体に隣接して形成された第1電極層と、第1電極層上に形成されたサーミスタ層と、サーミスタ層上に形成された第2電極層とを有している。サーミスタ層は、量子井戸層を少なくとも一層含み、複数の量子障壁層を有するとともに、第1電極層、サーミスタ層、第2電極層の積層方向に沿って量子井戸層と量子障壁層とが交互に配置されてなる。

そして、量子井戸層および量子障壁層は、これらの層により形成される量子井戸の障壁高さが0.34eVより大きい材料からなり、第1電極層の結晶格子に対する格子不整合率が、それぞれ、4%以下および0.9%以下の材料からなる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、赤外線ひいては温度を検出する量子井戸型赤外線温度センサに関する。

【背景技術】

【0002】

赤外線は温度を持ったすべての物体表面から放射されている。赤外線温度センサは、物体の温度に応じて変化する赤外線の放射強度を、離れた場所から捉え、例えば、物体表面の温度分布を画像化するために用いられる温度センサである。この温度センサは、夜間においても物体の動きを画像化できるため、セキュリティ監視に用いるセンサネットワークのキーデバイスとして、注目され、赤外線に対する感度の向上が求められている。

【0003】

赤外線温度センサとして、熱絶縁構造体が赤外線を吸収した際の温度上昇を、電気抵抗値の変化として検出する、所謂ボロメータが知られている。また、ボロメータタイプの赤外線温度センサとして、量子井戸型赤外線センサ(Quantum Well Infrared Photodetector : QWIP)が知られている。QWIPは、バンドギャップエネルギーの異なる複数種類の半導体をナノスケールで積層して量子井戸を形成し、エネルギー準位の差を用いて赤外線を受けたことによる温度変化を電気抵抗値の変化として検出する。積層される半導体として、特許文献1には、ガリウムヒ素(GaAs)とアルミニウムガリウムヒ素(AlGaAs)とを用いる例が示されている。この例では、GaAsが量子井戸層として機能し、AlGaAsが量子障壁層として機能している。また、特許文献1には、積層される半導体として、よりバンドギャップ差の大きいシリコン(Si)とシリコンゲルマニウム(Si1−xGex)とが用いられるSiGe/Si系の例も示されている(xはGe組成比)。この例では、SiGeが量子井戸層として機能し、Siが量子障壁層として機能している。

【0004】

ボロメータの赤外線検出感度を向上するためには、抵抗温度係数(Temperature Coefficient of Resistance : TCR)を大きくすることが必要である。QWIPのように、量子井戸が形成された半導体積層構造におけるTCRは、次式で表される。

【0005】

TCR=−1/kT2×(3kT/2+V−EF)

k:ボルツマン定数、T[K]:絶対温度、V(=EB−EW):障壁エネルギー、EB:量子障壁層の価電子帯の頂上(または伝導帯の底)のエネルギー、EW:井戸層の価電子帯の頂上(または伝導帯の底)のエネルギー、EF:フェルミ準位

ここで、量子井戸層がP型にドープされているときは、EB、EWはそれぞれ価電子帯の頂上を意味し、量子井戸層がN型にドープされているときは、EB、EWはそれぞれ伝導帯の底を意味する。

【0006】

このため、QWIPにおいて、赤外線検出感度を向上させる(|TCR|の値を大きくする)ためには、障壁高さVを大きくする、あるいは、フェルミ準位EFを小さくすることが必要である。例えば、上記したSiGe/Si系においては、量子井戸層であるP型にドープされたSi1−xGex層により形成される価電子帯の障壁高さVが、Ge組成比xに比例する。この系においては、V=0.84x[eV]と書き表せる。したがって、Ge組成比xが大きいほど、障壁高さVを大きくでき、|TCR|の値を大きくすることができる。非特許文献1には、Ge組成比x=0.4において、|TCR|≒3.5%/Kとなる構成が示されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特許第3573754号公報

【非特許文献】

【0008】

【非特許文献1】S G E Wissmar, H H Radamsson, Y Yamamoto, B Tillack, C Vieider, J Y Andersson, Journal of Physics: Conference Series 100 (2008) 042029, p.3

【発明の概要】

【発明が解決しようとする課題】

【0009】

ところで、一般に、格子定数の互いに異なる材料同士、例えば元素E1の表面上に元素E2が積層される場合においては、成膜される薄膜の膜厚に臨界膜厚が存在する。例えば、Si表面上のSiGe薄膜は、エピタキシャル成長により所定膜厚まで成長させると、Si−SiGe間における結晶格子の不整合による歪みを緩和するために、結晶欠陥を生じてしまう。結晶欠陥を生じると、暗電流などによるノイズが増大するため、赤外線温度センサのS/N比が低下してしまう。そして、図17に示されるように、この臨界膜厚は、格子不整合率rが大きいほど小さくなる。図17に記載されたラインA、ラインBは、理論より求められた格子不整合率に対する臨界膜厚を示すものであり、ラインAがPeopleらによるエネルギー平衡理論であり、ラインBがMatthewsらによる力学的平衡理論である。また、図17中のプロットは実験値である。ここで、格子不整合率rは、元素E1およびE2の格子定数aE1およびaE2に対して、次式で表される。

【0010】

r=(aE2−aE1)/aE1

Si1−xGex/Si系においては、この臨界膜厚が、Ge組成比xの増加に伴って減少する。換言すれば、Si表面上に形成される、量子井戸層としてのSiGe薄膜は、障壁高さVを増加させるためにGe組成比xを増加させると、その膜厚を薄膜化しなければならない。これは、Ge組成比xが増加するにしたがって、SiGe層とSi層との格子不整合率rが大きくなるためである。量子井戸層(Si表面上のSiGe薄膜)の膜厚が所定の厚さよりも薄くなると、量子効果によりフェルミ準位EFが急激に上昇するため、|TCR|が減少してしまう。また、量子障壁層(Si薄膜)の膜厚が所定の膜厚よりも薄くなると、隣り合う量子井戸層間でキャリアがトンネルしてしまい、見かけ上の障壁高さが減少し、|TCR|が減少してしまう。

【0011】

一方、AlGaAs/GaAs系においては、量子障壁層としてのAlGaAs薄膜の膜厚を薄膜化しなければならない。量子障壁層(GaAs表面上のAlGaAs薄膜)の膜厚が所定の膜厚よりも薄くなると、隣り合う量子井戸層間でキャリアがトンネルしてしまい、見かけ上の障壁高さが減少し、|TCR|が減少してしまう。また、量子井戸層(GaAs薄膜)の膜厚が所定の厚さよりも薄くなると、量子効果によりフェルミ準位EFが急激に上昇するため、|TCR|が減少してしまう。

【0012】

このように、障壁高さVとフェルミ準位EFは、量子井戸層を形成する半導体の組成と、量子井戸層の層厚をパラメータとしたトレードオフの関係にある。また、量子障壁層の薄膜化は、トンネル効果による|TCR|減少の原因となる。

【0013】

例えば、特許文献1に示されるような、GaAs表面上のInGaAs/AlGaAs系やサファイヤ表面上のGaN/AlGaN系では、Si1−xGex/Si系(x=1のときV≒0.84eV)に較べて高い障壁高さVを確保できるものの、そのような条件下では、格子不整合率rがSiGe/Si系に較べて大きいため、0.1nmのオーダーでしか量子井戸層および量子障壁層を成膜することができない。したがって、高い障壁高さVによる効果が、量子効果によるフェルミ準位EFの増加およびトンネル効果により相殺されてしまう。すなわち、量子井戸型の温度センサの構成として現実的ではない。

【0014】

また、Si1−xGex/Si系においても、非特許文献1に示されるx=0.4よりもGe組成比を大きくすると、量子井戸型の温度センサを構成する量子井戸層を薄膜化しなければならず、量子効果によるフェルミ準位EFの増加に起因する|TCR|の低下を引き起こす。

【0015】

本発明は、上記問題点に鑑みてなされたものであり、量子井戸構造を有する温度センサにおいて、高い障壁高さVを実現できる量子障壁層と量子井戸層とを、フェルミ準位の上昇およびトンネル効果が生じにくい膜厚を持って、形成することを目的とする。

【課題を解決するための手段】

【0016】

上記目的を達成するために、請求項1に記載の発明は、

基体と、

該基体上に形成された量子井戸構造体と、を備え、

量子井戸構造体は、基体に隣接して形成された第1導電型の第1電極層と、該第1電極層上に形成されたサーミスタ層と、該サーミスタ層上に形成された第1導電型の第2電極層と、を有する積層構造をなし、

サーミスタ層は、量子井戸層を少なくとも一層と、量子障壁層を複数層有するとともに、第1電極層、サーミスタ層、第2電極層の積層方向に沿って量子井戸層と量子障壁層とが交互に配置されてなる、量子井戸型の温度センサであって、

量子井戸層と、量子障壁層とは、これらの層が積層されることにより形成される量子井戸の障壁高さが0.34eVより大きい材料からなり、

量子井戸層は、第1電極層の結晶格子に対する格子不整合率が4%以下の材料からなり、

量子障壁層は、第1電極層の結晶格子に対する格子不整合率が0.9%以下の材料からなることを特徴としている。

【0017】

本発明では、量子井戸層と量子障壁層とが、これら層により形成される量子井戸の障壁高さが0.34eVより大きくなる材料から形成されている。これにより、例えば、Si1−xGex/Si系におけるx=0.4の場合よりも大きな障壁高さを実現することができる。

【0018】

そして、量子井戸層を構成する材料として、第1電極層の結晶格子に対する格子不整合率が4%以下になる材料を用いている。このような構成にすることにより、量子井戸層を、量子効果に起因したフェルミ準位EFの上昇が生じにくい層厚まで成膜することができる。発明者は、コンピュータシミュレーションを用いて、TCRの量子井戸層厚依存性を確認している(後述する[発明を実施するための形態]の図11参照)。量子井戸層の層厚を0.3nmよりも薄膜化すると、量子効果が支配的となり、フェルミ準位EFが急激に上昇して、層厚が4nm以上の場合に較べてTCRが低い値で推移することがわかる。すなわち、この量子効果を抑制するためには、量子井戸層の層厚を0.3nm以上にすることが好ましい。なお、臨界膜厚は格子不整合率rに依存することが一般に知られている。図17は、格子不整合率rに対する臨界膜厚を示す図であり、これによれば、層厚を0.3nm以上確保するために必要な格子不整合率rの条件はr≦4%である。したがって、量子井戸層を構成する材料を、第1電極層の結晶格子に対する格子不整合率が4%以下になるように選択することにより、TCRの減少を抑制することができる。

【0019】

また、量子障壁層を構成する材料として、第1電極層の結晶格子に対する格子不整合率が0.9%以下になる材料を用いている。このような構成にすることにより、隣り合う量子井戸層間でトンネルするキャリアの量QTが、障壁を越えて移動するキャリアの量Q以下になるような層厚まで量子障壁層を成膜することができる。トンネル効果によるキャリアの移動は、熱励起でない理由でキャリアが移動するため、見かけ上の障壁高さVを小さくしてしまい、|TCR|の値を小さくする原因となる。発明者は、コンピュータシミュレーションを用いて、QT/Qの量子障壁層厚依存性を確認している(後述する[発明を実施するための形態]の図12参照)。量子障壁層の層厚を5nm以上に設定することにより、QT/Q≦1を実現できていることがわかる。そして、図17によれば、層厚を5nm以上確保するために必要な格子不整合率rの条件はr≦0.9%となることがわかる。したがって、量子障壁層を構成する材料を、第1電極層の結晶格子に対する格子不整合率が0.9%以下になるように選択することにより、量子井戸層間のキャリアのトンネル現象を抑制でき、TCRの減少を抑制することができる。

【0020】

以上のような構成にすることにより、サーミスタ層において、エピタキシャル成長により形成される量子井戸層および量子障壁層の膜厚を、従来構造、例えば特許文献1に示されたSiGe/Si系、InGaAs/AlGaAs系およびGaN/AlGaN系に較べて、厚くすることができる。したがって、薄膜化による量子効果でフェルミ準位EFが上昇すること、ならびに、トンネル効果による意図しないキャリアの移動を抑制することができる。そして、障壁高さVが0.34eVよりも大きくなるような材料を量子井戸層および量子障壁層を構成する材料として選択することにより、|TCR|の値を従来構造の温度センサの値に較べて大きくすることができる。すなわち、温度センサの感度を向上させることができる。

【0021】

請求項2に記載のように、第1電極層、第2電極層、および量子井戸層はシリコンからなり、量子障壁層はガリウムリンからなるとよい。

【0022】

本発明では、第1電極層、第2電極層および量子井戸層の構成材料が、シリコンであり、それぞれ格子定数が同じである。このため、量子井戸層の第1電極層に対する格子不整合率はr=0である。また、量子障壁層の構成材料は、ガリウムリン(GaP)であり、格子定数はaGaP≒0.545nmである。したがって、シリコン(aSi≒0.543nm)に対する格子不整合率はr≒0.34%となり、図17によれば、GaP薄膜はSi表面上に略100nm成膜することができる。且つ、GaP/Si系の障壁高さはV≒1.44eVであり、従来構造、例えばSi1−xGex/Si系における障壁高さ(x=1では0.84eV、現実的な構成であるx=0.4ではV≒0.34eV)に較べて、大幅に大きくすることができる。すなわち、量子井戸におけるフェルミ準位EFの上昇、および量子障壁におけるトンネル効果を抑制しつつ、障壁高さVを大幅に向上させることができ、温度センサの感度を向上させることができる。

【0023】

加えて、請求項3に記載のように、量子障壁層は、層厚が7nm以上であるとよい。

【0024】

このような構成にすることにより、GaP/Si系において、隣り合う量子井戸層間でトンネルするキャリアの量QTが、障壁を越えて移動するキャリアの量Q以下(QT/Q≦1)になるようにすることができる(後述する[発明を実施するための形態]の図10参照)。トンネル効果によるキャリアの移動は、熱励起でない理由でキャリアが移動するため、見かけ上の障壁高さVを小さくしてしまい、|TCR|の値を小さくする原因となる。本発明の構成では、このトンネル効果を抑制することができるため、|TCR|の値の減少を抑制することができ、温度センサの感度の低下を抑制することができる。

【0025】

また、請求項4に記載のように、第1電極層、第2電極層、および量子井戸層はシリコンからなり、量子障壁層はアルミニウムリンからなるとよい。

【0026】

本発明では、第1電極層、第2電極層および量子井戸層の構成材料が、シリコンであり、それぞれ格子定数が同じである。このため、量子井戸層の第1電極層に対する格子不整合率はr=0である。また、量子障壁層の構成材料は、AlPであり、格子定数はaAlP≒0.546nmである。したがって、シリコン(aSi≒0.543nm)に対する格子不整合率はr≒0.58%となり、図17によれば、AlP薄膜はSi表面上に略10nm成膜することができる。且つ、AlP/Si系の障壁高さはV≒0.86eVであり、従来構造、例えばSi1−xGex/Si系における障壁高さ(x=1では0.84eV、現実的な構成であるx=0.4ではV≒0.34eV)に較べて、大きくすることができる。すなわち、量子井戸におけるフェルミ準位EFの上昇、および量子障壁におけるトンネル効果を抑制しつつ、障壁高さVを大幅に向上させることができ、温度センサの感度を向上させることができる。

【0027】

加えて、請求項5に記載のように、量子障壁層は、層厚が5nm以上であるとよい。

【0028】

このような構成にすることにより、AlP/Si系において、隣り合う量子井戸層間でトンネルするキャリアの量QTが、障壁を越えて移動するキャリアの量Q以下(QT/Q≦1)になるようにすることができる(後述する[発明を実施するための形態]の図12参照)。本発明の構成では、トンネル効果を抑制することができるため、|TCR|の値の減少を抑制することができ、温度センサの感度の低下を抑制することができる。

【0029】

請求項6に記載のように、量子障壁層は真性半導体からなり、量子井戸層は不純物がドープされたP型の半導体からなるとよい。

【0030】

これによれば、量子障壁層を真性半導体とすることにより、量子井戸層におけるフェルミ準位EFの増大を抑制することができる。また、量子井戸層に不純物をドープすることによってP型とし、ホールをキャリアとすることにより、価電子帯の障壁高さVを|TCR|の値に寄与させることができる。換言すれば、P型にドープされた量子井戸層においては、真性半導体に較べて、フェルミ準位が価電子帯に寄るため、キャリアはホールとなり、|TCR|の値に寄与するバンドは価電子帯となる。逆に、N型にドープされた量子井戸層においては、真性半導体に較べて、フェルミ準位が伝導帯に寄るため、キャリアは電子となり、|TCR|の値に寄与するバンドは伝導帯となる。そして、GaP/Si系およびAlP/Si系においては、価電子帯の障壁高さが伝導帯の障壁高さよりも大きい。すなわち、量子井戸層をP型の半導体で構成することにより、N型の半導体で構成する場合に較べて、|TCR|の値に寄与する障壁高さVを大きくすることができる。したがって、温度センサの感度を向上することができる。

【0031】

また、請求項7に記載のように、量子井戸層は、層厚が4nm以上であるとよい。

【0032】

このような構成においては、図11に示すように、TCRは層厚が4nmより小さい場合に較べて高い値で安定する。したがって、量子井戸層の薄膜化による量子効果を抑制でき、|TCR|の値を大きくすることができる。すなわち、温度センサの感度を向上させることができる。また、|TCR|の値が安定するため、製造ばらつきに起因する量子井戸層の層厚ばらつきに対して、|TCR|のばらつきを抑制することができる。したがって、温度センサは安定した感度を得ることができる。

【0033】

請求項8に記載のように、量子井戸構造体は、基体に形成されたメンブレン上に形成されるとよい。

【0034】

このようにすることにより、熱コンダクタンスを小さくすることができるため、感度を向上させることができる。すなわち、量子井戸構造体からの熱の逃げを小さくできるので、温度センサのS/N比を大きくすることができる。

【図面の簡単な説明】

【0035】

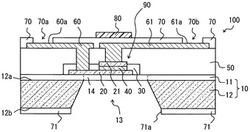

【図1】第1実施形態に係る温度センサの概略構成を示す断面図である。

【図2】図1に示す温度センサのうち、量子井戸構造体の周辺を拡大した断面図である。

【図3】温度センサの製造工程のうち、SOI基板の準備工程を示す断面図である。

【図4】温度センサの製造工程のうち、第1電極層の形成工程、および絶縁膜のパターニング工程を示す断面図である。

【図5】温度センサの製造工程のうち、サーミスタ層の形成工程を示す断面図である。

【図6】図5において、サーミスタ層を拡大した断面図である。

【図7】温度センサの製造工程のうち、第2電極層の形成工程を示す断面図である。

【図8】温度センサの製造工程のうち、絶縁膜のパターニング工程を示す断面図である。

【図9】温度センサの製造工程のうち、配線形成工程を示す断面図である。

【図10】障壁を越えて移動するキャリアの量Qに対する、隣り合う量子井戸層間でトンネルするキャリアの量QTの割合の、量子障壁層厚依存性を示すグラフである。

【図11】TCRに対する量子井戸層厚依存性を示すグラフである。

【図12】第2実施形態に係る温度センサにおいて、障壁を越えて移動するキャリアの量Qに対する、隣り合う量子井戸層間でトンネルするキャリアの量QTの割合の、量子障壁層厚依存性を示すグラフである。

【図13】その他実施例に係る温度センサの製造工程のうち、SOI基板の準備工程を示す断面図である。

【図14】温度センサの製造工程のうち、サーミスタ層の全面エピ成長工程を示す断面図である。

【図15】温度センサの製造工程のうち、サーミスタ層および第2電極層のパターニング工程を示す断面図である。

【図16】温度センサの製造工程のうち、絶縁膜のパターニング工程を示す断面図である。

【図17】臨界膜厚に対する格子不整合率依存性を示すグラフである。

【発明を実施するための形態】

【0036】

以下、本発明の実施の形態を図面に基づいて説明する。なお、以下の各図相互において、互いに同一もしくは均等である部分に、同一符号を付与する。

【0037】

(第1実施形態)

本実施形態における温度センサは、QW構造体(Quantum Well構造体、以下、サーミスタ層と示す)の温度の変化による電流変化を検出するものであり、特に赤外線センサとして好適なものである。換言すると、温度によって抵抗値が変化する検出部であるサーミスタ層を備えた温度センサである。なお、本実施形態における温度センサは、|TCR|が大きいため、赤外線の検出に適用することによって、非常に高感度に赤外線を検出することができる。

【0038】

最初に、図1および図2を参照して、本実施形態に係る温度センサ100の構成を説明する。

【0039】

図1に示すように、本実施形態における温度センサ100は、基体10として、一面上に絶縁膜11が形成された半導体基板12を有している。本実施形態では、単結晶シリコンからなる半導体基板12の一面12a側に絶縁膜11として酸化膜(SiO2)が形成されている。半導体基板12には、絶縁膜11を底面として、裏面12b側に開口する空洞部13が形成されている。そして、絶縁膜11における空洞部13の架橋部分(底面)が薄肉部としてのメンブレン14を成している。

【0040】

また、絶縁膜11における半導体基板12と反対の面上には、第1電極層20が形成されている。第1電極層20は、一部がメンブレン14上に位置し、メンブレン14上から半導体基板12上の部分まで延設されている。なお、本実施形態における第1電極層20は、単結晶シリコンからなり、後述するサーミスタ層40を構成する半導体層よりも濃度の高いP型とされている。例えば、濃度1×1020cm−3でホウ素(B)がドープされている。なお、半導体基板12、絶縁膜11および第1電極層20の積層構造は、SOI(silicon on insulator)基板を用いることにより得ることができる。この場合、SOI基板の活性層が第1電極層20に相当する。

【0041】

さらに、図2に示すように、この第1電極層20は、絶縁膜(例えばSiO2)30によって覆われ、この絶縁膜30の所定部位に形成された開口部30a(コンタクト用の開口部)を通じて、例えばアルミニウムなどで構成された配線60に電気的に接続されている。また、第1電極層20は、絶縁膜30の別の所定部位に形成された開口部30b(検出部用の開口部)が形成されることにより、露出した表面にサーミスタ層40が形成されている。なお、サーミスタ層40における第1電極層20と接する面と反対側の表面には、第1電極層20と同一の材料および不純物のドープにより形成された第2電極層21が形成されている。特許請求の範囲において、第1電極層20、第2電極層21およびサーミスタ層40を量子井戸構造体90と称している。サーミスタ層40および第2電極層21もメンブレン14上に位置し、ひいては、量子井戸構造体90がメンブレン14上に位置している。そして、第2電極層21は、例えばアルミニウムなどで構成された配線61に電気的に接続されている。

【0042】

サーミスタ層40は、図2に示すように、複数(本実施形態では2層)の量子障壁層41a,41bと、この量子障壁層41a,41bに挟まれた量子井戸層42とを備え、一方の量子障壁層41aが、第1電極層20に接し、他方の量子障壁層41bが第2電極層21に接している。換言すると、サーミスタ層40は、量子井戸層42と量子障壁層41a,41bとが、前記量子井戸層42を少なくとも一層含んで、第1電極層20の表面に垂直な方向に交互に積層されている。なお、本発明の特徴部分であるサーミスタ層40における各層の構成材料、不純物のドーズ量および膜厚については、後ほど詳述する。

【0043】

また、絶縁膜11、第1電極層20、第2電極層21、絶縁膜30およびサーミスタ層40を覆うように絶縁膜(例えば、SiO2)50が形成され、この絶縁膜50により量子井戸構造体90が保護されている。この絶縁膜50は、第1電極層20、サーミスタ層40、第2電極層21を積層した厚みよりも厚く形成されており、絶縁膜30に形成された開口部30a,30bや第2電極層21に対応する部位に、配線60,61が配置される開口部50a,50bが形成されている。すなわち、配線60は、絶縁膜50上および絶縁膜50に形成された開口部50aに形成され、絶縁膜30の開口部30a(コンタクト用)を通じて第1電極層20に電気的に接続されている。また、配線61は、絶縁膜50上および絶縁膜50に形成された別の開口部50bに形成され、第2電極層21に電気的に接続されている。

【0044】

この絶縁膜50に形成された配線60,61の表面には保護膜(例えば、SiN)70が形成されている。この保護膜70には、配線60,61におけるパッド部60a,61aを構成するための開口部70a,70bが形成されている。温度センサ100は、この開口部70a,70bを通じてパッド部60a,61aに対してワイヤボンディングなどがなされることで、外部に備えられる処理回路(図示省略)に電気的に接続されるようになっている。また、保護膜70におけるサーミスタ層40に対応する位置には、カーボンペーストなどからなる赤外線吸収膜80が形成されている。

【0045】

そして、半導体基板12における絶縁膜11と反対の裏面側には、保護膜(例えば、SiN)71が形成されている。この保護膜71には開口部71aが形成されており、この開口部71aに連通して半導体基板12の空洞部13が形成されている。

【0046】

このような構成の温度センサ100においては、紙面上方から入射した赤外線を赤外線吸収膜80で吸収する。この赤外線の吸収によって、サーミスタ層40の温度が上昇する。したがって、2つの配線60,61に直流電圧を与えることで、サーミスタ層40を流れる電流の変化により温度を検出することができる。

【0047】

次に、図3〜図9を参照して、本実施形態に係る温度センサ100の製造方法を説明する。

【0048】

まず、図3に示すように、半導体基板12、絶縁膜11および活性層20aからなるSOI基板を準備する。なお、特許請求の範囲における基体10は、絶縁膜11と半導体基板12とを有する基板を指す。ここで、本実施形態では、活性層20aとして、ホウ素が濃度1×1020cm−3でドープされた、単結晶シリコンからなるP型の半導体層を採用する。

【0049】

次いで、図示しないが、活性層20aをパターニングすることにより第1電極層20を形成する。具体的には、少なくとも、サーミスタ層40および配線60が電気的に接続される部位を残して活性層20aをパターニングして第1電極層20を形成する。そして、図4に示すように、形成された第1電極層20を覆うように、絶縁膜30を形成する。具体的には、プラズマCVD、低圧CVDなどによって、第1電極層20の表面に絶縁膜30を形成する。その後、その絶縁膜30をパターニングして、サーミスタ層40を形成する領域に開口部30bを形成する。

【0050】

次いで、図5に示すように、開口部30bに対して、サーミスタ層40を構成する各層を選択的に成膜(選択エピ成長)する。具体的には、図6に示すように、開口部30bによって露出した第1電極層20の表面に、一方の量子障壁層41a、量子井戸層42、および他方の量子障壁層41bを、この順番で選択的にエピタキシャル成長することにより成膜する。なお、本発明の特徴部分であるサーミスタ層40における各層の構成材料、不純物のドーズ量および膜厚については、後ほど詳述する。

【0051】

次いで、図7に示すように、サーミスタ層40の表面(第1電極層20と反対の面)に第2電極層21を形成して、量子井戸構造体90が形成される。本実施形態において、第2電極層21は、単結晶シリコンからなり、ホウ素が濃度1×1020cm−3でドープされた、P型の半導体層である。すなわち、第1電極層20と同一の材料およびドーズ量に設定している。そして、図8に示すように、量子井戸構造体90と絶縁膜30とを覆うように絶縁膜50を成膜して、その絶縁膜50と絶縁膜30とをパターニングして配線60,61を形成するための開口部50a,50b,30aを形成することによって、第1電極層20と第2電極層21とを部分的に露出させる。

【0052】

次いで、図9に示すように、開口部50a,50bが形成された絶縁膜50上に、配線60,61を構成する、例えばアルミニウムを成膜し、このアルミニウム膜をパターニングすることにより、配線60,61を形成する。これによって、配線60,61は、開口部30a,50a,50bおよび絶縁膜50の表面(上面)に形成され、第1電極層20および第2電極層21と電気的に接続される。その後、絶縁膜50および絶縁膜50上に形成された配線60,61上に、保護膜70を成膜する。そして、この保護膜70をパターニングしてパッド部60a,61aを形成するための開口部70a,70bを形成する。さらに、半導体基板12の裏面を研削・研磨し、次いで、保護膜71をプラズマCVDにより形成する。

【0053】

その後、サーミスタ層40がメンブレン14上に配置されるように、半導体基板12および保護膜71に空洞部13と開口部71aとを形成する。具体的には、保護膜71をパターニングして、空洞部13に対応する部分に開口部71aを形成する。そして、保護膜71をマスクとし、SOI基板の埋め込み層である絶縁膜11をエッチングストップ層として、半導体基板12の裏面から、半導体基板12をウェットエッチングして空洞部13を形成する。つまり、このように、半導体基板12の裏面から、半導体基板12をウェットエッチングしてメンブレン14を形成する。そして、保護膜70におけるサーミスタ層40に対応する位置に、カーボンペーストなどからなる赤外線吸収膜80を、例えば印刷法により形成する。

【0054】

なお、本実施形態の温度センサ100のような量子井戸型の赤外線温度センサは、CMOSプロセスで製造すれば、容易に回路を一体形成できノイズを抑制できる。また、既存の半導体工場で製造することができ、既存の生産ラインを利用することができる利点があり有利である。

【0055】

ここで、本発明の特徴部分であるサーミスタ層40の構成材料、不純物のドーズ量および各層の膜厚に関して説明する。

【0056】

まず、量子障壁層41a,41bおよび量子井戸層42を構成する材料について説明する。量子障壁層41a,41bは、量子井戸層42を構成する材料のバンドギャップよりも大きなバンドギャップを有する材料によって構成される。量子障壁層41a,41bおよび量子井戸層42を構成する材料の、それぞれのバンドギャップと電子親和力から、量子障壁層41a,41bおよび量子井戸層42により形成される量子井戸の障壁高さVが決まる。本実施形態では、量子障壁層41a,41bとして、ガリウムリン(GaP:バンドギャップ2.26eV、電子親和力4.30eV)が用いられ、量子井戸層42として、シリコン(バンドギャップ1.11eV、電子親和力4.01eV)が用いられる。これらの材料により構成される量子井戸の障壁高さVは1.44eVであり、従来構造、例えばSi1−xGex/Si系における障壁高さ(x=1では0.84eV、現実的な構成であるx=0.4ではV≒0.34eV)に較べて、大幅に大きくすることができる。

【0057】

また、本実施形態における材料構成、すなわち、量子障壁層41a,41bとして、ガリウムリン(格子定数aGaP≒0.545nm)が用いられ、量子井戸層42として、シリコン(格子定数aSi≒0.543nm)が用いられる構成においては、格子不整合率rが0.34%となる。この格子不整合率は、Si1−xGex/Si系における格子不整合率(x=1でr≒4.2%、x=0.4でr≒1.7%)に較べて小さい。このため、図17に示される実験値および理論から、GaPからなる量子障壁層41a,41bは、Siからなる量子井戸層42の表面上に、100nm程度(実験値からの概算)、または、略20nm程度(力学的平衡理論:Matthewsらの理論、図17中Bのライン)積層することができる。なお、量子井戸層42であるSiは、第1電極層20に対する格子不整合率がr=0であるため、SiをGaP層上に任意の膜厚で積層することができる。したがって、量子障壁層41a,41bをトンネルするキャリアの数を抑制することができ、且つ、量子井戸層42における、量子効果起因のフェルミ準位EFの上昇を抑制することができる。

【0058】

このように、本実施形態では、従来構造、例えばSi1−xGex/Si系における障壁高さに較べて、高い障壁高さを実現でき、且つ、量子障壁層41a,41bと量子井戸層42とを、フェルミ準位の上昇およびトンネル効果を生じない膜厚を持って形成することができる。このため、温度センサの|TCR|の値を増加させることができ、感度を向上させることができる。

【0059】

次に、量子障壁層41a,41bおよび量子井戸層42にドープする不純物のドーズ量について説明する。本実施形態では、量子障壁層41a,41bを真性半導体(不純物をドープしない)としている。これにより、量子障壁層41a,41bと量子井戸層52との接合時に、フェルミ準位が上昇することを抑制することができ、|TCR|の値の低下を抑制することができる。また、本実施形態では、伝導帯における障壁高さが0.29eV、価電子帯における障壁高さが1.44eVであるため、量子井戸層42にホウ素を不純物としてドープしている(ドーズ量は、例えば、略1×1016cm−3)。これにより、量子井戸層42はP型の半導体層となり、サーミスタ層40はホールをキャリアとして動作する。すなわち、|TCR|の値に寄与する障壁高さVは、価電子帯における障壁高さである1.44eVとなり、キャリアに電子を用いる場合に較べて、高い障壁高さを実現することができる。したがって、|TCR|の値を上昇させることができ、温度センサの感度を向上させることができる。なお、量子井戸層42にドープされる不純物の濃度は、高いほどフェルミ準位EFが増加するため、|TCR|の値が減少してしまう。したがって、この濃度は、なるべく低濃度とすることが好ましいが、濃度のばらつきによる|TCR|の製造ばらつきを抑制するため、本実施形態のように、1×1016cm−3程度の濃度とすることが好ましい。

【0060】

次に、量子障壁層41a,41bおよび量子井戸層42の層厚について具体的に説明する。本実施形態においては、量子障壁層41a,41bの層厚を、例えば、略7nmとすることができる。量子障壁層41a,41bの層厚は、隣り合う量子井戸層42間(本実施形態では、量子井戸層42は1層のみのため、量子井戸層42と第1電極層20または第2電極層21の間)でトンネルするキャリアを抑制するように設定する。すなわち、量子障壁層41a,41bをトンネルするキャリアの量QTが、障壁を越えて移動するキャリアの量Q以下(QT/Q≦1)になるように、量子障壁層41a,41bの層厚を設定する。発明者は、コンピュータシミュレーションを用いて、QT/Qの量子障壁層厚依存性を確認している。図10はこのコンピュータシミュレーションの結果である。図10に示すように、QT/Q≦1となる量子障壁層41a,41bの層厚は7nm以上である。トンネル効果により、意図しないキャリアの移動が生じると、見かけ上の障壁高さVが低下して|TCR|が減少してしまう。このため、本実施形態のように、量子障壁層41a,41bの層厚を7nmとすれば、量子障壁層41a,41bに欠陥を生じさせることなく、トンネル効果によるキャリアの移動を抑制することができ、|TCR|の値が低下することを抑制することができる。

【0061】

また、本実施形態においては、量子井戸層42の層厚を、例えば、略4nmとすることができる。量子井戸層42の層厚は、量子効果によりキャリア(本実施形態ではホール)が縮退して、フェルミ準位EFが上昇することを抑制するように設定する。発明者は、コンピュータシミュレーションを用いて、TCRの量子井戸層厚依存性を確認している。図11はこのコンピュータシミュレーションの結果である。図11には、本実施形態における材料構成、すなわち、サーミスタ層40を構成する量子障壁層41a,41bとして、ガリウムリンが用いられる構成の他に、第2実施形態にて後述するように、量子障壁層41a,41bとして、アルミニウムリンが用いられる構成のシミュレーション結果も併せて記載している。なお、各系において、量子井戸層42にドープする不純物濃度を変更したシミュレーション結果も併せて記載されている。図11に示すように、量子井戸層42の層厚を4nmとすることにより、TCRは、層厚が4nmより小さい場合に較べて高い値で安定する。したがって、量子井戸層42の薄膜化による量子効果を抑制でき、|TCR|の値を大きくすることができる。すなわち、温度センサの感度を向上させることができる。また、|TCR|の値が安定するため、製造ばらつきに起因する量子井戸層42の層厚ばらつきに対して、|TCR|のばらつきを抑制することができる。したがって、温度センサは安定した感度を得ることができる。

【0062】

(第2実施形態)

第1実施形態では、サーミスタ層40を構成する量子障壁層41a,41bとして、ガリウムリンが用いられ、量子井戸層42として、シリコンが用いられる例を示した。これに対して、本実施形態では、サーミスタ層40を構成する量子障壁層41a,41bとして、アルミニウムリンが用いられ、量子井戸層42として、シリコンが用いられる例を示す。

【0063】

サーミスタ層40を構成する材料、膜厚以外の要素に関しては、第1実施形態と同様であるため、詳細の記載を省略する。

【0064】

まず、本実施形態における量子障壁層41a,41bおよび量子井戸層42を構成する材料について説明する。第1実施形態でも記載のように、量子障壁層41a,41bおよび量子井戸層42により形成される量子井戸の障壁高さVは、量子障壁層41a,41bおよび量子井戸層42を構成する材料の、それぞれのバンドギャップと電子親和力により決まる。本実施形態では、量子障壁層41a,41bとして、アルミニウムリン(AlP:バンドギャップ2.48eV、電子親和力3.50eV)が用いられ、量子井戸層42として、シリコン(バンドギャップ1.11eV、電子親和力4.01eV)が用いられる。これらの材料により構成される量子井戸の障壁高さVは0.86eVであり、従来構造、例えばSi1−xGex/Si系における障壁高さ(x=1では0.84eV、現実的な構成であるx=0.4ではV≒0.34eV)に較べて、大きくすることができる。

【0065】

また、本実施形態における材料構成、すなわち、量子障壁層41a,41bとして、アルミニウムリン(格子定数aAlP≒0.546nm)が用いられ、量子井戸層42として、シリコン(格子定数aSi≒0.543nm)が用いられる構成においては、格子不整合率rが0.58%となる。この格子不整合率は、Si1−xGex/Si系における格子不整合率(x=1でr≒4.2%、x=0.4でr≒1.7%)に較べて小さい。このため、図17に示される実験値および理論から、AlPからなる量子障壁層41a,41bは、Siからなる量子井戸層42の表面上に、略10nm程度(力学的平衡理論:Matthewsらの理論)積層することができる。なお、量子井戸層42であるSiは、第1電極層20に対する格子不整合率がr=0であるため、SiをAlP層上に任意の膜厚で積層することができる。したがって、量子障壁層41a,41bをトンネルするキャリアの数を抑制することができ、且つ、量子井戸層42における、量子効果起因のフェルミ準位EFの上昇を抑制することができる。

【0066】

このように、本実施形態では、従来構造、例えばSi1−xGex/Si系における障壁高さに較べて、高い障壁高さを実現でき、且つ、量子障壁層41a,41bと量子井戸層42とを、フェルミ準位の上昇およびトンネル効果を生じない膜厚を持って形成することができる。このため、温度センサの|TCR|の値を増加させることができ、感度を向上させることができる。

【0067】

量子障壁層41a,41bおよび量子井戸層42にドープする不純物のドーズ量に関しては、第1実施形態と同様に、量子障壁層41a,41bを真性半導体(不純物をドープしない)とし、量子井戸層42にホウ素を不純物としてドープして、P型としている(ドーズ量は、例えば、略1×1016cm−3)。これは、本実施形態におけるサーミスタ層40の材料構成において、伝導帯における障壁高さが0.51eV、価電子帯における障壁高さが0.86eVであり、価電子帯の障壁高さが伝導帯の障壁高さよりも高いためである。すなわち、第1実施形態と同様に、ホールをキャリアとすることにより、キャリアに電子を用いる場合に較べて、高い障壁高さを実現することができる。したがって、|TCR|の値を上昇させることができ、温度センサの感度を向上させることができる。なお、第1実施形態と同様に、量子井戸層42にドープされる不純物の濃度は、なるべく低濃度とすることが好ましいが、濃度のばらつきによる|TCR|の製造ばらつきを抑制するため、本実施形態のように、1×1016cm−3程度の濃度とすることが好ましい。

【0068】

次に、量子障壁層41a,41bおよび量子井戸層42の層厚について具体的に説明する。本実施形態においては、量子障壁層41a,41bの層厚を、例えば、略5nmとすることができる。第1実施形態と同様に、量子障壁層41a,41bの層厚は、量子障壁層41a,41bをトンネルするキャリアの量QTが、障壁を越えて移動するキャリアの量Q以下(QT/Q≦1)になるように設定する。発明者は、コンピュータシミュレーションを用いて、QT/Qの量子障壁層厚依存性を確認している。図12はこのコンピュータシミュレーションの結果である。図12に示すように、QT/Q≦1となる量子障壁層41a,41bの層厚は5nm以上である。トンネル効果により、意図しないキャリアの移動が生じると、見かけ上の障壁高さVが低下して|TCR|が減少してしまう。このため、本実施形態のように、量子障壁層41a,41bの層厚を5nmとすれば、量子障壁層41a,41bに欠陥を生じさせることなく、トンネル効果によるキャリアの移動を抑制することができ、|TCR|の値が低下することを抑制することができる。

【0069】

また、第1実施形態と同様に、本実施形態においても、量子井戸層42の層厚を、例えば、略4nmとすることができる。図11に示すように、量子井戸層42の膜厚に対するTCRは、量子井戸層42の構成材料および不純物濃度に依存するが、TCRの変化率(換言すると、膜厚に対するグラフの形状)は、量子井戸層42の構成材料および不純物濃度に殆ど依存しない。すなわち、量子効果によりフェルミ準位EFが上昇する量子井戸層42の膜厚は、量子井戸層42を構成する材料、ドーズ量に依らない。したがって、本実施形態においても、量子井戸層42の層厚を略4nmとすることにより、第1実施形態の場合と同様に作用効果を得ることができる。すなわち、量子井戸層42の薄膜化による量子効果を抑制でき、|TCR|の値を大きくすることができる。したがって、温度センサの感度を向上させることができる。また、|TCR|の値が安定するため、製造ばらつきに起因する量子井戸層42の層厚ばらつきに対して、|TCR|のばらつきを抑制することができる。

【0070】

(その他の実施形態)

以上、本発明の好ましい実施形態について説明したが、本発明は上述した実施形態になんら制限されることなく、本発明の主旨を逸脱しない範囲において、種々変形して実施することが可能である。

【0071】

上記した各実施形態においては、第1電極層20、第2電極層21、および量子井戸層42にシリコンを用い、量子障壁層41a,41bにガリウムリンあるいはアルミニウムリンを用いた例を示した。しかしながら、上記例に限定されるものではない。量子井戸層42と、前記量子障壁層41a,41bとは、これらの層が積層されることにより形成される量子井戸の障壁高さが0.34eVより大きい材料からなり、量子井戸層42は、第1電極層20の結晶格子に対する格子不整合率rが4%以下の材料から構成されており、且つ、量子障壁層41a,41bは、第1電極層20の結晶格子に対する格子不整合率rが0.9%以下の材料から構成されていればよい。

【0072】

また、上記した各実施形態では、サーミスタ層40は、量子障壁層41a,41bに挟まれた一層の量子井戸層42からなる単層のQW構造を例として採用しているが、本発明は、これに限定されるものではない。例えば、量子井戸層と量子障壁層とが、複数の量子井戸層を含んで、第1電極層20の表面に垂直な方向に交互に積層されてなる、MQW(Multi Quantum Well)構造を採用するようにしてもよい。

【0073】

また、上記した各実施形態では、量子障壁層41a,41bが真性半導体からなる構成を例に示したが、本発明は、これに限定されるものではない。例えば、上記した各実施形態において、量子障壁層41a,41bに、不純物としてホウ素をドープして、量子井戸層42よりも不純物濃度の薄いP型としてもよい。

【0074】

また、上記した各実施形態では、量子井戸層42の不純物としてホウ素をドープしてP型とする例を示した。しかしながら、量子井戸層42の導電型は、P型に限定されるものではない。例えば、量子障壁層41a,41bおよび量子井戸層42を構成する材料を選定するにあたって、伝導帯の障壁高さが価電子帯の障壁高さよりも大きい構成とした場合には、量子井戸層42の導電型をN型にすることが好ましい。これにより、量子井戸層42が真性半導体である場合に較べて、フェルミ準位が伝導帯に寄るため、キャリアは電子となり、|TCR|の値に寄与するバンドは伝導帯となる。したがって、量子井戸層42をP型とする場合に較べて、|TCR|の値に寄与する障壁高さを大きくすることができ、温度センサの感度を向上させることができる。

【0075】

また、上記した各実施形態では、量子井戸層42の層厚を4nmとする例を示したが、量子井戸層42の層厚は、0.3nm以上であれば採用することができる。図11に示すように、量子井戸層の層厚が0.3nmより小さくなると、|TCR|の値は、層厚が4nm以上の場合に較べて低い値で推移する。これは、量子効果によるフェルミ準位EFの上昇が支配的になるためである。換言すれば、量子井戸層の層厚を0.3nm以上に設定することにより、フェルミ準位EFの上昇を抑制することができ、|TCR|の値の減少を抑制することができる。

【0076】

また、上記した各実施形態では、量子井戸構造体90が形成される基体10として、SOI基板を構成する半導体基板12、絶縁膜11および活性層20aのうち、単結晶シリコンからなる半導体基板12と絶縁膜11とで構成された基板を用いる例を示したが、本発明は、これに限定されるものではない。量子井戸構造体90が形成される基体10は、量子井戸構造体90との接触部分が少なくとも絶縁性の基板であればよい。例えば、単結晶以外のシリコン(Poly−Siや非晶質シリコン)および、その表面上に形成された絶縁膜を含む基板を基体10として用いても良いし、ガラス基板を基体10として用いても良い。

【0077】

また、上記した各実施形態では、温度センサ100の製造方法として、サーミスタ層40を選択エピ成長させて形成する例を示した。しかしながら、温度センサ100の製造方法は、上記例に限定されるものではない。例えば、図13〜図16に示す方法で製造することができる。以下、図13〜図16を用いて、温度センサ100の製造方法の一例を説明する。

【0078】

まず、図13に示すように、上記した各実施形態と同様、SOI基板を準備する。次いで、図14に示すように、サーミスタ層40を構成する量子障壁層41a,量子井戸層42、量子障壁層41bおよび第2電極層21を、この順番でエピタキシャル成長する(全面エピ成長)。各層の構成材料は、上記した実施形態と同一の組み合わせを用いることができる。そして、図15に示すように、全面エピ成長により成膜した量子障壁層41a,41b、量子井戸層42および第2電極層21をパターニングする。その後、図16に示すように、活性層20aをパターニングして第1電極層20を形成し、絶縁膜11、第1電極層20、サーミスタ層40および第2電極層21を覆うように絶縁膜50を形成する。そして、その絶縁膜50をパターニングして配線60,61を形成するための開口部50a,50bを形成することによって、第1電極層20と第2電極層21とを部分的に露出させる。本実施形態における図16の状態は、上記した各実施形態における図8に相当する。配線60,61を形成する工程以降の工程は、各実施形態と同一であるため、その記載を省略する。この全面エピ成長による方法によっても、本発明に係る温度センサ100を製造することができる。

【0079】

なお、上記した各実施形態においては、サーミスタ層40がメンブレン14上に配置される例を示したが、サーミスタ層40は必ずしもメンブレン14上に配置される必要はない。ただし、サーミスタ層40をメンブレン14上に配置することにより、熱コンダクタンスを小さくすることができるため、感度を向上させることができる。すなわち、サーミスタ層40からの熱の逃げを小さくできるので、温度センサのS/N比を大きくすることができる。

【符号の説明】

【0080】

10・・・基体

11,30,50・・・絶縁膜

12・・・半導体基板

14・・・メンブレン

20・・・第1電極層

21・・・第2電極層

40・・・サーミスタ層

60,61・・・配線

70,71・・・保護膜

80・・・赤外線吸収膜

90・・・量子井戸構造体

100・・・温度センサ

【技術分野】

【0001】

本発明は、赤外線ひいては温度を検出する量子井戸型赤外線温度センサに関する。

【背景技術】

【0002】

赤外線は温度を持ったすべての物体表面から放射されている。赤外線温度センサは、物体の温度に応じて変化する赤外線の放射強度を、離れた場所から捉え、例えば、物体表面の温度分布を画像化するために用いられる温度センサである。この温度センサは、夜間においても物体の動きを画像化できるため、セキュリティ監視に用いるセンサネットワークのキーデバイスとして、注目され、赤外線に対する感度の向上が求められている。

【0003】

赤外線温度センサとして、熱絶縁構造体が赤外線を吸収した際の温度上昇を、電気抵抗値の変化として検出する、所謂ボロメータが知られている。また、ボロメータタイプの赤外線温度センサとして、量子井戸型赤外線センサ(Quantum Well Infrared Photodetector : QWIP)が知られている。QWIPは、バンドギャップエネルギーの異なる複数種類の半導体をナノスケールで積層して量子井戸を形成し、エネルギー準位の差を用いて赤外線を受けたことによる温度変化を電気抵抗値の変化として検出する。積層される半導体として、特許文献1には、ガリウムヒ素(GaAs)とアルミニウムガリウムヒ素(AlGaAs)とを用いる例が示されている。この例では、GaAsが量子井戸層として機能し、AlGaAsが量子障壁層として機能している。また、特許文献1には、積層される半導体として、よりバンドギャップ差の大きいシリコン(Si)とシリコンゲルマニウム(Si1−xGex)とが用いられるSiGe/Si系の例も示されている(xはGe組成比)。この例では、SiGeが量子井戸層として機能し、Siが量子障壁層として機能している。

【0004】

ボロメータの赤外線検出感度を向上するためには、抵抗温度係数(Temperature Coefficient of Resistance : TCR)を大きくすることが必要である。QWIPのように、量子井戸が形成された半導体積層構造におけるTCRは、次式で表される。

【0005】

TCR=−1/kT2×(3kT/2+V−EF)

k:ボルツマン定数、T[K]:絶対温度、V(=EB−EW):障壁エネルギー、EB:量子障壁層の価電子帯の頂上(または伝導帯の底)のエネルギー、EW:井戸層の価電子帯の頂上(または伝導帯の底)のエネルギー、EF:フェルミ準位

ここで、量子井戸層がP型にドープされているときは、EB、EWはそれぞれ価電子帯の頂上を意味し、量子井戸層がN型にドープされているときは、EB、EWはそれぞれ伝導帯の底を意味する。

【0006】

このため、QWIPにおいて、赤外線検出感度を向上させる(|TCR|の値を大きくする)ためには、障壁高さVを大きくする、あるいは、フェルミ準位EFを小さくすることが必要である。例えば、上記したSiGe/Si系においては、量子井戸層であるP型にドープされたSi1−xGex層により形成される価電子帯の障壁高さVが、Ge組成比xに比例する。この系においては、V=0.84x[eV]と書き表せる。したがって、Ge組成比xが大きいほど、障壁高さVを大きくでき、|TCR|の値を大きくすることができる。非特許文献1には、Ge組成比x=0.4において、|TCR|≒3.5%/Kとなる構成が示されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特許第3573754号公報

【非特許文献】

【0008】

【非特許文献1】S G E Wissmar, H H Radamsson, Y Yamamoto, B Tillack, C Vieider, J Y Andersson, Journal of Physics: Conference Series 100 (2008) 042029, p.3

【発明の概要】

【発明が解決しようとする課題】

【0009】

ところで、一般に、格子定数の互いに異なる材料同士、例えば元素E1の表面上に元素E2が積層される場合においては、成膜される薄膜の膜厚に臨界膜厚が存在する。例えば、Si表面上のSiGe薄膜は、エピタキシャル成長により所定膜厚まで成長させると、Si−SiGe間における結晶格子の不整合による歪みを緩和するために、結晶欠陥を生じてしまう。結晶欠陥を生じると、暗電流などによるノイズが増大するため、赤外線温度センサのS/N比が低下してしまう。そして、図17に示されるように、この臨界膜厚は、格子不整合率rが大きいほど小さくなる。図17に記載されたラインA、ラインBは、理論より求められた格子不整合率に対する臨界膜厚を示すものであり、ラインAがPeopleらによるエネルギー平衡理論であり、ラインBがMatthewsらによる力学的平衡理論である。また、図17中のプロットは実験値である。ここで、格子不整合率rは、元素E1およびE2の格子定数aE1およびaE2に対して、次式で表される。

【0010】

r=(aE2−aE1)/aE1

Si1−xGex/Si系においては、この臨界膜厚が、Ge組成比xの増加に伴って減少する。換言すれば、Si表面上に形成される、量子井戸層としてのSiGe薄膜は、障壁高さVを増加させるためにGe組成比xを増加させると、その膜厚を薄膜化しなければならない。これは、Ge組成比xが増加するにしたがって、SiGe層とSi層との格子不整合率rが大きくなるためである。量子井戸層(Si表面上のSiGe薄膜)の膜厚が所定の厚さよりも薄くなると、量子効果によりフェルミ準位EFが急激に上昇するため、|TCR|が減少してしまう。また、量子障壁層(Si薄膜)の膜厚が所定の膜厚よりも薄くなると、隣り合う量子井戸層間でキャリアがトンネルしてしまい、見かけ上の障壁高さが減少し、|TCR|が減少してしまう。

【0011】

一方、AlGaAs/GaAs系においては、量子障壁層としてのAlGaAs薄膜の膜厚を薄膜化しなければならない。量子障壁層(GaAs表面上のAlGaAs薄膜)の膜厚が所定の膜厚よりも薄くなると、隣り合う量子井戸層間でキャリアがトンネルしてしまい、見かけ上の障壁高さが減少し、|TCR|が減少してしまう。また、量子井戸層(GaAs薄膜)の膜厚が所定の厚さよりも薄くなると、量子効果によりフェルミ準位EFが急激に上昇するため、|TCR|が減少してしまう。

【0012】

このように、障壁高さVとフェルミ準位EFは、量子井戸層を形成する半導体の組成と、量子井戸層の層厚をパラメータとしたトレードオフの関係にある。また、量子障壁層の薄膜化は、トンネル効果による|TCR|減少の原因となる。

【0013】

例えば、特許文献1に示されるような、GaAs表面上のInGaAs/AlGaAs系やサファイヤ表面上のGaN/AlGaN系では、Si1−xGex/Si系(x=1のときV≒0.84eV)に較べて高い障壁高さVを確保できるものの、そのような条件下では、格子不整合率rがSiGe/Si系に較べて大きいため、0.1nmのオーダーでしか量子井戸層および量子障壁層を成膜することができない。したがって、高い障壁高さVによる効果が、量子効果によるフェルミ準位EFの増加およびトンネル効果により相殺されてしまう。すなわち、量子井戸型の温度センサの構成として現実的ではない。

【0014】

また、Si1−xGex/Si系においても、非特許文献1に示されるx=0.4よりもGe組成比を大きくすると、量子井戸型の温度センサを構成する量子井戸層を薄膜化しなければならず、量子効果によるフェルミ準位EFの増加に起因する|TCR|の低下を引き起こす。

【0015】

本発明は、上記問題点に鑑みてなされたものであり、量子井戸構造を有する温度センサにおいて、高い障壁高さVを実現できる量子障壁層と量子井戸層とを、フェルミ準位の上昇およびトンネル効果が生じにくい膜厚を持って、形成することを目的とする。

【課題を解決するための手段】

【0016】

上記目的を達成するために、請求項1に記載の発明は、

基体と、

該基体上に形成された量子井戸構造体と、を備え、

量子井戸構造体は、基体に隣接して形成された第1導電型の第1電極層と、該第1電極層上に形成されたサーミスタ層と、該サーミスタ層上に形成された第1導電型の第2電極層と、を有する積層構造をなし、

サーミスタ層は、量子井戸層を少なくとも一層と、量子障壁層を複数層有するとともに、第1電極層、サーミスタ層、第2電極層の積層方向に沿って量子井戸層と量子障壁層とが交互に配置されてなる、量子井戸型の温度センサであって、

量子井戸層と、量子障壁層とは、これらの層が積層されることにより形成される量子井戸の障壁高さが0.34eVより大きい材料からなり、

量子井戸層は、第1電極層の結晶格子に対する格子不整合率が4%以下の材料からなり、

量子障壁層は、第1電極層の結晶格子に対する格子不整合率が0.9%以下の材料からなることを特徴としている。

【0017】

本発明では、量子井戸層と量子障壁層とが、これら層により形成される量子井戸の障壁高さが0.34eVより大きくなる材料から形成されている。これにより、例えば、Si1−xGex/Si系におけるx=0.4の場合よりも大きな障壁高さを実現することができる。

【0018】

そして、量子井戸層を構成する材料として、第1電極層の結晶格子に対する格子不整合率が4%以下になる材料を用いている。このような構成にすることにより、量子井戸層を、量子効果に起因したフェルミ準位EFの上昇が生じにくい層厚まで成膜することができる。発明者は、コンピュータシミュレーションを用いて、TCRの量子井戸層厚依存性を確認している(後述する[発明を実施するための形態]の図11参照)。量子井戸層の層厚を0.3nmよりも薄膜化すると、量子効果が支配的となり、フェルミ準位EFが急激に上昇して、層厚が4nm以上の場合に較べてTCRが低い値で推移することがわかる。すなわち、この量子効果を抑制するためには、量子井戸層の層厚を0.3nm以上にすることが好ましい。なお、臨界膜厚は格子不整合率rに依存することが一般に知られている。図17は、格子不整合率rに対する臨界膜厚を示す図であり、これによれば、層厚を0.3nm以上確保するために必要な格子不整合率rの条件はr≦4%である。したがって、量子井戸層を構成する材料を、第1電極層の結晶格子に対する格子不整合率が4%以下になるように選択することにより、TCRの減少を抑制することができる。

【0019】

また、量子障壁層を構成する材料として、第1電極層の結晶格子に対する格子不整合率が0.9%以下になる材料を用いている。このような構成にすることにより、隣り合う量子井戸層間でトンネルするキャリアの量QTが、障壁を越えて移動するキャリアの量Q以下になるような層厚まで量子障壁層を成膜することができる。トンネル効果によるキャリアの移動は、熱励起でない理由でキャリアが移動するため、見かけ上の障壁高さVを小さくしてしまい、|TCR|の値を小さくする原因となる。発明者は、コンピュータシミュレーションを用いて、QT/Qの量子障壁層厚依存性を確認している(後述する[発明を実施するための形態]の図12参照)。量子障壁層の層厚を5nm以上に設定することにより、QT/Q≦1を実現できていることがわかる。そして、図17によれば、層厚を5nm以上確保するために必要な格子不整合率rの条件はr≦0.9%となることがわかる。したがって、量子障壁層を構成する材料を、第1電極層の結晶格子に対する格子不整合率が0.9%以下になるように選択することにより、量子井戸層間のキャリアのトンネル現象を抑制でき、TCRの減少を抑制することができる。

【0020】

以上のような構成にすることにより、サーミスタ層において、エピタキシャル成長により形成される量子井戸層および量子障壁層の膜厚を、従来構造、例えば特許文献1に示されたSiGe/Si系、InGaAs/AlGaAs系およびGaN/AlGaN系に較べて、厚くすることができる。したがって、薄膜化による量子効果でフェルミ準位EFが上昇すること、ならびに、トンネル効果による意図しないキャリアの移動を抑制することができる。そして、障壁高さVが0.34eVよりも大きくなるような材料を量子井戸層および量子障壁層を構成する材料として選択することにより、|TCR|の値を従来構造の温度センサの値に較べて大きくすることができる。すなわち、温度センサの感度を向上させることができる。

【0021】

請求項2に記載のように、第1電極層、第2電極層、および量子井戸層はシリコンからなり、量子障壁層はガリウムリンからなるとよい。

【0022】

本発明では、第1電極層、第2電極層および量子井戸層の構成材料が、シリコンであり、それぞれ格子定数が同じである。このため、量子井戸層の第1電極層に対する格子不整合率はr=0である。また、量子障壁層の構成材料は、ガリウムリン(GaP)であり、格子定数はaGaP≒0.545nmである。したがって、シリコン(aSi≒0.543nm)に対する格子不整合率はr≒0.34%となり、図17によれば、GaP薄膜はSi表面上に略100nm成膜することができる。且つ、GaP/Si系の障壁高さはV≒1.44eVであり、従来構造、例えばSi1−xGex/Si系における障壁高さ(x=1では0.84eV、現実的な構成であるx=0.4ではV≒0.34eV)に較べて、大幅に大きくすることができる。すなわち、量子井戸におけるフェルミ準位EFの上昇、および量子障壁におけるトンネル効果を抑制しつつ、障壁高さVを大幅に向上させることができ、温度センサの感度を向上させることができる。

【0023】

加えて、請求項3に記載のように、量子障壁層は、層厚が7nm以上であるとよい。

【0024】

このような構成にすることにより、GaP/Si系において、隣り合う量子井戸層間でトンネルするキャリアの量QTが、障壁を越えて移動するキャリアの量Q以下(QT/Q≦1)になるようにすることができる(後述する[発明を実施するための形態]の図10参照)。トンネル効果によるキャリアの移動は、熱励起でない理由でキャリアが移動するため、見かけ上の障壁高さVを小さくしてしまい、|TCR|の値を小さくする原因となる。本発明の構成では、このトンネル効果を抑制することができるため、|TCR|の値の減少を抑制することができ、温度センサの感度の低下を抑制することができる。

【0025】

また、請求項4に記載のように、第1電極層、第2電極層、および量子井戸層はシリコンからなり、量子障壁層はアルミニウムリンからなるとよい。

【0026】

本発明では、第1電極層、第2電極層および量子井戸層の構成材料が、シリコンであり、それぞれ格子定数が同じである。このため、量子井戸層の第1電極層に対する格子不整合率はr=0である。また、量子障壁層の構成材料は、AlPであり、格子定数はaAlP≒0.546nmである。したがって、シリコン(aSi≒0.543nm)に対する格子不整合率はr≒0.58%となり、図17によれば、AlP薄膜はSi表面上に略10nm成膜することができる。且つ、AlP/Si系の障壁高さはV≒0.86eVであり、従来構造、例えばSi1−xGex/Si系における障壁高さ(x=1では0.84eV、現実的な構成であるx=0.4ではV≒0.34eV)に較べて、大きくすることができる。すなわち、量子井戸におけるフェルミ準位EFの上昇、および量子障壁におけるトンネル効果を抑制しつつ、障壁高さVを大幅に向上させることができ、温度センサの感度を向上させることができる。

【0027】

加えて、請求項5に記載のように、量子障壁層は、層厚が5nm以上であるとよい。

【0028】

このような構成にすることにより、AlP/Si系において、隣り合う量子井戸層間でトンネルするキャリアの量QTが、障壁を越えて移動するキャリアの量Q以下(QT/Q≦1)になるようにすることができる(後述する[発明を実施するための形態]の図12参照)。本発明の構成では、トンネル効果を抑制することができるため、|TCR|の値の減少を抑制することができ、温度センサの感度の低下を抑制することができる。

【0029】

請求項6に記載のように、量子障壁層は真性半導体からなり、量子井戸層は不純物がドープされたP型の半導体からなるとよい。

【0030】

これによれば、量子障壁層を真性半導体とすることにより、量子井戸層におけるフェルミ準位EFの増大を抑制することができる。また、量子井戸層に不純物をドープすることによってP型とし、ホールをキャリアとすることにより、価電子帯の障壁高さVを|TCR|の値に寄与させることができる。換言すれば、P型にドープされた量子井戸層においては、真性半導体に較べて、フェルミ準位が価電子帯に寄るため、キャリアはホールとなり、|TCR|の値に寄与するバンドは価電子帯となる。逆に、N型にドープされた量子井戸層においては、真性半導体に較べて、フェルミ準位が伝導帯に寄るため、キャリアは電子となり、|TCR|の値に寄与するバンドは伝導帯となる。そして、GaP/Si系およびAlP/Si系においては、価電子帯の障壁高さが伝導帯の障壁高さよりも大きい。すなわち、量子井戸層をP型の半導体で構成することにより、N型の半導体で構成する場合に較べて、|TCR|の値に寄与する障壁高さVを大きくすることができる。したがって、温度センサの感度を向上することができる。

【0031】

また、請求項7に記載のように、量子井戸層は、層厚が4nm以上であるとよい。

【0032】

このような構成においては、図11に示すように、TCRは層厚が4nmより小さい場合に較べて高い値で安定する。したがって、量子井戸層の薄膜化による量子効果を抑制でき、|TCR|の値を大きくすることができる。すなわち、温度センサの感度を向上させることができる。また、|TCR|の値が安定するため、製造ばらつきに起因する量子井戸層の層厚ばらつきに対して、|TCR|のばらつきを抑制することができる。したがって、温度センサは安定した感度を得ることができる。

【0033】

請求項8に記載のように、量子井戸構造体は、基体に形成されたメンブレン上に形成されるとよい。

【0034】

このようにすることにより、熱コンダクタンスを小さくすることができるため、感度を向上させることができる。すなわち、量子井戸構造体からの熱の逃げを小さくできるので、温度センサのS/N比を大きくすることができる。

【図面の簡単な説明】

【0035】

【図1】第1実施形態に係る温度センサの概略構成を示す断面図である。

【図2】図1に示す温度センサのうち、量子井戸構造体の周辺を拡大した断面図である。

【図3】温度センサの製造工程のうち、SOI基板の準備工程を示す断面図である。

【図4】温度センサの製造工程のうち、第1電極層の形成工程、および絶縁膜のパターニング工程を示す断面図である。

【図5】温度センサの製造工程のうち、サーミスタ層の形成工程を示す断面図である。

【図6】図5において、サーミスタ層を拡大した断面図である。

【図7】温度センサの製造工程のうち、第2電極層の形成工程を示す断面図である。

【図8】温度センサの製造工程のうち、絶縁膜のパターニング工程を示す断面図である。

【図9】温度センサの製造工程のうち、配線形成工程を示す断面図である。

【図10】障壁を越えて移動するキャリアの量Qに対する、隣り合う量子井戸層間でトンネルするキャリアの量QTの割合の、量子障壁層厚依存性を示すグラフである。

【図11】TCRに対する量子井戸層厚依存性を示すグラフである。

【図12】第2実施形態に係る温度センサにおいて、障壁を越えて移動するキャリアの量Qに対する、隣り合う量子井戸層間でトンネルするキャリアの量QTの割合の、量子障壁層厚依存性を示すグラフである。

【図13】その他実施例に係る温度センサの製造工程のうち、SOI基板の準備工程を示す断面図である。

【図14】温度センサの製造工程のうち、サーミスタ層の全面エピ成長工程を示す断面図である。

【図15】温度センサの製造工程のうち、サーミスタ層および第2電極層のパターニング工程を示す断面図である。

【図16】温度センサの製造工程のうち、絶縁膜のパターニング工程を示す断面図である。

【図17】臨界膜厚に対する格子不整合率依存性を示すグラフである。

【発明を実施するための形態】

【0036】

以下、本発明の実施の形態を図面に基づいて説明する。なお、以下の各図相互において、互いに同一もしくは均等である部分に、同一符号を付与する。

【0037】

(第1実施形態)

本実施形態における温度センサは、QW構造体(Quantum Well構造体、以下、サーミスタ層と示す)の温度の変化による電流変化を検出するものであり、特に赤外線センサとして好適なものである。換言すると、温度によって抵抗値が変化する検出部であるサーミスタ層を備えた温度センサである。なお、本実施形態における温度センサは、|TCR|が大きいため、赤外線の検出に適用することによって、非常に高感度に赤外線を検出することができる。

【0038】

最初に、図1および図2を参照して、本実施形態に係る温度センサ100の構成を説明する。

【0039】

図1に示すように、本実施形態における温度センサ100は、基体10として、一面上に絶縁膜11が形成された半導体基板12を有している。本実施形態では、単結晶シリコンからなる半導体基板12の一面12a側に絶縁膜11として酸化膜(SiO2)が形成されている。半導体基板12には、絶縁膜11を底面として、裏面12b側に開口する空洞部13が形成されている。そして、絶縁膜11における空洞部13の架橋部分(底面)が薄肉部としてのメンブレン14を成している。

【0040】

また、絶縁膜11における半導体基板12と反対の面上には、第1電極層20が形成されている。第1電極層20は、一部がメンブレン14上に位置し、メンブレン14上から半導体基板12上の部分まで延設されている。なお、本実施形態における第1電極層20は、単結晶シリコンからなり、後述するサーミスタ層40を構成する半導体層よりも濃度の高いP型とされている。例えば、濃度1×1020cm−3でホウ素(B)がドープされている。なお、半導体基板12、絶縁膜11および第1電極層20の積層構造は、SOI(silicon on insulator)基板を用いることにより得ることができる。この場合、SOI基板の活性層が第1電極層20に相当する。

【0041】

さらに、図2に示すように、この第1電極層20は、絶縁膜(例えばSiO2)30によって覆われ、この絶縁膜30の所定部位に形成された開口部30a(コンタクト用の開口部)を通じて、例えばアルミニウムなどで構成された配線60に電気的に接続されている。また、第1電極層20は、絶縁膜30の別の所定部位に形成された開口部30b(検出部用の開口部)が形成されることにより、露出した表面にサーミスタ層40が形成されている。なお、サーミスタ層40における第1電極層20と接する面と反対側の表面には、第1電極層20と同一の材料および不純物のドープにより形成された第2電極層21が形成されている。特許請求の範囲において、第1電極層20、第2電極層21およびサーミスタ層40を量子井戸構造体90と称している。サーミスタ層40および第2電極層21もメンブレン14上に位置し、ひいては、量子井戸構造体90がメンブレン14上に位置している。そして、第2電極層21は、例えばアルミニウムなどで構成された配線61に電気的に接続されている。

【0042】

サーミスタ層40は、図2に示すように、複数(本実施形態では2層)の量子障壁層41a,41bと、この量子障壁層41a,41bに挟まれた量子井戸層42とを備え、一方の量子障壁層41aが、第1電極層20に接し、他方の量子障壁層41bが第2電極層21に接している。換言すると、サーミスタ層40は、量子井戸層42と量子障壁層41a,41bとが、前記量子井戸層42を少なくとも一層含んで、第1電極層20の表面に垂直な方向に交互に積層されている。なお、本発明の特徴部分であるサーミスタ層40における各層の構成材料、不純物のドーズ量および膜厚については、後ほど詳述する。

【0043】

また、絶縁膜11、第1電極層20、第2電極層21、絶縁膜30およびサーミスタ層40を覆うように絶縁膜(例えば、SiO2)50が形成され、この絶縁膜50により量子井戸構造体90が保護されている。この絶縁膜50は、第1電極層20、サーミスタ層40、第2電極層21を積層した厚みよりも厚く形成されており、絶縁膜30に形成された開口部30a,30bや第2電極層21に対応する部位に、配線60,61が配置される開口部50a,50bが形成されている。すなわち、配線60は、絶縁膜50上および絶縁膜50に形成された開口部50aに形成され、絶縁膜30の開口部30a(コンタクト用)を通じて第1電極層20に電気的に接続されている。また、配線61は、絶縁膜50上および絶縁膜50に形成された別の開口部50bに形成され、第2電極層21に電気的に接続されている。

【0044】

この絶縁膜50に形成された配線60,61の表面には保護膜(例えば、SiN)70が形成されている。この保護膜70には、配線60,61におけるパッド部60a,61aを構成するための開口部70a,70bが形成されている。温度センサ100は、この開口部70a,70bを通じてパッド部60a,61aに対してワイヤボンディングなどがなされることで、外部に備えられる処理回路(図示省略)に電気的に接続されるようになっている。また、保護膜70におけるサーミスタ層40に対応する位置には、カーボンペーストなどからなる赤外線吸収膜80が形成されている。

【0045】

そして、半導体基板12における絶縁膜11と反対の裏面側には、保護膜(例えば、SiN)71が形成されている。この保護膜71には開口部71aが形成されており、この開口部71aに連通して半導体基板12の空洞部13が形成されている。

【0046】

このような構成の温度センサ100においては、紙面上方から入射した赤外線を赤外線吸収膜80で吸収する。この赤外線の吸収によって、サーミスタ層40の温度が上昇する。したがって、2つの配線60,61に直流電圧を与えることで、サーミスタ層40を流れる電流の変化により温度を検出することができる。

【0047】

次に、図3〜図9を参照して、本実施形態に係る温度センサ100の製造方法を説明する。

【0048】

まず、図3に示すように、半導体基板12、絶縁膜11および活性層20aからなるSOI基板を準備する。なお、特許請求の範囲における基体10は、絶縁膜11と半導体基板12とを有する基板を指す。ここで、本実施形態では、活性層20aとして、ホウ素が濃度1×1020cm−3でドープされた、単結晶シリコンからなるP型の半導体層を採用する。

【0049】

次いで、図示しないが、活性層20aをパターニングすることにより第1電極層20を形成する。具体的には、少なくとも、サーミスタ層40および配線60が電気的に接続される部位を残して活性層20aをパターニングして第1電極層20を形成する。そして、図4に示すように、形成された第1電極層20を覆うように、絶縁膜30を形成する。具体的には、プラズマCVD、低圧CVDなどによって、第1電極層20の表面に絶縁膜30を形成する。その後、その絶縁膜30をパターニングして、サーミスタ層40を形成する領域に開口部30bを形成する。

【0050】

次いで、図5に示すように、開口部30bに対して、サーミスタ層40を構成する各層を選択的に成膜(選択エピ成長)する。具体的には、図6に示すように、開口部30bによって露出した第1電極層20の表面に、一方の量子障壁層41a、量子井戸層42、および他方の量子障壁層41bを、この順番で選択的にエピタキシャル成長することにより成膜する。なお、本発明の特徴部分であるサーミスタ層40における各層の構成材料、不純物のドーズ量および膜厚については、後ほど詳述する。

【0051】

次いで、図7に示すように、サーミスタ層40の表面(第1電極層20と反対の面)に第2電極層21を形成して、量子井戸構造体90が形成される。本実施形態において、第2電極層21は、単結晶シリコンからなり、ホウ素が濃度1×1020cm−3でドープされた、P型の半導体層である。すなわち、第1電極層20と同一の材料およびドーズ量に設定している。そして、図8に示すように、量子井戸構造体90と絶縁膜30とを覆うように絶縁膜50を成膜して、その絶縁膜50と絶縁膜30とをパターニングして配線60,61を形成するための開口部50a,50b,30aを形成することによって、第1電極層20と第2電極層21とを部分的に露出させる。

【0052】

次いで、図9に示すように、開口部50a,50bが形成された絶縁膜50上に、配線60,61を構成する、例えばアルミニウムを成膜し、このアルミニウム膜をパターニングすることにより、配線60,61を形成する。これによって、配線60,61は、開口部30a,50a,50bおよび絶縁膜50の表面(上面)に形成され、第1電極層20および第2電極層21と電気的に接続される。その後、絶縁膜50および絶縁膜50上に形成された配線60,61上に、保護膜70を成膜する。そして、この保護膜70をパターニングしてパッド部60a,61aを形成するための開口部70a,70bを形成する。さらに、半導体基板12の裏面を研削・研磨し、次いで、保護膜71をプラズマCVDにより形成する。

【0053】

その後、サーミスタ層40がメンブレン14上に配置されるように、半導体基板12および保護膜71に空洞部13と開口部71aとを形成する。具体的には、保護膜71をパターニングして、空洞部13に対応する部分に開口部71aを形成する。そして、保護膜71をマスクとし、SOI基板の埋め込み層である絶縁膜11をエッチングストップ層として、半導体基板12の裏面から、半導体基板12をウェットエッチングして空洞部13を形成する。つまり、このように、半導体基板12の裏面から、半導体基板12をウェットエッチングしてメンブレン14を形成する。そして、保護膜70におけるサーミスタ層40に対応する位置に、カーボンペーストなどからなる赤外線吸収膜80を、例えば印刷法により形成する。

【0054】

なお、本実施形態の温度センサ100のような量子井戸型の赤外線温度センサは、CMOSプロセスで製造すれば、容易に回路を一体形成できノイズを抑制できる。また、既存の半導体工場で製造することができ、既存の生産ラインを利用することができる利点があり有利である。

【0055】

ここで、本発明の特徴部分であるサーミスタ層40の構成材料、不純物のドーズ量および各層の膜厚に関して説明する。

【0056】

まず、量子障壁層41a,41bおよび量子井戸層42を構成する材料について説明する。量子障壁層41a,41bは、量子井戸層42を構成する材料のバンドギャップよりも大きなバンドギャップを有する材料によって構成される。量子障壁層41a,41bおよび量子井戸層42を構成する材料の、それぞれのバンドギャップと電子親和力から、量子障壁層41a,41bおよび量子井戸層42により形成される量子井戸の障壁高さVが決まる。本実施形態では、量子障壁層41a,41bとして、ガリウムリン(GaP:バンドギャップ2.26eV、電子親和力4.30eV)が用いられ、量子井戸層42として、シリコン(バンドギャップ1.11eV、電子親和力4.01eV)が用いられる。これらの材料により構成される量子井戸の障壁高さVは1.44eVであり、従来構造、例えばSi1−xGex/Si系における障壁高さ(x=1では0.84eV、現実的な構成であるx=0.4ではV≒0.34eV)に較べて、大幅に大きくすることができる。

【0057】

また、本実施形態における材料構成、すなわち、量子障壁層41a,41bとして、ガリウムリン(格子定数aGaP≒0.545nm)が用いられ、量子井戸層42として、シリコン(格子定数aSi≒0.543nm)が用いられる構成においては、格子不整合率rが0.34%となる。この格子不整合率は、Si1−xGex/Si系における格子不整合率(x=1でr≒4.2%、x=0.4でr≒1.7%)に較べて小さい。このため、図17に示される実験値および理論から、GaPからなる量子障壁層41a,41bは、Siからなる量子井戸層42の表面上に、100nm程度(実験値からの概算)、または、略20nm程度(力学的平衡理論:Matthewsらの理論、図17中Bのライン)積層することができる。なお、量子井戸層42であるSiは、第1電極層20に対する格子不整合率がr=0であるため、SiをGaP層上に任意の膜厚で積層することができる。したがって、量子障壁層41a,41bをトンネルするキャリアの数を抑制することができ、且つ、量子井戸層42における、量子効果起因のフェルミ準位EFの上昇を抑制することができる。

【0058】

このように、本実施形態では、従来構造、例えばSi1−xGex/Si系における障壁高さに較べて、高い障壁高さを実現でき、且つ、量子障壁層41a,41bと量子井戸層42とを、フェルミ準位の上昇およびトンネル効果を生じない膜厚を持って形成することができる。このため、温度センサの|TCR|の値を増加させることができ、感度を向上させることができる。

【0059】

次に、量子障壁層41a,41bおよび量子井戸層42にドープする不純物のドーズ量について説明する。本実施形態では、量子障壁層41a,41bを真性半導体(不純物をドープしない)としている。これにより、量子障壁層41a,41bと量子井戸層52との接合時に、フェルミ準位が上昇することを抑制することができ、|TCR|の値の低下を抑制することができる。また、本実施形態では、伝導帯における障壁高さが0.29eV、価電子帯における障壁高さが1.44eVであるため、量子井戸層42にホウ素を不純物としてドープしている(ドーズ量は、例えば、略1×1016cm−3)。これにより、量子井戸層42はP型の半導体層となり、サーミスタ層40はホールをキャリアとして動作する。すなわち、|TCR|の値に寄与する障壁高さVは、価電子帯における障壁高さである1.44eVとなり、キャリアに電子を用いる場合に較べて、高い障壁高さを実現することができる。したがって、|TCR|の値を上昇させることができ、温度センサの感度を向上させることができる。なお、量子井戸層42にドープされる不純物の濃度は、高いほどフェルミ準位EFが増加するため、|TCR|の値が減少してしまう。したがって、この濃度は、なるべく低濃度とすることが好ましいが、濃度のばらつきによる|TCR|の製造ばらつきを抑制するため、本実施形態のように、1×1016cm−3程度の濃度とすることが好ましい。

【0060】

次に、量子障壁層41a,41bおよび量子井戸層42の層厚について具体的に説明する。本実施形態においては、量子障壁層41a,41bの層厚を、例えば、略7nmとすることができる。量子障壁層41a,41bの層厚は、隣り合う量子井戸層42間(本実施形態では、量子井戸層42は1層のみのため、量子井戸層42と第1電極層20または第2電極層21の間)でトンネルするキャリアを抑制するように設定する。すなわち、量子障壁層41a,41bをトンネルするキャリアの量QTが、障壁を越えて移動するキャリアの量Q以下(QT/Q≦1)になるように、量子障壁層41a,41bの層厚を設定する。発明者は、コンピュータシミュレーションを用いて、QT/Qの量子障壁層厚依存性を確認している。図10はこのコンピュータシミュレーションの結果である。図10に示すように、QT/Q≦1となる量子障壁層41a,41bの層厚は7nm以上である。トンネル効果により、意図しないキャリアの移動が生じると、見かけ上の障壁高さVが低下して|TCR|が減少してしまう。このため、本実施形態のように、量子障壁層41a,41bの層厚を7nmとすれば、量子障壁層41a,41bに欠陥を生じさせることなく、トンネル効果によるキャリアの移動を抑制することができ、|TCR|の値が低下することを抑制することができる。

【0061】

また、本実施形態においては、量子井戸層42の層厚を、例えば、略4nmとすることができる。量子井戸層42の層厚は、量子効果によりキャリア(本実施形態ではホール)が縮退して、フェルミ準位EFが上昇することを抑制するように設定する。発明者は、コンピュータシミュレーションを用いて、TCRの量子井戸層厚依存性を確認している。図11はこのコンピュータシミュレーションの結果である。図11には、本実施形態における材料構成、すなわち、サーミスタ層40を構成する量子障壁層41a,41bとして、ガリウムリンが用いられる構成の他に、第2実施形態にて後述するように、量子障壁層41a,41bとして、アルミニウムリンが用いられる構成のシミュレーション結果も併せて記載している。なお、各系において、量子井戸層42にドープする不純物濃度を変更したシミュレーション結果も併せて記載されている。図11に示すように、量子井戸層42の層厚を4nmとすることにより、TCRは、層厚が4nmより小さい場合に較べて高い値で安定する。したがって、量子井戸層42の薄膜化による量子効果を抑制でき、|TCR|の値を大きくすることができる。すなわち、温度センサの感度を向上させることができる。また、|TCR|の値が安定するため、製造ばらつきに起因する量子井戸層42の層厚ばらつきに対して、|TCR|のばらつきを抑制することができる。したがって、温度センサは安定した感度を得ることができる。

【0062】

(第2実施形態)

第1実施形態では、サーミスタ層40を構成する量子障壁層41a,41bとして、ガリウムリンが用いられ、量子井戸層42として、シリコンが用いられる例を示した。これに対して、本実施形態では、サーミスタ層40を構成する量子障壁層41a,41bとして、アルミニウムリンが用いられ、量子井戸層42として、シリコンが用いられる例を示す。

【0063】

サーミスタ層40を構成する材料、膜厚以外の要素に関しては、第1実施形態と同様であるため、詳細の記載を省略する。

【0064】

まず、本実施形態における量子障壁層41a,41bおよび量子井戸層42を構成する材料について説明する。第1実施形態でも記載のように、量子障壁層41a,41bおよび量子井戸層42により形成される量子井戸の障壁高さVは、量子障壁層41a,41bおよび量子井戸層42を構成する材料の、それぞれのバンドギャップと電子親和力により決まる。本実施形態では、量子障壁層41a,41bとして、アルミニウムリン(AlP:バンドギャップ2.48eV、電子親和力3.50eV)が用いられ、量子井戸層42として、シリコン(バンドギャップ1.11eV、電子親和力4.01eV)が用いられる。これらの材料により構成される量子井戸の障壁高さVは0.86eVであり、従来構造、例えばSi1−xGex/Si系における障壁高さ(x=1では0.84eV、現実的な構成であるx=0.4ではV≒0.34eV)に較べて、大きくすることができる。

【0065】

また、本実施形態における材料構成、すなわち、量子障壁層41a,41bとして、アルミニウムリン(格子定数aAlP≒0.546nm)が用いられ、量子井戸層42として、シリコン(格子定数aSi≒0.543nm)が用いられる構成においては、格子不整合率rが0.58%となる。この格子不整合率は、Si1−xGex/Si系における格子不整合率(x=1でr≒4.2%、x=0.4でr≒1.7%)に較べて小さい。このため、図17に示される実験値および理論から、AlPからなる量子障壁層41a,41bは、Siからなる量子井戸層42の表面上に、略10nm程度(力学的平衡理論:Matthewsらの理論)積層することができる。なお、量子井戸層42であるSiは、第1電極層20に対する格子不整合率がr=0であるため、SiをAlP層上に任意の膜厚で積層することができる。したがって、量子障壁層41a,41bをトンネルするキャリアの数を抑制することができ、且つ、量子井戸層42における、量子効果起因のフェルミ準位EFの上昇を抑制することができる。

【0066】

このように、本実施形態では、従来構造、例えばSi1−xGex/Si系における障壁高さに較べて、高い障壁高さを実現でき、且つ、量子障壁層41a,41bと量子井戸層42とを、フェルミ準位の上昇およびトンネル効果を生じない膜厚を持って形成することができる。このため、温度センサの|TCR|の値を増加させることができ、感度を向上させることができる。

【0067】

量子障壁層41a,41bおよび量子井戸層42にドープする不純物のドーズ量に関しては、第1実施形態と同様に、量子障壁層41a,41bを真性半導体(不純物をドープしない)とし、量子井戸層42にホウ素を不純物としてドープして、P型としている(ドーズ量は、例えば、略1×1016cm−3)。これは、本実施形態におけるサーミスタ層40の材料構成において、伝導帯における障壁高さが0.51eV、価電子帯における障壁高さが0.86eVであり、価電子帯の障壁高さが伝導帯の障壁高さよりも高いためである。すなわち、第1実施形態と同様に、ホールをキャリアとすることにより、キャリアに電子を用いる場合に較べて、高い障壁高さを実現することができる。したがって、|TCR|の値を上昇させることができ、温度センサの感度を向上させることができる。なお、第1実施形態と同様に、量子井戸層42にドープされる不純物の濃度は、なるべく低濃度とすることが好ましいが、濃度のばらつきによる|TCR|の製造ばらつきを抑制するため、本実施形態のように、1×1016cm−3程度の濃度とすることが好ましい。

【0068】

次に、量子障壁層41a,41bおよび量子井戸層42の層厚について具体的に説明する。本実施形態においては、量子障壁層41a,41bの層厚を、例えば、略5nmとすることができる。第1実施形態と同様に、量子障壁層41a,41bの層厚は、量子障壁層41a,41bをトンネルするキャリアの量QTが、障壁を越えて移動するキャリアの量Q以下(QT/Q≦1)になるように設定する。発明者は、コンピュータシミュレーションを用いて、QT/Qの量子障壁層厚依存性を確認している。図12はこのコンピュータシミュレーションの結果である。図12に示すように、QT/Q≦1となる量子障壁層41a,41bの層厚は5nm以上である。トンネル効果により、意図しないキャリアの移動が生じると、見かけ上の障壁高さVが低下して|TCR|が減少してしまう。このため、本実施形態のように、量子障壁層41a,41bの層厚を5nmとすれば、量子障壁層41a,41bに欠陥を生じさせることなく、トンネル効果によるキャリアの移動を抑制することができ、|TCR|の値が低下することを抑制することができる。

【0069】

また、第1実施形態と同様に、本実施形態においても、量子井戸層42の層厚を、例えば、略4nmとすることができる。図11に示すように、量子井戸層42の膜厚に対するTCRは、量子井戸層42の構成材料および不純物濃度に依存するが、TCRの変化率(換言すると、膜厚に対するグラフの形状)は、量子井戸層42の構成材料および不純物濃度に殆ど依存しない。すなわち、量子効果によりフェルミ準位EFが上昇する量子井戸層42の膜厚は、量子井戸層42を構成する材料、ドーズ量に依らない。したがって、本実施形態においても、量子井戸層42の層厚を略4nmとすることにより、第1実施形態の場合と同様に作用効果を得ることができる。すなわち、量子井戸層42の薄膜化による量子効果を抑制でき、|TCR|の値を大きくすることができる。したがって、温度センサの感度を向上させることができる。また、|TCR|の値が安定するため、製造ばらつきに起因する量子井戸層42の層厚ばらつきに対して、|TCR|のばらつきを抑制することができる。

【0070】

(その他の実施形態)

以上、本発明の好ましい実施形態について説明したが、本発明は上述した実施形態になんら制限されることなく、本発明の主旨を逸脱しない範囲において、種々変形して実施することが可能である。

【0071】

上記した各実施形態においては、第1電極層20、第2電極層21、および量子井戸層42にシリコンを用い、量子障壁層41a,41bにガリウムリンあるいはアルミニウムリンを用いた例を示した。しかしながら、上記例に限定されるものではない。量子井戸層42と、前記量子障壁層41a,41bとは、これらの層が積層されることにより形成される量子井戸の障壁高さが0.34eVより大きい材料からなり、量子井戸層42は、第1電極層20の結晶格子に対する格子不整合率rが4%以下の材料から構成されており、且つ、量子障壁層41a,41bは、第1電極層20の結晶格子に対する格子不整合率rが0.9%以下の材料から構成されていればよい。

【0072】

また、上記した各実施形態では、サーミスタ層40は、量子障壁層41a,41bに挟まれた一層の量子井戸層42からなる単層のQW構造を例として採用しているが、本発明は、これに限定されるものではない。例えば、量子井戸層と量子障壁層とが、複数の量子井戸層を含んで、第1電極層20の表面に垂直な方向に交互に積層されてなる、MQW(Multi Quantum Well)構造を採用するようにしてもよい。

【0073】

また、上記した各実施形態では、量子障壁層41a,41bが真性半導体からなる構成を例に示したが、本発明は、これに限定されるものではない。例えば、上記した各実施形態において、量子障壁層41a,41bに、不純物としてホウ素をドープして、量子井戸層42よりも不純物濃度の薄いP型としてもよい。

【0074】

また、上記した各実施形態では、量子井戸層42の不純物としてホウ素をドープしてP型とする例を示した。しかしながら、量子井戸層42の導電型は、P型に限定されるものではない。例えば、量子障壁層41a,41bおよび量子井戸層42を構成する材料を選定するにあたって、伝導帯の障壁高さが価電子帯の障壁高さよりも大きい構成とした場合には、量子井戸層42の導電型をN型にすることが好ましい。これにより、量子井戸層42が真性半導体である場合に較べて、フェルミ準位が伝導帯に寄るため、キャリアは電子となり、|TCR|の値に寄与するバンドは伝導帯となる。したがって、量子井戸層42をP型とする場合に較べて、|TCR|の値に寄与する障壁高さを大きくすることができ、温度センサの感度を向上させることができる。

【0075】

また、上記した各実施形態では、量子井戸層42の層厚を4nmとする例を示したが、量子井戸層42の層厚は、0.3nm以上であれば採用することができる。図11に示すように、量子井戸層の層厚が0.3nmより小さくなると、|TCR|の値は、層厚が4nm以上の場合に較べて低い値で推移する。これは、量子効果によるフェルミ準位EFの上昇が支配的になるためである。換言すれば、量子井戸層の層厚を0.3nm以上に設定することにより、フェルミ準位EFの上昇を抑制することができ、|TCR|の値の減少を抑制することができる。

【0076】

また、上記した各実施形態では、量子井戸構造体90が形成される基体10として、SOI基板を構成する半導体基板12、絶縁膜11および活性層20aのうち、単結晶シリコンからなる半導体基板12と絶縁膜11とで構成された基板を用いる例を示したが、本発明は、これに限定されるものではない。量子井戸構造体90が形成される基体10は、量子井戸構造体90との接触部分が少なくとも絶縁性の基板であればよい。例えば、単結晶以外のシリコン(Poly−Siや非晶質シリコン)および、その表面上に形成された絶縁膜を含む基板を基体10として用いても良いし、ガラス基板を基体10として用いても良い。

【0077】

また、上記した各実施形態では、温度センサ100の製造方法として、サーミスタ層40を選択エピ成長させて形成する例を示した。しかしながら、温度センサ100の製造方法は、上記例に限定されるものではない。例えば、図13〜図16に示す方法で製造することができる。以下、図13〜図16を用いて、温度センサ100の製造方法の一例を説明する。

【0078】

まず、図13に示すように、上記した各実施形態と同様、SOI基板を準備する。次いで、図14に示すように、サーミスタ層40を構成する量子障壁層41a,量子井戸層42、量子障壁層41bおよび第2電極層21を、この順番でエピタキシャル成長する(全面エピ成長)。各層の構成材料は、上記した実施形態と同一の組み合わせを用いることができる。そして、図15に示すように、全面エピ成長により成膜した量子障壁層41a,41b、量子井戸層42および第2電極層21をパターニングする。その後、図16に示すように、活性層20aをパターニングして第1電極層20を形成し、絶縁膜11、第1電極層20、サーミスタ層40および第2電極層21を覆うように絶縁膜50を形成する。そして、その絶縁膜50をパターニングして配線60,61を形成するための開口部50a,50bを形成することによって、第1電極層20と第2電極層21とを部分的に露出させる。本実施形態における図16の状態は、上記した各実施形態における図8に相当する。配線60,61を形成する工程以降の工程は、各実施形態と同一であるため、その記載を省略する。この全面エピ成長による方法によっても、本発明に係る温度センサ100を製造することができる。

【0079】

なお、上記した各実施形態においては、サーミスタ層40がメンブレン14上に配置される例を示したが、サーミスタ層40は必ずしもメンブレン14上に配置される必要はない。ただし、サーミスタ層40をメンブレン14上に配置することにより、熱コンダクタンスを小さくすることができるため、感度を向上させることができる。すなわち、サーミスタ層40からの熱の逃げを小さくできるので、温度センサのS/N比を大きくすることができる。

【符号の説明】

【0080】

10・・・基体

11,30,50・・・絶縁膜

12・・・半導体基板

14・・・メンブレン

20・・・第1電極層

21・・・第2電極層

40・・・サーミスタ層

60,61・・・配線

70,71・・・保護膜

80・・・赤外線吸収膜

90・・・量子井戸構造体

100・・・温度センサ

【特許請求の範囲】

【請求項1】

基体と、

該基体上に形成された量子井戸構造体と、を備え、

前記量子井戸構造体は、前記基体に隣接して形成された第1導電型の第1電極層と、該第1電極層上に形成されたサーミスタ層と、該サーミスタ層上に形成された第1導電型の第2電極層と、を有する積層構造をなし、

前記サーミスタ層は、量子井戸層を少なくとも一層と、量子障壁層を複数層有するとともに、前記第1電極層、前記サーミスタ層、前記第2電極層の積層方向に沿って前記量子井戸層と前記量子障壁層とが交互に配置されてなる、量子井戸型の温度センサであって、

前記量子井戸層と、前記量子障壁層とは、これらの層が積層されることにより形成される量子井戸の障壁高さが0.34eVより大きい材料からなり、

前記量子井戸層は、前記第1電極層の結晶格子に対する格子不整合率が4%以下の材料からなり、

前記量子障壁層は、前記第1電極層の結晶格子に対する格子不整合率が0.9%以下の材料からなることを特徴とする温度センサ。

【請求項2】

前記第1電極層、前記第2電極層、および前記量子井戸層はシリコンからなり、前記量子障壁層はガリウムリンからなることを特徴とする請求項1に記載の温度センサ。

【請求項3】

前記量子障壁層は、層厚が7nm以上であることを特徴とする請求項2に記載の温度センサ。

【請求項4】

前記第1電極層、前記第2電極層、および前記量子井戸層はシリコンからなり、前記量子障壁層はアルミニウムリンからなることを特徴とする請求項1に記載の温度センサ。

【請求項5】

前記量子障壁層は、層厚が5nm以上であることを特徴とする請求項4に記載の温度センサ。

【請求項6】

前記量子障壁層は真性半導体からなり、前記量子井戸層は不純物がドープされたP型の半導体からなることを特徴とする請求項2〜5のいずれか1項に記載の温度センサ。

【請求項7】

前記量子井戸層は、層厚が4nm以上であることを特徴とする請求項1〜6のいずれか1項に記載の温度センサ。

【請求項8】

前記量子井戸構造体は、前記基体に形成されたメンブレン上に形成されることを特徴とする請求項1〜7のいずれか1項に記載の温度センサ。

【請求項1】

基体と、

該基体上に形成された量子井戸構造体と、を備え、

前記量子井戸構造体は、前記基体に隣接して形成された第1導電型の第1電極層と、該第1電極層上に形成されたサーミスタ層と、該サーミスタ層上に形成された第1導電型の第2電極層と、を有する積層構造をなし、

前記サーミスタ層は、量子井戸層を少なくとも一層と、量子障壁層を複数層有するとともに、前記第1電極層、前記サーミスタ層、前記第2電極層の積層方向に沿って前記量子井戸層と前記量子障壁層とが交互に配置されてなる、量子井戸型の温度センサであって、

前記量子井戸層と、前記量子障壁層とは、これらの層が積層されることにより形成される量子井戸の障壁高さが0.34eVより大きい材料からなり、

前記量子井戸層は、前記第1電極層の結晶格子に対する格子不整合率が4%以下の材料からなり、

前記量子障壁層は、前記第1電極層の結晶格子に対する格子不整合率が0.9%以下の材料からなることを特徴とする温度センサ。

【請求項2】

前記第1電極層、前記第2電極層、および前記量子井戸層はシリコンからなり、前記量子障壁層はガリウムリンからなることを特徴とする請求項1に記載の温度センサ。

【請求項3】

前記量子障壁層は、層厚が7nm以上であることを特徴とする請求項2に記載の温度センサ。

【請求項4】

前記第1電極層、前記第2電極層、および前記量子井戸層はシリコンからなり、前記量子障壁層はアルミニウムリンからなることを特徴とする請求項1に記載の温度センサ。

【請求項5】

前記量子障壁層は、層厚が5nm以上であることを特徴とする請求項4に記載の温度センサ。

【請求項6】

前記量子障壁層は真性半導体からなり、前記量子井戸層は不純物がドープされたP型の半導体からなることを特徴とする請求項2〜5のいずれか1項に記載の温度センサ。

【請求項7】

前記量子井戸層は、層厚が4nm以上であることを特徴とする請求項1〜6のいずれか1項に記載の温度センサ。

【請求項8】

前記量子井戸構造体は、前記基体に形成されたメンブレン上に形成されることを特徴とする請求項1〜7のいずれか1項に記載の温度センサ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2013−96780(P2013−96780A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−238445(P2011−238445)

【出願日】平成23年10月31日(2011.10.31)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年10月31日(2011.10.31)

【出願人】(000004260)株式会社デンソー (27,639)

【Fターム(参考)】

[ Back to top ]