温度補償型水晶発振器制御用IC

【課題】端子を共用化するとともに、誤作動が起こる可能性を低減することができる温度補償型水晶発振器制御用ICを提供する。

【解決手段】温度補償型水晶発振器は、モードセレクタ回路100、制御ロジック回路シリアル・インターフェイス200、PROM回路300、発振制御回路400および発振回路500を有し、端子としては電源端子(VCC/CLK)11、入力端子(VC/DATA/PE)12、出力端子(OUT)13および接地端子(GND)14を備える。モードセレクタ回路100は、電源端子11から電源電圧にクロック信号が重畳された第1の信号が入力され、入力端子12から所定のパターンを有する第2の信号が入力された場合に、エミュレーションモードに切り替える。

【解決手段】温度補償型水晶発振器は、モードセレクタ回路100、制御ロジック回路シリアル・インターフェイス200、PROM回路300、発振制御回路400および発振回路500を有し、端子としては電源端子(VCC/CLK)11、入力端子(VC/DATA/PE)12、出力端子(OUT)13および接地端子(GND)14を備える。モードセレクタ回路100は、電源端子11から電源電圧にクロック信号が重畳された第1の信号が入力され、入力端子12から所定のパターンを有する第2の信号が入力された場合に、エミュレーションモードに切り替える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、温度補償型水晶発振器(以下「TCXO」という)制御用ICに関し、特に、水晶発振器及び制御用ICの端子の共用化に関するものである。

【背景技術】

【0002】

現在の水晶発振器は、小型化が急速に進んでいる。また水晶を制御する半導体も小型化が急速に進んでいる。水晶発振器には通常、電源端子(VCC1)と接地端子(GND)と周波数出力端子(OUT)と周波数制御端子(VC)とが備わっている(周波数制御機能がない場合もある)。また、水晶発振器には、水晶振動子の接続端子(XT1)、(XT2)も必要である。

【0003】

また、高精度な発振を行う水晶発振器では、内部にPROM回路を備えており、PROM回路を用いて温度補償回路などを制御している(TCXO、VCXOなど)。

【0004】

TCXOは、水晶の周波数の温度特性をキャンセルする制御を行うことにより、高精度な発振を行う。水晶の周波数のバラツキは個々に異なるため、TCXO1台毎に調整を行い、制御用ICに内蔵されているPROM回路に調整データを書き込んで温度補償を行っている。ここで、1タイムPROMを使用したTCXOの周波数調整について説明する。

【0005】

現状のTCXOの周波数調整には、3種類の動作モードが必要とされる。通常使用するモードでの使用に先立ち、PROM回路に書き込むデータ(書き込みビット)を決定するために、データを入力し周波数データを取得し計算するモード(エミュレーションモード以下EM)が有る。また、エミュレーションモードEMで決定したデータをPROM回路に書き込むモード(ライトモード以下WM)が有る。そして、通常使用するモード(リードモード以下RM)において、PROM回路に書き込まれたデータを読み出して周波数を制御する。これら3種類のモードを切り替えることにより、TCXOの周波数調整が行われる。

【0006】

このように高精度な発振を行う水晶発振器は、さらに、各モードでの制御を行う為に、専用の制御端子を必要とする。上記PROM回路の制御を行う為には、例えば、CLK端子、DATA端子、PROM電源端子が必要である。しかしながら、水晶発振器を一層小型化するためには、これ等端子の共用化を行う必要がある。

【0007】

端子共用化の例としては、特許文献1に記載の技術があり、周波数制御端子とDATA端子、発振出力端子とCLK端子の共用化が提案されている。

【0008】

また、本出願人は、図11に示すように、電源端子とCLK端子を共用した端子(Vcc,CLK)56、およびDATA端子とVC端子を共用した端子(DATA/VC)52を有するTCXOモジュールを既に提案している(特許文献2参照)。なお、図11に示すTCXOモジュールは、さらに水晶振動子の接続端子XT51,XTB55、PROM電圧端子53、書込みPE端子57、接地端子(GND)54および発振出力端子(OUT)58の8個の端子を備えている。

【0009】

図23は、上記特許文献2に記載された温度補償型水晶発振器の概略構成を示す図である。図23において、電源/CLK端子11Aは、モジュールの電源端子であり、この端子によって2.8Vの単一電圧を供給する。また、PROM回路にクロック信号を送るCLK端子の機能を有する。電圧制御/DATA端子12Aは、周波数を電圧制御する端子であり、PROM回路にデータを与える機能を有する。

【0010】

このように、この温度補償型水晶発振器は、PROM回路にクロック信号を与えるCLK端子と電源端子とを共有しており、電圧制御回路に電圧を与える電圧制御端子とPROM回路にデータを与えるDATA端子とを共用化している。

【0011】

図24は、この温度補償型水晶発振器における調整データ入力波形を示す図である。調整時には電源端子5Aを2.3Vに設定した後、電源端子11Aを介して制御用ICのレジスタにクロック信号を与え、端子12Aからデータ信号を与える。信号を与えた後に制御用ICを通常使用する電源電圧2.3〜3.3Vに固定する。また、端子12Aには、電圧制御範囲の電圧0V〜3.3Vを与えて発振周波数の調整を行う。

【0012】

一方、メモリーをEEPROMで構成した場合、書き換えが可能なためチップ面積に余裕が無い場合、エミュレーションモードを持たないこともある。その場合、周波数データを取るために、わざわざ書き込みを行い、その都度データを取る。その後そのデータに基づき最適ビットを算出する。以降の動作は、どのようなPROMでも同じである。

【0013】

この場合、基本の調整の方法は変らないが、エミュレーション時のデータの取り方の詳細は以下の動きをする。実際にはエミュレーションのデータを入力する。この時点では周波数は変化しない。次に書き込み動作を行う。これによりデータが出力に反映される。この作業を繰り返し行いデータを取っていく。

【0014】

【特許文献1】米国特許第5724009号明細書

【特許文献2】特開2003−188646号公報

【発明の開示】

【発明が解決しようとする課題】

【0015】

しかし、上記特許文献1に記載された手法では、アナログ信号とディジタル信号とで端子を共用するため、水晶発振器の調整を行うためには、非常に複雑な切り替えが必要となる。

【0016】

例えば、OUT端子とCLK端子を共用化した場合の切り替えにおいて、CLK入力時は、パルス発生電源を接続するのに対し、定常状態では、周波数をOUT端子より読み込むための周波数カウンタが必要となるため、その接続の切り替えが複雑である。

【0017】

一方、水晶発振器を調整するためにPROM回路を使用する場合、エミュレーションモードEMの設定をするためにシリアルデータを入力する必要があり、CLK端子とDATA端子を必要とする。また、リードモードRM、エミュレーションモードEMおよびライトモードWMのモード切り替えを行うための端子が必要になる。以下に具体例を示す。

【0018】

図12は、従来のTCXO制御用ICを示す。従来のTCXO制御用ICは、電源端子2(VCC2:モードセレクト用電源)62を備え、その電源端子2(62)でモード切り替えを行っていた。例えば、電源端子2(62)がオープンでリードモードRM、電源端子2(62)が2.3V時にエミュレーションモードEM、電源端子2(62)が3.5V時にライトモードWMというように使い分けを行っている。

【0019】

このように、従来のTCXO制御用ICは、リードモードRM、エミュレーションモードEMおよびライトモードWMを切り替える場合、電源端子2(62)から別電源(PROM電源VCC2:モードセレクト用電源)にてバイアスを与えてデータ入力を行っていた。しかし、最近の小型化の要求に応えるためには、ICのPAD(端子)あるいはTCXOモジュールの端子を一層削減する必要がある。

【0020】

本発明は、上記従来の事情に鑑みてなされたものであって、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる温度補償型水晶発振器を提供することを目的としている。

【課題を解決するための手段】

【0021】

本発明に係る温度補償型水晶発振器制御用ICは、電源電圧およびクロック信号が供給される電源端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記電源電圧に前記クロック信号が重畳されて入力される第1の信号と、所定の基準電圧との比較結果をクロック信号として出力する内部クロック発生回路を備える。

【0022】

上記構成によれば、電源電圧にクロック信号が重畳されて入力される第1の信号と、所定の基準電圧との比較結果をクロック信号として出力するので、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。

【0023】

本発明に係る温度補償型水晶発振器制御用ICは、電源電圧およびクロック信号が供給される電源端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器であって、前記電源端子から前記電源電圧に前記クロック信号が重畳された第1の信号が入力され、前記入力端子から所定のパターンを有する第2の信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える。

【0024】

上記構成によれば、端子を共用化するために電源端子から電源電圧にクロック信号が重畳された第1の信号を入力するとともに、入力端子から所定のパターンを有する第2の信号が入力された場合にエミュレーションモードに切り替えるので、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。また、端子共用化による誤作動が起こる可能性を低減することができる。

【0025】

また、本発明に係る温度補償型水晶発振器制御用ICにおいて、前記第1の信号のレベルは通常動作時の電圧より高い電圧である。

【0026】

上記構成によれば、温度補償型水晶発振器制御用ICとして実際に使用する電圧2.3V−3.3Vより高い電圧範囲(例えば、3.5V−5.5V)となり、モード設定を安定して行うことができる。

【0027】

また、本発明に係る温度補償型水晶発振器制御用ICは、前記第1のモードセレクタ回路が、前記第1の信号と所定の基準電圧との比較結果をパルス信号として出力するコンパレータと、前記コンパレータにより出力されたパルス信号に応じて、前記第2の信号をシフトする所定段の第1のフリップフロップ回路と、前記第1のフリップフロップ回路の出力信号に応じて、前記電源電圧を制御するトランジスタと、を有するものである。

【0028】

上記構成によれば、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。また、端子共用化による誤作動が起こる可能性を低減することができる。

【0029】

また、本発明に係る温度補償型水晶発振器制御用ICは、前記第1のフリップフロップ回路の各段の出力が前記所定のパターンに一致した場合に、前記トランジスタを制御する論理回路を備える。

【0030】

上記構成によれば、第1のフリップフロップ回路の各段の出力が所定のパターンに一致した場合にトランジスタを制御するので、端子の共用化に伴う誤動作の可能性を低減することができる。

【0031】

また、本発明に係る温度補償型水晶発振器制御用ICは、前記エミュレーションモードあるいはライトモードにおいて、前記第1のモードセレクタ回路、又は信号から前記電源電圧が制御されることにより動作し、前記PROM回路に書き込むデータを設定する制御ロジック回路を備える。

【0032】

上記構成によれば、制御ロジック回路は、第1のモードセレクタ回路から電源電圧が供給された場合に動作するので、ノイズ等によりエミュレーションモードEMに入り、PROM回路に誤ったデータが書き込まれることを防止することができる。

【0033】

また、本発明に係る温度補償型水晶発振器制御用ICは、前記制御ロジック回路が、前記クロック信号に応じて、前記第2の信号をシフトする所定段の第2のフリップフロップ回路を備える。

【0034】

上記構成によれば、第2のフリップフロップ回路は、第1のモードセレクタ回路から電源電圧が供給された場合に第2の信号をシフトするので、ノイズ等によりエミュレーションモードEMに入り、PROM回路に誤ったデータが書き込まれることを防止することができる。

【0035】

また、本発明に係る温度補償型水晶発振器制御用ICは、前記PROM回路が、前記入力端子に直列に接続され、書き込みデータ信号の振幅を制限する直列接続された複数のダイオードを備える。

【0036】

上記構成によれば、PROM回路は、書き込みデータ信号の振幅を制限する直列接続された複数のダイオードを備えるので、PE端子を入力端子と電気的に分離し、PE端子と入力端子を共用することができる。

【0037】

また、本発明に係る温度補償型水晶発振器制御用ICは、電源電圧およびクロック信号が供給される電源端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記電源端子から前記電源電圧に前記クロック信号が重畳された信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替えるモードセレクタ回路を備える。

【0038】

上記構成によれば、電源端子から電源電圧にクロック信号が重畳された信号が入力された場合にエミュレーションモードに切り替えるモードセレクタ回路を備えるので、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。

【0039】

また、本発明に係る温度補償型水晶発振器制御用ICは、前記第1の信号が供給される第1の端子、および前記第2の信号が供給される第2の端子を含む6個の端子を有する。また、本発明に係る温度補償型水晶発振器制御用ICは、前記電源端子から前記電源電圧に前記クロック信号が重畳された信号が供給される端子を含む6個の端子を有する。

【0040】

上記構成によれば、温度補償型水晶発振器の端子を従来の8パッドから6パッドに減らすことができ、TCXOモジュールとICを接続するパターン配線を減らすことが可能になるため、TCXOモジュールの小型化を実現することができる。

【0041】

また、本発明に係る温度補償型水晶発振器制御用ICは、発振器出力およびクロック信号が供給される出力端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記出力端子から前記クロック信号が重畳された第1の信号が入力され、前記入力端子から所定のパターンを有する第2の信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える。

【0042】

上記構成によれば、端子を共用化するために電源端子から電源電圧にクロック信号が重畳された第1の信号を入力するとともに、入力端子から所定のパターンを有する第2の信号が入力された場合にエミュレーションモードに切り替えるので、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。また、端子共用化による誤作動が起こる可能性を低減することができる。

【0043】

また、本発明に係る温度補償型水晶発振器制御用ICは、発振器出力およびクロック信号が供給される出力端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記出力端子から前記クロック信号が重畳された信号が入力された場合に、前記エミュレーションモード、あるいはライトモードに切り替えるモードセレクタ回路を備える。

【0044】

上記構成によれば、電源端子から電源電圧にクロック信号が重畳された信号が入力された場合にエミュレーションモードに切り替えるモードセレクタ回路を備えるので、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。

【0045】

また、本発明に係る温度補償型水晶発振器制御用ICは、発振器の制御信号が入力される入力端子およびクロック信号が供給される前記入力端子と、発振器の出力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記入力端子から前記クロック信号が重畳された第1の信号が入力され、かつ、前記出力端子から所定のパターンを有する第2の信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える。

【0046】

上記構成によれば、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。

【0047】

また、本発明に係る温度補償型水晶発振器制御用ICは、発振器の制御信号が入力される入力端子およびクロック信号が供給される前記入力端子と、発振器の出力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記入力端子から前記クロック信号が重畳された信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える。

【0048】

上記構成によれば、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。

【0049】

また、本発明に係る温度補償型水晶発振器制御用ICは、電源電圧およびクロック信号が供給される電源端子と、発振器の出力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記電源端子から前記クロック信号が重畳された第1の信号が入力され、かつ、前記出力端子から所定のパターンを有する第2の信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える。

【0050】

上記構成によれば、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。

【0051】

また、本発明に係る温度補償型水晶発振器制御用ICは、電源電圧およびクロック信号が供給される電源端子と、発振器の出力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記電源端子から前記クロック信号が重畳された信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える。

【0052】

上記構成によれば、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。

【0053】

また、本発明に係る温度補償型水晶発振器制御用ICは、水晶振動子が接続される水晶端子およびクロック信号が供給される水晶端子と、発振器の入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記水晶端子から前記クロック信号が重畳された第1の信号が入力され、かつ、前記入力端子から所定のパターンを有する第2の信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える。

【0054】

上記構成によれば、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。

【0055】

さらに、本発明に係る温度補償型水晶発振器制御用ICは、水晶振動子が接続される水晶端子およびクロック信号が供給される水晶端子と、発振器の入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記水晶端子から前記クロック信号が重畳された信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える。

【0056】

上記構成によれば、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。

【発明の効果】

【0057】

本発明によれば、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。これにより、TCXOモジュールとICを接続するパターン配線を減らすことが可能になるため、TCXOモジュールの小型化を実現する事ができる。

【発明を実施するための最良の形態】

【0058】

以下、温度補償型水晶発振器(TCXO)の制御用ICが有するDATA端子、CLK端子、制御回路の電源端子の共用化を、効率よく、かつ調整時の切り替えを要することなく行う手法について、図面を参照しながら説明する。

【0059】

(第1の実施形態)

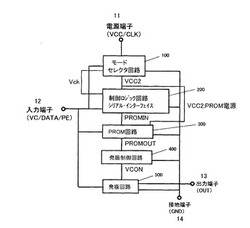

図1は、本実施形態のTCXO制御用ICのブロック図を示す。本実施形態のTCXO制御用ICは、モードセレクタ回路100、制御ロジック回路シリアル・インターフェイス200、PROM回路300、発振制御回路400および発振回路500を有し、端子としては電源端子(VCC/CLK)11、入力端子(VC/DATA/PE)12、出力端子(OUT)13および接地端子(GND)14を備える。

【0060】

電源端子(VCC/CLK)11は、モードセレクタ回路100に接続される。入力端子(VC/DATA/PE)12は、モードセレクタ回路100と制御ロジック回路200、発振回路500に接続される。出力端子(OUT)13は、発振回路500に接続され、出力端子(OUT)13から、数十MHzの発振出力がなされる。

【0061】

図1に示す本実施形態のTCXO制御用ICは、図12に示す従来のTCXO制御用ICのブロック図に、モードセレクタ回路100が追加されている。

【0062】

図2は、モードセレクタ回路100のブロック図である。モードセレクタ回路100は、ICの内部基準電圧VREFを基準とするコンパレータ120を備え、電源端子(VCC/CLK)11からは、コンパレータ120の入力として、例えば、3.5V−5.5VのCLK信号を与える。CLK信号を抵抗180と抵抗181で分圧してコンパレータ120の入力を調整する。すなわち、コンパレータ120は、電源端子(VCC/CLK)11から入力された信号の電圧(CLK信号を抵抗180と抵抗181で分圧したもの)と、ICの内部基準電圧VREFとの比較結果をパルス信号として出力する。これにより、F/F回路110の入力VCKとして、0V−VCCの信号を得る事が出来る。

【0063】

一方、入力端子(VC/DATA/PE)12からは、0V−5.5Vのデータを入力する。このデータは、電源端子(VCC/CLK)11からのCLK信号に重畳されて、F/F回路110〜112に送られる。

【0064】

F/F回路110〜112に特定の信号が入った場合、トランジスタM1(150)がONして、電源電圧VCC2が立ち上がり、制御ロジック回路シリアル・インターフェイス200に電源が供給されて、エミュレーションモードEMに切り替わる。

【0065】

本実施形態によれば、図12に示した従来の電源端子1(VCC1/CLK)61および電源端子2(VC2:モードセレクト用電源)62を、図1に示す電源端子(VCC/CLK)11として共用化し、電源端子(VCC/CLK)11と入力端子(VC/DATA/PE)12の信号によってモード切り替えを行う。そのため、通常TCXOとして使用しているときに、ノイズ等により、誤ってエミュレーションモードEMに切り替わってしまうおそれがある。そこで、本実施形態では、入力端子(VC/DATA/PE)12に、特定の信号パターンが入力されたときにのみモード切替を行うことにより、ICの誤動作を防ぐことができる。

【0066】

このように本実施形態では、モードセレクタ回路100を備えて、電源端子(VCC/CLK)11と入力端子(VC/DATA/PE)12より特定の信号が供給された場合にモードが切り替るように制御する。

【0067】

このとき、電源端子(VCC/CLK)11の入力のLOWレベルは、制御ロジックおよびシリアルコントロールの信号が動作可能な電圧に設定する。ここで電源端子(VCC/CLK)11のLOWレベルを0Vにしてしまうと、シリアルコントロールが当然効かなくなる。したがって、例えば、電圧3.5V−5.5Vの入力を電源端子(VCC/CLK)11へ入れてモード設定を行う。

【0068】

このため、電源端子(VCC/CLK)11下にコンパレータ120を設け、基準電圧(VREF)を反転入力、電源電圧VCCを抵抗180と抵抗181で分割した電圧を非反転入力とする。

【0069】

コンパレータ120のスレッシュレベル(VREF)を3Vに設定し、電源端子(VCC/CLK)11の抵抗比を調整し電源電圧VCCが4.5Vで切り替る設定にする。実際には電源電圧VCCを3.5V−5.5Vで印加すると、安定した0V−VCCのCLKパルスをインバータ121の出力であるVCK点で作る事が出来る。

【0070】

モードセレクタ回路100は、電源端子(VCC/CLK)11からCLK信号が入力され、入力端子(VC/DATA/PE)12からDATA信号が入力されており、ある特定のデータが入力された場合に、トランジスタM1(150)がON状態になることで電源電圧VCC2が電源電圧VCCと同電位になり、制御ロジック回路200の電源をONにすることができる。

【0071】

モード設定が完了した状態でトランジスタM1(150)がON状態になり電源電圧VCC2の電源が入り、制御ロジック回路シリアル・インターフェイス200を制御することが可能になる。これにより、エミュレーションモードEMに切り替わる。

【0072】

モードセレクタ回路100には、ある特定のビットを入力しないとエミュレーション動作しないように何段かのF/F回路110〜112を具備しておく事により、実使用時に何らかの入力が電源端子(VCC/CLK)11と入力端子(VC/DATA/PE)12に入ってしまったときに誤ってエミュレーションモードEMに入らないように設定をしておく。F/F回路110〜112の段数を増やすと、ICの誤動作防止に一層効果的である。

【0073】

エミュレーションモードEMに切り替わるために特定ビットに信号を入力した後は、3.5V〜5.5Vの信号で水晶の周波数を調整するための周波数データをとる事が出来る。

【0074】

なお、ノイズがない場合はモードセレクタ回路100のF/F回路110〜112等を省略することができる。図13は、図1に示したモードセレクタ回路100を内部クロック発生回路101に置き換えたTCXO制御用ICのブロック図を示す。図14は、内部クロック発生回路101のブロック図である。

【0075】

内部クロック発生回路101は、ICの内部基準電圧VREFを基準とするコンパレータ120を備え、電源端子(VCC/CLK)11からは、コンパレータ120の入力として、例えば、3.5V−5.5VのCLK信号を与える。CLK信号を抵抗180と抵抗181で分圧してコンパレータ120の入力を調整する。すなわち、コンパレータ120は、電源端子(VCC/CLK)11から入力された信号の電圧(CLK信号を抵抗180と抵抗181で分圧したもの)と、ICの内部基準電圧VREFとの比較結果をクロック信号VCKとして出力する。これにより、制御ロジック回路200へ供給する0V−VCCのクロック信号VCKを得る事が出来る。

【0076】

図3は、制御ロジック回路シリアル・インターフェイス200のブロック図である。モードセレクタ回路100において電源電圧VCC2が立ち上がると、制御ロジック回路シリアル・インターフェイス200に電源が供給されエミュレーションモードEMの動作が可能な状態になる。

【0077】

制御ロジック回路シリアル・インターフェイス200の入力クロックに信号VCKを入力し、DATAは入力端子(VC/DATA/PE)12より入力する。これ等のデータを複数のPROMビット分データを送り、PROM回路300にデータを送る。

【0078】

これらは水晶振動子の周波数の温度特性や発振器出力を調整するためのビット数分必要であり、通常は40〜60ビット程度である。

【0079】

図4はPROM回路300を示す。制御ロジック回路シリアル・インターフェイス200のF/F回路201からの出力251をPROM回路300に入力する。F/F回路201の信号によりPROMOUTが切換わり発振制御回路400に信号を入力し、周波数を制御する。ここで、所望の周波数に調整し、PROM回路300にデータを入力端子(VC/DATA/PE)12より書き込む。

【0080】

PROM回路300の書き込み端子(PE端子)が存在する場合は入力端子(VC端子)との共用を行う。本実施形態においては、図4に示すように、PE端子(入力端子12)にダイオードを複数個直列接続(D350×n個)して、PROM回路機能側と他の機能側とをDC的に分離することにより、PE端子とVC端子との共用化を実現する。PROM回路機能側のPE端子から書き込むPROM書き込み動作と他の機能側のVC端子から周波数をVCOとしての動作が両立しなければ、共用化は出来ない。VC端子の一般的な使用として1MΩ以上のインピーダンスが必要で、VCOとして3V付近まで動作させる必要がある。単純に従来のPE端子をVC端子を接続したのでは、VC端子のインピーダンスはD350のダイオード(n=1)でクランプされVC端子の電圧を上げることが出来ない。そこで、D350のダイオードをn個直列に接続することにより、VC端子はn×0.7Vの動作レンジを得ることが出来るようになる。D350のダイオードを積み上げることは、書き込みする上では書き込み時のPE端子の耐圧が十分あれば問題にならない。例えば、5VまでVC端子を動作させたい場合はn(8個)×0.7V=5.6Vなので、8個のダイオードを入れることによりPADの共用化が実現できる。

【0081】

リードモードRMにおける本PROM回路300は、定電流I380からなるカレントミラー電流で動作する。I390からなるカレントミラーはVCC2が立ち上がっていない状態のため電流はゼロである。Q350の電流によりQ304をONさせてZ300のアノードをLOWに固定する。Q351の電流がD300を介してZ300に流れるか、D310を介してQ305に流れるかによりPROMOUTの状態が変わる。すなわち、Z300の状態でPROMOUTが決定される事になる。以下それぞれの状態を説明する。

【0082】

例えばZ300のツェナーダイオードをPE端子より電流を印加してショート状態にした場合は、Q351からの電流はZ300側に流れQ310/305/306に電流は流れない。更にQ352の電流によりQ307がON状態になりPROMOUTはLOWになる。

【0083】

また、Z300がカソードから見てハイインピーダンスの場合はQ351の電流はQ310/305/306に流れ込みQ352の電流を全て引き込み、Q307はOFFしてPROMOUTはHIGHになる。

【0084】

エミュレーションモードEMでは、VCC/CLK端子とVCC2に電圧が印加されI380/I390に電流が流れている状態になり、VB1とVB2ラインが定電流源のベースラインとなる。この状態ではPROMOUTはPROMINの251の信号で制御される。

【0085】

信号251がHIGHの場合、Q303がONすることによりQ304がOFF状態になるので、Q351の電流はD310の方向に流れる。Q351の電流はQ305とQ306のカレントミラーで2倍になる。またQ352の電流はQ351と同じ電流であるため、Q307のベースはLOWとなりQ307はOFFになりPROMOUTはHIGHになる。251がLOWの場合、Q309がOFF状態になり、Q382の電流はQ308のベースに流れ込む。Q308がON状態になりPROMOUTはLOW状態になる。このように、信号251から信号256にデータを入れることによりエミュレーション動作を行うことが出来る。

【0086】

ライトモードWMでは、VCC/CLK端子とVCC2に電圧が印加されI380/I390に電流が流れている状態で、VB1とVB2ラインが定電流源のベースラインとなる。このモードではPROMOUTは関係なくメモリー素子のZ300の下のトランジスタQ304の状態をON状態にしてPE端子より電流を流して、PROMを書き込む作業を行う。PROMの書き込みビットを選択するには、信号251をLOWにする。これによりQ350の電流はQ304のベースに供給されQ304をON状態にする。この状態からPE端子よりZ300に電流を印加してショート状態にする。このとき、他のビットに信号252から256にHIGHを入力し、PROM回路300−2、PROM回路300−3のQ304をOFF状態にしておけば、VP1が全ビットつながっていても書き込まれる事はない。

【0087】

PE端子に入力端子と電気的に分離するためのダイオードD350をN個直列に繋ぐことにより、PE端子を入力端子と共用することが可能である。また、D350をいくつ直列に繋ぐかは、所望するVC端子の入力Dレンジによって決定される。例えばVC=2.4Vであれば、D350の順方向電圧0.7Vとして、4個直列に接続し0.7×4=2.8VまでVC電圧を上げる事が可能になる。

【0088】

図5(a)は、発振制御回路400のブロック図で、水晶の温度特性を温度補償するために3次関数発生回路を示す。ブロックとして、3次関数(α)、1次関数(β)、0次関数(γ)、変極点(T0)がある。この合成した出力が450に出力される。これ等の特性は以下の式1で表すことが出来る。

【0089】

VCON=α(Ta−T0)3+β(Ta−T0)+γ ・・・(式1)

【0090】

α、β、γ、T0をそれぞれ制御する複数のPROM回路が具備される。発振制御回路400の3次制御電圧出力VCONの温度特性を図5(b)に示す。

【0091】

図6は発振回路500のブロック図である。トランジスタM510のゲートに、発振制御回路400から温度補償電圧VCON450を印加することにより、温度に対して高安定な発振器出力を得る。またトランジスタM511のゲートには、入力端子VC/DATA/PE12よりVC電圧を印加し、VCO機能として使用する。

【0092】

水晶振動子500は、水晶端子1と水晶端子2間に接続する。INV520はインバータであり、その出力をバッファーしてOUT端子13に出力する。

【0093】

図7は、本実施形態における電源端子と入力端子の入力波形である。すなわち、図7(a)は、電源端子11へ供給される電源/クロック信号VCC/CLKを示し、図7(c)は、入力端子12へ供給される入力信号VC/DATA/PEを示す。

【0094】

これは、モードセレクタ回路100が3ビット構成(F/F回路110〜112:図2参照)の場合に、リードモードに続くモード設定区間における入力信号VC/DATA/PEデータを「H,L,L」とした場合である。なお、入力信号VC/DATA/PEは、電源/クロック信号VCC/CLKの立ち下りエッジで読み込まれる。

【0095】

入力信号VC/DATA/PEデータに、このパターン「H,L,L」が入力された場合に、図7(b)に示すように、PROM電源VCC2が立ち上がり、エミュレーションモードEMにする事が可能になる。すなわち、エミュレーションモードEMに切り替わった後は、入力端子12へ供給される入力信号DATAにより、PROM回路300の調整ビットの設定が行われる。

【0096】

図8(a)は、本実施形態のTCXOモジュールの端子構成を示す。本実施形態のTCXOモジュールは、電源端子(VCC1)21と接地端子(GND)22と周波数出力端子(OUT)23と入力端子(VC)24が備わっている(周波数制御機能がある場合)。

【0097】

また、図8(b)は、本実施形態のTCXO制御用ICの端子構成を示す。本実施形態のTCXO制御用ICは、接地端子(GND)25、出力端子(OUT)28、水晶端子1XT29、水晶端子2XTB26、入力端子(VC/DATA)27および電源端子(VCC/CLK)30の6端子で構成することができる。

【0098】

また、図8(c)は、本実施形態のTCXO制御用ICにおける他の端子構成を示す。本実施形態のTCXO制御用ICは、水晶端子1XT31、水晶端子2XTB34、入力端子(書込,DA,Vc)32、電源端子(PROM電源,Vcc,CLK)35、接地端子(GND)33、出力端子(OUT)36の6端子で構成することができる。

【0099】

以上説明したように、本実施形態によれば、端子を共用化することにより、TCXO制御用ICのPAD端子を従来の8パッドから6パッドに減らすことが出来る。これにより、TCXOモジュールとICを接続するパターン配線を減らすことが可能になり、TCXOモジュールの小型化を実現する事ができる。

【0100】

(第2の実施形態)

図9は、本発明の第2の実施形態にかかるTCXO制御用ICの構成を示す。本実施形態のTCXO制御用ICは、モードセレクタ回路100の切り替えを、電源端子(VCC/CLK)11へのCLKパルスのみで行う(Vccは3.5V〜5.5V)事を特徴としている。すなわち、本実施形態では、図2に示す入力端子(VC/DATA/PE)12の信号を入力設定の信号として用いずに、電源端子(VCC/CLK)11の信号だけでモード設定を行うことが可能である。

【0101】

図10は本実施形態における電源端子と入力端子の入力波形である。すなわち、図10(a)は、電源端子11へ供給される電源/クロック信号VCC/CLKの波形を示し、図10(b)は、入力端子12へ供給される入力信号VC/DATA/PEの波形を示す。

【0102】

電源端子11に、信号が入力された場合に、図10(c)に示すように、PROM電源VCC2が立ち上がり、エミュレーションモードEMにする事が可能になる。なお、モード設定区間において、入力信号VC/DATA/PE「L,L,L」が表れているが、本実施形態においては、図9に示したように、入力端子12とモードセレクタ回路100とは接続されていないため、入力信号VC/DATA/PEは、モードセレクタ回路100の動作には関与しない。エミュレーションモードEMに切り替わった後、PROM回路300の調整ビットの設定が行われる。このように、この場合は電源/クロック信号VCC/CLKのみでエミュレーションモードEMにする事が可能である。

【0103】

以上説明したように、上記実施形態にかかる温度補償型水晶発振器によれば、TCXO制御用ICのPAD端子を従来の8パッドから6パッドに減らすことができ、TCXOモジュールとICを接続するパターン配線を減らすことができるため、TCXOモジュールの小型化を実現することができる。

【0104】

また、上記実施形態のTCXOモジュールによれば、モードセレクタ回路100を設けて端子を共用したことによる誤動作を防ぎ、より安定したTCXOモジュールを提供することができる。

【0105】

(第3の実施形態)

上記の実施形態の内容はVCC/CLKの共用化をベースにしており、従来技術においてOUT端子とCLK端子を共用にした場合の問題点、課題を解決し、生産性の向上を図るものである。

【0106】

しかしながら、OUT/CLKの共用も可能である。OUT/CLK共用における従来技術の課題をより正確に説明すると、以下のようになる。VCCの電圧でモードセレクトして、OUT端子よりCLKを入力する構成では、VCC端子とOUT/CLK端子の両方を制御する必要があるため、生産工程が複雑になる。この課題を解決するために、VCCにモードセレクト機能を持たせずに、OUT/CLK端子を共用化することも可能である。すなわち、VCCのレベルを使わずに、OUT/CLK共用も実現可能である。

【0107】

図15,16は、本実施形態にかかるTCXO制御用ICのブロック図を示す。従来は、VCC=3.5VでエミュレーションモードEMにしてから、出力端子(OUT)13よりCLKを入れていたが、本実施形態では、VCCはそのままで、エミュレーションモードEMにするには出力端子(OUT)13からCLKを入れる。なお、第1の実施形態の内容はVCCからCLKを入れるものである。

【0108】

このように、VCC端子11からCLKを入れるのではなく、OUT端子13よりCLKを入れることも可能である。VCCは通常の電源電圧、例えば2.3〜3.3Vに設定し、OUT端子13よりモードセレクタに信号を入力する。モードセレクト信号を入れると、VCC2が立ち上がりエミュレーションモード、あるいはライトモードに切り替わる。基本動作は、VCC端子11からCLKを入れる場合と変わらないが、VCCを一定にして、OUT端子13とVC端子12より同じ動作をさせることが可能である。

【0109】

図17は、本実施形態にかかるモードセレクタ回路100のブロック図である。モードセレクタ回路100は、ICの内部基準電圧VREFを基準とするコンパレータ120を備え、出力端子(OUT/CLK)13からは、コンパレータ120の入力として、例えば、3.5V−5.5VのCLK信号を与える。CLK信号を抵抗180と抵抗181で分圧してコンパレータ120の入力を調整する。すなわち、コンパレータ120は、出力端子(OUT/CLK)13から入力された信号の電圧(CLK信号を抵抗180と抵抗181で分圧したもの)と、ICの内部基準電圧VREFとの比較結果をパルス信号として出力する。これにより、F/F回路110の入力VCKとして、0V−VCCの信号を得る事が出来る。

【0110】

図18は、本実施形態にかかる制御ロジック回路シリアル・インターフェイス200のブロック図である。モードセレクタ回路100において電源電圧VCC2が立ち上がると、制御ロジック回路シリアル・インターフェイス200に電源が供給されエミュレーションモードEMの動作が可能な状態になる。制御ロジック回路シリアル・インターフェイス200の入力クロックに信号VCKを入力し、DATAは入力端子(VC/DATA/PE)12より入力する。これ等のデータを複数のPROMビット分データを送り、PROM回路300にデータを送る。

【0111】

図19は、本実施形態にかかるPROM(1ビット)回路300のブロック図である。制御ロジック回路シリアル・インターフェイス200のF/F回路201からの出力251をPROM回路300に入力する。F/F回路201の信号によりPROMOUTが切換わり発振制御回路400に信号を入力し、周波数を制御する。ここで、所望の周波数に調整し、PROM回路300にデータを入力端子(VC/DATA/PE)12より書き込む。

【0112】

図20は、本実施形態にかかる(エミュレーションモード/リード)モード切替設定方法を説明するための図であり、図20(a)は、OUT/CLK端子13の入力波形、図20(b)は、電源端子11の電圧波形、図20(c)は、モードセレクタ回路100から供給される電源電圧VCC2の電圧波形、図20(d)は、入力端子(VC/DATA/PE)12の入力波形(図15の場合)、図20(e)は、入力端子(VC/DATA/PE)12の入力波形(図16の場合)である。

【0113】

OUT端子13は通常のリードモード時は0V〜1VのクリップドSIN(波形上下のピークが電圧クリップされた信号)で出力する。本実施形態においてOUT端子13よりCLKを入れる場合の入力/出力波形を示したものである。CLK波形は外部電源より3.5V−5.5Vで入力を行い、モードセットを行う。その後、入力波形を外すとエミュレーションモードでの周波数を測定することが可能になる。

【0114】

図21および図22は、本実施形態にかかるOUT端子13の一般的な出力形式を示す。OUT端子13の一般的な出力形式はNMOS出力(M1001、M1002)で構成されている。例えば、M1001のバックゲートがソースと出力端子13に接続されていた場合、OUT端子13をHighにすると、バックゲートードレイン端子の寄生のダイオードでVCCより高い電位を与えることが困難になる。

【0115】

そこで、図21では、M1001のドレイン側にバイポーラトランジスタでバッファすることにより、OUT端子13をHigh(5.5V)にすることが可能になる。これは、OUT端子13の印加電圧を上昇させていったときにQ1004のエミッターベース電圧でバックゲートードレイン端子の寄生のダイオードに電流が流れることを抑えることが出来る。

【0116】

また、図22ではバックゲートをGNDにすることにより、OUT端子13の印加電圧を上昇させたときにバックゲートードレイン端子の寄生のダイオードが出来なくして、5.5Vまで電圧が上がるように出来る。

【0117】

(第4の実施形態)

図25,図26は、本実施形態にかかるTCXO制御用ICのブロック図を示す。第1の実施形態の内容がVCCからCLKを入れるものであったのに対し、本実施形態では、エミュレーションモードEMにするには、入力端子(VC)12からCLKを入れる。

【0118】

このように、VCC端子11からCLKを入れるのではなく、VC端子12よりCLKを入れることも可能である。VCCは、通常の電源電圧、例えば2.3〜3.3Vに設定し、VC端子12よりモードセレクタに信号を入力する。モードセレクト信号を入れると、VCC2が立ち上がりエミュレーションモード、あるいはライトモードに切り替わる。

【0119】

基本動作は、VCC端子11からCLKを入れる場合と変わらないが、VCCを一定にして、OUT端子13とVC端子12より同じ動作をさせることが可能である。

【0120】

図27は、本実施形態にかかるモードセレクタ回路100のブロック図である。モードセレクタ回路100は、ICの内部基準電圧VREFを基準とするコンパレータ120を備え、入力端子(VC/CLK)12からは、コンパレータ120の入力として、例えば、3.5V−5.5VのCLK信号を与える。CLK信号を抵抗180と抵抗181で分圧してコンパレータ120の入力を調整する。

すなわち、コンパレータ120は、入力端子(VC/CLK)12から入力された信号の電圧(CLK信号を抵抗180と抵抗181で分圧したもの)と、ICの内部基準電圧VREFとの比較結果をパルス信号として出力する。

これにより、F/F回路110の入力VCKとして、0V−VCCの信号を得る事が出来る。

【0121】

図28は、本実施形態にかかる制御ロジック回路シリアル・インターフェイス200のブロック図である。モードセレクタ回路100において電源電圧VCC2が立ち上がると、制御ロジック回路シリアル・インターフェイス200に電源が供給されエミュレーションモードEMの動作が可能な状態になる。制御ロジック回路シリアル・インターフェイス200の入力クロックに信号VCKを入力し、DATAは出力端子(OUT/DATA)13より入力する。これ等のデータを複数のPROMビット分データを送り、PROM回路300にデータを送る。

【0122】

図29は、本実施形態にかかるPROM(1ビット)回路300のブロック図である。

制御ロジック回路シリアル・インターフェイス200のF/F回路201からの出力251をPROM回路300に入力する。F/F回路201の信号によりPROMOUTが切換わり発振制御回路400に信号を入力し、周波数を制御する。ここで、所望の周波数に調整し、PROM回路300にデータを入力端子(VC/CLK/PE)12より書き込む。

【0123】

図30は、本実施形態にかかる(エミュレーションモード/リード)モード切替設定方法を説明するための図である。図30(a)は、VC/CLK端子13の入力波形、図30(b)は、電源端子11の電圧波形、図30(c)は、モードセレクタ回路100から供給される電源電圧VCC2の電圧波形、図30(d)は、出力端子(OUT/DATA)13の入力波形(図25の場合)、図30(e)は、出力端子(OUT/DATA)13の入力波形(図26の場合)である。

【0124】

OUT端子13は、通常のリードモード時は0V〜1VのクリップドSIN(波形上下のピークが電圧クリップされた信号)で出力する。本実施形態においてOUT端子13よりDATAを入れる場合の入力/出力波形を示したものである。

DATA波形は外部電源より0V−5.5Vで入力を行い、モードセットを行う。

その後、入力波形を外すとエミュレーションモードでの周波数を測定することが可能になる。

【0125】

OUT端子を5.5VまでDATAとして上げるには、第2の実施形態と同じく図21,22のように構成すると簡単に0V−5.5Vを入力することが可能である。

【0126】

(第5の実施形態)

図31,図32は、本実施形態にかかるTCXO制御用ICのブロック図を示す。第1の実施形態の内容が、VCCからCLKを入れ、入力端子(VC)12からDATAを入れるものであったのに対し、本実施形態では、エミュレーションモードEMにするために、出力端子からDATAを入れるものである。

【0127】

このように、出力端子13よりDATAを入れることも可能である。VCC端子11よりモードセレクタ回路100に信号を入力する。モードセレクト信号を入れると、VCC2が立ち上がりエミュレーションモード、あるいはライトモードに切り替わる。

【0128】

基本動作は、VCC端子11からCLKを入れ、入力端子12よりDATAをいれる場合と同じである。

【0129】

図33は、本実施形態にかかるモードセレクタ回路100のブロック図である。モードセレクタ回路100は、ICの内部基準電圧VREFを基準とするコンパレータ120を備え、電源端子(VCC/CLK)12からは、コンパレータ120の入力として、例えば、3.5V−5.5VのCLK信号を与える。CLK信号を抵抗180と抵抗181で分圧してコンパレータ120の入力を調整する。

すなわち、コンパレータ120は、電源端子(VCC/CLK)12から入力された信号の電圧(CLK信号を抵抗180と抵抗181で分圧したもの)と、ICの内部基準電圧VREFとの比較結果をパルス信号として出力する。

これにより、F/F回路110の入力VCKとして、0V−VCCの信号を得る事が出来る。

【0130】

図34は、本実施形態にかかる制御ロジック回路シリアル・インターフェイス200のブロック図である。モードセレクタ回路100において電源電圧VCC2が立ち上がると、制御ロジック回路シリアル・インターフェイス200に電源が供給されエミュレーションモードEMの動作が可能な状態になる。制御ロジック回路シリアル・インターフェイス200の入力クロックに信号VCKを入力し、DATAは出力端子(OUT/DATA)13より入力する。これ等のデータを複数のPROMビット分データを送り、PROM回路300にデータを送る。

【0131】

図35は、本実施形態にかかるPROM(1ビット)回路300のブロック図である。

制御ロジック回路シリアル・インターフェイス200のF/F回路201からの出力251をPROM回路300に入力する。F/F回路201の信号によりPROMOUTが切換わり発振制御回路400に信号を入力し、周波数を制御する。ここで、所望の周波数に調整し、PROM回路300にデータを入力端子(VC/PE)12より書き込む。

【0132】

図36は、本実施形態にかかる(エミュレーションモード/リード)モード切替設定方法を説明するための図である。図36(a)は、VCC/CLK端子11の入力波形、図36(b)は、モードセレクタ回路100から供給される電源電圧VCC2の電圧波形、図36(c)は、出力端子(OUT/DATA)13の入力波形(図31の場合)、図36(d)は、出力端子(OUT/DATA)13の入力波形(図32の場合)である。

【0133】

OUT端子13は、通常のリードモード時は0V〜1VのクリップドSIN(波形上下のピークが電圧クリップされた信号)で出力する。図36(c)、(d)は、本実施形態においてOUT端子13よりDATAを入れる場合の入力/出力波形を示したものである。

DATA波形は、外部電源より0V−5.5Vで入力を行い、モードセットを行う。

その後、入力波形を外すとエミュレーションモードでの周波数を測定することが可能になる。

【0134】

OUT端子を5.5VまでDATAとして上げるには、第2の実施形態と同じく図21,22のように構成すると簡単に0V−5.5Vを入力することが可能である。

【0135】

(第6の実施形態)

図39,図40は、本実施形態にかかるTCXO制御用ICのブロック図を示す。水晶端子1または水晶端子2(XT1またはXT2)からCLKを入れ、入力端子(VC)12からDATAを入れてエミュレーションモードEMにするものである。

【0136】

このように、水晶端子のいずれかよりCLKを入れることも可能である。水晶端子のいずれかよりモードセレクタ回路100に信号を入力する。モードセレクト信号を入れると、VCC2が立ち上がりエミュレーションモード、あるいはライトモードに切り替わる。

【0137】

基本動作は、VCC端子11からCLKを入れ、入力端子12よりDATAをいれる場合と同じである。

【0138】

図41は、本実施形態にかかるモードセレクタ回路100のブロック図である。モードセレクタ回路100は、ICの内部基準電圧VREFを基準とするコンパレータ120を備え、電源端子(水晶端子1または2/CLK)からは、コンパレータ120の入力として、例えば、3.5V−5.5VのCLK信号を与える。CLK信号を抵抗180と抵抗181で分圧してコンパレータ120の入力を調整する。

すなわち、コンパレータ120は、水晶端子(XT1またはXT2/CLK)から入力された信号の電圧(CLK信号を抵抗180と抵抗181で分圧したもの)と、ICの内部基準電圧VREFとの比較結果をパルス信号として出力する。

これにより、F/F回路110の入力VCKとして、0V−VCCの信号を得る事が出来る。

【0139】

図42は本実施形態にかかる制御ロジック回路シリアル・インターフェイス200のブロック図である。モードセレクタ回路100において電源電圧VCC2が立ち上がると、制御ロジック回路シリアル・インターフェイス200に電源が供給されエミュレーションモードEMの動作が可能な状態になる。制御ロジック回路シリアル・インターフェイス200の入力クロックに信号VCKを入力し、DATAは入力端子(VC/DATA)より入力する。これ等のデータを複数のPROMビット分データを送り、PROM回路300にデータを送る。

【0140】

図43は、本実施形態にかかるPROM(1ビット)回路300のブロック図である。

制御ロジック回路シリアル・インターフェイス200のF/F回路201からの出力251をPROM回路300に入力する。F/F回路201の信号によりPROMOUTが切換わり発振制御回路400に信号を入力し、周波数を制御する。ここで、所望の周波数に調整し、PROM回路300にデータを入力端子(VC/PE)12より書き込む。

【0141】

図44は、本実施形態にかかる(エミュレーションモード/リード)モード切替設定方法を説明するための図である。図44(a)は、水晶端子XT1あるいはXT2/CLK端子の入力波形、図44(b)は、モードセレクタ回路100から供給される電源電圧VCC2の電圧波形、図44(c)は、入力端子(VC/DATA)の入力波形(図39の場合)、図44(d)は、出力端子(OUT/DATA)13の入力波形(図40の場合)である。

【0142】

水晶端子1,2は、通常のリードモード時は0V〜2VのSIN(波形上下のピークが電圧クリップされた信号)に近い波形で出力する。本実施形態において水晶端子1あるいは2よりCLKを入れる場合は注意が必要である。

水晶端子1,2は通常ハイ・インピーダンスで動作しており、外部より電圧を印加することを従来は推奨していなかった。

しかし本発明では、水晶端子が通常の動作領域で無い例えば3.5V〜5.5Vで入力しモードセットを行う。

その後、水晶端子1あるいは2を外すとエミュレーションモードでの周波数を測定することが可能になる。

【0143】

また、本説明では1タイムPROMを例としたためリードモード/エミュレーションモード/ライトモードの切り替えを説明した。しかし、ANYタイムPROM(複数回書き込み可能なPROM)で、特にエミュレーションモードが無くリードモード/ライトモードだけの場合も本実施形態を使用し端子の共用化が可能である。

【0144】

また、本説明では1タイムPROMを例としたためリードモード/エミュレーションモード/ライトモードの切り替えを説明した。しかし、ANYタイムPROM(複数書き込み可能なPROM)で、特にエミュレーションモードが無くリードモード/ライトモードだけの場合も本実施形態を使用し端子の共用化が可能である。以下、1タイムPROMおよびANYタイムPROMのそれぞれを使用したTCXOの調整時のフローについて説明する。

【0145】

図37は1タイムPROMを使用したTCXOの調整時のフローチャートである。

1タイムであるため書き込みは当然1度しか出来ない。従って、ステップ1でエミュレーションモードでデータのみを入力し、ステップ2で周波数測定を行う。これを各パラメータ、各温度において周波数データを繰り返し取得する。

前記ステップ2で取得した周波数をステップ3で分析し、もっとも周波数の安定度の高いROM設定を計算させる。

前記ステップ3で算出した最適パラメータを、ステップ4でライトモードに設定し、ステップ5でPROMに書き込む。

最後にステップ6でリードモードにて周波数が温度補償されていることを確認する。

【0146】

図38はANYタイムPROMを使用したTCXOの調整時のフローチャートである。ANYタイムPROMの場合は、その特徴を生かして、エミュレーションモード回路を省略し、その都度書き込みを行いデータを書き込み周波数データを取ることも可能である。

また、ANYタイムPROMは、非常に厳しい小チップサイズが要求される。そのため、エミュレーション用回路を省略しサイズの低減を行う代わりに、周波数データを取る度にROMに書き込む必要が有る。このため、書き込みに時間がかかりデータ取りに時間を要す場合がある。

【0147】

ステップ11でライトモードにしてデータを入力する。その後ステップ12で書き込みを実施し、ステップ13で周波数測を行う。これを各パラメータ、各温度において周波数データを繰り返し取得する。ここまでのステップは、後述するように、1タイムPROMを使用したTCXOの調整時のエミュレーションモードと同じである。

前記ステップ13で取得した周波数をステップ14で分析し、もっとも周波数の安定度の高いROM設定を計算させる。

前記ステップ14で算出した最適パラメータをステップ15でライトモードに設定し、ステップ16でPROMに書き込む。最後にステップ17でリードモードにて周波数が温度補償されていることを確認する。

ステップ13〜17の工程はPROMに関係なく同じである。

【0148】

図38のステップ11〜ステップ13の処理は図37のステップ1〜ステップ2と目的は同じである。すなわち、これらの処理は、最終書き込みを行うデータを決定するための目的の作業であり、共にエミュレーションモードになると言える。

以上のようにPROMの種類により、端子共用の構成、基本動作が変わることは無い。また、フローチャートも変わることは無い。

【0149】

上記説明では、CLK機能の共用化とDATA機能の共用化を各端子に行う手法を提案しているが、例えば、CLK機能とDATA機能を共用する端子を逆にしても同様の効果を得ることが出来る。

【0150】

実施例では、CLK機能の共用化とDATA機能の共用化を各端子に行う手法を提案しているが、例えば、CLK機能とDATA機能を共用する端子を逆にしても同様の効果を得ることが出来る。

【0151】

また、上記実施例の説明では、温度補償をする場合に、EM/WM/RMが必要である旨や、それに準じた動作が出来る場合を記載している。しかし、温度補償をする場合に限らず、水晶発振器の周波数の調整や、入力端子の機能の変更を行う場合に、PROMが必要になる場合がある。

したがって、本発明の端子共用が有効になる。本発明が入力端子の機能変更にも有効である理由を以下に説明する。

【0152】

本発明は、6端子という制約の中で端子機能を共用する技術に関する。ここで6端子とは電源端子、接地端子、出力端子、入力端子、水晶端子1、水晶端子2である。

近年、入力端子には、様々な機能を持たせて付加価値を付けている。例えば、スイープモード切替入力端子、スタンバイモード切替入力端子、温度センサ出力などが考えられる。これらの切り替えについても、本発明のように端子を共用化してDATA、CLKを入力し、少ない端子で容易にPROMに書き込むことにより、切り替えを行うことが可能になる。

【産業上の利用可能性】

【0153】

本発明は、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる効果を有し、TCXO等に有用である。

【図面の簡単な説明】

【0154】

【図1】本発明の第1の実施形態にかかるTCXO用ICのブロック図(1)

【図2】本発明の第1の実施形態にかかるモードセレクタ回路のブロック図

【図3】本発明の第1の実施形態にかかる制御ロジック部のブロック図

【図4】本発明の第1の実施形態にかかるPROM回路部のブロック図

【図5】本発明の第1の実施形態にかかる周波数制御回路の概要図

【図6】本発明の第1の実施形態にかかる発振回路のブロック図

【図7】本発明の第1の実施形態にかかる入力波形の一例を示す図

【図8】本発明の第1の実施形態にかかるTCXOモジュールおよびTCXO制御用ICの端子構成例を示す図

【図9】本発明の第2の実施形態にかかるTCXO用ICのブロック図(2)

【図10】本発明の第2の実施形態にかかる入力波形の一例を示す図

【図11】従来のTCXO用ICの端子構成例を示す図

【図12】従来のTCXO用ICのブロック図

【図13】本発明の第1の実施形態にかかるTCXO用ICのブロック図(3)

【図14】本発明の第1の実施形態にかかる内部クロック発生回路のブロック図

【図15】本発明の第3の実施形態にかかるTCXO用ICのブロック図(4)

【図16】本発明の第3の実施形態にかかるTCXO用ICのブロック図(5)

【図17】本発明の第3の実施形態にかかるモードセレクタ回路のブロック図

【図18】本発明の第3の実施形態にかかる制御ロジック部のブロック図

【図19】本発明の第3の実施形態にかかるPROM回路部のブロック図

【図20】本発明の第3の実施形態にかかる入力波形の一例を示す図

【図21】本発明の実施形態にかかるOUT端子13の一般的な出力形式を示す図

【図22】本発明の実施形態にかかるOUT端子13の一般的な出力形式を示す図

【図23】従来の温度補償型水晶発振器の概略構成を示す図

【図24】従来の温度補償型水晶発振器における調整データ入力波形を示す図

【図25】本発明の第4の実施形態にかかるTCXO用ICのブロック図(6)

【図26】本発明の第4の実施形態にかかるTCXO用ICのブロック図(7)

【図27】本発明の第4の実施形態にかかるモードセレクタ回路のブロック図

【図28】本発明の第4の実施形態にかかる制御ロジック部のブロック図

【図29】本発明の第4の実施形態にかかるPROM回路部のブロック図

【図30】本発明の第4の実施形態にかかる入力波形の一例を示す図

【図31】本発明の第5の実施形態にかかるTCXO用ICのブロック図(8)

【図32】本発明の第5の実施形態にかかるTCXO用ICのブロック図(9)

【図33】本発明の第5の実施形態にかかるモードセレクタ回路のブロック図

【図34】本発明の第5の実施形態にかかる制御ロジック部のブロック図

【図35】本発明の第5の実施形態にかかるPROM回路部のブロック図

【図36】本発明の第5の実施形態にかかる入力波形の一例を示す図

【図37】1タイムROMの場合の調整フロー例を示す図

【図38】ANYタイムROMの場合の調整フロー例を示す図

【図39】本発明の第6の実施形態にかかるTCXO用ICのブロック図(10)

【図40】本発明の第6の実施形態にかかるTCXO用ICのブロック図(11)

【図41】本発明の第6の実施形態にかかるモードセレクタ回路のブロック図

【図42】本発明の第6の実施形態にかかる制御ロジック部のブロック図

【図43】本発明の第6の実施形態にかかるPROM回路部のブロック図

【図44】本発明の第6の実施形態にかかる入力波形の一例を示す図

【符号の説明】

【0155】

11,21,30,35 電源端子

12,24,27,32 入力端子

13,23,28,36 出力端子

14,22,25,33 接地端子

26,34 水晶端子2

29,31 水晶端子1

100 モードセレクタ回路

101 内部クロック発生回路

110,111,112,201,202,203,204,205,206 F/F回路

120 コンパレータ

121,122,520 インバータ

123 NAND回路

150 トランジスタM1

200 制御ロジック回路シリアル・インターフェイス

300 PROM回路

350 ダイオード

400 発振制御回路

411 定電圧回路

412 温度センサ

413 3次関数生成回路

414 1次関数生成回路

415 0次関数生成回路

416 変極点調整回路

500 発振回路

550 水晶振動子

【技術分野】

【0001】

本発明は、温度補償型水晶発振器(以下「TCXO」という)制御用ICに関し、特に、水晶発振器及び制御用ICの端子の共用化に関するものである。

【背景技術】

【0002】

現在の水晶発振器は、小型化が急速に進んでいる。また水晶を制御する半導体も小型化が急速に進んでいる。水晶発振器には通常、電源端子(VCC1)と接地端子(GND)と周波数出力端子(OUT)と周波数制御端子(VC)とが備わっている(周波数制御機能がない場合もある)。また、水晶発振器には、水晶振動子の接続端子(XT1)、(XT2)も必要である。

【0003】

また、高精度な発振を行う水晶発振器では、内部にPROM回路を備えており、PROM回路を用いて温度補償回路などを制御している(TCXO、VCXOなど)。

【0004】

TCXOは、水晶の周波数の温度特性をキャンセルする制御を行うことにより、高精度な発振を行う。水晶の周波数のバラツキは個々に異なるため、TCXO1台毎に調整を行い、制御用ICに内蔵されているPROM回路に調整データを書き込んで温度補償を行っている。ここで、1タイムPROMを使用したTCXOの周波数調整について説明する。

【0005】

現状のTCXOの周波数調整には、3種類の動作モードが必要とされる。通常使用するモードでの使用に先立ち、PROM回路に書き込むデータ(書き込みビット)を決定するために、データを入力し周波数データを取得し計算するモード(エミュレーションモード以下EM)が有る。また、エミュレーションモードEMで決定したデータをPROM回路に書き込むモード(ライトモード以下WM)が有る。そして、通常使用するモード(リードモード以下RM)において、PROM回路に書き込まれたデータを読み出して周波数を制御する。これら3種類のモードを切り替えることにより、TCXOの周波数調整が行われる。

【0006】

このように高精度な発振を行う水晶発振器は、さらに、各モードでの制御を行う為に、専用の制御端子を必要とする。上記PROM回路の制御を行う為には、例えば、CLK端子、DATA端子、PROM電源端子が必要である。しかしながら、水晶発振器を一層小型化するためには、これ等端子の共用化を行う必要がある。

【0007】

端子共用化の例としては、特許文献1に記載の技術があり、周波数制御端子とDATA端子、発振出力端子とCLK端子の共用化が提案されている。

【0008】

また、本出願人は、図11に示すように、電源端子とCLK端子を共用した端子(Vcc,CLK)56、およびDATA端子とVC端子を共用した端子(DATA/VC)52を有するTCXOモジュールを既に提案している(特許文献2参照)。なお、図11に示すTCXOモジュールは、さらに水晶振動子の接続端子XT51,XTB55、PROM電圧端子53、書込みPE端子57、接地端子(GND)54および発振出力端子(OUT)58の8個の端子を備えている。

【0009】

図23は、上記特許文献2に記載された温度補償型水晶発振器の概略構成を示す図である。図23において、電源/CLK端子11Aは、モジュールの電源端子であり、この端子によって2.8Vの単一電圧を供給する。また、PROM回路にクロック信号を送るCLK端子の機能を有する。電圧制御/DATA端子12Aは、周波数を電圧制御する端子であり、PROM回路にデータを与える機能を有する。

【0010】

このように、この温度補償型水晶発振器は、PROM回路にクロック信号を与えるCLK端子と電源端子とを共有しており、電圧制御回路に電圧を与える電圧制御端子とPROM回路にデータを与えるDATA端子とを共用化している。

【0011】

図24は、この温度補償型水晶発振器における調整データ入力波形を示す図である。調整時には電源端子5Aを2.3Vに設定した後、電源端子11Aを介して制御用ICのレジスタにクロック信号を与え、端子12Aからデータ信号を与える。信号を与えた後に制御用ICを通常使用する電源電圧2.3〜3.3Vに固定する。また、端子12Aには、電圧制御範囲の電圧0V〜3.3Vを与えて発振周波数の調整を行う。

【0012】

一方、メモリーをEEPROMで構成した場合、書き換えが可能なためチップ面積に余裕が無い場合、エミュレーションモードを持たないこともある。その場合、周波数データを取るために、わざわざ書き込みを行い、その都度データを取る。その後そのデータに基づき最適ビットを算出する。以降の動作は、どのようなPROMでも同じである。

【0013】

この場合、基本の調整の方法は変らないが、エミュレーション時のデータの取り方の詳細は以下の動きをする。実際にはエミュレーションのデータを入力する。この時点では周波数は変化しない。次に書き込み動作を行う。これによりデータが出力に反映される。この作業を繰り返し行いデータを取っていく。

【0014】

【特許文献1】米国特許第5724009号明細書

【特許文献2】特開2003−188646号公報

【発明の開示】

【発明が解決しようとする課題】

【0015】

しかし、上記特許文献1に記載された手法では、アナログ信号とディジタル信号とで端子を共用するため、水晶発振器の調整を行うためには、非常に複雑な切り替えが必要となる。

【0016】

例えば、OUT端子とCLK端子を共用化した場合の切り替えにおいて、CLK入力時は、パルス発生電源を接続するのに対し、定常状態では、周波数をOUT端子より読み込むための周波数カウンタが必要となるため、その接続の切り替えが複雑である。

【0017】

一方、水晶発振器を調整するためにPROM回路を使用する場合、エミュレーションモードEMの設定をするためにシリアルデータを入力する必要があり、CLK端子とDATA端子を必要とする。また、リードモードRM、エミュレーションモードEMおよびライトモードWMのモード切り替えを行うための端子が必要になる。以下に具体例を示す。

【0018】

図12は、従来のTCXO制御用ICを示す。従来のTCXO制御用ICは、電源端子2(VCC2:モードセレクト用電源)62を備え、その電源端子2(62)でモード切り替えを行っていた。例えば、電源端子2(62)がオープンでリードモードRM、電源端子2(62)が2.3V時にエミュレーションモードEM、電源端子2(62)が3.5V時にライトモードWMというように使い分けを行っている。

【0019】

このように、従来のTCXO制御用ICは、リードモードRM、エミュレーションモードEMおよびライトモードWMを切り替える場合、電源端子2(62)から別電源(PROM電源VCC2:モードセレクト用電源)にてバイアスを与えてデータ入力を行っていた。しかし、最近の小型化の要求に応えるためには、ICのPAD(端子)あるいはTCXOモジュールの端子を一層削減する必要がある。

【0020】

本発明は、上記従来の事情に鑑みてなされたものであって、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる温度補償型水晶発振器を提供することを目的としている。

【課題を解決するための手段】

【0021】

本発明に係る温度補償型水晶発振器制御用ICは、電源電圧およびクロック信号が供給される電源端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記電源電圧に前記クロック信号が重畳されて入力される第1の信号と、所定の基準電圧との比較結果をクロック信号として出力する内部クロック発生回路を備える。

【0022】

上記構成によれば、電源電圧にクロック信号が重畳されて入力される第1の信号と、所定の基準電圧との比較結果をクロック信号として出力するので、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。

【0023】

本発明に係る温度補償型水晶発振器制御用ICは、電源電圧およびクロック信号が供給される電源端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器であって、前記電源端子から前記電源電圧に前記クロック信号が重畳された第1の信号が入力され、前記入力端子から所定のパターンを有する第2の信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える。

【0024】

上記構成によれば、端子を共用化するために電源端子から電源電圧にクロック信号が重畳された第1の信号を入力するとともに、入力端子から所定のパターンを有する第2の信号が入力された場合にエミュレーションモードに切り替えるので、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。また、端子共用化による誤作動が起こる可能性を低減することができる。

【0025】

また、本発明に係る温度補償型水晶発振器制御用ICにおいて、前記第1の信号のレベルは通常動作時の電圧より高い電圧である。

【0026】

上記構成によれば、温度補償型水晶発振器制御用ICとして実際に使用する電圧2.3V−3.3Vより高い電圧範囲(例えば、3.5V−5.5V)となり、モード設定を安定して行うことができる。

【0027】

また、本発明に係る温度補償型水晶発振器制御用ICは、前記第1のモードセレクタ回路が、前記第1の信号と所定の基準電圧との比較結果をパルス信号として出力するコンパレータと、前記コンパレータにより出力されたパルス信号に応じて、前記第2の信号をシフトする所定段の第1のフリップフロップ回路と、前記第1のフリップフロップ回路の出力信号に応じて、前記電源電圧を制御するトランジスタと、を有するものである。

【0028】

上記構成によれば、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。また、端子共用化による誤作動が起こる可能性を低減することができる。

【0029】

また、本発明に係る温度補償型水晶発振器制御用ICは、前記第1のフリップフロップ回路の各段の出力が前記所定のパターンに一致した場合に、前記トランジスタを制御する論理回路を備える。

【0030】

上記構成によれば、第1のフリップフロップ回路の各段の出力が所定のパターンに一致した場合にトランジスタを制御するので、端子の共用化に伴う誤動作の可能性を低減することができる。

【0031】

また、本発明に係る温度補償型水晶発振器制御用ICは、前記エミュレーションモードあるいはライトモードにおいて、前記第1のモードセレクタ回路、又は信号から前記電源電圧が制御されることにより動作し、前記PROM回路に書き込むデータを設定する制御ロジック回路を備える。

【0032】

上記構成によれば、制御ロジック回路は、第1のモードセレクタ回路から電源電圧が供給された場合に動作するので、ノイズ等によりエミュレーションモードEMに入り、PROM回路に誤ったデータが書き込まれることを防止することができる。

【0033】

また、本発明に係る温度補償型水晶発振器制御用ICは、前記制御ロジック回路が、前記クロック信号に応じて、前記第2の信号をシフトする所定段の第2のフリップフロップ回路を備える。

【0034】

上記構成によれば、第2のフリップフロップ回路は、第1のモードセレクタ回路から電源電圧が供給された場合に第2の信号をシフトするので、ノイズ等によりエミュレーションモードEMに入り、PROM回路に誤ったデータが書き込まれることを防止することができる。

【0035】

また、本発明に係る温度補償型水晶発振器制御用ICは、前記PROM回路が、前記入力端子に直列に接続され、書き込みデータ信号の振幅を制限する直列接続された複数のダイオードを備える。

【0036】

上記構成によれば、PROM回路は、書き込みデータ信号の振幅を制限する直列接続された複数のダイオードを備えるので、PE端子を入力端子と電気的に分離し、PE端子と入力端子を共用することができる。

【0037】

また、本発明に係る温度補償型水晶発振器制御用ICは、電源電圧およびクロック信号が供給される電源端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記電源端子から前記電源電圧に前記クロック信号が重畳された信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替えるモードセレクタ回路を備える。

【0038】

上記構成によれば、電源端子から電源電圧にクロック信号が重畳された信号が入力された場合にエミュレーションモードに切り替えるモードセレクタ回路を備えるので、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。

【0039】

また、本発明に係る温度補償型水晶発振器制御用ICは、前記第1の信号が供給される第1の端子、および前記第2の信号が供給される第2の端子を含む6個の端子を有する。また、本発明に係る温度補償型水晶発振器制御用ICは、前記電源端子から前記電源電圧に前記クロック信号が重畳された信号が供給される端子を含む6個の端子を有する。

【0040】

上記構成によれば、温度補償型水晶発振器の端子を従来の8パッドから6パッドに減らすことができ、TCXOモジュールとICを接続するパターン配線を減らすことが可能になるため、TCXOモジュールの小型化を実現することができる。

【0041】

また、本発明に係る温度補償型水晶発振器制御用ICは、発振器出力およびクロック信号が供給される出力端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記出力端子から前記クロック信号が重畳された第1の信号が入力され、前記入力端子から所定のパターンを有する第2の信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える。

【0042】

上記構成によれば、端子を共用化するために電源端子から電源電圧にクロック信号が重畳された第1の信号を入力するとともに、入力端子から所定のパターンを有する第2の信号が入力された場合にエミュレーションモードに切り替えるので、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。また、端子共用化による誤作動が起こる可能性を低減することができる。

【0043】

また、本発明に係る温度補償型水晶発振器制御用ICは、発振器出力およびクロック信号が供給される出力端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記出力端子から前記クロック信号が重畳された信号が入力された場合に、前記エミュレーションモード、あるいはライトモードに切り替えるモードセレクタ回路を備える。

【0044】

上記構成によれば、電源端子から電源電圧にクロック信号が重畳された信号が入力された場合にエミュレーションモードに切り替えるモードセレクタ回路を備えるので、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。

【0045】

また、本発明に係る温度補償型水晶発振器制御用ICは、発振器の制御信号が入力される入力端子およびクロック信号が供給される前記入力端子と、発振器の出力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記入力端子から前記クロック信号が重畳された第1の信号が入力され、かつ、前記出力端子から所定のパターンを有する第2の信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える。

【0046】

上記構成によれば、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。

【0047】

また、本発明に係る温度補償型水晶発振器制御用ICは、発振器の制御信号が入力される入力端子およびクロック信号が供給される前記入力端子と、発振器の出力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記入力端子から前記クロック信号が重畳された信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える。

【0048】

上記構成によれば、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。

【0049】

また、本発明に係る温度補償型水晶発振器制御用ICは、電源電圧およびクロック信号が供給される電源端子と、発振器の出力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記電源端子から前記クロック信号が重畳された第1の信号が入力され、かつ、前記出力端子から所定のパターンを有する第2の信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える。

【0050】

上記構成によれば、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。

【0051】

また、本発明に係る温度補償型水晶発振器制御用ICは、電源電圧およびクロック信号が供給される電源端子と、発振器の出力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記電源端子から前記クロック信号が重畳された信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える。

【0052】

上記構成によれば、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。

【0053】

また、本発明に係る温度補償型水晶発振器制御用ICは、水晶振動子が接続される水晶端子およびクロック信号が供給される水晶端子と、発振器の入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記水晶端子から前記クロック信号が重畳された第1の信号が入力され、かつ、前記入力端子から所定のパターンを有する第2の信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える。

【0054】

上記構成によれば、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。

【0055】

さらに、本発明に係る温度補償型水晶発振器制御用ICは、水晶振動子が接続される水晶端子およびクロック信号が供給される水晶端子と、発振器の入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、前記水晶端子から前記クロック信号が重畳された信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える。

【0056】

上記構成によれば、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。

【発明の効果】

【0057】

本発明によれば、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる。これにより、TCXOモジュールとICを接続するパターン配線を減らすことが可能になるため、TCXOモジュールの小型化を実現する事ができる。

【発明を実施するための最良の形態】

【0058】

以下、温度補償型水晶発振器(TCXO)の制御用ICが有するDATA端子、CLK端子、制御回路の電源端子の共用化を、効率よく、かつ調整時の切り替えを要することなく行う手法について、図面を参照しながら説明する。

【0059】

(第1の実施形態)

図1は、本実施形態のTCXO制御用ICのブロック図を示す。本実施形態のTCXO制御用ICは、モードセレクタ回路100、制御ロジック回路シリアル・インターフェイス200、PROM回路300、発振制御回路400および発振回路500を有し、端子としては電源端子(VCC/CLK)11、入力端子(VC/DATA/PE)12、出力端子(OUT)13および接地端子(GND)14を備える。

【0060】

電源端子(VCC/CLK)11は、モードセレクタ回路100に接続される。入力端子(VC/DATA/PE)12は、モードセレクタ回路100と制御ロジック回路200、発振回路500に接続される。出力端子(OUT)13は、発振回路500に接続され、出力端子(OUT)13から、数十MHzの発振出力がなされる。

【0061】

図1に示す本実施形態のTCXO制御用ICは、図12に示す従来のTCXO制御用ICのブロック図に、モードセレクタ回路100が追加されている。

【0062】

図2は、モードセレクタ回路100のブロック図である。モードセレクタ回路100は、ICの内部基準電圧VREFを基準とするコンパレータ120を備え、電源端子(VCC/CLK)11からは、コンパレータ120の入力として、例えば、3.5V−5.5VのCLK信号を与える。CLK信号を抵抗180と抵抗181で分圧してコンパレータ120の入力を調整する。すなわち、コンパレータ120は、電源端子(VCC/CLK)11から入力された信号の電圧(CLK信号を抵抗180と抵抗181で分圧したもの)と、ICの内部基準電圧VREFとの比較結果をパルス信号として出力する。これにより、F/F回路110の入力VCKとして、0V−VCCの信号を得る事が出来る。

【0063】

一方、入力端子(VC/DATA/PE)12からは、0V−5.5Vのデータを入力する。このデータは、電源端子(VCC/CLK)11からのCLK信号に重畳されて、F/F回路110〜112に送られる。

【0064】

F/F回路110〜112に特定の信号が入った場合、トランジスタM1(150)がONして、電源電圧VCC2が立ち上がり、制御ロジック回路シリアル・インターフェイス200に電源が供給されて、エミュレーションモードEMに切り替わる。

【0065】

本実施形態によれば、図12に示した従来の電源端子1(VCC1/CLK)61および電源端子2(VC2:モードセレクト用電源)62を、図1に示す電源端子(VCC/CLK)11として共用化し、電源端子(VCC/CLK)11と入力端子(VC/DATA/PE)12の信号によってモード切り替えを行う。そのため、通常TCXOとして使用しているときに、ノイズ等により、誤ってエミュレーションモードEMに切り替わってしまうおそれがある。そこで、本実施形態では、入力端子(VC/DATA/PE)12に、特定の信号パターンが入力されたときにのみモード切替を行うことにより、ICの誤動作を防ぐことができる。

【0066】

このように本実施形態では、モードセレクタ回路100を備えて、電源端子(VCC/CLK)11と入力端子(VC/DATA/PE)12より特定の信号が供給された場合にモードが切り替るように制御する。

【0067】

このとき、電源端子(VCC/CLK)11の入力のLOWレベルは、制御ロジックおよびシリアルコントロールの信号が動作可能な電圧に設定する。ここで電源端子(VCC/CLK)11のLOWレベルを0Vにしてしまうと、シリアルコントロールが当然効かなくなる。したがって、例えば、電圧3.5V−5.5Vの入力を電源端子(VCC/CLK)11へ入れてモード設定を行う。

【0068】

このため、電源端子(VCC/CLK)11下にコンパレータ120を設け、基準電圧(VREF)を反転入力、電源電圧VCCを抵抗180と抵抗181で分割した電圧を非反転入力とする。

【0069】

コンパレータ120のスレッシュレベル(VREF)を3Vに設定し、電源端子(VCC/CLK)11の抵抗比を調整し電源電圧VCCが4.5Vで切り替る設定にする。実際には電源電圧VCCを3.5V−5.5Vで印加すると、安定した0V−VCCのCLKパルスをインバータ121の出力であるVCK点で作る事が出来る。

【0070】

モードセレクタ回路100は、電源端子(VCC/CLK)11からCLK信号が入力され、入力端子(VC/DATA/PE)12からDATA信号が入力されており、ある特定のデータが入力された場合に、トランジスタM1(150)がON状態になることで電源電圧VCC2が電源電圧VCCと同電位になり、制御ロジック回路200の電源をONにすることができる。

【0071】

モード設定が完了した状態でトランジスタM1(150)がON状態になり電源電圧VCC2の電源が入り、制御ロジック回路シリアル・インターフェイス200を制御することが可能になる。これにより、エミュレーションモードEMに切り替わる。

【0072】

モードセレクタ回路100には、ある特定のビットを入力しないとエミュレーション動作しないように何段かのF/F回路110〜112を具備しておく事により、実使用時に何らかの入力が電源端子(VCC/CLK)11と入力端子(VC/DATA/PE)12に入ってしまったときに誤ってエミュレーションモードEMに入らないように設定をしておく。F/F回路110〜112の段数を増やすと、ICの誤動作防止に一層効果的である。

【0073】

エミュレーションモードEMに切り替わるために特定ビットに信号を入力した後は、3.5V〜5.5Vの信号で水晶の周波数を調整するための周波数データをとる事が出来る。

【0074】

なお、ノイズがない場合はモードセレクタ回路100のF/F回路110〜112等を省略することができる。図13は、図1に示したモードセレクタ回路100を内部クロック発生回路101に置き換えたTCXO制御用ICのブロック図を示す。図14は、内部クロック発生回路101のブロック図である。

【0075】

内部クロック発生回路101は、ICの内部基準電圧VREFを基準とするコンパレータ120を備え、電源端子(VCC/CLK)11からは、コンパレータ120の入力として、例えば、3.5V−5.5VのCLK信号を与える。CLK信号を抵抗180と抵抗181で分圧してコンパレータ120の入力を調整する。すなわち、コンパレータ120は、電源端子(VCC/CLK)11から入力された信号の電圧(CLK信号を抵抗180と抵抗181で分圧したもの)と、ICの内部基準電圧VREFとの比較結果をクロック信号VCKとして出力する。これにより、制御ロジック回路200へ供給する0V−VCCのクロック信号VCKを得る事が出来る。

【0076】

図3は、制御ロジック回路シリアル・インターフェイス200のブロック図である。モードセレクタ回路100において電源電圧VCC2が立ち上がると、制御ロジック回路シリアル・インターフェイス200に電源が供給されエミュレーションモードEMの動作が可能な状態になる。

【0077】

制御ロジック回路シリアル・インターフェイス200の入力クロックに信号VCKを入力し、DATAは入力端子(VC/DATA/PE)12より入力する。これ等のデータを複数のPROMビット分データを送り、PROM回路300にデータを送る。

【0078】

これらは水晶振動子の周波数の温度特性や発振器出力を調整するためのビット数分必要であり、通常は40〜60ビット程度である。

【0079】

図4はPROM回路300を示す。制御ロジック回路シリアル・インターフェイス200のF/F回路201からの出力251をPROM回路300に入力する。F/F回路201の信号によりPROMOUTが切換わり発振制御回路400に信号を入力し、周波数を制御する。ここで、所望の周波数に調整し、PROM回路300にデータを入力端子(VC/DATA/PE)12より書き込む。

【0080】

PROM回路300の書き込み端子(PE端子)が存在する場合は入力端子(VC端子)との共用を行う。本実施形態においては、図4に示すように、PE端子(入力端子12)にダイオードを複数個直列接続(D350×n個)して、PROM回路機能側と他の機能側とをDC的に分離することにより、PE端子とVC端子との共用化を実現する。PROM回路機能側のPE端子から書き込むPROM書き込み動作と他の機能側のVC端子から周波数をVCOとしての動作が両立しなければ、共用化は出来ない。VC端子の一般的な使用として1MΩ以上のインピーダンスが必要で、VCOとして3V付近まで動作させる必要がある。単純に従来のPE端子をVC端子を接続したのでは、VC端子のインピーダンスはD350のダイオード(n=1)でクランプされVC端子の電圧を上げることが出来ない。そこで、D350のダイオードをn個直列に接続することにより、VC端子はn×0.7Vの動作レンジを得ることが出来るようになる。D350のダイオードを積み上げることは、書き込みする上では書き込み時のPE端子の耐圧が十分あれば問題にならない。例えば、5VまでVC端子を動作させたい場合はn(8個)×0.7V=5.6Vなので、8個のダイオードを入れることによりPADの共用化が実現できる。

【0081】

リードモードRMにおける本PROM回路300は、定電流I380からなるカレントミラー電流で動作する。I390からなるカレントミラーはVCC2が立ち上がっていない状態のため電流はゼロである。Q350の電流によりQ304をONさせてZ300のアノードをLOWに固定する。Q351の電流がD300を介してZ300に流れるか、D310を介してQ305に流れるかによりPROMOUTの状態が変わる。すなわち、Z300の状態でPROMOUTが決定される事になる。以下それぞれの状態を説明する。

【0082】

例えばZ300のツェナーダイオードをPE端子より電流を印加してショート状態にした場合は、Q351からの電流はZ300側に流れQ310/305/306に電流は流れない。更にQ352の電流によりQ307がON状態になりPROMOUTはLOWになる。

【0083】

また、Z300がカソードから見てハイインピーダンスの場合はQ351の電流はQ310/305/306に流れ込みQ352の電流を全て引き込み、Q307はOFFしてPROMOUTはHIGHになる。

【0084】

エミュレーションモードEMでは、VCC/CLK端子とVCC2に電圧が印加されI380/I390に電流が流れている状態になり、VB1とVB2ラインが定電流源のベースラインとなる。この状態ではPROMOUTはPROMINの251の信号で制御される。

【0085】

信号251がHIGHの場合、Q303がONすることによりQ304がOFF状態になるので、Q351の電流はD310の方向に流れる。Q351の電流はQ305とQ306のカレントミラーで2倍になる。またQ352の電流はQ351と同じ電流であるため、Q307のベースはLOWとなりQ307はOFFになりPROMOUTはHIGHになる。251がLOWの場合、Q309がOFF状態になり、Q382の電流はQ308のベースに流れ込む。Q308がON状態になりPROMOUTはLOW状態になる。このように、信号251から信号256にデータを入れることによりエミュレーション動作を行うことが出来る。

【0086】

ライトモードWMでは、VCC/CLK端子とVCC2に電圧が印加されI380/I390に電流が流れている状態で、VB1とVB2ラインが定電流源のベースラインとなる。このモードではPROMOUTは関係なくメモリー素子のZ300の下のトランジスタQ304の状態をON状態にしてPE端子より電流を流して、PROMを書き込む作業を行う。PROMの書き込みビットを選択するには、信号251をLOWにする。これによりQ350の電流はQ304のベースに供給されQ304をON状態にする。この状態からPE端子よりZ300に電流を印加してショート状態にする。このとき、他のビットに信号252から256にHIGHを入力し、PROM回路300−2、PROM回路300−3のQ304をOFF状態にしておけば、VP1が全ビットつながっていても書き込まれる事はない。

【0087】

PE端子に入力端子と電気的に分離するためのダイオードD350をN個直列に繋ぐことにより、PE端子を入力端子と共用することが可能である。また、D350をいくつ直列に繋ぐかは、所望するVC端子の入力Dレンジによって決定される。例えばVC=2.4Vであれば、D350の順方向電圧0.7Vとして、4個直列に接続し0.7×4=2.8VまでVC電圧を上げる事が可能になる。

【0088】

図5(a)は、発振制御回路400のブロック図で、水晶の温度特性を温度補償するために3次関数発生回路を示す。ブロックとして、3次関数(α)、1次関数(β)、0次関数(γ)、変極点(T0)がある。この合成した出力が450に出力される。これ等の特性は以下の式1で表すことが出来る。

【0089】

VCON=α(Ta−T0)3+β(Ta−T0)+γ ・・・(式1)

【0090】

α、β、γ、T0をそれぞれ制御する複数のPROM回路が具備される。発振制御回路400の3次制御電圧出力VCONの温度特性を図5(b)に示す。

【0091】

図6は発振回路500のブロック図である。トランジスタM510のゲートに、発振制御回路400から温度補償電圧VCON450を印加することにより、温度に対して高安定な発振器出力を得る。またトランジスタM511のゲートには、入力端子VC/DATA/PE12よりVC電圧を印加し、VCO機能として使用する。

【0092】

水晶振動子500は、水晶端子1と水晶端子2間に接続する。INV520はインバータであり、その出力をバッファーしてOUT端子13に出力する。

【0093】

図7は、本実施形態における電源端子と入力端子の入力波形である。すなわち、図7(a)は、電源端子11へ供給される電源/クロック信号VCC/CLKを示し、図7(c)は、入力端子12へ供給される入力信号VC/DATA/PEを示す。

【0094】

これは、モードセレクタ回路100が3ビット構成(F/F回路110〜112:図2参照)の場合に、リードモードに続くモード設定区間における入力信号VC/DATA/PEデータを「H,L,L」とした場合である。なお、入力信号VC/DATA/PEは、電源/クロック信号VCC/CLKの立ち下りエッジで読み込まれる。

【0095】

入力信号VC/DATA/PEデータに、このパターン「H,L,L」が入力された場合に、図7(b)に示すように、PROM電源VCC2が立ち上がり、エミュレーションモードEMにする事が可能になる。すなわち、エミュレーションモードEMに切り替わった後は、入力端子12へ供給される入力信号DATAにより、PROM回路300の調整ビットの設定が行われる。

【0096】

図8(a)は、本実施形態のTCXOモジュールの端子構成を示す。本実施形態のTCXOモジュールは、電源端子(VCC1)21と接地端子(GND)22と周波数出力端子(OUT)23と入力端子(VC)24が備わっている(周波数制御機能がある場合)。

【0097】

また、図8(b)は、本実施形態のTCXO制御用ICの端子構成を示す。本実施形態のTCXO制御用ICは、接地端子(GND)25、出力端子(OUT)28、水晶端子1XT29、水晶端子2XTB26、入力端子(VC/DATA)27および電源端子(VCC/CLK)30の6端子で構成することができる。

【0098】

また、図8(c)は、本実施形態のTCXO制御用ICにおける他の端子構成を示す。本実施形態のTCXO制御用ICは、水晶端子1XT31、水晶端子2XTB34、入力端子(書込,DA,Vc)32、電源端子(PROM電源,Vcc,CLK)35、接地端子(GND)33、出力端子(OUT)36の6端子で構成することができる。

【0099】

以上説明したように、本実施形態によれば、端子を共用化することにより、TCXO制御用ICのPAD端子を従来の8パッドから6パッドに減らすことが出来る。これにより、TCXOモジュールとICを接続するパターン配線を減らすことが可能になり、TCXOモジュールの小型化を実現する事ができる。

【0100】

(第2の実施形態)

図9は、本発明の第2の実施形態にかかるTCXO制御用ICの構成を示す。本実施形態のTCXO制御用ICは、モードセレクタ回路100の切り替えを、電源端子(VCC/CLK)11へのCLKパルスのみで行う(Vccは3.5V〜5.5V)事を特徴としている。すなわち、本実施形態では、図2に示す入力端子(VC/DATA/PE)12の信号を入力設定の信号として用いずに、電源端子(VCC/CLK)11の信号だけでモード設定を行うことが可能である。

【0101】

図10は本実施形態における電源端子と入力端子の入力波形である。すなわち、図10(a)は、電源端子11へ供給される電源/クロック信号VCC/CLKの波形を示し、図10(b)は、入力端子12へ供給される入力信号VC/DATA/PEの波形を示す。

【0102】

電源端子11に、信号が入力された場合に、図10(c)に示すように、PROM電源VCC2が立ち上がり、エミュレーションモードEMにする事が可能になる。なお、モード設定区間において、入力信号VC/DATA/PE「L,L,L」が表れているが、本実施形態においては、図9に示したように、入力端子12とモードセレクタ回路100とは接続されていないため、入力信号VC/DATA/PEは、モードセレクタ回路100の動作には関与しない。エミュレーションモードEMに切り替わった後、PROM回路300の調整ビットの設定が行われる。このように、この場合は電源/クロック信号VCC/CLKのみでエミュレーションモードEMにする事が可能である。

【0103】

以上説明したように、上記実施形態にかかる温度補償型水晶発振器によれば、TCXO制御用ICのPAD端子を従来の8パッドから6パッドに減らすことができ、TCXOモジュールとICを接続するパターン配線を減らすことができるため、TCXOモジュールの小型化を実現することができる。

【0104】

また、上記実施形態のTCXOモジュールによれば、モードセレクタ回路100を設けて端子を共用したことによる誤動作を防ぎ、より安定したTCXOモジュールを提供することができる。

【0105】

(第3の実施形態)

上記の実施形態の内容はVCC/CLKの共用化をベースにしており、従来技術においてOUT端子とCLK端子を共用にした場合の問題点、課題を解決し、生産性の向上を図るものである。

【0106】

しかしながら、OUT/CLKの共用も可能である。OUT/CLK共用における従来技術の課題をより正確に説明すると、以下のようになる。VCCの電圧でモードセレクトして、OUT端子よりCLKを入力する構成では、VCC端子とOUT/CLK端子の両方を制御する必要があるため、生産工程が複雑になる。この課題を解決するために、VCCにモードセレクト機能を持たせずに、OUT/CLK端子を共用化することも可能である。すなわち、VCCのレベルを使わずに、OUT/CLK共用も実現可能である。

【0107】

図15,16は、本実施形態にかかるTCXO制御用ICのブロック図を示す。従来は、VCC=3.5VでエミュレーションモードEMにしてから、出力端子(OUT)13よりCLKを入れていたが、本実施形態では、VCCはそのままで、エミュレーションモードEMにするには出力端子(OUT)13からCLKを入れる。なお、第1の実施形態の内容はVCCからCLKを入れるものである。

【0108】

このように、VCC端子11からCLKを入れるのではなく、OUT端子13よりCLKを入れることも可能である。VCCは通常の電源電圧、例えば2.3〜3.3Vに設定し、OUT端子13よりモードセレクタに信号を入力する。モードセレクト信号を入れると、VCC2が立ち上がりエミュレーションモード、あるいはライトモードに切り替わる。基本動作は、VCC端子11からCLKを入れる場合と変わらないが、VCCを一定にして、OUT端子13とVC端子12より同じ動作をさせることが可能である。

【0109】

図17は、本実施形態にかかるモードセレクタ回路100のブロック図である。モードセレクタ回路100は、ICの内部基準電圧VREFを基準とするコンパレータ120を備え、出力端子(OUT/CLK)13からは、コンパレータ120の入力として、例えば、3.5V−5.5VのCLK信号を与える。CLK信号を抵抗180と抵抗181で分圧してコンパレータ120の入力を調整する。すなわち、コンパレータ120は、出力端子(OUT/CLK)13から入力された信号の電圧(CLK信号を抵抗180と抵抗181で分圧したもの)と、ICの内部基準電圧VREFとの比較結果をパルス信号として出力する。これにより、F/F回路110の入力VCKとして、0V−VCCの信号を得る事が出来る。

【0110】

図18は、本実施形態にかかる制御ロジック回路シリアル・インターフェイス200のブロック図である。モードセレクタ回路100において電源電圧VCC2が立ち上がると、制御ロジック回路シリアル・インターフェイス200に電源が供給されエミュレーションモードEMの動作が可能な状態になる。制御ロジック回路シリアル・インターフェイス200の入力クロックに信号VCKを入力し、DATAは入力端子(VC/DATA/PE)12より入力する。これ等のデータを複数のPROMビット分データを送り、PROM回路300にデータを送る。

【0111】

図19は、本実施形態にかかるPROM(1ビット)回路300のブロック図である。制御ロジック回路シリアル・インターフェイス200のF/F回路201からの出力251をPROM回路300に入力する。F/F回路201の信号によりPROMOUTが切換わり発振制御回路400に信号を入力し、周波数を制御する。ここで、所望の周波数に調整し、PROM回路300にデータを入力端子(VC/DATA/PE)12より書き込む。

【0112】

図20は、本実施形態にかかる(エミュレーションモード/リード)モード切替設定方法を説明するための図であり、図20(a)は、OUT/CLK端子13の入力波形、図20(b)は、電源端子11の電圧波形、図20(c)は、モードセレクタ回路100から供給される電源電圧VCC2の電圧波形、図20(d)は、入力端子(VC/DATA/PE)12の入力波形(図15の場合)、図20(e)は、入力端子(VC/DATA/PE)12の入力波形(図16の場合)である。

【0113】

OUT端子13は通常のリードモード時は0V〜1VのクリップドSIN(波形上下のピークが電圧クリップされた信号)で出力する。本実施形態においてOUT端子13よりCLKを入れる場合の入力/出力波形を示したものである。CLK波形は外部電源より3.5V−5.5Vで入力を行い、モードセットを行う。その後、入力波形を外すとエミュレーションモードでの周波数を測定することが可能になる。

【0114】

図21および図22は、本実施形態にかかるOUT端子13の一般的な出力形式を示す。OUT端子13の一般的な出力形式はNMOS出力(M1001、M1002)で構成されている。例えば、M1001のバックゲートがソースと出力端子13に接続されていた場合、OUT端子13をHighにすると、バックゲートードレイン端子の寄生のダイオードでVCCより高い電位を与えることが困難になる。

【0115】

そこで、図21では、M1001のドレイン側にバイポーラトランジスタでバッファすることにより、OUT端子13をHigh(5.5V)にすることが可能になる。これは、OUT端子13の印加電圧を上昇させていったときにQ1004のエミッターベース電圧でバックゲートードレイン端子の寄生のダイオードに電流が流れることを抑えることが出来る。

【0116】

また、図22ではバックゲートをGNDにすることにより、OUT端子13の印加電圧を上昇させたときにバックゲートードレイン端子の寄生のダイオードが出来なくして、5.5Vまで電圧が上がるように出来る。

【0117】

(第4の実施形態)

図25,図26は、本実施形態にかかるTCXO制御用ICのブロック図を示す。第1の実施形態の内容がVCCからCLKを入れるものであったのに対し、本実施形態では、エミュレーションモードEMにするには、入力端子(VC)12からCLKを入れる。

【0118】

このように、VCC端子11からCLKを入れるのではなく、VC端子12よりCLKを入れることも可能である。VCCは、通常の電源電圧、例えば2.3〜3.3Vに設定し、VC端子12よりモードセレクタに信号を入力する。モードセレクト信号を入れると、VCC2が立ち上がりエミュレーションモード、あるいはライトモードに切り替わる。

【0119】

基本動作は、VCC端子11からCLKを入れる場合と変わらないが、VCCを一定にして、OUT端子13とVC端子12より同じ動作をさせることが可能である。

【0120】

図27は、本実施形態にかかるモードセレクタ回路100のブロック図である。モードセレクタ回路100は、ICの内部基準電圧VREFを基準とするコンパレータ120を備え、入力端子(VC/CLK)12からは、コンパレータ120の入力として、例えば、3.5V−5.5VのCLK信号を与える。CLK信号を抵抗180と抵抗181で分圧してコンパレータ120の入力を調整する。

すなわち、コンパレータ120は、入力端子(VC/CLK)12から入力された信号の電圧(CLK信号を抵抗180と抵抗181で分圧したもの)と、ICの内部基準電圧VREFとの比較結果をパルス信号として出力する。

これにより、F/F回路110の入力VCKとして、0V−VCCの信号を得る事が出来る。

【0121】

図28は、本実施形態にかかる制御ロジック回路シリアル・インターフェイス200のブロック図である。モードセレクタ回路100において電源電圧VCC2が立ち上がると、制御ロジック回路シリアル・インターフェイス200に電源が供給されエミュレーションモードEMの動作が可能な状態になる。制御ロジック回路シリアル・インターフェイス200の入力クロックに信号VCKを入力し、DATAは出力端子(OUT/DATA)13より入力する。これ等のデータを複数のPROMビット分データを送り、PROM回路300にデータを送る。

【0122】

図29は、本実施形態にかかるPROM(1ビット)回路300のブロック図である。

制御ロジック回路シリアル・インターフェイス200のF/F回路201からの出力251をPROM回路300に入力する。F/F回路201の信号によりPROMOUTが切換わり発振制御回路400に信号を入力し、周波数を制御する。ここで、所望の周波数に調整し、PROM回路300にデータを入力端子(VC/CLK/PE)12より書き込む。

【0123】

図30は、本実施形態にかかる(エミュレーションモード/リード)モード切替設定方法を説明するための図である。図30(a)は、VC/CLK端子13の入力波形、図30(b)は、電源端子11の電圧波形、図30(c)は、モードセレクタ回路100から供給される電源電圧VCC2の電圧波形、図30(d)は、出力端子(OUT/DATA)13の入力波形(図25の場合)、図30(e)は、出力端子(OUT/DATA)13の入力波形(図26の場合)である。

【0124】

OUT端子13は、通常のリードモード時は0V〜1VのクリップドSIN(波形上下のピークが電圧クリップされた信号)で出力する。本実施形態においてOUT端子13よりDATAを入れる場合の入力/出力波形を示したものである。

DATA波形は外部電源より0V−5.5Vで入力を行い、モードセットを行う。

その後、入力波形を外すとエミュレーションモードでの周波数を測定することが可能になる。

【0125】

OUT端子を5.5VまでDATAとして上げるには、第2の実施形態と同じく図21,22のように構成すると簡単に0V−5.5Vを入力することが可能である。

【0126】

(第5の実施形態)

図31,図32は、本実施形態にかかるTCXO制御用ICのブロック図を示す。第1の実施形態の内容が、VCCからCLKを入れ、入力端子(VC)12からDATAを入れるものであったのに対し、本実施形態では、エミュレーションモードEMにするために、出力端子からDATAを入れるものである。

【0127】

このように、出力端子13よりDATAを入れることも可能である。VCC端子11よりモードセレクタ回路100に信号を入力する。モードセレクト信号を入れると、VCC2が立ち上がりエミュレーションモード、あるいはライトモードに切り替わる。

【0128】

基本動作は、VCC端子11からCLKを入れ、入力端子12よりDATAをいれる場合と同じである。

【0129】

図33は、本実施形態にかかるモードセレクタ回路100のブロック図である。モードセレクタ回路100は、ICの内部基準電圧VREFを基準とするコンパレータ120を備え、電源端子(VCC/CLK)12からは、コンパレータ120の入力として、例えば、3.5V−5.5VのCLK信号を与える。CLK信号を抵抗180と抵抗181で分圧してコンパレータ120の入力を調整する。

すなわち、コンパレータ120は、電源端子(VCC/CLK)12から入力された信号の電圧(CLK信号を抵抗180と抵抗181で分圧したもの)と、ICの内部基準電圧VREFとの比較結果をパルス信号として出力する。

これにより、F/F回路110の入力VCKとして、0V−VCCの信号を得る事が出来る。

【0130】

図34は、本実施形態にかかる制御ロジック回路シリアル・インターフェイス200のブロック図である。モードセレクタ回路100において電源電圧VCC2が立ち上がると、制御ロジック回路シリアル・インターフェイス200に電源が供給されエミュレーションモードEMの動作が可能な状態になる。制御ロジック回路シリアル・インターフェイス200の入力クロックに信号VCKを入力し、DATAは出力端子(OUT/DATA)13より入力する。これ等のデータを複数のPROMビット分データを送り、PROM回路300にデータを送る。

【0131】

図35は、本実施形態にかかるPROM(1ビット)回路300のブロック図である。

制御ロジック回路シリアル・インターフェイス200のF/F回路201からの出力251をPROM回路300に入力する。F/F回路201の信号によりPROMOUTが切換わり発振制御回路400に信号を入力し、周波数を制御する。ここで、所望の周波数に調整し、PROM回路300にデータを入力端子(VC/PE)12より書き込む。

【0132】

図36は、本実施形態にかかる(エミュレーションモード/リード)モード切替設定方法を説明するための図である。図36(a)は、VCC/CLK端子11の入力波形、図36(b)は、モードセレクタ回路100から供給される電源電圧VCC2の電圧波形、図36(c)は、出力端子(OUT/DATA)13の入力波形(図31の場合)、図36(d)は、出力端子(OUT/DATA)13の入力波形(図32の場合)である。

【0133】

OUT端子13は、通常のリードモード時は0V〜1VのクリップドSIN(波形上下のピークが電圧クリップされた信号)で出力する。図36(c)、(d)は、本実施形態においてOUT端子13よりDATAを入れる場合の入力/出力波形を示したものである。

DATA波形は、外部電源より0V−5.5Vで入力を行い、モードセットを行う。

その後、入力波形を外すとエミュレーションモードでの周波数を測定することが可能になる。

【0134】

OUT端子を5.5VまでDATAとして上げるには、第2の実施形態と同じく図21,22のように構成すると簡単に0V−5.5Vを入力することが可能である。

【0135】

(第6の実施形態)

図39,図40は、本実施形態にかかるTCXO制御用ICのブロック図を示す。水晶端子1または水晶端子2(XT1またはXT2)からCLKを入れ、入力端子(VC)12からDATAを入れてエミュレーションモードEMにするものである。

【0136】

このように、水晶端子のいずれかよりCLKを入れることも可能である。水晶端子のいずれかよりモードセレクタ回路100に信号を入力する。モードセレクト信号を入れると、VCC2が立ち上がりエミュレーションモード、あるいはライトモードに切り替わる。

【0137】

基本動作は、VCC端子11からCLKを入れ、入力端子12よりDATAをいれる場合と同じである。

【0138】

図41は、本実施形態にかかるモードセレクタ回路100のブロック図である。モードセレクタ回路100は、ICの内部基準電圧VREFを基準とするコンパレータ120を備え、電源端子(水晶端子1または2/CLK)からは、コンパレータ120の入力として、例えば、3.5V−5.5VのCLK信号を与える。CLK信号を抵抗180と抵抗181で分圧してコンパレータ120の入力を調整する。

すなわち、コンパレータ120は、水晶端子(XT1またはXT2/CLK)から入力された信号の電圧(CLK信号を抵抗180と抵抗181で分圧したもの)と、ICの内部基準電圧VREFとの比較結果をパルス信号として出力する。

これにより、F/F回路110の入力VCKとして、0V−VCCの信号を得る事が出来る。

【0139】

図42は本実施形態にかかる制御ロジック回路シリアル・インターフェイス200のブロック図である。モードセレクタ回路100において電源電圧VCC2が立ち上がると、制御ロジック回路シリアル・インターフェイス200に電源が供給されエミュレーションモードEMの動作が可能な状態になる。制御ロジック回路シリアル・インターフェイス200の入力クロックに信号VCKを入力し、DATAは入力端子(VC/DATA)より入力する。これ等のデータを複数のPROMビット分データを送り、PROM回路300にデータを送る。

【0140】

図43は、本実施形態にかかるPROM(1ビット)回路300のブロック図である。

制御ロジック回路シリアル・インターフェイス200のF/F回路201からの出力251をPROM回路300に入力する。F/F回路201の信号によりPROMOUTが切換わり発振制御回路400に信号を入力し、周波数を制御する。ここで、所望の周波数に調整し、PROM回路300にデータを入力端子(VC/PE)12より書き込む。

【0141】

図44は、本実施形態にかかる(エミュレーションモード/リード)モード切替設定方法を説明するための図である。図44(a)は、水晶端子XT1あるいはXT2/CLK端子の入力波形、図44(b)は、モードセレクタ回路100から供給される電源電圧VCC2の電圧波形、図44(c)は、入力端子(VC/DATA)の入力波形(図39の場合)、図44(d)は、出力端子(OUT/DATA)13の入力波形(図40の場合)である。

【0142】

水晶端子1,2は、通常のリードモード時は0V〜2VのSIN(波形上下のピークが電圧クリップされた信号)に近い波形で出力する。本実施形態において水晶端子1あるいは2よりCLKを入れる場合は注意が必要である。

水晶端子1,2は通常ハイ・インピーダンスで動作しており、外部より電圧を印加することを従来は推奨していなかった。

しかし本発明では、水晶端子が通常の動作領域で無い例えば3.5V〜5.5Vで入力しモードセットを行う。

その後、水晶端子1あるいは2を外すとエミュレーションモードでの周波数を測定することが可能になる。

【0143】

また、本説明では1タイムPROMを例としたためリードモード/エミュレーションモード/ライトモードの切り替えを説明した。しかし、ANYタイムPROM(複数回書き込み可能なPROM)で、特にエミュレーションモードが無くリードモード/ライトモードだけの場合も本実施形態を使用し端子の共用化が可能である。

【0144】

また、本説明では1タイムPROMを例としたためリードモード/エミュレーションモード/ライトモードの切り替えを説明した。しかし、ANYタイムPROM(複数書き込み可能なPROM)で、特にエミュレーションモードが無くリードモード/ライトモードだけの場合も本実施形態を使用し端子の共用化が可能である。以下、1タイムPROMおよびANYタイムPROMのそれぞれを使用したTCXOの調整時のフローについて説明する。

【0145】

図37は1タイムPROMを使用したTCXOの調整時のフローチャートである。

1タイムであるため書き込みは当然1度しか出来ない。従って、ステップ1でエミュレーションモードでデータのみを入力し、ステップ2で周波数測定を行う。これを各パラメータ、各温度において周波数データを繰り返し取得する。

前記ステップ2で取得した周波数をステップ3で分析し、もっとも周波数の安定度の高いROM設定を計算させる。

前記ステップ3で算出した最適パラメータを、ステップ4でライトモードに設定し、ステップ5でPROMに書き込む。

最後にステップ6でリードモードにて周波数が温度補償されていることを確認する。

【0146】

図38はANYタイムPROMを使用したTCXOの調整時のフローチャートである。ANYタイムPROMの場合は、その特徴を生かして、エミュレーションモード回路を省略し、その都度書き込みを行いデータを書き込み周波数データを取ることも可能である。

また、ANYタイムPROMは、非常に厳しい小チップサイズが要求される。そのため、エミュレーション用回路を省略しサイズの低減を行う代わりに、周波数データを取る度にROMに書き込む必要が有る。このため、書き込みに時間がかかりデータ取りに時間を要す場合がある。

【0147】

ステップ11でライトモードにしてデータを入力する。その後ステップ12で書き込みを実施し、ステップ13で周波数測を行う。これを各パラメータ、各温度において周波数データを繰り返し取得する。ここまでのステップは、後述するように、1タイムPROMを使用したTCXOの調整時のエミュレーションモードと同じである。

前記ステップ13で取得した周波数をステップ14で分析し、もっとも周波数の安定度の高いROM設定を計算させる。

前記ステップ14で算出した最適パラメータをステップ15でライトモードに設定し、ステップ16でPROMに書き込む。最後にステップ17でリードモードにて周波数が温度補償されていることを確認する。

ステップ13〜17の工程はPROMに関係なく同じである。

【0148】

図38のステップ11〜ステップ13の処理は図37のステップ1〜ステップ2と目的は同じである。すなわち、これらの処理は、最終書き込みを行うデータを決定するための目的の作業であり、共にエミュレーションモードになると言える。

以上のようにPROMの種類により、端子共用の構成、基本動作が変わることは無い。また、フローチャートも変わることは無い。

【0149】

上記説明では、CLK機能の共用化とDATA機能の共用化を各端子に行う手法を提案しているが、例えば、CLK機能とDATA機能を共用する端子を逆にしても同様の効果を得ることが出来る。

【0150】

実施例では、CLK機能の共用化とDATA機能の共用化を各端子に行う手法を提案しているが、例えば、CLK機能とDATA機能を共用する端子を逆にしても同様の効果を得ることが出来る。

【0151】

また、上記実施例の説明では、温度補償をする場合に、EM/WM/RMが必要である旨や、それに準じた動作が出来る場合を記載している。しかし、温度補償をする場合に限らず、水晶発振器の周波数の調整や、入力端子の機能の変更を行う場合に、PROMが必要になる場合がある。

したがって、本発明の端子共用が有効になる。本発明が入力端子の機能変更にも有効である理由を以下に説明する。

【0152】

本発明は、6端子という制約の中で端子機能を共用する技術に関する。ここで6端子とは電源端子、接地端子、出力端子、入力端子、水晶端子1、水晶端子2である。

近年、入力端子には、様々な機能を持たせて付加価値を付けている。例えば、スイープモード切替入力端子、スタンバイモード切替入力端子、温度センサ出力などが考えられる。これらの切り替えについても、本発明のように端子を共用化してDATA、CLKを入力し、少ない端子で容易にPROMに書き込むことにより、切り替えを行うことが可能になる。

【産業上の利用可能性】

【0153】

本発明は、周波数調整のための回路接続の切替を要することなく、端子を共用化することができる効果を有し、TCXO等に有用である。

【図面の簡単な説明】

【0154】

【図1】本発明の第1の実施形態にかかるTCXO用ICのブロック図(1)

【図2】本発明の第1の実施形態にかかるモードセレクタ回路のブロック図

【図3】本発明の第1の実施形態にかかる制御ロジック部のブロック図

【図4】本発明の第1の実施形態にかかるPROM回路部のブロック図

【図5】本発明の第1の実施形態にかかる周波数制御回路の概要図

【図6】本発明の第1の実施形態にかかる発振回路のブロック図

【図7】本発明の第1の実施形態にかかる入力波形の一例を示す図

【図8】本発明の第1の実施形態にかかるTCXOモジュールおよびTCXO制御用ICの端子構成例を示す図

【図9】本発明の第2の実施形態にかかるTCXO用ICのブロック図(2)

【図10】本発明の第2の実施形態にかかる入力波形の一例を示す図

【図11】従来のTCXO用ICの端子構成例を示す図

【図12】従来のTCXO用ICのブロック図

【図13】本発明の第1の実施形態にかかるTCXO用ICのブロック図(3)

【図14】本発明の第1の実施形態にかかる内部クロック発生回路のブロック図

【図15】本発明の第3の実施形態にかかるTCXO用ICのブロック図(4)

【図16】本発明の第3の実施形態にかかるTCXO用ICのブロック図(5)

【図17】本発明の第3の実施形態にかかるモードセレクタ回路のブロック図

【図18】本発明の第3の実施形態にかかる制御ロジック部のブロック図

【図19】本発明の第3の実施形態にかかるPROM回路部のブロック図

【図20】本発明の第3の実施形態にかかる入力波形の一例を示す図

【図21】本発明の実施形態にかかるOUT端子13の一般的な出力形式を示す図

【図22】本発明の実施形態にかかるOUT端子13の一般的な出力形式を示す図

【図23】従来の温度補償型水晶発振器の概略構成を示す図

【図24】従来の温度補償型水晶発振器における調整データ入力波形を示す図

【図25】本発明の第4の実施形態にかかるTCXO用ICのブロック図(6)

【図26】本発明の第4の実施形態にかかるTCXO用ICのブロック図(7)

【図27】本発明の第4の実施形態にかかるモードセレクタ回路のブロック図

【図28】本発明の第4の実施形態にかかる制御ロジック部のブロック図

【図29】本発明の第4の実施形態にかかるPROM回路部のブロック図

【図30】本発明の第4の実施形態にかかる入力波形の一例を示す図

【図31】本発明の第5の実施形態にかかるTCXO用ICのブロック図(8)

【図32】本発明の第5の実施形態にかかるTCXO用ICのブロック図(9)

【図33】本発明の第5の実施形態にかかるモードセレクタ回路のブロック図

【図34】本発明の第5の実施形態にかかる制御ロジック部のブロック図

【図35】本発明の第5の実施形態にかかるPROM回路部のブロック図

【図36】本発明の第5の実施形態にかかる入力波形の一例を示す図

【図37】1タイムROMの場合の調整フロー例を示す図

【図38】ANYタイムROMの場合の調整フロー例を示す図

【図39】本発明の第6の実施形態にかかるTCXO用ICのブロック図(10)

【図40】本発明の第6の実施形態にかかるTCXO用ICのブロック図(11)

【図41】本発明の第6の実施形態にかかるモードセレクタ回路のブロック図

【図42】本発明の第6の実施形態にかかる制御ロジック部のブロック図

【図43】本発明の第6の実施形態にかかるPROM回路部のブロック図

【図44】本発明の第6の実施形態にかかる入力波形の一例を示す図

【符号の説明】

【0155】

11,21,30,35 電源端子

12,24,27,32 入力端子

13,23,28,36 出力端子

14,22,25,33 接地端子

26,34 水晶端子2

29,31 水晶端子1

100 モードセレクタ回路

101 内部クロック発生回路

110,111,112,201,202,203,204,205,206 F/F回路

120 コンパレータ

121,122,520 インバータ

123 NAND回路

150 トランジスタM1

200 制御ロジック回路シリアル・インターフェイス

300 PROM回路

350 ダイオード

400 発振制御回路

411 定電圧回路

412 温度センサ

413 3次関数生成回路

414 1次関数生成回路

415 0次関数生成回路

416 変極点調整回路

500 発振回路

550 水晶振動子

【特許請求の範囲】

【請求項1】

電源電圧およびクロック信号が供給される電源端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、

前記電源電圧に前記クロック信号が重畳されて入力される第1の信号と、所定の基準電圧との比較結果をクロック信号として出力する内部クロック発生回路を備える温度補償型水晶発振器制御用IC。

【請求項2】

電源電圧およびクロック信号が供給される電源端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、

前記電源端子から前記電源電圧に前記クロック信号が重畳された第1の信号が入力され、前記入力端子から所定のパターンを有する第2の信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える温度補償型水晶発振器制御用IC。

【請求項3】

請求項2記載の温度補償型水晶発振器制御用ICであって、

前記第1の信号のレベルが、通常動作時の電圧より高い電圧である温度補償型水晶発振器制御用IC。

【請求項4】

請求項2記載の温度補償型水晶発振器制御用ICであって、

前記第1のモードセレクタ回路は、前記第1の信号と所定の基準電圧との比較結果をパルス信号として出力するコンパレータと、

前記コンパレータにより出力されたパルス信号に応じて、前記第2の信号をシフトする所定段の第1のフリップフロップ回路と、

前記第1のフリップフロップ回路の出力信号に応じて、前記電源電圧を制御するトランジスタと、を有する温度補償型水晶発振器制御用IC。

【請求項5】

請求項4記載の温度補償型水晶発振器制御用ICであって、

前記第1のフリップフロップ回路の各段の出力が前記所定のパターンに一致した場合に、前記トランジスタを制御する論理回路を備える温度補償型水晶発振器制御用IC。

【請求項6】

請求項2記載の温度補償型水晶発振器制御用ICであって、

前記エミュレーションモードあるいはライトモードにおいて、前記第1のモードセレクタ回路、又は信号から前記電源電圧が制御されることにより動作し、前記PROM回路に書き込むデータを設定する制御ロジック回路を備える温度補償型水晶発振器制御用IC。

【請求項7】

請求項6記載の温度補償型水晶発振器制御用ICであって、

前記制御ロジック回路は、前記クロック信号に応じて、前記第2の信号をシフトする所定段の第2のフリップフロップ回路を備える温度補償型水晶発振器制御用IC。

【請求項8】

請求項2記載の温度補償型水晶発振器制御用ICであって、

前記PROM回路は、前記入力端子に直列に接続され、書き込みデータ信号の振幅を制限する直列接続された複数のダイオードを有する温度補償型水晶発振器制御用IC。

【請求項9】

電源電圧およびクロック信号が供給される電源端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、

前記電源端子から前記電源電圧に前記クロック信号が重畳された信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替えるモードセレクタ回路を備える温度補償型水晶発振器制御用IC。

【請求項10】

請求項2記載の温度補償型水晶発振器制御用ICであって、

前記第1の信号が供給される第1の端子、および前記第2の信号が供給される第2の端子を含む6個の端子を有する温度補償型水晶発振器制御用IC。

【請求項11】

請求項9記載の温度補償型水晶発振器制御用ICであって、

前記電源端子から前記電源電圧に前記クロック信号が重畳された信号が供給される端子を含む6個の端子を有する温度補償型水晶発振器制御用IC。

【請求項12】

発振器出力およびクロック信号が供給される出力端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、

前記出力端子から前記クロック信号が重畳された第1の信号が入力され、前記入力端子から所定のパターンを有する第2の信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える温度補償型水晶発振器制御用IC。

【請求項13】

発振器出力およびクロック信号が供給される出力端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、

前記出力端子から前記クロック信号が重畳された信号が入力された場合に、前記エミュレーションモード、あるいはライトモードに切り替えるモードセレクタ回路を備える温度補償型水晶発振器制御用IC。

【請求項14】

発振器の制御信号が入力される入力端子およびクロック信号が供給される前記入力端子と、発振器の出力端子と、

水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、

前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、

前記PROM回路に書き込むデータを決定するエミュレーションモードと、

前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードと

を有する温度補償型水晶発振器制御用ICであって、

前記入力端子から前記クロック信号が重畳された第1の信号が入力され、かつ、前記出力端子から所定のパターンを有する第2の信号が入力された場合に、

前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える温度補償型水晶発振器制御用IC。

【請求項15】

発振器の制御信号が入力される入力端子およびクロック信号が供給される前記入力端子と、発振器の出力端子と、

水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、

前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、

前記PROM回路に書き込むデータを決定するエミュレーションモードと、

前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードと

を有する温度補償型水晶発振器制御用ICであって、

前記入力端子から前記クロック信号が重畳された信号が入力された場合に、

前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を

備える温度補償型水晶発振器制御用IC。

【請求項16】

電源電圧およびクロック信号が供給される電源端子と、発振器の出力端子と、

水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、

前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、

前記PROM回路に書き込むデータを決定するエミュレーションモードと、

前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードと

を有する温度補償型水晶発振器制御用ICであって、

前記電源端子から前記クロック信号が重畳された第1の信号が入力され、かつ、前記出力端子から所定のパターンを有する第2の信号が入力された場合に、

前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える温度補償型水晶発振器制御用IC。

【請求項17】

電源電圧およびクロック信号が供給される電源端子と、発振器の出力端子と、

水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、

前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、

前記PROM回路に書き込むデータを決定するエミュレーションモードと、

前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードと

を有する温度補償型水晶発振器制御用ICであって、

前記電源端子から前記クロック信号が重畳された信号が入力された場合に、

前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える温度補償型水晶発振器制御用IC。

【請求項18】

水晶振動子が接続される水晶端子およびクロック信号が供給される水晶端子と、発振器の入力端子と、

水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、

前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、

前記PROM回路に書き込むデータを決定するエミュレーションモードと、

前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードと

を有する温度補償型水晶発振器制御用ICであって、

前記水晶端子から前記クロック信号が重畳された第1の信号が入力され、かつ、

前記入力端子から所定のパターンを有する第2の信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える温度補償型水晶発振器制御用IC。

【請求項19】

水晶振動子が接続される水晶端子およびクロック信号が供給される水晶端子と、発振器の入力端子と、

水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、

前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、

前記PROM回路に書き込むデータを決定するエミュレーションモードと、

前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードと

を有する温度補償型水晶発振器制御用ICであって、

前記水晶端子から前記クロック信号が重畳された信号が入力された場合に、

前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える温度補償型水晶発振器制御用IC。

【請求項1】

電源電圧およびクロック信号が供給される電源端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、

前記電源電圧に前記クロック信号が重畳されて入力される第1の信号と、所定の基準電圧との比較結果をクロック信号として出力する内部クロック発生回路を備える温度補償型水晶発振器制御用IC。

【請求項2】

電源電圧およびクロック信号が供給される電源端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、

前記電源端子から前記電源電圧に前記クロック信号が重畳された第1の信号が入力され、前記入力端子から所定のパターンを有する第2の信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える温度補償型水晶発振器制御用IC。

【請求項3】

請求項2記載の温度補償型水晶発振器制御用ICであって、

前記第1の信号のレベルが、通常動作時の電圧より高い電圧である温度補償型水晶発振器制御用IC。

【請求項4】

請求項2記載の温度補償型水晶発振器制御用ICであって、

前記第1のモードセレクタ回路は、前記第1の信号と所定の基準電圧との比較結果をパルス信号として出力するコンパレータと、

前記コンパレータにより出力されたパルス信号に応じて、前記第2の信号をシフトする所定段の第1のフリップフロップ回路と、

前記第1のフリップフロップ回路の出力信号に応じて、前記電源電圧を制御するトランジスタと、を有する温度補償型水晶発振器制御用IC。

【請求項5】

請求項4記載の温度補償型水晶発振器制御用ICであって、

前記第1のフリップフロップ回路の各段の出力が前記所定のパターンに一致した場合に、前記トランジスタを制御する論理回路を備える温度補償型水晶発振器制御用IC。

【請求項6】

請求項2記載の温度補償型水晶発振器制御用ICであって、

前記エミュレーションモードあるいはライトモードにおいて、前記第1のモードセレクタ回路、又は信号から前記電源電圧が制御されることにより動作し、前記PROM回路に書き込むデータを設定する制御ロジック回路を備える温度補償型水晶発振器制御用IC。

【請求項7】

請求項6記載の温度補償型水晶発振器制御用ICであって、

前記制御ロジック回路は、前記クロック信号に応じて、前記第2の信号をシフトする所定段の第2のフリップフロップ回路を備える温度補償型水晶発振器制御用IC。

【請求項8】

請求項2記載の温度補償型水晶発振器制御用ICであって、

前記PROM回路は、前記入力端子に直列に接続され、書き込みデータ信号の振幅を制限する直列接続された複数のダイオードを有する温度補償型水晶発振器制御用IC。

【請求項9】

電源電圧およびクロック信号が供給される電源端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、

前記電源端子から前記電源電圧に前記クロック信号が重畳された信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替えるモードセレクタ回路を備える温度補償型水晶発振器制御用IC。

【請求項10】

請求項2記載の温度補償型水晶発振器制御用ICであって、

前記第1の信号が供給される第1の端子、および前記第2の信号が供給される第2の端子を含む6個の端子を有する温度補償型水晶発振器制御用IC。

【請求項11】

請求項9記載の温度補償型水晶発振器制御用ICであって、

前記電源端子から前記電源電圧に前記クロック信号が重畳された信号が供給される端子を含む6個の端子を有する温度補償型水晶発振器制御用IC。

【請求項12】

発振器出力およびクロック信号が供給される出力端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、

前記出力端子から前記クロック信号が重畳された第1の信号が入力され、前記入力端子から所定のパターンを有する第2の信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える温度補償型水晶発振器制御用IC。

【請求項13】

発振器出力およびクロック信号が供給される出力端子と、所定の制御信号が供給される入力端子と、水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、前記PROM回路に書き込むデータを決定するエミュレーションモードと、前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードとを有する温度補償型水晶発振器制御用ICであって、

前記出力端子から前記クロック信号が重畳された信号が入力された場合に、前記エミュレーションモード、あるいはライトモードに切り替えるモードセレクタ回路を備える温度補償型水晶発振器制御用IC。

【請求項14】

発振器の制御信号が入力される入力端子およびクロック信号が供給される前記入力端子と、発振器の出力端子と、

水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、

前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、

前記PROM回路に書き込むデータを決定するエミュレーションモードと、

前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードと

を有する温度補償型水晶発振器制御用ICであって、

前記入力端子から前記クロック信号が重畳された第1の信号が入力され、かつ、前記出力端子から所定のパターンを有する第2の信号が入力された場合に、

前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える温度補償型水晶発振器制御用IC。

【請求項15】

発振器の制御信号が入力される入力端子およびクロック信号が供給される前記入力端子と、発振器の出力端子と、

水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、

前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、

前記PROM回路に書き込むデータを決定するエミュレーションモードと、

前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードと

を有する温度補償型水晶発振器制御用ICであって、

前記入力端子から前記クロック信号が重畳された信号が入力された場合に、

前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を

備える温度補償型水晶発振器制御用IC。

【請求項16】

電源電圧およびクロック信号が供給される電源端子と、発振器の出力端子と、

水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、

前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、

前記PROM回路に書き込むデータを決定するエミュレーションモードと、

前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードと

を有する温度補償型水晶発振器制御用ICであって、

前記電源端子から前記クロック信号が重畳された第1の信号が入力され、かつ、前記出力端子から所定のパターンを有する第2の信号が入力された場合に、

前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える温度補償型水晶発振器制御用IC。

【請求項17】

電源電圧およびクロック信号が供給される電源端子と、発振器の出力端子と、

水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、

前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、

前記PROM回路に書き込むデータを決定するエミュレーションモードと、

前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードと

を有する温度補償型水晶発振器制御用ICであって、

前記電源端子から前記クロック信号が重畳された信号が入力された場合に、

前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える温度補償型水晶発振器制御用IC。

【請求項18】

水晶振動子が接続される水晶端子およびクロック信号が供給される水晶端子と、発振器の入力端子と、

水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、

前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、

前記PROM回路に書き込むデータを決定するエミュレーションモードと、

前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードと

を有する温度補償型水晶発振器制御用ICであって、

前記水晶端子から前記クロック信号が重畳された第1の信号が入力され、かつ、

前記入力端子から所定のパターンを有する第2の信号が入力された場合に、前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える温度補償型水晶発振器制御用IC。

【請求項19】

水晶振動子が接続される水晶端子およびクロック信号が供給される水晶端子と、発振器の入力端子と、

水晶発振器の温度特性をキャンセルする調整データが書き込まれるPROM回路とを備え、

前記PROM回路に書き込まれたデータを読み出して前記水晶発振器の周波数を制御するリードモードと、

前記PROM回路に書き込むデータを決定するエミュレーションモードと、

前記エミュレーションモードで決定したデータを前記PROM回路に書き込むライトモードと

を有する温度補償型水晶発振器制御用ICであって、

前記水晶端子から前記クロック信号が重畳された信号が入力された場合に、

前記エミュレーションモードあるいはライトモードに切り替える第1のモードセレクタ回路を備える温度補償型水晶発振器制御用IC。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

【図42】

【図43】

【図44】

【公開番号】特開2008−289139(P2008−289139A)

【公開日】平成20年11月27日(2008.11.27)

【国際特許分類】

【出願番号】特願2008−108302(P2008−108302)

【出願日】平成20年4月17日(2008.4.17)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成20年11月27日(2008.11.27)

【国際特許分類】

【出願日】平成20年4月17日(2008.4.17)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]