演算回路及び演算装置

【課題】3つ以上の値の条件分岐処理を要する比較演算を高速に行うことができる演算回路及び演算装置を提供すること。

【解決手段】本発明にかかる演算回路100は、加減算器CAL11〜CAL13、セレクタSEL11〜SEL13及び判定器40を有する。加減算器CAL11〜CAL13は、入力するデータD0〜D2に対して演算を行い、演算結果に基づいて生成した符号フラグF1〜F3出力する。セレクタSEL11〜SELは、加減算器CAL11〜CAL13に入力するデータD0〜D2のいずれかを選択する。判定器40は、符号フラグF1〜F3が入力し、セレクタSEL11〜SEL13のそれぞれの選択動作を制御する。

【解決手段】本発明にかかる演算回路100は、加減算器CAL11〜CAL13、セレクタSEL11〜SEL13及び判定器40を有する。加減算器CAL11〜CAL13は、入力するデータD0〜D2に対して演算を行い、演算結果に基づいて生成した符号フラグF1〜F3出力する。セレクタSEL11〜SELは、加減算器CAL11〜CAL13に入力するデータD0〜D2のいずれかを選択する。判定器40は、符号フラグF1〜F3が入力し、セレクタSEL11〜SEL13のそれぞれの選択動作を制御する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は演算回路及び演算装置に関し、特に並列演算処理を行う演算回路及び演算装置に関する。

【背景技術】

【0002】

一般に、画像を構成する画素の色情報を表現する手段として、色空間が用いられる。ディスプレイなどに画像を表示する場合には、赤(Red)、緑(Green)及び青(Blue)による加法混色を表現するRGB方式が広く用いられている。一方、コンピューター上でイラストなどを描画するために描画色を選ぶ場合などでは、ユーザーである人間の感覚に親和性があるとの理由から、HSV方式が用いられることが多い。HSV方式では、色相(Hue)、彩度(Saturation value)及び明度(Value)の3要素を用いて色情報を表現する。

【0003】

RGB方式で表現された色情報(以下、RGB色空間)とHSV方式で表現された色情報(以下、HSV色空間)とを取り扱うには、2つの方式間の変換作業が必要となる。この変換作業は、画像処理プロセッサなどにより行われる。画像処理プロセッサのような一般的な命令セットプロセッサにおいては、2入力1出力命令が多く用いられている。また、演算性能を高めるために、VLIW(Very Long Instruction Word:超長命令語)構成の命令語を利用するプロセッサも提案されている。

【0004】

RGB色空間からHSV色空間への変換を行う場合、色相H、彩度S及び明度Vは、以下のように表されることが知られている。なお、以下では、赤(R)、緑(G)及び青(B)の最小量を0、最大量を1とする。

【0005】

色相Hは、R、G及びBのいずれの値が最大であるかによって、算出式が異なる。まず、R、G及びBのうち、Rの値が最大である場合には、色相Hは以下の式(1)で表される。但し、MAXは最大値であるRの値を示す。また、MINは、R、G及びBの最小の値、すなわちG及びBの小さい方の値を示す。

【数1】

【0006】

R、G及びBのうち、Gの値が最大である場合には、色相Hは以下の式(2)で表される。但し、MAXは最大値であるGの値を示す。また、MINは、R、G及びBの最小の値、すなわちR及びBの小さい方の値を示す。

【数2】

【0007】

R、G及びBのうち、Bの値が最大である場合には、色相Hは以下の式(3)で表される。但し、MAXは最大値であるBの値を示す。また、MINは、R、G及びBの最小の値、すなわちR及びGの小さい方の値を示す。

【数3】

【0008】

彩度Sは、以下の式(4)で表される。

【数4】

【0009】

彩度Vは、以下の式(5)で表される。

【数5】

【0010】

式(1)〜(5)に示すように、RGB色空間からHSV色空間への変換作業では、色相Hを計算する際にR、G及びBの3つの値を比較する条件分岐や、R、G及びBの最大値MAX及び最小値MINを求める作業が必要である。また、最大値MAX以外の2つの値の差分(式(1)〜(3)の右辺第1項の分数部の分子)を求める必要もある。

【0011】

このような条件分岐や最大値及び最小値を算出するための演算プロセッサとして、例えばVLIWプロセッサが知られている。他にも、様々なプロセッサが提案されている。

【0012】

例えば、複数のプロセッサエレメントによる並列処理を行うことにより、条件分岐を伴う処理を高速に行う手法が提案されている(特許文献1)。この手法では、分岐条件に応じて、選択器を用いてプロセッサエレメントの出力を選択することにより、最大値や最小値の算出などの条件分岐を伴う処理を実現している。

【0013】

また、多くの命令サイクルにおいて、レジスタファイルの読み取りポートを無駄にしないため、多重化機能ユニット(プロセッサ)に対する命令を2以上の発行スロットに与える手法が提案されている(特許文献2)。これにより、多重化機能ユニットが用いられないサイクル中でも、他の機能ユニットが発行スロットを利用することができ、読み取りポートを効率的に利用することが可能となる。

【0014】

さらに、演算処理によってアクセスすべきアドレスが変わる場合(すなわち、分岐処理)に対応可能な構成(特許文献3)や、比較対象データ内の最大値又は最小値を有するプロセッサを効率的かつ高速に検出できる手法(特許文献4)が提案されている。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開2004−62401号公報

【特許文献2】特表2002−527812号公報

【特許文献3】特開2010−97356号公報

【特許文献4】特開2000−163384号公報

【発明の概要】

【発明が解決しようとする課題】

【0016】

ところが、発明者は、上述の手法には以下の問題点があることを見出した。通常、RGB色空間からHSV色空間への変換処理では、R、G及びBの3つの値の最大値、最小値及び最大値を除く2数の差分を計算する必要がある。例えば、3つの値r1〜r3の最大値を計算するには、以下の命令で示すように、2サイクルを要する。

第1サイクル max r1, r2, r4

第2サイクル max r4, r3, r4

第1サイクルでは、2つの値r1及びr2のうちの最大値を、値r4に格納する。第2サイクルでは、2つの値r3及びr4のうちの最大値を、値r4に格納する。つまり、第1のサイクルを実行した後に、値r4を一時的にレジスタファイルに格納し、第2のサイクルで格納した値r4を参照することとなる。これは、最小値を計算する場合も同様である。また、式(1)〜(3)による計算を行うためには、R、G及びBの最大値が既知でなければいけないため、前もって最大値を算出しなければならない。

【0017】

換言すれば、上述の手法では、3つ以上の値の大小関係を判定するには、2つの値の比較処理を繰り返して行う必要があり、比較処理の都度、比較結果をレジスタファイルなどの記憶手段に格納しなければならない。つまり、通常の手法では、3つ以上の値の比較演算を行うには複数のサイクルが必要であり、演算処理を高速化する上で妨げとなる。当然に、R、G及びBの3つの値の比較演算を要するRGB色空間からHSV色空間への変換処理の高速化も妨げられる。

【課題を解決するための手段】

【0018】

本発明の一態様である演算回路は、入力するデータに対して演算を行い、前記演算結果に基づいて生成したフラグ情報を出力する複数の演算器と、前記複数の演算器に入力する前記データのいずれかを選択する複数の選択回路と、前記複数の演算器からの前記フラグ情報が入力し、前記複数の選択回路のそれぞれの選択動作を制御する判定器と、を備えるものである。この演算回路では、演算回路に入力するデータの大小関係に基づいて選択回路の選択動作を制御し、選択回路に最大値、最小値及び3つの最大値以外の値の差分を選択させることができる。これにより、演算の途中経過においてデータをレジスタに格納することなく、単一のサイクルで最大値、最小値及び3つの最大値以外の値の差分を算出することができる。

【発明の効果】

【0019】

本発明によれば、3つ以上の値の条件分岐処理を要する比較演算を高速に行うことができる演算回路及び演算装置を提供することができる。

【図面の簡単な説明】

【0020】

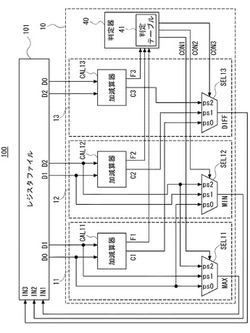

【図1】実施の形態1にかかる演算装置100の構成を模式的に示すブロック図である。

【図2】判定器40に格納された判定テーブル41を示す図である。

【図3】外部から判定テーブル41を設定する場合の演算装置100の構成を模式的に示すブロック図である。

【図4】判定テーブル41の設定値を表示した図である。

【図5】実施の形態1にかかる判定情報設定命令SETの値valの構成例を示す図である。

【図6】判定情報設定命令SETの値valと判定テーブル41の設定値との関係を示す図である。

【図7】実施の形態2にかかる演算装置200の構成を模式的に示すブロック図である。

【図8】判定器40に格納されたソート処理時の判定テーブル42を示す図である。

【図9】外部から判定テーブル42を設定する場合の演算装置200の構成を模式的に示すブロック図である。

【図10】実施の形態2にかかる判定情報設定命令SETの値valの構成例を示す図である。

【図11】実施の形態3にかかる演算装置300の構成を模式的に示すブロック図である。

【図12】判定器43に格納された判定テーブル44を示す図である。

【発明を実施するための形態】

【0021】

以下、図面を参照して本発明の実施の形態について説明する。各図面においては、同一要素には同一の符号が付されており、必要に応じて重複説明は省略される。

【0022】

実施の形態1

まず、実施の形態1にかかる演算装置100について説明する。図1は、実施の形態1にかかる演算装置100の構成を模式的に示すブロック図である。演算装置100は、レジスタファイル101及び演算回路10を有する。

【0023】

レジスタファイル101は、演算回路10の演算の用に供するデータや、演算回路10による演算により算出されたデータが格納される。レジスタファイル101には、図1に示すように、データが入力するポートIN1〜IN3が設けられる。また、レジスタファイル101は、演算回路10にデータD0〜D2を出力する。なお、データD0〜D2は、それぞれ第1〜第3のデータに対応する。レジスタファイル101は、この他にもポートや出力するデータを有する場合が有るが、いずれのポートを使用するか、いずれのデータを出力するかは、例えば外部の制御回路(不図示)からの命令により指定することが可能である。

【0024】

演算回路10は、複数のスロット11〜13及び判定器40を有する。スロット11〜13は、それぞれ加減算器CAL11〜CAL13及びセレクタSEL11〜SEL13を有する。加減算器は演算器の一例であり、加減算器CAL11〜CAL13は、それぞれ第1〜第3の演算器に対応する。セレクタSEL11〜SEL13は、3入力1出力のセレクタである。セレクタは、選択回路の一例であり、セレクタSEL11〜SEL13は、それぞれ第1〜第3の選択回路に対応する。

【0025】

スロット11では、加減算器CAL11に、レジスタファイル101からデータD0及びD1が入力する。そして、加減算器CAL11は、セレクタSEL13に演算結果C1を出力する。また、加減算器CAL11は、判定器40に符号フラグF1を出力する。セレクタSEL11の入力ポートps0〜ps2には、レジスタファイル101からデータD0〜D2がそれぞれ入力する。そして、セレクタSEL11は、判定器40からの制御信号CON1に基づき、レジスタファイル101のポートIN1に、データD0〜D2のいずれかを最大値MAXとして出力する。

【0026】

スロット12では、加減算器CAL12に、レジスタファイル101からデータD1及びD2が入力する。そして、加減算器CAL12は、セレクタSEL13に演算結果C2を出力する。また、加減算器CAL11は、判定器40に符号フラグF2を出力する。セレクタSEL12の入力ポートps0〜ps2には、レジスタファイル101からデータD0〜D2がそれぞれ入力する。そして、セレクタSEL12は、判定器40からの制御信号CON2に基づき、レジスタファイル101のポートIN2に、データD0〜D2のいずれかを最小値MINとして出力する。

【0027】

スロット13では、加減算器CAL13に、レジスタファイル101からデータD2及びD0が入力する。そして、加減算器CAL13は、セレクタSEL13に演算結果C3を出力する。また、加減算器CAL13は、判定器40に符号フラグF3を出力する。セレクタSEL13の入力ポートps0〜ps2には、加減算器CAL11〜CAL13の演算結果C1〜C3がそれぞれ入力する。そして、セレクタSEL13は、判定器40からの制御信号CON3に基づき、レジスタファイル101のポートIN3に、演算結果C1〜C3のいずれかを差分DIFFとして出力する。

【0028】

なお、符号フラグは、加減算器の演算結果に応じて出力されるフラグ情報であり、符号フラグF1〜F3は、それぞれ符号フラグに対応する。

【0029】

判定器40は、符号フラグF1〜F3に基づいて、格納されている判定テーブル41を参照し、セレクタSEL11〜SEL13に制御信号CON1〜CON3をそれぞれ出力する。なお、判定テーブル41は、第1の判定テーブルに対応する。

【0030】

続いて、演算装置100の動作について説明する。演算装置100では、演算回路10がレジスタファイル101から、データD0〜D2を読み込む。そして、データD0〜D2の最大値MAX、最小値MIN及び最大値MAXを除く2数の差分DIFFを検出する。そして、最大値MAX、最小値MIN及び最大値MAXを除く2数の差分DIFFを、レジスタファイル101に出力する。データD0〜D2を、RGB色空間における、R、G、Bのそれぞれに置き換えると、演算装置100は、前述の式(1)〜(5)を用いたRGB色空間からHSV色空間への変換処理(以下、HSV変換処理と称する)を行うことが可能となる。以下、演算装置100のHSV変換処理を具体的に説明する。

【0031】

スロット11では、加減算器CAL11が、データD0の値からデータD1の値を減算し、減算結果を演算結果C1として出力する。また、加減算器CAL11は、減算結果に応じて、符号フラグF1を出力する。具体的には、加減算器CAL11は、演算結果C1の符号がマイナスである場合、すなわちD0<D1である場合には、符号フラグF1として「1」を出力する。一方、演算結果C1の符号がマイナスではない場合、すなわちD0≧D1である場合には、符号フラグF1として「0」を出力する。

【0032】

同様に、スロット12では、加減算器CAL12が、データD1の値からデータD2の値を減算し、減算結果を演算結果C2として出力する。また、加減算器CAL12は、減算結果に応じて、符号フラグF2を出力する。具体的には、加減算器CAL12は、演算結果C2の符号がマイナスである場合、すなわちD1<D2である場合には、符号フラグF2として「1」を出力する。一方、演算結果C2の符号がマイナスではない場合、すなわちD1≧D2である場合には、符号フラグF2として「0」を出力する。

【0033】

同様に、スロット13では、加減算器CAL13が、データD2の値からデータD0の値を減算し、減算結果を演算結果C3として出力する。また、加減算器CAL13は、減算結果に応じて、符号フラグF3を出力する。具体的には、加減算器CAL13は、演算結果C3の符号がマイナスである場合、すなわちD2<D0である場合には、符号フラグF3として「1」を出力する。一方、演算結果C3の符号がマイナスではない場合、すなわちD2≧D0である場合には、符号フラグF3として「0」を出力する。

【0034】

判定器40は、符号フラグF1〜F3に基づいて、データD0〜D2の大小関係を判定する。そして、判定器40は、データD0〜D2の大小関係に基づいて、制御信号CON1〜CON3を出力する。図2は、判定器40に格納された判定テーブル41を示す図である。

【0035】

例えば、符号フラグF1〜F3が、それぞれ「0」、「0」、「1」であれば、命題「D0<D1」及び「D1<D2」は偽であり、命題「D2<D0」は真である。この場合、データD0〜D2については、「D0≧D1≧D2」の大小関係が成立している。この場合、判定器40は、制御信号CON1〜CON3として、それぞれ「0」、「2」、「1」を出力する。セレクタSEL11〜SEL13のそれぞれは、制御信号CON1〜CON3に応じて、入力ポートps0〜ps2のいずれかを選択する。具体的には、セレクタSEL11〜SEL13のそれぞれは、制御信号CON1〜CON3の値がk(kは0以上2以下の整数)である場合には、入力ポートpskを選択する。

【0036】

セレクタSEL11は、制御信号CON1の値「0」に応じて、入力ポートps0に入力するデータD0を選択する。これにより、データD0が最大値MAXとして特定される。つまり、セレクタSEL11は、最大値選択セレクタとして機能する。そして、セレクタSEL11は、最大値MAXであるデータD0を、レジスタファイル101のポートIN1へ出力する。よって、レジスタファイル101のポートIN1は、常に最大値MAXを受け取ることとなる。

【0037】

セレクタSEL12は、制御信号CON2の値「2」に応じて、入力ポートps2に入力するデータD2を選択する。これにより、データD2が最小値MINとして特定される。つまり、セレクタSEL12は、最小値選択セレクタとして機能する。そして、セレクタSEL12は、最小値MINであるデータD2を、レジスタファイル101のIN2へ出力する。よって、レジスタファイル101のポートIN2は、常に最小値MINを受け取ることとなる。

【0038】

セレクタSEL13は、制御信号CON3の値「1」に応じて、入力ポートps1に入力する演算結果C2を選択する。これにより、演算結果C2、すなわち(D1−D2)が最大値MAX(D0)を除く差分DIFFとして特定される。換言すると、セレクタSEL13は、制御信号CON3に応じて、最大値MAX(D0)が入力しない加減算器CAL12の演算結果C2を、差分DIFFとして選択する。つまり、セレクタSEL13は、差分選択セレクタとして機能する。そして、セレクタSEL13は、差分DIFFである演算結果C2を、レジスタファイル101のポートIN3へ出力する。よって、レジスタファイル101のポートIN3は、常に差分DIFFを受け取ることとなる。

【0039】

以上では、符号フラグF1〜F3が、それぞれ「0」、「0」、「1」である場合を例としたが、符号フラグF1〜F3が他の場合でも、セレクタSEL11〜SEL13は、最大値MAX、最小値MIN及び差分DIFFをそれぞれ出力することは言うまでもない。

【0040】

なお、演算装置100を用いてRGB色空間をHSV色空間に変換する場合、演算装置100に与える命令は、例えばC言語を用いると、以下の命令文で表される。

HSV変換処理を表す命令文

vmax = (d0>d1)?((d0>d2)?d0:d2):((d1>d2)?d1:d2);

vmin = (d0<d1)?((d0<d2)?d0:d2):((d1<d2)?d1:d2);

if (vmax == d0){

vdiff = d1-d2;

}else if (vmax == d1){

Vdiff = d2-d0;

}else{

Vdiff = d0-d1;

【0041】

上記の命令文において、vmaxは最大値MAXに、vminは最小値MINに、vdiffは差分DIFFに、d0〜d2はデータD0〜D2にそれぞれ対応する。第1文では、条件演算子を用いて、d0〜d2の最大値vmaxを算出する。第2文では、条件演算子を用いて、d0〜d2の最小値vminを算出する。第3文以降では、if文を用いて、d0〜d2のいずれが最大値であるかに応じて、差分vdiffを計算する。

【0042】

以上のように、演算回路10は、判定器40の判定結果を基に、最大値MAX、最小値MIN及び最大値MAXを除く2数の差分DIFFを検出する。そして、最大値MAX、最小値MIN及び最大値MAXを除く2数の差分DIFFを、レジスタファイル101の対応するポートIN1〜IN3のそれぞれに出力することができる。つまり、演算回路10は、レジスタファイル101からデータを読み込んでから、途中の演算結果をレジスタファイル101に一時的に格納することなく、1回のサイクルで最大値MAX、最小値MINを算出することができる。換言すれば、演算回路10は、3つ以上の値を比較し、その最大値や最小値などを特定するために条件分岐処理を要する演算を、1サイクルで行うことができる。よって、複数のサイクルを経て3以上の値の最大値MAXや最小値MIN及びを算出する場合に比べ、より高速な計算が可能である。従って、本構成によれば、3つ以上の値の条件分岐処理を要する比較演算を高速に行うことができる演算回路及び演算装置を実現することができる。

【0043】

また、RGB色空間からHSV色空間への変換処理では、R、G及びBのいずれの値が最大であるかによって、式(1)〜(3)のいずれを用いるかが決定される。このため、条件分岐命令を用いた場合分けが必要となる。従って、通常の演算装置を用いると、条件分岐処理が必要となり、RGB色空間からHSV色空間への変換処理の高速化が妨げられる。しかしながら、判定器40は、符号フラグF1〜F3を参照することにより、データD0〜D2のいずれが最大値であるかを判定し、式(1)〜(3)のいずれを用いるかを知ることができる。従って、本構成によれば、RGB色空間からHSV色空間への変換処理において条件分岐処理を高速に行うことができる演算回路及び演算装置をさらに実現することができる。

【0044】

さらに、本構成によれば、上述のように式(1)〜(3)のいずれを用いるかを知ることができる。よって、判定器40がセレクタSEL13を制御することにより、RGB色空間からHSV色空間への変換処理でいずれの式を用いる場合でも、適切な差分DIFFを1サイクルで求めることが可能である。よって、演算装置100及び演算回路10によれば、RGB色空間からHSV色空間への変換処理を高速かつ効率的に行うことが可能である。

【0045】

なお、以上では、判定テーブル41は、予め判定器40に格納されていた。しかしながら、判定テーブル41の内容は、外部から命令を与えることで設定することも可能である。以下では、外部からの命令により判定テーブル41を設定する方法について説明する。図3は、外部から判定テーブル41を設定する場合の演算装置100の構成を模式的に示すブロック図である。

【0046】

判定器40には、演算装置100の外部の制御回路102から、判定情報設定命令SETが与えられる。判定情報設定命令SETは、32bitの情報量を有する命令であり、判定テーブル41を構成する制御信号CON1〜CON3の値を設定する命令である。図4は、判定テーブル41の設定値を表示した図である。図4に示すように、制御信号CON1〜CON3には、設定値d01〜d03、d11〜d13、d21〜d23、d31〜d33、d41〜d43、d51〜d53、d61〜d63、d71〜d73が割り当てられる。但し、命題D0<D1、D1<D2及びD2<D0が、全て真であることは有り得ないので、実際には、設定値d01〜d03、d11〜d13、d21〜d23、d31〜d33、d41〜d43、d51〜d53、d61〜d63に値を設定すればよい。

【0047】

設定値のそれぞれは、3bitの情報量が割り当てられる。従って32bitの判定情報設定命令SETでは、一度に10個の設定値を設定することが可能である。つまり、32bitの判定情報設定命令SETを3回与えることにより、判定テーブル41の設定値d01〜d03、d11〜d13、d21〜d23、d31〜d33、d41〜d43、d51〜d53、d61〜d63に具体的な値を設定することができる。この場合、判定情報設定命令SETは、以下の命令文で表現することが可能である。

判定情報設定命令SETを示す命令文

setfusion idx, val

【0048】

idxは、判定情報設定命令SETの命令の順番を示し、判定情報設定命令SETが3回与えられる場合には、0〜2のいずれかが割り充てられる。値valは、設定値d01〜d03、d11〜d13、d21〜d23、d31〜d33、d41〜d43、d51〜d53、d61〜d63に割り当てる値を示す。以下では、値valは、32bit即値で表現するものとする。

【0049】

図5は、実施の形態1にかかる判定情報設定命令SETの値valの構成例を示す図である。判定情報設定命令SETの値valは、例えば、2つの空きbit50と、それぞれ3bitの値e0〜e9により構成される。図6は、判定情報設定命令SETの値valと判定テーブル41の設定値との関係を示す図である。例えば、制御信号CON1〜CON3として、図2に示す値を設定する場合について検討する。

【0050】

まず、idx=0の場合、値e0〜e9は、それぞれ「0」、「2」、「1」、「0」、「2」、「1」、「2」、「1」、「0」、「0」となる。よって、判定情報設定命令SETの値valは、2進数表示では、図5に示す値となる。これを16進数で表される32bit即値に変換すると、「0x00512050」となる。idx=1の場合には、値e0〜e9は、それぞれ「0」、「1」、「1」、「1」、「0」、「2」、「1」、「2」、「2」、「0」となる。よって、判定情報設定命令SETの値valは、2進数表示では、図5に示す値となる。これを16進数で表される32bit即値に変換すると、「0x048a0248」となる。idx=2の場合には、値e0〜e9は、それぞれ「2」、「0」、「0」、「0」、「0」、「0」、「0」、「0」、「0」、「0」となる。よって、判定情報設定命令SETの値valは、2進数表示では、図5に示す値となる。これを16進数で表される32bit即値に変換すると、「0x00000002」となる。この場合、判定情報設定命令SETは、以下の命令文で表現することが可能である。

判定情報設定命令SETを示す命令文

setfusion 0, 0x00512050

setfusion 1, 0x048a0248

setfusion 2, 0x00000002

【0051】

以上のように、判定器40に判定情報設定命令SETを与えることで、判定テーブル41内の値を具体的に設定することが可能である。

【0052】

実施の形態2

次に、実施の形態2にかかる演算装置200について説明する。演算装置200は、実施の形態1にかかる演算装置100で行うHSV変換処理に加えて、3つのデータD0〜D2のソート処理を行うことができる装置である。図7は、実施の形態2にかかる演算装置200の構成を模式的に示すブロック図である。演算装置200は、実施の形態1にかかる演算装置100の構成転換例であり、具体的には演算回路の構成が異なる。演算装置200は、レジスタファイル101及び演算回路20を有する。レジスタファイル101については、実施の形態1と同様であるので、説明を省略する。

【0053】

演算回路20は、スロット11、12及び23、判定器40を有する。スロット11では、加減算器CAL11は、セレクタSEL23に演算結果C1を出力する。スロット11のその他の構成は、実施の形態1と同様であるので説明を省略する。スロット12では、加減算器CAL12は、セレクタSEL23に演算結果C2を出力する。スロット12のその他の構成は、実施の形態1と同様であるので説明を省略する。また、判定器40は演算回路10と同様であるので、説明を省略する。

【0054】

スロット23は、加減算器CAL13及びセレクタSEL23を有する。セレクタSEL23は、6入力1出力のセレクタであり、第3の選択回路に対応する。加減算器CAL13は、セレクタSEL23に演算結果C3を出力する。セレクタSEL23の入力ポートps0〜ps2には加減算器CAL11〜CAL13の演算結果C1〜C3がそれぞれ入力し、入力ポートps3〜ps5にはデータD0〜D2がそれぞれ入力する。そして、セレクタSEL23は、判定器40からの制御信号CON3に基づき、レジスタファイル101のポートIN3に、データD0〜D2のいずれかを中間値MIDとして出力する。スロット23のその他の構成は、スロット13と同様であるので説明を省略する。

【0055】

続いて、演算装置200の動作について説明する。演算装置200におけるHSV変換処理については実施の形態1にかかる演算装置100と同様であるので説明を省略し、以下では、ソート処理について説明する。演算装置200は、外部の制御回路102から判定器40に入力する判定情報設定命令SETで判定テーブルの設定値を変更することにより、HSV変換処理及びソート処理のいずれの処理を行うかを切り替えることが可能である。以下、ソート処理について具体的に説明する。

【0056】

スロット11では、HSV変換処理時と同様に、加減算器CAL11が、データD0の値からデータD1の値を減算し、減算結果を演算結果C1として出力する。また、加減算器CAL11は、減算結果に応じて、符号フラグF1を出力する。具体的には、加減算器CAL11は、演算結果C1の符号がマイナスである場合、すなわちD0<D1である場合には、符号フラグF1として「1」を出力する。一方、演算結果C1の符号がマイナスではない場合、すなわちD0≧D1である場合には、符号フラグF1として「0」を出力する。

【0057】

同様に、スロット12では、HSV変換処理時と同様に、加減算器CAL12が、データD1の値からデータD2の値を減算し、減算結果を演算結果C2として出力する。また、加減算器CAL12は、減算結果に応じて、符号フラグF2を出力する。具体的には、加減算器CAL12は、演算結果C2の符号がマイナスである場合、すなわちD1<D2である場合には、符号フラグF2として「1」を出力する。一方、演算結果C2の符号がマイナスではない場合、すなわちD1≧D2である場合には、符号フラグF2として「0」を出力する。

【0058】

同様に、スロット23では、HSV変換処理時と同様に、加減算器CAL13が、データD2の値からデータD0の値を減算し、減算結果を演算結果C3として出力する。また、加減算器CAL13は、減算結果に応じて、符号フラグF3を出力する。具体的には、加減算器CAL13は、演算結果C3の符号がマイナスである場合、すなわちD2<D0である場合には、符号フラグF3として「1」を出力する。一方、演算結果C3の符号がマイナスではない場合、すなわちD2≧D0である場合には、符号フラグF3として「0」を出力する。

【0059】

判定器40は、符号フラグF1〜F3に基づいて、データD0〜D2の大小関係を判定する。そして、判定器40は、データD0〜D2の大小関係に基づいて、制御信号CON1〜CON3を出力する。図8は、判定器40に格納されたソート処理時の判定テーブル42を示す図である。なお、判定テーブル42は、第2の判定テーブルに対応する。

【0060】

例えば、符号フラグF1〜F3が、それぞれ「0」、「0」、「1」であれば、命題「D0<D1」及び「D1<D2」は偽であり、命題「D2<D0」は真である。この場合、データD0〜D2については、「D0≧D1≧D2」の大小関係が成立している。この場合、判定器40は、制御信号CON1〜CON3として、それぞれ「0」、「2」、「4」を出力する。セレクタSEL11及びSEL12のそれぞれは、制御信号CON1及びCON2に応じて、入力ポートps0〜ps2のいずれかを選択する。セレクタSEL23は、制御信号CON3に応じて、入力ポートps0〜ps5のいずれかを選択する。具体的には、セレクタSEL11及びSEL12のそれぞれは、制御信号CON1及びCON2の値がk(kは0以上2以下の整数)である場合には、入力ポートpskを選択する。セレクタSEL23は、制御信号CON3の値がj(jは0以上5以下の整数)である場合には、入力ポートpsjを選択する。

【0061】

セレクタSEL11は、HSV変換処理時と同様に、制御信号CON1の値「0」に応じて、入力ポートps0に入力するデータD0を選択する。これにより、データD0が最大値MAXとして特定される。つまり、セレクタSEL11は、最大値選択セレクタとして機能する。そして、セレクタSEL11は、最大値MAXであるデータD0を、レジスタファイル101のポートIN1へ出力する。よって、レジスタファイル101のポートIN1は、常に最大値MAXを受け取ることとなる。

【0062】

セレクタSEL12は、HSV変換処理時と同様に、制御信号CON2の値「2」に応じて、入力ポートps2に入力するデータD2を選択する。これにより、データD2が最小値MINとして特定される。つまり、セレクタSEL12は、最小値選択セレクタとして機能する。そして、セレクタSEL12は、最小値MINであるデータD2を、レジスタファイル101のIN2へ出力する。よって、レジスタファイル101のポートIN2は、常に最小値MINを受け取ることとなる。

【0063】

セレクタSEL23は、制御信号CON3の値「4」に応じて、入力ポートps4に入力するデータD1を選択する。これにより、データD1が中間値MIDとして特定される。つまり、セレクタSEL23は、中間値選択セレクタとして機能する。そして、セレクタSEL23は、中間値MIDであるデータD1を、レジスタファイル101のポートIN3へ出力する。よって、レジスタファイル101のポートIN3は、常に中間値MIDを受け取ることとなる。

【0064】

以上では、符号フラグF1〜F3が、それぞれ「0」、「0」、「1」である場合を例としたが、符号フラグF1〜F3が他の場合でも、セレクタSEL11、SEL12及びSEL23は、最大値MAX、最小値MIN及び中間値MIDをそれぞれ出力することは言うまでもない。

【0065】

続いて、ソート処理用の判定テーブル42を設定する方法について説明する。図9は、外部から判定テーブル42を設定する場合の演算装置200の構成を模式的に示すブロック図である。演算装置200では、判定情報設定命令SETにより、以下に示す要領で、判定テーブル41を判定テーブル42に置換することが可能である。なお、同様の要領で、判定テーブル42を判定テーブル41に置換することが可能であることは、言うまでもない。

【0066】

判定器40には、演算装置200の外部の制御回路102から、判定情報設定命令SETが与えられる。判定テーブル42の設定値については、図4を用いて既述した判定テーブル41と同様であるため説明を省略する。また、判定情報設定命令SETの値valの構成については、図5を用いて既述したため説明を省略する。判定情報設定命令SETの値valと判定テーブル42の設定値との関係についても、図6を用いて既述したため説明を省略する。以下では、例えば、制御信号CON1〜CON3として、図8に示す値を設定する場合について検討する。図10は、実施の形態2にかかる判定情報設定命令SETの値valの構成例を示す図である。

【0067】

まず、idx=0の場合、値e0〜e9は、それぞれ「0」、「2」、「4」、「0」、「2」、「4」、「2」、「1」、「3」、「0」となる。よって、判定情報設定命令SETの値valは、2進数表示では、図10に示す値となる。これを16進数で表される32bit即値に変換すると、「0x06542110」となる。idx=1の場合には、値e0〜e9は、それぞれ「0」、「1」、「5」、「1」、「0」、「5」、「1」、「2」、「3」、「0」となる。よって、判定情報設定命令SETの値valは、2進数表示では、図11に示す値となる。これを16進数で表される32bit即値に変換すると、「0x068d0348」となる。idx=2の場合には、値e0〜e9は、それぞれ「2」、「0」、「4」、「0」、「0」、「0」、「0」、「0」、「0」、「0」となる。よって、判定情報設定命令SETの値valは、2進数表示では、図11に示す値となる。これを16進数で表される32bit即値に変換すると、「0x00000102」となる。この場合、判定情報設定命令SETは、以下の命令文で表現することが可能である。

判定情報設定命令SETを示す命令文

setfusion 0, 0x06542110

setfusion 1, 0x068d0348

setfusion 2, 0x00000102

【0068】

以上のように、演算回路20は、判定器40の判定結果を基に、最大値MAX、最小値MIN及び中間値MIDを検出する。そして、最大値MAX、最小値MIN及び中間値MIDを、レジスタファイル101の対応するポートIN1〜IN3のそれぞれに出力することができる。よって、演算回路20は、HSV変換処理のみならず、レジスタファイル101から読み込んだデータD0〜D2の大小関係を判定し、値をソートすることが可能である。換言すれば、演算回路10は、3つ以上の値を比較し、その最大値や最小値などを特定するために条件分岐処理を要する演算、具体的にはソート処理を1サイクルで行うことができる。従って、本構成によれば、3つ以上の値の条件分岐処理を要する比較演算を高速に行うことができる演算回路及び演算装置を実現することができる。さらに、ソート処理が可能となったことで、演算装置100及び演算回路10よりも高機能かつ汎用性に優れる演算装置200及び演算回路20を提供することができる。

【0069】

また、演算回路20は、レジスタファイル101からデータを読み込んでから、途中の演算結果をレジスタファイル101に一時的に格納することなく、1回のサイクルで最大値MAX、最小値MIN及び中間値MIDを求めることが可能である。従って、演算回路20は、ソート処理を高速に行うことが可能である。

【0070】

実施の形態3

次に、実施の形態3にかかる演算装置300について説明する。演算装置300は、実施の形態1にかかる演算装置100で行うHSV変換処理に加えて、RGB色空間からHSV色空間への変換で用いる定数を同時に指定することができる装置である。図11は、実施の形態3にかかる演算装置300の構成を模式的に示すブロック図である。演算装置300は、実施の形態1にかかる演算装置100の構成転換例であり、具体的には演算回路の構成が異なる。演算装置300は、レジスタファイル101及び演算回路30を有する。レジスタファイル101については、ポートIN4が追加された他は、実施の形態1と同様であるので説明を省略する。演算回路30は、スロット11〜13及び34、判定器43を有する。スロット11〜13は、演算回路10と同様であるので、説明を省略する。

【0071】

スロット34は、定数レジスタ341〜343、セレクタSEL34を有する。セレクタSEL34は、3入力1出力のセレクタであり、第4の選択回路に対応する。セレクタSEL34の入力ポートps0〜ps2は、定数レジスタ341〜343から、定数データCD0〜CD2がそれぞれ入力する。そして、セレクタSEL34は、判定器43からの制御信号CON4に基づき、レジスタファイル101のポートIN4に、定数データCD0〜CD2のいずれかを定数CONSTとして出力する。

【0072】

判定器43は、符号フラグF1〜F3に基づいて、格納されている判定テーブル43を参照し、セレクタSEL11〜SEL13に制御信号CON1〜CON3をそれぞれ出力し、スロット34のセレクタSEL34に制御信号CON4を出力する。なお、判定テーブル43は、第3の判定テーブルに対応する。

【0073】

続いて、演算装置300の動作について説明する。演算装置300のうち、最大値MAX、最小値MIN及び差分DIFFの算出を行う上述のHSV変換処理については、実施の形態1にかかる演算装置100と同様であるので、説明を省略する。よって、以下では、定数CONSTの算出方法について説明する。

【0074】

データD0〜D2を、RGB色空間における、R、G、Bのそれぞれに置き換えると、演算装置300は、前述の式(1)〜(5)中のMAX、MIN及び差分だけでなく、さらに式(1)〜(3)中の定数の値を算出することが可能である。ここで、定数とは、式(1)〜(3)の右辺第2項の値を意味し、式(1)における「0」、式(2)における「120」、式(3)における「240」を指す。

【0075】

判定器43は、符号フラグF1〜F3に基づいて、データD0〜D2の大小関係を判定する。そして、判定器43は、データD0〜D2の大小関係に基づいて、制御信号CON1〜CON4を出力する。図12は、判定器43に格納された判定テーブル44を示す図である。

【0076】

例えば、符号フラグF1〜F3が、それぞれ「0」、「0」、「1」であれば、命題「D0<D1」及び「D1<D2」は偽であり、命題「D2<D0」は真である。この場合、データD0〜D2については、「D0≧D1≧D2」の大小関係が成立している。この場合、判定器43は、制御信号CON1〜CON4として、それぞれ「0」、「2」、「1」、「0」を出力する。

【0077】

セレクタSEL34は、制御信号CON4に応じて、入力ポートps0〜ps2のいずれかを選択する。具体的には、セレクタSEL34は、制御信号CON4の値がk(kは0以上2以下の整数)である場合には、入力ポートpskを選択する。上述のように、制御信号CON4は「0」であるので、セレクタSEL34は、入力ポートps0を選択する。セレクタSEL34は、定数データCD0を、定数CONSTとして出力する。

【0078】

このとき、データD0〜D2がRGB色空間のR、G及びBにそれぞれ対応すると考えると、定数データCD0〜CD2の値は、それぞれ「0」、「120」、「240」である。上述の例では、データD0が最大であるので、式(1)を用いた計算が行われる。従って、セレクタSEL34は、式(1)の定数部分を示す定数データCD0を、定数CONSTとして選択する。同様に、G又はB、すなわちデータD1又はD2が最大である場合にも、判定器43が判定テーブル44を用いて判定を行うことにより、適切な定数を算出することが可能である。

【0079】

なお、演算装置300を用いてHSV変換処理及び定数の算出処理を行う場合、演算装置300に与える命令は、例えばC言語を用いると、以下の命令文で表される。

HSV変換処理及び定数の演算処理を表す命令文

vmax=(d0>d1)?((d0>d2)?d0:d2):((d1>d2)?d1:d2);

vmin = (d0<d1)?((d0<d2)?d0:d2):((d1<d2)?d1:d2);

if (vmax == d0){

vdiff = d1-d2;

vconst=0;

}else if (vmax == d1){

Vdiff = d2-d0;

vconst=120;

}else{

Vdiff = d0-d1;

vconst=240;

H = (vdiff*60)/(vmax-vmin)+vconst

【0080】

上記の命令文において、vmaxは最大値MAXに、vminは最小値MINに、vdiffは差分DIFFに、constは定数CONSTに、d0〜d2はデータD0〜D2にそれぞれ対応する。第1文では、条件演算子を用いて、d0〜d2の最大値vmaxを算出する。第2文では、条件演算子を用いて、d0〜d2の最小値vminを算出する。第3文以降では、if文を用いて、d0〜d2のいずれが最大値であるかに応じて差分vdiffを計算するとともに、式(1)〜(3)における定数の値を特定する。

【0081】

その他の実施の形態

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。例えば、実施の形態3では、データD0〜D2のソート処理を行う例について説明したが、3つのレジスタに演算結果C1〜C3を入力させ、演算結果C1〜C3のソート処理を行う構成とすることも可能である。

【0082】

図3及び図9では、制御回路102は演算装置100及び200の内部に設けられているが、演算装置100及び200の外部に設けることも可能である。

【0083】

実施の形態2では、判定テーブル41は、判定情報設定命令SETにより書き換えられるが、これは例示に過ぎない。例えば、判定器40に、HSV変換処理用の判定テーブルとソート処理用の判定テーブルを予め格納しておき、制御回路からの選択信号により、用いる判定テーブルを指定することも可能である。

【0084】

上述の実施の形態における判定情報設定命令SETの構成はあくまで例示である。従って、判定情報設定命令SETの値valでの値e0〜e9は、別の順序で配置することも可能である。また、空きビットの位置も、別の位置とすることも可能である。さらに、判定テーブルの設定と値e0〜e9との対応関係も別の関係とすることもできる。なお、判定情報設定命令SETの値valを16進法を用いて表現したが、他の進法を用いて表現してもよい。

【符号の説明】

【0085】

11〜13、23、34 スロット

341〜343 定数レジスタ

10、20、30 演算回路

40、43 判定器

41、42、44 判定テーブル

100、200、300 演算装置

101 レジスタファイル

102 制御回路

C1〜C3 演算結果

CAL11〜CAL13 加減算器

CD0 定数データ

CD0〜CD2 定数データ

CON1〜CON4 制御信号

CONST 定数

D0〜D2 データ

DIFF 差分

F1〜F3 符号フラグ

IN1〜IN4 ポート

MAX 最大値

MID 中間値

MIN 最小値

ps0〜ps5 入力ポート

SEL11〜SEL13、SEL23、SEL34 セレクタ

SET 判定情報設定命令

【技術分野】

【0001】

本発明は演算回路及び演算装置に関し、特に並列演算処理を行う演算回路及び演算装置に関する。

【背景技術】

【0002】

一般に、画像を構成する画素の色情報を表現する手段として、色空間が用いられる。ディスプレイなどに画像を表示する場合には、赤(Red)、緑(Green)及び青(Blue)による加法混色を表現するRGB方式が広く用いられている。一方、コンピューター上でイラストなどを描画するために描画色を選ぶ場合などでは、ユーザーである人間の感覚に親和性があるとの理由から、HSV方式が用いられることが多い。HSV方式では、色相(Hue)、彩度(Saturation value)及び明度(Value)の3要素を用いて色情報を表現する。

【0003】

RGB方式で表現された色情報(以下、RGB色空間)とHSV方式で表現された色情報(以下、HSV色空間)とを取り扱うには、2つの方式間の変換作業が必要となる。この変換作業は、画像処理プロセッサなどにより行われる。画像処理プロセッサのような一般的な命令セットプロセッサにおいては、2入力1出力命令が多く用いられている。また、演算性能を高めるために、VLIW(Very Long Instruction Word:超長命令語)構成の命令語を利用するプロセッサも提案されている。

【0004】

RGB色空間からHSV色空間への変換を行う場合、色相H、彩度S及び明度Vは、以下のように表されることが知られている。なお、以下では、赤(R)、緑(G)及び青(B)の最小量を0、最大量を1とする。

【0005】

色相Hは、R、G及びBのいずれの値が最大であるかによって、算出式が異なる。まず、R、G及びBのうち、Rの値が最大である場合には、色相Hは以下の式(1)で表される。但し、MAXは最大値であるRの値を示す。また、MINは、R、G及びBの最小の値、すなわちG及びBの小さい方の値を示す。

【数1】

【0006】

R、G及びBのうち、Gの値が最大である場合には、色相Hは以下の式(2)で表される。但し、MAXは最大値であるGの値を示す。また、MINは、R、G及びBの最小の値、すなわちR及びBの小さい方の値を示す。

【数2】

【0007】

R、G及びBのうち、Bの値が最大である場合には、色相Hは以下の式(3)で表される。但し、MAXは最大値であるBの値を示す。また、MINは、R、G及びBの最小の値、すなわちR及びGの小さい方の値を示す。

【数3】

【0008】

彩度Sは、以下の式(4)で表される。

【数4】

【0009】

彩度Vは、以下の式(5)で表される。

【数5】

【0010】

式(1)〜(5)に示すように、RGB色空間からHSV色空間への変換作業では、色相Hを計算する際にR、G及びBの3つの値を比較する条件分岐や、R、G及びBの最大値MAX及び最小値MINを求める作業が必要である。また、最大値MAX以外の2つの値の差分(式(1)〜(3)の右辺第1項の分数部の分子)を求める必要もある。

【0011】

このような条件分岐や最大値及び最小値を算出するための演算プロセッサとして、例えばVLIWプロセッサが知られている。他にも、様々なプロセッサが提案されている。

【0012】

例えば、複数のプロセッサエレメントによる並列処理を行うことにより、条件分岐を伴う処理を高速に行う手法が提案されている(特許文献1)。この手法では、分岐条件に応じて、選択器を用いてプロセッサエレメントの出力を選択することにより、最大値や最小値の算出などの条件分岐を伴う処理を実現している。

【0013】

また、多くの命令サイクルにおいて、レジスタファイルの読み取りポートを無駄にしないため、多重化機能ユニット(プロセッサ)に対する命令を2以上の発行スロットに与える手法が提案されている(特許文献2)。これにより、多重化機能ユニットが用いられないサイクル中でも、他の機能ユニットが発行スロットを利用することができ、読み取りポートを効率的に利用することが可能となる。

【0014】

さらに、演算処理によってアクセスすべきアドレスが変わる場合(すなわち、分岐処理)に対応可能な構成(特許文献3)や、比較対象データ内の最大値又は最小値を有するプロセッサを効率的かつ高速に検出できる手法(特許文献4)が提案されている。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開2004−62401号公報

【特許文献2】特表2002−527812号公報

【特許文献3】特開2010−97356号公報

【特許文献4】特開2000−163384号公報

【発明の概要】

【発明が解決しようとする課題】

【0016】

ところが、発明者は、上述の手法には以下の問題点があることを見出した。通常、RGB色空間からHSV色空間への変換処理では、R、G及びBの3つの値の最大値、最小値及び最大値を除く2数の差分を計算する必要がある。例えば、3つの値r1〜r3の最大値を計算するには、以下の命令で示すように、2サイクルを要する。

第1サイクル max r1, r2, r4

第2サイクル max r4, r3, r4

第1サイクルでは、2つの値r1及びr2のうちの最大値を、値r4に格納する。第2サイクルでは、2つの値r3及びr4のうちの最大値を、値r4に格納する。つまり、第1のサイクルを実行した後に、値r4を一時的にレジスタファイルに格納し、第2のサイクルで格納した値r4を参照することとなる。これは、最小値を計算する場合も同様である。また、式(1)〜(3)による計算を行うためには、R、G及びBの最大値が既知でなければいけないため、前もって最大値を算出しなければならない。

【0017】

換言すれば、上述の手法では、3つ以上の値の大小関係を判定するには、2つの値の比較処理を繰り返して行う必要があり、比較処理の都度、比較結果をレジスタファイルなどの記憶手段に格納しなければならない。つまり、通常の手法では、3つ以上の値の比較演算を行うには複数のサイクルが必要であり、演算処理を高速化する上で妨げとなる。当然に、R、G及びBの3つの値の比較演算を要するRGB色空間からHSV色空間への変換処理の高速化も妨げられる。

【課題を解決するための手段】

【0018】

本発明の一態様である演算回路は、入力するデータに対して演算を行い、前記演算結果に基づいて生成したフラグ情報を出力する複数の演算器と、前記複数の演算器に入力する前記データのいずれかを選択する複数の選択回路と、前記複数の演算器からの前記フラグ情報が入力し、前記複数の選択回路のそれぞれの選択動作を制御する判定器と、を備えるものである。この演算回路では、演算回路に入力するデータの大小関係に基づいて選択回路の選択動作を制御し、選択回路に最大値、最小値及び3つの最大値以外の値の差分を選択させることができる。これにより、演算の途中経過においてデータをレジスタに格納することなく、単一のサイクルで最大値、最小値及び3つの最大値以外の値の差分を算出することができる。

【発明の効果】

【0019】

本発明によれば、3つ以上の値の条件分岐処理を要する比較演算を高速に行うことができる演算回路及び演算装置を提供することができる。

【図面の簡単な説明】

【0020】

【図1】実施の形態1にかかる演算装置100の構成を模式的に示すブロック図である。

【図2】判定器40に格納された判定テーブル41を示す図である。

【図3】外部から判定テーブル41を設定する場合の演算装置100の構成を模式的に示すブロック図である。

【図4】判定テーブル41の設定値を表示した図である。

【図5】実施の形態1にかかる判定情報設定命令SETの値valの構成例を示す図である。

【図6】判定情報設定命令SETの値valと判定テーブル41の設定値との関係を示す図である。

【図7】実施の形態2にかかる演算装置200の構成を模式的に示すブロック図である。

【図8】判定器40に格納されたソート処理時の判定テーブル42を示す図である。

【図9】外部から判定テーブル42を設定する場合の演算装置200の構成を模式的に示すブロック図である。

【図10】実施の形態2にかかる判定情報設定命令SETの値valの構成例を示す図である。

【図11】実施の形態3にかかる演算装置300の構成を模式的に示すブロック図である。

【図12】判定器43に格納された判定テーブル44を示す図である。

【発明を実施するための形態】

【0021】

以下、図面を参照して本発明の実施の形態について説明する。各図面においては、同一要素には同一の符号が付されており、必要に応じて重複説明は省略される。

【0022】

実施の形態1

まず、実施の形態1にかかる演算装置100について説明する。図1は、実施の形態1にかかる演算装置100の構成を模式的に示すブロック図である。演算装置100は、レジスタファイル101及び演算回路10を有する。

【0023】

レジスタファイル101は、演算回路10の演算の用に供するデータや、演算回路10による演算により算出されたデータが格納される。レジスタファイル101には、図1に示すように、データが入力するポートIN1〜IN3が設けられる。また、レジスタファイル101は、演算回路10にデータD0〜D2を出力する。なお、データD0〜D2は、それぞれ第1〜第3のデータに対応する。レジスタファイル101は、この他にもポートや出力するデータを有する場合が有るが、いずれのポートを使用するか、いずれのデータを出力するかは、例えば外部の制御回路(不図示)からの命令により指定することが可能である。

【0024】

演算回路10は、複数のスロット11〜13及び判定器40を有する。スロット11〜13は、それぞれ加減算器CAL11〜CAL13及びセレクタSEL11〜SEL13を有する。加減算器は演算器の一例であり、加減算器CAL11〜CAL13は、それぞれ第1〜第3の演算器に対応する。セレクタSEL11〜SEL13は、3入力1出力のセレクタである。セレクタは、選択回路の一例であり、セレクタSEL11〜SEL13は、それぞれ第1〜第3の選択回路に対応する。

【0025】

スロット11では、加減算器CAL11に、レジスタファイル101からデータD0及びD1が入力する。そして、加減算器CAL11は、セレクタSEL13に演算結果C1を出力する。また、加減算器CAL11は、判定器40に符号フラグF1を出力する。セレクタSEL11の入力ポートps0〜ps2には、レジスタファイル101からデータD0〜D2がそれぞれ入力する。そして、セレクタSEL11は、判定器40からの制御信号CON1に基づき、レジスタファイル101のポートIN1に、データD0〜D2のいずれかを最大値MAXとして出力する。

【0026】

スロット12では、加減算器CAL12に、レジスタファイル101からデータD1及びD2が入力する。そして、加減算器CAL12は、セレクタSEL13に演算結果C2を出力する。また、加減算器CAL11は、判定器40に符号フラグF2を出力する。セレクタSEL12の入力ポートps0〜ps2には、レジスタファイル101からデータD0〜D2がそれぞれ入力する。そして、セレクタSEL12は、判定器40からの制御信号CON2に基づき、レジスタファイル101のポートIN2に、データD0〜D2のいずれかを最小値MINとして出力する。

【0027】

スロット13では、加減算器CAL13に、レジスタファイル101からデータD2及びD0が入力する。そして、加減算器CAL13は、セレクタSEL13に演算結果C3を出力する。また、加減算器CAL13は、判定器40に符号フラグF3を出力する。セレクタSEL13の入力ポートps0〜ps2には、加減算器CAL11〜CAL13の演算結果C1〜C3がそれぞれ入力する。そして、セレクタSEL13は、判定器40からの制御信号CON3に基づき、レジスタファイル101のポートIN3に、演算結果C1〜C3のいずれかを差分DIFFとして出力する。

【0028】

なお、符号フラグは、加減算器の演算結果に応じて出力されるフラグ情報であり、符号フラグF1〜F3は、それぞれ符号フラグに対応する。

【0029】

判定器40は、符号フラグF1〜F3に基づいて、格納されている判定テーブル41を参照し、セレクタSEL11〜SEL13に制御信号CON1〜CON3をそれぞれ出力する。なお、判定テーブル41は、第1の判定テーブルに対応する。

【0030】

続いて、演算装置100の動作について説明する。演算装置100では、演算回路10がレジスタファイル101から、データD0〜D2を読み込む。そして、データD0〜D2の最大値MAX、最小値MIN及び最大値MAXを除く2数の差分DIFFを検出する。そして、最大値MAX、最小値MIN及び最大値MAXを除く2数の差分DIFFを、レジスタファイル101に出力する。データD0〜D2を、RGB色空間における、R、G、Bのそれぞれに置き換えると、演算装置100は、前述の式(1)〜(5)を用いたRGB色空間からHSV色空間への変換処理(以下、HSV変換処理と称する)を行うことが可能となる。以下、演算装置100のHSV変換処理を具体的に説明する。

【0031】

スロット11では、加減算器CAL11が、データD0の値からデータD1の値を減算し、減算結果を演算結果C1として出力する。また、加減算器CAL11は、減算結果に応じて、符号フラグF1を出力する。具体的には、加減算器CAL11は、演算結果C1の符号がマイナスである場合、すなわちD0<D1である場合には、符号フラグF1として「1」を出力する。一方、演算結果C1の符号がマイナスではない場合、すなわちD0≧D1である場合には、符号フラグF1として「0」を出力する。

【0032】

同様に、スロット12では、加減算器CAL12が、データD1の値からデータD2の値を減算し、減算結果を演算結果C2として出力する。また、加減算器CAL12は、減算結果に応じて、符号フラグF2を出力する。具体的には、加減算器CAL12は、演算結果C2の符号がマイナスである場合、すなわちD1<D2である場合には、符号フラグF2として「1」を出力する。一方、演算結果C2の符号がマイナスではない場合、すなわちD1≧D2である場合には、符号フラグF2として「0」を出力する。

【0033】

同様に、スロット13では、加減算器CAL13が、データD2の値からデータD0の値を減算し、減算結果を演算結果C3として出力する。また、加減算器CAL13は、減算結果に応じて、符号フラグF3を出力する。具体的には、加減算器CAL13は、演算結果C3の符号がマイナスである場合、すなわちD2<D0である場合には、符号フラグF3として「1」を出力する。一方、演算結果C3の符号がマイナスではない場合、すなわちD2≧D0である場合には、符号フラグF3として「0」を出力する。

【0034】

判定器40は、符号フラグF1〜F3に基づいて、データD0〜D2の大小関係を判定する。そして、判定器40は、データD0〜D2の大小関係に基づいて、制御信号CON1〜CON3を出力する。図2は、判定器40に格納された判定テーブル41を示す図である。

【0035】

例えば、符号フラグF1〜F3が、それぞれ「0」、「0」、「1」であれば、命題「D0<D1」及び「D1<D2」は偽であり、命題「D2<D0」は真である。この場合、データD0〜D2については、「D0≧D1≧D2」の大小関係が成立している。この場合、判定器40は、制御信号CON1〜CON3として、それぞれ「0」、「2」、「1」を出力する。セレクタSEL11〜SEL13のそれぞれは、制御信号CON1〜CON3に応じて、入力ポートps0〜ps2のいずれかを選択する。具体的には、セレクタSEL11〜SEL13のそれぞれは、制御信号CON1〜CON3の値がk(kは0以上2以下の整数)である場合には、入力ポートpskを選択する。

【0036】

セレクタSEL11は、制御信号CON1の値「0」に応じて、入力ポートps0に入力するデータD0を選択する。これにより、データD0が最大値MAXとして特定される。つまり、セレクタSEL11は、最大値選択セレクタとして機能する。そして、セレクタSEL11は、最大値MAXであるデータD0を、レジスタファイル101のポートIN1へ出力する。よって、レジスタファイル101のポートIN1は、常に最大値MAXを受け取ることとなる。

【0037】

セレクタSEL12は、制御信号CON2の値「2」に応じて、入力ポートps2に入力するデータD2を選択する。これにより、データD2が最小値MINとして特定される。つまり、セレクタSEL12は、最小値選択セレクタとして機能する。そして、セレクタSEL12は、最小値MINであるデータD2を、レジスタファイル101のIN2へ出力する。よって、レジスタファイル101のポートIN2は、常に最小値MINを受け取ることとなる。

【0038】

セレクタSEL13は、制御信号CON3の値「1」に応じて、入力ポートps1に入力する演算結果C2を選択する。これにより、演算結果C2、すなわち(D1−D2)が最大値MAX(D0)を除く差分DIFFとして特定される。換言すると、セレクタSEL13は、制御信号CON3に応じて、最大値MAX(D0)が入力しない加減算器CAL12の演算結果C2を、差分DIFFとして選択する。つまり、セレクタSEL13は、差分選択セレクタとして機能する。そして、セレクタSEL13は、差分DIFFである演算結果C2を、レジスタファイル101のポートIN3へ出力する。よって、レジスタファイル101のポートIN3は、常に差分DIFFを受け取ることとなる。

【0039】

以上では、符号フラグF1〜F3が、それぞれ「0」、「0」、「1」である場合を例としたが、符号フラグF1〜F3が他の場合でも、セレクタSEL11〜SEL13は、最大値MAX、最小値MIN及び差分DIFFをそれぞれ出力することは言うまでもない。

【0040】

なお、演算装置100を用いてRGB色空間をHSV色空間に変換する場合、演算装置100に与える命令は、例えばC言語を用いると、以下の命令文で表される。

HSV変換処理を表す命令文

vmax = (d0>d1)?((d0>d2)?d0:d2):((d1>d2)?d1:d2);

vmin = (d0<d1)?((d0<d2)?d0:d2):((d1<d2)?d1:d2);

if (vmax == d0){

vdiff = d1-d2;

}else if (vmax == d1){

Vdiff = d2-d0;

}else{

Vdiff = d0-d1;

【0041】

上記の命令文において、vmaxは最大値MAXに、vminは最小値MINに、vdiffは差分DIFFに、d0〜d2はデータD0〜D2にそれぞれ対応する。第1文では、条件演算子を用いて、d0〜d2の最大値vmaxを算出する。第2文では、条件演算子を用いて、d0〜d2の最小値vminを算出する。第3文以降では、if文を用いて、d0〜d2のいずれが最大値であるかに応じて、差分vdiffを計算する。

【0042】

以上のように、演算回路10は、判定器40の判定結果を基に、最大値MAX、最小値MIN及び最大値MAXを除く2数の差分DIFFを検出する。そして、最大値MAX、最小値MIN及び最大値MAXを除く2数の差分DIFFを、レジスタファイル101の対応するポートIN1〜IN3のそれぞれに出力することができる。つまり、演算回路10は、レジスタファイル101からデータを読み込んでから、途中の演算結果をレジスタファイル101に一時的に格納することなく、1回のサイクルで最大値MAX、最小値MINを算出することができる。換言すれば、演算回路10は、3つ以上の値を比較し、その最大値や最小値などを特定するために条件分岐処理を要する演算を、1サイクルで行うことができる。よって、複数のサイクルを経て3以上の値の最大値MAXや最小値MIN及びを算出する場合に比べ、より高速な計算が可能である。従って、本構成によれば、3つ以上の値の条件分岐処理を要する比較演算を高速に行うことができる演算回路及び演算装置を実現することができる。

【0043】

また、RGB色空間からHSV色空間への変換処理では、R、G及びBのいずれの値が最大であるかによって、式(1)〜(3)のいずれを用いるかが決定される。このため、条件分岐命令を用いた場合分けが必要となる。従って、通常の演算装置を用いると、条件分岐処理が必要となり、RGB色空間からHSV色空間への変換処理の高速化が妨げられる。しかしながら、判定器40は、符号フラグF1〜F3を参照することにより、データD0〜D2のいずれが最大値であるかを判定し、式(1)〜(3)のいずれを用いるかを知ることができる。従って、本構成によれば、RGB色空間からHSV色空間への変換処理において条件分岐処理を高速に行うことができる演算回路及び演算装置をさらに実現することができる。

【0044】

さらに、本構成によれば、上述のように式(1)〜(3)のいずれを用いるかを知ることができる。よって、判定器40がセレクタSEL13を制御することにより、RGB色空間からHSV色空間への変換処理でいずれの式を用いる場合でも、適切な差分DIFFを1サイクルで求めることが可能である。よって、演算装置100及び演算回路10によれば、RGB色空間からHSV色空間への変換処理を高速かつ効率的に行うことが可能である。

【0045】

なお、以上では、判定テーブル41は、予め判定器40に格納されていた。しかしながら、判定テーブル41の内容は、外部から命令を与えることで設定することも可能である。以下では、外部からの命令により判定テーブル41を設定する方法について説明する。図3は、外部から判定テーブル41を設定する場合の演算装置100の構成を模式的に示すブロック図である。

【0046】

判定器40には、演算装置100の外部の制御回路102から、判定情報設定命令SETが与えられる。判定情報設定命令SETは、32bitの情報量を有する命令であり、判定テーブル41を構成する制御信号CON1〜CON3の値を設定する命令である。図4は、判定テーブル41の設定値を表示した図である。図4に示すように、制御信号CON1〜CON3には、設定値d01〜d03、d11〜d13、d21〜d23、d31〜d33、d41〜d43、d51〜d53、d61〜d63、d71〜d73が割り当てられる。但し、命題D0<D1、D1<D2及びD2<D0が、全て真であることは有り得ないので、実際には、設定値d01〜d03、d11〜d13、d21〜d23、d31〜d33、d41〜d43、d51〜d53、d61〜d63に値を設定すればよい。

【0047】

設定値のそれぞれは、3bitの情報量が割り当てられる。従って32bitの判定情報設定命令SETでは、一度に10個の設定値を設定することが可能である。つまり、32bitの判定情報設定命令SETを3回与えることにより、判定テーブル41の設定値d01〜d03、d11〜d13、d21〜d23、d31〜d33、d41〜d43、d51〜d53、d61〜d63に具体的な値を設定することができる。この場合、判定情報設定命令SETは、以下の命令文で表現することが可能である。

判定情報設定命令SETを示す命令文

setfusion idx, val

【0048】

idxは、判定情報設定命令SETの命令の順番を示し、判定情報設定命令SETが3回与えられる場合には、0〜2のいずれかが割り充てられる。値valは、設定値d01〜d03、d11〜d13、d21〜d23、d31〜d33、d41〜d43、d51〜d53、d61〜d63に割り当てる値を示す。以下では、値valは、32bit即値で表現するものとする。

【0049】

図5は、実施の形態1にかかる判定情報設定命令SETの値valの構成例を示す図である。判定情報設定命令SETの値valは、例えば、2つの空きbit50と、それぞれ3bitの値e0〜e9により構成される。図6は、判定情報設定命令SETの値valと判定テーブル41の設定値との関係を示す図である。例えば、制御信号CON1〜CON3として、図2に示す値を設定する場合について検討する。

【0050】

まず、idx=0の場合、値e0〜e9は、それぞれ「0」、「2」、「1」、「0」、「2」、「1」、「2」、「1」、「0」、「0」となる。よって、判定情報設定命令SETの値valは、2進数表示では、図5に示す値となる。これを16進数で表される32bit即値に変換すると、「0x00512050」となる。idx=1の場合には、値e0〜e9は、それぞれ「0」、「1」、「1」、「1」、「0」、「2」、「1」、「2」、「2」、「0」となる。よって、判定情報設定命令SETの値valは、2進数表示では、図5に示す値となる。これを16進数で表される32bit即値に変換すると、「0x048a0248」となる。idx=2の場合には、値e0〜e9は、それぞれ「2」、「0」、「0」、「0」、「0」、「0」、「0」、「0」、「0」、「0」となる。よって、判定情報設定命令SETの値valは、2進数表示では、図5に示す値となる。これを16進数で表される32bit即値に変換すると、「0x00000002」となる。この場合、判定情報設定命令SETは、以下の命令文で表現することが可能である。

判定情報設定命令SETを示す命令文

setfusion 0, 0x00512050

setfusion 1, 0x048a0248

setfusion 2, 0x00000002

【0051】

以上のように、判定器40に判定情報設定命令SETを与えることで、判定テーブル41内の値を具体的に設定することが可能である。

【0052】

実施の形態2

次に、実施の形態2にかかる演算装置200について説明する。演算装置200は、実施の形態1にかかる演算装置100で行うHSV変換処理に加えて、3つのデータD0〜D2のソート処理を行うことができる装置である。図7は、実施の形態2にかかる演算装置200の構成を模式的に示すブロック図である。演算装置200は、実施の形態1にかかる演算装置100の構成転換例であり、具体的には演算回路の構成が異なる。演算装置200は、レジスタファイル101及び演算回路20を有する。レジスタファイル101については、実施の形態1と同様であるので、説明を省略する。

【0053】

演算回路20は、スロット11、12及び23、判定器40を有する。スロット11では、加減算器CAL11は、セレクタSEL23に演算結果C1を出力する。スロット11のその他の構成は、実施の形態1と同様であるので説明を省略する。スロット12では、加減算器CAL12は、セレクタSEL23に演算結果C2を出力する。スロット12のその他の構成は、実施の形態1と同様であるので説明を省略する。また、判定器40は演算回路10と同様であるので、説明を省略する。

【0054】

スロット23は、加減算器CAL13及びセレクタSEL23を有する。セレクタSEL23は、6入力1出力のセレクタであり、第3の選択回路に対応する。加減算器CAL13は、セレクタSEL23に演算結果C3を出力する。セレクタSEL23の入力ポートps0〜ps2には加減算器CAL11〜CAL13の演算結果C1〜C3がそれぞれ入力し、入力ポートps3〜ps5にはデータD0〜D2がそれぞれ入力する。そして、セレクタSEL23は、判定器40からの制御信号CON3に基づき、レジスタファイル101のポートIN3に、データD0〜D2のいずれかを中間値MIDとして出力する。スロット23のその他の構成は、スロット13と同様であるので説明を省略する。

【0055】

続いて、演算装置200の動作について説明する。演算装置200におけるHSV変換処理については実施の形態1にかかる演算装置100と同様であるので説明を省略し、以下では、ソート処理について説明する。演算装置200は、外部の制御回路102から判定器40に入力する判定情報設定命令SETで判定テーブルの設定値を変更することにより、HSV変換処理及びソート処理のいずれの処理を行うかを切り替えることが可能である。以下、ソート処理について具体的に説明する。

【0056】

スロット11では、HSV変換処理時と同様に、加減算器CAL11が、データD0の値からデータD1の値を減算し、減算結果を演算結果C1として出力する。また、加減算器CAL11は、減算結果に応じて、符号フラグF1を出力する。具体的には、加減算器CAL11は、演算結果C1の符号がマイナスである場合、すなわちD0<D1である場合には、符号フラグF1として「1」を出力する。一方、演算結果C1の符号がマイナスではない場合、すなわちD0≧D1である場合には、符号フラグF1として「0」を出力する。

【0057】

同様に、スロット12では、HSV変換処理時と同様に、加減算器CAL12が、データD1の値からデータD2の値を減算し、減算結果を演算結果C2として出力する。また、加減算器CAL12は、減算結果に応じて、符号フラグF2を出力する。具体的には、加減算器CAL12は、演算結果C2の符号がマイナスである場合、すなわちD1<D2である場合には、符号フラグF2として「1」を出力する。一方、演算結果C2の符号がマイナスではない場合、すなわちD1≧D2である場合には、符号フラグF2として「0」を出力する。

【0058】

同様に、スロット23では、HSV変換処理時と同様に、加減算器CAL13が、データD2の値からデータD0の値を減算し、減算結果を演算結果C3として出力する。また、加減算器CAL13は、減算結果に応じて、符号フラグF3を出力する。具体的には、加減算器CAL13は、演算結果C3の符号がマイナスである場合、すなわちD2<D0である場合には、符号フラグF3として「1」を出力する。一方、演算結果C3の符号がマイナスではない場合、すなわちD2≧D0である場合には、符号フラグF3として「0」を出力する。

【0059】

判定器40は、符号フラグF1〜F3に基づいて、データD0〜D2の大小関係を判定する。そして、判定器40は、データD0〜D2の大小関係に基づいて、制御信号CON1〜CON3を出力する。図8は、判定器40に格納されたソート処理時の判定テーブル42を示す図である。なお、判定テーブル42は、第2の判定テーブルに対応する。

【0060】

例えば、符号フラグF1〜F3が、それぞれ「0」、「0」、「1」であれば、命題「D0<D1」及び「D1<D2」は偽であり、命題「D2<D0」は真である。この場合、データD0〜D2については、「D0≧D1≧D2」の大小関係が成立している。この場合、判定器40は、制御信号CON1〜CON3として、それぞれ「0」、「2」、「4」を出力する。セレクタSEL11及びSEL12のそれぞれは、制御信号CON1及びCON2に応じて、入力ポートps0〜ps2のいずれかを選択する。セレクタSEL23は、制御信号CON3に応じて、入力ポートps0〜ps5のいずれかを選択する。具体的には、セレクタSEL11及びSEL12のそれぞれは、制御信号CON1及びCON2の値がk(kは0以上2以下の整数)である場合には、入力ポートpskを選択する。セレクタSEL23は、制御信号CON3の値がj(jは0以上5以下の整数)である場合には、入力ポートpsjを選択する。

【0061】

セレクタSEL11は、HSV変換処理時と同様に、制御信号CON1の値「0」に応じて、入力ポートps0に入力するデータD0を選択する。これにより、データD0が最大値MAXとして特定される。つまり、セレクタSEL11は、最大値選択セレクタとして機能する。そして、セレクタSEL11は、最大値MAXであるデータD0を、レジスタファイル101のポートIN1へ出力する。よって、レジスタファイル101のポートIN1は、常に最大値MAXを受け取ることとなる。

【0062】

セレクタSEL12は、HSV変換処理時と同様に、制御信号CON2の値「2」に応じて、入力ポートps2に入力するデータD2を選択する。これにより、データD2が最小値MINとして特定される。つまり、セレクタSEL12は、最小値選択セレクタとして機能する。そして、セレクタSEL12は、最小値MINであるデータD2を、レジスタファイル101のIN2へ出力する。よって、レジスタファイル101のポートIN2は、常に最小値MINを受け取ることとなる。

【0063】

セレクタSEL23は、制御信号CON3の値「4」に応じて、入力ポートps4に入力するデータD1を選択する。これにより、データD1が中間値MIDとして特定される。つまり、セレクタSEL23は、中間値選択セレクタとして機能する。そして、セレクタSEL23は、中間値MIDであるデータD1を、レジスタファイル101のポートIN3へ出力する。よって、レジスタファイル101のポートIN3は、常に中間値MIDを受け取ることとなる。

【0064】

以上では、符号フラグF1〜F3が、それぞれ「0」、「0」、「1」である場合を例としたが、符号フラグF1〜F3が他の場合でも、セレクタSEL11、SEL12及びSEL23は、最大値MAX、最小値MIN及び中間値MIDをそれぞれ出力することは言うまでもない。

【0065】

続いて、ソート処理用の判定テーブル42を設定する方法について説明する。図9は、外部から判定テーブル42を設定する場合の演算装置200の構成を模式的に示すブロック図である。演算装置200では、判定情報設定命令SETにより、以下に示す要領で、判定テーブル41を判定テーブル42に置換することが可能である。なお、同様の要領で、判定テーブル42を判定テーブル41に置換することが可能であることは、言うまでもない。

【0066】

判定器40には、演算装置200の外部の制御回路102から、判定情報設定命令SETが与えられる。判定テーブル42の設定値については、図4を用いて既述した判定テーブル41と同様であるため説明を省略する。また、判定情報設定命令SETの値valの構成については、図5を用いて既述したため説明を省略する。判定情報設定命令SETの値valと判定テーブル42の設定値との関係についても、図6を用いて既述したため説明を省略する。以下では、例えば、制御信号CON1〜CON3として、図8に示す値を設定する場合について検討する。図10は、実施の形態2にかかる判定情報設定命令SETの値valの構成例を示す図である。

【0067】

まず、idx=0の場合、値e0〜e9は、それぞれ「0」、「2」、「4」、「0」、「2」、「4」、「2」、「1」、「3」、「0」となる。よって、判定情報設定命令SETの値valは、2進数表示では、図10に示す値となる。これを16進数で表される32bit即値に変換すると、「0x06542110」となる。idx=1の場合には、値e0〜e9は、それぞれ「0」、「1」、「5」、「1」、「0」、「5」、「1」、「2」、「3」、「0」となる。よって、判定情報設定命令SETの値valは、2進数表示では、図11に示す値となる。これを16進数で表される32bit即値に変換すると、「0x068d0348」となる。idx=2の場合には、値e0〜e9は、それぞれ「2」、「0」、「4」、「0」、「0」、「0」、「0」、「0」、「0」、「0」となる。よって、判定情報設定命令SETの値valは、2進数表示では、図11に示す値となる。これを16進数で表される32bit即値に変換すると、「0x00000102」となる。この場合、判定情報設定命令SETは、以下の命令文で表現することが可能である。

判定情報設定命令SETを示す命令文

setfusion 0, 0x06542110

setfusion 1, 0x068d0348

setfusion 2, 0x00000102

【0068】

以上のように、演算回路20は、判定器40の判定結果を基に、最大値MAX、最小値MIN及び中間値MIDを検出する。そして、最大値MAX、最小値MIN及び中間値MIDを、レジスタファイル101の対応するポートIN1〜IN3のそれぞれに出力することができる。よって、演算回路20は、HSV変換処理のみならず、レジスタファイル101から読み込んだデータD0〜D2の大小関係を判定し、値をソートすることが可能である。換言すれば、演算回路10は、3つ以上の値を比較し、その最大値や最小値などを特定するために条件分岐処理を要する演算、具体的にはソート処理を1サイクルで行うことができる。従って、本構成によれば、3つ以上の値の条件分岐処理を要する比較演算を高速に行うことができる演算回路及び演算装置を実現することができる。さらに、ソート処理が可能となったことで、演算装置100及び演算回路10よりも高機能かつ汎用性に優れる演算装置200及び演算回路20を提供することができる。

【0069】

また、演算回路20は、レジスタファイル101からデータを読み込んでから、途中の演算結果をレジスタファイル101に一時的に格納することなく、1回のサイクルで最大値MAX、最小値MIN及び中間値MIDを求めることが可能である。従って、演算回路20は、ソート処理を高速に行うことが可能である。

【0070】

実施の形態3

次に、実施の形態3にかかる演算装置300について説明する。演算装置300は、実施の形態1にかかる演算装置100で行うHSV変換処理に加えて、RGB色空間からHSV色空間への変換で用いる定数を同時に指定することができる装置である。図11は、実施の形態3にかかる演算装置300の構成を模式的に示すブロック図である。演算装置300は、実施の形態1にかかる演算装置100の構成転換例であり、具体的には演算回路の構成が異なる。演算装置300は、レジスタファイル101及び演算回路30を有する。レジスタファイル101については、ポートIN4が追加された他は、実施の形態1と同様であるので説明を省略する。演算回路30は、スロット11〜13及び34、判定器43を有する。スロット11〜13は、演算回路10と同様であるので、説明を省略する。

【0071】

スロット34は、定数レジスタ341〜343、セレクタSEL34を有する。セレクタSEL34は、3入力1出力のセレクタであり、第4の選択回路に対応する。セレクタSEL34の入力ポートps0〜ps2は、定数レジスタ341〜343から、定数データCD0〜CD2がそれぞれ入力する。そして、セレクタSEL34は、判定器43からの制御信号CON4に基づき、レジスタファイル101のポートIN4に、定数データCD0〜CD2のいずれかを定数CONSTとして出力する。

【0072】

判定器43は、符号フラグF1〜F3に基づいて、格納されている判定テーブル43を参照し、セレクタSEL11〜SEL13に制御信号CON1〜CON3をそれぞれ出力し、スロット34のセレクタSEL34に制御信号CON4を出力する。なお、判定テーブル43は、第3の判定テーブルに対応する。

【0073】

続いて、演算装置300の動作について説明する。演算装置300のうち、最大値MAX、最小値MIN及び差分DIFFの算出を行う上述のHSV変換処理については、実施の形態1にかかる演算装置100と同様であるので、説明を省略する。よって、以下では、定数CONSTの算出方法について説明する。

【0074】

データD0〜D2を、RGB色空間における、R、G、Bのそれぞれに置き換えると、演算装置300は、前述の式(1)〜(5)中のMAX、MIN及び差分だけでなく、さらに式(1)〜(3)中の定数の値を算出することが可能である。ここで、定数とは、式(1)〜(3)の右辺第2項の値を意味し、式(1)における「0」、式(2)における「120」、式(3)における「240」を指す。

【0075】

判定器43は、符号フラグF1〜F3に基づいて、データD0〜D2の大小関係を判定する。そして、判定器43は、データD0〜D2の大小関係に基づいて、制御信号CON1〜CON4を出力する。図12は、判定器43に格納された判定テーブル44を示す図である。

【0076】

例えば、符号フラグF1〜F3が、それぞれ「0」、「0」、「1」であれば、命題「D0<D1」及び「D1<D2」は偽であり、命題「D2<D0」は真である。この場合、データD0〜D2については、「D0≧D1≧D2」の大小関係が成立している。この場合、判定器43は、制御信号CON1〜CON4として、それぞれ「0」、「2」、「1」、「0」を出力する。

【0077】

セレクタSEL34は、制御信号CON4に応じて、入力ポートps0〜ps2のいずれかを選択する。具体的には、セレクタSEL34は、制御信号CON4の値がk(kは0以上2以下の整数)である場合には、入力ポートpskを選択する。上述のように、制御信号CON4は「0」であるので、セレクタSEL34は、入力ポートps0を選択する。セレクタSEL34は、定数データCD0を、定数CONSTとして出力する。

【0078】

このとき、データD0〜D2がRGB色空間のR、G及びBにそれぞれ対応すると考えると、定数データCD0〜CD2の値は、それぞれ「0」、「120」、「240」である。上述の例では、データD0が最大であるので、式(1)を用いた計算が行われる。従って、セレクタSEL34は、式(1)の定数部分を示す定数データCD0を、定数CONSTとして選択する。同様に、G又はB、すなわちデータD1又はD2が最大である場合にも、判定器43が判定テーブル44を用いて判定を行うことにより、適切な定数を算出することが可能である。

【0079】

なお、演算装置300を用いてHSV変換処理及び定数の算出処理を行う場合、演算装置300に与える命令は、例えばC言語を用いると、以下の命令文で表される。

HSV変換処理及び定数の演算処理を表す命令文

vmax=(d0>d1)?((d0>d2)?d0:d2):((d1>d2)?d1:d2);

vmin = (d0<d1)?((d0<d2)?d0:d2):((d1<d2)?d1:d2);

if (vmax == d0){

vdiff = d1-d2;

vconst=0;

}else if (vmax == d1){

Vdiff = d2-d0;

vconst=120;

}else{

Vdiff = d0-d1;

vconst=240;

H = (vdiff*60)/(vmax-vmin)+vconst

【0080】

上記の命令文において、vmaxは最大値MAXに、vminは最小値MINに、vdiffは差分DIFFに、constは定数CONSTに、d0〜d2はデータD0〜D2にそれぞれ対応する。第1文では、条件演算子を用いて、d0〜d2の最大値vmaxを算出する。第2文では、条件演算子を用いて、d0〜d2の最小値vminを算出する。第3文以降では、if文を用いて、d0〜d2のいずれが最大値であるかに応じて差分vdiffを計算するとともに、式(1)〜(3)における定数の値を特定する。

【0081】

その他の実施の形態

なお、本発明は上記実施の形態に限られたものではなく、趣旨を逸脱しない範囲で適宜変更することが可能である。例えば、実施の形態3では、データD0〜D2のソート処理を行う例について説明したが、3つのレジスタに演算結果C1〜C3を入力させ、演算結果C1〜C3のソート処理を行う構成とすることも可能である。

【0082】

図3及び図9では、制御回路102は演算装置100及び200の内部に設けられているが、演算装置100及び200の外部に設けることも可能である。

【0083】

実施の形態2では、判定テーブル41は、判定情報設定命令SETにより書き換えられるが、これは例示に過ぎない。例えば、判定器40に、HSV変換処理用の判定テーブルとソート処理用の判定テーブルを予め格納しておき、制御回路からの選択信号により、用いる判定テーブルを指定することも可能である。

【0084】

上述の実施の形態における判定情報設定命令SETの構成はあくまで例示である。従って、判定情報設定命令SETの値valでの値e0〜e9は、別の順序で配置することも可能である。また、空きビットの位置も、別の位置とすることも可能である。さらに、判定テーブルの設定と値e0〜e9との対応関係も別の関係とすることもできる。なお、判定情報設定命令SETの値valを16進法を用いて表現したが、他の進法を用いて表現してもよい。

【符号の説明】

【0085】

11〜13、23、34 スロット

341〜343 定数レジスタ

10、20、30 演算回路

40、43 判定器

41、42、44 判定テーブル

100、200、300 演算装置

101 レジスタファイル

102 制御回路

C1〜C3 演算結果

CAL11〜CAL13 加減算器

CD0 定数データ

CD0〜CD2 定数データ

CON1〜CON4 制御信号

CONST 定数

D0〜D2 データ

DIFF 差分

F1〜F3 符号フラグ

IN1〜IN4 ポート

MAX 最大値

MID 中間値

MIN 最小値

ps0〜ps5 入力ポート

SEL11〜SEL13、SEL23、SEL34 セレクタ

SET 判定情報設定命令

【特許請求の範囲】

【請求項1】

入力するデータに対して演算を行い、前記演算結果に基づいて生成したフラグ情報を出力する複数の演算器と、

前記複数の演算器に入力する前記データのいずれかを選択する複数の選択回路と、

前記複数の演算器からの前記フラグ情報が入力し、前記複数の選択回路のそれぞれの選択動作を制御する判定器と、を備える、

演算回路。

【請求項2】

前記判定器は、格納された判定テーブルと前記フラグ情報とを照合して前記複数の演算器に入力する前記データの大小関係を判定し、判定結果に基づいて前記複数の選択回路のそれぞれの選択動作を制御することを特徴とする、

請求項1に記載の演算回路。

【請求項3】

前記複数の演算器のそれぞれは、2つのデータの一方から他方を減算した値の符号を示す符号フラグを、前記フラグ情報として出力する、

請求項1又は2に記載の演算回路。

【請求項4】

前記判定器は、前記複数の選択回路のいずれかに、前記複数の演算器に入力する前記データの最大値又は最小値を選択させることを特徴とする、

請求項3に記載の演算回路。

【請求項5】

前記複数の演算器は、第1及び第2のデータが入力する第1の演算器と、第2及び第3のデータが入力する第2の演算器と、第3及び第1のデータが入力する第3の演算器と、を含み、

前記複数の選択回路は、前記第1乃至第3のデータが入力する第1乃至第3の選択回路を含むことを特徴とする、

請求項4に記載の演算回路。

【請求項6】

前記第1の演算器は、前記第1のデータから前記第2のデータを減算した第1の演算結果の符号を示す第1の符号フラグを出力し、

前記第2の演算器は、前記第2のデータから前記第3のデータを減算した第2の演算結果の符号を示す第2の符号フラグを出力し、

前記第3の演算器は、前記第3のデータから前記第1のデータを減算した第3の演算結果の符号を示す第3の符号フラグを出力することを特徴とする、

請求項5に記載の演算回路。

【請求項7】

前記判定器は、格納された第1の判定テーブルと前記第1乃至第3の符号フラグとを照合することにより、前記第1乃至第3のデータの大小関係を判定し、

判定結果に基づいて、前記第1の選択回路に前記第1乃至第3のデータの最大値を選択させ、前記第2の選択回路に前記第1乃至第3のデータの最小値を選択させることを特徴とする、

請求項6に記載の演算回路。

【請求項8】

前記第1乃至第3の演算器は、それぞれ前記第1乃至第3の演算結果をさらに出力し、

前記第3の選択回路には、さらに前記第1乃至第3の演算結果が入力し、

前記判定器は、前記判定結果に基づいて、前記第3の選択回路に、前記第1乃至第3の演算器のうち、前記第1乃至第3のデータの最大値が入力しないものからの前記演算結果を選択させることを特徴とする、

請求項7に記載の演算回路。

【請求項9】

前記判定器は、格納された前記第1の判定テーブルとは異なる第2の判定テーブルと前記第1乃至第3の符号フラグとを照合することにより、前記第1乃至第3のデータの大小関係を判定し、

判定結果に基づいて、前記第1の選択回路に前記第1乃至第3のデータの最大値を選択させ、前記第2の選択回路に前記第1乃至第3のデータの最小値を選択させ、前記第3の選択回路に前記第1乃至第3のデータの前記最大値及び前記最小値以外の値を選択させることを特徴とする、

請求項6乃至8のいずれか一項に記載の演算回路。

【請求項10】

前記判定器には、当該判定器の外部からの信号により、前記第1の判定テーブル又は前記第2の判定テーブルが択一的に設定されることを特徴とする、

請求項9に記載の演算回路。

【請求項11】

前記第1乃至第3のデータに対応する定数がそれぞれ格納された第1乃至第3のレジスタを更に備え、

前記複数の選択回路は、前記第1乃至第3のレジスタに格納された定数のいずれかを選択する第4の選択回路をさら含み、

前記判定器は、格納された前記第1の判定テーブルとは異なる第3の判定テーブルと前記第1乃至第3の符号フラグとを照合することにより、前記第1乃至第3のデータの大小関係を判定し、

判定結果に基づいて、前記第1の選択回路に前記第1乃至第3のデータの最大値を選択させ、前記第2の選択回路に前記第1乃至第3のデータの最小値を選択させ、前記第3の選択回路に、前記第1乃至第3の演算器のうち、前記第1乃至第3のデータの最大値が入力しないものからの前記演算結果を選択させ、前記第4の選択回路に、前記第1乃至第3のレジスタに格納された定数のうち、最大値である前記第1乃至第3のデータいずれかに対応する前記定数を選択させることを特徴とする、

請求項6に記載の演算回路。

【請求項12】

前記第1乃至第3のデータは、それぞれRGB色空間におけるR、G及びBの値であることを特徴とする、

請求項5乃至11のいずれか一項に記載の演算回路。

【請求項13】

請求項1乃至12のいずれか一項に記載の前記演算回路を有することを特徴とする、

演算装置。

【請求項14】

前記複数の演算器に前記データを出力し、前記複数の選択回路からの出力を受け取るレジスタファイルを備えることを特徴とする、

請求項13に記載の演算装置。

【請求項1】

入力するデータに対して演算を行い、前記演算結果に基づいて生成したフラグ情報を出力する複数の演算器と、

前記複数の演算器に入力する前記データのいずれかを選択する複数の選択回路と、

前記複数の演算器からの前記フラグ情報が入力し、前記複数の選択回路のそれぞれの選択動作を制御する判定器と、を備える、

演算回路。

【請求項2】

前記判定器は、格納された判定テーブルと前記フラグ情報とを照合して前記複数の演算器に入力する前記データの大小関係を判定し、判定結果に基づいて前記複数の選択回路のそれぞれの選択動作を制御することを特徴とする、

請求項1に記載の演算回路。

【請求項3】

前記複数の演算器のそれぞれは、2つのデータの一方から他方を減算した値の符号を示す符号フラグを、前記フラグ情報として出力する、

請求項1又は2に記載の演算回路。

【請求項4】

前記判定器は、前記複数の選択回路のいずれかに、前記複数の演算器に入力する前記データの最大値又は最小値を選択させることを特徴とする、

請求項3に記載の演算回路。

【請求項5】

前記複数の演算器は、第1及び第2のデータが入力する第1の演算器と、第2及び第3のデータが入力する第2の演算器と、第3及び第1のデータが入力する第3の演算器と、を含み、

前記複数の選択回路は、前記第1乃至第3のデータが入力する第1乃至第3の選択回路を含むことを特徴とする、

請求項4に記載の演算回路。

【請求項6】

前記第1の演算器は、前記第1のデータから前記第2のデータを減算した第1の演算結果の符号を示す第1の符号フラグを出力し、

前記第2の演算器は、前記第2のデータから前記第3のデータを減算した第2の演算結果の符号を示す第2の符号フラグを出力し、

前記第3の演算器は、前記第3のデータから前記第1のデータを減算した第3の演算結果の符号を示す第3の符号フラグを出力することを特徴とする、

請求項5に記載の演算回路。

【請求項7】

前記判定器は、格納された第1の判定テーブルと前記第1乃至第3の符号フラグとを照合することにより、前記第1乃至第3のデータの大小関係を判定し、

判定結果に基づいて、前記第1の選択回路に前記第1乃至第3のデータの最大値を選択させ、前記第2の選択回路に前記第1乃至第3のデータの最小値を選択させることを特徴とする、

請求項6に記載の演算回路。

【請求項8】

前記第1乃至第3の演算器は、それぞれ前記第1乃至第3の演算結果をさらに出力し、

前記第3の選択回路には、さらに前記第1乃至第3の演算結果が入力し、

前記判定器は、前記判定結果に基づいて、前記第3の選択回路に、前記第1乃至第3の演算器のうち、前記第1乃至第3のデータの最大値が入力しないものからの前記演算結果を選択させることを特徴とする、

請求項7に記載の演算回路。

【請求項9】

前記判定器は、格納された前記第1の判定テーブルとは異なる第2の判定テーブルと前記第1乃至第3の符号フラグとを照合することにより、前記第1乃至第3のデータの大小関係を判定し、

判定結果に基づいて、前記第1の選択回路に前記第1乃至第3のデータの最大値を選択させ、前記第2の選択回路に前記第1乃至第3のデータの最小値を選択させ、前記第3の選択回路に前記第1乃至第3のデータの前記最大値及び前記最小値以外の値を選択させることを特徴とする、

請求項6乃至8のいずれか一項に記載の演算回路。

【請求項10】

前記判定器には、当該判定器の外部からの信号により、前記第1の判定テーブル又は前記第2の判定テーブルが択一的に設定されることを特徴とする、

請求項9に記載の演算回路。

【請求項11】

前記第1乃至第3のデータに対応する定数がそれぞれ格納された第1乃至第3のレジスタを更に備え、

前記複数の選択回路は、前記第1乃至第3のレジスタに格納された定数のいずれかを選択する第4の選択回路をさら含み、

前記判定器は、格納された前記第1の判定テーブルとは異なる第3の判定テーブルと前記第1乃至第3の符号フラグとを照合することにより、前記第1乃至第3のデータの大小関係を判定し、

判定結果に基づいて、前記第1の選択回路に前記第1乃至第3のデータの最大値を選択させ、前記第2の選択回路に前記第1乃至第3のデータの最小値を選択させ、前記第3の選択回路に、前記第1乃至第3の演算器のうち、前記第1乃至第3のデータの最大値が入力しないものからの前記演算結果を選択させ、前記第4の選択回路に、前記第1乃至第3のレジスタに格納された定数のうち、最大値である前記第1乃至第3のデータいずれかに対応する前記定数を選択させることを特徴とする、

請求項6に記載の演算回路。

【請求項12】

前記第1乃至第3のデータは、それぞれRGB色空間におけるR、G及びBの値であることを特徴とする、

請求項5乃至11のいずれか一項に記載の演算回路。

【請求項13】

請求項1乃至12のいずれか一項に記載の前記演算回路を有することを特徴とする、

演算装置。

【請求項14】

前記複数の演算器に前記データを出力し、前記複数の選択回路からの出力を受け取るレジスタファイルを備えることを特徴とする、

請求項13に記載の演算装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−37613(P2013−37613A)

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願番号】特願2011−174849(P2011−174849)

【出願日】平成23年8月10日(2011.8.10)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願日】平成23年8月10日(2011.8.10)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

[ Back to top ]