炭化珪素半導体装置の製造方法

【課題】炭化珪素ショットキーダイオードの製造において、ダイオードの順方向特性、特に障壁高さφBを安定させて、リーク電流のばらつきを低減させることが可能な半導体装置を提供する。

【解決手段】エピタキシャル層2上に乾式熱酸化によりシリコン酸化膜OX1を形成し、SiC基板1の裏面にオーミック電極3を形成し、その後、SiC基板1をアニールしてオーミック電極3とSiC基板1の裏面との間にオーミック接合を形成し、シリコン酸化膜OX1を除去した後、エピタキシャル層2上にショットキー電極4を形成する。その後、シンターを行い、ショットキー電極4とエピタキシャル層との間にショットキー接合を形成する。

【解決手段】エピタキシャル層2上に乾式熱酸化によりシリコン酸化膜OX1を形成し、SiC基板1の裏面にオーミック電極3を形成し、その後、SiC基板1をアニールしてオーミック電極3とSiC基板1の裏面との間にオーミック接合を形成し、シリコン酸化膜OX1を除去した後、エピタキシャル層2上にショットキー電極4を形成する。その後、シンターを行い、ショットキー電極4とエピタキシャル層との間にショットキー接合を形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は炭化珪素半導体装置の製造方法に関し、特に、炭化珪素ショットキーバリアダイオードの製造方法に関する。

【背景技術】

【0002】

炭化珪素ショットキーバリアダイオード(以下、SiC−SBDと記す)の製造においては、ショットキーメタルの選択と、順方向特性の安定化が重要である。ショットキーメタルとして、Ti(チタン)、Ni(ニッケル)、Mo(モリブデン)およびW(タングステン)などが一般的であるが、例えばTiショットキーバリアダイオードを製造する場合に、裏面の電極としてNiを採用しNiのオーミック接合を形成する場合には次のようなプロセス上の特徴および問題点を抱えることになる。

【0003】

すなわち、kV級の高耐圧のSiC−SBDは、炭化珪素基板上に形成されたn型のエピタキシャル層上にショットキー電極が形成される構成を有しているが、この構造では、エピタキシャル層とショットキー電極との接合面の端縁部に電界が集中し易くなるので、その接合面(ショットキー接合面)の端縁部に対応するエピタキシャル層の上層部に電界集中緩和のためのp型終端構造を形成することが一般的である。

【0004】

p型終端構造は、SBDの電極領域を囲むように形成されたp型不純物領域であり、その形成には、一般にAl(アルミニウム)、B(ボロン)等のp型不純物をn型のエピタキシャル層にイオン注入し、1500℃以上の高温熱処理で活性化アニールする方法が採られる。

【0005】

良好な特性のショットキー接合を得るには、この高温熱処理時に生じるSiC表面の変質層を除去する必要があるが、この変質層を除去する技術としては、例えば特許文献1〜5に記載された技術が知られている。

【0006】

特許文献1には、この変質層を除去する方法として、活性化アニール後にSiC表層を犠牲酸化し、表層に40nm以上140nm未満の犠牲酸化膜を形成し、その犠牲酸化膜と共に変質層を除去する方法が開示されている。

【0007】

特許文献2には、フッ酸処理による自然酸化膜の除去に続いて、水素と酸素との混合ガスのプラズマやフッ素原子を含むガスのプラズマによるプラズマエッチングによりSiCの表面を清浄化する方法が開示されている。

【0008】

特許文献3には、約100nmの厚さの変質層が生じること、および、約100nmの厚さの変質層を水素を含む雰囲気中のエッチングまたは機械的な研磨により除去する方法が開示されている。

【0009】

特許文献4には、活性化アニール後に、基板の表裏両面に1160℃の酸素雰囲気中で熱酸化膜を形成し、その直後に当該熱酸化膜をBHF溶液で除去する方法が開示されている。

【0010】

また、従来よりSiC−SBDの製造においては、ダイオードの順方向特性、特に障壁高さφBやn値(理想係数)を安定させるためには、ショットキーメタルを形成する直前まで炭化珪素基板上をプロセス保護膜で覆っておき、当該プロセス保護膜を除去してショットキーメタル(ここではTi)を成膜する方法や、ショットキーメタルを形成した後に、400〜600℃程度でTiシンターをする方法が効果的であることが知られている。

【0011】

例えばTiショットキーバリアダイオードにおいてシンターを実施しないと、障壁高さφBは、およそ1.05〜1.25eVの範囲に渡って大きくばらつく。これでは個々のSiC−SBD素子の特性のばらつきが大きくなり、シリコンIGBTやSiC−MOSFETと合わせてスイッチング素子、パワーモジュール等を構成する際、特性を揃えることができないという問題や、良品選別規格を厳しくした場合には良品率が低下するという問題が起こりうる。このため、特性の揃った半導体デバイスを製作することが量産プロセスおよび事業化に際して重要である。

【0012】

しかしながら、このようにプロセス保護膜として前工程で犠牲酸化膜を形成したり、ショットキーメタルとしてTiを形成した後に、400〜600℃程度のシンターを行っても、ダイオードの順方向特性、特に障壁高さφBの安定性は、実用化を想定して要求される仕様に対して満足すべき結果が得られず、逆方向リーク電流のばらつきも大きいという問題があった。

【先行技術文献】

【特許文献】

【0013】

【特許文献1】特開2008−53418号公報

【特許文献2】特開2001−35838号公報

【特許文献3】特開2004−363326号公報

【特許文献4】特開2007−141950号公報

【発明の概要】

【発明が解決しようとする課題】

【0014】

本発明は上記のような問題点を解消するためになされたもので、炭化珪素ショットキーダイオードの製造において、ダイオードの順方向特性、特に障壁高さφBを安定させて、リーク電流のばらつきを低減させることが可能な半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0015】

本発明に係る炭化珪素半導体装置の製造方法の態様は、第1導電型の炭化珪素基板を準備する工程(a)と、前記炭化珪素基板の一方主面上に第1導電型のエピタキシャル層《2》を形成する工程(b)と、前記エピタキシャル層の上層部に、電極領域《17》となる部分を囲むように第2導電型の不純物をイオン注入して、終端構造を形成する工程(c)と、前記エピタキシャル層上に乾式熱酸化によりシリコン酸化膜を形成する工程(d)と、前記炭化珪素基板の他方主面上に第1の金属層を形成する工程(e)と、前記工程(e)の後、前記炭化珪素基板を第1の温度で熱処理し、前記第1の金属層と前記炭化珪素基板の前記他方主面との間にオーミック接合を形成する工程(f)と、前記工程(f)の後、前記シリコン酸化膜を除去する工程(g)と、前記工程(g)の後、前記エピタキシャル層上に第2の金属層《4》を形成する工程(h)と、前記工程(h)の後、前記炭化珪素基板を第2の温度で熱処理し、前記第2の金属層と前記エピタキシャル層との間にショットキー接合を形成する工程(i)とを備えている。

【発明の効果】

【0016】

本発明に係る炭化珪素半導体装置の製造方法の態様によれば、ダイオードの順方向特性、特に障壁高さφBを安定させるとともに、逆方向リーク電流のばらつきを低減させた炭化珪素半導体装置を得ることができる。

【図面の簡単な説明】

【0017】

【図1】SiCウェハにおける半導体チップのレイアウトの一例を示す平面図である。

【図2】半導体チップのレイアウトの部分平面図である。

【図3】チップ領域の断面構成を示す断面図である。

【図4】本発明に係る実施の形態1のSiC−SBDの製造工程を示す断面図である。

【図5】本発明に係る実施の形態1のSiC−SBDの製造工程を示す断面図である。

【図6】本発明に係る実施の形態1のSiC−SBDの製造工程を示す断面図である。

【図7】本発明に係る実施の形態1のSiC−SBDの製造工程を示す断面図である。

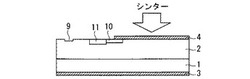

【図8】本発明に係る実施の形態1のSiC−SBDの製造工程を示す断面図である。

【図9】本発明に係る実施の形態1のSiC−SBDの製造工程を示す断面図である。

【図10】本発明に係る実施の形態1のSiC−SBDの製造工程を示す断面図である。

【図11】本発明に係る実施の形態1のSiC−SBDの製造工程を示す断面図である。

【図12】本発明に係る実施の形態1のSiC−SBDの製造工程を示す断面図である。

【図13】Tiシンターの最適温度を示す図である。

【図14】本発明に係る実施の形態2のSiC−SBDの製造工程を示す断面図である。

【図15】本発明に係る実施の形態2のSiC−SBDの製造工程を示す断面図である。

【図16】本発明に係る実施の形態2のSiC−SBDの製造工程を示す断面図である。

【図17】注入スルー膜を介さずにGR領域を形成した場合の注入不純物の濃度プロファイルを模式的に示す図である。

【図18】注入スルー膜を介してGR領域を形成した場合の注入不純物の濃度プロファイルを模式的に示す図である。

【図19】FLR領域を有するSiC−SBDの断面図である。

【図20】FLR領域の製造工程を示す断面図である。

【図21】本発明に係る実施の形態3のSiC−SBDの製造工程を示す断面図である。

【図22】本発明に係る実施の形態3のSiC−SBDの製造工程を示す断面図である。

【図23】本発明に係る実施の形態3のSiC−SBDの製造工程を示す断面図である。

【図24】本発明に係る実施の形態3のSiC−SBDの製造工程を示す断面図である。

【発明を実施するための形態】

【0018】

SiCのエピタキシャル成長においては、基板結晶のポリタイプを正しく継承させるため、ステップ制御エピタキシーが用いられる。ステップ制御エピタキシーでは、基板面方位を基本結晶面(basal plane)である(0001)面より数度傾けることでステップ状の表面構造を実現したオフ角(オフアングル)基板を使用する。

【0019】

ポリタイプが4HのSiC基板の場合は、<112_0>方向(“_”は2の上に付されるバーラインを示す)に8゜あるいは4゜傾斜させて得られた基板を用いることが標準的である。

【0020】

以下に説明する本発明に係る炭化珪素半導体装置の製造方法を用いて作製したSiC−SBDでは、オフ角が8゜の基板を用いた場合、ウェハプロセス完了後の障壁高さは1.25≦φB≦1.29の範囲となり、オフ角が4°基板を用いた場合、1.21≦φB≦1.25の範囲となり、何れの場合も安定した結果が得られた。

【0021】

以下、オフ角が8゜の基板を用いた場合を例に採って、本発明に係る炭化珪素半導体装置の製造方法の実施の形態について説明する。

【0022】

<実施の形態1>

図1は、SiCウェハWFにおける半導体チップのレイアウトの一例を示す平面図であり、SiCウェハWFに縦横に複数のダイシングラインDLが設定されている。ダイシングラインDLによって囲まれる四角形状の領域がチップ領域CHであり、チップ領域CHをダイシングすることで、個々に独立したSiC−SBDのチップが得られる。

【0023】

図2は、図1に示した領域Xで囲まれる部分を示す平面図であり、SiC−SBDの上面構造を示している。なお、図2においては、後にショットキー電極が形成される電極領域17と、それを囲むGR(Guard Ring)領域10およびJTE(Junction Termination Extension)領域11を示しており、電極領域17上のショットキー電極等が形成される前の状態を示している。

【0024】

なお、図2には2行2列の4つのチップ領域CHを示しているが、これは、フォトリソグラフィにおける1ショットで露光されるチップ領域が4つの場合を例示している。そして、当該4つのチップ領域を規定するダイシングラインDL上には、フォトリソグラフィに際して必要となる露光マスクの位置合わせのための位置合わせマーク9が複数設けられている。

【0025】

位置合わせマーク9は、平面視形状が四角形をなし、図面に向かって最上部左側のチップ領域CHの上辺側のダイシングラインDL上と、図面に向かって最下部右側のチップ領域CHの下辺側のダイシングラインDL上に設けられているが、位置合わせマーク9の平面視形状および配置は一例に過ぎない。

【0026】

図3は、図2におけるチップ領域CHのA−A線での断面構成を表す断面図である。図3に示すように、n型のSiC基板1上にn型のエピタキシャル層2が形成され、エピタキシャル層2の上層部の電極領域17の外側に深さ0.6μm程度、幅20μm程度のGR領域10および深さ0.8μm程度、幅20μm程度のJTE領域11が形成され、JTE領域11のさらに外側に位置合わせマーク9が形成されている。

【0027】

GR領域10およびJTE領域11は、SiC−SBDにkV超級の耐圧を安定して確保するために、ショットキー電極端部の電界集中を緩和するために設けられる。GR領域10だけでも電界の集中は緩和できるが、さらにその外側に連続してGR領域10よりも不純物濃度が若干薄いJTE領域11を設けることで、表面電界を低減する構成としている。

【0028】

次に、製造工程を順に示す断面図である図4〜図12を用いて、実施の形態1に係るSiC−SBDの製造方法について説明する。

【0029】

まず、図4に示す工程において、ポリタイプが4Hの(0001)シリコン面を有するオフ角8°のn型のSiC基板1を準備する。SiC基板1のn型不純物濃度は比較的高く(n+)、その抵抗率は、0.02Ω・cm程度である。

【0030】

次に、SiC基板1の(0001)シリコン面(これを一方主面と呼称)上に、SiC基板1に比べて比較的低濃度(5×1015/cm3程度)n型不純物を含むエピタキシャル層2をエピタキシャル成長させる。エピタキシャル層2の厚さは、耐圧に応じて決められ、600V〜1700V程度の耐圧の場合は、5〜15μm程度の厚さとする。

【0031】

その後、エピタキシャル層2上にレジストマスクRM1を形成し、そこに位置合わせマーク9の形成のための開口部OP1をフォトリソグラフィにより形成する。そして、開口部OP1を介してエピタキシャル層2の表面を0.3μm程度エッチングすることで位置合わせマーク9を形成する。以後の、フォトリソグラフィでは、この位置合わせマーク9を目印として用いて露光マスクの重ね合わせを行う。

【0032】

次に、レジストマスクRM1を除去した後、図5に示す工程においてエピタキシャル層2上にレジストマスクRM2を形成し、そこにGR領域10を形成するための開口部OP2をフォトリソグラフィによりパターニングする。そして、レジストマスクRM2の上方からp型不純物として、例えばAlのイオン注入を行い、開口部OP2を介してエピタキシャル層2の上層部にGR領域10を形成する。このときの注入条件は、例えば、350keVのエネルギーでピーク濃度が5×1017/cm3程度となるように注入を行う。

【0033】

次に、レジストマスクRM2を除去した後、図6に示す工程においてエピタキシャル層2上にレジストマスクRM3を形成し、そこにJTE領域11を形成するための開口部OP2をフォトリソグラフィによりパターニングする。そして、レジストマスクRM3の上方からp型不純物として、例えばAlのイオン注入を行い、開口部OP3を介してエピタキシャル層2の上層部にJTE領域11を形成する。このときの注入条件は、例えば、500keVのエネルギーでピーク濃度が2×1017/cm3程度となるように注入を行う。

【0034】

GR領域10およびJTE領域11を終端構造として完成させるためには、注入した不純物をアニールにより活性化する必要がある。このためには、レジストマスクRM2を除去した後、例えば、RTA(Rapid Thermal Annealing)タイプのアニール炉を用いて、常圧Ar雰囲気でアニールを行う。この場合、バンチングステップと呼ばれる凹凸面の発生を抑制する手法として、アニールに先だって、グラファイトキャップ(G−cap)と呼称されるカーボン保護膜をSiCウェハの全表面に形成することが一般的ある。グラファイトキャップを形成したSiCウェハを、例えば枚葉式RTAアニール炉を用いて、少なくとも1500〜1700℃の温度範囲で10分程度アニールすれば、p型不純物は50〜90%の比率で活性化し、終端構造として十分に機能する。

【0035】

終端構造の完成により、エピタキシャル層とショットキー電極との接合面の端縁部での電界集中を緩和することができる。

【0036】

また、グラファイトキャップを形成することで、1nm以上のバンチングステップが発生することもない。活性化率が高いことは注入工程で崩れた結晶の再結晶化状態をより完全な状態にしている指標となり、半導体デバイスとしての高信頼性の実現に寄与する。

【0037】

なお、グラファイトキャップを設けずにアニールすると、1nm以上のバンチングステップが発生し、後に形成する熱酸化膜の厚みのばらつきが増し、当該熱酸化膜除去後も局所的に酸化膜が残る原因となり、リーク電流を増大させる可能性がある。

【0038】

グラファイトキャップの形成には、例えば液体材料C2H5OHを用いCVD(Chemical Vapor Deposition)によりおよそ20nm以上の膜厚を形成すれば十分である。例えば900℃、60分で40〜50nm形成可能である。活性化アニール後の除去はドライアッシングすればよい。

【0039】

また、グラファイトキャップを形成せずにバンチングステップを抑制する方法として、ファーネスタイプのSiC−CVD装置を用いて、例えば、減圧されたH2およびC3H8雰囲気で1350℃、15分程度のアニールを実施する方法が挙げられる。このアニール条件はAr雰囲気でのアニールと比較しながら、バンチングステップを1nm未満に抑えられるよう雰囲気圧力、温度、時間を調整して得られたものであり、このようなアニール条件を採用することで、バンチングステップに代表されるアニール後の表面の凹凸を1nm未満に抑えることが可能となる。

【0040】

上述した活性化アニールを行った後は、エピタキシャル層2の最表面から100〜150nmの深さに及ぶ変質層(ダメージ層)を除去するために、ドライエッチングを行う。

【0041】

エピタキシャル層2の表面の変質層は、次の工程で形成する熱酸化膜では除去しきれないので、予めドライエッチングにより除去しておくことで、熱酸化膜除去後に、良質なエピタキシャル層2の表面にショットキー電極を形成することができる。

【0042】

変質層を除去した後は、SiCウェハの(0001_)カーボン面(“_”は1の上に付されるバーラインを示す)、すなわちSiC基板1のエピタキシャル層2が形成された一方主面とは反対側の他方主面(裏面)にオーミック電極を形成するが、それに先だって、図7に示す工程において、エピタキシャル層2の上に、15〜40nmの厚さのシリコン酸化膜OX1を形成する。

【0043】

このシリコン酸化膜OX1は、SiCウェハの裏面にオーミック電極を形成した後、1000℃程度のアニールを行うが、その際に、オーミック電極の材料であるNiや、アニール装置内部に滞留する金属不純物等でエピタキシャル層2の表面が汚染されるのを防止するプロセス保護膜であり、乾燥酸素雰囲気中で行う乾式熱酸化により形成される。

【0044】

ここで、乾式熱酸化によりシリコン酸化膜OX1を形成する理由について説明する。例えば1200Vの耐圧を有するSiC−SBDを製作する場合、注入不純物の活性化アニール後の熱酸化膜を乾式酸化および湿式酸化により形成した場合、完成したSBDの逆方向リーク電流特性に顕著な有意差が生じる。

【0045】

すなわち乾式酸化で形成したシリコン酸化膜をフッ酸の湿式エッチングにより除去した後、ショットキー電極(Ti)を形成して得られたSBDと、湿式酸化で形成したシリコン酸化膜をフッ酸の湿式エッチングにより除去した後、ショットキー電極(Ti)を形成して得られたSBDとでは、1200V印加時における逆方向リーク電流の典型値はそれぞれ、10〜100μA/cm2、1〜10mA/cm2であり、およそ1〜3桁も異なることとなる。

【0046】

この顕著な有意差を生じる理由については次のようなモデルで説明される。すなわち、乾式酸化ではゆっくりとした等方的な酸化が進行し、このため余剰炭素も熱平衡的に分散する傾向があると考えられる。

【0047】

一方、湿式酸化では化学的作用が顕著になり酸化速度の面方位依存性や結晶欠陥での優先的酸化、増殖酸化が進行し、余剰炭素の局所析出の可能性がある。この差異により酸化膜除去後の表面平坦性に関しては、湿式酸化で形成した酸化膜を除去する場合の方が局所的凹凸が発生しやすく、それらが逆リーク電流を増大させる要因となるものと考えられる。なおSiCの熱酸化についての一般的なモデル説明は例えば、「SiC素子の基礎と応用」(オーム社、荒井和雄・吉田貞史共編)の第82,83頁に記載がある。

【0048】

また、シリコン酸化膜OX1の厚さを15〜40nmとする理由は以下の通りである。すなわち、プロセス保護膜としての効果を得るには、最低でも数原子層以上に相当する15nm以上の厚みがいと物理的(機械的)にも化学的にも保護膜として機能しない。また上限については、乾式熱酸化は、湿式熱酸化等に比べて長い成膜時間が必要となるため、成膜時間を考慮すれば最大でも40nm程度が現実的な膜厚となる。

【0049】

また先に説明した湿式酸化と乾式酸化のモデルに基づけば、乾式酸化であっても、厚すぎるシリコン酸化膜OX1を形成することは余剰炭素の局所析出の可能性が増すので、40nm未満、より望ましくは20nm程度の厚さとする。

【0050】

ここで、SiC−SBDにおいて、最もデバイス特性に大きな影響を与える接合箇所は、ショットキー接合となるショットキー電極(例えばTi)とSiCとの接合界面であるので、先にショットキー電極を形成して、後にオーミック電極を形成する方が望ましいが、NiとSiCとの良好なオーミック接合を得るには1000℃程度のアニール(オーミックアニール)が必要とされる。しかし、TiとSiCとのショットキー接合は、この高温プロセスではダメージを受けるので、先にオーミック電極を形成している。

【0051】

このように、Niによるオーミック電極を形成する前に、乾式熱酸化によるシリコン酸化膜OX1膜で電極領域を保護することで、後述するTiシンターによる特性のばらつきを低減することが可能となる。

【0052】

なお、シリコン酸化膜OX1はSiCウェハの裏面にも形成されるので、オーミック電極の形成前には、裏面を研磨することで裏面のシリコン酸化膜OX1を除去する。図7には、裏面のシリコン酸化膜OX1を除去した状態を示している。

【0053】

次に、図8に示す工程において、SiCウェハの裏面、すなわちSiC基板1の裏面に、例えばスパッタリング法により厚さ100nm程度のNi膜を形成し、SiC基板1との間にオーミック接合を形成してオーミック電極3を得る。

【0054】

その後、先に説明したように1000℃程度のアニールを行うが、このアニール条件は、SiCとNiとの界面に余剰カーボンが偏析せず、良質のNiシリサイドが形成されるように設定する。

【0055】

次に、図9に示す工程において、エピタキシャル層2上のシリコン酸化膜OX1をフッ酸を用いた湿式エッチングにより除去した後、例えばスパッタリング法により厚さ200nm程度のTi膜を形成する。そして、ショットキー電極4を形成する部分の上にフォトリソグラフィによりレジストマスクを形成し、当該レジストマスクを用いて、Ti膜を例えばウエットエッチングによりパターニングすることで、ショットキー電極4を得る。このパターニングは、ショットキー電極4が、GR領域10で囲まれたエピタキシャル層2上およびGR領域10の一部上部に形成されるようにパターニングを行う。

【0056】

その後、450±50℃、より望ましくは450±20℃の温度範囲で15分程度のシンターを行う。Tiとn型のSiCとのショットキー接合においてはシンターすることにより障壁高さΦBが1.25eV程度に高まり、かつ、障壁高さΦBのばらつきを低減することができる。例えば、450℃のTiシンターでは障壁高さφbが1.250〜1.290eVに安定する。この結果、ダイオードの順方向特性が安定し、逆リーク電流のばらつきも低減することとなる。

【0057】

なお、実際のプロセスでは、GR領域10およびJTE領域11が露出するエピタキシャル層2の表面の保護のためにポリイミド樹脂を形成するが、そのキュアリングのため350℃程度の熱処理を行うので、仮にTiシンターを実施しない場合も350℃の熱履歴が生じる。

【0058】

Ti膜に、このキュアリングによる350℃の熱履歴さえも与えない場合の障壁高さφbは1.05eV程度であることを実験から確認している。

【0059】

また、実験により、障壁高さφbを十分に安定させるためには400℃以上、より望ましくは450℃でTiシンターすることが最適であることを確認した。この実験結果を図13に示す。図13においては、横軸にTiシンターの温度を、縦軸に障壁高さφbの値を示し、400℃、450℃、500℃および550℃の温度でTiシンターを行い、それぞれの温度で得られた障壁高さφbの最小値、最大値および平均値を示している。

【0060】

図13より、Tiシンターの温度が450℃の場合に、障壁高さφbが最大となり、変動幅(最大値と最小値との差)も最も小さくなることが判る。しかし、シンター温度が450℃を超えると、ショットキー接合の部分的な破壊が始まり、オーミック接合に変化するものと考えられ、障壁高さφbの低下や、障壁高さφbのばらつきが大きくなる。

【0061】

なお、Tiシンターのタイミングに関しては、ショットキー電極4のパターニング直後であって、ショットキー電極4上に表面電極パッド(後に説明)を形成する前が望ましい。すなわち、ショットキーメタルとSiCとの界面近傍に表面電極パッドを構成するAl等のショットキーメタル以外の金属が接近、混入、接触することがなく、設計通りの良好な接合を形成できるからである。

【0062】

また、ショットキー電極4のパターニング前にTiシンターを行うと、TiシンターによりTiとSiCとの界面にTiシリサイド層等の遷移層が形成され、例えばウエットエッチングでTi膜をパターニングする際に問題になる場合があるためである。

【0063】

ショットキー電極4のシンターが終了した後、図10に示す工程において、ショットキー電極4上、GR領域10、JTE領域11上およびエピタキシャル層2上に3〜5μm程度の厚さのAl膜を蒸着法またはスッパタリング法で形成する。その後、ショットキー電極4の上方に該当するAl膜の上部にフォトリソグラフィによりレジストマスクRM4を形成し、レジスト開口部を介して熱燐酸などでウエットエッチングすることで、Al膜をパターニングして表面電極パッド5を得る。

【0064】

また、ショットキー電極4の材料となるTi膜を形成し、その上にPt(白金)などのバッファ層を形成した後、3〜5μm程度のAl膜を形成し、Al膜とTi膜とをパターニングすることで、表面電極パッド5およびショットキー電極4を形成し、その後にTiシンターしても良い。なお、Pt等のウエットエッチングが容易でない金属に対してはドライエッチングを用いても良い。

【0065】

このPtなどのバッファ層の形成により、シンターによりショットキーメタルとSiCとの界面近傍にAlが接近、混入、接触することを防止でき、設計通りの良好なショットキー接合を形成することができるとともに、AlとTiとの界面の密着性を高めるのにも有効である。

【0066】

次に、図11に示す工程において、表面電極パッド5の上部にフォトリソグラフィによりレジストマスクRM5を形成し、レジスト開口部にポリイミド樹脂を塗布した後、例えば窒素雰囲気中で、60分間のキュアリングを行う。ここで、キュアリング温度をショットキー接合形成後のシンター温度より50℃以上低温、例えば350℃とすることで、Tiシンターにより安定したショットキー接合界面の状態を安定に保つことができる。

【0067】

ポリイミド樹脂のキュアリング後、ウェハ工程の最後に、図12に示すように、オーミック電極3上に、例えば直流スパッタリング法によりNi膜およびAu膜を、この順に連続成膜することで、裏面電極パッド8を得る。Ni膜およびAu膜のそれぞれの厚さは、例えば数百nmである。

【0068】

なお、下地であるオーミック電極3はニッケルシリサイドとなっており、ニッケルシリサイドとの密着性をより良好にするため、Ni膜の成膜直前に、高周波(RF)スパッタリングによりニッケルシリサイドの表面にダメージを与えることができるように、成膜装置には直流スパッタリングもRFスパッタリングも実行できる装置を用いることが望ましい。

【0069】

オーミック電極3上に裏面電極パッド8を形成することで、半導体チップの裏面をダイボンドする際に、半田の濡れ性を良好にできる。

【0070】

また、ポリイミド樹脂のキュアリング後に裏面電極パッド8を形成するので、キュアリング工程で、Ni膜がAu膜の表面に拡散して、裏面電極パッド8の表面にNi酸化物が形成されることが防止されるので、半田の濡れ性が低下するということもない。

【0071】

<実施の形態2>

以上説明した実施の形態1に係るSiC−SBDの製造方法では、図5および図6を用いてそれぞれ説明したイオン注入によるGR領域10およびJTE領域11の形成に際しては、エピタキシャル層2の表面にシリコン酸化膜は形成されていない。

【0072】

しかし、デバイス仕様に応じたイオン注入領域の不純物濃度プロファイルの最適化のため、イオン注入前にシリコン酸化膜を形成しておき、当該シリコン酸化膜を注入スルー膜として利用しても良い。

【0073】

以下、実施の形態2に係るSiC−SBDの製造方法として、注入スルー膜を介してGR領域10およびJTE領域11を形成する方法について、図14〜図16を用いて説明する。なお、図4〜図12を用いて説明した実施の形態1と同一の構成については同一の符号を付し、重複する説明は省略する。

【0074】

まず、図14に示す工程において、エピタキシャル層2上に乾式熱酸化により例えば100nmの厚さのシリコン酸化膜OX11を形成する。なお、シリコン酸化膜OX11は、SiC基板1の裏面にも形成される。

【0075】

次に、図4を用いて説明した工程を経て、エピタキシャル層2の表面を0.3μm程度エッチングすることで位置合わせマーク9を形成する。この場合、レジストマスクの開口部を介してシリコン酸化膜OX11をエッチングした後、シリコン酸化膜OX11の開口部を介してエピタキシャル層2の表面をエッチングすることとなる。

【0076】

その後、図15に示す工程において、シリコン酸化膜OX11上にレジストマスクRM11を形成し、そこにGR領域10を形成するための開口部OP11をフォトリソグラフィによりパターニングする。そして、レジストマスクRM11の上方からp型不純物として、例えばAlのイオン注入を行い、開口部OP11を介してエピタキシャル層2の上層部にGR領域10を形成する。このときの注入条件は、例えば、350keVのエネルギーでピーク濃度が5×1017/cm3程度となるように注入を行う。

【0077】

次に、レジストマスクRM11を除去した後、図16に示す工程においてシリコン酸化膜OX11上にレジストマスクRM12を形成し、そこにJTE領域11を形成するための開口部OP12をフォトリソグラフィによりパターニングする。そして、レジストマスクRM12の上方からp型不純物として、例えばAlのイオン注入を行い、開口部OP12を介してエピタキシャル層2の上層部にJTE領域11を形成する。このときの注入条件は、例えば、500keVのエネルギーでピーク濃度が2×1017/cm3程度となるように注入を行う。

【0078】

この後は、レジストマスクRM12を除去し、さらに、シリコン酸化膜OX11も除去した後、GR領域10およびJTE領域11を終端構造として完成させるために、注入した不純物の活性化アニールを行うが、活性化アニール以降の工程は実施の形態1と同じである。

【0079】

このように、注入スルー膜を介してGR領域10およびJTE領域11を形成することで、GR領域10およびJTE領域11の表面近傍での不純物濃度を高くすることが可能となる。

【0080】

この効果について、図17および図18を用いて説明する。図17は、実施の形態1において説明された、注入スルー膜を介さずにGR領域10を形成した場合の注入不純物の濃度プロファイルを模式的に示す図であり、図4におけるGR領域10中の領域Yに相当する部分を示している。また、図18は、実施の形態2において説明された、注入スルー膜を介してGR領域10を形成した場合の注入不純物の濃度プロファイルを模式的に示す図であり、図15におけるGR領域10中の領域Zに相当する部分を示している。

【0081】

図17に示すように、不純物領域を形成する場合は、その領域の深さ方向の中央部で濃度ピークが得られるように注入条件を設定するので、GR領域10の浅い部分、すなわち表面近傍では不純物濃度は比較的低い。

【0082】

一方、図18に示すように、注入スルー膜(シリコン酸化膜OX11)を介してGR領域10を形成した場合、図17の場合と同じ注入エネルギーで注入すると、シリコン酸化膜OX11の厚み分だけ不純物の濃度プロファイルが浅い方にシフトすることとなる。このため、GR領域10の浅い部分、すなわち表面近傍では不純物濃度が比較的高くなり、シリコン酸化膜OX11を除去することで、GR領域10の表面近傍での不純物濃度を高くすることが可能となる。

【0083】

この方法を採ることで、注入スルー膜の厚さを変えることで、GR領域10の表面近傍での不純物濃度を調整することが可能となる。

【0084】

<実施の形態3>

実施の形態1に係るSiC−SBDの製造方法では、終端構造としてGR領域10およびJTE領域11を形成した例を説明したが、終端構造はこれに限定されるものではなく、例えば、図19に示すFLR(Field Limiting Ring)領域13によっても終端構造を形成することができる。

【0085】

図19に示すFLR領域13は、電極領域17を複数のリング状のp型不純物領域131が多重に囲むことで構成されている。

【0086】

図20は、FLR領域13の製造工程を示す断面図であり、実施の形態1において図5および図6を用いてそれぞれ説明したGR領域10およびJTE領域11の形成工程に相当する工程を示している。

【0087】

図4を用いて説明した工程を経て、位置合わせマーク9が形成された後のエピタキシャル層2上にレジストマスクRM10を形成し、そこにFLR領域13を形成するための開口部OP101、OP102、OP103およびOP104をフォトリソグラフィによりパターニングする。そして、レジストマスクRM10の上方からp型不純物として、例えばAlのイオン注入を行い、開口部OP2を介してエピタキシャル層2の上層部に複数のp型不純物領域131を形成する。このときの注入条件は、例えば、350keVのエネルギーでピーク濃度が3×1017/cm3程度となるように注入を行う。

【0088】

ここで、開口部OP101とOP102との間隔をaとし、開口部OP102とOP103との間隔をbとし、開口部OP103とOP104との間隔をcとした場合、c>b>aとなるようにパターニングを行う。

【0089】

これにより、形成されるリング状のp型不純物領域131は、外側に向かうほど配設間隔が広くなり、FLR領域13の不純物濃度が外側に向かうほど低くなることと等価な状態となる。

【0090】

この結果、GR領域10およびJTE領域11を形成した構成と同じ機能を有することとなるが、GR領域10およびJTE領域11の形成には2回のフォトリソグラフィが必要であるのに対し、FLR領域13の形成は1回のフォトリソグラフィで済むという利点がある。

【0091】

また、例えば、間隔aを4μm、間隔bを6μm、間隔cを8μmとし、p型不純物領域131の幅を3μmとした場合、FLR領域13の全体の幅は30μmとなり、GR領域10およびJTE領域11を形成する場合よりも短くて済むという効果もある。

【0092】

<実施の形態4>

フォトリソグラフィの回数を減らすことは、半導体装置の製造コストを低減するという点で有利となるが、その観点に立てば、図21〜図24を用いて説明する実施の形態3に係るSiC−SBDの製造方法によってもフォトリソグラフィの回数を減らすことができる。

【0093】

すなわち、実施の形態1においては、図4〜図5を用いて説明したように、位置合わせマーク9の形成から、GR領域10およびJTE領域11の形成のために、3回のフォトリソグラフィが必要である。

【0094】

しかし、図21〜図24を用いて説明する実施の形態3に係る製造方法によれば2回のフォトリソグラフィで済む。

【0095】

すなわち、位置合わせマーク9が形成される前のエピタキシャル層2上にレジストマスクRM21を形成し、そこに位置合わせマーク9を形成するための開口部OP212と、GR領域211を形成するための開口部OP211をフォトリソグラフィによりパターニングする。そして、開口部OP212および開口部OP211を介してエピタキシャル層2の表面をそれぞれ0.3μm程度エッチングすることで、位置合わせマーク9およびGR用リセス部91を形成する。

【0096】

次に、図22に示す工程において、レジストマスクRM21の上方から、p型不純物として、例えばAlのイオン注入を行い、開口部OP212および開口部OP211を介して位置合わせマーク9およびGR用リセス部91の底面下にそれぞれ、p型不純物領域15およびGR領域10を形成する。このときの注入条件は、例えば、350keVのエネルギーでピーク濃度が5×1017/cm3程度となるように注入を行う。

【0097】

次に、レジストマスクRM21を除去した後、図23に示す工程においてエピタキシャル層2上にレジストマスクRM22を形成し、そこにJTE領域11を形成するための開口部OP22をフォトリソグラフィによりパターニングする。そして、開口部OP22を介してエピタキシャル層2の表面を0.3μm程度エッチングすることで、JTE用リセス部92を形成する。

【0098】

次に、図24に示す工程において、レジストマスクRM22の上方から、p型不純物として、例えばAlのイオン注入を行い、開口部OP22を介してJTE用リセス部92の底面下にJTE領域11を形成する。このときの注入条件は、例えば、500keVのエネルギーでピーク濃度が2×1017/cm3程度となるように注入を行う。このように、リセス部の底面下に不純物領域を設ける構成はリセス構造と呼称される。

【0099】

なお、実施の形態3において説明したFLR領域13についてもリセス構造を採用しても良い。その場合は、位置合わせマーク9のエッチングに使用するレジストマスクと、FLR領域13の形成に使用されるレジストマスクとを兼用することとなるので、位置合わせマーク9の形成とFLR領域13の形成が、1回のフォトリソグラフィで済むこととなり、さらなる製造コストの低減が可能となる。

【0100】

また、JTE領域11を設けずGR領域10のみを設ける場合にも、リセス構造を採用しても良い。この場合は、位置合わせマーク9の形成とGR領域10の形成が、1回のフォトリソグラフィで済むこととなり、さらなる製造コストの低減が可能となる。

【0101】

<ショットキーメタルの他の例>

以上説明した実施の形態1〜3においては、ショットキーメタルとしてTiを用いる場合について説明したが、他のショットキーメタル、例えばNi、W、Mo等を用いても良い。金属材料により、仕事関数や、SiCとのピニング効果が異なるので、ダイオード特性として得られる順方向の障壁高さφBを変えることができ、所望の障壁高さφBが得られるように材質を選択すれば良い。

【符号の説明】

【0102】

1 SiC基板、2 エピタキシャル層、3 オーミック電極、4 ショットキー電極、5 表面電極パッド、10 GR領域、11 JTE領域、13 FLR領域、OX1 シリコン酸化膜、17 電極領域。

【技術分野】

【0001】

本発明は炭化珪素半導体装置の製造方法に関し、特に、炭化珪素ショットキーバリアダイオードの製造方法に関する。

【背景技術】

【0002】

炭化珪素ショットキーバリアダイオード(以下、SiC−SBDと記す)の製造においては、ショットキーメタルの選択と、順方向特性の安定化が重要である。ショットキーメタルとして、Ti(チタン)、Ni(ニッケル)、Mo(モリブデン)およびW(タングステン)などが一般的であるが、例えばTiショットキーバリアダイオードを製造する場合に、裏面の電極としてNiを採用しNiのオーミック接合を形成する場合には次のようなプロセス上の特徴および問題点を抱えることになる。

【0003】

すなわち、kV級の高耐圧のSiC−SBDは、炭化珪素基板上に形成されたn型のエピタキシャル層上にショットキー電極が形成される構成を有しているが、この構造では、エピタキシャル層とショットキー電極との接合面の端縁部に電界が集中し易くなるので、その接合面(ショットキー接合面)の端縁部に対応するエピタキシャル層の上層部に電界集中緩和のためのp型終端構造を形成することが一般的である。

【0004】

p型終端構造は、SBDの電極領域を囲むように形成されたp型不純物領域であり、その形成には、一般にAl(アルミニウム)、B(ボロン)等のp型不純物をn型のエピタキシャル層にイオン注入し、1500℃以上の高温熱処理で活性化アニールする方法が採られる。

【0005】

良好な特性のショットキー接合を得るには、この高温熱処理時に生じるSiC表面の変質層を除去する必要があるが、この変質層を除去する技術としては、例えば特許文献1〜5に記載された技術が知られている。

【0006】

特許文献1には、この変質層を除去する方法として、活性化アニール後にSiC表層を犠牲酸化し、表層に40nm以上140nm未満の犠牲酸化膜を形成し、その犠牲酸化膜と共に変質層を除去する方法が開示されている。

【0007】

特許文献2には、フッ酸処理による自然酸化膜の除去に続いて、水素と酸素との混合ガスのプラズマやフッ素原子を含むガスのプラズマによるプラズマエッチングによりSiCの表面を清浄化する方法が開示されている。

【0008】

特許文献3には、約100nmの厚さの変質層が生じること、および、約100nmの厚さの変質層を水素を含む雰囲気中のエッチングまたは機械的な研磨により除去する方法が開示されている。

【0009】

特許文献4には、活性化アニール後に、基板の表裏両面に1160℃の酸素雰囲気中で熱酸化膜を形成し、その直後に当該熱酸化膜をBHF溶液で除去する方法が開示されている。

【0010】

また、従来よりSiC−SBDの製造においては、ダイオードの順方向特性、特に障壁高さφBやn値(理想係数)を安定させるためには、ショットキーメタルを形成する直前まで炭化珪素基板上をプロセス保護膜で覆っておき、当該プロセス保護膜を除去してショットキーメタル(ここではTi)を成膜する方法や、ショットキーメタルを形成した後に、400〜600℃程度でTiシンターをする方法が効果的であることが知られている。

【0011】

例えばTiショットキーバリアダイオードにおいてシンターを実施しないと、障壁高さφBは、およそ1.05〜1.25eVの範囲に渡って大きくばらつく。これでは個々のSiC−SBD素子の特性のばらつきが大きくなり、シリコンIGBTやSiC−MOSFETと合わせてスイッチング素子、パワーモジュール等を構成する際、特性を揃えることができないという問題や、良品選別規格を厳しくした場合には良品率が低下するという問題が起こりうる。このため、特性の揃った半導体デバイスを製作することが量産プロセスおよび事業化に際して重要である。

【0012】

しかしながら、このようにプロセス保護膜として前工程で犠牲酸化膜を形成したり、ショットキーメタルとしてTiを形成した後に、400〜600℃程度のシンターを行っても、ダイオードの順方向特性、特に障壁高さφBの安定性は、実用化を想定して要求される仕様に対して満足すべき結果が得られず、逆方向リーク電流のばらつきも大きいという問題があった。

【先行技術文献】

【特許文献】

【0013】

【特許文献1】特開2008−53418号公報

【特許文献2】特開2001−35838号公報

【特許文献3】特開2004−363326号公報

【特許文献4】特開2007−141950号公報

【発明の概要】

【発明が解決しようとする課題】

【0014】

本発明は上記のような問題点を解消するためになされたもので、炭化珪素ショットキーダイオードの製造において、ダイオードの順方向特性、特に障壁高さφBを安定させて、リーク電流のばらつきを低減させることが可能な半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0015】

本発明に係る炭化珪素半導体装置の製造方法の態様は、第1導電型の炭化珪素基板を準備する工程(a)と、前記炭化珪素基板の一方主面上に第1導電型のエピタキシャル層《2》を形成する工程(b)と、前記エピタキシャル層の上層部に、電極領域《17》となる部分を囲むように第2導電型の不純物をイオン注入して、終端構造を形成する工程(c)と、前記エピタキシャル層上に乾式熱酸化によりシリコン酸化膜を形成する工程(d)と、前記炭化珪素基板の他方主面上に第1の金属層を形成する工程(e)と、前記工程(e)の後、前記炭化珪素基板を第1の温度で熱処理し、前記第1の金属層と前記炭化珪素基板の前記他方主面との間にオーミック接合を形成する工程(f)と、前記工程(f)の後、前記シリコン酸化膜を除去する工程(g)と、前記工程(g)の後、前記エピタキシャル層上に第2の金属層《4》を形成する工程(h)と、前記工程(h)の後、前記炭化珪素基板を第2の温度で熱処理し、前記第2の金属層と前記エピタキシャル層との間にショットキー接合を形成する工程(i)とを備えている。

【発明の効果】

【0016】

本発明に係る炭化珪素半導体装置の製造方法の態様によれば、ダイオードの順方向特性、特に障壁高さφBを安定させるとともに、逆方向リーク電流のばらつきを低減させた炭化珪素半導体装置を得ることができる。

【図面の簡単な説明】

【0017】

【図1】SiCウェハにおける半導体チップのレイアウトの一例を示す平面図である。

【図2】半導体チップのレイアウトの部分平面図である。

【図3】チップ領域の断面構成を示す断面図である。

【図4】本発明に係る実施の形態1のSiC−SBDの製造工程を示す断面図である。

【図5】本発明に係る実施の形態1のSiC−SBDの製造工程を示す断面図である。

【図6】本発明に係る実施の形態1のSiC−SBDの製造工程を示す断面図である。

【図7】本発明に係る実施の形態1のSiC−SBDの製造工程を示す断面図である。

【図8】本発明に係る実施の形態1のSiC−SBDの製造工程を示す断面図である。

【図9】本発明に係る実施の形態1のSiC−SBDの製造工程を示す断面図である。

【図10】本発明に係る実施の形態1のSiC−SBDの製造工程を示す断面図である。

【図11】本発明に係る実施の形態1のSiC−SBDの製造工程を示す断面図である。

【図12】本発明に係る実施の形態1のSiC−SBDの製造工程を示す断面図である。

【図13】Tiシンターの最適温度を示す図である。

【図14】本発明に係る実施の形態2のSiC−SBDの製造工程を示す断面図である。

【図15】本発明に係る実施の形態2のSiC−SBDの製造工程を示す断面図である。

【図16】本発明に係る実施の形態2のSiC−SBDの製造工程を示す断面図である。

【図17】注入スルー膜を介さずにGR領域を形成した場合の注入不純物の濃度プロファイルを模式的に示す図である。

【図18】注入スルー膜を介してGR領域を形成した場合の注入不純物の濃度プロファイルを模式的に示す図である。

【図19】FLR領域を有するSiC−SBDの断面図である。

【図20】FLR領域の製造工程を示す断面図である。

【図21】本発明に係る実施の形態3のSiC−SBDの製造工程を示す断面図である。

【図22】本発明に係る実施の形態3のSiC−SBDの製造工程を示す断面図である。

【図23】本発明に係る実施の形態3のSiC−SBDの製造工程を示す断面図である。

【図24】本発明に係る実施の形態3のSiC−SBDの製造工程を示す断面図である。

【発明を実施するための形態】

【0018】

SiCのエピタキシャル成長においては、基板結晶のポリタイプを正しく継承させるため、ステップ制御エピタキシーが用いられる。ステップ制御エピタキシーでは、基板面方位を基本結晶面(basal plane)である(0001)面より数度傾けることでステップ状の表面構造を実現したオフ角(オフアングル)基板を使用する。

【0019】

ポリタイプが4HのSiC基板の場合は、<112_0>方向(“_”は2の上に付されるバーラインを示す)に8゜あるいは4゜傾斜させて得られた基板を用いることが標準的である。

【0020】

以下に説明する本発明に係る炭化珪素半導体装置の製造方法を用いて作製したSiC−SBDでは、オフ角が8゜の基板を用いた場合、ウェハプロセス完了後の障壁高さは1.25≦φB≦1.29の範囲となり、オフ角が4°基板を用いた場合、1.21≦φB≦1.25の範囲となり、何れの場合も安定した結果が得られた。

【0021】

以下、オフ角が8゜の基板を用いた場合を例に採って、本発明に係る炭化珪素半導体装置の製造方法の実施の形態について説明する。

【0022】

<実施の形態1>

図1は、SiCウェハWFにおける半導体チップのレイアウトの一例を示す平面図であり、SiCウェハWFに縦横に複数のダイシングラインDLが設定されている。ダイシングラインDLによって囲まれる四角形状の領域がチップ領域CHであり、チップ領域CHをダイシングすることで、個々に独立したSiC−SBDのチップが得られる。

【0023】

図2は、図1に示した領域Xで囲まれる部分を示す平面図であり、SiC−SBDの上面構造を示している。なお、図2においては、後にショットキー電極が形成される電極領域17と、それを囲むGR(Guard Ring)領域10およびJTE(Junction Termination Extension)領域11を示しており、電極領域17上のショットキー電極等が形成される前の状態を示している。

【0024】

なお、図2には2行2列の4つのチップ領域CHを示しているが、これは、フォトリソグラフィにおける1ショットで露光されるチップ領域が4つの場合を例示している。そして、当該4つのチップ領域を規定するダイシングラインDL上には、フォトリソグラフィに際して必要となる露光マスクの位置合わせのための位置合わせマーク9が複数設けられている。

【0025】

位置合わせマーク9は、平面視形状が四角形をなし、図面に向かって最上部左側のチップ領域CHの上辺側のダイシングラインDL上と、図面に向かって最下部右側のチップ領域CHの下辺側のダイシングラインDL上に設けられているが、位置合わせマーク9の平面視形状および配置は一例に過ぎない。

【0026】

図3は、図2におけるチップ領域CHのA−A線での断面構成を表す断面図である。図3に示すように、n型のSiC基板1上にn型のエピタキシャル層2が形成され、エピタキシャル層2の上層部の電極領域17の外側に深さ0.6μm程度、幅20μm程度のGR領域10および深さ0.8μm程度、幅20μm程度のJTE領域11が形成され、JTE領域11のさらに外側に位置合わせマーク9が形成されている。

【0027】

GR領域10およびJTE領域11は、SiC−SBDにkV超級の耐圧を安定して確保するために、ショットキー電極端部の電界集中を緩和するために設けられる。GR領域10だけでも電界の集中は緩和できるが、さらにその外側に連続してGR領域10よりも不純物濃度が若干薄いJTE領域11を設けることで、表面電界を低減する構成としている。

【0028】

次に、製造工程を順に示す断面図である図4〜図12を用いて、実施の形態1に係るSiC−SBDの製造方法について説明する。

【0029】

まず、図4に示す工程において、ポリタイプが4Hの(0001)シリコン面を有するオフ角8°のn型のSiC基板1を準備する。SiC基板1のn型不純物濃度は比較的高く(n+)、その抵抗率は、0.02Ω・cm程度である。

【0030】

次に、SiC基板1の(0001)シリコン面(これを一方主面と呼称)上に、SiC基板1に比べて比較的低濃度(5×1015/cm3程度)n型不純物を含むエピタキシャル層2をエピタキシャル成長させる。エピタキシャル層2の厚さは、耐圧に応じて決められ、600V〜1700V程度の耐圧の場合は、5〜15μm程度の厚さとする。

【0031】

その後、エピタキシャル層2上にレジストマスクRM1を形成し、そこに位置合わせマーク9の形成のための開口部OP1をフォトリソグラフィにより形成する。そして、開口部OP1を介してエピタキシャル層2の表面を0.3μm程度エッチングすることで位置合わせマーク9を形成する。以後の、フォトリソグラフィでは、この位置合わせマーク9を目印として用いて露光マスクの重ね合わせを行う。

【0032】

次に、レジストマスクRM1を除去した後、図5に示す工程においてエピタキシャル層2上にレジストマスクRM2を形成し、そこにGR領域10を形成するための開口部OP2をフォトリソグラフィによりパターニングする。そして、レジストマスクRM2の上方からp型不純物として、例えばAlのイオン注入を行い、開口部OP2を介してエピタキシャル層2の上層部にGR領域10を形成する。このときの注入条件は、例えば、350keVのエネルギーでピーク濃度が5×1017/cm3程度となるように注入を行う。

【0033】

次に、レジストマスクRM2を除去した後、図6に示す工程においてエピタキシャル層2上にレジストマスクRM3を形成し、そこにJTE領域11を形成するための開口部OP2をフォトリソグラフィによりパターニングする。そして、レジストマスクRM3の上方からp型不純物として、例えばAlのイオン注入を行い、開口部OP3を介してエピタキシャル層2の上層部にJTE領域11を形成する。このときの注入条件は、例えば、500keVのエネルギーでピーク濃度が2×1017/cm3程度となるように注入を行う。

【0034】

GR領域10およびJTE領域11を終端構造として完成させるためには、注入した不純物をアニールにより活性化する必要がある。このためには、レジストマスクRM2を除去した後、例えば、RTA(Rapid Thermal Annealing)タイプのアニール炉を用いて、常圧Ar雰囲気でアニールを行う。この場合、バンチングステップと呼ばれる凹凸面の発生を抑制する手法として、アニールに先だって、グラファイトキャップ(G−cap)と呼称されるカーボン保護膜をSiCウェハの全表面に形成することが一般的ある。グラファイトキャップを形成したSiCウェハを、例えば枚葉式RTAアニール炉を用いて、少なくとも1500〜1700℃の温度範囲で10分程度アニールすれば、p型不純物は50〜90%の比率で活性化し、終端構造として十分に機能する。

【0035】

終端構造の完成により、エピタキシャル層とショットキー電極との接合面の端縁部での電界集中を緩和することができる。

【0036】

また、グラファイトキャップを形成することで、1nm以上のバンチングステップが発生することもない。活性化率が高いことは注入工程で崩れた結晶の再結晶化状態をより完全な状態にしている指標となり、半導体デバイスとしての高信頼性の実現に寄与する。

【0037】

なお、グラファイトキャップを設けずにアニールすると、1nm以上のバンチングステップが発生し、後に形成する熱酸化膜の厚みのばらつきが増し、当該熱酸化膜除去後も局所的に酸化膜が残る原因となり、リーク電流を増大させる可能性がある。

【0038】

グラファイトキャップの形成には、例えば液体材料C2H5OHを用いCVD(Chemical Vapor Deposition)によりおよそ20nm以上の膜厚を形成すれば十分である。例えば900℃、60分で40〜50nm形成可能である。活性化アニール後の除去はドライアッシングすればよい。

【0039】

また、グラファイトキャップを形成せずにバンチングステップを抑制する方法として、ファーネスタイプのSiC−CVD装置を用いて、例えば、減圧されたH2およびC3H8雰囲気で1350℃、15分程度のアニールを実施する方法が挙げられる。このアニール条件はAr雰囲気でのアニールと比較しながら、バンチングステップを1nm未満に抑えられるよう雰囲気圧力、温度、時間を調整して得られたものであり、このようなアニール条件を採用することで、バンチングステップに代表されるアニール後の表面の凹凸を1nm未満に抑えることが可能となる。

【0040】

上述した活性化アニールを行った後は、エピタキシャル層2の最表面から100〜150nmの深さに及ぶ変質層(ダメージ層)を除去するために、ドライエッチングを行う。

【0041】

エピタキシャル層2の表面の変質層は、次の工程で形成する熱酸化膜では除去しきれないので、予めドライエッチングにより除去しておくことで、熱酸化膜除去後に、良質なエピタキシャル層2の表面にショットキー電極を形成することができる。

【0042】

変質層を除去した後は、SiCウェハの(0001_)カーボン面(“_”は1の上に付されるバーラインを示す)、すなわちSiC基板1のエピタキシャル層2が形成された一方主面とは反対側の他方主面(裏面)にオーミック電極を形成するが、それに先だって、図7に示す工程において、エピタキシャル層2の上に、15〜40nmの厚さのシリコン酸化膜OX1を形成する。

【0043】

このシリコン酸化膜OX1は、SiCウェハの裏面にオーミック電極を形成した後、1000℃程度のアニールを行うが、その際に、オーミック電極の材料であるNiや、アニール装置内部に滞留する金属不純物等でエピタキシャル層2の表面が汚染されるのを防止するプロセス保護膜であり、乾燥酸素雰囲気中で行う乾式熱酸化により形成される。

【0044】

ここで、乾式熱酸化によりシリコン酸化膜OX1を形成する理由について説明する。例えば1200Vの耐圧を有するSiC−SBDを製作する場合、注入不純物の活性化アニール後の熱酸化膜を乾式酸化および湿式酸化により形成した場合、完成したSBDの逆方向リーク電流特性に顕著な有意差が生じる。

【0045】

すなわち乾式酸化で形成したシリコン酸化膜をフッ酸の湿式エッチングにより除去した後、ショットキー電極(Ti)を形成して得られたSBDと、湿式酸化で形成したシリコン酸化膜をフッ酸の湿式エッチングにより除去した後、ショットキー電極(Ti)を形成して得られたSBDとでは、1200V印加時における逆方向リーク電流の典型値はそれぞれ、10〜100μA/cm2、1〜10mA/cm2であり、およそ1〜3桁も異なることとなる。

【0046】

この顕著な有意差を生じる理由については次のようなモデルで説明される。すなわち、乾式酸化ではゆっくりとした等方的な酸化が進行し、このため余剰炭素も熱平衡的に分散する傾向があると考えられる。

【0047】

一方、湿式酸化では化学的作用が顕著になり酸化速度の面方位依存性や結晶欠陥での優先的酸化、増殖酸化が進行し、余剰炭素の局所析出の可能性がある。この差異により酸化膜除去後の表面平坦性に関しては、湿式酸化で形成した酸化膜を除去する場合の方が局所的凹凸が発生しやすく、それらが逆リーク電流を増大させる要因となるものと考えられる。なおSiCの熱酸化についての一般的なモデル説明は例えば、「SiC素子の基礎と応用」(オーム社、荒井和雄・吉田貞史共編)の第82,83頁に記載がある。

【0048】

また、シリコン酸化膜OX1の厚さを15〜40nmとする理由は以下の通りである。すなわち、プロセス保護膜としての効果を得るには、最低でも数原子層以上に相当する15nm以上の厚みがいと物理的(機械的)にも化学的にも保護膜として機能しない。また上限については、乾式熱酸化は、湿式熱酸化等に比べて長い成膜時間が必要となるため、成膜時間を考慮すれば最大でも40nm程度が現実的な膜厚となる。

【0049】

また先に説明した湿式酸化と乾式酸化のモデルに基づけば、乾式酸化であっても、厚すぎるシリコン酸化膜OX1を形成することは余剰炭素の局所析出の可能性が増すので、40nm未満、より望ましくは20nm程度の厚さとする。

【0050】

ここで、SiC−SBDにおいて、最もデバイス特性に大きな影響を与える接合箇所は、ショットキー接合となるショットキー電極(例えばTi)とSiCとの接合界面であるので、先にショットキー電極を形成して、後にオーミック電極を形成する方が望ましいが、NiとSiCとの良好なオーミック接合を得るには1000℃程度のアニール(オーミックアニール)が必要とされる。しかし、TiとSiCとのショットキー接合は、この高温プロセスではダメージを受けるので、先にオーミック電極を形成している。

【0051】

このように、Niによるオーミック電極を形成する前に、乾式熱酸化によるシリコン酸化膜OX1膜で電極領域を保護することで、後述するTiシンターによる特性のばらつきを低減することが可能となる。

【0052】

なお、シリコン酸化膜OX1はSiCウェハの裏面にも形成されるので、オーミック電極の形成前には、裏面を研磨することで裏面のシリコン酸化膜OX1を除去する。図7には、裏面のシリコン酸化膜OX1を除去した状態を示している。

【0053】

次に、図8に示す工程において、SiCウェハの裏面、すなわちSiC基板1の裏面に、例えばスパッタリング法により厚さ100nm程度のNi膜を形成し、SiC基板1との間にオーミック接合を形成してオーミック電極3を得る。

【0054】

その後、先に説明したように1000℃程度のアニールを行うが、このアニール条件は、SiCとNiとの界面に余剰カーボンが偏析せず、良質のNiシリサイドが形成されるように設定する。

【0055】

次に、図9に示す工程において、エピタキシャル層2上のシリコン酸化膜OX1をフッ酸を用いた湿式エッチングにより除去した後、例えばスパッタリング法により厚さ200nm程度のTi膜を形成する。そして、ショットキー電極4を形成する部分の上にフォトリソグラフィによりレジストマスクを形成し、当該レジストマスクを用いて、Ti膜を例えばウエットエッチングによりパターニングすることで、ショットキー電極4を得る。このパターニングは、ショットキー電極4が、GR領域10で囲まれたエピタキシャル層2上およびGR領域10の一部上部に形成されるようにパターニングを行う。

【0056】

その後、450±50℃、より望ましくは450±20℃の温度範囲で15分程度のシンターを行う。Tiとn型のSiCとのショットキー接合においてはシンターすることにより障壁高さΦBが1.25eV程度に高まり、かつ、障壁高さΦBのばらつきを低減することができる。例えば、450℃のTiシンターでは障壁高さφbが1.250〜1.290eVに安定する。この結果、ダイオードの順方向特性が安定し、逆リーク電流のばらつきも低減することとなる。

【0057】

なお、実際のプロセスでは、GR領域10およびJTE領域11が露出するエピタキシャル層2の表面の保護のためにポリイミド樹脂を形成するが、そのキュアリングのため350℃程度の熱処理を行うので、仮にTiシンターを実施しない場合も350℃の熱履歴が生じる。

【0058】

Ti膜に、このキュアリングによる350℃の熱履歴さえも与えない場合の障壁高さφbは1.05eV程度であることを実験から確認している。

【0059】

また、実験により、障壁高さφbを十分に安定させるためには400℃以上、より望ましくは450℃でTiシンターすることが最適であることを確認した。この実験結果を図13に示す。図13においては、横軸にTiシンターの温度を、縦軸に障壁高さφbの値を示し、400℃、450℃、500℃および550℃の温度でTiシンターを行い、それぞれの温度で得られた障壁高さφbの最小値、最大値および平均値を示している。

【0060】

図13より、Tiシンターの温度が450℃の場合に、障壁高さφbが最大となり、変動幅(最大値と最小値との差)も最も小さくなることが判る。しかし、シンター温度が450℃を超えると、ショットキー接合の部分的な破壊が始まり、オーミック接合に変化するものと考えられ、障壁高さφbの低下や、障壁高さφbのばらつきが大きくなる。

【0061】

なお、Tiシンターのタイミングに関しては、ショットキー電極4のパターニング直後であって、ショットキー電極4上に表面電極パッド(後に説明)を形成する前が望ましい。すなわち、ショットキーメタルとSiCとの界面近傍に表面電極パッドを構成するAl等のショットキーメタル以外の金属が接近、混入、接触することがなく、設計通りの良好な接合を形成できるからである。

【0062】

また、ショットキー電極4のパターニング前にTiシンターを行うと、TiシンターによりTiとSiCとの界面にTiシリサイド層等の遷移層が形成され、例えばウエットエッチングでTi膜をパターニングする際に問題になる場合があるためである。

【0063】

ショットキー電極4のシンターが終了した後、図10に示す工程において、ショットキー電極4上、GR領域10、JTE領域11上およびエピタキシャル層2上に3〜5μm程度の厚さのAl膜を蒸着法またはスッパタリング法で形成する。その後、ショットキー電極4の上方に該当するAl膜の上部にフォトリソグラフィによりレジストマスクRM4を形成し、レジスト開口部を介して熱燐酸などでウエットエッチングすることで、Al膜をパターニングして表面電極パッド5を得る。

【0064】

また、ショットキー電極4の材料となるTi膜を形成し、その上にPt(白金)などのバッファ層を形成した後、3〜5μm程度のAl膜を形成し、Al膜とTi膜とをパターニングすることで、表面電極パッド5およびショットキー電極4を形成し、その後にTiシンターしても良い。なお、Pt等のウエットエッチングが容易でない金属に対してはドライエッチングを用いても良い。

【0065】

このPtなどのバッファ層の形成により、シンターによりショットキーメタルとSiCとの界面近傍にAlが接近、混入、接触することを防止でき、設計通りの良好なショットキー接合を形成することができるとともに、AlとTiとの界面の密着性を高めるのにも有効である。

【0066】

次に、図11に示す工程において、表面電極パッド5の上部にフォトリソグラフィによりレジストマスクRM5を形成し、レジスト開口部にポリイミド樹脂を塗布した後、例えば窒素雰囲気中で、60分間のキュアリングを行う。ここで、キュアリング温度をショットキー接合形成後のシンター温度より50℃以上低温、例えば350℃とすることで、Tiシンターにより安定したショットキー接合界面の状態を安定に保つことができる。

【0067】

ポリイミド樹脂のキュアリング後、ウェハ工程の最後に、図12に示すように、オーミック電極3上に、例えば直流スパッタリング法によりNi膜およびAu膜を、この順に連続成膜することで、裏面電極パッド8を得る。Ni膜およびAu膜のそれぞれの厚さは、例えば数百nmである。

【0068】

なお、下地であるオーミック電極3はニッケルシリサイドとなっており、ニッケルシリサイドとの密着性をより良好にするため、Ni膜の成膜直前に、高周波(RF)スパッタリングによりニッケルシリサイドの表面にダメージを与えることができるように、成膜装置には直流スパッタリングもRFスパッタリングも実行できる装置を用いることが望ましい。

【0069】

オーミック電極3上に裏面電極パッド8を形成することで、半導体チップの裏面をダイボンドする際に、半田の濡れ性を良好にできる。

【0070】

また、ポリイミド樹脂のキュアリング後に裏面電極パッド8を形成するので、キュアリング工程で、Ni膜がAu膜の表面に拡散して、裏面電極パッド8の表面にNi酸化物が形成されることが防止されるので、半田の濡れ性が低下するということもない。

【0071】

<実施の形態2>

以上説明した実施の形態1に係るSiC−SBDの製造方法では、図5および図6を用いてそれぞれ説明したイオン注入によるGR領域10およびJTE領域11の形成に際しては、エピタキシャル層2の表面にシリコン酸化膜は形成されていない。

【0072】

しかし、デバイス仕様に応じたイオン注入領域の不純物濃度プロファイルの最適化のため、イオン注入前にシリコン酸化膜を形成しておき、当該シリコン酸化膜を注入スルー膜として利用しても良い。

【0073】

以下、実施の形態2に係るSiC−SBDの製造方法として、注入スルー膜を介してGR領域10およびJTE領域11を形成する方法について、図14〜図16を用いて説明する。なお、図4〜図12を用いて説明した実施の形態1と同一の構成については同一の符号を付し、重複する説明は省略する。

【0074】

まず、図14に示す工程において、エピタキシャル層2上に乾式熱酸化により例えば100nmの厚さのシリコン酸化膜OX11を形成する。なお、シリコン酸化膜OX11は、SiC基板1の裏面にも形成される。

【0075】

次に、図4を用いて説明した工程を経て、エピタキシャル層2の表面を0.3μm程度エッチングすることで位置合わせマーク9を形成する。この場合、レジストマスクの開口部を介してシリコン酸化膜OX11をエッチングした後、シリコン酸化膜OX11の開口部を介してエピタキシャル層2の表面をエッチングすることとなる。

【0076】

その後、図15に示す工程において、シリコン酸化膜OX11上にレジストマスクRM11を形成し、そこにGR領域10を形成するための開口部OP11をフォトリソグラフィによりパターニングする。そして、レジストマスクRM11の上方からp型不純物として、例えばAlのイオン注入を行い、開口部OP11を介してエピタキシャル層2の上層部にGR領域10を形成する。このときの注入条件は、例えば、350keVのエネルギーでピーク濃度が5×1017/cm3程度となるように注入を行う。

【0077】

次に、レジストマスクRM11を除去した後、図16に示す工程においてシリコン酸化膜OX11上にレジストマスクRM12を形成し、そこにJTE領域11を形成するための開口部OP12をフォトリソグラフィによりパターニングする。そして、レジストマスクRM12の上方からp型不純物として、例えばAlのイオン注入を行い、開口部OP12を介してエピタキシャル層2の上層部にJTE領域11を形成する。このときの注入条件は、例えば、500keVのエネルギーでピーク濃度が2×1017/cm3程度となるように注入を行う。

【0078】

この後は、レジストマスクRM12を除去し、さらに、シリコン酸化膜OX11も除去した後、GR領域10およびJTE領域11を終端構造として完成させるために、注入した不純物の活性化アニールを行うが、活性化アニール以降の工程は実施の形態1と同じである。

【0079】

このように、注入スルー膜を介してGR領域10およびJTE領域11を形成することで、GR領域10およびJTE領域11の表面近傍での不純物濃度を高くすることが可能となる。

【0080】

この効果について、図17および図18を用いて説明する。図17は、実施の形態1において説明された、注入スルー膜を介さずにGR領域10を形成した場合の注入不純物の濃度プロファイルを模式的に示す図であり、図4におけるGR領域10中の領域Yに相当する部分を示している。また、図18は、実施の形態2において説明された、注入スルー膜を介してGR領域10を形成した場合の注入不純物の濃度プロファイルを模式的に示す図であり、図15におけるGR領域10中の領域Zに相当する部分を示している。

【0081】

図17に示すように、不純物領域を形成する場合は、その領域の深さ方向の中央部で濃度ピークが得られるように注入条件を設定するので、GR領域10の浅い部分、すなわち表面近傍では不純物濃度は比較的低い。

【0082】

一方、図18に示すように、注入スルー膜(シリコン酸化膜OX11)を介してGR領域10を形成した場合、図17の場合と同じ注入エネルギーで注入すると、シリコン酸化膜OX11の厚み分だけ不純物の濃度プロファイルが浅い方にシフトすることとなる。このため、GR領域10の浅い部分、すなわち表面近傍では不純物濃度が比較的高くなり、シリコン酸化膜OX11を除去することで、GR領域10の表面近傍での不純物濃度を高くすることが可能となる。

【0083】

この方法を採ることで、注入スルー膜の厚さを変えることで、GR領域10の表面近傍での不純物濃度を調整することが可能となる。

【0084】

<実施の形態3>

実施の形態1に係るSiC−SBDの製造方法では、終端構造としてGR領域10およびJTE領域11を形成した例を説明したが、終端構造はこれに限定されるものではなく、例えば、図19に示すFLR(Field Limiting Ring)領域13によっても終端構造を形成することができる。

【0085】

図19に示すFLR領域13は、電極領域17を複数のリング状のp型不純物領域131が多重に囲むことで構成されている。

【0086】

図20は、FLR領域13の製造工程を示す断面図であり、実施の形態1において図5および図6を用いてそれぞれ説明したGR領域10およびJTE領域11の形成工程に相当する工程を示している。

【0087】

図4を用いて説明した工程を経て、位置合わせマーク9が形成された後のエピタキシャル層2上にレジストマスクRM10を形成し、そこにFLR領域13を形成するための開口部OP101、OP102、OP103およびOP104をフォトリソグラフィによりパターニングする。そして、レジストマスクRM10の上方からp型不純物として、例えばAlのイオン注入を行い、開口部OP2を介してエピタキシャル層2の上層部に複数のp型不純物領域131を形成する。このときの注入条件は、例えば、350keVのエネルギーでピーク濃度が3×1017/cm3程度となるように注入を行う。

【0088】

ここで、開口部OP101とOP102との間隔をaとし、開口部OP102とOP103との間隔をbとし、開口部OP103とOP104との間隔をcとした場合、c>b>aとなるようにパターニングを行う。

【0089】

これにより、形成されるリング状のp型不純物領域131は、外側に向かうほど配設間隔が広くなり、FLR領域13の不純物濃度が外側に向かうほど低くなることと等価な状態となる。

【0090】

この結果、GR領域10およびJTE領域11を形成した構成と同じ機能を有することとなるが、GR領域10およびJTE領域11の形成には2回のフォトリソグラフィが必要であるのに対し、FLR領域13の形成は1回のフォトリソグラフィで済むという利点がある。

【0091】

また、例えば、間隔aを4μm、間隔bを6μm、間隔cを8μmとし、p型不純物領域131の幅を3μmとした場合、FLR領域13の全体の幅は30μmとなり、GR領域10およびJTE領域11を形成する場合よりも短くて済むという効果もある。

【0092】

<実施の形態4>

フォトリソグラフィの回数を減らすことは、半導体装置の製造コストを低減するという点で有利となるが、その観点に立てば、図21〜図24を用いて説明する実施の形態3に係るSiC−SBDの製造方法によってもフォトリソグラフィの回数を減らすことができる。

【0093】

すなわち、実施の形態1においては、図4〜図5を用いて説明したように、位置合わせマーク9の形成から、GR領域10およびJTE領域11の形成のために、3回のフォトリソグラフィが必要である。

【0094】

しかし、図21〜図24を用いて説明する実施の形態3に係る製造方法によれば2回のフォトリソグラフィで済む。

【0095】

すなわち、位置合わせマーク9が形成される前のエピタキシャル層2上にレジストマスクRM21を形成し、そこに位置合わせマーク9を形成するための開口部OP212と、GR領域211を形成するための開口部OP211をフォトリソグラフィによりパターニングする。そして、開口部OP212および開口部OP211を介してエピタキシャル層2の表面をそれぞれ0.3μm程度エッチングすることで、位置合わせマーク9およびGR用リセス部91を形成する。

【0096】

次に、図22に示す工程において、レジストマスクRM21の上方から、p型不純物として、例えばAlのイオン注入を行い、開口部OP212および開口部OP211を介して位置合わせマーク9およびGR用リセス部91の底面下にそれぞれ、p型不純物領域15およびGR領域10を形成する。このときの注入条件は、例えば、350keVのエネルギーでピーク濃度が5×1017/cm3程度となるように注入を行う。

【0097】

次に、レジストマスクRM21を除去した後、図23に示す工程においてエピタキシャル層2上にレジストマスクRM22を形成し、そこにJTE領域11を形成するための開口部OP22をフォトリソグラフィによりパターニングする。そして、開口部OP22を介してエピタキシャル層2の表面を0.3μm程度エッチングすることで、JTE用リセス部92を形成する。

【0098】

次に、図24に示す工程において、レジストマスクRM22の上方から、p型不純物として、例えばAlのイオン注入を行い、開口部OP22を介してJTE用リセス部92の底面下にJTE領域11を形成する。このときの注入条件は、例えば、500keVのエネルギーでピーク濃度が2×1017/cm3程度となるように注入を行う。このように、リセス部の底面下に不純物領域を設ける構成はリセス構造と呼称される。

【0099】

なお、実施の形態3において説明したFLR領域13についてもリセス構造を採用しても良い。その場合は、位置合わせマーク9のエッチングに使用するレジストマスクと、FLR領域13の形成に使用されるレジストマスクとを兼用することとなるので、位置合わせマーク9の形成とFLR領域13の形成が、1回のフォトリソグラフィで済むこととなり、さらなる製造コストの低減が可能となる。

【0100】

また、JTE領域11を設けずGR領域10のみを設ける場合にも、リセス構造を採用しても良い。この場合は、位置合わせマーク9の形成とGR領域10の形成が、1回のフォトリソグラフィで済むこととなり、さらなる製造コストの低減が可能となる。

【0101】

<ショットキーメタルの他の例>

以上説明した実施の形態1〜3においては、ショットキーメタルとしてTiを用いる場合について説明したが、他のショットキーメタル、例えばNi、W、Mo等を用いても良い。金属材料により、仕事関数や、SiCとのピニング効果が異なるので、ダイオード特性として得られる順方向の障壁高さφBを変えることができ、所望の障壁高さφBが得られるように材質を選択すれば良い。

【符号の説明】

【0102】

1 SiC基板、2 エピタキシャル層、3 オーミック電極、4 ショットキー電極、5 表面電極パッド、10 GR領域、11 JTE領域、13 FLR領域、OX1 シリコン酸化膜、17 電極領域。

【特許請求の範囲】

【請求項1】

(a)第1導電型の炭化珪素基板を準備する工程と、

(b)前記炭化珪素基板の一方主面上に第1導電型のエピタキシャル層を形成する工程と、

(c)前記エピタキシャル層の上層部に、電極領域となる部分を囲むように第2導電型の不純物をイオン注入して、終端構造を形成する工程と、

(d)前記エピタキシャル層上に乾式熱酸化によりシリコン酸化膜を形成する工程と、

(e)前記炭化珪素基板の他方主面上に第1の金属膜を形成する工程と、

(f)前記工程(e)の後、前記炭化珪素基板を第1の温度で熱処理し、前記第1の金属膜と前記炭化珪素基板の前記他方主面との間にオーミック接合を形成する工程と、

(g)前記工程(f)の後、前記シリコン酸化膜を除去する工程と、

(h)前記工程(g)の後、前記エピタキシャル層上に第2の金属膜を形成する工程と、

(i)前記工程(h)の後、前記炭化珪素基板を第2の温度で熱処理し、前記第2の金属膜と前記エピタキシャル層との間にショットキー接合を形成する工程と、を備える炭化珪素半導体装置の製造方法。

【請求項2】

前記工程(c)と前記工程(d)との間に、

(d1)注入された前記第2導電型の不純物を活性化するアニールを行う工程と、

(d2)前記アニールの後、前記エピタキシャル層を、最表面から100〜150nmの深さまで除去する工程と、をさらに備える、請求項1記載の炭化珪素半導体装置の製造方法。

【請求項3】

前記工程(c)は、

前記電極領域となる部分を囲むように前記第2導電型の不純物をイオン注入して、終端構造を形成する工程を含む、請求項1記載の炭化珪素半導体装置の製造方法。

【請求項4】

前記工程(c)は、

(c1)前記第2導電型の不純物を第1の濃度でイオン注入してガードリング領域を形成する工程と、

(c2)前記ガードリング層のさらに外側に連続し、前記第1の濃度より低い第2の濃度となるように前記第2導電型の不純物をイオン注入してJTE(Junction Termination Extension)領域を形成する工程と、を含む、請求項3記載の炭化珪素半導体装置の製造方法。

【請求項5】

前記工程(c)は、

(c1)第2導電型の不純物領域が前記エピタキシャル層の平面内で間隔を開けて複数形成されるように前記第2導電型の不純物を多重にイオン注入する工程を含む、請求項3記載の炭化珪素半導体装置の製造方法。

【請求項6】

前記工程(h)は、前記第2の金属膜をTiで形成する工程を含み、

前記工程(i)は、前記第2の温度として、450±50℃の温度範囲内の温度で熱処理する工程を含む、請求項1記載の炭化珪素半導体装置の製造方法。

【請求項7】

前記工程(i)は、前記第2の温度として、450±20℃の温度範囲内の温度で熱処理する工程を含む、請求項6記載の炭化珪素半導体装置の製造方法。

【請求項8】

前記工程(d)は、前記シリコン酸化膜を15〜40nmの厚さに形成する工程を含む、請求項1記載の炭化珪素半導体装置の製造方法。

【請求項9】

前記工程(i)の後、

前記第2の金属膜上に、第3の金属膜を形成する工程をさらに備える、請求項1記載の炭化珪素半導体装置の製造方法。

【請求項1】

(a)第1導電型の炭化珪素基板を準備する工程と、

(b)前記炭化珪素基板の一方主面上に第1導電型のエピタキシャル層を形成する工程と、

(c)前記エピタキシャル層の上層部に、電極領域となる部分を囲むように第2導電型の不純物をイオン注入して、終端構造を形成する工程と、

(d)前記エピタキシャル層上に乾式熱酸化によりシリコン酸化膜を形成する工程と、

(e)前記炭化珪素基板の他方主面上に第1の金属膜を形成する工程と、

(f)前記工程(e)の後、前記炭化珪素基板を第1の温度で熱処理し、前記第1の金属膜と前記炭化珪素基板の前記他方主面との間にオーミック接合を形成する工程と、

(g)前記工程(f)の後、前記シリコン酸化膜を除去する工程と、

(h)前記工程(g)の後、前記エピタキシャル層上に第2の金属膜を形成する工程と、

(i)前記工程(h)の後、前記炭化珪素基板を第2の温度で熱処理し、前記第2の金属膜と前記エピタキシャル層との間にショットキー接合を形成する工程と、を備える炭化珪素半導体装置の製造方法。

【請求項2】

前記工程(c)と前記工程(d)との間に、

(d1)注入された前記第2導電型の不純物を活性化するアニールを行う工程と、

(d2)前記アニールの後、前記エピタキシャル層を、最表面から100〜150nmの深さまで除去する工程と、をさらに備える、請求項1記載の炭化珪素半導体装置の製造方法。

【請求項3】

前記工程(c)は、

前記電極領域となる部分を囲むように前記第2導電型の不純物をイオン注入して、終端構造を形成する工程を含む、請求項1記載の炭化珪素半導体装置の製造方法。

【請求項4】

前記工程(c)は、

(c1)前記第2導電型の不純物を第1の濃度でイオン注入してガードリング領域を形成する工程と、

(c2)前記ガードリング層のさらに外側に連続し、前記第1の濃度より低い第2の濃度となるように前記第2導電型の不純物をイオン注入してJTE(Junction Termination Extension)領域を形成する工程と、を含む、請求項3記載の炭化珪素半導体装置の製造方法。

【請求項5】

前記工程(c)は、

(c1)第2導電型の不純物領域が前記エピタキシャル層の平面内で間隔を開けて複数形成されるように前記第2導電型の不純物を多重にイオン注入する工程を含む、請求項3記載の炭化珪素半導体装置の製造方法。

【請求項6】

前記工程(h)は、前記第2の金属膜をTiで形成する工程を含み、

前記工程(i)は、前記第2の温度として、450±50℃の温度範囲内の温度で熱処理する工程を含む、請求項1記載の炭化珪素半導体装置の製造方法。

【請求項7】

前記工程(i)は、前記第2の温度として、450±20℃の温度範囲内の温度で熱処理する工程を含む、請求項6記載の炭化珪素半導体装置の製造方法。

【請求項8】

前記工程(d)は、前記シリコン酸化膜を15〜40nmの厚さに形成する工程を含む、請求項1記載の炭化珪素半導体装置の製造方法。

【請求項9】

前記工程(i)の後、

前記第2の金属膜上に、第3の金属膜を形成する工程をさらに備える、請求項1記載の炭化珪素半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【公開番号】特開2012−248648(P2012−248648A)

【公開日】平成24年12月13日(2012.12.13)

【国際特許分類】

【出願番号】特願2011−118661(P2011−118661)

【出願日】平成23年5月27日(2011.5.27)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成24年12月13日(2012.12.13)

【国際特許分類】

【出願日】平成23年5月27日(2011.5.27)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]