炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置

【課題】炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置を提供する。

【解決手段】炭化珪素基板1の製造方法は、炭化珪素からなるベース基板10および単結晶炭化珪素からなるSiC基板20を準備する工程と、ベース基板10の主面10A上に接触するようにSiC基板20を載置して、積層基板を作製する工程と、積層基板を、SiC基板20よりもベース基板10の温度が高くなるように加熱することにより、ベース基板10とSiC基板20とを接合する工程と、SiC基板20が接合されたベース基板10の、SiC基板20とは反対側の主面10B上にエピタキシャル成長層30を形成する工程とを備えている。

【解決手段】炭化珪素基板1の製造方法は、炭化珪素からなるベース基板10および単結晶炭化珪素からなるSiC基板20を準備する工程と、ベース基板10の主面10A上に接触するようにSiC基板20を載置して、積層基板を作製する工程と、積層基板を、SiC基板20よりもベース基板10の温度が高くなるように加熱することにより、ベース基板10とSiC基板20とを接合する工程と、SiC基板20が接合されたベース基板10の、SiC基板20とは反対側の主面10B上にエピタキシャル成長層30を形成する工程とを備えている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置に関し、より特定的には、炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置に関するものである。

【背景技術】

【0002】

近年、半導体装置の高耐圧化、低損失化、高温環境下での使用などを可能とするため、半導体装置を構成する材料として炭化珪素の採用が進められつつある。炭化珪素は、従来から半導体装置を構成する材料として広く使用されている珪素に比べてバンドギャップが大きいワイドバンドギャップ半導体である。そのため、半導体装置を構成する材料として炭化珪素を採用することにより、半導体装置の高耐圧化、オン抵抗の低減などを達成することができる。また、炭化珪素を材料として採用した半導体装置は、珪素を材料として採用した半導体装置に比べて、高温環境下で使用された場合の特性の低下が小さいという利点も有している。

【0003】

このような状況の下、半導体装置の製造に用いられる炭化珪素結晶および炭化珪素基板の製造方法については、種々の検討がなされ、様々なアイデアが提案されている(たとえば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2002−280531号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、炭化珪素は常圧で液相を持たない。また、結晶成長温度が2000℃以上と非常に高く、成長条件の制御や、その安定化が困難である。そのため、炭化珪素単結晶は、高品質を維持しつつ大口径化することが困難であり、大口径の高品質な炭化珪素基板を得ることは容易ではない。そして、大口径の炭化珪素基板の作製が困難であることに起因して、炭化珪素基板の製造コストが上昇するだけでなく、当該炭化珪素基板を用いて半導体装置を製造するに際しては、1バッチあたりの生産個数が少なくなり、半導体装置の製造コストが高くなるという問題があった。また、製造コストの高い炭化珪素単結晶を基板として有効に利用することにより、半導体装置の製造コストを低減できるものと考えられる。

【0006】

そこで、本発明の目的は、炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置を提供することである。

【課題を解決するための手段】

【0007】

本発明に従った炭化珪素基板の製造方法は、炭化珪素からなるベース基板および単結晶炭化珪素からなるSiC基板を準備する工程と、ベース基板の主面上に接触するようにSiC基板を載置して、積層基板を作製する工程と、積層基板を、SiC基板よりもベース基板の温度が高くなるように加熱することにより、ベース基板とSiC基板とを接合する工程と、SiC基板が接合されたベース基板の、SiC基板とは反対側の主面上にエピタキシャル成長層を形成する工程とを備えている。

【0008】

上述のように、高品質な炭化珪素単結晶は、大口径化が困難である。一方、炭化珪素基板を用いた半導体装置の製造プロセスにおいて効率よく製造を行なうためには、所定の形状および大きさに統一された基板が必要である。そのため、高品質な炭化珪素単結晶(たとえば欠陥密度が小さい炭化珪素単結晶)が得られた場合でも、切断等によって所定の形状等に加工できない領域は、有効に利用されない可能性がある。

【0009】

これに対し、本発明の炭化珪素基板の製造方法においては、ベース基板上に単結晶炭化珪素からなるSiC基板が載置されて作製された積層基板が加熱されることによりベース基板とSiC基板とが接合されて、炭化珪素基板が製造される。そのため、たとえば欠陥密度が大きく、低品質な炭化珪素結晶からなるベース基板を上記所定の形状および大きさに加工し、当該ベース基板上に高品質であるものの所望の形状等が実現されていない炭化珪素単結晶をSiC基板として載置し、加熱することにより炭化珪素基板を製造することができる。このようにして得られた炭化珪素基板は、全体として所定の形状および大きさに統一されているため、半導体装置の製造の効率化に寄与することができる。また、このような炭化珪素基板の高品質なSiC基板上に、たとえばエピタキシャル成長により半導体層を形成して半導体装置を製造することが可能であるため、炭化珪素単結晶を有効に利用することができる。その結果、本発明の炭化珪素基板によれば、炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板を製造することができる。

【0010】

さらに、上記接合前の積層基板においては、ベース基板やSiC基板の反り、うねりなどに起因して、ベース基板とSiC基板との間に隙間が形成される。そのため、接合後の積層基板においては当該隙間を起源とするボイドが形成される。そして、ベース基板とSiC基板とを接合する工程において、SiC基板よりもベース基板の温度が高くなるように積層基板が加熱されることにより、当該ボイドはベース基板側に移動し、最終的にはベース基板のSiC基板とは反対側の主面にまで到達する場合がある。その場合、当該ボイドに起因して、ベース基板のSiC基板とは反対側の主面の粗さが大きくなり、炭化珪素基板を用いた半導体装置の製造プロセスに不具合が生じるおそれがある。具体的には、たとえば半導体装置の製造プロセスにおいて炭化珪素基板を真空チャックにより保持する際、十分な吸着力が得られない場合がある。

【0011】

これに対し、本発明の炭化珪素基板の製造方法では、SiC基板が接合されたベース基板の、SiC基板とは反対側の主面上にエピタキシャル成長層を形成する工程を備えている。このように、ボイドの到達により粗さが大きくなるおそれのある上記主面をエピタキシャル成長層により覆うことにより、上記半導体装置の製造プロセスにおける不具合を抑制することができる。

【0012】

上記炭化珪素基板の製造方法においては、ベース基板とSiC基板とを接合する工程では、ベース基板が、ベース基板を構成する炭化珪素の昇華温度以上の温度域に加熱されてもよい。

【0013】

これにより、ベース基板を構成する炭化珪素が昇華し、SiC基板上で再結晶する。その結果、ベース基板とSiC基板との接合が容易に進行する。

【0014】

上記炭化珪素基板の製造方法においては、エピタキシャル成長層を形成する工程よりも後に、SiC基板のベース基板とは反対側の主面を研磨する工程をさらに備えていてもよい。

【0015】

これにより、SiC基板の主面上に半導体装置のバッファ層や耐圧保持層などとして機能する高品質な半導体層をエピタキシャル成長により形成することが容易となる。

【0016】

上記炭化珪素基板の製造方法においては、エピタキシャル成長層を形成する工程では、液相法により上記エピタキシャル成長層が形成されてもよい。また、上記炭化珪素基板の製造方法においては、エピタキシャル成長層を形成する工程では、化学気相成長法により上記エピタキシャル成長層が形成されてもよい。このように、液相法や化学気相成長法を採用することにより、上記エピタキシャル成長層を容易に形成することができる。

【0017】

上記炭化珪素基板の製造方法においては、積層基板を作製する工程よりも前に、積層基板を作製する工程において互いに接触すべきベース基板およびSiC基板の主面を平坦化する工程をさらに備えていてもよい。ベース基板とSiC基板との接合面となるべき面を予め平坦化しておくことにより、ベース基板とSiC基板とをより確実に接合することができる。

【0018】

上記炭化珪素基板の製造方法においては、積層基板を作製する工程は、積層基板を作製する工程よりも前に、積層基板を作製する工程において互いに接触すべきベース基板およびSiC基板の主面を研磨することなく実施されてもよい。これにより、炭化珪素基板の製造コストを低減することができる。ここで、積層基板を作製する工程において互いに接触すべきベース基板およびSiC基板の主面は、上述のように研磨されなくてもよい。しかし、基板作製時におけるスライスなどにより形成された表面付近のダメージ層を除去する観点から、たとえばエッチングによって当該ダメージ層が除去される工程が実施された後に上記積層基板を作製する工程が実施されることが好ましい。

【0019】

上記炭化珪素基板の製造方法においては、積層基板を作製する工程では、SiC基板は、平面的に見て複数並べて載置されてもよい。別の観点から説明すると、SiC基板は、ベース基板の主面に沿って複数並べて載置されてもよい。

【0020】

上述のように、高品質な炭化珪素単結晶は、大口径化が困難である。これに対し、高品質な炭化珪素単結晶から採取した複数のSiC基板を平面的に複数並べて配置したうえで、ベース基板とSiC基板とを接合することにより、高品質なSiC層を有する大口径な基板として取り扱うことが可能な炭化珪素基板を得ることができる。そして、この炭化珪素基板を用いることにより、半導体装置の製造プロセスを効率化することができる。なお、半導体装置の製造プロセスを効率化するためには、上記複数のSiC基板のうち互いに隣り合うSiC基板は、互いに接触して配置されていることが好ましい。より具体的には、たとえば上記複数のSiC基板は、平面的に見てマトリックス状に敷き詰められていることが好ましい。

【0021】

上記炭化珪素基板の製造方法においては、積層基板を作製する工程では、SiC基板のベース基板とは反対側の主面は、{0001}面に対するオフ角が50°以上65°以下となっていてもよい。

【0022】

六方晶の単結晶炭化珪素は、<0001>方向に成長させることにより、高品質な単結晶を効率よく作製することができる。そして、<0001>方向に成長させた炭化珪素単結晶からは、{0001}面を主面とする炭化珪素基板を効率よく採取することができる。一方、面方位{0001}に対するオフ角が50°以上65°以下である主面を有する炭化珪素基板を用いることにより、高性能な半導体装置を製造できる場合がある。

【0023】

具体的には、たとえばMOSFET(Metal Oxide Semiconductor Field Effect Transistor;酸化膜電界効果トランジスタ)の作製に用いられる炭化珪素基板は、面方位{0001}に対するオフ角が8°程度以下である主面を有していることが一般的である。そして、当該主面上にエピタキシャル成長により半導体層が形成されるとともに、当該半導体層上に酸化膜、電極などが形成され、MOSFETが得られる。このMOSFETにおいては、半導体層と酸化膜との界面を含む領域にチャネル領域が形成される。しかし、このような構造を有するMOSFETにおいては、基板の主面の{0001}面に対するオフ角が8°程度以下であることに起因して、チャネル領域が形成される半導体層と酸化膜との界面付近において多くの界面準位が形成され、キャリアの走行の妨げとなって、チャネル移動度が低下する。

【0024】

これに対し、上記積層基板を作製する工程において、SiC基板のベース基板とは反対側の主面の、{0001}面に対するオフ角を50°以上65°以下とすることにより、製造される炭化珪素基板の主面の{0001}面に対するオフ角が50°以上65°以下となる。そのため、上記界面準位の形成が低減され、オン抵抗が低減されたMOSFET等を作製可能な炭化珪素基板を製造することができる。

【0025】

上記炭化珪素基板の製造方法においては、積層基板を作製する工程では、SiC基板のベース基板とは反対側の主面のオフ方位と<1−100>方向とのなす角は5°以下となっていてもよい。

【0026】

<1−100>方向は、炭化珪素基板における代表的なオフ方位である。そして、基板の製造工程におけるスライス加工のばらつき等に起因したオフ方位のばらつきを5°以下とすることにより、炭化珪素基板上への半導体層の形成などを容易にすることができる。

【0027】

上記炭化珪素基板の製造方法においては、積層基板を作製する工程では、SiC基板のベース基板とは反対側の主面の、<1−100>方向における{03−38}面に対するオフ角は−3°以上5°以下とすることができる。

【0028】

これにより、炭化珪素基板を用いてMOSFETを作製した場合におけるチャネル移動度を、より一層向上させることができる。ここで、面方位{03−38}に対するオフ角を−3°以上+5°以下としたのは、チャネル移動度と当該オフ角との関係を調査した結果、この範囲内で特に高いチャネル移動度が得られたことに基づいている。

【0029】

また、「<1−100>方向における{03−38}面に対するオフ角」とは、<1−100>方向および<0001>方向の張る平面への上記主面の法線の正射影と、{03−38}面の法線とのなす角度であり、その符号は、上記正射影が<1−100>方向に対して平行に近づく場合が正であり、上記正射影が<0001>方向に対して平行に近づく場合が負である。

【0030】

なお、上記主面の面方位は、実質的に{03−38}であることがより好ましく、上記主面の面方位は{03−38}であることがさらに好ましい。ここで、主面の面方位が実質的に{03−38}であるとは、基板の加工精度などを考慮して実質的に面方位が{03−38}とみなせるオフ角の範囲に基板の主面の面方位が含まれていることを意味し、この場合のオフ角の範囲はたとえば{03−38}に対してオフ角が±2°の範囲である。これにより、上述したチャネル移動度をより一層向上させることができる。

【0031】

上記炭化珪素基板の製造方法においては、積層基板を作製する工程では、SiC基板のベース基板とは反対側の主面のオフ方位と<11−20>方向とのなす角は5°以下となっていてもよい。

【0032】

<11−20>方向は、上記<1−100>方向と同様に、炭化珪素基板における代表的なオフ方位である。そして、基板の製造工程におけるスライス加工のばらつき等に起因したオフ方位のばらつきを±5°とすることにより、SiC基板上への半導体層の形成などを容易にすることができる。

【0033】

上記炭化珪素基板の製造方法においては、ベース基板とSiC基板とを接合する工程では、大気雰囲気を減圧することにより得られた雰囲気中において積層基板が加熱されてもよい。これにより、炭化珪素基板の製造コストを低減することができる。

【0034】

上記炭化珪素基板の製造方法においては、ベース基板とSiC基板とを接合する工程では、10−1Paよりも高く104Paよりも低い圧力下において積層基板が加熱されてもよい。これにより、簡素な装置により上記接合を実施することが可能になるとともに比較的短時間で接合を実施するための雰囲気を得ることが可能となる。その結果、炭化珪素基板の製造コストを低減することができる。

【0035】

本発明に従った半導体装置の製造方法は、炭化珪素基板を準備する工程と、炭化珪素基板上にエピタキシャル成長により半導体層を形成する工程と、半導体層上に電極を形成する工程とを備えている。そして、炭化珪素基板を準備する工程では、上記本発明の炭化珪素基板の製造方法により炭化珪素基板が製造される。本発明の半導体装置の製造方法によれば、上記本発明の炭化珪素基板の製造方法により製造された炭化珪素基板を用いて半導体装置が製造されるため、半導体装置の製造コストを低減することができる。

【0036】

本発明に従った炭化珪素基板は、上記本発明の炭化珪素基板の製造方法により製造されている。これにより、本発明の炭化珪素基板は、炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板となっている。

【0037】

本発明に従った半導体装置は、上記本発明の半導体装置の製造方法により製造されている。これにより、本発明の半導体装置は、製造コストが低減された半導体装置となっている。

【発明の効果】

【0038】

以上の説明から明らかなように、本発明の炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置によれば、炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置を提供することができる。

【図面の簡単な説明】

【0039】

【図1】炭化珪素基板の製造方法の概略を示すフローチャートである。

【図2】炭化珪素基板の製造方法を説明するための概略断面図である。

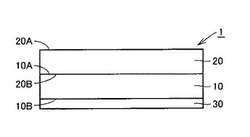

【図3】炭化珪素基板の構造を示す概略断面図である。

【図4】実施の形態2における炭化珪素基板の製造方法を説明するための概略断面図である。

【図5】実施の形態2における炭化珪素基板の構造を示す概略断面図である。

【図6】縦型MOSFETの構造を示す概略断面図である。

【図7】縦型MOSFETの製造方法の概略を示すフローチャートである。

【図8】縦型MOSFETの製造方法を説明するための概略断面図である。

【図9】縦型MOSFETの製造方法を説明するための概略断面図である。

【図10】縦型MOSFETの製造方法を説明するための概略断面図である。

【図11】縦型MOSFETの製造方法を説明するための概略断面図である。

【発明を実施するための形態】

【0040】

以下、図面に基づいて本発明の実施の形態を説明する。なお、以下の図面において同一または相当する部分には同一の参照番号を付し、その説明は繰返さない。

【0041】

(実施の形態1)

まず、本発明の一実施の形態である実施の形態1について説明する。図1を参照して、本実施の形態における炭化珪素基板の製造方法では、まず工程(S10)として基板準備工程が実施される。この工程(S10)では、図2を参照して、炭化珪素からなるベース基板10および単結晶炭化珪素からなるSiC基板20が準備される。このとき、SiC基板20の主面20Aは、この製造方法により得られるSiC層20の主面20Aとなることから(後述の図3参照)、所望の主面20Aの面方位に合わせて、SiC基板20の主面20Aの面方位を選択する。また、ベース基板10には、たとえば不純物濃度が2×1019cm−3よりも大きい基板が採用される。そして、SiC基板20には、不純物濃度が5×1018cm−3よりも大きく2×1019cm−3よりも小さい基板を採用することができる。これにより、抵抗率の小さいベース層10を形成しつつ、デバイスプロセスにおける熱処理が実施された場合でも、少なくともSiC層20において積層欠陥の発生を抑制することができる。また、ベース基板10としては、単結晶炭化珪素、多結晶炭化珪素、非晶質炭化珪素、炭化珪素焼結体などからなる基板を採用することができる。

【0042】

次に、工程(S20)として基板平坦化工程が実施される。この工程(S20)では、後述する工程(S30)において互いに接触すべきベース基板10の主面10AおよびSiC基板20の主面20B(接合面)が、たとえば研磨により平坦化される。なお、この工程(S20)は必須の工程ではないが、これを実施しておくことにより、互いに対向するベース基板10とSiC基板20との間の隙間の大きさが均一となるため、後述する工程(S40)において接合面内での反応(接合)の均一性が向上する。その結果、ベース基板10とSiC基板20とをより確実に接合することができる。また、一層確実にベース基板10とSiC基板とを接合するためには、上記接合面の面粗さRaは100nm未満であることが好ましく、50nm未満であることが好ましい。さらに、接合面の面粗さRaを10nm未満とすることにより、より確実な接合を達成することができる。

【0043】

一方、工程(S20)を省略し、互いに接触すべきベース基板10およびSiC基板20の主面を研磨することなく工程(S30)が実施されてもよい。これにより、炭化珪素基板1の製造コストを低減することができる。また、ベース基板10およびSiC基板20の作製時におけるスライスなどにより形成された表面付近のダメージ層を除去する観点から、たとえばエッチングによって当該ダメージ層が除去される工程が上記工程(S20)に代えて、あるいは上記工程(S20)の後に実施された上で、後述する工程(S30)が実施されてもよい。

【0044】

次に、工程(S30)として、積層工程が実施される。この工程(S30)では、図2を参照して、ベース基板10の主面10A上に接触するようにSiC基板20が載置されて、積層基板2が作製される。ここで、この工程(S30)では、SiC基板20のベース基板10とは反対側の主面20Aは、{0001}面に対するオフ角が50°以上65°以下となっていてもよい。これにより、SiC層20の主面20Aが、{0001}面に対するオフ角が50°以上65°以下となっている炭化珪素基板1を容易に製造することができる。また、工程(S30)では、上記主面20Aのオフ方位と<1−100>方向とのなす角は5°以下となっていてもよい。これにより、作製される炭化珪素基板1上(主面20A上)への半導体層の形成などを容易にすることができる。さらに、工程(S30)では、主面20Aの、<1−100>方向における{03−38}面に対するオフ角は−3°以上5°以下であってもよい。これにより、製造される炭化珪素基板1を用いてMOSFETなどを作製した場合におけるチャネル移動度を、より一層向上させることができる。

【0045】

一方、工程(S30)では、主面20Aのオフ方位と<11−20>方向とのなす角は5°以下となっていてもよい。これにより、作製される炭化珪素基板1上への半導体層の形成などを容易にすることができる。

【0046】

次に、工程(S40)として、接合工程が実施される。この工程(S40)では、積層基板2が、SiC基板20よりもベース基板10の温度が高くなるように加熱されることにより、ベース基板10とSiC基板20とが接合される。このとき、ベース基板10は、ベース基板10を構成する炭化珪素の昇華温度以上の温度域に加熱されることが好ましい。これにより、ベース基板10を構成する炭化珪素の昇華、再結晶によって、ベース基板10とSiC基板20との接合が容易に進行する。

【0047】

次に、工程(S50)として、エピタキシャル成長工程が実施される。この工程(S50)では、図2および図3を参照して、SiC基板20が接合されたベース基板10の、SiC基板20とは反対側の主面10B上にエピタキシャル成長層30が形成される。エピタキシャル成長層30の厚みは、たとえば10μm程度とすることができる。

【0048】

ここで、工程(S50)では、液相法によりエピタキシャル成長層30が形成されてもよい。より具体的には、たとえば雰囲気ガスとしてアルゴンなどの不活性ガスを採用し、融液上部の温度を1600℃〜1650℃程度、るつぼ下部の温度を1550℃〜1600℃程度とする条件で炭化珪素をエピタキシャル成長させ、余分な珪素をふっ硝酸にて除去することによりエピタキシャル成長層30を形成することができる。

【0049】

一方、工程(S50)では、化学気相成長法によりエピタキシャル成長層30が形成されてもよい。より具体的には、たとえばSiH4/H2を0.03%〜0.05%程度、C/Siを0.5〜1.2程度、成長温度を1500℃〜1600℃程度とする条件で炭化珪素をエピタキシャル成長させ、エピタキシャル成長層30を形成することができる。

【0050】

次に、工程(S60)として研磨工程が実施される。この工程(S60)では

、SiC基板20のベース基板10とは反対側の主面20Aが研磨される。この工程(S60)は必須の工程ではないが、これを実施することにより、SiC基板20の主面20A上に半導体装置のバッファ層や耐圧保持層などとして機能する高品質な半導体層をエピタキシャル成長により形成することが容易となる。また、この工程(S60)を実施することにより、工程(S50)においてSiC基板20の主面20A上に付着した炭化珪素を除去することができる。以上の手順により、本実施の形態における炭化珪素基板の製造方法が完了し、図3に示す炭化珪素基板1が得られる。

【0051】

図3を参照して、上記製造方法により得られる炭化珪素基板1は、炭化珪素からなるベース層10と、ベース層10の主面10A上に形成され、ベース層10とは別の単結晶炭化珪素からなるSiC層20と、SiC層20とは反対側のベース層10の主面10B上に形成されたエピタキシャル成長層30とを備えている。ここで、SiC層20がベース層10とは別の単結晶炭化珪素からなる状態とは、ベース層10がSiC層20とは別の結晶からなっている場合をいう。ベース層10とSiC層20とが別の結晶からなっている状態とは、ベース層10とSiC層20との間に境界が存在し、たとえば当該境界の一方側と他方側とで欠陥密度が異なっている状態を意味する。このとき、欠陥密度が当該境界において不連続となっていてもよい。

【0052】

上記本実施の形態における炭化珪素基板1の製造方法においては、ベース基板10上に単結晶炭化珪素からなるSiC基板20が載置されて作製された積層基板2が加熱されることにより接合されて、炭化珪素基板1が製造される。そのため、たとえば欠陥密度が大きく、低品質な炭化珪素結晶からなるベース基板10を半導体装置の製造に適した形状および大きさに加工し、当該ベース基板10上に高品質であるものの適切な形状等が実現されていない炭化珪素単結晶をSiC基板20として載置し、加熱することにより炭化珪素基板1を製造することができる。その結果、本発明の炭化珪素基板1は、炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板となっている。

【0053】

さらに、本実施の形態における炭化珪素基板1の製造方法においては、工程(S50)においてエピタキシャル成長層30が形成される。これにより、工程(S40)において形成されるボイドが到達して粗さが大きくなるおそれのあるベース基板10の主面10Bがエピタキシャル成長層30により覆われる。その結果、製造される炭化珪素基板1のベース層10側の主面が真空チャックにより十分に吸着できないなどの不具合を抑制することができる。なお、本実施の形態における上記ボイドの体積は、1μm3以上となり得る。その結果、たとえば工程(S40)が完了した状態におけるベース基板10の主面10Bの粗さ(ラフネス)Raは、5μm以上となり得る。この粗さRaは、ベース基板10の作製時におけるスライスを実施した状態(アズスライス状態)における粗さRa(0.2μm程度)と比較して著しく大きい。

【0054】

また、上記本実施の形態における炭化珪素基板1の製造方法では、工程(S40)では、大気雰囲気を減圧することにより得られた雰囲気中において積層基板2が加熱されてもよい。これにより、炭化珪素基板1の製造コストを低減することができる。

【0055】

さらに、上記本実施の形態における炭化珪素基板1の製造方法では、工程(S40)では、10−1Paよりも高く104Paよりも低い圧力下において積層基板2が加熱されてもよい。これにより、簡素な装置により上記接合を実施することが可能になるとともに比較的短時間で接合を実施するための雰囲気を得ることが可能となる。その結果、炭化珪素基板1の製造コストを低減することができる。

【0056】

ここで、工程(S30)において作製された積層基板2においては、ベース基板10とSiC基板20との間に形成される隙間が100μm以下となっていることが好ましい。これにより、工程(S40)において、ベース基板10とSiC基板20との均一な接合を達成することができる。

【0057】

また、工程(S40)における積層基板2の加熱温度は1800℃以上2500℃以下であることが好ましい。加熱温度が1800℃よりも低い場合、ベース基板10とSiC基板20との接合に長時間を要し、炭化珪素基板1の製造効率が低下する。一方、加熱温度が2500℃を超えると、ベース基板10およびSiC基板20の表面が荒れ、作製される炭化珪素基板1における結晶欠陥の発生が多くなるおそれがある。炭化珪素基板1における欠陥の発生を一層抑制しつつ製造効率を向上させるためには、工程(S40)における積層基板2の加熱温度は1900℃以上2100℃以下であることが好ましい。

【0058】

また、工程(S40)における加熱時の雰囲気は、不活性ガス雰囲気であってもよい。そして、当該雰囲気に不活性ガス雰囲気を採用する場合、アルゴン、ヘリウムおよび窒素からなる群から選択される少なくとも1つを含む不活性ガス雰囲気であることが好ましい。

【0059】

(実施の形態2)

次に、本発明の他の実施の形態である実施の形態2について図4および図5に基づいて説明する。実施の形態2における炭化珪素基板の製造方法は、基本的には実施の形態1における炭化珪素基板の製造方法と同様の手順で実施され、同様の効果を奏する。しかし、実施の形態2における炭化珪素基板の製造方法では、工程(S30)においてSiC基板20が平面的に見て複数並べて配置されている点で、実施の形態1の場合とは異なっている。

【0060】

すなわち、本実施の形態における炭化珪素基板の製造方法においては、まず工程(S10)において実施の形態1の場合と同様にベース基板10が準備されるとともに、SiC基板20が複数枚準備される。次に、工程(S20)が必要に応じて実施の形態1の場合と同様に実施される。その後、図4を参照して、工程(S30)において、SiC基板20が、ベース基板10の主面10A上に平面的に見て複数並べて載置されて積層基板2が作製される。すなわち、SiC基板20は、ベース基板10の主面10Aに沿って複数並べて配置される。

【0061】

より具体的には、たとえば複数枚のSiC基板20は、ベース基板10の主面10A上において隣接するSiC基板20同士が互いに接触するように、マトリックス状に配置される。その後、実施の形態1の場合と同様に工程(S40)および(S50)が実施され、かつ必要に応じて工程(S60)が実施されて図5に示す炭化珪素基板1が得られる。本実施の形態においては、工程(S30)において複数枚のSiC基板20がベース基板10上に載置され、当該複数枚のSiC基板20とベース基板10とが工程(S40)において接合される。そのため、本実施の形態における炭化珪素基板の製造方法によれば、高品質なSiC層20を有する大口径な基板として取り扱うことが可能な炭化珪素基板1を製造することができる。そして、この炭化珪素基板1を用いることにより、半導体装置の製造プロセスを効率化することができる。

【0062】

また、図4を参照して、SiC基板20の端面20Cは、当該SiC基板20の主面20Aに対し実質的に垂直となっていることが好ましい。これにより、炭化珪素基板1を容易に製造することができる。ここで、たとえば上記端面20Cと主面20Aとのなす角が85°以上95°以下であれば、上記端面20Cと主面20Aとは実質的に垂直であると判断することができる。

【0063】

(実施の形態3)

次に、上記本発明の炭化珪素基板を用いて作製される半導体装置の一例を実施の形態3として説明する。図6を参照して、本発明による半導体装置101は、縦型DiMOSFET(Double Implanted MOSFET)であって、基板102、バッファ層121、耐圧保持層122、p領域123、n+領域124、p+領域125、酸化膜126、ソース電極111および上部ソース電極127、ゲート電極110および基板102の裏面側に形成されたドレイン電極112を備える。具体的には、導電型がn型の炭化珪素からなる基板102の表面上に、炭化珪素からなるバッファ層121が形成されている。基板102としては、上記実施の形態1および2において説明した製造方法を含む本発明の炭化珪素基板の製造方法により製造された炭化珪素基板が採用される。そして、上記実施の形態1および2の炭化珪素基板1が採用される場合、バッファ層121は、炭化珪素基板1のSiC層20上に形成される。バッファ層121は導電型がn型であり、その厚みはたとえば0.5μmである。また、バッファ層121におけるn型の導電性不純物の濃度はたとえば5×1017cm−3とすることができる。このバッファ層121上には耐圧保持層122が形成されている。この耐圧保持層122は、導電型がn型の炭化珪素からなり、たとえばその厚みは10μmである。また、耐圧保持層122におけるn型の導電性不純物の濃度としては、たとえば5×1015cm−3という値を用いることができる。

【0064】

この耐圧保持層122の表面には、導電型がp型であるp領域123が互いに間隔を隔てて形成されている。p領域123の内部においては、p領域123の表面層にn+領域124が形成されている。また、このn+領域124に隣接する位置には、p+領域125が形成されている。一方のp領域123におけるn+領域124上から、p領域123、2つのp領域123の間において露出する耐圧保持層122、他方のp領域123および当該他方のp領域123におけるn+領域124上にまで延在するように、酸化膜126が形成されている。酸化膜126上にはゲート電極110が形成されている。また、n+領域124およびp+領域125上にはソース電極111が形成されている。このソース電極111上には上部ソース電極127が形成されている。そして、基板102において、バッファ層121が形成された側の表面とは反対側の面である裏面にドレイン電極112が形成されている。

【0065】

本実施の形態における半導体装置101においては、基板102として上記実施の形態1および2において説明した製造方法を含む本発明の炭化珪素基板の製造方法により製造された炭化珪素基板が採用される。すなわち、半導体装置101は、炭化珪素基板としての基板102と、基板102上に形成されたエピタキシャル成長層としてのバッファ層121および耐圧保持層122と、耐圧保持層122上に形成されたソース電極111とを備えている。そして、当該基板102は、本発明の炭化珪素基板の製造方法により製造されている。ここで、上述のように、本発明の炭化珪素基板の製造方法により製造された基板は、半導体装置の製造コストの低減を実現可能な炭化珪素基板となっている。そのため、半導体装置101は、製造コストが低減された半導体装置となっている。

【0066】

次に、図7〜図11を参照して、図6に示した半導体装置101の製造方法を説明する。図7を参照して、まず、炭化珪素基板準備工程(S110)を実施する。ここでは、たとえば(03−38)面が主面となった炭化珪素からなる基板102(図8参照)を準備する。この基板102としては、上記実施の形態1および2において説明した製造方法により製造された炭化珪素基板1を含む上記本発明の炭化珪素基板が準備される。

【0067】

また、この基板102(図8参照)としては、たとえば導電型がn型であり、基板抵抗が0.02Ωcmといった基板を用いてもよい。

【0068】

次に、図7に示すように、エピタキシャル層形成工程(S120)を実施する。具体的には、基板102の表面上にバッファ層121を形成する。このバッファ層121は、基板102として採用される炭化珪素基板1のSiC層20の主面20A上(図3参照)に形成される。バッファ層121としては、導電型がn型の炭化珪素からなり、たとえばその厚みが0.5μmのエピタキシャル層を形成する。バッファ層121における導電型不純物の密度は、たとえば5×1017cm−3といった値を用いることができる。そして、このバッファ層121上に、図8に示すように耐圧保持層122を形成する。この耐圧保持層122としては、導電型がn型の炭化珪素からなる層をエピタキシャル成長法によって形成する。この耐圧保持層122の厚みとしては、たとえば10μmといった値を用いることができる。また、この耐圧保持層122におけるn型の導電性不純物の密度としては、たとえば5×1015cm−3といった値を用いることができる。

【0069】

次に、図7に示すように注入工程(S130)を実施する。具体的には、フォトリソグラフィおよびエッチングを用いて形成した酸化膜をマスクとして用いて、導電型がp型の不純物を耐圧保持層122に注入することにより、図9に示すようにp領域123を形成する。また、用いた酸化膜を除去した後、再度新たなパターンを有する酸化膜を、フォトリソグラフィおよびエッチングを用いて形成する。そして、当該酸化膜をマスクとして、n型の導電性不純物を所定の領域に注入することにより、n+領域124を形成する。また、同様の手法により、導電型がp型の導電性不純物を注入することにより、p+領域125を形成する。その結果、図9に示すような構造を得る。

【0070】

このような注入工程の後、活性化アニール処理を行なう。この活性化アニール処理としては、たとえばアルゴンガスを雰囲気ガスとして用いて、加熱温度1700℃、加熱時間30分といった条件を用いることができる。

【0071】

次に、図7に示すようにゲート絶縁膜形成工程(S140)を実施する。具体的には、図10に示すように、耐圧保持層122、p領域123、n+領域124、p+領域125上を覆うように酸化膜126を形成する。この酸化膜126を形成するための条件としては、たとえばドライ酸化(熱酸化)を行なってもよい。このドライ酸化の条件としては、加熱温度を1200℃、加熱時間を30分といった条件を用いることができる。

【0072】

その後、図7に示すように窒化処理工程(S150)を実施する。具体的には、雰囲気ガスを一酸化窒素(NO)として、アニール処理を行なう。アニール処理の温度条件としては、たとえば加熱温度を1100℃、加熱時間を120分とする。この結果、酸化膜126と下層の耐圧保持層122、p領域123、n+領域124、p+領域125との間の界面近傍に窒素原子が導入される。また、この一酸化窒素を雰囲気ガスとして用いたアニール工程の後、さらに不活性ガスであるアルゴン(Ar)ガスを用いたアニールを行なってもよい。具体的には、アルゴンガスを雰囲気ガスとして用いて、加熱温度を1100℃、加熱時間を60分といった条件を用いてもよい。

【0073】

次に、図7に示すように電極形成工程(S160)を実施する。具体的には、酸化膜126上にフォトリソグラフィ法を用いてパターンを有するレジスト膜を形成する。当該レジスト膜をマスクとして用いて、n+領域124およびp+領域125上に位置する酸化膜の部分をエッチングにより除去する。この後、レジスト膜上および当該酸化膜126において形成された開口部内部においてn+領域124およびp+領域125と接触するように、金属などの導電体膜を形成する。その後、レジスト膜を除去することにより、当該レジスト膜上に位置していた導電体膜を除去(リフトオフ)する。ここで、導電体としては、たとえばニッケル(Ni)を用いることができる。この結果、図11に示すように、ソース電極111およびドレイン電極112を得ることができる。なお、ここでアロイ化のための熱処理を行なうことが好ましい。具体的には、たとえば雰囲気ガスとして不活性ガスであるアルゴン(Ar)ガスを用い、加熱温度を950℃、加熱時間を2分といった熱処理(アロイ化処理)を行なう。

【0074】

その後、ソース電極111上に上部ソース電極127(図6参照)を形成する。また、酸化膜126上にゲート電極110(図6参照)を形成する。このようにして、図6に示す半導体装置101を得ることができる。

【0075】

なお、上記実施の形態3においては、本発明の炭化珪素基板を用いて作製可能な半導体装置の一例として、縦型MOSFETに関して説明したが、作製可能な半導体装置はこれに限られない。たとえばJFET(Junction Field Effect Transistor;接合型電界効果トランジスタ)、IGBT(Insulated Gate Bipolar Transistor;絶縁ゲートバイポーラトランジスタ)、ショットキーバリアダイオードなど、種々の半導体装置が本発明の炭化珪素基板を用いて作製可能である。

【0076】

また、上記実施の形態3においては、(03−38)面を主面とする炭化珪素基板上に動作層として機能するエピタキシャル層を形成して半導体装置が作製される場合について説明したが、上記主面として採用可能な結晶面はこれに限られず、(0001)面を含めて用途に応じた任意の結晶面を上記主面として採用することができる。

【0077】

さらに、上記主面(炭化珪素基板1のSiC基板(SiC層)20の主面20A)として、<01−10>方向における(0−33−8)面に対するオフ角が−3°以上+5°以下である主面を採用することにより、炭化珪素基板を用いてMOSFET等を作製した場合におけるチャネル移動度を、より一層向上させることができる。ここで、六方晶の単結晶炭化珪素の(0001)面はシリコン面、(000−1)面はカーボン面と定義される。また、「<01−10>方向における(0−33−8)面に対するオフ角」とは、<000−1>方向およびオフ方位の基準としての<01−10>方向の張る平面への上記主表面の法線の正射影と、(0−33−8)面の法線とのなす角度であり、その符号は、上記正射影が<01−10>方向に対して平行に近づく場合が正であり、上記正射影が<000−1>方向に対して平行に近づく場合が負である。そして、上記<01−10>方向における(0−33−8)面に対するオフ角が−3°以上+5°以下である主面とは、当該主面が炭化珪素結晶において上記条件を満たすカーボン面側の面を意味する。なお、本願において(0−33−8)面は、結晶面を規定するための軸の設定により表現が異なる等価なカーボン面側の面を含むとともに、シリコン面側の面を含まない。

【0078】

なお、上記本発明の炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置において、ベース基板(ベース層)の直径は2インチ以上であることが好ましく、6インチ以上であることがより好ましい。また、パワーデバイスへの適用を考慮すると、SiC層(SiC基板)を構成する炭化珪素のポリタイプは4H型であることが好ましい。また、ベース基板とSiC基板は結晶構造が同一であることが好ましい。また、ベース層とSiC層との熱膨張率の差は、炭化珪素基板を用いた半導体装置の製造プロセスにおいて割れが発生しない程度に小さいことが好ましい。また、ベース基板およびSiC基板のそれぞれにおいて、面内における厚みのばらつきは小さいことが好ましく、具体的には当該厚みのばらつきは10μm以下であることが好ましい。また、炭化珪素基板の厚み方向に電流が流れる縦型デバイスへの適用を考慮すると、ベース層の電気抵抗率は50mΩcm未満であることが好ましく、10mΩcm未満であることが好ましい。また、取り扱いを容易にする観点から、炭化珪素基板の厚みは300μm以上であることが好ましい。また、ベース基板とSiC基板とを接合する工程における積層基板の加熱には、たとえば抵抗加熱法、高周波誘導加熱法、ランプアニール法などを採用することができる。

【0079】

今回開示された実施の形態はすべての点で例示であって、制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味、および範囲内でのすべての変更が含まれることが意図される。

【産業上の利用可能性】

【0080】

本発明の炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置は、炭化珪素基板を用いた半導体装置の製造コストの低減が求められる炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置に、特に有利に適用され得る。

【符号の説明】

【0081】

1 炭化珪素基板、2 積層基板、10 ベース層(ベース基板)、10A,10B 主面、20 SiC層(SiC基板)、20A,20B 主面、20C 端面、30 エピタキシャル成長層、101 半導体装置、102 基板、110 ゲート電極、111 ソース電極、112 ドレイン電極、121 バッファ層、122 耐圧保持層、123 p領域、124 n+領域、125 p+領域、126 酸化膜、127 上部ソース電極。

【技術分野】

【0001】

本発明は炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置に関し、より特定的には、炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置に関するものである。

【背景技術】

【0002】

近年、半導体装置の高耐圧化、低損失化、高温環境下での使用などを可能とするため、半導体装置を構成する材料として炭化珪素の採用が進められつつある。炭化珪素は、従来から半導体装置を構成する材料として広く使用されている珪素に比べてバンドギャップが大きいワイドバンドギャップ半導体である。そのため、半導体装置を構成する材料として炭化珪素を採用することにより、半導体装置の高耐圧化、オン抵抗の低減などを達成することができる。また、炭化珪素を材料として採用した半導体装置は、珪素を材料として採用した半導体装置に比べて、高温環境下で使用された場合の特性の低下が小さいという利点も有している。

【0003】

このような状況の下、半導体装置の製造に用いられる炭化珪素結晶および炭化珪素基板の製造方法については、種々の検討がなされ、様々なアイデアが提案されている(たとえば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2002−280531号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、炭化珪素は常圧で液相を持たない。また、結晶成長温度が2000℃以上と非常に高く、成長条件の制御や、その安定化が困難である。そのため、炭化珪素単結晶は、高品質を維持しつつ大口径化することが困難であり、大口径の高品質な炭化珪素基板を得ることは容易ではない。そして、大口径の炭化珪素基板の作製が困難であることに起因して、炭化珪素基板の製造コストが上昇するだけでなく、当該炭化珪素基板を用いて半導体装置を製造するに際しては、1バッチあたりの生産個数が少なくなり、半導体装置の製造コストが高くなるという問題があった。また、製造コストの高い炭化珪素単結晶を基板として有効に利用することにより、半導体装置の製造コストを低減できるものと考えられる。

【0006】

そこで、本発明の目的は、炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置を提供することである。

【課題を解決するための手段】

【0007】

本発明に従った炭化珪素基板の製造方法は、炭化珪素からなるベース基板および単結晶炭化珪素からなるSiC基板を準備する工程と、ベース基板の主面上に接触するようにSiC基板を載置して、積層基板を作製する工程と、積層基板を、SiC基板よりもベース基板の温度が高くなるように加熱することにより、ベース基板とSiC基板とを接合する工程と、SiC基板が接合されたベース基板の、SiC基板とは反対側の主面上にエピタキシャル成長層を形成する工程とを備えている。

【0008】

上述のように、高品質な炭化珪素単結晶は、大口径化が困難である。一方、炭化珪素基板を用いた半導体装置の製造プロセスにおいて効率よく製造を行なうためには、所定の形状および大きさに統一された基板が必要である。そのため、高品質な炭化珪素単結晶(たとえば欠陥密度が小さい炭化珪素単結晶)が得られた場合でも、切断等によって所定の形状等に加工できない領域は、有効に利用されない可能性がある。

【0009】

これに対し、本発明の炭化珪素基板の製造方法においては、ベース基板上に単結晶炭化珪素からなるSiC基板が載置されて作製された積層基板が加熱されることによりベース基板とSiC基板とが接合されて、炭化珪素基板が製造される。そのため、たとえば欠陥密度が大きく、低品質な炭化珪素結晶からなるベース基板を上記所定の形状および大きさに加工し、当該ベース基板上に高品質であるものの所望の形状等が実現されていない炭化珪素単結晶をSiC基板として載置し、加熱することにより炭化珪素基板を製造することができる。このようにして得られた炭化珪素基板は、全体として所定の形状および大きさに統一されているため、半導体装置の製造の効率化に寄与することができる。また、このような炭化珪素基板の高品質なSiC基板上に、たとえばエピタキシャル成長により半導体層を形成して半導体装置を製造することが可能であるため、炭化珪素単結晶を有効に利用することができる。その結果、本発明の炭化珪素基板によれば、炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板を製造することができる。

【0010】

さらに、上記接合前の積層基板においては、ベース基板やSiC基板の反り、うねりなどに起因して、ベース基板とSiC基板との間に隙間が形成される。そのため、接合後の積層基板においては当該隙間を起源とするボイドが形成される。そして、ベース基板とSiC基板とを接合する工程において、SiC基板よりもベース基板の温度が高くなるように積層基板が加熱されることにより、当該ボイドはベース基板側に移動し、最終的にはベース基板のSiC基板とは反対側の主面にまで到達する場合がある。その場合、当該ボイドに起因して、ベース基板のSiC基板とは反対側の主面の粗さが大きくなり、炭化珪素基板を用いた半導体装置の製造プロセスに不具合が生じるおそれがある。具体的には、たとえば半導体装置の製造プロセスにおいて炭化珪素基板を真空チャックにより保持する際、十分な吸着力が得られない場合がある。

【0011】

これに対し、本発明の炭化珪素基板の製造方法では、SiC基板が接合されたベース基板の、SiC基板とは反対側の主面上にエピタキシャル成長層を形成する工程を備えている。このように、ボイドの到達により粗さが大きくなるおそれのある上記主面をエピタキシャル成長層により覆うことにより、上記半導体装置の製造プロセスにおける不具合を抑制することができる。

【0012】

上記炭化珪素基板の製造方法においては、ベース基板とSiC基板とを接合する工程では、ベース基板が、ベース基板を構成する炭化珪素の昇華温度以上の温度域に加熱されてもよい。

【0013】

これにより、ベース基板を構成する炭化珪素が昇華し、SiC基板上で再結晶する。その結果、ベース基板とSiC基板との接合が容易に進行する。

【0014】

上記炭化珪素基板の製造方法においては、エピタキシャル成長層を形成する工程よりも後に、SiC基板のベース基板とは反対側の主面を研磨する工程をさらに備えていてもよい。

【0015】

これにより、SiC基板の主面上に半導体装置のバッファ層や耐圧保持層などとして機能する高品質な半導体層をエピタキシャル成長により形成することが容易となる。

【0016】

上記炭化珪素基板の製造方法においては、エピタキシャル成長層を形成する工程では、液相法により上記エピタキシャル成長層が形成されてもよい。また、上記炭化珪素基板の製造方法においては、エピタキシャル成長層を形成する工程では、化学気相成長法により上記エピタキシャル成長層が形成されてもよい。このように、液相法や化学気相成長法を採用することにより、上記エピタキシャル成長層を容易に形成することができる。

【0017】

上記炭化珪素基板の製造方法においては、積層基板を作製する工程よりも前に、積層基板を作製する工程において互いに接触すべきベース基板およびSiC基板の主面を平坦化する工程をさらに備えていてもよい。ベース基板とSiC基板との接合面となるべき面を予め平坦化しておくことにより、ベース基板とSiC基板とをより確実に接合することができる。

【0018】

上記炭化珪素基板の製造方法においては、積層基板を作製する工程は、積層基板を作製する工程よりも前に、積層基板を作製する工程において互いに接触すべきベース基板およびSiC基板の主面を研磨することなく実施されてもよい。これにより、炭化珪素基板の製造コストを低減することができる。ここで、積層基板を作製する工程において互いに接触すべきベース基板およびSiC基板の主面は、上述のように研磨されなくてもよい。しかし、基板作製時におけるスライスなどにより形成された表面付近のダメージ層を除去する観点から、たとえばエッチングによって当該ダメージ層が除去される工程が実施された後に上記積層基板を作製する工程が実施されることが好ましい。

【0019】

上記炭化珪素基板の製造方法においては、積層基板を作製する工程では、SiC基板は、平面的に見て複数並べて載置されてもよい。別の観点から説明すると、SiC基板は、ベース基板の主面に沿って複数並べて載置されてもよい。

【0020】

上述のように、高品質な炭化珪素単結晶は、大口径化が困難である。これに対し、高品質な炭化珪素単結晶から採取した複数のSiC基板を平面的に複数並べて配置したうえで、ベース基板とSiC基板とを接合することにより、高品質なSiC層を有する大口径な基板として取り扱うことが可能な炭化珪素基板を得ることができる。そして、この炭化珪素基板を用いることにより、半導体装置の製造プロセスを効率化することができる。なお、半導体装置の製造プロセスを効率化するためには、上記複数のSiC基板のうち互いに隣り合うSiC基板は、互いに接触して配置されていることが好ましい。より具体的には、たとえば上記複数のSiC基板は、平面的に見てマトリックス状に敷き詰められていることが好ましい。

【0021】

上記炭化珪素基板の製造方法においては、積層基板を作製する工程では、SiC基板のベース基板とは反対側の主面は、{0001}面に対するオフ角が50°以上65°以下となっていてもよい。

【0022】

六方晶の単結晶炭化珪素は、<0001>方向に成長させることにより、高品質な単結晶を効率よく作製することができる。そして、<0001>方向に成長させた炭化珪素単結晶からは、{0001}面を主面とする炭化珪素基板を効率よく採取することができる。一方、面方位{0001}に対するオフ角が50°以上65°以下である主面を有する炭化珪素基板を用いることにより、高性能な半導体装置を製造できる場合がある。

【0023】

具体的には、たとえばMOSFET(Metal Oxide Semiconductor Field Effect Transistor;酸化膜電界効果トランジスタ)の作製に用いられる炭化珪素基板は、面方位{0001}に対するオフ角が8°程度以下である主面を有していることが一般的である。そして、当該主面上にエピタキシャル成長により半導体層が形成されるとともに、当該半導体層上に酸化膜、電極などが形成され、MOSFETが得られる。このMOSFETにおいては、半導体層と酸化膜との界面を含む領域にチャネル領域が形成される。しかし、このような構造を有するMOSFETにおいては、基板の主面の{0001}面に対するオフ角が8°程度以下であることに起因して、チャネル領域が形成される半導体層と酸化膜との界面付近において多くの界面準位が形成され、キャリアの走行の妨げとなって、チャネル移動度が低下する。

【0024】

これに対し、上記積層基板を作製する工程において、SiC基板のベース基板とは反対側の主面の、{0001}面に対するオフ角を50°以上65°以下とすることにより、製造される炭化珪素基板の主面の{0001}面に対するオフ角が50°以上65°以下となる。そのため、上記界面準位の形成が低減され、オン抵抗が低減されたMOSFET等を作製可能な炭化珪素基板を製造することができる。

【0025】

上記炭化珪素基板の製造方法においては、積層基板を作製する工程では、SiC基板のベース基板とは反対側の主面のオフ方位と<1−100>方向とのなす角は5°以下となっていてもよい。

【0026】

<1−100>方向は、炭化珪素基板における代表的なオフ方位である。そして、基板の製造工程におけるスライス加工のばらつき等に起因したオフ方位のばらつきを5°以下とすることにより、炭化珪素基板上への半導体層の形成などを容易にすることができる。

【0027】

上記炭化珪素基板の製造方法においては、積層基板を作製する工程では、SiC基板のベース基板とは反対側の主面の、<1−100>方向における{03−38}面に対するオフ角は−3°以上5°以下とすることができる。

【0028】

これにより、炭化珪素基板を用いてMOSFETを作製した場合におけるチャネル移動度を、より一層向上させることができる。ここで、面方位{03−38}に対するオフ角を−3°以上+5°以下としたのは、チャネル移動度と当該オフ角との関係を調査した結果、この範囲内で特に高いチャネル移動度が得られたことに基づいている。

【0029】

また、「<1−100>方向における{03−38}面に対するオフ角」とは、<1−100>方向および<0001>方向の張る平面への上記主面の法線の正射影と、{03−38}面の法線とのなす角度であり、その符号は、上記正射影が<1−100>方向に対して平行に近づく場合が正であり、上記正射影が<0001>方向に対して平行に近づく場合が負である。

【0030】

なお、上記主面の面方位は、実質的に{03−38}であることがより好ましく、上記主面の面方位は{03−38}であることがさらに好ましい。ここで、主面の面方位が実質的に{03−38}であるとは、基板の加工精度などを考慮して実質的に面方位が{03−38}とみなせるオフ角の範囲に基板の主面の面方位が含まれていることを意味し、この場合のオフ角の範囲はたとえば{03−38}に対してオフ角が±2°の範囲である。これにより、上述したチャネル移動度をより一層向上させることができる。

【0031】

上記炭化珪素基板の製造方法においては、積層基板を作製する工程では、SiC基板のベース基板とは反対側の主面のオフ方位と<11−20>方向とのなす角は5°以下となっていてもよい。

【0032】

<11−20>方向は、上記<1−100>方向と同様に、炭化珪素基板における代表的なオフ方位である。そして、基板の製造工程におけるスライス加工のばらつき等に起因したオフ方位のばらつきを±5°とすることにより、SiC基板上への半導体層の形成などを容易にすることができる。

【0033】

上記炭化珪素基板の製造方法においては、ベース基板とSiC基板とを接合する工程では、大気雰囲気を減圧することにより得られた雰囲気中において積層基板が加熱されてもよい。これにより、炭化珪素基板の製造コストを低減することができる。

【0034】

上記炭化珪素基板の製造方法においては、ベース基板とSiC基板とを接合する工程では、10−1Paよりも高く104Paよりも低い圧力下において積層基板が加熱されてもよい。これにより、簡素な装置により上記接合を実施することが可能になるとともに比較的短時間で接合を実施するための雰囲気を得ることが可能となる。その結果、炭化珪素基板の製造コストを低減することができる。

【0035】

本発明に従った半導体装置の製造方法は、炭化珪素基板を準備する工程と、炭化珪素基板上にエピタキシャル成長により半導体層を形成する工程と、半導体層上に電極を形成する工程とを備えている。そして、炭化珪素基板を準備する工程では、上記本発明の炭化珪素基板の製造方法により炭化珪素基板が製造される。本発明の半導体装置の製造方法によれば、上記本発明の炭化珪素基板の製造方法により製造された炭化珪素基板を用いて半導体装置が製造されるため、半導体装置の製造コストを低減することができる。

【0036】

本発明に従った炭化珪素基板は、上記本発明の炭化珪素基板の製造方法により製造されている。これにより、本発明の炭化珪素基板は、炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板となっている。

【0037】

本発明に従った半導体装置は、上記本発明の半導体装置の製造方法により製造されている。これにより、本発明の半導体装置は、製造コストが低減された半導体装置となっている。

【発明の効果】

【0038】

以上の説明から明らかなように、本発明の炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置によれば、炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置を提供することができる。

【図面の簡単な説明】

【0039】

【図1】炭化珪素基板の製造方法の概略を示すフローチャートである。

【図2】炭化珪素基板の製造方法を説明するための概略断面図である。

【図3】炭化珪素基板の構造を示す概略断面図である。

【図4】実施の形態2における炭化珪素基板の製造方法を説明するための概略断面図である。

【図5】実施の形態2における炭化珪素基板の構造を示す概略断面図である。

【図6】縦型MOSFETの構造を示す概略断面図である。

【図7】縦型MOSFETの製造方法の概略を示すフローチャートである。

【図8】縦型MOSFETの製造方法を説明するための概略断面図である。

【図9】縦型MOSFETの製造方法を説明するための概略断面図である。

【図10】縦型MOSFETの製造方法を説明するための概略断面図である。

【図11】縦型MOSFETの製造方法を説明するための概略断面図である。

【発明を実施するための形態】

【0040】

以下、図面に基づいて本発明の実施の形態を説明する。なお、以下の図面において同一または相当する部分には同一の参照番号を付し、その説明は繰返さない。

【0041】

(実施の形態1)

まず、本発明の一実施の形態である実施の形態1について説明する。図1を参照して、本実施の形態における炭化珪素基板の製造方法では、まず工程(S10)として基板準備工程が実施される。この工程(S10)では、図2を参照して、炭化珪素からなるベース基板10および単結晶炭化珪素からなるSiC基板20が準備される。このとき、SiC基板20の主面20Aは、この製造方法により得られるSiC層20の主面20Aとなることから(後述の図3参照)、所望の主面20Aの面方位に合わせて、SiC基板20の主面20Aの面方位を選択する。また、ベース基板10には、たとえば不純物濃度が2×1019cm−3よりも大きい基板が採用される。そして、SiC基板20には、不純物濃度が5×1018cm−3よりも大きく2×1019cm−3よりも小さい基板を採用することができる。これにより、抵抗率の小さいベース層10を形成しつつ、デバイスプロセスにおける熱処理が実施された場合でも、少なくともSiC層20において積層欠陥の発生を抑制することができる。また、ベース基板10としては、単結晶炭化珪素、多結晶炭化珪素、非晶質炭化珪素、炭化珪素焼結体などからなる基板を採用することができる。

【0042】

次に、工程(S20)として基板平坦化工程が実施される。この工程(S20)では、後述する工程(S30)において互いに接触すべきベース基板10の主面10AおよびSiC基板20の主面20B(接合面)が、たとえば研磨により平坦化される。なお、この工程(S20)は必須の工程ではないが、これを実施しておくことにより、互いに対向するベース基板10とSiC基板20との間の隙間の大きさが均一となるため、後述する工程(S40)において接合面内での反応(接合)の均一性が向上する。その結果、ベース基板10とSiC基板20とをより確実に接合することができる。また、一層確実にベース基板10とSiC基板とを接合するためには、上記接合面の面粗さRaは100nm未満であることが好ましく、50nm未満であることが好ましい。さらに、接合面の面粗さRaを10nm未満とすることにより、より確実な接合を達成することができる。

【0043】

一方、工程(S20)を省略し、互いに接触すべきベース基板10およびSiC基板20の主面を研磨することなく工程(S30)が実施されてもよい。これにより、炭化珪素基板1の製造コストを低減することができる。また、ベース基板10およびSiC基板20の作製時におけるスライスなどにより形成された表面付近のダメージ層を除去する観点から、たとえばエッチングによって当該ダメージ層が除去される工程が上記工程(S20)に代えて、あるいは上記工程(S20)の後に実施された上で、後述する工程(S30)が実施されてもよい。

【0044】

次に、工程(S30)として、積層工程が実施される。この工程(S30)では、図2を参照して、ベース基板10の主面10A上に接触するようにSiC基板20が載置されて、積層基板2が作製される。ここで、この工程(S30)では、SiC基板20のベース基板10とは反対側の主面20Aは、{0001}面に対するオフ角が50°以上65°以下となっていてもよい。これにより、SiC層20の主面20Aが、{0001}面に対するオフ角が50°以上65°以下となっている炭化珪素基板1を容易に製造することができる。また、工程(S30)では、上記主面20Aのオフ方位と<1−100>方向とのなす角は5°以下となっていてもよい。これにより、作製される炭化珪素基板1上(主面20A上)への半導体層の形成などを容易にすることができる。さらに、工程(S30)では、主面20Aの、<1−100>方向における{03−38}面に対するオフ角は−3°以上5°以下であってもよい。これにより、製造される炭化珪素基板1を用いてMOSFETなどを作製した場合におけるチャネル移動度を、より一層向上させることができる。

【0045】

一方、工程(S30)では、主面20Aのオフ方位と<11−20>方向とのなす角は5°以下となっていてもよい。これにより、作製される炭化珪素基板1上への半導体層の形成などを容易にすることができる。

【0046】

次に、工程(S40)として、接合工程が実施される。この工程(S40)では、積層基板2が、SiC基板20よりもベース基板10の温度が高くなるように加熱されることにより、ベース基板10とSiC基板20とが接合される。このとき、ベース基板10は、ベース基板10を構成する炭化珪素の昇華温度以上の温度域に加熱されることが好ましい。これにより、ベース基板10を構成する炭化珪素の昇華、再結晶によって、ベース基板10とSiC基板20との接合が容易に進行する。

【0047】

次に、工程(S50)として、エピタキシャル成長工程が実施される。この工程(S50)では、図2および図3を参照して、SiC基板20が接合されたベース基板10の、SiC基板20とは反対側の主面10B上にエピタキシャル成長層30が形成される。エピタキシャル成長層30の厚みは、たとえば10μm程度とすることができる。

【0048】

ここで、工程(S50)では、液相法によりエピタキシャル成長層30が形成されてもよい。より具体的には、たとえば雰囲気ガスとしてアルゴンなどの不活性ガスを採用し、融液上部の温度を1600℃〜1650℃程度、るつぼ下部の温度を1550℃〜1600℃程度とする条件で炭化珪素をエピタキシャル成長させ、余分な珪素をふっ硝酸にて除去することによりエピタキシャル成長層30を形成することができる。

【0049】

一方、工程(S50)では、化学気相成長法によりエピタキシャル成長層30が形成されてもよい。より具体的には、たとえばSiH4/H2を0.03%〜0.05%程度、C/Siを0.5〜1.2程度、成長温度を1500℃〜1600℃程度とする条件で炭化珪素をエピタキシャル成長させ、エピタキシャル成長層30を形成することができる。

【0050】

次に、工程(S60)として研磨工程が実施される。この工程(S60)では

、SiC基板20のベース基板10とは反対側の主面20Aが研磨される。この工程(S60)は必須の工程ではないが、これを実施することにより、SiC基板20の主面20A上に半導体装置のバッファ層や耐圧保持層などとして機能する高品質な半導体層をエピタキシャル成長により形成することが容易となる。また、この工程(S60)を実施することにより、工程(S50)においてSiC基板20の主面20A上に付着した炭化珪素を除去することができる。以上の手順により、本実施の形態における炭化珪素基板の製造方法が完了し、図3に示す炭化珪素基板1が得られる。

【0051】

図3を参照して、上記製造方法により得られる炭化珪素基板1は、炭化珪素からなるベース層10と、ベース層10の主面10A上に形成され、ベース層10とは別の単結晶炭化珪素からなるSiC層20と、SiC層20とは反対側のベース層10の主面10B上に形成されたエピタキシャル成長層30とを備えている。ここで、SiC層20がベース層10とは別の単結晶炭化珪素からなる状態とは、ベース層10がSiC層20とは別の結晶からなっている場合をいう。ベース層10とSiC層20とが別の結晶からなっている状態とは、ベース層10とSiC層20との間に境界が存在し、たとえば当該境界の一方側と他方側とで欠陥密度が異なっている状態を意味する。このとき、欠陥密度が当該境界において不連続となっていてもよい。

【0052】

上記本実施の形態における炭化珪素基板1の製造方法においては、ベース基板10上に単結晶炭化珪素からなるSiC基板20が載置されて作製された積層基板2が加熱されることにより接合されて、炭化珪素基板1が製造される。そのため、たとえば欠陥密度が大きく、低品質な炭化珪素結晶からなるベース基板10を半導体装置の製造に適した形状および大きさに加工し、当該ベース基板10上に高品質であるものの適切な形状等が実現されていない炭化珪素単結晶をSiC基板20として載置し、加熱することにより炭化珪素基板1を製造することができる。その結果、本発明の炭化珪素基板1は、炭化珪素基板を用いた半導体装置の製造コストの低減を実現可能な炭化珪素基板となっている。

【0053】

さらに、本実施の形態における炭化珪素基板1の製造方法においては、工程(S50)においてエピタキシャル成長層30が形成される。これにより、工程(S40)において形成されるボイドが到達して粗さが大きくなるおそれのあるベース基板10の主面10Bがエピタキシャル成長層30により覆われる。その結果、製造される炭化珪素基板1のベース層10側の主面が真空チャックにより十分に吸着できないなどの不具合を抑制することができる。なお、本実施の形態における上記ボイドの体積は、1μm3以上となり得る。その結果、たとえば工程(S40)が完了した状態におけるベース基板10の主面10Bの粗さ(ラフネス)Raは、5μm以上となり得る。この粗さRaは、ベース基板10の作製時におけるスライスを実施した状態(アズスライス状態)における粗さRa(0.2μm程度)と比較して著しく大きい。

【0054】

また、上記本実施の形態における炭化珪素基板1の製造方法では、工程(S40)では、大気雰囲気を減圧することにより得られた雰囲気中において積層基板2が加熱されてもよい。これにより、炭化珪素基板1の製造コストを低減することができる。

【0055】

さらに、上記本実施の形態における炭化珪素基板1の製造方法では、工程(S40)では、10−1Paよりも高く104Paよりも低い圧力下において積層基板2が加熱されてもよい。これにより、簡素な装置により上記接合を実施することが可能になるとともに比較的短時間で接合を実施するための雰囲気を得ることが可能となる。その結果、炭化珪素基板1の製造コストを低減することができる。

【0056】

ここで、工程(S30)において作製された積層基板2においては、ベース基板10とSiC基板20との間に形成される隙間が100μm以下となっていることが好ましい。これにより、工程(S40)において、ベース基板10とSiC基板20との均一な接合を達成することができる。

【0057】

また、工程(S40)における積層基板2の加熱温度は1800℃以上2500℃以下であることが好ましい。加熱温度が1800℃よりも低い場合、ベース基板10とSiC基板20との接合に長時間を要し、炭化珪素基板1の製造効率が低下する。一方、加熱温度が2500℃を超えると、ベース基板10およびSiC基板20の表面が荒れ、作製される炭化珪素基板1における結晶欠陥の発生が多くなるおそれがある。炭化珪素基板1における欠陥の発生を一層抑制しつつ製造効率を向上させるためには、工程(S40)における積層基板2の加熱温度は1900℃以上2100℃以下であることが好ましい。

【0058】

また、工程(S40)における加熱時の雰囲気は、不活性ガス雰囲気であってもよい。そして、当該雰囲気に不活性ガス雰囲気を採用する場合、アルゴン、ヘリウムおよび窒素からなる群から選択される少なくとも1つを含む不活性ガス雰囲気であることが好ましい。

【0059】

(実施の形態2)

次に、本発明の他の実施の形態である実施の形態2について図4および図5に基づいて説明する。実施の形態2における炭化珪素基板の製造方法は、基本的には実施の形態1における炭化珪素基板の製造方法と同様の手順で実施され、同様の効果を奏する。しかし、実施の形態2における炭化珪素基板の製造方法では、工程(S30)においてSiC基板20が平面的に見て複数並べて配置されている点で、実施の形態1の場合とは異なっている。

【0060】

すなわち、本実施の形態における炭化珪素基板の製造方法においては、まず工程(S10)において実施の形態1の場合と同様にベース基板10が準備されるとともに、SiC基板20が複数枚準備される。次に、工程(S20)が必要に応じて実施の形態1の場合と同様に実施される。その後、図4を参照して、工程(S30)において、SiC基板20が、ベース基板10の主面10A上に平面的に見て複数並べて載置されて積層基板2が作製される。すなわち、SiC基板20は、ベース基板10の主面10Aに沿って複数並べて配置される。

【0061】

より具体的には、たとえば複数枚のSiC基板20は、ベース基板10の主面10A上において隣接するSiC基板20同士が互いに接触するように、マトリックス状に配置される。その後、実施の形態1の場合と同様に工程(S40)および(S50)が実施され、かつ必要に応じて工程(S60)が実施されて図5に示す炭化珪素基板1が得られる。本実施の形態においては、工程(S30)において複数枚のSiC基板20がベース基板10上に載置され、当該複数枚のSiC基板20とベース基板10とが工程(S40)において接合される。そのため、本実施の形態における炭化珪素基板の製造方法によれば、高品質なSiC層20を有する大口径な基板として取り扱うことが可能な炭化珪素基板1を製造することができる。そして、この炭化珪素基板1を用いることにより、半導体装置の製造プロセスを効率化することができる。

【0062】

また、図4を参照して、SiC基板20の端面20Cは、当該SiC基板20の主面20Aに対し実質的に垂直となっていることが好ましい。これにより、炭化珪素基板1を容易に製造することができる。ここで、たとえば上記端面20Cと主面20Aとのなす角が85°以上95°以下であれば、上記端面20Cと主面20Aとは実質的に垂直であると判断することができる。

【0063】

(実施の形態3)

次に、上記本発明の炭化珪素基板を用いて作製される半導体装置の一例を実施の形態3として説明する。図6を参照して、本発明による半導体装置101は、縦型DiMOSFET(Double Implanted MOSFET)であって、基板102、バッファ層121、耐圧保持層122、p領域123、n+領域124、p+領域125、酸化膜126、ソース電極111および上部ソース電極127、ゲート電極110および基板102の裏面側に形成されたドレイン電極112を備える。具体的には、導電型がn型の炭化珪素からなる基板102の表面上に、炭化珪素からなるバッファ層121が形成されている。基板102としては、上記実施の形態1および2において説明した製造方法を含む本発明の炭化珪素基板の製造方法により製造された炭化珪素基板が採用される。そして、上記実施の形態1および2の炭化珪素基板1が採用される場合、バッファ層121は、炭化珪素基板1のSiC層20上に形成される。バッファ層121は導電型がn型であり、その厚みはたとえば0.5μmである。また、バッファ層121におけるn型の導電性不純物の濃度はたとえば5×1017cm−3とすることができる。このバッファ層121上には耐圧保持層122が形成されている。この耐圧保持層122は、導電型がn型の炭化珪素からなり、たとえばその厚みは10μmである。また、耐圧保持層122におけるn型の導電性不純物の濃度としては、たとえば5×1015cm−3という値を用いることができる。

【0064】

この耐圧保持層122の表面には、導電型がp型であるp領域123が互いに間隔を隔てて形成されている。p領域123の内部においては、p領域123の表面層にn+領域124が形成されている。また、このn+領域124に隣接する位置には、p+領域125が形成されている。一方のp領域123におけるn+領域124上から、p領域123、2つのp領域123の間において露出する耐圧保持層122、他方のp領域123および当該他方のp領域123におけるn+領域124上にまで延在するように、酸化膜126が形成されている。酸化膜126上にはゲート電極110が形成されている。また、n+領域124およびp+領域125上にはソース電極111が形成されている。このソース電極111上には上部ソース電極127が形成されている。そして、基板102において、バッファ層121が形成された側の表面とは反対側の面である裏面にドレイン電極112が形成されている。

【0065】

本実施の形態における半導体装置101においては、基板102として上記実施の形態1および2において説明した製造方法を含む本発明の炭化珪素基板の製造方法により製造された炭化珪素基板が採用される。すなわち、半導体装置101は、炭化珪素基板としての基板102と、基板102上に形成されたエピタキシャル成長層としてのバッファ層121および耐圧保持層122と、耐圧保持層122上に形成されたソース電極111とを備えている。そして、当該基板102は、本発明の炭化珪素基板の製造方法により製造されている。ここで、上述のように、本発明の炭化珪素基板の製造方法により製造された基板は、半導体装置の製造コストの低減を実現可能な炭化珪素基板となっている。そのため、半導体装置101は、製造コストが低減された半導体装置となっている。

【0066】

次に、図7〜図11を参照して、図6に示した半導体装置101の製造方法を説明する。図7を参照して、まず、炭化珪素基板準備工程(S110)を実施する。ここでは、たとえば(03−38)面が主面となった炭化珪素からなる基板102(図8参照)を準備する。この基板102としては、上記実施の形態1および2において説明した製造方法により製造された炭化珪素基板1を含む上記本発明の炭化珪素基板が準備される。

【0067】

また、この基板102(図8参照)としては、たとえば導電型がn型であり、基板抵抗が0.02Ωcmといった基板を用いてもよい。

【0068】

次に、図7に示すように、エピタキシャル層形成工程(S120)を実施する。具体的には、基板102の表面上にバッファ層121を形成する。このバッファ層121は、基板102として採用される炭化珪素基板1のSiC層20の主面20A上(図3参照)に形成される。バッファ層121としては、導電型がn型の炭化珪素からなり、たとえばその厚みが0.5μmのエピタキシャル層を形成する。バッファ層121における導電型不純物の密度は、たとえば5×1017cm−3といった値を用いることができる。そして、このバッファ層121上に、図8に示すように耐圧保持層122を形成する。この耐圧保持層122としては、導電型がn型の炭化珪素からなる層をエピタキシャル成長法によって形成する。この耐圧保持層122の厚みとしては、たとえば10μmといった値を用いることができる。また、この耐圧保持層122におけるn型の導電性不純物の密度としては、たとえば5×1015cm−3といった値を用いることができる。

【0069】

次に、図7に示すように注入工程(S130)を実施する。具体的には、フォトリソグラフィおよびエッチングを用いて形成した酸化膜をマスクとして用いて、導電型がp型の不純物を耐圧保持層122に注入することにより、図9に示すようにp領域123を形成する。また、用いた酸化膜を除去した後、再度新たなパターンを有する酸化膜を、フォトリソグラフィおよびエッチングを用いて形成する。そして、当該酸化膜をマスクとして、n型の導電性不純物を所定の領域に注入することにより、n+領域124を形成する。また、同様の手法により、導電型がp型の導電性不純物を注入することにより、p+領域125を形成する。その結果、図9に示すような構造を得る。

【0070】

このような注入工程の後、活性化アニール処理を行なう。この活性化アニール処理としては、たとえばアルゴンガスを雰囲気ガスとして用いて、加熱温度1700℃、加熱時間30分といった条件を用いることができる。

【0071】

次に、図7に示すようにゲート絶縁膜形成工程(S140)を実施する。具体的には、図10に示すように、耐圧保持層122、p領域123、n+領域124、p+領域125上を覆うように酸化膜126を形成する。この酸化膜126を形成するための条件としては、たとえばドライ酸化(熱酸化)を行なってもよい。このドライ酸化の条件としては、加熱温度を1200℃、加熱時間を30分といった条件を用いることができる。

【0072】

その後、図7に示すように窒化処理工程(S150)を実施する。具体的には、雰囲気ガスを一酸化窒素(NO)として、アニール処理を行なう。アニール処理の温度条件としては、たとえば加熱温度を1100℃、加熱時間を120分とする。この結果、酸化膜126と下層の耐圧保持層122、p領域123、n+領域124、p+領域125との間の界面近傍に窒素原子が導入される。また、この一酸化窒素を雰囲気ガスとして用いたアニール工程の後、さらに不活性ガスであるアルゴン(Ar)ガスを用いたアニールを行なってもよい。具体的には、アルゴンガスを雰囲気ガスとして用いて、加熱温度を1100℃、加熱時間を60分といった条件を用いてもよい。

【0073】

次に、図7に示すように電極形成工程(S160)を実施する。具体的には、酸化膜126上にフォトリソグラフィ法を用いてパターンを有するレジスト膜を形成する。当該レジスト膜をマスクとして用いて、n+領域124およびp+領域125上に位置する酸化膜の部分をエッチングにより除去する。この後、レジスト膜上および当該酸化膜126において形成された開口部内部においてn+領域124およびp+領域125と接触するように、金属などの導電体膜を形成する。その後、レジスト膜を除去することにより、当該レジスト膜上に位置していた導電体膜を除去(リフトオフ)する。ここで、導電体としては、たとえばニッケル(Ni)を用いることができる。この結果、図11に示すように、ソース電極111およびドレイン電極112を得ることができる。なお、ここでアロイ化のための熱処理を行なうことが好ましい。具体的には、たとえば雰囲気ガスとして不活性ガスであるアルゴン(Ar)ガスを用い、加熱温度を950℃、加熱時間を2分といった熱処理(アロイ化処理)を行なう。

【0074】

その後、ソース電極111上に上部ソース電極127(図6参照)を形成する。また、酸化膜126上にゲート電極110(図6参照)を形成する。このようにして、図6に示す半導体装置101を得ることができる。

【0075】

なお、上記実施の形態3においては、本発明の炭化珪素基板を用いて作製可能な半導体装置の一例として、縦型MOSFETに関して説明したが、作製可能な半導体装置はこれに限られない。たとえばJFET(Junction Field Effect Transistor;接合型電界効果トランジスタ)、IGBT(Insulated Gate Bipolar Transistor;絶縁ゲートバイポーラトランジスタ)、ショットキーバリアダイオードなど、種々の半導体装置が本発明の炭化珪素基板を用いて作製可能である。

【0076】

また、上記実施の形態3においては、(03−38)面を主面とする炭化珪素基板上に動作層として機能するエピタキシャル層を形成して半導体装置が作製される場合について説明したが、上記主面として採用可能な結晶面はこれに限られず、(0001)面を含めて用途に応じた任意の結晶面を上記主面として採用することができる。

【0077】

さらに、上記主面(炭化珪素基板1のSiC基板(SiC層)20の主面20A)として、<01−10>方向における(0−33−8)面に対するオフ角が−3°以上+5°以下である主面を採用することにより、炭化珪素基板を用いてMOSFET等を作製した場合におけるチャネル移動度を、より一層向上させることができる。ここで、六方晶の単結晶炭化珪素の(0001)面はシリコン面、(000−1)面はカーボン面と定義される。また、「<01−10>方向における(0−33−8)面に対するオフ角」とは、<000−1>方向およびオフ方位の基準としての<01−10>方向の張る平面への上記主表面の法線の正射影と、(0−33−8)面の法線とのなす角度であり、その符号は、上記正射影が<01−10>方向に対して平行に近づく場合が正であり、上記正射影が<000−1>方向に対して平行に近づく場合が負である。そして、上記<01−10>方向における(0−33−8)面に対するオフ角が−3°以上+5°以下である主面とは、当該主面が炭化珪素結晶において上記条件を満たすカーボン面側の面を意味する。なお、本願において(0−33−8)面は、結晶面を規定するための軸の設定により表現が異なる等価なカーボン面側の面を含むとともに、シリコン面側の面を含まない。

【0078】

なお、上記本発明の炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置において、ベース基板(ベース層)の直径は2インチ以上であることが好ましく、6インチ以上であることがより好ましい。また、パワーデバイスへの適用を考慮すると、SiC層(SiC基板)を構成する炭化珪素のポリタイプは4H型であることが好ましい。また、ベース基板とSiC基板は結晶構造が同一であることが好ましい。また、ベース層とSiC層との熱膨張率の差は、炭化珪素基板を用いた半導体装置の製造プロセスにおいて割れが発生しない程度に小さいことが好ましい。また、ベース基板およびSiC基板のそれぞれにおいて、面内における厚みのばらつきは小さいことが好ましく、具体的には当該厚みのばらつきは10μm以下であることが好ましい。また、炭化珪素基板の厚み方向に電流が流れる縦型デバイスへの適用を考慮すると、ベース層の電気抵抗率は50mΩcm未満であることが好ましく、10mΩcm未満であることが好ましい。また、取り扱いを容易にする観点から、炭化珪素基板の厚みは300μm以上であることが好ましい。また、ベース基板とSiC基板とを接合する工程における積層基板の加熱には、たとえば抵抗加熱法、高周波誘導加熱法、ランプアニール法などを採用することができる。

【0079】

今回開示された実施の形態はすべての点で例示であって、制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味、および範囲内でのすべての変更が含まれることが意図される。

【産業上の利用可能性】

【0080】

本発明の炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置は、炭化珪素基板を用いた半導体装置の製造コストの低減が求められる炭化珪素基板の製造方法、半導体装置の製造方法、炭化珪素基板および半導体装置に、特に有利に適用され得る。

【符号の説明】

【0081】

1 炭化珪素基板、2 積層基板、10 ベース層(ベース基板)、10A,10B 主面、20 SiC層(SiC基板)、20A,20B 主面、20C 端面、30 エピタキシャル成長層、101 半導体装置、102 基板、110 ゲート電極、111 ソース電極、112 ドレイン電極、121 バッファ層、122 耐圧保持層、123 p領域、124 n+領域、125 p+領域、126 酸化膜、127 上部ソース電極。

【特許請求の範囲】

【請求項1】

炭化珪素からなるベース基板および単結晶炭化珪素からなるSiC基板を準備する工程と、

前記ベース基板の主面上に接触するように前記SiC基板を載置して、積層基板を作製する工程と、

前記積層基板を、前記SiC基板よりも前記ベース基板の温度が高くなるように加熱することにより、前記ベース基板と前記SiC基板とを接合する工程と、

前記SiC基板が接合された前記ベース基板の、前記SiC基板とは反対側の主面上にエピタキシャル成長層を形成する工程とを備えた、炭化珪素基板の製造方法。

【請求項2】

前記ベース基板と前記SiC基板とを接合する工程では、前記ベース基板が前記ベース基板を構成する炭化珪素の昇華温度以上の温度域に加熱される、請求項1に記載の炭化珪素基板の製造方法。

【請求項3】

前記エピタキシャル成長層を形成する工程よりも後に、前記SiC基板の前記ベース基板とは反対側の主面を研磨する工程をさらに備えた、請求項1または2に記載の炭化珪素基板の製造方法。

【請求項4】

前記エピタキシャル成長層を形成する工程では、液相法により前記エピタキシャル成長層が形成される、請求項1〜3のいずれか1項に記載の炭化珪素基板の製造方法。

【請求項5】

前記エピタキシャル成長層を形成する工程では、化学気相成長法により前記エピタキシャル成長層が形成される、請求項1〜3のいずれか1項に記載の炭化珪素基板の製造方法。

【請求項6】

前記積層基板を作製する工程よりも前に、前記積層基板を作製する工程において互いに接触すべき前記ベース基板および前記SiC基板の主面を平坦化する工程をさらに備えた、請求項1〜5のいずれか1項に記載の炭化珪素基板の製造方法。

【請求項7】

前記積層基板を作製する工程は、前記積層基板を作製する工程よりも前に、前記積層基板を作製する工程において互いに接触すべき前記ベース基板および前記SiC基板の主面を研磨することなく実施される、請求項1〜5のいずれか1項に記載の炭化珪素基板の製造方法。

【請求項8】

前記積層基板を作製する工程では、前記SiC基板は、平面的に見て複数並べて載置される、請求項1〜7のいずれか1項に記載の炭化珪素基板の製造方法。

【請求項9】

前記積層基板を作製する工程では、前記SiC基板の前記ベース基板とは反対側の主面は、{0001}面に対するオフ角が50°以上65°以下となっている、請求項1〜8のいずれか1項に記載の炭化珪素基板の製造方法。

【請求項10】

前記積層基板を作製する工程では、前記SiC基板の前記ベース基板とは反対側の主面のオフ方位と<1−100>方向とのなす角は5°以下となっている、請求項9に記載の炭化珪素基板の製造方法。

【請求項11】

前記積層基板を作製する工程では、前記SiC基板の前記ベース基板とは反対側の主面の、<1−100>方向における{03−38}面に対するオフ角は−3°以上5°以下である、請求項10に記載の炭化珪素基板の製造方法。

【請求項12】

前記積層基板を作製する工程では、前記SiC基板の前記ベース基板とは反対側の主面のオフ方位と<11−20>方向とのなす角は5°以下となっている、請求項9に記載の炭化珪素基板の製造方法。

【請求項13】

前記ベース基板と前記SiC基板とを接合する工程では、大気雰囲気を減圧することにより得られた雰囲気中において前記積層基板が加熱される、請求項1〜12のいずれか1項に記載の炭化珪素基板の製造方法。

【請求項14】

前記ベース基板と前記SiC基板とを接合する工程では、10−1Paよりも高く104Paよりも低い圧力下において前記積層基板が加熱される、請求項1〜13のいずれか1項に記載の炭化珪素基板の製造方法。

【請求項15】

炭化珪素基板を準備する工程と、

前記炭化珪素基板上にエピタキシャル成長により半導体層を形成する工程と、

前記半導体層上に電極を形成する工程とを備え、

前記炭化珪素基板を準備する工程では、請求項1〜14のいずれか1項に記載の炭化珪素基板の製造方法により前記炭化珪素基板が製造される、半導体装置の製造方法。

【請求項16】

請求項1〜14のいずれか1項に記載の炭化珪素基板の製造方法により製造された、炭化珪素基板。

【請求項17】

請求項15に記載の半導体装置の製造方法により製造された、半導体装置。

【請求項1】

炭化珪素からなるベース基板および単結晶炭化珪素からなるSiC基板を準備する工程と、

前記ベース基板の主面上に接触するように前記SiC基板を載置して、積層基板を作製する工程と、

前記積層基板を、前記SiC基板よりも前記ベース基板の温度が高くなるように加熱することにより、前記ベース基板と前記SiC基板とを接合する工程と、

前記SiC基板が接合された前記ベース基板の、前記SiC基板とは反対側の主面上にエピタキシャル成長層を形成する工程とを備えた、炭化珪素基板の製造方法。

【請求項2】

前記ベース基板と前記SiC基板とを接合する工程では、前記ベース基板が前記ベース基板を構成する炭化珪素の昇華温度以上の温度域に加熱される、請求項1に記載の炭化珪素基板の製造方法。

【請求項3】

前記エピタキシャル成長層を形成する工程よりも後に、前記SiC基板の前記ベース基板とは反対側の主面を研磨する工程をさらに備えた、請求項1または2に記載の炭化珪素基板の製造方法。

【請求項4】

前記エピタキシャル成長層を形成する工程では、液相法により前記エピタキシャル成長層が形成される、請求項1〜3のいずれか1項に記載の炭化珪素基板の製造方法。

【請求項5】

前記エピタキシャル成長層を形成する工程では、化学気相成長法により前記エピタキシャル成長層が形成される、請求項1〜3のいずれか1項に記載の炭化珪素基板の製造方法。

【請求項6】

前記積層基板を作製する工程よりも前に、前記積層基板を作製する工程において互いに接触すべき前記ベース基板および前記SiC基板の主面を平坦化する工程をさらに備えた、請求項1〜5のいずれか1項に記載の炭化珪素基板の製造方法。

【請求項7】

前記積層基板を作製する工程は、前記積層基板を作製する工程よりも前に、前記積層基板を作製する工程において互いに接触すべき前記ベース基板および前記SiC基板の主面を研磨することなく実施される、請求項1〜5のいずれか1項に記載の炭化珪素基板の製造方法。

【請求項8】

前記積層基板を作製する工程では、前記SiC基板は、平面的に見て複数並べて載置される、請求項1〜7のいずれか1項に記載の炭化珪素基板の製造方法。

【請求項9】

前記積層基板を作製する工程では、前記SiC基板の前記ベース基板とは反対側の主面は、{0001}面に対するオフ角が50°以上65°以下となっている、請求項1〜8のいずれか1項に記載の炭化珪素基板の製造方法。

【請求項10】

前記積層基板を作製する工程では、前記SiC基板の前記ベース基板とは反対側の主面のオフ方位と<1−100>方向とのなす角は5°以下となっている、請求項9に記載の炭化珪素基板の製造方法。

【請求項11】

前記積層基板を作製する工程では、前記SiC基板の前記ベース基板とは反対側の主面の、<1−100>方向における{03−38}面に対するオフ角は−3°以上5°以下である、請求項10に記載の炭化珪素基板の製造方法。

【請求項12】

前記積層基板を作製する工程では、前記SiC基板の前記ベース基板とは反対側の主面のオフ方位と<11−20>方向とのなす角は5°以下となっている、請求項9に記載の炭化珪素基板の製造方法。

【請求項13】

前記ベース基板と前記SiC基板とを接合する工程では、大気雰囲気を減圧することにより得られた雰囲気中において前記積層基板が加熱される、請求項1〜12のいずれか1項に記載の炭化珪素基板の製造方法。

【請求項14】

前記ベース基板と前記SiC基板とを接合する工程では、10−1Paよりも高く104Paよりも低い圧力下において前記積層基板が加熱される、請求項1〜13のいずれか1項に記載の炭化珪素基板の製造方法。

【請求項15】

炭化珪素基板を準備する工程と、

前記炭化珪素基板上にエピタキシャル成長により半導体層を形成する工程と、

前記半導体層上に電極を形成する工程とを備え、

前記炭化珪素基板を準備する工程では、請求項1〜14のいずれか1項に記載の炭化珪素基板の製造方法により前記炭化珪素基板が製造される、半導体装置の製造方法。

【請求項16】

請求項1〜14のいずれか1項に記載の炭化珪素基板の製造方法により製造された、炭化珪素基板。

【請求項17】

請求項15に記載の半導体装置の製造方法により製造された、半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2011−243771(P2011−243771A)

【公開日】平成23年12月1日(2011.12.1)

【国際特許分類】

【出願番号】特願2010−115030(P2010−115030)

【出願日】平成22年5月19日(2010.5.19)

【出願人】(000002130)住友電気工業株式会社 (12,747)

【Fターム(参考)】

【公開日】平成23年12月1日(2011.12.1)

【国際特許分類】

【出願日】平成22年5月19日(2010.5.19)

【出願人】(000002130)住友電気工業株式会社 (12,747)

【Fターム(参考)】

[ Back to top ]