無線タグ及び無線タグを用いたシステム

【課題】 複数の独立な情報を記憶させておくことが可能な無線タグを提供する。

【解決手段】 磁波による交流信号の送受信を行なうアンテナ部と、前記アンテナ部にて受信した交流信号を基に書き込み若しくは読み出しが行なわれる複数の電気フューズから構成される複数のメモリブロックと、前記複数のメモリブロックのうち、どのメモリブロックに書き込み若しくは読み出しを行なうかを切り替える切り替え部とを有し、前記切り替えは、前記アンテナ部で受信した交流信号に基づいて行なわれることを特徴とする無線タグ。

【解決手段】 磁波による交流信号の送受信を行なうアンテナ部と、前記アンテナ部にて受信した交流信号を基に書き込み若しくは読み出しが行なわれる複数の電気フューズから構成される複数のメモリブロックと、前記複数のメモリブロックのうち、どのメモリブロックに書き込み若しくは読み出しを行なうかを切り替える切り替え部とを有し、前記切り替えは、前記アンテナ部で受信した交流信号に基づいて行なわれることを特徴とする無線タグ。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、無線により情報を送受信する無線タグ及び無線タグを用いたシステムに関するものである。

【背景技術】

【0002】

近年、工場の自動搬送システムや小売店での物品管理等にリーダ・ライタ装置との無線通信を行なう無線タグが使用されている。この無線タグの記憶素子には、EEPROM、FeRAM、マスクROMなどが用いられている。

【0003】

このような無線タグの中には、例えば、特許文献1に開示されているようなものがある。

【0004】

特許文献1には、無線タグの記憶素子に、フューズ型若しくはアンチフューズ型の電気フューズを記憶素子として用いた無線タグが開示されている。

【0005】

このような従来の電気フューズを記憶素子として用いた無線タグは、EEPROMやFeRAM等のメモリに比べて安価に製造可能なCMOSの製造プロセスを用いて製造することが可能であるため、安価に無線タグを製造することが可能であった。

【0006】

しかし、電気フューズを記憶素子として用いた無線タグは、電気フューズの持つ電気的特性を不可逆的に変化させ情報を記憶させるものであるため、無線タグには情報を一度しか書き込むことができず、また、書き込んだ情報を書き換えることは不可能であった。

【0007】

さらに、電気フューズを記憶素子として用いた無線タグは、無線タグ内に一つの記憶領域しか有していなかったため、一つの無線タグ内に複数の情報を記憶させておくことは不可能であり、一つの無線タグ内には一つの情報しか記憶させておくことができなかった。

【0008】

また、書き換え可能なEEPROMやFeRAM等を記憶素子として用いた書き換え可能な無線タグも存在するが、このようなEEPROMやFeRAM等の記憶素子は、電気フューズの製造プロセスであるCMOS製造プロセスに比べて複雑であるため、製造コストが高くなり、ひいては、単価の低減に対して社会からの要望が強い無線タグの単価が高くなってしまうという問題があった。

【特許文献1】特開平4-165583号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

本発明は、安価に製造可能であり且つ複数の独立な情報を記憶させておくことが可能な無線タグ及び無線タグを用いたシステムを提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明の一態様の無線タグは、磁波による交流信号の送受信を行なうアンテナ部と、前記アンテナ部にて受信した交流信号を基に書き込み若しくは読み出しが行なわれる複数の電気フューズから構成される複数のメモリブロックと、前記複数のメモリブロックのうち、どのメモリブロックに書き込み若しくは読み出しを行なうかを切り替える切り替え部とを有し、前記切り替えは、前記アンテナ部で受信した交流信号に基づいて行なわれることを特徴としている。

【0011】

また、本発明の一態様の無線タグを用いたシステムは、電磁波を用いて信号の送受信を行なうリーダ装置と無線タグを有する無線タグを用いたシステムにおいて、該無線タグは、電磁波による交流信号の送受信を行なうアンテナ部と、前記アンテナ部にて受信した交流信号を基に読み出しが行なわれる複数の電気フューズから構成される複数のメモリブロックと、前記複数のメモリブロックのうち、どのメモリブロックに読み出しを行なうかを切り替える切り替え部とを有し、前記切り替えが、前記リーダ装置から送信した電磁波により行なわれることを特徴としている。

【0012】

また、本発明の一態様の無線タグを用いたシステムは、電磁波を用いて信号の送受信を行なうライタ装置と無線タグを有する無線タグを用いたシステムにおいて、該無線タグは、電磁波による交流信号の送受信を行なうアンテナ部と、前記アンテナ部にて受信した交流信号を基に書き込みが行なわれる複数の電気フューズから構成される複数のメモリブロックと、前記複数のメモリブロックのうち、どのメモリブロックに書き込みを行なうかを切り替える切り替え部とを有し、前記切り替えが、前記ライタ装置から送信した電磁波により行なわれることを特徴としている。

【発明の効果】

【0013】

本発明によれば、安価に製造可能であり且つ複数の独立な情報を記憶させておくことが可能な無線タグ及びそれを用いたシステムを提供することができる。

【発明を実施するための最良の形態】

【0014】

以下、本発明の実施例について、図面を参照して説明する。

【実施例】

【0015】

本発明の実施例に係る無線タグ及び無線タグを用いたシステムを図1乃至図4を用いて説明する。図1は、本発明の実施例に係る無線タグを用いたシステムのシステム概略図である。

【0016】

本発明に用いられる「無線タグ」という言葉は、「RFID(radio frequency identification)」、「非接触ICタグ」、「非接触データキャリア」、「無線ICタグ」、「無線TAG」、「非接触IC」、「非接触ICラベル」、「非接触ICカード」等と、種々の名称で表現される場合もあるが、本発明においては、代表して「無線タグ」と表現し、前記のように表現されている名称のものも包含するものとする。

【0017】

本実施例に係る無線タグを用いたシステムは、無線タグ1及びリーダ・ライタ装置2から構成されている。無線タグ1とリーダ・ライタ装置2は、電磁波を用いて無線通信を行い、リーダ・ライタ装置2は無線タグ1に対して情報の書き込み及び読み出しを行なう。無線通信の交信信号(搬送波)として、例えば、13.56MHzの周波数の電磁波を用いる。

【0018】

本実施例に係るリーダ・ライタ装置2は、アンテナ、コントローラ等を有しており、無線タグ1に対して情報の書き込みを行なうライタ機能と、無線タグ1に対して読み出しを行なうリーダ機能とを備えているが、ライタ機能とリーダ機能とを必ずしも同一の装置内に備えていなくても良い。つまり、書き込みを行なう際にはライタ機能を備えているライタ装置により無線タグ1に対して書き込みを行い、読み出しを行なう際にはリーダ機能を備えているリーダ装置により無線タグ1に対して読み出しを行っても良い。

【0019】

無線タグ1は、アンテナ部3、それぞれ独立したメモリブロックA、メモリブロックB、メモリブロックC及びメモリブロックDという4つのメモリブロックを有するメモリ部4、アンテナ部3によって外部との間で送受信される交流信号に基づいて、メモリ部4の動作を制御する部分である周辺回路部5を有しており、メモリブロックAに情報A、メモリブロックBに情報B、メモリブロックCに情報C、メモリブロックDには情報Dというように、それぞれのメモリブロックに互いに独立な情報を記憶させておくことが可能である。

【0020】

各メモリブロックは、電気フューズ(e-fuse若しくはeFuseとも言う)を記憶素子としている。

【0021】

電気フューズは、高電圧または大電流を加え、その電気フューズ素子の電気的特性を不可逆的に変化させるものであり、高電圧または大電流を加え、金属またはポリシリコンからなる配線等を電気的に溶断しオープン状態に変化させるフューズ(fuse)型と、キャパシタを破壊しショートさせるアンチフューズ(anti fuse)型とがある。フューズ型及びアンチフューズ型ともに、フューズの破壊時と非破壊時の抵抗差を用いて、“0”若しくは“1”を記憶するものであるため、無線タグの製造後、無線タグの使用者によって、各メモリブロックに対して情報を一回限り書き込みを行なうことが可能である。

【0022】

リーダ・ライタ装置2から無線タグ1への情報の書き込みは、次のようにして行われる。まず、リーダ・ライタ装置2から無線タグ1へ書き込み信号Swを送信する。この書き込み信号Swには、メモリブロックA、メモリブロックB、メモリブロックC及びメモリブロックDのうち、どのメモリブロックに書き込むかというアドレス情報と、該メモリブロックに書き込む情報(データ)に関するデータ情報とが記されている。無線タグ1は、この書き込み信号Swを基に、書き込み動作を行い、指定されたメモリブロックに情報を書き込む。この後、無線タグ1からリーダ・ライタ装置2への応答信号として、例えば、書き込みを終了したという信号を送っても良い。

【0023】

各メモリブロックは、電気フューズから構成されているため、各メモリブロック内の情報は書き換えることはできないが、メモリブロックA、メモリブロックB、メモリブロックC、メモリブロックDと4つのメモリブロックを有しているため、4つの情報(4種類の情報)を一つの無線タグに記憶させておくことが可能である。

【0024】

リーダ・ライタ装置2から無線タグ1に記憶されている情報の読み出しは、次のようにして行われる。まず、リーダ・ライタ装置2から無線タグ1へ読み出し信号Srを送信する。この読み出し信号Srには、メモリブロックA、メモリブロックB、メモリブロックC及びメモリブロックDのうち、どのメモリブロックに記憶されている情報を読み出すかというアドレス情報が記されている。無線タグ1は、この読み出し信号Srを基に、読み出し動作を行い、指定されたメモリブロックに記録されている情報(読み出しデータ)を、無線タグ1からリーダ・ライタ装置2への応答信号として、リーダ・ライタ装置2へ送信する。

【0025】

このように、読み出し信号Srによって、無線タグ1内に記憶されている任意のメモリブロックの情報を読み出すことが可能である。また、各メモリブロックには、それぞれ、書き換え不可能な状態で情報が記憶される。従って、複数の書き換えられたくない情報を記憶させておくことが可能である。

【0026】

例えば、本実施例に係る無線タグを用いたシステムが製造工程管理に用いられた場合について説明する。ここで、製造工程管理が行われる製造物は、工程管理のために無線タグが付されており、製造工程1、2、3を経て製造される。各製造工程での加工条件を無線タグのメモリブロックA、B、Cに書き込み記憶させておき、製造工程毎に無線タグの情報を読み出し、その情報に基づき加工を行なう。

【0027】

まず、製造工程1においては、製造工程1の加工条件のみが必要であり、この加工条件を基に加工が施されるため、無線タグのメモリブロックAの情報を読み出し、その加工条件に基づいて加工を行なう。

【0028】

続いて、製造工程2においては、製造工程2の加工条件のみが必要であり、この加工条件を基に加工が施されるため、無線タグのメモリブロックBの情報を読み出し、その加工条件に基づいて加工を行なう。

【0029】

そして、製造工程3においては、製造工程3の加工条件のみが必要であり、この加工条件を基に加工が施されるため、無線タグのメモリブロックCの情報を読み出し、その加工条件に基づいて加工を行なう。

【0030】

このように、本実施例に係る無線タグを用いたシステムは、無線タグ1の記憶素子に複数の独立な情報を記憶させておくことが可能であり、且つリーダ・ライタ装置2からの読み出し信号Srにより、任意のメモリブロックの情報を読み出すことが可能であるため、本実施例に係る無線タグを用いたシステムでは、一つの無線タグによって複数の独立な情報を管理することが可能である。

【0031】

また、各メモリブロックを構成する記憶素子として、一回のみ電気的に書き込み可能である電気フューズを記憶素子として用いているため、各メモリブロックに保持された情報は改ざんされにくい。

【0032】

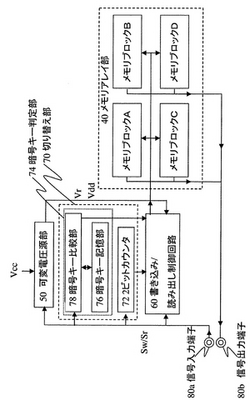

次に、本発明の実施例に係る無線タグ1の構造を図2乃至図4を用いて説明する。図2は、本発明の実施例に係る無線タグのブロック図である。

【0033】

図2に示すように、本実施例に係る無線タグ1は、リーダ・ライタ装置2との間で交流信号(搬送波)を送受信するためのアンテナ部3と、情報を記憶するためのメモリ部4と、メモリ部4とリーダ・ライタ装置2との間におけるデータ授受を制御するための周辺回路部5とを有している。

【0034】

アンテナ部3は、チップ外周部にループ状に形成されたインダクタンス配線6によって形成されている。このインダクタンス配線6は、リーダ・ライタ装置2から受信する交流信号から電磁誘導により誘導電流を生成する。アンテナ部3が受信する交流信号として、無線タグ1に情報が書き込まれる場合に受信する書き込み信号Swと、無線タグ1に記憶してある情報が読み出される場合に受信する読み出し信号Srの2種類がある。

【0035】

以降、この書き込み信号Sw及び読み出し信号Srは、周波数の変化や、暗号化、復号化等されるが、それらを代表して書き込み信号Swまたは読み出し信号Srと呼ぶ。

【0036】

周辺回路部5は、アンテナ部3によって外部との間で送受信される交流信号に基づいて、メモリ部4の動作を制御する部分であり、電源生成、レギュレート、搬送波抽出等を行なうRFアナログブロック7、データ変調・復調、データ処理等を行なうデジタルブロック8から構成されている。

【0037】

このRFアナログブロック7は、電源制御部9と送受信部10とを有している。

【0038】

電源制御部9は、アンテナ部3において受信した交流信号によってインダクタンス配線6に生じた誘導電流を源として、無線タグ1の動作電源電圧である内部電源電圧Vccを発生させるとともに、その電圧レベルを制御する機能を有する部分であり、整流器12と、BGR回路13と、シャントレギュレータ14と、シリーズレギュレータ15と、電源配線16と、パワーオンリセット回路17とを有する。

【0039】

整流器12は、アンテナ部3を構成するインダクタンス配線6に生じた誘導電流を直流電流に変換する。

【0040】

BGR回路13は、半導体のバイポーラアクションを利用して、バンドギャップに基づいて基準電圧Vprを高精度に生成する。例えば、基準電圧Vprは、約1.3V程度に設定される。

【0041】

シャントレギュレータ14は、整流器12によって直流電流に変換された誘導電流を源に、基準電圧Vprに基づいた内部電源電圧Vccを生成し、シリーズレギュレータ15により内部電源電圧Vccを安定化させ、安定した内部電源電圧Vccを電源配線16に供給する。

【0042】

この電源配線16は、メモリ部4及びデジタルブロック8等の無線タグ1の回路構成要素へ内部電源電圧Vccを伝達する。

【0043】

パワーオンリセット回路17は、電源配線16の内部電源電圧Vccが所定レベルに達しているかどうかを検出する。すなわち、内部電源電圧Vccが所定レベル以上である場合には、無線タグ1は回路動作が保証されるので、パワーオンリセット回路17は、通常の書き込みまたは読み出しの内部回路動作を許可する信号を生成する。

【0044】

送受信部10は、アンテナ部3を介して、メモリ部4に対する入出力データを、リーダ・ライタ装置2との間で送受信する機能を有する部分であり、通信コントロール回路18と、搬送波抽出回路19と、送信回路20と、発振器21とを有する。

【0045】

通信コントロール回路18は、アンテナ部3を介してリーダ・ライタ装置2との間での交流信号の送受信を制御する。具体的には、通信コントロール回路18は、交流信号の送受信タイミングの制御を主に行なう。例えば、通信コントロール回路18は、外部のリーダ・ライタ装置2からの交流信号受信期間には、アンテナ部3からの交流信号の送信を停止させる。また、通信コントロール回路18は、外部のリーダ・ライタ装置2への交流信号送信期間には、リーダ・ライタ装置2からデータ受信体制が整ったことの通知を受け、搬送波抽出回路19で該通知を抽出し、通信コントロール回路18に入力されてから、リーダ・ライタ装置2への送信を開始させる。

【0046】

搬送波抽出回路19は、アンテナ部3において受信した交流信号(搬送波)をデジタルブロック8にて復調できるように矩形波に整形する。この搬送波は、書き込み信号Sw若しくは読み出し信号Srを有している。なお、この書き込み信号Sw及び読み出し信号Srは、セキュリティ確保のために、暗号化された状態で搬送波に乗せられている。

【0047】

送信回路20は、外部のリーダ・ライタ装置2に送信する交流信号を、アンテナ部3に対して送出する。

【0048】

デジタルブロック8は、送受信部10から入力される搬送波を復調し、メモリ部4に対する動作指示情報を生成する機能と、メモリ部4から入力される信号を変調し、送受信部10に入力する機能を有し、同期調整回路22と、復調回路23と、データ処理回路24と、変調回路25とを有する。

【0049】

同期調整回路22は、PLL(phased locked loop)等で形成され、発振器21によって生成された基準周波数foの基準クロックを基に、搬送波と同期したクロック信号CKcを生成する。同期調整されたクロック信号CKcは、復調回路23及び変調回路25に入力される。

【0050】

復調回路23は、クロック信号CKcを用いて、搬送波に乗って送信されてくる、書き込み信号Sw若しくは読み出し信号Srを搬送波から抽出(デコード)する。復調回路23において抽出された書き込み信号Sw若しくは読み出し信号Srは、データ処理回路24に入力される。

【0051】

データ処理回路24は、暗号化された書き込み信号Sw若しくは読み出し信号Srの復号処理を行なう部分であり、読み出し動作実行時には、読み出し信号Srに対するメモリ部4からの応答信号である読み出しデータを暗号化して、変調回路25へ送出する。復号処理が施された書き込み信号Sw及び読み出し信号Srは、メモリ部4に入力される。

【0052】

変調回路25は、データ処理回路24から入力される読み出しデータを、送受信部10へ出力する搬送波に乗せるための処理(エンコード)を行なう。

【0053】

メモリ部4は、デジタルブロック8から入力される書き込み信号Sw若しくは読み出し信号Srを基に、メモリブロックA、メモリブロックB、メモリブロックC、メモリブロックDに、書き込み動作若しくは情報の読み出し動作が行なわれる。

【0054】

次に、図3を用いてメモリ部4について説明する。図3に示すように、メモリ部4はアンチフューズを一つのメモリセルとし、このメモリセルを複数個有するメモリブロックA、メモリブロックB、メモリブロックC、メモリブロックDからなるメモリアレイ部40と、メモリセルに対する書き込み動作を実行するためのブロー電圧VDD及び読み出し動作を実行するための読み出し電圧Vrを生成する可変電圧源部50と、メモリアレイ部40に対する読み出し動作及び書き込み動作を実行するための書き込み/読み出し制御部60と、搬送波に乗せられているアドレス情報を読み出し、メモリアレイ部40のメモリブロックA、メモリブロックB、メモリブロックC、メモリブロックDのうち、書き込み動作若しくは読み出し動作を行なう対象のメモリブロックをどのメモリブロックにするかを切り替える切り替え部70を有する。

【0055】

メモリアレイ部40は、メモリブロックA、メモリブロックB、メモリブロックC、メモリブロックDの4つのメモリブロックから構成されている。この各メモリブロックは、互いに独立しており、各メモリブロックに選択的に書き込み動作若しくは読み出し動作を行なうことが可能である。さらに、各メモリブロックは、図4に示すようなキャパシタを有するアンチフューズを一つのメモリセルとし、このメモリセルが複数個、例えば512個を一つのメモリブロックとして構成するようにして成っている。

【0056】

可変電圧源部50は、電源配線16を介して入力された電源電圧Vccから、メモリアレイ部40に対して書き込み動作を実行する際のブロー(書き込み)電圧VDD及び、メモリアレイ部40に対して読み出し動作を実行する際の読み出し電圧Vrを生成する。ブロー電圧Vdd及び読み出し電圧Vrは、一般に知られている昇圧回路等から生成される。

【0057】

また、可変電圧源部50は、デジタルブロック8から書き込み信号Sw若しくは読み出し信号Srが入力され、デジタルブロック8から書き込み信号Srが入力された時には、ブロー電圧Vddを生成し、読み出し信号Swが入力された時には、読み出し電圧Vrを生成する。このブロー電圧VDD及び読み出し電圧Vrは、書き込み/読み出し制御部60に供給される。

【0058】

切り替え部70は、デジタルブロック8から入力される書き込み信号Sw若しくは読み出し信号Srに記されている、どのメモリブロックに書き込み若しくは読み出しを行なうかというアドレス情報に基づき、そのメモリブロックに対して信号が入出力可能となるように切り替えを行なう部分であり、2ビットカウンタ72と暗号キー判定部74とを有している。

【0059】

2ビットカウンタ72は、入力された書き込み信号Sw若しくは読み出し信号Sr内に含まれるアドレス情報を抽出する。このアドレス情報は、書き込み信号Sw若しくは読み出し信号Sr内のある部分、例えば先頭に、乗せられている。アドレス情報は、メモリブロックの数に応じた情報量を有していればよく、本実施例のようにメモリアレイ部40に4つのメモリブロックが設けられている場合には、アドレス情報は2ビットの情報量を有している。2ビットカウンタ72は、この書き込み信号Sw若しくは読み出し信号Srを計数し、2ビットのアドレス情報を抽出する。そして、この2ビットのアドレス情報は、書き込み/読み出し制御部60に入力される。

【0060】

暗号キー判定部74は、メモリブロックに対しての読み出し若しくは書き込みについて、可否を判定する部分であり、暗号キー記憶部76と、暗号キー比較部78とを有している。

【0061】

暗号キー記憶部76には、暗号キーが記憶されている。この暗号キーは、無線タグを使用することのできる人によって予め設定されており、この暗号キーを知っている使用者以外は、無線タグに書き込みや読み出しをすることができないようにするためのものである。

【0062】

暗号キー比較部78は、暗号キー記憶部76に記憶されている暗号キーと、リーダ・ライタ装置2から送信されてくる暗号キー情報とを比較し、この暗号キーと暗号キー情報とが一致することにより、書き込み若しくは読み出しのどちらか一方、あるいは書き込み及び読み出しの両方を可能とすることができる。暗号キーと暗号キー情報が一致したときには、読み出し若しくは書き込みのどちらか一方、あるいは書き込み及び読み出しの両方を可能にする書き込み読み出し可能信号を書き込み/読み出し制御回路60に入力し、一致しなかったときには、読み出し若しくは書き込みのどちらか一方、あるいは書き込み及び読み出しの両方を不可能にする書き込み読み出し不可能信号を、書き込み/読み出し制御回路60に入力する。

【0063】

なお、この暗号キー情報は、無線タグを使用する人によって、リーダ・ライタ装置2に入力され、この暗号キー情報が、電磁波に乗せられて、無線タグ1に入力される。

【0064】

ここで本実施例における暗号キー比較部78は、暗号キーと、暗号キー情報とが、一致したときに、読み出し若しくは書き込みを可能にするというように構成されているが、必ずしも暗号キーと、暗号キー情報とが、一致したときにのみ、読み出し若しくは書き込みを可能にするという構成に限らず、例えば、暗号キー情報と暗号キーとが一対一対応が取れているときに、読み出し若しくは書き込みを可能にするという構成等、種々の構成が考えられる。

【0065】

書き込み/読み出し制御部60は、デジタルブロック8から信号入力端子80aを介して書き込み信号Sw若しくは読み出し信号Srが入力され、書き込み信号Swが入力された時には、書き込み制御信号を生成し、読み出し信号Srが入力された時には、読み出し制御信号を生成する。

【0066】

書き込み制御信号は、メモリブロック内の各メモリセルに入力され、この信号を基に、メモリセルに対して書き込み動作が行なわれ、メモリブロックに情報が書き込まれる。また、読み出し制御信号は、メモリブロック内の各メモリセルに入力され、この信号を基に、メモリセルに対して読み出し動作が行なわれ、メモリブロックに記憶してある情報が読み出される。

【0067】

書き込み/読み出し制御部60は、暗号キー判定部74から、書き込み読み出し可能信号が入力されたときには、2ビットのアドレス情報を基にして、読み出し若しくは書き込みを行なう対象のメモリブロックに、書き込み制御信号若しくは読み出し制御信号を入力し、その対象のメモリブロックに対して書き込み動作若しくは読み出し動作を行なう。なお、書き込み/読み出し制御部60は、暗号キー判定部74から、書き込み読み出し不可能信号が入力されたときには、書き込み若しくは読み出し動作を行なわない。

【0068】

例えば、書き込み読み出し可能信号が入力され、読み出し信号SrにメモリブロックBに対応するアドレス情報が記してあれば、書き込み/読み出し制御部60は、書き込み/読み出し制御部60において生成された読み出し制御信号をメモリブロックBに入力し、メモリブロックBの情報を読み出す。また、書き込み信号SwにメモリブロックDに対応するアドレス情報が記してあれば、書き込み読み出し可能信号が入力され、書き込み/読み出し制御部60は、書き込み/読み出し制御部60において生成された書き込み制御信号をメモリブロックDに入力し、メモリブロックDに情報を書き込む。

【0069】

ここで、各メモリブロックを構成しているメモリセルの構造及びメモリセルに対する書き込み動作及び読み出し動作について、図4を参照して説明する。

【0070】

図4に示すアンチフューズは、記憶素子となるキャパシタ101、第1のトランジスタ102及び第2のトランジスタ103を有し、キャパシタ101が導通しているか否かにより、情報を記憶するものである。

【0071】

キャパシタ101は、電源入力端子Din、第1のトランジスタ102と第2のトランジスタ103に接続されている。電源入力端子Dinからは、ブロー電圧Vdd、0V(GND電位)及び読み出し電圧Vrの少なくとも3種類の電圧が入力される。第1のトランジスタ102の他方は、出力端子Doutとなっている。第2のトランジスタ103の他方は、GNDに接地されている。第1のトランジスタ102のゲート電極にはφ1、第2のトランジスタ103のゲート電極にはφ2という書き込み制御信号及び読み出し制御信号が、書き込み/読み出し制御部60から入力され、ゲート電極の電圧を変化させる。

【0072】

情報の書き込みは次のように行なう。第1のトランジスタ102をOFFにしたままの状態で第2のトランジスタ103をONする。第2のトランジスタ103はGNDに接地されているため、第2のトランジスタ103をONすることによりキャパシタ101の陰極の電位は0Vとなる。電源入力端子Dinに入力する電圧をキャパシタ101の絶縁耐圧(ブロー電圧Vdd)以上の高電圧に設定することにより、キャパシタ101は絶縁破壊を起こし、情報の記憶状態になる。例えばキャパシタ101が絶縁破壊された状態を情報“1”が記憶され、絶縁破壊されていない状態を情報“0”が記憶されていると定義する。この時電源入力端子Dinから供給された電流は、破壊されたキャパシタ101、第2のトランジスタ103を通って、GNDへと流れる。

【0073】

情報の読み出しは次のように行なう。まず電源入力端子Dinに入力する電圧を読み出し電圧Vrに設定する。この読み出し電圧Vrは、キャパシタ101に印加してもキャパシタ101が絶縁破壊を生じない程度に低い電圧である。次に第2のトランジスタ103をOFFにし、第1のトランジスタ102をONにする。キャパシタ101に情報“1”が記憶されている場合には、キャパシタ101は電極間が導通しているため、電源入力端子Dinから入力された電流は、キャパシタ101と第1のトランジスタ102を通過して、出力端子Doutを介して外部に電流が出力される。

【0074】

一方で、キャパシタ101に情報“0”が記憶されている場合は、キャパシタ101は絶縁破壊されておらず、互いの電極は絶縁されたままであるため、出力端子Doutを介して外部へ電流は出力されない。従って、出力端子Doutを流れる電流の有無により情報“1”または“0”が記憶されたか否かを判別することができる。

【0075】

以上のように、本実施例に係る無線タグ1は構成されている。

【0076】

本実施例に係る無線タグ1によれば、一つの無線タグ内に複数のメモリブロックがあり、且つ書き込み信号Sw内のアドレス情報に基づいて切り替え部70において切り替えを行ない、各メモリブロックに選択的に情報を書き込むことが可能である。そのため、一つの無線タグに複数の情報を記憶させておくことが可能である。さらに各メモリブロックに記憶された情報を読み出し信号Srに応じて、選択的に読み出すことが可能である。

【0077】

また、CMOS製造プロセスにより製造することが可能であるフューズ型若しくはアンチフューズ型の電気フューズを記憶素子として用いているため、安価に製造することが可能である。

【0078】

次に、無線タグ1が書き込み信号Swを受信し、情報を記憶する場合の無線タグ1の書き込み動作について説明する。

【0079】

まず始めに、アンテナ部3は、リーダ・ライタ装置2から発信された交流信号(書き込み信号Sw)を受信し、この交流信号から誘導電流を生成する。

【0080】

次に、電源制御部9において、誘導電流から安定した内部電源電圧Vccを生成し、無線タグ1内のメモリ部4、周辺回路部5等の各内部回路群に供給する。

【0081】

アンテナ部3において受信した交流信号は、搬送波抽出回路19に入力され、交流信号が矩形波に整形され、デジタルブロック8に入力される。

【0082】

デジタルブロック8内で、搬送波に乗せられて入力された書き込み信号Swに、変調、復号処理等が施され、書き込み信号Swがメモリ部4に入力される。

【0083】

メモリ部4に入力された書き込み信号Swは、切り替え部70に入力され、切り替え部70において、書き込み情報Sw内のアドレス情報を基に、メモリアレイ部40内のどのメモリブロックに情報の書き込みが行なわれるかというアドレス情報が抽出される。

【0084】

また、書き込み/読み出し制御部60において、メモリアレイ部40に書き込み動作を行なう書き込み制御信号が生成され、アドレス情報に基づき選択されたメモリブロックに、書き込み制御信号が供給され、選択されたメモリブロックに書き込み動作が行なわれる。

【0085】

このようにして、外部のリーダ・ライタ装置2から入力された交流信号により、無線タグ1のメモリブロックに情報が書き込まれる。

【0086】

次に、無線タグ1が読み出し信号Srを受信し、情報を記憶する場合の無線タグ1の読み出し動作について説明する。

【0087】

まず始めに、アンテナ部3は、リーダ・ライタ装置2から発信された交流信号(読み出し信号Sr)を受信し、この交流信号から誘導電流を生成する。

【0088】

次に、電源制御部9において、誘導電流から安定した内部電源電圧Vccを発生させ、無線タグ1内のメモリ部4、周辺回路部5等の各内部回路群に供給する。

【0089】

アンテナ部3において受信した交流信号は、搬送波抽出回路19に入力され、交流信号が矩形波に整形され、デジタルブロック8に入力される。

【0090】

デジタルブロック8内で、搬送波に乗せられて入力された読み出し信号Srに、変調、復号処理等が施され、読み出し信号Srがメモリ部4に入力される。

【0091】

メモリ部4に入力された読み出し信号Srは、切り替え部70に入力され、切り替え部70においてメモリアレイ部40内のどのメモリブロックの情報を読み出すかが読み出し信号Srのアドレス情報が抽出される。

【0092】

書き込み/読み出し制御部60において、メモリアレイ部40に読み出し動作を行なう読み出し制御信号が生成される。

【0093】

続いて、アドレス情報に基づき選択されたメモリブロックに、読み出し制御信号が供給され、選択されたメモリブロックに読み出し動作が行なわれる。

【0094】

次に、選択されたメモリブロックに入力される読み出し制御信号に対する出力信号として、読み出しデータが信号出力端子80bを介して、デジタルブロック8に入力される。

【0095】

この読み出しデータに、暗号化、変調化等の処理がなされ、通信コントロール回路18、送信回路20を介して、整流器12、アンテナ部2から読み出し信号Srに対する応答信号として読み出しデータが、リーダ・ライタ装置2に送信される。

【0096】

このようにして、外部のリーダ・ライタ装置2から入力された交流信号により、無線タグ1に記録された情報が読み出される。

【0097】

以上のように、リーダ・ライタ装置2からの書き込み信号Swにより、指定したメモリブロックに情報を書き込むことが可能である。また、読み出し信号Srにより、任意のメモリブロックの情報を読み出すことが可能である。そのため、一つの無線タグ1に対して、複数の独立した情報を記憶させておくことが可能であり、リード・ライト装置2からの読み出し信号Srによって、任意のメモリブロックから情報を読み出すことが可能である。

【0098】

また、各メモリブロックは、書き換え不可能な電気フューズを記憶素子としているため、各メモリブロックに一度書き込まれた情報が改ざんされるという危険を防止することが可能である。

【0099】

本実施例に係る無線タグは、複数種のデータを一つの無線タグ内に記憶することが可能であり、無線タグのメモリ部をCMOSプロセスで製造可能であるため、EEPROMを用いた無線タグよりも安価に製造することが可能である。

【0100】

(実施例の変形例)

本実施例の変形例に係る無線タグ100を図5に示す。実施例に示した無線タグ1は、リーダ・ライタ装置2から送信される交流信号からアンテナコイルにおいて誘導電流を生成し、この誘導電流を無線タグの電源としていたが、本実施例の変形例に係る無線タグ100は、無線タグ100の外部から、リード線などの配線により無線タグ100に対して電源電圧Vccが供給される。実施例と同一部分には同一符号を付して、その説明を省略する。

【0101】

本実施例の変形例によれば、電源供給手段を有するもの(例えば、携帯情報端末)の内部に無線タグ100を付す時に特に有効となる。

【0102】

外部から交流信号により電源を供給する無線タグ1は、配線を介して電源を供給する無線タグ100に比べて、信号を送受信する交流信号として、長時間若しくは高い振幅の電磁波を用いる必要がある。この長時間若しくは高い振幅の交流信号は、ノイズを生み出しやすい。このように、無線タグ100が付されたものに、電源供給源が存在する場合には、配線により供給することも可能である。

【図面の簡単な説明】

【0103】

【図1】本発明の実施例に係る無線タグを用いたシステムの概略図。

【図2】本発明の実施例に係る無線タグのブロック図。

【図3】本発明の実施例に係る無線タグのメモリ部の概略図。

【図4】本発明の実施例に係る無線タグのメモリセルの図。

【図5】本発明の実施例の変形例に係る無線タグのブロック図。

【符号の説明】

【0104】

1、100 無線タグ

2 リーダ・ライタ装置

3 アンテナ部

4 メモリ部

5 周辺回路部

6 インダクタンス配線

7 RFアナログブロック

8 デジタルブロック

9 電源制御部

10 送受信部

12 整流器

13 BGR回路

14 シャントレギュレータ

15 シリーズレギュレータ

16 電源配線

17 パワーオンリセット回路

18 通信コントロール回路

19 搬送波抽出回路

20 送信回路

21 発振器

22 同期調整回路(PLL)

23 復調回路

24 データ処理回路

25 変調回路

40 メモリアレイ部

50 可変電圧源部

60 書き込み/読み出し制御部

70 切り替え部

72 2ビットカウンタ

74 暗号キー判定部

76 暗号キー記憶部

78 暗号キー比較部

80a 信号入力端子

80b 信号出力端子

101 可変電圧源

102 キャパシタ(記憶素子)

103 第1のトランジスタ

104 第2のトランジスタ

【技術分野】

【0001】

本発明は、無線により情報を送受信する無線タグ及び無線タグを用いたシステムに関するものである。

【背景技術】

【0002】

近年、工場の自動搬送システムや小売店での物品管理等にリーダ・ライタ装置との無線通信を行なう無線タグが使用されている。この無線タグの記憶素子には、EEPROM、FeRAM、マスクROMなどが用いられている。

【0003】

このような無線タグの中には、例えば、特許文献1に開示されているようなものがある。

【0004】

特許文献1には、無線タグの記憶素子に、フューズ型若しくはアンチフューズ型の電気フューズを記憶素子として用いた無線タグが開示されている。

【0005】

このような従来の電気フューズを記憶素子として用いた無線タグは、EEPROMやFeRAM等のメモリに比べて安価に製造可能なCMOSの製造プロセスを用いて製造することが可能であるため、安価に無線タグを製造することが可能であった。

【0006】

しかし、電気フューズを記憶素子として用いた無線タグは、電気フューズの持つ電気的特性を不可逆的に変化させ情報を記憶させるものであるため、無線タグには情報を一度しか書き込むことができず、また、書き込んだ情報を書き換えることは不可能であった。

【0007】

さらに、電気フューズを記憶素子として用いた無線タグは、無線タグ内に一つの記憶領域しか有していなかったため、一つの無線タグ内に複数の情報を記憶させておくことは不可能であり、一つの無線タグ内には一つの情報しか記憶させておくことができなかった。

【0008】

また、書き換え可能なEEPROMやFeRAM等を記憶素子として用いた書き換え可能な無線タグも存在するが、このようなEEPROMやFeRAM等の記憶素子は、電気フューズの製造プロセスであるCMOS製造プロセスに比べて複雑であるため、製造コストが高くなり、ひいては、単価の低減に対して社会からの要望が強い無線タグの単価が高くなってしまうという問題があった。

【特許文献1】特開平4-165583号公報

【発明の開示】

【発明が解決しようとする課題】

【0009】

本発明は、安価に製造可能であり且つ複数の独立な情報を記憶させておくことが可能な無線タグ及び無線タグを用いたシステムを提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明の一態様の無線タグは、磁波による交流信号の送受信を行なうアンテナ部と、前記アンテナ部にて受信した交流信号を基に書き込み若しくは読み出しが行なわれる複数の電気フューズから構成される複数のメモリブロックと、前記複数のメモリブロックのうち、どのメモリブロックに書き込み若しくは読み出しを行なうかを切り替える切り替え部とを有し、前記切り替えは、前記アンテナ部で受信した交流信号に基づいて行なわれることを特徴としている。

【0011】

また、本発明の一態様の無線タグを用いたシステムは、電磁波を用いて信号の送受信を行なうリーダ装置と無線タグを有する無線タグを用いたシステムにおいて、該無線タグは、電磁波による交流信号の送受信を行なうアンテナ部と、前記アンテナ部にて受信した交流信号を基に読み出しが行なわれる複数の電気フューズから構成される複数のメモリブロックと、前記複数のメモリブロックのうち、どのメモリブロックに読み出しを行なうかを切り替える切り替え部とを有し、前記切り替えが、前記リーダ装置から送信した電磁波により行なわれることを特徴としている。

【0012】

また、本発明の一態様の無線タグを用いたシステムは、電磁波を用いて信号の送受信を行なうライタ装置と無線タグを有する無線タグを用いたシステムにおいて、該無線タグは、電磁波による交流信号の送受信を行なうアンテナ部と、前記アンテナ部にて受信した交流信号を基に書き込みが行なわれる複数の電気フューズから構成される複数のメモリブロックと、前記複数のメモリブロックのうち、どのメモリブロックに書き込みを行なうかを切り替える切り替え部とを有し、前記切り替えが、前記ライタ装置から送信した電磁波により行なわれることを特徴としている。

【発明の効果】

【0013】

本発明によれば、安価に製造可能であり且つ複数の独立な情報を記憶させておくことが可能な無線タグ及びそれを用いたシステムを提供することができる。

【発明を実施するための最良の形態】

【0014】

以下、本発明の実施例について、図面を参照して説明する。

【実施例】

【0015】

本発明の実施例に係る無線タグ及び無線タグを用いたシステムを図1乃至図4を用いて説明する。図1は、本発明の実施例に係る無線タグを用いたシステムのシステム概略図である。

【0016】

本発明に用いられる「無線タグ」という言葉は、「RFID(radio frequency identification)」、「非接触ICタグ」、「非接触データキャリア」、「無線ICタグ」、「無線TAG」、「非接触IC」、「非接触ICラベル」、「非接触ICカード」等と、種々の名称で表現される場合もあるが、本発明においては、代表して「無線タグ」と表現し、前記のように表現されている名称のものも包含するものとする。

【0017】

本実施例に係る無線タグを用いたシステムは、無線タグ1及びリーダ・ライタ装置2から構成されている。無線タグ1とリーダ・ライタ装置2は、電磁波を用いて無線通信を行い、リーダ・ライタ装置2は無線タグ1に対して情報の書き込み及び読み出しを行なう。無線通信の交信信号(搬送波)として、例えば、13.56MHzの周波数の電磁波を用いる。

【0018】

本実施例に係るリーダ・ライタ装置2は、アンテナ、コントローラ等を有しており、無線タグ1に対して情報の書き込みを行なうライタ機能と、無線タグ1に対して読み出しを行なうリーダ機能とを備えているが、ライタ機能とリーダ機能とを必ずしも同一の装置内に備えていなくても良い。つまり、書き込みを行なう際にはライタ機能を備えているライタ装置により無線タグ1に対して書き込みを行い、読み出しを行なう際にはリーダ機能を備えているリーダ装置により無線タグ1に対して読み出しを行っても良い。

【0019】

無線タグ1は、アンテナ部3、それぞれ独立したメモリブロックA、メモリブロックB、メモリブロックC及びメモリブロックDという4つのメモリブロックを有するメモリ部4、アンテナ部3によって外部との間で送受信される交流信号に基づいて、メモリ部4の動作を制御する部分である周辺回路部5を有しており、メモリブロックAに情報A、メモリブロックBに情報B、メモリブロックCに情報C、メモリブロックDには情報Dというように、それぞれのメモリブロックに互いに独立な情報を記憶させておくことが可能である。

【0020】

各メモリブロックは、電気フューズ(e-fuse若しくはeFuseとも言う)を記憶素子としている。

【0021】

電気フューズは、高電圧または大電流を加え、その電気フューズ素子の電気的特性を不可逆的に変化させるものであり、高電圧または大電流を加え、金属またはポリシリコンからなる配線等を電気的に溶断しオープン状態に変化させるフューズ(fuse)型と、キャパシタを破壊しショートさせるアンチフューズ(anti fuse)型とがある。フューズ型及びアンチフューズ型ともに、フューズの破壊時と非破壊時の抵抗差を用いて、“0”若しくは“1”を記憶するものであるため、無線タグの製造後、無線タグの使用者によって、各メモリブロックに対して情報を一回限り書き込みを行なうことが可能である。

【0022】

リーダ・ライタ装置2から無線タグ1への情報の書き込みは、次のようにして行われる。まず、リーダ・ライタ装置2から無線タグ1へ書き込み信号Swを送信する。この書き込み信号Swには、メモリブロックA、メモリブロックB、メモリブロックC及びメモリブロックDのうち、どのメモリブロックに書き込むかというアドレス情報と、該メモリブロックに書き込む情報(データ)に関するデータ情報とが記されている。無線タグ1は、この書き込み信号Swを基に、書き込み動作を行い、指定されたメモリブロックに情報を書き込む。この後、無線タグ1からリーダ・ライタ装置2への応答信号として、例えば、書き込みを終了したという信号を送っても良い。

【0023】

各メモリブロックは、電気フューズから構成されているため、各メモリブロック内の情報は書き換えることはできないが、メモリブロックA、メモリブロックB、メモリブロックC、メモリブロックDと4つのメモリブロックを有しているため、4つの情報(4種類の情報)を一つの無線タグに記憶させておくことが可能である。

【0024】

リーダ・ライタ装置2から無線タグ1に記憶されている情報の読み出しは、次のようにして行われる。まず、リーダ・ライタ装置2から無線タグ1へ読み出し信号Srを送信する。この読み出し信号Srには、メモリブロックA、メモリブロックB、メモリブロックC及びメモリブロックDのうち、どのメモリブロックに記憶されている情報を読み出すかというアドレス情報が記されている。無線タグ1は、この読み出し信号Srを基に、読み出し動作を行い、指定されたメモリブロックに記録されている情報(読み出しデータ)を、無線タグ1からリーダ・ライタ装置2への応答信号として、リーダ・ライタ装置2へ送信する。

【0025】

このように、読み出し信号Srによって、無線タグ1内に記憶されている任意のメモリブロックの情報を読み出すことが可能である。また、各メモリブロックには、それぞれ、書き換え不可能な状態で情報が記憶される。従って、複数の書き換えられたくない情報を記憶させておくことが可能である。

【0026】

例えば、本実施例に係る無線タグを用いたシステムが製造工程管理に用いられた場合について説明する。ここで、製造工程管理が行われる製造物は、工程管理のために無線タグが付されており、製造工程1、2、3を経て製造される。各製造工程での加工条件を無線タグのメモリブロックA、B、Cに書き込み記憶させておき、製造工程毎に無線タグの情報を読み出し、その情報に基づき加工を行なう。

【0027】

まず、製造工程1においては、製造工程1の加工条件のみが必要であり、この加工条件を基に加工が施されるため、無線タグのメモリブロックAの情報を読み出し、その加工条件に基づいて加工を行なう。

【0028】

続いて、製造工程2においては、製造工程2の加工条件のみが必要であり、この加工条件を基に加工が施されるため、無線タグのメモリブロックBの情報を読み出し、その加工条件に基づいて加工を行なう。

【0029】

そして、製造工程3においては、製造工程3の加工条件のみが必要であり、この加工条件を基に加工が施されるため、無線タグのメモリブロックCの情報を読み出し、その加工条件に基づいて加工を行なう。

【0030】

このように、本実施例に係る無線タグを用いたシステムは、無線タグ1の記憶素子に複数の独立な情報を記憶させておくことが可能であり、且つリーダ・ライタ装置2からの読み出し信号Srにより、任意のメモリブロックの情報を読み出すことが可能であるため、本実施例に係る無線タグを用いたシステムでは、一つの無線タグによって複数の独立な情報を管理することが可能である。

【0031】

また、各メモリブロックを構成する記憶素子として、一回のみ電気的に書き込み可能である電気フューズを記憶素子として用いているため、各メモリブロックに保持された情報は改ざんされにくい。

【0032】

次に、本発明の実施例に係る無線タグ1の構造を図2乃至図4を用いて説明する。図2は、本発明の実施例に係る無線タグのブロック図である。

【0033】

図2に示すように、本実施例に係る無線タグ1は、リーダ・ライタ装置2との間で交流信号(搬送波)を送受信するためのアンテナ部3と、情報を記憶するためのメモリ部4と、メモリ部4とリーダ・ライタ装置2との間におけるデータ授受を制御するための周辺回路部5とを有している。

【0034】

アンテナ部3は、チップ外周部にループ状に形成されたインダクタンス配線6によって形成されている。このインダクタンス配線6は、リーダ・ライタ装置2から受信する交流信号から電磁誘導により誘導電流を生成する。アンテナ部3が受信する交流信号として、無線タグ1に情報が書き込まれる場合に受信する書き込み信号Swと、無線タグ1に記憶してある情報が読み出される場合に受信する読み出し信号Srの2種類がある。

【0035】

以降、この書き込み信号Sw及び読み出し信号Srは、周波数の変化や、暗号化、復号化等されるが、それらを代表して書き込み信号Swまたは読み出し信号Srと呼ぶ。

【0036】

周辺回路部5は、アンテナ部3によって外部との間で送受信される交流信号に基づいて、メモリ部4の動作を制御する部分であり、電源生成、レギュレート、搬送波抽出等を行なうRFアナログブロック7、データ変調・復調、データ処理等を行なうデジタルブロック8から構成されている。

【0037】

このRFアナログブロック7は、電源制御部9と送受信部10とを有している。

【0038】

電源制御部9は、アンテナ部3において受信した交流信号によってインダクタンス配線6に生じた誘導電流を源として、無線タグ1の動作電源電圧である内部電源電圧Vccを発生させるとともに、その電圧レベルを制御する機能を有する部分であり、整流器12と、BGR回路13と、シャントレギュレータ14と、シリーズレギュレータ15と、電源配線16と、パワーオンリセット回路17とを有する。

【0039】

整流器12は、アンテナ部3を構成するインダクタンス配線6に生じた誘導電流を直流電流に変換する。

【0040】

BGR回路13は、半導体のバイポーラアクションを利用して、バンドギャップに基づいて基準電圧Vprを高精度に生成する。例えば、基準電圧Vprは、約1.3V程度に設定される。

【0041】

シャントレギュレータ14は、整流器12によって直流電流に変換された誘導電流を源に、基準電圧Vprに基づいた内部電源電圧Vccを生成し、シリーズレギュレータ15により内部電源電圧Vccを安定化させ、安定した内部電源電圧Vccを電源配線16に供給する。

【0042】

この電源配線16は、メモリ部4及びデジタルブロック8等の無線タグ1の回路構成要素へ内部電源電圧Vccを伝達する。

【0043】

パワーオンリセット回路17は、電源配線16の内部電源電圧Vccが所定レベルに達しているかどうかを検出する。すなわち、内部電源電圧Vccが所定レベル以上である場合には、無線タグ1は回路動作が保証されるので、パワーオンリセット回路17は、通常の書き込みまたは読み出しの内部回路動作を許可する信号を生成する。

【0044】

送受信部10は、アンテナ部3を介して、メモリ部4に対する入出力データを、リーダ・ライタ装置2との間で送受信する機能を有する部分であり、通信コントロール回路18と、搬送波抽出回路19と、送信回路20と、発振器21とを有する。

【0045】

通信コントロール回路18は、アンテナ部3を介してリーダ・ライタ装置2との間での交流信号の送受信を制御する。具体的には、通信コントロール回路18は、交流信号の送受信タイミングの制御を主に行なう。例えば、通信コントロール回路18は、外部のリーダ・ライタ装置2からの交流信号受信期間には、アンテナ部3からの交流信号の送信を停止させる。また、通信コントロール回路18は、外部のリーダ・ライタ装置2への交流信号送信期間には、リーダ・ライタ装置2からデータ受信体制が整ったことの通知を受け、搬送波抽出回路19で該通知を抽出し、通信コントロール回路18に入力されてから、リーダ・ライタ装置2への送信を開始させる。

【0046】

搬送波抽出回路19は、アンテナ部3において受信した交流信号(搬送波)をデジタルブロック8にて復調できるように矩形波に整形する。この搬送波は、書き込み信号Sw若しくは読み出し信号Srを有している。なお、この書き込み信号Sw及び読み出し信号Srは、セキュリティ確保のために、暗号化された状態で搬送波に乗せられている。

【0047】

送信回路20は、外部のリーダ・ライタ装置2に送信する交流信号を、アンテナ部3に対して送出する。

【0048】

デジタルブロック8は、送受信部10から入力される搬送波を復調し、メモリ部4に対する動作指示情報を生成する機能と、メモリ部4から入力される信号を変調し、送受信部10に入力する機能を有し、同期調整回路22と、復調回路23と、データ処理回路24と、変調回路25とを有する。

【0049】

同期調整回路22は、PLL(phased locked loop)等で形成され、発振器21によって生成された基準周波数foの基準クロックを基に、搬送波と同期したクロック信号CKcを生成する。同期調整されたクロック信号CKcは、復調回路23及び変調回路25に入力される。

【0050】

復調回路23は、クロック信号CKcを用いて、搬送波に乗って送信されてくる、書き込み信号Sw若しくは読み出し信号Srを搬送波から抽出(デコード)する。復調回路23において抽出された書き込み信号Sw若しくは読み出し信号Srは、データ処理回路24に入力される。

【0051】

データ処理回路24は、暗号化された書き込み信号Sw若しくは読み出し信号Srの復号処理を行なう部分であり、読み出し動作実行時には、読み出し信号Srに対するメモリ部4からの応答信号である読み出しデータを暗号化して、変調回路25へ送出する。復号処理が施された書き込み信号Sw及び読み出し信号Srは、メモリ部4に入力される。

【0052】

変調回路25は、データ処理回路24から入力される読み出しデータを、送受信部10へ出力する搬送波に乗せるための処理(エンコード)を行なう。

【0053】

メモリ部4は、デジタルブロック8から入力される書き込み信号Sw若しくは読み出し信号Srを基に、メモリブロックA、メモリブロックB、メモリブロックC、メモリブロックDに、書き込み動作若しくは情報の読み出し動作が行なわれる。

【0054】

次に、図3を用いてメモリ部4について説明する。図3に示すように、メモリ部4はアンチフューズを一つのメモリセルとし、このメモリセルを複数個有するメモリブロックA、メモリブロックB、メモリブロックC、メモリブロックDからなるメモリアレイ部40と、メモリセルに対する書き込み動作を実行するためのブロー電圧VDD及び読み出し動作を実行するための読み出し電圧Vrを生成する可変電圧源部50と、メモリアレイ部40に対する読み出し動作及び書き込み動作を実行するための書き込み/読み出し制御部60と、搬送波に乗せられているアドレス情報を読み出し、メモリアレイ部40のメモリブロックA、メモリブロックB、メモリブロックC、メモリブロックDのうち、書き込み動作若しくは読み出し動作を行なう対象のメモリブロックをどのメモリブロックにするかを切り替える切り替え部70を有する。

【0055】

メモリアレイ部40は、メモリブロックA、メモリブロックB、メモリブロックC、メモリブロックDの4つのメモリブロックから構成されている。この各メモリブロックは、互いに独立しており、各メモリブロックに選択的に書き込み動作若しくは読み出し動作を行なうことが可能である。さらに、各メモリブロックは、図4に示すようなキャパシタを有するアンチフューズを一つのメモリセルとし、このメモリセルが複数個、例えば512個を一つのメモリブロックとして構成するようにして成っている。

【0056】

可変電圧源部50は、電源配線16を介して入力された電源電圧Vccから、メモリアレイ部40に対して書き込み動作を実行する際のブロー(書き込み)電圧VDD及び、メモリアレイ部40に対して読み出し動作を実行する際の読み出し電圧Vrを生成する。ブロー電圧Vdd及び読み出し電圧Vrは、一般に知られている昇圧回路等から生成される。

【0057】

また、可変電圧源部50は、デジタルブロック8から書き込み信号Sw若しくは読み出し信号Srが入力され、デジタルブロック8から書き込み信号Srが入力された時には、ブロー電圧Vddを生成し、読み出し信号Swが入力された時には、読み出し電圧Vrを生成する。このブロー電圧VDD及び読み出し電圧Vrは、書き込み/読み出し制御部60に供給される。

【0058】

切り替え部70は、デジタルブロック8から入力される書き込み信号Sw若しくは読み出し信号Srに記されている、どのメモリブロックに書き込み若しくは読み出しを行なうかというアドレス情報に基づき、そのメモリブロックに対して信号が入出力可能となるように切り替えを行なう部分であり、2ビットカウンタ72と暗号キー判定部74とを有している。

【0059】

2ビットカウンタ72は、入力された書き込み信号Sw若しくは読み出し信号Sr内に含まれるアドレス情報を抽出する。このアドレス情報は、書き込み信号Sw若しくは読み出し信号Sr内のある部分、例えば先頭に、乗せられている。アドレス情報は、メモリブロックの数に応じた情報量を有していればよく、本実施例のようにメモリアレイ部40に4つのメモリブロックが設けられている場合には、アドレス情報は2ビットの情報量を有している。2ビットカウンタ72は、この書き込み信号Sw若しくは読み出し信号Srを計数し、2ビットのアドレス情報を抽出する。そして、この2ビットのアドレス情報は、書き込み/読み出し制御部60に入力される。

【0060】

暗号キー判定部74は、メモリブロックに対しての読み出し若しくは書き込みについて、可否を判定する部分であり、暗号キー記憶部76と、暗号キー比較部78とを有している。

【0061】

暗号キー記憶部76には、暗号キーが記憶されている。この暗号キーは、無線タグを使用することのできる人によって予め設定されており、この暗号キーを知っている使用者以外は、無線タグに書き込みや読み出しをすることができないようにするためのものである。

【0062】

暗号キー比較部78は、暗号キー記憶部76に記憶されている暗号キーと、リーダ・ライタ装置2から送信されてくる暗号キー情報とを比較し、この暗号キーと暗号キー情報とが一致することにより、書き込み若しくは読み出しのどちらか一方、あるいは書き込み及び読み出しの両方を可能とすることができる。暗号キーと暗号キー情報が一致したときには、読み出し若しくは書き込みのどちらか一方、あるいは書き込み及び読み出しの両方を可能にする書き込み読み出し可能信号を書き込み/読み出し制御回路60に入力し、一致しなかったときには、読み出し若しくは書き込みのどちらか一方、あるいは書き込み及び読み出しの両方を不可能にする書き込み読み出し不可能信号を、書き込み/読み出し制御回路60に入力する。

【0063】

なお、この暗号キー情報は、無線タグを使用する人によって、リーダ・ライタ装置2に入力され、この暗号キー情報が、電磁波に乗せられて、無線タグ1に入力される。

【0064】

ここで本実施例における暗号キー比較部78は、暗号キーと、暗号キー情報とが、一致したときに、読み出し若しくは書き込みを可能にするというように構成されているが、必ずしも暗号キーと、暗号キー情報とが、一致したときにのみ、読み出し若しくは書き込みを可能にするという構成に限らず、例えば、暗号キー情報と暗号キーとが一対一対応が取れているときに、読み出し若しくは書き込みを可能にするという構成等、種々の構成が考えられる。

【0065】

書き込み/読み出し制御部60は、デジタルブロック8から信号入力端子80aを介して書き込み信号Sw若しくは読み出し信号Srが入力され、書き込み信号Swが入力された時には、書き込み制御信号を生成し、読み出し信号Srが入力された時には、読み出し制御信号を生成する。

【0066】

書き込み制御信号は、メモリブロック内の各メモリセルに入力され、この信号を基に、メモリセルに対して書き込み動作が行なわれ、メモリブロックに情報が書き込まれる。また、読み出し制御信号は、メモリブロック内の各メモリセルに入力され、この信号を基に、メモリセルに対して読み出し動作が行なわれ、メモリブロックに記憶してある情報が読み出される。

【0067】

書き込み/読み出し制御部60は、暗号キー判定部74から、書き込み読み出し可能信号が入力されたときには、2ビットのアドレス情報を基にして、読み出し若しくは書き込みを行なう対象のメモリブロックに、書き込み制御信号若しくは読み出し制御信号を入力し、その対象のメモリブロックに対して書き込み動作若しくは読み出し動作を行なう。なお、書き込み/読み出し制御部60は、暗号キー判定部74から、書き込み読み出し不可能信号が入力されたときには、書き込み若しくは読み出し動作を行なわない。

【0068】

例えば、書き込み読み出し可能信号が入力され、読み出し信号SrにメモリブロックBに対応するアドレス情報が記してあれば、書き込み/読み出し制御部60は、書き込み/読み出し制御部60において生成された読み出し制御信号をメモリブロックBに入力し、メモリブロックBの情報を読み出す。また、書き込み信号SwにメモリブロックDに対応するアドレス情報が記してあれば、書き込み読み出し可能信号が入力され、書き込み/読み出し制御部60は、書き込み/読み出し制御部60において生成された書き込み制御信号をメモリブロックDに入力し、メモリブロックDに情報を書き込む。

【0069】

ここで、各メモリブロックを構成しているメモリセルの構造及びメモリセルに対する書き込み動作及び読み出し動作について、図4を参照して説明する。

【0070】

図4に示すアンチフューズは、記憶素子となるキャパシタ101、第1のトランジスタ102及び第2のトランジスタ103を有し、キャパシタ101が導通しているか否かにより、情報を記憶するものである。

【0071】

キャパシタ101は、電源入力端子Din、第1のトランジスタ102と第2のトランジスタ103に接続されている。電源入力端子Dinからは、ブロー電圧Vdd、0V(GND電位)及び読み出し電圧Vrの少なくとも3種類の電圧が入力される。第1のトランジスタ102の他方は、出力端子Doutとなっている。第2のトランジスタ103の他方は、GNDに接地されている。第1のトランジスタ102のゲート電極にはφ1、第2のトランジスタ103のゲート電極にはφ2という書き込み制御信号及び読み出し制御信号が、書き込み/読み出し制御部60から入力され、ゲート電極の電圧を変化させる。

【0072】

情報の書き込みは次のように行なう。第1のトランジスタ102をOFFにしたままの状態で第2のトランジスタ103をONする。第2のトランジスタ103はGNDに接地されているため、第2のトランジスタ103をONすることによりキャパシタ101の陰極の電位は0Vとなる。電源入力端子Dinに入力する電圧をキャパシタ101の絶縁耐圧(ブロー電圧Vdd)以上の高電圧に設定することにより、キャパシタ101は絶縁破壊を起こし、情報の記憶状態になる。例えばキャパシタ101が絶縁破壊された状態を情報“1”が記憶され、絶縁破壊されていない状態を情報“0”が記憶されていると定義する。この時電源入力端子Dinから供給された電流は、破壊されたキャパシタ101、第2のトランジスタ103を通って、GNDへと流れる。

【0073】

情報の読み出しは次のように行なう。まず電源入力端子Dinに入力する電圧を読み出し電圧Vrに設定する。この読み出し電圧Vrは、キャパシタ101に印加してもキャパシタ101が絶縁破壊を生じない程度に低い電圧である。次に第2のトランジスタ103をOFFにし、第1のトランジスタ102をONにする。キャパシタ101に情報“1”が記憶されている場合には、キャパシタ101は電極間が導通しているため、電源入力端子Dinから入力された電流は、キャパシタ101と第1のトランジスタ102を通過して、出力端子Doutを介して外部に電流が出力される。

【0074】

一方で、キャパシタ101に情報“0”が記憶されている場合は、キャパシタ101は絶縁破壊されておらず、互いの電極は絶縁されたままであるため、出力端子Doutを介して外部へ電流は出力されない。従って、出力端子Doutを流れる電流の有無により情報“1”または“0”が記憶されたか否かを判別することができる。

【0075】

以上のように、本実施例に係る無線タグ1は構成されている。

【0076】

本実施例に係る無線タグ1によれば、一つの無線タグ内に複数のメモリブロックがあり、且つ書き込み信号Sw内のアドレス情報に基づいて切り替え部70において切り替えを行ない、各メモリブロックに選択的に情報を書き込むことが可能である。そのため、一つの無線タグに複数の情報を記憶させておくことが可能である。さらに各メモリブロックに記憶された情報を読み出し信号Srに応じて、選択的に読み出すことが可能である。

【0077】

また、CMOS製造プロセスにより製造することが可能であるフューズ型若しくはアンチフューズ型の電気フューズを記憶素子として用いているため、安価に製造することが可能である。

【0078】

次に、無線タグ1が書き込み信号Swを受信し、情報を記憶する場合の無線タグ1の書き込み動作について説明する。

【0079】

まず始めに、アンテナ部3は、リーダ・ライタ装置2から発信された交流信号(書き込み信号Sw)を受信し、この交流信号から誘導電流を生成する。

【0080】

次に、電源制御部9において、誘導電流から安定した内部電源電圧Vccを生成し、無線タグ1内のメモリ部4、周辺回路部5等の各内部回路群に供給する。

【0081】

アンテナ部3において受信した交流信号は、搬送波抽出回路19に入力され、交流信号が矩形波に整形され、デジタルブロック8に入力される。

【0082】

デジタルブロック8内で、搬送波に乗せられて入力された書き込み信号Swに、変調、復号処理等が施され、書き込み信号Swがメモリ部4に入力される。

【0083】

メモリ部4に入力された書き込み信号Swは、切り替え部70に入力され、切り替え部70において、書き込み情報Sw内のアドレス情報を基に、メモリアレイ部40内のどのメモリブロックに情報の書き込みが行なわれるかというアドレス情報が抽出される。

【0084】

また、書き込み/読み出し制御部60において、メモリアレイ部40に書き込み動作を行なう書き込み制御信号が生成され、アドレス情報に基づき選択されたメモリブロックに、書き込み制御信号が供給され、選択されたメモリブロックに書き込み動作が行なわれる。

【0085】

このようにして、外部のリーダ・ライタ装置2から入力された交流信号により、無線タグ1のメモリブロックに情報が書き込まれる。

【0086】

次に、無線タグ1が読み出し信号Srを受信し、情報を記憶する場合の無線タグ1の読み出し動作について説明する。

【0087】

まず始めに、アンテナ部3は、リーダ・ライタ装置2から発信された交流信号(読み出し信号Sr)を受信し、この交流信号から誘導電流を生成する。

【0088】

次に、電源制御部9において、誘導電流から安定した内部電源電圧Vccを発生させ、無線タグ1内のメモリ部4、周辺回路部5等の各内部回路群に供給する。

【0089】

アンテナ部3において受信した交流信号は、搬送波抽出回路19に入力され、交流信号が矩形波に整形され、デジタルブロック8に入力される。

【0090】

デジタルブロック8内で、搬送波に乗せられて入力された読み出し信号Srに、変調、復号処理等が施され、読み出し信号Srがメモリ部4に入力される。

【0091】

メモリ部4に入力された読み出し信号Srは、切り替え部70に入力され、切り替え部70においてメモリアレイ部40内のどのメモリブロックの情報を読み出すかが読み出し信号Srのアドレス情報が抽出される。

【0092】

書き込み/読み出し制御部60において、メモリアレイ部40に読み出し動作を行なう読み出し制御信号が生成される。

【0093】

続いて、アドレス情報に基づき選択されたメモリブロックに、読み出し制御信号が供給され、選択されたメモリブロックに読み出し動作が行なわれる。

【0094】

次に、選択されたメモリブロックに入力される読み出し制御信号に対する出力信号として、読み出しデータが信号出力端子80bを介して、デジタルブロック8に入力される。

【0095】

この読み出しデータに、暗号化、変調化等の処理がなされ、通信コントロール回路18、送信回路20を介して、整流器12、アンテナ部2から読み出し信号Srに対する応答信号として読み出しデータが、リーダ・ライタ装置2に送信される。

【0096】

このようにして、外部のリーダ・ライタ装置2から入力された交流信号により、無線タグ1に記録された情報が読み出される。

【0097】

以上のように、リーダ・ライタ装置2からの書き込み信号Swにより、指定したメモリブロックに情報を書き込むことが可能である。また、読み出し信号Srにより、任意のメモリブロックの情報を読み出すことが可能である。そのため、一つの無線タグ1に対して、複数の独立した情報を記憶させておくことが可能であり、リード・ライト装置2からの読み出し信号Srによって、任意のメモリブロックから情報を読み出すことが可能である。

【0098】

また、各メモリブロックは、書き換え不可能な電気フューズを記憶素子としているため、各メモリブロックに一度書き込まれた情報が改ざんされるという危険を防止することが可能である。

【0099】

本実施例に係る無線タグは、複数種のデータを一つの無線タグ内に記憶することが可能であり、無線タグのメモリ部をCMOSプロセスで製造可能であるため、EEPROMを用いた無線タグよりも安価に製造することが可能である。

【0100】

(実施例の変形例)

本実施例の変形例に係る無線タグ100を図5に示す。実施例に示した無線タグ1は、リーダ・ライタ装置2から送信される交流信号からアンテナコイルにおいて誘導電流を生成し、この誘導電流を無線タグの電源としていたが、本実施例の変形例に係る無線タグ100は、無線タグ100の外部から、リード線などの配線により無線タグ100に対して電源電圧Vccが供給される。実施例と同一部分には同一符号を付して、その説明を省略する。

【0101】

本実施例の変形例によれば、電源供給手段を有するもの(例えば、携帯情報端末)の内部に無線タグ100を付す時に特に有効となる。

【0102】

外部から交流信号により電源を供給する無線タグ1は、配線を介して電源を供給する無線タグ100に比べて、信号を送受信する交流信号として、長時間若しくは高い振幅の電磁波を用いる必要がある。この長時間若しくは高い振幅の交流信号は、ノイズを生み出しやすい。このように、無線タグ100が付されたものに、電源供給源が存在する場合には、配線により供給することも可能である。

【図面の簡単な説明】

【0103】

【図1】本発明の実施例に係る無線タグを用いたシステムの概略図。

【図2】本発明の実施例に係る無線タグのブロック図。

【図3】本発明の実施例に係る無線タグのメモリ部の概略図。

【図4】本発明の実施例に係る無線タグのメモリセルの図。

【図5】本発明の実施例の変形例に係る無線タグのブロック図。

【符号の説明】

【0104】

1、100 無線タグ

2 リーダ・ライタ装置

3 アンテナ部

4 メモリ部

5 周辺回路部

6 インダクタンス配線

7 RFアナログブロック

8 デジタルブロック

9 電源制御部

10 送受信部

12 整流器

13 BGR回路

14 シャントレギュレータ

15 シリーズレギュレータ

16 電源配線

17 パワーオンリセット回路

18 通信コントロール回路

19 搬送波抽出回路

20 送信回路

21 発振器

22 同期調整回路(PLL)

23 復調回路

24 データ処理回路

25 変調回路

40 メモリアレイ部

50 可変電圧源部

60 書き込み/読み出し制御部

70 切り替え部

72 2ビットカウンタ

74 暗号キー判定部

76 暗号キー記憶部

78 暗号キー比較部

80a 信号入力端子

80b 信号出力端子

101 可変電圧源

102 キャパシタ(記憶素子)

103 第1のトランジスタ

104 第2のトランジスタ

【特許請求の範囲】

【請求項1】

電磁波による交流信号の送受信を行なうアンテナ部と、

前記アンテナ部にて受信した交流信号を基に書き込み若しくは読み出しが行なわれる複数の電気フューズから構成される複数のメモリブロックと、

前記複数のメモリブロックのうち、どのメモリブロックに書き込み若しくは読み出しを行なうかを切り替える切り替え部とを有し、

前記切り替えは、前記アンテナ部で受信した交流信号に基づいて行なわれることを特徴とする無線タグ。

【請求項2】

前記切り替え部は、暗号キーが記憶された暗号キー判定部をさらに備え、

前記アンテナ部で受信した交流信号には、メモリブロックに対する書き込み若しくは読み出しを可能とする暗号キー情報が含まれており、

前記暗号キー判定部は、前記暗号キー判定部内に記憶された前記暗号キーと、前記交流信号に含まれる暗号キーとを比較し、前記比較結果に応じて前記メモリブロックに対して書き込み若しくは読み出しの少なくとも一方を可能とすることを特徴とする請求項1記載の無線タグ。

【請求項3】

電磁波を用いて信号の送受信を行なうリーダ装置と無線タグを有する無線タグを用いたシステムにおいて、

該無線タグは、電磁波による交流信号の送受信を行なうアンテナ部と、前記アンテナ部にて受信した交流信号を基に読み出しが行なわれる複数の電気フューズから構成される複数のメモリブロックと、前記複数のメモリブロックのうち、どのメモリブロックに読み出しを行なうかを切り替える切り替え部とを有し、

前記切り替えが、前記リーダ装置から送信した電磁波により行なわれることを特徴とする無線タグを用いたシステム。

【請求項4】

前記切り替え部は、暗号キーが記憶された暗号キー判定部をさらに備え、

前記アンテナ部で受信した交流信号には、メモリブロックに対する読み出しを可能とする暗号キー情報が含まれており、

前記暗号キー判定部は、前記暗号キー判定部内に記憶された前記暗号キーと、前記交流信号に含まれる暗号キーとを比較し、前記比較結果に応じて前記メモリブロックに対して読み出しを可能とすることを特徴とする請求項3に記載の無線タグを用いたシステム。

【請求項5】

電磁波を用いて信号の送受信を行なうライタ装置と無線タグを有する無線タグを用いたシステムにおいて、

該無線タグは、電磁波による交流信号の送受信を行なうアンテナ部と、前記アンテナ部にて受信した交流信号を基に書き込みが行なわれる複数の電気フューズから構成される複数のメモリブロックと、前記複数のメモリブロックのうち、どのメモリブロックに書き込みを行なうかを切り替える切り替え部とを有し、

前記切り替えが、前記ライタ装置から送信した電磁波により行なわれることを特徴とする無線タグを用いたシステム。

【請求項6】

前記切り替え部は、暗号キーが記憶された暗号キー判定部をさらに備え、

前記アンテナ部で受信した交流信号には、メモリブロックに対する書き込みを可能とする暗号キー情報が含まれており、

前記暗号キー判定部は、前記暗号キー判定部内に記憶された前記暗号キーと、前記交流信号に含まれる暗号キーとを比較し、前記比較結果に応じて前記メモリブロックに対して書き込みを可能とすることを特徴とする請求項5に記載の無線タグを用いたシステム。

【請求項1】

電磁波による交流信号の送受信を行なうアンテナ部と、

前記アンテナ部にて受信した交流信号を基に書き込み若しくは読み出しが行なわれる複数の電気フューズから構成される複数のメモリブロックと、

前記複数のメモリブロックのうち、どのメモリブロックに書き込み若しくは読み出しを行なうかを切り替える切り替え部とを有し、

前記切り替えは、前記アンテナ部で受信した交流信号に基づいて行なわれることを特徴とする無線タグ。

【請求項2】

前記切り替え部は、暗号キーが記憶された暗号キー判定部をさらに備え、

前記アンテナ部で受信した交流信号には、メモリブロックに対する書き込み若しくは読み出しを可能とする暗号キー情報が含まれており、

前記暗号キー判定部は、前記暗号キー判定部内に記憶された前記暗号キーと、前記交流信号に含まれる暗号キーとを比較し、前記比較結果に応じて前記メモリブロックに対して書き込み若しくは読み出しの少なくとも一方を可能とすることを特徴とする請求項1記載の無線タグ。

【請求項3】

電磁波を用いて信号の送受信を行なうリーダ装置と無線タグを有する無線タグを用いたシステムにおいて、

該無線タグは、電磁波による交流信号の送受信を行なうアンテナ部と、前記アンテナ部にて受信した交流信号を基に読み出しが行なわれる複数の電気フューズから構成される複数のメモリブロックと、前記複数のメモリブロックのうち、どのメモリブロックに読み出しを行なうかを切り替える切り替え部とを有し、

前記切り替えが、前記リーダ装置から送信した電磁波により行なわれることを特徴とする無線タグを用いたシステム。

【請求項4】

前記切り替え部は、暗号キーが記憶された暗号キー判定部をさらに備え、

前記アンテナ部で受信した交流信号には、メモリブロックに対する読み出しを可能とする暗号キー情報が含まれており、

前記暗号キー判定部は、前記暗号キー判定部内に記憶された前記暗号キーと、前記交流信号に含まれる暗号キーとを比較し、前記比較結果に応じて前記メモリブロックに対して読み出しを可能とすることを特徴とする請求項3に記載の無線タグを用いたシステム。

【請求項5】

電磁波を用いて信号の送受信を行なうライタ装置と無線タグを有する無線タグを用いたシステムにおいて、

該無線タグは、電磁波による交流信号の送受信を行なうアンテナ部と、前記アンテナ部にて受信した交流信号を基に書き込みが行なわれる複数の電気フューズから構成される複数のメモリブロックと、前記複数のメモリブロックのうち、どのメモリブロックに書き込みを行なうかを切り替える切り替え部とを有し、

前記切り替えが、前記ライタ装置から送信した電磁波により行なわれることを特徴とする無線タグを用いたシステム。

【請求項6】

前記切り替え部は、暗号キーが記憶された暗号キー判定部をさらに備え、

前記アンテナ部で受信した交流信号には、メモリブロックに対する書き込みを可能とする暗号キー情報が含まれており、

前記暗号キー判定部は、前記暗号キー判定部内に記憶された前記暗号キーと、前記交流信号に含まれる暗号キーとを比較し、前記比較結果に応じて前記メモリブロックに対して書き込みを可能とすることを特徴とする請求項5に記載の無線タグを用いたシステム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2006−163469(P2006−163469A)

【公開日】平成18年6月22日(2006.6.22)

【国際特許分類】

【出願番号】特願2004−349429(P2004−349429)

【出願日】平成16年12月2日(2004.12.2)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成18年6月22日(2006.6.22)

【国際特許分類】

【出願日】平成16年12月2日(2004.12.2)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]