無線装置およびその製造方法

【課題】ICチップのプロセスばらつきによって高周波特性がばらついた場合でも、回路特性を最適化できるICチップを基板にフリップチップ実装する無線装置を提供する。

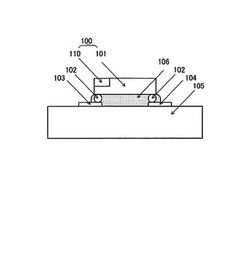

【解決手段】無線装置は、マイクロ波、ミリ波帯の電力増幅器用高周波ICチップ100、バンプ102、入力端子103、出力端子104、基板105、アンダーフィル106、プロセスばらつき検出部110を有する。プロセスばらつき検出部は、プロセスばらつきによる回路特性の変動量をモニタし、モニタされた回路特性の変動量を用いて、算出されたパラーメータを有するアンダーフィル106が、基板105とミリ波帯の電力増幅器用高周波ICチップ100との間に充填されることで、プロセスばらつき及びアンダーフィルの影響があっても、所望の回路特性が得られる無線装置を提供できる。

【解決手段】無線装置は、マイクロ波、ミリ波帯の電力増幅器用高周波ICチップ100、バンプ102、入力端子103、出力端子104、基板105、アンダーフィル106、プロセスばらつき検出部110を有する。プロセスばらつき検出部は、プロセスばらつきによる回路特性の変動量をモニタし、モニタされた回路特性の変動量を用いて、算出されたパラーメータを有するアンダーフィル106が、基板105とミリ波帯の電力増幅器用高周波ICチップ100との間に充填されることで、プロセスばらつき及びアンダーフィルの影響があっても、所望の回路特性が得られる無線装置を提供できる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、無線装置およびその製造方法に係り、特に高周波回路を備えた無線装置に関する。

【背景技術】

【0002】

主にマイクロ波、ミリ波帯では、高周波ICチップを、例えば、金(Au)、又は、半田のバンプを用いて実装基板に実装するフリップチップ実装が広く用いられている。フリップチップ実装では、実装基板と高周波ICチップとを短距離(最短)によって接続できるので、接続間での損失を小さくできる。

【0003】

一例を図17に従って説明する。モジュールの母体基板である実装基板1として、例えばセラミック基板を用い、入出力端子2、3に、例えば、高周波ICチップとして、増幅器のMMIC(モノリシックマイクロ波集積回路)チップ4の回路5をバンプ6によって接続する。さらに、接続の補強、又は、MMICチップ4のシールのために、実装基板1とMMICチップ4との間にアンダーフィル7として樹脂が充填される。

【0004】

しかしながら、上述したアンダーフィル7が充填されると、寄生容量が増大するために、MMICチップ4の特性が低周波数側にずれ、更に、利得が下がる特性劣化が発生する。

【0005】

そこで、フリップチップ実装におけるアンダーフィルの影響を受けにくいマイクロ波・ミリ波回路装置が提案されている(特許文献1参照)。

【0006】

図18は、特許文献1に記載の従来例のフリップチップ実装したマイクロ波・ミリ波回路装置を示す図である。マイクロ波・ミリ波回路装置は、実装基板1に対して、対向配置されたMMICチップ4がフリップチップ実装されている。MMICチップ4は、内側に回路5を囲む絶縁体壁11を設け、外側にアンダーフィル7を施す。この形態によれば、回路5(主部)を囲んで絶縁体壁11が形成されているので、アンダーフィル7を施しても樹脂が回路5の下に入らず、回路の特性が変化することは少ない。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2000−269384号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、特許文献1に記載のフリップチップ実装したマイクロ波・ミリ波回路装置は、MMICチップ4が、内側に回路5を囲む絶縁体壁11を設け、外側にアンダーフィル7を施す必要がある。このため、特許文献1の構成ではMMICチップ4の回路5の下は空洞となっており、十分な実装強度を得るのは困難である。

【0009】

また、高周波ICチップの製造ばらつき(プロセスばらつき)によって高周波ICチップの特性がばらついた場合には、回路特性が変化し、モジュールとして性能が劣化する場合がある。

【0010】

つまり、フリップチップ実装における特性劣化は抑制できても、高周波ICチップのプロセスばらつきに起因する特性劣化は残り、モジュールとしての歩留まりが低下してしまうという課題がある。

【0011】

本発明は前記実情に鑑みてなされたもので、実装強度を確保し、更に、特性劣化を抑制した無線装置を提供することを目的とする。

【課題を解決するための手段】

【0012】

そこで本発明は、実装基板と、前記実装基板上にフリップチップ実装された高周波ICチップとを備え、前記高周波ICチップと前記実装基板との間にアンダーフィルが充填された無線装置であって、前記高周波ICチップは、主回路を構成する素子部と、前記高周波ICチップのプロセスばらつきを検出するプロセスばらつき検出部を具備し、前記充填されたアンダーフィルは、前記検出したプロセスばらつきに基づいて調整されたパラメータを有することを特徴とする。

【0013】

また本発明は、上記無線装置であって、前記プロセスばらつき検出部は前記素子部の一部として機能するものを含む。

【0014】

また本発明は、上記無線装置であって、前記プロセスばらつき検出部は、前記高周波ICチップ上において前記素子部とは分離されたものを含む。

【0015】

また本発明は、上記無線装置であって、前記プロセスばらつき検出部はトランジスタを用いて構成されたものを含む。

【0016】

また本発明は、上記無線装置であって、前記プロセスばらつき検出部はリングオシレーターを用いて構成されたものを含む。

【0017】

また本発明は、上記無線装置であって、前記アンダーフィルのパラメータはアンダーフィルとして充填する樹脂の比誘電率であるものを含む。

【0018】

また本発明は、上記無線装置であって、前記アンダーフィルのパラメータは前記高周波ICチップと前記実装基板間の距離であるものを含む。

【0019】

また本発明は、上記無線装置であって、前記高周波ICチップはバンプを介して前記実装基板と接続し、前記バンプは前記高周波ICチップ上において非対称に配置されているものを含む。

【0020】

また本発明は、上記無線装置であって、前記高周波ICチップと前記実装基板の間のアンダーフィルは、前記高周波ICチップをフリップチップ実装した領域内において厚さが異なるものを含む。

【0021】

また本発明は、上記無線装置であって、前記プロセスばらつき検出部はPCM(ProcessControl Monitor)データを用いるものを含む。

【0022】

また本発明は、主回路を構成する素子部と、プロセスばらつき検出部とを備えた高周波ICチップを製造する工程と、前記高周波ICチップの前記プロセスばらつき検出部を用いてプロセスばらつきを検出する工程と、前記検出する工程において検出されたデータに基づいてアンダーフィルのパラメータを調整する工程と、前記調整する工程において得られた前記パラメータを有するアンダーフィルを充填して、実装基板上に前記高周波ICチップを実装する工程と、を含むことを特徴とする。

【図面の簡単な説明】

【0023】

【図1】本発明の実施の形態1のマイクロ波・ミリ波回路に対応した電力増幅器を含む無線装置の説明図

【図2】本発明の実施の形態1のマイクロ波・ミリ波回路に対応した電力増幅器の等価回路図

【図3】電力増幅器におけるプロセスばらつき検出部を構成するMOSFETの等価回路図

【図4】閾値電圧Vthがプロセスばらつきによって変動した場合の電力増幅器の入力反射係数および、出力反射係数を示す図(アンダーフィルがない場合)

【図5】樹脂をアンダーフィルとして充填した場合の電力増幅器の入力反射係数および、出力反射係数を示す図(アンダーフィルがない場合/ある場合)

【図6】図3に示したMOSトランジスタのゲート電圧−ドレイン電流特性を示す図

【図7】樹脂の比誘電率Erに対する反射係数のノッチの周波数の変動量を示す図

【図8】実装基板と電力増幅器ICチップ間の距離に対するノッチ周波数の変動量を示す図

【図9】プロセスばらつき及びアンダーフィルの影響による変化に対する反射係数のノッチ周波数すなわち反射係数が最小となる周波数の変動の関係を示す図

【図10】プロセスばらつきに基づく回路特性の変動量を補償するためのアンダーフィルの選択を含む実装工程を示すフローチャートを示す図

【図11】本発明の実施の形態2の無線装置におけるプロセスばらつき検出部を示す図

【図12】本発明の実施の形態3における無線装置を示す図であり、(a)は電力増幅器ICチップを下方から見た図、(b)は、実装状態を示す断面図

【図13】本発明の実施の形態3における無線装置の電力増幅器ICチップの変形例

【図14】本発明の実施の形態3における無線装置の電力増幅器ICチップの変形例

【図15】本発明の実施の形態3における無線装置の電力増幅器ICチップの変形例

【図16】本発明の実施の形態4における無線装置の電力増幅器ICチップを形成するためのウェハの一例を示す図

【図17】従来例の無線装置を示す図

【図18】従来例のマイクロ波・ミリ波回路装置を示す図

【発明を実施するための形態】

【0024】

(実施の形態1)

図1に、本発明の実施の形態1としてマイクロ波・ミリ波回路に対応した電力増幅器を含む無線装置の構成の一例を示す。

【0025】

本実施の形態1の無線装置では、高周波ICチップとして電力増幅器用高周波ICチップ100を用いており、電力増幅器を構成する電力増幅器用高周波ICチップ100に対し、主回路101に加え、ばらつき検出回路を構成するプロセスばらつき検出部110を集積化している。

【0026】

図1は、本実施の形態1のプロセスばらつき検出部110を有する電力増幅器用高周波ICチップ100を搭載した無線装置の説明図である。図2は同電力増幅器用高周波ICチップ100の等価回路図である。図3は同電力増幅器用高周波ICチップにおけるプロセスばらつき検出部110を構成するMOSFETの等価回路図である。

【0027】

本発明に係る実施の形態1の電力増幅器用高周波ICチップについての説明に先立ち、マイクロ波・ミリ波回路に対応した電力増幅器用高周波ICチップの動作について説明する。電力増幅器用高周波ICチップ100の主回路101は一般的な回路であるが、本実施の形態では、図1及び図2に示すように、主回路101を構成する素子部500に、プロセスばらつき検出部110が集積化されている。

【0028】

図2に、本発明の実施の形態1のマイクロ波・ミリ波回路に対応した 電力増幅器用高周波ICチップの等価回路を示す。電力増幅器においては、主回路101を構成する素子部500の入力端子502に、直流阻止用容量504を設け、出力端子503に、直流阻止用容量505を設けている。

【0029】

電力増幅用のトランジスタ501のゲートGと入力端子502との間に入力整合用の伝送線路506、507が設けられており、ドレインDと出力端子503との間には、出力整合用の伝送線路508、509が設けられている。

【0030】

トランジスタ501用のゲート電圧端子510と電力増幅用のトランジスタ501のゲートGとの間に、入力整合用の伝送線路506、507が直列接続されている。また電力増幅用のトランジスタ501用のドレイン電圧端子511と電力増幅用のトランジスタ501のドレインDとの間に、出力整合用の伝送線路508、509が直列接続されている。

【0031】

入力信号Sinは入力端子502から直流阻止用容量504、伝送線路507を介してトランジスタ501のゲートGに入力される。ゲートGは伝送線路506、507を介してゲート電圧端子510に接続され、ゲート電圧Vgが印加される。トランジスタ501のソースSはグランドに接地される。

【0032】

トランジスタ501のドレインDは伝送線路509、508を介してドレイン電圧端子511に接続され、ドレイン電圧Vdが印加される。伝送線路509、508の接続点から直流阻止用容量505を介して出力端子503から出力信号Soutは出力される。電力増幅用のトランジスタ501には、ドレイン電流Idが流れ、トランジスタ501のソースSには、ソース端子501Sが設けられている。

【0033】

一般に、トランジスタは、プロセスばらつきによって閾値電圧Vthが変動し、閾値電圧Vthが低いとドレイン電流Idは増加し、閾値電圧Vthが高いとドレイン電流Idは減少する。また、トランジスタの最大動作周波数fmaxは、閾値電圧Vthが低いと増加し、閾値電圧Vthが高いと減少し、最大動作周波数fmaxが高い方がトランジスタの高周波特性が良好となる。

【0034】

従って、図3に示す、プロセスばらつき検出部を構成するMOSFETについても、プロセスばらつきによって閾値電圧Vthは変動し、閾値電圧Vthが低いとドレイン電流Id’は増加し、閾値電圧Vthが高いとドレイン電流Id’は減少する。

【0035】

図4は、閾値電圧Vthをパラメータにした電力増幅器用高周波ICチップ100の入力反射係数S11及び出力反射係数S22と周波数特性との関係を示すグラフである。なお、プロセスばらつきによって、閾値電圧Vthが変動している。縦軸は反射係数、横軸は周波数(GHZ)を示す。

【0036】

実線はプロセスばらつきがない場合の理想の閾値電圧であり、以後、閾値電圧Vthが中心の場合と記載し、波線はプロセスばらつきがあり、理想の閾値電圧よりも低い電圧として、閾値電圧Vthが低い場合と記載し、一点鎖線はプロセスばらつきがあり、理想の閾値電圧よりも高い電圧として、閾値電圧Vthが高い場合と記載する。

【0037】

図4では、反射係数S11と反射係数S22とを同じ軸を用いて表記しているが、入力反射係数S11と出力反射係数S22とは、異なる特性であってもよい。

【0038】

閾値電圧Vthが低いほどドレイン電流Idが増加し、ドレイン電流Idの増加によってトランジスタ501の寄生容量が増加する。

例えば、閾値電圧Vthが中心の場合に入力反射係数S11及び出力反射係数S22のノッチ、すなわち、反射係数が最も小さくなる位置が所望の周波数(ノッチ周波数)fcとなるように設計をしたとしても、プロセスばらつきとしてのトランジスタ501の寄生容量によって、図4に示すように閾値電圧Vthが低くなると、入力反射係数S11及び出力反射係数S22のノッチの位置が低周波数側にシフトする。

【0039】

図5は、アンダーフィル106の有無をパラメータとした電力増幅器用高周波ICチップ100の入力反射係数S11及び出力反射係数S22と周波数特性との関係を示すグラフである。図2の電力増幅器が搭載された電力増幅器ICチップ、すなわち電力増幅器用高周波ICチップを実装基板105にフリップチップ実装し、図17に示すように、電力増幅器ICチップと実装基板105の間に樹脂をアンダーフィル106(UL)として充填した場合と、充填しない場合とを示している。

【0040】

アンダーフィルとして使用される樹脂は、一般的には誘電体であるため、寄生容量が増加する。実線はアンダーフィル(UF)がない場合、波線はフリップチップ実装しアンダーフィル(UF)がある場合の反射係数S11、S22を示す。

【0041】

図5では、電力増幅用のトランジスタ501の閾値電圧Vthが中心であり、アンダーフィル(UF)がない状態において、反射係数S11、S22のノッチの位置が周波数fcであったとしても、アンダーフィルを充填すると、アンダーフィルの影響としての寄生容量によって、反射係数S11、S22のノッチの位置が低周波数側にシフトする。

【0042】

なお、図5では、アンダーフィルの比誘電率が3.3であり、図8に示す実装基板−電力増幅器ICチップ間の距離が20μm以上である。

【0043】

本発明は、以上の点に着目してなされたもので、本実施の形態1では、高周波回路を備えた無線装置において、フリップチップ実装におけるアンダーフィルによる影響及びプロセスばらつきによる周波数特性劣化の課題を解決するものである。

【0044】

この課題を解決するために、対象の電力増幅器ICチップにおいてプロセスばらつき検出部110を構成するトランジスタを用いてプロセスばらつきを検出する構成を持つ。そして、検出結果を補償する材質又は充填量の条件を満たすアンダーフィルを充填することで、所望の周波数特性を得る。

【0045】

ここで、本発明の実施の形態1の無線装置の説明に戻る。図1は、本発明の実施の形態1における無線装置の構成を示す図である。無線装置は、マイクロ波又はミリ波回路に対応した電力増幅器用高周波ICチップ100、バンプ102、入力端子103、出力端子104、実装基板105、アンダーフィル106、プロセスばらつき検出部110を有する。電力増幅器用高周波ICチップ100はバンプ102を介して実装基板105上の入出力端子103、104に接続され、電力増幅器用高周波ICチップ100と実装基板105との間に樹脂がアンダーフィル106として充填される。更に電力増幅器用高周波ICチップ100は、電力増幅器用高周波ICチップ100のプロセスばらつきを検出するプロセスばらつき検出部110を有する。

【0046】

図3にプロセスばらつき検出部110の一例であるMOSトランジスタの等価回路図を示す。図6に図3に示したMOSトランジスタのゲート電圧−ドレイン電流特性を示す。図3のプロセスばらつき検出部はMOSトランジスタを用いて構成される。一般的にトランジスタは図6に示すようなゲート電圧−ドレイン電流特性を示し、図3のゲート電圧Vg’が閾値電圧Vth’を超えるとドレイン電流Id’が流れる。図6に示すようなゲート電圧−ドレイン電流特性を測定することによって、プロセスばらつき検出部110を構成するMOSトランジスタの閾値電圧Vth’を得ることが可能となる。

【0047】

一方、図5に示すようにフリップ実装においてアンダーフィルとして樹脂を充填すると、反射係数のノッチの位置に対応する周波数(以後、ノッチ周波数と記載する)すなわち反射係数が最小となる周波数が低下する。ノッチ周波数の変動量は図7に示すように樹脂の比誘電率Erによっても変化する。

【0048】

図7は樹脂の比誘電率Erに対する反射係数S11、S22のノッチ周波数すなわち反射係数が最小となる周波数の変動量を示しており、比誘電率Erが大きくなると、寄生容量が大きくなり、ノッチ周波数は低下する。アンダーフィルとして充填する樹脂の材料、又は、配合を変えることによって比誘電率が変わり、ノッチ周波数の変動量を調整できる。

【0049】

図8に、図1の実装基板105と電力増幅器用高周波ICチップ100との間の距離に対するノッチ周波数の変動量を示す。実装基板105と電力増幅器用高周波ICチップ100との間の距離が近いと、寄生容量が大きくなりノッチ周波数は変動量が大きい。

【0050】

実装基板105と電力増幅器用高周波ICチップ100との間の距離が遠くなると、距離に対する寄生容量の値は一定になりノッチ周波数の変動量は一定になる。ノッチ周波数の変動量が実装基板105−電力増幅器用高周波ICチップ100間の距離に比例する実装基板105−電力増幅器用高周波ICチップ100間の距離を距離Aとすると、距離Aを変化させることによってノッチ周波数の変動量を制御できる。例えば、アンダーフィルの充填量を調整することで、ノッチ周波数の変動量を制御できる。

【0051】

また、電力増幅器用高周波ICチップ100を実装基板105にフリップチップ実装する場合、電力増幅器用高周波ICチップ100の上方から圧力を加えて加工するが、上方からの圧力を変えることによって距離Aを変化できる。

【0052】

図9に、プロセスばらつき及びアンダーフィルの影響による変動に対する入力反射係数S11及び出力反射係数S22とノッチ周波数の変動との関係を示す。

【0053】

ここで、プロセスばらつきによる変化とは、トランジスタの閾値電圧Vthによる変化である。また、アンダーフィルの影響による変化とは、アンダーフィルの比誘電率Erによる変化と、実装基板105−電力増幅器用高周波ICチップ100間の距離に比例する実装基板105−電力増幅器用高周波ICチップ100間の距離Aによる変化と、のいずれかである。

【0054】

図9のノッチ周波数fcは、図4および図5と同様にMOSトランジスタの閾値電圧Vthが中心であり、アンダーフィル(UF)がない場合の入力反射係数S11及び出力反射係数S22のノッチの位置である。プロセスばらつきによって、ノッチ周波数は範囲Xにおいて変化し、上限・下限をそれぞれfxh、fxlとする。また、アンダーフィルの影響によって、ノッチ周波数は範囲Yにおいて変化し、上限・下限をそれぞれfyh、fylとする。

【0055】

ここで、アンダーフィルがない場合のノッチ周波数fcとアンダーフィルの影響によるノッチ周波数の上限fyhは等しい。プロセスばらつきとアンダーフィルの影響による変動量は、fylからfxhの範囲となり、所望の周波数ftがこの範囲に入れば良い。プロセスばらつきによる周波数の変動量をdfx、アンダーフィルの影響による周波数の変動量をdfyとすると、両方の影響を受けた後の周波数fzはfz=fc+dfx+dfyとなり、周波数fzを所望の周波数ftとすれば良い。

【0056】

以下、電力増幅器用高周波ICチップ100を搭載した無線装置の製造方法について説明する。まず、プロセスばらつきに基づく特性変動を補償するためのアンダーフィルの選択を含む実装工程を示すフローチャートを、図10に示す。

【0057】

電力増幅器用高周波ICチップ100を製造し(ステップS1001)、電力増幅器用高周波ICチップ100のプロセスばらつきをモニタする(ステップS1002)。ここで、例えばプロセスばらつきは、トランジスタの閾値電圧Vthを用いる。

【0058】

次に、モニタしたプロセスばらつきを用いて、回路特性の変動量を算出する(ステップS1003)。ここで、例えば回路特性は電力増幅器の入力反射係数S11及び出力反射係数S22とする。

【0059】

次に、算出した回路特性の変動分から所望の回路特性になるアンダーフィルの影響での変動量を決定する(ステップS1004)。最後に決定したアンダーフィルの影響での変動量に基づいてフリップチップ実装する(ステップS1005)。ここで、例えば、所望の回路特性を得るために必要なアンダーフィルの選択については、ステップS1005において決定されたアンダーフィルの影響での変動量に基づいて、樹脂の比誘電率の変更、又は、実装基板−電力増幅器用高周波ICチップ100間の距離の制御によって実行される。

【0060】

例えば、ステップS1002によって得られたプロセスばらつきに起因するトランジスタの閾値電圧をVthsとする。トランジスタの閾値電圧Vthが中心であるノッチ周波数fcに対して、プロセスばらつきによるノッチ周波数の変動量(dfx)を図4の入力反射係数S11及び出力反射係数S22を用いて算出する。

【0061】

次に、ノッチ周波数の変動量dfxを用いて、ノッチ周波数が所望の周波数ftとなるように、図7の結果に基づいてアンダーフィルの比誘電率Erの材料を選択する。

【0062】

プロセスばらつきによるノッチ周波数の変動量dfxを打ち消すように、アンダーフィルによるノッチ周波数の変動量(dfy)を決定し、決定した変動量dfyに対応する非誘電率Erの材料を選定する。あるいは、決定した変動量dfyに対応する実装基板105−電力増幅器用高周波ICチップ100間の距離を決定する。

【0063】

以上より、図10に示すフローチャートを用いて実装条件を決定することによって、プロセスばらつきによる特性の変動とアンダーフィルによる影響の変動が発生しても、回路特性を所望の特性に調整できる。

【0064】

つまり、プロセスばらつき検出部110において高周波ICチップのプロセスばらつきによる回路特性の変動量をモニタし、モニタした回路特性の変動量を用いて、アンダーフィルのパラメータを算出し、算出したパラメータのアンダーフィルを充填する。この構成によって、プロセスばらつき及びアンダーフィルの影響があっても、所望の回路特性が得られる。

【0065】

なお、本実施の形態では、プロセスばらつき検出部110としてトランジスタの閾値電圧Vthをモニタするとしたが、特にこれに限定されない。例えば、抵抗の抵抗値でも良いし、インダクタのインダクタンス値でも良いし、容量のキャパシタンス値でも良い。なお、抵抗は、例えば、ポリシリコン抵抗を用いることが出来る。

【0066】

また、実施の形態1では、プロセスばらつき検出部110は、主回路101を構成するMOSトランジスタ501とは別途独立して、MOSトランジスタを用いて分離形成した。

なお、変形例として、主回路101を構成するMOSトランジスタ501をばらつき検出回路(プロセスばらつき検出部)と兼用して用いることも可能である。

【0067】

他部については、実施の形態1の無線装置と同様に形成すればよい。これにより、チップの大型化を招くことなく、信頼性の高いプロセスばらつき検出およびプロセスばらつき補償が可能となる。

【0068】

また、プロセスばらつき以外にも、例えば、周辺回路との関係において容量調整をする目的であっても、アンダーフィルのパラメータを調整できる。

【0069】

(実施の形態2)

次に、ばらつき検出回路の回路構成を変更した実施の形態について説明する。

【0070】

本実施の形態では、ばらつき検出回路を構成するプロセスばらつき検出部110として、MOSFETに代えて図11に示すリングオシレーターを用いる。他の構成については実施の形態1と同様であるので、ここでの説明は省略する。

【0071】

本実施の形態においても、プロセスばらつき検出部110のゲート電圧−ドレイン電流特性を測定することにより、閾値電圧Vthの変動量を検出する。そして、検出した閾値電圧Vthの変動量に応じて、実装に用いられるアンダーフィルのパラメータを決定する。つまりプロセスばらつき検出部110によって、MOSトランジスタの閾値電圧Vthをモニタすることにより、図4に示した電圧増幅器の入力反射係数S11、出力反射係数S22のノッチの位置(ノッチ周波数)を推測できる。

【0072】

図11に示すように、リングオシレーターは、奇数個のインバータ121〜125が直列接続されてなり、出力側のインバータ125から出力される出力信号が入力側のインバータ121の入力へフィードバックされる。リングオシレーターのインバータ121に電源電圧を供給すると、インバータの動作遅延時間に依存する周波数において発振し、出力端子126から出力される。

【0073】

図11のリングオシレーターにおいて、インバータの動作遅延時間はプロセスばらつきによって変化する。例えば、トランジスタの閾値電圧Vthがプロセスばらつきによって低くなると、インバータの動作遅延時間が短くなり、リングオシレーターの発振周波数が高くなる。反対にトランジスタの閾値電圧Vthがプロセスばらつきによって高くなると、インバータの動作遅延時間が長くなり、リングオシレーターの発振周波数が低くなる。

【0074】

リングオシレーターの発振周波数をモニタすることによって、トランジスタの閾値電圧Vthを得ることが可能となる。プロセスばらつき検出部110によって、トランジスタの閾値電圧Vthをモニタすることによって、例えば図2に示した電圧増幅器の入力反射係数S11、出力反射係数S22のノッチの位置(ノッチ周波数)を推測できる。

【0075】

従って本実施の形態においても、実施の形態1と同様、図10に示したフローチャートを用いてパラメータを算出し、プロセスばらつきを補償するための実装条件を決定する。

【0076】

(実施の形態3)

次に本発明の実施の形態3について説明する。図12(a)は、本発明の実施の形態3における無線装置を構成する電力増幅器ICチップを下方から見た図である。図12(a)は、電力増幅器用高周波ICチップ100の下面にバンプ102が非対称に配置されている。

【0077】

電力増幅器用高周波ICチップ100を実装基板105にフリップチップ実装する場合、チップの上方から圧力を加えて加工するが、図12(a)に示すように、非対称なバンプの配置では、バンプ数が少ない領域にバンプ一つ当たりに加わる圧力が大きくなる。このため、図12(b)に示す断面図のように、実装基板−電力増幅器ICチップ間の距離が短くなる。

【0078】

したがって、電力増幅器用高周波ICチップ100全体に対して、同じ圧力を加えて加工した場合、アンダーフィルの厚さもバンプ数が少ない領域では薄くなる。バンプ配置が非対称となる構造によって、電力増幅器用高周波ICチップ100がフリップ実装される領域内120において 、アンダーフィルの影響による電気的特性を変化させることが可能となる。

【0079】

例えば、電力増幅器を図12(a)及び(b)に示す電力増幅器用高周波ICチップ100の左側と右側に配置した場合、左側はアンダーフィルの厚さが薄くなり寄生容量が増加し、右側はアンダーフィルの厚さが厚くなり寄生容量が低下する。このため、左側の電力増幅器の入力反射係数S11、出力反射係数S22が最低となるノッチ周波数は図8より大きく低下する。従って、右側の電力増幅器の入力反射係数S11、出力反射係数S22のノッチ周波数は左側の電力増幅器より変動量は小さくなる。

【0080】

従って本実施の形態においても、前記実施の形態1と同様、図10に示したようなフローチャートを用いてパラメータを算出し、実装条件を決定し、バンプ配置を調整する。

【0081】

次に、本発明の実施の形態3の変形例について説明する。

通常、電力増幅器ICチップのバンプ数を最小とする構成であるが、実装基板−電力増幅器ICチップ間の距離を調整するため、あるいは、電力増幅器用高周波ICチップ内がフリップチップ実装される領域内120において距離を非対称にするために、前記実施の形態3の無線装置用の電力増幅器用高周波ICチップ100の構成に加え、図13に示すように予備のバンプ115を配置すれば良い。

【0082】

予備のバンプ115は、例えば回路のグランド端子として使用すれば良く、回路特性の劣化を抑制できる。

【0083】

なお、本実施の形態では、図12(a)に示すように、バンプが外周に配置されているが、特に限定されない。例えば、図14のようにバンプが電力増幅器ICチップの実装基板への搭載面に一様に配置されている構造においても、電力増幅器用高周波ICチップ100がフリップチップ実装される領域内120において、実装基板との距離を非対称にするために、バンプ102の配置を非対称にすることで、同様の効果が得られる。

【0084】

本実施の形態では、バンプの非対称配置によって、電力増幅器用高周波ICチップ100がフリップ実装される領域内120において実装基板と距離を非対称にしたが、バンプを非対称に配置することなく、電力増幅器用高周波ICチップ100がフリップ実装される領域内120において、アンダーフィルの厚さを調整してもよい。

【0085】

例えば、バンプを介して電力増幅器用高周波ICチップ100を実装基板上に実装するリフロー工程における加圧力を調整してもよい。電力増幅器用高周波ICチップ100を実装する工程において、電力増幅器用高周波ICチップ100と実装基板の間のアンダーフィルの厚さが、電力増幅器用高周波ICチップ100がフリップ実装される領域内120において異なればよい。

【0086】

従って本実施の形態においても、実施の形態1と同様、図10に示したようなフローチャートを用いてパラメータを算出し、実装条件を決定できる。

【0087】

(実施の形態4)

次に本発明の実施の形態4について説明する。本発明の実施の形態1および2では、プロセスばらつき検出部110の一例として、トランジスタの閾値電圧Vthを検出するためにトランジスタ又はリングオシレーターを使用したが、本発明の実施の形態4では、PCM(ProcessControl Monitor)データをばらつき検出部の検出値として使用する。なお、PCMデータは、電力増幅器ICチップの製造における、チップの品質管理に用いるデータ(出来栄えを示すデータ)である。

【0088】

従来、半導体プロセスを用いてチップを製造する場合、チップの品質をモニタするために、同一のウェハ上に各種デバイスを搭載して、モニタしている。例えば、トランジスタの閾値電圧Vth、ドレイン電流Id、アルミニウム又は銅の配線の抵抗値、ポリシリコンの抵抗値である。なお、閾値電圧Vthは、例えば、下限をFF、上限をSS、中心をTTとして表現され、PCMデータとして管理されている。

【0089】

図15にチップの構成を示す。増幅器用高周波ICチップ100上に主回路101と、モニタ部Mとが形成されており、モニタ部Mに例えばポリシリコン抵抗31が形成されている。ポリシリコン抵抗31は、両端の電圧および電流が測定可能であり、抵抗値が算出できる。

【0090】

PCMデータのうち、ポリシリコン抵抗31の抵抗値を使用し、抵抗値が大きい場合は、パターン幅が小さくなるプロセスばらつきが生じていると判断できる。

【0091】

つまり、PCMデータを用いることで、プロセスばらつきをモニタでき、実施の形態1と同様にモニタした数値を用いて、アンダーフィルのパラメータが算出できる。このため、実装に用いるアンダーフィルのパラメータを調整することで、プロセスばらつきを補償できる。

【0092】

これにより、プロセスばらつき及びアンダーフィルの影響があっても所望の回路特性を得ることが可能となる。

【0093】

また、実施の形態4では、電力増幅器用高周波ICチップ100毎にモニタ部Mを形成したが、ウェハ毎Wにモニタ部Mを形成してもよい。

この方法は、ウェハ毎に少なくとも一つのプロセスばらつき検出部を有するとともに、主回路を構成する素子部を備えた複数の高周波ICチップ形成部を有するウェハを製造する工程と、前記プロセスばらつき検出部を用いてプロセスばらつきを検出する工程と、前記ウェハを複数の高周波ICチップに分割する工程と、前記検出する工程において検出されたデータに基づいてアンダーフィルのパラメータを調整する工程と、前記調整する工程において得られた前記パラメータを有するアンダーフィルを充填して、実装基板上に前記高周波ICチップを実装する工程と、を含む。

すなわち、図16に示すように、ウェハW上の所定位置に、例えば、電力増幅器用高周波ICチップ100を配列した素子部500と、モニタ部Mとが形成されており、モニタ部Mに例えばポリシリコン抵抗が形成されている。なお、ポリシリコン抵抗は、両端の電圧および電流が測定可能であるため、抵抗値が算出できる。

【0094】

以上より、実施形態1と同様に、PCMデータを用いてモニタしたプロセスばらつきの値を用いて、アンダーフィルのパラメータを算出し、算出したパラメータのアンダーフィルを充填することで、プロセスばらつき及びアンダーフィルの影響があっても所望の回路特性を得ることが可能となる。

【0095】

また、実施の形態4の無線装置とは異なり、電力増幅器用高周波ICチップ100にはモニタ部及びばらつき検出部を形成していないため、チップ面積の増大を抑制できる。

【0096】

以上のように、マイクロ波・ミリ波帯の高周波回路に対応した電力増幅器用高周波ICチップを実装基板にフリップチップ実装した無線装置において、プロセスばらつき検出部において、電力増幅器用高周波ICチップの製造におけるプロセスばらつきによる回路特性の変動量をモニタし、モニタした回路特性の変動量を用いて、アンダーフィルのパラメータを算出し、算出したパラメータに対応する材料または比誘電率のアンダーフィルを充填することによって、プロセスばらつき及びアンダーフィルの影響による周波数特性変動を抑制し、所望の回路特性が得られる無線装置を提供できる。

【0097】

特に、ミリ波帯を用いて無線通信する無線装置では、信号の周波数が高くアンダーフィルの影響が大きいため、より大きな効果が得られる。

【0098】

つまり、本発明においては、プロセスばらつき検出部を高周波ICチップ内に持つことは必須ではない。つまり、主回路を構成する素子部を備えた高周波ICチップを製造する工程と、プロセスばらつき検出部を用いて前記高周波ICチップのプロセスばらつきを検出する工程と、前記検出する工程において検出されたデータに基づいてアンダーフィルのパラメータを調整する工程と、前記調整する工程において得られた前記パラメータを有するアンダーフィルを充填して、実装基板上に前記高周波ICチップを実装する工程と、を含む無線装置の製造方法を用いても良い。

【産業上の利用可能性】

【0099】

以上説明してきたように、本発明によれば、高周波、特にマイクロ波帯・ミリ波帯を用いて無線通信する無線装置において、高周波特性に優れた半導体装置を提供できる。

【符号の説明】

【0100】

100 高周波ICチップ(電力増幅器用高周波ICチップ)

101 主回路

110 プロセスばらつき検出部

102 バンプ

103 入力端子

104 出力端子

105 実装基板

106 アンダーフィル

500 素子部

501 電力増幅用のトランジスタ

502 入力端子

503 出力端子

504、505 直流阻止用容量

506、507 入力整合用の伝送線路

508、509 主回路を構成する素子部

510 ゲート電圧端子

511 ドレイン電圧端子

【技術分野】

【0001】

本発明は、無線装置およびその製造方法に係り、特に高周波回路を備えた無線装置に関する。

【背景技術】

【0002】

主にマイクロ波、ミリ波帯では、高周波ICチップを、例えば、金(Au)、又は、半田のバンプを用いて実装基板に実装するフリップチップ実装が広く用いられている。フリップチップ実装では、実装基板と高周波ICチップとを短距離(最短)によって接続できるので、接続間での損失を小さくできる。

【0003】

一例を図17に従って説明する。モジュールの母体基板である実装基板1として、例えばセラミック基板を用い、入出力端子2、3に、例えば、高周波ICチップとして、増幅器のMMIC(モノリシックマイクロ波集積回路)チップ4の回路5をバンプ6によって接続する。さらに、接続の補強、又は、MMICチップ4のシールのために、実装基板1とMMICチップ4との間にアンダーフィル7として樹脂が充填される。

【0004】

しかしながら、上述したアンダーフィル7が充填されると、寄生容量が増大するために、MMICチップ4の特性が低周波数側にずれ、更に、利得が下がる特性劣化が発生する。

【0005】

そこで、フリップチップ実装におけるアンダーフィルの影響を受けにくいマイクロ波・ミリ波回路装置が提案されている(特許文献1参照)。

【0006】

図18は、特許文献1に記載の従来例のフリップチップ実装したマイクロ波・ミリ波回路装置を示す図である。マイクロ波・ミリ波回路装置は、実装基板1に対して、対向配置されたMMICチップ4がフリップチップ実装されている。MMICチップ4は、内側に回路5を囲む絶縁体壁11を設け、外側にアンダーフィル7を施す。この形態によれば、回路5(主部)を囲んで絶縁体壁11が形成されているので、アンダーフィル7を施しても樹脂が回路5の下に入らず、回路の特性が変化することは少ない。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2000−269384号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、特許文献1に記載のフリップチップ実装したマイクロ波・ミリ波回路装置は、MMICチップ4が、内側に回路5を囲む絶縁体壁11を設け、外側にアンダーフィル7を施す必要がある。このため、特許文献1の構成ではMMICチップ4の回路5の下は空洞となっており、十分な実装強度を得るのは困難である。

【0009】

また、高周波ICチップの製造ばらつき(プロセスばらつき)によって高周波ICチップの特性がばらついた場合には、回路特性が変化し、モジュールとして性能が劣化する場合がある。

【0010】

つまり、フリップチップ実装における特性劣化は抑制できても、高周波ICチップのプロセスばらつきに起因する特性劣化は残り、モジュールとしての歩留まりが低下してしまうという課題がある。

【0011】

本発明は前記実情に鑑みてなされたもので、実装強度を確保し、更に、特性劣化を抑制した無線装置を提供することを目的とする。

【課題を解決するための手段】

【0012】

そこで本発明は、実装基板と、前記実装基板上にフリップチップ実装された高周波ICチップとを備え、前記高周波ICチップと前記実装基板との間にアンダーフィルが充填された無線装置であって、前記高周波ICチップは、主回路を構成する素子部と、前記高周波ICチップのプロセスばらつきを検出するプロセスばらつき検出部を具備し、前記充填されたアンダーフィルは、前記検出したプロセスばらつきに基づいて調整されたパラメータを有することを特徴とする。

【0013】

また本発明は、上記無線装置であって、前記プロセスばらつき検出部は前記素子部の一部として機能するものを含む。

【0014】

また本発明は、上記無線装置であって、前記プロセスばらつき検出部は、前記高周波ICチップ上において前記素子部とは分離されたものを含む。

【0015】

また本発明は、上記無線装置であって、前記プロセスばらつき検出部はトランジスタを用いて構成されたものを含む。

【0016】

また本発明は、上記無線装置であって、前記プロセスばらつき検出部はリングオシレーターを用いて構成されたものを含む。

【0017】

また本発明は、上記無線装置であって、前記アンダーフィルのパラメータはアンダーフィルとして充填する樹脂の比誘電率であるものを含む。

【0018】

また本発明は、上記無線装置であって、前記アンダーフィルのパラメータは前記高周波ICチップと前記実装基板間の距離であるものを含む。

【0019】

また本発明は、上記無線装置であって、前記高周波ICチップはバンプを介して前記実装基板と接続し、前記バンプは前記高周波ICチップ上において非対称に配置されているものを含む。

【0020】

また本発明は、上記無線装置であって、前記高周波ICチップと前記実装基板の間のアンダーフィルは、前記高周波ICチップをフリップチップ実装した領域内において厚さが異なるものを含む。

【0021】

また本発明は、上記無線装置であって、前記プロセスばらつき検出部はPCM(ProcessControl Monitor)データを用いるものを含む。

【0022】

また本発明は、主回路を構成する素子部と、プロセスばらつき検出部とを備えた高周波ICチップを製造する工程と、前記高周波ICチップの前記プロセスばらつき検出部を用いてプロセスばらつきを検出する工程と、前記検出する工程において検出されたデータに基づいてアンダーフィルのパラメータを調整する工程と、前記調整する工程において得られた前記パラメータを有するアンダーフィルを充填して、実装基板上に前記高周波ICチップを実装する工程と、を含むことを特徴とする。

【図面の簡単な説明】

【0023】

【図1】本発明の実施の形態1のマイクロ波・ミリ波回路に対応した電力増幅器を含む無線装置の説明図

【図2】本発明の実施の形態1のマイクロ波・ミリ波回路に対応した電力増幅器の等価回路図

【図3】電力増幅器におけるプロセスばらつき検出部を構成するMOSFETの等価回路図

【図4】閾値電圧Vthがプロセスばらつきによって変動した場合の電力増幅器の入力反射係数および、出力反射係数を示す図(アンダーフィルがない場合)

【図5】樹脂をアンダーフィルとして充填した場合の電力増幅器の入力反射係数および、出力反射係数を示す図(アンダーフィルがない場合/ある場合)

【図6】図3に示したMOSトランジスタのゲート電圧−ドレイン電流特性を示す図

【図7】樹脂の比誘電率Erに対する反射係数のノッチの周波数の変動量を示す図

【図8】実装基板と電力増幅器ICチップ間の距離に対するノッチ周波数の変動量を示す図

【図9】プロセスばらつき及びアンダーフィルの影響による変化に対する反射係数のノッチ周波数すなわち反射係数が最小となる周波数の変動の関係を示す図

【図10】プロセスばらつきに基づく回路特性の変動量を補償するためのアンダーフィルの選択を含む実装工程を示すフローチャートを示す図

【図11】本発明の実施の形態2の無線装置におけるプロセスばらつき検出部を示す図

【図12】本発明の実施の形態3における無線装置を示す図であり、(a)は電力増幅器ICチップを下方から見た図、(b)は、実装状態を示す断面図

【図13】本発明の実施の形態3における無線装置の電力増幅器ICチップの変形例

【図14】本発明の実施の形態3における無線装置の電力増幅器ICチップの変形例

【図15】本発明の実施の形態3における無線装置の電力増幅器ICチップの変形例

【図16】本発明の実施の形態4における無線装置の電力増幅器ICチップを形成するためのウェハの一例を示す図

【図17】従来例の無線装置を示す図

【図18】従来例のマイクロ波・ミリ波回路装置を示す図

【発明を実施するための形態】

【0024】

(実施の形態1)

図1に、本発明の実施の形態1としてマイクロ波・ミリ波回路に対応した電力増幅器を含む無線装置の構成の一例を示す。

【0025】

本実施の形態1の無線装置では、高周波ICチップとして電力増幅器用高周波ICチップ100を用いており、電力増幅器を構成する電力増幅器用高周波ICチップ100に対し、主回路101に加え、ばらつき検出回路を構成するプロセスばらつき検出部110を集積化している。

【0026】

図1は、本実施の形態1のプロセスばらつき検出部110を有する電力増幅器用高周波ICチップ100を搭載した無線装置の説明図である。図2は同電力増幅器用高周波ICチップ100の等価回路図である。図3は同電力増幅器用高周波ICチップにおけるプロセスばらつき検出部110を構成するMOSFETの等価回路図である。

【0027】

本発明に係る実施の形態1の電力増幅器用高周波ICチップについての説明に先立ち、マイクロ波・ミリ波回路に対応した電力増幅器用高周波ICチップの動作について説明する。電力増幅器用高周波ICチップ100の主回路101は一般的な回路であるが、本実施の形態では、図1及び図2に示すように、主回路101を構成する素子部500に、プロセスばらつき検出部110が集積化されている。

【0028】

図2に、本発明の実施の形態1のマイクロ波・ミリ波回路に対応した 電力増幅器用高周波ICチップの等価回路を示す。電力増幅器においては、主回路101を構成する素子部500の入力端子502に、直流阻止用容量504を設け、出力端子503に、直流阻止用容量505を設けている。

【0029】

電力増幅用のトランジスタ501のゲートGと入力端子502との間に入力整合用の伝送線路506、507が設けられており、ドレインDと出力端子503との間には、出力整合用の伝送線路508、509が設けられている。

【0030】

トランジスタ501用のゲート電圧端子510と電力増幅用のトランジスタ501のゲートGとの間に、入力整合用の伝送線路506、507が直列接続されている。また電力増幅用のトランジスタ501用のドレイン電圧端子511と電力増幅用のトランジスタ501のドレインDとの間に、出力整合用の伝送線路508、509が直列接続されている。

【0031】

入力信号Sinは入力端子502から直流阻止用容量504、伝送線路507を介してトランジスタ501のゲートGに入力される。ゲートGは伝送線路506、507を介してゲート電圧端子510に接続され、ゲート電圧Vgが印加される。トランジスタ501のソースSはグランドに接地される。

【0032】

トランジスタ501のドレインDは伝送線路509、508を介してドレイン電圧端子511に接続され、ドレイン電圧Vdが印加される。伝送線路509、508の接続点から直流阻止用容量505を介して出力端子503から出力信号Soutは出力される。電力増幅用のトランジスタ501には、ドレイン電流Idが流れ、トランジスタ501のソースSには、ソース端子501Sが設けられている。

【0033】

一般に、トランジスタは、プロセスばらつきによって閾値電圧Vthが変動し、閾値電圧Vthが低いとドレイン電流Idは増加し、閾値電圧Vthが高いとドレイン電流Idは減少する。また、トランジスタの最大動作周波数fmaxは、閾値電圧Vthが低いと増加し、閾値電圧Vthが高いと減少し、最大動作周波数fmaxが高い方がトランジスタの高周波特性が良好となる。

【0034】

従って、図3に示す、プロセスばらつき検出部を構成するMOSFETについても、プロセスばらつきによって閾値電圧Vthは変動し、閾値電圧Vthが低いとドレイン電流Id’は増加し、閾値電圧Vthが高いとドレイン電流Id’は減少する。

【0035】

図4は、閾値電圧Vthをパラメータにした電力増幅器用高周波ICチップ100の入力反射係数S11及び出力反射係数S22と周波数特性との関係を示すグラフである。なお、プロセスばらつきによって、閾値電圧Vthが変動している。縦軸は反射係数、横軸は周波数(GHZ)を示す。

【0036】

実線はプロセスばらつきがない場合の理想の閾値電圧であり、以後、閾値電圧Vthが中心の場合と記載し、波線はプロセスばらつきがあり、理想の閾値電圧よりも低い電圧として、閾値電圧Vthが低い場合と記載し、一点鎖線はプロセスばらつきがあり、理想の閾値電圧よりも高い電圧として、閾値電圧Vthが高い場合と記載する。

【0037】

図4では、反射係数S11と反射係数S22とを同じ軸を用いて表記しているが、入力反射係数S11と出力反射係数S22とは、異なる特性であってもよい。

【0038】

閾値電圧Vthが低いほどドレイン電流Idが増加し、ドレイン電流Idの増加によってトランジスタ501の寄生容量が増加する。

例えば、閾値電圧Vthが中心の場合に入力反射係数S11及び出力反射係数S22のノッチ、すなわち、反射係数が最も小さくなる位置が所望の周波数(ノッチ周波数)fcとなるように設計をしたとしても、プロセスばらつきとしてのトランジスタ501の寄生容量によって、図4に示すように閾値電圧Vthが低くなると、入力反射係数S11及び出力反射係数S22のノッチの位置が低周波数側にシフトする。

【0039】

図5は、アンダーフィル106の有無をパラメータとした電力増幅器用高周波ICチップ100の入力反射係数S11及び出力反射係数S22と周波数特性との関係を示すグラフである。図2の電力増幅器が搭載された電力増幅器ICチップ、すなわち電力増幅器用高周波ICチップを実装基板105にフリップチップ実装し、図17に示すように、電力増幅器ICチップと実装基板105の間に樹脂をアンダーフィル106(UL)として充填した場合と、充填しない場合とを示している。

【0040】

アンダーフィルとして使用される樹脂は、一般的には誘電体であるため、寄生容量が増加する。実線はアンダーフィル(UF)がない場合、波線はフリップチップ実装しアンダーフィル(UF)がある場合の反射係数S11、S22を示す。

【0041】

図5では、電力増幅用のトランジスタ501の閾値電圧Vthが中心であり、アンダーフィル(UF)がない状態において、反射係数S11、S22のノッチの位置が周波数fcであったとしても、アンダーフィルを充填すると、アンダーフィルの影響としての寄生容量によって、反射係数S11、S22のノッチの位置が低周波数側にシフトする。

【0042】

なお、図5では、アンダーフィルの比誘電率が3.3であり、図8に示す実装基板−電力増幅器ICチップ間の距離が20μm以上である。

【0043】

本発明は、以上の点に着目してなされたもので、本実施の形態1では、高周波回路を備えた無線装置において、フリップチップ実装におけるアンダーフィルによる影響及びプロセスばらつきによる周波数特性劣化の課題を解決するものである。

【0044】

この課題を解決するために、対象の電力増幅器ICチップにおいてプロセスばらつき検出部110を構成するトランジスタを用いてプロセスばらつきを検出する構成を持つ。そして、検出結果を補償する材質又は充填量の条件を満たすアンダーフィルを充填することで、所望の周波数特性を得る。

【0045】

ここで、本発明の実施の形態1の無線装置の説明に戻る。図1は、本発明の実施の形態1における無線装置の構成を示す図である。無線装置は、マイクロ波又はミリ波回路に対応した電力増幅器用高周波ICチップ100、バンプ102、入力端子103、出力端子104、実装基板105、アンダーフィル106、プロセスばらつき検出部110を有する。電力増幅器用高周波ICチップ100はバンプ102を介して実装基板105上の入出力端子103、104に接続され、電力増幅器用高周波ICチップ100と実装基板105との間に樹脂がアンダーフィル106として充填される。更に電力増幅器用高周波ICチップ100は、電力増幅器用高周波ICチップ100のプロセスばらつきを検出するプロセスばらつき検出部110を有する。

【0046】

図3にプロセスばらつき検出部110の一例であるMOSトランジスタの等価回路図を示す。図6に図3に示したMOSトランジスタのゲート電圧−ドレイン電流特性を示す。図3のプロセスばらつき検出部はMOSトランジスタを用いて構成される。一般的にトランジスタは図6に示すようなゲート電圧−ドレイン電流特性を示し、図3のゲート電圧Vg’が閾値電圧Vth’を超えるとドレイン電流Id’が流れる。図6に示すようなゲート電圧−ドレイン電流特性を測定することによって、プロセスばらつき検出部110を構成するMOSトランジスタの閾値電圧Vth’を得ることが可能となる。

【0047】

一方、図5に示すようにフリップ実装においてアンダーフィルとして樹脂を充填すると、反射係数のノッチの位置に対応する周波数(以後、ノッチ周波数と記載する)すなわち反射係数が最小となる周波数が低下する。ノッチ周波数の変動量は図7に示すように樹脂の比誘電率Erによっても変化する。

【0048】

図7は樹脂の比誘電率Erに対する反射係数S11、S22のノッチ周波数すなわち反射係数が最小となる周波数の変動量を示しており、比誘電率Erが大きくなると、寄生容量が大きくなり、ノッチ周波数は低下する。アンダーフィルとして充填する樹脂の材料、又は、配合を変えることによって比誘電率が変わり、ノッチ周波数の変動量を調整できる。

【0049】

図8に、図1の実装基板105と電力増幅器用高周波ICチップ100との間の距離に対するノッチ周波数の変動量を示す。実装基板105と電力増幅器用高周波ICチップ100との間の距離が近いと、寄生容量が大きくなりノッチ周波数は変動量が大きい。

【0050】

実装基板105と電力増幅器用高周波ICチップ100との間の距離が遠くなると、距離に対する寄生容量の値は一定になりノッチ周波数の変動量は一定になる。ノッチ周波数の変動量が実装基板105−電力増幅器用高周波ICチップ100間の距離に比例する実装基板105−電力増幅器用高周波ICチップ100間の距離を距離Aとすると、距離Aを変化させることによってノッチ周波数の変動量を制御できる。例えば、アンダーフィルの充填量を調整することで、ノッチ周波数の変動量を制御できる。

【0051】

また、電力増幅器用高周波ICチップ100を実装基板105にフリップチップ実装する場合、電力増幅器用高周波ICチップ100の上方から圧力を加えて加工するが、上方からの圧力を変えることによって距離Aを変化できる。

【0052】

図9に、プロセスばらつき及びアンダーフィルの影響による変動に対する入力反射係数S11及び出力反射係数S22とノッチ周波数の変動との関係を示す。

【0053】

ここで、プロセスばらつきによる変化とは、トランジスタの閾値電圧Vthによる変化である。また、アンダーフィルの影響による変化とは、アンダーフィルの比誘電率Erによる変化と、実装基板105−電力増幅器用高周波ICチップ100間の距離に比例する実装基板105−電力増幅器用高周波ICチップ100間の距離Aによる変化と、のいずれかである。

【0054】

図9のノッチ周波数fcは、図4および図5と同様にMOSトランジスタの閾値電圧Vthが中心であり、アンダーフィル(UF)がない場合の入力反射係数S11及び出力反射係数S22のノッチの位置である。プロセスばらつきによって、ノッチ周波数は範囲Xにおいて変化し、上限・下限をそれぞれfxh、fxlとする。また、アンダーフィルの影響によって、ノッチ周波数は範囲Yにおいて変化し、上限・下限をそれぞれfyh、fylとする。

【0055】

ここで、アンダーフィルがない場合のノッチ周波数fcとアンダーフィルの影響によるノッチ周波数の上限fyhは等しい。プロセスばらつきとアンダーフィルの影響による変動量は、fylからfxhの範囲となり、所望の周波数ftがこの範囲に入れば良い。プロセスばらつきによる周波数の変動量をdfx、アンダーフィルの影響による周波数の変動量をdfyとすると、両方の影響を受けた後の周波数fzはfz=fc+dfx+dfyとなり、周波数fzを所望の周波数ftとすれば良い。

【0056】

以下、電力増幅器用高周波ICチップ100を搭載した無線装置の製造方法について説明する。まず、プロセスばらつきに基づく特性変動を補償するためのアンダーフィルの選択を含む実装工程を示すフローチャートを、図10に示す。

【0057】

電力増幅器用高周波ICチップ100を製造し(ステップS1001)、電力増幅器用高周波ICチップ100のプロセスばらつきをモニタする(ステップS1002)。ここで、例えばプロセスばらつきは、トランジスタの閾値電圧Vthを用いる。

【0058】

次に、モニタしたプロセスばらつきを用いて、回路特性の変動量を算出する(ステップS1003)。ここで、例えば回路特性は電力増幅器の入力反射係数S11及び出力反射係数S22とする。

【0059】

次に、算出した回路特性の変動分から所望の回路特性になるアンダーフィルの影響での変動量を決定する(ステップS1004)。最後に決定したアンダーフィルの影響での変動量に基づいてフリップチップ実装する(ステップS1005)。ここで、例えば、所望の回路特性を得るために必要なアンダーフィルの選択については、ステップS1005において決定されたアンダーフィルの影響での変動量に基づいて、樹脂の比誘電率の変更、又は、実装基板−電力増幅器用高周波ICチップ100間の距離の制御によって実行される。

【0060】

例えば、ステップS1002によって得られたプロセスばらつきに起因するトランジスタの閾値電圧をVthsとする。トランジスタの閾値電圧Vthが中心であるノッチ周波数fcに対して、プロセスばらつきによるノッチ周波数の変動量(dfx)を図4の入力反射係数S11及び出力反射係数S22を用いて算出する。

【0061】

次に、ノッチ周波数の変動量dfxを用いて、ノッチ周波数が所望の周波数ftとなるように、図7の結果に基づいてアンダーフィルの比誘電率Erの材料を選択する。

【0062】

プロセスばらつきによるノッチ周波数の変動量dfxを打ち消すように、アンダーフィルによるノッチ周波数の変動量(dfy)を決定し、決定した変動量dfyに対応する非誘電率Erの材料を選定する。あるいは、決定した変動量dfyに対応する実装基板105−電力増幅器用高周波ICチップ100間の距離を決定する。

【0063】

以上より、図10に示すフローチャートを用いて実装条件を決定することによって、プロセスばらつきによる特性の変動とアンダーフィルによる影響の変動が発生しても、回路特性を所望の特性に調整できる。

【0064】

つまり、プロセスばらつき検出部110において高周波ICチップのプロセスばらつきによる回路特性の変動量をモニタし、モニタした回路特性の変動量を用いて、アンダーフィルのパラメータを算出し、算出したパラメータのアンダーフィルを充填する。この構成によって、プロセスばらつき及びアンダーフィルの影響があっても、所望の回路特性が得られる。

【0065】

なお、本実施の形態では、プロセスばらつき検出部110としてトランジスタの閾値電圧Vthをモニタするとしたが、特にこれに限定されない。例えば、抵抗の抵抗値でも良いし、インダクタのインダクタンス値でも良いし、容量のキャパシタンス値でも良い。なお、抵抗は、例えば、ポリシリコン抵抗を用いることが出来る。

【0066】

また、実施の形態1では、プロセスばらつき検出部110は、主回路101を構成するMOSトランジスタ501とは別途独立して、MOSトランジスタを用いて分離形成した。

なお、変形例として、主回路101を構成するMOSトランジスタ501をばらつき検出回路(プロセスばらつき検出部)と兼用して用いることも可能である。

【0067】

他部については、実施の形態1の無線装置と同様に形成すればよい。これにより、チップの大型化を招くことなく、信頼性の高いプロセスばらつき検出およびプロセスばらつき補償が可能となる。

【0068】

また、プロセスばらつき以外にも、例えば、周辺回路との関係において容量調整をする目的であっても、アンダーフィルのパラメータを調整できる。

【0069】

(実施の形態2)

次に、ばらつき検出回路の回路構成を変更した実施の形態について説明する。

【0070】

本実施の形態では、ばらつき検出回路を構成するプロセスばらつき検出部110として、MOSFETに代えて図11に示すリングオシレーターを用いる。他の構成については実施の形態1と同様であるので、ここでの説明は省略する。

【0071】

本実施の形態においても、プロセスばらつき検出部110のゲート電圧−ドレイン電流特性を測定することにより、閾値電圧Vthの変動量を検出する。そして、検出した閾値電圧Vthの変動量に応じて、実装に用いられるアンダーフィルのパラメータを決定する。つまりプロセスばらつき検出部110によって、MOSトランジスタの閾値電圧Vthをモニタすることにより、図4に示した電圧増幅器の入力反射係数S11、出力反射係数S22のノッチの位置(ノッチ周波数)を推測できる。

【0072】

図11に示すように、リングオシレーターは、奇数個のインバータ121〜125が直列接続されてなり、出力側のインバータ125から出力される出力信号が入力側のインバータ121の入力へフィードバックされる。リングオシレーターのインバータ121に電源電圧を供給すると、インバータの動作遅延時間に依存する周波数において発振し、出力端子126から出力される。

【0073】

図11のリングオシレーターにおいて、インバータの動作遅延時間はプロセスばらつきによって変化する。例えば、トランジスタの閾値電圧Vthがプロセスばらつきによって低くなると、インバータの動作遅延時間が短くなり、リングオシレーターの発振周波数が高くなる。反対にトランジスタの閾値電圧Vthがプロセスばらつきによって高くなると、インバータの動作遅延時間が長くなり、リングオシレーターの発振周波数が低くなる。

【0074】

リングオシレーターの発振周波数をモニタすることによって、トランジスタの閾値電圧Vthを得ることが可能となる。プロセスばらつき検出部110によって、トランジスタの閾値電圧Vthをモニタすることによって、例えば図2に示した電圧増幅器の入力反射係数S11、出力反射係数S22のノッチの位置(ノッチ周波数)を推測できる。

【0075】

従って本実施の形態においても、実施の形態1と同様、図10に示したフローチャートを用いてパラメータを算出し、プロセスばらつきを補償するための実装条件を決定する。

【0076】

(実施の形態3)

次に本発明の実施の形態3について説明する。図12(a)は、本発明の実施の形態3における無線装置を構成する電力増幅器ICチップを下方から見た図である。図12(a)は、電力増幅器用高周波ICチップ100の下面にバンプ102が非対称に配置されている。

【0077】

電力増幅器用高周波ICチップ100を実装基板105にフリップチップ実装する場合、チップの上方から圧力を加えて加工するが、図12(a)に示すように、非対称なバンプの配置では、バンプ数が少ない領域にバンプ一つ当たりに加わる圧力が大きくなる。このため、図12(b)に示す断面図のように、実装基板−電力増幅器ICチップ間の距離が短くなる。

【0078】

したがって、電力増幅器用高周波ICチップ100全体に対して、同じ圧力を加えて加工した場合、アンダーフィルの厚さもバンプ数が少ない領域では薄くなる。バンプ配置が非対称となる構造によって、電力増幅器用高周波ICチップ100がフリップ実装される領域内120において 、アンダーフィルの影響による電気的特性を変化させることが可能となる。

【0079】

例えば、電力増幅器を図12(a)及び(b)に示す電力増幅器用高周波ICチップ100の左側と右側に配置した場合、左側はアンダーフィルの厚さが薄くなり寄生容量が増加し、右側はアンダーフィルの厚さが厚くなり寄生容量が低下する。このため、左側の電力増幅器の入力反射係数S11、出力反射係数S22が最低となるノッチ周波数は図8より大きく低下する。従って、右側の電力増幅器の入力反射係数S11、出力反射係数S22のノッチ周波数は左側の電力増幅器より変動量は小さくなる。

【0080】

従って本実施の形態においても、前記実施の形態1と同様、図10に示したようなフローチャートを用いてパラメータを算出し、実装条件を決定し、バンプ配置を調整する。

【0081】

次に、本発明の実施の形態3の変形例について説明する。

通常、電力増幅器ICチップのバンプ数を最小とする構成であるが、実装基板−電力増幅器ICチップ間の距離を調整するため、あるいは、電力増幅器用高周波ICチップ内がフリップチップ実装される領域内120において距離を非対称にするために、前記実施の形態3の無線装置用の電力増幅器用高周波ICチップ100の構成に加え、図13に示すように予備のバンプ115を配置すれば良い。

【0082】

予備のバンプ115は、例えば回路のグランド端子として使用すれば良く、回路特性の劣化を抑制できる。

【0083】

なお、本実施の形態では、図12(a)に示すように、バンプが外周に配置されているが、特に限定されない。例えば、図14のようにバンプが電力増幅器ICチップの実装基板への搭載面に一様に配置されている構造においても、電力増幅器用高周波ICチップ100がフリップチップ実装される領域内120において、実装基板との距離を非対称にするために、バンプ102の配置を非対称にすることで、同様の効果が得られる。

【0084】

本実施の形態では、バンプの非対称配置によって、電力増幅器用高周波ICチップ100がフリップ実装される領域内120において実装基板と距離を非対称にしたが、バンプを非対称に配置することなく、電力増幅器用高周波ICチップ100がフリップ実装される領域内120において、アンダーフィルの厚さを調整してもよい。

【0085】

例えば、バンプを介して電力増幅器用高周波ICチップ100を実装基板上に実装するリフロー工程における加圧力を調整してもよい。電力増幅器用高周波ICチップ100を実装する工程において、電力増幅器用高周波ICチップ100と実装基板の間のアンダーフィルの厚さが、電力増幅器用高周波ICチップ100がフリップ実装される領域内120において異なればよい。

【0086】

従って本実施の形態においても、実施の形態1と同様、図10に示したようなフローチャートを用いてパラメータを算出し、実装条件を決定できる。

【0087】

(実施の形態4)

次に本発明の実施の形態4について説明する。本発明の実施の形態1および2では、プロセスばらつき検出部110の一例として、トランジスタの閾値電圧Vthを検出するためにトランジスタ又はリングオシレーターを使用したが、本発明の実施の形態4では、PCM(ProcessControl Monitor)データをばらつき検出部の検出値として使用する。なお、PCMデータは、電力増幅器ICチップの製造における、チップの品質管理に用いるデータ(出来栄えを示すデータ)である。

【0088】

従来、半導体プロセスを用いてチップを製造する場合、チップの品質をモニタするために、同一のウェハ上に各種デバイスを搭載して、モニタしている。例えば、トランジスタの閾値電圧Vth、ドレイン電流Id、アルミニウム又は銅の配線の抵抗値、ポリシリコンの抵抗値である。なお、閾値電圧Vthは、例えば、下限をFF、上限をSS、中心をTTとして表現され、PCMデータとして管理されている。

【0089】

図15にチップの構成を示す。増幅器用高周波ICチップ100上に主回路101と、モニタ部Mとが形成されており、モニタ部Mに例えばポリシリコン抵抗31が形成されている。ポリシリコン抵抗31は、両端の電圧および電流が測定可能であり、抵抗値が算出できる。

【0090】

PCMデータのうち、ポリシリコン抵抗31の抵抗値を使用し、抵抗値が大きい場合は、パターン幅が小さくなるプロセスばらつきが生じていると判断できる。

【0091】

つまり、PCMデータを用いることで、プロセスばらつきをモニタでき、実施の形態1と同様にモニタした数値を用いて、アンダーフィルのパラメータが算出できる。このため、実装に用いるアンダーフィルのパラメータを調整することで、プロセスばらつきを補償できる。

【0092】

これにより、プロセスばらつき及びアンダーフィルの影響があっても所望の回路特性を得ることが可能となる。

【0093】

また、実施の形態4では、電力増幅器用高周波ICチップ100毎にモニタ部Mを形成したが、ウェハ毎Wにモニタ部Mを形成してもよい。

この方法は、ウェハ毎に少なくとも一つのプロセスばらつき検出部を有するとともに、主回路を構成する素子部を備えた複数の高周波ICチップ形成部を有するウェハを製造する工程と、前記プロセスばらつき検出部を用いてプロセスばらつきを検出する工程と、前記ウェハを複数の高周波ICチップに分割する工程と、前記検出する工程において検出されたデータに基づいてアンダーフィルのパラメータを調整する工程と、前記調整する工程において得られた前記パラメータを有するアンダーフィルを充填して、実装基板上に前記高周波ICチップを実装する工程と、を含む。

すなわち、図16に示すように、ウェハW上の所定位置に、例えば、電力増幅器用高周波ICチップ100を配列した素子部500と、モニタ部Mとが形成されており、モニタ部Mに例えばポリシリコン抵抗が形成されている。なお、ポリシリコン抵抗は、両端の電圧および電流が測定可能であるため、抵抗値が算出できる。

【0094】

以上より、実施形態1と同様に、PCMデータを用いてモニタしたプロセスばらつきの値を用いて、アンダーフィルのパラメータを算出し、算出したパラメータのアンダーフィルを充填することで、プロセスばらつき及びアンダーフィルの影響があっても所望の回路特性を得ることが可能となる。

【0095】

また、実施の形態4の無線装置とは異なり、電力増幅器用高周波ICチップ100にはモニタ部及びばらつき検出部を形成していないため、チップ面積の増大を抑制できる。

【0096】

以上のように、マイクロ波・ミリ波帯の高周波回路に対応した電力増幅器用高周波ICチップを実装基板にフリップチップ実装した無線装置において、プロセスばらつき検出部において、電力増幅器用高周波ICチップの製造におけるプロセスばらつきによる回路特性の変動量をモニタし、モニタした回路特性の変動量を用いて、アンダーフィルのパラメータを算出し、算出したパラメータに対応する材料または比誘電率のアンダーフィルを充填することによって、プロセスばらつき及びアンダーフィルの影響による周波数特性変動を抑制し、所望の回路特性が得られる無線装置を提供できる。

【0097】

特に、ミリ波帯を用いて無線通信する無線装置では、信号の周波数が高くアンダーフィルの影響が大きいため、より大きな効果が得られる。

【0098】

つまり、本発明においては、プロセスばらつき検出部を高周波ICチップ内に持つことは必須ではない。つまり、主回路を構成する素子部を備えた高周波ICチップを製造する工程と、プロセスばらつき検出部を用いて前記高周波ICチップのプロセスばらつきを検出する工程と、前記検出する工程において検出されたデータに基づいてアンダーフィルのパラメータを調整する工程と、前記調整する工程において得られた前記パラメータを有するアンダーフィルを充填して、実装基板上に前記高周波ICチップを実装する工程と、を含む無線装置の製造方法を用いても良い。

【産業上の利用可能性】

【0099】

以上説明してきたように、本発明によれば、高周波、特にマイクロ波帯・ミリ波帯を用いて無線通信する無線装置において、高周波特性に優れた半導体装置を提供できる。

【符号の説明】

【0100】

100 高周波ICチップ(電力増幅器用高周波ICチップ)

101 主回路

110 プロセスばらつき検出部

102 バンプ

103 入力端子

104 出力端子

105 実装基板

106 アンダーフィル

500 素子部

501 電力増幅用のトランジスタ

502 入力端子

503 出力端子

504、505 直流阻止用容量

506、507 入力整合用の伝送線路

508、509 主回路を構成する素子部

510 ゲート電圧端子

511 ドレイン電圧端子

【特許請求の範囲】

【請求項1】

実装基板と、

前記実装基板上にフリップチップ実装された高周波ICチップと、を備え、

前記高周波ICチップと前記実装基板との間にアンダーフィルが充填された無線装置であって、

前記高周波ICチップは、主回路を構成する素子部と、前記高周波ICチップのプロセスばらつきを検出するプロセスばらつき検出部と、

を具備し、

前記充填されたアンダーフィルは、前記検出したプロセスばらつきに基づいて調整されたパラメータを有する

無線装置。

【請求項2】

請求項1に記載の無線装置であって、前記プロセスばらつき検出部は前記素子部の一部として機能する無線装置。

【請求項3】

請求項1に記載の無線装置であって、前記プロセスばらつき検出部は、前記高周波ICチップ上において、前記素子部とは分離された無線装置。

【請求項4】

請求項1乃至3のいずれか1項に記載の無線装置であって、

前記プロセスばらつき検出部はトランジスタを用いて構成された無線装置。

【請求項5】

請求項1乃至3のいずれか1項に記載の無線装置であって、

前記プロセスばらつき検出部は、リングオシレーターを用いて構成された無線装置。

【請求項6】

請求項1に記載の無線装置であって、

前記アンダーフィルのパラメータは、アンダーフィルとして充填する材料の比誘電率である無線装置。

【請求項7】

請求項1に記載の無線装置であって、

前記アンダーフィルのパラメータは前記高周波ICチップと前記実装基板間の距離である無線装置。

【請求項8】

請求項1に記載の無線装置であって、

前記高周波ICチップはバンプを介して前記実装基板と接続し、

前記バンプは、前記高周波ICチップ上において、非対称に配置されている無線装置。

【請求項9】

請求項1に記載の無線装置であって、

前記高周波ICチップと前記実装基板との間のアンダーフィルは、前記高周波ICチップをフリップチップ実装した領域内において厚さが異なる無線装置。

【請求項10】

請求項1に記載の無線装置であって、

前記プロセスばらつき検出部はPCM(Process Control Monitor)データを用いる無線装置。

【請求項11】

主回路を構成する素子部と、プロセスばらつき検出部とを備えた高周波ICチップを製造する工程と、

前記高周波ICチップの前記プロセスばらつき検出部を用いてプロセスばらつきを検出する工程と、

前記検出する工程において検出されたデータに基づいてアンダーフィルのパラメータを調整する工程と、

前記調整する工程において得られた前記パラメータを有するアンダーフィルを充填して、実装基板上に前記高周波ICチップを実装する工程と、を含む無線装置の製造方法。

【請求項1】

実装基板と、

前記実装基板上にフリップチップ実装された高周波ICチップと、を備え、

前記高周波ICチップと前記実装基板との間にアンダーフィルが充填された無線装置であって、

前記高周波ICチップは、主回路を構成する素子部と、前記高周波ICチップのプロセスばらつきを検出するプロセスばらつき検出部と、

を具備し、

前記充填されたアンダーフィルは、前記検出したプロセスばらつきに基づいて調整されたパラメータを有する

無線装置。

【請求項2】

請求項1に記載の無線装置であって、前記プロセスばらつき検出部は前記素子部の一部として機能する無線装置。

【請求項3】

請求項1に記載の無線装置であって、前記プロセスばらつき検出部は、前記高周波ICチップ上において、前記素子部とは分離された無線装置。

【請求項4】

請求項1乃至3のいずれか1項に記載の無線装置であって、

前記プロセスばらつき検出部はトランジスタを用いて構成された無線装置。

【請求項5】

請求項1乃至3のいずれか1項に記載の無線装置であって、

前記プロセスばらつき検出部は、リングオシレーターを用いて構成された無線装置。

【請求項6】

請求項1に記載の無線装置であって、

前記アンダーフィルのパラメータは、アンダーフィルとして充填する材料の比誘電率である無線装置。

【請求項7】

請求項1に記載の無線装置であって、

前記アンダーフィルのパラメータは前記高周波ICチップと前記実装基板間の距離である無線装置。

【請求項8】

請求項1に記載の無線装置であって、

前記高周波ICチップはバンプを介して前記実装基板と接続し、

前記バンプは、前記高周波ICチップ上において、非対称に配置されている無線装置。

【請求項9】

請求項1に記載の無線装置であって、

前記高周波ICチップと前記実装基板との間のアンダーフィルは、前記高周波ICチップをフリップチップ実装した領域内において厚さが異なる無線装置。

【請求項10】

請求項1に記載の無線装置であって、

前記プロセスばらつき検出部はPCM(Process Control Monitor)データを用いる無線装置。

【請求項11】

主回路を構成する素子部と、プロセスばらつき検出部とを備えた高周波ICチップを製造する工程と、

前記高周波ICチップの前記プロセスばらつき検出部を用いてプロセスばらつきを検出する工程と、

前記検出する工程において検出されたデータに基づいてアンダーフィルのパラメータを調整する工程と、

前記調整する工程において得られた前記パラメータを有するアンダーフィルを充填して、実装基板上に前記高周波ICチップを実装する工程と、を含む無線装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2013−102356(P2013−102356A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2011−244970(P2011−244970)

【出願日】平成23年11月8日(2011.11.8)

【国等の委託研究の成果に係る記載事項】(出願人による申告)「平成23年度、総務省、超高速近距離無線伝送技術等の研究開発の委託事業、産業技術力強化法第19条の適用を受ける特許出願」

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願日】平成23年11月8日(2011.11.8)

【国等の委託研究の成果に係る記載事項】(出願人による申告)「平成23年度、総務省、超高速近距離無線伝送技術等の研究開発の委託事業、産業技術力強化法第19条の適用を受ける特許出願」

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]