物理乱数生成装置及び物理乱数生成回路

【課題】方法で真正な乱数を簡単に取り出すことができる物理乱数生成装置及び物理乱数生成回路を提供する。

【解決手段】出力レベルがランダムに変動するノイズ源からの信号を所定の周期でサンプリングしてディジタル値に変換するA/D変換手段と、前記A/D変換手段によってサンプリングされたディジタル値を所定期間にわたり保持するディジタル値保持手段と、前記ディジタル値保持手段に保持されている値と、その後にサンプリングされたディジタル値との差を算出する演算手段と、前記演算手段による演算結果を乱数値として出力する出力手段とを具備する。ノイズ源から出力される信号をあるタイミングでサンプリングしたときに、その値から前回サンプリングされた値を差し引いた値が乱数値として出力され、真正度の高い乱数が得られる。

【解決手段】出力レベルがランダムに変動するノイズ源からの信号を所定の周期でサンプリングしてディジタル値に変換するA/D変換手段と、前記A/D変換手段によってサンプリングされたディジタル値を所定期間にわたり保持するディジタル値保持手段と、前記ディジタル値保持手段に保持されている値と、その後にサンプリングされたディジタル値との差を算出する演算手段と、前記演算手段による演算結果を乱数値として出力する出力手段とを具備する。ノイズ源から出力される信号をあるタイミングでサンプリングしたときに、その値から前回サンプリングされた値を差し引いた値が乱数値として出力され、真正度の高い乱数が得られる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ランダムに発生する物理現象に基づいて乱数を生成する物理乱数生成装置及び物理乱数生成回路に関する。

【背景技術】

【0002】

自然現象に基づいて物理乱数を取り出す方法の一つに、抵抗、ダイオード等の半導体、あるいは導体を熱雑音発生素子として用いる方法が知られている。これらの熱雑音発生素子において発生する熱雑音信号は、発生頻度、振幅ともランダムであるため、この熱雑音に基づいて物理乱数を取り出すことができる。例えば、熱雑音発生素子から発生される信号を一定周期でサンプリングしてA/D変換すれば、得られたディジタル値は、熱雑音発生素子の内部においてランダムに起こる事象に起因した乱数と考えることができる。

【0003】

上記の考え方に基づいて物理乱数を生成する装置及び方法が、特許文献1に記載されている。この文献記載の方法及び装置は、ノイズ源からのノイズ信号から、コンデンサなどによる交流結合によって、ノイズ信号の直流成分を通過させないようにしつつ増幅を行うことを特徴としている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特許第2980576号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上記のようにして得られるディジタル値は、熱雑音発生素子の内部で起こったランダムな事象に起因するものの、これを電気信号として取り出す場合には、ある時点における電圧値又は電流値は、その直前の電圧値又は電流値の影響を全く受けていないとは言えない。例えば、熱雑音発生素子から出力され、これを増幅した電圧信号を一定のサンプリング周期でサンプリングした場合には、あるタイミングでサンプリングした値がその一つ前にサンプリングされた値に全く影響を受けていないとは言えないので、このようにして得られたディジタル値をそのまま出力しただけでは、真正な乱数とは言えない可能性がある。

【0006】

また、上記特許文献1のように、交流結合を介在させるのは、ノイズ信号から直流成分を除去して信号の振幅の中心点をゼロに移動させることを目的としている。しかしながら、このように信号振幅の中心点をゼロに移動させるだけでは直前の影響を除去することはできず、交流結合を通過したあとのノイズ信号においても信号の各時点における電圧値又は電流値にはやはりその直前の影響が残る。

【0007】

さらに、得られたディジタル値を人為的に加工して、その加工後の値を乱数値とした場合、その頻度分布が正規分布から外れるあるいは規則的な乱れが生じるなどというように乱数性自体に問題が生じることもある。

【0008】

本発明は、新たな方法で真正な乱数を簡単に取り出すことができる物理乱数生成装置及び物理乱数生成回路を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記の目的を達成するために、第1の発明に係る物理乱数生成装置は、出力レベルがランダムに変動するノイズ源からの信号を所定の周期でサンプリングしてディジタル値に変換するA/D変換手段と、前記A/D変換手段によってサンプリングされたディジタル値を所定期間にわたり保持するディジタル値保持手段と、前記ディジタル値保持手段に保持されている値と、その後にサンプリングされたディジタル値との差を算出する演算手段と、前記演算手段による演算結果を乱数値として出力する出力手段とを具備することを特徴とする。

【0010】

上記の目的を達成するために、第2の発明に係る物理乱数生成装置は、出力レベルがランダムに変動するノイズ源からの信号を所定の周期でサンプリングしてディジタル値に変換するA/D変換手段と、前記A/D変換手段によってサンプリングされたディジタル値を所定期間にわたり保持するディジタル値保持手段と、前記ディジタル値保持手段に保持されている一つ前にサンプリングされた値と、現時点でサンプリングされたディジタル値との差を算出する演算手段と、前記演算によって得られた差を所定の閾値と比較し、前記差が前記閾値を超えている期間に所定の信号を出力する比較手段と、前記比較手段から前記所定の信号が出力されている時間を計時しこれを乱数値として出力する計時手段とを具備することを特徴とする。

【0011】

上記の目的を達成するために、第3の発明に係る物理乱数生成回路は、ノイズ源と、第1のクロック信号によって開閉する第1のスイッチを介して、前記ノイズ源からの信号を入力されるアンプと、前記アンプの入力とグランドとの間に接続された第1のコンデンサと、前記アンプの出力に直列に接続された第2のコンデンサと、前記第2のコンデンサの前記アンプとは反対の側に接続され、第3のクロックによってサンプリング動作を行うA/Dコンバータと、前記A/Dコンバータの入力とグランドとの間に接続され、第2のクロック信号によって開閉する第2のスイッチとを含んでおり、前記第1、第3、第2の各スイッチがこの順番で所定期間閉じる動作を繰り返すよう前記第1、第2、第3のクロック信号を供給して、前記A/Dコンバータから乱数値を取り出すことを特徴とする。

【0012】

上記の目的を達成するために、第4の発明に係る物理乱数生成回路は、ノイズ源と、第1のクロック信号によって開閉する第1のスイッチを介して、前記ノイズ源からの信号を入力されるアンプと、前記アンプの入力とグランドとの間に接続された第1のコンデンサと、前記アンプの出力に直列に接続された第2のコンデンサと、前記第2のコンデンサの前記アンプとは反対の側に接続され、前記第2のコンデンサが接続された入力端子に入力される信号のレベルを所定の閾値と比較し、前記レベルが前記閾値を超えたときにその旨の信号を出力するコンパレータと、前記コンパレータの入力とグランドとの間に接続され、第2のクロック信号によって開閉する第2のスイッチとを含んでおり、前記コンパレータの入力とグランドとの間に接続され、第2のクロック信号によって開閉する第2のスイッチとを含んでおり、前記第1、第2の各スイッチがこの順番で所定期間閉じる動作を繰り返すよう前記第1、第2のクロック信号を供給し、前記コンパレータから信号が出力される期間を計時し、その時間値を乱数として値を取り出すことを特徴とする。

【発明の効果】

【0013】

上記の第1及び第3の発明によれば、ノイズ源から出力される信号をあるタイミングでサンプリングしたときに、その値から、前回サンプリングされた値を差し引いた値が乱数値として出力される。このため、ある時点においてサンプリングされた値が、前回サンプリングされた値の影響を受けていたとしても、この影響が排除されることになるので、このようにして得られる乱数値は、真正度の高い乱数となる。

【0014】

上記第2及び第4の発明によれば、ノイズ源から出力される信号をあるタイミングでサンプリングしたときに、その値から、前回サンプリングされた値を差し引いた値が所定の閾値を超えたときに、その超えている期間の時間の長さが乱数値として出力される。このため、ある時点においてサンプリングされた値が、前回サンプリングされた値の影響を受けていたとしても、この影響が排除されることになるので、このようにして得られる乱数値は、真正度の高い乱数となる。

【図面の簡単な説明】

【0015】

【図1】第1の実施形態に係る乱数生成を行うためのハードウェア構成を示したブロック図である。

【図2】図1に示したハードウェア上でソフトウェア的に乱数生成を実行するアルゴリズムを示したフローチャートである。

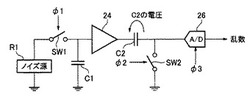

【図3】本発明の第2の実施形態であるハードウェア的に乱数を取得する回路のブロック図である。

【図4】図3に示したノイズ源R1の出力電圧からクロック信号φ1、φ2、φ3を制御して乱数値を取り出すタイミングを示したタイミングチャートである。

【図5】図4(a)に示したクロック信号φ1、φ2、φ3の点線で囲んだ部分だけを時間的に拡大して示した図である。

【図6】第3実施形態に係る、ソフトウェア的に乱数生成を実行するアルゴリズムを示したフローチャートである。

【図7】本発明の第4の実施形態である、ハードウェア的に乱数を取得する回路のブロック図である。

【図8】図7に示したノイズ源R1の出力電圧からクロック信号φ1、φ2、φ3を制御して乱数値を取り出すタイミングを示したタイミングチャートである。

【発明を実施するための形態】

【0016】

[第1実施形態]

以下に図面を参照して、本発明の実施の形態について説明する。前述のように、本発明の基本的な思想は、物理現象によってランダムに変化する電位(ノイズ電位)を一定周期でサンプリングし、そのサンプリングされた電位から、一つ前にサンプリングされた電位を差し引いて得られる差分を、乱数値として取得するという点にある。第1の実施形態を示した図1は、この考え方をコンピュータを使ってソフトウェア的に実現するためのブロック図であり、図2は、図1のブロック図で実現するアルゴリズムを示したフローチャートである。

【0017】

図1において、ノイズ源R1は、例えば熱雑音によって出力レベルがランダムに変動する微少電圧を出力する抵抗や半導体などからなる熱雑音素子である。この熱雑音素子R1からの出力は、アナログ/ディジタルコンバータ(A/Dコンバータ)20に入力される。なお、必要に応じて、熱雑音素子R1からの出力を増幅するためのアンプを、熱雑音素子R1とA/Dコンバータ20との間に挿入してもよい。A/Dコンバータ20は、R1からの出力電圧を一定周期でサンプリングし、ディジタル値に変換する。マイコン22は、A/Dコンバータ20が出力するディジタル値を後述のようにソフトウェア的に処理することで、乱数を出力する。なお、A/Dコンバータ20がサンプリングを行う周期は、ノイズ源R1からの出力される信号レベルの変動の周波数に応じた適切な値とする。

【0018】

マイコン22は、図2に示した処理を行う。まず、変数CRR、PRVを予め用意しておく。ここで、変数CRRは、現在時点においてサンプリングされたノイズの電圧値を示し、変数PRVは、一つ前にサンプリングされたノイズの電圧値を示している。最初にPRVに値「0」を代入する(ステップ101)。続いて、最初のノイズの電圧のアナログ値をA/Dコンバータ20でサンプリングしてディジタル値に変換し(S102)、このディジタル値を変数CRRに代入する(S103)。そして、CRRの値からPRVの値を引き算し、その結果を乱数値として出力する(S104)。最後にこれまでCRRに代入されていた値を変数PRVに代入する(S105)。

【0019】

図2において、当初におけるPRVの値は「0」であるから最初の乱数値は、そのときのCRRの値そのものであるが、次回以降は、現時点においてサンプリングされた電圧値から前回にサンプリングされた電圧値を差し引いた値が乱数値として出力される。すなわち、前回のサンプリング時点からの変化分だけを乱数値として利用する。このため、たとえ現時点における電圧値に、前回のランプリング時点における電圧の影響があったとしても、図2のような処理を行うことによって、今回のサンプリングにおいて想定される前回のランプリング時点における電圧の影響を排除することができ、完全に独立した事象に基づいて乱数を得ていることになる。したがって、得られる乱数の真正度が高く、より質の高い乱数が得られる。

【0020】

[第2実施形態]

図3は、本発明の第2の実施形態である、ハードウェア的に乱数を取得する回路のブロック図である。同図において、R1は、図1と同様、熱雑音によってランダムに変動する微少電圧を出力する抵抗や半導体などからなる熱雑音素子である。図3において、SW1、SW2はそれぞれ、不図示のクロック発生回路からのクロック信号φ1、φ2がハイ(H)レベルのときにオンとなり、ロー(L)レベルのときオフとなるスイッチである。C1、C2はコンデンサであり、24はゲイン(増幅度)が1倍のアンプであり、26は不図示のクロック信号φ3の立ち上がりで動作するA/Dコンバータである。

【0021】

φ1がHレベルのときにスイッチSW1はオンとなり、コンデンサC1の両端の電圧は、その時点におけるノイズ源R1の出力電圧と等しくなる。φ1がLレベルとなってスイッチSW1がオフになると、コンデンサC1は、スイッチSW1がオフとなった時点におけるノイズ源R1の電圧を保持する。すなわちC1の電圧は、クロック信号φ1の立ち下がりのタイミングでR1の電圧をサンプリングする。

【0022】

クロック信号φ2がHレベルのときはSW2がオンとなり、このときコンデンサC2はアンプ24の出力によって充電され、その両端間電圧はアンプ24の出力電圧に等しくなる。スイッチSW2がオフになると、コンデンサC2の両端間には、スイッチSW2が前回オンとなったときにアンプ24の出力によって充電されたときの電位差が保持される。したがって、このときA/Dコンバータ26の入力には、アンプ24の出力電圧からコンデンサC2の両端間の電圧を差し引いた電圧が入力される。この状態でクロック信号φ3が立ち上がると、A/Dコンバータ26は、この電圧値のサンプリングとA/D変換を行い、こうして得られるディジタル値を乱数値として出力する。

【0023】

図4は、図3に示したノイズ源R1の出力電圧からクロック信号φ1、φ2、φ3を制御して乱数値を取り出すタイミングを示したタイミングチャートであり、図5は、図4(a)に示したクロック信号φ1、φ2、φ3の点線で囲んだ部分だけを時間的に拡大して示した図である。図4において、(b)はノイズ源R1の出力電圧を示しており、ここに示すように、R1の出力レベルは物理現象に基づいて不規則に変動する。(c)は、(b)のように変動する電圧値に基づいて、ある時点のサンプリング電圧から1つ前のサンプリング電圧を差し引いた値が乱数値として出力される様子を示している。

【0024】

このように、ある時点のサンプリング電圧から1つ前のサンプリング電圧を差し引くことにより、たとえ現時点における電圧値に、前回のランプリング時点における電圧の影響があったとしても、今回のサンプリングにおいて想定される前回のランプリング時点における電圧の影響を排除することができ、完全に独立した事象に基づいて乱数を得ることができる。

【0025】

[第3実施形態]

これまでの実施形態では、サンプルされた電位から一つ前にサンプルされた電位を差し引いて得られる差分を乱数値として出力したが、本実施形態では、サンプルされた電位から一つ前にサンプルされた電位を差し引いて得られる差分が所定の閾値を超えたときに、その時点から次ぎに閾値を超えるまでの時間を計測し、この時間値を乱数値として出力する。図6は、この第3実施形態の考え方をマイコンなどでソフトウェア的に実現するアルゴリズムを示したフローチャートである。なお、ハードウェア的には図1と同様の構成となる。

【0026】

図6において、まず、変数CRR、PRV、THを予め用意しておく。ここで、変数CRRは、現在時点においてサンプリングされたノイズの電圧値を示し、変数PRVは、一つ前にサンプリングされたノイズの電圧値を示し、THは予め決定しておく閾値を示している。最初にPRVに値「0」を、またTHに予め決定した当該閾値を代入する(ステップ601)。続いて、最初のノイズの電圧のアナログ値をA/Dコンバータ20でサンプリングしてディジタル値に変換し(S602)、このディジタル値を変数CRRに代入する(S603)。そして、CRRの値からPRVの値を引き算し、その差が閾値THよりも大きいか否かを判定する(S604)。これが閾値THよりも小さい場合(S604でNoの場合)は「現象なし」とする(S605)。一方、閾値THよりも大きい場合(S605でYesの場合)は「現象あり」とする(S606)。この「現象あり」の場合には、「現象あり」のサンプリング期間が継続する数をカウントする(S607)。例えば、例えば、この「現象あり」の期間が10サンプリング期間継続し、次のサンプリング期間で「現象なし」となった場合には、値10を乱数として出力する。「最後にこれまでCRRに代入されていた値を変数PRVに代入する(S105)。

【0027】

図6に示すアルゴリズムを実行すると、「現象あり」のサンプリング期間同士は互いに独立した事象と考えることができ、また、最初にある時点のサンプリング電圧から1つ前のサンプリング電圧を差し引いているので、直前の影響は排除されており、したがってこれが継続するサンプリング期間の数は真正度の高い乱数となる。

【0028】

[第4実施形態]

図7は、本発明の第4の実施形態である、ハードウェア的に乱数を取得する回路のブロック図である。本実施形態の考え方は、基本的に第3実施形態のそれと同じである。図7において、図3の回路と同様の構成部分には同一の符号を付し、その説明を省略する。符号28はコンパレータ、符号30はコンパレータ26の閾値を設定するためのD/Aコンバータ、符号32はクロック信号φ3の立ち上がりで動作するDフリップ・フロップをそれぞれ示している。

【0029】

図7において、クロック信号φ1がHレベルのときにスイッチSW1はオンとなり、コンデンサC1の両端の電圧は、その時点におけるノイズ源R1の出力電圧と等しくなる。φ1がLレベルとなってスイッチSW1がオフになると、コンデンサC1は、スイッチSW1がオフとなった時点におけるノイズ源R1の電圧を保持する。すなわちC1の電圧は、クロック信号φ1の立ち下がりタイミングでR1の電圧をサンプリングする。

【0030】

クロック信号φ2がHレベルのときはSW2がオンとなり、このときコンデンサC2はアンプ24の出力によって充電され、その両端間電圧はアンプ24の出力電圧に等しくなる。スイッチSW2がオフになると、コンデンサC2の両端間には、スイッチSW2が前回オンとなったときにアンプ24の出力によって充電されたときの電位差が保持される。したがって、このときコンパレータ28の非反転(+)入力には、アンプ24の出力電圧からコンデンサC2の両端間の電圧を差し引いた電圧が入力される。コンパレータ28の反転(−)入力には、D/Aコンバータ30から閾値が入力されている。

【0031】

コンパレータ28は、非反転入力の値が反転入力の値よりも大きいときにHレベルの信号を出力し、これはDフリップ・フロップ32にデータ入力端子に入力される。Dフリップ・フロップ32は、クロック信号φ3が立ち下がる時点においてデータ入力端子に入力されている入力データを出力する。また、クロック信号φ2がHレベルになるとスイッチSW2はオンとなり、そのときコンデンサC2の両端間の電圧はアンプ24の出力電圧と同じくなる。

【0032】

図8は、図7に示したノイズ源R1の出力電圧からクロック信号φ1、φ2、φ3を制御して乱数値を取り出すタイミングを示したタイミングチャートである。φ1、φ2、φ3相互の時間的な関係は、図5と同様である。図8において、(a)〜(c)は、図4(a)〜(c)と同じである。図8(d)はコンパレータ28の出力信号を示しており、コンパレータ28の入力が閾値THよりも大きいときのみHレベルとなっている。この(d)に示す信号の時間幅は、R1の出力電圧が物理現象に基づいて不規則に変動することに起因して不規則な長さとなる。また、最初にある時点のサンプリング電圧から1つ前のサンプリング電圧を差し引いているので、直前の影響は排除されている。したがってこの時間幅(Hレベルとなっている連続するサンプリング時間)をカウントし、これを乱数として出力することにより、真正度の高い乱数が得られる。

【符号の説明】

【0033】

20、26、30 A/Dコンバータ

22 マイコン

24 アンプ

28 コンパレータ

32 Dフリップ・フロップ

【技術分野】

【0001】

本発明は、ランダムに発生する物理現象に基づいて乱数を生成する物理乱数生成装置及び物理乱数生成回路に関する。

【背景技術】

【0002】

自然現象に基づいて物理乱数を取り出す方法の一つに、抵抗、ダイオード等の半導体、あるいは導体を熱雑音発生素子として用いる方法が知られている。これらの熱雑音発生素子において発生する熱雑音信号は、発生頻度、振幅ともランダムであるため、この熱雑音に基づいて物理乱数を取り出すことができる。例えば、熱雑音発生素子から発生される信号を一定周期でサンプリングしてA/D変換すれば、得られたディジタル値は、熱雑音発生素子の内部においてランダムに起こる事象に起因した乱数と考えることができる。

【0003】

上記の考え方に基づいて物理乱数を生成する装置及び方法が、特許文献1に記載されている。この文献記載の方法及び装置は、ノイズ源からのノイズ信号から、コンデンサなどによる交流結合によって、ノイズ信号の直流成分を通過させないようにしつつ増幅を行うことを特徴としている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特許第2980576号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上記のようにして得られるディジタル値は、熱雑音発生素子の内部で起こったランダムな事象に起因するものの、これを電気信号として取り出す場合には、ある時点における電圧値又は電流値は、その直前の電圧値又は電流値の影響を全く受けていないとは言えない。例えば、熱雑音発生素子から出力され、これを増幅した電圧信号を一定のサンプリング周期でサンプリングした場合には、あるタイミングでサンプリングした値がその一つ前にサンプリングされた値に全く影響を受けていないとは言えないので、このようにして得られたディジタル値をそのまま出力しただけでは、真正な乱数とは言えない可能性がある。

【0006】

また、上記特許文献1のように、交流結合を介在させるのは、ノイズ信号から直流成分を除去して信号の振幅の中心点をゼロに移動させることを目的としている。しかしながら、このように信号振幅の中心点をゼロに移動させるだけでは直前の影響を除去することはできず、交流結合を通過したあとのノイズ信号においても信号の各時点における電圧値又は電流値にはやはりその直前の影響が残る。

【0007】

さらに、得られたディジタル値を人為的に加工して、その加工後の値を乱数値とした場合、その頻度分布が正規分布から外れるあるいは規則的な乱れが生じるなどというように乱数性自体に問題が生じることもある。

【0008】

本発明は、新たな方法で真正な乱数を簡単に取り出すことができる物理乱数生成装置及び物理乱数生成回路を提供することを目的とする。

【課題を解決するための手段】

【0009】

上記の目的を達成するために、第1の発明に係る物理乱数生成装置は、出力レベルがランダムに変動するノイズ源からの信号を所定の周期でサンプリングしてディジタル値に変換するA/D変換手段と、前記A/D変換手段によってサンプリングされたディジタル値を所定期間にわたり保持するディジタル値保持手段と、前記ディジタル値保持手段に保持されている値と、その後にサンプリングされたディジタル値との差を算出する演算手段と、前記演算手段による演算結果を乱数値として出力する出力手段とを具備することを特徴とする。

【0010】

上記の目的を達成するために、第2の発明に係る物理乱数生成装置は、出力レベルがランダムに変動するノイズ源からの信号を所定の周期でサンプリングしてディジタル値に変換するA/D変換手段と、前記A/D変換手段によってサンプリングされたディジタル値を所定期間にわたり保持するディジタル値保持手段と、前記ディジタル値保持手段に保持されている一つ前にサンプリングされた値と、現時点でサンプリングされたディジタル値との差を算出する演算手段と、前記演算によって得られた差を所定の閾値と比較し、前記差が前記閾値を超えている期間に所定の信号を出力する比較手段と、前記比較手段から前記所定の信号が出力されている時間を計時しこれを乱数値として出力する計時手段とを具備することを特徴とする。

【0011】

上記の目的を達成するために、第3の発明に係る物理乱数生成回路は、ノイズ源と、第1のクロック信号によって開閉する第1のスイッチを介して、前記ノイズ源からの信号を入力されるアンプと、前記アンプの入力とグランドとの間に接続された第1のコンデンサと、前記アンプの出力に直列に接続された第2のコンデンサと、前記第2のコンデンサの前記アンプとは反対の側に接続され、第3のクロックによってサンプリング動作を行うA/Dコンバータと、前記A/Dコンバータの入力とグランドとの間に接続され、第2のクロック信号によって開閉する第2のスイッチとを含んでおり、前記第1、第3、第2の各スイッチがこの順番で所定期間閉じる動作を繰り返すよう前記第1、第2、第3のクロック信号を供給して、前記A/Dコンバータから乱数値を取り出すことを特徴とする。

【0012】

上記の目的を達成するために、第4の発明に係る物理乱数生成回路は、ノイズ源と、第1のクロック信号によって開閉する第1のスイッチを介して、前記ノイズ源からの信号を入力されるアンプと、前記アンプの入力とグランドとの間に接続された第1のコンデンサと、前記アンプの出力に直列に接続された第2のコンデンサと、前記第2のコンデンサの前記アンプとは反対の側に接続され、前記第2のコンデンサが接続された入力端子に入力される信号のレベルを所定の閾値と比較し、前記レベルが前記閾値を超えたときにその旨の信号を出力するコンパレータと、前記コンパレータの入力とグランドとの間に接続され、第2のクロック信号によって開閉する第2のスイッチとを含んでおり、前記コンパレータの入力とグランドとの間に接続され、第2のクロック信号によって開閉する第2のスイッチとを含んでおり、前記第1、第2の各スイッチがこの順番で所定期間閉じる動作を繰り返すよう前記第1、第2のクロック信号を供給し、前記コンパレータから信号が出力される期間を計時し、その時間値を乱数として値を取り出すことを特徴とする。

【発明の効果】

【0013】

上記の第1及び第3の発明によれば、ノイズ源から出力される信号をあるタイミングでサンプリングしたときに、その値から、前回サンプリングされた値を差し引いた値が乱数値として出力される。このため、ある時点においてサンプリングされた値が、前回サンプリングされた値の影響を受けていたとしても、この影響が排除されることになるので、このようにして得られる乱数値は、真正度の高い乱数となる。

【0014】

上記第2及び第4の発明によれば、ノイズ源から出力される信号をあるタイミングでサンプリングしたときに、その値から、前回サンプリングされた値を差し引いた値が所定の閾値を超えたときに、その超えている期間の時間の長さが乱数値として出力される。このため、ある時点においてサンプリングされた値が、前回サンプリングされた値の影響を受けていたとしても、この影響が排除されることになるので、このようにして得られる乱数値は、真正度の高い乱数となる。

【図面の簡単な説明】

【0015】

【図1】第1の実施形態に係る乱数生成を行うためのハードウェア構成を示したブロック図である。

【図2】図1に示したハードウェア上でソフトウェア的に乱数生成を実行するアルゴリズムを示したフローチャートである。

【図3】本発明の第2の実施形態であるハードウェア的に乱数を取得する回路のブロック図である。

【図4】図3に示したノイズ源R1の出力電圧からクロック信号φ1、φ2、φ3を制御して乱数値を取り出すタイミングを示したタイミングチャートである。

【図5】図4(a)に示したクロック信号φ1、φ2、φ3の点線で囲んだ部分だけを時間的に拡大して示した図である。

【図6】第3実施形態に係る、ソフトウェア的に乱数生成を実行するアルゴリズムを示したフローチャートである。

【図7】本発明の第4の実施形態である、ハードウェア的に乱数を取得する回路のブロック図である。

【図8】図7に示したノイズ源R1の出力電圧からクロック信号φ1、φ2、φ3を制御して乱数値を取り出すタイミングを示したタイミングチャートである。

【発明を実施するための形態】

【0016】

[第1実施形態]

以下に図面を参照して、本発明の実施の形態について説明する。前述のように、本発明の基本的な思想は、物理現象によってランダムに変化する電位(ノイズ電位)を一定周期でサンプリングし、そのサンプリングされた電位から、一つ前にサンプリングされた電位を差し引いて得られる差分を、乱数値として取得するという点にある。第1の実施形態を示した図1は、この考え方をコンピュータを使ってソフトウェア的に実現するためのブロック図であり、図2は、図1のブロック図で実現するアルゴリズムを示したフローチャートである。

【0017】

図1において、ノイズ源R1は、例えば熱雑音によって出力レベルがランダムに変動する微少電圧を出力する抵抗や半導体などからなる熱雑音素子である。この熱雑音素子R1からの出力は、アナログ/ディジタルコンバータ(A/Dコンバータ)20に入力される。なお、必要に応じて、熱雑音素子R1からの出力を増幅するためのアンプを、熱雑音素子R1とA/Dコンバータ20との間に挿入してもよい。A/Dコンバータ20は、R1からの出力電圧を一定周期でサンプリングし、ディジタル値に変換する。マイコン22は、A/Dコンバータ20が出力するディジタル値を後述のようにソフトウェア的に処理することで、乱数を出力する。なお、A/Dコンバータ20がサンプリングを行う周期は、ノイズ源R1からの出力される信号レベルの変動の周波数に応じた適切な値とする。

【0018】

マイコン22は、図2に示した処理を行う。まず、変数CRR、PRVを予め用意しておく。ここで、変数CRRは、現在時点においてサンプリングされたノイズの電圧値を示し、変数PRVは、一つ前にサンプリングされたノイズの電圧値を示している。最初にPRVに値「0」を代入する(ステップ101)。続いて、最初のノイズの電圧のアナログ値をA/Dコンバータ20でサンプリングしてディジタル値に変換し(S102)、このディジタル値を変数CRRに代入する(S103)。そして、CRRの値からPRVの値を引き算し、その結果を乱数値として出力する(S104)。最後にこれまでCRRに代入されていた値を変数PRVに代入する(S105)。

【0019】

図2において、当初におけるPRVの値は「0」であるから最初の乱数値は、そのときのCRRの値そのものであるが、次回以降は、現時点においてサンプリングされた電圧値から前回にサンプリングされた電圧値を差し引いた値が乱数値として出力される。すなわち、前回のサンプリング時点からの変化分だけを乱数値として利用する。このため、たとえ現時点における電圧値に、前回のランプリング時点における電圧の影響があったとしても、図2のような処理を行うことによって、今回のサンプリングにおいて想定される前回のランプリング時点における電圧の影響を排除することができ、完全に独立した事象に基づいて乱数を得ていることになる。したがって、得られる乱数の真正度が高く、より質の高い乱数が得られる。

【0020】

[第2実施形態]

図3は、本発明の第2の実施形態である、ハードウェア的に乱数を取得する回路のブロック図である。同図において、R1は、図1と同様、熱雑音によってランダムに変動する微少電圧を出力する抵抗や半導体などからなる熱雑音素子である。図3において、SW1、SW2はそれぞれ、不図示のクロック発生回路からのクロック信号φ1、φ2がハイ(H)レベルのときにオンとなり、ロー(L)レベルのときオフとなるスイッチである。C1、C2はコンデンサであり、24はゲイン(増幅度)が1倍のアンプであり、26は不図示のクロック信号φ3の立ち上がりで動作するA/Dコンバータである。

【0021】

φ1がHレベルのときにスイッチSW1はオンとなり、コンデンサC1の両端の電圧は、その時点におけるノイズ源R1の出力電圧と等しくなる。φ1がLレベルとなってスイッチSW1がオフになると、コンデンサC1は、スイッチSW1がオフとなった時点におけるノイズ源R1の電圧を保持する。すなわちC1の電圧は、クロック信号φ1の立ち下がりのタイミングでR1の電圧をサンプリングする。

【0022】

クロック信号φ2がHレベルのときはSW2がオンとなり、このときコンデンサC2はアンプ24の出力によって充電され、その両端間電圧はアンプ24の出力電圧に等しくなる。スイッチSW2がオフになると、コンデンサC2の両端間には、スイッチSW2が前回オンとなったときにアンプ24の出力によって充電されたときの電位差が保持される。したがって、このときA/Dコンバータ26の入力には、アンプ24の出力電圧からコンデンサC2の両端間の電圧を差し引いた電圧が入力される。この状態でクロック信号φ3が立ち上がると、A/Dコンバータ26は、この電圧値のサンプリングとA/D変換を行い、こうして得られるディジタル値を乱数値として出力する。

【0023】

図4は、図3に示したノイズ源R1の出力電圧からクロック信号φ1、φ2、φ3を制御して乱数値を取り出すタイミングを示したタイミングチャートであり、図5は、図4(a)に示したクロック信号φ1、φ2、φ3の点線で囲んだ部分だけを時間的に拡大して示した図である。図4において、(b)はノイズ源R1の出力電圧を示しており、ここに示すように、R1の出力レベルは物理現象に基づいて不規則に変動する。(c)は、(b)のように変動する電圧値に基づいて、ある時点のサンプリング電圧から1つ前のサンプリング電圧を差し引いた値が乱数値として出力される様子を示している。

【0024】

このように、ある時点のサンプリング電圧から1つ前のサンプリング電圧を差し引くことにより、たとえ現時点における電圧値に、前回のランプリング時点における電圧の影響があったとしても、今回のサンプリングにおいて想定される前回のランプリング時点における電圧の影響を排除することができ、完全に独立した事象に基づいて乱数を得ることができる。

【0025】

[第3実施形態]

これまでの実施形態では、サンプルされた電位から一つ前にサンプルされた電位を差し引いて得られる差分を乱数値として出力したが、本実施形態では、サンプルされた電位から一つ前にサンプルされた電位を差し引いて得られる差分が所定の閾値を超えたときに、その時点から次ぎに閾値を超えるまでの時間を計測し、この時間値を乱数値として出力する。図6は、この第3実施形態の考え方をマイコンなどでソフトウェア的に実現するアルゴリズムを示したフローチャートである。なお、ハードウェア的には図1と同様の構成となる。

【0026】

図6において、まず、変数CRR、PRV、THを予め用意しておく。ここで、変数CRRは、現在時点においてサンプリングされたノイズの電圧値を示し、変数PRVは、一つ前にサンプリングされたノイズの電圧値を示し、THは予め決定しておく閾値を示している。最初にPRVに値「0」を、またTHに予め決定した当該閾値を代入する(ステップ601)。続いて、最初のノイズの電圧のアナログ値をA/Dコンバータ20でサンプリングしてディジタル値に変換し(S602)、このディジタル値を変数CRRに代入する(S603)。そして、CRRの値からPRVの値を引き算し、その差が閾値THよりも大きいか否かを判定する(S604)。これが閾値THよりも小さい場合(S604でNoの場合)は「現象なし」とする(S605)。一方、閾値THよりも大きい場合(S605でYesの場合)は「現象あり」とする(S606)。この「現象あり」の場合には、「現象あり」のサンプリング期間が継続する数をカウントする(S607)。例えば、例えば、この「現象あり」の期間が10サンプリング期間継続し、次のサンプリング期間で「現象なし」となった場合には、値10を乱数として出力する。「最後にこれまでCRRに代入されていた値を変数PRVに代入する(S105)。

【0027】

図6に示すアルゴリズムを実行すると、「現象あり」のサンプリング期間同士は互いに独立した事象と考えることができ、また、最初にある時点のサンプリング電圧から1つ前のサンプリング電圧を差し引いているので、直前の影響は排除されており、したがってこれが継続するサンプリング期間の数は真正度の高い乱数となる。

【0028】

[第4実施形態]

図7は、本発明の第4の実施形態である、ハードウェア的に乱数を取得する回路のブロック図である。本実施形態の考え方は、基本的に第3実施形態のそれと同じである。図7において、図3の回路と同様の構成部分には同一の符号を付し、その説明を省略する。符号28はコンパレータ、符号30はコンパレータ26の閾値を設定するためのD/Aコンバータ、符号32はクロック信号φ3の立ち上がりで動作するDフリップ・フロップをそれぞれ示している。

【0029】

図7において、クロック信号φ1がHレベルのときにスイッチSW1はオンとなり、コンデンサC1の両端の電圧は、その時点におけるノイズ源R1の出力電圧と等しくなる。φ1がLレベルとなってスイッチSW1がオフになると、コンデンサC1は、スイッチSW1がオフとなった時点におけるノイズ源R1の電圧を保持する。すなわちC1の電圧は、クロック信号φ1の立ち下がりタイミングでR1の電圧をサンプリングする。

【0030】

クロック信号φ2がHレベルのときはSW2がオンとなり、このときコンデンサC2はアンプ24の出力によって充電され、その両端間電圧はアンプ24の出力電圧に等しくなる。スイッチSW2がオフになると、コンデンサC2の両端間には、スイッチSW2が前回オンとなったときにアンプ24の出力によって充電されたときの電位差が保持される。したがって、このときコンパレータ28の非反転(+)入力には、アンプ24の出力電圧からコンデンサC2の両端間の電圧を差し引いた電圧が入力される。コンパレータ28の反転(−)入力には、D/Aコンバータ30から閾値が入力されている。

【0031】

コンパレータ28は、非反転入力の値が反転入力の値よりも大きいときにHレベルの信号を出力し、これはDフリップ・フロップ32にデータ入力端子に入力される。Dフリップ・フロップ32は、クロック信号φ3が立ち下がる時点においてデータ入力端子に入力されている入力データを出力する。また、クロック信号φ2がHレベルになるとスイッチSW2はオンとなり、そのときコンデンサC2の両端間の電圧はアンプ24の出力電圧と同じくなる。

【0032】

図8は、図7に示したノイズ源R1の出力電圧からクロック信号φ1、φ2、φ3を制御して乱数値を取り出すタイミングを示したタイミングチャートである。φ1、φ2、φ3相互の時間的な関係は、図5と同様である。図8において、(a)〜(c)は、図4(a)〜(c)と同じである。図8(d)はコンパレータ28の出力信号を示しており、コンパレータ28の入力が閾値THよりも大きいときのみHレベルとなっている。この(d)に示す信号の時間幅は、R1の出力電圧が物理現象に基づいて不規則に変動することに起因して不規則な長さとなる。また、最初にある時点のサンプリング電圧から1つ前のサンプリング電圧を差し引いているので、直前の影響は排除されている。したがってこの時間幅(Hレベルとなっている連続するサンプリング時間)をカウントし、これを乱数として出力することにより、真正度の高い乱数が得られる。

【符号の説明】

【0033】

20、26、30 A/Dコンバータ

22 マイコン

24 アンプ

28 コンパレータ

32 Dフリップ・フロップ

【特許請求の範囲】

【請求項1】

出力レベルがランダムに変動するノイズ源からの信号を所定の周期でサンプリングしてディジタル値に変換するA/D変換手段と、

前記A/D変換手段によってサンプリングされたディジタル値を所定期間にわたり保持するディジタル値保持手段と、

前記ディジタル値保持手段に保持されている値と、その後にサンプリングされたディジタル値との差を算出する演算手段と、

前記演算手段による演算結果を乱数値として出力する出力手段と、

を具備することを特徴とする物理乱数生成装置。

【請求項2】

ノイズ源と、

第1のクロック信号によって開閉する第1のスイッチを介して、前記ノイズ源からの信号を入力されるアンプと、

前記アンプの入力とグランドとの間に接続された第1のコンデンサと、

前記アンプの出力に直列に接続された第2のコンデンサと、

前記第2のコンデンサの前記アンプとは反対の側に接続され、第3のクロックによってサンプリング動作を行うA/Dコンバータと、

前記A/Dコンバータの入力とグランドとの間に接続され、第2のクロック信号によって開閉する第2のスイッチとを含んでおり、

前記第1、第3、第2の各スイッチがこの順番で所定期間閉じる動作を繰り返すよう前記第1、第2、第3のクロックを供給して、前記A/Dコンバータから乱数値を取り出すことを特徴とする物理乱数生成回路。

【請求項1】

出力レベルがランダムに変動するノイズ源からの信号を所定の周期でサンプリングしてディジタル値に変換するA/D変換手段と、

前記A/D変換手段によってサンプリングされたディジタル値を所定期間にわたり保持するディジタル値保持手段と、

前記ディジタル値保持手段に保持されている値と、その後にサンプリングされたディジタル値との差を算出する演算手段と、

前記演算手段による演算結果を乱数値として出力する出力手段と、

を具備することを特徴とする物理乱数生成装置。

【請求項2】

ノイズ源と、

第1のクロック信号によって開閉する第1のスイッチを介して、前記ノイズ源からの信号を入力されるアンプと、

前記アンプの入力とグランドとの間に接続された第1のコンデンサと、

前記アンプの出力に直列に接続された第2のコンデンサと、

前記第2のコンデンサの前記アンプとは反対の側に接続され、第3のクロックによってサンプリング動作を行うA/Dコンバータと、

前記A/Dコンバータの入力とグランドとの間に接続され、第2のクロック信号によって開閉する第2のスイッチとを含んでおり、

前記第1、第3、第2の各スイッチがこの順番で所定期間閉じる動作を繰り返すよう前記第1、第2、第3のクロックを供給して、前記A/Dコンバータから乱数値を取り出すことを特徴とする物理乱数生成回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2011−238268(P2011−238268A)

【公開日】平成23年11月24日(2011.11.24)

【国際特許分類】

【出願番号】特願2011−151900(P2011−151900)

【出願日】平成23年7月8日(2011.7.8)

【分割の表示】特願2006−335360(P2006−335360)の分割

【原出願日】平成18年12月13日(2006.12.13)

【出願人】(591107481)株式会社エルイーテック (37)

【出願人】(501462686)株式会社アイ・エイ・エス総合研究所 (4)

【Fターム(参考)】

【公開日】平成23年11月24日(2011.11.24)

【国際特許分類】

【出願日】平成23年7月8日(2011.7.8)

【分割の表示】特願2006−335360(P2006−335360)の分割

【原出願日】平成18年12月13日(2006.12.13)

【出願人】(591107481)株式会社エルイーテック (37)

【出願人】(501462686)株式会社アイ・エイ・エス総合研究所 (4)

【Fターム(参考)】

[ Back to top ]