物理量検知装置およびその駆動方法

【課題】A/D変換の周波数の増加を抑えつつ、出力画像の画質を向上させる固体撮像装置を提供する。

【解決手段】デジタルカメラ等の撮像装置に搭載される固体撮像装置において、1または複数の画素列ごとに、画素信号をA/D変換するランプ型A/D変換回路106を設ける。各ランプ型A/D変換回路106内に設けられたカラムカウンタ208に上位ビットを保持させ、1または複数個のラッチ308にクロック信号121を供給し、下位ビットを保持させることで、クロック周波数の増加を抑えながら高速・高精度のA/D変換を実現する。

【解決手段】デジタルカメラ等の撮像装置に搭載される固体撮像装置において、1または複数の画素列ごとに、画素信号をA/D変換するランプ型A/D変換回路106を設ける。各ランプ型A/D変換回路106内に設けられたカラムカウンタ208に上位ビットを保持させ、1または複数個のラッチ308にクロック信号121を供給し、下位ビットを保持させることで、クロック周波数の増加を抑えながら高速・高精度のA/D変換を実現する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、可視光、電磁波、アルファ線、およびベータ線などの粒子放射線などの物理量分布を検知するための2次元物理量検知装置に関し、より詳細には、行列状に配列された光電変換素子などのセンシング素子と、センシング素子からの出力信号を受けるA/D変換回路とが設けられた固体撮像素子、および撮像システムに関する。

【背景技術】

【0002】

従来、イメージセンサとして主流であったCCD(Charge Coupled Device;電荷結合素子)型センサ(以後、「CCDセンサ」と称する)に加えて、今日ではロジックLSIに使われている標準プロセスを活用したMOS型のイメージセンサ(以後、「MOSセンサ」と称する)が広く市場に出回るようになった。MOSセンサは、CCDセンサとは異なり、各種アナログ回路やデジタル回路を画素アレーと同一基板上に集積化できるという特徴を備えている。CCDセンサでは、アナログ信号増幅機能やA/D変換機能に特化したアナログフロントエンドプロセサ(以後、AFE)や、AFEの機能を備えたデジタル信号処理プロセッサ(以後、DSP)など、A/D変換機能を備えた別個のチップを画素アレーに接続することで、はじめてデジタル出力を得ることができる。これに対し、MOSセンサでは、画素アレーとともにA/D変換回路を同一チップ上に集積したものが既に製品化されている。

【0003】

MOSセンサが搭載するA/D変換回路には、AFEに広く搭載されている方式でもあるパイプライン型A/D変換方式や、1ライン分の画素データを同時並列的にA/D変換するカラム型A/D変換方式、さらには、すべての画素データを同時並列的にA/D変換する方式まで多岐にわたる方式の提案がある。カラム型A/D変換方式だけに絞っても、例えば、特許文献1〜3に示される構成のものがある。

【0004】

図16は、特許文献1に記載された第1の従来例に係るMOSセンサの構成を示す図である。

【0005】

第1の従来例に係るMOSセンサは、画素1101の列毎に、比較器1107およびデジタルメモリ1108で構成されたカラムA/D変換回路1106を備えている。バイナリカウンタ1104から出力されるバイナリ値は、D/A変換回路(以後、DACと称す)1105に入力される。DAC1105は、入力されたバイナリ値に応じたアナログランプ電圧(三角波)1122を生成し、このアナログランプ電圧1122を参照電位として比較器1107に出力する。バイナリカウンタ1104の出力はバイナリ→グレイコード変換器1115にも入力され、グレイコードに変換された後、各列のデジタルメモリ1108に分配される。各カラムA/D変換回路1106内の比較器1107のもう一方の入力部には、画素1101から読み出し信号線1103を介して画素信号が入力される。

【0006】

次に、第1の従来例に係るMOSセンサのA/D変換動作を説明する。まず、クロック生成回路1120から入力されるクロック信号1121に同期して、バイナリカウンタ1104がその初期値からカウントを開始すると同時に、DAC1105がアナログランプ電圧1122の生成を開始する。そして、各列の画素1101からの読み出し信号と、バイナリカウンタ1104の計数値と同期して変化する共通のアナログランプ電圧1122とが各列の比較器1107に入力される。これと並行して、バイナリカウンタ1104の計数値はバイナリ→グレイコード変換器1115でグレイコード計数値1124に変換され、デジタルメモリ1108に分配される。ある列の比較器1107への2つの入力信号の大小関係が入れ替わると、その比較器1107の出力信号が反転し、その列のデジタルメモリ1108はバイナリ→グレイコード変換器1115が出力するグレイコード計数値1124を保持する。比較器1107に入力されるアナログランプ電圧1122とデジタルメモリ1108に入力されるグレイコード計数値1124とはバイナリカウンタ1104を介して互いに同期しているので、以上の動作により、画素からの読み出し信号(アナログ信号)がデジタルメモリに保持された値(デジタル信号)にA/D変換されることとなる。

【0007】

このように、特許文献1に示された第1の従来例に係るMOSセンサでは、デジタルメモリに供給するデジタル値の表現方法としてグレイコードを用いている。これにより、グレイコード計数値1124は常にハミング距離が最小の「1」で遷移するため、クロックとして分配されるビット間にスキューがあっても、サンプリング誤差を小さくすることができる。また、グレイコードでは前後の計数値において、全ビット中のうち1つのビットしか反転しないため、ノイズが抑制されている。また、消費電力の低減も図ることができる。

【0008】

図17は、特許文献2や特許文献3に記載された第2の従来例に係るMOSセンサの構成を示す図である。同図を用いて、もう1つのカラム型A/D変換回路を含む第2の従来例に係るMOSセンサの構成を説明する。

【0009】

第2の従来例に係るMOSセンサは、画素1101の列毎に、比較器1107とカラムカウンタ1208とで構成されたカラムA/D変換回路1106を備えている。クロック生成回路1120はクロック信号1121をバイナリカウンタ1104だけでなく、カラムA/D変換回路1106内のカラムカウンタ1208にも供給する。バイナリカウンタ1104から出力されるバイナリ値はD/A変換回路(DAC)1105に入力され、DAC1105は入力されたバイナリ値に従ってアナログランプ電圧(三角波)1122を生成する。このアナログランプ電圧1122は参照電位として比較器1107に入力される。比較器1107のもう一方の入力には、画素1101から読み出し信号線1103を介して画素信号が入力される。

【0010】

図17に示す第2の従来例に係るMOSセンサでは、カラムA/D変換回路アレーに供給される信号は、クロック生成回路1120で生成されたクロック信号1121だけである。

【0011】

次に、第2の従来例に係るMOSセンサのA/D変換動作を説明する。

【0012】

まず、カラムA/D変換回路1106内のカラムカウンタ1208およびバイナリカウンタ1104を初期化信号(図示せず)により初期化し、DAC1105からアナログランプ電圧1122の初期値を比較器1107の一方の入力部に供給しておく。次に、選択した行の画素1101から画素信号を読み出し、比較器1107の他方の入力部に供給する。この状態で、バイナリカウンタ1104およびカラムカウンタ1208へのクロック信号1121の入力を開始することで、バイナリカウンタ1104がその初期値からカウントを開始する。すると、DAC1105もバイナリカウンタ1104の計数値に従ってアナログランプ電圧1122の生成を初期値から開始する。また、カラムA/D変換回路1106内のカラムカウンタ1208も、入力されるクロック信号1121の計数を開始する。

【0013】

次いで、ある列の比較器1107に入力される2つの信号の大小関係が入れ替わり、その比較器1107の出力信号が反転すると、その列のカラムカウンタ1208に入力されるクロック信号1121がマスクされ、カラムカウンタ1208はその時点での計数値を保持する。アナログランプ電圧1122とカラムカウンタ1208の計数値とはクロック信号1121により互いに同期しているので、以上の動作により、画素からの読み出し信号(アナログ信号)がデジタルメモリに保持された値(デジタル信号)にA/D変換されることとなる。

【0014】

以上で説明した2つのA/D変換方式は、カラムA/D変換方式の中でも、特にランプ型A/D変換(Ramp Run-up ADC)と呼ばれる種類のもので、A/D変換一般の方式分類によると、いずれもカウンティングADC(計数型A/D変換)と呼ばれる種類のものである。参照電位として三角波を用いることは、画素からのアナログ信号電位を時間の長さに変換するのと等価であり、さらに固定周波数のクロック信号を用いて時間の長さを計ることでA/D変換を実現するため、この名称がある。

【0015】

例えば、10bitのA/D変換であれば、画素からの信号とDACで生成される参照電位(アナログランプ電圧)との比較を行うとき、10bitの階調数分(すなわち1024回)カウントする必要がある。画素からの信号が1つだけであれば、その信号電位と参照電位の大小関係が反転した段階でA/D変換が完了し、以後の比較動作は不要となるが、MOS型センサに搭載する場合のように、たとえば1行分の画素を並列でA/D変換する場合、すべての画素で変換が完了しているかどうかを通常の構成では確認できないので、いずれにせよ1024回の比較動作が必要となる。

【0016】

ここで、具体的製品の例として、携帯電話のカメラを考えてみる。携帯電話でもMegaクラスの画素数が普通となってきており、たとえば500万画素、フレームレートが15frame/secというスペックが必要である。

【0017】

説明を容易にするため、500万画素の画素アレーの縦横比を2000行×2500列として、さらに単純化のためにブランキング期間がないものとすると、1行の読み出し期間は、

15frame/sec×2000行/frame=30Kline/sec

となる。つまり、1行の読み出しレートは30KHzとなる。

【0018】

この製品に「ランプ型A/D変換」を適用する場合、10bitA/D変換であれば、1行の読み出し時間にその階調数210=1024回の比較をする必要があり、1行の読み出しレートの約千倍、30MHz程度でデジタルメモリに出力するカウンタの計数値を変える必要がある。

【0019】

この計算では、A/D変換回路が画素からデータを受け取るまでの待機期間やA/D変換結果の出力メモリへの転送期間、すなわちA/D変換としての比較動作ができない期間を考慮しておらず、また、上記画素数以外にOB(Optical Black)画素期間やブランキング期間を除いているため、実際には、この見積り周波数よりも高い周波数(たとえば50MHz程度)になる。

【特許文献1】特開2005−347931号公報(第2図)

【特許文献2】USP5,877,715

【特許文献3】特開2005−323331号公報

【発明の開示】

【発明が解決しようとする課題】

【0020】

ランプ型A/D変換に限らず、1行分の画素を同時に変換するカラム型のA/D変換では、A/D変換レートは以下の式で決まる。

【0021】

変換レート =(フレームレート)×(1フレームの行数)

ここで、「1フレームの行数」とは、実際に有効な画素を読み出す期間だけでなく、OB画素からの信号を読み出す期間やブランキング期間も含むものとする。

【0022】

1フレームの行数は画素数のほぼ平方根に相当するが、近年、ディジタルスチルカメラ(DSC)の分野での画素数増大が激しいのはよく知られているところである。また、DSCでも動画撮影などのニーズが強まっており、画素数もフレームレートも高まる傾向にある。したがって上式から、カラム型A/D変換の変換レートも高まる傾向にあるといえる。

【0023】

さて、ランプ型A/D変換回路などのカラム型で且つ計数型のA/D変換回路における単位時間あたりの比較回数(すなわちデジタルメモリに分配するカウンタ値の変化の回数。以後、比較周波数と称す)は、A/D変換の階調数や上記変換レートと以下のような関係にある。

【0024】

比較周波数 = (階調数)/[{1/(変換レート)}−υ]

階調数 = 2(変換ビット幅)

ここでυは、A/D変換としての比較動作ができない期間である。υをゼロと近似すると、単に

比較周波数 = (階調数)×(変換レート)

となる。つまり、ランプ型A/D変換回路には、変換ビット幅が1ビット増えるだけで、変換のための比較周波数が2倍に増えるという特徴があることがわかる。

【0025】

例えば、先に述べた500万画素のイメージセンサにおけるA/D変換の比較周波数への影響は、10bitのA/D変換ビット幅を11bitに増やす場合と、500万画素を4倍の2000万画素に増やす場合とで同じであることがわかる。

【0026】

しかしながら、画質の向上という観点から、A/D変換の変換精度も求められるようになってきており、ビット幅として14bitや16bitという潜在ニーズも出てきている。

【0027】

A/D変換のビット幅が14bitの場合、先に説明した500万画素のデジタルメモリに出力するカウンタの周波数はビット幅が10bitの時の16倍の800MHzとなり、16bitの場合には、ビット幅が10bitの時の64倍の3.2GHzにもなるため、デジタルメモリ部へのカウンタ計数値信号の分配に不具合を生じる。

【0028】

具体的には以下の不具合が発生する。

(1) チップ内であっても、特にGHzオーダーのクロックは、その発生が極めて困難である。

(2) 仮にクロックを発生することができても、1行の画素数分の回路が配線負荷となり、かつ配線が長く寄生RCが大きいため、デジタルメモリの全領域で正しく駆動するのは困難である。

(3)クロックドライバの能力強化、デジタルメモリの両側からの駆動、リピーターの挿入などの対策も考えられるが、何とか動作可能な駆動波形を得ることができたとしても、消費電力が大幅に増大するため、解決手段として適切でない。また複数列毎に1個のリピーターを入れる方法だと、その周期でのノイズが画像に発生することが懸念される。また全列にリピーターを入れるのは、消費電力のさらなる増大とチップ面積の増大に加えて、リピーターによるクロックの遅延が大きくなり、ランプ型A/D変換回路の本来の動作ができなくなる懸念もある。

【0029】

以下では、特に上記(2)の不具合について詳述する。ランプ型A/D変換回路は、1列、または複数の画素列に1つ設けるのが普通である。したがって、例えば1列毎にランプ型A/D変換回路を備える場合、デジタルメモリの各ビットに供給すべきクロック信号は、1行の画素数(上述した500万画素の場合、2500列)分のデジタルメモリをその負荷とすることになる。また、配線の長さは画素数だけでなく画素の大きさにも依存するが、いわゆる大判と呼ばれるイメージセンサの場合、35mmフィルムサイズ相当の撮像面を持つので、配線の長さはフィルムの横の長さである36mmにもなり、従って、寄生RCも相当な大きさとなる。

【0030】

図18(a)は、例えば図16に示す第1の従来例と同タイプのMOSセンサのデジタルメモリに供給されるクロック信号とデジタルメモリの位置の関係を概略的に示す図であり、(b)は、クロック周波数がfである場合の(a)における点Aと点Cでのクロック波形を示す図であり、(c)は、クロック周波数が2fである場合の(a)における点Aと点Cでのクロック波形を示す図である。なお、ここで示すMOSセンサは、バイナリ→グレイコード変換器1115は設けられていないものとする。

【0031】

図18(a)に示すように、クロック生成回路1120(あるいはバイナリ→グレイコード変換器1115)から点A、点B、点Cと離れるに従って、クロック波形は寄生RC成分により鈍ってゆく。このような場合、図18(b)、(c)に示すように、点Aではいずれの周波数でも問題は生じないが、点CではRC負荷が大きくなるため、立ち上がり時間、立ち下がり時間ともに大きく延びる。このため、周波数2fでは特にクロック信号がフルスイングすることができず、信号振幅が小さくなっている。このように、変換精度を高めるために周波数を上げる程、クロック信号の供給源からの距離が長い列でのA/D変換動作に不具合が生じる可能性が高くなってしまう。

【0032】

図16に示す第1の従来例では、最下位ビットをグレイコード表現とし、それ以外のビットをバイナリ表現とすることで、バイナリ表現のみを用いる場合に比べて必要とされるスイッチングレート(周波数)を半分にすることができる。

【0033】

しかしながら、これだけでは、14bitでのクロック周波数が400MHz、16bitでの周波数が1.6GHzになるだけであり、難易度が幾分下がったとはいえ、上で述べた3つの課題は残ったままである。

【0034】

本発明の目的は、画素数やフレームレート、および変換ビット幅などが増加しても高画質で高速処理が可能な固体撮像装置を提供することにある。

【課題を解決するための手段】

【0035】

上記の課題を解決するため、本願発明者らは、種々の検討を重ね、各A/D変換回路内にラッチを設け、当該ラッチにクロック信号、あるいはクロック信号をグレイコードや位相シフトコードに変換したものの値を保持させることで、A/D変換値の下位ビットを表現させることに想到した。これにより、クロック信号の最大周波数を上げることなく、変換時間も変えずにA/D変換値のビット幅を増やすことが可能となる。あるいは、A/D変換値のビット幅を増やさない場合には、クロック信号の最大周波数を下げることができる。特に、ラッチに保持させる値をグレイコード表現や位相シフトコード表現にする場合には、ハミング距離を常に最小の1にすることができ、ビット間にスキューがあってもサンプリング誤差の影響を最小に抑えることができる。また、計数値による消費電流の変化が小さいので、ノイズの発生を抑制することができ、バイナリコードを用いる場合に比べて消費電力の低減も図ることができる。特に、位相シフトコードを用いれば、クロック信号の周波数と処理時間を同じにした場合にビット精度を高めることができる。

【0036】

すなわち、本発明の物理量検知装置は、物理量を検知する感応素子が行列状に配置されてなる感応素子アレーと、前記感応素子の1列、または複数列ごとに設けられ、各列の前記感応素子から出力される信号をデジタル信号に変換するためのカラムA/D変換回路と、各列の前記カラムA/D変換回路から出力されるデジタル信号を伝送する出力信号バスと、前記カラムA/D変換回路にカウンタ用クロック信号とラッチ用クロック信号とを供給するクロック生成回路と、三角波を出力するD/Aコンバータとを備えた物理量検知装置であって、前記各カラムA/D変換回路は、所定の期間に前記感応素子から出力される前記信号と前記三角波の電位とを比較する比較器と、前記カウンタ用クロック信号のパルスをカウントするとともに、前記比較器の出力が変化する時点での計数値を保持するカラムカウンタと、前記ラッチ用クロック信号を受け、前記比較器からの出力が変化する時点での前記ラッチ用クロック信号の値を保持する1個または複数個のラッチを有し、前記カラムカウンタの計数値と前記ラッチが保持する値とを組み合わせて表現されるA/D変換値に応じた大きさの前記デジタル信号を前記出力信号バスに出力する。

【0037】

この構成により、ラッチにA/D変換値の一部のビット(特に下位ビット)を保持させることができる。これにより、カラムカウンタに供給するカウンタ用クロック信号の最大周波数を低減することができる。また、同じ周波数で処理時間を同じとした場合には、従来の物理量検知装置に比べてビット精度を大きく向上させることが可能となる。ラッチに保持させるラッチ用クロック信号はバイナリコード、グレイコード、位相シフトコードなどで表現されていてもよいが、特にグレイコードや位相シフトコードを用いることが好ましい。中でも、位相シフトコードを用いるとカウンタ用クロック信号およびラッチ用クロック信号の周波数を変えることなくA/D変換のビット精度を大きく向上させることが可能となるので、より好ましい。

【0038】

また、本発明の物理量検知装置の駆動方法は、物理量を検知する感応素子が行列状に配置されてなる感応素子アレーと、前記感応素子の1列、または複数列ごとに設けられ、各々が比較器と、カラムカウンタと、1個または複数個のラッチとを有し、各列の前記感応素子から出力される信号をデジタル信号に変換するためのカラムA/D変換回路と、各列の前記カラムA/D変換回路から出力されるデジタル信号を伝送する出力信号バスと、前記カラムA/D変換回路にカウンタ用クロック信号とs個のラッチ用クロック信号とを供給するクロック生成回路と、三角波を出力するD/Aコンバータとを備えた物理量検知装置の駆動方法であって、前記比較器が、前記感応素子から読み出された信号の電位と前記三角波の電位とを所定の期間に比較するステップ(a)と、前記比較器による比較開始時から、前記カラムカウンタが前記カウンタ用クロック信号のパルスをカウントするステップ(b)と、前記ステップ(b)の後、前記比較器からの出力が変化する時点で前記カラムカウンタに入力される前記カウンタ用クロック信号がマスクされ、前記カウンタ部の計数値を保持するステップ(c)と、前記ステップ(b)の後、前記比較器からの出力が変化する時点でのs個の前記ラッチ用クロック信号のそれぞれの電位を前記ラッチが保持するステップ(d)と、前記ステップ(d)で前記ラッチが保持する値を下位mビットとし、前記ステップ(c)で保持された前記カラムカウンタの計数値と組み合わせて表現される値をもとにして、所定の電圧のデジタル信号を前記カラムA/D変換回路が前記出力信号バスに出力するステップ(e)とを備えている。

【0039】

この方法によれば、カラムカウンタに保持された計数値とラッチに保持されたラッチ用クロック信号(あるいは位相シフトコードやグレイコードなどに変換されたラッチ用クロック信号)の値とを組み合わせて感応素子から読み出した信号のA/D変換を行うので、A/D変換のビット精度を維持したままクロック信号の周波数を低減することが可能になる。また、クロック信号の周波数を所定値に維持したままビット精度を向上させることができる。

【発明の効果】

【0040】

ランプ波参照方式のカラムA/D変換回路のそれぞれに、A/D変換の下位ビットを保持するラッチを設けることで、カウンタ用クロック信号の周波数を上げることなく、同じA/D変換時間で、A/D変換の分解能を向上させることが可能となる。

【0041】

これにより、画質向上のため変換ビット幅や画素数を増やす場合、あるいは、高速化のためにフレームレートを上げる場合にも、カウンタ用クロック信号の波形なまり等による不具合の発生を抑えることができる。

【発明を実施するための最良の形態】

【0042】

以下では、図面を参照して本発明の各実施形態として二次元アレータイプのMOSセンサについて説明する。ただし、これは一例であって、本発明に係る構成あるいは駆動方法は、光や放射線など、外部から入力される電磁波に対して感応する単位構成要素をライン状もしくは行列状に複数個配置してなる物理量分布検知用の半導体装置に広く適用できる。

【0043】

以下、第1および第2の実施形態の固体撮像装置では、画素からの読み出した信号レベルから同じく画素から読み出したリセットレベルをオフセットとして差し引く、いわゆるCDS(相関二重サンプリング)動作をS/H(サンプルホールド)容量などを用いてアナログ領域で行うのが普通であるが、本発明のポイントには直接関係しないので、説明をシンプルにするために省略している。

【0044】

(第1の実施形態)

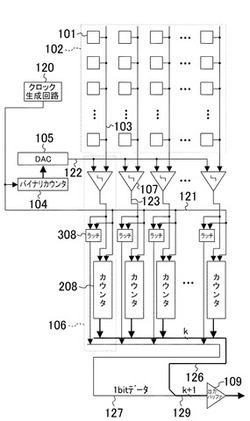

図1は、本発明の第1の実施形態に係る固体撮像装置(MOSセンサ)の構成を示す図である。

【0045】

同図に示すように、本実施形態のMOSセンサは、画素(感応素子)101が行列状に配置されてなる画素アレー(感応素子アレー)102と、画素101の1列、または複数列ごとに設けられ、画素101から出力される信号をデジタル信号に変換するためのカラムA/D変換回路106と、カラムA/D変換回路106で変換、保持されたデジタル信号の出力制御を行う列走査手段(図示せず)と、カラムA/D変換回路106から出力されるデジタル信号を伝送する出力信号バス126、127と、クロック信号(カウンタ用クロック信号およびラッチ用クロック信号)を供給するクロック生成回路120と、バイナリカウンタ104と、D/A変換回路(DAC;参照電位発生回路)105と、入力部に出力信号バス126、127が接続される出力バッファ109とを備えている。ここで、画素とは、少なくともフォトダイオードやフォトゲートなどの光感応素子を含み、光電変換により生じた信号を読み出すためのデバイス構造や、初期化動作を可能とする構造が必要に応じて設けられた単位素子のことである。なお、図1は、列ごとにカラムA/D変換回路106が設けられている例を示している。

【0046】

各カラムA/D変換回路106は、比較器107と、ラッチ308と、カラムカウンタ208とを有している。

【0047】

クロック生成回路120は、クロック信号121をバイナリカウンタ104、カラムカウンタ208、およびラッチ308に供給する。バイナリカウンタ104はバイナリ値をDAC105に供給し、DAC105は、入力されたバイナリ値に従ってアナログランプ電圧(三角波)122を生成する。このアナログランプ電圧122は参照電位として比較器107に入力される。比較器107のもう一方の入力には、画素101から読み出し信号線103を介して読み出された画素信号が入力され、比較器107からの出力はカラムカウンタ208とラッチ308に入力される。

【0048】

本実施形態のMOSセンサは、カラムA/D変換回路106内にカラムカウンタ208が設けられている点は図17に示すMOSセンサと同じであるが、比較器107からの信号出力を受けてデジタル値を確定する機構として、カラムカウンタ208に加えてラッチ308が設けられている点が当該従来のMOSセンサと異なっている。

【0049】

次に、本実施形態のMOSセンサにおけるA/D変換動作を説明する。

【0050】

まず、カラムA/D変換回路106内のカラムカウンタ208およびバイナリカウンタ104を初期化信号(図示せず)により初期化し、DAC105からアナログランプ電圧122の初期値を比較器107の一方の入力部に供給しておく。次いで、選択した行の画素101から画素信号を読み出し、比較器107の他方の入力部に当該画素信号を供給する。この状態で、クロック生成回路120からのクロック信号121の入力を開始することで、バイナリカウンタ104がその初期値からカウントを開始する。すると、DAC105もバイナリカウンタ104の計数値に従ってアナログランプ電圧122の生成をその初期値から開始する。また、これと同時にカラムA/D変換回路106内のカラムカウンタ208も、入力されるクロック信号(カウンタ用クロック信号)121の計数を開始する。

【0051】

次いで、ある列の比較器107に入力される2つの信号の大小関係が入れ替わると、比較器出力信号123が反転する。すると、当該列のカラムカウンタ208に入力されるクロック信号(カウンタ用クロック信号)121がマスクされ、これと同時にカラムカウンタ208の計数が止まり、カラムカウンタ208にその計数値が保持される。これと同じく、比較器出力信号123の反転により、ラッチ308は、カラムカウンタ208の計数停止と同じタイミングでクロック信号(ラッチ用クロック信号)121をデータとして保持する。アナログランプ電圧122とカラムカウンタ208の計数値はクロック信号121により同期しているので、以上の動作により、画素101からの読み出し信号(アナログ信号)がカラムカウンタ208およびラッチ308に保持された値(デジタル信号)にA/D変換されることとなる。なお、以上のA/D変換動作が全ての列の画素信号について各列の比較器出力信号123の反転タイミングの違いを除き、同時並行的に行われる。バイナリカウンタ104が所定のビット幅のカウントを終了した後、列走査手段(図示せず)によって列ごとにラッチ308からの出力とカラムカウンタ208からの出力とが同時に読み出され、出力バッファ109からA/D変換値が出力される。

【0052】

次に、図2を用いて、カラムA/D変換回路106内にラッチ308を追加することで、どのような効果が得られるかを説明する。図2(a)は、第2の従来例に係るMOSセンサのカラムA/D変換回路における動作波形を示す図であり、(b)は、本実施形態のMOSセンサのA/D変換回路における動作波形を示す図である。なお、各列の比較器107、1107ではそれぞれの列の画素信号を同時に比較するため、図2(a)、(b)では参考のため、比較器出力信号が反転した特定の列のカラムカウンタやラッチが保持する値をそのまま実線で示し、反転していない列での値の変化を破線で示す。

【0053】

以下の説明では、カラムカウンタ208のビット幅をkビットとし、計数値をCount[k−1:0]とし、ラッチ308が保持、出力する値をLatch[0]と表記する。また、図2(b)には、クロック信号121、および比較器出力信号123の波形も記載している。カラムカウンタ208としては、例えばクロック信号121の立下りエッジで値が変化する構成を仮定する。また、比較器出力信号123について、画素信号とアナログランプ電圧122との大小関係が反転する前の信号はH、反転後の信号はLとする。

【0054】

図2(a)に示すように、第2の従来例に係るMOSセンサでは、比較器出力信号が反転した時点以降のカラムカウンタの計数値がA/D変換結果のデジタル値を表しており、Count[3:0]が二進数で「1010」という結果を得ていることが分かる(図2(a)に付した○印部分参照)。なお、下から5bit(bit4)以上の上位ビットは表記を省略している。

【0055】

一方、図2(b)に示すように、本実施形態のMOSセンサでも、比較器出力信号123が反転した時点以降のカラムカウンタ208の計数値およびラッチ308の出力値(保持値)がA/D変換結果のデジタル値を表す。ただし、従来のMOSセンサと異なり、同じ値のCount[3:0]に加えて、Latch[0]=1を得ており、同じ周波数、同じ時間で比べた場合、本実施形態のMOSセンサでは、クロック周波数を上げずに下位ビット側の精度を向上できていることが分かる。最下位ビットは上位ビットに比べて値の変動が激しいが、本実施形態のMOSセンサでは、下位ビットの精度を向上できるので、画素数やフレームレートを増加させてもA/D変換動作に不具合が生じず、画質の劣化を抑えることができる。なお、最下位ビットをラッチ308の出力だけで表現させる場合、カラムカウンタに供給される信号の最大周波数を第2の従来例のMOSセンサにおける最大周波数の半分にしつつ、A/D変換のビット幅を増やすことができる。

【0056】

そもそも、従来のカラムカウンタ方式でA/D変換結果として得ることができるデータの最大周波数は、カラムカウンタに供給されるクロック信号の周波数の半分にしかならない。しかしながら、本実施形態のMOSセンサによれば、クロック信号をそのままデータとして扱い、ラッチ308に供給することで、A/D変換に要する時間を増やすことなく分解能の向上を図ることができる。

【0057】

ここで、仮に、カラムカウンタ208の計数値がクロック信号121の立ち上がりエッジで変化する場合について検討する。

【0058】

図3(a)は、第2の従来例に係るMOSセンサのカラムA/D変換回路における動作波形を示す図であり、(b)は、本実施形態のMOSセンサのカラムA/D変換回路における動作波形を示す図である。

【0059】

第2の従来例に係るMOSセンサでは、図3(a)と図2(a)との比較から分かるように、クロック信号の立ち上がりエッジで計数値が変化する場合と立ち下がりエッジで計数値が変化する場合とでは、クロック信号が反転するだけでA/D変換結果への影響はない。

【0060】

これに対し、本実施形態のMOSセンサでは、図3(b)と図2(b)との比較から分かるように、クロック信号の立ち上がりエッジで計数値が変化する場合と立ち下がりエッジで計数値が変化する場合とでは、クロック信号が反転するだけでなく、Latch[0]のデータも反転する。このため、カラムカウンタ208がクロック信号121の立ち上がりエッジで変化する場合には、A/D変換結果の最下位ビットの1/0が、先の場合と逆になることがわかる。従って、この場合、図4に示すように、本実施形態のMOSセンサの構成に変更を加えればよい。

【0061】

図4は、本実施形態のMOSセンサの変形例を示す図である。本変形例のMOSセンサは、破線で示したインバータ119をいずれか一方の箇所に挿入する以外は、図1に示す本実施形態のMOSセンサと同じ構成である。

【0062】

図4に示すように、最下位ビットを示す値が反転するのを防ぐためには、インバータ119をクロック生成回路120とラッチ308との間に設ければよい。これにより、クロック信号121を反転させた信号(反転クロック信号141)がラッチ308に入力されるので、最下位ビットの反転は解消できる。

【0063】

あるいは、インバータ119をラッチ308からの信号読み出し経路である出力信号バス127上に挿入しても最下位ビットの反転は解消できる。これにより、カラムカウンタ208に供給するクロック信号とラッチに供給するクロック信号とを共用できるので、ラッチにクロック信号を供給するための信号線の本数を減らすことができる。また、いずれの場合も全ての列に対してインバータを1つ追加するだけであるので、面積の増加も小さく、製造も容易である。

【0064】

なお、図1に示すすべての構成は同一の半導体基板上に形成することが可能であるため、A/D変換を固体撮像装置の外部で行うCCDセンサに比べて部品点数を減らし、撮像装置(カメラセットなど)のサイズを小さくすることができる。

【0065】

(第2の実施形態)

図5は、本発明の第2の実施形態に係るMOSセンサの構成を示す図である。同図において、図1に示す第1の実施形態のMOSセンサと同じ機能、構成を有する回路・部材については説明を省略あるいは簡略化する。

【0066】

図5に示すように、本実施形態のMOSセンサは、画素アレー102から比較器107への接続は第1の実施形態のMOSセンサと同じである。ただし、各カラムA/D変換回路106は、比較器107およびカラムカウンタ208に加え、2m−1ビット・ラッチ408を有している点で第1の実施形態のカラムA/D変換回路と異なっている。カラムA/D変換回路106は、図5に示す例では列ごとに設けられている。

【0067】

また、本実施形態のMOSセンサは、クロック信号121を受けるπ/2m−1位相シフトコード生成回路112と、2m−1ビット・ラッチ408からの出力信号を伝達する出力信号バス128上に設けられた位相シフトコード/バイナリ変換器113とをさらに備えている。π/2m−1位相シフトコード生成回路112は、位相がπ/2m−1ずつずれたm個のクロック信号(ラッチ用クロック信号)を出力する。

【0068】

クロック生成回路120はクロック信号121をバイナリカウンタ104に加えて、カラムA/D変換回路106内のカラムカウンタ208、および2m−1ビット・ラッチ408にも供給する。

【0069】

バイナリカウンタ104から出力されるバイナリ値はDAC105に入力され、DAC105は、入力されたバイナリ値に従ってアナログランプ電圧(三角波)122を生成する。このアナログランプ電圧122は参照電位として比較器107の入力部に入力される。比較器107のもう一方の入力部には、画素101から読み出し信号線103を介して読み出された画素信号が入力される。比較器107からの出力はカラムカウンタ208と2m−1ビット・ラッチ408とに入力される。

【0070】

以上のように、本実施形態のMOSセンサの特徴は、位相シフトコードに変換された値が入力される2m−1ビット・ラッチ408と、2m−1ビット・ラッチ408からの出力信号をバイナリ値に戻す位相シフトコード/バイナリ変換器113とを備えていることにある。なお、本明細書において、「位相シフトコード」とは、値が1増減する場合にビットが1つだけ変化する二進数であって、値が増えるに従って下位ビットから上位ビットへとビットが1つずつ順次変化していくコードのことを意味する。すなわち、ビット幅をPとするときの位相シフトコードでは、「全ビットゼロ」→「最下位ビットのみ1」→「下位2ビットのみが11」、・・・と順次1が増え、全ビットが1になると、今度は最下位ビットのみ0、下位2ビットが00、と順次0が増え、全ビットがゼロで元に戻る。よって、位相シフトコードでは、計2P通りの区別ができる。例えば、P=4の場合の位相シフトコード表現は以下の通りである。

【0071】

0:0000

1:0001

2:0011

3:0111

4:1111

5:1110

6:1100

7:1000

8:0000

図6は、第2の実施形態に係るMOSセンサにおいて、A/D変換値の下位4ビット分を位相シフトコードに置き換えた場合の波形図である。同図から分かるように、π/2m−1位相シフトコード生成回路112は、クロック信号121と同一の周波数を持ち、π/2m−1ずつ位相がずれた信号を2m−1ビット・ラッチ408にそれぞれ供給する。図6では、下位4ビットをシフトコードで表現する例を示している。この場合、2m−1ビット・ラッチ408は少なくとも24−1=8個のラッチで構成されていることになる。

【0072】

次に、本実施形態に係るMOSセンサのA/D変換動作を説明する。

【0073】

まず、前もってカラムA/D変換回路106内のカラムカウンタ208、バイナリカウンタ104、およびπ/2m−1位相シフトコード生成回路112を初期化信号(図示せず)により初期化し、DAC105からアナログランプ電圧122の初期値を比較器107の一方の入力部に供給しておく。次いで、選択した行の画素101から画素信号を読み出し、比較器107の他方の入力部に当該画素信号を供給する。この状態で、クロック生成回路120からのクロック信号121の入力を開始することで、バイナリカウンタ104がその初期値からカウントを開始する。すると、DAC105もバイナリカウンタ104の計数値に従ってアナログランプ電圧122の生成を初期値から開始する。また、クロック信号(カウンタ用クロック信号)121の供給開始とともに、カラムA/D変換回路106内のカラムカウンタ208も、クロック信号121の計数を開始する。これと同時に、π/2m−1位相シフトコード生成回路112も位相シフトコードの生成を開始する。

【0074】

その後、ある列の比較器107への2つの入力信号の大小関係が入れ替わると、その比較器107の比較器出力信号123が反転する。すると、当該列のカラムカウンタ208へのクロック信号121がマスクされ、これと同時にカラムカウンタ208の計数が止まり、カラムカウンタ208にその計数値が保持される。これと同じく、比較器出力信号123の反転により、2m−1ビット・ラッチ408は、カラムカウンタ208の計数停止と同じタイミングで位相シフトコード125をデータとして保持する。アナログランプ電圧122とカラムカウンタ208およびπ/2m−1位相シフトコード生成回路112などの計数値はクロック信号121により互いに同期しているので、以上の動作により、画素101からの読み出し信号(アナログ信号)がカラムカウンタ208および2m−1ビット・ラッチ408に保持された値(デジタル信号)にA/D変換されることとなる。

【0075】

図6に示すように、位相シフトコードに置き換えられたビットを除く上位ビットはカラムカウンタ208で計数するが、このカラムカウンタ208は、π/2m−1位相シフトコード生成回路112の出力信号と同じ周波数のクロック信号で駆動すればよいことが分かる。従って、本実施形態のMOSセンサによれば、下位2m−1ビットをシフトコードに置き換えてカラムA/D変換回路106内のラッチに保持させることで、A/D変換のビット幅を従来のMOSセンサと同一にした場合にはクロック周波数を1/2m−1(図6の例では1/16)にすることができる。これとは逆に、従来のMOSセンサと同一のクロック周波数を適用した場合には、ビット精度を2m−1(図6の例では4ビット)も上げることができる。

【0076】

これは、例えば、従来のMOSセンサでは800MHzのクロック周波数が必要だったところ、本実施形態のMOSセンサでは50MHzでよくなるということであり、アレー状に並ぶカラムカウンタ208での信号波形なまりによる不具合が大幅に緩和されるだけでなく、クロック生成回路120に周波数逓倍機能を持たせない構成が可能になる。また、アレイ状に配置され、各列のA/D変換値を記憶するデジタルメモリ108を設ける場合にも、信号波形のなまりによる不具合の発生を抑えることができる。なお、本実施形態の例では、50MHzのクロック信号の位相を22.5度ずつずらした信号を生成する必要があるが、このためにはDLL(Delay Locked Loop)回路を搭載すればよい。

【0077】

また、位相シフトコードでは、値が1変化した場合に常に1ビットしか変化しないので、カラムA/D変換回路106からの出力電圧の変化を均一にすることができる上、信号の読み取り誤差を小さくすることができる。また、バイナリコードを用いる場合に比べ、消費電力の低減を図ることも可能である。

【0078】

また、本実施形態のMOSセンサでは、A/D変換値を位相シフトコード/バイナリ変換器113を用いてシフトコード表現からバイナリコード表現に戻している。これにより、出力バッファ109に入力される信号の本数を減らすことができるので、特に、位相シフトコードで表現するビット数が多い場合には回路面積の縮小等の効果が得られる。また、シフトコードのままでMOSセンサの外部に出力した場合に比べて、DSP等での演算処理を容易にすることができる。

【0079】

このように、本実施形態のMOSセンサによれば、画質向上のために変換ビット幅や画素数を増やす場合、高速化のためにフレームレートを上げる場合にカウンタ用クロック信号の波形なまり等による不具合の発生を抑えることが可能となる。

【0080】

なお、π/2m−1位相シフトコード生成回路112に代えてグレイコードを出力するグレイコード生成回路を設け、カラムA/D変換回路106内に設けられたラッチにグレイコードで下位ビットを表現する場合でも、従来のMOSセンサに比べてクロック周波数を低減したり、A/D変換のビット精度を向上させたりすることが可能となる。

【0081】

(第3の実施形態)

図7は、本発明の第3の実施形態に係るMOSセンサの構成を示す図である。

【0082】

同図に示すように、本実施形態のMOSセンサは、画素アレー102から比較器への接続は第1の実施形態のMOSセンサと同じである。ただし、本実施形態のMOSセンサは、画素101の列毎に設けられたカラムA/D変換回路106内にUp/Downカウンタ(以後、U/Dカウンタと略す)218を有していることを特徴とする。また、本実施形態のMOSセンサはシーケンサ338を備えている。

【0083】

各カラムA/D変換回路106は、比較器107と、上述のU/Dカウンタ218と、Upカウント用ラッチ(以後、U用ラッチと略す)318と、Downカウント用ラッチ(以後、D用ラッチと略す)328とを有している。

【0084】

クロック生成回路120は、クロック信号121をバイナリカウンタ104に加えて、各列のU/Dカウンタ218、U用ラッチ318およびD用ラッチ328にも供給する。バイナリカウンタ104から出力されるバイナリ値はDAC105に入力され、DAC105は、入力されたバイナリ値に従ってアナログランプ電圧(三角波)122を生成する。このアナログランプ電圧は参照電位として比較器107の入力部に入力される。比較器107のもう一方の入力には、画素101から読み出し信号線103を介して読み出された画素信号が入力される。そして、比較器出力信号123はU/Dカウンタ218、U用ラッチ318、およびD用ラッチ328に入力される。

【0085】

次に、本実施形態に係るMOSセンサのA/D変換動作を説明する。

【0086】

シーケンサ338は、MOSセンサ(あるいは撮像装置)の動作モードの切り替えを担っている。ここでは、シーケンサ338は、U/Dカウンタ218のカウント方向を制御するためのカウントモード切替信号130と、Upカウント時とDownカウント時で使用するラッチを切り替えるためのUp用ラッチ選択信号131と、Down用ラッチ選択信号132とを制御する。

【0087】

まず、前もってカラムA/D変換回路106内のU/Dカウンタ218、およびバイナリカウンタ104を初期化信号(図示せず)により初期化し、DAC105からアナログランプ電圧122の初期値を比較器107の一方の入力部に供給しておく。また、先にDownカウントを行うとして、Down用ラッチ選択信号132でD用ラッチ328をアクティブ化し、カウントモード切替信号130でU/Dカウンタ218をダウンモード(Dモード)にしておく。次に、選択した行の画素101から当該画素101のリセットレベルを読み出し、これを比較器107の他方の入力部に供給する。それから、クロック生成回路120で生成されたクロック信号121の入力を開始することで、バイナリカウンタ104がその初期値からカウントを開始する。DAC105は、バイナリカウンタ104の計数値に従って、アナログランプ電圧122の生成を初期値から開始する。ここで、バイナリカウンタ104の計数方向はダウンカウント時とアップカウント時で常に同じである。また、クロック信号121の供給開始とともに、カラムA/D変換回路106内のU/Dカウンタ218も、入力されるクロック信号121のダウンカウントを開始する。

【0088】

その後、ある列の比較器107への2つの入力信号の大小関係が入れ替わると、その比較器107の比較器出力信号123が反転し、その列のU/Dカウンタ218へのクロック信号121がマスクされ、これと同時にU/Dカウンタ218の計数が止まり、U/Dカウンタ218にその計数値が保持される。これと同じく、比較器出力信号123の反転により、D用ラッチ328は、U/Dカウンタ218の計数停止と同じタイミングでクロック信号121をデータとして保持する。アナログランプ電圧122とU/Dカウンタ218の計数値、およびD用ラッチ328の値はクロック信号121により同期しているので、ここまでの動作により、画素101のリセットレベル(アナログ信号)がU/Dカウンタ218やD用ラッチ328に保持された値(デジタル信号)にA/D変換されたことになる。

【0089】

次に、以下の手順でアップカウントを行う。

【0090】

まず、Up用ラッチ選択信号131でU用ラッチ318をアクティブ化し、カウントモード切替信号130でU/Dカウンタ218をアップモード(Uモード)にしておく。このとき、U/Dカウンタ218はDモードで保持した値をそのまま保持している。次に、選択した行の画素101から画素信号を読み出し、これを比較器107の他方の入力部に供給する。それから、クロック生成回路120で生成されたクロック信号121の入力を開始することで、バイナリカウンタ104がその初期値からカウントを開始する。DAC105は、バイナリカウンタ104の計数値に従って、アナログランプ電圧122の生成を初期値から開始する。また、クロック信号121の供給開始とともに、カラムA/D変換回路106内のU/Dカウンタ218も、入力されるクロック信号121のアップカウントを、その保持した値から開始する。その後、ある列の比較器107への2つの入力信号の大小関係が入れ替わると、その比較器107の比較器出力信号123が反転し、その列のU/Dカウンタ218へのクロック信号121がマスクされ、これと同時にU/Dカウンタ218の計数が止まり、U/Dカウンタ218にその計数値が保持される。このとき保持される値は、

(Uモードでのアップカウント数)−(Dモードでのダウンカウント数)

となっている。

【0091】

これと同じく、比較器出力信号123の反転により、U用ラッチ318は、U/Dカウンタ218の計数停止と同じタイミングでクロック信号121をデータとして保持する。

【0092】

次に、U/Dカウンタ218から出力されたkビットのデータとU用ラッチ318から出力された1ビットのデータは、出力信号バス126、227でk+1ビットデータとして束ねられて、減算器117に入力される。また、D用ラッチ328から出力されたデータは、出力信号バス127、228を介して減算器117に入力される。次いで、減算器117から出力された画像信号は、出力信号バス230、出力バッファ109を介してMOSセンサの外部へと出力される。このように、アップカウント期間でのA/D変換値とダウンカウント期間でのA/D変換値との差分を求め、この差分に応じた信号を出力することで、A/D変換が行われる。

【0093】

以上のように、U/Dカウンタ218を用いることで各列の画素からカラムA/D変換回路までのオフセットノイズの影響を除去することができるので、良好な出力画像を得ることができるようになる。

【0094】

本実施形態のように、U/Dカウンタ218と1ビット分のラッチを各列のカラムA/D変換回路106に設ける場合でも、第1の実施形態のMOSセンサと同様に、ラッチに最下位ビットを表すデータを保持させることでクロック信号121の周波数を半減できる。あるいは、クロック信号121の周波数を変えない場合には、ラッチを設けない場合に比べてA/D変換の精度を1ビット分向上させることができる。

【0095】

また、第1の実施形態のMOSセンサと同様に、本実施形態のMOSセンサにおいても、ラッチに入力する信号をU/Dカウンタ218用のクロック信号と兼用にした場合に、最下位ビットとなるべきラッチのデータの極性が逆になることがありえる。この場合、図9に示すように、インバータ119をクロック生成回路120とU用ラッチ318およびD用ラッチ328との間に設ければよい。あるいは、インバータ119を、信号出力バス127上に挿入してもよい。あるいは、U用とD用の1bitデータ出力の接続関係を入れ替えて、カウンタ出力をD用データとして束ねて、減算器の+側に入力し、U用データを減算器の−側に入力してもよい。これにより、ラッチにクロック信号を供給するための信号線の本数を減らすことができる。

【0096】

なお、詳述はしないが、図8に示すように、カラムA/D変換回路106内にそれぞれ2m−1個のUp用ラッチ、Down用ラッチ(U用2m−1ビット・ラッチ358、D用2m−1ビット・ラッチ368)を設け、位相シフトコードを適用する場合も、先に説明した第2の実施形態と同じクロック周波数の低減効果、またはA/D変換精度の向上効果を得ることができる。図8に示す本実施形態の変形例に係るMOSセンサは、図5に示す第2の実施形態のMOSセンサと同様に、π/2m−1位相シフトコード生成回路112と、入力されたデータの表現を位相シフトコードからバイナリコードに戻す位相シフトコード/バイナリ変換器113を備えている。ただし、位相シフトコード/バイナリ変換器113はU用ラッチデータを伝達するための出力信号バス227上とD用ラッチデータを伝達するための出力信号バス228上のそれぞれに設けられる。出力信号バス227上の位相シフトコード/バイナリ変換器113により出力されるバイナリ信号は、出力信号バス327を介して減算器117に入力される。また、出力信号バス228上の位相シフトコード/バイナリ変換器113により出力されるバイナリ信号は、出力信号バス348を介して減算器117に入力される。減算器117から出力されたフルビットの画像信号は、出力バッファ109からMOSセンサの外部へと出力される。

【0097】

以上、位相シフトコードを用いてA/D変換値の下位4ビットまでをラッチ用クロック信号を用いて表現する事例を説明した。画像信号の下位5ビット以上についても同様にラッチ用クロック信号を用いて表現することは可能であり、これにより、クロック用周波数を大きく低減することが可能である。ただし、ラッチ用クロック信号を供給するための配線本数が1ビット増えるごとに倍増するため、レイアウト面積の増加とクロック周波数の低減効果とのトレードオフを考慮して、用途に応じて最適なビット数を選択することが好ましい。

【0098】

なお、各実施形態のカラムA/D変換回路106において、デジタルメモリやカウンタに付随させるラッチなど、いずれもA/D変換のためのメモリないしラッチに説明を限定しているが、カラム型A/D変換は1水平走査期間(1H)という限られた時間に読み出しとA/D変換を並列で行うことが多い。すなわち、1ライン前にA/D変換したデータのチップ外部への読出しと現在のラインのA/D変換との並列動作を行うことが多い。この場合、カラムA/D変換回路106内に、下位ビットのデータを保持するラッチからの出力とカラムカウンタ(あるいはU/Dカウンタ)からの出力とを受け、A/D変換値を保持できる出力用のメモリをさらに設けてもよい。

【0099】

図10は、第1の実施形態に係るMOSセンサのカラムA/D変換回路106内に出力用メモリを設けた場合のMOSセンサを示す図である。この出力用メモリ250は、カラムカウンタ208に保持される上位kビットのデータをコピーするためのk個の出力用ラッチと、2m−1個のラッチに保持される下位mビットのデータをコピーするための2m−1個(図10の例では1個)の出力用ラッチとで構成される。なお、A/D変換のビット数をnビットとすると、n=k+mである。この場合、1行分の画素信号についてのA/D変換の終了時にそれぞれr個(ただし、r=k+2m−1)の出力用ラッチに保持された各列のA/D変換値を、制御線750を駆動する列走査手段(制御部)によって順次出力用データバスに読み出す。この読み出し動作とともに、次の行の画素のA/D変換を行う。この処理を順次行うことにより、A/D変換された1画面分の画素信号の出力を迅速に行うことができる。

【0100】

また、ここまでの説明では、画素101から出力された画像信号の電圧がアナログランプ電圧122の電位と等しくなるまではカラムカウンタ208あるいはU/Dカウンタ218にカウンタ用クロック信号を供給し、画素101から出力された画像信号の電圧がランプ波の電位と等しくなる時点以後の期間、カラムカウンタ208あるいはU/Dカウンタ218へのクロック供給をマスクする手段を明示していない。しかし、このマスク手段としては、クロック信号121と比較器出力信号123とを入力とするANDゲートを入れるなど、一般的なマスク手法を利用することができる。

【0101】

なお、画素101からの読出しシーケンスの一部として一般的に行われているアナログCDS動作について、第1〜第3の実施形態のMOSセンサは説明を分かりやすくするため省略した。しかし、各実施形態のMOSセンサにおいて、アナログCDS動作を行ってもよい。この場合、画素を1行ずつ、順次読み出していくシーケンスにおいて、1行分の処理時間(1H)の間に処理すべき項目が増えるが、本発明のMOSセンサを用いればA/D変換の高速化を図ることができるので、不具合なくCDS動作を行うことができる。

【0102】

また、以上では、DAC105でアナログランプ電圧122を生成するためにカウンタ値を使う方法を説明したが、DAC105は、カウンタ値を使わずに、リセット信号で初期化され、クロック信号の入力により自走する方式のD/A変換回路であってもよい。

【0103】

さらに、RC時定数による放電によりアナログランプ波を発生する方式等を本発明のA/D変換方法に適用した場合、クロック信号の入力が不要となり、D/A変換回路105内に設けられた容量の電位の初期化をリセット信号により行うだけでA/D変換を行うことができる。

【0104】

また、位相シフトコードをそのまま出力すると出力バッファ109に入力される信号の本数が多くなるため、図5、図8などでは位相シフトコードで表現されたデータをバイナリコードに変換して出力することを前提に説明したが、位相シフトコードを適用するビット数が少ない場合、バイナリコードのみを用いる場合と比べても信号線の増加は少なくて済むので、位相シフトコードのデータをそのまま外部へ出力してもよい。

【0105】

また、以上の説明では、位相シフトコードの生成回路とシフトコードからバイナリコードへの変換回路とを備えた構成を示したが、MOSセンサは、バイナリコードからグレイコードへの変換回路と、グレイコードからバイナリコードへの変換回路を備えた構成であってもよい。あるいは、バイナリコードからグレイコードへの変換回路のみを備え、グレイコードで画像信号を出力する方式であっても本発明のクロック周波数の低減効果やビット精度の向上効果は失われない。

【0106】

また、いずれの実施形態においても、比較器107として2入力タイプのものを示したが、いわゆるチョッパー型の比較器を用いても本発明の効果を得ることができる。

【0107】

また、読み出し信号線103による画素と比較器107との接続関係は、分かりやすさを優先して単純な接続として説明したが、比較器107の入力側にアナログ信号増幅機能やCDS機能を有する回路を搭載するような構成であっても本発明の効果は失われない。

【0108】

また、出力バッファ109から出力された画像信号を処理するための画像処理回路(DSP回路)は画素アレー102と同一基板上に形成されていてもよいし、異なる基板上に形成されていてもよい。

【0109】

また、図8、図9に示すシーケンサ338は、第1および第2の実施形態に係るMOSセンサに設けられていてもよい。

【0110】

(その他の実施形態)

以下に、図5および図8に示すMOSセンサにおいて、π/2m−1位相シフトコード生成回路112の具体構成について説明する。

【0111】

−位相シフトコード生成回路の第1の構成例−

図11(a)、図12(a)は、ジョンソンカウンタを用いた第1の構成例に係る位相シフトコード生成回路を示す回路図であり、図11(b)、図12(b)は、それぞれ第1の構成例に係る位相シフトコード生成回路における信号波形を示す図である。図11(a)はビット数2m−1が2の場合であり、図12(a)は、ビット数2m−1が4の場合である。ここで、mはバイナリを用いた場合のビット数を意味する。

【0112】

図11(a)に示す位相シフトコード生成回路は、それぞれクロック信号CLK(ラッチ用クロック信号)を受けるD型フリップフロップ901a、901bと、J〔0〕を出力するインバータ902aと、J〔1〕を出力するインバータ902bとを有している。第1段のD型フリップフロップ901aの出力は第2段のD型フリップフロップ901bに入力され、このD型フリップフロップ901bの反転出力はD型フリップフロップ901aに入力されている。すなわち、D型フリップフロップ901a、901bは全体としてループを構成している。また、D型フリップフロップ901aの反転出力はインバータ902aに入力され、D型フリップフロップ901bの反転出力はインバータ902bに入力される。

【0113】

以上の構成により、図11(b)に示すように、初期値オールゼロの状態からCLKの周期分だけ位相が異なる位相シフトコードJ[1:0]を生成できる。

【0114】

また、図12(a)に示すように、4段のD型フリップフロップ901a、901b、901c、901dを通常のシフトレジスタと同様に直列に接続するとともに、最終段のD型フリップフロップ901dの反転出力を第1段のD型フリップフロップ901aに入力することで、インバータ902a、902b、902c、902dからそれぞれCLKの周期分だけ位相がずれたJ〔0〕、J〔1〕、J〔2〕、J〔3〕を出力できる。すなわち、図12(a)に示す構成によれば、図12(b)に示すように、初期値オールゼロの状態からCLKの周期分だけ位相が異なる位相シフトコードJ[3:0]を生成できる。

【0115】

なお、第1の構成例に係るジョンソンカウンタの場合、これを駆動するために周波数の高いクロック信号(図11、図12におけるCLK、図5におけるクロック信号121)の入力が必要である。しかし、位相シフトコード生成回路は全列のカラムA/D変換回路に対して1つ設けられていればよいため、位相シフトコード生成回路に高い周波数のクロック信号が供給されても、クロック信号のなまりが発生する等の不具合は起こらない。そのため、第1の構成例によれば、波形なまりなどの不具合を発生させることなく位相シフトコードを生成することが可能である。

【0116】

図12(a)に示す位相シフトコード生成回路はビット数が2m−1=4の場合であり、これを第3の実施形態として説明したMOSセンサに搭載する場合、バイナリのみを用いてA/D変換する場合に比べて、信号の最大周波数を8分の1にすることができ、グレイコードのみの場合に比べて、4分の1の周波数にまで周波数を抑制することができる。あるいは、グレイコードのみを用いるA/D変換回路と同じ周波数のクロック信号を用いる場合、バイナリのみの場合に比べて3ビットの精度向上、グレイコードのみの場合に比べて2ビットの精度向上が可能である。

【0117】

なお、ビット数が2、4の場合の位相シフトコード生成回路の構成をそれぞれ説明したが、ビット数分のD型フリップフロップを直列に接続し、最終段のD型フリップフロップの反転出力を第1段のD型フリップフロップに入力することで、任意のビット幅に対応した位相シフトコード生成回路を構成することができる。

【0118】

−位相シフトコード生成回路の第2の構成例−

周波数が非常に高くなってきた場合、クロック信号を分配する際の波形なまりの問題以前に、素子性能の限界などから高速クロックの生成が困難になってくる。これに対して、遅延ロックループ回路(以下、DLL)を用いることで、入力クロック信号の周波数を位相シフトコード生成回路を生成する位相シフトコードと同じ周波数レベルに入力クロック周波数を抑えることができる。

【0119】

図13(a)〜(c)は、DLLを用いた第2の構成例に係る位相シフトコード生成回路を示す図である。

【0120】

まず、図13(a)に示す位相シフトコード生成回路の構成例は、位相比較器802と、電荷ポンプ回路803と、遅延部801とを有している。この構成例では、位相比較器802に入力されたクロック信号RCLK(ラッチ用クロック信号)を遅延部801により遅延し、DCLKとして出力する。具体的には、遅延量がちょうど1サイクルになるように、RCLKとDCLKとを位相比較器802で比較し、早い/遅いというずれに対してUPまたはDOWNの信号を生成し、電荷ポンプ回路803が位相比較器802からの信号を受けてこれに応じた電圧信号VCONを生成する。

【0121】

遅延部801は、図13(b)に示すように、インバータ804を多段に接続してなるインバーターチェーンに負荷としての容量806をNMOSトランジスタスイッチ(以下、MOSスイッチと称す)805を介して付加した回路である。VCONはこの容量806に接続されるMOSスイッチ805のゲート電位を制御する。このVCONを高くすると、MOSスイッチ805のオン抵抗が小さくなり、容量が負荷として重くなり、遅延が大きくなる。逆にVCONの電位を低くするとMOSスイッチ805のオン抵抗が大きくなり、容量が負荷として軽くなり、遅延は小さくなる。

【0122】

図14は、図13(a)、(b)に示すDLLの回路構成を利用し、π/2m−1ずつ位相がずれた信号を出力する位相シフトコード生成回路の構成例を示す図である。

【0123】

図14に示すように、元のクロック信号(RCLK)と16個の遅延段を経た遅延クロック(DCLK)の位相を揃えるDLLの働きにより、遅延段毎に1サイクルの16分の1ずつ遅延(位相遅延π/8)させたクロック信号n〔1〕、n〔2〕、…、n〔15〕、n〔16〕(=DCLK)を得ることができる。このうち隣接する8つのノードからクロック信号(例えば、n〔1〕〜n〔8〕をクロックバッファ807によりバッファされたD〔1〕〜D〔8〕)を取り出すことで、図14に示す回路は位相シフトコード生成回路として使用可能になっている。なお、ノードn〔9〕〜n〔16〕からクロックを取り出す必要はないが、各遅延段における負荷を均等にしてタイミング精度を上げるために、これらのノードにもバッファを付ける方がより望ましい。

【0124】

以上では、特定のビット幅の位相シフトコードを生成する第2の構成例の位相シフトコード生成回路について説明したが、位相シフトコード生成回路中のシフトレジスタ段数、またはDLLの遅延段数を変えることで、ビット幅の異なる位相シフトコードを容易に生成することができる。

【0125】

なお、図14に示す位相シフトコード生成回路はビット幅m=4の場合であり、これを第3の実施形態として説明したMOSセンサに搭載する場合、信号の最大周波数を、バイナリのみを用いてA/D変換を行う場合に比べて16分の1、グレイコードのみを用いてA/D変換を行う場合に比べて8分の1にまで抑制することができる。または、同じ周波数の信号を使う場合、バイナリのみの場合に比べて4ビット分の精度向上を実現でき、グレイコードのみの場合に比べて3ビット分の精度向上が可能である。

【0126】

本発明のその他の実施形態において、ジョンソンカウンタを用いた位相シフトコード生成回路を搭載することで、RC負荷が大きいカラムA/D変換回路部などに分配するクロック信号、ないしは計数値信号に、むやみに急峻な立ち上がり・立下り特性を要求する必要がなくなるという効果を有する。

【0127】

また、DLLを用いた位相シフト生成回路を搭載することで、各列のカラムA/D変換回路に分配される(クロック)信号だけでなく、クロック生成回路で生成されるクロック信号に関しても、GHz級のクロック信号を生成をしなくてよいという設計上のスペック緩和が可能となる。そのため、撮像素子(固体撮像装置)に必須の高画質プロセスに対して必ずしも相容れない特性を備える高速CMOSプロセスを無理に融合する必要がなくなるという効果を有する。また、システムとしても撮像素子の中のノイズ低減や電磁輻射の低減につながるという効果を有する。

【0128】

また、図15(a)、(b)は、図5、図8に示す2m−1ビット位相シフトコード/バイナリ変換器113の構成例を示す図である。図15(a)は、ビット幅m=2の場合を示し、(b)は、ビット幅m=3の場合を示す。

【0129】

図15(a)に示すように、m=2の場合、位相シフトコード/バイナリ変換器に入力された位相シフトコードのPS〔0〕およびPS〔1〕は共に排他的論理和回路905に入力され、排他的論理和回路905でバイナリのBIN〔0〕に変換される。また、位相シフトコードの最上位ビットであるPS〔1〕はそのままバイナリの最上位ビットBIN〔1〕として出力される。

【0130】

また、図15(b)に示すように、m=3の場合、排他的論理和回路905が三個設けられ、一段目の排他的論理和回路905aにはPS〔0〕とPS〔2〕が入力され、同じく一段目の排他的論理和回路905bにはPS〔1〕とPS〔3〕が入力される。排他的論理和回路905a、905bの出力は二段目の排他的論理和回路905cに入力され、排他的論理和回路905cからはバイナリの最下位ビットBIN〔0〕が出力される。バイナリのBIN〔1〕は排他的論理和回路905bから出力され、バイナリの最上位ビットBIN〔2〕としては、位相シフトコードの最上位ビットPS〔3〕がそのまま出力される。このように、位相シフトコードからバイナリへの変換は、排他的論理和回路を組み合わせて容易に行うことができる。

【産業上の利用可能性】

【0131】

以上説明したように、本発明の固体撮像装置およびその駆動方法は、光や放射線など種々の物理量分布を検知するための撮像装置に有用である。

【図面の簡単な説明】

【0132】

【図1】本発明の第1の実施形態に係る固体撮像装置(MOSセンサ)の構成を示す図である。

【図2】(a)は、第2の従来例に係るMOSセンサのカラムA/D変換回路における動作波形を示す図であり、(b)は、第1の実施形態に係るMOSセンサのA/D変換回路における動作波形を示す図である。

【図3】(a)は、第2の従来例に係るMOSセンサのカラムA/D変換回路における動作波形を示す図であり、(b)は、第1の実施形態に係るMOSセンサのカラムA/D変換回路における動作波形を示す図である。

【図4】第1の実施形態に係るMOSセンサの変形例を示す図である。

【図5】本発明の第2の実施形態に係るMOSセンサの構成を示す図である。

【図6】第2の実施形態に係るMOSセンサにおいて、A/D変換値の下位4ビット分を位相シフトコードに置き換えた場合の波形図である。

【図7】本発明の第3の実施形態に係るMOSセンサの構成を示す図である。

【図8】第3の実施形態に係るMOSセンサの変形例を示す図である。

【図9】第3の実施形態に係るMOSセンサの変形例を示す図である。

【図10】第1の実施形態に係るMOSセンサのカラムA/D変換回路内に出力用メモリを設けた場合のMOSセンサを示す図である。

【図11】(a)は、ジョンソンカウンタを用いた第1の構成例に係る2m−1ビット位相シフトコード生成回路を示す回路図であり、(b)は、第1の構成例に係る2m−1ビット位相シフトコード生成回路における信号波形を示す図である。

【図12】(a)は、ジョンソンカウンタを用いた第1の構成例に係る2m−1ビット位相シフトコード生成回路を示す回路図であり(b)は、第1の構成例に係る2m−1ビット位相シフトコード生成回路における信号波形を示す図である。

【図13】(a)〜(c)は、DLLを用いた第2の構成例に係る2m−1ビット位相シフトコード生成回路を示す図である。

【図14】図13(a)、(b)に示すDLLの回路構成を利用し、π/2m−1ずつ位相がずれた信号を出力する2m−1ビット位相シフトコード生成回路の構成例を示す図である。

【図15】(a)、(b)は、図5、図8に示す2m−1ビット位相シフトコード/バイナリ変換器113の構成例を示す図である。

【図16】第1の従来例に係るMOSセンサの構成を示す図である。

【図17】第2の従来例に係るMOSセンサの構成を示す図である。

【図18】(a)は、第1の従来例と同タイプのMOSセンサのデジタルメモリに供給されるクロック信号とデジタルメモリの位置の関係を概略的に示す図であり、(b)は、クロック周波数がfである場合の(a)における点Aと点Cでのクロック波形を示す図であり、(c)は、クロック周波数が2fである場合の(a)における点Aと点Cでのクロック波形を示す図である。

【符号の説明】

【0133】

101 画素

102 画素アレー

103 読み出し信号線

104 バイナリカウンタ

105 DAC

106 カラムA/D変換回路

107 比較器

108 デジタルメモリ

109 出力バッファ

112 π/2m−1位相シフトコード生成回路

113 位相シフトコード/バイナリ変換器

117 減算器

119 インバータ

120 クロック生成回路

121 クロック信号

122 アナログランプ電圧

123 比較器出力信号

125 位相シフトコード

126、127、128、228、327、348 出力信号バス

130 カウントモード切替信号

131 Up用ラッチ選択信号

132 Down用ラッチ選択信号

141 反転クロック信号

208 カラムカウンタ

218 U/Dカウンタ

308 ラッチ

318 U用ラッチ

328 D用ラッチ

338 シーケンサ

358 U用2m−1ビット・ラッチ

368 D用2m−1ビット・ラッチ

408 2m−1ビット・ラッチ

801 遅延部

802 位相比較器

803 電荷ポンプ回路

804 インバータ

805 MOSスイッチ

806 容量

807 クロックバッファ

901a、901b、901c、901d D型フリップフロップ

902a、902b、902c、902d インバータ

905、905a、905b 排他的論理和回路

【技術分野】

【0001】

本発明は、可視光、電磁波、アルファ線、およびベータ線などの粒子放射線などの物理量分布を検知するための2次元物理量検知装置に関し、より詳細には、行列状に配列された光電変換素子などのセンシング素子と、センシング素子からの出力信号を受けるA/D変換回路とが設けられた固体撮像素子、および撮像システムに関する。

【背景技術】

【0002】

従来、イメージセンサとして主流であったCCD(Charge Coupled Device;電荷結合素子)型センサ(以後、「CCDセンサ」と称する)に加えて、今日ではロジックLSIに使われている標準プロセスを活用したMOS型のイメージセンサ(以後、「MOSセンサ」と称する)が広く市場に出回るようになった。MOSセンサは、CCDセンサとは異なり、各種アナログ回路やデジタル回路を画素アレーと同一基板上に集積化できるという特徴を備えている。CCDセンサでは、アナログ信号増幅機能やA/D変換機能に特化したアナログフロントエンドプロセサ(以後、AFE)や、AFEの機能を備えたデジタル信号処理プロセッサ(以後、DSP)など、A/D変換機能を備えた別個のチップを画素アレーに接続することで、はじめてデジタル出力を得ることができる。これに対し、MOSセンサでは、画素アレーとともにA/D変換回路を同一チップ上に集積したものが既に製品化されている。

【0003】

MOSセンサが搭載するA/D変換回路には、AFEに広く搭載されている方式でもあるパイプライン型A/D変換方式や、1ライン分の画素データを同時並列的にA/D変換するカラム型A/D変換方式、さらには、すべての画素データを同時並列的にA/D変換する方式まで多岐にわたる方式の提案がある。カラム型A/D変換方式だけに絞っても、例えば、特許文献1〜3に示される構成のものがある。

【0004】

図16は、特許文献1に記載された第1の従来例に係るMOSセンサの構成を示す図である。

【0005】

第1の従来例に係るMOSセンサは、画素1101の列毎に、比較器1107およびデジタルメモリ1108で構成されたカラムA/D変換回路1106を備えている。バイナリカウンタ1104から出力されるバイナリ値は、D/A変換回路(以後、DACと称す)1105に入力される。DAC1105は、入力されたバイナリ値に応じたアナログランプ電圧(三角波)1122を生成し、このアナログランプ電圧1122を参照電位として比較器1107に出力する。バイナリカウンタ1104の出力はバイナリ→グレイコード変換器1115にも入力され、グレイコードに変換された後、各列のデジタルメモリ1108に分配される。各カラムA/D変換回路1106内の比較器1107のもう一方の入力部には、画素1101から読み出し信号線1103を介して画素信号が入力される。

【0006】

次に、第1の従来例に係るMOSセンサのA/D変換動作を説明する。まず、クロック生成回路1120から入力されるクロック信号1121に同期して、バイナリカウンタ1104がその初期値からカウントを開始すると同時に、DAC1105がアナログランプ電圧1122の生成を開始する。そして、各列の画素1101からの読み出し信号と、バイナリカウンタ1104の計数値と同期して変化する共通のアナログランプ電圧1122とが各列の比較器1107に入力される。これと並行して、バイナリカウンタ1104の計数値はバイナリ→グレイコード変換器1115でグレイコード計数値1124に変換され、デジタルメモリ1108に分配される。ある列の比較器1107への2つの入力信号の大小関係が入れ替わると、その比較器1107の出力信号が反転し、その列のデジタルメモリ1108はバイナリ→グレイコード変換器1115が出力するグレイコード計数値1124を保持する。比較器1107に入力されるアナログランプ電圧1122とデジタルメモリ1108に入力されるグレイコード計数値1124とはバイナリカウンタ1104を介して互いに同期しているので、以上の動作により、画素からの読み出し信号(アナログ信号)がデジタルメモリに保持された値(デジタル信号)にA/D変換されることとなる。

【0007】

このように、特許文献1に示された第1の従来例に係るMOSセンサでは、デジタルメモリに供給するデジタル値の表現方法としてグレイコードを用いている。これにより、グレイコード計数値1124は常にハミング距離が最小の「1」で遷移するため、クロックとして分配されるビット間にスキューがあっても、サンプリング誤差を小さくすることができる。また、グレイコードでは前後の計数値において、全ビット中のうち1つのビットしか反転しないため、ノイズが抑制されている。また、消費電力の低減も図ることができる。

【0008】

図17は、特許文献2や特許文献3に記載された第2の従来例に係るMOSセンサの構成を示す図である。同図を用いて、もう1つのカラム型A/D変換回路を含む第2の従来例に係るMOSセンサの構成を説明する。

【0009】

第2の従来例に係るMOSセンサは、画素1101の列毎に、比較器1107とカラムカウンタ1208とで構成されたカラムA/D変換回路1106を備えている。クロック生成回路1120はクロック信号1121をバイナリカウンタ1104だけでなく、カラムA/D変換回路1106内のカラムカウンタ1208にも供給する。バイナリカウンタ1104から出力されるバイナリ値はD/A変換回路(DAC)1105に入力され、DAC1105は入力されたバイナリ値に従ってアナログランプ電圧(三角波)1122を生成する。このアナログランプ電圧1122は参照電位として比較器1107に入力される。比較器1107のもう一方の入力には、画素1101から読み出し信号線1103を介して画素信号が入力される。

【0010】

図17に示す第2の従来例に係るMOSセンサでは、カラムA/D変換回路アレーに供給される信号は、クロック生成回路1120で生成されたクロック信号1121だけである。

【0011】

次に、第2の従来例に係るMOSセンサのA/D変換動作を説明する。

【0012】

まず、カラムA/D変換回路1106内のカラムカウンタ1208およびバイナリカウンタ1104を初期化信号(図示せず)により初期化し、DAC1105からアナログランプ電圧1122の初期値を比較器1107の一方の入力部に供給しておく。次に、選択した行の画素1101から画素信号を読み出し、比較器1107の他方の入力部に供給する。この状態で、バイナリカウンタ1104およびカラムカウンタ1208へのクロック信号1121の入力を開始することで、バイナリカウンタ1104がその初期値からカウントを開始する。すると、DAC1105もバイナリカウンタ1104の計数値に従ってアナログランプ電圧1122の生成を初期値から開始する。また、カラムA/D変換回路1106内のカラムカウンタ1208も、入力されるクロック信号1121の計数を開始する。

【0013】

次いで、ある列の比較器1107に入力される2つの信号の大小関係が入れ替わり、その比較器1107の出力信号が反転すると、その列のカラムカウンタ1208に入力されるクロック信号1121がマスクされ、カラムカウンタ1208はその時点での計数値を保持する。アナログランプ電圧1122とカラムカウンタ1208の計数値とはクロック信号1121により互いに同期しているので、以上の動作により、画素からの読み出し信号(アナログ信号)がデジタルメモリに保持された値(デジタル信号)にA/D変換されることとなる。

【0014】

以上で説明した2つのA/D変換方式は、カラムA/D変換方式の中でも、特にランプ型A/D変換(Ramp Run-up ADC)と呼ばれる種類のもので、A/D変換一般の方式分類によると、いずれもカウンティングADC(計数型A/D変換)と呼ばれる種類のものである。参照電位として三角波を用いることは、画素からのアナログ信号電位を時間の長さに変換するのと等価であり、さらに固定周波数のクロック信号を用いて時間の長さを計ることでA/D変換を実現するため、この名称がある。

【0015】

例えば、10bitのA/D変換であれば、画素からの信号とDACで生成される参照電位(アナログランプ電圧)との比較を行うとき、10bitの階調数分(すなわち1024回)カウントする必要がある。画素からの信号が1つだけであれば、その信号電位と参照電位の大小関係が反転した段階でA/D変換が完了し、以後の比較動作は不要となるが、MOS型センサに搭載する場合のように、たとえば1行分の画素を並列でA/D変換する場合、すべての画素で変換が完了しているかどうかを通常の構成では確認できないので、いずれにせよ1024回の比較動作が必要となる。

【0016】

ここで、具体的製品の例として、携帯電話のカメラを考えてみる。携帯電話でもMegaクラスの画素数が普通となってきており、たとえば500万画素、フレームレートが15frame/secというスペックが必要である。

【0017】

説明を容易にするため、500万画素の画素アレーの縦横比を2000行×2500列として、さらに単純化のためにブランキング期間がないものとすると、1行の読み出し期間は、

15frame/sec×2000行/frame=30Kline/sec

となる。つまり、1行の読み出しレートは30KHzとなる。

【0018】

この製品に「ランプ型A/D変換」を適用する場合、10bitA/D変換であれば、1行の読み出し時間にその階調数210=1024回の比較をする必要があり、1行の読み出しレートの約千倍、30MHz程度でデジタルメモリに出力するカウンタの計数値を変える必要がある。

【0019】

この計算では、A/D変換回路が画素からデータを受け取るまでの待機期間やA/D変換結果の出力メモリへの転送期間、すなわちA/D変換としての比較動作ができない期間を考慮しておらず、また、上記画素数以外にOB(Optical Black)画素期間やブランキング期間を除いているため、実際には、この見積り周波数よりも高い周波数(たとえば50MHz程度)になる。

【特許文献1】特開2005−347931号公報(第2図)

【特許文献2】USP5,877,715

【特許文献3】特開2005−323331号公報

【発明の開示】

【発明が解決しようとする課題】

【0020】

ランプ型A/D変換に限らず、1行分の画素を同時に変換するカラム型のA/D変換では、A/D変換レートは以下の式で決まる。

【0021】

変換レート =(フレームレート)×(1フレームの行数)

ここで、「1フレームの行数」とは、実際に有効な画素を読み出す期間だけでなく、OB画素からの信号を読み出す期間やブランキング期間も含むものとする。

【0022】

1フレームの行数は画素数のほぼ平方根に相当するが、近年、ディジタルスチルカメラ(DSC)の分野での画素数増大が激しいのはよく知られているところである。また、DSCでも動画撮影などのニーズが強まっており、画素数もフレームレートも高まる傾向にある。したがって上式から、カラム型A/D変換の変換レートも高まる傾向にあるといえる。

【0023】

さて、ランプ型A/D変換回路などのカラム型で且つ計数型のA/D変換回路における単位時間あたりの比較回数(すなわちデジタルメモリに分配するカウンタ値の変化の回数。以後、比較周波数と称す)は、A/D変換の階調数や上記変換レートと以下のような関係にある。

【0024】

比較周波数 = (階調数)/[{1/(変換レート)}−υ]

階調数 = 2(変換ビット幅)

ここでυは、A/D変換としての比較動作ができない期間である。υをゼロと近似すると、単に

比較周波数 = (階調数)×(変換レート)

となる。つまり、ランプ型A/D変換回路には、変換ビット幅が1ビット増えるだけで、変換のための比較周波数が2倍に増えるという特徴があることがわかる。

【0025】

例えば、先に述べた500万画素のイメージセンサにおけるA/D変換の比較周波数への影響は、10bitのA/D変換ビット幅を11bitに増やす場合と、500万画素を4倍の2000万画素に増やす場合とで同じであることがわかる。

【0026】

しかしながら、画質の向上という観点から、A/D変換の変換精度も求められるようになってきており、ビット幅として14bitや16bitという潜在ニーズも出てきている。

【0027】

A/D変換のビット幅が14bitの場合、先に説明した500万画素のデジタルメモリに出力するカウンタの周波数はビット幅が10bitの時の16倍の800MHzとなり、16bitの場合には、ビット幅が10bitの時の64倍の3.2GHzにもなるため、デジタルメモリ部へのカウンタ計数値信号の分配に不具合を生じる。

【0028】

具体的には以下の不具合が発生する。

(1) チップ内であっても、特にGHzオーダーのクロックは、その発生が極めて困難である。

(2) 仮にクロックを発生することができても、1行の画素数分の回路が配線負荷となり、かつ配線が長く寄生RCが大きいため、デジタルメモリの全領域で正しく駆動するのは困難である。

(3)クロックドライバの能力強化、デジタルメモリの両側からの駆動、リピーターの挿入などの対策も考えられるが、何とか動作可能な駆動波形を得ることができたとしても、消費電力が大幅に増大するため、解決手段として適切でない。また複数列毎に1個のリピーターを入れる方法だと、その周期でのノイズが画像に発生することが懸念される。また全列にリピーターを入れるのは、消費電力のさらなる増大とチップ面積の増大に加えて、リピーターによるクロックの遅延が大きくなり、ランプ型A/D変換回路の本来の動作ができなくなる懸念もある。

【0029】

以下では、特に上記(2)の不具合について詳述する。ランプ型A/D変換回路は、1列、または複数の画素列に1つ設けるのが普通である。したがって、例えば1列毎にランプ型A/D変換回路を備える場合、デジタルメモリの各ビットに供給すべきクロック信号は、1行の画素数(上述した500万画素の場合、2500列)分のデジタルメモリをその負荷とすることになる。また、配線の長さは画素数だけでなく画素の大きさにも依存するが、いわゆる大判と呼ばれるイメージセンサの場合、35mmフィルムサイズ相当の撮像面を持つので、配線の長さはフィルムの横の長さである36mmにもなり、従って、寄生RCも相当な大きさとなる。

【0030】

図18(a)は、例えば図16に示す第1の従来例と同タイプのMOSセンサのデジタルメモリに供給されるクロック信号とデジタルメモリの位置の関係を概略的に示す図であり、(b)は、クロック周波数がfである場合の(a)における点Aと点Cでのクロック波形を示す図であり、(c)は、クロック周波数が2fである場合の(a)における点Aと点Cでのクロック波形を示す図である。なお、ここで示すMOSセンサは、バイナリ→グレイコード変換器1115は設けられていないものとする。

【0031】

図18(a)に示すように、クロック生成回路1120(あるいはバイナリ→グレイコード変換器1115)から点A、点B、点Cと離れるに従って、クロック波形は寄生RC成分により鈍ってゆく。このような場合、図18(b)、(c)に示すように、点Aではいずれの周波数でも問題は生じないが、点CではRC負荷が大きくなるため、立ち上がり時間、立ち下がり時間ともに大きく延びる。このため、周波数2fでは特にクロック信号がフルスイングすることができず、信号振幅が小さくなっている。このように、変換精度を高めるために周波数を上げる程、クロック信号の供給源からの距離が長い列でのA/D変換動作に不具合が生じる可能性が高くなってしまう。

【0032】

図16に示す第1の従来例では、最下位ビットをグレイコード表現とし、それ以外のビットをバイナリ表現とすることで、バイナリ表現のみを用いる場合に比べて必要とされるスイッチングレート(周波数)を半分にすることができる。

【0033】

しかしながら、これだけでは、14bitでのクロック周波数が400MHz、16bitでの周波数が1.6GHzになるだけであり、難易度が幾分下がったとはいえ、上で述べた3つの課題は残ったままである。

【0034】

本発明の目的は、画素数やフレームレート、および変換ビット幅などが増加しても高画質で高速処理が可能な固体撮像装置を提供することにある。

【課題を解決するための手段】

【0035】

上記の課題を解決するため、本願発明者らは、種々の検討を重ね、各A/D変換回路内にラッチを設け、当該ラッチにクロック信号、あるいはクロック信号をグレイコードや位相シフトコードに変換したものの値を保持させることで、A/D変換値の下位ビットを表現させることに想到した。これにより、クロック信号の最大周波数を上げることなく、変換時間も変えずにA/D変換値のビット幅を増やすことが可能となる。あるいは、A/D変換値のビット幅を増やさない場合には、クロック信号の最大周波数を下げることができる。特に、ラッチに保持させる値をグレイコード表現や位相シフトコード表現にする場合には、ハミング距離を常に最小の1にすることができ、ビット間にスキューがあってもサンプリング誤差の影響を最小に抑えることができる。また、計数値による消費電流の変化が小さいので、ノイズの発生を抑制することができ、バイナリコードを用いる場合に比べて消費電力の低減も図ることができる。特に、位相シフトコードを用いれば、クロック信号の周波数と処理時間を同じにした場合にビット精度を高めることができる。

【0036】

すなわち、本発明の物理量検知装置は、物理量を検知する感応素子が行列状に配置されてなる感応素子アレーと、前記感応素子の1列、または複数列ごとに設けられ、各列の前記感応素子から出力される信号をデジタル信号に変換するためのカラムA/D変換回路と、各列の前記カラムA/D変換回路から出力されるデジタル信号を伝送する出力信号バスと、前記カラムA/D変換回路にカウンタ用クロック信号とラッチ用クロック信号とを供給するクロック生成回路と、三角波を出力するD/Aコンバータとを備えた物理量検知装置であって、前記各カラムA/D変換回路は、所定の期間に前記感応素子から出力される前記信号と前記三角波の電位とを比較する比較器と、前記カウンタ用クロック信号のパルスをカウントするとともに、前記比較器の出力が変化する時点での計数値を保持するカラムカウンタと、前記ラッチ用クロック信号を受け、前記比較器からの出力が変化する時点での前記ラッチ用クロック信号の値を保持する1個または複数個のラッチを有し、前記カラムカウンタの計数値と前記ラッチが保持する値とを組み合わせて表現されるA/D変換値に応じた大きさの前記デジタル信号を前記出力信号バスに出力する。

【0037】

この構成により、ラッチにA/D変換値の一部のビット(特に下位ビット)を保持させることができる。これにより、カラムカウンタに供給するカウンタ用クロック信号の最大周波数を低減することができる。また、同じ周波数で処理時間を同じとした場合には、従来の物理量検知装置に比べてビット精度を大きく向上させることが可能となる。ラッチに保持させるラッチ用クロック信号はバイナリコード、グレイコード、位相シフトコードなどで表現されていてもよいが、特にグレイコードや位相シフトコードを用いることが好ましい。中でも、位相シフトコードを用いるとカウンタ用クロック信号およびラッチ用クロック信号の周波数を変えることなくA/D変換のビット精度を大きく向上させることが可能となるので、より好ましい。

【0038】

また、本発明の物理量検知装置の駆動方法は、物理量を検知する感応素子が行列状に配置されてなる感応素子アレーと、前記感応素子の1列、または複数列ごとに設けられ、各々が比較器と、カラムカウンタと、1個または複数個のラッチとを有し、各列の前記感応素子から出力される信号をデジタル信号に変換するためのカラムA/D変換回路と、各列の前記カラムA/D変換回路から出力されるデジタル信号を伝送する出力信号バスと、前記カラムA/D変換回路にカウンタ用クロック信号とs個のラッチ用クロック信号とを供給するクロック生成回路と、三角波を出力するD/Aコンバータとを備えた物理量検知装置の駆動方法であって、前記比較器が、前記感応素子から読み出された信号の電位と前記三角波の電位とを所定の期間に比較するステップ(a)と、前記比較器による比較開始時から、前記カラムカウンタが前記カウンタ用クロック信号のパルスをカウントするステップ(b)と、前記ステップ(b)の後、前記比較器からの出力が変化する時点で前記カラムカウンタに入力される前記カウンタ用クロック信号がマスクされ、前記カウンタ部の計数値を保持するステップ(c)と、前記ステップ(b)の後、前記比較器からの出力が変化する時点でのs個の前記ラッチ用クロック信号のそれぞれの電位を前記ラッチが保持するステップ(d)と、前記ステップ(d)で前記ラッチが保持する値を下位mビットとし、前記ステップ(c)で保持された前記カラムカウンタの計数値と組み合わせて表現される値をもとにして、所定の電圧のデジタル信号を前記カラムA/D変換回路が前記出力信号バスに出力するステップ(e)とを備えている。

【0039】

この方法によれば、カラムカウンタに保持された計数値とラッチに保持されたラッチ用クロック信号(あるいは位相シフトコードやグレイコードなどに変換されたラッチ用クロック信号)の値とを組み合わせて感応素子から読み出した信号のA/D変換を行うので、A/D変換のビット精度を維持したままクロック信号の周波数を低減することが可能になる。また、クロック信号の周波数を所定値に維持したままビット精度を向上させることができる。

【発明の効果】

【0040】

ランプ波参照方式のカラムA/D変換回路のそれぞれに、A/D変換の下位ビットを保持するラッチを設けることで、カウンタ用クロック信号の周波数を上げることなく、同じA/D変換時間で、A/D変換の分解能を向上させることが可能となる。

【0041】

これにより、画質向上のため変換ビット幅や画素数を増やす場合、あるいは、高速化のためにフレームレートを上げる場合にも、カウンタ用クロック信号の波形なまり等による不具合の発生を抑えることができる。

【発明を実施するための最良の形態】

【0042】

以下では、図面を参照して本発明の各実施形態として二次元アレータイプのMOSセンサについて説明する。ただし、これは一例であって、本発明に係る構成あるいは駆動方法は、光や放射線など、外部から入力される電磁波に対して感応する単位構成要素をライン状もしくは行列状に複数個配置してなる物理量分布検知用の半導体装置に広く適用できる。

【0043】

以下、第1および第2の実施形態の固体撮像装置では、画素からの読み出した信号レベルから同じく画素から読み出したリセットレベルをオフセットとして差し引く、いわゆるCDS(相関二重サンプリング)動作をS/H(サンプルホールド)容量などを用いてアナログ領域で行うのが普通であるが、本発明のポイントには直接関係しないので、説明をシンプルにするために省略している。

【0044】

(第1の実施形態)

図1は、本発明の第1の実施形態に係る固体撮像装置(MOSセンサ)の構成を示す図である。

【0045】

同図に示すように、本実施形態のMOSセンサは、画素(感応素子)101が行列状に配置されてなる画素アレー(感応素子アレー)102と、画素101の1列、または複数列ごとに設けられ、画素101から出力される信号をデジタル信号に変換するためのカラムA/D変換回路106と、カラムA/D変換回路106で変換、保持されたデジタル信号の出力制御を行う列走査手段(図示せず)と、カラムA/D変換回路106から出力されるデジタル信号を伝送する出力信号バス126、127と、クロック信号(カウンタ用クロック信号およびラッチ用クロック信号)を供給するクロック生成回路120と、バイナリカウンタ104と、D/A変換回路(DAC;参照電位発生回路)105と、入力部に出力信号バス126、127が接続される出力バッファ109とを備えている。ここで、画素とは、少なくともフォトダイオードやフォトゲートなどの光感応素子を含み、光電変換により生じた信号を読み出すためのデバイス構造や、初期化動作を可能とする構造が必要に応じて設けられた単位素子のことである。なお、図1は、列ごとにカラムA/D変換回路106が設けられている例を示している。

【0046】

各カラムA/D変換回路106は、比較器107と、ラッチ308と、カラムカウンタ208とを有している。

【0047】

クロック生成回路120は、クロック信号121をバイナリカウンタ104、カラムカウンタ208、およびラッチ308に供給する。バイナリカウンタ104はバイナリ値をDAC105に供給し、DAC105は、入力されたバイナリ値に従ってアナログランプ電圧(三角波)122を生成する。このアナログランプ電圧122は参照電位として比較器107に入力される。比較器107のもう一方の入力には、画素101から読み出し信号線103を介して読み出された画素信号が入力され、比較器107からの出力はカラムカウンタ208とラッチ308に入力される。

【0048】

本実施形態のMOSセンサは、カラムA/D変換回路106内にカラムカウンタ208が設けられている点は図17に示すMOSセンサと同じであるが、比較器107からの信号出力を受けてデジタル値を確定する機構として、カラムカウンタ208に加えてラッチ308が設けられている点が当該従来のMOSセンサと異なっている。

【0049】

次に、本実施形態のMOSセンサにおけるA/D変換動作を説明する。

【0050】

まず、カラムA/D変換回路106内のカラムカウンタ208およびバイナリカウンタ104を初期化信号(図示せず)により初期化し、DAC105からアナログランプ電圧122の初期値を比較器107の一方の入力部に供給しておく。次いで、選択した行の画素101から画素信号を読み出し、比較器107の他方の入力部に当該画素信号を供給する。この状態で、クロック生成回路120からのクロック信号121の入力を開始することで、バイナリカウンタ104がその初期値からカウントを開始する。すると、DAC105もバイナリカウンタ104の計数値に従ってアナログランプ電圧122の生成をその初期値から開始する。また、これと同時にカラムA/D変換回路106内のカラムカウンタ208も、入力されるクロック信号(カウンタ用クロック信号)121の計数を開始する。

【0051】

次いで、ある列の比較器107に入力される2つの信号の大小関係が入れ替わると、比較器出力信号123が反転する。すると、当該列のカラムカウンタ208に入力されるクロック信号(カウンタ用クロック信号)121がマスクされ、これと同時にカラムカウンタ208の計数が止まり、カラムカウンタ208にその計数値が保持される。これと同じく、比較器出力信号123の反転により、ラッチ308は、カラムカウンタ208の計数停止と同じタイミングでクロック信号(ラッチ用クロック信号)121をデータとして保持する。アナログランプ電圧122とカラムカウンタ208の計数値はクロック信号121により同期しているので、以上の動作により、画素101からの読み出し信号(アナログ信号)がカラムカウンタ208およびラッチ308に保持された値(デジタル信号)にA/D変換されることとなる。なお、以上のA/D変換動作が全ての列の画素信号について各列の比較器出力信号123の反転タイミングの違いを除き、同時並行的に行われる。バイナリカウンタ104が所定のビット幅のカウントを終了した後、列走査手段(図示せず)によって列ごとにラッチ308からの出力とカラムカウンタ208からの出力とが同時に読み出され、出力バッファ109からA/D変換値が出力される。

【0052】

次に、図2を用いて、カラムA/D変換回路106内にラッチ308を追加することで、どのような効果が得られるかを説明する。図2(a)は、第2の従来例に係るMOSセンサのカラムA/D変換回路における動作波形を示す図であり、(b)は、本実施形態のMOSセンサのA/D変換回路における動作波形を示す図である。なお、各列の比較器107、1107ではそれぞれの列の画素信号を同時に比較するため、図2(a)、(b)では参考のため、比較器出力信号が反転した特定の列のカラムカウンタやラッチが保持する値をそのまま実線で示し、反転していない列での値の変化を破線で示す。

【0053】

以下の説明では、カラムカウンタ208のビット幅をkビットとし、計数値をCount[k−1:0]とし、ラッチ308が保持、出力する値をLatch[0]と表記する。また、図2(b)には、クロック信号121、および比較器出力信号123の波形も記載している。カラムカウンタ208としては、例えばクロック信号121の立下りエッジで値が変化する構成を仮定する。また、比較器出力信号123について、画素信号とアナログランプ電圧122との大小関係が反転する前の信号はH、反転後の信号はLとする。

【0054】

図2(a)に示すように、第2の従来例に係るMOSセンサでは、比較器出力信号が反転した時点以降のカラムカウンタの計数値がA/D変換結果のデジタル値を表しており、Count[3:0]が二進数で「1010」という結果を得ていることが分かる(図2(a)に付した○印部分参照)。なお、下から5bit(bit4)以上の上位ビットは表記を省略している。

【0055】

一方、図2(b)に示すように、本実施形態のMOSセンサでも、比較器出力信号123が反転した時点以降のカラムカウンタ208の計数値およびラッチ308の出力値(保持値)がA/D変換結果のデジタル値を表す。ただし、従来のMOSセンサと異なり、同じ値のCount[3:0]に加えて、Latch[0]=1を得ており、同じ周波数、同じ時間で比べた場合、本実施形態のMOSセンサでは、クロック周波数を上げずに下位ビット側の精度を向上できていることが分かる。最下位ビットは上位ビットに比べて値の変動が激しいが、本実施形態のMOSセンサでは、下位ビットの精度を向上できるので、画素数やフレームレートを増加させてもA/D変換動作に不具合が生じず、画質の劣化を抑えることができる。なお、最下位ビットをラッチ308の出力だけで表現させる場合、カラムカウンタに供給される信号の最大周波数を第2の従来例のMOSセンサにおける最大周波数の半分にしつつ、A/D変換のビット幅を増やすことができる。

【0056】

そもそも、従来のカラムカウンタ方式でA/D変換結果として得ることができるデータの最大周波数は、カラムカウンタに供給されるクロック信号の周波数の半分にしかならない。しかしながら、本実施形態のMOSセンサによれば、クロック信号をそのままデータとして扱い、ラッチ308に供給することで、A/D変換に要する時間を増やすことなく分解能の向上を図ることができる。

【0057】

ここで、仮に、カラムカウンタ208の計数値がクロック信号121の立ち上がりエッジで変化する場合について検討する。

【0058】

図3(a)は、第2の従来例に係るMOSセンサのカラムA/D変換回路における動作波形を示す図であり、(b)は、本実施形態のMOSセンサのカラムA/D変換回路における動作波形を示す図である。

【0059】

第2の従来例に係るMOSセンサでは、図3(a)と図2(a)との比較から分かるように、クロック信号の立ち上がりエッジで計数値が変化する場合と立ち下がりエッジで計数値が変化する場合とでは、クロック信号が反転するだけでA/D変換結果への影響はない。

【0060】

これに対し、本実施形態のMOSセンサでは、図3(b)と図2(b)との比較から分かるように、クロック信号の立ち上がりエッジで計数値が変化する場合と立ち下がりエッジで計数値が変化する場合とでは、クロック信号が反転するだけでなく、Latch[0]のデータも反転する。このため、カラムカウンタ208がクロック信号121の立ち上がりエッジで変化する場合には、A/D変換結果の最下位ビットの1/0が、先の場合と逆になることがわかる。従って、この場合、図4に示すように、本実施形態のMOSセンサの構成に変更を加えればよい。

【0061】

図4は、本実施形態のMOSセンサの変形例を示す図である。本変形例のMOSセンサは、破線で示したインバータ119をいずれか一方の箇所に挿入する以外は、図1に示す本実施形態のMOSセンサと同じ構成である。

【0062】

図4に示すように、最下位ビットを示す値が反転するのを防ぐためには、インバータ119をクロック生成回路120とラッチ308との間に設ければよい。これにより、クロック信号121を反転させた信号(反転クロック信号141)がラッチ308に入力されるので、最下位ビットの反転は解消できる。

【0063】

あるいは、インバータ119をラッチ308からの信号読み出し経路である出力信号バス127上に挿入しても最下位ビットの反転は解消できる。これにより、カラムカウンタ208に供給するクロック信号とラッチに供給するクロック信号とを共用できるので、ラッチにクロック信号を供給するための信号線の本数を減らすことができる。また、いずれの場合も全ての列に対してインバータを1つ追加するだけであるので、面積の増加も小さく、製造も容易である。

【0064】

なお、図1に示すすべての構成は同一の半導体基板上に形成することが可能であるため、A/D変換を固体撮像装置の外部で行うCCDセンサに比べて部品点数を減らし、撮像装置(カメラセットなど)のサイズを小さくすることができる。

【0065】

(第2の実施形態)

図5は、本発明の第2の実施形態に係るMOSセンサの構成を示す図である。同図において、図1に示す第1の実施形態のMOSセンサと同じ機能、構成を有する回路・部材については説明を省略あるいは簡略化する。

【0066】

図5に示すように、本実施形態のMOSセンサは、画素アレー102から比較器107への接続は第1の実施形態のMOSセンサと同じである。ただし、各カラムA/D変換回路106は、比較器107およびカラムカウンタ208に加え、2m−1ビット・ラッチ408を有している点で第1の実施形態のカラムA/D変換回路と異なっている。カラムA/D変換回路106は、図5に示す例では列ごとに設けられている。

【0067】

また、本実施形態のMOSセンサは、クロック信号121を受けるπ/2m−1位相シフトコード生成回路112と、2m−1ビット・ラッチ408からの出力信号を伝達する出力信号バス128上に設けられた位相シフトコード/バイナリ変換器113とをさらに備えている。π/2m−1位相シフトコード生成回路112は、位相がπ/2m−1ずつずれたm個のクロック信号(ラッチ用クロック信号)を出力する。

【0068】

クロック生成回路120はクロック信号121をバイナリカウンタ104に加えて、カラムA/D変換回路106内のカラムカウンタ208、および2m−1ビット・ラッチ408にも供給する。

【0069】

バイナリカウンタ104から出力されるバイナリ値はDAC105に入力され、DAC105は、入力されたバイナリ値に従ってアナログランプ電圧(三角波)122を生成する。このアナログランプ電圧122は参照電位として比較器107の入力部に入力される。比較器107のもう一方の入力部には、画素101から読み出し信号線103を介して読み出された画素信号が入力される。比較器107からの出力はカラムカウンタ208と2m−1ビット・ラッチ408とに入力される。

【0070】

以上のように、本実施形態のMOSセンサの特徴は、位相シフトコードに変換された値が入力される2m−1ビット・ラッチ408と、2m−1ビット・ラッチ408からの出力信号をバイナリ値に戻す位相シフトコード/バイナリ変換器113とを備えていることにある。なお、本明細書において、「位相シフトコード」とは、値が1増減する場合にビットが1つだけ変化する二進数であって、値が増えるに従って下位ビットから上位ビットへとビットが1つずつ順次変化していくコードのことを意味する。すなわち、ビット幅をPとするときの位相シフトコードでは、「全ビットゼロ」→「最下位ビットのみ1」→「下位2ビットのみが11」、・・・と順次1が増え、全ビットが1になると、今度は最下位ビットのみ0、下位2ビットが00、と順次0が増え、全ビットがゼロで元に戻る。よって、位相シフトコードでは、計2P通りの区別ができる。例えば、P=4の場合の位相シフトコード表現は以下の通りである。

【0071】

0:0000

1:0001

2:0011

3:0111

4:1111

5:1110

6:1100

7:1000

8:0000

図6は、第2の実施形態に係るMOSセンサにおいて、A/D変換値の下位4ビット分を位相シフトコードに置き換えた場合の波形図である。同図から分かるように、π/2m−1位相シフトコード生成回路112は、クロック信号121と同一の周波数を持ち、π/2m−1ずつ位相がずれた信号を2m−1ビット・ラッチ408にそれぞれ供給する。図6では、下位4ビットをシフトコードで表現する例を示している。この場合、2m−1ビット・ラッチ408は少なくとも24−1=8個のラッチで構成されていることになる。

【0072】

次に、本実施形態に係るMOSセンサのA/D変換動作を説明する。

【0073】

まず、前もってカラムA/D変換回路106内のカラムカウンタ208、バイナリカウンタ104、およびπ/2m−1位相シフトコード生成回路112を初期化信号(図示せず)により初期化し、DAC105からアナログランプ電圧122の初期値を比較器107の一方の入力部に供給しておく。次いで、選択した行の画素101から画素信号を読み出し、比較器107の他方の入力部に当該画素信号を供給する。この状態で、クロック生成回路120からのクロック信号121の入力を開始することで、バイナリカウンタ104がその初期値からカウントを開始する。すると、DAC105もバイナリカウンタ104の計数値に従ってアナログランプ電圧122の生成を初期値から開始する。また、クロック信号(カウンタ用クロック信号)121の供給開始とともに、カラムA/D変換回路106内のカラムカウンタ208も、クロック信号121の計数を開始する。これと同時に、π/2m−1位相シフトコード生成回路112も位相シフトコードの生成を開始する。

【0074】

その後、ある列の比較器107への2つの入力信号の大小関係が入れ替わると、その比較器107の比較器出力信号123が反転する。すると、当該列のカラムカウンタ208へのクロック信号121がマスクされ、これと同時にカラムカウンタ208の計数が止まり、カラムカウンタ208にその計数値が保持される。これと同じく、比較器出力信号123の反転により、2m−1ビット・ラッチ408は、カラムカウンタ208の計数停止と同じタイミングで位相シフトコード125をデータとして保持する。アナログランプ電圧122とカラムカウンタ208およびπ/2m−1位相シフトコード生成回路112などの計数値はクロック信号121により互いに同期しているので、以上の動作により、画素101からの読み出し信号(アナログ信号)がカラムカウンタ208および2m−1ビット・ラッチ408に保持された値(デジタル信号)にA/D変換されることとなる。

【0075】

図6に示すように、位相シフトコードに置き換えられたビットを除く上位ビットはカラムカウンタ208で計数するが、このカラムカウンタ208は、π/2m−1位相シフトコード生成回路112の出力信号と同じ周波数のクロック信号で駆動すればよいことが分かる。従って、本実施形態のMOSセンサによれば、下位2m−1ビットをシフトコードに置き換えてカラムA/D変換回路106内のラッチに保持させることで、A/D変換のビット幅を従来のMOSセンサと同一にした場合にはクロック周波数を1/2m−1(図6の例では1/16)にすることができる。これとは逆に、従来のMOSセンサと同一のクロック周波数を適用した場合には、ビット精度を2m−1(図6の例では4ビット)も上げることができる。

【0076】

これは、例えば、従来のMOSセンサでは800MHzのクロック周波数が必要だったところ、本実施形態のMOSセンサでは50MHzでよくなるということであり、アレー状に並ぶカラムカウンタ208での信号波形なまりによる不具合が大幅に緩和されるだけでなく、クロック生成回路120に周波数逓倍機能を持たせない構成が可能になる。また、アレイ状に配置され、各列のA/D変換値を記憶するデジタルメモリ108を設ける場合にも、信号波形のなまりによる不具合の発生を抑えることができる。なお、本実施形態の例では、50MHzのクロック信号の位相を22.5度ずつずらした信号を生成する必要があるが、このためにはDLL(Delay Locked Loop)回路を搭載すればよい。

【0077】

また、位相シフトコードでは、値が1変化した場合に常に1ビットしか変化しないので、カラムA/D変換回路106からの出力電圧の変化を均一にすることができる上、信号の読み取り誤差を小さくすることができる。また、バイナリコードを用いる場合に比べ、消費電力の低減を図ることも可能である。

【0078】

また、本実施形態のMOSセンサでは、A/D変換値を位相シフトコード/バイナリ変換器113を用いてシフトコード表現からバイナリコード表現に戻している。これにより、出力バッファ109に入力される信号の本数を減らすことができるので、特に、位相シフトコードで表現するビット数が多い場合には回路面積の縮小等の効果が得られる。また、シフトコードのままでMOSセンサの外部に出力した場合に比べて、DSP等での演算処理を容易にすることができる。

【0079】

このように、本実施形態のMOSセンサによれば、画質向上のために変換ビット幅や画素数を増やす場合、高速化のためにフレームレートを上げる場合にカウンタ用クロック信号の波形なまり等による不具合の発生を抑えることが可能となる。

【0080】

なお、π/2m−1位相シフトコード生成回路112に代えてグレイコードを出力するグレイコード生成回路を設け、カラムA/D変換回路106内に設けられたラッチにグレイコードで下位ビットを表現する場合でも、従来のMOSセンサに比べてクロック周波数を低減したり、A/D変換のビット精度を向上させたりすることが可能となる。

【0081】

(第3の実施形態)

図7は、本発明の第3の実施形態に係るMOSセンサの構成を示す図である。

【0082】

同図に示すように、本実施形態のMOSセンサは、画素アレー102から比較器への接続は第1の実施形態のMOSセンサと同じである。ただし、本実施形態のMOSセンサは、画素101の列毎に設けられたカラムA/D変換回路106内にUp/Downカウンタ(以後、U/Dカウンタと略す)218を有していることを特徴とする。また、本実施形態のMOSセンサはシーケンサ338を備えている。

【0083】

各カラムA/D変換回路106は、比較器107と、上述のU/Dカウンタ218と、Upカウント用ラッチ(以後、U用ラッチと略す)318と、Downカウント用ラッチ(以後、D用ラッチと略す)328とを有している。

【0084】

クロック生成回路120は、クロック信号121をバイナリカウンタ104に加えて、各列のU/Dカウンタ218、U用ラッチ318およびD用ラッチ328にも供給する。バイナリカウンタ104から出力されるバイナリ値はDAC105に入力され、DAC105は、入力されたバイナリ値に従ってアナログランプ電圧(三角波)122を生成する。このアナログランプ電圧は参照電位として比較器107の入力部に入力される。比較器107のもう一方の入力には、画素101から読み出し信号線103を介して読み出された画素信号が入力される。そして、比較器出力信号123はU/Dカウンタ218、U用ラッチ318、およびD用ラッチ328に入力される。

【0085】

次に、本実施形態に係るMOSセンサのA/D変換動作を説明する。

【0086】

シーケンサ338は、MOSセンサ(あるいは撮像装置)の動作モードの切り替えを担っている。ここでは、シーケンサ338は、U/Dカウンタ218のカウント方向を制御するためのカウントモード切替信号130と、Upカウント時とDownカウント時で使用するラッチを切り替えるためのUp用ラッチ選択信号131と、Down用ラッチ選択信号132とを制御する。

【0087】

まず、前もってカラムA/D変換回路106内のU/Dカウンタ218、およびバイナリカウンタ104を初期化信号(図示せず)により初期化し、DAC105からアナログランプ電圧122の初期値を比較器107の一方の入力部に供給しておく。また、先にDownカウントを行うとして、Down用ラッチ選択信号132でD用ラッチ328をアクティブ化し、カウントモード切替信号130でU/Dカウンタ218をダウンモード(Dモード)にしておく。次に、選択した行の画素101から当該画素101のリセットレベルを読み出し、これを比較器107の他方の入力部に供給する。それから、クロック生成回路120で生成されたクロック信号121の入力を開始することで、バイナリカウンタ104がその初期値からカウントを開始する。DAC105は、バイナリカウンタ104の計数値に従って、アナログランプ電圧122の生成を初期値から開始する。ここで、バイナリカウンタ104の計数方向はダウンカウント時とアップカウント時で常に同じである。また、クロック信号121の供給開始とともに、カラムA/D変換回路106内のU/Dカウンタ218も、入力されるクロック信号121のダウンカウントを開始する。

【0088】

その後、ある列の比較器107への2つの入力信号の大小関係が入れ替わると、その比較器107の比較器出力信号123が反転し、その列のU/Dカウンタ218へのクロック信号121がマスクされ、これと同時にU/Dカウンタ218の計数が止まり、U/Dカウンタ218にその計数値が保持される。これと同じく、比較器出力信号123の反転により、D用ラッチ328は、U/Dカウンタ218の計数停止と同じタイミングでクロック信号121をデータとして保持する。アナログランプ電圧122とU/Dカウンタ218の計数値、およびD用ラッチ328の値はクロック信号121により同期しているので、ここまでの動作により、画素101のリセットレベル(アナログ信号)がU/Dカウンタ218やD用ラッチ328に保持された値(デジタル信号)にA/D変換されたことになる。

【0089】

次に、以下の手順でアップカウントを行う。

【0090】

まず、Up用ラッチ選択信号131でU用ラッチ318をアクティブ化し、カウントモード切替信号130でU/Dカウンタ218をアップモード(Uモード)にしておく。このとき、U/Dカウンタ218はDモードで保持した値をそのまま保持している。次に、選択した行の画素101から画素信号を読み出し、これを比較器107の他方の入力部に供給する。それから、クロック生成回路120で生成されたクロック信号121の入力を開始することで、バイナリカウンタ104がその初期値からカウントを開始する。DAC105は、バイナリカウンタ104の計数値に従って、アナログランプ電圧122の生成を初期値から開始する。また、クロック信号121の供給開始とともに、カラムA/D変換回路106内のU/Dカウンタ218も、入力されるクロック信号121のアップカウントを、その保持した値から開始する。その後、ある列の比較器107への2つの入力信号の大小関係が入れ替わると、その比較器107の比較器出力信号123が反転し、その列のU/Dカウンタ218へのクロック信号121がマスクされ、これと同時にU/Dカウンタ218の計数が止まり、U/Dカウンタ218にその計数値が保持される。このとき保持される値は、

(Uモードでのアップカウント数)−(Dモードでのダウンカウント数)

となっている。

【0091】

これと同じく、比較器出力信号123の反転により、U用ラッチ318は、U/Dカウンタ218の計数停止と同じタイミングでクロック信号121をデータとして保持する。

【0092】

次に、U/Dカウンタ218から出力されたkビットのデータとU用ラッチ318から出力された1ビットのデータは、出力信号バス126、227でk+1ビットデータとして束ねられて、減算器117に入力される。また、D用ラッチ328から出力されたデータは、出力信号バス127、228を介して減算器117に入力される。次いで、減算器117から出力された画像信号は、出力信号バス230、出力バッファ109を介してMOSセンサの外部へと出力される。このように、アップカウント期間でのA/D変換値とダウンカウント期間でのA/D変換値との差分を求め、この差分に応じた信号を出力することで、A/D変換が行われる。

【0093】

以上のように、U/Dカウンタ218を用いることで各列の画素からカラムA/D変換回路までのオフセットノイズの影響を除去することができるので、良好な出力画像を得ることができるようになる。

【0094】

本実施形態のように、U/Dカウンタ218と1ビット分のラッチを各列のカラムA/D変換回路106に設ける場合でも、第1の実施形態のMOSセンサと同様に、ラッチに最下位ビットを表すデータを保持させることでクロック信号121の周波数を半減できる。あるいは、クロック信号121の周波数を変えない場合には、ラッチを設けない場合に比べてA/D変換の精度を1ビット分向上させることができる。

【0095】

また、第1の実施形態のMOSセンサと同様に、本実施形態のMOSセンサにおいても、ラッチに入力する信号をU/Dカウンタ218用のクロック信号と兼用にした場合に、最下位ビットとなるべきラッチのデータの極性が逆になることがありえる。この場合、図9に示すように、インバータ119をクロック生成回路120とU用ラッチ318およびD用ラッチ328との間に設ければよい。あるいは、インバータ119を、信号出力バス127上に挿入してもよい。あるいは、U用とD用の1bitデータ出力の接続関係を入れ替えて、カウンタ出力をD用データとして束ねて、減算器の+側に入力し、U用データを減算器の−側に入力してもよい。これにより、ラッチにクロック信号を供給するための信号線の本数を減らすことができる。

【0096】

なお、詳述はしないが、図8に示すように、カラムA/D変換回路106内にそれぞれ2m−1個のUp用ラッチ、Down用ラッチ(U用2m−1ビット・ラッチ358、D用2m−1ビット・ラッチ368)を設け、位相シフトコードを適用する場合も、先に説明した第2の実施形態と同じクロック周波数の低減効果、またはA/D変換精度の向上効果を得ることができる。図8に示す本実施形態の変形例に係るMOSセンサは、図5に示す第2の実施形態のMOSセンサと同様に、π/2m−1位相シフトコード生成回路112と、入力されたデータの表現を位相シフトコードからバイナリコードに戻す位相シフトコード/バイナリ変換器113を備えている。ただし、位相シフトコード/バイナリ変換器113はU用ラッチデータを伝達するための出力信号バス227上とD用ラッチデータを伝達するための出力信号バス228上のそれぞれに設けられる。出力信号バス227上の位相シフトコード/バイナリ変換器113により出力されるバイナリ信号は、出力信号バス327を介して減算器117に入力される。また、出力信号バス228上の位相シフトコード/バイナリ変換器113により出力されるバイナリ信号は、出力信号バス348を介して減算器117に入力される。減算器117から出力されたフルビットの画像信号は、出力バッファ109からMOSセンサの外部へと出力される。

【0097】

以上、位相シフトコードを用いてA/D変換値の下位4ビットまでをラッチ用クロック信号を用いて表現する事例を説明した。画像信号の下位5ビット以上についても同様にラッチ用クロック信号を用いて表現することは可能であり、これにより、クロック用周波数を大きく低減することが可能である。ただし、ラッチ用クロック信号を供給するための配線本数が1ビット増えるごとに倍増するため、レイアウト面積の増加とクロック周波数の低減効果とのトレードオフを考慮して、用途に応じて最適なビット数を選択することが好ましい。

【0098】

なお、各実施形態のカラムA/D変換回路106において、デジタルメモリやカウンタに付随させるラッチなど、いずれもA/D変換のためのメモリないしラッチに説明を限定しているが、カラム型A/D変換は1水平走査期間(1H)という限られた時間に読み出しとA/D変換を並列で行うことが多い。すなわち、1ライン前にA/D変換したデータのチップ外部への読出しと現在のラインのA/D変換との並列動作を行うことが多い。この場合、カラムA/D変換回路106内に、下位ビットのデータを保持するラッチからの出力とカラムカウンタ(あるいはU/Dカウンタ)からの出力とを受け、A/D変換値を保持できる出力用のメモリをさらに設けてもよい。

【0099】

図10は、第1の実施形態に係るMOSセンサのカラムA/D変換回路106内に出力用メモリを設けた場合のMOSセンサを示す図である。この出力用メモリ250は、カラムカウンタ208に保持される上位kビットのデータをコピーするためのk個の出力用ラッチと、2m−1個のラッチに保持される下位mビットのデータをコピーするための2m−1個(図10の例では1個)の出力用ラッチとで構成される。なお、A/D変換のビット数をnビットとすると、n=k+mである。この場合、1行分の画素信号についてのA/D変換の終了時にそれぞれr個(ただし、r=k+2m−1)の出力用ラッチに保持された各列のA/D変換値を、制御線750を駆動する列走査手段(制御部)によって順次出力用データバスに読み出す。この読み出し動作とともに、次の行の画素のA/D変換を行う。この処理を順次行うことにより、A/D変換された1画面分の画素信号の出力を迅速に行うことができる。

【0100】

また、ここまでの説明では、画素101から出力された画像信号の電圧がアナログランプ電圧122の電位と等しくなるまではカラムカウンタ208あるいはU/Dカウンタ218にカウンタ用クロック信号を供給し、画素101から出力された画像信号の電圧がランプ波の電位と等しくなる時点以後の期間、カラムカウンタ208あるいはU/Dカウンタ218へのクロック供給をマスクする手段を明示していない。しかし、このマスク手段としては、クロック信号121と比較器出力信号123とを入力とするANDゲートを入れるなど、一般的なマスク手法を利用することができる。

【0101】

なお、画素101からの読出しシーケンスの一部として一般的に行われているアナログCDS動作について、第1〜第3の実施形態のMOSセンサは説明を分かりやすくするため省略した。しかし、各実施形態のMOSセンサにおいて、アナログCDS動作を行ってもよい。この場合、画素を1行ずつ、順次読み出していくシーケンスにおいて、1行分の処理時間(1H)の間に処理すべき項目が増えるが、本発明のMOSセンサを用いればA/D変換の高速化を図ることができるので、不具合なくCDS動作を行うことができる。

【0102】

また、以上では、DAC105でアナログランプ電圧122を生成するためにカウンタ値を使う方法を説明したが、DAC105は、カウンタ値を使わずに、リセット信号で初期化され、クロック信号の入力により自走する方式のD/A変換回路であってもよい。

【0103】

さらに、RC時定数による放電によりアナログランプ波を発生する方式等を本発明のA/D変換方法に適用した場合、クロック信号の入力が不要となり、D/A変換回路105内に設けられた容量の電位の初期化をリセット信号により行うだけでA/D変換を行うことができる。

【0104】

また、位相シフトコードをそのまま出力すると出力バッファ109に入力される信号の本数が多くなるため、図5、図8などでは位相シフトコードで表現されたデータをバイナリコードに変換して出力することを前提に説明したが、位相シフトコードを適用するビット数が少ない場合、バイナリコードのみを用いる場合と比べても信号線の増加は少なくて済むので、位相シフトコードのデータをそのまま外部へ出力してもよい。

【0105】

また、以上の説明では、位相シフトコードの生成回路とシフトコードからバイナリコードへの変換回路とを備えた構成を示したが、MOSセンサは、バイナリコードからグレイコードへの変換回路と、グレイコードからバイナリコードへの変換回路を備えた構成であってもよい。あるいは、バイナリコードからグレイコードへの変換回路のみを備え、グレイコードで画像信号を出力する方式であっても本発明のクロック周波数の低減効果やビット精度の向上効果は失われない。

【0106】

また、いずれの実施形態においても、比較器107として2入力タイプのものを示したが、いわゆるチョッパー型の比較器を用いても本発明の効果を得ることができる。

【0107】

また、読み出し信号線103による画素と比較器107との接続関係は、分かりやすさを優先して単純な接続として説明したが、比較器107の入力側にアナログ信号増幅機能やCDS機能を有する回路を搭載するような構成であっても本発明の効果は失われない。

【0108】

また、出力バッファ109から出力された画像信号を処理するための画像処理回路(DSP回路)は画素アレー102と同一基板上に形成されていてもよいし、異なる基板上に形成されていてもよい。

【0109】

また、図8、図9に示すシーケンサ338は、第1および第2の実施形態に係るMOSセンサに設けられていてもよい。

【0110】

(その他の実施形態)

以下に、図5および図8に示すMOSセンサにおいて、π/2m−1位相シフトコード生成回路112の具体構成について説明する。

【0111】

−位相シフトコード生成回路の第1の構成例−

図11(a)、図12(a)は、ジョンソンカウンタを用いた第1の構成例に係る位相シフトコード生成回路を示す回路図であり、図11(b)、図12(b)は、それぞれ第1の構成例に係る位相シフトコード生成回路における信号波形を示す図である。図11(a)はビット数2m−1が2の場合であり、図12(a)は、ビット数2m−1が4の場合である。ここで、mはバイナリを用いた場合のビット数を意味する。

【0112】

図11(a)に示す位相シフトコード生成回路は、それぞれクロック信号CLK(ラッチ用クロック信号)を受けるD型フリップフロップ901a、901bと、J〔0〕を出力するインバータ902aと、J〔1〕を出力するインバータ902bとを有している。第1段のD型フリップフロップ901aの出力は第2段のD型フリップフロップ901bに入力され、このD型フリップフロップ901bの反転出力はD型フリップフロップ901aに入力されている。すなわち、D型フリップフロップ901a、901bは全体としてループを構成している。また、D型フリップフロップ901aの反転出力はインバータ902aに入力され、D型フリップフロップ901bの反転出力はインバータ902bに入力される。

【0113】

以上の構成により、図11(b)に示すように、初期値オールゼロの状態からCLKの周期分だけ位相が異なる位相シフトコードJ[1:0]を生成できる。

【0114】

また、図12(a)に示すように、4段のD型フリップフロップ901a、901b、901c、901dを通常のシフトレジスタと同様に直列に接続するとともに、最終段のD型フリップフロップ901dの反転出力を第1段のD型フリップフロップ901aに入力することで、インバータ902a、902b、902c、902dからそれぞれCLKの周期分だけ位相がずれたJ〔0〕、J〔1〕、J〔2〕、J〔3〕を出力できる。すなわち、図12(a)に示す構成によれば、図12(b)に示すように、初期値オールゼロの状態からCLKの周期分だけ位相が異なる位相シフトコードJ[3:0]を生成できる。

【0115】

なお、第1の構成例に係るジョンソンカウンタの場合、これを駆動するために周波数の高いクロック信号(図11、図12におけるCLK、図5におけるクロック信号121)の入力が必要である。しかし、位相シフトコード生成回路は全列のカラムA/D変換回路に対して1つ設けられていればよいため、位相シフトコード生成回路に高い周波数のクロック信号が供給されても、クロック信号のなまりが発生する等の不具合は起こらない。そのため、第1の構成例によれば、波形なまりなどの不具合を発生させることなく位相シフトコードを生成することが可能である。

【0116】

図12(a)に示す位相シフトコード生成回路はビット数が2m−1=4の場合であり、これを第3の実施形態として説明したMOSセンサに搭載する場合、バイナリのみを用いてA/D変換する場合に比べて、信号の最大周波数を8分の1にすることができ、グレイコードのみの場合に比べて、4分の1の周波数にまで周波数を抑制することができる。あるいは、グレイコードのみを用いるA/D変換回路と同じ周波数のクロック信号を用いる場合、バイナリのみの場合に比べて3ビットの精度向上、グレイコードのみの場合に比べて2ビットの精度向上が可能である。

【0117】

なお、ビット数が2、4の場合の位相シフトコード生成回路の構成をそれぞれ説明したが、ビット数分のD型フリップフロップを直列に接続し、最終段のD型フリップフロップの反転出力を第1段のD型フリップフロップに入力することで、任意のビット幅に対応した位相シフトコード生成回路を構成することができる。

【0118】

−位相シフトコード生成回路の第2の構成例−

周波数が非常に高くなってきた場合、クロック信号を分配する際の波形なまりの問題以前に、素子性能の限界などから高速クロックの生成が困難になってくる。これに対して、遅延ロックループ回路(以下、DLL)を用いることで、入力クロック信号の周波数を位相シフトコード生成回路を生成する位相シフトコードと同じ周波数レベルに入力クロック周波数を抑えることができる。

【0119】

図13(a)〜(c)は、DLLを用いた第2の構成例に係る位相シフトコード生成回路を示す図である。

【0120】

まず、図13(a)に示す位相シフトコード生成回路の構成例は、位相比較器802と、電荷ポンプ回路803と、遅延部801とを有している。この構成例では、位相比較器802に入力されたクロック信号RCLK(ラッチ用クロック信号)を遅延部801により遅延し、DCLKとして出力する。具体的には、遅延量がちょうど1サイクルになるように、RCLKとDCLKとを位相比較器802で比較し、早い/遅いというずれに対してUPまたはDOWNの信号を生成し、電荷ポンプ回路803が位相比較器802からの信号を受けてこれに応じた電圧信号VCONを生成する。

【0121】

遅延部801は、図13(b)に示すように、インバータ804を多段に接続してなるインバーターチェーンに負荷としての容量806をNMOSトランジスタスイッチ(以下、MOSスイッチと称す)805を介して付加した回路である。VCONはこの容量806に接続されるMOSスイッチ805のゲート電位を制御する。このVCONを高くすると、MOSスイッチ805のオン抵抗が小さくなり、容量が負荷として重くなり、遅延が大きくなる。逆にVCONの電位を低くするとMOSスイッチ805のオン抵抗が大きくなり、容量が負荷として軽くなり、遅延は小さくなる。

【0122】

図14は、図13(a)、(b)に示すDLLの回路構成を利用し、π/2m−1ずつ位相がずれた信号を出力する位相シフトコード生成回路の構成例を示す図である。

【0123】

図14に示すように、元のクロック信号(RCLK)と16個の遅延段を経た遅延クロック(DCLK)の位相を揃えるDLLの働きにより、遅延段毎に1サイクルの16分の1ずつ遅延(位相遅延π/8)させたクロック信号n〔1〕、n〔2〕、…、n〔15〕、n〔16〕(=DCLK)を得ることができる。このうち隣接する8つのノードからクロック信号(例えば、n〔1〕〜n〔8〕をクロックバッファ807によりバッファされたD〔1〕〜D〔8〕)を取り出すことで、図14に示す回路は位相シフトコード生成回路として使用可能になっている。なお、ノードn〔9〕〜n〔16〕からクロックを取り出す必要はないが、各遅延段における負荷を均等にしてタイミング精度を上げるために、これらのノードにもバッファを付ける方がより望ましい。

【0124】

以上では、特定のビット幅の位相シフトコードを生成する第2の構成例の位相シフトコード生成回路について説明したが、位相シフトコード生成回路中のシフトレジスタ段数、またはDLLの遅延段数を変えることで、ビット幅の異なる位相シフトコードを容易に生成することができる。

【0125】

なお、図14に示す位相シフトコード生成回路はビット幅m=4の場合であり、これを第3の実施形態として説明したMOSセンサに搭載する場合、信号の最大周波数を、バイナリのみを用いてA/D変換を行う場合に比べて16分の1、グレイコードのみを用いてA/D変換を行う場合に比べて8分の1にまで抑制することができる。または、同じ周波数の信号を使う場合、バイナリのみの場合に比べて4ビット分の精度向上を実現でき、グレイコードのみの場合に比べて3ビット分の精度向上が可能である。

【0126】

本発明のその他の実施形態において、ジョンソンカウンタを用いた位相シフトコード生成回路を搭載することで、RC負荷が大きいカラムA/D変換回路部などに分配するクロック信号、ないしは計数値信号に、むやみに急峻な立ち上がり・立下り特性を要求する必要がなくなるという効果を有する。

【0127】

また、DLLを用いた位相シフト生成回路を搭載することで、各列のカラムA/D変換回路に分配される(クロック)信号だけでなく、クロック生成回路で生成されるクロック信号に関しても、GHz級のクロック信号を生成をしなくてよいという設計上のスペック緩和が可能となる。そのため、撮像素子(固体撮像装置)に必須の高画質プロセスに対して必ずしも相容れない特性を備える高速CMOSプロセスを無理に融合する必要がなくなるという効果を有する。また、システムとしても撮像素子の中のノイズ低減や電磁輻射の低減につながるという効果を有する。

【0128】

また、図15(a)、(b)は、図5、図8に示す2m−1ビット位相シフトコード/バイナリ変換器113の構成例を示す図である。図15(a)は、ビット幅m=2の場合を示し、(b)は、ビット幅m=3の場合を示す。

【0129】

図15(a)に示すように、m=2の場合、位相シフトコード/バイナリ変換器に入力された位相シフトコードのPS〔0〕およびPS〔1〕は共に排他的論理和回路905に入力され、排他的論理和回路905でバイナリのBIN〔0〕に変換される。また、位相シフトコードの最上位ビットであるPS〔1〕はそのままバイナリの最上位ビットBIN〔1〕として出力される。

【0130】

また、図15(b)に示すように、m=3の場合、排他的論理和回路905が三個設けられ、一段目の排他的論理和回路905aにはPS〔0〕とPS〔2〕が入力され、同じく一段目の排他的論理和回路905bにはPS〔1〕とPS〔3〕が入力される。排他的論理和回路905a、905bの出力は二段目の排他的論理和回路905cに入力され、排他的論理和回路905cからはバイナリの最下位ビットBIN〔0〕が出力される。バイナリのBIN〔1〕は排他的論理和回路905bから出力され、バイナリの最上位ビットBIN〔2〕としては、位相シフトコードの最上位ビットPS〔3〕がそのまま出力される。このように、位相シフトコードからバイナリへの変換は、排他的論理和回路を組み合わせて容易に行うことができる。

【産業上の利用可能性】

【0131】

以上説明したように、本発明の固体撮像装置およびその駆動方法は、光や放射線など種々の物理量分布を検知するための撮像装置に有用である。

【図面の簡単な説明】

【0132】

【図1】本発明の第1の実施形態に係る固体撮像装置(MOSセンサ)の構成を示す図である。

【図2】(a)は、第2の従来例に係るMOSセンサのカラムA/D変換回路における動作波形を示す図であり、(b)は、第1の実施形態に係るMOSセンサのA/D変換回路における動作波形を示す図である。

【図3】(a)は、第2の従来例に係るMOSセンサのカラムA/D変換回路における動作波形を示す図であり、(b)は、第1の実施形態に係るMOSセンサのカラムA/D変換回路における動作波形を示す図である。

【図4】第1の実施形態に係るMOSセンサの変形例を示す図である。

【図5】本発明の第2の実施形態に係るMOSセンサの構成を示す図である。

【図6】第2の実施形態に係るMOSセンサにおいて、A/D変換値の下位4ビット分を位相シフトコードに置き換えた場合の波形図である。

【図7】本発明の第3の実施形態に係るMOSセンサの構成を示す図である。

【図8】第3の実施形態に係るMOSセンサの変形例を示す図である。

【図9】第3の実施形態に係るMOSセンサの変形例を示す図である。

【図10】第1の実施形態に係るMOSセンサのカラムA/D変換回路内に出力用メモリを設けた場合のMOSセンサを示す図である。

【図11】(a)は、ジョンソンカウンタを用いた第1の構成例に係る2m−1ビット位相シフトコード生成回路を示す回路図であり、(b)は、第1の構成例に係る2m−1ビット位相シフトコード生成回路における信号波形を示す図である。

【図12】(a)は、ジョンソンカウンタを用いた第1の構成例に係る2m−1ビット位相シフトコード生成回路を示す回路図であり(b)は、第1の構成例に係る2m−1ビット位相シフトコード生成回路における信号波形を示す図である。

【図13】(a)〜(c)は、DLLを用いた第2の構成例に係る2m−1ビット位相シフトコード生成回路を示す図である。

【図14】図13(a)、(b)に示すDLLの回路構成を利用し、π/2m−1ずつ位相がずれた信号を出力する2m−1ビット位相シフトコード生成回路の構成例を示す図である。

【図15】(a)、(b)は、図5、図8に示す2m−1ビット位相シフトコード/バイナリ変換器113の構成例を示す図である。

【図16】第1の従来例に係るMOSセンサの構成を示す図である。

【図17】第2の従来例に係るMOSセンサの構成を示す図である。

【図18】(a)は、第1の従来例と同タイプのMOSセンサのデジタルメモリに供給されるクロック信号とデジタルメモリの位置の関係を概略的に示す図であり、(b)は、クロック周波数がfである場合の(a)における点Aと点Cでのクロック波形を示す図であり、(c)は、クロック周波数が2fである場合の(a)における点Aと点Cでのクロック波形を示す図である。

【符号の説明】

【0133】

101 画素

102 画素アレー

103 読み出し信号線

104 バイナリカウンタ

105 DAC

106 カラムA/D変換回路

107 比較器

108 デジタルメモリ

109 出力バッファ

112 π/2m−1位相シフトコード生成回路

113 位相シフトコード/バイナリ変換器

117 減算器

119 インバータ

120 クロック生成回路

121 クロック信号

122 アナログランプ電圧

123 比較器出力信号

125 位相シフトコード

126、127、128、228、327、348 出力信号バス

130 カウントモード切替信号

131 Up用ラッチ選択信号

132 Down用ラッチ選択信号

141 反転クロック信号

208 カラムカウンタ

218 U/Dカウンタ

308 ラッチ

318 U用ラッチ

328 D用ラッチ

338 シーケンサ

358 U用2m−1ビット・ラッチ

368 D用2m−1ビット・ラッチ

408 2m−1ビット・ラッチ

801 遅延部

802 位相比較器

803 電荷ポンプ回路

804 インバータ

805 MOSスイッチ

806 容量

807 クロックバッファ

901a、901b、901c、901d D型フリップフロップ

902a、902b、902c、902d インバータ

905、905a、905b 排他的論理和回路

【特許請求の範囲】

【請求項1】

物理量を検知する感応素子が行列状に配置されてなる感応素子アレーと、

前記感応素子の1列、または複数列ごとに設けられ、各列の前記感応素子から出力される信号をデジタル信号に変換するためのカラムA/D変換回路と、

各列の前記カラムA/D変換回路から出力されるデジタル信号を伝送する出力信号バスと、

前記カラムA/D変換回路にカウンタ用クロック信号とラッチ用クロック信号とを供給するクロック生成回路と、

三角波を出力するD/Aコンバータとを備えた物理量検知装置であって、

前記各カラムA/D変換回路は、

所定の期間に前記感応素子から出力される前記信号と前記三角波の電位とを比較する比較器と、

前記カウンタ用クロック信号のパルスをカウントするとともに、前記比較器の出力が変化する時点での計数値を保持するカラムカウンタと、

前記ラッチ用クロック信号を受け、前記比較器からの出力が変化する時点での前記ラッチ用クロック信号の値を保持する1個または複数個のラッチを有し、前記カラムカウンタの計数値と前記ラッチが保持する値とを組み合わせて表現されるA/D変換値に応じた大きさの前記デジタル信号を前記出力信号バスに出力する物理量検知装置。

【請求項2】

前記感応素子は受光部を有する画素であり、

前記感応素子アレーは画素アレーであり、

前記物理量検知装置は固体撮像装置であることを特徴とする請求項1に記載の物理量検知装置。

【請求項3】

前記ラッチ用クロック信号は周波数が異なるs個の信号または周波数が同じで位相が異なるs個の信号を含んでおり、

前記ラッチは複数個設けられ、且つ前記s個のクロック信号をそれぞれ保持しており、

前記ラッチに保持された値は前記A/D変換値の下位mビット(mは正の整数)を表現し、s=2(m−1) であることを特徴とする請求項1または2に記載の物理量検知装置。

【請求項4】

前記カウンタ用クロック信号の周波数は前記ラッチ用クロック信号と同じ周波数であることを特徴とする請求項3に記載の物理量検知装置。

【請求項5】

前記各カラムA/D変換回路は、

前記カラムカウンタに保持された計数値と前記ラッチに保持された値とをコピーするための出力用メモリをさらに有しており、

前記物理量検知装置は、各列の前記出力用メモリに保持された前記A/D変換値を順次選択して前記出力信号バスに出力させる列選択手段をさらに備えていることを特徴とする請求項1〜4のうちいずれか1つに記載の物理量検知装置。

【請求項6】

前記クロック生成回路から出力された周波数fのクロック信号から、周波数がfで位相がπ/sずつずれたs個の信号を生成して前記ラッチに供給する位相シフトコード生成回路をさらに備えていることを特徴とする請求項3に記載の物理量検知装置。

【請求項7】

位相シフトコードで表現された前記ラッチの出力をバイナリコード表現に変換する位相シフトコード/バイナリ変換器をさらに備えていることを特徴とする請求項6に記載の物理量検知装置。

【請求項8】

前記クロック生成回路から出力された周波数fのクロック信号から、周波数がf/(2s)で位相がπ/sずつずれたs個の信号を生成して前記ラッチに供給する位相シフトコード生成回路をさらに備えていることを特徴とする請求項3に記載の物理量検知装置。

【請求項9】

前記位相シフトコード生成回路には前記クロック信号が入力され、

前記位相シフトコード生成回路は複数の遅延段を含み、周波数が互いに同一で位相がπ/sずつずれたs個の信号を出力するDLL回路を有することを特徴とする請求項6または7に記載の物理量検知装置。

【請求項10】

前記クロック生成回路から出力されたクロック信号を受け、前記D/Aコンバータにバイナリ値を出力するバイナリカウンタをさらに備え、

前記D/Aコンバータは、前記バイナリ値の入力に応じて前記三角波を出力することを特徴とする請求項1〜9のうちいずれか1つに記載の物理量検知装置。

【請求項11】

前記カラムカウンタでの計数値は、前記カウンタ用クロック信号の立ち上がりエッジまたは立ち下がりエッジで変化することを特徴とする請求項1〜10のうちいずれか1つに記載の物理量検知装置。

【請求項12】

前記カラムカウンタでの計数値は前記カウンタ用クロック信号の立ち上がりエッジで変化し、

前記物理量検知装置は、前記クロック生成回路と各列の前記ラッチとの間に介設された第1のインバータ、または各列の前記ラッチからの出力信号を反転させる第2のインバータを備えていることを特徴とする請求項1〜11のうちいずれか1つに記載の物理量検知装置。

【請求項13】

前記ラッチに保持された値はバイナリコードにより前記A/D変換値の最下位側の1ビットまたは複数ビットを表現していることを特徴とする請求項1または2に記載の物理量検知装置。

【請求項14】

前記カラムカウンタは前記感応素子から出力された信号の上位ビットをアップカウントするとともに、リセット時に前記感応素子から出力された信号の上位ビットをダウンカウントするアップダウンカウンタであり、

前記ラッチは、前記感応素子から出力された信号の下位ビットを保持するアップ用ラッチと、リセット時の前記感応素子から出力される信号の下位ビットを保持するダウン用ラッチとで構成されており、

前記出力信号バスには、前記アップ用ラッチの出力、前記ダウン用ラッチの出力、および前記カラムカウンタにおけるアップカウント時の計数値とダウンカウント時の計数値の差分が列ごとに出力されることを特徴とする請求項1〜13のうちいずれか1つに記載の物理量検知装置。

【請求項15】

物理量を検知する感応素子が行列状に配置されてなる感応素子アレーと、前記感応素子の1列、または複数列ごとに設けられ、各々が比較器と、カラムカウンタと、1個または複数個のラッチとを有し、各列の前記感応素子から出力される信号をデジタル信号に変換するためのカラムA/D変換回路と、各列の前記カラムA/D変換回路から出力されるデジタル信号を伝送する出力信号バスと、前記カラムA/D変換回路にカウンタ用クロック信号とs個のラッチ用クロック信号とを供給するクロック生成回路と、三角波を出力するD/Aコンバータとを備えた物理量検知装置の駆動方法であって、

前記比較器が、前記感応素子から読み出された信号の電位と前記三角波の電位とを所定の期間に比較するステップ(a)と、

前記比較器による比較開始時から、前記カラムカウンタが前記カウンタ用クロック信号のパルスをカウントするステップ(b)と、

前記ステップ(b)の後、前記比較器からの出力が変化する時点で前記カラムカウンタに入力される前記カウンタ用クロック信号がマスクされ、前記カウンタ部の計数値を保持するステップ(c)と、

前記ステップ(b)の後、前記比較器からの出力が変化する時点でのs個の前記ラッチ用クロック信号のそれぞれの電位を前記ラッチが保持するステップ(d)と、

前記ステップ(d)で前記ラッチが保持する値を下位mビットとし、前記ステップ(c)で保持された前記カラムカウンタの計数値と組み合わせて表現される値をもとにして、所定の電圧のデジタル信号を前記カラムA/D変換回路が前記出力信号バスに出力するステップ(e)とを備えている物理量検知装置の駆動方法。

【請求項16】

前記物理量検知装置は、前記各カラムA/D変換回路内に設けられ、前記カラムカウンタの出力部および前記ラッチの出力部に接続された出力用メモリと、列選択手段とをさらに備えており、

前記ステップ(e)では、全列分の前記感応素子から読み出された信号について前記ステップ(c)、(d)が終了した後、前記カラムカウンタと前記ラッチで保持されている全列分のデジタル信号を前記出力用メモリにコピーした後、前記感応素子アレーの次の選択行に対する、前記ステップ(a)の動作と並行して、前記列選択手段により前記出力用メモリから各列の前記デジタル信号を順次前記出力信号バスに読み出すことを特徴とする請求項15に記載の物理量検知装置の駆動方法。

【請求項1】

物理量を検知する感応素子が行列状に配置されてなる感応素子アレーと、

前記感応素子の1列、または複数列ごとに設けられ、各列の前記感応素子から出力される信号をデジタル信号に変換するためのカラムA/D変換回路と、

各列の前記カラムA/D変換回路から出力されるデジタル信号を伝送する出力信号バスと、

前記カラムA/D変換回路にカウンタ用クロック信号とラッチ用クロック信号とを供給するクロック生成回路と、

三角波を出力するD/Aコンバータとを備えた物理量検知装置であって、

前記各カラムA/D変換回路は、

所定の期間に前記感応素子から出力される前記信号と前記三角波の電位とを比較する比較器と、

前記カウンタ用クロック信号のパルスをカウントするとともに、前記比較器の出力が変化する時点での計数値を保持するカラムカウンタと、

前記ラッチ用クロック信号を受け、前記比較器からの出力が変化する時点での前記ラッチ用クロック信号の値を保持する1個または複数個のラッチを有し、前記カラムカウンタの計数値と前記ラッチが保持する値とを組み合わせて表現されるA/D変換値に応じた大きさの前記デジタル信号を前記出力信号バスに出力する物理量検知装置。

【請求項2】

前記感応素子は受光部を有する画素であり、

前記感応素子アレーは画素アレーであり、

前記物理量検知装置は固体撮像装置であることを特徴とする請求項1に記載の物理量検知装置。

【請求項3】

前記ラッチ用クロック信号は周波数が異なるs個の信号または周波数が同じで位相が異なるs個の信号を含んでおり、

前記ラッチは複数個設けられ、且つ前記s個のクロック信号をそれぞれ保持しており、

前記ラッチに保持された値は前記A/D変換値の下位mビット(mは正の整数)を表現し、s=2(m−1) であることを特徴とする請求項1または2に記載の物理量検知装置。

【請求項4】

前記カウンタ用クロック信号の周波数は前記ラッチ用クロック信号と同じ周波数であることを特徴とする請求項3に記載の物理量検知装置。

【請求項5】

前記各カラムA/D変換回路は、

前記カラムカウンタに保持された計数値と前記ラッチに保持された値とをコピーするための出力用メモリをさらに有しており、

前記物理量検知装置は、各列の前記出力用メモリに保持された前記A/D変換値を順次選択して前記出力信号バスに出力させる列選択手段をさらに備えていることを特徴とする請求項1〜4のうちいずれか1つに記載の物理量検知装置。

【請求項6】

前記クロック生成回路から出力された周波数fのクロック信号から、周波数がfで位相がπ/sずつずれたs個の信号を生成して前記ラッチに供給する位相シフトコード生成回路をさらに備えていることを特徴とする請求項3に記載の物理量検知装置。

【請求項7】

位相シフトコードで表現された前記ラッチの出力をバイナリコード表現に変換する位相シフトコード/バイナリ変換器をさらに備えていることを特徴とする請求項6に記載の物理量検知装置。

【請求項8】

前記クロック生成回路から出力された周波数fのクロック信号から、周波数がf/(2s)で位相がπ/sずつずれたs個の信号を生成して前記ラッチに供給する位相シフトコード生成回路をさらに備えていることを特徴とする請求項3に記載の物理量検知装置。

【請求項9】

前記位相シフトコード生成回路には前記クロック信号が入力され、

前記位相シフトコード生成回路は複数の遅延段を含み、周波数が互いに同一で位相がπ/sずつずれたs個の信号を出力するDLL回路を有することを特徴とする請求項6または7に記載の物理量検知装置。

【請求項10】

前記クロック生成回路から出力されたクロック信号を受け、前記D/Aコンバータにバイナリ値を出力するバイナリカウンタをさらに備え、

前記D/Aコンバータは、前記バイナリ値の入力に応じて前記三角波を出力することを特徴とする請求項1〜9のうちいずれか1つに記載の物理量検知装置。

【請求項11】

前記カラムカウンタでの計数値は、前記カウンタ用クロック信号の立ち上がりエッジまたは立ち下がりエッジで変化することを特徴とする請求項1〜10のうちいずれか1つに記載の物理量検知装置。

【請求項12】

前記カラムカウンタでの計数値は前記カウンタ用クロック信号の立ち上がりエッジで変化し、

前記物理量検知装置は、前記クロック生成回路と各列の前記ラッチとの間に介設された第1のインバータ、または各列の前記ラッチからの出力信号を反転させる第2のインバータを備えていることを特徴とする請求項1〜11のうちいずれか1つに記載の物理量検知装置。

【請求項13】

前記ラッチに保持された値はバイナリコードにより前記A/D変換値の最下位側の1ビットまたは複数ビットを表現していることを特徴とする請求項1または2に記載の物理量検知装置。

【請求項14】

前記カラムカウンタは前記感応素子から出力された信号の上位ビットをアップカウントするとともに、リセット時に前記感応素子から出力された信号の上位ビットをダウンカウントするアップダウンカウンタであり、

前記ラッチは、前記感応素子から出力された信号の下位ビットを保持するアップ用ラッチと、リセット時の前記感応素子から出力される信号の下位ビットを保持するダウン用ラッチとで構成されており、

前記出力信号バスには、前記アップ用ラッチの出力、前記ダウン用ラッチの出力、および前記カラムカウンタにおけるアップカウント時の計数値とダウンカウント時の計数値の差分が列ごとに出力されることを特徴とする請求項1〜13のうちいずれか1つに記載の物理量検知装置。

【請求項15】

物理量を検知する感応素子が行列状に配置されてなる感応素子アレーと、前記感応素子の1列、または複数列ごとに設けられ、各々が比較器と、カラムカウンタと、1個または複数個のラッチとを有し、各列の前記感応素子から出力される信号をデジタル信号に変換するためのカラムA/D変換回路と、各列の前記カラムA/D変換回路から出力されるデジタル信号を伝送する出力信号バスと、前記カラムA/D変換回路にカウンタ用クロック信号とs個のラッチ用クロック信号とを供給するクロック生成回路と、三角波を出力するD/Aコンバータとを備えた物理量検知装置の駆動方法であって、

前記比較器が、前記感応素子から読み出された信号の電位と前記三角波の電位とを所定の期間に比較するステップ(a)と、

前記比較器による比較開始時から、前記カラムカウンタが前記カウンタ用クロック信号のパルスをカウントするステップ(b)と、

前記ステップ(b)の後、前記比較器からの出力が変化する時点で前記カラムカウンタに入力される前記カウンタ用クロック信号がマスクされ、前記カウンタ部の計数値を保持するステップ(c)と、

前記ステップ(b)の後、前記比較器からの出力が変化する時点でのs個の前記ラッチ用クロック信号のそれぞれの電位を前記ラッチが保持するステップ(d)と、

前記ステップ(d)で前記ラッチが保持する値を下位mビットとし、前記ステップ(c)で保持された前記カラムカウンタの計数値と組み合わせて表現される値をもとにして、所定の電圧のデジタル信号を前記カラムA/D変換回路が前記出力信号バスに出力するステップ(e)とを備えている物理量検知装置の駆動方法。

【請求項16】

前記物理量検知装置は、前記各カラムA/D変換回路内に設けられ、前記カラムカウンタの出力部および前記ラッチの出力部に接続された出力用メモリと、列選択手段とをさらに備えており、

前記ステップ(e)では、全列分の前記感応素子から読み出された信号について前記ステップ(c)、(d)が終了した後、前記カラムカウンタと前記ラッチで保持されている全列分のデジタル信号を前記出力用メモリにコピーした後、前記感応素子アレーの次の選択行に対する、前記ステップ(a)の動作と並行して、前記列選択手段により前記出力用メモリから各列の前記デジタル信号を順次前記出力信号バスに読み出すことを特徴とする請求項15に記載の物理量検知装置の駆動方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2009−38726(P2009−38726A)

【公開日】平成21年2月19日(2009.2.19)

【国際特許分類】

【出願番号】特願2007−203037(P2007−203037)

【出願日】平成19年8月3日(2007.8.3)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成21年2月19日(2009.2.19)

【国際特許分類】

【出願日】平成19年8月3日(2007.8.3)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]