画像データ処理装置及びプログラム

【課題】画像処理回路に対してラインメモリを介して画像データを供給する装置において、非可逆圧縮方式を用いる場合よりも画質劣化を抑えつつも、圧縮結果がラインメモリに収まらない場合があるという可逆圧縮方式の欠点を克服する。

【解決手段】DRP10の構成メモリ16には、2次元フィルタ処理用の回路構成として、生の画像データ1ライン分のラインメモリを複数備えた構成Xと、この構成よりも回路規模の小さい圧縮データ用の構成Yとが記憶されている。圧縮・最大圧縮ライン長判定部22は、処理単位(例えばページ)ごとに、その処理単位の画像データをラインごとに実際にランレングス圧縮し、その処理単位における圧縮ライン長の最大値Max-Lを求める。Max-Lが構成Yのラインメモリの容量以下であれば、構成選択部26は構成Yを選択し、そうでなければ構成Xを選択する。

【解決手段】DRP10の構成メモリ16には、2次元フィルタ処理用の回路構成として、生の画像データ1ライン分のラインメモリを複数備えた構成Xと、この構成よりも回路規模の小さい圧縮データ用の構成Yとが記憶されている。圧縮・最大圧縮ライン長判定部22は、処理単位(例えばページ)ごとに、その処理単位の画像データをラインごとに実際にランレングス圧縮し、その処理単位における圧縮ライン長の最大値Max-Lを求める。Max-Lが構成Yのラインメモリの容量以下であれば、構成選択部26は構成Yを選択し、そうでなければ構成Xを選択する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像データ処理装置及びプログラムに関する。

【背景技術】

【0002】

例えば、デジタル複写機やデジタル複合機(スキャナ、プリンタ、複写機等の機能を兼ね備えた装置)等の画像処理装置では、ライン順次の読取走査により画像データが生成され、生成された画像データに対し、生成順に、色空間変換や各種フィルタ処理等の画像処理が施される。ここで、例えばN×N画素(Nは2以上の整数)のデジタルフィルタを用いる二次元フィルタ処理では、例えば(N−1)ライン分のラインメモリに直近のラインの画像データを保持し、これら各ラインメモリのデータを現在読取中のラインの画像データと同期して読み出して、フィルタ回路に供給する。このような構成では、読取解像度の増大に伴い、ラインメモリの必要容量も大きくなる。

【0003】

このような課題に対し、特許文献1の装置では、読取走査により得られる各ラインの画像データを非可逆圧縮方式で圧縮してラインメモリに入力することで、小容量のラインメモリで対応可能としている。また、特許文献1の装置では、ラインごとに圧縮率を可変制御することで、各ラインの画像データがラインメモリの容量に収まるようにしている。

【0004】

特許文献2に開示される装置では、2次元フィルタ処理において、対象の画像を短冊状に分割することで、必要なラインメモリのサイズを削減している。

【0005】

特許文献3に開示される装置では、メモリ上の画像データをバンド単位で圧縮手段で圧縮して、該圧縮後のデータを、トグルバッファを介して画像メモリに転送して保管する。また、この装置では、圧縮前よりも圧縮後の方がそのデータ量が多くなって圧縮率が悪化する場合には、該バンドデータについては、該圧縮手段による圧縮前のバンドデータ(すなわち非圧縮のバンドデータ)を該画像メモリに転送して保管することで、圧縮手段の圧縮率が悪い場合にも、最悪、圧縮前のデータ量を維持している。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平11−331614号公報

【特許文献2】特開2002−304624号公報

【特許文献3】特開2009−055141号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明は、画像処理回路に対してラインメモリを介して画像データを供給する装置において、非可逆圧縮方式を用いる場合よりも画質劣化を抑えつつも、圧縮結果がラインメモリに収まらない場合があるという可逆圧縮方式の欠点を克服することを目的とする。

【課題を解決するための手段】

【0008】

請求項1に係る発明は、画像データをラインごとに可逆圧縮する可逆圧縮手段と、再構成可能回路上に、前記可逆圧縮手段の可逆圧縮により得られた圧縮データを保持するための第1のラインメモリと当該圧縮データを伸長するための伸長回路とを含む第1の構成と、非圧縮の前記画像データを保持するための第2のラインメモリを含む第2の構成と、を選択的に構成する制御を行う構成制御手段であって、前記第1のラインメモリの容量は、前記第1の構成の回路規模が前記第2の構成の回路規模以下となるように定められていることを特徴とする構成制御手段と、処理単位の画像データ内の各ラインを前記可逆圧縮手段で圧縮した場合のラインごとの圧縮データのデータサイズの最大値を判定する最大値判定手段と、前記最大値判定手段が判定した前記最大値が前記第1のラインメモリの容量に対応するあらかじめ定められた閾値以下である場合には、前記構成制御手段に対して前記第1の構成を前記再構成回路上に構成するよう指示すると共に、前記画像データの前記可逆圧縮手段による圧縮データを、前記第1のラインメモリを介して画像処理回路に出力し、前記最大値判定手段が判定した前記最大値が前記閾値を上回る場合には、前記構成制御手段に対して前記第2の構成を前記再構成回路上に構成するよう指示すると共に、非圧縮の前記画像データを、前記第2のラインメモリを介して前記画像処理回路に出力するよう制御する出力制御手段と、を備える画像データ処理装置である。

【0009】

請求項2に係る発明は、前記構成制御手段は、前記第1のラインメモリの容量が異なる複数の前記第1の構成を選択的に前記再構成可能回路上に構成可能であり、前記出力制御手段は、複数の前記第1の構成のうち前記第1のラインメモリの容量が前記最大値判定手段により判定された前記最大値以上であるものの中で、前記第1のラインメモリの容量が最小である第1の構成を、前記構成制御手段に構成させる、ことを特徴とする請求項1に記載の画像データ処理装置である。

【0010】

請求項3に係る発明は、前記最大値判定手段は、前記可逆圧縮手段に対して前記処理単位の画像データをラインごとに圧縮させ、この圧縮により得られた各ラインの圧縮データのデータサイズから前記最大値を判定し、前記出力制御手段は、前記最大値判定手段が判定した前記最大値が前記閾値以下である場合には、前記最大値判定手段の判定のための圧縮により得られた前記圧縮データを保存しておき、当該処理単位の画像データについて前記画像処理回路に処理させる際に、保存しておいた前記圧縮データを前記第1のラインメモリを介して前記画像処理回路に出力する、ことを特徴とする請求項1〜2のいずれか1項に記載の画像データ処理装置である。

【0011】

請求項4に係る発明は、前記出力制御手段がある処理単位の画像データ又は圧縮データを前記第1のラインメモリ又は前記第2のラインメモリを介して前記画像処理回路に出力している間に、前記可逆圧縮手段及び前記最大値判定手段が後続の別の処理単位についての圧縮及び前記最大値の判定を行う、ことを特徴とする請求項3に記載の画像データ処理装置である。

【0012】

請求項5に係る発明は、前記再構成可能回路上に構成されたラインメモリを含まない第3の回路構成に、ある処理単位についての処理を実行させている間に、前記可逆圧縮手段及び前記最大値判定手段がその処理単位より前の処理単位についての圧縮及び前記最大値の判定を行う、ことを特徴とする請求項3又は4に記載の画像データ処理装置である。

【0013】

請求項6に係る発明は、コンピュータを、画像データをラインごとに可逆圧縮する可逆圧縮手段、再構成可能回路上に、前記可逆圧縮手段の可逆圧縮により得られた圧縮データを保持するための第1のラインメモリと当該圧縮データを伸長するための伸長回路とを含む第1の構成と、非圧縮の前記画像データを保持するための第2のラインメモリを含む第2の構成と、を選択的に構成する制御を行う構成制御手段であって、前記第1のラインメモリの容量は、前記第1の構成の回路規模が前記第2の構成の回路規模以下となるように定められていることを特徴とする構成制御手段、処理単位の画像データ内の各ラインを前記可逆圧縮手段で圧縮した場合のラインごとの圧縮データのデータサイズの最大値を判定する最大値判定手段、前記最大値判定手段が判定した前記最大値が前記第1のラインメモリの容量に対応するあらかじめ定められた閾値以下である場合には、前記構成制御手段に対して前記第1の構成を前記再構成回路上に構成するよう指示すると共に、前記画像データの前記可逆圧縮手段による圧縮データを、前記第1のラインメモリを介して画像処理回路に出力し、前記最大値判定手段が判定した前記最大値が前記閾値を上回る場合には、前記構成制御手段に対して前記第2の構成を前記再構成回路上に構成するよう指示すると共に、非圧縮の前記画像データを、前記第2のラインメモリを介して前記画像処理回路に出力するよう制御する出力制御手段、として機能させるためのプログラムである。

【発明の効果】

【0014】

請求項1又は6に係る発明によれば、非可逆圧縮方式を用いる場合よりも画質劣化を抑えつつも、圧縮結果がラインメモリに収まらない場合があるという可逆圧縮方式の欠点を克服することができる。

【0015】

請求項2に係る発明によれば、処理単位の画像データを処理するのに必要な最小の回路規模の構成を選択することができる。

【0016】

請求項3に係る発明によれば、処理単位における各ラインの圧縮データのデータサイズの最大値を判定する処理と、それら各ラインの圧縮処理と、を別々に行う場合に比べて、演算処理に必要なコストを低減することができる。

【0017】

請求項4又は5に係る発明によれば、圧縮及び最大値の判定の処理に必要な時間の少なくとも一部分を、再構成可能回路が他の処理を行っている期間により隠蔽することができる。

【図面の簡単な説明】

【0018】

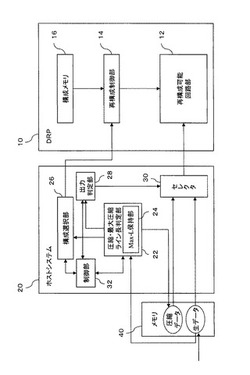

【図1】実施形態の画像データ処理装置の構成例を示す図である。

【図2】複数ライン分のラインメモリを備えた圧縮データ用の回路構成の一例を示す図である。

【図3】複数ライン分のラインメモリを備えた生データ用の回路構成の一例を示す図である。

【図4】画像圧縮及び回路構成の判定処理と、他の処理と、のコンカレント処理の例を説明するための図である。

【図5】画像圧縮及び回路構成の判定処理と、他の処理と、のコンカレント処理の別の例を説明するための図である。

【図6】実施形態の画像データ処理装置の全体的な処理手順の一例を示すフローチャートである。

【図7】圧縮・最大圧縮ライン長判定処理の手順の一例を示すフローチャートである。

【図8】出力判定処理の手順の一例を示すフローチャートである。

【図9】ラインメモリ長の異なる複数の回路構成(コンフィギュレーション)の情報を格納したデータベースのデータ内容の例を示す図である。

【図10】ラインメモリ長選択処理の手順の一例を示すフローチャートである。

【発明を実施するための形態】

【0019】

以下、図面を参照して、実施形態の画像データ処理装置の機能構成の例を説明する。図1に示す画像データ処理装置は、例えば、上位装置に内蔵又は接続され、上位装置から供給されたビットマップ画像データに対して画像処理を行う。上位装置は、プリンタ、スキャナ、ファクシミリ装置、デジタル複写機、デジタル複合機、デジタルカメラなどの画像処理装置であってもよいし、汎用コンピュータ装置であってもよい。

【0020】

図1に示す画像データ処理装置は、DRP(Dynamic Reconfigurable Processor:動的再構成可能プロセッサ)10、ホストシステム20及びメモリ40を備える。

【0021】

DRP10は、内部の論理回路の構成を動的(例えば1クロックの間)に変更(再構成)可能なプロセッサである。DRP10の一例としては、例えば特開2009−3765号公報に紹介されているDAP・DNAアーキテクチャのプロセッサがあるが、もちろんこれに限定されるものではない。DRP10は、再構成可能回路部12、再構成制御部14及び構成メモリ16を備える。

【0022】

再構成可能回路部12は、多数の論理回路要素を備えており、それら各論理回路要素の機能パラメータや論理回路要素同士の接続関係を動的に再構成(リコンフィギュレーション)可能となっている。再構成可能回路部12としては、例えば、特開2009−3765号公報に紹介されているDNAなど、様々な既存の又はこれから開発される回路を用いることができる。例えば、DNAは、PE(プロセッサエレメント)と呼ぶ論理回路要素を多数備えるアレイであり、それらPE間の接続構成を構成(コンフィギュレーション)データに従って高速(例えば1クロックの間に)組み替え可能となっている。

【0023】

再構成制御部14は、再構成可能回路部12内の論理回路要素の接続関係を制御することで、再構成可能回路部12上にデータ処理のための回路を再構成する。また、再構成制御部14は、再構成可能回路部12上に再構成された回路に対してホストシステム20からの指示に応じて入力データを供給したり、その回路からの出力データをホストシステム20に返したりする制御を行う。なお、特開2009−3765号公報で紹介されたDAP・DNAアーキテクチャをこの実施形態に採用した場合、再構成制御部14はDAPと呼ばれる汎用プロセッサコアで制御プログラムを実行することにより実現される(但し、これは一例に過ぎない)。

【0024】

再構成可能回路部12内の回路の再構成は、構成(コンフィギュレーション)メモリ16に記憶された構成(コンフィギュレーション)データに従って行われる。構成メモリ16には、複数の構成データが記憶される。DRP10は、ホストシステム20からの指示に応じて、構成メモリ16に新たな構成データを追加したり、構成メモリ16内の構成データを削除したりする機能を備える。

【0025】

ホストシステム20は、DRP10を制御して画像処理を実行させる制御システムである。ホストシステム20は、例えば、デジタル複合機等の上位装置からビットマップ画像データを受け取ってメモリ40に記憶し、この画像データをDRP10に処理させる。ホストシステム20は、後述する機能モジュール22〜30群をすべてハードウエア回路で実装することにより実現したものであってもよいし、すべてソフトウエアにより実装することにより実現したものであってもよいし、一部をハードウエア回路で実装し残りをソフトウエアで実装することにより実現したものであってもよい。ホストシステム20の機能モジュール群の一部又は全部をソフトウエアで実装する場合、そのソフトウエアのプログラムの実行は、(a)DRP10内のプロセッサが行ってもよいし、(b)DRP10と同じ基板上に実装されるプロセッサが行ってもよいし、(c)デジタル複合機等の上位装置のプロセッサが行ってもよいし、それらプロセッサのうちの2以上で分担して行ってもよい。例えば、(a)の場合、DRP10自体がこの実施形態の画像データ処理装置であり、(b)の場合、DRP10とプロセッサを搭載した基板がこの実施形態の画像データ処理装置であり、(c)の場合、DRP10と上位装置のプロセッサとの組合せがこの実施形態の画像データ処理装置である。メモリ40は、ランダムアクセスメモリ等の高速に読み書き可能な記憶装置であり、DRP10に内蔵されたものであってもよいし、DRP10と同じ基板に実装されるものであってもよいし、デジタル複合機等の上位装置のメモリであってもよい。

【0026】

ホストシステム20は、圧縮・最大圧縮ライン長判定部22、構成選択部26、出力判定部28、セレクタ30、制御部32を有する。

【0027】

圧縮・最大圧縮ライン長判定部22は、処理対象のビットマップ画像データをライン(走査線)ごとに圧縮すると共に、ラインごとの圧縮結果のライン長の最大値Max-Lを判定する(詳細は後述)。Max-L保持部24は、最大圧縮ライン長Max-Lを保持する記憶領域である。構成選択部26は、圧縮・最大圧縮ライン長判定部22が求めた最大圧縮ライン長Max-Lに基づき、再構成可能回路部12に再構成する回路構成(コンフィギュレーション)を選択する(詳細は後述)。出力判定部28は、最大圧縮ライン長Max-Lに基づき、ビットマップ画像データの生データ又は圧縮データのいずれをDRP10に出力するかを判定する。セレクタ30は、出力判定部28の判定結果に従い、ビットマップ画像データの生データ又は圧縮データのいずれか一方を選択してDRP10に供給する。制御部32は、ホストシステム20内の他の各機能モジュールを制御する。

【0028】

本実施形態の画像データ処理装置では、再構成可能回路部12に、2次元フィルタ処理などのように、複数のラインメモリを必要とする画像処理回路を再構成する。ここで、DRP10内に再構成するラインメモリ群の回路規模を小さくできるようにするために、本実施形態では、処理対象のビットマップ画像データを、圧縮・最大圧縮ライン長判定部22で圧縮している。圧縮・最大圧縮ライン長判定部22が行う画像データ圧縮として、以下ではランレングス圧縮方式を例にとる。ランレングス圧縮は、可逆圧縮であり、画質劣化がない。なお、以下に示す本実施形態の制御は、ランレングス圧縮以外の他の可逆圧縮方式を用いる場合でも同様に適用可能である。このように、可逆圧縮した画像データをラインメモリに入れる構成をとる場合、ラインメモリ内のデータを画像処理回路に入力する前に伸長する回路が必要となる。このように圧縮した画像データを受け入れて処理する場合に再構成可能回路部12に構成される回路構成の例を、図2に示す。

【0029】

図2に示す第1の回路構成100Aは、画像処理回路の一例として5×5画素の2次元フィルタ処理(例えば平均処理、エッジ強調処理などの各種フィルタ処理のうちのいずれか)を行うフィルタ処理回路106を備えるとともに、それぞれ1ページの画像のうちの1ライン(走査線)分の圧縮データを保持するための5つのラインメモリ102a〜102eを備える。各ラインメモリ102a〜102eはFIFO(先入れ先出し)方式のバッファメモリである。各ラインメモリ102a〜102eの容量は、互いに等しい値であり、それぞれ、あらかじめ想定した圧縮率に対応する1ライン分の圧縮データを収容することを想定した値である。初段のラインメモリ102aには、ホストシステム20側から圧縮データが入力される。ラインメモリ102aの出力は、伸長回路104aと、第2段のラインメモリ102bの入力とに接続されている。同様に、第2、3、4段のラインメモリ102b、102c、102dは、入力側がそれぞれ前段のラインメモリ102a、102b、102cの出力に接続されており、出力側がそれぞれ対応する伸長回路104b、104c、104dと第3、4、5段のラインメモリ102c、102d、102eの入力側に接続されている。また、第5段のラインメモリ102eの出力は、対応する伸長回路104eに接続されている。したがって、この回路構成では、ホストシステム20側からDRP10に入力される圧縮データは、まず初段のラインメモリ102aに入力され、その後順番に、第2、3、4、5段の102b、102c、102d、102eへと移動していくことになる。各時点では、5つのラインメモリ102a〜102eに、連続する5ライン分の圧縮データが保持されていることになる。

【0030】

また、各伸長回路104a〜104eの出力側は、それぞれFIFO(先入れ先出し)メモリを介してフィルタ処理回路106に接続されている。各FIFOメモリは、伸長回路104a〜104eからそれぞれ出力される伸長結果の画像データを、画素順に互いにタイミング合わせ(同期)してフィルタ処理回路106に供給するために用いられる、小容量のバッファメモリである。各FIFOメモリは、タイミング合わせがよいので、1ライン分の画像データの量よりもはるかに小さい容量でよい。フィルタ処理回路106は、各FIFOを介して順に供給される、隣接する5ラインの画像データに対して、フィルタ処理を実行し、フィルタ処理結果の画素値を順に出力する。フィルタ処理回路106から順に出力される各画素の値は、ホストシステム20に返される。

【0031】

さて、フィルタ処理を正常に実行するには、第1の回路構成100Aの各ラインメモリ102a〜102eには、それぞれ1ライン(走査線)分の圧縮データが収容されなければならない。しかし、圧縮対象の画像データの性質によって圧縮率は変わってくるので、ある決まった容量のラインメモリ102a〜102eに1ラインの圧縮データが必ず収まるとは限らない。利用する圧縮方式にもとの画像データの性質が適していない場合、もとの画像データよりも圧縮データの方が、データ量が大きくなる場合もある。そのような極端な場合も考慮したのでは、ラインメモリ102a〜102eのサイズが大きくなりすぎる。そこで、この実施形態では、1ライン分の圧縮データが第1の回路構成100Aの各ラインメモリ102a〜102eに収容できない場合のための備えとして、図3に示す第2の回路構成100Bを用意する。

【0032】

第2の回路構成100Bのフィルタ処理回路106は、第1の回路構成100Aのフィルタ処理回路106と同じものである。第2の回路構成100Bは、フィルタ処理回路106の前段に5つのラインメモリ108a〜108eを備える。各ラインメモリ108a〜108eは、それぞれ1ライン分のビットマップ画像データの量に対応する容量を持つ。初段のラインメモリ108aは、入力側がホストシステム20に接続されており、出力側がフィルタ処理回路106と第2段のラインメモリ108bの入力側とに接続されている。第2〜4段のラインメモリ108b、108c、108dは、入力側が各々の前段のラインメモリ108a、108b、108cの出力側に接続されており、出力側がフィルタ処理回路106と各々の次段のラインメモリ108c、108d、108eに接続されている。そして、第5段のラインメモリ108eの出力は、フィルタ処理回路106に接続されている。

【0033】

この第2の回路構成100Bには、ホストシステム20から生の画像データがラインごとに順に入力される。入力されたラインごとの画像データは、ラインメモリ108a〜108eを順に移動していくとともに、各ラインメモリ108a〜108eの出力側から互いに同期して(すなわちライン上での同一の画素番号の画素データが互いに同時に)フィルタ処理回路106に供給される。フィルタ処理回路106は、ラインメモリ108a〜108eを介して順に供給される、隣接する5ラインの画像データに対してフィルタ処理を実行し、フィルタ処理結果の画素値を順にホストシステム20に返す。

【0034】

DRP10の構成メモリ16には、以上に説明した第1の回路構成100Aを表す構成(コンフィギュレーション)データと第2の回路構成100Bを表す構成データとが少なくとも記憶されている。

【0035】

圧縮データ用の第1の回路構成100Aは、少なくとも、生(非圧縮)データ用の第2の回路構成100Bよりも回路規模(回路構成を実現するために使用する回路要素の数)が小さい。すなわち、各ラインメモリ102a〜102eの容量は、各ラインメモリ108a〜108eの容量から各伸長回路104a〜104eと各FIFOの回路規模に相当する容量を引いた容量よりも小さい。

【0036】

実用的には、ラインメモリのための回路規模の低減効果を得るために、第1の回路構成100Aは、第2の回路構成100Bよりもかなりの程度(例えば数割程度)小さくする。例えば、テキストのみの画像やテキストとグラフ等の図形からなる画像などのように、ランレングス圧縮等の可逆圧縮でも大きな圧縮率が得られる画像は少なくないので、第1の回路構成100Aの回路規模(すなわちラインメモリ102a〜102eの容量)をかなり小さくした場合でも、実用的にはかなり多くの画像に対して対応できる。そして、第1の回路構成100Aではラインメモリ102a〜102eに1ライン分の圧縮データが収まらない例外的なケースにのみ、第2の回路構成100Bを利用する。このような回路構成の切換利用を行うと、第1の回路構成100Aを用いている間は、第2の回路構成100Bを用いている間よりも、フィルタ処理のために使用する回路要素の数が少なくて済むので、空いた回路要素を別の処理のための回路のために用いる。

【0037】

本実施形態では、あらかじめ定めた画像データの処理単位ごとに、第1の回路構成100Aと第2の回路構成100Bとのうちの適切な方を選択して使用する。処理単位は、例えばページである。また、ページを分割したバンドを処理単位としてもよい。バンドは、あらかじめ定めた数の連続したライン(走査線)からなる画像部分である。以下では、処理単位を「ページ」とする場合の例を説明するが、ページ以外の処理単位(例えば「バンド」)を用いる場合にも、この実施形態の手法は同様に適用される。

【0038】

第1の回路構成100Aと第2の回路構成100Bとのいずれを用いるかの選択に当たり、本実施形態では、圧縮・最大圧縮ライン長判定部22により処理単位の画像データを実際に圧縮する。そして、その処理単位のすべてのラインの圧縮結果が第1の回路構成100Aのラインメモリ102a〜102eに完全に収容されることが確認されれば、第1の回路構成100Aを選択し、そうでなければ第2の回路構成100Bを選択する。また、少なくとも第1の回路構成100Aを選択した処理単位については、圧縮・最大圧縮ライン長判定部22による判定の際に求めた圧縮結果のデータをメモリ40に保存しておき、後でその処理単位の処理順序が来たときに、その圧縮データをDRP10上の第1の回路構成100Aに供給する。

【0039】

このように実際に画像データを圧縮してみることで圧縮率が十分かどうかを判定する方式では、画像データに対してDRP10による画像処理を実行する前に、その画像データを圧縮する必要がある。1つの例では、DRPが別の処理を実行中に、圧縮・最大圧縮ライン長判定部22がこの事前の圧縮及び判定の処理を行うことで、その圧縮処理に要する時間を隠蔽する。このような処理の一例を、図4を参照して説明する。

【0040】

図4の例では、画像データに対してDRP10を用いて2種類の画像処理a及びbを行う場合を想定する。このうち、画像処理aはラインメモリを必要としない処理(例えば、色空間変換などのように他のラインの画素値を参照しなくてよい処理)であり、画像処理bが複数ライン分のラインメモリを必要とする処理(例えば2次元フィルタ処理)であるとする。DRP10は、画像処理aについては単一の回路構成を用いるが、画像処理bについては上述の第1の回路構成100Aと第2の回路構成100Bを切り替えつつ使用するとする。また、図4の例ではページを処理単位としている。

【0041】

図4の例では、まずDRP10の再構成可能回路部12上に画像処理a用の回路構成「構成−a」を再構成し、その構成−aにより対象の文書の第1ページ(「ページ1」)及び第2ページの画像データを処理(図中の「ページ1−a」、「ページ2−a」)する。そして、第2ページについて画像処理aを実行している間に、第1ページの画像データについての画像処理aの処理結果をホストシステム20の圧縮・最大圧縮ライン長判定部22に圧縮させる。この圧縮処理により得られる圧縮データは、メモリ40に記憶される。また、圧縮・最大圧縮ライン長判定部22は、この圧縮処理により得られる各ラインの圧縮データのデータ長(以下、「圧縮ライン長」と呼ぶ)に基づき、構成選択部26が第1及び第2の回路構成100A及び100Bのうちのいずれの構成を採用するかを決定する。ここでは、第1の回路構成100A(圧縮データ用。図では「構成−bA」と表記)を採用すると判定されたとする。処理「ページ2−a」の終了後、構成選択部26の指示に応じて再構成制御部14が再構成可能回路部12を構成−bAへと再構成し、出力判定部28の制御に応じてセレクタ30が第1ページについての画像処理aの処理結果の圧縮データを選択し、その圧縮データを再構成可能回路部12上の構成−bAに供給して処理させる(図中の「ページ1−b」)。また、DRP10がこの処理「ページ1−b」を実行している間に、第2ページについての画像処理aの処理結果を圧縮・最大圧縮ライン長判定部22に圧縮させ、その圧縮結果に基づき、第1及び第2の回路構成100A及び100Bのうちのいずれの構成を採用するかを決定する。ここで第1の回路構成100A(「構成−bA」)を採用すると判定されたとすると、処理「ページ1−b」の後、回路構成を構成−bAのままとして、第2ページについての画像処理aの処理結果を、その構成−bAにより処理する(図中の「ページ2−b」)。以降、2ページごとに同様の処理を繰り返す。このような2ページごとの処理によれば、ラインメモリを用いる画像処理bのための回路構成の選択の処理に必要な時間が、別のページについての画像処理a(ラインメモリを用いない)の実行時間、又は先行するページについての画像処理bの実行時間の中に隠蔽されることになる。

【0042】

また、別の例として、図5に示す例がある。この例は、ラインメモリを用いる単一の画像処理を複数のページからなる文書に対して行う場合の例である。この例では、まず文書の第1ページの画像データを、ホストシステム20の圧縮・最大圧縮ライン長判定部22に圧縮させ、各ラインの圧縮ライン長に基づき、構成選択部26が第1ページに対して第1及び第2の回路構成100A及び100Bのうちのいずれの構成を採用するかを決定する。図5の例では、第1ページには第1の回路構成100A(圧縮データ用。図では「構成−A」と表記)を採用すると決定される。この決定の後、構成選択部26からの指示に従い、DRP10の再構成制御部14が、再構成可能回路部12上に第1の回路構成100Aを再構成する。その再構成の後、出力判定部28の制御により、セレクタ30が圧縮データ側を選択し、セレクタ30を介して再構成可能回路部12上の第1の回路構成100Aに対して第1ページの圧縮データが供給される。このようにしてDRP10が第1ページに対して画像処理を実行している間に、ホストシステム20は第2ページのための回路構成を第1及び第2の回路構成100A及び100Bのいずれにするかを選択する。図5の例では、第2ページに対して構成−Aが選択される。したがって、第1ページの画像処理が終わった後、再構成可能回路部12を構成−Aとしたまま、第2ページの圧縮データが構成−Aに供給され、処理される。そして、DRP10による第2ページの画像処理中に、ホストシステム20により第3ページの処理に用いる回路構成として第2の回路構成100B(生データ用。図では「構成−B」と表記)が選択され、第2ページについての画像処理の終了後、再構成可能回路部12の回路構成が構成−Bに変更され、セレクタ30により第3ページの生データが選択されて、再構成可能回路部12上の構成−Bにて処理される。以上のように、図5の例では、文書中の第2ページ以降については、画像データ圧縮及び回路構成の判定処理の所要時間が、DRP10による当該ページの直前のページの画像処理の期間の中に隠蔽される。

【0043】

図4の例から分かるように、異なる複数の画像処理のための回路をDRP10上に順に再構成する場合において、ラインメモリを用いる画像処理bの直前の画像処理aがラインメモリを用いない処理である場合には、判定対象のページについての画像処理aの実行後、その判定対象のページの後続の他のページに対して画像処理aを実行している間に、当該判定対象のページについての画像処理bのための回路構成の判定が行われる。

【0044】

また、図4及び図5の例から分かるように、判定対象のページに先行する他のページについて、ラインメモリを用いる画像処理bを実行中に、当該判定対象のページについての画像処理bのための回路構成の判定が行われる。

【0045】

さて、本実施形態では、圧縮データに対応するためのDRP10の回路構成として、ラインメモリの容量が異なる複数の回路構成を用意し、ページごとに、そのページに応じた容量のラインメモリを持つ回路構成を選択するようにしてもよい。これら複数の回路構成は、ラインメモリの長さは互いに異なるが、それ以外の構成、すなわちラインメモリの数、伸長回路104a〜104e、フィルタ処理回路106などは、互いに共通である。この例では、用意した複数の回路構成のうち、例えば、圧縮・最大圧縮ライン長判定部22が求めた当該ページの最大圧縮ライン長を収容可能な最小容量のラインメモリを持つ回路構成を選択する。当該ページの処理に必要な最小のラインメモリを持つ回路構成を選択することで、再構成可能回路部12の回路要素のうち当該画像処理に使用するものの数が少なくなり、他の処理に適用可能な空き回路要素が増える。

【0046】

次に、本実施形態の画像データ処理装置の処理手順の一例を説明する。図6は、画像データ処理装置の全体的な処理手順の一例を示す。図6の手順は、ラインメモリを用いる画像処理(便宜上「画像処理X」と呼ぶ)についての処理手順である。

【0047】

図6の手順では、ホストシステム20の制御部32は、まずページ番号を表す変数nの値を1(すなわち画像処理Xの対象の文書の最初のページの番号)に設定し(S10)、上位システムからメモリ40内に供給された対象文書のデータのうち、第nページの画像データにアクセスする(S12)。そして、制御部32は、その第nページの画像データを圧縮・最大圧縮ライン長判定部22に処理させる(S14)。S14の処理により、メモリ40には第nページの圧縮データが記憶され、またMax-L保持部24には第nページの各ラインの圧縮結果のうちの最大長の値(=最大圧縮ライン長Max-L)が保持される。なお、S14の詳細な手順の例は、後で図7を参照して説明する。

【0048】

S14の後、出力判定部28により、DRP10に対して出力する第nページのデータを、圧縮データとするか、生データ(非圧縮のデータ)とするかを判定する(S16)。なお、S16の詳細な手順の例は、後で図8を参照して説明する。S16にて圧縮データを出力すると判定された場合(S18の判定結果がY)、制御部32は、構成選択部26に、圧縮データ用に用意したラインメモリの容量の異なる複数の第1の回路構成100Aの中から、第nページの処理に用いる回路構成を選択させる(S20)。なお、S20の詳細な手順の例は、後で図10を参照して説明する。S16にて生データを出力すると判定された場合(S18の判定結果がN)、制御部32は、構成選択部26に、生データ用の回路構成(第2の回路構成100B)を選択させる(S22)。

【0049】

そして、制御部32は、第nページについての画像処理XをDRP10に実行させるタイミングが来ると、構成選択部26を介してDRP10の再構成制御部14に対して、S20又はS22で選択した回路構成の再構成を指示する(S24)。なお、S24では、第nページについて選択された回路構成が、再構成可能回路部12上に既に構成されている場合は、再構成は行わなくてもよい。そして、制御部32は、セレクタ30を、圧縮データ出力又は生データ出力のうち、出力判定部28によるS16の判定結果に応じた方に切り替え、その切り替えに応じてセレクタ30を介して出力される第nページの圧縮データ又は生データを、再構成可能回路部12上に構成された回路構成に処理させる(S26)。このS24及びS26の実行中に、コンカレント(同時並列的)に、ホストシステム20が、後続のページについてS12〜S22の処理を実行してもよい。

【0050】

そして、未処理のページがあれば(S28の判定結果がY)、ページ番号nを1だけ増加させ(S30)、S12に戻る。以上に説明したS12〜S30の処理を対象文書の全ページについて繰り返した後、図6の処理は終了する。

【0051】

次に、図7を参照して、図6のS14の詳細な処理手順の一例を説明する。図7の手順は、画像データの可逆圧縮処理として、ランレングス圧縮方式を用いる場合の例である。図7の手順は、ページごとに実行される。

【0052】

図7の手順では、まず圧縮・最大圧縮ライン長判定部22は、Max-L保持部24に保持される最大圧縮ライン長Max-Lを初期化する(図7の例では、初期値は0)(S102)。次に、1ライン(走査線)内での注目画素の番号を示す画素カウンタPixCtr、ラン長RunLen、圧縮ライン長L−cntの変数をそれぞれ0に初期化する(S104)。次に、圧縮・最大圧縮ライン長判定部22は、メモリ40内の圧縮対象のページの先頭画素から順に、ラスター走査順に各画素のデータを入力する。この入力は、ページの最後の画素まで1画素ずつ行われる。そして、1画素入力するごとに、入力したその画素の値を変数「現画素」に代入するとともに(S108)、現時点での画素カウンタPixCtrの値が0であるかどうかを判定し(S110)、0であれば(S110の判定結果がY)、「現画素」の1つ前の画素の値を保持する変数「前画素」に対し、現画素の値を代入する(S112)。S112は、ラインの先頭の画素についての「前画素」を設定するため、及びランが切れた場合(後述するS116の判定結果がNとなった場合)の「前画素」の初期設定のための処理である。なお、S110の判定結果がNの場合は、S112は実行しない。そして、圧縮・最大圧縮ライン長判定部22は、画素カウンタPixCtrの値を1増加させる(S114)。

【0053】

次に、圧縮・最大圧縮ライン長判定部22は、現画素と前画素の画素値が等しいかどうかを判定する(S116)。等しい場合(S116の判定結果がY)、画素カウンタPixCtrの値がページのライン長(すなわちページの主走査方向の画素数)に達したかどうかを判定し(S118)、達していなければ、ラン長RunLenを1だけ増加させるとともに、(S120)、S106に戻ってメモリ40から次の画素を入力する。この場合、ラン長RunLenはS124で「0」に初期化されているので、S110の判定結果がYとなり、S112で「前画素」が「現画素」の値に初期化される。

【0054】

ランが続いている間、すなわち同じ値の画素が連続している間は、S116〜S120によりラン長RunLenがインクリメントされていくことになる。そして、ランがとぎれた場合、S116で現画素が前画素と異なると判定された場合は、そのランを表す符号を、現在のラン長RunLenの値と前画素のデータ値との組合せから求める(S122)。求められた符号は、メモリ40内の当該ページの圧縮データの末尾に追加される。その後、圧縮・最大圧縮ライン長判定部22は、ラン長RunLenの値を0に初期化し、S122で求めた符号の符号長を圧縮ライン長L−cntに加算し(S124)、S106に戻ってメモリ40から次の画素を入力する。この場合、ラン長RunLenはS120でインクリメントされており「0」ではないので、S110の判定結果がNとなり、S112はスキップされる。

【0055】

また、図7の処理では、符号化を1ラインごとに完結させるので、S116で現画素の値が前画素の値と等しいと判定した場合でも、画素カウンタPixCtrの値がライン長に達していれば(S118の判定結果がY)、圧縮・最大圧縮ライン長判定部22は、そのランを表す符号を、現在のラン長RunLenの値と前画素のデータ値との組合せから求める(S126)。そして、S126で求めた符号の符号長を圧縮ライン長L−cntに加算し(S128)、その加算結果の値を、Max-L保持部24に保持された原次元での最大圧縮ライン長Max-Lと比較する(S130)。加算結果が現時点のMax-Lより大きければ(S130の判定結果がY)、その加算結果をMax-Lに代入する(S132)。加算結果が現時点のMax-L以下であれば、Max-Lの値は更新しない。以上の処理の後、S104に戻り、次のラインについての処理を行う。

【0056】

以上に説明した処理を、ページの最後の画素まで繰り返す。ページの最後の画素まで処理を完了すると(S106の判定結果がY)、圧縮・最大圧縮ライン長判定部22は、Max-L保持部24に保持している最大圧縮ライン長Max-Lの値を、当該ページのページ番号と対応づけて制御部32に出力する(S34)。制御部32は、この最大圧縮ライン長の値を構成選択部26及び出力判定部28に供給する。

【0057】

次に、図8を参照して、出力判定部28の処理手順の一例を説明する。図8の手順において、出力判定部28は、制御部32から供給された当該ページの最大圧縮ライン長Max-Lが、用意している複数の回路構成のラインメモリ長(「最大ラインメモリ長」と予備)の最大値よりも大きいかどうかを判定する(S142)。

【0058】

例えば、実施形態の画像データ処理装置が、ラインメモリを使用するある画像処理のための回路構成として、図9に示すように、ラインメモリ長の異なるN個の回路構成を有しているとする。図9の例では、回路構成を識別する番号(「構成番号」)が若いほど、ラインメモリ長が長い。構成番号1の回路構成は用意された回路構成の中で最大の回路規模を有するが、その回路規模でも、生データ用の回路構成よりは回路規模が小さい。この場合、最大ラインメモリ長は、構成番号1のラインメモリ長Config-Line(1)のことであり、S142では、ラインメモリ長Config-Line(1)と最大圧縮ライン長Max-Lとを比較する。

【0059】

そして、Max-Lが最大ラインメモリ長より大きければ(S142の判定結果がY)、当該ページについては圧縮データではなく生データをDRP10に出力すべきと判定する(S144)。また、Max-Lが最大ラインメモリ長以下であれば(S142の判定結果がN)、当該ページについては圧縮データをDRP10に出力すべきと判定する(S146)。

【0060】

出力判定部28は、例えば、図8の手順により判定した各ページについての判定結果をFIFOメモリ(図示省略)に保持し、制御部32から新たなページの出力を指示されるごとに、FIFOメモリの先頭の判定結果を取り出し、その判定結果に応じてセレクタ30を切り替える。なお、制御部32は、例えば、DRP10からページの画像処理の終了を表す信号を受け取るごとに、出力判定部28に対して新たなページの出力指示を行う。

【0061】

次に、図10を参照して、構成選択部26の処理手順の一例を説明する。この処理のために、画像データ処理装置は、各回路構成のラインメモリ長を表す図9に例示したようなデータを保持しているとする。図10の手順では、構成選択部26は、まず回路構成を識別する構成番号nを1に初期化し、第n番目の回路構成のラインメモリ長Config-Line(n)から最大圧縮ライン長Max-Lを減算した減算結果ΔEの最小値MinΔEを、あらかじめ定めた大きい定数(図では「High」と表記)に初期化する(S152)。すなわち、この手順では、構成番号が若い、すなわちラインメモリ長が大きい回路構成から順に、当該ページにとって適切であるかどうかを判定していく。次に、ΔEを計算し(S154)、計算結果のΔEが0より小さいかどうかを判定する(S156)。図10の処理は、S16(図8の処理手順)でMax-Lが最大ラインメモリ長(=構成番号1のラインメモリ長)以下であると判定された場合にしか実行されないので、構成番号n=1のときにS154で求められるΔEは必ず正の値であり、S156の判定結果はNとなる。次に、ΔEがMinΔEよりも小さいかどうかを判定する(S158)。小さければ、ΔEをMinΔEに代入するとともに、変数Min−nに対して現在の構成番号nを代入する(S160)。変数Min−nは、当該ページに対する現時点での最適な回路構成(すなわち、ラインメモリ長が当該ページの最大圧縮ライン長以上の回路構成のうち、ラインメモリ長が最小のもの)の番号を保持する変数である。S160の後、構成番号nの値を1増加させ(すなわち今検査し終えた回路構成よりもラインメモリ長が1段階短い回路構成を次の検査対象として)(S162)、S154に戻る。

【0062】

そして、S156の判定結果がYとなる(すなわち、ΔEの値が0より小さくなる)まで、S154〜S162の処理を繰り返す。そして、S156の判定結果がYとなると、その時点の変数Min−nの値を、当該ページに対する最適な回路構成の識別番号とする(S164)。

【0063】

構成選択部26は、例えば、図10の手順により判定した各ページについての最適な回路構成の識別番号をFIFOメモリ(図示省略)に保持し、制御部32から新たなページのための回路再構成を指示されるごとに、FIFOメモリの先頭の番号を取り出し、その再構成制御部14に対してその番号の回路構成への切り替えを指示する。なお、制御部32は、例えば、DRP10からページの画像処理の終了を表す信号を受け取るごとに、構成選択部26に対して新たなページのための回路再構成の指示を行う。

【0064】

以上に説明した実施形態の画像データ処理装置のうちのホストシステム20は、例えば、汎用のコンピュータに上述したホストシステム20の各機能モジュールの処理を表すプログラムを実行させることにより実現される。ここで、コンピュータは、例えば、ハードウエアとして、CPU等のマイクロプロセッサ、ランダムアクセスメモリ(RAM)およびリードオンリメモリ(ROM)等のメモリ(一次記憶)、HDD(ハードディスクドライブ)を制御するHDDコントローラ、各種I/O(入出力)インタフェース、ローカルエリアネットワークなどのネットワークとの接続のための制御を行うネットワークインタフェース等が、たとえばバスを介して接続された回路構成を有する。また、そのバスに対し、例えばI/Oインタフェース経由で、CDやDVDなどの可搬型ディスク記録媒体に対する読み取り及び/又は書き込みのためのディスクドライブ、フラッシュメモリなどの各種規格の可搬型の不揮発性記録媒体に対する読み取り及び/又は書き込みのためのメモリリーダライタ、などが接続されてもよい。上に例示した各機能モジュールの処理内容が記述されたプログラムがCDやDVD等の記録媒体を経由して、又はネットワーク等の通信手段経由で、ハードディスクドライブ等の固定記憶装置に保存され、コンピュータにインストールされる。固定記憶装置に記憶されたプログラムがRAMに読み出されCPU等のマイクロプロセッサにより実行されることにより、上に例示した機能モジュール群が実現される。なお、それら機能モジュール群のうちの一部又は全部を、専用LSI(Large Scale Integration)、ASIC(Application Specific Integrated Circuit、特定用途向け集積回路)又はFPGA(Field Programmable Gate Array)等のハードウエア回路として構成してもよい。

【符号の説明】

【0065】

10 DRP、12 再構成可能回路部、14 再構成制御部、16 構成メモリ、20 ホストシステム、22 圧縮・最大圧縮ライン長判定部、24 Max-L保持部、26 構成選択部、28 出力判定部、30 セレクタ、32 制御部、40 メモリ。

【技術分野】

【0001】

本発明は、画像データ処理装置及びプログラムに関する。

【背景技術】

【0002】

例えば、デジタル複写機やデジタル複合機(スキャナ、プリンタ、複写機等の機能を兼ね備えた装置)等の画像処理装置では、ライン順次の読取走査により画像データが生成され、生成された画像データに対し、生成順に、色空間変換や各種フィルタ処理等の画像処理が施される。ここで、例えばN×N画素(Nは2以上の整数)のデジタルフィルタを用いる二次元フィルタ処理では、例えば(N−1)ライン分のラインメモリに直近のラインの画像データを保持し、これら各ラインメモリのデータを現在読取中のラインの画像データと同期して読み出して、フィルタ回路に供給する。このような構成では、読取解像度の増大に伴い、ラインメモリの必要容量も大きくなる。

【0003】

このような課題に対し、特許文献1の装置では、読取走査により得られる各ラインの画像データを非可逆圧縮方式で圧縮してラインメモリに入力することで、小容量のラインメモリで対応可能としている。また、特許文献1の装置では、ラインごとに圧縮率を可変制御することで、各ラインの画像データがラインメモリの容量に収まるようにしている。

【0004】

特許文献2に開示される装置では、2次元フィルタ処理において、対象の画像を短冊状に分割することで、必要なラインメモリのサイズを削減している。

【0005】

特許文献3に開示される装置では、メモリ上の画像データをバンド単位で圧縮手段で圧縮して、該圧縮後のデータを、トグルバッファを介して画像メモリに転送して保管する。また、この装置では、圧縮前よりも圧縮後の方がそのデータ量が多くなって圧縮率が悪化する場合には、該バンドデータについては、該圧縮手段による圧縮前のバンドデータ(すなわち非圧縮のバンドデータ)を該画像メモリに転送して保管することで、圧縮手段の圧縮率が悪い場合にも、最悪、圧縮前のデータ量を維持している。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平11−331614号公報

【特許文献2】特開2002−304624号公報

【特許文献3】特開2009−055141号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明は、画像処理回路に対してラインメモリを介して画像データを供給する装置において、非可逆圧縮方式を用いる場合よりも画質劣化を抑えつつも、圧縮結果がラインメモリに収まらない場合があるという可逆圧縮方式の欠点を克服することを目的とする。

【課題を解決するための手段】

【0008】

請求項1に係る発明は、画像データをラインごとに可逆圧縮する可逆圧縮手段と、再構成可能回路上に、前記可逆圧縮手段の可逆圧縮により得られた圧縮データを保持するための第1のラインメモリと当該圧縮データを伸長するための伸長回路とを含む第1の構成と、非圧縮の前記画像データを保持するための第2のラインメモリを含む第2の構成と、を選択的に構成する制御を行う構成制御手段であって、前記第1のラインメモリの容量は、前記第1の構成の回路規模が前記第2の構成の回路規模以下となるように定められていることを特徴とする構成制御手段と、処理単位の画像データ内の各ラインを前記可逆圧縮手段で圧縮した場合のラインごとの圧縮データのデータサイズの最大値を判定する最大値判定手段と、前記最大値判定手段が判定した前記最大値が前記第1のラインメモリの容量に対応するあらかじめ定められた閾値以下である場合には、前記構成制御手段に対して前記第1の構成を前記再構成回路上に構成するよう指示すると共に、前記画像データの前記可逆圧縮手段による圧縮データを、前記第1のラインメモリを介して画像処理回路に出力し、前記最大値判定手段が判定した前記最大値が前記閾値を上回る場合には、前記構成制御手段に対して前記第2の構成を前記再構成回路上に構成するよう指示すると共に、非圧縮の前記画像データを、前記第2のラインメモリを介して前記画像処理回路に出力するよう制御する出力制御手段と、を備える画像データ処理装置である。

【0009】

請求項2に係る発明は、前記構成制御手段は、前記第1のラインメモリの容量が異なる複数の前記第1の構成を選択的に前記再構成可能回路上に構成可能であり、前記出力制御手段は、複数の前記第1の構成のうち前記第1のラインメモリの容量が前記最大値判定手段により判定された前記最大値以上であるものの中で、前記第1のラインメモリの容量が最小である第1の構成を、前記構成制御手段に構成させる、ことを特徴とする請求項1に記載の画像データ処理装置である。

【0010】

請求項3に係る発明は、前記最大値判定手段は、前記可逆圧縮手段に対して前記処理単位の画像データをラインごとに圧縮させ、この圧縮により得られた各ラインの圧縮データのデータサイズから前記最大値を判定し、前記出力制御手段は、前記最大値判定手段が判定した前記最大値が前記閾値以下である場合には、前記最大値判定手段の判定のための圧縮により得られた前記圧縮データを保存しておき、当該処理単位の画像データについて前記画像処理回路に処理させる際に、保存しておいた前記圧縮データを前記第1のラインメモリを介して前記画像処理回路に出力する、ことを特徴とする請求項1〜2のいずれか1項に記載の画像データ処理装置である。

【0011】

請求項4に係る発明は、前記出力制御手段がある処理単位の画像データ又は圧縮データを前記第1のラインメモリ又は前記第2のラインメモリを介して前記画像処理回路に出力している間に、前記可逆圧縮手段及び前記最大値判定手段が後続の別の処理単位についての圧縮及び前記最大値の判定を行う、ことを特徴とする請求項3に記載の画像データ処理装置である。

【0012】

請求項5に係る発明は、前記再構成可能回路上に構成されたラインメモリを含まない第3の回路構成に、ある処理単位についての処理を実行させている間に、前記可逆圧縮手段及び前記最大値判定手段がその処理単位より前の処理単位についての圧縮及び前記最大値の判定を行う、ことを特徴とする請求項3又は4に記載の画像データ処理装置である。

【0013】

請求項6に係る発明は、コンピュータを、画像データをラインごとに可逆圧縮する可逆圧縮手段、再構成可能回路上に、前記可逆圧縮手段の可逆圧縮により得られた圧縮データを保持するための第1のラインメモリと当該圧縮データを伸長するための伸長回路とを含む第1の構成と、非圧縮の前記画像データを保持するための第2のラインメモリを含む第2の構成と、を選択的に構成する制御を行う構成制御手段であって、前記第1のラインメモリの容量は、前記第1の構成の回路規模が前記第2の構成の回路規模以下となるように定められていることを特徴とする構成制御手段、処理単位の画像データ内の各ラインを前記可逆圧縮手段で圧縮した場合のラインごとの圧縮データのデータサイズの最大値を判定する最大値判定手段、前記最大値判定手段が判定した前記最大値が前記第1のラインメモリの容量に対応するあらかじめ定められた閾値以下である場合には、前記構成制御手段に対して前記第1の構成を前記再構成回路上に構成するよう指示すると共に、前記画像データの前記可逆圧縮手段による圧縮データを、前記第1のラインメモリを介して画像処理回路に出力し、前記最大値判定手段が判定した前記最大値が前記閾値を上回る場合には、前記構成制御手段に対して前記第2の構成を前記再構成回路上に構成するよう指示すると共に、非圧縮の前記画像データを、前記第2のラインメモリを介して前記画像処理回路に出力するよう制御する出力制御手段、として機能させるためのプログラムである。

【発明の効果】

【0014】

請求項1又は6に係る発明によれば、非可逆圧縮方式を用いる場合よりも画質劣化を抑えつつも、圧縮結果がラインメモリに収まらない場合があるという可逆圧縮方式の欠点を克服することができる。

【0015】

請求項2に係る発明によれば、処理単位の画像データを処理するのに必要な最小の回路規模の構成を選択することができる。

【0016】

請求項3に係る発明によれば、処理単位における各ラインの圧縮データのデータサイズの最大値を判定する処理と、それら各ラインの圧縮処理と、を別々に行う場合に比べて、演算処理に必要なコストを低減することができる。

【0017】

請求項4又は5に係る発明によれば、圧縮及び最大値の判定の処理に必要な時間の少なくとも一部分を、再構成可能回路が他の処理を行っている期間により隠蔽することができる。

【図面の簡単な説明】

【0018】

【図1】実施形態の画像データ処理装置の構成例を示す図である。

【図2】複数ライン分のラインメモリを備えた圧縮データ用の回路構成の一例を示す図である。

【図3】複数ライン分のラインメモリを備えた生データ用の回路構成の一例を示す図である。

【図4】画像圧縮及び回路構成の判定処理と、他の処理と、のコンカレント処理の例を説明するための図である。

【図5】画像圧縮及び回路構成の判定処理と、他の処理と、のコンカレント処理の別の例を説明するための図である。

【図6】実施形態の画像データ処理装置の全体的な処理手順の一例を示すフローチャートである。

【図7】圧縮・最大圧縮ライン長判定処理の手順の一例を示すフローチャートである。

【図8】出力判定処理の手順の一例を示すフローチャートである。

【図9】ラインメモリ長の異なる複数の回路構成(コンフィギュレーション)の情報を格納したデータベースのデータ内容の例を示す図である。

【図10】ラインメモリ長選択処理の手順の一例を示すフローチャートである。

【発明を実施するための形態】

【0019】

以下、図面を参照して、実施形態の画像データ処理装置の機能構成の例を説明する。図1に示す画像データ処理装置は、例えば、上位装置に内蔵又は接続され、上位装置から供給されたビットマップ画像データに対して画像処理を行う。上位装置は、プリンタ、スキャナ、ファクシミリ装置、デジタル複写機、デジタル複合機、デジタルカメラなどの画像処理装置であってもよいし、汎用コンピュータ装置であってもよい。

【0020】

図1に示す画像データ処理装置は、DRP(Dynamic Reconfigurable Processor:動的再構成可能プロセッサ)10、ホストシステム20及びメモリ40を備える。

【0021】

DRP10は、内部の論理回路の構成を動的(例えば1クロックの間)に変更(再構成)可能なプロセッサである。DRP10の一例としては、例えば特開2009−3765号公報に紹介されているDAP・DNAアーキテクチャのプロセッサがあるが、もちろんこれに限定されるものではない。DRP10は、再構成可能回路部12、再構成制御部14及び構成メモリ16を備える。

【0022】

再構成可能回路部12は、多数の論理回路要素を備えており、それら各論理回路要素の機能パラメータや論理回路要素同士の接続関係を動的に再構成(リコンフィギュレーション)可能となっている。再構成可能回路部12としては、例えば、特開2009−3765号公報に紹介されているDNAなど、様々な既存の又はこれから開発される回路を用いることができる。例えば、DNAは、PE(プロセッサエレメント)と呼ぶ論理回路要素を多数備えるアレイであり、それらPE間の接続構成を構成(コンフィギュレーション)データに従って高速(例えば1クロックの間に)組み替え可能となっている。

【0023】

再構成制御部14は、再構成可能回路部12内の論理回路要素の接続関係を制御することで、再構成可能回路部12上にデータ処理のための回路を再構成する。また、再構成制御部14は、再構成可能回路部12上に再構成された回路に対してホストシステム20からの指示に応じて入力データを供給したり、その回路からの出力データをホストシステム20に返したりする制御を行う。なお、特開2009−3765号公報で紹介されたDAP・DNAアーキテクチャをこの実施形態に採用した場合、再構成制御部14はDAPと呼ばれる汎用プロセッサコアで制御プログラムを実行することにより実現される(但し、これは一例に過ぎない)。

【0024】

再構成可能回路部12内の回路の再構成は、構成(コンフィギュレーション)メモリ16に記憶された構成(コンフィギュレーション)データに従って行われる。構成メモリ16には、複数の構成データが記憶される。DRP10は、ホストシステム20からの指示に応じて、構成メモリ16に新たな構成データを追加したり、構成メモリ16内の構成データを削除したりする機能を備える。

【0025】

ホストシステム20は、DRP10を制御して画像処理を実行させる制御システムである。ホストシステム20は、例えば、デジタル複合機等の上位装置からビットマップ画像データを受け取ってメモリ40に記憶し、この画像データをDRP10に処理させる。ホストシステム20は、後述する機能モジュール22〜30群をすべてハードウエア回路で実装することにより実現したものであってもよいし、すべてソフトウエアにより実装することにより実現したものであってもよいし、一部をハードウエア回路で実装し残りをソフトウエアで実装することにより実現したものであってもよい。ホストシステム20の機能モジュール群の一部又は全部をソフトウエアで実装する場合、そのソフトウエアのプログラムの実行は、(a)DRP10内のプロセッサが行ってもよいし、(b)DRP10と同じ基板上に実装されるプロセッサが行ってもよいし、(c)デジタル複合機等の上位装置のプロセッサが行ってもよいし、それらプロセッサのうちの2以上で分担して行ってもよい。例えば、(a)の場合、DRP10自体がこの実施形態の画像データ処理装置であり、(b)の場合、DRP10とプロセッサを搭載した基板がこの実施形態の画像データ処理装置であり、(c)の場合、DRP10と上位装置のプロセッサとの組合せがこの実施形態の画像データ処理装置である。メモリ40は、ランダムアクセスメモリ等の高速に読み書き可能な記憶装置であり、DRP10に内蔵されたものであってもよいし、DRP10と同じ基板に実装されるものであってもよいし、デジタル複合機等の上位装置のメモリであってもよい。

【0026】

ホストシステム20は、圧縮・最大圧縮ライン長判定部22、構成選択部26、出力判定部28、セレクタ30、制御部32を有する。

【0027】

圧縮・最大圧縮ライン長判定部22は、処理対象のビットマップ画像データをライン(走査線)ごとに圧縮すると共に、ラインごとの圧縮結果のライン長の最大値Max-Lを判定する(詳細は後述)。Max-L保持部24は、最大圧縮ライン長Max-Lを保持する記憶領域である。構成選択部26は、圧縮・最大圧縮ライン長判定部22が求めた最大圧縮ライン長Max-Lに基づき、再構成可能回路部12に再構成する回路構成(コンフィギュレーション)を選択する(詳細は後述)。出力判定部28は、最大圧縮ライン長Max-Lに基づき、ビットマップ画像データの生データ又は圧縮データのいずれをDRP10に出力するかを判定する。セレクタ30は、出力判定部28の判定結果に従い、ビットマップ画像データの生データ又は圧縮データのいずれか一方を選択してDRP10に供給する。制御部32は、ホストシステム20内の他の各機能モジュールを制御する。

【0028】

本実施形態の画像データ処理装置では、再構成可能回路部12に、2次元フィルタ処理などのように、複数のラインメモリを必要とする画像処理回路を再構成する。ここで、DRP10内に再構成するラインメモリ群の回路規模を小さくできるようにするために、本実施形態では、処理対象のビットマップ画像データを、圧縮・最大圧縮ライン長判定部22で圧縮している。圧縮・最大圧縮ライン長判定部22が行う画像データ圧縮として、以下ではランレングス圧縮方式を例にとる。ランレングス圧縮は、可逆圧縮であり、画質劣化がない。なお、以下に示す本実施形態の制御は、ランレングス圧縮以外の他の可逆圧縮方式を用いる場合でも同様に適用可能である。このように、可逆圧縮した画像データをラインメモリに入れる構成をとる場合、ラインメモリ内のデータを画像処理回路に入力する前に伸長する回路が必要となる。このように圧縮した画像データを受け入れて処理する場合に再構成可能回路部12に構成される回路構成の例を、図2に示す。

【0029】

図2に示す第1の回路構成100Aは、画像処理回路の一例として5×5画素の2次元フィルタ処理(例えば平均処理、エッジ強調処理などの各種フィルタ処理のうちのいずれか)を行うフィルタ処理回路106を備えるとともに、それぞれ1ページの画像のうちの1ライン(走査線)分の圧縮データを保持するための5つのラインメモリ102a〜102eを備える。各ラインメモリ102a〜102eはFIFO(先入れ先出し)方式のバッファメモリである。各ラインメモリ102a〜102eの容量は、互いに等しい値であり、それぞれ、あらかじめ想定した圧縮率に対応する1ライン分の圧縮データを収容することを想定した値である。初段のラインメモリ102aには、ホストシステム20側から圧縮データが入力される。ラインメモリ102aの出力は、伸長回路104aと、第2段のラインメモリ102bの入力とに接続されている。同様に、第2、3、4段のラインメモリ102b、102c、102dは、入力側がそれぞれ前段のラインメモリ102a、102b、102cの出力に接続されており、出力側がそれぞれ対応する伸長回路104b、104c、104dと第3、4、5段のラインメモリ102c、102d、102eの入力側に接続されている。また、第5段のラインメモリ102eの出力は、対応する伸長回路104eに接続されている。したがって、この回路構成では、ホストシステム20側からDRP10に入力される圧縮データは、まず初段のラインメモリ102aに入力され、その後順番に、第2、3、4、5段の102b、102c、102d、102eへと移動していくことになる。各時点では、5つのラインメモリ102a〜102eに、連続する5ライン分の圧縮データが保持されていることになる。

【0030】

また、各伸長回路104a〜104eの出力側は、それぞれFIFO(先入れ先出し)メモリを介してフィルタ処理回路106に接続されている。各FIFOメモリは、伸長回路104a〜104eからそれぞれ出力される伸長結果の画像データを、画素順に互いにタイミング合わせ(同期)してフィルタ処理回路106に供給するために用いられる、小容量のバッファメモリである。各FIFOメモリは、タイミング合わせがよいので、1ライン分の画像データの量よりもはるかに小さい容量でよい。フィルタ処理回路106は、各FIFOを介して順に供給される、隣接する5ラインの画像データに対して、フィルタ処理を実行し、フィルタ処理結果の画素値を順に出力する。フィルタ処理回路106から順に出力される各画素の値は、ホストシステム20に返される。

【0031】

さて、フィルタ処理を正常に実行するには、第1の回路構成100Aの各ラインメモリ102a〜102eには、それぞれ1ライン(走査線)分の圧縮データが収容されなければならない。しかし、圧縮対象の画像データの性質によって圧縮率は変わってくるので、ある決まった容量のラインメモリ102a〜102eに1ラインの圧縮データが必ず収まるとは限らない。利用する圧縮方式にもとの画像データの性質が適していない場合、もとの画像データよりも圧縮データの方が、データ量が大きくなる場合もある。そのような極端な場合も考慮したのでは、ラインメモリ102a〜102eのサイズが大きくなりすぎる。そこで、この実施形態では、1ライン分の圧縮データが第1の回路構成100Aの各ラインメモリ102a〜102eに収容できない場合のための備えとして、図3に示す第2の回路構成100Bを用意する。

【0032】

第2の回路構成100Bのフィルタ処理回路106は、第1の回路構成100Aのフィルタ処理回路106と同じものである。第2の回路構成100Bは、フィルタ処理回路106の前段に5つのラインメモリ108a〜108eを備える。各ラインメモリ108a〜108eは、それぞれ1ライン分のビットマップ画像データの量に対応する容量を持つ。初段のラインメモリ108aは、入力側がホストシステム20に接続されており、出力側がフィルタ処理回路106と第2段のラインメモリ108bの入力側とに接続されている。第2〜4段のラインメモリ108b、108c、108dは、入力側が各々の前段のラインメモリ108a、108b、108cの出力側に接続されており、出力側がフィルタ処理回路106と各々の次段のラインメモリ108c、108d、108eに接続されている。そして、第5段のラインメモリ108eの出力は、フィルタ処理回路106に接続されている。

【0033】

この第2の回路構成100Bには、ホストシステム20から生の画像データがラインごとに順に入力される。入力されたラインごとの画像データは、ラインメモリ108a〜108eを順に移動していくとともに、各ラインメモリ108a〜108eの出力側から互いに同期して(すなわちライン上での同一の画素番号の画素データが互いに同時に)フィルタ処理回路106に供給される。フィルタ処理回路106は、ラインメモリ108a〜108eを介して順に供給される、隣接する5ラインの画像データに対してフィルタ処理を実行し、フィルタ処理結果の画素値を順にホストシステム20に返す。

【0034】

DRP10の構成メモリ16には、以上に説明した第1の回路構成100Aを表す構成(コンフィギュレーション)データと第2の回路構成100Bを表す構成データとが少なくとも記憶されている。

【0035】

圧縮データ用の第1の回路構成100Aは、少なくとも、生(非圧縮)データ用の第2の回路構成100Bよりも回路規模(回路構成を実現するために使用する回路要素の数)が小さい。すなわち、各ラインメモリ102a〜102eの容量は、各ラインメモリ108a〜108eの容量から各伸長回路104a〜104eと各FIFOの回路規模に相当する容量を引いた容量よりも小さい。

【0036】

実用的には、ラインメモリのための回路規模の低減効果を得るために、第1の回路構成100Aは、第2の回路構成100Bよりもかなりの程度(例えば数割程度)小さくする。例えば、テキストのみの画像やテキストとグラフ等の図形からなる画像などのように、ランレングス圧縮等の可逆圧縮でも大きな圧縮率が得られる画像は少なくないので、第1の回路構成100Aの回路規模(すなわちラインメモリ102a〜102eの容量)をかなり小さくした場合でも、実用的にはかなり多くの画像に対して対応できる。そして、第1の回路構成100Aではラインメモリ102a〜102eに1ライン分の圧縮データが収まらない例外的なケースにのみ、第2の回路構成100Bを利用する。このような回路構成の切換利用を行うと、第1の回路構成100Aを用いている間は、第2の回路構成100Bを用いている間よりも、フィルタ処理のために使用する回路要素の数が少なくて済むので、空いた回路要素を別の処理のための回路のために用いる。

【0037】

本実施形態では、あらかじめ定めた画像データの処理単位ごとに、第1の回路構成100Aと第2の回路構成100Bとのうちの適切な方を選択して使用する。処理単位は、例えばページである。また、ページを分割したバンドを処理単位としてもよい。バンドは、あらかじめ定めた数の連続したライン(走査線)からなる画像部分である。以下では、処理単位を「ページ」とする場合の例を説明するが、ページ以外の処理単位(例えば「バンド」)を用いる場合にも、この実施形態の手法は同様に適用される。

【0038】

第1の回路構成100Aと第2の回路構成100Bとのいずれを用いるかの選択に当たり、本実施形態では、圧縮・最大圧縮ライン長判定部22により処理単位の画像データを実際に圧縮する。そして、その処理単位のすべてのラインの圧縮結果が第1の回路構成100Aのラインメモリ102a〜102eに完全に収容されることが確認されれば、第1の回路構成100Aを選択し、そうでなければ第2の回路構成100Bを選択する。また、少なくとも第1の回路構成100Aを選択した処理単位については、圧縮・最大圧縮ライン長判定部22による判定の際に求めた圧縮結果のデータをメモリ40に保存しておき、後でその処理単位の処理順序が来たときに、その圧縮データをDRP10上の第1の回路構成100Aに供給する。

【0039】

このように実際に画像データを圧縮してみることで圧縮率が十分かどうかを判定する方式では、画像データに対してDRP10による画像処理を実行する前に、その画像データを圧縮する必要がある。1つの例では、DRPが別の処理を実行中に、圧縮・最大圧縮ライン長判定部22がこの事前の圧縮及び判定の処理を行うことで、その圧縮処理に要する時間を隠蔽する。このような処理の一例を、図4を参照して説明する。

【0040】

図4の例では、画像データに対してDRP10を用いて2種類の画像処理a及びbを行う場合を想定する。このうち、画像処理aはラインメモリを必要としない処理(例えば、色空間変換などのように他のラインの画素値を参照しなくてよい処理)であり、画像処理bが複数ライン分のラインメモリを必要とする処理(例えば2次元フィルタ処理)であるとする。DRP10は、画像処理aについては単一の回路構成を用いるが、画像処理bについては上述の第1の回路構成100Aと第2の回路構成100Bを切り替えつつ使用するとする。また、図4の例ではページを処理単位としている。

【0041】

図4の例では、まずDRP10の再構成可能回路部12上に画像処理a用の回路構成「構成−a」を再構成し、その構成−aにより対象の文書の第1ページ(「ページ1」)及び第2ページの画像データを処理(図中の「ページ1−a」、「ページ2−a」)する。そして、第2ページについて画像処理aを実行している間に、第1ページの画像データについての画像処理aの処理結果をホストシステム20の圧縮・最大圧縮ライン長判定部22に圧縮させる。この圧縮処理により得られる圧縮データは、メモリ40に記憶される。また、圧縮・最大圧縮ライン長判定部22は、この圧縮処理により得られる各ラインの圧縮データのデータ長(以下、「圧縮ライン長」と呼ぶ)に基づき、構成選択部26が第1及び第2の回路構成100A及び100Bのうちのいずれの構成を採用するかを決定する。ここでは、第1の回路構成100A(圧縮データ用。図では「構成−bA」と表記)を採用すると判定されたとする。処理「ページ2−a」の終了後、構成選択部26の指示に応じて再構成制御部14が再構成可能回路部12を構成−bAへと再構成し、出力判定部28の制御に応じてセレクタ30が第1ページについての画像処理aの処理結果の圧縮データを選択し、その圧縮データを再構成可能回路部12上の構成−bAに供給して処理させる(図中の「ページ1−b」)。また、DRP10がこの処理「ページ1−b」を実行している間に、第2ページについての画像処理aの処理結果を圧縮・最大圧縮ライン長判定部22に圧縮させ、その圧縮結果に基づき、第1及び第2の回路構成100A及び100Bのうちのいずれの構成を採用するかを決定する。ここで第1の回路構成100A(「構成−bA」)を採用すると判定されたとすると、処理「ページ1−b」の後、回路構成を構成−bAのままとして、第2ページについての画像処理aの処理結果を、その構成−bAにより処理する(図中の「ページ2−b」)。以降、2ページごとに同様の処理を繰り返す。このような2ページごとの処理によれば、ラインメモリを用いる画像処理bのための回路構成の選択の処理に必要な時間が、別のページについての画像処理a(ラインメモリを用いない)の実行時間、又は先行するページについての画像処理bの実行時間の中に隠蔽されることになる。

【0042】

また、別の例として、図5に示す例がある。この例は、ラインメモリを用いる単一の画像処理を複数のページからなる文書に対して行う場合の例である。この例では、まず文書の第1ページの画像データを、ホストシステム20の圧縮・最大圧縮ライン長判定部22に圧縮させ、各ラインの圧縮ライン長に基づき、構成選択部26が第1ページに対して第1及び第2の回路構成100A及び100Bのうちのいずれの構成を採用するかを決定する。図5の例では、第1ページには第1の回路構成100A(圧縮データ用。図では「構成−A」と表記)を採用すると決定される。この決定の後、構成選択部26からの指示に従い、DRP10の再構成制御部14が、再構成可能回路部12上に第1の回路構成100Aを再構成する。その再構成の後、出力判定部28の制御により、セレクタ30が圧縮データ側を選択し、セレクタ30を介して再構成可能回路部12上の第1の回路構成100Aに対して第1ページの圧縮データが供給される。このようにしてDRP10が第1ページに対して画像処理を実行している間に、ホストシステム20は第2ページのための回路構成を第1及び第2の回路構成100A及び100Bのいずれにするかを選択する。図5の例では、第2ページに対して構成−Aが選択される。したがって、第1ページの画像処理が終わった後、再構成可能回路部12を構成−Aとしたまま、第2ページの圧縮データが構成−Aに供給され、処理される。そして、DRP10による第2ページの画像処理中に、ホストシステム20により第3ページの処理に用いる回路構成として第2の回路構成100B(生データ用。図では「構成−B」と表記)が選択され、第2ページについての画像処理の終了後、再構成可能回路部12の回路構成が構成−Bに変更され、セレクタ30により第3ページの生データが選択されて、再構成可能回路部12上の構成−Bにて処理される。以上のように、図5の例では、文書中の第2ページ以降については、画像データ圧縮及び回路構成の判定処理の所要時間が、DRP10による当該ページの直前のページの画像処理の期間の中に隠蔽される。

【0043】

図4の例から分かるように、異なる複数の画像処理のための回路をDRP10上に順に再構成する場合において、ラインメモリを用いる画像処理bの直前の画像処理aがラインメモリを用いない処理である場合には、判定対象のページについての画像処理aの実行後、その判定対象のページの後続の他のページに対して画像処理aを実行している間に、当該判定対象のページについての画像処理bのための回路構成の判定が行われる。

【0044】

また、図4及び図5の例から分かるように、判定対象のページに先行する他のページについて、ラインメモリを用いる画像処理bを実行中に、当該判定対象のページについての画像処理bのための回路構成の判定が行われる。

【0045】

さて、本実施形態では、圧縮データに対応するためのDRP10の回路構成として、ラインメモリの容量が異なる複数の回路構成を用意し、ページごとに、そのページに応じた容量のラインメモリを持つ回路構成を選択するようにしてもよい。これら複数の回路構成は、ラインメモリの長さは互いに異なるが、それ以外の構成、すなわちラインメモリの数、伸長回路104a〜104e、フィルタ処理回路106などは、互いに共通である。この例では、用意した複数の回路構成のうち、例えば、圧縮・最大圧縮ライン長判定部22が求めた当該ページの最大圧縮ライン長を収容可能な最小容量のラインメモリを持つ回路構成を選択する。当該ページの処理に必要な最小のラインメモリを持つ回路構成を選択することで、再構成可能回路部12の回路要素のうち当該画像処理に使用するものの数が少なくなり、他の処理に適用可能な空き回路要素が増える。

【0046】

次に、本実施形態の画像データ処理装置の処理手順の一例を説明する。図6は、画像データ処理装置の全体的な処理手順の一例を示す。図6の手順は、ラインメモリを用いる画像処理(便宜上「画像処理X」と呼ぶ)についての処理手順である。

【0047】

図6の手順では、ホストシステム20の制御部32は、まずページ番号を表す変数nの値を1(すなわち画像処理Xの対象の文書の最初のページの番号)に設定し(S10)、上位システムからメモリ40内に供給された対象文書のデータのうち、第nページの画像データにアクセスする(S12)。そして、制御部32は、その第nページの画像データを圧縮・最大圧縮ライン長判定部22に処理させる(S14)。S14の処理により、メモリ40には第nページの圧縮データが記憶され、またMax-L保持部24には第nページの各ラインの圧縮結果のうちの最大長の値(=最大圧縮ライン長Max-L)が保持される。なお、S14の詳細な手順の例は、後で図7を参照して説明する。

【0048】

S14の後、出力判定部28により、DRP10に対して出力する第nページのデータを、圧縮データとするか、生データ(非圧縮のデータ)とするかを判定する(S16)。なお、S16の詳細な手順の例は、後で図8を参照して説明する。S16にて圧縮データを出力すると判定された場合(S18の判定結果がY)、制御部32は、構成選択部26に、圧縮データ用に用意したラインメモリの容量の異なる複数の第1の回路構成100Aの中から、第nページの処理に用いる回路構成を選択させる(S20)。なお、S20の詳細な手順の例は、後で図10を参照して説明する。S16にて生データを出力すると判定された場合(S18の判定結果がN)、制御部32は、構成選択部26に、生データ用の回路構成(第2の回路構成100B)を選択させる(S22)。

【0049】

そして、制御部32は、第nページについての画像処理XをDRP10に実行させるタイミングが来ると、構成選択部26を介してDRP10の再構成制御部14に対して、S20又はS22で選択した回路構成の再構成を指示する(S24)。なお、S24では、第nページについて選択された回路構成が、再構成可能回路部12上に既に構成されている場合は、再構成は行わなくてもよい。そして、制御部32は、セレクタ30を、圧縮データ出力又は生データ出力のうち、出力判定部28によるS16の判定結果に応じた方に切り替え、その切り替えに応じてセレクタ30を介して出力される第nページの圧縮データ又は生データを、再構成可能回路部12上に構成された回路構成に処理させる(S26)。このS24及びS26の実行中に、コンカレント(同時並列的)に、ホストシステム20が、後続のページについてS12〜S22の処理を実行してもよい。

【0050】

そして、未処理のページがあれば(S28の判定結果がY)、ページ番号nを1だけ増加させ(S30)、S12に戻る。以上に説明したS12〜S30の処理を対象文書の全ページについて繰り返した後、図6の処理は終了する。

【0051】

次に、図7を参照して、図6のS14の詳細な処理手順の一例を説明する。図7の手順は、画像データの可逆圧縮処理として、ランレングス圧縮方式を用いる場合の例である。図7の手順は、ページごとに実行される。

【0052】

図7の手順では、まず圧縮・最大圧縮ライン長判定部22は、Max-L保持部24に保持される最大圧縮ライン長Max-Lを初期化する(図7の例では、初期値は0)(S102)。次に、1ライン(走査線)内での注目画素の番号を示す画素カウンタPixCtr、ラン長RunLen、圧縮ライン長L−cntの変数をそれぞれ0に初期化する(S104)。次に、圧縮・最大圧縮ライン長判定部22は、メモリ40内の圧縮対象のページの先頭画素から順に、ラスター走査順に各画素のデータを入力する。この入力は、ページの最後の画素まで1画素ずつ行われる。そして、1画素入力するごとに、入力したその画素の値を変数「現画素」に代入するとともに(S108)、現時点での画素カウンタPixCtrの値が0であるかどうかを判定し(S110)、0であれば(S110の判定結果がY)、「現画素」の1つ前の画素の値を保持する変数「前画素」に対し、現画素の値を代入する(S112)。S112は、ラインの先頭の画素についての「前画素」を設定するため、及びランが切れた場合(後述するS116の判定結果がNとなった場合)の「前画素」の初期設定のための処理である。なお、S110の判定結果がNの場合は、S112は実行しない。そして、圧縮・最大圧縮ライン長判定部22は、画素カウンタPixCtrの値を1増加させる(S114)。

【0053】

次に、圧縮・最大圧縮ライン長判定部22は、現画素と前画素の画素値が等しいかどうかを判定する(S116)。等しい場合(S116の判定結果がY)、画素カウンタPixCtrの値がページのライン長(すなわちページの主走査方向の画素数)に達したかどうかを判定し(S118)、達していなければ、ラン長RunLenを1だけ増加させるとともに、(S120)、S106に戻ってメモリ40から次の画素を入力する。この場合、ラン長RunLenはS124で「0」に初期化されているので、S110の判定結果がYとなり、S112で「前画素」が「現画素」の値に初期化される。

【0054】

ランが続いている間、すなわち同じ値の画素が連続している間は、S116〜S120によりラン長RunLenがインクリメントされていくことになる。そして、ランがとぎれた場合、S116で現画素が前画素と異なると判定された場合は、そのランを表す符号を、現在のラン長RunLenの値と前画素のデータ値との組合せから求める(S122)。求められた符号は、メモリ40内の当該ページの圧縮データの末尾に追加される。その後、圧縮・最大圧縮ライン長判定部22は、ラン長RunLenの値を0に初期化し、S122で求めた符号の符号長を圧縮ライン長L−cntに加算し(S124)、S106に戻ってメモリ40から次の画素を入力する。この場合、ラン長RunLenはS120でインクリメントされており「0」ではないので、S110の判定結果がNとなり、S112はスキップされる。

【0055】

また、図7の処理では、符号化を1ラインごとに完結させるので、S116で現画素の値が前画素の値と等しいと判定した場合でも、画素カウンタPixCtrの値がライン長に達していれば(S118の判定結果がY)、圧縮・最大圧縮ライン長判定部22は、そのランを表す符号を、現在のラン長RunLenの値と前画素のデータ値との組合せから求める(S126)。そして、S126で求めた符号の符号長を圧縮ライン長L−cntに加算し(S128)、その加算結果の値を、Max-L保持部24に保持された原次元での最大圧縮ライン長Max-Lと比較する(S130)。加算結果が現時点のMax-Lより大きければ(S130の判定結果がY)、その加算結果をMax-Lに代入する(S132)。加算結果が現時点のMax-L以下であれば、Max-Lの値は更新しない。以上の処理の後、S104に戻り、次のラインについての処理を行う。

【0056】

以上に説明した処理を、ページの最後の画素まで繰り返す。ページの最後の画素まで処理を完了すると(S106の判定結果がY)、圧縮・最大圧縮ライン長判定部22は、Max-L保持部24に保持している最大圧縮ライン長Max-Lの値を、当該ページのページ番号と対応づけて制御部32に出力する(S34)。制御部32は、この最大圧縮ライン長の値を構成選択部26及び出力判定部28に供給する。

【0057】

次に、図8を参照して、出力判定部28の処理手順の一例を説明する。図8の手順において、出力判定部28は、制御部32から供給された当該ページの最大圧縮ライン長Max-Lが、用意している複数の回路構成のラインメモリ長(「最大ラインメモリ長」と予備)の最大値よりも大きいかどうかを判定する(S142)。

【0058】

例えば、実施形態の画像データ処理装置が、ラインメモリを使用するある画像処理のための回路構成として、図9に示すように、ラインメモリ長の異なるN個の回路構成を有しているとする。図9の例では、回路構成を識別する番号(「構成番号」)が若いほど、ラインメモリ長が長い。構成番号1の回路構成は用意された回路構成の中で最大の回路規模を有するが、その回路規模でも、生データ用の回路構成よりは回路規模が小さい。この場合、最大ラインメモリ長は、構成番号1のラインメモリ長Config-Line(1)のことであり、S142では、ラインメモリ長Config-Line(1)と最大圧縮ライン長Max-Lとを比較する。

【0059】

そして、Max-Lが最大ラインメモリ長より大きければ(S142の判定結果がY)、当該ページについては圧縮データではなく生データをDRP10に出力すべきと判定する(S144)。また、Max-Lが最大ラインメモリ長以下であれば(S142の判定結果がN)、当該ページについては圧縮データをDRP10に出力すべきと判定する(S146)。

【0060】

出力判定部28は、例えば、図8の手順により判定した各ページについての判定結果をFIFOメモリ(図示省略)に保持し、制御部32から新たなページの出力を指示されるごとに、FIFOメモリの先頭の判定結果を取り出し、その判定結果に応じてセレクタ30を切り替える。なお、制御部32は、例えば、DRP10からページの画像処理の終了を表す信号を受け取るごとに、出力判定部28に対して新たなページの出力指示を行う。

【0061】

次に、図10を参照して、構成選択部26の処理手順の一例を説明する。この処理のために、画像データ処理装置は、各回路構成のラインメモリ長を表す図9に例示したようなデータを保持しているとする。図10の手順では、構成選択部26は、まず回路構成を識別する構成番号nを1に初期化し、第n番目の回路構成のラインメモリ長Config-Line(n)から最大圧縮ライン長Max-Lを減算した減算結果ΔEの最小値MinΔEを、あらかじめ定めた大きい定数(図では「High」と表記)に初期化する(S152)。すなわち、この手順では、構成番号が若い、すなわちラインメモリ長が大きい回路構成から順に、当該ページにとって適切であるかどうかを判定していく。次に、ΔEを計算し(S154)、計算結果のΔEが0より小さいかどうかを判定する(S156)。図10の処理は、S16(図8の処理手順)でMax-Lが最大ラインメモリ長(=構成番号1のラインメモリ長)以下であると判定された場合にしか実行されないので、構成番号n=1のときにS154で求められるΔEは必ず正の値であり、S156の判定結果はNとなる。次に、ΔEがMinΔEよりも小さいかどうかを判定する(S158)。小さければ、ΔEをMinΔEに代入するとともに、変数Min−nに対して現在の構成番号nを代入する(S160)。変数Min−nは、当該ページに対する現時点での最適な回路構成(すなわち、ラインメモリ長が当該ページの最大圧縮ライン長以上の回路構成のうち、ラインメモリ長が最小のもの)の番号を保持する変数である。S160の後、構成番号nの値を1増加させ(すなわち今検査し終えた回路構成よりもラインメモリ長が1段階短い回路構成を次の検査対象として)(S162)、S154に戻る。

【0062】

そして、S156の判定結果がYとなる(すなわち、ΔEの値が0より小さくなる)まで、S154〜S162の処理を繰り返す。そして、S156の判定結果がYとなると、その時点の変数Min−nの値を、当該ページに対する最適な回路構成の識別番号とする(S164)。

【0063】

構成選択部26は、例えば、図10の手順により判定した各ページについての最適な回路構成の識別番号をFIFOメモリ(図示省略)に保持し、制御部32から新たなページのための回路再構成を指示されるごとに、FIFOメモリの先頭の番号を取り出し、その再構成制御部14に対してその番号の回路構成への切り替えを指示する。なお、制御部32は、例えば、DRP10からページの画像処理の終了を表す信号を受け取るごとに、構成選択部26に対して新たなページのための回路再構成の指示を行う。

【0064】

以上に説明した実施形態の画像データ処理装置のうちのホストシステム20は、例えば、汎用のコンピュータに上述したホストシステム20の各機能モジュールの処理を表すプログラムを実行させることにより実現される。ここで、コンピュータは、例えば、ハードウエアとして、CPU等のマイクロプロセッサ、ランダムアクセスメモリ(RAM)およびリードオンリメモリ(ROM)等のメモリ(一次記憶)、HDD(ハードディスクドライブ)を制御するHDDコントローラ、各種I/O(入出力)インタフェース、ローカルエリアネットワークなどのネットワークとの接続のための制御を行うネットワークインタフェース等が、たとえばバスを介して接続された回路構成を有する。また、そのバスに対し、例えばI/Oインタフェース経由で、CDやDVDなどの可搬型ディスク記録媒体に対する読み取り及び/又は書き込みのためのディスクドライブ、フラッシュメモリなどの各種規格の可搬型の不揮発性記録媒体に対する読み取り及び/又は書き込みのためのメモリリーダライタ、などが接続されてもよい。上に例示した各機能モジュールの処理内容が記述されたプログラムがCDやDVD等の記録媒体を経由して、又はネットワーク等の通信手段経由で、ハードディスクドライブ等の固定記憶装置に保存され、コンピュータにインストールされる。固定記憶装置に記憶されたプログラムがRAMに読み出されCPU等のマイクロプロセッサにより実行されることにより、上に例示した機能モジュール群が実現される。なお、それら機能モジュール群のうちの一部又は全部を、専用LSI(Large Scale Integration)、ASIC(Application Specific Integrated Circuit、特定用途向け集積回路)又はFPGA(Field Programmable Gate Array)等のハードウエア回路として構成してもよい。

【符号の説明】

【0065】

10 DRP、12 再構成可能回路部、14 再構成制御部、16 構成メモリ、20 ホストシステム、22 圧縮・最大圧縮ライン長判定部、24 Max-L保持部、26 構成選択部、28 出力判定部、30 セレクタ、32 制御部、40 メモリ。

【特許請求の範囲】

【請求項1】

画像データをラインごとに可逆圧縮する可逆圧縮手段と、

再構成可能回路上に、前記可逆圧縮手段の可逆圧縮により得られた圧縮データを保持するための第1のラインメモリと当該圧縮データを伸長するための伸長回路とを含む第1の構成と、非圧縮の前記画像データを保持するための第2のラインメモリを含む第2の構成と、を選択的に構成する制御を行う構成制御手段であって、前記第1のラインメモリの容量は、前記第1の構成の回路規模が前記第2の構成の回路規模以下となるように定められていることを特徴とする構成制御手段と、

処理単位の画像データ内の各ラインを前記可逆圧縮手段で圧縮した場合のラインごとの圧縮データのデータサイズの最大値を判定する最大値判定手段と、

前記最大値判定手段が判定した前記最大値が前記第1のラインメモリの容量に対応するあらかじめ定められた閾値以下である場合には、前記構成制御手段に対して前記第1の構成を前記再構成回路上に構成するよう指示すると共に、前記画像データの前記可逆圧縮手段による圧縮データを、前記第1のラインメモリを介して画像処理回路に出力し、前記最大値判定手段が判定した前記最大値が前記閾値を上回る場合には、前記構成制御手段に対して前記第2の構成を前記再構成回路上に構成するよう指示すると共に、非圧縮の前記画像データを、前記第2のラインメモリを介して前記画像処理回路に出力するよう制御する出力制御手段と、

を備える画像データ処理装置。

【請求項2】

前記構成制御手段は、前記第1のラインメモリの容量が異なる複数の前記第1の構成を選択的に前記再構成可能回路上に構成可能であり、

前記出力制御手段は、複数の前記第1の構成のうち前記第1のラインメモリの容量が前記最大値判定手段により判定された前記最大値以上であるものの中で、前記第1のラインメモリの容量が最小である第1の構成を、前記構成制御手段に構成させる、

ことを特徴とする請求項1に記載の画像データ処理装置。

【請求項3】

前記最大値判定手段は、前記可逆圧縮手段に対して前記処理単位の画像データをラインごとに圧縮させ、この圧縮により得られた各ラインの圧縮データのデータサイズから前記最大値を判定し、

前記出力制御手段は、前記最大値判定手段が判定した前記最大値が前記閾値以下である場合には、前記最大値判定手段の判定のための圧縮により得られた前記圧縮データを保存しておき、当該処理単位の画像データについて前記画像処理回路に処理させる際に、保存しておいた前記圧縮データを前記第1のラインメモリを介して前記画像処理回路に出力する、

ことを特徴とする請求項1〜2のいずれか1項に記載の画像データ処理装置。

【請求項4】

前記出力制御手段がある処理単位の画像データ又は圧縮データを前記第1のラインメモリ又は前記第2のラインメモリを介して前記画像処理回路に出力している間に、前記可逆圧縮手段及び前記最大値判定手段が後続の別の処理単位についての圧縮及び前記最大値の判定を行う、

ことを特徴とする請求項3に記載の画像データ処理装置。

【請求項5】

前記再構成可能回路上に構成されたラインメモリを含まない第3の回路構成に、ある処理単位についての処理を実行させている間に、前記可逆圧縮手段及び前記最大値判定手段がその処理単位より前の処理単位についての圧縮及び前記最大値の判定を行う、

ことを特徴とする請求項3又は4に記載の画像データ処理装置。

【請求項6】

コンピュータを、

画像データをラインごとに可逆圧縮する可逆圧縮手段、

再構成可能回路上に、前記可逆圧縮手段の可逆圧縮により得られた圧縮データを保持するための第1のラインメモリと当該圧縮データを伸長するための伸長回路とを含む第1の構成と、非圧縮の前記画像データを保持するための第2のラインメモリを含む第2の構成と、を選択的に構成する制御を行う構成制御手段であって、前記第1のラインメモリの容量は、前記第1の構成の回路規模が前記第2の構成の回路規模以下となるように定められていることを特徴とする構成制御手段、

処理単位の画像データ内の各ラインを前記可逆圧縮手段で圧縮した場合のラインごとの圧縮データのデータサイズの最大値を判定する最大値判定手段、

前記最大値判定手段が判定した前記最大値が前記第1のラインメモリの容量に対応するあらかじめ定められた閾値以下である場合には、前記構成制御手段に対して前記第1の構成を前記再構成回路上に構成するよう指示すると共に、前記画像データの前記可逆圧縮手段による圧縮データを、前記第1のラインメモリを介して画像処理回路に出力し、前記最大値判定手段が判定した前記最大値が前記閾値を上回る場合には、前記構成制御手段に対して前記第2の構成を前記再構成回路上に構成するよう指示すると共に、非圧縮の前記画像データを、前記第2のラインメモリを介して前記画像処理回路に出力するよう制御する出力制御手段、

として機能させるためのプログラム。

【請求項1】

画像データをラインごとに可逆圧縮する可逆圧縮手段と、

再構成可能回路上に、前記可逆圧縮手段の可逆圧縮により得られた圧縮データを保持するための第1のラインメモリと当該圧縮データを伸長するための伸長回路とを含む第1の構成と、非圧縮の前記画像データを保持するための第2のラインメモリを含む第2の構成と、を選択的に構成する制御を行う構成制御手段であって、前記第1のラインメモリの容量は、前記第1の構成の回路規模が前記第2の構成の回路規模以下となるように定められていることを特徴とする構成制御手段と、

処理単位の画像データ内の各ラインを前記可逆圧縮手段で圧縮した場合のラインごとの圧縮データのデータサイズの最大値を判定する最大値判定手段と、

前記最大値判定手段が判定した前記最大値が前記第1のラインメモリの容量に対応するあらかじめ定められた閾値以下である場合には、前記構成制御手段に対して前記第1の構成を前記再構成回路上に構成するよう指示すると共に、前記画像データの前記可逆圧縮手段による圧縮データを、前記第1のラインメモリを介して画像処理回路に出力し、前記最大値判定手段が判定した前記最大値が前記閾値を上回る場合には、前記構成制御手段に対して前記第2の構成を前記再構成回路上に構成するよう指示すると共に、非圧縮の前記画像データを、前記第2のラインメモリを介して前記画像処理回路に出力するよう制御する出力制御手段と、

を備える画像データ処理装置。

【請求項2】

前記構成制御手段は、前記第1のラインメモリの容量が異なる複数の前記第1の構成を選択的に前記再構成可能回路上に構成可能であり、

前記出力制御手段は、複数の前記第1の構成のうち前記第1のラインメモリの容量が前記最大値判定手段により判定された前記最大値以上であるものの中で、前記第1のラインメモリの容量が最小である第1の構成を、前記構成制御手段に構成させる、

ことを特徴とする請求項1に記載の画像データ処理装置。

【請求項3】

前記最大値判定手段は、前記可逆圧縮手段に対して前記処理単位の画像データをラインごとに圧縮させ、この圧縮により得られた各ラインの圧縮データのデータサイズから前記最大値を判定し、

前記出力制御手段は、前記最大値判定手段が判定した前記最大値が前記閾値以下である場合には、前記最大値判定手段の判定のための圧縮により得られた前記圧縮データを保存しておき、当該処理単位の画像データについて前記画像処理回路に処理させる際に、保存しておいた前記圧縮データを前記第1のラインメモリを介して前記画像処理回路に出力する、

ことを特徴とする請求項1〜2のいずれか1項に記載の画像データ処理装置。

【請求項4】

前記出力制御手段がある処理単位の画像データ又は圧縮データを前記第1のラインメモリ又は前記第2のラインメモリを介して前記画像処理回路に出力している間に、前記可逆圧縮手段及び前記最大値判定手段が後続の別の処理単位についての圧縮及び前記最大値の判定を行う、

ことを特徴とする請求項3に記載の画像データ処理装置。

【請求項5】

前記再構成可能回路上に構成されたラインメモリを含まない第3の回路構成に、ある処理単位についての処理を実行させている間に、前記可逆圧縮手段及び前記最大値判定手段がその処理単位より前の処理単位についての圧縮及び前記最大値の判定を行う、

ことを特徴とする請求項3又は4に記載の画像データ処理装置。

【請求項6】

コンピュータを、

画像データをラインごとに可逆圧縮する可逆圧縮手段、

再構成可能回路上に、前記可逆圧縮手段の可逆圧縮により得られた圧縮データを保持するための第1のラインメモリと当該圧縮データを伸長するための伸長回路とを含む第1の構成と、非圧縮の前記画像データを保持するための第2のラインメモリを含む第2の構成と、を選択的に構成する制御を行う構成制御手段であって、前記第1のラインメモリの容量は、前記第1の構成の回路規模が前記第2の構成の回路規模以下となるように定められていることを特徴とする構成制御手段、

処理単位の画像データ内の各ラインを前記可逆圧縮手段で圧縮した場合のラインごとの圧縮データのデータサイズの最大値を判定する最大値判定手段、

前記最大値判定手段が判定した前記最大値が前記第1のラインメモリの容量に対応するあらかじめ定められた閾値以下である場合には、前記構成制御手段に対して前記第1の構成を前記再構成回路上に構成するよう指示すると共に、前記画像データの前記可逆圧縮手段による圧縮データを、前記第1のラインメモリを介して画像処理回路に出力し、前記最大値判定手段が判定した前記最大値が前記閾値を上回る場合には、前記構成制御手段に対して前記第2の構成を前記再構成回路上に構成するよう指示すると共に、非圧縮の前記画像データを、前記第2のラインメモリを介して前記画像処理回路に出力するよう制御する出力制御手段、

として機能させるためのプログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−231215(P2012−231215A)

【公開日】平成24年11月22日(2012.11.22)

【国際特許分類】

【出願番号】特願2011−96942(P2011−96942)

【出願日】平成23年4月25日(2011.4.25)

【出願人】(000005496)富士ゼロックス株式会社 (21,908)

【Fターム(参考)】

【公開日】平成24年11月22日(2012.11.22)

【国際特許分類】

【出願日】平成23年4月25日(2011.4.25)

【出願人】(000005496)富士ゼロックス株式会社 (21,908)

【Fターム(参考)】

[ Back to top ]