画像処理システム

【課題】多様な画像を容易に処理可能として汎用性を向上させる。

【解決手段】画像処理システム10は、複数の画面表示装置13にて表示される複数画面分の画像データを1つの画面分の画像データに統合して、1フレーム毎の画像データ(統合画像データ)として記憶する際に、ドットクロック周期の最大公約数または該最大公約数の1/2である共通のドットクロック周期によって複数画面分の描画を行なう画像描画装置11と、1フレーム毎の統合画像データを構成する複数の画像データのそれぞれに対して設定された分周比によって共通のドットクロック周期を分周して得られる個別のドットクロック周期によって統合画像データを複数の画像データに分割する画像分割装置12と、を備える。

【解決手段】画像処理システム10は、複数の画面表示装置13にて表示される複数画面分の画像データを1つの画面分の画像データに統合して、1フレーム毎の画像データ(統合画像データ)として記憶する際に、ドットクロック周期の最大公約数または該最大公約数の1/2である共通のドットクロック周期によって複数画面分の描画を行なう画像描画装置11と、1フレーム毎の統合画像データを構成する複数の画像データのそれぞれに対して設定された分周比によって共通のドットクロック周期を分周して得られる個別のドットクロック周期によって統合画像データを複数の画像データに分割する画像分割装置12と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、画像処理システムに関する。

【背景技術】

【0002】

従来、例えば2以上の任意の自然数mによるm個の表示器に表示する異なる画像を1つの画像として1台の画像生成装置から出力する画像表示システムが知られている。(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2000−3164号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、上記従来技術に係る画像表示システムにおいては、画像生成装置から出力された1つの画像を、1/m周期づつずれた同期信号に応じてm個の画像に分解してm個の表示器に表示させている。

つまり、m個の表示器に対応したm個の画像は同一の解像度を有していることが前提になっており、例えば異なる解像度のm個の画像を混在させて1つの画像とした場合には、1/m周期づつずれた同期信号を用いても、この1つの画像を適切に分解することはできないという問題が生じる。

このような問題が生じることに対して、例えば異なる解像度のm個の画像を混在させて1つの画像とした場合などにも適切に対応して、画像表示の多様性およびシステムの汎用性を向上させることが望まれている。

【0005】

本発明は上記事情に鑑みてなされたもので、多様な画像を容易に処理可能として汎用性を向上させることが可能な画像処理システムを提供することを目的としている。

【課題を解決するための手段】

【0006】

上記課題を解決して係る目的を達成するために、本発明の画像処理システムは、複数の画像のクロック周期の最大公約数または該最大公約数の1/2である共通のクロック周期によって前記複数の画像を1つの統合画像に統合する画像生成手段と、前記複数の画像の分周比によって前記共通のクロック周期を分周して得られる個別のクロック周期によって前記統合画像を前記複数の画像に分割する画像分割手段と、を備える。

【発明の効果】

【0007】

本発明の画像処理システムによれば、クロック周期が異なる複数の画像に対して、複数の異なるクロック周期の最大公約数または該最大公約数の1/2である共通のクロック周期を用いて、統合および分割の処理を行なうことから、例えばドットクロックおよび解像度などが異なる複数の画像を複数の異なる表示画面に表示する場合であっても、1つの画像生成手段から1つの統合画像を出力するだけで済み、システム構成が複雑化することを防止しつつ、多様な画像を容易に処理可能として汎用性を向上させることができる。

【図面の簡単な説明】

【0008】

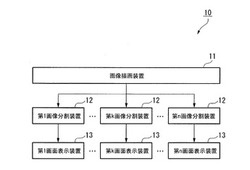

【図1】本発明の実施の形態に係る画像処理システムの構成図である。

【図2】本発明の実施の形態に係る画像処理システムにより生成される合成画像の例を示す図である。

【図3】本発明の実施の形態に係る画像分割装置の構成図である。

【図4】本発明の実施の形態の変形例に係る画像処理システムの構成図である。

【発明を実施するための形態】

【0009】

以下、本発明の一実施形態に係る画像処理システムについて添付図面を参照しながら説明する。

本実施の形態による画像処理システム10は、例えば図1に示すように、1つの画像描画装置11と、複数(例えば、2以上の任意の自然数k,n(n>k)によるn個)の画像分割装置12および画面表示装置13とを備えて構成されている。

【0010】

画像描画装置11は、例えばグラフィックチップなどのICやLSIなどからなるVDP(Video Display Processor)であって、水晶振動子などの発振器(図示略)およびメモリ(図示略)などを備えて構成されている。

【0011】

画像描画装置11は、例えば、複数の画面表示装置13にて表示される複数画面分の画像データ(例えば、RGBデータなど)を外部メモリ(図示略)などから取得し、これらの複数画面分の画像データを仮想的に描画するようにしてメモリに展開することによって1つの画面分の画像データに統合して、1フレーム毎の画像データ(統合画像データ)としてメモリに一時的に記憶する。

特に、画像描画装置11は、例えばドットクロックおよび解像度などが異なる複数の画像データに対して、複数の画像データのドットクロック周期の最大公約数または該最大公約数の1/2である共通のドットクロック周期によって複数画面分の描画を行なう。

【0012】

より詳細には、画像描画装置11は、例えば、複数の画像データのドットクロック周期の最大公約数が、複数の画像データの何れかの画像データのドットクロック周期と同一である場合には、最大公約数の1/2を共通のドットクロック周期とし、複数の画像データのドットクロック周期の最大公約数が、複数の画像データの何れの画像データのドットクロック周期とも異なる場合には、この最大公約数の1/2を共通のドットクロック周期とする。

【0013】

例えば図2(A)に示すように2画面A,B分の同一解像度かつ同一ドットクロック周期(例えば、25nsec)の2つの画像データに対しては、各画像データのドットクロック周期の1/2を共通のドットクロック周期(12.5nsec)として、この共通のドットクロック周期により2画面A,B分の描画を行なう。

【0014】

また、例えば図2(B)に示すように2画面A,B分の異なる解像度かつ異なるドットクロック周期(例えば、24nsecおよび32nsec)の2つの画像データに対しては、各画像データのドットクロック周期の最大公約数を共通のドットクロック周期(例えば、8nsec)として、この共通のドットクロック周期により2画面A,B分の描画を行なう。

【0015】

また、画像描画装置11は、複数の画像データに対する共通のドットクロック周期によって複数画面分の描画を行なう際に、例えば所定のドットパターンを有する制御用データによって複数の画像データを区分する。

【0016】

画像描画装置11は、例えば図2(A),(B)に示すような1ドットずつ黒色と白色とを繰り返すドットパターンなどの所定の制御用データ(例えば、制御用DATA1,2)を、各画像データに隣接して配置する。

【0017】

例えば図2(A)に示すように1フレーム毎の統合画像データにおいて2画面A,B分の同一解像度かつ同一ドットクロック周期の2つの画像データが水平方向に配列されている場合には、水平方向で各画像データに隣接して、例えば同一のドットパターンを有する2つの制御用データ(例えば、制御用DATA1,2)を付与する。

【0018】

また、例えば図2(B)に示すように1フレーム毎の統合画像データにおいて2画面A,B分の異なる解像度かつ異なるドットクロック周期の2つの画像データが水平方向に配列されている場合には、水平方向で各画像データに隣接して、例えば異なるドットパターンを有する2つの制御用データ(例えば、制御用DATA1,2)を付与する。

【0019】

なお、例えば図2(B)に示すように2画面A,B分の2つの画像データが異なる解像度を有することに起因して、1フレーム毎の統合画像データにおいて垂直方向で画面Bの画像データの下方に画像データが存在しない場合などのように、垂直方向での画像データの区分を示す必要がある場合には、垂直方向においてドットパターンが変更された制御用データ(例えば、垂直方向での画像データの区分を示す境界位置の上方と下方とにおいて異なるドットパターンを有する制御用DATA1)を2画面A,B分の2つの画像データ間に付与する。

【0020】

上述したように、画像描画装置11は、例えば発振器の発振による基準信号に基づいて、複数の画像データのドットクロック周期の最大公約数または該最大公約数の1/2である共通のドットクロック周期を有するドットクロック信号(つまり、1フレーム毎の統合画像データにおいて1ドットの点を描画する周波数を示す信号)を生成する。

【0021】

さらに、画像描画装置11は、ドットクロック信号に基づいて、複数画面分の画像データを仮想的に描画するようにしてメモリに展開するための垂直同期信号(VSYNC)および水平同期信号(HSYNC)およびデータイネーブル信号(DE)などの同期信号を生成する。

【0022】

なお、水平同期信号(HSYNC)は、1フレーム毎の統合画像データの水平方向における画素1ライン分の画像データの描画タイミングを示す信号である。

垂直同期信号(VSYNC)は、1フレーム毎の統合画像データの垂直方向における画素1フレーム分の画像データの描画タイミングを示す信号である。

データイネーブル信号(DE)は、1フレーム毎の統合画像データの水平方向における1ライン分の画像データの描画期間を示す信号である。

【0023】

そして、画像描画装置11は、例えば、メモリに一時的に記憶した1フレーム毎の統合画像データを各ライン毎に読み出して、各ライン毎の統合画像データ(ラインデータ)を同期信号に応じたタイミングで出力すると共に、共通のドットクロック周期を有するドットクロック信号および該ドットクロック信号に応じた同期信号を出力する。

【0024】

画像分割装置12は、例えば図3に示すように、分周回路21と、制御回路22と、レジスタ23とを備えて構成され、画像描画装置11から出力された統合画像データのラインデータを構成する複数の画像データのうちから、この画像分割装置12に対応した画面表示装置13にて表示される所定の何れか1つの画像データを抽出する。

【0025】

分周回路21は、例えばカウンタやPLLなどを備えて構成され、画像描画装置11から出力されたドットクロック信号に基づき、1フレーム毎の統合画像データを構成する複数の画像データのそれぞれに対して設定された分周比のうちの所定の何れか1つによって、ドットクロック信号の共通のドットクロック周期を分周して得られる個別のドットクロック周期を有する個別のドットクロック信号を出力する。

【0026】

制御回路22は、例えば、画像描画装置11から出力された統合画像データのラインデータに含まれる制御用データおよびドットクロック信号および同期信号と、分周回路21から出力された個別のドットクロック信号とに基づき、1フレーム毎の統合画像データを構成する複数の画像データのうちの所定の何れか1つの画像データを画面表示装置13の表示画面に表示するための個別のドットクロック信号に応じた垂直同期信号(VSYNC)および水平同期信号(HSYNC)およびデータイネーブル信号(DE)などの個別の同期信号を生成し、これらの同期信号を出力する。

【0027】

また、制御回路22は、例えば、画像描画装置11から出力された統合画像データのラインデータに含まれる制御用データおよび画像描画装置11から出力された同期信号に基づき、統合画像データのラインデータを構成する複数の画像データに対して、所定の何れか1つの画像データであるか否かを判定し、この判定結果を示す信号を出力する。

【0028】

レジスタ23は、例えばFIFOなどを備えて構成され、分周回路21および制御回路22に同期して、画像描画装置11から出力された画像データの入力および保存および出力を行なう。

より具体的には、レジスタ23は、制御回路22から出力された判定結果の信号に応じて、画像描画装置11から出力された統合画像データのラインデータを構成する複数の画像データのうちから、所定の何れか1つの画像データを抽出して、該画像データを分周回路21から出力された個別のドットクロック信号に同期して出力する。

【0029】

画面表示装置13は、例えば液晶ディスプレイやブラウン管ディスプレイなどを備えて構成され、画像分割装置12から出力された個別のドットクロック信号および個別の同期信号に応じて、画像分割装置12から出力された画像データ(つまり、画像描画装置11から出力された統合画像データのラインデータを構成する複数の画像データのうちの所定の何れか1つの画像データ)を表示する。

【0030】

上述したように、本実施の形態による画像処理システム10によれば、ドットクロックが異なる複数の画像データに対して、複数の異なるドットクロック周期の最大公約数または該最大公約数の1/2である共通のドットクロック周期を用いて、統合および分割の処理を行なう。

これにより、例えばドットクロックおよび解像度などが異なる複数の画像データを複数の異なる表示画面に表示する場合であっても、1つの画像描画装置11から1つの統合画像データを出力するだけで済み、システム構成が複雑化することを防止しつつ、多様な画像を容易に処理可能として汎用性を向上させることができる。

【0031】

しかも、制御用データによって、統合画像データを構成する複数の画像データを容易かつ適正に区分することができる。

【0032】

なお、上述した実施の形態においては、制御用データに基づいて統合画像データを構成する複数の画像データの何れであるかを判定するとしたが、これに限定されず、例えば制御用データを省略して、他の信号、例えば複数画面分の画像データのドットクロックの信号などに基づいて統合画像データを構成する複数の画像データの何れであるかを判定してもよい。

この場合、画像描画装置11は、共通のドットクロック周期を有するドットクロック信号に加えて、複数画面分の画像データのドットクロックの信号を出力すればよく、画像分割装置12の制御回路22は、複数画面分の画像データのドットクロックの信号に基づいて、統合画像データのラインデータを構成する複数の画像データに対して、所定の何れか1つの画像データであるか否かを判定すればよい。

【0033】

なお、上述した実施の形態においては、例えば図4に示す変形例のように、1つの画像描画装置11と、複数(例えば、2以上の任意の自然数k,n(n>k)によるn個)の画像分割装置12および画面表示装置13とを制御する制御装置30を備え、この制御装置30の制御に応じて、複数の画面表示装置13にて表示される複数画面分の画像データの組み合わせおよびドットクロックおよび解像度および分周比などが適宜に変更されてもよい。

【符号の説明】

【0034】

10 画像処理システム

11 画像描画装置

12 画像分割装置

13 画面表示装置

21 分周回路

22 制御回路

23 レジスタ

【技術分野】

【0001】

この発明は、画像処理システムに関する。

【背景技術】

【0002】

従来、例えば2以上の任意の自然数mによるm個の表示器に表示する異なる画像を1つの画像として1台の画像生成装置から出力する画像表示システムが知られている。(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2000−3164号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、上記従来技術に係る画像表示システムにおいては、画像生成装置から出力された1つの画像を、1/m周期づつずれた同期信号に応じてm個の画像に分解してm個の表示器に表示させている。

つまり、m個の表示器に対応したm個の画像は同一の解像度を有していることが前提になっており、例えば異なる解像度のm個の画像を混在させて1つの画像とした場合には、1/m周期づつずれた同期信号を用いても、この1つの画像を適切に分解することはできないという問題が生じる。

このような問題が生じることに対して、例えば異なる解像度のm個の画像を混在させて1つの画像とした場合などにも適切に対応して、画像表示の多様性およびシステムの汎用性を向上させることが望まれている。

【0005】

本発明は上記事情に鑑みてなされたもので、多様な画像を容易に処理可能として汎用性を向上させることが可能な画像処理システムを提供することを目的としている。

【課題を解決するための手段】

【0006】

上記課題を解決して係る目的を達成するために、本発明の画像処理システムは、複数の画像のクロック周期の最大公約数または該最大公約数の1/2である共通のクロック周期によって前記複数の画像を1つの統合画像に統合する画像生成手段と、前記複数の画像の分周比によって前記共通のクロック周期を分周して得られる個別のクロック周期によって前記統合画像を前記複数の画像に分割する画像分割手段と、を備える。

【発明の効果】

【0007】

本発明の画像処理システムによれば、クロック周期が異なる複数の画像に対して、複数の異なるクロック周期の最大公約数または該最大公約数の1/2である共通のクロック周期を用いて、統合および分割の処理を行なうことから、例えばドットクロックおよび解像度などが異なる複数の画像を複数の異なる表示画面に表示する場合であっても、1つの画像生成手段から1つの統合画像を出力するだけで済み、システム構成が複雑化することを防止しつつ、多様な画像を容易に処理可能として汎用性を向上させることができる。

【図面の簡単な説明】

【0008】

【図1】本発明の実施の形態に係る画像処理システムの構成図である。

【図2】本発明の実施の形態に係る画像処理システムにより生成される合成画像の例を示す図である。

【図3】本発明の実施の形態に係る画像分割装置の構成図である。

【図4】本発明の実施の形態の変形例に係る画像処理システムの構成図である。

【発明を実施するための形態】

【0009】

以下、本発明の一実施形態に係る画像処理システムについて添付図面を参照しながら説明する。

本実施の形態による画像処理システム10は、例えば図1に示すように、1つの画像描画装置11と、複数(例えば、2以上の任意の自然数k,n(n>k)によるn個)の画像分割装置12および画面表示装置13とを備えて構成されている。

【0010】

画像描画装置11は、例えばグラフィックチップなどのICやLSIなどからなるVDP(Video Display Processor)であって、水晶振動子などの発振器(図示略)およびメモリ(図示略)などを備えて構成されている。

【0011】

画像描画装置11は、例えば、複数の画面表示装置13にて表示される複数画面分の画像データ(例えば、RGBデータなど)を外部メモリ(図示略)などから取得し、これらの複数画面分の画像データを仮想的に描画するようにしてメモリに展開することによって1つの画面分の画像データに統合して、1フレーム毎の画像データ(統合画像データ)としてメモリに一時的に記憶する。

特に、画像描画装置11は、例えばドットクロックおよび解像度などが異なる複数の画像データに対して、複数の画像データのドットクロック周期の最大公約数または該最大公約数の1/2である共通のドットクロック周期によって複数画面分の描画を行なう。

【0012】

より詳細には、画像描画装置11は、例えば、複数の画像データのドットクロック周期の最大公約数が、複数の画像データの何れかの画像データのドットクロック周期と同一である場合には、最大公約数の1/2を共通のドットクロック周期とし、複数の画像データのドットクロック周期の最大公約数が、複数の画像データの何れの画像データのドットクロック周期とも異なる場合には、この最大公約数の1/2を共通のドットクロック周期とする。

【0013】

例えば図2(A)に示すように2画面A,B分の同一解像度かつ同一ドットクロック周期(例えば、25nsec)の2つの画像データに対しては、各画像データのドットクロック周期の1/2を共通のドットクロック周期(12.5nsec)として、この共通のドットクロック周期により2画面A,B分の描画を行なう。

【0014】

また、例えば図2(B)に示すように2画面A,B分の異なる解像度かつ異なるドットクロック周期(例えば、24nsecおよび32nsec)の2つの画像データに対しては、各画像データのドットクロック周期の最大公約数を共通のドットクロック周期(例えば、8nsec)として、この共通のドットクロック周期により2画面A,B分の描画を行なう。

【0015】

また、画像描画装置11は、複数の画像データに対する共通のドットクロック周期によって複数画面分の描画を行なう際に、例えば所定のドットパターンを有する制御用データによって複数の画像データを区分する。

【0016】

画像描画装置11は、例えば図2(A),(B)に示すような1ドットずつ黒色と白色とを繰り返すドットパターンなどの所定の制御用データ(例えば、制御用DATA1,2)を、各画像データに隣接して配置する。

【0017】

例えば図2(A)に示すように1フレーム毎の統合画像データにおいて2画面A,B分の同一解像度かつ同一ドットクロック周期の2つの画像データが水平方向に配列されている場合には、水平方向で各画像データに隣接して、例えば同一のドットパターンを有する2つの制御用データ(例えば、制御用DATA1,2)を付与する。

【0018】

また、例えば図2(B)に示すように1フレーム毎の統合画像データにおいて2画面A,B分の異なる解像度かつ異なるドットクロック周期の2つの画像データが水平方向に配列されている場合には、水平方向で各画像データに隣接して、例えば異なるドットパターンを有する2つの制御用データ(例えば、制御用DATA1,2)を付与する。

【0019】

なお、例えば図2(B)に示すように2画面A,B分の2つの画像データが異なる解像度を有することに起因して、1フレーム毎の統合画像データにおいて垂直方向で画面Bの画像データの下方に画像データが存在しない場合などのように、垂直方向での画像データの区分を示す必要がある場合には、垂直方向においてドットパターンが変更された制御用データ(例えば、垂直方向での画像データの区分を示す境界位置の上方と下方とにおいて異なるドットパターンを有する制御用DATA1)を2画面A,B分の2つの画像データ間に付与する。

【0020】

上述したように、画像描画装置11は、例えば発振器の発振による基準信号に基づいて、複数の画像データのドットクロック周期の最大公約数または該最大公約数の1/2である共通のドットクロック周期を有するドットクロック信号(つまり、1フレーム毎の統合画像データにおいて1ドットの点を描画する周波数を示す信号)を生成する。

【0021】

さらに、画像描画装置11は、ドットクロック信号に基づいて、複数画面分の画像データを仮想的に描画するようにしてメモリに展開するための垂直同期信号(VSYNC)および水平同期信号(HSYNC)およびデータイネーブル信号(DE)などの同期信号を生成する。

【0022】

なお、水平同期信号(HSYNC)は、1フレーム毎の統合画像データの水平方向における画素1ライン分の画像データの描画タイミングを示す信号である。

垂直同期信号(VSYNC)は、1フレーム毎の統合画像データの垂直方向における画素1フレーム分の画像データの描画タイミングを示す信号である。

データイネーブル信号(DE)は、1フレーム毎の統合画像データの水平方向における1ライン分の画像データの描画期間を示す信号である。

【0023】

そして、画像描画装置11は、例えば、メモリに一時的に記憶した1フレーム毎の統合画像データを各ライン毎に読み出して、各ライン毎の統合画像データ(ラインデータ)を同期信号に応じたタイミングで出力すると共に、共通のドットクロック周期を有するドットクロック信号および該ドットクロック信号に応じた同期信号を出力する。

【0024】

画像分割装置12は、例えば図3に示すように、分周回路21と、制御回路22と、レジスタ23とを備えて構成され、画像描画装置11から出力された統合画像データのラインデータを構成する複数の画像データのうちから、この画像分割装置12に対応した画面表示装置13にて表示される所定の何れか1つの画像データを抽出する。

【0025】

分周回路21は、例えばカウンタやPLLなどを備えて構成され、画像描画装置11から出力されたドットクロック信号に基づき、1フレーム毎の統合画像データを構成する複数の画像データのそれぞれに対して設定された分周比のうちの所定の何れか1つによって、ドットクロック信号の共通のドットクロック周期を分周して得られる個別のドットクロック周期を有する個別のドットクロック信号を出力する。

【0026】

制御回路22は、例えば、画像描画装置11から出力された統合画像データのラインデータに含まれる制御用データおよびドットクロック信号および同期信号と、分周回路21から出力された個別のドットクロック信号とに基づき、1フレーム毎の統合画像データを構成する複数の画像データのうちの所定の何れか1つの画像データを画面表示装置13の表示画面に表示するための個別のドットクロック信号に応じた垂直同期信号(VSYNC)および水平同期信号(HSYNC)およびデータイネーブル信号(DE)などの個別の同期信号を生成し、これらの同期信号を出力する。

【0027】

また、制御回路22は、例えば、画像描画装置11から出力された統合画像データのラインデータに含まれる制御用データおよび画像描画装置11から出力された同期信号に基づき、統合画像データのラインデータを構成する複数の画像データに対して、所定の何れか1つの画像データであるか否かを判定し、この判定結果を示す信号を出力する。

【0028】

レジスタ23は、例えばFIFOなどを備えて構成され、分周回路21および制御回路22に同期して、画像描画装置11から出力された画像データの入力および保存および出力を行なう。

より具体的には、レジスタ23は、制御回路22から出力された判定結果の信号に応じて、画像描画装置11から出力された統合画像データのラインデータを構成する複数の画像データのうちから、所定の何れか1つの画像データを抽出して、該画像データを分周回路21から出力された個別のドットクロック信号に同期して出力する。

【0029】

画面表示装置13は、例えば液晶ディスプレイやブラウン管ディスプレイなどを備えて構成され、画像分割装置12から出力された個別のドットクロック信号および個別の同期信号に応じて、画像分割装置12から出力された画像データ(つまり、画像描画装置11から出力された統合画像データのラインデータを構成する複数の画像データのうちの所定の何れか1つの画像データ)を表示する。

【0030】

上述したように、本実施の形態による画像処理システム10によれば、ドットクロックが異なる複数の画像データに対して、複数の異なるドットクロック周期の最大公約数または該最大公約数の1/2である共通のドットクロック周期を用いて、統合および分割の処理を行なう。

これにより、例えばドットクロックおよび解像度などが異なる複数の画像データを複数の異なる表示画面に表示する場合であっても、1つの画像描画装置11から1つの統合画像データを出力するだけで済み、システム構成が複雑化することを防止しつつ、多様な画像を容易に処理可能として汎用性を向上させることができる。

【0031】

しかも、制御用データによって、統合画像データを構成する複数の画像データを容易かつ適正に区分することができる。

【0032】

なお、上述した実施の形態においては、制御用データに基づいて統合画像データを構成する複数の画像データの何れであるかを判定するとしたが、これに限定されず、例えば制御用データを省略して、他の信号、例えば複数画面分の画像データのドットクロックの信号などに基づいて統合画像データを構成する複数の画像データの何れであるかを判定してもよい。

この場合、画像描画装置11は、共通のドットクロック周期を有するドットクロック信号に加えて、複数画面分の画像データのドットクロックの信号を出力すればよく、画像分割装置12の制御回路22は、複数画面分の画像データのドットクロックの信号に基づいて、統合画像データのラインデータを構成する複数の画像データに対して、所定の何れか1つの画像データであるか否かを判定すればよい。

【0033】

なお、上述した実施の形態においては、例えば図4に示す変形例のように、1つの画像描画装置11と、複数(例えば、2以上の任意の自然数k,n(n>k)によるn個)の画像分割装置12および画面表示装置13とを制御する制御装置30を備え、この制御装置30の制御に応じて、複数の画面表示装置13にて表示される複数画面分の画像データの組み合わせおよびドットクロックおよび解像度および分周比などが適宜に変更されてもよい。

【符号の説明】

【0034】

10 画像処理システム

11 画像描画装置

12 画像分割装置

13 画面表示装置

21 分周回路

22 制御回路

23 レジスタ

【特許請求の範囲】

【請求項1】

複数の画像のクロック周期の最大公約数または該最大公約数の1/2である共通のクロック周期によって前記複数の画像を1つの統合画像に統合する画像生成手段と、

前記複数の画像の分周比によって前記共通のクロック周期を分周して得られる個別のクロック周期によって前記統合画像を前記複数の画像に分割する画像分割手段と、を備えることを特徴とする画像処理システム。

【請求項2】

前記画像生成手段は、前記複数の画像を前記統合画像に統合する際に、制御用データによって前記複数の画像を区分し、

前記画像分割手段は、前記統合画像を前記複数の画像に分割する際に、前記制御用データによって前記複数の画像の何れであるかを判定することを特徴とする請求項1に記載の画像処理システム。

【請求項3】

前記画像分割手段は、前記統合画像を前記複数の画像に分割する際に、前記複数の画像のクロック周期によって前記複数の画像の何れであるかを判定することを特徴とする請求項1に記載の画像処理システム。

【請求項1】

複数の画像のクロック周期の最大公約数または該最大公約数の1/2である共通のクロック周期によって前記複数の画像を1つの統合画像に統合する画像生成手段と、

前記複数の画像の分周比によって前記共通のクロック周期を分周して得られる個別のクロック周期によって前記統合画像を前記複数の画像に分割する画像分割手段と、を備えることを特徴とする画像処理システム。

【請求項2】

前記画像生成手段は、前記複数の画像を前記統合画像に統合する際に、制御用データによって前記複数の画像を区分し、

前記画像分割手段は、前記統合画像を前記複数の画像に分割する際に、前記制御用データによって前記複数の画像の何れであるかを判定することを特徴とする請求項1に記載の画像処理システム。

【請求項3】

前記画像分割手段は、前記統合画像を前記複数の画像に分割する際に、前記複数の画像のクロック周期によって前記複数の画像の何れであるかを判定することを特徴とする請求項1に記載の画像処理システム。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2013−72913(P2013−72913A)

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願番号】特願2011−210107(P2011−210107)

【出願日】平成23年9月27日(2011.9.27)

【出願人】(302069930)NECエンベデッドプロダクツ株式会社 (738)

【Fターム(参考)】

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願日】平成23年9月27日(2011.9.27)

【出願人】(302069930)NECエンベデッドプロダクツ株式会社 (738)

【Fターム(参考)】

[ Back to top ]