画像処理装置、画像処理回路、及び画像処理方法

【課題】ブロック単位で処理を行う画像処理装置において、フィルタリング処理時間をより短くする。

【解決手段】原画像データの所定の領域であるブロック画像データについて、主走査幅N、副走査幅Mのフィルターを用いてフィルタリングを行う画像処理装置は、画素データを複数方向にシフト可能なレジスターを用いて、ブロック画像データを構成する副走査方向の画素データ列それぞれを、副走査方向とその逆方向を交互に処理し、また、主走査方向の列の順に処理する。

【解決手段】原画像データの所定の領域であるブロック画像データについて、主走査幅N、副走査幅Mのフィルターを用いてフィルタリングを行う画像処理装置は、画素データを複数方向にシフト可能なレジスターを用いて、ブロック画像データを構成する副走査方向の画素データ列それぞれを、副走査方向とその逆方向を交互に処理し、また、主走査方向の列の順に処理する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ブロック単位で画像データを処理する画像処理技術に関する。

【背景技術】

【0002】

プリンター、スキャナー、コピー機、複合機等の画像処理装置において、例えば、1ページ分の画像データ(主走査幅W、副走査幅H)について、ブロック(主走査幅W、副走査幅L(L:L<H))単位で処理対象の画像データを切り出し、所定の画像処理(例えば、フィルタリング処理等)を行う技術が知られている(例えば、特許文献1)。

【0003】

各ブロックの画像データは、副走査方向の画素データの列(主走査幅1、副走査幅L)ごとに、副走査方向に順次処理される。各画素データ列の処理が終了した場合には、当該列の主走査方向に隣接する画素データ列が次に処理される。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2001−251502号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

特許文献1では、RAMに格納された原画像データから切り出されたブロック画像に含まれる画素データのうち、フィルタリング処理の対象となる画素データが一旦レジスターに格納される。また、当該レジスターから出力される画素データを用いてフィルタリング処理が行われる。

【0006】

しかしながら、特許文献1では、ある画素データ列の副走査方向のフィルタリング処理が終了し、次の画素データ列のフィルタリング処理が開始される場合、当該画素データ列の先頭部分の画素データをレジスターに格納する必要がある。すなわち、フィルタリング処理が終了したときにレジスターに格納されている画素データ(フィルタリング処理が終了した画素データ列の後尾部分の画素データ)は、削除する必要がある。そのため、各画素データ列のフィルタリング処理を開始するために、画素データを入れ替える必要があり、処理時間が増加する。

【0007】

そこで、本発明は、ブロック単位で処理を行う画像処理装置において、フィルタリング処理時間をより短くすることを目的とする。

【課題を解決するための手段】

【0008】

上記の課題を解決するための本発明の第一の態様は、原画像データの所定の領域であるブロック画像データについて、主走査幅N、副走査幅Mのフィルターを用いてフィルタリングを行う画像処理装置であって、前記ブロック画像データを構成する副走査方向の画素データ列それぞれを、副走査方向とその逆方向を交互に処理し、また、主走査方向の列の順に処理する、ことを特徴とする。

【0009】

ここで、上記の画像処理装置であって、前記ブロック画像データの少なくとも一部を格納するメモリーと、主走査幅N+1、副走査幅Mの容量であって、格納される画像データを複数の方向にシフト可能なシフトレジスターで構成され、前記メモリーから主走査幅N+1、副走査幅1の画像データを順次取得して格納し、主走査幅N、副走査幅Mの画像データを出力するレジスター部と、前記レジスター部から主走査幅N、副走査幅Mの画像データを取得して、前記フィルターを用いてフィルタリングを行うフィルター演算部と、

前記レジスター部の画像データのシフト方向を制御する制御部と、を備える、ことを特徴としていてもよい。

【0010】

また、上記の画像処理装置であって、前記メモリーは、前記ブロック画像データから取得した少なくとも主走査幅N+1、副走査幅2Mの画像データを格納し、前記レジスター部は、副走査方向、副走査の逆方向、及び主走査の逆方向のシフトが可能であり、各方向のシフトの際に、主走査幅N、副走査幅Mの画像データを出力し、副走査方向及び副走査の逆方向のシフトの際には、前記メモリーから画像データを取得して格納し、前記制御部は、画素データ列ごとに、副走査方向のシフトとその逆方向のシフトを交互に前記レジスターに指示し、ある画素データ列の処理が終わった場合には主走査の逆方向のシフトを前記レジスターに指示する、ことを特徴としていてもよい。

【0011】

上記の課題を解決するための本発明の第二の態様は、原画像データの所定の領域であるブロック画像データについて、主走査幅N、副走査幅Mのフィルターを用いてフィルタリングを行う画像処理回路であって、前記ブロック画像データを構成する副走査方向の画素データ列それぞれを、副走査方向とその逆方向を交互に処理し、また、主走査方向の列の順に処理する、ことを特徴とする。

【0012】

上記の課題を解決するための本発明の第三の態様は、原画像データの所定の領域であるブロック画像データについて、主走査幅N、副走査幅Mのフィルターを用いてフィルタリングを行う画像処理方法であって、前記ブロック画像データを構成する副走査方向の画素データ列それぞれを、副走査方向とその逆方向を交互に処理し、また、主走査方向の列の順に処理する、ことを特徴とする。

【図面の簡単な説明】

【0013】

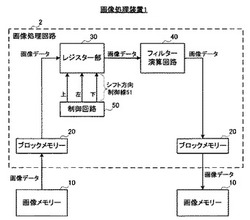

【図1】本発明の一実施形態の一例に係る画像処理装置1の概略構成を示すブロック図。

【図2】ブロック画像の画素データの処理順序を説明する図。

【図3】レジスター部30の構成の一例を示す図。

【図4】レジスター部30に画素データを格納する手順を説明する図。

【図5】レジスター部30に画素データを格納する手順を説明するフロー図。

【発明を実施するための形態】

【0014】

以下、本発明の一実施形態について図面を参照して説明する。

【0015】

図1は、本発明の一実施形態の一例に係る画像処理装置1の概略構成を示すブロック図である。本実施形態では、モノクロ画像の処理について説明する。

【0016】

画像処理装置1は、ブロック単位でフィルタリング処理を行う機能を有する装置である。画像処理装置1は、例えば、プリンター、スキャナー、コピー機、複合機などの画像処理装置である。本図では、フィルタリング処理に関する構成を中心に示している。従って、フィルタリング処理に関連が低い構成要素は省略されている。

【0017】

画像処理装置1は、画像メモリー10、ブロックメモリー20、レジスター部30、フィルター演算回路40、制御回路50を有する。ブロックメモリー20、レジスター部30、フィルター演算回路40、及び制御回路50は、例えば、画像処理ASIC(Application Specific Integrated Circuit)等の画像処理回路2として構成される。

【0018】

画像メモリー10は、画像データを格納するための大容量の記憶装置であり、例えば、DDR−SDRAM(Double Data Rate SDRAM)である。画像メモリー10は、例えば、フィルタリング処理前後それぞれ1ページの画像データを格納することができる。

【0019】

ブロックメモリー20は、画像メモリー10に格納された画像データをブロック単位で切り出した画像データの少なくとも一部を格納するための記憶装置であり、例えば、SRAM(Static RAM)、デュアルポートRAMにより構成することができる。ブロックメモリー20は、フィルタリング処理前後それぞれの画像データを格納することができる。

【0020】

画像メモリー10からブロックメモリー20への画像データの入力と、ブロックメモリー20からレジスター部30へ画像データの出力とは、並列的に実行することができる。従って、ブロックメモリー20は、ブロック画像の一部の画像データを順次格納できればよい。ブロックメモリー20の容量は、例えば、フィルター演算回路40で使用されるマトリックスが主走査幅N、副走査幅Mである場合に、少なくとも主走査幅N+1、副走査幅2Mとすることができる。

【0021】

なお、ブロック画像は、例えば、画像処理装置1のCPU(不図示)やDMA(不図示)の制御により、画像メモリー10からブロックメモリー20に格納され、またブロックメモリー20から画像メモリー10に格納される。

【0022】

レジスター部30は、制御回路50の制御の下、ある注目画素のフィルタリング処理に必要な画素データをフィルター演算回路40に出力するとともに、次の注目画素のフィルタリング処理に必要な画素データを格納する。詳細は後述するが、レジスター部30は、シフトレジスターにより構成される。レジスター部30の容量は、例えば、フィルター演算回路40で使用されるマトリックスが主走査幅N、副走査幅Mである場合に、主走査幅N+1、副走査幅Mとすることができる。

【0023】

フィルター演算回路40は、レジスター部30から出力された注目画素を含む画素データに対してフィルタリング処理を行い、注目画素に対するフィルター演算結果を、ブロックメモリー20に出力する。使用するマトリックスは、例えば、主走査幅N、副走査幅Mとすることができる。

【0024】

制御回路50は、レジスター部30の画素データの入出力を制御する。制御回路50は、例えば、画素データのシフト方向を指示する信号を、後述する所定の手順に従ってレジスター部30に出力する。そのため、制御回路50とレジスター部30は、上方向へのシフト(副走査方向の逆方向へのシフト)、左方向へのシフト(主走査方向の逆方向のシフト)、及び下方向へのシフト(副走査方向へのシフト)を指示する信号を送るためのシフト方向制御線51で接続されている。

【0025】

さて、上記のように構成される本実施形態の画像処理装置1は、図2(A)に示すような順序で、ブロック画像に含まれる各画素のフィルタリング処理を実行する。具体的には、副走査方向の画素データの列ごとに、順次、副走査方向及び副走査方向の逆方向の交互に処理される。すなわち、各列の処理が終了した場合には、処理が終了した列の主走査方向に隣接する列について、処理が終了した列の処理方向(副走査方向又は副走査方向の逆方向)の逆方向に処理される。

【0026】

上述の処理手順を実現するため、レジスター部30は、図3に示すような構成を有する。図3は、レジスター部30の構成の一例を示す図である。

【0027】

なお、以下の説明では、フィルターのマトリックスが主走査幅N=3、副走査幅M=3であるものとする。

【0028】

レジスター部30は、主走査幅4(主走査位置0〜3)、副走査幅3(副走査位置0〜2)のシフトレジスターにより構成される。シフトレジスターを構成する各レジスター31(主走査位置0〜3、副走査位置0〜2)は、上シフト、左シフト、下シフトができるようになっている。

【0029】

レジスター31(0〜3、0)には、下シフトにより、ブロックメモリー20からロードされた画素データが格納される。レジスター31(0〜3、2)には、上シフトにより、ブロックメモリー20からロードされた画素データが格納される。また、レジスター31(0〜2、0〜2)の画素データは、フィルター演算回路40に出力される。

【0030】

なお、上述したように、レジスター部30の大きさは、フィルターのマトリックスの大きさに対応しており、フィルターのマトリックスが主走査幅N、副走査幅Mである場合、レジスター部30は、主走査幅N+1、副走査幅Mとなる。

【0031】

図4は、レジスター部30に画素データを格納する制御手順を説明する図である。本図は、ブロック画像の処理対象(斜線部分:画素データ列(1、1〜4)、(2、1〜4)、(3、1〜4))についてフィルタリング処理が実行される場合を示している。

【0032】

状態1:レジスター部30は空である。

状態2:上シフトにより、ブロックメモリー20からレジスター部30に画素データ(0〜3、0)がロードされる。

状態3:上シフトにより、レジスター部30に画素データ(0〜3、1)がロードされる。

状態4:上シフトにより、レジスター部30に画素データ(0〜3、2)がロードされる。

状態5:上シフトのタイミングで、レジスター部30から画素データ(0〜2、0〜2)がフィルター演算回路40に出力され、注目画素(1、1)についてのフィルタリングが行われる。また、上シフトにより、レジスター部30に画素データ(0〜3、3)がロードされる。

状態6:上シフトのタイミングで、レジスター部30から画素データ(0〜2、1〜3)がフィルター演算回路40に出力され、注目画素(1、2)についてのフィルタリングが行われる。また、上シフトにより、レジスター部30に画素データ(0〜3、4)がロードされる。

状態7:上シフトのタイミングで、レジスター部30から画素データ(0〜2、2〜4)がフィルター演算回路40に出力され、注目画素(1、3)についてのフィルタリングが行われる。また、上シフトにより、レジスター部30に画素データ(0〜3、5)がロードされる。

状態8:左シフトのタイミングで、レジスター部30から画素データ(0〜2、3〜5)がフィルター演算回路40に出力され、注目画素(1、4)についてのフィルタリングが行われる。また、左シフトにより、レジスター部30のレジスター31(3、0〜2)は空になる。

状態9:下シフトのタイミングで、レジスター部30から画素データ(1〜3、3〜5)がフィルター演算回路40に出力され、注目画素(2、4)についてのフィルタリングが行われる。また、下シフトにより、レジスター部30に画素データ(1〜4、2)がロードされる。

状態10:下シフトのタイミングで、レジスター部30から画素データ(1〜3、2〜4)がフィルター演算回路40に出力され、注目画素(2、3)についてのフィルタリングが行われる。また、下シフトにより、レジスター部30に画素データ(1〜4、1)がロードされる。

状態11:下シフトのタイミングで、レジスター部30から画素データ(1〜3、1〜3)がフィルター演算回路40に出力され、注目画素(2、2)についてのフィルタリングが行われる。また、下シフトにより、レジスター部30に画素データ(1〜4、0)がロードされる。

状態12:左シフトのタイミングで、レジスター部30から画素データ(1〜3、0〜2)がフィルター演算回路40に出力され、注目画素(2、1)についてのフィルタリングが行われる。また、左シフトにより、レジスター部30のレジスター31(3、0〜2)は空になる。

状態13:上シフトのタイミングで、レジスター部30から画素データ(2〜4、0〜2)がフィルター演算回路40に出力され、注目画素(3、1)についてのフィルタリングが行われる。また、上シフトにより、レジスター部30に画素データ(2〜5、3)がロードされる。

状態14:上シフトのタイミングで、レジスター部30から画素データ(2〜4、1〜3)がフィルター演算回路40に出力され、注目画素(3、2)についてのフィルタリングが行われる。また、上シフトにより、レジスター部30に画素データ(2〜5、4)がロードされる。

状態15:上シフトのタイミングで、レジスター部30から画素データ(2〜4、2〜4)がフィルター演算回路40に出力され、注目画素(3、3)についてのフィルタリングが行われる。また、上シフトにより、レジスター部30に画素データ(2〜5、5)がロードされる。

【0033】

上記の画像処理装置1及び画像処理回路2の構成は、本願発明の特徴を説明するにあたって主要構成を説明したのであって、上記の構成に限られない。また、一般的な画像処理装置及び画像処理回路が備える他の構成を排除するものではない。また、上記した各構成要素は、画像処理装置1及び画像処理回路2の構成を理解容易にするために、主な処理内容に応じて分類したものである。構成要素の分類の仕方や名称によって、本願発明が制限されることはない。画像処理装置1及び画像処理回路2の構成は、処理内容に応じて、さらに多くの構成要素に分類することもできる。また、1つの構成要素がさらに多くの処理を実行するように分類することもできる。また、各構成要素の処理は、1つのハードウェアで実行されてもよいし、複数のハードウェアで実行されてもよい。

【0034】

図5は、レジスター部30に画像データを格納する制御手順を説明するフロー図である。本フローは、例えば、1ブロックの画像データに対するフィルタリング処理を開始する指示があった場合に開始される。

【0035】

S10では、レジスター部30にフィルタリング演算対象の画素が格納される。具体的には、制御回路50は、上又は下シフト信号を3回出力し、最初の注目画素を処理するために使用される画素データでレジスター部30を満たす。例えば、図4のように、主走査位置が1の列から下方向にフィルタリング処理が開始される場合、制御回路50は、上シフト信号により、レジスター部30を状態4にする。そして、制御回路50は、処理をS20に進める。

【0036】

S20では、制御回路50は、注目画素の主走査位置が奇数であるか偶数であるかを判定する。具体的には、ブロック画像における注目画素の主走査方向の位置が奇数(1、3、5・・・)であるか偶数(0、2、4・・・)であるかを判定する。例えば、図4のブロック画像の例では、画素データ(1、1)及び(3、1)の主走査位置は奇数、画素データ(2、1)の主走査位置は偶数となる。注目画素の主走査位置が奇数である場合(S20:奇数)、処理をS30に進める。注目画素の主走査位置が偶数である場合(S20:偶数)、処理をS60に進める。

【0037】

S30では、制御回路50は、注目画素の副走査位置(ライン位置)が下端であるか否かを判定する。具体的には、注目画素が、当該画素データ列の注目画素として処理される画素データのうち一番下の画素であるか否かを判定する。例えば、図4のブロック画像の例では、画素データ(1、4)が下端の画素に当たる。注目画素の副走査位置が下端である場合(S30:YES)、処理をS50に進める。注目画素の副走査位置が下端でない場合(S30:NO)、処理をS40に進める。

【0038】

S40では、制御回路50は、上シフト信号を出力する。この上シフト信号を契機に、現在レジスター部30に格納されている下端の画素データ行(主走査方向)の副走査方向に隣接する次の画素データ行が、ブロックメモリー20からレジスター部30にロードされる。また、同時に、現在レジスター部30に格納されている各画素データ行が上方向にシフトされるとともに、レジスター31(0〜2、0〜2)に格納されていた画素データがフィルター演算回路40に出力される。このとき、ロードされた画素データ行がレジスター部30の下の行に格納される。また、同時に、レジスター部30から出力された画素データを用いて、フィルター演算回路40により注目画素のフィルター演算が実行される。それから、制御回路50は、処理をS90に進める。

【0039】

S50では、制御回路50は、左シフト信号を出力する。この左シフト信号を契機に、現在レジスター部30に格納されている各画素データ列が左方向にシフトされるとともに、レジスター31(0〜2、0〜2)に格納されていた画素データがフィルター演算回路40に出力される。このとき、レジスター部30の右端の列は空となる。また、同時に、レジスター部30から出力された画素データを用いて、フィルター演算回路40により注目画素のフィルター演算が実行される。それから、制御回路50は、処理をS90に進める。

【0040】

S60では、制御回路50は、注目画素の副走査位置(ライン位置)が上端であるか否かを判定する。具体的には、注目画素が、当該画素データ列の注目画素として処理される画素データのうち一番上の画素であるか否かを判定する。例えば、図4のブロック画像の例では、画素データ(2、1)が上端の画素に当たる。注目画素の副走査位置が上端である場合(S60:YES)、処理をS80に進める。注目画素の副走査位置が上端でない場合(S60:NO)、処理をS70に進める。

【0041】

S70では、制御回路50は、下シフト信号を出力する。この下シフト信号を契機に、現在レジスター部30に格納されている上端の画素データ行(主走査方向)の副走査逆方向に隣接する次の画素データ行が、ブロックメモリー20からレジスター部30にロードされる。また、同時に、現在レジスター部30に格納されている各画素データ行が下方向にシフトされるとともに、レジスター31(0〜2、0〜2)に格納されていた画素データがフィルター演算回路40に出力される。このとき、ロードされた画素データ行がレジスター部30の上の行に格納される。また、同時に、レジスター部30から出力された画素データを用いて、フィルター演算回路40により注目画素のフィルター演算が実行される。それから、制御回路50は、処理をS90に進める。

【0042】

S80では、制御回路50は、左シフト信号を出力する。この処理は、S50と同様である。

【0043】

S90では、制御回路50は、注目画素がブロック画像データ内の最終画素であるか否かを判定する。具体的には、制御回路50は、S40、S50、S70、又はS80でフィルタリング処理された注目画素が、ブロック画像データ内のフィルタリング演算対象の最後の画素データであるか否かを判定する。注目画素が最終画素でない場合(S90:NO)、制御回路50は、処理をS20に戻す。注目画素が最終画素である場合(S90:YES)、制御回路50は、本フローを終了する。

【0044】

なお、本フローが終了した場合、次のブロック画像がある場合は当該ブロック画像について本フローの処理が開始される。

【0045】

以上の図4及び図5の各処理単位は、画像処理装置1及び画像処理回路2の処理を理解容易にするために、主な処理内容に応じて分割したものである。処理単位の分割の仕方や名称によって、本願発明が制限されることはない。画像処理装置1及び画像処理回路2の処理は、処理内容に応じて、さらに多くの処理単位に分割することもできる。また、1つの処理単位がさらに多くの処理を含むように分割することもできる。

【0046】

なお、上記の実施形態では、ブロック画像の奇数列について副走査方向に処理(上シフト(副走査方向の逆方向)により処理)し、偶数列について副走査方向の逆方向に処理(下シフト(副走査方向)により処理)しているが、逆であってもよい。

【0047】

以上、本発明の一実施形態について説明した。本実施形態によれば、ブロック単位で処理を行う画像処理装置において、フィルタリング処理時間をより短くすることができる。

【0048】

すなわち、本実施形態によれば、フィルタリングに使用された、画素データ列の先頭又は後尾の画素データを、レジスター部30に格納したまま、次の画素データ列の先頭又は後尾のフィルタリングに再利用される。このような構成により、各画素データ列のフィルタリング処理を開始するために、画素データを全て入れ替える必要がなくなり、フィルタリング処理時間が短縮される。

【0049】

以上の本発明の実施形態は、本発明の要旨と範囲を例示することを意図し、限定するものではない。多くの代替物、修正および変形例が当業者にとって明らかである。

【0050】

例えば、本発明は、カラー画像の処理にも適用できる。具体的には、画像メモリー及びブロックメモリーにRGB3色の画像データを格納できるようにする。また、レジスター部及びフィルター演算回路をRGB各色について設ける。制御回路は、RGB各色のレジスター部を制御する。もちろん、フィルター演算部を1つとし、RGB各色で共用するようにしてもよい。

【符号の説明】

【0051】

1:画像処理装置、2:画像処理回路、10:画像メモリー、20:ブロックメモリー、30:レジスター部、31:レジスター、40:フィルター演算回路、50:制御回路、51:シフト方向制御線

【技術分野】

【0001】

本発明は、ブロック単位で画像データを処理する画像処理技術に関する。

【背景技術】

【0002】

プリンター、スキャナー、コピー機、複合機等の画像処理装置において、例えば、1ページ分の画像データ(主走査幅W、副走査幅H)について、ブロック(主走査幅W、副走査幅L(L:L<H))単位で処理対象の画像データを切り出し、所定の画像処理(例えば、フィルタリング処理等)を行う技術が知られている(例えば、特許文献1)。

【0003】

各ブロックの画像データは、副走査方向の画素データの列(主走査幅1、副走査幅L)ごとに、副走査方向に順次処理される。各画素データ列の処理が終了した場合には、当該列の主走査方向に隣接する画素データ列が次に処理される。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2001−251502号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

特許文献1では、RAMに格納された原画像データから切り出されたブロック画像に含まれる画素データのうち、フィルタリング処理の対象となる画素データが一旦レジスターに格納される。また、当該レジスターから出力される画素データを用いてフィルタリング処理が行われる。

【0006】

しかしながら、特許文献1では、ある画素データ列の副走査方向のフィルタリング処理が終了し、次の画素データ列のフィルタリング処理が開始される場合、当該画素データ列の先頭部分の画素データをレジスターに格納する必要がある。すなわち、フィルタリング処理が終了したときにレジスターに格納されている画素データ(フィルタリング処理が終了した画素データ列の後尾部分の画素データ)は、削除する必要がある。そのため、各画素データ列のフィルタリング処理を開始するために、画素データを入れ替える必要があり、処理時間が増加する。

【0007】

そこで、本発明は、ブロック単位で処理を行う画像処理装置において、フィルタリング処理時間をより短くすることを目的とする。

【課題を解決するための手段】

【0008】

上記の課題を解決するための本発明の第一の態様は、原画像データの所定の領域であるブロック画像データについて、主走査幅N、副走査幅Mのフィルターを用いてフィルタリングを行う画像処理装置であって、前記ブロック画像データを構成する副走査方向の画素データ列それぞれを、副走査方向とその逆方向を交互に処理し、また、主走査方向の列の順に処理する、ことを特徴とする。

【0009】

ここで、上記の画像処理装置であって、前記ブロック画像データの少なくとも一部を格納するメモリーと、主走査幅N+1、副走査幅Mの容量であって、格納される画像データを複数の方向にシフト可能なシフトレジスターで構成され、前記メモリーから主走査幅N+1、副走査幅1の画像データを順次取得して格納し、主走査幅N、副走査幅Mの画像データを出力するレジスター部と、前記レジスター部から主走査幅N、副走査幅Mの画像データを取得して、前記フィルターを用いてフィルタリングを行うフィルター演算部と、

前記レジスター部の画像データのシフト方向を制御する制御部と、を備える、ことを特徴としていてもよい。

【0010】

また、上記の画像処理装置であって、前記メモリーは、前記ブロック画像データから取得した少なくとも主走査幅N+1、副走査幅2Mの画像データを格納し、前記レジスター部は、副走査方向、副走査の逆方向、及び主走査の逆方向のシフトが可能であり、各方向のシフトの際に、主走査幅N、副走査幅Mの画像データを出力し、副走査方向及び副走査の逆方向のシフトの際には、前記メモリーから画像データを取得して格納し、前記制御部は、画素データ列ごとに、副走査方向のシフトとその逆方向のシフトを交互に前記レジスターに指示し、ある画素データ列の処理が終わった場合には主走査の逆方向のシフトを前記レジスターに指示する、ことを特徴としていてもよい。

【0011】

上記の課題を解決するための本発明の第二の態様は、原画像データの所定の領域であるブロック画像データについて、主走査幅N、副走査幅Mのフィルターを用いてフィルタリングを行う画像処理回路であって、前記ブロック画像データを構成する副走査方向の画素データ列それぞれを、副走査方向とその逆方向を交互に処理し、また、主走査方向の列の順に処理する、ことを特徴とする。

【0012】

上記の課題を解決するための本発明の第三の態様は、原画像データの所定の領域であるブロック画像データについて、主走査幅N、副走査幅Mのフィルターを用いてフィルタリングを行う画像処理方法であって、前記ブロック画像データを構成する副走査方向の画素データ列それぞれを、副走査方向とその逆方向を交互に処理し、また、主走査方向の列の順に処理する、ことを特徴とする。

【図面の簡単な説明】

【0013】

【図1】本発明の一実施形態の一例に係る画像処理装置1の概略構成を示すブロック図。

【図2】ブロック画像の画素データの処理順序を説明する図。

【図3】レジスター部30の構成の一例を示す図。

【図4】レジスター部30に画素データを格納する手順を説明する図。

【図5】レジスター部30に画素データを格納する手順を説明するフロー図。

【発明を実施するための形態】

【0014】

以下、本発明の一実施形態について図面を参照して説明する。

【0015】

図1は、本発明の一実施形態の一例に係る画像処理装置1の概略構成を示すブロック図である。本実施形態では、モノクロ画像の処理について説明する。

【0016】

画像処理装置1は、ブロック単位でフィルタリング処理を行う機能を有する装置である。画像処理装置1は、例えば、プリンター、スキャナー、コピー機、複合機などの画像処理装置である。本図では、フィルタリング処理に関する構成を中心に示している。従って、フィルタリング処理に関連が低い構成要素は省略されている。

【0017】

画像処理装置1は、画像メモリー10、ブロックメモリー20、レジスター部30、フィルター演算回路40、制御回路50を有する。ブロックメモリー20、レジスター部30、フィルター演算回路40、及び制御回路50は、例えば、画像処理ASIC(Application Specific Integrated Circuit)等の画像処理回路2として構成される。

【0018】

画像メモリー10は、画像データを格納するための大容量の記憶装置であり、例えば、DDR−SDRAM(Double Data Rate SDRAM)である。画像メモリー10は、例えば、フィルタリング処理前後それぞれ1ページの画像データを格納することができる。

【0019】

ブロックメモリー20は、画像メモリー10に格納された画像データをブロック単位で切り出した画像データの少なくとも一部を格納するための記憶装置であり、例えば、SRAM(Static RAM)、デュアルポートRAMにより構成することができる。ブロックメモリー20は、フィルタリング処理前後それぞれの画像データを格納することができる。

【0020】

画像メモリー10からブロックメモリー20への画像データの入力と、ブロックメモリー20からレジスター部30へ画像データの出力とは、並列的に実行することができる。従って、ブロックメモリー20は、ブロック画像の一部の画像データを順次格納できればよい。ブロックメモリー20の容量は、例えば、フィルター演算回路40で使用されるマトリックスが主走査幅N、副走査幅Mである場合に、少なくとも主走査幅N+1、副走査幅2Mとすることができる。

【0021】

なお、ブロック画像は、例えば、画像処理装置1のCPU(不図示)やDMA(不図示)の制御により、画像メモリー10からブロックメモリー20に格納され、またブロックメモリー20から画像メモリー10に格納される。

【0022】

レジスター部30は、制御回路50の制御の下、ある注目画素のフィルタリング処理に必要な画素データをフィルター演算回路40に出力するとともに、次の注目画素のフィルタリング処理に必要な画素データを格納する。詳細は後述するが、レジスター部30は、シフトレジスターにより構成される。レジスター部30の容量は、例えば、フィルター演算回路40で使用されるマトリックスが主走査幅N、副走査幅Mである場合に、主走査幅N+1、副走査幅Mとすることができる。

【0023】

フィルター演算回路40は、レジスター部30から出力された注目画素を含む画素データに対してフィルタリング処理を行い、注目画素に対するフィルター演算結果を、ブロックメモリー20に出力する。使用するマトリックスは、例えば、主走査幅N、副走査幅Mとすることができる。

【0024】

制御回路50は、レジスター部30の画素データの入出力を制御する。制御回路50は、例えば、画素データのシフト方向を指示する信号を、後述する所定の手順に従ってレジスター部30に出力する。そのため、制御回路50とレジスター部30は、上方向へのシフト(副走査方向の逆方向へのシフト)、左方向へのシフト(主走査方向の逆方向のシフト)、及び下方向へのシフト(副走査方向へのシフト)を指示する信号を送るためのシフト方向制御線51で接続されている。

【0025】

さて、上記のように構成される本実施形態の画像処理装置1は、図2(A)に示すような順序で、ブロック画像に含まれる各画素のフィルタリング処理を実行する。具体的には、副走査方向の画素データの列ごとに、順次、副走査方向及び副走査方向の逆方向の交互に処理される。すなわち、各列の処理が終了した場合には、処理が終了した列の主走査方向に隣接する列について、処理が終了した列の処理方向(副走査方向又は副走査方向の逆方向)の逆方向に処理される。

【0026】

上述の処理手順を実現するため、レジスター部30は、図3に示すような構成を有する。図3は、レジスター部30の構成の一例を示す図である。

【0027】

なお、以下の説明では、フィルターのマトリックスが主走査幅N=3、副走査幅M=3であるものとする。

【0028】

レジスター部30は、主走査幅4(主走査位置0〜3)、副走査幅3(副走査位置0〜2)のシフトレジスターにより構成される。シフトレジスターを構成する各レジスター31(主走査位置0〜3、副走査位置0〜2)は、上シフト、左シフト、下シフトができるようになっている。

【0029】

レジスター31(0〜3、0)には、下シフトにより、ブロックメモリー20からロードされた画素データが格納される。レジスター31(0〜3、2)には、上シフトにより、ブロックメモリー20からロードされた画素データが格納される。また、レジスター31(0〜2、0〜2)の画素データは、フィルター演算回路40に出力される。

【0030】

なお、上述したように、レジスター部30の大きさは、フィルターのマトリックスの大きさに対応しており、フィルターのマトリックスが主走査幅N、副走査幅Mである場合、レジスター部30は、主走査幅N+1、副走査幅Mとなる。

【0031】

図4は、レジスター部30に画素データを格納する制御手順を説明する図である。本図は、ブロック画像の処理対象(斜線部分:画素データ列(1、1〜4)、(2、1〜4)、(3、1〜4))についてフィルタリング処理が実行される場合を示している。

【0032】

状態1:レジスター部30は空である。

状態2:上シフトにより、ブロックメモリー20からレジスター部30に画素データ(0〜3、0)がロードされる。

状態3:上シフトにより、レジスター部30に画素データ(0〜3、1)がロードされる。

状態4:上シフトにより、レジスター部30に画素データ(0〜3、2)がロードされる。

状態5:上シフトのタイミングで、レジスター部30から画素データ(0〜2、0〜2)がフィルター演算回路40に出力され、注目画素(1、1)についてのフィルタリングが行われる。また、上シフトにより、レジスター部30に画素データ(0〜3、3)がロードされる。

状態6:上シフトのタイミングで、レジスター部30から画素データ(0〜2、1〜3)がフィルター演算回路40に出力され、注目画素(1、2)についてのフィルタリングが行われる。また、上シフトにより、レジスター部30に画素データ(0〜3、4)がロードされる。

状態7:上シフトのタイミングで、レジスター部30から画素データ(0〜2、2〜4)がフィルター演算回路40に出力され、注目画素(1、3)についてのフィルタリングが行われる。また、上シフトにより、レジスター部30に画素データ(0〜3、5)がロードされる。

状態8:左シフトのタイミングで、レジスター部30から画素データ(0〜2、3〜5)がフィルター演算回路40に出力され、注目画素(1、4)についてのフィルタリングが行われる。また、左シフトにより、レジスター部30のレジスター31(3、0〜2)は空になる。

状態9:下シフトのタイミングで、レジスター部30から画素データ(1〜3、3〜5)がフィルター演算回路40に出力され、注目画素(2、4)についてのフィルタリングが行われる。また、下シフトにより、レジスター部30に画素データ(1〜4、2)がロードされる。

状態10:下シフトのタイミングで、レジスター部30から画素データ(1〜3、2〜4)がフィルター演算回路40に出力され、注目画素(2、3)についてのフィルタリングが行われる。また、下シフトにより、レジスター部30に画素データ(1〜4、1)がロードされる。

状態11:下シフトのタイミングで、レジスター部30から画素データ(1〜3、1〜3)がフィルター演算回路40に出力され、注目画素(2、2)についてのフィルタリングが行われる。また、下シフトにより、レジスター部30に画素データ(1〜4、0)がロードされる。

状態12:左シフトのタイミングで、レジスター部30から画素データ(1〜3、0〜2)がフィルター演算回路40に出力され、注目画素(2、1)についてのフィルタリングが行われる。また、左シフトにより、レジスター部30のレジスター31(3、0〜2)は空になる。

状態13:上シフトのタイミングで、レジスター部30から画素データ(2〜4、0〜2)がフィルター演算回路40に出力され、注目画素(3、1)についてのフィルタリングが行われる。また、上シフトにより、レジスター部30に画素データ(2〜5、3)がロードされる。

状態14:上シフトのタイミングで、レジスター部30から画素データ(2〜4、1〜3)がフィルター演算回路40に出力され、注目画素(3、2)についてのフィルタリングが行われる。また、上シフトにより、レジスター部30に画素データ(2〜5、4)がロードされる。

状態15:上シフトのタイミングで、レジスター部30から画素データ(2〜4、2〜4)がフィルター演算回路40に出力され、注目画素(3、3)についてのフィルタリングが行われる。また、上シフトにより、レジスター部30に画素データ(2〜5、5)がロードされる。

【0033】

上記の画像処理装置1及び画像処理回路2の構成は、本願発明の特徴を説明するにあたって主要構成を説明したのであって、上記の構成に限られない。また、一般的な画像処理装置及び画像処理回路が備える他の構成を排除するものではない。また、上記した各構成要素は、画像処理装置1及び画像処理回路2の構成を理解容易にするために、主な処理内容に応じて分類したものである。構成要素の分類の仕方や名称によって、本願発明が制限されることはない。画像処理装置1及び画像処理回路2の構成は、処理内容に応じて、さらに多くの構成要素に分類することもできる。また、1つの構成要素がさらに多くの処理を実行するように分類することもできる。また、各構成要素の処理は、1つのハードウェアで実行されてもよいし、複数のハードウェアで実行されてもよい。

【0034】

図5は、レジスター部30に画像データを格納する制御手順を説明するフロー図である。本フローは、例えば、1ブロックの画像データに対するフィルタリング処理を開始する指示があった場合に開始される。

【0035】

S10では、レジスター部30にフィルタリング演算対象の画素が格納される。具体的には、制御回路50は、上又は下シフト信号を3回出力し、最初の注目画素を処理するために使用される画素データでレジスター部30を満たす。例えば、図4のように、主走査位置が1の列から下方向にフィルタリング処理が開始される場合、制御回路50は、上シフト信号により、レジスター部30を状態4にする。そして、制御回路50は、処理をS20に進める。

【0036】

S20では、制御回路50は、注目画素の主走査位置が奇数であるか偶数であるかを判定する。具体的には、ブロック画像における注目画素の主走査方向の位置が奇数(1、3、5・・・)であるか偶数(0、2、4・・・)であるかを判定する。例えば、図4のブロック画像の例では、画素データ(1、1)及び(3、1)の主走査位置は奇数、画素データ(2、1)の主走査位置は偶数となる。注目画素の主走査位置が奇数である場合(S20:奇数)、処理をS30に進める。注目画素の主走査位置が偶数である場合(S20:偶数)、処理をS60に進める。

【0037】

S30では、制御回路50は、注目画素の副走査位置(ライン位置)が下端であるか否かを判定する。具体的には、注目画素が、当該画素データ列の注目画素として処理される画素データのうち一番下の画素であるか否かを判定する。例えば、図4のブロック画像の例では、画素データ(1、4)が下端の画素に当たる。注目画素の副走査位置が下端である場合(S30:YES)、処理をS50に進める。注目画素の副走査位置が下端でない場合(S30:NO)、処理をS40に進める。

【0038】

S40では、制御回路50は、上シフト信号を出力する。この上シフト信号を契機に、現在レジスター部30に格納されている下端の画素データ行(主走査方向)の副走査方向に隣接する次の画素データ行が、ブロックメモリー20からレジスター部30にロードされる。また、同時に、現在レジスター部30に格納されている各画素データ行が上方向にシフトされるとともに、レジスター31(0〜2、0〜2)に格納されていた画素データがフィルター演算回路40に出力される。このとき、ロードされた画素データ行がレジスター部30の下の行に格納される。また、同時に、レジスター部30から出力された画素データを用いて、フィルター演算回路40により注目画素のフィルター演算が実行される。それから、制御回路50は、処理をS90に進める。

【0039】

S50では、制御回路50は、左シフト信号を出力する。この左シフト信号を契機に、現在レジスター部30に格納されている各画素データ列が左方向にシフトされるとともに、レジスター31(0〜2、0〜2)に格納されていた画素データがフィルター演算回路40に出力される。このとき、レジスター部30の右端の列は空となる。また、同時に、レジスター部30から出力された画素データを用いて、フィルター演算回路40により注目画素のフィルター演算が実行される。それから、制御回路50は、処理をS90に進める。

【0040】

S60では、制御回路50は、注目画素の副走査位置(ライン位置)が上端であるか否かを判定する。具体的には、注目画素が、当該画素データ列の注目画素として処理される画素データのうち一番上の画素であるか否かを判定する。例えば、図4のブロック画像の例では、画素データ(2、1)が上端の画素に当たる。注目画素の副走査位置が上端である場合(S60:YES)、処理をS80に進める。注目画素の副走査位置が上端でない場合(S60:NO)、処理をS70に進める。

【0041】

S70では、制御回路50は、下シフト信号を出力する。この下シフト信号を契機に、現在レジスター部30に格納されている上端の画素データ行(主走査方向)の副走査逆方向に隣接する次の画素データ行が、ブロックメモリー20からレジスター部30にロードされる。また、同時に、現在レジスター部30に格納されている各画素データ行が下方向にシフトされるとともに、レジスター31(0〜2、0〜2)に格納されていた画素データがフィルター演算回路40に出力される。このとき、ロードされた画素データ行がレジスター部30の上の行に格納される。また、同時に、レジスター部30から出力された画素データを用いて、フィルター演算回路40により注目画素のフィルター演算が実行される。それから、制御回路50は、処理をS90に進める。

【0042】

S80では、制御回路50は、左シフト信号を出力する。この処理は、S50と同様である。

【0043】

S90では、制御回路50は、注目画素がブロック画像データ内の最終画素であるか否かを判定する。具体的には、制御回路50は、S40、S50、S70、又はS80でフィルタリング処理された注目画素が、ブロック画像データ内のフィルタリング演算対象の最後の画素データであるか否かを判定する。注目画素が最終画素でない場合(S90:NO)、制御回路50は、処理をS20に戻す。注目画素が最終画素である場合(S90:YES)、制御回路50は、本フローを終了する。

【0044】

なお、本フローが終了した場合、次のブロック画像がある場合は当該ブロック画像について本フローの処理が開始される。

【0045】

以上の図4及び図5の各処理単位は、画像処理装置1及び画像処理回路2の処理を理解容易にするために、主な処理内容に応じて分割したものである。処理単位の分割の仕方や名称によって、本願発明が制限されることはない。画像処理装置1及び画像処理回路2の処理は、処理内容に応じて、さらに多くの処理単位に分割することもできる。また、1つの処理単位がさらに多くの処理を含むように分割することもできる。

【0046】

なお、上記の実施形態では、ブロック画像の奇数列について副走査方向に処理(上シフト(副走査方向の逆方向)により処理)し、偶数列について副走査方向の逆方向に処理(下シフト(副走査方向)により処理)しているが、逆であってもよい。

【0047】

以上、本発明の一実施形態について説明した。本実施形態によれば、ブロック単位で処理を行う画像処理装置において、フィルタリング処理時間をより短くすることができる。

【0048】

すなわち、本実施形態によれば、フィルタリングに使用された、画素データ列の先頭又は後尾の画素データを、レジスター部30に格納したまま、次の画素データ列の先頭又は後尾のフィルタリングに再利用される。このような構成により、各画素データ列のフィルタリング処理を開始するために、画素データを全て入れ替える必要がなくなり、フィルタリング処理時間が短縮される。

【0049】

以上の本発明の実施形態は、本発明の要旨と範囲を例示することを意図し、限定するものではない。多くの代替物、修正および変形例が当業者にとって明らかである。

【0050】

例えば、本発明は、カラー画像の処理にも適用できる。具体的には、画像メモリー及びブロックメモリーにRGB3色の画像データを格納できるようにする。また、レジスター部及びフィルター演算回路をRGB各色について設ける。制御回路は、RGB各色のレジスター部を制御する。もちろん、フィルター演算部を1つとし、RGB各色で共用するようにしてもよい。

【符号の説明】

【0051】

1:画像処理装置、2:画像処理回路、10:画像メモリー、20:ブロックメモリー、30:レジスター部、31:レジスター、40:フィルター演算回路、50:制御回路、51:シフト方向制御線

【特許請求の範囲】

【請求項1】

原画像データの所定の領域であるブロック画像データについて、主走査幅N、副走査幅Mのフィルターを用いてフィルタリングを行う画像処理装置であって、

前記ブロック画像データを構成する副走査方向の画素データ列それぞれを、副走査方向とその逆方向を交互に処理し、また、主走査方向の列の順に処理する、

ことを特徴とする画像処理装置。

【請求項2】

請求項1に記載の画像処理装置であって、

前記ブロック画像データの少なくとも一部を格納するメモリーと、

主走査幅N+1、副走査幅Mの容量であって、格納される画像データを複数の方向にシフト可能なシフトレジスターで構成され、前記メモリーから主走査幅N+1、副走査幅1の画像データを順次取得して格納し、主走査幅N、副走査幅Mの画像データを出力するレジスター部と、

前記レジスター部から主走査幅N、副走査幅Mの画像データを取得して、前記フィルターを用いてフィルタリングを行うフィルター演算部と、

前記レジスター部の画像データのシフト方向を制御する制御部と、を備える、

ことを特徴とする画像処理装置。

【請求項3】

請求項2に記載の画像処理装置であって、

前記メモリーは、前記ブロック画像データから取得した少なくとも主走査幅N+1、副走査幅2Mの画像データを格納し、

前記レジスター部は、副走査方向、副走査の逆方向、及び主走査の逆方向のシフトが可能であり、各方向のシフトの際に、主走査幅N、副走査幅Mの画像データを出力し、副走査方向及び副走査の逆方向のシフトの際には、前記メモリーから画像データを取得して格納し、

前記制御部は、画素データ列ごとに、副走査方向のシフトとその逆方向のシフトを交互に前記レジスターに指示し、ある画素データ列の処理が終わった場合には主走査の逆方向のシフトを前記レジスターに指示する、

ことを特徴とする画像処理装置。

【請求項4】

原画像データの所定の領域であるブロック画像データについて、主走査幅N、副走査幅Mのフィルターを用いてフィルタリングを行う画像処理回路であって、

前記ブロック画像データを構成する副走査方向の画素データ列それぞれを、副走査方向とその逆方向を交互に処理し、また、主走査方向の列の順に処理する、

ことを特徴とする画像処理回路。

【請求項5】

原画像データの所定の領域であるブロック画像データについて、主走査幅N、副走査幅Mのフィルターを用いてフィルタリングを行う画像処理方法であって、

前記ブロック画像データを構成する副走査方向の画素データ列それぞれを、副走査方向とその逆方向を交互に処理し、また、主走査方向の列の順に処理する、

ことを特徴とする画像処理方法。

【請求項1】

原画像データの所定の領域であるブロック画像データについて、主走査幅N、副走査幅Mのフィルターを用いてフィルタリングを行う画像処理装置であって、

前記ブロック画像データを構成する副走査方向の画素データ列それぞれを、副走査方向とその逆方向を交互に処理し、また、主走査方向の列の順に処理する、

ことを特徴とする画像処理装置。

【請求項2】

請求項1に記載の画像処理装置であって、

前記ブロック画像データの少なくとも一部を格納するメモリーと、

主走査幅N+1、副走査幅Mの容量であって、格納される画像データを複数の方向にシフト可能なシフトレジスターで構成され、前記メモリーから主走査幅N+1、副走査幅1の画像データを順次取得して格納し、主走査幅N、副走査幅Mの画像データを出力するレジスター部と、

前記レジスター部から主走査幅N、副走査幅Mの画像データを取得して、前記フィルターを用いてフィルタリングを行うフィルター演算部と、

前記レジスター部の画像データのシフト方向を制御する制御部と、を備える、

ことを特徴とする画像処理装置。

【請求項3】

請求項2に記載の画像処理装置であって、

前記メモリーは、前記ブロック画像データから取得した少なくとも主走査幅N+1、副走査幅2Mの画像データを格納し、

前記レジスター部は、副走査方向、副走査の逆方向、及び主走査の逆方向のシフトが可能であり、各方向のシフトの際に、主走査幅N、副走査幅Mの画像データを出力し、副走査方向及び副走査の逆方向のシフトの際には、前記メモリーから画像データを取得して格納し、

前記制御部は、画素データ列ごとに、副走査方向のシフトとその逆方向のシフトを交互に前記レジスターに指示し、ある画素データ列の処理が終わった場合には主走査の逆方向のシフトを前記レジスターに指示する、

ことを特徴とする画像処理装置。

【請求項4】

原画像データの所定の領域であるブロック画像データについて、主走査幅N、副走査幅Mのフィルターを用いてフィルタリングを行う画像処理回路であって、

前記ブロック画像データを構成する副走査方向の画素データ列それぞれを、副走査方向とその逆方向を交互に処理し、また、主走査方向の列の順に処理する、

ことを特徴とする画像処理回路。

【請求項5】

原画像データの所定の領域であるブロック画像データについて、主走査幅N、副走査幅Mのフィルターを用いてフィルタリングを行う画像処理方法であって、

前記ブロック画像データを構成する副走査方向の画素データ列それぞれを、副走査方向とその逆方向を交互に処理し、また、主走査方向の列の順に処理する、

ことを特徴とする画像処理方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2011−165132(P2011−165132A)

【公開日】平成23年8月25日(2011.8.25)

【国際特許分類】

【出願番号】特願2010−30261(P2010−30261)

【出願日】平成22年2月15日(2010.2.15)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成23年8月25日(2011.8.25)

【国際特許分類】

【出願日】平成22年2月15日(2010.2.15)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]