画像処理装置、画像処理方法、及びコンピュータプログラム

【課題】小さな回路構成で画像処理回路、あるいは画像処理回路を構成する機能モジュールの異常を簡単に特定できるようにする。

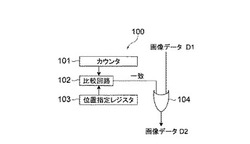

【解決手段】入力画像データに対して所定の画像処理を行う画像処理装置において、前記処理手段のそれぞれについてデバッグ用に同時にテストパターンを発生させるカウンタ101、比較回路102、位置指定レジスタ103及びオア回路104を含むパターン発生回路100を備え、位置指定レジスタ103はテストパターンを出力する位置を比較回路103側に出力し、比較回路103はカウンタ101からのカウント値と位置指定レジスタ103の値とを比較し、一致したときに一致信号を出力し、これにより画像データに前記比較回路102からの一致信号が重畳された画像データD2がオア回路104から出力され、主走査方向、副走査方向にテストパターンを出力する。

【解決手段】入力画像データに対して所定の画像処理を行う画像処理装置において、前記処理手段のそれぞれについてデバッグ用に同時にテストパターンを発生させるカウンタ101、比較回路102、位置指定レジスタ103及びオア回路104を含むパターン発生回路100を備え、位置指定レジスタ103はテストパターンを出力する位置を比較回路103側に出力し、比較回路103はカウンタ101からのカウント値と位置指定レジスタ103の値とを比較し、一致したときに一致信号を出力し、これにより画像データに前記比較回路102からの一致信号が重畳された画像データD2がオア回路104から出力され、主走査方向、副走査方向にテストパターンを出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数のテストパターンを使用して複数の画像処理手段の中のどの画像処理手段が画像の異常を発生させたかを検出する機能を有する画像処理装置、この画像処理装置で実行される画像処理方法、及びこの画像処理方法をコンピュータで実行するためのコンピュータプログラムに関する。

【背景技術】

【0002】

画像処理に際してテストパターンを使用して異常の検知を行う技術として例えば特許文献1及び2に記載された発明が公知である。このうち特許文献1には、外部から多値画像データを入力する入力手段と、多値画像データに所定の変換を施す変換手段と、多値のテストパターンをあらわす多値画像データを発生する第1のパターン発生手段と、前記入力手段によって入力された多値画像データ又は前記第1のパターン発生手段によって発生された前記多値画像データを、選択的に前記変換手段に供給する選択手段と、2値のテストパターンをあらわす2値画像データを発生する第2のパターン発生手段と、前記変換手段により変換された多値画像データ又は前記2値画像データに基づく可視像を印字出力する出力手段と、を備え、前記2値のテストパターンをあらわす2値画像データについては、前記変換手段によって変換されることなく前記出力手段に供給するようにした発明が記載されている。

【0003】

また、特許文献2には、入力画像データを記憶して画像処理を行うメモリを有する画像データ処理装置において、前記メモリの前段に設けられてテストパターンを発生するテストパターン発生手段と、前段の画像処理回路から入力する画像データ又は前記テストパターン発生手段が発生するテストパターンを選択して前記メモリに出力する選択手段と、を備えた発明が記載されている。

【特許文献1】特許第3368037号公報

【特許文献2】特開平11−143306号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

特許文献1記載の発明では、多値のテストパターンと2値のテストパターンの2種類のテストパターンを発生させ、プリント異常の発生個所をエンジン側かコントローラ側を切り分けるようにしている。しかし、この発明のように2種のテストパターンを発生させるためにはそれぞれのパターンを発生させるための専用の回路が必要であり、あるいは、ソフトウェアで発生させる場合にはそのプログラムとそのためのメモリなどが必要であり、回路構成が大きくなる。

【0005】

また、特許文献2記載の発明では、画像データ処理回路の構成が異常なのか、その前段の回路構成が異常なのか、その後段のプリンタ側の回路構成が異常なのかを特定することはできるが、画像データ処理回路の構成のどのモジュールが異常なのかは特定することはできない。

【0006】

そこで、本発明が解決しようとする課題は、小さな回路構成で画像処理回路、あるいは画像処理回路を構成する機能モジュールの異常を簡単に特定できるようにすることにある。

【課題を解決するための手段】

【0007】

前記課題を解決するため、第1の手段は、画像読み取り手段又はネットワークから入力された画像データに所定の処理を施して出力する複数の処理手段を有し、入力画像データに対して所定の画像処理を行う画像処理装置において、前記処理手段のそれぞれについてデバッグ用に同時にテストパターンを発生させるパターン発生手段を備え、前記テストパターンは内部カウンタによりそれぞれ主走査方向又は副走査方向、あるいはその両方の方向の1ラインを含むパターンとして出力されることを特徴とする。

【0008】

第2の手段は、第1の手段において、前記テストパターンを発生させる主走査カウンタ又は副走査カウンタ、あるいはその両方のカウンタは、前記各画像処理ブロックが必要とする内部カウンタと共用することを特徴とする。

【0009】

第3の手段は、第1又は第2の手段において、主走査方向又は副走査方向、あるいはその両方の1ラインを含む前記テストパターンは、1つのカウンタのカウント値に基づいて発生することを特徴とする。

【0010】

第4の手段は、第1ないし第3のいずれかの手段において、主走査方向又は副走査方向、あるいはその両方の1ラインを含むパターンとして出力される複数のテストパターンは、内部レジスタによる固定値に基づいて発生位置が設定されることを特徴とする。

【0011】

第5の手段は、第1ないし第4のいずれかの手段において、前記複数の処理手段が、シェーディング補正、スキャナγ、色補正、変倍、フィルタ及びプリンタγの1つの処理を含むことを特徴とする。

【0012】

第6の手段は、第5の手段において、前記複数の処理手段の各々が、当該処理手段の機能を実現するための少なくとも1つの機能モジュールを含むことを特徴とする。

【0013】

第7の手段は、画像読み取り手段又はネットワークから入力された画像データに所定の複数の処理を施して出力し、入力画像データに対して所定の画像処理を行う画像処理方法において、前記複数の処理のそれぞれについてデバッグ用に同時にテストパターンを発生させ、前記テストパターンは内部カウンタによりそれぞれ主走査方向又は副走査方向、あるいはその両方の方法の1ラインを含むパターンとして出力されることを特徴とする。

【0014】

第8の手段は、画像読み取り手段又はネットワークから入力された画像データに所定の複数の処理を施して出力し、入力画像データに対して行われる所定の画像処理をコンピュータによって実行するためのコンピュータプログラムにおいて、前記複数の処理のそれぞれについてデバッグ用に同時にテストパターンを発生させる手順を備え、当該手順で、前記テストパターンは内部カウンタによりそれぞれ主走査方向又は副走査方向、あるいはその両方の方法の1ラインを含むパターンとして出力されることを特徴とする。

【0015】

なお、後述の実施形態では、処理手段はシェーディング補正部71、スキャナγ部72、色補正部73、変倍部74、フィルタ部75及びプリンタγ部76に、パターン発生手段はテストパターン発生回路100に、内部カウンタはカウンタ101に、内部レジスタは位置指定固定値出力回路123に、機能モジュールは、画像処理LSIに設定されている設定された機能を実現するためのモジュールに、それぞれ対応する。

【発明の効果】

【0016】

本発明によれば、小さな回路構成で画像処理回路、あるいは画像処理回路を構成する機能モジュールの異常を簡単に特定することができる。

【発明を実施するための最良の形態】

【0017】

以下、本発明の実施形態について、図面を参照しながら説明する。

【0018】

図1は本発明の実施形態に係る画像処理装置の構成を示すブロック図である。同図において、画像処理装置は、CPU1、ROM2、RAM3、NV−RAM4、パネル制御部5、操作パネル6、画像処理部7、エンジン制御部8、スキャナユニット9、プリンタユニット10、ディスクドライバ11、記憶装置12、モデム13、外部I/F14及び通信制御部15を含み、これらの各部がデータバス16を介して接続され、1つのシステムを構成している。なお、これらのシステム全体はCPU1の制御下にある。

【0019】

ROM2は、プログラムコード、フォント及びその他の静的なデータを格納している。RAM3は、CPU1のワークメモリとして機能すると共に、一時的な記憶場所として使用される。NV−RAM4には、不揮発性を必要とするデータが格納される。パネル制御部5と操作パネル6は、ユーザとのインタフェースを司る。画像処理部7は読み取った画像データを印刷可能な画像データに変換する等の画像印字出力のための画像処理を行う。エンジン制御部8、スキャナユニット9及びプリンタユニット10は、イメージデータの入出力ユニットとして紙原稿の読み取りと転写紙への印刷とを実行する。ディスクドライバ11とハードディスク等の記憶装置12は、大量のイメージデータ等を蓄積し、また、データベースを記憶する。通信制御部15は、イーサネット(登録商標)等のネットワークと接続され、外部機器との通信を可能とするものである。モデム13は、公衆回線と接続され、外部機器との通信のために使用される。外部I/F14は、セントロニクスやRS232等のインタフェースを用いて通信を行うために使用され、データバス124は、前述した各種デバイス相互間及びCPU1と各デバイス間の通信に使用される。

【0020】

図2は一般的な複写機の画像処理を実行する画像処理ユニットを示すブロック図である。なお、以下の説明において、本実施形態に係る画像処理ユニットは、画像処理部7内にハードウェアにより構成されているものとして説明するが、この画像処理ユニットは、プログラムにより構成することもできる。プログラムによって構成した場合には、RAM3内にロードされてCPU1により実行されることにより必要な機能が構築される。

【0021】

図2は、一般的な複写機の画像処理構成を示すブロック図である。同図において、スキャナユニット9で読み取った画像データをプリンタユニット10から出力する場合、読み取りデータが印字データにするための処理が行われる。この処理を実行するために、本実施形態では、画像処理部7は、シェーディング補正部71、スキャナγ部72、色補正部73、変倍部74、フィルタ部75、及びプリンタγ部76の各部を備えている。

【0022】

シェーディング補正部71では、撮像素子の感度の不均一性等によって生じる対象画像の本来の輝度と映像信号との間の変換特性の不整合を補正する。スキャナγ部72では、画像データを反射率リニアから濃度リニアのデータに変換する。色補正部73は、黒エッジ文字領域以外では、R,G,Bデータを一次濃度マスキング法等でC,M,Yデータに変換する。画像データの色再現を向上させるために、C,M,Yデータの共通部分をUCR(加色除去)処理してBkデータを生成し、C,M,Y,Bkデータを出力する。変倍部74では、変倍率に応じて原画像データに対して拡大、縮小処理、更には、拡大にともなう画素間の補間処理などを行う。フィルタ処理部75では、像域分離信号によりフィルタ処理を切り換える。文字領域(黒エッジ文字と色エッジ文字)では判読性を重視して鮮鋭化処理を行う。写真領域では、画像データ内の急峻な濃度変化をエッジ量として、エッジ量に応じて平滑化処理や鮮鋭化処理を行う。急峻なエッジを鮮鋭化するのは、絵の中の文字を判読しやすくするためである。プリンタγ部76では、プロッタの周波数特性に応じてγ補正を行う。

【0023】

画像処理部7では、画像データがこれらの処理部71〜76を通る間に異常画像が発生した場合、どの処理で画像に異常が発生したか特定するために各画像処理ブロック1〜6でテストパターンを発生させる。このとき、どの画像処理ブロック1〜6から発生させたテストパターンが異常パターンになっているかによってどの処理ブロックで異常画像が発生したかを特定する。

【0024】

例えば後段のブロックから順にテストパターンを発生させていき、あるブロックから発生させたテストパターンが異常になっていたとすると、そのブロックが異常画像を発生させていると特定できる。このような方法で異常画像の発生個所の特定を行うには各ブロックがそれぞれテストパターンを発生させることができなければならない。そこで、図3の例では、各ブロック1ないし6がそれぞれテストパターン発生回路71a,72a,73a,74a,75a,76aを備えている。

【0025】

しかし、テストパターン発生回路71a〜76aはテストパターン画像を発生させるという回路であることから通常、回路規模が大きい。回路規模が大きくなると、その分コストが嵩む。このコストの削減を図ってテストパターン発生回路71a〜76aを少なくすると、図3のように構成した例では、各ブロック71a〜76aからテストパターンを発生させることができなくなるので、異常個所の特定範囲が広くなってしまう。

【0026】

そこで、図4に示した例では、1つのテストパターン発生回路77を備え、設定切替で出力するブロック位置を変えるようにしている。この場合、テストパターン発生回路は、図に示すように1つで良いがやはり回路規模は大きいものである。

【0027】

元々テストパターン発生回路は通常の処理では使用されないデバッグ用回路であるため特にコストを掛けたくない部分である。また、効率を考えるとテストパターンで効率的に異常画像発生ブロックを特定するには同時にテストパターンを発生させる必要がある。この場合、テストパターンを同時に発生させても、どのブロックから出たテストパターンであるか見分けることができなければならない。

【0028】

このようなことから、テストパターン発生回路の規模が小さく、同時にパターン発生が可能で、ブロックごとにテストパターンを見分けることができるという要求を満たすパターンは、図5(a)、(b)、(c)に示すような主副1ライン又はそのどちらか1ラインで構成されたパターンであることが分かる。すなわち、図5(a)に示したテストパターンTP1は主走査方向及び副走査方向の1ラインからなり、図5(b)に示したパターンTP2は主走査方向の1ラインからなり、部5(c)に示したパターンTP3は副走査方向の1ラインからなる。このようなパターンを採用すると、画像の主走査及び副走査又はどちらかのカウンタが1つあれば簡単にこのパターンを発生させることができる。

【0029】

図6は、このようなカウンタ1つでパターンを発生させる回路の一例を示す図である。同図において、パターン発生回路100は、カウンタ101、比較回路102、位置指定レジスタ103及びオア回路104を備えている。オア回路104には、スキャナユニット9側から転送されてくる画像データD1と比較回路102からの出力が入力され、両者の論理和を取って画像データD2が出力される。

【0030】

位置指定レジスタ103はテストパターンを出力する位置を比較回路103側に出力し、比較回路103はカウンタ101からのカウント値と位置指定レジスタ103の値とを比較し、一致したときに一致信号を出力する。これにより、画像データに前記比較回路102からの一致信号が重畳された画像データD2がオア回路104から出力され、主走査方向、副走査方向にテストパターンを出力することができる。これにより、記録紙上に画像GとテストパターンTP1(TP2,TP3)が重畳された画像が出力される。

【0031】

図5(a)のように主走査方向と副走査方向のいずれにもパターンを出力する場合には、主走査方向のラインをカウントするカウンタと、副走査方向のラインをカウントするカウンタ101の2つのカウンタを備えれば良く、図5(b)、(c)のように主走査方向あるいは副走査方向のいずれかにのみパターンを出力する場合には、いずれかの方向のラインをカウントするカウンタ101を1つ備えれば良い。

【0032】

前記カウンタ101は一般的な画像処理ブロックに通常の画像処理用として使用されているものを共用することが可能である。そのため特にテストパターン発生用としてカウンタを新たに用意しなくとも良い。また、簡単な画像とパターン発生回路であることから、画像上のテストパターン位置の変更、調整、指定も容易に行える。さらに1つのテストパターンは全体の画像面積に対して極めて小さいことから、図7に示すように非常に多くのテストパターンTPを重ね合わせることも容易である。

【0033】

また、そのテストパターン発生の制御をより容易にするためにそのためのカウンタを別に持っても良い。こうすることでテストパターン発生を一元的に制御することができる。図8は、この例を示すブロック図である。同図において、パターン発生回路100は、カウンタ111、比較回路112−1,2,・・・、位置指定レジスタ113−1,2,・・・、オア回路114−1,2,3・・・、画像処理ブロック70−1,2,・・・を備えている。比較回路112,位置指定レジスタ113及びオア回路114は図6における比較回路102、位置指定レジスタ103及びオア回路104に対応し、オア回路114から出力される画像データD2が画像処理ブロック70−1に入力され、当該画像処理ブロック70−1で処理された画像データD2がさらに後段のオア回路114−2に入力され画像データD3として出力され、というようにして各画像処理ブロック70−1,2,・・・の処理結果(画像データD2,D3,D4)が次段の画像処理ブロック70−2,3,・・・に入力され、テストパターンと重畳された画像が出力されることになる。なお、画像処理ブロック70−1,2,・・・は図1における画像処理部7の各処理ブロックであるシェーディング補正部71、スキャナγ部72、色補正部73、変倍部74、フィルタ部75及びプリンタγ部76に対応する。この場合においても主走査及び副走査又はどちらかのカウンタが1つあればどのブロックからでも複数同時にテストパターンを発生させることができる。

【0034】

また、図8の構成をより簡易にする方法として画像上のテストパターン位置指定を内部値で固定することもできる。図9はこの例を示すブロック図である。同図では、図8の構成に対して、2段目以降の比較回路112−2,3,・・・と位置指定レジスタ113−2,3,・・・を省略し、1段目の位置指定レジスタ113−1を位置指定固定値出力回路(内部レジスタ)123とする。このように構成すると、位置指定制御が不要になり、さらに回路規模も削減することができる。この場合、各画像処理ブロック70−1,2,・・・から同じテストパターンがそれぞれ同時に発生するが、各画像処理ブロック70−1,2,・・・のもつ処理遅延が、そのままテストパターンのズレに反映されるためテストパターンが重なることはない。この状態を図10に示す。図10は図9の回路構成としたときの画像をテストパターンの出力状態を示している。

【0035】

テストパターンは異常画像の発生ブロック(モジュール)を特定するためのものである。そこで、以下、異常を発生したブロックの特定方法について説明する。

【0036】

図11はコピー機能の使用時に画像処理ブロックの幾つかに不良があった場合の最終出力画像の例を説明する図である。コピー機能使用時に図2で順に接続された画像処理ブロックのうち、どこかを境に幾つかに不良が生じ、図11に示すような画像の一部がずれたような異常画像が出力されたものとする。この例の場合、テストパターンの状況を見ると、4番目までのテストパターンが異常で、5番目以降のテストパターンが正常であることが分かる。

【0037】

図12〜図15は図11に示すような異常画像が出力される原因となった画像処理ブロックを特定する考え方を示すための説明図である。

【0038】

いま、全ての画像処理ブロック71〜76が正常であった場合、色補正部73迄の処理が終了し、変倍部74に入力された時点の画像は、図13に示すようなものとなるはずである。図12に示す画像に、変倍部74がテストパターンを重ねて処理を行って出力すると、その画像は、図13に示すようなものとなるはずである。ところで、画像処理ブロック74に障害が発生していた場合、色補正部73が出力した画像を変倍部74が処理をしてフィルタ部75に出力した時点の画像が、図14に示すような画像であることが考えられる。そして、正常なフィルタ部75がテストパターンを重ねて処理を行って出力する画像は、図15に示すようなものとなる。図15に示すような画像となる理由は、5番目以降のテストパターンは、4番目の変倍部74からの画像の出力時点では画像に存在せず、フィルタ部75が重ねる5番目のテストパターンは、入力された画像が正常か異常かに関わらず特定の5番目の位置に重ねて出力されるからである。これ以降の画像処理ブロックが正常であれば、以降の画像処理ブロックからのテストパターンも異常なく出力されるので、図11に示したような出力画像となる。

【0039】

このようにテストパターンを各画像処理ブロックが同時に、そしてそのテストパターンが画像処理ブロック別に識別可能位置に出力することにより、1つの異常画像出力から異常を出力した画像処理ブロックを容易に特定することができる。

【0040】

なお、ここでは、画像処理ブロックとして説明しているが、各画像処理ブロックは複数の画像処理LSIから構成され、さらに、画像処理LSIは複数の機能モジュールを備え、各機能モジュールの機能を実現することにより、所望の画像処理が行われる。そのため、前記テストパターンは各機能処理モジュール単位で発生させることもできる。

【0041】

なお、本実施形態では、テストパターンは主走査方向又は副走査方向、あるいは主走査方向及び副走査方向の両者に1ラインずつ出力しているが、ごく少数のライン、例えば5ライン以下のラインで構成することもできる。この場合には、位置指定レジスタ113の値を使用するライン数分設定すれば良い。

【0042】

以上のように、本実施形態によれば、

1)テストパターンを主走査方向又は副走査方向又はその両方の1ライン又は少数ラインで構成するので、簡単な回路構成で有効なテストパターンを同時に発生させることができる。

2)簡単で有効なテストパターンを設定することにより共通のカウンタ又は他の画像処理回路のカウンタと組み合わすことができ、それにより非常に簡単な回路でテストパターンを同時に複数発生させることができる。

3)テストパターンを発生させる主走査カウンタ又は副走査カウンタは、各画像処理ブロックが必要とする内部カウンタを使用するので、テストパターン発生用の追加のカウンタ回路を削減することができる。

4)比較回路の比較値を位置指定レジスタによって複数種用意することにより、主走査カウンタ又は副走査カウンタ、あるいはその両方で同時に発生する複数のテストパターンを、1つのカウンタで容易に発生させることができる。

5)比較回路の比較値を内部レジスタの固定値とすることにより、主走査カウンタ又は副走査カウンタ、あるいはその両方で同時に発生する複数のテストパターンを発生させるための発生位置制御が不要となり、回路の簡略化を促進することができる。

等の効果を奏する。

【0043】

なお、本発明は本実施形態に限定されるものではなく、特許請求の範囲に記載された技術思想に含まれる技術的事項の全てが対象となることは言うまでもない。

【図面の簡単な説明】

【0044】

【図1】本発明の一実施形態に係る画像処理装置の構成の一例を示すブロック図である。

【図2】一般的な複写機の画像処理を実行する画像処理ユニットを示すブロック図である。

【図3】各画像処理ブロックそれぞれテストパターン発生回路を備えた例を示すブロック図である。

【図4】各画像処理ブロックに対して1つのテストパターン発生回路でテストパターンを出力させる回路構成を示すブロック図である。

【図5】本実施形態に係るテストパターンの例を示す図である。

【図6】本実施形態に係るパターン出力回路を示すブロック図で、カウンタ1つでパターンを発生させる回路の一例を示す。

【図7】非常に多くのテストパターンを重ね合わせたテストパターンの例を示す図である。

【図8】図7のテストパターンを出力するパターン発生回路の一例を示すブロック図である。

【図9】図8のパターン発生回路を簡素化した例を示すブロック図である。

【図10】図9のパターン発生回路によるテストパターンの出力例を示す図である。

【図11】コピー機能の使用時に画像処理ブロックの幾つかに不良があった場合の最終出力画像の例を説明する図である。

【図12】図11に示すような異常画像が出力される原因となった画像処理ブロックを特定する考え方を説明する各画像処理ブロックから出力される画像の例を説明する図(その1)である。

【図13】図11に示すような異常画像が出力される原因となった画像処理ブロックを特定する考え方を説明する各画像処理ブロックから出力される画像の例を説明する図(その2)である。

【図14】図11に示すような異常画像が出力される原因となった画像処理ブロックを特定する考え方を説明する各画像処理ブロックから出力される画像の例を説明する図(その3)である。

【図15】図11に示すような異常画像が出力される原因となった画像処理ブロックを特定する考え方を説明する各画像処理ブロックから出力される画像の例を説明する図(その4)である。

【符号の説明】

【0045】

1 CPU

7 画像処理装置

70−1,2 画像処理ブロック

71 シェーディング補正部

72 スキャナγ部

73 色補正部

74 変倍部

75 フィルタ部

76 プリンタγ部

9 スキャナユニット

10 プリンタユニット

100 パターン発生回路

101,111,121 カウンタ

102,112−1,2,3,122 比較回路

103,113−1,2,3 位置指定レジスタ

104,114−1,2,3 オア回路

123 位置指定固定値出力回路(内部レジスタ)

D−1,2,3,4 画像データ

G 画像

TP,TP1,TP2,TP3 テストパターン

【技術分野】

【0001】

本発明は、複数のテストパターンを使用して複数の画像処理手段の中のどの画像処理手段が画像の異常を発生させたかを検出する機能を有する画像処理装置、この画像処理装置で実行される画像処理方法、及びこの画像処理方法をコンピュータで実行するためのコンピュータプログラムに関する。

【背景技術】

【0002】

画像処理に際してテストパターンを使用して異常の検知を行う技術として例えば特許文献1及び2に記載された発明が公知である。このうち特許文献1には、外部から多値画像データを入力する入力手段と、多値画像データに所定の変換を施す変換手段と、多値のテストパターンをあらわす多値画像データを発生する第1のパターン発生手段と、前記入力手段によって入力された多値画像データ又は前記第1のパターン発生手段によって発生された前記多値画像データを、選択的に前記変換手段に供給する選択手段と、2値のテストパターンをあらわす2値画像データを発生する第2のパターン発生手段と、前記変換手段により変換された多値画像データ又は前記2値画像データに基づく可視像を印字出力する出力手段と、を備え、前記2値のテストパターンをあらわす2値画像データについては、前記変換手段によって変換されることなく前記出力手段に供給するようにした発明が記載されている。

【0003】

また、特許文献2には、入力画像データを記憶して画像処理を行うメモリを有する画像データ処理装置において、前記メモリの前段に設けられてテストパターンを発生するテストパターン発生手段と、前段の画像処理回路から入力する画像データ又は前記テストパターン発生手段が発生するテストパターンを選択して前記メモリに出力する選択手段と、を備えた発明が記載されている。

【特許文献1】特許第3368037号公報

【特許文献2】特開平11−143306号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

特許文献1記載の発明では、多値のテストパターンと2値のテストパターンの2種類のテストパターンを発生させ、プリント異常の発生個所をエンジン側かコントローラ側を切り分けるようにしている。しかし、この発明のように2種のテストパターンを発生させるためにはそれぞれのパターンを発生させるための専用の回路が必要であり、あるいは、ソフトウェアで発生させる場合にはそのプログラムとそのためのメモリなどが必要であり、回路構成が大きくなる。

【0005】

また、特許文献2記載の発明では、画像データ処理回路の構成が異常なのか、その前段の回路構成が異常なのか、その後段のプリンタ側の回路構成が異常なのかを特定することはできるが、画像データ処理回路の構成のどのモジュールが異常なのかは特定することはできない。

【0006】

そこで、本発明が解決しようとする課題は、小さな回路構成で画像処理回路、あるいは画像処理回路を構成する機能モジュールの異常を簡単に特定できるようにすることにある。

【課題を解決するための手段】

【0007】

前記課題を解決するため、第1の手段は、画像読み取り手段又はネットワークから入力された画像データに所定の処理を施して出力する複数の処理手段を有し、入力画像データに対して所定の画像処理を行う画像処理装置において、前記処理手段のそれぞれについてデバッグ用に同時にテストパターンを発生させるパターン発生手段を備え、前記テストパターンは内部カウンタによりそれぞれ主走査方向又は副走査方向、あるいはその両方の方向の1ラインを含むパターンとして出力されることを特徴とする。

【0008】

第2の手段は、第1の手段において、前記テストパターンを発生させる主走査カウンタ又は副走査カウンタ、あるいはその両方のカウンタは、前記各画像処理ブロックが必要とする内部カウンタと共用することを特徴とする。

【0009】

第3の手段は、第1又は第2の手段において、主走査方向又は副走査方向、あるいはその両方の1ラインを含む前記テストパターンは、1つのカウンタのカウント値に基づいて発生することを特徴とする。

【0010】

第4の手段は、第1ないし第3のいずれかの手段において、主走査方向又は副走査方向、あるいはその両方の1ラインを含むパターンとして出力される複数のテストパターンは、内部レジスタによる固定値に基づいて発生位置が設定されることを特徴とする。

【0011】

第5の手段は、第1ないし第4のいずれかの手段において、前記複数の処理手段が、シェーディング補正、スキャナγ、色補正、変倍、フィルタ及びプリンタγの1つの処理を含むことを特徴とする。

【0012】

第6の手段は、第5の手段において、前記複数の処理手段の各々が、当該処理手段の機能を実現するための少なくとも1つの機能モジュールを含むことを特徴とする。

【0013】

第7の手段は、画像読み取り手段又はネットワークから入力された画像データに所定の複数の処理を施して出力し、入力画像データに対して所定の画像処理を行う画像処理方法において、前記複数の処理のそれぞれについてデバッグ用に同時にテストパターンを発生させ、前記テストパターンは内部カウンタによりそれぞれ主走査方向又は副走査方向、あるいはその両方の方法の1ラインを含むパターンとして出力されることを特徴とする。

【0014】

第8の手段は、画像読み取り手段又はネットワークから入力された画像データに所定の複数の処理を施して出力し、入力画像データに対して行われる所定の画像処理をコンピュータによって実行するためのコンピュータプログラムにおいて、前記複数の処理のそれぞれについてデバッグ用に同時にテストパターンを発生させる手順を備え、当該手順で、前記テストパターンは内部カウンタによりそれぞれ主走査方向又は副走査方向、あるいはその両方の方法の1ラインを含むパターンとして出力されることを特徴とする。

【0015】

なお、後述の実施形態では、処理手段はシェーディング補正部71、スキャナγ部72、色補正部73、変倍部74、フィルタ部75及びプリンタγ部76に、パターン発生手段はテストパターン発生回路100に、内部カウンタはカウンタ101に、内部レジスタは位置指定固定値出力回路123に、機能モジュールは、画像処理LSIに設定されている設定された機能を実現するためのモジュールに、それぞれ対応する。

【発明の効果】

【0016】

本発明によれば、小さな回路構成で画像処理回路、あるいは画像処理回路を構成する機能モジュールの異常を簡単に特定することができる。

【発明を実施するための最良の形態】

【0017】

以下、本発明の実施形態について、図面を参照しながら説明する。

【0018】

図1は本発明の実施形態に係る画像処理装置の構成を示すブロック図である。同図において、画像処理装置は、CPU1、ROM2、RAM3、NV−RAM4、パネル制御部5、操作パネル6、画像処理部7、エンジン制御部8、スキャナユニット9、プリンタユニット10、ディスクドライバ11、記憶装置12、モデム13、外部I/F14及び通信制御部15を含み、これらの各部がデータバス16を介して接続され、1つのシステムを構成している。なお、これらのシステム全体はCPU1の制御下にある。

【0019】

ROM2は、プログラムコード、フォント及びその他の静的なデータを格納している。RAM3は、CPU1のワークメモリとして機能すると共に、一時的な記憶場所として使用される。NV−RAM4には、不揮発性を必要とするデータが格納される。パネル制御部5と操作パネル6は、ユーザとのインタフェースを司る。画像処理部7は読み取った画像データを印刷可能な画像データに変換する等の画像印字出力のための画像処理を行う。エンジン制御部8、スキャナユニット9及びプリンタユニット10は、イメージデータの入出力ユニットとして紙原稿の読み取りと転写紙への印刷とを実行する。ディスクドライバ11とハードディスク等の記憶装置12は、大量のイメージデータ等を蓄積し、また、データベースを記憶する。通信制御部15は、イーサネット(登録商標)等のネットワークと接続され、外部機器との通信を可能とするものである。モデム13は、公衆回線と接続され、外部機器との通信のために使用される。外部I/F14は、セントロニクスやRS232等のインタフェースを用いて通信を行うために使用され、データバス124は、前述した各種デバイス相互間及びCPU1と各デバイス間の通信に使用される。

【0020】

図2は一般的な複写機の画像処理を実行する画像処理ユニットを示すブロック図である。なお、以下の説明において、本実施形態に係る画像処理ユニットは、画像処理部7内にハードウェアにより構成されているものとして説明するが、この画像処理ユニットは、プログラムにより構成することもできる。プログラムによって構成した場合には、RAM3内にロードされてCPU1により実行されることにより必要な機能が構築される。

【0021】

図2は、一般的な複写機の画像処理構成を示すブロック図である。同図において、スキャナユニット9で読み取った画像データをプリンタユニット10から出力する場合、読み取りデータが印字データにするための処理が行われる。この処理を実行するために、本実施形態では、画像処理部7は、シェーディング補正部71、スキャナγ部72、色補正部73、変倍部74、フィルタ部75、及びプリンタγ部76の各部を備えている。

【0022】

シェーディング補正部71では、撮像素子の感度の不均一性等によって生じる対象画像の本来の輝度と映像信号との間の変換特性の不整合を補正する。スキャナγ部72では、画像データを反射率リニアから濃度リニアのデータに変換する。色補正部73は、黒エッジ文字領域以外では、R,G,Bデータを一次濃度マスキング法等でC,M,Yデータに変換する。画像データの色再現を向上させるために、C,M,Yデータの共通部分をUCR(加色除去)処理してBkデータを生成し、C,M,Y,Bkデータを出力する。変倍部74では、変倍率に応じて原画像データに対して拡大、縮小処理、更には、拡大にともなう画素間の補間処理などを行う。フィルタ処理部75では、像域分離信号によりフィルタ処理を切り換える。文字領域(黒エッジ文字と色エッジ文字)では判読性を重視して鮮鋭化処理を行う。写真領域では、画像データ内の急峻な濃度変化をエッジ量として、エッジ量に応じて平滑化処理や鮮鋭化処理を行う。急峻なエッジを鮮鋭化するのは、絵の中の文字を判読しやすくするためである。プリンタγ部76では、プロッタの周波数特性に応じてγ補正を行う。

【0023】

画像処理部7では、画像データがこれらの処理部71〜76を通る間に異常画像が発生した場合、どの処理で画像に異常が発生したか特定するために各画像処理ブロック1〜6でテストパターンを発生させる。このとき、どの画像処理ブロック1〜6から発生させたテストパターンが異常パターンになっているかによってどの処理ブロックで異常画像が発生したかを特定する。

【0024】

例えば後段のブロックから順にテストパターンを発生させていき、あるブロックから発生させたテストパターンが異常になっていたとすると、そのブロックが異常画像を発生させていると特定できる。このような方法で異常画像の発生個所の特定を行うには各ブロックがそれぞれテストパターンを発生させることができなければならない。そこで、図3の例では、各ブロック1ないし6がそれぞれテストパターン発生回路71a,72a,73a,74a,75a,76aを備えている。

【0025】

しかし、テストパターン発生回路71a〜76aはテストパターン画像を発生させるという回路であることから通常、回路規模が大きい。回路規模が大きくなると、その分コストが嵩む。このコストの削減を図ってテストパターン発生回路71a〜76aを少なくすると、図3のように構成した例では、各ブロック71a〜76aからテストパターンを発生させることができなくなるので、異常個所の特定範囲が広くなってしまう。

【0026】

そこで、図4に示した例では、1つのテストパターン発生回路77を備え、設定切替で出力するブロック位置を変えるようにしている。この場合、テストパターン発生回路は、図に示すように1つで良いがやはり回路規模は大きいものである。

【0027】

元々テストパターン発生回路は通常の処理では使用されないデバッグ用回路であるため特にコストを掛けたくない部分である。また、効率を考えるとテストパターンで効率的に異常画像発生ブロックを特定するには同時にテストパターンを発生させる必要がある。この場合、テストパターンを同時に発生させても、どのブロックから出たテストパターンであるか見分けることができなければならない。

【0028】

このようなことから、テストパターン発生回路の規模が小さく、同時にパターン発生が可能で、ブロックごとにテストパターンを見分けることができるという要求を満たすパターンは、図5(a)、(b)、(c)に示すような主副1ライン又はそのどちらか1ラインで構成されたパターンであることが分かる。すなわち、図5(a)に示したテストパターンTP1は主走査方向及び副走査方向の1ラインからなり、図5(b)に示したパターンTP2は主走査方向の1ラインからなり、部5(c)に示したパターンTP3は副走査方向の1ラインからなる。このようなパターンを採用すると、画像の主走査及び副走査又はどちらかのカウンタが1つあれば簡単にこのパターンを発生させることができる。

【0029】

図6は、このようなカウンタ1つでパターンを発生させる回路の一例を示す図である。同図において、パターン発生回路100は、カウンタ101、比較回路102、位置指定レジスタ103及びオア回路104を備えている。オア回路104には、スキャナユニット9側から転送されてくる画像データD1と比較回路102からの出力が入力され、両者の論理和を取って画像データD2が出力される。

【0030】

位置指定レジスタ103はテストパターンを出力する位置を比較回路103側に出力し、比較回路103はカウンタ101からのカウント値と位置指定レジスタ103の値とを比較し、一致したときに一致信号を出力する。これにより、画像データに前記比較回路102からの一致信号が重畳された画像データD2がオア回路104から出力され、主走査方向、副走査方向にテストパターンを出力することができる。これにより、記録紙上に画像GとテストパターンTP1(TP2,TP3)が重畳された画像が出力される。

【0031】

図5(a)のように主走査方向と副走査方向のいずれにもパターンを出力する場合には、主走査方向のラインをカウントするカウンタと、副走査方向のラインをカウントするカウンタ101の2つのカウンタを備えれば良く、図5(b)、(c)のように主走査方向あるいは副走査方向のいずれかにのみパターンを出力する場合には、いずれかの方向のラインをカウントするカウンタ101を1つ備えれば良い。

【0032】

前記カウンタ101は一般的な画像処理ブロックに通常の画像処理用として使用されているものを共用することが可能である。そのため特にテストパターン発生用としてカウンタを新たに用意しなくとも良い。また、簡単な画像とパターン発生回路であることから、画像上のテストパターン位置の変更、調整、指定も容易に行える。さらに1つのテストパターンは全体の画像面積に対して極めて小さいことから、図7に示すように非常に多くのテストパターンTPを重ね合わせることも容易である。

【0033】

また、そのテストパターン発生の制御をより容易にするためにそのためのカウンタを別に持っても良い。こうすることでテストパターン発生を一元的に制御することができる。図8は、この例を示すブロック図である。同図において、パターン発生回路100は、カウンタ111、比較回路112−1,2,・・・、位置指定レジスタ113−1,2,・・・、オア回路114−1,2,3・・・、画像処理ブロック70−1,2,・・・を備えている。比較回路112,位置指定レジスタ113及びオア回路114は図6における比較回路102、位置指定レジスタ103及びオア回路104に対応し、オア回路114から出力される画像データD2が画像処理ブロック70−1に入力され、当該画像処理ブロック70−1で処理された画像データD2がさらに後段のオア回路114−2に入力され画像データD3として出力され、というようにして各画像処理ブロック70−1,2,・・・の処理結果(画像データD2,D3,D4)が次段の画像処理ブロック70−2,3,・・・に入力され、テストパターンと重畳された画像が出力されることになる。なお、画像処理ブロック70−1,2,・・・は図1における画像処理部7の各処理ブロックであるシェーディング補正部71、スキャナγ部72、色補正部73、変倍部74、フィルタ部75及びプリンタγ部76に対応する。この場合においても主走査及び副走査又はどちらかのカウンタが1つあればどのブロックからでも複数同時にテストパターンを発生させることができる。

【0034】

また、図8の構成をより簡易にする方法として画像上のテストパターン位置指定を内部値で固定することもできる。図9はこの例を示すブロック図である。同図では、図8の構成に対して、2段目以降の比較回路112−2,3,・・・と位置指定レジスタ113−2,3,・・・を省略し、1段目の位置指定レジスタ113−1を位置指定固定値出力回路(内部レジスタ)123とする。このように構成すると、位置指定制御が不要になり、さらに回路規模も削減することができる。この場合、各画像処理ブロック70−1,2,・・・から同じテストパターンがそれぞれ同時に発生するが、各画像処理ブロック70−1,2,・・・のもつ処理遅延が、そのままテストパターンのズレに反映されるためテストパターンが重なることはない。この状態を図10に示す。図10は図9の回路構成としたときの画像をテストパターンの出力状態を示している。

【0035】

テストパターンは異常画像の発生ブロック(モジュール)を特定するためのものである。そこで、以下、異常を発生したブロックの特定方法について説明する。

【0036】

図11はコピー機能の使用時に画像処理ブロックの幾つかに不良があった場合の最終出力画像の例を説明する図である。コピー機能使用時に図2で順に接続された画像処理ブロックのうち、どこかを境に幾つかに不良が生じ、図11に示すような画像の一部がずれたような異常画像が出力されたものとする。この例の場合、テストパターンの状況を見ると、4番目までのテストパターンが異常で、5番目以降のテストパターンが正常であることが分かる。

【0037】

図12〜図15は図11に示すような異常画像が出力される原因となった画像処理ブロックを特定する考え方を示すための説明図である。

【0038】

いま、全ての画像処理ブロック71〜76が正常であった場合、色補正部73迄の処理が終了し、変倍部74に入力された時点の画像は、図13に示すようなものとなるはずである。図12に示す画像に、変倍部74がテストパターンを重ねて処理を行って出力すると、その画像は、図13に示すようなものとなるはずである。ところで、画像処理ブロック74に障害が発生していた場合、色補正部73が出力した画像を変倍部74が処理をしてフィルタ部75に出力した時点の画像が、図14に示すような画像であることが考えられる。そして、正常なフィルタ部75がテストパターンを重ねて処理を行って出力する画像は、図15に示すようなものとなる。図15に示すような画像となる理由は、5番目以降のテストパターンは、4番目の変倍部74からの画像の出力時点では画像に存在せず、フィルタ部75が重ねる5番目のテストパターンは、入力された画像が正常か異常かに関わらず特定の5番目の位置に重ねて出力されるからである。これ以降の画像処理ブロックが正常であれば、以降の画像処理ブロックからのテストパターンも異常なく出力されるので、図11に示したような出力画像となる。

【0039】

このようにテストパターンを各画像処理ブロックが同時に、そしてそのテストパターンが画像処理ブロック別に識別可能位置に出力することにより、1つの異常画像出力から異常を出力した画像処理ブロックを容易に特定することができる。

【0040】

なお、ここでは、画像処理ブロックとして説明しているが、各画像処理ブロックは複数の画像処理LSIから構成され、さらに、画像処理LSIは複数の機能モジュールを備え、各機能モジュールの機能を実現することにより、所望の画像処理が行われる。そのため、前記テストパターンは各機能処理モジュール単位で発生させることもできる。

【0041】

なお、本実施形態では、テストパターンは主走査方向又は副走査方向、あるいは主走査方向及び副走査方向の両者に1ラインずつ出力しているが、ごく少数のライン、例えば5ライン以下のラインで構成することもできる。この場合には、位置指定レジスタ113の値を使用するライン数分設定すれば良い。

【0042】

以上のように、本実施形態によれば、

1)テストパターンを主走査方向又は副走査方向又はその両方の1ライン又は少数ラインで構成するので、簡単な回路構成で有効なテストパターンを同時に発生させることができる。

2)簡単で有効なテストパターンを設定することにより共通のカウンタ又は他の画像処理回路のカウンタと組み合わすことができ、それにより非常に簡単な回路でテストパターンを同時に複数発生させることができる。

3)テストパターンを発生させる主走査カウンタ又は副走査カウンタは、各画像処理ブロックが必要とする内部カウンタを使用するので、テストパターン発生用の追加のカウンタ回路を削減することができる。

4)比較回路の比較値を位置指定レジスタによって複数種用意することにより、主走査カウンタ又は副走査カウンタ、あるいはその両方で同時に発生する複数のテストパターンを、1つのカウンタで容易に発生させることができる。

5)比較回路の比較値を内部レジスタの固定値とすることにより、主走査カウンタ又は副走査カウンタ、あるいはその両方で同時に発生する複数のテストパターンを発生させるための発生位置制御が不要となり、回路の簡略化を促進することができる。

等の効果を奏する。

【0043】

なお、本発明は本実施形態に限定されるものではなく、特許請求の範囲に記載された技術思想に含まれる技術的事項の全てが対象となることは言うまでもない。

【図面の簡単な説明】

【0044】

【図1】本発明の一実施形態に係る画像処理装置の構成の一例を示すブロック図である。

【図2】一般的な複写機の画像処理を実行する画像処理ユニットを示すブロック図である。

【図3】各画像処理ブロックそれぞれテストパターン発生回路を備えた例を示すブロック図である。

【図4】各画像処理ブロックに対して1つのテストパターン発生回路でテストパターンを出力させる回路構成を示すブロック図である。

【図5】本実施形態に係るテストパターンの例を示す図である。

【図6】本実施形態に係るパターン出力回路を示すブロック図で、カウンタ1つでパターンを発生させる回路の一例を示す。

【図7】非常に多くのテストパターンを重ね合わせたテストパターンの例を示す図である。

【図8】図7のテストパターンを出力するパターン発生回路の一例を示すブロック図である。

【図9】図8のパターン発生回路を簡素化した例を示すブロック図である。

【図10】図9のパターン発生回路によるテストパターンの出力例を示す図である。

【図11】コピー機能の使用時に画像処理ブロックの幾つかに不良があった場合の最終出力画像の例を説明する図である。

【図12】図11に示すような異常画像が出力される原因となった画像処理ブロックを特定する考え方を説明する各画像処理ブロックから出力される画像の例を説明する図(その1)である。

【図13】図11に示すような異常画像が出力される原因となった画像処理ブロックを特定する考え方を説明する各画像処理ブロックから出力される画像の例を説明する図(その2)である。

【図14】図11に示すような異常画像が出力される原因となった画像処理ブロックを特定する考え方を説明する各画像処理ブロックから出力される画像の例を説明する図(その3)である。

【図15】図11に示すような異常画像が出力される原因となった画像処理ブロックを特定する考え方を説明する各画像処理ブロックから出力される画像の例を説明する図(その4)である。

【符号の説明】

【0045】

1 CPU

7 画像処理装置

70−1,2 画像処理ブロック

71 シェーディング補正部

72 スキャナγ部

73 色補正部

74 変倍部

75 フィルタ部

76 プリンタγ部

9 スキャナユニット

10 プリンタユニット

100 パターン発生回路

101,111,121 カウンタ

102,112−1,2,3,122 比較回路

103,113−1,2,3 位置指定レジスタ

104,114−1,2,3 オア回路

123 位置指定固定値出力回路(内部レジスタ)

D−1,2,3,4 画像データ

G 画像

TP,TP1,TP2,TP3 テストパターン

【特許請求の範囲】

【請求項1】

画像読み取り手段又はネットワークから入力された画像データに所定の処理を施して出力する複数の処理手段を有し、入力画像データに対して所定の画像処理を行う画像処理装置において、

前記処理手段のそれぞれについてデバッグ用に同時にテストパターンを発生させるパターン発生手段を備え、

前記テストパターンは内部カウンタによりそれぞれ主走査方向又は副走査方向、あるいはその両方の方向の1ラインを含むパターンとして出力されることを特徴とする画像処理装置。

【請求項2】

請求項1記載の画像処理装置において、

前記テストパターンを発生させる主走査カウンタ又は副走査カウンタ、あるいはその両方のカウンタは、前記各画像処理ブロックが必要とする内部カウンタと共用することを特徴とする画像処理装置。

【請求項3】

請求項1又は2記載の画像処理装置において、

主走査方向又は副走査方向、あるいはその両方の1ラインを含む前記テストパターンは、1つのカウンタのカウント値に基づいて発生することを特徴とする画像処理装置。

【請求項4】

請求項1ないし3のいずれか1項に記載の画像処理装置において、

主走査方向又は副走査方向、あるいはその両方の1ラインを含むパターンとして出力される複数のテストパターンは、内部レジスタによる固定値に基づいて発生位置が設定されることを特徴とする画像処理装置。

【請求項5】

請求項1ないし4のいずれか1項に記載の画像処理装置において、

前記複数の処理手段が、シェーディング補正、スキャナγ、色補正、変倍、フィルタ及びプリンタγの1つを含むことを特徴とする画像処理装置。

【請求項6】

請求項5記載の画像処理装置において、

前記複数の処理手段の各々が、当該処理手段の機能を実現するための少なくとも1つの機能モジュールを含むことを特徴とする画像処理装置。

【請求項7】

画像読み取り手段又はネットワークから入力された画像データに所定の複数の処理を施して出力し、入力画像データに対して所定の画像処理を行う画像処理方法において、

前記複数の処理のそれぞれについてデバッグ用に同時にテストパターンを発生させ、

前記テストパターンは内部カウンタによりそれぞれ主走査方向又は副走査方向、あるいはその両方の方法の1ラインを含むパターンとして出力されることを特徴とする画像処理方法。

【請求項8】

画像読み取り手段又はネットワークから入力された画像データに所定の複数の処理を施して出力し、入力画像データに対して行われる所定の画像処理をコンピュータによって実行するためのコンピュータプログラムにおいて、

前記複数の処理のそれぞれについてデバッグ用に同時にテストパターンを発生させる手順を備え、

当該手順で、前記テストパターンは内部カウンタによりそれぞれ主走査方向又は副走査方向、あるいはその両方の方法の1ラインを含むパターンとして出力されることを特徴とするコンピュータプログラム。

【請求項1】

画像読み取り手段又はネットワークから入力された画像データに所定の処理を施して出力する複数の処理手段を有し、入力画像データに対して所定の画像処理を行う画像処理装置において、

前記処理手段のそれぞれについてデバッグ用に同時にテストパターンを発生させるパターン発生手段を備え、

前記テストパターンは内部カウンタによりそれぞれ主走査方向又は副走査方向、あるいはその両方の方向の1ラインを含むパターンとして出力されることを特徴とする画像処理装置。

【請求項2】

請求項1記載の画像処理装置において、

前記テストパターンを発生させる主走査カウンタ又は副走査カウンタ、あるいはその両方のカウンタは、前記各画像処理ブロックが必要とする内部カウンタと共用することを特徴とする画像処理装置。

【請求項3】

請求項1又は2記載の画像処理装置において、

主走査方向又は副走査方向、あるいはその両方の1ラインを含む前記テストパターンは、1つのカウンタのカウント値に基づいて発生することを特徴とする画像処理装置。

【請求項4】

請求項1ないし3のいずれか1項に記載の画像処理装置において、

主走査方向又は副走査方向、あるいはその両方の1ラインを含むパターンとして出力される複数のテストパターンは、内部レジスタによる固定値に基づいて発生位置が設定されることを特徴とする画像処理装置。

【請求項5】

請求項1ないし4のいずれか1項に記載の画像処理装置において、

前記複数の処理手段が、シェーディング補正、スキャナγ、色補正、変倍、フィルタ及びプリンタγの1つを含むことを特徴とする画像処理装置。

【請求項6】

請求項5記載の画像処理装置において、

前記複数の処理手段の各々が、当該処理手段の機能を実現するための少なくとも1つの機能モジュールを含むことを特徴とする画像処理装置。

【請求項7】

画像読み取り手段又はネットワークから入力された画像データに所定の複数の処理を施して出力し、入力画像データに対して所定の画像処理を行う画像処理方法において、

前記複数の処理のそれぞれについてデバッグ用に同時にテストパターンを発生させ、

前記テストパターンは内部カウンタによりそれぞれ主走査方向又は副走査方向、あるいはその両方の方法の1ラインを含むパターンとして出力されることを特徴とする画像処理方法。

【請求項8】

画像読み取り手段又はネットワークから入力された画像データに所定の複数の処理を施して出力し、入力画像データに対して行われる所定の画像処理をコンピュータによって実行するためのコンピュータプログラムにおいて、

前記複数の処理のそれぞれについてデバッグ用に同時にテストパターンを発生させる手順を備え、

当該手順で、前記テストパターンは内部カウンタによりそれぞれ主走査方向又は副走査方向、あるいはその両方の方法の1ラインを含むパターンとして出力されることを特徴とするコンピュータプログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2010−28755(P2010−28755A)

【公開日】平成22年2月4日(2010.2.4)

【国際特許分類】

【出願番号】特願2008−191057(P2008−191057)

【出願日】平成20年7月24日(2008.7.24)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成22年2月4日(2010.2.4)

【国際特許分類】

【出願日】平成20年7月24日(2008.7.24)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]