画像処理装置

【課題】画像フィルタに制限されずに希望する画像処理回路を構築することを可能とする画像処理手順を学習することができ、画像処理の処理速度を向上させることが可能な画像処理装置を提供する。

【解決手段】画像処理装置1は、プロセッサ2と、シフトレジスタ3と、学習ユニット4と、マルチプレクサ5と、学習手段6とを備えている。さらに、各学習ユニット4xは、関数処理回路が並列に配置された演算ユニットと各関数処理回路に入力するデータを選択する選択器で構成されている。複数個が直列に連結されている学習ユニット4の各選択器は、画像処理の手順を示す選択信号SSに従って各関数処理回路に入力するデータを選択し、学習手段6は各学習ユニット4の選択器に割り当てる選択信号SSを学習により最適化する。

【解決手段】画像処理装置1は、プロセッサ2と、シフトレジスタ3と、学習ユニット4と、マルチプレクサ5と、学習手段6とを備えている。さらに、各学習ユニット4xは、関数処理回路が並列に配置された演算ユニットと各関数処理回路に入力するデータを選択する選択器で構成されている。複数個が直列に連結されている学習ユニット4の各選択器は、画像処理の手順を示す選択信号SSに従って各関数処理回路に入力するデータを選択し、学習手段6は各学習ユニット4の選択器に割り当てる選択信号SSを学習により最適化する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像処理装置に係り、特に、画像処理を行うための関数処理回路を選択する選択信号を学習により形成可能な画像処理装置に関する。

【背景技術】

【0002】

近年、TVカメラやCCDカメラ等の画像入力手段で被写体や風景等を撮像し、得られた動画像に画像処理を施して、その画像の中から特定の対象、例えば、環境内を移動する物体やその動き等を抽出するための画像処理装置の研究が盛んに行われている。

【0003】

静止画像に対する画像処理としては、各種画像フィルタを図17に示すように木構造状に組み合わせた処理プログラムに基づいて入力画像に画像処理を施す画像処理技術(ACTIT、非特許文献1参照)が開発されている。

【非特許文献1】青木紳也、外1名、「木構造状画像変換の自動構築法ACTIT」、映像情報メディア学会誌、社団法人映像情報メディア学会、1999年、第53巻、第6号、p.888〜894

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、前記のような画像処理装置では、画像処理に用いられる画像フィルタの組み合わせの範囲内でしか画像処理を行うことができず、必ずしも思い通りの画像処理を行うことができない場合がある。また、学習の際に予めどのような種類の画像フィルタをそれぞれ何個ずつ用意するかによって画像処理の最適化が制限を受ける。

【0005】

一方、このような画像処理装置を車両やロボット等に搭載する場合、例えば、汎用コンピュータを用いて画像処理装置を構成し、前記処理プログラムをソフトウエア処理するように構成すると画像処理に時間がかかる。そのため、画像データをリアルタイムに処理すること、すなわち実用的な時間内で処理することが必ずしも容易にはできない。

【0006】

本発明は、前記事情に鑑みてなされたものであり、画像フィルタに制限されずに希望する画像処理回路を構築することを可能とする画像処理手順を学習することができる画像処理装置を提供することを目的とする。さらに、画像処理の処理速度を向上させることが可能な画像処理装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

前記の問題を解決するために、第1の発明は、

画像処理の手順を学習する画像処理装置であって、

関数処理回路が並列に配置された演算ユニットと前記各関数処理回路に入力するデータを選択する選択器とからなる学習ユニットと、

前記学習ユニットによる演算の順序を最適化する学習手段とを備え、

前記学習ユニットは、複数個が直列に連結され、

前記複数の学習ユニットの各選択器は、画像処理の手順を示す選択信号に従って各関数処理回路に入力するデータを選択し、

前記学習手段は、各学習ユニットの選択器に割り当てる前記選択信号を学習により最適化することを特徴とする。

【0008】

第2の発明は、第1の発明の画像処理装置において、前記学習ユニットは、自らに属する各選択器からそれぞれに対応する関数処理回路へのデータの入力をクロック信号に合わせ同期させて行うことを特徴とする。

【0009】

第3の発明は、第1または第2の発明の画像処理装置において、前記学習手段は、各学習ユニットの選択器に割り当てる前記選択信号の列を遺伝子とし、画像処理により得られるべき目標画像を教師画像として遺伝的アルゴリズムの手法に基づいて学習を行うことを特徴とする。

【0010】

第4の発明は、第3の発明の画像処理装置において、前記学習手段は、前記遺伝子が前記関数処理回路に用いられる定数を含み、前記学習により前記定数の最適化を同時に行うことを特徴とする。

【0011】

第5の発明は、第3または第4の発明の画像処理装置において、前記学習手段は、前記学習において、教師画像である画像処理により得られるべき目標画像と演算により算出された出力画像との各画素の輝度値の差に基づいて評価値を算出することを特徴とする。

【0012】

第6の発明は、第3から第5の発明のいずれかの画像処理装置において、前記学習手段は、前記学習において、演算を行う前記関数処理回路の数に基づいて評価値を算出することを特徴とする。

【0013】

第7の発明は、第3から第6の発明のいずれかの画像処理装置において、

前記関数処理回路は、入力されたデータを1クロック分遅延させる機能を有する遅延回路を含み、

前記学習手段は、前記学習において、前記遅延回路しか演算を行わない学習ユニットの数に基づいて評価値を算出することを特徴とする。

【0014】

第8の発明は、第7の発明の画像処理装置において、前記学習手段は、算出した最適化された前記選択信号から前記遅延処理の演算しか行わない学習ユニットによる演算処理に対応する信号部分を削除して新たに最適化された選択信号を再構成して出力することを特徴とする。

【0015】

第9の発明は、第3から第8の発明のいずれかの画像処理装置において、前記学習手段は、前記教師画像中から任意に選択された所定個数の画素について評価値の算出を行うことを特徴とする。

【0016】

第10の発明は、第3から第8の発明のいずれかの画像処理装置において、前記学習手段は、前記教師画像の輝度値が0でない画素の中から任意に選択された所定個数の画素について評価値の算出を行うことを特徴とする。

【0017】

第11の発明は、第1から第10の発明のいずれかの画像処理装置であって、

前記画像処理装置の学習手段により最適化された前記選択信号に従って画像処理を行わせると遅延処理の演算しか行わない学習ユニットがある場合には、当該学習ユニットによる演算処理を削除し、当該学習ユニットの処理下流側に遅延処理以外の演算を行う他の学習ユニットがある場合には当該他の学習ユニットの演算処理を上流側の学習ユニットに移して、遅延処理以外の演算を行う最下流の学習ユニットから出力される処理結果を出力することを特徴とする。

【0018】

第12の発明は、第1から第10の発明のいずれかの画像処理装置であり、最適化された前記選択信号に基づいて画像処理を行う画像処理装置であって、

前記画像処理装置が前記選択信号に従って画像処理を行った場合に遅延処理の演算しか行わない学習ユニットに対応する演算処理があるときは、前記選択信号から当該演算処理に対応する信号部分を削除して選択信号を再構成し、再構成された選択信号に基づいて前記関数処理回路による画像処理回路を構築することを特徴とする。

【発明の効果】

【0019】

第1の発明によれば、従来の画像処理装置のような画像フィルタの組み合わせではなく加算器のような単純な関数処理回路の組み合わせで構築された画像処理回路に対する画像処理手順を提供することができる。そのため、その手順に従えば、画像処理の種類が画像フィルタやその組み合わせに制限されずに思い通りの画像処理を行うことが可能な画像処理回路を構築することが可能となる。

【0020】

また、希望する画像処理を学習するために複数の教師画像に基づいて学習を行うことで、希望する画像処理をさらに精度良く行うことができる画像処理回路を構築するための画像処理手順を提供することが可能となる。

【0021】

さらに、第1の発明に係る画像処理装置により出力される最適化された選択信号に従えば、処理プログラムによるソフトウエア処理と同等の画像処理をハードウエア処理で行ってクロック単位で演算処理を行うようにすることができるため、画像処理装置の画像処理速度を飛躍的に向上させることが可能となり、画像データをリアルタイムに処理することが可能となる。

【0022】

第2の発明によれば、前記第1の発明の効果に加え、関数処理回路の演算処理をクロック信号に合わせて同期させて行うことが可能となるため、関数処理回路による処理時間の違いに起因して演算処理に乱れが生じることを防止することが可能となり、的確なタイミングで演算処理を行って最適化された選択信号を確実に獲得することが可能となる。

【0023】

第3の発明によれば、前記各発明の効果に加え、遺伝的アルゴリズムの手法に基づく学習により最適化された選択信号を得ることで、人為的に最適化された選択信号を構成する場合と比較して、効率良くかつより的確に最適化された選択信号を獲得することが可能となる。

【0024】

第4の発明によれば、前記各発明の効果に加え、遺伝的アルゴリズムの手法に基づいて関数処理回路の定数の最適値を容易にかつ的確に獲得することが可能となる。

【0025】

第5の発明によれば、前記各発明の効果に加え、選択信号の最適化において、教師画像と出力画像との各画素の輝度値の差に基づいて評価値を算出することで、入力画像に演算処理を施して教師画像をより良く再現し、希望する画像処理を的確に行うことを可能にする最適化された選択信号を獲得することが可能となる。

【0026】

第6の発明によれば、前記各発明の効果に加え、選択信号の最適化において、演算を行う関数処理回路の数に基づいて評価値を算出し、使用する関数処理回路の数が少ない選択信号に対してより良い評価を与えることで、出力される最適化された選択信号をリソースの数を低減可能な選択信号として出力することが可能になる。

【0027】

第7の発明によれば、前記各発明の効果に加え、選択信号の最適化において、遅延回路しか演算を行わない学習ユニットの数に基づいて評価値を算出し、そのような学習ユニットを多く含む選択信号に対してより良い評価を与えることで、最適化された選択信号には遅延回路しか行わない学習ユニットによる演算処理が多数含まれたものとなる。

【0028】

そのため、装置への実装の段階で、例えば、遅延回路しか演算を行わない学習ユニットによる演算処理を削除することで削除された学習ユニット分だけ処理時間をさらに短縮することが可能となり、処理速度をさらに向上させることが可能となる。また、削除された学習ユニット分だけ少ないリソースで画像処理回路を構成することが可能となる。

【0029】

第8の発明によれば、遅延回路しか行わない学習ユニットによる演算処理が多数含まれた最適化された選択信号からそのような学習ユニットに対応する信号部分を削除して新たに最適化された選択信号を再構成することで、再構成された選択信号が実装された装置では、削除された学習ユニット分だけ処理時間をさらに短縮することが可能となり、処理速度をさらに向上させることが可能となる。また、削除された学習ユニット分だけ少ないリソースで画像処理回路を構成することが可能となる。このように第8の発明では、前記第7の発明の効果がより的確に発揮される。

【0030】

第9の発明によれば、学習手段における学習の際、例えば、256×256画素の画像に対して最初から全画素について遺伝的アルゴリズムの手法を適用すると探索範囲が非常に大きくなり最適解に収束するまでの時間が非常に長くかかるが、少数の画素に限定して個体を進化させることで、少数の画素に対しても評価が低いような選択信号を有する個体が早急に淘汰される。

【0031】

そのため、前記各発明の効果に加え、最終的に全画素について遺伝的アルゴリズムの手法を適用する際には、既に評価値がある程度高い個体が比較的多数存在する状態となり、最適解への収束の速度を向上させることが可能となる。

【0032】

第10の発明によれば、学習手段における学習において、入力に対して出力を与えないような意味のない選択信号を有する個体が生成されることを許す場合、意味のない選択信号からの出力画像の各画素の輝度値は0になる。一方、前記第9の発明のように教師画像の全画素中から選択された少数の画素の輝度値が0であると、意味のない個体が最高の評価を得てしまうため、意味があり評価値が高い個体を多数生き残らせて最適解への収束の速度を向上させるという目的が達成できなくなる。

【0033】

そのため、前記のような場合には、教師画像の輝度値が0でない画素の中から少数の画素を任意に選択して評価値の算出を行うことで、前記第9の発明と同様の効果を得ることが可能となる。

【0034】

第11の発明によれば、画像処理装置において、遅延処理の演算しか行わない学習ユニットによる演算処理を削除し、当該学習ユニットの処理下流側で行われる遅延処理以外の演算を上流側に移すことで、前記各発明の効果が的確に発揮されるとともに、遅延処理の演算しか行わない学習ユニットの演算処理が削除される分だけ処理時間をさらに短縮し、処理速度を向上させることが可能となる。また、削除された学習ユニット分だけ少ないリソースで画像処理回路を構成することが可能となる。

【0035】

第12の発明によれば、前記各発明の効果が的確に発揮されるとともに、最適化された選択信号の中に存在する遅延処理の演算しか行わない学習ユニットに対応する演算処理の信号部分を削除して選択信号を再構成し、再構成された選択信号に基づいて組み立てられた関数処理回路によって画像処理を行うことで、前記削除された信号部分の分だけより少ないリソースで画像処理回路を構成することが可能となる。また、その分処理時間をさらに短縮することが可能となり、処理速度を向上させることが可能となる。

【発明を実施するための最良の形態】

【0036】

以下、本発明に係る画像処理装置の実施の形態について、図面を参照して説明する。

【0037】

[第1の実施の形態]

第1の実施形態では、画像処理装置がFPGA(Field Programmable Gate Array)評価用ボード(ALTERA社製)上に構築される場合について述べるが、これに限定されない。

【0038】

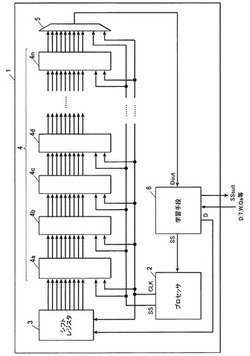

本実施形態に係る画像処理装置1は、画像処理の手順を自律的に学習する装置である。画像処理装置1は、図1に示すように、プロセッサ2と、シフトレジスタ3と、複数の学習ユニット4と、マルチプレクサ5と、学習手段6とを備えている。

【0039】

本実施形態では、画像処理の対象となる画像データは、画像を構成する各画素の0〜255の256階調の輝度階調に補正された輝度値のデータであり、以下、個々の画素の輝度値のデータを画素データという。また、本実施形態では、画像のサイズが256×256画素であり、また、画像中の3×3画素を対象に画像処理を行う場合について説明する。

【0040】

また、本実施形態では、画像のデータは、原画像の水平方向に延びる1画素幅のライン上を左端の画素から右方向に、かつ、最上端のラインから順次下方のラインに向かう順番で1画素ずつ入力され画像処理される場合について述べる。

【0041】

プロセッサ2は、シフトレジスタ3や学習ユニット4、マルチプレクサ5にクロック信号CLKを送信してそれらをクロックに同期させて動作させるようになっている。また、各学習ユニット4とマルチプレクサ5に後述する学習手段6から送信されてくる選択信号SSを送信するようになっている。

【0042】

シフトレジスタ3はラインバッファ機能を有し、少なくとも514個の画素データを一時保存できるようになっている。シフトレジスタ3には、図2(A)〜(C)に示すように、画素データがクロックごとに学習手段6から順次入力されるようになっており、シフトレジスタ3はこれらの画素データを順々にシフトさせるようになっている。なお、図2(A)〜(C)で、00、01、02はそれぞれ画像の第0行第0列目、第0行第1列目、第0行第2列目の画素データを表している。

【0043】

シフトレジスタ3は、先頭の画素データが図3に示すように513番地にシフトしたクロックタイミングで、256番地の画素データを中心に0、1、255、256、257、511、512、513の各番地の画素データとこのクロックタイミングで入力された画素データとの9個の画素データを学習ユニット4に送信するようになっている。

【0044】

また、シフトレジスタ3は、次のクロックタイミングでそれらの画素データをシフトさせるとともに、シフトされた前記番地の8個の画素データとこのクロックタイミングで入力された画素データとの9個の画素データを学習ユニット4に送信するようになっている。以下、この動作を繰り返す。

【0045】

なお、256×256画素の画像中のn×n画素を対象に画像処理を行う場合には、図4に示すように、シフトレジスタ3は少なくとも257×(n−1)個の画素データを一時保存できる容量を有するものであることが望ましい。

【0046】

学習ユニット4は、図5に示すように、関数処理回路F1〜F9が並列に配置された演算ユニット41と、演算ユニット41の各関数処理回路F1〜F9に入力する画像データを選択する選択器42とで構成されている。演算ユニット41の各関数処理回路F1〜F9および選択器42にはそれぞれプロセッサ2からのクロック信号CLKが入力されるようになっている。

【0047】

演算ユニット41の関数処理回路Fには、2入力の加算器ADDRや減算器SUB、1入力の乗算器MULTや絶対値ABS、遅延回路DFF、含意素子IF_THEN等の単純な演算を行う関数処理回路が用いられている。

【0048】

ここで、本実施形態では、乗算器MULTは入力されたデータを定数倍するものであり、その定数は学習手段6における学習で最適化されるようになっている。また、本実施形態では、定数は各学習ユニット4で同一の値とされているが、異なった値としてもよい。また、遅延回路DFFにはディレイフリップフロップ(Delay flip-flop)が用いられており、1クロックの遅延が行われるようになっている。さらに、本実施形態では、含意素子IF_THENは入力されるデータの値が255より大きい場合には255にするようになっている。

【0049】

以下、演算ユニット41の関数処理回路Fの構成例として、図6に示すように、加算器ADDRを4個、減算器SUB、乗算器MULT、絶対値ABS、遅延回路DFF、含意素子IF_THENをそれぞれ1個ずつの計9個の関数処理回路を組み合わせる場合について述べる。しかし、関数処理回路Fの構成はこれに限定されず、用いられる関数処理回路Fの種類や数は適宜設定される。また、学習ユニット4の数も適宜設定される。

【0050】

選択器42には、学習手段6からプロセッサ2を経由して送信される選択信号SSが入力されるようになっている。また、本実施形態では、選択器42には、シフトレジスタ3や処理の上流側の学習ユニット4から9個のデータが入力され、2入力の4個の加算器ADDRおよび減算器SUBにそれぞれ2個ずつ、および1入力の乗算器MULT、絶対値ABS、遅延回路DFF、含意素子IF_THENにそれぞれ1個ずつデータを入力するために計14個のデータを出力するようになっている。

【0051】

選択器42の構造は、図6の円内に示される拡大図のように、1個の出力につきそれぞれ1個のマルチプレクサ様の素子が対応付けられており、素子により入力された9個のデータの中から1つのデータが選択されて出力され、対応する関数処理回路Fに入力されるようになっている。本実施形態では、選択器42には14個のマルチプレクサ様の素子が内蔵されている。

【0052】

また、選択器42のそれぞれの素子は、学習手段6から送信される選択信号SSに従って対応する関数処理回路に入力するデータを選択し、或いは選択せずに関数処理回路にデータを入力しないようになっている。

【0053】

選択信号SSは、各学習ユニット4に画像処理の手順を示すための信号であり、本実施形態では、例えば図7に示すように、各学習ユニット4の選択器42の各素子およびマルチプレクサ5が選択すべき入力データ番号が列記された選択信号の列である。各学習ユニット4の選択器42は選択信号SSの中から自らが指定されている数値部分を読み出して、各素子に選択信号を予め割り当てるようになっている。なお、図7の選択信号SS中、−で示される数値部分は選択信号が割り当てられていないことを示しており、対応する素子からはデータが出力されない。

【0054】

図7に示した選択信号SSの例では、選択信号SSが入力されると、学習ユニット4aの選択器42aは1番目の素子に0、2番目の素子に1、…、8番目の素子に8、11番目の素子に4をそれぞれ割り当て、学習ユニット4bの選択器42bは1番目の素子に0、…、4番目の素子に3、13番目の素子に6をそれぞれ割り当ててセットアップする。

【0055】

各素子は、図8に示すように、このようにして予め割り当てられた選択信号に従ってそれぞれの番号の入力データを選択して対応する関数処理回路Fにデータを送信するようになっている。このように、各学習ユニット4の選択器の各素子に選択信号が割り当てられることで、各学習ユニット4による画像処理の手順が決定される。

【0056】

また、選択器42は、プロセッサ2から送信されるクロック信号CLKの立ち上がりに合わせて各素子からデータを出力させて対応する各関数処理回路Fにデータを同期させて入力し、演算ユニット41の各関数処理回路Fは、次のクロック信号CLKの立ち上がりで同時に演算を開始して演算後のデータを出力するようになっている。

【0057】

なお、図1に示した複数の学習ユニット4a〜4nは、すべて図5や図6に示した学習ユニット4と同一の構成を有している。そして、選択信号SSによって処理に供される関数処理回路Fが選択され、それぞれ異なる演算を行うようになっている。

【0058】

マルチプレクサ5には、処理の最下流の学習ユニット4nからの出力データが入力されるようになっており、マルチプレクサ5は、学習手段6からプロセッサ2を経由して送信される選択信号SSに従って入力されたデータの中からデータを選択して出力するようになっている。

【0059】

学習手段6は、図1に示すように、学習ユニット4a〜4nの各選択器に割り当てる選択信号SSを予め学習により最適化し、最適化された選択信号SSsuitを出力するように構成されている。

【0060】

本実施形態では、学習は、遺伝的アルゴリズムの手法に基づいて行われるようになっており、学習手段6には、学習に用いられる図9に示すような原画像Dと教師画像としての画像処理により得られるべき図10に示すような目標画像Tが入力されるようになっている。また、評価値の算出の際に重み付けするための図11に示すような重み画像Wを入力しておくことも可能である。

【0061】

なお、目標画像Tおよび重み画像Wは原画像Dに基づいて予め作成される。図10に示した目標画像Tは、抽出領域EXに属する画素の輝度値は255に、非抽出領域NEに属する画素の輝度値は0になるように作成されている。また、図11に示した重み画像Wは、目標画像Tの抽出領域EXと非抽出領域NEに対応してそれぞれの領域で重みwがそれぞれの面積比の逆数の比になるように作成されるようになっている。

【0062】

原画像D、目標画像Tおよび重み画像Wは学習手段6の図示しない記憶手段に保存されるようになっている。

【0063】

一方、本実施形態に係る学習手段6では、まず、教師画像である目標画像T中の10画素等の所定個数の画素に対して学習を行い、その後、目標画像Tの全画素に対して学習を行うように構成されている。

【0064】

また、個体の評価を、出力画像Doutと目標画像Tとの各画素の輝度値の差のほか、出力画像Doutを得るために用いた関数処理回路の数や、遅延回路しか演算を行わない学習ユニットを除いた実質的な演算を行う学習ユニットの数に基づいて判断するように構成されている。

【0065】

図12は、本実施形態に係る学習手段の構成を示すブロック図である。学習手段6は、初期個体生成手段61と、評価値算出手段62と、終了判定手段63と、親選択手段64と、交叉手段65と、突然変異手段66とを備えている。

【0066】

初期個体生成手段61は、学習開始指示に応じて、図7に示したような各学習ユニット4a〜4nの各選択器およびマルチプレクサ5に割り当てる選択信号SSの列を遺伝子とする個体をランダムに例えば100個体等の一定数生成させるようになっている。また、初期個体生成手段61は、各個体ごとに乗算器MULTで用いられる定数をランダムに生成させて選択信号SSのヘッダに書き込むようになっている。定数を各学習ユニット4a〜4nで個別に設定する場合には、各学習ユニット4a〜4nのそれぞれについて定数をランダムに生成させてヘッダに書き込む。

【0067】

個体を生成し或いは交叉させ突然変異させる際には、意味のない個体が生じるような生成や交叉、突然変異を行わないように予め設定しておくことが好ましい。ここで、意味のない個体とは、その個体に含まれる選択信号SSに従うと、例えば、学習ユニット4の関数処理回路Fで演算されて出力されたデータが次の学習ユニット4での演算に用いられなかったり、学習ユニット4の関数処理回路Fからデータの出力がないにもかかわらずその関数処理回路Fからの出力を次の学習ユニット4の関数処理回路Fに入力するような個体である。また、最終の学習ユニット4nからの出力データをマルチプレクサ5が誤った選択をして出力しないような個体も意味のない個体とされる。

【0068】

評価値算出手段62は、図13に示すように、入力された教師画像である目標画像Tの画像中から例えば10個の画素Pをランダムに選択する。また、図14に示すように、目標画像T中から選択された10個の画素Pのそれぞれについて、原画像D中から対応する位置の画素を抽出し、その画素およびその周囲の8画素の計9画素の画素データをそれぞれ画素データの組COMとして抽出するようになっている。なお、図13や図14では、画素が実際より大きく表現されている。また、10個の画素Pは各世代ごとにランダムに選択される。

【0069】

評価値算出手段62は、続いて、初期個体生成手段61から送信されてきた全個体中の1つの個体について、それに含まれる選択信号SSをプロセッサ2を介して各学習ユニット4a〜4nに送信して各選択器42の各素子をセットアップする。また、各学習ユニット4a〜4nは、ヘッダから乗算器MULTの定数を読み出して、自らの演算ユニット41の乗算器MULTをセットアップする。

【0070】

そして、評価値算出手段62は、前記画素データの組COMの9個の画素データをシフトレジスタ3を介さずに1組ずつ直接学習ユニット4aに入力する。学習ユニット4a〜4nでは9個の画素データの入力に対して演算が行われ、マルチプレクサ5から1つの画素画像Doutの画素データが出力されて評価値算出手段62に入力される。

【0071】

評価値算出手段62は、このシミュレーション演算を組COMのすべてについて行い、その個体について、目標画像Tと出力画像Doutとの各画素の輝度値の差に基づく評価値Q1を下記(1)式に従って算出するようになっている。

【0072】

【数1】

【0073】

ここで、本実施形態では、前記(1)式のmは10であり、Tkはk番目の画素Pの輝度値、Doutkは対応するk番目の組COMに基づいて算出された出力画像Doutの画素の輝度値を表す。

【0074】

なお、前述した重み画像Wを用いて下記(2)式に従って評価値Q1を重み付けして算出することも可能である。

【0075】

【数2】

【0076】

ここで、Wkは、目標画像Tのk番目の画素Pに対応する重み画像W上の位置の画素の輝度値を表す。m、Tk、Doutkについては前記(1)式と同様である。

【0077】

また、評価値算出手段62は、同時に、個体に含まれる選択信号SSから出力画像Doutを得るために用いた関数処理回路の数Mおよび遅延回路DFFしか演算を行わない学習ユニットの数Nを算出し、下記(3)式および(4)式に従って評価値Q2、Q3を算出するようになっている。なお、下記(3)式のFNは本実施形態における関数処理回路Fの総数を表し、下記(4)式のUNは本実施形態における学習ユニット4の総数を表す。

【0078】

【数3】

【0079】

なお、遅延回路DFFしか演算を行わない学習ユニットとは、例えば図15に示すような学習ユニットをいい、図8に示した学習ユニット4bのように遅延回路DFFの演算を行うが他の関数処理回路Fでも演算を行う学習ユニットは含まれない。また、遅延回路DFFを複数備える学習ユニットにおいて複数の遅延回路DFFで演算が行われ他の関数処理回路Fでは演算が行われないような学習ユニットは遅延回路DFFしか演算を行わない学習ユニットに含まれる。さらに、図8において、例えば学習ユニット4aでは遅延回路DFFしか演算を行わずその出力データに対して学習ユニット4bの加算器ADDRによる演算が行われるような場合には、学習ユニット4aが遅延回路DFFしか演算を行わない学習ユニットに含まれる。

【0080】

評価値算出手段62は、評価値Q2、Q3を評価値Q1とともにそれぞれ各個体に対応付けるようになっている。評価値算出手段62は、以上のようにして100個の個体すべてについて評価値Q1、Q2、Q3を算出するようになっている。

【0081】

終了判定手段63は、評価値算出手段62から送信された各個体とメモリ67にエリート保存されている個体があればそれを含めてすべての個体の中で評価値Q1が目標評価値である1に達した個体がなければ、各個体を親選択手段64に送信するようになっている。

【0082】

親選択手段64は、各個体の中で評価値Q1が最も高い個体をエリート保存してメモリ67に隔離するとともに、その個体のコピーと残りの個体との中から評価値Q1に基づいてトーナメント選択により次世代に残すべき100個体の処理プログラムの選択およびそれらの処理プログラムの増殖を行うようになっている。なお、ルーレット選択や期待値選択、ランキング選択等の他の方法で親選択を行うことも可能である。

【0083】

交叉手段65では、親選択手段64で選択され増殖された親個体について2個体ずつ対にして、それぞれの個体対ごとにランダムに選ばれた交叉部分で所定の割合で互いに交叉させて、子個体を生成させるようになっている。また、突然変異手段66では、各個体ごとに所定の割合で選択信号SSの数値の変更や選択信号SSのヘッダ部分に書き込まれた乗算器MULTの定数の変更等が行われるようになっている。

【0084】

このようにして、評価値Q1が1の個体が現れるまで前記シミュレーション演算や世代交代が繰り返されるようになっている。

【0085】

終了判定手段63は、評価値Q1が目標評価値である1の個体が現れると、評価値算出手段62に対して目標画像Tの画像中からランダムに選択する画素Pの数を100個に増やすように指示を出すようになっている。

【0086】

そのため、評価値算出手段62では、次世代からは、目標画像T中から選択された100個の画素Pのそれぞれについて、原画像D中から対応する位置の画素を抽出し、その画素およびその周囲の8画素の計9画素の画素データをそれぞれ画素データの組COMを100組抽出するようになっている。そして、その100組についてシミュレーション演算を行い、前記(1)式または(2)式中のnを100として各個体について評価値Q1を新たに算出するようになっている。

【0087】

このように、終了判定手段63は、評価値Q1が設定された目標評価値に達した個体が現れると、目標画像T中からランダムに選択する画素数を増やすように評価値算出手段62に指示を送るようになっている。画素数はこの後、例えば1000画素、10000画素のように増加され、最終的には原画像Dの全画素数である256×256=65536画素まで増加される。また、目標評価値は、例えば10画素では1、100画素では0.95、1000画素では0.9、10000画素では0.85のように徐々に小さい値が設定されるようになっている。

【0088】

なお、目標画像T中からランダムに選択する画素数を増やす基準を、例えば設定された世代数ごととすることも可能である。また、画素数が原画像Dの全画素数まで増加された段階で、評価値算出手段62は、原画像Dの水平方向に延びる1画素幅のライン上を左端の画素から右方向に、かつ、最上端のラインから順次下方のラインに向かう順番で1画素ずつ画素データをシフトレジスタ3に入力する。シフトレジスタ3からは9個の画素データが順次学習ユニット4aに入力される。

【0089】

一方、学習手段6は、終了判定手段63により評価値算出手段62におけるシミュレーション演算の範囲が原画像Dの全画素まで拡大され、評価値Q1が例えば0.8等に設定された目標評価値以上の個体が現れると、エリート保存の基準と終了判定の基準を変更するようになっている。

【0090】

具体的には、本実施形態では、親選択手段64は、メモリ67に保存されているエリート個体の評価値Q1、Q2、Q3のいずれに対してもそれらに等しいかそれらを上回る評価値Q1、Q2、Q3を有する個体が現れない限りエリートを更新しないようになっている。すなわち、評価値Q1がエリート以上の個体が現れても、その個体の評価値Q2或いは評価値Q3がエリートの評価値Q2或いは評価値Q3より小さければエリートとしないようになっている。

【0091】

また、終了判定手段63は、終了判定の基準を変更するようになっている。本実施形態では、終了判定手段63は、原画像Dの全画素に対するシミュレーション演算で評価値Q1が0.8以上の個体が現れた段階で、予め設定された最終的な目標評価値Qa、Qb、Qc以上の評価値Q1、Q2、Q3を有する個体が現れることを最終的な終了判定の基準として設定するようになっている。なお、この他にも、例えば、予め設定された世代数に達した時点で終了することを最終的な終了判定の基準として設定するように構成することも可能である。

【0092】

終了判定手段63は、この最終的な終了判定基準が満たされたと判定すると、以上のルーチンを終了するようになっている。そして、終了判定手段63は、最終的な終了判定基準を満した個体からそれに含まれる選択信号SSを抽出し、選択信号SSに遅延処理の演算しか行わない学習ユニットによる演算処理に対応する信号部分があればその信号部分を選択信号SSから削除するようになっている。

【0093】

終了判定手段63は、このようにして再構成した選択信号SSを、各学習ユニット4a〜4nに割り当てるべき最適化された選択信号SSsuitとして出力するようになっている。

【0094】

次に、本実施形態に係る画像処理装置1の作用について説明する。

【0095】

本実施形態の画像処理装置1のプロセッサ2、シフトレジスタ3、学習ユニット4およびマルチプレクサ5の作用については前記構成で述べたとおりであるので説明を省略する。

【0096】

学習手段6は、まず、初期個体生成手段61が生成した個体の中から、前記(1)式または(2)式に従って算出される評価値Q1が低い個体すなわち教師画像である目標画像Tと出力画像Doutとの各画素の輝度値の差が大きい個体を淘汰するために、目標画像T上の限定された数の画素を対象として進化過程を進める。

【0097】

このように少数の画素に限定して個体を進化させることで、目標画像T上の限定された数の画素を対象としても目標画像Tとの輝度値の差が大きい出力画像Doutしか出力できないような選択信号SSを有する個体が早急に淘汰される。

【0098】

従って、終了判定手段63が評価値算出手段62におけるシミュレーション演算の範囲を原画像Dの全画素まで拡大する際には、既に目標画像Tとの距離が近い出力画像Doutを出力させ得る選択信号SSを含む個体が比較的多数存在する状態となり、最適解への収束の速度が向上する。

【0099】

一方、学習手段6は、この時点で終了判定条件を切り替え、評価値Q1が例えば0.8等に設定された目標評価値以上の個体が現れた段階で、評価値Q1のみによる評価を離れて評価値Q2や評価値Q3をも考慮して最適解を探索するようになる。

【0100】

評価値Q2は、前記(3)式に示されるように、出力画像Doutを得るために用いた関数処理回路の数Mが少ないほど大きな値を取る。従って、評価値Q2が高い値であるということは、その個体に含まれる選択信号SSによれば、より少ないリソースすなわち関数処理回路で画像処理回路を構成することができることを意味する。

【0101】

また、評価値Q3は、前記(4)式に示されるように、遅延回路DFFしか演算を行わない学習ユニットの数Nが多いほど大きな値を取る。従って、評価値Q3が高い値であるということは、その個体に含まれる選択信号SSによれば、より多くの遅延回路DFFしか演算を行わない学習ユニットが含まれる画像処理回路が構成されることを意味する。

【0102】

遅延回路DFFしか演算を行わない学習ユニットによる演算処理は、実装段階ではいわば省略してもよい演算処理である。また、学習ユニットの数が増えるほど遅延回路DFFしか演算を行わない学習ユニットの数も増える可能性が高くなり、省略できる演算処理の数も増える可能性が高くなる。

【0103】

そのため、本実施形態のように、最終的な終了判定基準を満たした選択信号SSからさらに遅延回路DFFしか演算を行わない学習ユニットに対応する信号部分を削除して新たに最適化された選択信号SSsuitを再構成することで、削除された学習ユニット分だけ処理時間が短縮され、処理速度が向上する。また、削除された学習ユニット分だけ少ないリソースで画像処理回路を構成することが可能となる。

【0104】

前述したように、本実施形態では1個の学習ユニットの処理あたり選択器42と演算ユニット41の2クロックを要するから、結局、削除された学習ユニットの個数の2倍のクロック数分の処理時間の短縮と処理速度の向上を図ることができる。また、本実施形態では1個の学習ユニットあたり9個の関数処理回路が用いられているから、その分リソースを減らすことができる。

【0105】

評価値Q2、Q3はそれぞれ前記のような意味を持つものであり、本実施形態では、出力画像Doutと目標画像Tとの輝度値の差を小さくすることを前提としてリソースの低減と処理速度の向上との両方を達成することを目的として、前述したような厳しい最終的な終了判定の基準を設定した。しかし、リソースの数を減らすことを重視して評価値Q2が高い個体を新たなエリートとしたり、処理時間の短縮や処理速度を向上を優先ために評価値Q3が高い個体をエリートとして更新するように構成することも可能である。

【0106】

以上のように、本実施形態に係る画像処理装置1によれば、まず、従来の画像処理装置のような画像フィルタの組み合わせではなく、加算器ADDRのような単純な関数処理回路Fの組み合わせで構築された画像処理回路に対する画像処理手順を提供することができるため、その手順に従えば、画像処理の種類が画像フィルタやその組み合わせに制限されず、思い通りの画像処理を行うことが可能な画像処理回路を構築することが可能となる。

【0107】

また、本実施形態では、教師画像として目標画像Tを1種類だけ与えて学習を行う場合について述べたが、希望する画像処理を学習するためにさらに複数の教師画像に基づいて学習を行うことで、希望する画像処理をさらに精度良く行うことができる画像処理回路を構築するための画像処理手順を提供することが可能となる。

【0108】

さらに、本実施形態に係る画像処理装置1により出力される最適化された選択信号SSsuitに従えば、処理プログラムによるソフトウエア処理と同等の画像処理をハードウエア処理で行ってクロック単位で演算処理を行うようにすることができるため、画像処理速度を飛躍的に向上させることが可能となり、画像データをリアルタイムに処理することが可能となる。

【0109】

また、選択信号SSの最適化において、使用する関数処理回路Fの数が少ない選択信号に対してより良い評価を与えることで、出力される最適化された選択信号SSsuitをリソースの数を低減可能な選択信号として出力することが可能になる。

【0110】

また、遅延回路DFFしか行わない学習ユニットは実装段階では省いてよい演算処理であるから、選択信号SSの最適化において、遅延回路DFFしか行わない学習ユニットを多く含む選択信号に対してより良い評価を与えることで、最終的な終了判定基準を満たした選択信号SSには遅延回路DFFしか行わない学習ユニットによる演算処理が多数含まれたものとなる。

【0111】

そのため、そのような選択信号SSから遅延回路DFFしか演算を行わない学習ユニットに対応する信号部分を削除して新たに最適化された選択信号SSsuitを再構成することで、削除された学習ユニット分だけ処理時間をさらに短縮することが可能となり、処理速度を向上させることが可能となる。また、削除された学習ユニット分だけ少ないリソースで画像処理回路を構成することが可能となる。

【0112】

なお、学習手段6における遺伝的アルゴリズムを用いた学習において、個体の生成や交叉、突然変異の際に前述したような意味のない個体が生成等されないような制限を加えない場合には、学習ユニット4a〜4nに画素データを入力してもマルチプレクサ5からデータが出力されず、結果的に輝度値が0のデータが出力されたことと同じになる場合がある。

【0113】

このような場合に、教師画像である目標画像Tから任意に例えば10個の画素を選択してそれらがすべて輝度値0の画素であると、意味のない個体の評価値Q1が1という最高の評価を得てしまうため、目標画像Tから少数画素を選択して進化過程を進め意味があり評価値が高い個体を多数生き残らせて最適解への収束の速度を向上させるという目的が達成できなくなる。

【0114】

そのため、前記のような制限を設けずに目標画像Tから少数の画素を選択して進化過程を進める場合には、目標画像Tの輝度値が0でない画素の中から少数の画素を任意に選択して評価値Q1の算出を行うように構成することが好ましい。

【0115】

また、学習手段6の終了判定手段63において、選択信号SSから遅延処理の演算しか行わない学習ユニットによる演算処理に対応する信号部分の削除に加えて、さらに、余分な関数処理回路Fを削除するように構成すれば、より少ないリソースで画像処理回路を構成することが可能となる。

【0116】

具体的には、例えば、本実施形態のように1個の学習ユニットにつき4個の加算器ADDRを設けたが、最適化された選択信号SSsuitを解析して1個の学習ユニットにつき最大で3個の加算器ADDRしか使用していない場合には、選択信号SSsuitを3個の加算器ADDRを用いるように改変して新たな最適化された選択信号SSsuitとすることで、使用する加算器ADDRの数を低減させることが可能となる。

【0117】

さらに、本実施形態では、目標画像Tとして、抽出領域EXの画素の輝度値が255、非抽出領域NEの画素の輝度値が0の画像の場合を示したが、目標画像Tをこのような2値的な画像として作成する必要はなく、各画素が0〜255の輝度値を有する画像として作成することが可能である。

【0118】

また、本実施形態では、原画像Dすなわち学習ユニット4a〜4nの演算処理に入力される画像が1種類の画像である場合について述べたが、この他にも、例えば、2種類の画像を入力してその2種類の画像に対して加算や減算等を行うように構成することも可能である。

【0119】

例えば、2種類の画像を入力するように構成する場合には、本実施形態のシフトレジスタ3を2つ設け、2つのシフトレジスタから出力される18個の画素データを学習ユニット4aに入力するように構成する。また、学習ユニット4の演算ユニット41の関数処理回路Fを計18個備えるようにし、最終的に学習ユニット4nから出力される18個のデータから1個のデータをマルチプレクサ5で選択して出力するように構成する。

【0120】

[第2の実施の形態]

次に、前記第1の実施形態に係る画像処理装置1を改良した画像処理装置について説明する。第1の実施形態と同様の機能を奏する部材については同一の符号を付して説明する。

【0121】

第2の実施形態に係る画像処理装置10は、図16に示すように、基本的には第1の実施形態に示した画像処理装置1の構成と同様であるが、学習手段6での学習により得られた最適化された選択信号SSsuitがプロセッサ2に出力されるようになっていて、プロセッサ2から各学習ユニット4a〜4nに送られて各学習ユニット4a〜4nがセットアップされるようになっている。

【0122】

また、シフトレジスタ3には、外部から画像データDinが入力されるようになっていて、マルチプレクサ5からの出力が出力データDoutとして外部に出力されるようになっている。さらに、各学習ユニット4a〜4nの出力がすべてマルチプレクサ5に入力されるように配線されている。

【0123】

また、プロセッサ2は、学習手段6から送信されてきた最適化された選択信号SSsuitをチェックして、選択信号SSsuitの中に遅延処理の演算しか行わない学習ユニットによる演算処理に対応する信号部分があればその信号部分を選択信号SSから削除して、最適化された選択信号SSsuitを再構成するようになっている。

【0124】

なお、学習手段6による学習は画像処理装置10の稼動開始前に行われ、画像処理装置10の実稼動中には学習手段6の動作は停止されるようになっている。

【0125】

このように最適化された選択信号SSsuitを再構成することで、遅延処理の演算しか行わない学習ユニットによる演算処理を削除し、その学習ユニットの処理下流側に遅延処理以外の演算処理を行う他の学習ユニットがある場合には当該他の学習ユニットの演算処理を上流側の学習ユニットに移すことが可能となる。

【0126】

そして、遅延処理以外の演算を行う最下流の学習ユニットから出力される処理結果がマルチプレクサ5に送信され、マルチプレクサ5がその学習ユニットからの出力を選択することで出力データDoutが出力される。

【0127】

以上のように、本実施形態に係る画像処理装置10によれば、前記第1の実施形態で述べた画像処理装置1の効果と同様の効果が有効に発揮され、画像データDinをリアルタイムに画像処理することが可能となる。

【0128】

特に、再構成された最適化された選択信号SSsuitにより、遅延処理の演算しか行わない学習ユニットの演算処理を削除して、その処理下流側で行われる遅延処理以外の演算処理をより上流側の学習ユニットで行うことが可能となる。また、遅延処理の演算しか行わない学習ユニットの演算処理を削除して、その出力を直接マルチプレクサ5に入力させることができる。

【0129】

そのため、遅延処理の演算しか行わない学習ユニットの演算処理が削除される分だけ処理時間をさらに短縮することが可能となり、処理速度を向上させることが可能となる。また、削除された学習ユニット分だけ少ないリソースで画像処理回路を構成することが可能となる。

【0130】

また、本実施形態に係る画像処理装置10では、学習手段6の構成がそのまま残されているため、学習手段6で初期個体を新たに生成して別の教師画像に基づいて学習を行って最適化された選択信号SSsuitを得ることで既に学習された画像処理とは異なる種類の画像処理を行うことが可能となり、新たな画像処理の機能を獲得することが可能となる。

【0131】

なお、本実施形態に係る画像処理装置10を、最初に学習された画像処理に専用の装置とする場合には、遅延処理以外の演算処理を行う最終の学習ユニットからの出力のみをマルチプレクサ5に入力するように配線することができる。

【0132】

[第3の実施の形態]

次に、前記第1の実施形態に係る画像処理装置1の改良型として、最適化された選択信号SSsuitを用いて画像処理を行う画像処理装置について説明する。

【0133】

第3の実施形態に係る画像処理装置では、各関数処理回路Fを図1に示した学習ユニットのように構成しない場合もある。しかし、その場合でも、最適化された選択信号SSsuitの中に遅延処理の演算しか行わない学習ユニットによる演算処理に対応する信号部分があるときは、その信号部分を選択信号SSsuitから削除して最適化された選択信号SSsuitを再構成したうえで、再構成された選択信号SSsuitに基づいて加算器ADDRや減算器SUB、乗算器MULT、絶対値ABS、遅延回路DFF、含意素子IF_THEN等を接続して関数処理回路による画像処理回路を構築する。

【0134】

このように再構成された最適化された選択信号SSsuitに基づいて画像処理回路を構築することで、本実施形態に係る画像処理装置では、前記第1の実施形態で述べた画像処理装置1の効果と同様の効果が有効に発揮され、画像データをリアルタイムに画像処理することが可能となる。

【0135】

また、最適化された選択信号SSsuitの中の遅延処理の演算しか行わない学習ユニットによる演算処理に対応する信号部分を削除して画像処理回路を構築できるので、その分処理時間をさらに短縮することが可能となり、処理速度を向上させることが可能となる。また、削除された学習ユニットに対応する分だけ少ないリソースで画像処理回路を構成することが可能となる。

【0136】

さらに、最適化された選択信号SSsuitに基づいてデータの演算処理に関与しない関数処理回路を省いて画像処理回路を構築することができるため、さらに少ないリソースで画像処理回路を構成することが可能となる。

【図面の簡単な説明】

【0137】

【図1】第1実施形態に係る画像処理装置の構成を示すブロック図である。

【図2】シフトレジスタ内での画素データのシフトを説明する図である。

【図3】演算処理の対象となる3×3画素の画素データのシフトレジスタ内での番地を示す図である。

【図4】n×n画素の画素データのシフトレジスタ内での保存位置を示す図である。

【図5】学習ユニットの構成を示すブロック図である。

【図6】本実施形態における学習ユニットの構成例を示すブロック図である。

【図7】選択信号の構成を示す図である。

【図8】図7の選択信号が割り当てられた学習ユニットにおけるデータ処理の流れを説明する図である。

【図9】本実施形態で用いられる原画像を示す図である。

【図10】本実施形態で用いられる目標画像を示す図である。

【図11】重み画像を示す図である。

【図12】学習手段の構成を示すブロック図である。

【図13】目標画像中から選択された画素を表す図である。

【図14】図13の画素に対応する原画像中の画素位置に抽出された画素の組を表す図である。

【図15】遅延回路しか演算を行わない学習ユニットの例を示す図である。

【図16】第2実施形態に係る画像処理装置の構成を示すブロック図である。

【図17】画像フィルタを木構造状に組み合わせた処理プログラムを表す図である。

【符号の説明】

【0138】

1、10 画像処理装置

4 学習ユニット

41 演算ユニット

42 選択器

6 学習手段

F 関数処理回路

DFF 遅延回路

SS 選択信号

SSsuit 最適化された選択信号

CLK クロック信号

T 目標画像

Dout 出力画像

Q1、Q2、Q3 評価値

M 関数処理回路の数

N 遅延回路しか演算を行わない学習ユニットの数

P 教師画像中から選択された画素

【技術分野】

【0001】

本発明は、画像処理装置に係り、特に、画像処理を行うための関数処理回路を選択する選択信号を学習により形成可能な画像処理装置に関する。

【背景技術】

【0002】

近年、TVカメラやCCDカメラ等の画像入力手段で被写体や風景等を撮像し、得られた動画像に画像処理を施して、その画像の中から特定の対象、例えば、環境内を移動する物体やその動き等を抽出するための画像処理装置の研究が盛んに行われている。

【0003】

静止画像に対する画像処理としては、各種画像フィルタを図17に示すように木構造状に組み合わせた処理プログラムに基づいて入力画像に画像処理を施す画像処理技術(ACTIT、非特許文献1参照)が開発されている。

【非特許文献1】青木紳也、外1名、「木構造状画像変換の自動構築法ACTIT」、映像情報メディア学会誌、社団法人映像情報メディア学会、1999年、第53巻、第6号、p.888〜894

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、前記のような画像処理装置では、画像処理に用いられる画像フィルタの組み合わせの範囲内でしか画像処理を行うことができず、必ずしも思い通りの画像処理を行うことができない場合がある。また、学習の際に予めどのような種類の画像フィルタをそれぞれ何個ずつ用意するかによって画像処理の最適化が制限を受ける。

【0005】

一方、このような画像処理装置を車両やロボット等に搭載する場合、例えば、汎用コンピュータを用いて画像処理装置を構成し、前記処理プログラムをソフトウエア処理するように構成すると画像処理に時間がかかる。そのため、画像データをリアルタイムに処理すること、すなわち実用的な時間内で処理することが必ずしも容易にはできない。

【0006】

本発明は、前記事情に鑑みてなされたものであり、画像フィルタに制限されずに希望する画像処理回路を構築することを可能とする画像処理手順を学習することができる画像処理装置を提供することを目的とする。さらに、画像処理の処理速度を向上させることが可能な画像処理装置を提供することを目的とする。

【課題を解決するための手段】

【0007】

前記の問題を解決するために、第1の発明は、

画像処理の手順を学習する画像処理装置であって、

関数処理回路が並列に配置された演算ユニットと前記各関数処理回路に入力するデータを選択する選択器とからなる学習ユニットと、

前記学習ユニットによる演算の順序を最適化する学習手段とを備え、

前記学習ユニットは、複数個が直列に連結され、

前記複数の学習ユニットの各選択器は、画像処理の手順を示す選択信号に従って各関数処理回路に入力するデータを選択し、

前記学習手段は、各学習ユニットの選択器に割り当てる前記選択信号を学習により最適化することを特徴とする。

【0008】

第2の発明は、第1の発明の画像処理装置において、前記学習ユニットは、自らに属する各選択器からそれぞれに対応する関数処理回路へのデータの入力をクロック信号に合わせ同期させて行うことを特徴とする。

【0009】

第3の発明は、第1または第2の発明の画像処理装置において、前記学習手段は、各学習ユニットの選択器に割り当てる前記選択信号の列を遺伝子とし、画像処理により得られるべき目標画像を教師画像として遺伝的アルゴリズムの手法に基づいて学習を行うことを特徴とする。

【0010】

第4の発明は、第3の発明の画像処理装置において、前記学習手段は、前記遺伝子が前記関数処理回路に用いられる定数を含み、前記学習により前記定数の最適化を同時に行うことを特徴とする。

【0011】

第5の発明は、第3または第4の発明の画像処理装置において、前記学習手段は、前記学習において、教師画像である画像処理により得られるべき目標画像と演算により算出された出力画像との各画素の輝度値の差に基づいて評価値を算出することを特徴とする。

【0012】

第6の発明は、第3から第5の発明のいずれかの画像処理装置において、前記学習手段は、前記学習において、演算を行う前記関数処理回路の数に基づいて評価値を算出することを特徴とする。

【0013】

第7の発明は、第3から第6の発明のいずれかの画像処理装置において、

前記関数処理回路は、入力されたデータを1クロック分遅延させる機能を有する遅延回路を含み、

前記学習手段は、前記学習において、前記遅延回路しか演算を行わない学習ユニットの数に基づいて評価値を算出することを特徴とする。

【0014】

第8の発明は、第7の発明の画像処理装置において、前記学習手段は、算出した最適化された前記選択信号から前記遅延処理の演算しか行わない学習ユニットによる演算処理に対応する信号部分を削除して新たに最適化された選択信号を再構成して出力することを特徴とする。

【0015】

第9の発明は、第3から第8の発明のいずれかの画像処理装置において、前記学習手段は、前記教師画像中から任意に選択された所定個数の画素について評価値の算出を行うことを特徴とする。

【0016】

第10の発明は、第3から第8の発明のいずれかの画像処理装置において、前記学習手段は、前記教師画像の輝度値が0でない画素の中から任意に選択された所定個数の画素について評価値の算出を行うことを特徴とする。

【0017】

第11の発明は、第1から第10の発明のいずれかの画像処理装置であって、

前記画像処理装置の学習手段により最適化された前記選択信号に従って画像処理を行わせると遅延処理の演算しか行わない学習ユニットがある場合には、当該学習ユニットによる演算処理を削除し、当該学習ユニットの処理下流側に遅延処理以外の演算を行う他の学習ユニットがある場合には当該他の学習ユニットの演算処理を上流側の学習ユニットに移して、遅延処理以外の演算を行う最下流の学習ユニットから出力される処理結果を出力することを特徴とする。

【0018】

第12の発明は、第1から第10の発明のいずれかの画像処理装置であり、最適化された前記選択信号に基づいて画像処理を行う画像処理装置であって、

前記画像処理装置が前記選択信号に従って画像処理を行った場合に遅延処理の演算しか行わない学習ユニットに対応する演算処理があるときは、前記選択信号から当該演算処理に対応する信号部分を削除して選択信号を再構成し、再構成された選択信号に基づいて前記関数処理回路による画像処理回路を構築することを特徴とする。

【発明の効果】

【0019】

第1の発明によれば、従来の画像処理装置のような画像フィルタの組み合わせではなく加算器のような単純な関数処理回路の組み合わせで構築された画像処理回路に対する画像処理手順を提供することができる。そのため、その手順に従えば、画像処理の種類が画像フィルタやその組み合わせに制限されずに思い通りの画像処理を行うことが可能な画像処理回路を構築することが可能となる。

【0020】

また、希望する画像処理を学習するために複数の教師画像に基づいて学習を行うことで、希望する画像処理をさらに精度良く行うことができる画像処理回路を構築するための画像処理手順を提供することが可能となる。

【0021】

さらに、第1の発明に係る画像処理装置により出力される最適化された選択信号に従えば、処理プログラムによるソフトウエア処理と同等の画像処理をハードウエア処理で行ってクロック単位で演算処理を行うようにすることができるため、画像処理装置の画像処理速度を飛躍的に向上させることが可能となり、画像データをリアルタイムに処理することが可能となる。

【0022】

第2の発明によれば、前記第1の発明の効果に加え、関数処理回路の演算処理をクロック信号に合わせて同期させて行うことが可能となるため、関数処理回路による処理時間の違いに起因して演算処理に乱れが生じることを防止することが可能となり、的確なタイミングで演算処理を行って最適化された選択信号を確実に獲得することが可能となる。

【0023】

第3の発明によれば、前記各発明の効果に加え、遺伝的アルゴリズムの手法に基づく学習により最適化された選択信号を得ることで、人為的に最適化された選択信号を構成する場合と比較して、効率良くかつより的確に最適化された選択信号を獲得することが可能となる。

【0024】

第4の発明によれば、前記各発明の効果に加え、遺伝的アルゴリズムの手法に基づいて関数処理回路の定数の最適値を容易にかつ的確に獲得することが可能となる。

【0025】

第5の発明によれば、前記各発明の効果に加え、選択信号の最適化において、教師画像と出力画像との各画素の輝度値の差に基づいて評価値を算出することで、入力画像に演算処理を施して教師画像をより良く再現し、希望する画像処理を的確に行うことを可能にする最適化された選択信号を獲得することが可能となる。

【0026】

第6の発明によれば、前記各発明の効果に加え、選択信号の最適化において、演算を行う関数処理回路の数に基づいて評価値を算出し、使用する関数処理回路の数が少ない選択信号に対してより良い評価を与えることで、出力される最適化された選択信号をリソースの数を低減可能な選択信号として出力することが可能になる。

【0027】

第7の発明によれば、前記各発明の効果に加え、選択信号の最適化において、遅延回路しか演算を行わない学習ユニットの数に基づいて評価値を算出し、そのような学習ユニットを多く含む選択信号に対してより良い評価を与えることで、最適化された選択信号には遅延回路しか行わない学習ユニットによる演算処理が多数含まれたものとなる。

【0028】

そのため、装置への実装の段階で、例えば、遅延回路しか演算を行わない学習ユニットによる演算処理を削除することで削除された学習ユニット分だけ処理時間をさらに短縮することが可能となり、処理速度をさらに向上させることが可能となる。また、削除された学習ユニット分だけ少ないリソースで画像処理回路を構成することが可能となる。

【0029】

第8の発明によれば、遅延回路しか行わない学習ユニットによる演算処理が多数含まれた最適化された選択信号からそのような学習ユニットに対応する信号部分を削除して新たに最適化された選択信号を再構成することで、再構成された選択信号が実装された装置では、削除された学習ユニット分だけ処理時間をさらに短縮することが可能となり、処理速度をさらに向上させることが可能となる。また、削除された学習ユニット分だけ少ないリソースで画像処理回路を構成することが可能となる。このように第8の発明では、前記第7の発明の効果がより的確に発揮される。

【0030】

第9の発明によれば、学習手段における学習の際、例えば、256×256画素の画像に対して最初から全画素について遺伝的アルゴリズムの手法を適用すると探索範囲が非常に大きくなり最適解に収束するまでの時間が非常に長くかかるが、少数の画素に限定して個体を進化させることで、少数の画素に対しても評価が低いような選択信号を有する個体が早急に淘汰される。

【0031】

そのため、前記各発明の効果に加え、最終的に全画素について遺伝的アルゴリズムの手法を適用する際には、既に評価値がある程度高い個体が比較的多数存在する状態となり、最適解への収束の速度を向上させることが可能となる。

【0032】

第10の発明によれば、学習手段における学習において、入力に対して出力を与えないような意味のない選択信号を有する個体が生成されることを許す場合、意味のない選択信号からの出力画像の各画素の輝度値は0になる。一方、前記第9の発明のように教師画像の全画素中から選択された少数の画素の輝度値が0であると、意味のない個体が最高の評価を得てしまうため、意味があり評価値が高い個体を多数生き残らせて最適解への収束の速度を向上させるという目的が達成できなくなる。

【0033】

そのため、前記のような場合には、教師画像の輝度値が0でない画素の中から少数の画素を任意に選択して評価値の算出を行うことで、前記第9の発明と同様の効果を得ることが可能となる。

【0034】

第11の発明によれば、画像処理装置において、遅延処理の演算しか行わない学習ユニットによる演算処理を削除し、当該学習ユニットの処理下流側で行われる遅延処理以外の演算を上流側に移すことで、前記各発明の効果が的確に発揮されるとともに、遅延処理の演算しか行わない学習ユニットの演算処理が削除される分だけ処理時間をさらに短縮し、処理速度を向上させることが可能となる。また、削除された学習ユニット分だけ少ないリソースで画像処理回路を構成することが可能となる。

【0035】

第12の発明によれば、前記各発明の効果が的確に発揮されるとともに、最適化された選択信号の中に存在する遅延処理の演算しか行わない学習ユニットに対応する演算処理の信号部分を削除して選択信号を再構成し、再構成された選択信号に基づいて組み立てられた関数処理回路によって画像処理を行うことで、前記削除された信号部分の分だけより少ないリソースで画像処理回路を構成することが可能となる。また、その分処理時間をさらに短縮することが可能となり、処理速度を向上させることが可能となる。

【発明を実施するための最良の形態】

【0036】

以下、本発明に係る画像処理装置の実施の形態について、図面を参照して説明する。

【0037】

[第1の実施の形態]

第1の実施形態では、画像処理装置がFPGA(Field Programmable Gate Array)評価用ボード(ALTERA社製)上に構築される場合について述べるが、これに限定されない。

【0038】

本実施形態に係る画像処理装置1は、画像処理の手順を自律的に学習する装置である。画像処理装置1は、図1に示すように、プロセッサ2と、シフトレジスタ3と、複数の学習ユニット4と、マルチプレクサ5と、学習手段6とを備えている。

【0039】

本実施形態では、画像処理の対象となる画像データは、画像を構成する各画素の0〜255の256階調の輝度階調に補正された輝度値のデータであり、以下、個々の画素の輝度値のデータを画素データという。また、本実施形態では、画像のサイズが256×256画素であり、また、画像中の3×3画素を対象に画像処理を行う場合について説明する。

【0040】

また、本実施形態では、画像のデータは、原画像の水平方向に延びる1画素幅のライン上を左端の画素から右方向に、かつ、最上端のラインから順次下方のラインに向かう順番で1画素ずつ入力され画像処理される場合について述べる。

【0041】

プロセッサ2は、シフトレジスタ3や学習ユニット4、マルチプレクサ5にクロック信号CLKを送信してそれらをクロックに同期させて動作させるようになっている。また、各学習ユニット4とマルチプレクサ5に後述する学習手段6から送信されてくる選択信号SSを送信するようになっている。

【0042】

シフトレジスタ3はラインバッファ機能を有し、少なくとも514個の画素データを一時保存できるようになっている。シフトレジスタ3には、図2(A)〜(C)に示すように、画素データがクロックごとに学習手段6から順次入力されるようになっており、シフトレジスタ3はこれらの画素データを順々にシフトさせるようになっている。なお、図2(A)〜(C)で、00、01、02はそれぞれ画像の第0行第0列目、第0行第1列目、第0行第2列目の画素データを表している。

【0043】

シフトレジスタ3は、先頭の画素データが図3に示すように513番地にシフトしたクロックタイミングで、256番地の画素データを中心に0、1、255、256、257、511、512、513の各番地の画素データとこのクロックタイミングで入力された画素データとの9個の画素データを学習ユニット4に送信するようになっている。

【0044】

また、シフトレジスタ3は、次のクロックタイミングでそれらの画素データをシフトさせるとともに、シフトされた前記番地の8個の画素データとこのクロックタイミングで入力された画素データとの9個の画素データを学習ユニット4に送信するようになっている。以下、この動作を繰り返す。

【0045】

なお、256×256画素の画像中のn×n画素を対象に画像処理を行う場合には、図4に示すように、シフトレジスタ3は少なくとも257×(n−1)個の画素データを一時保存できる容量を有するものであることが望ましい。

【0046】

学習ユニット4は、図5に示すように、関数処理回路F1〜F9が並列に配置された演算ユニット41と、演算ユニット41の各関数処理回路F1〜F9に入力する画像データを選択する選択器42とで構成されている。演算ユニット41の各関数処理回路F1〜F9および選択器42にはそれぞれプロセッサ2からのクロック信号CLKが入力されるようになっている。

【0047】

演算ユニット41の関数処理回路Fには、2入力の加算器ADDRや減算器SUB、1入力の乗算器MULTや絶対値ABS、遅延回路DFF、含意素子IF_THEN等の単純な演算を行う関数処理回路が用いられている。

【0048】

ここで、本実施形態では、乗算器MULTは入力されたデータを定数倍するものであり、その定数は学習手段6における学習で最適化されるようになっている。また、本実施形態では、定数は各学習ユニット4で同一の値とされているが、異なった値としてもよい。また、遅延回路DFFにはディレイフリップフロップ(Delay flip-flop)が用いられており、1クロックの遅延が行われるようになっている。さらに、本実施形態では、含意素子IF_THENは入力されるデータの値が255より大きい場合には255にするようになっている。

【0049】

以下、演算ユニット41の関数処理回路Fの構成例として、図6に示すように、加算器ADDRを4個、減算器SUB、乗算器MULT、絶対値ABS、遅延回路DFF、含意素子IF_THENをそれぞれ1個ずつの計9個の関数処理回路を組み合わせる場合について述べる。しかし、関数処理回路Fの構成はこれに限定されず、用いられる関数処理回路Fの種類や数は適宜設定される。また、学習ユニット4の数も適宜設定される。

【0050】

選択器42には、学習手段6からプロセッサ2を経由して送信される選択信号SSが入力されるようになっている。また、本実施形態では、選択器42には、シフトレジスタ3や処理の上流側の学習ユニット4から9個のデータが入力され、2入力の4個の加算器ADDRおよび減算器SUBにそれぞれ2個ずつ、および1入力の乗算器MULT、絶対値ABS、遅延回路DFF、含意素子IF_THENにそれぞれ1個ずつデータを入力するために計14個のデータを出力するようになっている。

【0051】

選択器42の構造は、図6の円内に示される拡大図のように、1個の出力につきそれぞれ1個のマルチプレクサ様の素子が対応付けられており、素子により入力された9個のデータの中から1つのデータが選択されて出力され、対応する関数処理回路Fに入力されるようになっている。本実施形態では、選択器42には14個のマルチプレクサ様の素子が内蔵されている。

【0052】

また、選択器42のそれぞれの素子は、学習手段6から送信される選択信号SSに従って対応する関数処理回路に入力するデータを選択し、或いは選択せずに関数処理回路にデータを入力しないようになっている。

【0053】

選択信号SSは、各学習ユニット4に画像処理の手順を示すための信号であり、本実施形態では、例えば図7に示すように、各学習ユニット4の選択器42の各素子およびマルチプレクサ5が選択すべき入力データ番号が列記された選択信号の列である。各学習ユニット4の選択器42は選択信号SSの中から自らが指定されている数値部分を読み出して、各素子に選択信号を予め割り当てるようになっている。なお、図7の選択信号SS中、−で示される数値部分は選択信号が割り当てられていないことを示しており、対応する素子からはデータが出力されない。

【0054】

図7に示した選択信号SSの例では、選択信号SSが入力されると、学習ユニット4aの選択器42aは1番目の素子に0、2番目の素子に1、…、8番目の素子に8、11番目の素子に4をそれぞれ割り当て、学習ユニット4bの選択器42bは1番目の素子に0、…、4番目の素子に3、13番目の素子に6をそれぞれ割り当ててセットアップする。

【0055】

各素子は、図8に示すように、このようにして予め割り当てられた選択信号に従ってそれぞれの番号の入力データを選択して対応する関数処理回路Fにデータを送信するようになっている。このように、各学習ユニット4の選択器の各素子に選択信号が割り当てられることで、各学習ユニット4による画像処理の手順が決定される。

【0056】

また、選択器42は、プロセッサ2から送信されるクロック信号CLKの立ち上がりに合わせて各素子からデータを出力させて対応する各関数処理回路Fにデータを同期させて入力し、演算ユニット41の各関数処理回路Fは、次のクロック信号CLKの立ち上がりで同時に演算を開始して演算後のデータを出力するようになっている。

【0057】

なお、図1に示した複数の学習ユニット4a〜4nは、すべて図5や図6に示した学習ユニット4と同一の構成を有している。そして、選択信号SSによって処理に供される関数処理回路Fが選択され、それぞれ異なる演算を行うようになっている。

【0058】

マルチプレクサ5には、処理の最下流の学習ユニット4nからの出力データが入力されるようになっており、マルチプレクサ5は、学習手段6からプロセッサ2を経由して送信される選択信号SSに従って入力されたデータの中からデータを選択して出力するようになっている。

【0059】

学習手段6は、図1に示すように、学習ユニット4a〜4nの各選択器に割り当てる選択信号SSを予め学習により最適化し、最適化された選択信号SSsuitを出力するように構成されている。

【0060】

本実施形態では、学習は、遺伝的アルゴリズムの手法に基づいて行われるようになっており、学習手段6には、学習に用いられる図9に示すような原画像Dと教師画像としての画像処理により得られるべき図10に示すような目標画像Tが入力されるようになっている。また、評価値の算出の際に重み付けするための図11に示すような重み画像Wを入力しておくことも可能である。

【0061】

なお、目標画像Tおよび重み画像Wは原画像Dに基づいて予め作成される。図10に示した目標画像Tは、抽出領域EXに属する画素の輝度値は255に、非抽出領域NEに属する画素の輝度値は0になるように作成されている。また、図11に示した重み画像Wは、目標画像Tの抽出領域EXと非抽出領域NEに対応してそれぞれの領域で重みwがそれぞれの面積比の逆数の比になるように作成されるようになっている。

【0062】

原画像D、目標画像Tおよび重み画像Wは学習手段6の図示しない記憶手段に保存されるようになっている。

【0063】

一方、本実施形態に係る学習手段6では、まず、教師画像である目標画像T中の10画素等の所定個数の画素に対して学習を行い、その後、目標画像Tの全画素に対して学習を行うように構成されている。

【0064】

また、個体の評価を、出力画像Doutと目標画像Tとの各画素の輝度値の差のほか、出力画像Doutを得るために用いた関数処理回路の数や、遅延回路しか演算を行わない学習ユニットを除いた実質的な演算を行う学習ユニットの数に基づいて判断するように構成されている。

【0065】

図12は、本実施形態に係る学習手段の構成を示すブロック図である。学習手段6は、初期個体生成手段61と、評価値算出手段62と、終了判定手段63と、親選択手段64と、交叉手段65と、突然変異手段66とを備えている。

【0066】

初期個体生成手段61は、学習開始指示に応じて、図7に示したような各学習ユニット4a〜4nの各選択器およびマルチプレクサ5に割り当てる選択信号SSの列を遺伝子とする個体をランダムに例えば100個体等の一定数生成させるようになっている。また、初期個体生成手段61は、各個体ごとに乗算器MULTで用いられる定数をランダムに生成させて選択信号SSのヘッダに書き込むようになっている。定数を各学習ユニット4a〜4nで個別に設定する場合には、各学習ユニット4a〜4nのそれぞれについて定数をランダムに生成させてヘッダに書き込む。

【0067】

個体を生成し或いは交叉させ突然変異させる際には、意味のない個体が生じるような生成や交叉、突然変異を行わないように予め設定しておくことが好ましい。ここで、意味のない個体とは、その個体に含まれる選択信号SSに従うと、例えば、学習ユニット4の関数処理回路Fで演算されて出力されたデータが次の学習ユニット4での演算に用いられなかったり、学習ユニット4の関数処理回路Fからデータの出力がないにもかかわらずその関数処理回路Fからの出力を次の学習ユニット4の関数処理回路Fに入力するような個体である。また、最終の学習ユニット4nからの出力データをマルチプレクサ5が誤った選択をして出力しないような個体も意味のない個体とされる。

【0068】

評価値算出手段62は、図13に示すように、入力された教師画像である目標画像Tの画像中から例えば10個の画素Pをランダムに選択する。また、図14に示すように、目標画像T中から選択された10個の画素Pのそれぞれについて、原画像D中から対応する位置の画素を抽出し、その画素およびその周囲の8画素の計9画素の画素データをそれぞれ画素データの組COMとして抽出するようになっている。なお、図13や図14では、画素が実際より大きく表現されている。また、10個の画素Pは各世代ごとにランダムに選択される。

【0069】

評価値算出手段62は、続いて、初期個体生成手段61から送信されてきた全個体中の1つの個体について、それに含まれる選択信号SSをプロセッサ2を介して各学習ユニット4a〜4nに送信して各選択器42の各素子をセットアップする。また、各学習ユニット4a〜4nは、ヘッダから乗算器MULTの定数を読み出して、自らの演算ユニット41の乗算器MULTをセットアップする。

【0070】

そして、評価値算出手段62は、前記画素データの組COMの9個の画素データをシフトレジスタ3を介さずに1組ずつ直接学習ユニット4aに入力する。学習ユニット4a〜4nでは9個の画素データの入力に対して演算が行われ、マルチプレクサ5から1つの画素画像Doutの画素データが出力されて評価値算出手段62に入力される。

【0071】

評価値算出手段62は、このシミュレーション演算を組COMのすべてについて行い、その個体について、目標画像Tと出力画像Doutとの各画素の輝度値の差に基づく評価値Q1を下記(1)式に従って算出するようになっている。

【0072】

【数1】

【0073】

ここで、本実施形態では、前記(1)式のmは10であり、Tkはk番目の画素Pの輝度値、Doutkは対応するk番目の組COMに基づいて算出された出力画像Doutの画素の輝度値を表す。

【0074】

なお、前述した重み画像Wを用いて下記(2)式に従って評価値Q1を重み付けして算出することも可能である。

【0075】

【数2】

【0076】

ここで、Wkは、目標画像Tのk番目の画素Pに対応する重み画像W上の位置の画素の輝度値を表す。m、Tk、Doutkについては前記(1)式と同様である。

【0077】

また、評価値算出手段62は、同時に、個体に含まれる選択信号SSから出力画像Doutを得るために用いた関数処理回路の数Mおよび遅延回路DFFしか演算を行わない学習ユニットの数Nを算出し、下記(3)式および(4)式に従って評価値Q2、Q3を算出するようになっている。なお、下記(3)式のFNは本実施形態における関数処理回路Fの総数を表し、下記(4)式のUNは本実施形態における学習ユニット4の総数を表す。

【0078】

【数3】

【0079】

なお、遅延回路DFFしか演算を行わない学習ユニットとは、例えば図15に示すような学習ユニットをいい、図8に示した学習ユニット4bのように遅延回路DFFの演算を行うが他の関数処理回路Fでも演算を行う学習ユニットは含まれない。また、遅延回路DFFを複数備える学習ユニットにおいて複数の遅延回路DFFで演算が行われ他の関数処理回路Fでは演算が行われないような学習ユニットは遅延回路DFFしか演算を行わない学習ユニットに含まれる。さらに、図8において、例えば学習ユニット4aでは遅延回路DFFしか演算を行わずその出力データに対して学習ユニット4bの加算器ADDRによる演算が行われるような場合には、学習ユニット4aが遅延回路DFFしか演算を行わない学習ユニットに含まれる。

【0080】

評価値算出手段62は、評価値Q2、Q3を評価値Q1とともにそれぞれ各個体に対応付けるようになっている。評価値算出手段62は、以上のようにして100個の個体すべてについて評価値Q1、Q2、Q3を算出するようになっている。

【0081】

終了判定手段63は、評価値算出手段62から送信された各個体とメモリ67にエリート保存されている個体があればそれを含めてすべての個体の中で評価値Q1が目標評価値である1に達した個体がなければ、各個体を親選択手段64に送信するようになっている。

【0082】

親選択手段64は、各個体の中で評価値Q1が最も高い個体をエリート保存してメモリ67に隔離するとともに、その個体のコピーと残りの個体との中から評価値Q1に基づいてトーナメント選択により次世代に残すべき100個体の処理プログラムの選択およびそれらの処理プログラムの増殖を行うようになっている。なお、ルーレット選択や期待値選択、ランキング選択等の他の方法で親選択を行うことも可能である。

【0083】

交叉手段65では、親選択手段64で選択され増殖された親個体について2個体ずつ対にして、それぞれの個体対ごとにランダムに選ばれた交叉部分で所定の割合で互いに交叉させて、子個体を生成させるようになっている。また、突然変異手段66では、各個体ごとに所定の割合で選択信号SSの数値の変更や選択信号SSのヘッダ部分に書き込まれた乗算器MULTの定数の変更等が行われるようになっている。

【0084】

このようにして、評価値Q1が1の個体が現れるまで前記シミュレーション演算や世代交代が繰り返されるようになっている。

【0085】

終了判定手段63は、評価値Q1が目標評価値である1の個体が現れると、評価値算出手段62に対して目標画像Tの画像中からランダムに選択する画素Pの数を100個に増やすように指示を出すようになっている。

【0086】

そのため、評価値算出手段62では、次世代からは、目標画像T中から選択された100個の画素Pのそれぞれについて、原画像D中から対応する位置の画素を抽出し、その画素およびその周囲の8画素の計9画素の画素データをそれぞれ画素データの組COMを100組抽出するようになっている。そして、その100組についてシミュレーション演算を行い、前記(1)式または(2)式中のnを100として各個体について評価値Q1を新たに算出するようになっている。

【0087】

このように、終了判定手段63は、評価値Q1が設定された目標評価値に達した個体が現れると、目標画像T中からランダムに選択する画素数を増やすように評価値算出手段62に指示を送るようになっている。画素数はこの後、例えば1000画素、10000画素のように増加され、最終的には原画像Dの全画素数である256×256=65536画素まで増加される。また、目標評価値は、例えば10画素では1、100画素では0.95、1000画素では0.9、10000画素では0.85のように徐々に小さい値が設定されるようになっている。

【0088】

なお、目標画像T中からランダムに選択する画素数を増やす基準を、例えば設定された世代数ごととすることも可能である。また、画素数が原画像Dの全画素数まで増加された段階で、評価値算出手段62は、原画像Dの水平方向に延びる1画素幅のライン上を左端の画素から右方向に、かつ、最上端のラインから順次下方のラインに向かう順番で1画素ずつ画素データをシフトレジスタ3に入力する。シフトレジスタ3からは9個の画素データが順次学習ユニット4aに入力される。

【0089】

一方、学習手段6は、終了判定手段63により評価値算出手段62におけるシミュレーション演算の範囲が原画像Dの全画素まで拡大され、評価値Q1が例えば0.8等に設定された目標評価値以上の個体が現れると、エリート保存の基準と終了判定の基準を変更するようになっている。

【0090】

具体的には、本実施形態では、親選択手段64は、メモリ67に保存されているエリート個体の評価値Q1、Q2、Q3のいずれに対してもそれらに等しいかそれらを上回る評価値Q1、Q2、Q3を有する個体が現れない限りエリートを更新しないようになっている。すなわち、評価値Q1がエリート以上の個体が現れても、その個体の評価値Q2或いは評価値Q3がエリートの評価値Q2或いは評価値Q3より小さければエリートとしないようになっている。

【0091】

また、終了判定手段63は、終了判定の基準を変更するようになっている。本実施形態では、終了判定手段63は、原画像Dの全画素に対するシミュレーション演算で評価値Q1が0.8以上の個体が現れた段階で、予め設定された最終的な目標評価値Qa、Qb、Qc以上の評価値Q1、Q2、Q3を有する個体が現れることを最終的な終了判定の基準として設定するようになっている。なお、この他にも、例えば、予め設定された世代数に達した時点で終了することを最終的な終了判定の基準として設定するように構成することも可能である。

【0092】

終了判定手段63は、この最終的な終了判定基準が満たされたと判定すると、以上のルーチンを終了するようになっている。そして、終了判定手段63は、最終的な終了判定基準を満した個体からそれに含まれる選択信号SSを抽出し、選択信号SSに遅延処理の演算しか行わない学習ユニットによる演算処理に対応する信号部分があればその信号部分を選択信号SSから削除するようになっている。

【0093】

終了判定手段63は、このようにして再構成した選択信号SSを、各学習ユニット4a〜4nに割り当てるべき最適化された選択信号SSsuitとして出力するようになっている。

【0094】

次に、本実施形態に係る画像処理装置1の作用について説明する。

【0095】

本実施形態の画像処理装置1のプロセッサ2、シフトレジスタ3、学習ユニット4およびマルチプレクサ5の作用については前記構成で述べたとおりであるので説明を省略する。

【0096】

学習手段6は、まず、初期個体生成手段61が生成した個体の中から、前記(1)式または(2)式に従って算出される評価値Q1が低い個体すなわち教師画像である目標画像Tと出力画像Doutとの各画素の輝度値の差が大きい個体を淘汰するために、目標画像T上の限定された数の画素を対象として進化過程を進める。

【0097】

このように少数の画素に限定して個体を進化させることで、目標画像T上の限定された数の画素を対象としても目標画像Tとの輝度値の差が大きい出力画像Doutしか出力できないような選択信号SSを有する個体が早急に淘汰される。

【0098】

従って、終了判定手段63が評価値算出手段62におけるシミュレーション演算の範囲を原画像Dの全画素まで拡大する際には、既に目標画像Tとの距離が近い出力画像Doutを出力させ得る選択信号SSを含む個体が比較的多数存在する状態となり、最適解への収束の速度が向上する。

【0099】

一方、学習手段6は、この時点で終了判定条件を切り替え、評価値Q1が例えば0.8等に設定された目標評価値以上の個体が現れた段階で、評価値Q1のみによる評価を離れて評価値Q2や評価値Q3をも考慮して最適解を探索するようになる。

【0100】

評価値Q2は、前記(3)式に示されるように、出力画像Doutを得るために用いた関数処理回路の数Mが少ないほど大きな値を取る。従って、評価値Q2が高い値であるということは、その個体に含まれる選択信号SSによれば、より少ないリソースすなわち関数処理回路で画像処理回路を構成することができることを意味する。

【0101】

また、評価値Q3は、前記(4)式に示されるように、遅延回路DFFしか演算を行わない学習ユニットの数Nが多いほど大きな値を取る。従って、評価値Q3が高い値であるということは、その個体に含まれる選択信号SSによれば、より多くの遅延回路DFFしか演算を行わない学習ユニットが含まれる画像処理回路が構成されることを意味する。

【0102】

遅延回路DFFしか演算を行わない学習ユニットによる演算処理は、実装段階ではいわば省略してもよい演算処理である。また、学習ユニットの数が増えるほど遅延回路DFFしか演算を行わない学習ユニットの数も増える可能性が高くなり、省略できる演算処理の数も増える可能性が高くなる。

【0103】

そのため、本実施形態のように、最終的な終了判定基準を満たした選択信号SSからさらに遅延回路DFFしか演算を行わない学習ユニットに対応する信号部分を削除して新たに最適化された選択信号SSsuitを再構成することで、削除された学習ユニット分だけ処理時間が短縮され、処理速度が向上する。また、削除された学習ユニット分だけ少ないリソースで画像処理回路を構成することが可能となる。

【0104】

前述したように、本実施形態では1個の学習ユニットの処理あたり選択器42と演算ユニット41の2クロックを要するから、結局、削除された学習ユニットの個数の2倍のクロック数分の処理時間の短縮と処理速度の向上を図ることができる。また、本実施形態では1個の学習ユニットあたり9個の関数処理回路が用いられているから、その分リソースを減らすことができる。

【0105】

評価値Q2、Q3はそれぞれ前記のような意味を持つものであり、本実施形態では、出力画像Doutと目標画像Tとの輝度値の差を小さくすることを前提としてリソースの低減と処理速度の向上との両方を達成することを目的として、前述したような厳しい最終的な終了判定の基準を設定した。しかし、リソースの数を減らすことを重視して評価値Q2が高い個体を新たなエリートとしたり、処理時間の短縮や処理速度を向上を優先ために評価値Q3が高い個体をエリートとして更新するように構成することも可能である。

【0106】

以上のように、本実施形態に係る画像処理装置1によれば、まず、従来の画像処理装置のような画像フィルタの組み合わせではなく、加算器ADDRのような単純な関数処理回路Fの組み合わせで構築された画像処理回路に対する画像処理手順を提供することができるため、その手順に従えば、画像処理の種類が画像フィルタやその組み合わせに制限されず、思い通りの画像処理を行うことが可能な画像処理回路を構築することが可能となる。

【0107】

また、本実施形態では、教師画像として目標画像Tを1種類だけ与えて学習を行う場合について述べたが、希望する画像処理を学習するためにさらに複数の教師画像に基づいて学習を行うことで、希望する画像処理をさらに精度良く行うことができる画像処理回路を構築するための画像処理手順を提供することが可能となる。

【0108】

さらに、本実施形態に係る画像処理装置1により出力される最適化された選択信号SSsuitに従えば、処理プログラムによるソフトウエア処理と同等の画像処理をハードウエア処理で行ってクロック単位で演算処理を行うようにすることができるため、画像処理速度を飛躍的に向上させることが可能となり、画像データをリアルタイムに処理することが可能となる。

【0109】

また、選択信号SSの最適化において、使用する関数処理回路Fの数が少ない選択信号に対してより良い評価を与えることで、出力される最適化された選択信号SSsuitをリソースの数を低減可能な選択信号として出力することが可能になる。

【0110】

また、遅延回路DFFしか行わない学習ユニットは実装段階では省いてよい演算処理であるから、選択信号SSの最適化において、遅延回路DFFしか行わない学習ユニットを多く含む選択信号に対してより良い評価を与えることで、最終的な終了判定基準を満たした選択信号SSには遅延回路DFFしか行わない学習ユニットによる演算処理が多数含まれたものとなる。

【0111】

そのため、そのような選択信号SSから遅延回路DFFしか演算を行わない学習ユニットに対応する信号部分を削除して新たに最適化された選択信号SSsuitを再構成することで、削除された学習ユニット分だけ処理時間をさらに短縮することが可能となり、処理速度を向上させることが可能となる。また、削除された学習ユニット分だけ少ないリソースで画像処理回路を構成することが可能となる。

【0112】

なお、学習手段6における遺伝的アルゴリズムを用いた学習において、個体の生成や交叉、突然変異の際に前述したような意味のない個体が生成等されないような制限を加えない場合には、学習ユニット4a〜4nに画素データを入力してもマルチプレクサ5からデータが出力されず、結果的に輝度値が0のデータが出力されたことと同じになる場合がある。

【0113】

このような場合に、教師画像である目標画像Tから任意に例えば10個の画素を選択してそれらがすべて輝度値0の画素であると、意味のない個体の評価値Q1が1という最高の評価を得てしまうため、目標画像Tから少数画素を選択して進化過程を進め意味があり評価値が高い個体を多数生き残らせて最適解への収束の速度を向上させるという目的が達成できなくなる。

【0114】

そのため、前記のような制限を設けずに目標画像Tから少数の画素を選択して進化過程を進める場合には、目標画像Tの輝度値が0でない画素の中から少数の画素を任意に選択して評価値Q1の算出を行うように構成することが好ましい。

【0115】

また、学習手段6の終了判定手段63において、選択信号SSから遅延処理の演算しか行わない学習ユニットによる演算処理に対応する信号部分の削除に加えて、さらに、余分な関数処理回路Fを削除するように構成すれば、より少ないリソースで画像処理回路を構成することが可能となる。

【0116】

具体的には、例えば、本実施形態のように1個の学習ユニットにつき4個の加算器ADDRを設けたが、最適化された選択信号SSsuitを解析して1個の学習ユニットにつき最大で3個の加算器ADDRしか使用していない場合には、選択信号SSsuitを3個の加算器ADDRを用いるように改変して新たな最適化された選択信号SSsuitとすることで、使用する加算器ADDRの数を低減させることが可能となる。

【0117】

さらに、本実施形態では、目標画像Tとして、抽出領域EXの画素の輝度値が255、非抽出領域NEの画素の輝度値が0の画像の場合を示したが、目標画像Tをこのような2値的な画像として作成する必要はなく、各画素が0〜255の輝度値を有する画像として作成することが可能である。

【0118】

また、本実施形態では、原画像Dすなわち学習ユニット4a〜4nの演算処理に入力される画像が1種類の画像である場合について述べたが、この他にも、例えば、2種類の画像を入力してその2種類の画像に対して加算や減算等を行うように構成することも可能である。

【0119】

例えば、2種類の画像を入力するように構成する場合には、本実施形態のシフトレジスタ3を2つ設け、2つのシフトレジスタから出力される18個の画素データを学習ユニット4aに入力するように構成する。また、学習ユニット4の演算ユニット41の関数処理回路Fを計18個備えるようにし、最終的に学習ユニット4nから出力される18個のデータから1個のデータをマルチプレクサ5で選択して出力するように構成する。

【0120】

[第2の実施の形態]

次に、前記第1の実施形態に係る画像処理装置1を改良した画像処理装置について説明する。第1の実施形態と同様の機能を奏する部材については同一の符号を付して説明する。

【0121】

第2の実施形態に係る画像処理装置10は、図16に示すように、基本的には第1の実施形態に示した画像処理装置1の構成と同様であるが、学習手段6での学習により得られた最適化された選択信号SSsuitがプロセッサ2に出力されるようになっていて、プロセッサ2から各学習ユニット4a〜4nに送られて各学習ユニット4a〜4nがセットアップされるようになっている。

【0122】

また、シフトレジスタ3には、外部から画像データDinが入力されるようになっていて、マルチプレクサ5からの出力が出力データDoutとして外部に出力されるようになっている。さらに、各学習ユニット4a〜4nの出力がすべてマルチプレクサ5に入力されるように配線されている。

【0123】

また、プロセッサ2は、学習手段6から送信されてきた最適化された選択信号SSsuitをチェックして、選択信号SSsuitの中に遅延処理の演算しか行わない学習ユニットによる演算処理に対応する信号部分があればその信号部分を選択信号SSから削除して、最適化された選択信号SSsuitを再構成するようになっている。

【0124】

なお、学習手段6による学習は画像処理装置10の稼動開始前に行われ、画像処理装置10の実稼動中には学習手段6の動作は停止されるようになっている。

【0125】

このように最適化された選択信号SSsuitを再構成することで、遅延処理の演算しか行わない学習ユニットによる演算処理を削除し、その学習ユニットの処理下流側に遅延処理以外の演算処理を行う他の学習ユニットがある場合には当該他の学習ユニットの演算処理を上流側の学習ユニットに移すことが可能となる。

【0126】

そして、遅延処理以外の演算を行う最下流の学習ユニットから出力される処理結果がマルチプレクサ5に送信され、マルチプレクサ5がその学習ユニットからの出力を選択することで出力データDoutが出力される。

【0127】

以上のように、本実施形態に係る画像処理装置10によれば、前記第1の実施形態で述べた画像処理装置1の効果と同様の効果が有効に発揮され、画像データDinをリアルタイムに画像処理することが可能となる。

【0128】

特に、再構成された最適化された選択信号SSsuitにより、遅延処理の演算しか行わない学習ユニットの演算処理を削除して、その処理下流側で行われる遅延処理以外の演算処理をより上流側の学習ユニットで行うことが可能となる。また、遅延処理の演算しか行わない学習ユニットの演算処理を削除して、その出力を直接マルチプレクサ5に入力させることができる。

【0129】

そのため、遅延処理の演算しか行わない学習ユニットの演算処理が削除される分だけ処理時間をさらに短縮することが可能となり、処理速度を向上させることが可能となる。また、削除された学習ユニット分だけ少ないリソースで画像処理回路を構成することが可能となる。

【0130】

また、本実施形態に係る画像処理装置10では、学習手段6の構成がそのまま残されているため、学習手段6で初期個体を新たに生成して別の教師画像に基づいて学習を行って最適化された選択信号SSsuitを得ることで既に学習された画像処理とは異なる種類の画像処理を行うことが可能となり、新たな画像処理の機能を獲得することが可能となる。

【0131】

なお、本実施形態に係る画像処理装置10を、最初に学習された画像処理に専用の装置とする場合には、遅延処理以外の演算処理を行う最終の学習ユニットからの出力のみをマルチプレクサ5に入力するように配線することができる。

【0132】

[第3の実施の形態]

次に、前記第1の実施形態に係る画像処理装置1の改良型として、最適化された選択信号SSsuitを用いて画像処理を行う画像処理装置について説明する。

【0133】

第3の実施形態に係る画像処理装置では、各関数処理回路Fを図1に示した学習ユニットのように構成しない場合もある。しかし、その場合でも、最適化された選択信号SSsuitの中に遅延処理の演算しか行わない学習ユニットによる演算処理に対応する信号部分があるときは、その信号部分を選択信号SSsuitから削除して最適化された選択信号SSsuitを再構成したうえで、再構成された選択信号SSsuitに基づいて加算器ADDRや減算器SUB、乗算器MULT、絶対値ABS、遅延回路DFF、含意素子IF_THEN等を接続して関数処理回路による画像処理回路を構築する。

【0134】

このように再構成された最適化された選択信号SSsuitに基づいて画像処理回路を構築することで、本実施形態に係る画像処理装置では、前記第1の実施形態で述べた画像処理装置1の効果と同様の効果が有効に発揮され、画像データをリアルタイムに画像処理することが可能となる。

【0135】

また、最適化された選択信号SSsuitの中の遅延処理の演算しか行わない学習ユニットによる演算処理に対応する信号部分を削除して画像処理回路を構築できるので、その分処理時間をさらに短縮することが可能となり、処理速度を向上させることが可能となる。また、削除された学習ユニットに対応する分だけ少ないリソースで画像処理回路を構成することが可能となる。

【0136】

さらに、最適化された選択信号SSsuitに基づいてデータの演算処理に関与しない関数処理回路を省いて画像処理回路を構築することができるため、さらに少ないリソースで画像処理回路を構成することが可能となる。

【図面の簡単な説明】

【0137】

【図1】第1実施形態に係る画像処理装置の構成を示すブロック図である。

【図2】シフトレジスタ内での画素データのシフトを説明する図である。

【図3】演算処理の対象となる3×3画素の画素データのシフトレジスタ内での番地を示す図である。

【図4】n×n画素の画素データのシフトレジスタ内での保存位置を示す図である。

【図5】学習ユニットの構成を示すブロック図である。

【図6】本実施形態における学習ユニットの構成例を示すブロック図である。

【図7】選択信号の構成を示す図である。

【図8】図7の選択信号が割り当てられた学習ユニットにおけるデータ処理の流れを説明する図である。

【図9】本実施形態で用いられる原画像を示す図である。

【図10】本実施形態で用いられる目標画像を示す図である。

【図11】重み画像を示す図である。

【図12】学習手段の構成を示すブロック図である。

【図13】目標画像中から選択された画素を表す図である。

【図14】図13の画素に対応する原画像中の画素位置に抽出された画素の組を表す図である。

【図15】遅延回路しか演算を行わない学習ユニットの例を示す図である。

【図16】第2実施形態に係る画像処理装置の構成を示すブロック図である。

【図17】画像フィルタを木構造状に組み合わせた処理プログラムを表す図である。

【符号の説明】

【0138】

1、10 画像処理装置

4 学習ユニット

41 演算ユニット

42 選択器

6 学習手段

F 関数処理回路

DFF 遅延回路

SS 選択信号

SSsuit 最適化された選択信号

CLK クロック信号

T 目標画像

Dout 出力画像

Q1、Q2、Q3 評価値

M 関数処理回路の数

N 遅延回路しか演算を行わない学習ユニットの数

P 教師画像中から選択された画素

【特許請求の範囲】

【請求項1】

画像処理の手順を学習する画像処理装置であって、

関数処理回路が並列に配置された演算ユニットと前記各関数処理回路に入力するデータを選択する選択器とからなる学習ユニットと、

前記学習ユニットによる演算の順序を最適化する学習手段とを備え、

前記学習ユニットは、複数個が直列に連結され、

前記複数の学習ユニットの各選択器は、画像処理の手順を示す選択信号に従って各関数処理回路に入力するデータを選択し、

前記学習手段は、各学習ユニットの選択器に割り当てる前記選択信号を学習により最適化することを特徴とする画像処理装置。

【請求項2】

前記学習ユニットは、自らに属する各選択器からそれぞれに対応する関数処理回路へのデータの入力をクロック信号に合わせ同期させて行うことを特徴とする請求項1に記載の画像処理装置。

【請求項3】

前記学習手段は、各学習ユニットの選択器に割り当てる前記選択信号の列を遺伝子とし、画像処理により得られるべき目標画像を教師画像として遺伝的アルゴリズムの手法に基づいて学習を行うことを特徴とする請求項1または請求項2に記載の画像処理装置。

【請求項4】

前記学習手段は、前記遺伝子が前記関数処理回路に用いられる定数を含み、前記学習により前記定数の最適化を同時に行うことを特徴とする請求項3に記載の画像処理装置。

【請求項5】

前記学習手段は、前記学習において、教師画像である画像処理により得られるべき目標画像と演算により算出された出力画像との各画素の輝度値の差に基づいて評価値を算出することを特徴とする請求項3または請求項4に記載の画像処理装置。

【請求項6】

前記学習手段は、前記学習において、演算を行う前記関数処理回路の数に基づいて評価値を算出することを特徴とする請求項3から請求項5のいずれか一項に記載の画像処理装置。

【請求項7】

前記関数処理回路は、入力されたデータを1クロック分遅延させる機能を有する遅延回路を含み、

前記学習手段は、前記学習において、前記遅延回路しか演算を行わない学習ユニットの数に基づいて評価値を算出することを特徴とする請求項3から請求項6のいずれか一項に記載の画像処理装置。

【請求項8】

前記学習手段は、算出した最適化された前記選択信号から前記遅延処理の演算しか行わない学習ユニットによる演算処理に対応する信号部分を削除して新たに最適化された選択信号を再構成して出力することを特徴とする請求項7に記載の画像処理装置。

【請求項9】

前記学習手段は、前記教師画像中から任意に選択された所定個数の画素について評価値の算出を行うことを特徴とする請求項3から請求項8のいずれか一項に記載の画像処理装置。

【請求項10】

前記学習手段は、前記教師画像の輝度値が0でない画素の中から任意に選択された所定個数の画素について評価値の算出を行うことを特徴とする請求項3から請求項8のいずれか一項に記載の画像処理装置。

【請求項11】

請求項1から請求項10のいずれか一項に記載の画像処理装置であって、

前記画像処理装置の学習手段により最適化された前記選択信号に従って画像処理を行わせると遅延処理の演算しか行わない学習ユニットがある場合には、当該学習ユニットによる演算処理を削除し、当該学習ユニットの処理下流側に遅延処理以外の演算を行う他の学習ユニットがある場合には当該他の学習ユニットの演算処理を上流側の学習ユニットに移して、遅延処理以外の演算を行う最下流の学習ユニットから出力される処理結果を出力することを特徴とする画像処理装置。

【請求項12】

請求項1から請求項10のいずれか一項に記載され、最適化された前記選択信号に基づいて画像処理を行う画像処理装置であって、

前記画像処理装置が前記選択信号に従って画像処理を行った場合に遅延処理の演算しか行わない学習ユニットに対応する演算処理があるときは、前記選択信号から当該演算処理に対応する信号部分を削除して選択信号を再構成し、再構成された選択信号に基づいて前記関数処理回路による画像処理回路を構築することを特徴とする画像処理装置。

【請求項1】

画像処理の手順を学習する画像処理装置であって、

関数処理回路が並列に配置された演算ユニットと前記各関数処理回路に入力するデータを選択する選択器とからなる学習ユニットと、

前記学習ユニットによる演算の順序を最適化する学習手段とを備え、

前記学習ユニットは、複数個が直列に連結され、

前記複数の学習ユニットの各選択器は、画像処理の手順を示す選択信号に従って各関数処理回路に入力するデータを選択し、

前記学習手段は、各学習ユニットの選択器に割り当てる前記選択信号を学習により最適化することを特徴とする画像処理装置。

【請求項2】

前記学習ユニットは、自らに属する各選択器からそれぞれに対応する関数処理回路へのデータの入力をクロック信号に合わせ同期させて行うことを特徴とする請求項1に記載の画像処理装置。

【請求項3】

前記学習手段は、各学習ユニットの選択器に割り当てる前記選択信号の列を遺伝子とし、画像処理により得られるべき目標画像を教師画像として遺伝的アルゴリズムの手法に基づいて学習を行うことを特徴とする請求項1または請求項2に記載の画像処理装置。

【請求項4】

前記学習手段は、前記遺伝子が前記関数処理回路に用いられる定数を含み、前記学習により前記定数の最適化を同時に行うことを特徴とする請求項3に記載の画像処理装置。

【請求項5】

前記学習手段は、前記学習において、教師画像である画像処理により得られるべき目標画像と演算により算出された出力画像との各画素の輝度値の差に基づいて評価値を算出することを特徴とする請求項3または請求項4に記載の画像処理装置。

【請求項6】

前記学習手段は、前記学習において、演算を行う前記関数処理回路の数に基づいて評価値を算出することを特徴とする請求項3から請求項5のいずれか一項に記載の画像処理装置。

【請求項7】

前記関数処理回路は、入力されたデータを1クロック分遅延させる機能を有する遅延回路を含み、

前記学習手段は、前記学習において、前記遅延回路しか演算を行わない学習ユニットの数に基づいて評価値を算出することを特徴とする請求項3から請求項6のいずれか一項に記載の画像処理装置。

【請求項8】

前記学習手段は、算出した最適化された前記選択信号から前記遅延処理の演算しか行わない学習ユニットによる演算処理に対応する信号部分を削除して新たに最適化された選択信号を再構成して出力することを特徴とする請求項7に記載の画像処理装置。

【請求項9】

前記学習手段は、前記教師画像中から任意に選択された所定個数の画素について評価値の算出を行うことを特徴とする請求項3から請求項8のいずれか一項に記載の画像処理装置。

【請求項10】

前記学習手段は、前記教師画像の輝度値が0でない画素の中から任意に選択された所定個数の画素について評価値の算出を行うことを特徴とする請求項3から請求項8のいずれか一項に記載の画像処理装置。

【請求項11】

請求項1から請求項10のいずれか一項に記載の画像処理装置であって、

前記画像処理装置の学習手段により最適化された前記選択信号に従って画像処理を行わせると遅延処理の演算しか行わない学習ユニットがある場合には、当該学習ユニットによる演算処理を削除し、当該学習ユニットの処理下流側に遅延処理以外の演算を行う他の学習ユニットがある場合には当該他の学習ユニットの演算処理を上流側の学習ユニットに移して、遅延処理以外の演算を行う最下流の学習ユニットから出力される処理結果を出力することを特徴とする画像処理装置。

【請求項12】

請求項1から請求項10のいずれか一項に記載され、最適化された前記選択信号に基づいて画像処理を行う画像処理装置であって、

前記画像処理装置が前記選択信号に従って画像処理を行った場合に遅延処理の演算しか行わない学習ユニットに対応する演算処理があるときは、前記選択信号から当該演算処理に対応する信号部分を削除して選択信号を再構成し、再構成された選択信号に基づいて前記関数処理回路による画像処理回路を構築することを特徴とする画像処理装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2007−279967(P2007−279967A)

【公開日】平成19年10月25日(2007.10.25)

【国際特許分類】

【出願番号】特願2006−104323(P2006−104323)

【出願日】平成18年4月5日(2006.4.5)

【出願人】(000005348)富士重工業株式会社 (3,010)

【Fターム(参考)】

【公開日】平成19年10月25日(2007.10.25)

【国際特許分類】

【出願日】平成18年4月5日(2006.4.5)

【出願人】(000005348)富士重工業株式会社 (3,010)

【Fターム(参考)】

[ Back to top ]