画像処理装置

【課題】少ないメモリ容量で高速な処理を行う画像処理装置を得る。

【解決手段】処理対象画像のサイズおよび各画素のデータサイズなどの画像情報を設定する画像情報設定部22と、プラットホーム3に搭載されたキャッシュ32の構成およびサイズなどのキャッシュ情報を設定するキャッシュ情報設定部21と、画像情報設定部22が設定した画像情報から、処理対象画像の行方向のデータサイズおよび列方向のデータサイズを特定し、当該行方向および列方向のデータサイズを有する画像領域31aを生成すると共に、画像情報設定部22が設定した画像情報およびキャッシュ情報設定部21が設定したキャッシュ情報から、所定のサイズを行方向のデータサイズとし、処理対象画像の行方向のデータサイズを列方向のデータサイズとした作業領域31bを生成し、生成した画像領域31aおよび作業領域31bを画像処理プログラムに割り付けるメモリ割付部23とを備える。

【解決手段】処理対象画像のサイズおよび各画素のデータサイズなどの画像情報を設定する画像情報設定部22と、プラットホーム3に搭載されたキャッシュ32の構成およびサイズなどのキャッシュ情報を設定するキャッシュ情報設定部21と、画像情報設定部22が設定した画像情報から、処理対象画像の行方向のデータサイズおよび列方向のデータサイズを特定し、当該行方向および列方向のデータサイズを有する画像領域31aを生成すると共に、画像情報設定部22が設定した画像情報およびキャッシュ情報設定部21が設定したキャッシュ情報から、所定のサイズを行方向のデータサイズとし、処理対象画像の行方向のデータサイズを列方向のデータサイズとした作業領域31bを生成し、生成した画像領域31aおよび作業領域31bを画像処理プログラムに割り付けるメモリ割付部23とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、二次元の画像に対して、行方向と列方向の処理を行う画像処理装置に関するものである。

【背景技術】

【0002】

二次元の画像に対して、行方向と列方向の処理を行う画像処理の1つに、SAR(Synthetic Aperture Radar:合成開口レーダ)画像の再生処理がある。SAR画像再生処理は、非特許文献1に記載されているように、前半でレンジ方向の処理であるレンジ圧縮を行い、後半でアジマス方向の処理であるアジマス圧縮を行う。

【0003】

SAR画像再生処理をPCやワークステーションなどの汎用のコンピュータで行う場合は、キャッシュ機構を備えたメモリ上にデータを格納するため、連続したアドレス順にデータをアクセスする場合はキャッシュがヒットして高速に処理を行うことができるが、連続していないアドレス順でデータをアクセスする場合はキャッシュミスを起こして低速となる。すなわち、処理する方向にデータが格納されている場合には高速で処理することができるが、処理する方向にデータが格納されていない場合には処理が低速になってしまう。

【0004】

この問題を解決する方法として、特許文献1には前半のレンジ方向の処理と後半のアジマス方向の処理の間に、メモリ上のデータの行と列(縦横)を入れ替える(転置する)コーナーターンを行い、このコーナーターンの際にキャッシュミスが発生しないように、正方形のブロック単位でメモリ上のデータを転置する方法が開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特許第3850599号公報

【非特許文献】

【0006】

【非特許文献1】飯坂譲二監修、日本写真測量学会編、「合成開口レーダ画像ハンドブック」朝倉書店、1998年5月20日 初版第1刷

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、上述した特許文献1に開示された技術では、コーナーターンにおいて、レンジとアジマス(横と縦)の二つの方向にデータを格納するので、本来の画像のデータ量に対して、2倍のメモリ量が必要となり、装置に大容量メモリを搭載する必要があるという課題があった。さらに大容量メモリを搭載することにより装置が大型化するという課題があった。

【0008】

この発明は、上記のような課題を解決するためになされたもので、少ないメモリ容量で高速な処理を行う画像処理装置を得ることを目的とする。

【課題を解決するための手段】

【0009】

この発明に係る画像処理装置は、処理対象画像のサイズおよび各画素のデータサイズなどの画像情報を設定する画像情報設定部と、プラットホームに搭載されたキャッシュの構成およびサイズなどのキャッシュ情報を設定するキャッシュ情報設定部と、画像情報設定部が設定した画像情報から、処理対象画像の行方向のデータサイズおよび列方向のデータサイズを特定し、当該行方向および列方向のデータサイズを有する画像領域を生成すると共に、画像情報設定部が設定した画像情報およびキャッシュ情報設定部が設定したキャッシュ情報から、所定のサイズを行方向のデータサイズとし、処理対象画像の行方向のデータサイズを列方向のデータサイズとした作業領域を生成し、生成した画像領域および作業領域を画像処理プログラムに割り付けるメモリ割付部とを備えたものである。

【発明の効果】

【0010】

この発明によれば、少ないメモリ容量で、高速に画像処理を行うことができる。

【図面の簡単な説明】

【0011】

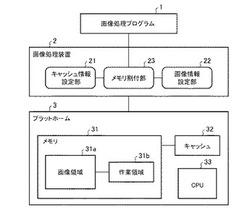

【図1】実施の形態1による画像処理装置の構成を示すブロック図である。

【図2】実施の形態1による画像処理装置の動作を示すフローチャートである。

【図3】実施の形態1による画像処理装置のアジマス圧縮処理を示すフローチャートである。

【図4】実施の形態1による画像処理装置の画像領域から作業領域へのデータ移動を示す。

【図5】実施の形態1による画像処理装置の画像領域から作業領域へのデータ移動の際のキャッシュを示す説明図である。

【発明を実施するための形態】

【0012】

実施の形態1.

実施の形態1に係る画像処理装置について、図1から図7を参照しながら説明する。図1は、この発明の実施の形態1による画像処理装置の構成を示すブロック図である。図1において、画像処理プログラム1は、SAR画像の再生処理を実行する。画像処理装置2は、プラットホーム3上で動作し、画像データのメモリへの割り付け方法などを画像処理プログラム1に指示する。プラットホーム3は、メモリ31、キャッシュ32およびCPU33などにより構成される。

【0013】

また、図1に示した画像処理装置2は、キャッシュ情報設定部21、画像情報設定部22およびメモリ割付部23で構成されている。

キャッシュ情報設定部21は、キャッシュ32の構成やサイズなどキャッシュ情報を設定する。画像情報設定部22は、処理対象となる画像のサイズ(画素数)および各画素のデータサイズを設定する。メモリ割付部23は、キャッシュ情報設定部21および画像情報設定部22からキャッシュ情報および画像情報を取得し、1キャッシュラインのデータサイズの整数倍×アジマス方向のデータサイズ(画素数×1画素当たりのByte数)を作業領域のサイズとして算出し、算出したサイズの作業領域をメモリ31上に割り付けるように画像処理プログラム1に指示する。

【0014】

なお以下の説明では、処理対象画像を、1画素当たり8Byte、画像サイズはレンジ方向、アジマス方向とも20480画素と仮定する。また、プラットホーム3に搭載されているキャッシュ32は、データキャッシュ、1キャッシュライン当たり32Byte×512ライン、1次キャッシュのみを仮定する。

【0015】

画像情報設定部22は、処理対象画像の情報として、画像のサイズ(画素数)、各画素のデータサイズなどを設定するが、この具体例では、1画素当たり8Byte、画像サイズはレンジ方向20480画素×アジマス方向20480画素という情報を設定する。画像情報設定部22への画像情報の入力は、ユーザ入力などにより手動で行うほか、画像データや画像処理プログラム1から自動的に行うように構成してもよい。

【0016】

キャッシュ情報設定部21は、プラットホーム3に搭載されているキャッシュ32の各ラインのサイズ(容量)、キャッシュライン数などのキャッシュ情報を設定するが、この具体例では、キャッシュ32は、データキャッシュ、1キャッシュライン当たり32Byte×512ライン、1次キャッシュのみとする。キャッシュ情報設定部21へのキャッシュ情報の入力は、ユーザ入力などにより手動で行うほか、システムが用意するI/F(Interface)経由などで自動的に行うように構成してもよい。

【0017】

次に動作について説明する。

図2は、この発明の実施の形態1による画像処理装置の動作を示すフローチャートである。

メモリ割付部23は、画像情報設定部22が設定した画像情報を取得し(ステップST1)、取得した画像情報の画像のサイズ(画素数)に基づいてプラットホーム3のメモリ31上に画像領域31a(図1参照)を確保する(ステップST2)。さらにメモリ割付部23は、ステップST2で確保した画像領域31aに画像データを入力する(ステップST3)。ステップST3で画像データが入力されると、画像処理プログラム1は、SAR画像再生処理に必要なパラメータの計算を行い(ステップST4)、レンジ方向の処理であるレンジ圧縮処理を画像領域31a上で行う(ステップST5)。

【0018】

次に、メモリ割付部23は、キャッシュ情報設定部21が設定したキャッシュ情報を取得し(ステップST6)、取得したキャッシュ情報と、ステップST1で取得した画像情報とに基づいて作業領域31b(図1参照)の領域サイズを算出する(ステップST7)。この領域サイズは、キャッシュミスが最小限になるよう、キャッシュの1ラインのByte数の整数倍と画像データのアジマス方向のByte数を掛けたサイズとなる。ここでは、キャッシュの1ラインのByte数の整数倍を1倍とする。従って、32Byte×163840Byte(20480画素×8Byte)となる。

【0019】

メモリ割付部23は、ステップST7で算出したサイズの作業領域31bをプラットホーム3のメモリ31上に確保する(ステップST8)。画像処理プログラム1は、ステップST8で確保した作業領域31bを用いてアジマス方向の処理であるアジマス圧縮を行い(ステップST9)、処理を終了する。

【0020】

次に、上述したステップST9で示した作業領域31bを用いたアジマス圧縮処理の動作について図3のフローチャートを参照しながら説明する。

画像処理プログラム1は、画像領域31aに入力された画像データについて、レンジ方向の先頭から順に作業領域31bへそのサイズ分のデータを移動させる(ステップST91)。作業領域31b内のデータに対してアジマス圧縮処理を行う(ステップST92)。ここでは、作業領域が32Byteで4画素分となるので、4つのアジマス方向のデータに対してアジマス圧縮処理を行う。次に、ステップST92の処理結果を作業領域31bから画像領域31aの元の領域に移動させる(ステップST93)。

【0021】

なお、上述したステップST91からステップST93の処理を、レンジ方向に順にずらしながら全ての画像データについて処理するまで繰り返す。すなわち、レンジ方向の画素数20480を作業領域31bのレンジ方向のサイズ4で割った回数である5120回繰り返す。そのため、画像処理プログラム1は、ステップST93の処理を行うと、全ての画像データについて処理を行ったか判定を行う(ステップST94)。全ての画像データについて処理を行っていないと判定された場合(ステップST94;NO)、ステップST91の処理に戻り、上述した処理を繰り返す。一方、全ての画像データについて処理を行ったと判定された場合(ステップST94;YES)、処理を終了する。

【0022】

次に画像領域31aから作業領域31bへのデータ移動について図4から図7を参照しながら説明する。図4は画像領域から作業領域へのデータ移動を示す説明図であり、図4(a)はその全体図、図4(b)は詳細図である。

図4(a)では画像領域31aの先頭の4画素分のアジマス方向のデータAを作業領域31bへデータ移動させる場合を示している。画像領域31aのデータは、レンジ方向にアドレスが連続するよう画素データが格納されている。図4(b)は、4画素分のアジマス方向のデータAのデータ内容を示している。各々数値が記載されている四角が1画素を表しており、画像領域31aと作業領域31bにおける同一の数値はそれぞれで対応する同じ画素データを表している。

【0023】

図5は、画像領域から作業領域へのデータ移動の際のキャッシュを示す説明図である。まず図5(a)は、画素11から画素44までのデータの移動の際の画像領域と作業領域のキャッシュラインの様子を示したものである。まず画像領域31aの画素11をリードすると、初めてのアクセスなのでキャッシュミスとなり、メモリ31からキャッシュ32へ画素11を含む1キャッシュライン分のデータ(11,12,13,14)が読み込まれる。そのデータを作業領域31bの「11」の場所へ書き込むが、これも初めてのアクセスなのでキャッシュミスとなり、メモリ31からキャッシュ32へ画素11の場所を含む1キャッシュライン分のデータ読み込まれ、キャッシュ32上で画素11のデータが書き込まれる。

【0024】

次に画像領域31aの画素12をリードすると、既にキャッシュ32へデータが読み込まれているのでメモリ31へのアクセスは発生しない。このデータを作業領域の「12」の場所へ書き込むが、これは初めてのアクセスなのでキャッシュミスとなり、メモリ31からキャッシュ32へ画素12の場所を含む1キャッシュライン分のデータ読み込まれ、キャッシュ32上で画素12のデータが書き込まれる。画素13,14についても、動作は同様である。

【0025】

次に画像領域の画素21をリードすると、初めてのアクセスなのでキャッシュミスとなり、メモリからキャッシュへ画素21を含む1キャッシュライン分のデータ(21,22,23,24)が読み込まれる。そのデータを作業領域の21の場所へ書き込むが、この部分は上述の画素11の書き込みにおいて既にキャッシュ32へ読み込まれているのでメモリ31へのアクセスは発生せず、キャッシュ32への書き込みだけとなる。そして、画素22,23,24は、画像領域31aおよび作業領域31bにおいて、既にキャッシュ32に読み込まれているので、メモリ31へのアクセスは発生しない。

【0026】

同様に、画素31および画素41は、画像領域31aではキャッシュミスを起こすが、作業領域31bではキャッシュヒットし、メモリ31へのアクセスは発生しない。また、画素32,33,34、42,43,44は、画像領域31aおよび作業領域31bにおいて、既にキャッシュ32に読み込まれているので、メモリ31へアクセスは発生しない。

【0027】

図5(b)は、画素51以降のデータの移動の際の画像領域31aと作業領域31bのキャッシュラインの様子を示したものである。

画像領域31aの画素51をリードすると、初めてのアクセスなのでキャッシュミスとなり、メモリ31からキャッシュ32へ画素51を含む1キャッシュライン分のデータ(51,52,53,54)が読み込まれる。そのデータを作業領域31bの「51」の場所へ書き込むが、これも初めてのアクセスなのでキャッシュミスとなり、メモリ31からキャッシュ32へ画素51の場所を含む1キャッシュライン分のデータ読み込まれ、キャッシュ32上で画素51のデータが書き込まれる。

【0028】

次に画像領域31aの画素52をリードすると、既にキャッシュ32へデータが読み込まれているのでメモリ31へのアクセスは発生しない。このデータを作業領域の52の場所へ書き込むが、これは初めてのアクセスなのでキャッシュミスとなり、メモリ31からキャッシュ32へ画素52の場所を含む1キャッシュライン分のデータ読み込まれ、キャッシュ32上で画素52のデータが書き込まれる。画素53および画素54についても、動作は同様である。

【0029】

次に画像領域31aの画素61をリードすると、初めてのアクセスなのでキャッシュミスとなり、メモリ31からキャッシュ32へ画素61を含む1キャッシュライン分のデータ(61,62,63,64)が読み込まれる。そのデータを作業領域31bの「61」の場所へ書き込むが、この部分は先ほどの画素51の書き込みにおいて既にキャッシュ32へ読み込まれているのでメモリ31へのアクセスは発生せず、キャッシュ32への書き込みだけとなる。そして、画素62,63,64は、画像領域31aおよび作業領域31bにおいて、既にキャッシュ32に読み込まれているので、メモリ31へのアクセスは発生しない。

【0030】

同様に、画素71および画素81は、画像領域31aではキャッシュミスを起こすが、作業領域31bではキャッシュヒットし、メモリ31へのアクセスは発生しない。また、画素72,73,74、82,83,84は、画像領域31aでも作業領域31bでも、既にキャッシュ32に読み込まれているので、メモリ31へアクセスは発生しない。画素91以降のデータ移動の動作も同様である。

【0031】

以上のように、この実施の形態1によれば、作業領域31bのサイズを「1キャッシュラインのデータサイズの整数倍×アジマス方向のデータサイズ」として算出し、算出したサイズの作業領域31bをメモリ31上に確保するメモリ割付部23を備え、画像領域31aから当該作業領域31bに画像データを移動してアジマス方向の処理であるアジマス圧縮を行うように構成したので、少ないメモリ容量でアジマス圧縮処理を行うことができ、さらに画像領域31aから作業領域31bに画像データを移動させる際にキャッシュヒットしてデータ移動の時間が抑制され、高速に画像処理を行うことができる。これにより、画像処理装置の小型化を実現することができる。

【0032】

なお、上述した実施の形態1では、画像のサイズ(画素数)および各画素のデータサイズを具体例を用いて説明したが、上述した数値に限定されるものではなく、適宜変更可能である。

【0033】

また、上述した実施の形態1では、画像領域のアジマス方向に並ぶデータを作業領域の行方向に並べる構成を示したが、画像領域のレンジ方向に並ぶデータを作業領域の列方向に並べるように構成してもよい。

【0034】

また、上述した実施の形態1では、画像処理プログラム1がSAR画像の再生処理を実行する構成を示したが、SAR画像の再生処理に限定されるものではなく、光学画像(例えば、一般のカメラで撮影された画像)における雑音除去などで行われるウェーブレット変換などにも適用可能である。

【0035】

なお、本願発明はその発明の範囲内において、実施の形態の任意の構成要素の変形、もしくは実施の形態の任意の構成要素の省略が可能である。

【符号の説明】

【0036】

1 画像処理プログラム、2 画像処理装置、3 プラットホーム、21 キャッシュ情報設定部、22 画像情報設定部、23 メモリ割付部、31 メモリ、31a 画像領域、31b 作業領域、32 キャッシュ、33 CPU、A データ。

【技術分野】

【0001】

この発明は、二次元の画像に対して、行方向と列方向の処理を行う画像処理装置に関するものである。

【背景技術】

【0002】

二次元の画像に対して、行方向と列方向の処理を行う画像処理の1つに、SAR(Synthetic Aperture Radar:合成開口レーダ)画像の再生処理がある。SAR画像再生処理は、非特許文献1に記載されているように、前半でレンジ方向の処理であるレンジ圧縮を行い、後半でアジマス方向の処理であるアジマス圧縮を行う。

【0003】

SAR画像再生処理をPCやワークステーションなどの汎用のコンピュータで行う場合は、キャッシュ機構を備えたメモリ上にデータを格納するため、連続したアドレス順にデータをアクセスする場合はキャッシュがヒットして高速に処理を行うことができるが、連続していないアドレス順でデータをアクセスする場合はキャッシュミスを起こして低速となる。すなわち、処理する方向にデータが格納されている場合には高速で処理することができるが、処理する方向にデータが格納されていない場合には処理が低速になってしまう。

【0004】

この問題を解決する方法として、特許文献1には前半のレンジ方向の処理と後半のアジマス方向の処理の間に、メモリ上のデータの行と列(縦横)を入れ替える(転置する)コーナーターンを行い、このコーナーターンの際にキャッシュミスが発生しないように、正方形のブロック単位でメモリ上のデータを転置する方法が開示されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特許第3850599号公報

【非特許文献】

【0006】

【非特許文献1】飯坂譲二監修、日本写真測量学会編、「合成開口レーダ画像ハンドブック」朝倉書店、1998年5月20日 初版第1刷

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、上述した特許文献1に開示された技術では、コーナーターンにおいて、レンジとアジマス(横と縦)の二つの方向にデータを格納するので、本来の画像のデータ量に対して、2倍のメモリ量が必要となり、装置に大容量メモリを搭載する必要があるという課題があった。さらに大容量メモリを搭載することにより装置が大型化するという課題があった。

【0008】

この発明は、上記のような課題を解決するためになされたもので、少ないメモリ容量で高速な処理を行う画像処理装置を得ることを目的とする。

【課題を解決するための手段】

【0009】

この発明に係る画像処理装置は、処理対象画像のサイズおよび各画素のデータサイズなどの画像情報を設定する画像情報設定部と、プラットホームに搭載されたキャッシュの構成およびサイズなどのキャッシュ情報を設定するキャッシュ情報設定部と、画像情報設定部が設定した画像情報から、処理対象画像の行方向のデータサイズおよび列方向のデータサイズを特定し、当該行方向および列方向のデータサイズを有する画像領域を生成すると共に、画像情報設定部が設定した画像情報およびキャッシュ情報設定部が設定したキャッシュ情報から、所定のサイズを行方向のデータサイズとし、処理対象画像の行方向のデータサイズを列方向のデータサイズとした作業領域を生成し、生成した画像領域および作業領域を画像処理プログラムに割り付けるメモリ割付部とを備えたものである。

【発明の効果】

【0010】

この発明によれば、少ないメモリ容量で、高速に画像処理を行うことができる。

【図面の簡単な説明】

【0011】

【図1】実施の形態1による画像処理装置の構成を示すブロック図である。

【図2】実施の形態1による画像処理装置の動作を示すフローチャートである。

【図3】実施の形態1による画像処理装置のアジマス圧縮処理を示すフローチャートである。

【図4】実施の形態1による画像処理装置の画像領域から作業領域へのデータ移動を示す。

【図5】実施の形態1による画像処理装置の画像領域から作業領域へのデータ移動の際のキャッシュを示す説明図である。

【発明を実施するための形態】

【0012】

実施の形態1.

実施の形態1に係る画像処理装置について、図1から図7を参照しながら説明する。図1は、この発明の実施の形態1による画像処理装置の構成を示すブロック図である。図1において、画像処理プログラム1は、SAR画像の再生処理を実行する。画像処理装置2は、プラットホーム3上で動作し、画像データのメモリへの割り付け方法などを画像処理プログラム1に指示する。プラットホーム3は、メモリ31、キャッシュ32およびCPU33などにより構成される。

【0013】

また、図1に示した画像処理装置2は、キャッシュ情報設定部21、画像情報設定部22およびメモリ割付部23で構成されている。

キャッシュ情報設定部21は、キャッシュ32の構成やサイズなどキャッシュ情報を設定する。画像情報設定部22は、処理対象となる画像のサイズ(画素数)および各画素のデータサイズを設定する。メモリ割付部23は、キャッシュ情報設定部21および画像情報設定部22からキャッシュ情報および画像情報を取得し、1キャッシュラインのデータサイズの整数倍×アジマス方向のデータサイズ(画素数×1画素当たりのByte数)を作業領域のサイズとして算出し、算出したサイズの作業領域をメモリ31上に割り付けるように画像処理プログラム1に指示する。

【0014】

なお以下の説明では、処理対象画像を、1画素当たり8Byte、画像サイズはレンジ方向、アジマス方向とも20480画素と仮定する。また、プラットホーム3に搭載されているキャッシュ32は、データキャッシュ、1キャッシュライン当たり32Byte×512ライン、1次キャッシュのみを仮定する。

【0015】

画像情報設定部22は、処理対象画像の情報として、画像のサイズ(画素数)、各画素のデータサイズなどを設定するが、この具体例では、1画素当たり8Byte、画像サイズはレンジ方向20480画素×アジマス方向20480画素という情報を設定する。画像情報設定部22への画像情報の入力は、ユーザ入力などにより手動で行うほか、画像データや画像処理プログラム1から自動的に行うように構成してもよい。

【0016】

キャッシュ情報設定部21は、プラットホーム3に搭載されているキャッシュ32の各ラインのサイズ(容量)、キャッシュライン数などのキャッシュ情報を設定するが、この具体例では、キャッシュ32は、データキャッシュ、1キャッシュライン当たり32Byte×512ライン、1次キャッシュのみとする。キャッシュ情報設定部21へのキャッシュ情報の入力は、ユーザ入力などにより手動で行うほか、システムが用意するI/F(Interface)経由などで自動的に行うように構成してもよい。

【0017】

次に動作について説明する。

図2は、この発明の実施の形態1による画像処理装置の動作を示すフローチャートである。

メモリ割付部23は、画像情報設定部22が設定した画像情報を取得し(ステップST1)、取得した画像情報の画像のサイズ(画素数)に基づいてプラットホーム3のメモリ31上に画像領域31a(図1参照)を確保する(ステップST2)。さらにメモリ割付部23は、ステップST2で確保した画像領域31aに画像データを入力する(ステップST3)。ステップST3で画像データが入力されると、画像処理プログラム1は、SAR画像再生処理に必要なパラメータの計算を行い(ステップST4)、レンジ方向の処理であるレンジ圧縮処理を画像領域31a上で行う(ステップST5)。

【0018】

次に、メモリ割付部23は、キャッシュ情報設定部21が設定したキャッシュ情報を取得し(ステップST6)、取得したキャッシュ情報と、ステップST1で取得した画像情報とに基づいて作業領域31b(図1参照)の領域サイズを算出する(ステップST7)。この領域サイズは、キャッシュミスが最小限になるよう、キャッシュの1ラインのByte数の整数倍と画像データのアジマス方向のByte数を掛けたサイズとなる。ここでは、キャッシュの1ラインのByte数の整数倍を1倍とする。従って、32Byte×163840Byte(20480画素×8Byte)となる。

【0019】

メモリ割付部23は、ステップST7で算出したサイズの作業領域31bをプラットホーム3のメモリ31上に確保する(ステップST8)。画像処理プログラム1は、ステップST8で確保した作業領域31bを用いてアジマス方向の処理であるアジマス圧縮を行い(ステップST9)、処理を終了する。

【0020】

次に、上述したステップST9で示した作業領域31bを用いたアジマス圧縮処理の動作について図3のフローチャートを参照しながら説明する。

画像処理プログラム1は、画像領域31aに入力された画像データについて、レンジ方向の先頭から順に作業領域31bへそのサイズ分のデータを移動させる(ステップST91)。作業領域31b内のデータに対してアジマス圧縮処理を行う(ステップST92)。ここでは、作業領域が32Byteで4画素分となるので、4つのアジマス方向のデータに対してアジマス圧縮処理を行う。次に、ステップST92の処理結果を作業領域31bから画像領域31aの元の領域に移動させる(ステップST93)。

【0021】

なお、上述したステップST91からステップST93の処理を、レンジ方向に順にずらしながら全ての画像データについて処理するまで繰り返す。すなわち、レンジ方向の画素数20480を作業領域31bのレンジ方向のサイズ4で割った回数である5120回繰り返す。そのため、画像処理プログラム1は、ステップST93の処理を行うと、全ての画像データについて処理を行ったか判定を行う(ステップST94)。全ての画像データについて処理を行っていないと判定された場合(ステップST94;NO)、ステップST91の処理に戻り、上述した処理を繰り返す。一方、全ての画像データについて処理を行ったと判定された場合(ステップST94;YES)、処理を終了する。

【0022】

次に画像領域31aから作業領域31bへのデータ移動について図4から図7を参照しながら説明する。図4は画像領域から作業領域へのデータ移動を示す説明図であり、図4(a)はその全体図、図4(b)は詳細図である。

図4(a)では画像領域31aの先頭の4画素分のアジマス方向のデータAを作業領域31bへデータ移動させる場合を示している。画像領域31aのデータは、レンジ方向にアドレスが連続するよう画素データが格納されている。図4(b)は、4画素分のアジマス方向のデータAのデータ内容を示している。各々数値が記載されている四角が1画素を表しており、画像領域31aと作業領域31bにおける同一の数値はそれぞれで対応する同じ画素データを表している。

【0023】

図5は、画像領域から作業領域へのデータ移動の際のキャッシュを示す説明図である。まず図5(a)は、画素11から画素44までのデータの移動の際の画像領域と作業領域のキャッシュラインの様子を示したものである。まず画像領域31aの画素11をリードすると、初めてのアクセスなのでキャッシュミスとなり、メモリ31からキャッシュ32へ画素11を含む1キャッシュライン分のデータ(11,12,13,14)が読み込まれる。そのデータを作業領域31bの「11」の場所へ書き込むが、これも初めてのアクセスなのでキャッシュミスとなり、メモリ31からキャッシュ32へ画素11の場所を含む1キャッシュライン分のデータ読み込まれ、キャッシュ32上で画素11のデータが書き込まれる。

【0024】

次に画像領域31aの画素12をリードすると、既にキャッシュ32へデータが読み込まれているのでメモリ31へのアクセスは発生しない。このデータを作業領域の「12」の場所へ書き込むが、これは初めてのアクセスなのでキャッシュミスとなり、メモリ31からキャッシュ32へ画素12の場所を含む1キャッシュライン分のデータ読み込まれ、キャッシュ32上で画素12のデータが書き込まれる。画素13,14についても、動作は同様である。

【0025】

次に画像領域の画素21をリードすると、初めてのアクセスなのでキャッシュミスとなり、メモリからキャッシュへ画素21を含む1キャッシュライン分のデータ(21,22,23,24)が読み込まれる。そのデータを作業領域の21の場所へ書き込むが、この部分は上述の画素11の書き込みにおいて既にキャッシュ32へ読み込まれているのでメモリ31へのアクセスは発生せず、キャッシュ32への書き込みだけとなる。そして、画素22,23,24は、画像領域31aおよび作業領域31bにおいて、既にキャッシュ32に読み込まれているので、メモリ31へのアクセスは発生しない。

【0026】

同様に、画素31および画素41は、画像領域31aではキャッシュミスを起こすが、作業領域31bではキャッシュヒットし、メモリ31へのアクセスは発生しない。また、画素32,33,34、42,43,44は、画像領域31aおよび作業領域31bにおいて、既にキャッシュ32に読み込まれているので、メモリ31へアクセスは発生しない。

【0027】

図5(b)は、画素51以降のデータの移動の際の画像領域31aと作業領域31bのキャッシュラインの様子を示したものである。

画像領域31aの画素51をリードすると、初めてのアクセスなのでキャッシュミスとなり、メモリ31からキャッシュ32へ画素51を含む1キャッシュライン分のデータ(51,52,53,54)が読み込まれる。そのデータを作業領域31bの「51」の場所へ書き込むが、これも初めてのアクセスなのでキャッシュミスとなり、メモリ31からキャッシュ32へ画素51の場所を含む1キャッシュライン分のデータ読み込まれ、キャッシュ32上で画素51のデータが書き込まれる。

【0028】

次に画像領域31aの画素52をリードすると、既にキャッシュ32へデータが読み込まれているのでメモリ31へのアクセスは発生しない。このデータを作業領域の52の場所へ書き込むが、これは初めてのアクセスなのでキャッシュミスとなり、メモリ31からキャッシュ32へ画素52の場所を含む1キャッシュライン分のデータ読み込まれ、キャッシュ32上で画素52のデータが書き込まれる。画素53および画素54についても、動作は同様である。

【0029】

次に画像領域31aの画素61をリードすると、初めてのアクセスなのでキャッシュミスとなり、メモリ31からキャッシュ32へ画素61を含む1キャッシュライン分のデータ(61,62,63,64)が読み込まれる。そのデータを作業領域31bの「61」の場所へ書き込むが、この部分は先ほどの画素51の書き込みにおいて既にキャッシュ32へ読み込まれているのでメモリ31へのアクセスは発生せず、キャッシュ32への書き込みだけとなる。そして、画素62,63,64は、画像領域31aおよび作業領域31bにおいて、既にキャッシュ32に読み込まれているので、メモリ31へのアクセスは発生しない。

【0030】

同様に、画素71および画素81は、画像領域31aではキャッシュミスを起こすが、作業領域31bではキャッシュヒットし、メモリ31へのアクセスは発生しない。また、画素72,73,74、82,83,84は、画像領域31aでも作業領域31bでも、既にキャッシュ32に読み込まれているので、メモリ31へアクセスは発生しない。画素91以降のデータ移動の動作も同様である。

【0031】

以上のように、この実施の形態1によれば、作業領域31bのサイズを「1キャッシュラインのデータサイズの整数倍×アジマス方向のデータサイズ」として算出し、算出したサイズの作業領域31bをメモリ31上に確保するメモリ割付部23を備え、画像領域31aから当該作業領域31bに画像データを移動してアジマス方向の処理であるアジマス圧縮を行うように構成したので、少ないメモリ容量でアジマス圧縮処理を行うことができ、さらに画像領域31aから作業領域31bに画像データを移動させる際にキャッシュヒットしてデータ移動の時間が抑制され、高速に画像処理を行うことができる。これにより、画像処理装置の小型化を実現することができる。

【0032】

なお、上述した実施の形態1では、画像のサイズ(画素数)および各画素のデータサイズを具体例を用いて説明したが、上述した数値に限定されるものではなく、適宜変更可能である。

【0033】

また、上述した実施の形態1では、画像領域のアジマス方向に並ぶデータを作業領域の行方向に並べる構成を示したが、画像領域のレンジ方向に並ぶデータを作業領域の列方向に並べるように構成してもよい。

【0034】

また、上述した実施の形態1では、画像処理プログラム1がSAR画像の再生処理を実行する構成を示したが、SAR画像の再生処理に限定されるものではなく、光学画像(例えば、一般のカメラで撮影された画像)における雑音除去などで行われるウェーブレット変換などにも適用可能である。

【0035】

なお、本願発明はその発明の範囲内において、実施の形態の任意の構成要素の変形、もしくは実施の形態の任意の構成要素の省略が可能である。

【符号の説明】

【0036】

1 画像処理プログラム、2 画像処理装置、3 プラットホーム、21 キャッシュ情報設定部、22 画像情報設定部、23 メモリ割付部、31 メモリ、31a 画像領域、31b 作業領域、32 キャッシュ、33 CPU、A データ。

【特許請求の範囲】

【請求項1】

プロセッサ、メモリおよびキャッシュを含むプラットホーム上で動作し、二次元の画像に対して行方向および列方向の処理を行う画像処理プログラムに、所定の領域の割り付けを指示する画像処理装置において、

処理対象画像のサイズおよび各画素のデータサイズなどの画像情報を設定する画像情報設定部と、

前記プラットホームに搭載された前記キャッシュの構成およびサイズなどのキャッシュ情報を設定するキャッシュ情報設定部と、

前記画像情報設定部が設定した画像情報から、前記処理対象画像の行方向のデータサイズおよび列方向のデータサイズを特定し、当該行方向および列方向のデータサイズを有する画像領域を生成すると共に、前記画像情報設定部が設定した画像情報および前記キャッシュ情報設定部が設定したキャッシュ情報から、所定のサイズを行方向のデータサイズとし、前記処理対象画像の行方向のデータサイズを列方向のデータサイズとした作業領域を生成し、生成した前記画像領域および前記作業領域を前記画像処理プログラムに割り付けるメモリ割付部とを備えたことを特徴とする画像処理装置。

【請求項2】

前記メモリ割付部は、1キャッシュラインのデータサイズの整数倍を行方向のデータサイズとし、前記処理対象画像の行方向のデータサイズを列方向のデータサイズとした作業領域を生成することを特徴とする請求項1記載の画像処理装置。

【請求項3】

前記画像処理プログラムは、前記画像領域内の処理対象画像から前記作業領域のデータサイズ分の処理対象画像を取得して前記作業領域に移動させ、当該作業領域において前記列方向の処理を行い、前記全ての処理対象画像に対して前記列方向の処理を実行するまで、前記作業領域への処理対象画像の移動を繰り返し行うことを特徴とする請求項1または請求項2記載の画像処理装置。

【請求項1】

プロセッサ、メモリおよびキャッシュを含むプラットホーム上で動作し、二次元の画像に対して行方向および列方向の処理を行う画像処理プログラムに、所定の領域の割り付けを指示する画像処理装置において、

処理対象画像のサイズおよび各画素のデータサイズなどの画像情報を設定する画像情報設定部と、

前記プラットホームに搭載された前記キャッシュの構成およびサイズなどのキャッシュ情報を設定するキャッシュ情報設定部と、

前記画像情報設定部が設定した画像情報から、前記処理対象画像の行方向のデータサイズおよび列方向のデータサイズを特定し、当該行方向および列方向のデータサイズを有する画像領域を生成すると共に、前記画像情報設定部が設定した画像情報および前記キャッシュ情報設定部が設定したキャッシュ情報から、所定のサイズを行方向のデータサイズとし、前記処理対象画像の行方向のデータサイズを列方向のデータサイズとした作業領域を生成し、生成した前記画像領域および前記作業領域を前記画像処理プログラムに割り付けるメモリ割付部とを備えたことを特徴とする画像処理装置。

【請求項2】

前記メモリ割付部は、1キャッシュラインのデータサイズの整数倍を行方向のデータサイズとし、前記処理対象画像の行方向のデータサイズを列方向のデータサイズとした作業領域を生成することを特徴とする請求項1記載の画像処理装置。

【請求項3】

前記画像処理プログラムは、前記画像領域内の処理対象画像から前記作業領域のデータサイズ分の処理対象画像を取得して前記作業領域に移動させ、当該作業領域において前記列方向の処理を行い、前記全ての処理対象画像に対して前記列方向の処理を実行するまで、前記作業領域への処理対象画像の移動を繰り返し行うことを特徴とする請求項1または請求項2記載の画像処理装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2012−247843(P2012−247843A)

【公開日】平成24年12月13日(2012.12.13)

【国際特許分類】

【出願番号】特願2011−117056(P2011−117056)

【出願日】平成23年5月25日(2011.5.25)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

【公開日】平成24年12月13日(2012.12.13)

【国際特許分類】

【出願日】平成23年5月25日(2011.5.25)

【出願人】(000006013)三菱電機株式会社 (33,312)

【Fターム(参考)】

[ Back to top ]