画像処理装置

【課題】画像データの処理効率を改善する画像処理装置を提供する。

【解決手段】矩形領域を構成する第1領域と第2領域と第3領域と第4領域とのうち第2領域、第3領域および第4領域の所定方向の幅に対しては所定の画素数が割り当てられている、矩形領域を記憶領域としてデータを格納するメモリを有する。第1領域と、第2領域と、第3領域もしくは第4領域とのそれぞれに格納されたデータに対して所定の処理を行。所定の処理前に、第1領域と第2領域それぞれにデータを格納し、かつ、第2領域に格納したデータと同じデータを第3領域または第4領域に格納する。第3領域にデータを格納した場合、処理されるべき領域として第1領域、第2領域及び第4領域を選択し、第4領域にデータを格納した場合、処理されるべき領域として第1領域、第2領域及び第3領域を選択する。

【解決手段】矩形領域を構成する第1領域と第2領域と第3領域と第4領域とのうち第2領域、第3領域および第4領域の所定方向の幅に対しては所定の画素数が割り当てられている、矩形領域を記憶領域としてデータを格納するメモリを有する。第1領域と、第2領域と、第3領域もしくは第4領域とのそれぞれに格納されたデータに対して所定の処理を行。所定の処理前に、第1領域と第2領域それぞれにデータを格納し、かつ、第2領域に格納したデータと同じデータを第3領域または第4領域に格納する。第3領域にデータを格納した場合、処理されるべき領域として第1領域、第2領域及び第4領域を選択し、第4領域にデータを格納した場合、処理されるべき領域として第1領域、第2領域及び第3領域を選択する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像データを処理する画像処理装置に関する。

【背景技術】

【0002】

従来、記録ヘッドからインクを吐出して記録媒体に記録するインクジェット記録装置が知られている。一般的に、インクジェット記録装置は、記録ヘッドおよびインクタンクを搭載したキャリッジと、記録媒体を搬送する搬送機構と、それらの動作を制御する制御構成とを備えている。インクジェット記録装置は、記録ヘッドを記録媒体の搬送方向(副走査方向)と交差する方向(主走査方向)に走査させながらインクを吐出し、各走査間において記録媒体を間欠搬送する。複数回の走査と間欠搬送によって、インクジェット記録装置は記録媒体上の全画像領域の記録を行なうことができる。また、記録ヘッドには複数種類のインク色に応じた複数のノズル列を備えており、各ノズル列から吐出されるインク滴を重ねあわせる若しくは近接して着弾することによって、カラー画像を記録することができる。インクジェット記録装置は、比較的容易で優れた記録方法として幅広い産業分野で需要が高まっており、記録速度のさらなる高速化や、より一層の高品位画像が要求されている。そのような要求に応じて、近年のインクジェット記録装置の記録ヘッドはますます高精細化、多ノズル化が実現されている。

【0003】

上記のような動きの中、単位時間あたりに要求されるデータ処理量もますます多くなってきており、インクジェット記録装置の画像データ処理系の高速化も要求されてきている。特許文献1には、画像データ処理系の高速化を図るために、各画像処理部からのアクセスのみを専用に受け付ける画像処理専用SRAMを設けた構成が記載されている。特許文献1では、そのような構成により、ホスト装置から受信して画像データを格納したDRAMに各画像処理部がアクセスする構成よりも高速化を図ることができると記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2002−248813号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記の画像処理部には、例えば、スムージング処理がある。スムージング処理とは、記録しようとする画素(注目画素)に対してその注目画素を囲む周辺領域(例えば11×9画素)のデータを参照し、その結果に応じて注目画素を変更するものである。その際には、ドット群で構成される図形の輪郭がスムースに記録されるような画像データに変更される。

【0006】

従って、スムージング処理においては、注目画素の周辺領域の画素データを参照して、その特徴を調べる必要があるので、実際の処理対象領域よりも大きい領域をDRAMから画像処理専用SRAMに予め読み出しておく必要がある。また、注目画素に対して参照する領域のデータはスムージング処理によって変更される前のデータであることが必要である。

【0007】

ここで、画像データを予め定められた単位領域で順に処理を行っていく場合を考えると、n回目の処理を行なう際に、参照のための周辺領域分、(n−1)回目の処理と重複する領域が存在してしまう。また、(n−1)回目の処理の際に使用したデータは既に画素情報が変更されてしまっているので、n回目の処理の際に周辺領域の参照のためにデータを再使用することができない。従って、少なくともその重複する領域分について、データが変更されていない画像データを、再度、DRAMから読み出す必要が生じてしまう。

【0008】

しかしながら、通常は、画像処理専用SRAMで処理された画像データはDRAMに書き戻されるので、上記の実現のためには、DRAM内でホスト装置から受信した画像データを重複して格納しておくか、ホスト装置からその都度、画像データを受信する必要がある。

【0009】

本発明の目的は、このような従来の問題点を解決することにある。本発明は、上記の点に鑑み、画像データの処理効率を改善する画像処理装置を提供することを目的とする。

【課題を解決するための手段】

【0010】

上記課題を解決するため、本発明に係る画像処理装置は、矩形領域を構成する第1領域と第2領域と第3領域と第4領域とのうち前記第2領域、前記第3領域および前記第4領域の所定方向の幅に対しては所定の画素数が割り当てられている、前記矩形領域を記憶領域としてデータを格納するメモリと、前記第1領域と、前記第2領域と、前記第3領域もしくは前記第4領域と、のそれぞれに格納されたデータに対して所定の処理を行う処理手段と、前記処理手段が前記所定の処理を行う前に、前記第1領域と前記第2領域それぞれにデータを格納し、かつ、前記第2領域に格納したデータと同じデータを前記第3領域または前記第4領域に格納する格納手段と、前記格納手段が前記第3領域にデータを格納した場合には、前記処理手段により処理されるべき領域として、前記第1領域、前記第2領域および前記第4領域を選択し、前記格納手段が前記第4領域にデータを格納した場合には、前記処理手段により処理されるべき領域として、前記第1領域、前記第2領域および前記第3領域を選択する選択手段と、を備えることを特徴とする。

【発明の効果】

【0011】

本発明によれば、画像データの処理効率を改善することができる。

【図面の簡単な説明】

【0012】

【図1】インクジェット記録装置の構成の概要を示す外観斜視図である。

【図2】インクジェット記録装置の制御構成を示すブロック図である。

【図3】インクジェット記録装置の記録部の概略構成を示す斜視図である。

【図4】インクジェット記録装置の画像処理部周辺の構成を示すブロック図である。

【図5】画像処理専用メモリコントローラの内部構成を示すブロック図である。

【図6】画像処理専用メモリコントローラ周辺の接続構成を示す図である。

【図7】各ブロック間でのデータアクセスの際のタイミングチャート図である。

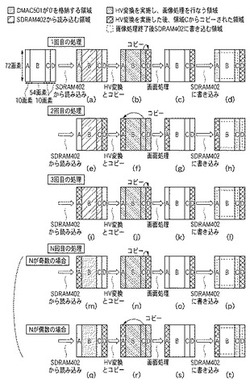

【図8】本実施例における画像処理の手順を説明するための図である。

【図9】本実施例における画像処理の手順を説明するための他の図である。

【図10】SRAMの他の構成例を示す図である。

【図11】スムージング処理を説明するための第1の図である。

【図12】スムージング処理を説明するための第2の図である。

【図13】スムージング処理を説明するための第3の図である。

【図14】スムージング処理を説明するための第4の図である。

【図15】スムージング処理を説明するための第5の図である。

【発明を実施するための形態】

【0013】

以下、添付図面を参照して本発明の好適な実施例を詳しく説明する。尚、以下の実施例は特許請求の範囲に係る本発明を限定するものでなく、また本実施例で説明されている特徴の組み合わせの全てが本発明の解決手段に必須のものとは限らない。なお、同一の構成要素には同一の参照番号を付して、説明を省略する。

【0014】

<インクジェット記録装置の説明>

図1は本発明の代表的な実施例であるインクジェット記録装置の構成の概要を示す外観斜視図である。

【0015】

図1に示すように、インクジェット記録装置100は、インクジェット方式に従ってインクを吐出して記録を行なう記録ヘッド103を搭載したキャリッジ102にキャリッジモータM1によって発生する駆動力を伝達機構104より伝え、キャリッジ102を矢印A方向に往復移動させるとともに、例えば、記録紙などの記録媒体Pを給紙機構105を介して給紙し、記録位置まで搬送し、その記録位置において記録ヘッド103から記録媒体Pにインクを吐出することで記録を行なう。

【0016】

また、記録ヘッド103の状態を良好に維持するためにキャリッジ102を回復装置110の位置まで移動させ、間欠的に記録ヘッド103の吐出回復処理を行う。

【0017】

インクジェット記録装置100のキャリッジ102には記録ヘッド103を搭載するのみならず、記録ヘッド103に供給するインクを貯留するインクカートリッジ106が装着される。インクカートリッジ106は、キャリッジ102に対して着脱自在になっている。

【0018】

図1に示したインクジェット記録装置100はカラー記録が可能であり、そのためにキャリッジ102は、マゼンタ(M)、シアン(C)、イエロー(Y)、ブラック(K)のインクを夫々、収容した4つのインクカートリッジを搭載している。これら4つのインクカートリッジは夫々独立に着脱可能である。

【0019】

さて、キャリッジ102と記録ヘッド103とは、両部材の接合面が適正に接触されて所要の電気的接続を達成維持できるようになっている。記録ヘッド103は、記録信号に応じてエネルギーを印加することにより、複数の吐出口からインクを選択的に吐出して記録する。特に、本実施例における記録ヘッド103は、熱エネルギーを利用してインクを吐出するインクジェット方式を採用しており、熱エネルギーを発生するために電気熱変換体を備え、その電気熱変換体に印加される電気エネルギーが熱エネルギーへと変換され、その熱エネルギーをインクに与えることにより生じる膜沸騰による気泡の成長、収縮によって生じる圧力変化を利用して、吐出口よりインクを吐出させる。この電気熱変換体は各吐出口のそれぞれに対応して設けられ、記録信号に応じて対応する電気熱変換体にパルス電圧を印加することによって対応する吐出口からインクを吐出する。

【0020】

図1に示されているように、キャリッジ102はキャリッジモータM1の駆動力を伝達する伝達機構104の駆動ベルト107の一部に連結されており、ガイドシャフト113に沿って矢印A方向に摺動自在に案内支持されるようになっている。従って、キャリッジ102は、キャリッジモータM1の正転及び逆転によってガイドシャフト113に沿って往復移動する。また、キャリッジ102の移動方向(矢印A方向)に沿ってキャリッジ102の位置を示すためのスケール108(CRエンコーダフィルム)が備えられている。この実施例では、スケール108は透明なPETフィルムに必要なピッチで黒色のバーを印刷したものを用いており、その一方はシャーシ109に固着され、他方は板バネ(不図示)で支持されている。

【0021】

また、インクジェット記録装置100には、記録ヘッド103の吐出口(不図示)が形成された吐出口面に対向してプラテン(不図示)が設けられており、キャリッジモータM1の駆動力によって記録ヘッド103を搭載したキャリッジ102が往復移動されると同時に、記録ヘッド103に記録信号を与えてインクを吐出することによって、プラテン上に搬送された記録媒体Pの全幅にわたって記録が行われる。

【0022】

さらに、図1における搬送ローラ114は、記録媒体Pを搬送するために搬送モータM2によって駆動される。また、ピンチローラ115は、バネ(不図示)により記録媒体Pを搬送ローラ114に当接する。また、ピンチローラホルダ116は、ピンチローラ115を回転自在に支持する。また、搬送ローラギヤ117は、搬送ローラ114の一端に固着されている。そして、搬送ローラギヤ117に中間ギヤ(不図示)を介して伝達された搬送モータM2の回転により、搬送ローラ114が駆動される。

【0023】

また、排出ローラ120は、記録ヘッド103によって画像が形成された記録媒体Pをインクジェット記録装置外ヘ排出する。排出ローラ120は、搬送モータM2の回転が伝達されることで駆動されるようになっている。なお、排出ローラ120は、記録媒体Pをバネ(不図示)により圧接する拍車ローラ(不図示)により当接する。拍車ホルダ122は、拍車ローラを回転自在に支持する。

【0024】

また、インクジェット記録装置100には、図1に示されているように、記録ヘッド103を搭載するキャリッジ102の記録動作のための往復運動の範囲外(記録領域外)の所望位置(例えば、ホームポジションに対応する位置)に、記録ヘッド103の吐出不良を回復するための回復装置110が配設されている。

【0025】

回復装置110は、記録ヘッド103の吐出口面をキャッピングするキャッピング機構111と記録ヘッド103の吐出口面をクリーニングするワイピング機構112を備えており、キャッピング機構111による吐出口面のキャッピングに連動して回復装置内の吸引構成(吸引ポンプ等)により吐出口からインクを強制的に排出させ、それによって、記録ヘッド103のインク流路内の粘度の増したインクや気泡等を除去するなどの吐出回復処理を行う。

【0026】

また、非記録動作時等には、記録ヘッド103の吐出口面をキャッピング機構111によりキャッピングすることによって、記録ヘッド103を保護するとともにインクの蒸発や乾燥を防止することができる。一方、ワイピング機構112はキャッピング機構111の近傍に配され、記録ヘッド103の吐出口面に付着したインク液滴を拭き取るようになっている。

【0027】

これらキャッピング機構111及びワイピング機構112により、記録ヘッド103のインク吐出状態を正常に保つことが可能となっている。

【0028】

<インクジェット記録装置の制御構成>

図2は図1に示したインクジェット記録装置100の制御構成を示すブロック図である。

【0029】

図2に示すように、制御部210は、MPU211と、後述する制御シーケンスに対応したプログラム、所要のテーブル、その他の固定データを格納したROM212と、キャリッジモータM1や搬送モータM2の制御、及び、記録ヘッド103の制御のための制御信号を生成する特殊用途集積回路(ASIC)213と、画像データの展開領域やプログラム実行のための作業用領域等を設けたRAM214と、各ブロックを相互に接続してデータの授受を行うシステムバス215と、以下に説明するセンサ群からのアナログ信号を入力してA/D変換し、デジタル信号をMPU211に供給するA/D変換器216とを含んで構成される。

【0030】

また、図2において、ホスト装置200は、画像データの供給源となるコンピュータ(或いは、画像読取り用のリーダやデジタルカメラなど)である。ホスト装置200とインクジェット記録装置100との間ではインタフェース(I/F)201を介して画像データ、コマンド、ステータス信号等を送受信する。

【0031】

さらに、スイッチ群220は、電源スイッチ221、プリント開始を指令するためのプリントスイッチ222、及び記録ヘッド103のインク吐出性能を良好な状態に維持するための処理(回復処理)の起動を指示するための回復スイッチ223など、操作者による指令入力を受けるためのスイッチから構成される。センサ群230は、ホームポジションを検出するためのフォトカプラなどの位置センサ231、環境温度を検出するためにインクジェット記録装置100の適宜の箇所に設けられた温度センサ232等から構成されるインクジェット記録装置100の状態を検出するためのセンサ群である。

【0032】

さらに、キャリッジモータドライバ240は、キャリッジ102を図1に示す矢印A方向に往復走査させるためのキャリッジモータM1を駆動させる。また、搬送モータドライバ250は、記録媒体Pを搬送するための搬送モータM2を駆動させる。

【0033】

ASIC213は、記録ヘッド103による記録走査の際に、ROM212の記憶領域に直接アクセスしながら記録ヘッドに対して記録素子(吐出ヒータ)の駆動データを転送する。

【0034】

なお、図1に示す構成は、インクカートリッジ106と記録ヘッド103とが分離可能な構成であるが、これらが一体的に形成されて交換可能なヘッドカートリッジを構成しても良い。

【0035】

さらに、以下の実施例において、記録ヘッドから吐出される液滴はインクであるとして説明し、さらにインクタンクに収容される液体はインクであるとして説明したが、その収容物はインクに限定されるものではない。例えば、記録画像の定着性や耐水性を高めたり、その画像品質を高めたりするために記録媒体に対して吐出される処理液のようなものがインクタンクに収容されていても良い。

【0036】

以下の実施例は、特にインクジェット記録方式の中でも、インク吐出を行わせるために利用されるエネルギーとして熱エネルギーを発生する構成(例えば電気熱変換体やレーザ光等)を備え、熱エネルギーによりインクの状態変化を生起させる方式を用いることにより記録の高密度化、高精細化が達成できる。

【0037】

さらに、インクジェット記録装置100が記録できる記録媒体の最大幅に対応した長さを有するフルラインタイプの記録ヘッドとしては、上述した明細書に開示されているような複数記録ヘッドの組み合わせによってその長さを満たす構成や、一体的に形成された1個の記録ヘッドとしての構成のいずれでもよい。

【0038】

加えて、上記で説明した記録ヘッド自体に一体的にインクタンクが設けられたカートリッジタイプの記録ヘッドのみならず、装置本体に装着されることで、装置本体との電気的な接続や装置本体からのインクの供給が可能になる交換自在のチップタイプの記録ヘッドを用いてもよい。

【0039】

さらに加えて、本実施例におけるインクジェット記録装置100の形態としては、コンピュータ等の情報処理機器の画像出力端末として一体または別体に設けられるものの他、読取装置等と組み合わせられた複写装置、さらには送受信機能を有するファクシミリ装置の形態を取るものであっても良い。

【0040】

図3は、インクジェット記録装置100の記録部の概略構成を示す斜視図である。同図において、インクカートリッジ301は、ブラック(Bk)、シアン(C)、マゼンタ(M)、イエロー(Y)の4色のインクをそれぞれ個別に貯留するように構成され、複数のインクタンクを一体として構成している。記録ヘッドカートリッジ302は、インクカートリッジ301に貯留される各インクに対応した記録素子列が1色あたり2つ、計8つの記録素子列を収納する。キャリッジ303に、インクカートリッジ301および記録ヘッドカートリッジ302をそれぞれ着脱自在に装着することができる。キャリッジ303は、ガイド軸310と摺動自在に結合することによってガイド軸310に沿って移動することができる。

【0041】

エンコーダスケール304は、キャリッジ303に対向する面に設置され、300dpiの間隔でスリットが設けられている。そして、不図示のエンコーダセンサが発光した光がエンコーダスケール304に照射され、その透過光に基づいてキャリッジ303の走査位置についての信号がエンコーダセンサから出力される。紙送りローラ305は、補助ローラ306とともに記録媒体309を挟持しつつ図中の矢印の方向に回転することによって、記録媒体309を図中y方向に搬送する。また、一対の給紙ローラ307及び308は、記録媒体309を挟持しつつ、その給紙を行なう。

【0042】

図4は、インクジェット記録装置100の画像処理部周辺の構成を示すブロック図である。CPU401は、各ブロックのレジスタ設定、割り込み処理などインクジェット記録装置100全体を制御する。SDRAM402は、外部のホスト装置から受信した画像データに対して色変換、マスキング、ガンマ変換など記録のための所定の画像処理を実行した後、最終的に2値化処理を行なって得られる二値画像データを一時的に格納する。メモリコントローラ403は、各ブロックからのSDRAM402へのアクセスリクエストに対して予め設定された優先順序に則ってアクセス許可を行ない、SDRAM402に対するリード、ライト制御を行なう。

なお、このSDRAM402には、スムージング処理前のラスタデータを保持する領域と、スムージング処理済のデータを格納する領域とを備える。

【0043】

画像処理専用メモリコントローラ404は、SDRAM402に格納された画像データを読出す為にメモリコントローラ403に要求を出し、メモリコントローラ403により読み出された画像データを画像処理専用SRAM405に格納する。そのような構成により、各画像処理部406〜409(後述)は、各画像処理を行なうことができる。また、画像処理専用メモリコントローラ404は、各画像処理部406〜409からの要求に応じて、画像データを画像処理専用SRAM405から読み出して要求のあった各画像処理部に渡す。また、画像処理専用メモリコントローラ404は、各画像処理部からの書き込み要求に応じて、処理された画像データを受け取って画像処理専用SRAM405に書き込む。更に、画像処理専用メモリコントローラ404は、所望の全ての画像処理が行なわれた画像処理専用SRAM405に格納されている画像データを読み出す。そして、画像処理専用メモリコントローラ404は、SDRAM402に読み出した画像データを格納する為にメモリコントローラ1203に要求を出す。画像処理専用SRAM405は、各画像処理部406〜409が画像処理を行なう為に、画像処理専用メモリコントローラ404がSDRAM402から読み出してきた画像データを格納する。画像処理専用SRAM405の容量は、少なくとも1回あたりの画像処理に必要な画像データを格納できる容量である。

【0044】

HV変換処理部406は、SDRAM402から読み出されて画像処理専用SRAM405に格納されている画像データを、画像処理専用メモリコントローラ404に要求を出して読み込む。読み込まれた画像データは、全てラスタ方向に整列されているラスタ形式のデータであるので、これを記録素子列の方向(カラム方向)に整列されているカラム形式のデータに変換する。つまり、HV変換処理部406は、カラム形式のデータ(カラムデータ)を生成するデータ生成部である。変換後は、再び、画像処理専用メモリコントローラ404に要求を出して画像処理専用SRAM405に書き戻す。また、HV変換処理部406が画像データを画像処理専用SRAM405に書き込む際に、画像処理専用メモリコントローラ404は、書き戻す画像データの一部を画像処理専用SRAM405の所定の2箇所の領域(後述)に対して書き戻す。スムージング処理部407は、SDRAM402から読み出され、画像処理専用SRAM405に格納されている画像データを、画像処理専用メモリコントローラ404に要求を出して読み込む。そして、スムージング処理後、画像処理専用メモリコントローラ404に要求を出して画像処理専用SRAM405に書き戻す。

【0045】

画像処理部408と画像処理部409は、SDRAM402から読み出されて画像処理専用SRAM405に格納されている画像データを、画像処理専用メモリコントローラ404に要求を出して読み込む。そして、画像処理部408と画像処理部409は、所定の画像処理を行なった後に、画像処理専用メモリコントローラ404に要求を出して画像処理専用SRAM405に書き戻す。

【0046】

ここで、スムージング処理について説明する。スムージング処理とは、図11に示すように印刷しようとする画素A(注目画素)に対する周辺領域(主走査方向11画素×副走査方向9画素)の画素データを参照し、その特徴に応じて、注目画素を変更するものである。具体的には、例えば、図12に示したアルファベット文字「a」のドットデータ群のうち注目画素Aに対してスムージング処理をする場合には注目画素Aを囲む領域S(主走査方向11画素×副走査方向9画素=99画素)のドットデータを一次メモリに格納する。これによって、図13に示すようなドットデータを記憶する。その後、領域S内のドットデータ群を参照し、それらの特徴に応じて印刷すべき注目画素Aのデータを変更する。その際には、ドットデータ群で構成される図形の輪郭がスムースに印刷されるようなデータに変更される。さらに、注目画素Aとなるべき対象を変更してスムージング処理を続ける場合には、その新たな注目画素Aを囲む新たな領域Sについて、スムージング処理前の画素データが必要となる。

【0047】

このように、スムージング処理においては、注目画素Aの周辺領域の画素データを参照する必要があることが特徴である。図14(a)と図14(b)に示すように、領域141はスムージング処理の対象領域である。領域142は、参照のみされる領域である。データ143は、領域141において上流側のデータである。データ144は、領域141において下流側のデータである。補足すると、図8(d)においては、データ143は領域Aに格納され、データ144は領域Cに格納されている。また、図8(h)においては、データ143は領域Dに格納され、データ144は領域Cに格納されている。スムージング処理は、図14(a)に示すように順に行われる。符号Aは主走査方向であり、図1の符号Aに対応している。符号Fは副走査方向である。図14(b)に示すように、スムージング処理対象領域141の周囲に参照領域142(主走査方向の両側に5画素、副走査方向の両側に4画素の領域)が割り当てられている。補足すると、図9で示した領域902〜906は、それぞれ図14(b)に示す領域141と領域142に対応している。図14(c)に示すように、n番目の処理を行う場合には、n−1番目の処理で参照した領域145を参照する。なお、図9において、領域902〜906のデータ格納量は、同じである。

【0048】

図5は、画像処理専用メモリコントローラ404の内部構成を示すブロック図である。DMAC(Direct Memory Access Controller)501は、データを転送するための構成である。DMAC501は、メモリコントローラ403に読み出し要求を出して、メモリコントローラ403がSDRAM402から読み出した画像データを受け取り、画像処理専用SRAM405に書き込む。また、画像処理専用SRAM405からデータを読み出し、メモリコントローラ403に書き込み要求を出して、メモリコントローラ403経由でSDRAM402に画像データを書き込む。

【0049】

アービタ502は、各画像処理部406〜409及びCPU401からの、画像処理専用SRAM405に格納されている画像データへの読み出し又は書き込み要求に対して、所定の優先順位に基づいて読み出し又は書き込み許可を出す。各画像処理部又はCPU401に対して読み出し又は書き込み許可を出した場合には、要求内容に応じて画像処理専用SRAM405に対しての画像データの読み出し又は書き込みを行なう。セレクタ503は、DMAC501とアービタ502とから画像処理専用SRAM405に対しての信号線のいずれかが波形生成回路504に接続されるように切り替える。波形生成回路504は、セレクタ503を介して出されるDMAC501又はアービタ502からの画像処理専用SRAM405に対するアクセス要求を受けて、画像処理専用SRAM405の物理的構造に適応したアクセス信号を生成する。

【0050】

図6は、図5に示す画像処理専用メモリコントローラ404の内部及びメモリコントローラ403との詳細な接続関係を説明する図である。図6に示すように、セレクタ503と波形生成回路504との間で、sram_cex601、sram_wex602、sram_address[9:0]603、sram_wr_data[64:0]604、sram_rd_data[64:0]605の5種類の信号線が接続される。また、セレクタ503とDMAC501との間で、cex1606、wex1607、address1[9:0]608、wr_data1[64:0]609、rd_data1[64:0]610の5種類の信号線が接続される。

【0051】

セレクタ503とアービタ502との間で、cex2611、wex2612、address2[9:0]613、wr_data2[64:0]614、rd_data2[64:0]615の5種類の信号線が接続される。DMAC501とメモリコントローラ403との間で、req3620、wex3621、address3[31:3]622、req_ackx3623、wr_data3624、rd_data3[64:0]625、dt_ackx3[64:0]626の7種類の信号線が接続される。アービタ502とHV変換処理部406との間で、req4630、wex4631、address4[31:3]632、req_ackx4633、wr_data4634、rd_data4[64:0]635、dt_ackx4[64:0]636の7種類の信号線が接続される。 アービタ502とスムージング処理部407との間で、req5640、wex5641、address5[31:3]642、req_ackx5643、wr_data5644、rd_data5[64:0]645、dt_ackx5[64:0]646の7種類の信号線が接続される。アービタ502と画像処理部408との間で、req6650、wex6651、address6[31:3]652、req_ackx6653、wr_data6654、rd_data6[64:0]655、dt_ackx6[64:0]656の7種類の信号線が接続される。アービタ502と画像処理部409との間で、req7660、wex7661、address7[31:3]662、req_ackx7663、wr_data7664、rd_data7[64:0]665、dt_ackx[64:0]666の7種類の信号線が接続される。

【0052】

図7は、図6で示す各ブロック間でデータアクセスを行なう際のタイミングチャート図であり、クロック信号clkのサイクルに同期した通信が行なわれる。図7(a)及び(b)は、DMAC501とメモリコントローラ403との間、アービタ502とHV変換処理部406との間、アービタ502とスムージング処理部407との間、アービタ502と画像処理部408との間、アービタ502と画像処理部409との間で各データアクセスを行なう場合のタイミングチャート図である。また、図7(a)及び(b)におけるreqは各ブロック間のreq3〜req7に対応し、wexは各ブロック間のwex3〜wex7に対応する。また、addressは各ブロック間のaddress3〜address7に対応し、req_ackxは各ブロック間のreq_ackx3〜req_ackx7に対応する。また、wr_dataは各ブロック間のwr_data3〜wr_data7に対応し、rd_dataは各ブロック間のrd_data3〜rd_data7に対応する。また、dt_ackxは各ブロック間のdt_ackx3〜dt_ackx7に対応する。

【0053】

図7(a)はデータ読み出し時のタイミングチャート図であり、図7(b)はデータ書き込み時のタイミングチャート図である。図7(c)及び(d)は、セレクタ503と波形生成回路504との間、セレクタ503とDMAC501との間、セレクタ503とアービタ502との間で各データアクセスを行なう場合のタイミングチャート図である。図7(c)及び(d)におけるcsxは各ブロック間のsram_csx、csx1、csx2に対応し、wexは各ブロック間のsram_wex、wex1、wex2に対応する。また、addressは各ブロック間のsram_address、address1、address2に対応し、wr_dataは各ブロック間のsram_wr_data、wr_data1、wr_data2に対応する。また、rd_dataは各ブロック間のsram_rd_data、rd_data1、rd_data2に対応する。また、図7(c)はデータ読み出し時のタイミングチャート図であり、図7(d)はデータ書き込み時のタイミングチャート図である。

【0054】

以下、本実施理例における画像処理のシーケンスの詳細を図8及び図9(a)〜(d)を参照して説明する。図8は、図4に示す構成で行なわれる画像処理のシーケンスを画像処理専用SRAM405に格納された画像データのイメージに基づき示した図である。図9(a)〜(d)は、図8に示す画像処理で、記録媒体中のいずれの位置の処理を現在行なっているかを示している。

【0055】

図8には、画像処理専用SRAM405に格納された記録時に用いられる画像データのイメージが示され、ここでは、画像処理専用SRAM405の矩形領域のサイズは、横84画素×縦72画素である。本実施例においては、横84画素×縦72画素の領域は、さらに所定方向に対応して領域A(第4領域)、B(第1領域)、C(第2領域)、D(第3領域)に分けられる。領域Aは横10画素×縦72画素であり、領域Bは横54画素×縦72画素であり、領域Cは横10画素×縦72画素であり、領域Dは横10画素×縦72画素である。領域AとCとDには、所定方向に10画素数が割り当てられている。上述したように、SRAM405には、領域の大きさに対応した量の画像データが格納される。この所定方向は、上述した主走査方向である。

【0056】

図9(a)に示す領域902は、最初に画像処理専用SRAM405において処理を行なう領域であり、記録媒体901上では左上の端部に対応する。領域902に対して図8(a)〜(d)に示す処理が行なわれる(1回目の処理)。まず、図8(a)では、領域Aは記録媒体901外の部分であるので、DMAC501は、領域Aの全領域に対してヌルデータ「0」を書き込む。DMAC501は、ヌルデータ「0」を生成するヌルデータ生成部を備えている。同時に、DMAC501は、領域B、Cに対してSDRAM402から画像データを読み出して格納する。このような、ヌルデータや画像データの格納する領域の選択は、例えばCPU401が行う。

【0057】

図8(b)に示すように、領域B及びCの全ての画像データをHV変換処理部406が読み出してHV変換処理を行なった後、再度、領域B及びCに書き戻す。波形生成回路504はHV変換処理部406からの書き戻し要求が出されると、領域Cに書き戻される画像データを、領域Dにも書き込む。領域Cと領域Dに対する画像データの書き込む手順は、領域Cと領域Dに順に書き込む手順でも、領域Cと領域Dに同時に書き込む手順でも構わない。つまり、ここで領域Dにコピーされる画像データは、画像処理前(スムージング処理前)の画像データである。

【0058】

図8(c)に示すように、領域A、B、Cの画像データに対して、スムージング処理部407、画像処理部408、画像処理部409がそれぞれ所定の処理を行なう為に、画像処理専用SRAM405から画像データを読み出し、処理を終了した後、再度、画像処理専用SRAM405に画像データを書き戻す。このような、画像データの読み出しを行う領域の選択、所定の処理を行う領域の選択も、例えばCPU401が行う。

【0059】

図8(d)に示すように、画像処理を終了した領域A、B、Cの画像データをDMAC501がSDRAM402に書き戻す。ここで、領域A、B、Cの画像データにおいて実際にスムージング処理が行われたのは破線で囲まれた領域である。つまり、破線で囲まれた領域の外側の画像データは、スムージング処理を行なう際に参照されただけであるので、SDRAM402に書き戻す画像データも破線で囲まれた領域の画像データのみである。

【0060】

次に処理を行なうのは、図9(b)に示す903の領域であり、1回目に処理を行なった領域902と所定方向に隣接する領域である。領域903に対して図8(e)〜(h)に示す処理を行なう(2回目の処理)。

【0061】

まず、図8(e)に示すように、DMAC501は、領域B及びCに対してSDRAM402から画像データを読み出して格納する。図8(f)に示すように、領域B及びCの全ての画像データをHV変換処理部406が読み出してHV変換処理を行なった後、再度、領域B及びCに書き戻す。波形生成回路504は、HV変換処理部406からの書き戻し要求が出されると、領域Cに書き戻される画像データを、同時に領域Aにも書き込む。

【0062】

図8(g)に示すように、上記1回目の処理で既にHV変換処理を終了している領域Dの画像データと領域B、Cの画像データが領域D、B、Cの順でイメージ上は連続である。従って、領域D、B、Cの画像データに対して、スムージング処理部407、画像処理部408、画像処理部409がそれぞれ所定の処理を行なう為に、画像処理専用SRAM405から画像データを読み出し、処理を終了した後、再度、画像処理専用SRAM405に画像データを書き戻す。

【0063】

図8(h)に示すように、DMAC501は、画像処理を終了した画像データをSDRAM1202に書き戻す。ここでも、1回目の処理と同様に領域D、B、Cの画像データにおいて実際に画像処理を行なったのは破線で囲まれた領域であり、破線で囲まれた領域の外側の画像データは、スムージング処理を行なう際に参照されただけであるので、SDRAM402に書き戻す画像データも破線で囲まれた領域の画像データのみである。

【0064】

次に処理を行なうのは図9(c)に示す904の領域であり、2回目に処理を行なった領域903と隣接する領域である。領域904に対して図8(i)〜(l)に示す処理を行なう(3回目の処理)。

【0065】

まず(i)では、DMAC501は、領域B、Cに対してSDRAM402から画像データを読み出して格納する。図8(j)に示すように、領域B及びCの全ての画像データをHV変換処理部406が読み出してHV変換処理を行なった後、再度、領域B及びCに書き戻す。波形生成回路504は、HV変換処理部406からの書き戻し要求が出されると、領域Cに書き戻される画像データを、同時に領域Dにも書き込む。

【0066】

図8(k)に示すように、2回目の処理で既にHV変換処理を終了している領域Aの画像データと領域B、Cの画像データが領域A、B、Cの順でイメージ上は連続であるので、領域A、B、Cの画像データに対して、スムージング処理部407、画像処理部408、画像処理部409がそれぞれ所定の処理を行なう為に、画像処理専用SRAM405から画像データを読み出し、処理を終了した後には再度、画像処理専用SRAM405に画像データを書き戻す。

【0067】

図8(l)に示すように、DMAC501は、画像処理を終了した画像データをSDRAM402に書き戻す。ここでも1回目及び2回目の処理と同様に領域A、B、Cの画像データにおいて実際に画像処理を行なったのは破線で囲まれた領域であり、破線で囲まれた領域の外側の画像データは、スムージング処理を行なう際に参照されただけであるので、SDRAM402に書き戻す画像データも破線で囲まれた領域の画像データのみである。

【0068】

その後も偶数回目の処理では、2回目の処理と同様の処理を繰り返し、また、奇数回目の処理では、3回目の処理と同様の処理を順次繰り返して行く。このように、次々と処理を繰り返して行き、記録媒体901上では右上の端部にあたる図9(d)の906の領域に対して、その処理が奇数回目である場合には、図8(m)〜(p)に示す処理を行い、偶数回目である場合には、図8(q)〜(t)に示す処理を行なう(N回目の処理)。

【0069】

ここで、N回目の処理が奇数回目であった場合について述べる。まず、図8(m)に示すように、領域Bは記録媒体外の部分であるので、DMAC501は、領域Bの全領域に対して「0」を書き込む。

【0070】

図8(n)に示すように、領域B及びCの全ての画像データをHV変換処理部406が読み出してHV変換処理を行なった後、再度、領域B及びCに書き戻す。波形生成回路504はHV変換処理部406からの書き戻し要求が出されると、領域Cに書き戻される画像データを、同時に領域Dにも書き込む。

【0071】

図8(o)に示すように、領域A、B、Cの画像データに対して、スムージング処理部407、画像処理部408、画像処理部409がそれぞれ所定の処理を行なう為に、画像処理専用SRAM405から画像データを読み出し、処理を終了した後、再度、画像処理専用SRAM405に画像データを書き戻す。

【0072】

図8(p)に示すように、画像処理を終了した領域A、B、Cの画像データをDMAC501がSDRAM402に書き戻す。領域A、B、Cの画像データにおいて実際に画像処理を行なったのは破線で囲まれた領域であり、破線で囲まれた領域の外側の画像データは、スムージング処理を行なう際に参照されただけであるので、SDRAM402に書き戻す画像データも破線で囲まれた領域の画像データのみである。

【0073】

次にN回目の処理が偶数回目であった場合について述べる。

【0074】

まず、図8(q)に示すように、領域Bは記録媒体外の部分であるので、DMAC501は、領域Bの全領域に対して「0」を書き込む。

【0075】

図8(r)に示すように、領域B及びCの全ての画像データをHV変換処理部406が読み出してHV変換処理を行なった後、再度、領域B及びCに書き戻す。波形生成回路504はHV変換処理部406からの書き戻し要求が出されると、領域Cに書き戻される画像データを、同時に領域Aにも書き込む。

【0076】

図8(s)に示すように、1回目の処理で既にHV変換処理を終了している領域Dの画像データと領域B、Cの画像データが領域D、B、Cの順でイメージ上は連続であるので、領域D、B、Cの画像データに対して、スムージング処理部407、画像処理部408、画像処理部409がそれぞれ所定の処理を行なう為に、画像処理専用SRAM405から画像データを読み出し、処理を終了した後、再度、画像処理専用SRAM405に画像データを書き戻す。

【0077】

図8(t)に示すように、画像処理を終了した画像データをDMAC501がSDRAM402に書き戻す。ここでも1回目の処理と同様に領域D、B、Cの画像データにおいて実際に画像処理を行なったのは破線で囲まれた領域であり、破線で囲まれた領域の外側の画像データは、スムージング処理を行なう際に参照されただけであるので、SDRAM402に書き戻す画像データも破線で囲まれた領域の画像データのみである。以上のように、CPU401の制御によって、HV変換処理部406を動作させた後に、スムージング処理部407を動作させる工程を、複数回行う。

【0078】

次に、図15(a)と図15(b)を用いて、図8において、SRAM405に保持されているスムージング処理されたデータのうち、SDRAM402に書き込むデータ量とデータ領域を説明する。例えば、図8(d)において、図15(a)に示すように、斜線領域151のデータが読み出されて、SDRAM402に格納される。これは、図8(i)や図8(p)のデータの読み出しは、図8(d)におけるデータの読み出しと同様である。また、図8(h)において、図15(b)に示すように、斜線領域152、153のデータが、読み出されてSDRAM402に格納される。図8(t)のデータの読み出しは、図8(h)におけるデータの読み出しと同様である。

【0079】

なお、画像処理専用SRAM405のサイズは、上述した構成に限定するものではない。また、領域A、B、C、Dのサイズは全て等しく場合でも構わない。例えば、領域A、B、C、Dの横サイズはすべて128画素でもかまわない。

【0080】

以上のように、本実施例においては、図14に示したように、画像処理単位の順序に対応して、画像処理を行う前に、次の画像処理における対象のデータや参照データを、CPU401によって指定された領域に格納する。図8を参照して具体的に説明すると、1回目の画像処理において、図8(b)のように領域Cに格納されたデータを領域Dに格納する。また、2回目の画像処理において、図8(f)のように領域Cに格納されたデータを領域Aに格納する。

【0081】

上記の画像処理のシーケンスにおいて、HV変換処理部406がHV変換処理を行なった後、画像データを領域B及びCに書き戻す際に、波形生成回路504は領域Cに書き戻される画像データを同時に領域A若しくは領域Dにも書き込むが、画像処理専用SRAM405の異なる箇所に並列にデータを書き込む事が可能なように画像処理専用SRAM405はデュアルポート仕様のSRAMであるか、若しくは図10に示すように領域A及びDで物理的に1つのSRAM_AD1001、領域B及びDで物理的に1つのSRAM_BD1002となっているような構成であっても良い。この構成は、画像処理専用SRAM405と波形生成回路504との間に、バス(1010〜1014、2010〜2014)が設けられる。この構成により、SRAM_AD1001、SRAM_AD1002と波形生成回路504との間で独立にデータのリードとライトを行える。但し、要求される処理時間に余裕がある場合や、回路のゲート規模に余裕がない場合には、領域Cに画像データを書き込む前後の時間に領域A若しくは領域Dに領域Cに書き込む画像データと同じ画像データを書き込むようにして、画像処理専用SRAM405をシングルポート仕様で且つ物理的に1つのSRAMで構成されるようにしても良い。

【0082】

本実施例においては、スムージング処理でなくても、実際に処理を行なう領域よりも大きな領域を参照し、且つ前回の画像処理の際に使用したデータを再利用できない画像処理を行うのであれば、(n−1)回目の処理とn回目の処理とで重複する領域をSRAM内でコピーしておくことで、同様の処理が可能となる。

【0083】

本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(またはCPUやMPU等)がプログラムを読み出して実行する処理である。

【技術分野】

【0001】

本発明は、画像データを処理する画像処理装置に関する。

【背景技術】

【0002】

従来、記録ヘッドからインクを吐出して記録媒体に記録するインクジェット記録装置が知られている。一般的に、インクジェット記録装置は、記録ヘッドおよびインクタンクを搭載したキャリッジと、記録媒体を搬送する搬送機構と、それらの動作を制御する制御構成とを備えている。インクジェット記録装置は、記録ヘッドを記録媒体の搬送方向(副走査方向)と交差する方向(主走査方向)に走査させながらインクを吐出し、各走査間において記録媒体を間欠搬送する。複数回の走査と間欠搬送によって、インクジェット記録装置は記録媒体上の全画像領域の記録を行なうことができる。また、記録ヘッドには複数種類のインク色に応じた複数のノズル列を備えており、各ノズル列から吐出されるインク滴を重ねあわせる若しくは近接して着弾することによって、カラー画像を記録することができる。インクジェット記録装置は、比較的容易で優れた記録方法として幅広い産業分野で需要が高まっており、記録速度のさらなる高速化や、より一層の高品位画像が要求されている。そのような要求に応じて、近年のインクジェット記録装置の記録ヘッドはますます高精細化、多ノズル化が実現されている。

【0003】

上記のような動きの中、単位時間あたりに要求されるデータ処理量もますます多くなってきており、インクジェット記録装置の画像データ処理系の高速化も要求されてきている。特許文献1には、画像データ処理系の高速化を図るために、各画像処理部からのアクセスのみを専用に受け付ける画像処理専用SRAMを設けた構成が記載されている。特許文献1では、そのような構成により、ホスト装置から受信して画像データを格納したDRAMに各画像処理部がアクセスする構成よりも高速化を図ることができると記載されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2002−248813号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

上記の画像処理部には、例えば、スムージング処理がある。スムージング処理とは、記録しようとする画素(注目画素)に対してその注目画素を囲む周辺領域(例えば11×9画素)のデータを参照し、その結果に応じて注目画素を変更するものである。その際には、ドット群で構成される図形の輪郭がスムースに記録されるような画像データに変更される。

【0006】

従って、スムージング処理においては、注目画素の周辺領域の画素データを参照して、その特徴を調べる必要があるので、実際の処理対象領域よりも大きい領域をDRAMから画像処理専用SRAMに予め読み出しておく必要がある。また、注目画素に対して参照する領域のデータはスムージング処理によって変更される前のデータであることが必要である。

【0007】

ここで、画像データを予め定められた単位領域で順に処理を行っていく場合を考えると、n回目の処理を行なう際に、参照のための周辺領域分、(n−1)回目の処理と重複する領域が存在してしまう。また、(n−1)回目の処理の際に使用したデータは既に画素情報が変更されてしまっているので、n回目の処理の際に周辺領域の参照のためにデータを再使用することができない。従って、少なくともその重複する領域分について、データが変更されていない画像データを、再度、DRAMから読み出す必要が生じてしまう。

【0008】

しかしながら、通常は、画像処理専用SRAMで処理された画像データはDRAMに書き戻されるので、上記の実現のためには、DRAM内でホスト装置から受信した画像データを重複して格納しておくか、ホスト装置からその都度、画像データを受信する必要がある。

【0009】

本発明の目的は、このような従来の問題点を解決することにある。本発明は、上記の点に鑑み、画像データの処理効率を改善する画像処理装置を提供することを目的とする。

【課題を解決するための手段】

【0010】

上記課題を解決するため、本発明に係る画像処理装置は、矩形領域を構成する第1領域と第2領域と第3領域と第4領域とのうち前記第2領域、前記第3領域および前記第4領域の所定方向の幅に対しては所定の画素数が割り当てられている、前記矩形領域を記憶領域としてデータを格納するメモリと、前記第1領域と、前記第2領域と、前記第3領域もしくは前記第4領域と、のそれぞれに格納されたデータに対して所定の処理を行う処理手段と、前記処理手段が前記所定の処理を行う前に、前記第1領域と前記第2領域それぞれにデータを格納し、かつ、前記第2領域に格納したデータと同じデータを前記第3領域または前記第4領域に格納する格納手段と、前記格納手段が前記第3領域にデータを格納した場合には、前記処理手段により処理されるべき領域として、前記第1領域、前記第2領域および前記第4領域を選択し、前記格納手段が前記第4領域にデータを格納した場合には、前記処理手段により処理されるべき領域として、前記第1領域、前記第2領域および前記第3領域を選択する選択手段と、を備えることを特徴とする。

【発明の効果】

【0011】

本発明によれば、画像データの処理効率を改善することができる。

【図面の簡単な説明】

【0012】

【図1】インクジェット記録装置の構成の概要を示す外観斜視図である。

【図2】インクジェット記録装置の制御構成を示すブロック図である。

【図3】インクジェット記録装置の記録部の概略構成を示す斜視図である。

【図4】インクジェット記録装置の画像処理部周辺の構成を示すブロック図である。

【図5】画像処理専用メモリコントローラの内部構成を示すブロック図である。

【図6】画像処理専用メモリコントローラ周辺の接続構成を示す図である。

【図7】各ブロック間でのデータアクセスの際のタイミングチャート図である。

【図8】本実施例における画像処理の手順を説明するための図である。

【図9】本実施例における画像処理の手順を説明するための他の図である。

【図10】SRAMの他の構成例を示す図である。

【図11】スムージング処理を説明するための第1の図である。

【図12】スムージング処理を説明するための第2の図である。

【図13】スムージング処理を説明するための第3の図である。

【図14】スムージング処理を説明するための第4の図である。

【図15】スムージング処理を説明するための第5の図である。

【発明を実施するための形態】

【0013】

以下、添付図面を参照して本発明の好適な実施例を詳しく説明する。尚、以下の実施例は特許請求の範囲に係る本発明を限定するものでなく、また本実施例で説明されている特徴の組み合わせの全てが本発明の解決手段に必須のものとは限らない。なお、同一の構成要素には同一の参照番号を付して、説明を省略する。

【0014】

<インクジェット記録装置の説明>

図1は本発明の代表的な実施例であるインクジェット記録装置の構成の概要を示す外観斜視図である。

【0015】

図1に示すように、インクジェット記録装置100は、インクジェット方式に従ってインクを吐出して記録を行なう記録ヘッド103を搭載したキャリッジ102にキャリッジモータM1によって発生する駆動力を伝達機構104より伝え、キャリッジ102を矢印A方向に往復移動させるとともに、例えば、記録紙などの記録媒体Pを給紙機構105を介して給紙し、記録位置まで搬送し、その記録位置において記録ヘッド103から記録媒体Pにインクを吐出することで記録を行なう。

【0016】

また、記録ヘッド103の状態を良好に維持するためにキャリッジ102を回復装置110の位置まで移動させ、間欠的に記録ヘッド103の吐出回復処理を行う。

【0017】

インクジェット記録装置100のキャリッジ102には記録ヘッド103を搭載するのみならず、記録ヘッド103に供給するインクを貯留するインクカートリッジ106が装着される。インクカートリッジ106は、キャリッジ102に対して着脱自在になっている。

【0018】

図1に示したインクジェット記録装置100はカラー記録が可能であり、そのためにキャリッジ102は、マゼンタ(M)、シアン(C)、イエロー(Y)、ブラック(K)のインクを夫々、収容した4つのインクカートリッジを搭載している。これら4つのインクカートリッジは夫々独立に着脱可能である。

【0019】

さて、キャリッジ102と記録ヘッド103とは、両部材の接合面が適正に接触されて所要の電気的接続を達成維持できるようになっている。記録ヘッド103は、記録信号に応じてエネルギーを印加することにより、複数の吐出口からインクを選択的に吐出して記録する。特に、本実施例における記録ヘッド103は、熱エネルギーを利用してインクを吐出するインクジェット方式を採用しており、熱エネルギーを発生するために電気熱変換体を備え、その電気熱変換体に印加される電気エネルギーが熱エネルギーへと変換され、その熱エネルギーをインクに与えることにより生じる膜沸騰による気泡の成長、収縮によって生じる圧力変化を利用して、吐出口よりインクを吐出させる。この電気熱変換体は各吐出口のそれぞれに対応して設けられ、記録信号に応じて対応する電気熱変換体にパルス電圧を印加することによって対応する吐出口からインクを吐出する。

【0020】

図1に示されているように、キャリッジ102はキャリッジモータM1の駆動力を伝達する伝達機構104の駆動ベルト107の一部に連結されており、ガイドシャフト113に沿って矢印A方向に摺動自在に案内支持されるようになっている。従って、キャリッジ102は、キャリッジモータM1の正転及び逆転によってガイドシャフト113に沿って往復移動する。また、キャリッジ102の移動方向(矢印A方向)に沿ってキャリッジ102の位置を示すためのスケール108(CRエンコーダフィルム)が備えられている。この実施例では、スケール108は透明なPETフィルムに必要なピッチで黒色のバーを印刷したものを用いており、その一方はシャーシ109に固着され、他方は板バネ(不図示)で支持されている。

【0021】

また、インクジェット記録装置100には、記録ヘッド103の吐出口(不図示)が形成された吐出口面に対向してプラテン(不図示)が設けられており、キャリッジモータM1の駆動力によって記録ヘッド103を搭載したキャリッジ102が往復移動されると同時に、記録ヘッド103に記録信号を与えてインクを吐出することによって、プラテン上に搬送された記録媒体Pの全幅にわたって記録が行われる。

【0022】

さらに、図1における搬送ローラ114は、記録媒体Pを搬送するために搬送モータM2によって駆動される。また、ピンチローラ115は、バネ(不図示)により記録媒体Pを搬送ローラ114に当接する。また、ピンチローラホルダ116は、ピンチローラ115を回転自在に支持する。また、搬送ローラギヤ117は、搬送ローラ114の一端に固着されている。そして、搬送ローラギヤ117に中間ギヤ(不図示)を介して伝達された搬送モータM2の回転により、搬送ローラ114が駆動される。

【0023】

また、排出ローラ120は、記録ヘッド103によって画像が形成された記録媒体Pをインクジェット記録装置外ヘ排出する。排出ローラ120は、搬送モータM2の回転が伝達されることで駆動されるようになっている。なお、排出ローラ120は、記録媒体Pをバネ(不図示)により圧接する拍車ローラ(不図示)により当接する。拍車ホルダ122は、拍車ローラを回転自在に支持する。

【0024】

また、インクジェット記録装置100には、図1に示されているように、記録ヘッド103を搭載するキャリッジ102の記録動作のための往復運動の範囲外(記録領域外)の所望位置(例えば、ホームポジションに対応する位置)に、記録ヘッド103の吐出不良を回復するための回復装置110が配設されている。

【0025】

回復装置110は、記録ヘッド103の吐出口面をキャッピングするキャッピング機構111と記録ヘッド103の吐出口面をクリーニングするワイピング機構112を備えており、キャッピング機構111による吐出口面のキャッピングに連動して回復装置内の吸引構成(吸引ポンプ等)により吐出口からインクを強制的に排出させ、それによって、記録ヘッド103のインク流路内の粘度の増したインクや気泡等を除去するなどの吐出回復処理を行う。

【0026】

また、非記録動作時等には、記録ヘッド103の吐出口面をキャッピング機構111によりキャッピングすることによって、記録ヘッド103を保護するとともにインクの蒸発や乾燥を防止することができる。一方、ワイピング機構112はキャッピング機構111の近傍に配され、記録ヘッド103の吐出口面に付着したインク液滴を拭き取るようになっている。

【0027】

これらキャッピング機構111及びワイピング機構112により、記録ヘッド103のインク吐出状態を正常に保つことが可能となっている。

【0028】

<インクジェット記録装置の制御構成>

図2は図1に示したインクジェット記録装置100の制御構成を示すブロック図である。

【0029】

図2に示すように、制御部210は、MPU211と、後述する制御シーケンスに対応したプログラム、所要のテーブル、その他の固定データを格納したROM212と、キャリッジモータM1や搬送モータM2の制御、及び、記録ヘッド103の制御のための制御信号を生成する特殊用途集積回路(ASIC)213と、画像データの展開領域やプログラム実行のための作業用領域等を設けたRAM214と、各ブロックを相互に接続してデータの授受を行うシステムバス215と、以下に説明するセンサ群からのアナログ信号を入力してA/D変換し、デジタル信号をMPU211に供給するA/D変換器216とを含んで構成される。

【0030】

また、図2において、ホスト装置200は、画像データの供給源となるコンピュータ(或いは、画像読取り用のリーダやデジタルカメラなど)である。ホスト装置200とインクジェット記録装置100との間ではインタフェース(I/F)201を介して画像データ、コマンド、ステータス信号等を送受信する。

【0031】

さらに、スイッチ群220は、電源スイッチ221、プリント開始を指令するためのプリントスイッチ222、及び記録ヘッド103のインク吐出性能を良好な状態に維持するための処理(回復処理)の起動を指示するための回復スイッチ223など、操作者による指令入力を受けるためのスイッチから構成される。センサ群230は、ホームポジションを検出するためのフォトカプラなどの位置センサ231、環境温度を検出するためにインクジェット記録装置100の適宜の箇所に設けられた温度センサ232等から構成されるインクジェット記録装置100の状態を検出するためのセンサ群である。

【0032】

さらに、キャリッジモータドライバ240は、キャリッジ102を図1に示す矢印A方向に往復走査させるためのキャリッジモータM1を駆動させる。また、搬送モータドライバ250は、記録媒体Pを搬送するための搬送モータM2を駆動させる。

【0033】

ASIC213は、記録ヘッド103による記録走査の際に、ROM212の記憶領域に直接アクセスしながら記録ヘッドに対して記録素子(吐出ヒータ)の駆動データを転送する。

【0034】

なお、図1に示す構成は、インクカートリッジ106と記録ヘッド103とが分離可能な構成であるが、これらが一体的に形成されて交換可能なヘッドカートリッジを構成しても良い。

【0035】

さらに、以下の実施例において、記録ヘッドから吐出される液滴はインクであるとして説明し、さらにインクタンクに収容される液体はインクであるとして説明したが、その収容物はインクに限定されるものではない。例えば、記録画像の定着性や耐水性を高めたり、その画像品質を高めたりするために記録媒体に対して吐出される処理液のようなものがインクタンクに収容されていても良い。

【0036】

以下の実施例は、特にインクジェット記録方式の中でも、インク吐出を行わせるために利用されるエネルギーとして熱エネルギーを発生する構成(例えば電気熱変換体やレーザ光等)を備え、熱エネルギーによりインクの状態変化を生起させる方式を用いることにより記録の高密度化、高精細化が達成できる。

【0037】

さらに、インクジェット記録装置100が記録できる記録媒体の最大幅に対応した長さを有するフルラインタイプの記録ヘッドとしては、上述した明細書に開示されているような複数記録ヘッドの組み合わせによってその長さを満たす構成や、一体的に形成された1個の記録ヘッドとしての構成のいずれでもよい。

【0038】

加えて、上記で説明した記録ヘッド自体に一体的にインクタンクが設けられたカートリッジタイプの記録ヘッドのみならず、装置本体に装着されることで、装置本体との電気的な接続や装置本体からのインクの供給が可能になる交換自在のチップタイプの記録ヘッドを用いてもよい。

【0039】

さらに加えて、本実施例におけるインクジェット記録装置100の形態としては、コンピュータ等の情報処理機器の画像出力端末として一体または別体に設けられるものの他、読取装置等と組み合わせられた複写装置、さらには送受信機能を有するファクシミリ装置の形態を取るものであっても良い。

【0040】

図3は、インクジェット記録装置100の記録部の概略構成を示す斜視図である。同図において、インクカートリッジ301は、ブラック(Bk)、シアン(C)、マゼンタ(M)、イエロー(Y)の4色のインクをそれぞれ個別に貯留するように構成され、複数のインクタンクを一体として構成している。記録ヘッドカートリッジ302は、インクカートリッジ301に貯留される各インクに対応した記録素子列が1色あたり2つ、計8つの記録素子列を収納する。キャリッジ303に、インクカートリッジ301および記録ヘッドカートリッジ302をそれぞれ着脱自在に装着することができる。キャリッジ303は、ガイド軸310と摺動自在に結合することによってガイド軸310に沿って移動することができる。

【0041】

エンコーダスケール304は、キャリッジ303に対向する面に設置され、300dpiの間隔でスリットが設けられている。そして、不図示のエンコーダセンサが発光した光がエンコーダスケール304に照射され、その透過光に基づいてキャリッジ303の走査位置についての信号がエンコーダセンサから出力される。紙送りローラ305は、補助ローラ306とともに記録媒体309を挟持しつつ図中の矢印の方向に回転することによって、記録媒体309を図中y方向に搬送する。また、一対の給紙ローラ307及び308は、記録媒体309を挟持しつつ、その給紙を行なう。

【0042】

図4は、インクジェット記録装置100の画像処理部周辺の構成を示すブロック図である。CPU401は、各ブロックのレジスタ設定、割り込み処理などインクジェット記録装置100全体を制御する。SDRAM402は、外部のホスト装置から受信した画像データに対して色変換、マスキング、ガンマ変換など記録のための所定の画像処理を実行した後、最終的に2値化処理を行なって得られる二値画像データを一時的に格納する。メモリコントローラ403は、各ブロックからのSDRAM402へのアクセスリクエストに対して予め設定された優先順序に則ってアクセス許可を行ない、SDRAM402に対するリード、ライト制御を行なう。

なお、このSDRAM402には、スムージング処理前のラスタデータを保持する領域と、スムージング処理済のデータを格納する領域とを備える。

【0043】

画像処理専用メモリコントローラ404は、SDRAM402に格納された画像データを読出す為にメモリコントローラ403に要求を出し、メモリコントローラ403により読み出された画像データを画像処理専用SRAM405に格納する。そのような構成により、各画像処理部406〜409(後述)は、各画像処理を行なうことができる。また、画像処理専用メモリコントローラ404は、各画像処理部406〜409からの要求に応じて、画像データを画像処理専用SRAM405から読み出して要求のあった各画像処理部に渡す。また、画像処理専用メモリコントローラ404は、各画像処理部からの書き込み要求に応じて、処理された画像データを受け取って画像処理専用SRAM405に書き込む。更に、画像処理専用メモリコントローラ404は、所望の全ての画像処理が行なわれた画像処理専用SRAM405に格納されている画像データを読み出す。そして、画像処理専用メモリコントローラ404は、SDRAM402に読み出した画像データを格納する為にメモリコントローラ1203に要求を出す。画像処理専用SRAM405は、各画像処理部406〜409が画像処理を行なう為に、画像処理専用メモリコントローラ404がSDRAM402から読み出してきた画像データを格納する。画像処理専用SRAM405の容量は、少なくとも1回あたりの画像処理に必要な画像データを格納できる容量である。

【0044】

HV変換処理部406は、SDRAM402から読み出されて画像処理専用SRAM405に格納されている画像データを、画像処理専用メモリコントローラ404に要求を出して読み込む。読み込まれた画像データは、全てラスタ方向に整列されているラスタ形式のデータであるので、これを記録素子列の方向(カラム方向)に整列されているカラム形式のデータに変換する。つまり、HV変換処理部406は、カラム形式のデータ(カラムデータ)を生成するデータ生成部である。変換後は、再び、画像処理専用メモリコントローラ404に要求を出して画像処理専用SRAM405に書き戻す。また、HV変換処理部406が画像データを画像処理専用SRAM405に書き込む際に、画像処理専用メモリコントローラ404は、書き戻す画像データの一部を画像処理専用SRAM405の所定の2箇所の領域(後述)に対して書き戻す。スムージング処理部407は、SDRAM402から読み出され、画像処理専用SRAM405に格納されている画像データを、画像処理専用メモリコントローラ404に要求を出して読み込む。そして、スムージング処理後、画像処理専用メモリコントローラ404に要求を出して画像処理専用SRAM405に書き戻す。

【0045】

画像処理部408と画像処理部409は、SDRAM402から読み出されて画像処理専用SRAM405に格納されている画像データを、画像処理専用メモリコントローラ404に要求を出して読み込む。そして、画像処理部408と画像処理部409は、所定の画像処理を行なった後に、画像処理専用メモリコントローラ404に要求を出して画像処理専用SRAM405に書き戻す。

【0046】

ここで、スムージング処理について説明する。スムージング処理とは、図11に示すように印刷しようとする画素A(注目画素)に対する周辺領域(主走査方向11画素×副走査方向9画素)の画素データを参照し、その特徴に応じて、注目画素を変更するものである。具体的には、例えば、図12に示したアルファベット文字「a」のドットデータ群のうち注目画素Aに対してスムージング処理をする場合には注目画素Aを囲む領域S(主走査方向11画素×副走査方向9画素=99画素)のドットデータを一次メモリに格納する。これによって、図13に示すようなドットデータを記憶する。その後、領域S内のドットデータ群を参照し、それらの特徴に応じて印刷すべき注目画素Aのデータを変更する。その際には、ドットデータ群で構成される図形の輪郭がスムースに印刷されるようなデータに変更される。さらに、注目画素Aとなるべき対象を変更してスムージング処理を続ける場合には、その新たな注目画素Aを囲む新たな領域Sについて、スムージング処理前の画素データが必要となる。

【0047】

このように、スムージング処理においては、注目画素Aの周辺領域の画素データを参照する必要があることが特徴である。図14(a)と図14(b)に示すように、領域141はスムージング処理の対象領域である。領域142は、参照のみされる領域である。データ143は、領域141において上流側のデータである。データ144は、領域141において下流側のデータである。補足すると、図8(d)においては、データ143は領域Aに格納され、データ144は領域Cに格納されている。また、図8(h)においては、データ143は領域Dに格納され、データ144は領域Cに格納されている。スムージング処理は、図14(a)に示すように順に行われる。符号Aは主走査方向であり、図1の符号Aに対応している。符号Fは副走査方向である。図14(b)に示すように、スムージング処理対象領域141の周囲に参照領域142(主走査方向の両側に5画素、副走査方向の両側に4画素の領域)が割り当てられている。補足すると、図9で示した領域902〜906は、それぞれ図14(b)に示す領域141と領域142に対応している。図14(c)に示すように、n番目の処理を行う場合には、n−1番目の処理で参照した領域145を参照する。なお、図9において、領域902〜906のデータ格納量は、同じである。

【0048】

図5は、画像処理専用メモリコントローラ404の内部構成を示すブロック図である。DMAC(Direct Memory Access Controller)501は、データを転送するための構成である。DMAC501は、メモリコントローラ403に読み出し要求を出して、メモリコントローラ403がSDRAM402から読み出した画像データを受け取り、画像処理専用SRAM405に書き込む。また、画像処理専用SRAM405からデータを読み出し、メモリコントローラ403に書き込み要求を出して、メモリコントローラ403経由でSDRAM402に画像データを書き込む。

【0049】

アービタ502は、各画像処理部406〜409及びCPU401からの、画像処理専用SRAM405に格納されている画像データへの読み出し又は書き込み要求に対して、所定の優先順位に基づいて読み出し又は書き込み許可を出す。各画像処理部又はCPU401に対して読み出し又は書き込み許可を出した場合には、要求内容に応じて画像処理専用SRAM405に対しての画像データの読み出し又は書き込みを行なう。セレクタ503は、DMAC501とアービタ502とから画像処理専用SRAM405に対しての信号線のいずれかが波形生成回路504に接続されるように切り替える。波形生成回路504は、セレクタ503を介して出されるDMAC501又はアービタ502からの画像処理専用SRAM405に対するアクセス要求を受けて、画像処理専用SRAM405の物理的構造に適応したアクセス信号を生成する。

【0050】

図6は、図5に示す画像処理専用メモリコントローラ404の内部及びメモリコントローラ403との詳細な接続関係を説明する図である。図6に示すように、セレクタ503と波形生成回路504との間で、sram_cex601、sram_wex602、sram_address[9:0]603、sram_wr_data[64:0]604、sram_rd_data[64:0]605の5種類の信号線が接続される。また、セレクタ503とDMAC501との間で、cex1606、wex1607、address1[9:0]608、wr_data1[64:0]609、rd_data1[64:0]610の5種類の信号線が接続される。

【0051】

セレクタ503とアービタ502との間で、cex2611、wex2612、address2[9:0]613、wr_data2[64:0]614、rd_data2[64:0]615の5種類の信号線が接続される。DMAC501とメモリコントローラ403との間で、req3620、wex3621、address3[31:3]622、req_ackx3623、wr_data3624、rd_data3[64:0]625、dt_ackx3[64:0]626の7種類の信号線が接続される。アービタ502とHV変換処理部406との間で、req4630、wex4631、address4[31:3]632、req_ackx4633、wr_data4634、rd_data4[64:0]635、dt_ackx4[64:0]636の7種類の信号線が接続される。 アービタ502とスムージング処理部407との間で、req5640、wex5641、address5[31:3]642、req_ackx5643、wr_data5644、rd_data5[64:0]645、dt_ackx5[64:0]646の7種類の信号線が接続される。アービタ502と画像処理部408との間で、req6650、wex6651、address6[31:3]652、req_ackx6653、wr_data6654、rd_data6[64:0]655、dt_ackx6[64:0]656の7種類の信号線が接続される。アービタ502と画像処理部409との間で、req7660、wex7661、address7[31:3]662、req_ackx7663、wr_data7664、rd_data7[64:0]665、dt_ackx[64:0]666の7種類の信号線が接続される。

【0052】

図7は、図6で示す各ブロック間でデータアクセスを行なう際のタイミングチャート図であり、クロック信号clkのサイクルに同期した通信が行なわれる。図7(a)及び(b)は、DMAC501とメモリコントローラ403との間、アービタ502とHV変換処理部406との間、アービタ502とスムージング処理部407との間、アービタ502と画像処理部408との間、アービタ502と画像処理部409との間で各データアクセスを行なう場合のタイミングチャート図である。また、図7(a)及び(b)におけるreqは各ブロック間のreq3〜req7に対応し、wexは各ブロック間のwex3〜wex7に対応する。また、addressは各ブロック間のaddress3〜address7に対応し、req_ackxは各ブロック間のreq_ackx3〜req_ackx7に対応する。また、wr_dataは各ブロック間のwr_data3〜wr_data7に対応し、rd_dataは各ブロック間のrd_data3〜rd_data7に対応する。また、dt_ackxは各ブロック間のdt_ackx3〜dt_ackx7に対応する。

【0053】

図7(a)はデータ読み出し時のタイミングチャート図であり、図7(b)はデータ書き込み時のタイミングチャート図である。図7(c)及び(d)は、セレクタ503と波形生成回路504との間、セレクタ503とDMAC501との間、セレクタ503とアービタ502との間で各データアクセスを行なう場合のタイミングチャート図である。図7(c)及び(d)におけるcsxは各ブロック間のsram_csx、csx1、csx2に対応し、wexは各ブロック間のsram_wex、wex1、wex2に対応する。また、addressは各ブロック間のsram_address、address1、address2に対応し、wr_dataは各ブロック間のsram_wr_data、wr_data1、wr_data2に対応する。また、rd_dataは各ブロック間のsram_rd_data、rd_data1、rd_data2に対応する。また、図7(c)はデータ読み出し時のタイミングチャート図であり、図7(d)はデータ書き込み時のタイミングチャート図である。

【0054】

以下、本実施理例における画像処理のシーケンスの詳細を図8及び図9(a)〜(d)を参照して説明する。図8は、図4に示す構成で行なわれる画像処理のシーケンスを画像処理専用SRAM405に格納された画像データのイメージに基づき示した図である。図9(a)〜(d)は、図8に示す画像処理で、記録媒体中のいずれの位置の処理を現在行なっているかを示している。

【0055】

図8には、画像処理専用SRAM405に格納された記録時に用いられる画像データのイメージが示され、ここでは、画像処理専用SRAM405の矩形領域のサイズは、横84画素×縦72画素である。本実施例においては、横84画素×縦72画素の領域は、さらに所定方向に対応して領域A(第4領域)、B(第1領域)、C(第2領域)、D(第3領域)に分けられる。領域Aは横10画素×縦72画素であり、領域Bは横54画素×縦72画素であり、領域Cは横10画素×縦72画素であり、領域Dは横10画素×縦72画素である。領域AとCとDには、所定方向に10画素数が割り当てられている。上述したように、SRAM405には、領域の大きさに対応した量の画像データが格納される。この所定方向は、上述した主走査方向である。

【0056】

図9(a)に示す領域902は、最初に画像処理専用SRAM405において処理を行なう領域であり、記録媒体901上では左上の端部に対応する。領域902に対して図8(a)〜(d)に示す処理が行なわれる(1回目の処理)。まず、図8(a)では、領域Aは記録媒体901外の部分であるので、DMAC501は、領域Aの全領域に対してヌルデータ「0」を書き込む。DMAC501は、ヌルデータ「0」を生成するヌルデータ生成部を備えている。同時に、DMAC501は、領域B、Cに対してSDRAM402から画像データを読み出して格納する。このような、ヌルデータや画像データの格納する領域の選択は、例えばCPU401が行う。

【0057】

図8(b)に示すように、領域B及びCの全ての画像データをHV変換処理部406が読み出してHV変換処理を行なった後、再度、領域B及びCに書き戻す。波形生成回路504はHV変換処理部406からの書き戻し要求が出されると、領域Cに書き戻される画像データを、領域Dにも書き込む。領域Cと領域Dに対する画像データの書き込む手順は、領域Cと領域Dに順に書き込む手順でも、領域Cと領域Dに同時に書き込む手順でも構わない。つまり、ここで領域Dにコピーされる画像データは、画像処理前(スムージング処理前)の画像データである。

【0058】

図8(c)に示すように、領域A、B、Cの画像データに対して、スムージング処理部407、画像処理部408、画像処理部409がそれぞれ所定の処理を行なう為に、画像処理専用SRAM405から画像データを読み出し、処理を終了した後、再度、画像処理専用SRAM405に画像データを書き戻す。このような、画像データの読み出しを行う領域の選択、所定の処理を行う領域の選択も、例えばCPU401が行う。

【0059】

図8(d)に示すように、画像処理を終了した領域A、B、Cの画像データをDMAC501がSDRAM402に書き戻す。ここで、領域A、B、Cの画像データにおいて実際にスムージング処理が行われたのは破線で囲まれた領域である。つまり、破線で囲まれた領域の外側の画像データは、スムージング処理を行なう際に参照されただけであるので、SDRAM402に書き戻す画像データも破線で囲まれた領域の画像データのみである。

【0060】

次に処理を行なうのは、図9(b)に示す903の領域であり、1回目に処理を行なった領域902と所定方向に隣接する領域である。領域903に対して図8(e)〜(h)に示す処理を行なう(2回目の処理)。

【0061】

まず、図8(e)に示すように、DMAC501は、領域B及びCに対してSDRAM402から画像データを読み出して格納する。図8(f)に示すように、領域B及びCの全ての画像データをHV変換処理部406が読み出してHV変換処理を行なった後、再度、領域B及びCに書き戻す。波形生成回路504は、HV変換処理部406からの書き戻し要求が出されると、領域Cに書き戻される画像データを、同時に領域Aにも書き込む。

【0062】

図8(g)に示すように、上記1回目の処理で既にHV変換処理を終了している領域Dの画像データと領域B、Cの画像データが領域D、B、Cの順でイメージ上は連続である。従って、領域D、B、Cの画像データに対して、スムージング処理部407、画像処理部408、画像処理部409がそれぞれ所定の処理を行なう為に、画像処理専用SRAM405から画像データを読み出し、処理を終了した後、再度、画像処理専用SRAM405に画像データを書き戻す。

【0063】

図8(h)に示すように、DMAC501は、画像処理を終了した画像データをSDRAM1202に書き戻す。ここでも、1回目の処理と同様に領域D、B、Cの画像データにおいて実際に画像処理を行なったのは破線で囲まれた領域であり、破線で囲まれた領域の外側の画像データは、スムージング処理を行なう際に参照されただけであるので、SDRAM402に書き戻す画像データも破線で囲まれた領域の画像データのみである。

【0064】

次に処理を行なうのは図9(c)に示す904の領域であり、2回目に処理を行なった領域903と隣接する領域である。領域904に対して図8(i)〜(l)に示す処理を行なう(3回目の処理)。

【0065】

まず(i)では、DMAC501は、領域B、Cに対してSDRAM402から画像データを読み出して格納する。図8(j)に示すように、領域B及びCの全ての画像データをHV変換処理部406が読み出してHV変換処理を行なった後、再度、領域B及びCに書き戻す。波形生成回路504は、HV変換処理部406からの書き戻し要求が出されると、領域Cに書き戻される画像データを、同時に領域Dにも書き込む。

【0066】

図8(k)に示すように、2回目の処理で既にHV変換処理を終了している領域Aの画像データと領域B、Cの画像データが領域A、B、Cの順でイメージ上は連続であるので、領域A、B、Cの画像データに対して、スムージング処理部407、画像処理部408、画像処理部409がそれぞれ所定の処理を行なう為に、画像処理専用SRAM405から画像データを読み出し、処理を終了した後には再度、画像処理専用SRAM405に画像データを書き戻す。

【0067】

図8(l)に示すように、DMAC501は、画像処理を終了した画像データをSDRAM402に書き戻す。ここでも1回目及び2回目の処理と同様に領域A、B、Cの画像データにおいて実際に画像処理を行なったのは破線で囲まれた領域であり、破線で囲まれた領域の外側の画像データは、スムージング処理を行なう際に参照されただけであるので、SDRAM402に書き戻す画像データも破線で囲まれた領域の画像データのみである。

【0068】

その後も偶数回目の処理では、2回目の処理と同様の処理を繰り返し、また、奇数回目の処理では、3回目の処理と同様の処理を順次繰り返して行く。このように、次々と処理を繰り返して行き、記録媒体901上では右上の端部にあたる図9(d)の906の領域に対して、その処理が奇数回目である場合には、図8(m)〜(p)に示す処理を行い、偶数回目である場合には、図8(q)〜(t)に示す処理を行なう(N回目の処理)。

【0069】

ここで、N回目の処理が奇数回目であった場合について述べる。まず、図8(m)に示すように、領域Bは記録媒体外の部分であるので、DMAC501は、領域Bの全領域に対して「0」を書き込む。

【0070】

図8(n)に示すように、領域B及びCの全ての画像データをHV変換処理部406が読み出してHV変換処理を行なった後、再度、領域B及びCに書き戻す。波形生成回路504はHV変換処理部406からの書き戻し要求が出されると、領域Cに書き戻される画像データを、同時に領域Dにも書き込む。

【0071】

図8(o)に示すように、領域A、B、Cの画像データに対して、スムージング処理部407、画像処理部408、画像処理部409がそれぞれ所定の処理を行なう為に、画像処理専用SRAM405から画像データを読み出し、処理を終了した後、再度、画像処理専用SRAM405に画像データを書き戻す。

【0072】

図8(p)に示すように、画像処理を終了した領域A、B、Cの画像データをDMAC501がSDRAM402に書き戻す。領域A、B、Cの画像データにおいて実際に画像処理を行なったのは破線で囲まれた領域であり、破線で囲まれた領域の外側の画像データは、スムージング処理を行なう際に参照されただけであるので、SDRAM402に書き戻す画像データも破線で囲まれた領域の画像データのみである。

【0073】

次にN回目の処理が偶数回目であった場合について述べる。

【0074】

まず、図8(q)に示すように、領域Bは記録媒体外の部分であるので、DMAC501は、領域Bの全領域に対して「0」を書き込む。

【0075】

図8(r)に示すように、領域B及びCの全ての画像データをHV変換処理部406が読み出してHV変換処理を行なった後、再度、領域B及びCに書き戻す。波形生成回路504はHV変換処理部406からの書き戻し要求が出されると、領域Cに書き戻される画像データを、同時に領域Aにも書き込む。

【0076】

図8(s)に示すように、1回目の処理で既にHV変換処理を終了している領域Dの画像データと領域B、Cの画像データが領域D、B、Cの順でイメージ上は連続であるので、領域D、B、Cの画像データに対して、スムージング処理部407、画像処理部408、画像処理部409がそれぞれ所定の処理を行なう為に、画像処理専用SRAM405から画像データを読み出し、処理を終了した後、再度、画像処理専用SRAM405に画像データを書き戻す。

【0077】

図8(t)に示すように、画像処理を終了した画像データをDMAC501がSDRAM402に書き戻す。ここでも1回目の処理と同様に領域D、B、Cの画像データにおいて実際に画像処理を行なったのは破線で囲まれた領域であり、破線で囲まれた領域の外側の画像データは、スムージング処理を行なう際に参照されただけであるので、SDRAM402に書き戻す画像データも破線で囲まれた領域の画像データのみである。以上のように、CPU401の制御によって、HV変換処理部406を動作させた後に、スムージング処理部407を動作させる工程を、複数回行う。

【0078】

次に、図15(a)と図15(b)を用いて、図8において、SRAM405に保持されているスムージング処理されたデータのうち、SDRAM402に書き込むデータ量とデータ領域を説明する。例えば、図8(d)において、図15(a)に示すように、斜線領域151のデータが読み出されて、SDRAM402に格納される。これは、図8(i)や図8(p)のデータの読み出しは、図8(d)におけるデータの読み出しと同様である。また、図8(h)において、図15(b)に示すように、斜線領域152、153のデータが、読み出されてSDRAM402に格納される。図8(t)のデータの読み出しは、図8(h)におけるデータの読み出しと同様である。

【0079】

なお、画像処理専用SRAM405のサイズは、上述した構成に限定するものではない。また、領域A、B、C、Dのサイズは全て等しく場合でも構わない。例えば、領域A、B、C、Dの横サイズはすべて128画素でもかまわない。

【0080】

以上のように、本実施例においては、図14に示したように、画像処理単位の順序に対応して、画像処理を行う前に、次の画像処理における対象のデータや参照データを、CPU401によって指定された領域に格納する。図8を参照して具体的に説明すると、1回目の画像処理において、図8(b)のように領域Cに格納されたデータを領域Dに格納する。また、2回目の画像処理において、図8(f)のように領域Cに格納されたデータを領域Aに格納する。

【0081】

上記の画像処理のシーケンスにおいて、HV変換処理部406がHV変換処理を行なった後、画像データを領域B及びCに書き戻す際に、波形生成回路504は領域Cに書き戻される画像データを同時に領域A若しくは領域Dにも書き込むが、画像処理専用SRAM405の異なる箇所に並列にデータを書き込む事が可能なように画像処理専用SRAM405はデュアルポート仕様のSRAMであるか、若しくは図10に示すように領域A及びDで物理的に1つのSRAM_AD1001、領域B及びDで物理的に1つのSRAM_BD1002となっているような構成であっても良い。この構成は、画像処理専用SRAM405と波形生成回路504との間に、バス(1010〜1014、2010〜2014)が設けられる。この構成により、SRAM_AD1001、SRAM_AD1002と波形生成回路504との間で独立にデータのリードとライトを行える。但し、要求される処理時間に余裕がある場合や、回路のゲート規模に余裕がない場合には、領域Cに画像データを書き込む前後の時間に領域A若しくは領域Dに領域Cに書き込む画像データと同じ画像データを書き込むようにして、画像処理専用SRAM405をシングルポート仕様で且つ物理的に1つのSRAMで構成されるようにしても良い。

【0082】

本実施例においては、スムージング処理でなくても、実際に処理を行なう領域よりも大きな領域を参照し、且つ前回の画像処理の際に使用したデータを再利用できない画像処理を行うのであれば、(n−1)回目の処理とn回目の処理とで重複する領域をSRAM内でコピーしておくことで、同様の処理が可能となる。

【0083】

本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(またはCPUやMPU等)がプログラムを読み出して実行する処理である。

【特許請求の範囲】

【請求項1】

矩形領域を構成する第1領域と第2領域と第3領域と第4領域とのうち前記第2領域、前記第3領域および前記第4領域の所定方向の幅に対しては所定の画素数が割り当てられている、前記矩形領域を記憶領域としてデータを格納するメモリと、

前記第1領域と、前記第2領域と、前記第3領域もしくは前記第4領域と、のそれぞれに格納されたデータに対して所定の処理を行う処理手段と、

前記処理手段が前記所定の処理を行う前に、前記第1領域と前記第2領域それぞれにデータを格納し、かつ、前記処理手段が前記所定の処理を行う前に、前記第2領域に格納したデータと同じデータを前記第3領域または前記第4領域に格納する格納手段と、

前記格納手段が前記第3領域にデータを格納した場合には、前記処理手段により処理されるべき領域として、前記第1領域、前記第2領域および前記第4領域を選択し、前記格納手段が前記第4領域にデータを格納した場合には、前記処理手段により処理されるべき領域として、前記第1領域、前記第2領域および前記第3領域を選択する選択手段と、

を備えることを特徴とする画像処理装置。

【請求項2】

前記処理手段が前記所定の処理を行った後に、前記第1領域と、前記第2領域と、前記第3領域もしくは前記4領域と、からデータの読み出しを行う読出手段、をさらに備えることを特徴とする請求項1に記載の画像処理装置。

【請求項3】

前記所定の処理は、スムージング処理であることを特徴とする請求項1又は2に記載の画像処理装置。

【請求項4】

HV変換を行うことにより前記矩形領域に格納される前記データを生成する生成手段、をさらに備えることを特徴とする請求項1乃至3のいずれか1項に記載の画像処理装置。

【請求項5】

前記生成手段による生成の後に、前記処理手段による前記所定の処理を行わせる処理を複数回行うように、前記生成手段と前記処理手段を制御する制御手段、をさらに備えることを特徴とする請求項4に記載の画像処理装置。

【請求項1】

矩形領域を構成する第1領域と第2領域と第3領域と第4領域とのうち前記第2領域、前記第3領域および前記第4領域の所定方向の幅に対しては所定の画素数が割り当てられている、前記矩形領域を記憶領域としてデータを格納するメモリと、

前記第1領域と、前記第2領域と、前記第3領域もしくは前記第4領域と、のそれぞれに格納されたデータに対して所定の処理を行う処理手段と、

前記処理手段が前記所定の処理を行う前に、前記第1領域と前記第2領域それぞれにデータを格納し、かつ、前記処理手段が前記所定の処理を行う前に、前記第2領域に格納したデータと同じデータを前記第3領域または前記第4領域に格納する格納手段と、

前記格納手段が前記第3領域にデータを格納した場合には、前記処理手段により処理されるべき領域として、前記第1領域、前記第2領域および前記第4領域を選択し、前記格納手段が前記第4領域にデータを格納した場合には、前記処理手段により処理されるべき領域として、前記第1領域、前記第2領域および前記第3領域を選択する選択手段と、

を備えることを特徴とする画像処理装置。

【請求項2】

前記処理手段が前記所定の処理を行った後に、前記第1領域と、前記第2領域と、前記第3領域もしくは前記4領域と、からデータの読み出しを行う読出手段、をさらに備えることを特徴とする請求項1に記載の画像処理装置。

【請求項3】

前記所定の処理は、スムージング処理であることを特徴とする請求項1又は2に記載の画像処理装置。

【請求項4】

HV変換を行うことにより前記矩形領域に格納される前記データを生成する生成手段、をさらに備えることを特徴とする請求項1乃至3のいずれか1項に記載の画像処理装置。

【請求項5】

前記生成手段による生成の後に、前記処理手段による前記所定の処理を行わせる処理を複数回行うように、前記生成手段と前記処理手段を制御する制御手段、をさらに備えることを特徴とする請求項4に記載の画像処理装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2013−49262(P2013−49262A)

【公開日】平成25年3月14日(2013.3.14)

【国際特許分類】

【出願番号】特願2012−160941(P2012−160941)

【出願日】平成24年7月19日(2012.7.19)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成25年3月14日(2013.3.14)

【国際特許分類】

【出願日】平成24年7月19日(2012.7.19)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]