画像処理装置

【課題】ハードウェアの規模の拡大を抑えて、ハードウェアによる色変換処理の高速化を図る。

【解決手段】画像処理装置は、1ブロックを複数段階で分割し、分割段階の順に分割されたサブブロック単位で各画素にアドレスを割り当てる入力バッファー11と、アドレス順に色変換処理する色変換部12と、最後の分割段階のサブブロック内の画素間で画素値を比較するとともに、各サブブロック内でアドレスが先頭の1画素を用いて、同じ分割段階で分割されたサブブロック間の画素値を比較する比較部Mbと、最後の分割段階のサブブロック内の画素間で画素値が一致し、何れかの分割段階のサブブロック間で画素値が一致する場合、当該サブブロック間で最初に色変換処理された画素の色変換処理後の画素値を、各サブブロックの画素にコピーして記憶する出力バッファー13と、を備える。

【解決手段】画像処理装置は、1ブロックを複数段階で分割し、分割段階の順に分割されたサブブロック単位で各画素にアドレスを割り当てる入力バッファー11と、アドレス順に色変換処理する色変換部12と、最後の分割段階のサブブロック内の画素間で画素値を比較するとともに、各サブブロック内でアドレスが先頭の1画素を用いて、同じ分割段階で分割されたサブブロック間の画素値を比較する比較部Mbと、最後の分割段階のサブブロック内の画素間で画素値が一致し、何れかの分割段階のサブブロック間で画素値が一致する場合、当該サブブロック間で最初に色変換処理された画素の色変換処理後の画素値を、各サブブロックの画素にコピーして記憶する出力バッファー13と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像処理装置に関する。

【背景技術】

【0002】

プリンターやコピー機等の画像形成装置においては、画像データを色変換処理し、入力された画像データの色空間を、画像形成装置が表現可能な色空間に一致させている。

色空間同士は複雑な関係にあるため、色変換処理では、色変換後の画素値を逐一演算するのではなく、入力値に対し色変換後の出力値が定められたLUT(Look Up Table)が利用されている(例えば、特許文献1参照)。LUTにおいて、全ての入力値に対応する出力値を定めると、大容量のメモリーが必要となるため、LUTは、通常、代表色についてのみ入力値と出力値が定められ、他は補間演算によって出力値を得ている。

【0003】

代表色のみ入力値と出力値を保持するようにしても、必要なメモリー容量は小さくない。そのうえ、色空間を構成する色数が増えれば、それだけLUTに保持すべき入力値と出力値が増え、大容量のメモリーが必要となる。そのため、色変換処理を、LSI(Large Scale Integration)のようなハードウェアで行うには、負担が大きいことが知られている。特に、出力がCMYKの色空間である画像形成装置の場合、色数が多く、負担が大きい。

【0004】

ハードウェアによる処理速度を高速化するためには、処理回路を複数設けて、並列に処理していく方法が一般的であるが、色変換処理に関しては、上述したような容量の大きいLUTを並列に設けることになるため、ハードウェアへの実装は困難を伴う。

【0005】

そのため、従来、色変換処理は、ハードウェアではなく、ソフトウェアにより実現されることが多かった(例えば、特許文献1、2参照)。文字や図形の画像領域内は同一色である場合が多く、ソフトウェアによれば、そのような同一色の領域では色変換処理の結果を一括変換し、処理時間を短縮することができる。特許文献1によれば、注目画素と同一画素値を持つ画素の連続数を求め、その連続数だけ注目画素の色変換処理後の画素値に置換することにより、色変換処理する画素数を減じて処理時間を短縮する。特許文献2によれば、プリンタドライバーにより印刷データを生成する段階で、特許文献1と同様の処理を実現することができる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−205636号公報

【特許文献2】特開2004−54653号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

一方、写真の画像領域は、隣接画素の画素値が同一であるとは限らず、予測できない。そのため、全画素について1画素ずつ色変換処理する以外に方法が無く、処理速度の低下の要因となっている。結果として、ソフトウェアによる色変換処理は、ハードウェアによって処理する場合に比べて、やはり処理速度が遅く、高速化が望まれている。

【0008】

本発明の課題は、ハードウェアの規模の拡大を抑えて、ハードウェアによる色変換処理の高速化を図ることである。

【課題を解決するための手段】

【0009】

請求項1に記載の発明によれば、

画像データをブロック単位で入力し、入力された1ブロックを複数段階で分割し、分割段階の順に、分割されたサブブロック単位で、各画素にアドレスを割り当てる入力バッファーと、

前記入力バッファーからアドレス順に画素単位で画素値を入力し、色変換処理する色変換部と、

前記色変換部によって色変換処理された各画素の画素値を、各画素に割り当てられた前記アドレスに対応付けて記憶する出力バッファーと、

前記入力バッファーから、1ブロックが複数段階で分割されたサブブロック単位で各画素の画素値を入力し、最後の分割段階で分割されたサブブロック内の画素間で画素値を比較するとともに、同じ分割段階で分割されたサブブロック間で画素値を比較する比較部と、を備え、

前記比較部は、各サブブロック内でアドレスが先頭の1画素の画素値を用いて、サブブロック間の画素値を比較し、

前記出力バッファーは、前記比較部による比較の結果、最後の分割段階で分割されたサブブロック内の画素間で画素値が一致し、何れかの分割段階のサブブロック間で画素値が一致する場合、当該サブブロック間で最初に色変換処理された画素の色変換処理後の画素値を、各サブブロックの画素にコピーして記憶する画像処理装置が提供される。

【0010】

請求項2に記載の発明によれば、

前記最後の分割段階で分割されたサブブロック内の画素間で画素値が一致しない場合、

前記色変換部は、前記最後の分割段階で分割されたサブブロック内の各画素を色変換処理し、

前記出力バッファーは、色変換処理された各画素の画素値を、前記最後の分割段階で分割されたサブブロック内の各画素の色変換処理後の画素値として記憶する請求項1に記載の画像処理装置が提供される。

【0011】

請求項3に記載の発明によれば、

前記比較器は、画素の画素値とともに、当該画素値が属する色空間を比較し、

前記出力バッファーは、前記比較部による比較の結果、画素値と色空間が一致する場合のみ、前記画素値のコピーを行う請求項1又は2に記載の画像処理装置が提供される。

【0012】

請求項4に記載の発明によれば、

前記比較部は、画素の画素値とともに、当該画素の画像の属性を比較し、

前記出力バッファーは、前記比較部による比較の結果、画素値と属性が一致する場合のみ、前記画素値のコピーを行う請求項1〜3の何れか一項に記載の画像処理装置が提供される。

【発明の効果】

【0013】

本発明によれば、色変換処理において、1画素の色変換処理結果を他の画素にコピーする処理をハードウェアによって実現することができる。コピーにより、複数の色変換部を並列に設けずとも色変換処理の高速化が可能であり、ハードウェアの規模の拡大を抑えて、ハードウェアによる色変換処理の高速化を図ることができる。

また、アドレスを分割段階の順に割り当てることにより、色変換処理結果を効率良くコピーすることができ、さらなる高速化を図ることができる。

【図面の簡単な説明】

【0014】

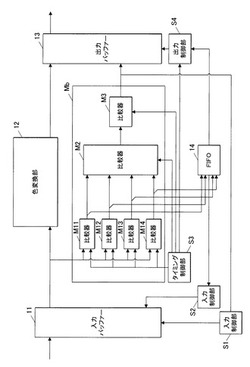

【図1】画像形成装置の構成図である。

【図2】本実施の形態に係る画像処理装置の構成図である。

【図3】1ブロックが複数段階で分割されたときの各分割段階のサブブロック単位と、分割段階順にサブブロック単位で各画素に割り当てられたアドレスを示す図である。

【図4】アドレスと色変換処理の順番の関係を示す図である。

【図5】図3に示すアドレスが割り当てられた場合の色変換処理の処理時間を示す図である。

【図6】他のアドレスの割り当て例を示す図である。

【図7】図6に示すアドレスが割り当てられた場合の色変換処理の処理時間を示す図である。

【図8】各分割段階のサブブロック間での画素値の比較の結果と、色変換処理後の画素値のコピー例を示す図である。

【発明を実施するための形態】

【0015】

以下、図面を参照して、本発明に係る画像処理装置の実施の形態について説明する。

【0016】

図1は、画像形成装置Tの機能ブロック図を示す。画像形成装置Tには、本実施の形態に係る画像処理装置Gが搭載されている。画像形成装置Tは、コピーの他、ユーザー端末から送信されたPDL(Page Description Language)データを印刷することができる。

画像形成装置Tは、図1に示すように、コントローラー1、画像読取部2、画像処理装置G、画像メモリー3、画像形成部4、制御部5、記憶部6、操作部7、表示部8を備えている。

【0017】

コントローラー1は、ユーザー端末から送信されたPDLデータをラスタライズ処理し、ビットマップ形式の画像データを生成する。コントローラー1は、PDLデータから印刷コマンドを抽出し、画像データとともに出力する。印刷コマンドは、ユーザー端末において設定された、印刷部数、印刷サイズ、給紙トレイ等の基本的な印刷指示の他、ページ割付、スタンプの付加、ページ番号の付加等のオプションの印刷指示を含む。

【0018】

コントローラー1は、ラスタライズ処理時、各画素について画像の属性を示す属性データを生成する。画像の属性としては、文字(text)、図形(graphic)、写真(photograph)が挙げられる。属性データは、画像データとともに出力される。

【0019】

画像読取部2は、スキャナーを備え、原稿をスキャンして画像データを生成する。画像読取部2により生成された画像データの色空間は、R(赤)、G(緑)、B(青)の色空間である。

【0020】

画像処理装置Gは、画像データを色変換処理し、画像データの色空間を、画像形成部4により表現可能なC(シアン)、M(マジェンタ)、Y(イエロー)、K(黒)の色空間に変換する。画像読取部2により生成された画像データはRGBの色空間に属するので、画像処理装置Gは、RGBの色空間をCMYKの色空間に変換する。コントローラー1により生成された画像データはCMYKの色空間に属するが、この色空間には、元のデータを作成したユーザー端末や、画像データを生成したコントローラー1に固有の色特性が反映されているので、画像処理装置Gは、CMYKの色空間を、ユーザー端末、コントローラー1の色特性が補正されたCMYKの色空間に変換する。

【0021】

その他、画像処理装置Gは、画像データに各種画像処理を施す。

例えば、画像処理装置Gは、色変換処理された画像データを圧縮処理し、画像メモリー3に出力する。また、画像処理装置Gは、画像メモリー3から圧縮処理された画像データを読み出し、伸張処理する。

画像処理装置Gは、印刷コマンドに従って、画像データに拡大縮小、回転、スタンプやページ番号の付加等の画像処理を施すこともできる。

また、画像処理装置Gは、画像データにスクリーン処理を施す。

【0022】

画像メモリー3は、画像処理装置Gによって圧縮処理された画像データを記憶する。画像メモリー3としては、DRAM(Dynamic Random Access Memory)を用いることができる。

【0023】

画像形成部4は、給紙部、露光部、現像部、感光ドラム、定着装置等を備え、電子写真方式の印刷処理を行う。印刷処理において、露光部はPWM変換された画像データに基づき、帯電した感光ドラム上にレーザ光を照射する。感光ドラム上には静電潜像が形成される。現像部が感光ドラムを現像すると、感光ドラム上にトナーの画像が形成され、当該トナー画像は中間転写ベルトに1次転写される。CMYKの4色のトナーについて同様の画像形成が繰り返し行われ、中間転写ベルト上に4色分のトナー画像が重ねられ、カラー画像が形成される。カラー画像は、給紙部から給紙された用紙上に2次転写され、用紙は定着装置に搬送されて定着処理される。

【0024】

制御部5は、CPU(Central Processing Unit)、RAM等を備えて構成されている。制御部5は、記憶部6に記憶されているプログラムを読み出し、当該プログラムとの協働によって各種処理を実行し、画像形成装置Tの各部を制御する。

記憶部6は、制御部5により用いられるプログラムやデータ等を記憶している。

【0025】

操作部7は、タッチパネルやキー等を備え、これらの操作に応じた操作信号を制御部5に出力する。

表示部8は、制御部5の指示に従い、タッチパネルやディスプレイ上に、操作画面等を表示する。

【0026】

次に、画像処理装置Gによる色変換処理について説明する。

図2は、上記画像処理装置Gの構成図であるが、色変換処理に関する構成部のみ示している。

図2に示すように、画像処理装置Gは、入力バッファー11、色変換部12、出力バッファー13、FIFO(First In First Out)14、比較部Mb、入力制御部S1、S2、タイミング制御部S3、出力制御部S4を備えて構成されている。

【0027】

入力バッファー11は、入力制御部S1から入力された制御信号に応じて、画像データをm×n画素のブロック単位で入力し、保持するメモリーである。ブロックのサイズm×n画素は、任意に設定することができる。サイズm×n画素が大きければ、ブロック内の全画素が同一の画素値であった場合、そのうちの1画素のみ色変換処理すればよいので、処理時間の短縮が可能である。サイズm×n画素が小さければ、入力バッファー11及び出力バッファー13を、小容量化することができ、色変換処理を行うハードウェア、つまり画像処理装置Gの規模を縮小することができる。

【0028】

入力バッファー11は、入力された1ブロックを分割し、分割されたサブブロック内を分割することを繰り返して、入れ子構造のように、1ブロックを複数段階で分割する。分割は、等分割であってもよいし、非等分割として異なるサイズのサブブロックを得てもよい。

【0029】

入力バッファー11は、分割されたサブブロック単位で各画素にアドレスを割り当てるが、分割段階の順に、最初の分割段階で分割されたサブブロック単位から、最後の分割段階で分割されたサブブロック単位の順に割り当てる。

【0030】

図3は、1ブロックとして入力された8×8画素のアドレス例を示す。

図3に示すように、入力バッファー11は、入力された1ブロックを4分割し、4分割されたサブブロック内をさらに4分割して、2段階で分割する。1段階目の分割によるサブブロックをサブブロック[1]、2段階目の分割によるサブブロックをサブブロック[2]と表す。

【0031】

複数段階で分割されたサブブロック[1]、[2]のうち、最初の分割段階で分割されたサブブロック単位はサブブロック[1]であるので、図3に示すように、4つのサブブロック[1]のそれぞれ左上の画素に、0、1、2、3のアドレスが割り当てられている。次の分割段階のサブブロック単位は、最後の分割段階で分割されたサブブロック[2]である。よって、サブブロック[1]と代表画素が共通し、既にアドレスが割り当てられたサブブロック[2]を除き、図3に示すように、12のサブブロック[2]のそれぞれの左上の画素に、4〜15のアドレスが割り当てられている。これらのアドレス0〜15が割り当てられた画素が、各サブブロック[1]、[2]の代表画素である。代表画素は、サブブロック[1]、[2]間の比較の際、その画素値が用いられる画素である。図3の例では、サブブロック[1]、[2]の左上に位置する画素を代表画素としたが、サブブロック[2]、[1]内の何れか1画素を選択するのであれば、どの画素を代表画素として選択するかは特に限定されない。

【0032】

サブブロック[2]内の代表画素を除く他の画素には、各サブブロック[2]に割り当てられたアドレス0〜15に、サブブロック[2]内の画素の位置を表すa〜cを組み合わせたアドレスが割り当てられている。例えば、代表画素のアドレスが0のサブブロック[2]であれば、右上の画素に0a、左下の画素に0b、右下の画素に0cのアドレスが、それぞれ割り当てられている。

【0033】

入力バッファー11は、上述のようにアドレスが割り当てられた画素のうち、入力制御部S2から出力されたアドレスの画素の画素値を、当該アドレスに対応付けて色変換部12に出力する。

また、入力バッファー11は、サブブロック[2]単位で各画素の画素値を、比較部Mbの比較器M11〜M14にそれぞれ出力する。

【0034】

色変換部12は、入力バッファー11からアドレス順に画素単位で入力された画素値を色変換処理する。

色変換部12は、LUTを用いて色変換処理する。LUTは2種類準備され、1つはコントローラー1から出力された画像データ用に、CMYKの色空間の画素値に対し、同じくCMYKの色空間の画素値が設定されたLUTである。もう1つは、画像読取部2から出力された画像データ用に、RGBの色空間の画素値に対し、CMYKの色空間の画素値が設定されたLUTである。コントローラー1、画像読取部2、画像形成部4は、それぞれに固有の色特性を有するが、色変換処理後のCMYKの色空間の画素値は、これらの色特性が補正された画素値である。

【0035】

LUTのデータ量を減じるため、色空間の全ての画素値ではなく、代表値のみ設定されたLUTが用いられる。色変換部12は、LUTに設定された代表値を補間演算することによって、代表値間の画素値を求める。

【0036】

様々な色空間に対応するため、色変換部12は、入力される画像データの色空間毎にLUTを備え、色変換処理する画素値が属する色空間によって、LUTを切り替えることが好ましい。色空間毎のLUTとしては、例えばL*a*b*の色空間をCMYKの色空間に変換するLUT、L*u*v*の色空間をCMYKの色空間に変換するLUTが挙げられる。また、RGBの中でも、sRGB、Adobe(登録商標)RGBがあるので、これらをCMYKの色空間に変換するLUTをそれぞれ備えてもよい。

【0037】

また、色変換部12は、画像の属性毎にLUTを備えることが好ましい。画像の属性によって、例えば文字と写真とでは求められる色特性が異なる。よって、色変換部12が、それぞれの属性に応じた色特性を実現するように、入力値に対する出力値が定められたLUTを備え、色変換処理する画素の画像の属性によって、LUTを切り替えることが好ましい。各画素の画像の属性は、画像データとともに出力された属性データに基づいて判断することができる。

【0038】

出力バッファー13は、1ブロックの各画素の色変換処理後の画素値を記憶するメモリーである。出力バッファー13は、入力バッファー11により各画素に割り当てられたアドレスに対応付けて、色変換処理後の画素値を記憶し、1ブロック分の色変換処理後の画素値が得られると、これを出力する。

【0039】

比較部Mbによる比較の結果、サブブロック[2]内の画素間で画素値が一致し、サブブロック[2]間で画素値が一致する場合、当該サブブロック[2]からなるサブブロック[1]内で画素値が一致することを示すフラグ信号が、比較部Mbから出力バッファー13に入力される。出力バッファー13は、当該フラグ信号とともに入力されたサブブロック[1]の代表画素のアドレスに対応付けて、色変換部12から出力された当該代表画素の色変換処理後の画素値を記憶するとともに、同じサブブロック[1]内の他のサブブロック[2]の画素にコピーして記憶する。

【0040】

比較部Mbによる比較の結果、サブブロック[2]内の画素間で画素値が一致し、サブブロック[2]間でもサブブロック[1]間でも画素値が一致する場合、1ブロック内で画素値が一致することを示すフラグ信号が、比較部Mbから出力バッファー13に入力される。出力バッファー13は、サブブロック[1]間で最初に色変換処理された画素の色変換処理後の画素値を、他の画素にコピーして記憶する。

【0041】

FIFO14は、メモリーやフリップフロップ等から構成されている。FIFO14は、比較部Mbの比較器M11〜M14から出力された、サブブロック内で画素値が一致しない各画素のアドレスを記憶する。FIFO14は、当該アドレスを入力制御部S2、出力制御部S4にそれぞれ出力する。

【0042】

比較部Mbは、比較器M11〜M14、M2、M3を備えている。

各比較器M11〜M14、M2、M3は、タイミング制御部S3から出力されたイネーブル信号に応じて、入力された画素値同士を比較する。

【0043】

比較器M11〜M14は、入力バッファー11から、1ブロックが分割されたサブブロック[2]単位で各画素の画素値を入力し、サブブロック[2]内の画素間で画素値を比較する。

図3に示すようにアドレスが割り当てられた場合、比較器M11にはアドレス0、0a、0b、0cの画素の画素値が入力され、比較器M12にはアドレス4、4a、4b、4cの画素値が入力される。同様に、比較器M13にはアドレス5、5a、5b、5cの画素値が入力され、比較器M14には6、6a、6b、6cの画素値が入力される。比較器M11〜M14は、それぞれ入力された4画素の画素値を比較する。比較が終了すると、次に、代表画素のアドレスが1、7〜9のサブブロック[2]の画素値が、それぞれ比較器M11〜M14に入力され、比較される。同様にして、代表画素のアドレスが2、10〜12のサブブロック[2]、3、13〜15のサブブロック[2]の画素値が、順次比較器M11〜M14に入力され、比較される。

【0044】

比較器M11〜M14は、比較の結果、サブブロック[2]内の全ての画素間で画素値が一致した場合、一致することを示すフラグ信号を比較器M3に出力する。また、比較器M11〜M14は、当該サブブロック[2]の代表画素の画素値を、そのアドレスに対応付けて比較器M2に出力する。

比較器M11〜M14は、サブブロック[2]内の全ての画素間で画素値が一致しなかった場合、一致しないことを示すフラグ信号を比較器M2に出力する。また、比較器M11〜M14は、画素値が一致しないサブブロック[2]内の各画素のアドレスを、FIFO14に出力する。

【0045】

比較器M2は、同じサブブロック[1]に属する4つのサブブロック[2]間の画素値を比較する。比較器M2は、4つのサブブロック[2]内でアドレスが先頭の画素、つまり代表画素の画素値を用いて、サブブロック[2]間の画素値を比較する。比較は、比較器M11〜M14による比較の結果、4つのサブブロック[2]全てがサブブロック[2]内の画素値が一致する場合に限り、実施される。

比較器M2は、4つのサブブロック[2]間の画素値が一致する場合、サブブロック[1]で画素値が一致することを示すフラグ信号とともに、4つのサブブロック[2]が属するサブブロック[1]の代表画素の画素値をそのアドレスに対応付けて出力する。

比較器M2は、比較しなかった場合、又は4つのサブブロック[2]間の画素値が一致しない場合、比較器M11〜M14からの出力をそのまま比較器M3に転送する。

【0046】

比較器M3は、4つのサブブロック[1]間の画素値を比較する。比較器M3は、各サブブロック[1]内でアドレスが先頭の画素、つまり代表画素の画素値を用いて、サブブロック[1]間の画素値を比較する。比較は、4つのサブブロック[1]全てがサブブロック[1]内のサブブロック[2]間で画素値が一致する場合に限り、実施される。

比較器M3は、4つのサブブロック[1]間の画素値が一致する場合、1ブロック内の全画素間で画素値が一致することを示すフラグ信号を出力する。

比較器M3は、比較しなかった場合、又は4つのサブブロック[1]間の画素値が一致しない場合、比較器M2からの出力をそのまま出力バッファー13に転送する。

【0047】

上記比較器M11〜M14、M2、M3は、画素の画素値とともに、当該画素値が属する色空間を比較する。上述のように、色変換部12が入力される画像データの色空間毎にLUTを備えている場合、色空間が異なれば、色変換処理に用いられるLUTが切り替えられる。よって、比較器M11〜M14、M2、M3が、サブブロック内の各画素の画素値及びその色空間が一致する場合のみ、一致したことを示すフラグ信号を出力し、出力バッファー13が、画素値だけでなく色空間も一致する場合のみ、色変換処理後の画素値をコピーするようにすればよい。

【0048】

比較器M11〜M14、M2、M3は、画素の画素値とともに、当該画素の画像の属性を比較することが好ましい。上述のように、画像の属性によって色特性が異なり、色変換部12が画像の属性毎にLUTを備えている場合、画像の属性によって、用いられるLUTが切り替えられる。よって、比較器M11〜M14、M2、M3が、サブブロック内の各画素の画素値及び属性が一致する場合のみ、一致したことを示すフラグ信号を出力し、出力バッファー13が、画素値だけでなく画像の属性も一致する場合のみ、色変換処理後の画素値をコピーするようにすればよい。

【0049】

なお、比較器M11〜M14、M2、M3が、画素の画素値とともに、当該画素の属性及び当該画素値が属する色空間を比較してもよい。

【0050】

入力制御部S1は、入力バッファー11がブロック単位の画像データを入力するタイミングを制御する。入力制御部S1は、比較部Mbから1ブロック分の比較結果が出力されると、次の1ブロックの画像データの入力を指示する制御信号を、入力バッファー11に出力する。これにより、間をおかずに次のブロックの画像データの入力が可能となる。

【0051】

入力制御部S2は、入力バッファー11に対し、代表画素のアドレス0〜15を順次出力し、0〜15のアドレス順に色変換処理されるように調整する。FIFO14から入力されたアドレスがあれば、当該アドレスをアドレス0〜15に続けて出力する。これにより、図4に示すように、入力バッファー11から色変換部12へは、アドレス0〜15の順に代表画素の画素値が出力され、その後、サブブロック[2]内で画素値が一致しない画素の画素値が順次出力される。

【0052】

タイミング制御部S3は、比較部Mbの比較器M11〜M14、M2、M3にイネーブル信号を出力し、比較部Mbが画素値を比較するタイミングを制御する。1回の比較に1クロック要する場合、タイミング制御部S3は、各比較器M11〜M14に1クロック毎にイネーブル信号を4回出力する。タイミング制御部S3は、比較器M11〜M14に4回目のイネーブル信号を出力した後、比較器M2に1クロック毎にイネーブル信号を4回出力する。比較器M3に対しては、タイミング制御部S3は、比較器M2に4回目のイネーブル信号を出力した次のクロックでイネーブル信号を出力する。

【0053】

タイミング制御部S3は、出力制御部S4にイネーブル信号を出力し、FIFO14から出力されたアドレスを、出力制御部S4が出力バッファー13に出力するタイミングを制御する。比較部Mbから比較結果が出力されるタイミングに合わせて、FIFO14からのアドレスを出力する場合、タイミング制御部S3は、比較器M3にイネーブル信号を出力した次のクロックで、出力制御部S4にイネーブル信号を出力する。

【0054】

出力制御部S4は、タイミング制御部S3から出力されたイネーブル信号に応じて、出力バッファー13に、FIFO14から出力されたアドレスを転送する。

【0055】

図2に示された画像処理装置Gによる色変換処理の流れを説明する。

まず、入力バッファー11が1ブロックの画像データを入力する。入力バッファー11は1ブロックを4分割し、分割された各サブブロック[1]の左上に位置する画素を代表画素として、アドレス0〜3を割り当てる。入力バッファー11は、さらに各サブブロック[1]を4分割し、既にアドレスが割り当てられているサブブロック[2]を除き、分割された各サブブロック[2]の左上に位置する画素を代表画素として、アドレス4〜15を割り当てる。最後に、入力バッファー11は、サブブロック[2]内の代表画素以外の他の画素に、アドレス(0a、0b、0c)〜(15a、15b、15c)を割り当てる。これにより、図3に示すようにアドレスが割り当てられる。

【0056】

分割段階の順にサブブロック単位でアドレスを割り当てることにより、色変換処理される代表画素の順番が、最初の分割段階のサブブロック[1]から最後の分割段階のサブブロック[2]の順番となるように、調整することができる。これにより、比較部Mbの比較結果に合わせて色変換処理結果を得ることができ、色変換処理全体として処理時間を短縮することができる。

【0057】

図5に示すように、色変換部12が1クロック毎に1画素入力し、1画素の色変換処理に100クロックの処理時間を要する場合、1ブロックの全64画素を個々に色変換処理すると、163(163=100+64−1)クロックの処理時間を要する。

比較部Mbは、1画素の色変換処理の処理時間100クロックに比べて、はるかに短時間で比較を終えることができる。比較部Mbの比較の結果、1ブロック内の全画素の画素値が一致する場合、最初の1画素の色変換処理後の画素値を他の画素にコピーすればよいので、色変換処理は1画素の処理時間、つまり100クロックで終了する。この場合、処理時間はアドレスの割り当てに左右されない。

【0058】

アドレスの割り当てによって処理時間が変わるのは、サブブロック[1]内で画素値をコピーする場合である。

図3に示すように、分割段階の順に、サブブロック[1]単位からサブブロック[2]単位の順に、アドレスが割り当てられた場合、サブブロック[1]の代表画素のアドレスが、アドレスの先頭に位置するので、サブブロック[1]の代表画素から先に色変換処理される。そのため、サブブロック[1]の代表画素の色変換処理後の画素値を、当該サブブロック[1]内の他の画素にコピーする場合、図5に示すように、アドレス0〜3の代表画素の色変換処理結果が得られれば、各サブブロック[1]内で画素値をコピーでき、最大で100+4−1=103クロックの処理時間で終了する。

【0059】

これに対し、図6に示すように、分割段階の順番に関係無く、サブブロック[2]単位でアドレス0〜15が割り当てられた場合、色変換処理に無駄が生じることがある。例えば、アドレス0のサブブロック[1]内で画素値が一致している場合、アドレス0の代表画素の画素値を他の画素にコピーすればいいので、代表画素1、4、5の色変換処理は無駄となる。全てのサブブロック[1]内で画素値が一致している場合、アドレス0、2、8、10の代表画素が色変換処理されるまで、各サブブロック[1]内の他の画素に、代表画素の色変換処理結果をコピーすることができない。図7に示すように、アドレス10の代表画素の色変換処理結果が得られるまで、最大で100+11−1=110クロックの処理時間を要する。

【0060】

結果として、図3に示すアドレスの割り当ての場合、図6に示すアドレスの割り当ての場合と比較して、7クロック分の短縮が可能である。7クロックという処理時間の短縮は、短縮の程度が小さいように見えるが、例えば600dpiでA4サイズの画像データは、4961×2480画素であるのに対し、1ブロックは8×8画素であるので、画像データの全領域に対するブロック数は非常に多い。よって、1ブロックで7クロックの短縮ができれば、全領域の処理時間を大きく短縮することができる。

また、1ブロックのサイズが大きければ大きいほど、サブブロック[1]の数が増えるので、処理時間の短縮の効果がより大きく働く。

【0061】

サブブロック[2]内で代表画素の色変換処理後の画素値をコピーする場合も同様に、アドレス0〜15の代表画素が色変換処理されるまでコピーができない。最大で、アドレス15の画素の色変換処理結果が得られるまで、100+16−1=115(クロック)の処理時間を要する。しかし、サブブロック[1]と異なり、サブブロック[2]の場合、アドレスの割り当てによる処理時間の短縮の効果は無い。アドレスの割り当てによる処理時間の短縮の効果があるのは、最後の分割段階で分割されたサブブロック単位より前の分割段階で分割されたサブブロック単位の比較に対してである。

【0062】

なお、4分割を2段階で行う例で説明したが、例えば16画素×16画素を1ブロックとして入力し、4分割を3段階で行う場合、最初の1段階目の分割によって4つのサブブロック[1]、2段階目の分割によって16のサブブロック[2]、最後の3段階目の分割によって64のサブブロック[3]が得られる。この場合は、最初の分割段階のサブブロック単位であるサブブロック[1]から先にアドレスを割り当て、続いて、次の分割段階のサブブロック[2]、最後の分割段階のサブブロック単位であるサブブロック[3]の順にアドレスを割り当てればよい。これにより、サブブロック[1]、[2]内で色変換処理後の画素値をコピーするとき、上述のように処理時間の短縮の効果が得られる。

【0063】

アドレスが割り当てられると、入力制御部S2から代表画素のアドレス0〜15が順次入力されるので、入力バッファー11は、当該アドレスの代表画素の画素値を、アドレスに対応付けて色変換部12に順次出力する。色変換部12は、アドレス0〜15の順に出力された代表画素の画素値を色変換処理する。

また、入力バッファー11は、代表画素のアドレスが0のサブブロック[1]に属する4つのサブブロック[2]内の各画素の画素値を、比較器M11〜M14に出力する。これにより、アドレス0、0a、0b、0cの画素が比較器M11に、アドレス4、4a、4b、4cの画素が比較器M12に、アドレス5、5a、5b、5cの画素が比較器M13に、アドレス6、6a、6b、6cの画素が比較器M14に、それぞれ出力される。

【0064】

比較器M11〜M14は、サブブロック[2]内の画素間で画素値が一致する場合、一致したことを示すフラグ信号と、当該サブブロック[2]の代表画素の画素値を、そのアドレスに対応付けて比較器M3に出力する。

【0065】

比較器M11〜M14は、サブブロック[2]内の画素間で画素値が一致しない場合、一致しなかったことを示すフラグ信号を比較器M2に出力する。また、比較器M11〜M14は、画素値が一致しなかったサブブロック[2]内の各画素のアドレスを、FIFO14に出力する。

【0066】

FIFO14に出力されたアドレスは、入力制御部S2を介して入力バッファー11に出力される。入力バッファー11は、アドレス0〜15の代表画素に続けて、画素値が一致しなかったサブブロック[2]内の各画素の画素値を、そのアドレスに対応付けて色変換部12に出力する。

また、FIFO14に出力されたアドレスは、出力制御部S4を介して出力バッファー13に出力される。

【0067】

比較器M2は、比較器M11〜M14の全てから、サブブロック[2]内の画素間で画素値が一致したことを示すフラグ信号が入力された場合、フラグ信号とともに入力された各サブブロック[2]の代表画素の画素値を比較し、代表画素のアドレスが0のサブブロック[1]に属する4つのサブブロック[2]間で画素値を比較する。つまり、アドレス0、4、5、6の代表画素間で、それぞれ画素値が比較される。

【0068】

比較器M2は、4つのサブブロック[2]の代表画素間で画素値が一致した場合、代表画素のアドレスが0のサブブロック[1]内で画素値が一致することを示すフラグ信号と、当該サブブロック[1]の代表画素の画素値をそのアドレス0に対応付けて出力する。

比較器M2は、4つのサブブロック[2]の代表画素間で画素値が一致しなかった場合、代表画素のアドレスが0のサブブロック[1]内で画素値が一致しないことを示すフラグ信号とともに、比較器M11〜M14から入力されたフラグ信号、代表画素の画素値等をそのまま比較器M3に転送する。

【0069】

一方、比較器M11〜M14の何れかから、サブブロック[2]内の画素間で画素値が一致しないことを示すフラグ信号が入力された場合、比較器M2は比較を行わず、代表画素のアドレスが0のサブブロック[1]内で画素値が一致しないことを示すフラグ信号とともに、比較器M11〜M14から入力されたフラグ信号、代表画素の画素値等をそのまま比較器M3に転送する。

【0070】

比較器M11〜M14、M2は、上記代表画素のアドレス0のサブブロック[1]と同様にして、代表画素のアドレス1、2、3のサブブロック[1]についても、順次比較する。

【0071】

比較器M3は、比較器M2から、4つ全てのサブブロック[1]について、サブブロック[1]内の画素値が一致することを示すフラグ信号が入力された場合、当該フラグ信号とともに入力された各サブブロック[1]の代表画素の画素値を用いて、サブブロック[1]間の画素値を比較する。つまり、アドレス0、1、2、3の代表画素の画素値が比較される。

【0072】

比較器M3は、全てのサブブロック[1]の代表画素の画素値が一致した場合、1ブロック内の全画素間で画素値が一致することを示すフラグ信号を出力バッファー13に出力する。

出力バッファー13は、当該フラグ信号に応じて、最初に色変換部12から出力されたアドレス0の代表画素の色変換処理後の画素値を、1ブロック内の他の画素にコピーし、記憶する。

【0073】

比較器M3は、比較器M2から、4つのうち、何れかのサブブロック[1]内で画素値が一致しないことを示すフラグ信号が入力された場合、比較は行わず、比較器M2から出力されたフラグ信号等を出力バッファー13に転送する。

出力バッファー13は、当該フラグ信号に応じて、サブブロック[2]間で画素値が一致するサブブロック[1]については、その代表画素の色変換処理後の画素値を、当該サブブロック[1]内の代表画素以外の他の画素にコピーし、記憶する。

同様に、出力バッファー13は、サブブロック[2]内で画素値が一致するサブブロック[2]についても、その代表画素の色変換処理後の画素値を、当該サブブロック[2]内の代表画素以外の他の画素にコピーし、記憶する。

サブブロック[2]内でも画素値が一致しないサブブロック[2]については、当該サブブロック[2]内の各画素がそれぞれ色変換部12に出力され、色変換処理される。出力バッファー13には、出力制御部S4から当該サブブロック[2]内の各画素のアドレスが入力されるので、出力バッファー13は、当該アドレスの画素の色変換処理後の画素値を記憶する。

【0074】

図8は、色変換処理後の画素値のコピー例を示す。図8中、×の記号は画素値が一致しないことを表し、○の記号は画素値が一致することを表している。

図8に示すように、比較器M11〜M14による比較の結果、代表画素のアドレス0のサブブロック[2]以外のサブブロック[2]内の画素値が一致している。

比較器M2による比較の結果、代表画素のアドレス1、2、3のサブブロック[1]内のサブブロック[2]間で画素値が一致している。比較器M2は、アドレス0のサブブロック[1]に属するサブブロック[2]間では画素値の比較を行わず、比較器M11〜M14の比較結果をそのまま出力する。

比較器M3は、比較されなかったサブブロック[1]があるため、サブブロック[1]間で画素値の比較を行わず、比較器M2からの出力をそのまま出力バッファー13に出力する。

【0075】

以上の比較の結果、出力バッファー13では、アドレス0のサブブロック[2]については、アドレス0、0a、0b、0cの各画素の色変換処理後の画素値が記憶される。代表画素のアドレスが4、5、6のサブブロック[2]については、アドレス4、5、6の各代表画素の色変換処理後の画素値が、それぞれのサブブロック[2]内の他の画素にコピーされる。アドレス1、2、3のサブブロック[1]についても同様に、アドレス1、2、3の各代表画素の色変換処理後の画素値が、それぞれのサブブロック[1]内の他の画素にコピーされる。

【0076】

以上のように、本実施の形態によれば、画像処理装置Gは、画像データをブロック単位で入力し、入力された1ブロックを複数段階で分割し、分割段階の順に、分割されたサブブロック単位で、各画素にアドレスを割り当てる入力バッファー11と、入力バッファー11からアドレス順に画素単位で画素値を入力し、色変換処理する色変換部12と、色変換部12によって色変換処理された各画素の画素値を、各画素に割り当てられたアドレスに対応付けて記憶する出力バッファー13と、入力バッファー11から、1ブロックが複数段階で分割されたサブブロック[2]単位で各画素の画素値を入力し、最後の分割段階で分割されたサブブロック[2]内の画素間で画素値を比較するとともに、各サブブロック[1]、[2]内でアドレスが先頭の1画素の画素値を用いて、同じ分割段階で分割されたサブブロック[1]、[2]間で画素値を比較する比較部Mbと、を備える。出力バッファー13は、比較部Mbによる比較の結果、最後の分割段階で分割されたサブブロック[2]内の画素間で画素値が一致し、何れかの分割段階のサブブロック[1]、[2]間で画素値が一致する場合、当該サブブロック[1]、[2]間で最初に色変換処理された画素の色変換処理後の画素値を、各サブブロック[1]、[2]の画素にコピーして記憶する。

【0077】

これにより、色変換処理と並行して画素値を比較し、1画素の色変換処理結果を他の画素にコピーする処理をハードウェアによって実現することができる。コピーにより、複数の色変換部を並列に設けずとも色変換処理の高速化が可能であり、ハードウェアの規模の拡大を抑えて、ハードウェアによる色変換処理の高速化を図ることができる。

一般に、画像データ全体のサイズに対し、1ブロックのサイズは非常に小さく、1ブロック内の画素値が一致することが多いと考えられる。この場合、1ブロックの処理時間は実質1画素の処理時間となり、ソフトウェアによって画像データを1画素ずつ処理する場合に比べて、大幅な処理時間の短縮が見込める。

【0078】

また、同じ分割段階のサブブロック[1]、[2]間で画素値を比較するので、色変換処理結果をコピーする領域を段階的に拡大することができ、1ブロック内に異なる画素値が存在する場合にコピーの効率が良い。

さらに、アドレスを分割段階の順に割り当てることにより、比較の結果に合わせて色変換処理結果を効率良くコピーすることができ、色変換処理のさらなる高速化を図ることができる。

【0079】

また、本実施の形態によれば、最後の分割段階で分割されたサブブロック[2]内の画素間で画素値が一致しない場合、色変換部12は、最後の分割段階で分割されたサブブロック[2]内の各画素を色変換処理し、出力バッファー13は、色変換処理された各画素の画素値を、最後の分割段階で分割されたサブブロック[2]内の各画素の色変換処理後の画素値として記憶する。

画素値が一致しないサブブロックのみ、各画素が色変換処理されるので、色変換処理全体の処理速度を高速化することができる。

【0080】

上記実施の形態は本発明の好適な一例であり、これに限定されない。本発明の主旨を逸脱しない範囲で適宜変更可能である。

【符号の説明】

【0081】

T 画像形成装置

1 コントローラー

2 画像読取部

3 画像メモリー

4 画像形成部

G 画像処理装置

11 入力バッファー

12 色変換部

13 出力バッファー

14 メモリー

Mb 比較部

M11〜M14、M2、M3 比較器

S1、S2 入力制御部

S4 出力制御部

【技術分野】

【0001】

本発明は、画像処理装置に関する。

【背景技術】

【0002】

プリンターやコピー機等の画像形成装置においては、画像データを色変換処理し、入力された画像データの色空間を、画像形成装置が表現可能な色空間に一致させている。

色空間同士は複雑な関係にあるため、色変換処理では、色変換後の画素値を逐一演算するのではなく、入力値に対し色変換後の出力値が定められたLUT(Look Up Table)が利用されている(例えば、特許文献1参照)。LUTにおいて、全ての入力値に対応する出力値を定めると、大容量のメモリーが必要となるため、LUTは、通常、代表色についてのみ入力値と出力値が定められ、他は補間演算によって出力値を得ている。

【0003】

代表色のみ入力値と出力値を保持するようにしても、必要なメモリー容量は小さくない。そのうえ、色空間を構成する色数が増えれば、それだけLUTに保持すべき入力値と出力値が増え、大容量のメモリーが必要となる。そのため、色変換処理を、LSI(Large Scale Integration)のようなハードウェアで行うには、負担が大きいことが知られている。特に、出力がCMYKの色空間である画像形成装置の場合、色数が多く、負担が大きい。

【0004】

ハードウェアによる処理速度を高速化するためには、処理回路を複数設けて、並列に処理していく方法が一般的であるが、色変換処理に関しては、上述したような容量の大きいLUTを並列に設けることになるため、ハードウェアへの実装は困難を伴う。

【0005】

そのため、従来、色変換処理は、ハードウェアではなく、ソフトウェアにより実現されることが多かった(例えば、特許文献1、2参照)。文字や図形の画像領域内は同一色である場合が多く、ソフトウェアによれば、そのような同一色の領域では色変換処理の結果を一括変換し、処理時間を短縮することができる。特許文献1によれば、注目画素と同一画素値を持つ画素の連続数を求め、その連続数だけ注目画素の色変換処理後の画素値に置換することにより、色変換処理する画素数を減じて処理時間を短縮する。特許文献2によれば、プリンタドライバーにより印刷データを生成する段階で、特許文献1と同様の処理を実現することができる。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008−205636号公報

【特許文献2】特開2004−54653号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

一方、写真の画像領域は、隣接画素の画素値が同一であるとは限らず、予測できない。そのため、全画素について1画素ずつ色変換処理する以外に方法が無く、処理速度の低下の要因となっている。結果として、ソフトウェアによる色変換処理は、ハードウェアによって処理する場合に比べて、やはり処理速度が遅く、高速化が望まれている。

【0008】

本発明の課題は、ハードウェアの規模の拡大を抑えて、ハードウェアによる色変換処理の高速化を図ることである。

【課題を解決するための手段】

【0009】

請求項1に記載の発明によれば、

画像データをブロック単位で入力し、入力された1ブロックを複数段階で分割し、分割段階の順に、分割されたサブブロック単位で、各画素にアドレスを割り当てる入力バッファーと、

前記入力バッファーからアドレス順に画素単位で画素値を入力し、色変換処理する色変換部と、

前記色変換部によって色変換処理された各画素の画素値を、各画素に割り当てられた前記アドレスに対応付けて記憶する出力バッファーと、

前記入力バッファーから、1ブロックが複数段階で分割されたサブブロック単位で各画素の画素値を入力し、最後の分割段階で分割されたサブブロック内の画素間で画素値を比較するとともに、同じ分割段階で分割されたサブブロック間で画素値を比較する比較部と、を備え、

前記比較部は、各サブブロック内でアドレスが先頭の1画素の画素値を用いて、サブブロック間の画素値を比較し、

前記出力バッファーは、前記比較部による比較の結果、最後の分割段階で分割されたサブブロック内の画素間で画素値が一致し、何れかの分割段階のサブブロック間で画素値が一致する場合、当該サブブロック間で最初に色変換処理された画素の色変換処理後の画素値を、各サブブロックの画素にコピーして記憶する画像処理装置が提供される。

【0010】

請求項2に記載の発明によれば、

前記最後の分割段階で分割されたサブブロック内の画素間で画素値が一致しない場合、

前記色変換部は、前記最後の分割段階で分割されたサブブロック内の各画素を色変換処理し、

前記出力バッファーは、色変換処理された各画素の画素値を、前記最後の分割段階で分割されたサブブロック内の各画素の色変換処理後の画素値として記憶する請求項1に記載の画像処理装置が提供される。

【0011】

請求項3に記載の発明によれば、

前記比較器は、画素の画素値とともに、当該画素値が属する色空間を比較し、

前記出力バッファーは、前記比較部による比較の結果、画素値と色空間が一致する場合のみ、前記画素値のコピーを行う請求項1又は2に記載の画像処理装置が提供される。

【0012】

請求項4に記載の発明によれば、

前記比較部は、画素の画素値とともに、当該画素の画像の属性を比較し、

前記出力バッファーは、前記比較部による比較の結果、画素値と属性が一致する場合のみ、前記画素値のコピーを行う請求項1〜3の何れか一項に記載の画像処理装置が提供される。

【発明の効果】

【0013】

本発明によれば、色変換処理において、1画素の色変換処理結果を他の画素にコピーする処理をハードウェアによって実現することができる。コピーにより、複数の色変換部を並列に設けずとも色変換処理の高速化が可能であり、ハードウェアの規模の拡大を抑えて、ハードウェアによる色変換処理の高速化を図ることができる。

また、アドレスを分割段階の順に割り当てることにより、色変換処理結果を効率良くコピーすることができ、さらなる高速化を図ることができる。

【図面の簡単な説明】

【0014】

【図1】画像形成装置の構成図である。

【図2】本実施の形態に係る画像処理装置の構成図である。

【図3】1ブロックが複数段階で分割されたときの各分割段階のサブブロック単位と、分割段階順にサブブロック単位で各画素に割り当てられたアドレスを示す図である。

【図4】アドレスと色変換処理の順番の関係を示す図である。

【図5】図3に示すアドレスが割り当てられた場合の色変換処理の処理時間を示す図である。

【図6】他のアドレスの割り当て例を示す図である。

【図7】図6に示すアドレスが割り当てられた場合の色変換処理の処理時間を示す図である。

【図8】各分割段階のサブブロック間での画素値の比較の結果と、色変換処理後の画素値のコピー例を示す図である。

【発明を実施するための形態】

【0015】

以下、図面を参照して、本発明に係る画像処理装置の実施の形態について説明する。

【0016】

図1は、画像形成装置Tの機能ブロック図を示す。画像形成装置Tには、本実施の形態に係る画像処理装置Gが搭載されている。画像形成装置Tは、コピーの他、ユーザー端末から送信されたPDL(Page Description Language)データを印刷することができる。

画像形成装置Tは、図1に示すように、コントローラー1、画像読取部2、画像処理装置G、画像メモリー3、画像形成部4、制御部5、記憶部6、操作部7、表示部8を備えている。

【0017】

コントローラー1は、ユーザー端末から送信されたPDLデータをラスタライズ処理し、ビットマップ形式の画像データを生成する。コントローラー1は、PDLデータから印刷コマンドを抽出し、画像データとともに出力する。印刷コマンドは、ユーザー端末において設定された、印刷部数、印刷サイズ、給紙トレイ等の基本的な印刷指示の他、ページ割付、スタンプの付加、ページ番号の付加等のオプションの印刷指示を含む。

【0018】

コントローラー1は、ラスタライズ処理時、各画素について画像の属性を示す属性データを生成する。画像の属性としては、文字(text)、図形(graphic)、写真(photograph)が挙げられる。属性データは、画像データとともに出力される。

【0019】

画像読取部2は、スキャナーを備え、原稿をスキャンして画像データを生成する。画像読取部2により生成された画像データの色空間は、R(赤)、G(緑)、B(青)の色空間である。

【0020】

画像処理装置Gは、画像データを色変換処理し、画像データの色空間を、画像形成部4により表現可能なC(シアン)、M(マジェンタ)、Y(イエロー)、K(黒)の色空間に変換する。画像読取部2により生成された画像データはRGBの色空間に属するので、画像処理装置Gは、RGBの色空間をCMYKの色空間に変換する。コントローラー1により生成された画像データはCMYKの色空間に属するが、この色空間には、元のデータを作成したユーザー端末や、画像データを生成したコントローラー1に固有の色特性が反映されているので、画像処理装置Gは、CMYKの色空間を、ユーザー端末、コントローラー1の色特性が補正されたCMYKの色空間に変換する。

【0021】

その他、画像処理装置Gは、画像データに各種画像処理を施す。

例えば、画像処理装置Gは、色変換処理された画像データを圧縮処理し、画像メモリー3に出力する。また、画像処理装置Gは、画像メモリー3から圧縮処理された画像データを読み出し、伸張処理する。

画像処理装置Gは、印刷コマンドに従って、画像データに拡大縮小、回転、スタンプやページ番号の付加等の画像処理を施すこともできる。

また、画像処理装置Gは、画像データにスクリーン処理を施す。

【0022】

画像メモリー3は、画像処理装置Gによって圧縮処理された画像データを記憶する。画像メモリー3としては、DRAM(Dynamic Random Access Memory)を用いることができる。

【0023】

画像形成部4は、給紙部、露光部、現像部、感光ドラム、定着装置等を備え、電子写真方式の印刷処理を行う。印刷処理において、露光部はPWM変換された画像データに基づき、帯電した感光ドラム上にレーザ光を照射する。感光ドラム上には静電潜像が形成される。現像部が感光ドラムを現像すると、感光ドラム上にトナーの画像が形成され、当該トナー画像は中間転写ベルトに1次転写される。CMYKの4色のトナーについて同様の画像形成が繰り返し行われ、中間転写ベルト上に4色分のトナー画像が重ねられ、カラー画像が形成される。カラー画像は、給紙部から給紙された用紙上に2次転写され、用紙は定着装置に搬送されて定着処理される。

【0024】

制御部5は、CPU(Central Processing Unit)、RAM等を備えて構成されている。制御部5は、記憶部6に記憶されているプログラムを読み出し、当該プログラムとの協働によって各種処理を実行し、画像形成装置Tの各部を制御する。

記憶部6は、制御部5により用いられるプログラムやデータ等を記憶している。

【0025】

操作部7は、タッチパネルやキー等を備え、これらの操作に応じた操作信号を制御部5に出力する。

表示部8は、制御部5の指示に従い、タッチパネルやディスプレイ上に、操作画面等を表示する。

【0026】

次に、画像処理装置Gによる色変換処理について説明する。

図2は、上記画像処理装置Gの構成図であるが、色変換処理に関する構成部のみ示している。

図2に示すように、画像処理装置Gは、入力バッファー11、色変換部12、出力バッファー13、FIFO(First In First Out)14、比較部Mb、入力制御部S1、S2、タイミング制御部S3、出力制御部S4を備えて構成されている。

【0027】

入力バッファー11は、入力制御部S1から入力された制御信号に応じて、画像データをm×n画素のブロック単位で入力し、保持するメモリーである。ブロックのサイズm×n画素は、任意に設定することができる。サイズm×n画素が大きければ、ブロック内の全画素が同一の画素値であった場合、そのうちの1画素のみ色変換処理すればよいので、処理時間の短縮が可能である。サイズm×n画素が小さければ、入力バッファー11及び出力バッファー13を、小容量化することができ、色変換処理を行うハードウェア、つまり画像処理装置Gの規模を縮小することができる。

【0028】

入力バッファー11は、入力された1ブロックを分割し、分割されたサブブロック内を分割することを繰り返して、入れ子構造のように、1ブロックを複数段階で分割する。分割は、等分割であってもよいし、非等分割として異なるサイズのサブブロックを得てもよい。

【0029】

入力バッファー11は、分割されたサブブロック単位で各画素にアドレスを割り当てるが、分割段階の順に、最初の分割段階で分割されたサブブロック単位から、最後の分割段階で分割されたサブブロック単位の順に割り当てる。

【0030】

図3は、1ブロックとして入力された8×8画素のアドレス例を示す。

図3に示すように、入力バッファー11は、入力された1ブロックを4分割し、4分割されたサブブロック内をさらに4分割して、2段階で分割する。1段階目の分割によるサブブロックをサブブロック[1]、2段階目の分割によるサブブロックをサブブロック[2]と表す。

【0031】

複数段階で分割されたサブブロック[1]、[2]のうち、最初の分割段階で分割されたサブブロック単位はサブブロック[1]であるので、図3に示すように、4つのサブブロック[1]のそれぞれ左上の画素に、0、1、2、3のアドレスが割り当てられている。次の分割段階のサブブロック単位は、最後の分割段階で分割されたサブブロック[2]である。よって、サブブロック[1]と代表画素が共通し、既にアドレスが割り当てられたサブブロック[2]を除き、図3に示すように、12のサブブロック[2]のそれぞれの左上の画素に、4〜15のアドレスが割り当てられている。これらのアドレス0〜15が割り当てられた画素が、各サブブロック[1]、[2]の代表画素である。代表画素は、サブブロック[1]、[2]間の比較の際、その画素値が用いられる画素である。図3の例では、サブブロック[1]、[2]の左上に位置する画素を代表画素としたが、サブブロック[2]、[1]内の何れか1画素を選択するのであれば、どの画素を代表画素として選択するかは特に限定されない。

【0032】

サブブロック[2]内の代表画素を除く他の画素には、各サブブロック[2]に割り当てられたアドレス0〜15に、サブブロック[2]内の画素の位置を表すa〜cを組み合わせたアドレスが割り当てられている。例えば、代表画素のアドレスが0のサブブロック[2]であれば、右上の画素に0a、左下の画素に0b、右下の画素に0cのアドレスが、それぞれ割り当てられている。

【0033】

入力バッファー11は、上述のようにアドレスが割り当てられた画素のうち、入力制御部S2から出力されたアドレスの画素の画素値を、当該アドレスに対応付けて色変換部12に出力する。

また、入力バッファー11は、サブブロック[2]単位で各画素の画素値を、比較部Mbの比較器M11〜M14にそれぞれ出力する。

【0034】

色変換部12は、入力バッファー11からアドレス順に画素単位で入力された画素値を色変換処理する。

色変換部12は、LUTを用いて色変換処理する。LUTは2種類準備され、1つはコントローラー1から出力された画像データ用に、CMYKの色空間の画素値に対し、同じくCMYKの色空間の画素値が設定されたLUTである。もう1つは、画像読取部2から出力された画像データ用に、RGBの色空間の画素値に対し、CMYKの色空間の画素値が設定されたLUTである。コントローラー1、画像読取部2、画像形成部4は、それぞれに固有の色特性を有するが、色変換処理後のCMYKの色空間の画素値は、これらの色特性が補正された画素値である。

【0035】

LUTのデータ量を減じるため、色空間の全ての画素値ではなく、代表値のみ設定されたLUTが用いられる。色変換部12は、LUTに設定された代表値を補間演算することによって、代表値間の画素値を求める。

【0036】

様々な色空間に対応するため、色変換部12は、入力される画像データの色空間毎にLUTを備え、色変換処理する画素値が属する色空間によって、LUTを切り替えることが好ましい。色空間毎のLUTとしては、例えばL*a*b*の色空間をCMYKの色空間に変換するLUT、L*u*v*の色空間をCMYKの色空間に変換するLUTが挙げられる。また、RGBの中でも、sRGB、Adobe(登録商標)RGBがあるので、これらをCMYKの色空間に変換するLUTをそれぞれ備えてもよい。

【0037】

また、色変換部12は、画像の属性毎にLUTを備えることが好ましい。画像の属性によって、例えば文字と写真とでは求められる色特性が異なる。よって、色変換部12が、それぞれの属性に応じた色特性を実現するように、入力値に対する出力値が定められたLUTを備え、色変換処理する画素の画像の属性によって、LUTを切り替えることが好ましい。各画素の画像の属性は、画像データとともに出力された属性データに基づいて判断することができる。

【0038】

出力バッファー13は、1ブロックの各画素の色変換処理後の画素値を記憶するメモリーである。出力バッファー13は、入力バッファー11により各画素に割り当てられたアドレスに対応付けて、色変換処理後の画素値を記憶し、1ブロック分の色変換処理後の画素値が得られると、これを出力する。

【0039】

比較部Mbによる比較の結果、サブブロック[2]内の画素間で画素値が一致し、サブブロック[2]間で画素値が一致する場合、当該サブブロック[2]からなるサブブロック[1]内で画素値が一致することを示すフラグ信号が、比較部Mbから出力バッファー13に入力される。出力バッファー13は、当該フラグ信号とともに入力されたサブブロック[1]の代表画素のアドレスに対応付けて、色変換部12から出力された当該代表画素の色変換処理後の画素値を記憶するとともに、同じサブブロック[1]内の他のサブブロック[2]の画素にコピーして記憶する。

【0040】

比較部Mbによる比較の結果、サブブロック[2]内の画素間で画素値が一致し、サブブロック[2]間でもサブブロック[1]間でも画素値が一致する場合、1ブロック内で画素値が一致することを示すフラグ信号が、比較部Mbから出力バッファー13に入力される。出力バッファー13は、サブブロック[1]間で最初に色変換処理された画素の色変換処理後の画素値を、他の画素にコピーして記憶する。

【0041】

FIFO14は、メモリーやフリップフロップ等から構成されている。FIFO14は、比較部Mbの比較器M11〜M14から出力された、サブブロック内で画素値が一致しない各画素のアドレスを記憶する。FIFO14は、当該アドレスを入力制御部S2、出力制御部S4にそれぞれ出力する。

【0042】

比較部Mbは、比較器M11〜M14、M2、M3を備えている。

各比較器M11〜M14、M2、M3は、タイミング制御部S3から出力されたイネーブル信号に応じて、入力された画素値同士を比較する。

【0043】

比較器M11〜M14は、入力バッファー11から、1ブロックが分割されたサブブロック[2]単位で各画素の画素値を入力し、サブブロック[2]内の画素間で画素値を比較する。

図3に示すようにアドレスが割り当てられた場合、比較器M11にはアドレス0、0a、0b、0cの画素の画素値が入力され、比較器M12にはアドレス4、4a、4b、4cの画素値が入力される。同様に、比較器M13にはアドレス5、5a、5b、5cの画素値が入力され、比較器M14には6、6a、6b、6cの画素値が入力される。比較器M11〜M14は、それぞれ入力された4画素の画素値を比較する。比較が終了すると、次に、代表画素のアドレスが1、7〜9のサブブロック[2]の画素値が、それぞれ比較器M11〜M14に入力され、比較される。同様にして、代表画素のアドレスが2、10〜12のサブブロック[2]、3、13〜15のサブブロック[2]の画素値が、順次比較器M11〜M14に入力され、比較される。

【0044】

比較器M11〜M14は、比較の結果、サブブロック[2]内の全ての画素間で画素値が一致した場合、一致することを示すフラグ信号を比較器M3に出力する。また、比較器M11〜M14は、当該サブブロック[2]の代表画素の画素値を、そのアドレスに対応付けて比較器M2に出力する。

比較器M11〜M14は、サブブロック[2]内の全ての画素間で画素値が一致しなかった場合、一致しないことを示すフラグ信号を比較器M2に出力する。また、比較器M11〜M14は、画素値が一致しないサブブロック[2]内の各画素のアドレスを、FIFO14に出力する。

【0045】

比較器M2は、同じサブブロック[1]に属する4つのサブブロック[2]間の画素値を比較する。比較器M2は、4つのサブブロック[2]内でアドレスが先頭の画素、つまり代表画素の画素値を用いて、サブブロック[2]間の画素値を比較する。比較は、比較器M11〜M14による比較の結果、4つのサブブロック[2]全てがサブブロック[2]内の画素値が一致する場合に限り、実施される。

比較器M2は、4つのサブブロック[2]間の画素値が一致する場合、サブブロック[1]で画素値が一致することを示すフラグ信号とともに、4つのサブブロック[2]が属するサブブロック[1]の代表画素の画素値をそのアドレスに対応付けて出力する。

比較器M2は、比較しなかった場合、又は4つのサブブロック[2]間の画素値が一致しない場合、比較器M11〜M14からの出力をそのまま比較器M3に転送する。

【0046】

比較器M3は、4つのサブブロック[1]間の画素値を比較する。比較器M3は、各サブブロック[1]内でアドレスが先頭の画素、つまり代表画素の画素値を用いて、サブブロック[1]間の画素値を比較する。比較は、4つのサブブロック[1]全てがサブブロック[1]内のサブブロック[2]間で画素値が一致する場合に限り、実施される。

比較器M3は、4つのサブブロック[1]間の画素値が一致する場合、1ブロック内の全画素間で画素値が一致することを示すフラグ信号を出力する。

比較器M3は、比較しなかった場合、又は4つのサブブロック[1]間の画素値が一致しない場合、比較器M2からの出力をそのまま出力バッファー13に転送する。

【0047】

上記比較器M11〜M14、M2、M3は、画素の画素値とともに、当該画素値が属する色空間を比較する。上述のように、色変換部12が入力される画像データの色空間毎にLUTを備えている場合、色空間が異なれば、色変換処理に用いられるLUTが切り替えられる。よって、比較器M11〜M14、M2、M3が、サブブロック内の各画素の画素値及びその色空間が一致する場合のみ、一致したことを示すフラグ信号を出力し、出力バッファー13が、画素値だけでなく色空間も一致する場合のみ、色変換処理後の画素値をコピーするようにすればよい。

【0048】

比較器M11〜M14、M2、M3は、画素の画素値とともに、当該画素の画像の属性を比較することが好ましい。上述のように、画像の属性によって色特性が異なり、色変換部12が画像の属性毎にLUTを備えている場合、画像の属性によって、用いられるLUTが切り替えられる。よって、比較器M11〜M14、M2、M3が、サブブロック内の各画素の画素値及び属性が一致する場合のみ、一致したことを示すフラグ信号を出力し、出力バッファー13が、画素値だけでなく画像の属性も一致する場合のみ、色変換処理後の画素値をコピーするようにすればよい。

【0049】

なお、比較器M11〜M14、M2、M3が、画素の画素値とともに、当該画素の属性及び当該画素値が属する色空間を比較してもよい。

【0050】

入力制御部S1は、入力バッファー11がブロック単位の画像データを入力するタイミングを制御する。入力制御部S1は、比較部Mbから1ブロック分の比較結果が出力されると、次の1ブロックの画像データの入力を指示する制御信号を、入力バッファー11に出力する。これにより、間をおかずに次のブロックの画像データの入力が可能となる。

【0051】

入力制御部S2は、入力バッファー11に対し、代表画素のアドレス0〜15を順次出力し、0〜15のアドレス順に色変換処理されるように調整する。FIFO14から入力されたアドレスがあれば、当該アドレスをアドレス0〜15に続けて出力する。これにより、図4に示すように、入力バッファー11から色変換部12へは、アドレス0〜15の順に代表画素の画素値が出力され、その後、サブブロック[2]内で画素値が一致しない画素の画素値が順次出力される。

【0052】

タイミング制御部S3は、比較部Mbの比較器M11〜M14、M2、M3にイネーブル信号を出力し、比較部Mbが画素値を比較するタイミングを制御する。1回の比較に1クロック要する場合、タイミング制御部S3は、各比較器M11〜M14に1クロック毎にイネーブル信号を4回出力する。タイミング制御部S3は、比較器M11〜M14に4回目のイネーブル信号を出力した後、比較器M2に1クロック毎にイネーブル信号を4回出力する。比較器M3に対しては、タイミング制御部S3は、比較器M2に4回目のイネーブル信号を出力した次のクロックでイネーブル信号を出力する。

【0053】

タイミング制御部S3は、出力制御部S4にイネーブル信号を出力し、FIFO14から出力されたアドレスを、出力制御部S4が出力バッファー13に出力するタイミングを制御する。比較部Mbから比較結果が出力されるタイミングに合わせて、FIFO14からのアドレスを出力する場合、タイミング制御部S3は、比較器M3にイネーブル信号を出力した次のクロックで、出力制御部S4にイネーブル信号を出力する。

【0054】

出力制御部S4は、タイミング制御部S3から出力されたイネーブル信号に応じて、出力バッファー13に、FIFO14から出力されたアドレスを転送する。

【0055】

図2に示された画像処理装置Gによる色変換処理の流れを説明する。

まず、入力バッファー11が1ブロックの画像データを入力する。入力バッファー11は1ブロックを4分割し、分割された各サブブロック[1]の左上に位置する画素を代表画素として、アドレス0〜3を割り当てる。入力バッファー11は、さらに各サブブロック[1]を4分割し、既にアドレスが割り当てられているサブブロック[2]を除き、分割された各サブブロック[2]の左上に位置する画素を代表画素として、アドレス4〜15を割り当てる。最後に、入力バッファー11は、サブブロック[2]内の代表画素以外の他の画素に、アドレス(0a、0b、0c)〜(15a、15b、15c)を割り当てる。これにより、図3に示すようにアドレスが割り当てられる。

【0056】

分割段階の順にサブブロック単位でアドレスを割り当てることにより、色変換処理される代表画素の順番が、最初の分割段階のサブブロック[1]から最後の分割段階のサブブロック[2]の順番となるように、調整することができる。これにより、比較部Mbの比較結果に合わせて色変換処理結果を得ることができ、色変換処理全体として処理時間を短縮することができる。

【0057】

図5に示すように、色変換部12が1クロック毎に1画素入力し、1画素の色変換処理に100クロックの処理時間を要する場合、1ブロックの全64画素を個々に色変換処理すると、163(163=100+64−1)クロックの処理時間を要する。

比較部Mbは、1画素の色変換処理の処理時間100クロックに比べて、はるかに短時間で比較を終えることができる。比較部Mbの比較の結果、1ブロック内の全画素の画素値が一致する場合、最初の1画素の色変換処理後の画素値を他の画素にコピーすればよいので、色変換処理は1画素の処理時間、つまり100クロックで終了する。この場合、処理時間はアドレスの割り当てに左右されない。

【0058】

アドレスの割り当てによって処理時間が変わるのは、サブブロック[1]内で画素値をコピーする場合である。

図3に示すように、分割段階の順に、サブブロック[1]単位からサブブロック[2]単位の順に、アドレスが割り当てられた場合、サブブロック[1]の代表画素のアドレスが、アドレスの先頭に位置するので、サブブロック[1]の代表画素から先に色変換処理される。そのため、サブブロック[1]の代表画素の色変換処理後の画素値を、当該サブブロック[1]内の他の画素にコピーする場合、図5に示すように、アドレス0〜3の代表画素の色変換処理結果が得られれば、各サブブロック[1]内で画素値をコピーでき、最大で100+4−1=103クロックの処理時間で終了する。

【0059】

これに対し、図6に示すように、分割段階の順番に関係無く、サブブロック[2]単位でアドレス0〜15が割り当てられた場合、色変換処理に無駄が生じることがある。例えば、アドレス0のサブブロック[1]内で画素値が一致している場合、アドレス0の代表画素の画素値を他の画素にコピーすればいいので、代表画素1、4、5の色変換処理は無駄となる。全てのサブブロック[1]内で画素値が一致している場合、アドレス0、2、8、10の代表画素が色変換処理されるまで、各サブブロック[1]内の他の画素に、代表画素の色変換処理結果をコピーすることができない。図7に示すように、アドレス10の代表画素の色変換処理結果が得られるまで、最大で100+11−1=110クロックの処理時間を要する。

【0060】

結果として、図3に示すアドレスの割り当ての場合、図6に示すアドレスの割り当ての場合と比較して、7クロック分の短縮が可能である。7クロックという処理時間の短縮は、短縮の程度が小さいように見えるが、例えば600dpiでA4サイズの画像データは、4961×2480画素であるのに対し、1ブロックは8×8画素であるので、画像データの全領域に対するブロック数は非常に多い。よって、1ブロックで7クロックの短縮ができれば、全領域の処理時間を大きく短縮することができる。

また、1ブロックのサイズが大きければ大きいほど、サブブロック[1]の数が増えるので、処理時間の短縮の効果がより大きく働く。

【0061】

サブブロック[2]内で代表画素の色変換処理後の画素値をコピーする場合も同様に、アドレス0〜15の代表画素が色変換処理されるまでコピーができない。最大で、アドレス15の画素の色変換処理結果が得られるまで、100+16−1=115(クロック)の処理時間を要する。しかし、サブブロック[1]と異なり、サブブロック[2]の場合、アドレスの割り当てによる処理時間の短縮の効果は無い。アドレスの割り当てによる処理時間の短縮の効果があるのは、最後の分割段階で分割されたサブブロック単位より前の分割段階で分割されたサブブロック単位の比較に対してである。

【0062】

なお、4分割を2段階で行う例で説明したが、例えば16画素×16画素を1ブロックとして入力し、4分割を3段階で行う場合、最初の1段階目の分割によって4つのサブブロック[1]、2段階目の分割によって16のサブブロック[2]、最後の3段階目の分割によって64のサブブロック[3]が得られる。この場合は、最初の分割段階のサブブロック単位であるサブブロック[1]から先にアドレスを割り当て、続いて、次の分割段階のサブブロック[2]、最後の分割段階のサブブロック単位であるサブブロック[3]の順にアドレスを割り当てればよい。これにより、サブブロック[1]、[2]内で色変換処理後の画素値をコピーするとき、上述のように処理時間の短縮の効果が得られる。

【0063】

アドレスが割り当てられると、入力制御部S2から代表画素のアドレス0〜15が順次入力されるので、入力バッファー11は、当該アドレスの代表画素の画素値を、アドレスに対応付けて色変換部12に順次出力する。色変換部12は、アドレス0〜15の順に出力された代表画素の画素値を色変換処理する。

また、入力バッファー11は、代表画素のアドレスが0のサブブロック[1]に属する4つのサブブロック[2]内の各画素の画素値を、比較器M11〜M14に出力する。これにより、アドレス0、0a、0b、0cの画素が比較器M11に、アドレス4、4a、4b、4cの画素が比較器M12に、アドレス5、5a、5b、5cの画素が比較器M13に、アドレス6、6a、6b、6cの画素が比較器M14に、それぞれ出力される。

【0064】

比較器M11〜M14は、サブブロック[2]内の画素間で画素値が一致する場合、一致したことを示すフラグ信号と、当該サブブロック[2]の代表画素の画素値を、そのアドレスに対応付けて比較器M3に出力する。

【0065】

比較器M11〜M14は、サブブロック[2]内の画素間で画素値が一致しない場合、一致しなかったことを示すフラグ信号を比較器M2に出力する。また、比較器M11〜M14は、画素値が一致しなかったサブブロック[2]内の各画素のアドレスを、FIFO14に出力する。

【0066】

FIFO14に出力されたアドレスは、入力制御部S2を介して入力バッファー11に出力される。入力バッファー11は、アドレス0〜15の代表画素に続けて、画素値が一致しなかったサブブロック[2]内の各画素の画素値を、そのアドレスに対応付けて色変換部12に出力する。

また、FIFO14に出力されたアドレスは、出力制御部S4を介して出力バッファー13に出力される。

【0067】

比較器M2は、比較器M11〜M14の全てから、サブブロック[2]内の画素間で画素値が一致したことを示すフラグ信号が入力された場合、フラグ信号とともに入力された各サブブロック[2]の代表画素の画素値を比較し、代表画素のアドレスが0のサブブロック[1]に属する4つのサブブロック[2]間で画素値を比較する。つまり、アドレス0、4、5、6の代表画素間で、それぞれ画素値が比較される。

【0068】

比較器M2は、4つのサブブロック[2]の代表画素間で画素値が一致した場合、代表画素のアドレスが0のサブブロック[1]内で画素値が一致することを示すフラグ信号と、当該サブブロック[1]の代表画素の画素値をそのアドレス0に対応付けて出力する。

比較器M2は、4つのサブブロック[2]の代表画素間で画素値が一致しなかった場合、代表画素のアドレスが0のサブブロック[1]内で画素値が一致しないことを示すフラグ信号とともに、比較器M11〜M14から入力されたフラグ信号、代表画素の画素値等をそのまま比較器M3に転送する。

【0069】

一方、比較器M11〜M14の何れかから、サブブロック[2]内の画素間で画素値が一致しないことを示すフラグ信号が入力された場合、比較器M2は比較を行わず、代表画素のアドレスが0のサブブロック[1]内で画素値が一致しないことを示すフラグ信号とともに、比較器M11〜M14から入力されたフラグ信号、代表画素の画素値等をそのまま比較器M3に転送する。

【0070】

比較器M11〜M14、M2は、上記代表画素のアドレス0のサブブロック[1]と同様にして、代表画素のアドレス1、2、3のサブブロック[1]についても、順次比較する。

【0071】

比較器M3は、比較器M2から、4つ全てのサブブロック[1]について、サブブロック[1]内の画素値が一致することを示すフラグ信号が入力された場合、当該フラグ信号とともに入力された各サブブロック[1]の代表画素の画素値を用いて、サブブロック[1]間の画素値を比較する。つまり、アドレス0、1、2、3の代表画素の画素値が比較される。

【0072】

比較器M3は、全てのサブブロック[1]の代表画素の画素値が一致した場合、1ブロック内の全画素間で画素値が一致することを示すフラグ信号を出力バッファー13に出力する。

出力バッファー13は、当該フラグ信号に応じて、最初に色変換部12から出力されたアドレス0の代表画素の色変換処理後の画素値を、1ブロック内の他の画素にコピーし、記憶する。

【0073】

比較器M3は、比較器M2から、4つのうち、何れかのサブブロック[1]内で画素値が一致しないことを示すフラグ信号が入力された場合、比較は行わず、比較器M2から出力されたフラグ信号等を出力バッファー13に転送する。

出力バッファー13は、当該フラグ信号に応じて、サブブロック[2]間で画素値が一致するサブブロック[1]については、その代表画素の色変換処理後の画素値を、当該サブブロック[1]内の代表画素以外の他の画素にコピーし、記憶する。

同様に、出力バッファー13は、サブブロック[2]内で画素値が一致するサブブロック[2]についても、その代表画素の色変換処理後の画素値を、当該サブブロック[2]内の代表画素以外の他の画素にコピーし、記憶する。

サブブロック[2]内でも画素値が一致しないサブブロック[2]については、当該サブブロック[2]内の各画素がそれぞれ色変換部12に出力され、色変換処理される。出力バッファー13には、出力制御部S4から当該サブブロック[2]内の各画素のアドレスが入力されるので、出力バッファー13は、当該アドレスの画素の色変換処理後の画素値を記憶する。

【0074】

図8は、色変換処理後の画素値のコピー例を示す。図8中、×の記号は画素値が一致しないことを表し、○の記号は画素値が一致することを表している。

図8に示すように、比較器M11〜M14による比較の結果、代表画素のアドレス0のサブブロック[2]以外のサブブロック[2]内の画素値が一致している。

比較器M2による比較の結果、代表画素のアドレス1、2、3のサブブロック[1]内のサブブロック[2]間で画素値が一致している。比較器M2は、アドレス0のサブブロック[1]に属するサブブロック[2]間では画素値の比較を行わず、比較器M11〜M14の比較結果をそのまま出力する。

比較器M3は、比較されなかったサブブロック[1]があるため、サブブロック[1]間で画素値の比較を行わず、比較器M2からの出力をそのまま出力バッファー13に出力する。

【0075】

以上の比較の結果、出力バッファー13では、アドレス0のサブブロック[2]については、アドレス0、0a、0b、0cの各画素の色変換処理後の画素値が記憶される。代表画素のアドレスが4、5、6のサブブロック[2]については、アドレス4、5、6の各代表画素の色変換処理後の画素値が、それぞれのサブブロック[2]内の他の画素にコピーされる。アドレス1、2、3のサブブロック[1]についても同様に、アドレス1、2、3の各代表画素の色変換処理後の画素値が、それぞれのサブブロック[1]内の他の画素にコピーされる。

【0076】

以上のように、本実施の形態によれば、画像処理装置Gは、画像データをブロック単位で入力し、入力された1ブロックを複数段階で分割し、分割段階の順に、分割されたサブブロック単位で、各画素にアドレスを割り当てる入力バッファー11と、入力バッファー11からアドレス順に画素単位で画素値を入力し、色変換処理する色変換部12と、色変換部12によって色変換処理された各画素の画素値を、各画素に割り当てられたアドレスに対応付けて記憶する出力バッファー13と、入力バッファー11から、1ブロックが複数段階で分割されたサブブロック[2]単位で各画素の画素値を入力し、最後の分割段階で分割されたサブブロック[2]内の画素間で画素値を比較するとともに、各サブブロック[1]、[2]内でアドレスが先頭の1画素の画素値を用いて、同じ分割段階で分割されたサブブロック[1]、[2]間で画素値を比較する比較部Mbと、を備える。出力バッファー13は、比較部Mbによる比較の結果、最後の分割段階で分割されたサブブロック[2]内の画素間で画素値が一致し、何れかの分割段階のサブブロック[1]、[2]間で画素値が一致する場合、当該サブブロック[1]、[2]間で最初に色変換処理された画素の色変換処理後の画素値を、各サブブロック[1]、[2]の画素にコピーして記憶する。

【0077】

これにより、色変換処理と並行して画素値を比較し、1画素の色変換処理結果を他の画素にコピーする処理をハードウェアによって実現することができる。コピーにより、複数の色変換部を並列に設けずとも色変換処理の高速化が可能であり、ハードウェアの規模の拡大を抑えて、ハードウェアによる色変換処理の高速化を図ることができる。

一般に、画像データ全体のサイズに対し、1ブロックのサイズは非常に小さく、1ブロック内の画素値が一致することが多いと考えられる。この場合、1ブロックの処理時間は実質1画素の処理時間となり、ソフトウェアによって画像データを1画素ずつ処理する場合に比べて、大幅な処理時間の短縮が見込める。

【0078】

また、同じ分割段階のサブブロック[1]、[2]間で画素値を比較するので、色変換処理結果をコピーする領域を段階的に拡大することができ、1ブロック内に異なる画素値が存在する場合にコピーの効率が良い。

さらに、アドレスを分割段階の順に割り当てることにより、比較の結果に合わせて色変換処理結果を効率良くコピーすることができ、色変換処理のさらなる高速化を図ることができる。

【0079】

また、本実施の形態によれば、最後の分割段階で分割されたサブブロック[2]内の画素間で画素値が一致しない場合、色変換部12は、最後の分割段階で分割されたサブブロック[2]内の各画素を色変換処理し、出力バッファー13は、色変換処理された各画素の画素値を、最後の分割段階で分割されたサブブロック[2]内の各画素の色変換処理後の画素値として記憶する。

画素値が一致しないサブブロックのみ、各画素が色変換処理されるので、色変換処理全体の処理速度を高速化することができる。

【0080】

上記実施の形態は本発明の好適な一例であり、これに限定されない。本発明の主旨を逸脱しない範囲で適宜変更可能である。

【符号の説明】

【0081】

T 画像形成装置

1 コントローラー

2 画像読取部

3 画像メモリー

4 画像形成部

G 画像処理装置

11 入力バッファー

12 色変換部

13 出力バッファー

14 メモリー

Mb 比較部

M11〜M14、M2、M3 比較器

S1、S2 入力制御部

S4 出力制御部

【特許請求の範囲】

【請求項1】

画像データをブロック単位で入力し、入力された1ブロックを複数段階で分割し、分割段階の順に、分割されたサブブロック単位で、各画素にアドレスを割り当てる入力バッファーと、

前記入力バッファーからアドレス順に画素単位で画素値を入力し、色変換処理する色変換部と、

前記色変換部によって色変換処理された各画素の画素値を、各画素に割り当てられた前記アドレスに対応付けて記憶する出力バッファーと、

前記入力バッファーから、1ブロックが複数段階で分割されたサブブロック単位で各画素の画素値を入力し、最後の分割段階で分割されたサブブロック内の画素間で画素値を比較するとともに、各サブブロック内でアドレスが先頭の1画素の画素値を用いて、同じ分割段階で分割されたサブブロック間で画素値を比較する比較部と、を備え、

前記出力バッファーは、前記比較部による比較の結果、最後の分割段階で分割されたサブブロック内の画素間で画素値が一致し、何れかの分割段階のサブブロック間で画素値が一致する場合、当該サブブロック間で最初に色変換処理された画素の色変換処理後の画素値を、各サブブロックの画素にコピーして記憶する画像処理装置。

【請求項2】

前記最後の分割段階で分割されたサブブロック内の画素間で画素値が一致しない場合、

前記色変換部は、前記最後の分割段階で分割されたサブブロック内の各画素を色変換処理し、

前記出力バッファーは、色変換処理された各画素の画素値を、前記最後の分割段階で分割されたサブブロック内の各画素の色変換処理後の画素値として記憶する請求項1に記載の画像処理装置。

【請求項3】

前記比較器は、画素の画素値とともに、当該画素値が属する色空間を比較し、

前記出力バッファーは、前記比較部による比較の結果、画素値と色空間が一致する場合のみ、前記画素値のコピーを行う請求項1又は2に記載の画像処理装置。

【請求項4】

前記比較部は、画素の画素値とともに、当該画素の画像の属性を比較し、

前記出力バッファーは、前記比較部による比較の結果、画素値と属性が一致する場合のみ、前記画素値のコピーを行う請求項1〜3の何れか一項に記載の画像処理装置。

【請求項1】

画像データをブロック単位で入力し、入力された1ブロックを複数段階で分割し、分割段階の順に、分割されたサブブロック単位で、各画素にアドレスを割り当てる入力バッファーと、

前記入力バッファーからアドレス順に画素単位で画素値を入力し、色変換処理する色変換部と、

前記色変換部によって色変換処理された各画素の画素値を、各画素に割り当てられた前記アドレスに対応付けて記憶する出力バッファーと、

前記入力バッファーから、1ブロックが複数段階で分割されたサブブロック単位で各画素の画素値を入力し、最後の分割段階で分割されたサブブロック内の画素間で画素値を比較するとともに、各サブブロック内でアドレスが先頭の1画素の画素値を用いて、同じ分割段階で分割されたサブブロック間で画素値を比較する比較部と、を備え、

前記出力バッファーは、前記比較部による比較の結果、最後の分割段階で分割されたサブブロック内の画素間で画素値が一致し、何れかの分割段階のサブブロック間で画素値が一致する場合、当該サブブロック間で最初に色変換処理された画素の色変換処理後の画素値を、各サブブロックの画素にコピーして記憶する画像処理装置。

【請求項2】

前記最後の分割段階で分割されたサブブロック内の画素間で画素値が一致しない場合、

前記色変換部は、前記最後の分割段階で分割されたサブブロック内の各画素を色変換処理し、

前記出力バッファーは、色変換処理された各画素の画素値を、前記最後の分割段階で分割されたサブブロック内の各画素の色変換処理後の画素値として記憶する請求項1に記載の画像処理装置。

【請求項3】

前記比較器は、画素の画素値とともに、当該画素値が属する色空間を比較し、

前記出力バッファーは、前記比較部による比較の結果、画素値と色空間が一致する場合のみ、前記画素値のコピーを行う請求項1又は2に記載の画像処理装置。

【請求項4】

前記比較部は、画素の画素値とともに、当該画素の画像の属性を比較し、

前記出力バッファーは、前記比較部による比較の結果、画素値と属性が一致する場合のみ、前記画素値のコピーを行う請求項1〜3の何れか一項に記載の画像処理装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−98811(P2013−98811A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−240790(P2011−240790)

【出願日】平成23年11月2日(2011.11.2)

【出願人】(303000372)コニカミノルタビジネステクノロジーズ株式会社 (12,802)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年11月2日(2011.11.2)

【出願人】(303000372)コニカミノルタビジネステクノロジーズ株式会社 (12,802)

【Fターム(参考)】

[ Back to top ]