画像形成装置およびメモリ格納プログラム

【課題】画像形成装置のメモリの寿命の短命化を抑制する。

【解決手段】画像データから2値データを生成するラスタライザ102と、再書込み回数が制限される記憶部109と、2値データをnビット毎に分割して、分割されたnビットの2値データが、2n種類に組み合わされたビットパタンのいずれに適合するかを特定し、特定したビットパタンの適合数を計数する計数部104と、適合数を計数したビットパタンのうち、互いに反転関係にある第1、第2のビットパタンの適合数を比較する比較部105と、比較の結果に基づいて、nビットの2値データを反転する反転部107と、反転したnビットの2値データと、その反転を示す反転フラグとを記憶部109に書き込む書込部108と、記憶部109から、nビットの2値データおよび反転フラグを読み出し、反転部107に、反転したnビットの2値データを復元させる読出部110と、を備える。

【解決手段】画像データから2値データを生成するラスタライザ102と、再書込み回数が制限される記憶部109と、2値データをnビット毎に分割して、分割されたnビットの2値データが、2n種類に組み合わされたビットパタンのいずれに適合するかを特定し、特定したビットパタンの適合数を計数する計数部104と、適合数を計数したビットパタンのうち、互いに反転関係にある第1、第2のビットパタンの適合数を比較する比較部105と、比較の結果に基づいて、nビットの2値データを反転する反転部107と、反転したnビットの2値データと、その反転を示す反転フラグとを記憶部109に書き込む書込部108と、記憶部109から、nビットの2値データおよび反転フラグを読み出し、反転部107に、反転したnビットの2値データを復元させる読出部110と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像形成装置における画像データの記憶の技術に関する。

【背景技術】

【0002】

近年の画像形成装置は、画像印刷の際に実行される認証印刷機能を有している。この「認証印刷機能」とは、画像印刷を行う者の正当性を確認してから画像印刷を実行する機能である。具体的には、PCは、まず、ユーザが予め個人認証用コードと画像データとを画像形成装置に送信しておく。次に、画像形成装置は、印刷出力する際に画像出力要求者に対して個人認証用コードを入力するように要求する。画像形成装置は、その者から入力されたコードと予め送信された個人認証用コードとを比較し、合致していると認証された場合に画像印刷を実行する。

【0003】

この認証印刷機能を有する画像形成装置は、認証印刷用の画像データを受信した際に予めその画像データをラスタライズしてメモリに格納するといった形態のものがある。この形態の画像形成装置は、認証完了時に画像印刷を直ちに実行できる。

【0004】

特許文献1には、受信した画像データをラスタライズしてメモリに格納しておき、所定の時間内に画像印刷を行わないと、メモリに格納した、ラスタライズされた画像データを消去する技術が開示されている。この技術により、メモリの効率利用が実現される。しかし、その結果として、メモリに対する、画像データなどのデータの書き込みおよび消去は、頻繁に発生する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2004−350024号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

現在、画像形成装置のデータ格納用メモリとして、大容量のNAND Flash ROM(Read Only Memory)(「NANDフラッシュメモリ」と称する場合がある)が用いられている。

しかしながら、前記したような、データの書き込みおよび消去を頻繁に行うことで、NAND Flash ROM 自体の寿命が短くなる、といった問題がある。

【0007】

そこで、このような事情を鑑みて、本発明は、画像データを記憶するメモリの寿命の短命化を抑制することを目的とする。

【課題を解決するための手段】

【0008】

前記目的を達成するため、本発明の画像形成装置は、

画像データから2値データを生成するラスタライザと、

再書込み回数が制限され、n(nは自然数)ビットのデータ毎に記憶するメモリと、

前記2値データをnビット毎に分割して、前記分割されたnビットの2値データが、2n種類に組み合わされたビットパタンのいずれに適合するかを特定し、前記分割されたnビットの2値データと、前記特定したビットパタンとが適合する適合数を計数する計数部と、

前記適合数を計数したビットパタンのうち、第1のビットパタンの適合数と、前記第1のビットパタンと反転関係にある第2のビットパタンの適合数とを比較する比較部と、

前記比較の結果に基づいて、nビットの2値データを反転する反転部と、

前記反転したnビットの2値データと、反転したことを示す反転フラグとを前記メモリに書き込む書込部と、

前記メモリから、前記nビットの2値データおよび前記反転フラグを読み出し、前記反転部に、反転したnビットの2値データを復元させる読出部と、

前記復元したnビットの2値データを用いて、画像を形成する画像形成部と、を備えることを特徴とする。

【0009】

つまり、反転関係にあるnビットの2値データの数を比較して、メモリに多くの電子数を必要とする2値データの数のほうが多い場合には、その2値データを反転させてメモリに記憶させ、メモリからその2値データを読み出すときには再度反転する。

詳細は、後記する。

【発明の効果】

【0010】

本発明によれば、画像データを記憶するメモリの寿命の短命化を抑制することができる。

【図面の簡単な説明】

【0011】

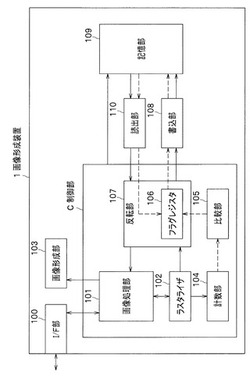

【図1】第1の実施形態の画像形成装置1の構成を示すブロック図である。

【図2】NANDフラッシュメモリがデータを記憶する様子を模式的に示す図である。

【図3】格納ビット数とビットパタンとの対応関係を示す図である。

【図4】計数部104、比較部105、反転部107が備える機能を説明するための具体例を示す図である。

【図5】ビットパタンの適合数を計数する処理を示すフローチャートである。

【図6】反転関係にあるビットパタン適合数の大小関係を比較する処理を示すフローチャートである。

【図7】記憶部109への書込処理を示すフローチャートである。

【図8】記憶部109からの読出処理を示すフローチャートである。

【図9】第2の実施形態の画像形成装置1の構成を示すブロック図である。

【図10】記憶部109への書込処理を示すフローチャートである。

【図11】記憶部109からの読出処理を示すフローチャートである。

【発明を実施するための形態】

【0012】

次に、本発明を実施するための形態(以下、「実施形態」という。)について、適宜図面を参照しながら説明する。

【0013】

≪第1の実施形態≫

〔構成〕

図1は、第1の実施形態の画像形成装置1の構成を示すブロック図である。この画像形成装置1は、I/F部100、制御部C、画像処理部101、ラスタライザ102、画像形成部103、計数部104、比較部105、フラグレジスタ106、反転部107、書込部108、記憶部109、および読出部110といった構成要素(部位)を備える。次に、これらの構成要素の機能概要を説明する。

【0014】

I/F部100は、外部ホストやスキャナなどの読み取り装置から画像データを受信する部位である。I/F部100は、例えば、LAN(Local Area Network)、USB(Universal Serial Bus)、LVDS(Low-Voltage Differential Signaling)などである。

【0015】

制御部Cは、画像形成装置1の画像処理を統括する部位である。制御部Cは、例えば、画像処理用のCPU(Central Processing Unit)、インストラクション格納用のROM(Read Only Memory)、画像処理用の記憶領域となるRAM(Random Access Memory)といった構成を備え、周辺の集積回路と通信可能なASIC(Application Specific Integrated Circuit)である。

【0016】

画像処理部101は、I/F部100から画像データを受信すると、画像データの伸張処理、コマンド解析、カラーマッチングなどの画像処理を実行し、そのような画像処理をした画像データをラスタライザ102に送信する。また、画像処理部101は、画像形成部103が画像形成を行う際、各色の画像形成用データに変換し、画像形成部103に所定のタイミングでその画像形成用データをバンド毎に送信する。

【0017】

ラスタライザ102は、画像形成を行うために、画像処理部101が画像処理した画像データの2値化処理を行い、2値データを生成する部位である。説明の便宜上、2値データを、単に「データ」と称する場合がある。よって、以降の説明において、特段の事情がない限り、単に「データ」と記載した場合には、2値データを意味する。

【0018】

画像形成部103は、画像処理部101から受信する各色の画像形成用データに基づいて、電子写真方式の露光、現像、転写、定着などといったプロセスを通して画像を形成する部位である。画像形成部103は、例えば、電子写真方式で印字を行う機構である。

【0019】

計数部104は、ラスタライザ102が生成した2値データ内に、所定のビットパタンの個数を計数する部位である。前記所定のビットパタンは、一度に扱うビット数に応じて複数種類存在する。例えば、“0”と“1”の2値があって、3ビットの場合、8(=23)種類存在する。計数部104は、ビットパタンの種類ごとにその個数を計数する。説明の便宜上、ビットパタンを、単に「パタン」と称する場合がある。また、各パタンの個数を「適合数」と称する場合がある。

【0020】

比較部105は、計数部104が計数した、あるパタンの適合数と、別のパタンの適合数とを比較する部位である。比較対象となるパタンを選ぶ方法については、後記する。

【0021】

フラグレジスタ106は、記憶部109へのデータの書き込みの際に、比較部105が比較した比較結果に基づいて定まる値を持つ反転フラグを一時的に格納する部位である。また、フラグレジスタ106は、記憶部109からのデータの読み出しの際に、データを復元するために、書き込み時に記憶部109に記憶した反転フラグの値を一時的に格納しておく部位でもある。この反転フラグは、データの反転の有無を示すが、詳細は、後記する。なお、データの復元とは、反転したデータを元に戻すことをいうが、詳細は、後記する。

【0022】

反転部107は、フラグレジスタ106が格納する反転フラグに基づいて、データの反転および復元を行う部位である。

【0023】

書込部108は、反転部107による処理を施したデータおよびフラグレジスタ106が格納する反転フラグを記憶部109に書き込む部位である。書込部108は、例えば、LSI(Large Scale Integration)である。

【0024】

記憶部109は、データおよび反転フラグの記憶を行う部位であり、再書込み回数が制限されているメモリである。本実施形態では、前記メモリは、NANDフラッシュメモリである。

【0025】

読出部110は、記憶部109が記憶するデータおよび反転フラグを読み出し、反転部107にデータおよび反転フラグを送信する部位である。読出部110は、例えば、LSI(Large Scale Integration)である。

【0026】

画像形成装置1の構成要素のうち、I/F部100、制御部C、画像処理部101、画像形成部103、書込部108、記憶部109および読出部110は、すでに述べたようなハードウェアとして実装する。一方、前記構成要素のうち、ラスタライザ102、計数部104、比較部105、フラグレジスタ106、および反転部107は、ハードウェアとプログラム(メモリ格納プログラムを含む)とが協働することで、実現される。

【0027】

なお、画像処理部101、ラスタライザ102、画像形成部103、計数部104、比較部105、フラグレジスタ106、反転部107は、制御部Cの一部として機能する。

また、フラグレジスタ106は、反転部107の一部として機能する。

【0028】

記憶部109としてのNANDフラッシュメモリについて詳細に説明する。

図2は、NANDフラッシュメモリがデータを記憶する様子を模式的に示す図である。NANDフラッシュメモリは、所定単位の情報を蓄積するのに必要な回路が集積した構成を備える。前記回路は、「セル」とよばれる。それぞれのセルは、例えば、シリコン基板上にp型半導体層が積層され、ソースおよびドレインとなる2つのn型半導体部分がp型半導体層を挟むように構成されている。そのp型半導体層の表面には、トンネル酸化膜(単に「酸化膜」と称する場合がある)を持ち、ポリシリコン製であるフローティングゲート(FG:Floating Gate)が積層されている。また、フローティングゲートの表面には、コントロールゲート(Control Gate)が積層されている。

【0029】

フローティングゲートは、絶縁体中に存在する電極として機能する。データの書き込みや読み出しのときには、このフローティングゲートに電子が注入され、データの消去のときには、このフローティングゲートから電子が抜き取られる。フローティングゲート内に注入された電子は、絶縁体により保持されるため、NANDフラッシュメモリは、電源電力を供給することなく、長期間に亘ってデータを記憶することができる不揮発性メモリとして機能する。

【0030】

コントロールゲートは、所定の電圧を閾値電圧Vthとしてかけることでセルに電流を流す電極として機能する。この閾値電圧Vthは、複数設定することができ、フローティングゲートに保持される電子の状態と、設定した閾値電圧Vthとを対応付けることができる。前記「電子の状態」とは、例えば、1つのセルに注入される電子の個数である。よって、セルにかける閾値電圧Vthを調整して、セルに注入される電子の個数を特定し、セルが記憶するデータの内容を定めることができる。

一般的には、セルにかける閾値電圧が高いほど、セルに注入される電子の個数は多くなる。NANDフラッシュメモリの設計者は、所望の値を持つデータをセルに注入するのに必要な大きさの閾値電圧を設定し、相当数の電子がそのセルに注入されるように設計する。

【0031】

NANDフラッシュメモリの設計上、1つのセルに注入される電子の個数を任意に設定することができる。よって、1つのセルに割り当てる情報量としてのビット数を設定することができ、データのビットパタンに応じた個数の電子をセルに注入することができる。本実施形態では、セルに設定するビット数を「格納ビット数」と称する。また、セルに電子を注入することで、セルが記憶することになる(また記憶することが事実上決定している)データを「セルデータ」と称する。また、意味が明らかであれば、セルデータに関する説明をする際、セルデータを単にデータと称する。格納ビット数をn(nは自然数)とした場合、セルデータの値によって示されるビットパタンについて以下のことがいえる。

【0032】

(1)n=1のとき、セルデータが“0”と、“1”となる2種類のビットパタンが存在する。このとき、セルに注入される電子の個数は、例えば、0個または7個となる。

(2)n=2のとき、セルデータが“00”と、“01”と、“10”と、“11”となる4種類のビットパタンが存在する。このとき、セルに注入される電子の個数は、例えば、0個、3個、5個または7個となる。

(3)n=3のとき、セルデータが“000”と、“001”と、“010”と、“011”と、“100”と、“101”と、“110”と、“111”となる8種類のビットパタンが存在する。このとき、セルに注入される電子の個数は、例えば、0個〜7個となる。

以降、格納ビット数nにつき、2n種類のビットパタンが存在する。

【0033】

本実施形態では、図2に示すとおり、セルデータの値が小さいほど、フローティングゲートに保持される電子の数が多くなる、という取り決めを定める。また、閾値電圧Vthが高くなるほど、フローティングゲートに保持される電子の数が多くなる、という取り決めを定める。

【0034】

よって、この取り決めによれば、

(1)n=1のとき、フローティングゲートに保持される電子の数が0であるとき、セルデータは“1”であり、閾値電圧Vthは相対的に低い。また、フローティングゲートに保持される電子の数が7であるとき、セルデータは“0”であり、閾値電圧Vthは相対的に高い。

(2)n=2のとき、フローティングゲートに保持される電子の数が0であるとき、セルデータは“11”であり、閾値電圧Vthは最低である。フローティングゲートに保持される電子の数が7であるとき、セルデータは“00”であり、閾値電圧Vthは最高である。

(3)n=3のとき、フローティングゲートに保持される電子の数が0であるとき、セルデータは“111”であり、閾値電圧Vthは最低である。フローティングゲートに保持される電子の数が7であるとき、セルデータは“000”であり、閾値電圧Vthは最高である。

【0035】

NANDフラッシュメモリは、フローティングゲートにおける電子の注入および抜取を行うたびに酸化膜の劣化が進む。このため、データの保持能力が徐々に低下し、NANDフラッシュメモリの寿命が短命化する。本実施形態では、この短命化を抑制するために、相対的に多くの電子をフローティングゲートに注入するセルデータを記憶部109に書き込む際、その注入する電子の数を少なくする手法をとる。

【0036】

以上の説明を踏まえ、計数部104、比較部105、フラグレジスタ106、反転部107、書込部108、読出部110について詳細に説明する。

【0037】

計数部104は、セルに設定した格納ビット数nの値に応じて、2値データ内の所定のビットパタンの適合数を計数する。計数部104による計数の対象となるビットパタンは、2n種類存在する。

図3は、格納ビット数とビットパタンとの対応関係を示す図である。図3に図示されている図形や線などは、図2に図示したものに倣っているため、適宜図2も参照する。

n=1の場合において、セルデータ“0”、“1”を構成するビットパタンを、それぞれ「P1パタン」「P2パタン」と称する。

n=2の場合において、セルデータ“00”、“01”、“10”、“11”、を構成するビットパタンを、それぞれ「P1パタン」、「P2パタン」、「P3パタン」、「P4パタン」と称する。

n=3の場合において、セルデータ“000”、“001”、“010”、“011”、“100”、“101”、“110”、“111”、を構成するビットパタンを、それぞれ「P1パタン」、「P2パタン」、「P3パタン」、「P4パタン」、「P5パタン」、「P6パタン」、「P7パタン」、「P8パタン」と称する。

格納ビット数nについては、P1パタン〜P2nパタンといった2n種類のビットパタンの組み合わせが存在する。計数部104は、P1パタン〜P2nパタンそれぞれの適合数を決定する。

【0038】

図4は、計数部104、比較部105、反転部107が備える機能を説明するための具体例を示す図である。

図4を参照して、計数部104がビットパタンの適合数を決定する具体例について説明する。

図4に示す「計数対象データ」は、ラスタライザ103が生成した2値データの一部であって、“0”と“1”との組み合わせからなる30ビットのデータである。また、図4において、格納ビット数nは、n=2とする。

なお、本実施形態では、ラスタライザ103が生成した2値データは、所定の大きさのバンド毎に分割して処理されることとする。したがって、図4において、30ビット以上ある2値データは、計数対象データとして、30ビット毎に分割される。

【0039】

まず、計数対象データを、先頭から2ビットごとに分割する。分割した計数対象データを「元データ」と称する。元データには、15個のセルデータが存在する。次に、15個のセルデータがP1パタン〜P4パタンのいずれに該当するか特定し、P1パタン〜P4パタンの適合数E(1)〜E(4)を計数する。図4によれば、P1パタンの適合数E(1)=5、P2パタンの適合数E(2)=3、P3パタンの適合数E(3)=3、P4パタンの適合数E(4)=4である。

【0040】

比較部105は、格納ビット数nに応じたセルデータの集合において、互いに反転関係にあるビットパタン(第1のビットパタン、第2のビットパタン)の適合数を比較する。ビットパタンの「反転関係」とは、片方のビットパタンに含まれる“0”を“1”に変え、“1”を“0”に変えたとき、もう片方のビットパタンに一致する関係であり、つまり、1の補数関係をいう。n=2の場合、セルデータが“00”となるP1パタンと、“11”となるP4パタンが反転関係にある。また、セルデータが“01”となるP2パタンと、“10”となるP3パタンとが反転関係にある。また、説明の便宜上、ビットパタンに反転関係がある場合、そのビットパタンを持つセルデータ(第1のデータ、第2のデータ)について、セルデータの反転関係が存在する、といった表現をする場合がある。

【0041】

比較部105による比較は、2n−1回(n=2の場合、2回)行われる。図4によれば、

比較部105は、P1パタンの適合数E(1)と、P4パタンの適合数E(4)とを比較し、E(1)>E(4)という大小関係を、関係式が「真」となる比較結果として出力する。また、比較部105は、P2パタンの適合数E(2)と、P3パタンの適合数E(3)とを比較し、E(2)=E(3)(E(2)>E(3)ではない)という大小関係を、関係式が「偽」となる比較結果として出力する。出力した比較結果は、フラグレジスタ106に送信される。

【0042】

前記した取り決めに従えば、一般的には、反転関係にあるビットパタンのうち、セルに注入される電子の数がより多いビットパタンの適合数E(L)(L=1、・・・、2n−1)が、セルに注入される電子の数がより少ないビットパタンの適合数E(2n−L+1)よりも多い場合、比較部105は、関係式が真となる比較結果を出力し、そうでない場合、関係式が偽となる比較結果を出力する。

【0043】

フラグレジスタ106は、比較部105が出力した比較結果を反転フラグとして一時的に格納する。フラグレジスタ106は、比較結果の関係式が真である場合、反転フラグを「1」にセットする。また、比較結果の関係式が偽である場合、反転フラグを「0」にセットする。反転フラグが「1」であることは、セルに注入される電子の数がより多いビットパタンを、反転関係にあり、セルに注入される電子の数がより少ないビットパタンに変更することを意味する。また、反転フラグが「0」であることは、前記変更をしないことを意味する。格納ビット数がnである場合、反転フラグは2n−1個存在する。したがって、反転フラグは、2n−1ビットの情報量を持つ情報として実現される。

【0044】

反転フラグは、前記取り決めに従い、セルに注入される電子の数が多いP1パタン〜P2n−1パタンにそれぞれ割り当てる。各P1パタン〜P2n−1パタンに割り当てた反転フラグをそれぞれ、F(1)〜F(2n−1)と称する。図4によれば、E(1)>E(4)であるため、P1パタンに割り当てた反転フラグF(1)は、F(1)=1となる。また、E(2)>E(3)ではないため、P2パタンに割り当てた反転フラグF(2)は、F(2)=0となる。また、説明の便宜上、反転フラグF(1)とF(2)とを合わせたものを、F(1:2)と表記する。F(1)=1、F(2)=0の場合、F(1:2)=(1、0)となる。F(1:2)は4ビットの情報量を持つ情報として実現される。また、説明の便宜上、反転フラグの符号を、単に「F」と表記する場合もある。

【0045】

なお、反転フラグは、図4に示す計数対象データ毎に添加される。つまり、ラスタライザ103が生成した2値データを分割して生成したバンドそれぞれに対して反転フラグが添加される。よって、図4によれば、反転フラグは、2ビットの情報量を持つ。反転フラグは、反転部107に送信される。

【0046】

反転部107は、反転フラグに基づいてセルデータを反転する。例えば、

(a)n=1のとき、F(1)=1であれば、セルデータ“0”を“1”に反転する。

(b)n=2のとき、F(1)=1であれば、セルデータ“00”を“11”に反転する。また、F(2)=1であれば、セルデータ“01”を“10”に反転する。

(c)n=3のとき、F(1)=1であれば、セルデータ“000”を“111”に反転する。また、F(2)=1であれば、セルデータ“001”を“110”に反転する。また、F(3)=1であれば、セルデータ“010”を“101”に反転する。また、F(4)=1であれば、セルデータ“011”を“100”に反転する。

【0047】

反転フラグの値が「0」となるセルデータについては反転しない。図4によれば、15個のビットパタンを持つ元データに対して、F(1:2)=(1、0)に従うと、“00”を“11”に反転するが、“01”を“10”に反転しない。その結果、図4に示す「反転データ」が生成される。この反転データは、書込部108に送信される。また、反転フラグも、書込部108に送信される。

【0048】

書込部108は、反転部107の処理を施したデータおよび反転フラグを記憶部109に書き込む。なお、図2に図示されているセルの模式図において、説明の便宜上、反転フラグの状態を示す電子の図示は省略しているが、フローティングゲートには、そのような電子も注入される。

【0049】

読出部110は、画像形成のためのデータの読み出し時に、記憶部109が記憶するデータおよび反転フラグを反転部107に送信する。反転部107は、反転フラグに基づいて読み出したデータを反転し、読み出したデータを復元する。図4によれば、反転部107は、反転データを元データに復元する。

【0050】

〔処理〕

次に、本実施形態の画像形成装置1の処理について説明する。この処理は、画像形成装置1の主要な構成要素による動作として実現される。

まず、画像形成装置1の電源が投入されると、制御部Cは画像形成装置1の各部位の初期化を行い、画像形成装置1が、認証印刷用の画像データの受信が可能な待機状態にされる。この初期化時に、制御部Cは記憶部109のID(Identifier)を読み込み、そのIDで識別される記憶部109を構成するセルの設計上設定された格納ビット数nを取得する。格納ビット数nは、制御部Cを構成するCPUの内部にあるレジスタに保持される。

【0051】

その後、前記待機状態にて画像形成装置1が認証印刷用の画像データを受信すると、画像データは、I/F部100経由で制御部C内のRAMに一時格納される。次に、画像処理部101は、RAMに一時格納した画像データに画像処理を施し、画像処理を施した画像データをラスタライザ102に送信する。ラスタライザ102は、受信した画像データを2値化し、計数部104と反転部107とに2値データを送信する。

【0052】

図5は、ビットパタンの適合数を計数する処理を示すフローチャートである。

まず、ステップS501において、計数部104は、制御部Cから記憶部109の格納ビット数nを取得するとともに、ラスタライザ102から計数対象となる2値データを取得する。この2値データの総情報量はkビットであるとし、2値データの総数kとして取り扱う。2値データは、所定の大きさのバンド毎に分割され、計数対象データとして扱う(図4参照)。計数部104は、計数対象データのアドレスAを、A=0(先頭のアドレス)にリセットするとともに、2n個分のビットパタン適合数E(1)〜E(2n)をすべて、E(1)〜E(2n)=0にリセットする。ステップS501の後、ステップS502に進む。

【0053】

ステップS502において、計数部104は、計数対象データにおいて、アドレスAから(A+n−1)までのnビット分のデータを抽出し、検査する。ステップS502の後、ステップS503に進む。

【0054】

ステップS503において、計数部104は、検査の対象となるデータが適合するビットパタンを特定する。つまり、データが持つ“0”と“1”との組み合わせの配列が、P1パタンからP2nパタンまでのいずれと一致するか判定する。ステップS503の後、ステップS504に進む。

【0055】

ステップS504において、計数部104は、特定したビットパタンの適合数をインクリメントする。これにより、該当するビットパタンの適合数をカウントする。ステップS504の後、ステップS505に進む。

【0056】

ステップS505において、計数部104は、アドレスAをnビット単位でインクリメントする。これにより、ステップS502による検査の対象が次のnビットのデータに移る。ステップS505の後、ステップS506に進む。

【0057】

ステップS506において、計数部104は、現在の検査対象となるデータのアドレスAが2値データの総数kに達したかまたは上回っているか判定する。達したかまたは上回っていれば(ステップS506でYes)、処理全体が終了する。そうでなければ(ステップS506でNo)、ステップS502に戻る。

図5に示す処理により、ラスタライザ102が生成した2値データにおけるすべてのビットパタン適合数を取得することができる。

【0058】

図6は、反転関係にあるビットパタン適合数の大小関係を比較する処理を示すフローチャートである。

まず、ステップS601において、比較部105は、制御部Cから記憶部109の格納ビット数nを取得するとともに、計数部104から、P1パタンからP2nパタンまでの2n個分のビットパタン適合数E(1)〜E(2n)を取得する。また、比較部105は、適合数の比較に用いる比較カウンタLを、L=0にリセットするとともに、フラグレジスタ106は、P1パタンからP2n−1パタンにそれぞれ割り当てた反転フラグF(1)〜F(2n−1)を、F(1)〜F(2n−1)=0にリセットする。なお、図4の表記に倣い、F(1)〜F(2n−1)までの集合をF(1:2n−1)と表記することができる。

説明の便宜上、nビットのセルデータの値が小さくなる程、閾値電圧Vthが高くなるように、P1パタンからP2nパタンまでが順番に並んでいるものとする。つまりP1パタンからP2nパタンは、NANDフラッシュメモリのフローティングゲートに注入される電子の総量が増え、酸化膜の破損を招くリスクが高まる順番に並んでいる。ステップS601の後、ステップS602に進む。

【0059】

ステップS602において、比較部105は、比較カウンタLをインクリメントする。ステップS602の後、ステップS603に進む。

【0060】

ステップS603において、比較部105は、反転関係にある2つのビットパタン、つまりPLパタンとP2n−L+1パタンの適合数の大小関係を比較する。具体的には、PLパタンの適合数E(L)がP2n−L+1パタンの適合数E(2n−L+1)よりも大きいか否か判定する。なお、いままでの説明から明らかであるが、PLパタンのセルデータに注入される電子の数は、P2n−L+1パタンのセルデータに注入される電子の数よりも多い。E(L)>E(2n−L+1)である場合(ステップS603でYes、関係式が真)、ステップS604に進む。そうでない場合(ステップS603でNo、関係式が偽)、ステップS605に進む。これにより、PLパタンのセルデータを反転しないことが決定する。

【0061】

ステップS604において、フラグレジスタ106は、ステップS603による比較結果に従い、PLパタンに割り当てた反転フラグF(L)を「1」にセットする。これにより、PLパタンのセルデータを反転することが決定する。ステップS604の後、ステップS605に進む。

【0062】

ステップS605において、比較部105は、比較カウンタLがインクリメントされた結果、2n−1に一致したか否か判定する。一致した場合(ステップS605でYes)、すべての反転フラグF(1)〜F(2n−1)の値が決定することを意味し、処理全体が終了する。一致しない場合(ステップS605でNo)、ステップS602に戻る。

【0063】

図6に示す処理により、P1パタンからP2n−1パタンのセルデータの反転の有無を決定することができる。反転部107は、比較部105から図6の処理により出力された比較結果を受信すると、書込部108に対し、記憶部109のデータおよび反転フラグの書き込みを指示する。

【0064】

図7は、記憶部109への書込処理を示すフローチャートである。

まず、ステップS701において、書込部108は、画像処理部101から記憶部109の格納ビット数nを取得するとともに、ラスタライザ102から計数対象となる2値データの総数kを取得する。また、書込部108は、計数対象データの書き込み用のアドレスWAを、WA=0(先頭のアドレス)にリセットする。ステップS701の後、ステップS702に進む。

【0065】

ステップS702において、書込部108は、計数対象データにおいて、アドレスWAから(WA+n−1)までのnビット分のデータを抽出し、検査する。ステップS702の後、ステップS703に進む。

【0066】

ステップS703において、書込部108は、検査の対象となるデータが適合するビットパタンを特定する。ここでは、書込部108は、例えば、計数部104によるビットパタンの特定の方法と同じ方法を用いる(図5のステップS503参照)。ステップS703の後、ステップS704に進む。

【0067】

ステップS704において、書込部108は、特定したビットパタンに対応する(割り当てられた)反転フラグF(L)(L=1〜2n−1)が、F(L)=1であるか否か判定する。F(L)=1である場合(ステップS704でYes)、ステップS705に進む。F(L)=1でない場合(ステップS704でNo)、F(L)=0であり、ステップS706に進む。なお、F(L)=0であるとき、PLパタンのデータは反転しない。

【0068】

ステップS705において、反転部107は、決定した反転フラグF(L)が1であれば、PLパタンのデータを反転し、Pn−L+1パタンのデータと同じにする。ステップS705の後、ステップS706に進む。

【0069】

ステップS706において、書込部108は、反転フラグF(L)によって反転するかしないか決定したデータを記憶部109に書き込む。ステップS706の後、ステップS707に進む。

【0070】

ステップS707において、書込部108は、アドレスWAをnビット単位でインクリメントする。これにより、ステップS702による検査の対象が次のnビットのデータに移る。ステップS707の後、ステップS708に進む。

【0071】

ステップS708において、書込部108は、現在の検査対象となるデータのアドレスWAが2値データの総数kに達したかまたは上回っているか判定する。達したかまたは上回っていれば(ステップS708でYes)、ステップS709に進む。そうでなければ(ステップS708でNo)、ステップS702に戻る。

【0072】

ステップS709において、書込部108は、反転部107からすべての反転フラグF(L)(L=1〜2n−1)を取得し、記憶部109に書き込む。ステップS706の後、処理全体が終了する。

図7に示す処理により、ラスタライザ102が生成し、必要に応じて反転した2値データおよびデータの反転を定める反転フラグを、記憶部109に記憶させることができる。

なお、書込部108により書き込まれたデータおよび反転フラグは、認証印刷用の画像データを送信したユーザが画像形成装置1にて認証確認を行うか、所定のデータ保持時間が経過するまで、記憶部109に記憶される。

【0073】

認証印刷用の画像データを送信したユーザは、画像形成装置1にて認証確認を行う。ユーザの正当性が確認されると、制御部Cは、2値データの復元をするため、読出部110に対し、記憶部109から該当のデータの読み出しを指示する。

【0074】

図8は、記憶部109からの読出処理を示すフローチャートである。

まず、ステップS801において、読出部110は、記憶部109からデータおよび反転フラグF(L)を読み出す。ここで、読み出すデータは、ステップS706(図7)による処理により反転されたデータである。また、読出部110は、記憶部109から読み出す反転フラグF(L)が、記憶部109から読み出すデータに対応していることは認識している。ステップS801の後、ステップS802に進む。

【0075】

ステップS802において、読出部110は、制御部Cから記憶部109の格納ビット数nを取得するとともに、ラスタライザ102から計数対象となる2値データの総数kを取得する。また、読出部110は、計数対象データの読み出し用のアドレスRAを、RA=0(先頭のアドレス)にリセットする。ステップS802の後、ステップS803に進む。

【0076】

ステップS803において、読出部110は、計数対象データにおいて、アドレスRAから(RA+n−1)までのnビット分のデータを抽出し、検査する。ステップS803の後、ステップS804に進む。

【0077】

ステップS804において、読出部110は、検査の対象となるデータが適合するビットパタンを特定する。ここでは、読出部110は、例えば、計数部104によるビットパタンの特定の方法と同じ方法を用いる(図5のステップS503参照)。ステップS804の後、ステップS805に進む。

【0078】

ステップS805において、読出部110は、特定したビットパタンに対応する(割り当てられた)反転フラグF(L)(L=1〜2n−1)が、F(L)=1であるか否か判定する。F(L)=1である場合(ステップS805でYes)、ステップS806に進む。F(L)=1でない場合(ステップS805でNo)、F(L)=0であり、ステップS807に進む。なお、F(L)=0であるとき、PLパタンのデータは復元しない。

【0079】

ステップS806において、反転部107は、決定した反転フラグF(L)が1であれば、PLパタンのデータを復元する。ステップS806の後、ステップS807に進む。

【0080】

ステップS807において、反転部107は、復元したデータを画像処理部101に送信する。なお、反転部107は、例えば、読出部110に対し、画像処理部101にデータを送信した旨を通知する。ステップS807の後、ステップS808に進む。

【0081】

ステップS808において、読出部110は、アドレスRAをnビット単位でインクリメントする。これにより、ステップS808による検査の対象が次のnビットのデータに移る。ステップS808の後、ステップS809に進む。

【0082】

ステップS809において、読出部110は、現在の検査対象となるデータのアドレスRAが2値データの総数kに達したかまたは上回っているか判定する。達したかまたは上回っていれば(ステップS809でYes)、処理全体が終了する。そうでなければ(ステップS809でNo)、ステップS803に戻る。

【0083】

図8に示す処理により、記憶部109に記憶したデータを復元して、制御部Cに送信することができる。

なお、画像処理部101は、反転部107が復元したデータを画像データに変換し、変換した画像データを画像形成部103に転送する。画像処理部101は、画像データに変換するとき、ラスタライザ102の機能を用いる。また、画像形成部103は、転送された画像データに基づいて画像形成を行う。

【0084】

第1の実施形態によれば、記憶部109としてのNANDフラッシュメモリに注入および抜取される電子の総数を低減化することができる。注入する電子の数が相対的に多いデータを記憶部109に書き込むことになる場合は、反転フラグを用いてそのデータを反転することで、注入する電子の数が相対的に少ないデータに変えるからである。つまり、互いに反転関係にある2つのビットパタンの適合数を比較し、データを反転するための条件を満たせば、注入する電子の数が相対的に多いビットパタンを、注入する電子の数が相対的に少ないビットパタンに変えるからである。反転フラグを用いているので、記憶部109に記憶されているデータの復元するべき箇所は把握することができる。これにより、NANDフラッシュメモリの注入および抜取に起因する酸化膜の破損を遅らせ、画像形成装置のメモリの寿命の短命化を抑制することができる。

【0085】

≪第2の実施形態≫

第2の実施形態の画像形成装置について説明する。第2の実施形態は、格納ビット数がnとなるNANDフラッシュメモリを、格納ビット数1となるNANDフラッシュメモリとして取り扱う形態である。第2の実施形態の説明の際、第1の実施形態の構成要素と同一の構成要素には同一の符号を付す。また、第1の実施形態の説明と重複する場合、その説明は、基本的には、省略する。

【0086】

〔構成〕

図9は、第2の実施形態の画像形成装置1の構成を示すブロック図である。この画像形成装置1は、第1の実施形態の画像形成装置1の構成要素のほかに、重要度レジスタ901およびマップ変更通知部902を備える。

【0087】

重要度レジスタ901は、画像処理部101がラスタライザ102に送信する画像データが重要データであるか否かを定める値を重要度として格納する部位である。注目するデータをxとし、重要度をI(x)とすると、I(x)=1のとき、データxを重要データとし、 I(x)=0のとき、データxを通常データとする。このように、I(x)は、1ビットの情報量を持つ。重要度I(x)は、制御部Cが画像データとともに管理する管理データに含まれる。なお、管理データは、認証印刷用画像データを画像形成装置1に送信し認証印刷を行うユーザの認証コードデータも含む。重要データは、例えば、認証印刷用画像データに付加されており、ユーザは予め重要度I(x)の値を指定する。

なお、説明の便宜上、あるデータの重要度は、「I」と表現する。重要データであればI=1であり、通常データであれば、I=0である。また、重要データは、通常データよりも重要であるデータということであるが、データが重要であるという意味は、所定の条件(例:NANDフラッシュメモリが劣化したとしても極力破損することを避けたいデータであること)を満たすこととするが、画像形成装置1を設計する者や利用する者などの考え方、都合などを踏まえて多様に解釈することができる。本明細書では、第2の実施形態によって処理することが決定したデータは、重要であるとみなす。

【0088】

重要度Iは、画像データがラスタライズされる際、計数部104および反転部107に送信される。反転部107に具備されるフラグレジスタ106は、重要度Iの値を格納する。このとき、例えば、フラグレジスタ106が格納する反転フラグFに重要度Iの値を付加してもよい。なお、本実施形態においては、データの反転は不要であるため、反転フラグFそのものは、基本的には、何ら役割を果たさない。

【0089】

マップ変更通知部902は、記憶部109に書き込んだり、記憶部109から読み出したりするデータが重要データであるか否かを書込部108および読出部110に通知(送信)する部位である。マップ変更通知部902は、フラグレジスタ106に格納された重要度Iの値を参照してデータの重要度を知る。

【0090】

重要度レジスタ901およびマップ変更通知部902は、ハードウェアとプログラムとの協働によって実現される。重要度レジスタ901は、制御部Cの一部として機能する。

【0091】

書込部108は、重要データとなるデータを、セルの格納ビット数がnであるNANDフラッシュメモリを持つ記憶部109に書き込む場合、そのセルの格納ビット数が1になるように、データのアドレスを修正する。すなわち、書込部108は、データを構成するビットそれぞれのアドレスを、1ビットごとにnビット分インクリメントし、記憶部109に書き込む。これにより、1ビット分のデータをnビット分のデータとして扱うことができる。この書き込みの処理の詳細については、後記する。

【0092】

このことを異なる観点から説明するために、図2および図3を参照する。書込部108は、反転部107から受信した1ビット分のデータの値が“1”である場合、そのデータをP2nパタンのセルデータとして扱い、記憶部109に記憶する。図2および図3によれば、P2nパタンとは、セルのフローティングに注入される電子がない状態を示すビットパタンであるといえる。

また、書込部108は、反転部107から受信した1ビット分のデータの値が“0”である場合、そのデータをP2n−1パタンのセルデータとして扱い、記憶部109に記憶する。図2および図3によれば、P2n−1パタンとは、セルのフローティングに電子が注入される場合には、その電子の数がもっとも少ない状態を示すビットパタンであるといえる。

【0093】

一方、読出部110は、(本来は1ビットであるが)nビット分のデータとして記憶部109に格納した重要データを、記憶部109から読み出す場合、その重要データのアドレスを修正して、1ビット分のデータに戻す。この読み出しの処理の詳細については、後記する。

【0094】

このことを異なる観点から説明するために、図2および図3を参照する。読出部110は、記憶部109から読み出したデータがP2nパタンのセルデータであった場合、“1”の値を持つ1ビット分のデータとして反転部107に送信する。

また、読出部110は、記憶部109から読み出したデータがP2n−1パタンのセルデータであった場合、“0”の値を持つ1ビット分のデータとして反転部107に送信する。

【0095】

〔処理〕

次に、本実施形態の画像形成装置1の処理について説明する。この処理は、画像形成装置1の主要な構成要素による動作として実現される。

【0096】

図10は、記憶部109への書込処理を示すフローチャートである。

まず、ステップS1001において、書込部108は、マップ変更通知部902による通知に従い、反転部107から受信したデータに対応する重要度Iが1であるか否か判定する。制御部Cは、管理データに含まれる、認証印刷用の画像データの重要度を反転部107に送信し、反転部107は、前記画像データをラスタライズした2値データに前記重要度を対応付けて書込部108に送信する。

重要度Iが1である場合(ステップS1001でYes)、反転部107から受信したデータが重要データであることを意味し、ステップS1002に進む。一方、重要度Iが1でない場合(ステップS1001でNo)、I=0であって、反転部107から受信したデータが通常データであることを意味し、ステップS1010に進む。

なお、重要度Iは、第1の実施形態に倣い、所定のバンド毎に、データに割り当ててフラグレジスタ106に格納される。

【0097】

ステップS1002において、書込部108は、制御部Cから記憶部109の格納ビット数nを取得するとともに、ラスタライザ102から計数対象となる2値データの総数kを取得する。また、書込部108は、計数対象データの検査用のアドレスである検査アドレスCAを、CA=0(先頭のアドレス)にリセットするとともに、計数対象データの書き込み用のアドレスである書込アドレスWAを、WA=0(先頭のアドレス)にリセットする。ステップS1002の後、ステップS1003に進む。

【0098】

ステップS1003において、書込部108は、計数対象データにおいて、検査アドレスCAから(CA+1)までの1ビット分のデータを抽出し、検査する。ステップS1003の後、ステップS1004に進む。

【0099】

ステップS1004において、書込部108は、検査の対象となるデータの値が“0”であるか否か判定する。データの値が“0”である場合(ステップS1004でYes)、そのデータのビットパタンが、格納ビット数n=1におけるP1パタン(図3参照)と同等であることを意味し、ステップS1005に進む。データの値が“0”でない場合(ステップS1004でNo)、データの値は“1”であって、そのデータのビットパタンが、格納ビット数n=1におけるP2パタン(図3参照)と同等であることを意味し、ステップS1006に進む。

なお、検査の対象となるデータが適合するビットパタンの特定は、計数部104による処理(図5のステップS503参照)と同様である。また、これまでの説明から明らかであるが、前記したP1パタン、P2パタンの説明において、格納ビット数nが1であることを述べたが、本ステップで説明する格納ビット数nは、ステップS1002の格納ビット数nとは意味が異なる点に留意されたい。

【0100】

ステップS1005において、書込部108は、検査の対象となるデータを、P2n−1パタンとして記憶部109に書き込む。ステップS1005の後、ステップS1007に進む。

【0101】

ステップS1006において、書込部108は、検査の対象となるデータを、P2nパタンとして記憶部109に書き込む。ステップS1006の後、ステップS1007に進む。

【0102】

ステップS1007において、書込部108は、検査アドレスCAを1ビット単位でインクリメントするとともに、書込アドレスWAをnビット単位でインクリメントする。これにより、ステップS1003による検査の対象が次の1ビットのデータに移るとともに、検査した1ビット分のデータをnビットのデータとして記憶部109に書き込むことができる。ステップS1007の後、ステップS1008に進む。

【0103】

ステップS1008において、書込部108は、現在の検査対象となるデータの検査アドレスCAが2値データの総数kに達したかまたは上回っているか判定する。達したかまたは上回っていれば(ステップS1008でYes)、すべてのデータを記憶部109へ書き込んだことを意味し、ステップS1009に進む。そうでなければ(ステップS1008でNo)、ステップS1003に戻る。

【0104】

ステップS1009において、書込部108は、検査したデータに対応するすべての重要度Iを記憶部109に書き込む。なお、本ステップにおける重要度Iはすべて、I=1である。ステップS1009の後、処理全体が終了する。

【0105】

ステップS1010において、書込部108は、重要度Iが0である通常データに対して、図7のフローチャートの処理を含む第1の実施形態における処理を書込処理として実行する。

図10に示す処理により、格納ビット数nのNANDフラッシュメモリのセルを、格納ビット数1のセルとみなしてデータを書き込むことができる。

なお、書込部108により書き込まれたデータおよび重要度は、認証印刷用の画像データを送信したユーザが画像形成装置1にて認証確認を行うか、所定のデータ保持時間が経過するまで、記憶部109に記憶される。

【0106】

認証印刷用の画像データを送信したユーザは、画像形成装置1にて認証確認を行う。ユーザの正当性が確認されると、制御部Cは、読出部110に対し、記憶部109から該当のデータの読み出しを指示する。

【0107】

図11は、記憶部109からの読出処理を示すフローチャートである。

まず、ステップS1101において、読出部110は、記憶部109からデータおよび重要度を読み出す。読出部110は、記憶部109から読み出す重要度が、記憶部109から読み出すデータに対応していることは認識している。ステップS1101の後、ステップS1102に進む。

【0108】

ステップS1102において、読出部110は、マップ変更通知部902による通知に従い、記憶部109から読み出したデータに対応する重要度Iが1であるか否か判定する。重要度Iが1である場合(ステップS1102でYes)、記憶部109から読み出したデータが重要データであることを意味し、ステップS1103に進む。重要度Iが1でない場合(ステップS1102でNo)、I=0であって、記憶部109から読み出したデータが通常データであることを意味し、ステップS1110に進む。

【0109】

ステップS1103において、読出部110は、制御部Cから記憶部109の格納ビット数nを取得するとともに、ラスタライザ102から計数対象となる2値データの総数kを取得する。また、読出部110は、計数対象データの検査用のアドレスである検査アドレスCAを、CA=0(先頭のアドレス)にリセットするとともに、計数対象データの読み出し用の読出アドレスRAを、RA=0(先頭のアドレス)にリセットする。ステップS1103の後、ステップS1104に進む。

【0110】

ステップS1104において、読出部110は、計数対象データにおいて、検査アドレスCAからCA+n−1までのnビット分のデータを抽出し、検査する。ステップS1104の後、ステップS1105に進む。

【0111】

ステップS1105において、読出部110は、検査の対象となるデータが、P2n−1パタンのデータであるか否か判定する。P2n−1パタンのデータである場合(ステップS1105でYes)、記憶部109に記憶されていたセルデータの値が“0”であることを意味し、ステップS1106に進む。P2n−1パタンのデータでない場合(ステップS1105でNo)、P2nパタンのデータということであって、記憶部109に記憶されていたセルデータの値が“1”であることを意味し、ステップS1107に進む。

【0112】

ステップS1106において、読出部110は、値が“0”となるデータを記憶部109から読み出す。ステップS1106の後、ステップS1108に進む。

【0113】

ステップS1107において、読出部110は、値が“1”となるデータを記憶部109から読み出す。ステップS1107の後、ステップS1108に進む。

【0114】

ステップS1108において、読出部110は、検査アドレスCAをnビット単位でインクリメントするとともに、読出アドレスRAを1ビット単位でインクリメントする。これにより、ステップS1104による検査の対象が次のnビットのデータに移るとともに、検査したnビット分のデータを1ビットのデータとして記憶部109から読み出すことができる。ステップS1108の後、ステップS1109に進む。

【0115】

ステップS1109において、読出部110は、現在の検査対象となるデータの検査アドレスCAが2値データの総数kに達したかまたは上回っているか判定する。達したかまたは上回っていれば(ステップS1109でYes)、記憶部109からすべてのデータを読み出したことを意味し、処理全体が終了する。そうでなければ(ステップS1109でNo)、ステップS1104に戻る。

【0116】

ステップS1110において、読出部110は、重要度Iが0である通常データに対して、図8のフローチャートの処理を含む第1の実施形態における処理を読出処理として実行する。

図11に示す処理により、格納ビット数nのNANDフラッシュメモリのセルを、格納ビット数のセルとみなしてデータを書き込むことができる。

【0117】

第2の実施形態によれば、記憶部109としてのNANDフラッシュメモリに注入および抜取される電子の総数を極力低減化することができる。格納ビット数がnのセルに対して電子を、注入する場合には最小数だけ注入するという手法を用いたからである。重要度を用いているので、前記手法を用いるデータ、つまり重要データであるか否かを把握することができる。これにより、画像形成装置のメモリの寿命の短命化をさらに抑制することができる。

【0118】

さらに、第2の実施形態によれば、セルに注入する電子数を1通りで済ませることができるため、セル内の電子の有無でデータの内容を管理できる。その結果、メモリに記憶されるデータの信頼性を高めることができる。

NAND型フラッシュメモリがnビットのデータを記憶して管理するためには、格納ビット数nのセルには、(2n−1)個の閾値電圧を設定して相当数の電子数をセルに注入する必要がある(図2参照)。よって、NAND型フラッシュメモリは、閾値電圧の値を調整することでnビットのデータを管理しているといえる。

しかし、酸化膜の劣化が進むと、セルが電子を保持する能力は低下し、複数個保持している電子の一部がフローティングゲートからp型半導体やn型半導体の層に流出してしまう可能性が高くなる。その結果、セルに注入されている電子数と、そのセルにかけていた閾値電圧の値と、セルが記憶するデータとの関係が崩れてしまい、データの信頼性が損なわれてしまう可能性が高くなる。

このような状況に対し、第2の実施形態は、閾値電圧の値やセルが保持する電子の個数とは無関係に、セルが保持する電子の有無で、セルが記憶するデータを管理するものである。よって、酸化膜の劣化が進み、セルが保持する電子の一部がフローティングゲートから流出しても、セルが保持する電子は一応存在している。この場合には、セルが記憶するデータは、正しいデータを管理しているといえる。この意味において、データの信頼性は決して損なわれていない。

従って、第2の実施形態によれば、メモリに格納されたデータの信頼性を高めることができる。

【0119】

≪その他≫

なお、前記形態は、本発明を実施する好適なものであるが、その実施形式はこれに限定するものではない。したがって、本発明の要旨を逸脱しない範囲において、その実施形式を種々変形することが可能である。

【0120】

例えば、本明細書で説明した画像形成装置は、例えば、情報処理装置プリンタ(SFP)、MFP(Multi Functional Printer)、ファクシミリ、複写装置、およびこれらの複合機においても利用可能である。

【0121】

また、本発明は、電子写真方式、帯電方式、露光方式、現像方式などの各方式を採用した画像形成装置に適用することができる。

【0122】

また、本実施形態では、再書込み回数が制限されるメモリとしてNANDフラッシュメモリについて説明したが、この発明はこれに限定されるものではない。例えば、前記メモリとして、EEPROM(Electrically Erasable Programmable Read-Only Memory)を用いてもよい。

【0123】

また、本実施形態は、メモリに記憶されるセルデータの値が小さい程、フローティングゲートに注入される電子が多くなる、という対応順位関係を取り決めた形態であった。しかし、対応順位関係はこれに限定されない。

例えば、図3において、格納ビット数n=2のとき、フローティングゲートに保持される電子の数が0、3、5、7であるとき、セルデータはそれぞれ“11”、“10”、“01”、“00”であるという対応順位関係を取り決めていた。この対応順位関係を、電子の数が0、3、5、7であるとき、セルデータはそれぞれ“11”、“01”、“10”、“00”としてもよい。

また、図3において、格納ビット数n=3のとき、フローティングゲートに保持される電子の数が0、1、2、3、4、5、6、7であるとき、セルデータはそれぞれ“111”、“110”、“101”、“100”、“011”、“010”、“001”、“000”であるという対応順位関係を取り決めていた。この対応順位関係を、電子の数が0、1、2、3、4、5、6、7であるとき、セルデータはそれぞれ“111”、“110”、“101”、“011”、“100”、“010”、“001”、“000”としてもよい。

基本的には、フローティングゲートに保持される電子の数と、セルデータの値とが1対1に対応していればよい。

【0124】

また、第2の実施形態では、1つのセルにnビット分のデータを記憶できるメモリに対し、1ビット分のデータを記憶するように用いた。そして、2n種類のビットパタンをとり得るデータのうち、フローティングゲートに電子がない状態であるP2nパタンのデータの値を“1”に対応させた。また、前記データのうち、フローティングゲート中の電子が最も少ない状態であるP2n―1パタンのデータの値を“0”に対応させた。しかし、フローティングゲート内の電子の数と、データの値との対応関係は、この場合に限定されない。

例えば、第2の実施形態で説明した方法を、図2および図3を用いた説明にあてはめると、格納ビット数n=2のときには、フローティングゲートに保持される電子の数が0となるP4パタンのデータの値を“1”に設定していた。そして、フローティングゲートに保持される電子の数が3(n=2のときは、もっとも少ない)となるP3パタンのデータの値を“0”に設定していた。しかし、例えば、フローティングゲートに保持される電子の数が5(n=2のときは、もっとも少ないわけではない)となるP2パタンのデータの値を“0”に設定するように対応関係を定めてもよい。

また、格納ビット数n=3のときには、フローティングゲートに保持される電子の数が0となるP8パタンのデータの値を“1”に設定していた。そして、フローティングゲートに保持される電子の数が1(n=3のときは、もっとも少ない)となるP7パタンのデータの値を“0”に設定していた。しかし、例えば、フローティングゲートに保持される電子の数が6(n=2のときは、もっとも少ないわけではない)となるP2パタンのデータの値を“0”に設定するように対応関係を定めてもよい。

基本的には、1ビット分のデータの値の一方に対応するビットパタンと、他方に対応するビットパタンとを違えればよい。

【0125】

また、本実施形態で説明した種々の技術を適宜組み合わせた技術を実現することもできる。

また、本実施形態で説明したソフトウェア(プログラム)をハードウェアとして実現することもでき、ハードウェアをソフトウェアと協働させて実現することもできる。例えば、画像形成装置1の構成要素のうちソフトウェアとして実装したラスタライザ102、計数部104、比較部105、フラグレジスタ106、反転部107、重要度レジスタ901およびマップ変更通知部902は、ハードウェアとして実装することで、画像処理の高速化を実現することができる。フラグレジスタ106をハードウェアとして実装する場合は、ハードウェアとして実装した反転部107に内蔵することが好ましい。重要度レジスタ901をハードウェアとして実装する場合は、ハードウェアとして実装した画像処理部101に内蔵することが好ましい。

【0126】

その他、ハードウェア、ソフトウェア、各フローチャートなどの具体的な構成について、本発明の趣旨を逸脱しない範囲で適宜変更が可能である。

【符号の説明】

【0127】

1 画像形成装置

C 制御部

100 I/F部

101 画像処理部

102 ラスタライザ

103 画像形成部

104 計数部

105 比較部

106 フラグレジスタ

107 反転部

108 書込部

109 記憶部

110 読出部

901 重要度レジスタ

902 マップ変更通知部

【技術分野】

【0001】

本発明は、画像形成装置における画像データの記憶の技術に関する。

【背景技術】

【0002】

近年の画像形成装置は、画像印刷の際に実行される認証印刷機能を有している。この「認証印刷機能」とは、画像印刷を行う者の正当性を確認してから画像印刷を実行する機能である。具体的には、PCは、まず、ユーザが予め個人認証用コードと画像データとを画像形成装置に送信しておく。次に、画像形成装置は、印刷出力する際に画像出力要求者に対して個人認証用コードを入力するように要求する。画像形成装置は、その者から入力されたコードと予め送信された個人認証用コードとを比較し、合致していると認証された場合に画像印刷を実行する。

【0003】

この認証印刷機能を有する画像形成装置は、認証印刷用の画像データを受信した際に予めその画像データをラスタライズしてメモリに格納するといった形態のものがある。この形態の画像形成装置は、認証完了時に画像印刷を直ちに実行できる。

【0004】

特許文献1には、受信した画像データをラスタライズしてメモリに格納しておき、所定の時間内に画像印刷を行わないと、メモリに格納した、ラスタライズされた画像データを消去する技術が開示されている。この技術により、メモリの効率利用が実現される。しかし、その結果として、メモリに対する、画像データなどのデータの書き込みおよび消去は、頻繁に発生する。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2004−350024号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

現在、画像形成装置のデータ格納用メモリとして、大容量のNAND Flash ROM(Read Only Memory)(「NANDフラッシュメモリ」と称する場合がある)が用いられている。

しかしながら、前記したような、データの書き込みおよび消去を頻繁に行うことで、NAND Flash ROM 自体の寿命が短くなる、といった問題がある。

【0007】

そこで、このような事情を鑑みて、本発明は、画像データを記憶するメモリの寿命の短命化を抑制することを目的とする。

【課題を解決するための手段】

【0008】

前記目的を達成するため、本発明の画像形成装置は、

画像データから2値データを生成するラスタライザと、

再書込み回数が制限され、n(nは自然数)ビットのデータ毎に記憶するメモリと、

前記2値データをnビット毎に分割して、前記分割されたnビットの2値データが、2n種類に組み合わされたビットパタンのいずれに適合するかを特定し、前記分割されたnビットの2値データと、前記特定したビットパタンとが適合する適合数を計数する計数部と、

前記適合数を計数したビットパタンのうち、第1のビットパタンの適合数と、前記第1のビットパタンと反転関係にある第2のビットパタンの適合数とを比較する比較部と、

前記比較の結果に基づいて、nビットの2値データを反転する反転部と、

前記反転したnビットの2値データと、反転したことを示す反転フラグとを前記メモリに書き込む書込部と、

前記メモリから、前記nビットの2値データおよび前記反転フラグを読み出し、前記反転部に、反転したnビットの2値データを復元させる読出部と、

前記復元したnビットの2値データを用いて、画像を形成する画像形成部と、を備えることを特徴とする。

【0009】

つまり、反転関係にあるnビットの2値データの数を比較して、メモリに多くの電子数を必要とする2値データの数のほうが多い場合には、その2値データを反転させてメモリに記憶させ、メモリからその2値データを読み出すときには再度反転する。

詳細は、後記する。

【発明の効果】

【0010】

本発明によれば、画像データを記憶するメモリの寿命の短命化を抑制することができる。

【図面の簡単な説明】

【0011】

【図1】第1の実施形態の画像形成装置1の構成を示すブロック図である。

【図2】NANDフラッシュメモリがデータを記憶する様子を模式的に示す図である。

【図3】格納ビット数とビットパタンとの対応関係を示す図である。

【図4】計数部104、比較部105、反転部107が備える機能を説明するための具体例を示す図である。

【図5】ビットパタンの適合数を計数する処理を示すフローチャートである。

【図6】反転関係にあるビットパタン適合数の大小関係を比較する処理を示すフローチャートである。

【図7】記憶部109への書込処理を示すフローチャートである。

【図8】記憶部109からの読出処理を示すフローチャートである。

【図9】第2の実施形態の画像形成装置1の構成を示すブロック図である。

【図10】記憶部109への書込処理を示すフローチャートである。

【図11】記憶部109からの読出処理を示すフローチャートである。

【発明を実施するための形態】

【0012】

次に、本発明を実施するための形態(以下、「実施形態」という。)について、適宜図面を参照しながら説明する。

【0013】

≪第1の実施形態≫

〔構成〕

図1は、第1の実施形態の画像形成装置1の構成を示すブロック図である。この画像形成装置1は、I/F部100、制御部C、画像処理部101、ラスタライザ102、画像形成部103、計数部104、比較部105、フラグレジスタ106、反転部107、書込部108、記憶部109、および読出部110といった構成要素(部位)を備える。次に、これらの構成要素の機能概要を説明する。

【0014】

I/F部100は、外部ホストやスキャナなどの読み取り装置から画像データを受信する部位である。I/F部100は、例えば、LAN(Local Area Network)、USB(Universal Serial Bus)、LVDS(Low-Voltage Differential Signaling)などである。

【0015】

制御部Cは、画像形成装置1の画像処理を統括する部位である。制御部Cは、例えば、画像処理用のCPU(Central Processing Unit)、インストラクション格納用のROM(Read Only Memory)、画像処理用の記憶領域となるRAM(Random Access Memory)といった構成を備え、周辺の集積回路と通信可能なASIC(Application Specific Integrated Circuit)である。

【0016】

画像処理部101は、I/F部100から画像データを受信すると、画像データの伸張処理、コマンド解析、カラーマッチングなどの画像処理を実行し、そのような画像処理をした画像データをラスタライザ102に送信する。また、画像処理部101は、画像形成部103が画像形成を行う際、各色の画像形成用データに変換し、画像形成部103に所定のタイミングでその画像形成用データをバンド毎に送信する。

【0017】

ラスタライザ102は、画像形成を行うために、画像処理部101が画像処理した画像データの2値化処理を行い、2値データを生成する部位である。説明の便宜上、2値データを、単に「データ」と称する場合がある。よって、以降の説明において、特段の事情がない限り、単に「データ」と記載した場合には、2値データを意味する。

【0018】

画像形成部103は、画像処理部101から受信する各色の画像形成用データに基づいて、電子写真方式の露光、現像、転写、定着などといったプロセスを通して画像を形成する部位である。画像形成部103は、例えば、電子写真方式で印字を行う機構である。

【0019】

計数部104は、ラスタライザ102が生成した2値データ内に、所定のビットパタンの個数を計数する部位である。前記所定のビットパタンは、一度に扱うビット数に応じて複数種類存在する。例えば、“0”と“1”の2値があって、3ビットの場合、8(=23)種類存在する。計数部104は、ビットパタンの種類ごとにその個数を計数する。説明の便宜上、ビットパタンを、単に「パタン」と称する場合がある。また、各パタンの個数を「適合数」と称する場合がある。

【0020】

比較部105は、計数部104が計数した、あるパタンの適合数と、別のパタンの適合数とを比較する部位である。比較対象となるパタンを選ぶ方法については、後記する。

【0021】

フラグレジスタ106は、記憶部109へのデータの書き込みの際に、比較部105が比較した比較結果に基づいて定まる値を持つ反転フラグを一時的に格納する部位である。また、フラグレジスタ106は、記憶部109からのデータの読み出しの際に、データを復元するために、書き込み時に記憶部109に記憶した反転フラグの値を一時的に格納しておく部位でもある。この反転フラグは、データの反転の有無を示すが、詳細は、後記する。なお、データの復元とは、反転したデータを元に戻すことをいうが、詳細は、後記する。

【0022】

反転部107は、フラグレジスタ106が格納する反転フラグに基づいて、データの反転および復元を行う部位である。

【0023】

書込部108は、反転部107による処理を施したデータおよびフラグレジスタ106が格納する反転フラグを記憶部109に書き込む部位である。書込部108は、例えば、LSI(Large Scale Integration)である。

【0024】

記憶部109は、データおよび反転フラグの記憶を行う部位であり、再書込み回数が制限されているメモリである。本実施形態では、前記メモリは、NANDフラッシュメモリである。

【0025】

読出部110は、記憶部109が記憶するデータおよび反転フラグを読み出し、反転部107にデータおよび反転フラグを送信する部位である。読出部110は、例えば、LSI(Large Scale Integration)である。

【0026】

画像形成装置1の構成要素のうち、I/F部100、制御部C、画像処理部101、画像形成部103、書込部108、記憶部109および読出部110は、すでに述べたようなハードウェアとして実装する。一方、前記構成要素のうち、ラスタライザ102、計数部104、比較部105、フラグレジスタ106、および反転部107は、ハードウェアとプログラム(メモリ格納プログラムを含む)とが協働することで、実現される。

【0027】

なお、画像処理部101、ラスタライザ102、画像形成部103、計数部104、比較部105、フラグレジスタ106、反転部107は、制御部Cの一部として機能する。

また、フラグレジスタ106は、反転部107の一部として機能する。

【0028】

記憶部109としてのNANDフラッシュメモリについて詳細に説明する。

図2は、NANDフラッシュメモリがデータを記憶する様子を模式的に示す図である。NANDフラッシュメモリは、所定単位の情報を蓄積するのに必要な回路が集積した構成を備える。前記回路は、「セル」とよばれる。それぞれのセルは、例えば、シリコン基板上にp型半導体層が積層され、ソースおよびドレインとなる2つのn型半導体部分がp型半導体層を挟むように構成されている。そのp型半導体層の表面には、トンネル酸化膜(単に「酸化膜」と称する場合がある)を持ち、ポリシリコン製であるフローティングゲート(FG:Floating Gate)が積層されている。また、フローティングゲートの表面には、コントロールゲート(Control Gate)が積層されている。

【0029】

フローティングゲートは、絶縁体中に存在する電極として機能する。データの書き込みや読み出しのときには、このフローティングゲートに電子が注入され、データの消去のときには、このフローティングゲートから電子が抜き取られる。フローティングゲート内に注入された電子は、絶縁体により保持されるため、NANDフラッシュメモリは、電源電力を供給することなく、長期間に亘ってデータを記憶することができる不揮発性メモリとして機能する。

【0030】

コントロールゲートは、所定の電圧を閾値電圧Vthとしてかけることでセルに電流を流す電極として機能する。この閾値電圧Vthは、複数設定することができ、フローティングゲートに保持される電子の状態と、設定した閾値電圧Vthとを対応付けることができる。前記「電子の状態」とは、例えば、1つのセルに注入される電子の個数である。よって、セルにかける閾値電圧Vthを調整して、セルに注入される電子の個数を特定し、セルが記憶するデータの内容を定めることができる。

一般的には、セルにかける閾値電圧が高いほど、セルに注入される電子の個数は多くなる。NANDフラッシュメモリの設計者は、所望の値を持つデータをセルに注入するのに必要な大きさの閾値電圧を設定し、相当数の電子がそのセルに注入されるように設計する。

【0031】

NANDフラッシュメモリの設計上、1つのセルに注入される電子の個数を任意に設定することができる。よって、1つのセルに割り当てる情報量としてのビット数を設定することができ、データのビットパタンに応じた個数の電子をセルに注入することができる。本実施形態では、セルに設定するビット数を「格納ビット数」と称する。また、セルに電子を注入することで、セルが記憶することになる(また記憶することが事実上決定している)データを「セルデータ」と称する。また、意味が明らかであれば、セルデータに関する説明をする際、セルデータを単にデータと称する。格納ビット数をn(nは自然数)とした場合、セルデータの値によって示されるビットパタンについて以下のことがいえる。

【0032】

(1)n=1のとき、セルデータが“0”と、“1”となる2種類のビットパタンが存在する。このとき、セルに注入される電子の個数は、例えば、0個または7個となる。

(2)n=2のとき、セルデータが“00”と、“01”と、“10”と、“11”となる4種類のビットパタンが存在する。このとき、セルに注入される電子の個数は、例えば、0個、3個、5個または7個となる。

(3)n=3のとき、セルデータが“000”と、“001”と、“010”と、“011”と、“100”と、“101”と、“110”と、“111”となる8種類のビットパタンが存在する。このとき、セルに注入される電子の個数は、例えば、0個〜7個となる。

以降、格納ビット数nにつき、2n種類のビットパタンが存在する。

【0033】

本実施形態では、図2に示すとおり、セルデータの値が小さいほど、フローティングゲートに保持される電子の数が多くなる、という取り決めを定める。また、閾値電圧Vthが高くなるほど、フローティングゲートに保持される電子の数が多くなる、という取り決めを定める。

【0034】

よって、この取り決めによれば、

(1)n=1のとき、フローティングゲートに保持される電子の数が0であるとき、セルデータは“1”であり、閾値電圧Vthは相対的に低い。また、フローティングゲートに保持される電子の数が7であるとき、セルデータは“0”であり、閾値電圧Vthは相対的に高い。

(2)n=2のとき、フローティングゲートに保持される電子の数が0であるとき、セルデータは“11”であり、閾値電圧Vthは最低である。フローティングゲートに保持される電子の数が7であるとき、セルデータは“00”であり、閾値電圧Vthは最高である。

(3)n=3のとき、フローティングゲートに保持される電子の数が0であるとき、セルデータは“111”であり、閾値電圧Vthは最低である。フローティングゲートに保持される電子の数が7であるとき、セルデータは“000”であり、閾値電圧Vthは最高である。

【0035】

NANDフラッシュメモリは、フローティングゲートにおける電子の注入および抜取を行うたびに酸化膜の劣化が進む。このため、データの保持能力が徐々に低下し、NANDフラッシュメモリの寿命が短命化する。本実施形態では、この短命化を抑制するために、相対的に多くの電子をフローティングゲートに注入するセルデータを記憶部109に書き込む際、その注入する電子の数を少なくする手法をとる。

【0036】

以上の説明を踏まえ、計数部104、比較部105、フラグレジスタ106、反転部107、書込部108、読出部110について詳細に説明する。

【0037】

計数部104は、セルに設定した格納ビット数nの値に応じて、2値データ内の所定のビットパタンの適合数を計数する。計数部104による計数の対象となるビットパタンは、2n種類存在する。

図3は、格納ビット数とビットパタンとの対応関係を示す図である。図3に図示されている図形や線などは、図2に図示したものに倣っているため、適宜図2も参照する。

n=1の場合において、セルデータ“0”、“1”を構成するビットパタンを、それぞれ「P1パタン」「P2パタン」と称する。

n=2の場合において、セルデータ“00”、“01”、“10”、“11”、を構成するビットパタンを、それぞれ「P1パタン」、「P2パタン」、「P3パタン」、「P4パタン」と称する。

n=3の場合において、セルデータ“000”、“001”、“010”、“011”、“100”、“101”、“110”、“111”、を構成するビットパタンを、それぞれ「P1パタン」、「P2パタン」、「P3パタン」、「P4パタン」、「P5パタン」、「P6パタン」、「P7パタン」、「P8パタン」と称する。

格納ビット数nについては、P1パタン〜P2nパタンといった2n種類のビットパタンの組み合わせが存在する。計数部104は、P1パタン〜P2nパタンそれぞれの適合数を決定する。

【0038】

図4は、計数部104、比較部105、反転部107が備える機能を説明するための具体例を示す図である。

図4を参照して、計数部104がビットパタンの適合数を決定する具体例について説明する。

図4に示す「計数対象データ」は、ラスタライザ103が生成した2値データの一部であって、“0”と“1”との組み合わせからなる30ビットのデータである。また、図4において、格納ビット数nは、n=2とする。

なお、本実施形態では、ラスタライザ103が生成した2値データは、所定の大きさのバンド毎に分割して処理されることとする。したがって、図4において、30ビット以上ある2値データは、計数対象データとして、30ビット毎に分割される。

【0039】

まず、計数対象データを、先頭から2ビットごとに分割する。分割した計数対象データを「元データ」と称する。元データには、15個のセルデータが存在する。次に、15個のセルデータがP1パタン〜P4パタンのいずれに該当するか特定し、P1パタン〜P4パタンの適合数E(1)〜E(4)を計数する。図4によれば、P1パタンの適合数E(1)=5、P2パタンの適合数E(2)=3、P3パタンの適合数E(3)=3、P4パタンの適合数E(4)=4である。

【0040】

比較部105は、格納ビット数nに応じたセルデータの集合において、互いに反転関係にあるビットパタン(第1のビットパタン、第2のビットパタン)の適合数を比較する。ビットパタンの「反転関係」とは、片方のビットパタンに含まれる“0”を“1”に変え、“1”を“0”に変えたとき、もう片方のビットパタンに一致する関係であり、つまり、1の補数関係をいう。n=2の場合、セルデータが“00”となるP1パタンと、“11”となるP4パタンが反転関係にある。また、セルデータが“01”となるP2パタンと、“10”となるP3パタンとが反転関係にある。また、説明の便宜上、ビットパタンに反転関係がある場合、そのビットパタンを持つセルデータ(第1のデータ、第2のデータ)について、セルデータの反転関係が存在する、といった表現をする場合がある。

【0041】

比較部105による比較は、2n−1回(n=2の場合、2回)行われる。図4によれば、

比較部105は、P1パタンの適合数E(1)と、P4パタンの適合数E(4)とを比較し、E(1)>E(4)という大小関係を、関係式が「真」となる比較結果として出力する。また、比較部105は、P2パタンの適合数E(2)と、P3パタンの適合数E(3)とを比較し、E(2)=E(3)(E(2)>E(3)ではない)という大小関係を、関係式が「偽」となる比較結果として出力する。出力した比較結果は、フラグレジスタ106に送信される。

【0042】

前記した取り決めに従えば、一般的には、反転関係にあるビットパタンのうち、セルに注入される電子の数がより多いビットパタンの適合数E(L)(L=1、・・・、2n−1)が、セルに注入される電子の数がより少ないビットパタンの適合数E(2n−L+1)よりも多い場合、比較部105は、関係式が真となる比較結果を出力し、そうでない場合、関係式が偽となる比較結果を出力する。

【0043】

フラグレジスタ106は、比較部105が出力した比較結果を反転フラグとして一時的に格納する。フラグレジスタ106は、比較結果の関係式が真である場合、反転フラグを「1」にセットする。また、比較結果の関係式が偽である場合、反転フラグを「0」にセットする。反転フラグが「1」であることは、セルに注入される電子の数がより多いビットパタンを、反転関係にあり、セルに注入される電子の数がより少ないビットパタンに変更することを意味する。また、反転フラグが「0」であることは、前記変更をしないことを意味する。格納ビット数がnである場合、反転フラグは2n−1個存在する。したがって、反転フラグは、2n−1ビットの情報量を持つ情報として実現される。

【0044】

反転フラグは、前記取り決めに従い、セルに注入される電子の数が多いP1パタン〜P2n−1パタンにそれぞれ割り当てる。各P1パタン〜P2n−1パタンに割り当てた反転フラグをそれぞれ、F(1)〜F(2n−1)と称する。図4によれば、E(1)>E(4)であるため、P1パタンに割り当てた反転フラグF(1)は、F(1)=1となる。また、E(2)>E(3)ではないため、P2パタンに割り当てた反転フラグF(2)は、F(2)=0となる。また、説明の便宜上、反転フラグF(1)とF(2)とを合わせたものを、F(1:2)と表記する。F(1)=1、F(2)=0の場合、F(1:2)=(1、0)となる。F(1:2)は4ビットの情報量を持つ情報として実現される。また、説明の便宜上、反転フラグの符号を、単に「F」と表記する場合もある。

【0045】

なお、反転フラグは、図4に示す計数対象データ毎に添加される。つまり、ラスタライザ103が生成した2値データを分割して生成したバンドそれぞれに対して反転フラグが添加される。よって、図4によれば、反転フラグは、2ビットの情報量を持つ。反転フラグは、反転部107に送信される。

【0046】

反転部107は、反転フラグに基づいてセルデータを反転する。例えば、

(a)n=1のとき、F(1)=1であれば、セルデータ“0”を“1”に反転する。

(b)n=2のとき、F(1)=1であれば、セルデータ“00”を“11”に反転する。また、F(2)=1であれば、セルデータ“01”を“10”に反転する。

(c)n=3のとき、F(1)=1であれば、セルデータ“000”を“111”に反転する。また、F(2)=1であれば、セルデータ“001”を“110”に反転する。また、F(3)=1であれば、セルデータ“010”を“101”に反転する。また、F(4)=1であれば、セルデータ“011”を“100”に反転する。

【0047】

反転フラグの値が「0」となるセルデータについては反転しない。図4によれば、15個のビットパタンを持つ元データに対して、F(1:2)=(1、0)に従うと、“00”を“11”に反転するが、“01”を“10”に反転しない。その結果、図4に示す「反転データ」が生成される。この反転データは、書込部108に送信される。また、反転フラグも、書込部108に送信される。

【0048】

書込部108は、反転部107の処理を施したデータおよび反転フラグを記憶部109に書き込む。なお、図2に図示されているセルの模式図において、説明の便宜上、反転フラグの状態を示す電子の図示は省略しているが、フローティングゲートには、そのような電子も注入される。

【0049】

読出部110は、画像形成のためのデータの読み出し時に、記憶部109が記憶するデータおよび反転フラグを反転部107に送信する。反転部107は、反転フラグに基づいて読み出したデータを反転し、読み出したデータを復元する。図4によれば、反転部107は、反転データを元データに復元する。

【0050】

〔処理〕

次に、本実施形態の画像形成装置1の処理について説明する。この処理は、画像形成装置1の主要な構成要素による動作として実現される。

まず、画像形成装置1の電源が投入されると、制御部Cは画像形成装置1の各部位の初期化を行い、画像形成装置1が、認証印刷用の画像データの受信が可能な待機状態にされる。この初期化時に、制御部Cは記憶部109のID(Identifier)を読み込み、そのIDで識別される記憶部109を構成するセルの設計上設定された格納ビット数nを取得する。格納ビット数nは、制御部Cを構成するCPUの内部にあるレジスタに保持される。

【0051】

その後、前記待機状態にて画像形成装置1が認証印刷用の画像データを受信すると、画像データは、I/F部100経由で制御部C内のRAMに一時格納される。次に、画像処理部101は、RAMに一時格納した画像データに画像処理を施し、画像処理を施した画像データをラスタライザ102に送信する。ラスタライザ102は、受信した画像データを2値化し、計数部104と反転部107とに2値データを送信する。

【0052】

図5は、ビットパタンの適合数を計数する処理を示すフローチャートである。

まず、ステップS501において、計数部104は、制御部Cから記憶部109の格納ビット数nを取得するとともに、ラスタライザ102から計数対象となる2値データを取得する。この2値データの総情報量はkビットであるとし、2値データの総数kとして取り扱う。2値データは、所定の大きさのバンド毎に分割され、計数対象データとして扱う(図4参照)。計数部104は、計数対象データのアドレスAを、A=0(先頭のアドレス)にリセットするとともに、2n個分のビットパタン適合数E(1)〜E(2n)をすべて、E(1)〜E(2n)=0にリセットする。ステップS501の後、ステップS502に進む。

【0053】

ステップS502において、計数部104は、計数対象データにおいて、アドレスAから(A+n−1)までのnビット分のデータを抽出し、検査する。ステップS502の後、ステップS503に進む。

【0054】

ステップS503において、計数部104は、検査の対象となるデータが適合するビットパタンを特定する。つまり、データが持つ“0”と“1”との組み合わせの配列が、P1パタンからP2nパタンまでのいずれと一致するか判定する。ステップS503の後、ステップS504に進む。

【0055】

ステップS504において、計数部104は、特定したビットパタンの適合数をインクリメントする。これにより、該当するビットパタンの適合数をカウントする。ステップS504の後、ステップS505に進む。

【0056】

ステップS505において、計数部104は、アドレスAをnビット単位でインクリメントする。これにより、ステップS502による検査の対象が次のnビットのデータに移る。ステップS505の後、ステップS506に進む。

【0057】

ステップS506において、計数部104は、現在の検査対象となるデータのアドレスAが2値データの総数kに達したかまたは上回っているか判定する。達したかまたは上回っていれば(ステップS506でYes)、処理全体が終了する。そうでなければ(ステップS506でNo)、ステップS502に戻る。

図5に示す処理により、ラスタライザ102が生成した2値データにおけるすべてのビットパタン適合数を取得することができる。

【0058】

図6は、反転関係にあるビットパタン適合数の大小関係を比較する処理を示すフローチャートである。

まず、ステップS601において、比較部105は、制御部Cから記憶部109の格納ビット数nを取得するとともに、計数部104から、P1パタンからP2nパタンまでの2n個分のビットパタン適合数E(1)〜E(2n)を取得する。また、比較部105は、適合数の比較に用いる比較カウンタLを、L=0にリセットするとともに、フラグレジスタ106は、P1パタンからP2n−1パタンにそれぞれ割り当てた反転フラグF(1)〜F(2n−1)を、F(1)〜F(2n−1)=0にリセットする。なお、図4の表記に倣い、F(1)〜F(2n−1)までの集合をF(1:2n−1)と表記することができる。

説明の便宜上、nビットのセルデータの値が小さくなる程、閾値電圧Vthが高くなるように、P1パタンからP2nパタンまでが順番に並んでいるものとする。つまりP1パタンからP2nパタンは、NANDフラッシュメモリのフローティングゲートに注入される電子の総量が増え、酸化膜の破損を招くリスクが高まる順番に並んでいる。ステップS601の後、ステップS602に進む。

【0059】

ステップS602において、比較部105は、比較カウンタLをインクリメントする。ステップS602の後、ステップS603に進む。

【0060】

ステップS603において、比較部105は、反転関係にある2つのビットパタン、つまりPLパタンとP2n−L+1パタンの適合数の大小関係を比較する。具体的には、PLパタンの適合数E(L)がP2n−L+1パタンの適合数E(2n−L+1)よりも大きいか否か判定する。なお、いままでの説明から明らかであるが、PLパタンのセルデータに注入される電子の数は、P2n−L+1パタンのセルデータに注入される電子の数よりも多い。E(L)>E(2n−L+1)である場合(ステップS603でYes、関係式が真)、ステップS604に進む。そうでない場合(ステップS603でNo、関係式が偽)、ステップS605に進む。これにより、PLパタンのセルデータを反転しないことが決定する。

【0061】

ステップS604において、フラグレジスタ106は、ステップS603による比較結果に従い、PLパタンに割り当てた反転フラグF(L)を「1」にセットする。これにより、PLパタンのセルデータを反転することが決定する。ステップS604の後、ステップS605に進む。

【0062】

ステップS605において、比較部105は、比較カウンタLがインクリメントされた結果、2n−1に一致したか否か判定する。一致した場合(ステップS605でYes)、すべての反転フラグF(1)〜F(2n−1)の値が決定することを意味し、処理全体が終了する。一致しない場合(ステップS605でNo)、ステップS602に戻る。

【0063】

図6に示す処理により、P1パタンからP2n−1パタンのセルデータの反転の有無を決定することができる。反転部107は、比較部105から図6の処理により出力された比較結果を受信すると、書込部108に対し、記憶部109のデータおよび反転フラグの書き込みを指示する。

【0064】

図7は、記憶部109への書込処理を示すフローチャートである。

まず、ステップS701において、書込部108は、画像処理部101から記憶部109の格納ビット数nを取得するとともに、ラスタライザ102から計数対象となる2値データの総数kを取得する。また、書込部108は、計数対象データの書き込み用のアドレスWAを、WA=0(先頭のアドレス)にリセットする。ステップS701の後、ステップS702に進む。

【0065】

ステップS702において、書込部108は、計数対象データにおいて、アドレスWAから(WA+n−1)までのnビット分のデータを抽出し、検査する。ステップS702の後、ステップS703に進む。

【0066】

ステップS703において、書込部108は、検査の対象となるデータが適合するビットパタンを特定する。ここでは、書込部108は、例えば、計数部104によるビットパタンの特定の方法と同じ方法を用いる(図5のステップS503参照)。ステップS703の後、ステップS704に進む。

【0067】

ステップS704において、書込部108は、特定したビットパタンに対応する(割り当てられた)反転フラグF(L)(L=1〜2n−1)が、F(L)=1であるか否か判定する。F(L)=1である場合(ステップS704でYes)、ステップS705に進む。F(L)=1でない場合(ステップS704でNo)、F(L)=0であり、ステップS706に進む。なお、F(L)=0であるとき、PLパタンのデータは反転しない。

【0068】

ステップS705において、反転部107は、決定した反転フラグF(L)が1であれば、PLパタンのデータを反転し、Pn−L+1パタンのデータと同じにする。ステップS705の後、ステップS706に進む。

【0069】

ステップS706において、書込部108は、反転フラグF(L)によって反転するかしないか決定したデータを記憶部109に書き込む。ステップS706の後、ステップS707に進む。

【0070】

ステップS707において、書込部108は、アドレスWAをnビット単位でインクリメントする。これにより、ステップS702による検査の対象が次のnビットのデータに移る。ステップS707の後、ステップS708に進む。

【0071】

ステップS708において、書込部108は、現在の検査対象となるデータのアドレスWAが2値データの総数kに達したかまたは上回っているか判定する。達したかまたは上回っていれば(ステップS708でYes)、ステップS709に進む。そうでなければ(ステップS708でNo)、ステップS702に戻る。

【0072】

ステップS709において、書込部108は、反転部107からすべての反転フラグF(L)(L=1〜2n−1)を取得し、記憶部109に書き込む。ステップS706の後、処理全体が終了する。

図7に示す処理により、ラスタライザ102が生成し、必要に応じて反転した2値データおよびデータの反転を定める反転フラグを、記憶部109に記憶させることができる。

なお、書込部108により書き込まれたデータおよび反転フラグは、認証印刷用の画像データを送信したユーザが画像形成装置1にて認証確認を行うか、所定のデータ保持時間が経過するまで、記憶部109に記憶される。

【0073】

認証印刷用の画像データを送信したユーザは、画像形成装置1にて認証確認を行う。ユーザの正当性が確認されると、制御部Cは、2値データの復元をするため、読出部110に対し、記憶部109から該当のデータの読み出しを指示する。

【0074】

図8は、記憶部109からの読出処理を示すフローチャートである。

まず、ステップS801において、読出部110は、記憶部109からデータおよび反転フラグF(L)を読み出す。ここで、読み出すデータは、ステップS706(図7)による処理により反転されたデータである。また、読出部110は、記憶部109から読み出す反転フラグF(L)が、記憶部109から読み出すデータに対応していることは認識している。ステップS801の後、ステップS802に進む。

【0075】

ステップS802において、読出部110は、制御部Cから記憶部109の格納ビット数nを取得するとともに、ラスタライザ102から計数対象となる2値データの総数kを取得する。また、読出部110は、計数対象データの読み出し用のアドレスRAを、RA=0(先頭のアドレス)にリセットする。ステップS802の後、ステップS803に進む。

【0076】

ステップS803において、読出部110は、計数対象データにおいて、アドレスRAから(RA+n−1)までのnビット分のデータを抽出し、検査する。ステップS803の後、ステップS804に進む。

【0077】

ステップS804において、読出部110は、検査の対象となるデータが適合するビットパタンを特定する。ここでは、読出部110は、例えば、計数部104によるビットパタンの特定の方法と同じ方法を用いる(図5のステップS503参照)。ステップS804の後、ステップS805に進む。

【0078】

ステップS805において、読出部110は、特定したビットパタンに対応する(割り当てられた)反転フラグF(L)(L=1〜2n−1)が、F(L)=1であるか否か判定する。F(L)=1である場合(ステップS805でYes)、ステップS806に進む。F(L)=1でない場合(ステップS805でNo)、F(L)=0であり、ステップS807に進む。なお、F(L)=0であるとき、PLパタンのデータは復元しない。

【0079】

ステップS806において、反転部107は、決定した反転フラグF(L)が1であれば、PLパタンのデータを復元する。ステップS806の後、ステップS807に進む。

【0080】

ステップS807において、反転部107は、復元したデータを画像処理部101に送信する。なお、反転部107は、例えば、読出部110に対し、画像処理部101にデータを送信した旨を通知する。ステップS807の後、ステップS808に進む。

【0081】

ステップS808において、読出部110は、アドレスRAをnビット単位でインクリメントする。これにより、ステップS808による検査の対象が次のnビットのデータに移る。ステップS808の後、ステップS809に進む。

【0082】

ステップS809において、読出部110は、現在の検査対象となるデータのアドレスRAが2値データの総数kに達したかまたは上回っているか判定する。達したかまたは上回っていれば(ステップS809でYes)、処理全体が終了する。そうでなければ(ステップS809でNo)、ステップS803に戻る。

【0083】

図8に示す処理により、記憶部109に記憶したデータを復元して、制御部Cに送信することができる。

なお、画像処理部101は、反転部107が復元したデータを画像データに変換し、変換した画像データを画像形成部103に転送する。画像処理部101は、画像データに変換するとき、ラスタライザ102の機能を用いる。また、画像形成部103は、転送された画像データに基づいて画像形成を行う。

【0084】

第1の実施形態によれば、記憶部109としてのNANDフラッシュメモリに注入および抜取される電子の総数を低減化することができる。注入する電子の数が相対的に多いデータを記憶部109に書き込むことになる場合は、反転フラグを用いてそのデータを反転することで、注入する電子の数が相対的に少ないデータに変えるからである。つまり、互いに反転関係にある2つのビットパタンの適合数を比較し、データを反転するための条件を満たせば、注入する電子の数が相対的に多いビットパタンを、注入する電子の数が相対的に少ないビットパタンに変えるからである。反転フラグを用いているので、記憶部109に記憶されているデータの復元するべき箇所は把握することができる。これにより、NANDフラッシュメモリの注入および抜取に起因する酸化膜の破損を遅らせ、画像形成装置のメモリの寿命の短命化を抑制することができる。

【0085】

≪第2の実施形態≫

第2の実施形態の画像形成装置について説明する。第2の実施形態は、格納ビット数がnとなるNANDフラッシュメモリを、格納ビット数1となるNANDフラッシュメモリとして取り扱う形態である。第2の実施形態の説明の際、第1の実施形態の構成要素と同一の構成要素には同一の符号を付す。また、第1の実施形態の説明と重複する場合、その説明は、基本的には、省略する。

【0086】

〔構成〕

図9は、第2の実施形態の画像形成装置1の構成を示すブロック図である。この画像形成装置1は、第1の実施形態の画像形成装置1の構成要素のほかに、重要度レジスタ901およびマップ変更通知部902を備える。

【0087】

重要度レジスタ901は、画像処理部101がラスタライザ102に送信する画像データが重要データであるか否かを定める値を重要度として格納する部位である。注目するデータをxとし、重要度をI(x)とすると、I(x)=1のとき、データxを重要データとし、 I(x)=0のとき、データxを通常データとする。このように、I(x)は、1ビットの情報量を持つ。重要度I(x)は、制御部Cが画像データとともに管理する管理データに含まれる。なお、管理データは、認証印刷用画像データを画像形成装置1に送信し認証印刷を行うユーザの認証コードデータも含む。重要データは、例えば、認証印刷用画像データに付加されており、ユーザは予め重要度I(x)の値を指定する。

なお、説明の便宜上、あるデータの重要度は、「I」と表現する。重要データであればI=1であり、通常データであれば、I=0である。また、重要データは、通常データよりも重要であるデータということであるが、データが重要であるという意味は、所定の条件(例:NANDフラッシュメモリが劣化したとしても極力破損することを避けたいデータであること)を満たすこととするが、画像形成装置1を設計する者や利用する者などの考え方、都合などを踏まえて多様に解釈することができる。本明細書では、第2の実施形態によって処理することが決定したデータは、重要であるとみなす。

【0088】

重要度Iは、画像データがラスタライズされる際、計数部104および反転部107に送信される。反転部107に具備されるフラグレジスタ106は、重要度Iの値を格納する。このとき、例えば、フラグレジスタ106が格納する反転フラグFに重要度Iの値を付加してもよい。なお、本実施形態においては、データの反転は不要であるため、反転フラグFそのものは、基本的には、何ら役割を果たさない。

【0089】

マップ変更通知部902は、記憶部109に書き込んだり、記憶部109から読み出したりするデータが重要データであるか否かを書込部108および読出部110に通知(送信)する部位である。マップ変更通知部902は、フラグレジスタ106に格納された重要度Iの値を参照してデータの重要度を知る。

【0090】

重要度レジスタ901およびマップ変更通知部902は、ハードウェアとプログラムとの協働によって実現される。重要度レジスタ901は、制御部Cの一部として機能する。

【0091】

書込部108は、重要データとなるデータを、セルの格納ビット数がnであるNANDフラッシュメモリを持つ記憶部109に書き込む場合、そのセルの格納ビット数が1になるように、データのアドレスを修正する。すなわち、書込部108は、データを構成するビットそれぞれのアドレスを、1ビットごとにnビット分インクリメントし、記憶部109に書き込む。これにより、1ビット分のデータをnビット分のデータとして扱うことができる。この書き込みの処理の詳細については、後記する。

【0092】

このことを異なる観点から説明するために、図2および図3を参照する。書込部108は、反転部107から受信した1ビット分のデータの値が“1”である場合、そのデータをP2nパタンのセルデータとして扱い、記憶部109に記憶する。図2および図3によれば、P2nパタンとは、セルのフローティングに注入される電子がない状態を示すビットパタンであるといえる。

また、書込部108は、反転部107から受信した1ビット分のデータの値が“0”である場合、そのデータをP2n−1パタンのセルデータとして扱い、記憶部109に記憶する。図2および図3によれば、P2n−1パタンとは、セルのフローティングに電子が注入される場合には、その電子の数がもっとも少ない状態を示すビットパタンであるといえる。

【0093】

一方、読出部110は、(本来は1ビットであるが)nビット分のデータとして記憶部109に格納した重要データを、記憶部109から読み出す場合、その重要データのアドレスを修正して、1ビット分のデータに戻す。この読み出しの処理の詳細については、後記する。

【0094】

このことを異なる観点から説明するために、図2および図3を参照する。読出部110は、記憶部109から読み出したデータがP2nパタンのセルデータであった場合、“1”の値を持つ1ビット分のデータとして反転部107に送信する。

また、読出部110は、記憶部109から読み出したデータがP2n−1パタンのセルデータであった場合、“0”の値を持つ1ビット分のデータとして反転部107に送信する。

【0095】

〔処理〕

次に、本実施形態の画像形成装置1の処理について説明する。この処理は、画像形成装置1の主要な構成要素による動作として実現される。

【0096】

図10は、記憶部109への書込処理を示すフローチャートである。

まず、ステップS1001において、書込部108は、マップ変更通知部902による通知に従い、反転部107から受信したデータに対応する重要度Iが1であるか否か判定する。制御部Cは、管理データに含まれる、認証印刷用の画像データの重要度を反転部107に送信し、反転部107は、前記画像データをラスタライズした2値データに前記重要度を対応付けて書込部108に送信する。

重要度Iが1である場合(ステップS1001でYes)、反転部107から受信したデータが重要データであることを意味し、ステップS1002に進む。一方、重要度Iが1でない場合(ステップS1001でNo)、I=0であって、反転部107から受信したデータが通常データであることを意味し、ステップS1010に進む。

なお、重要度Iは、第1の実施形態に倣い、所定のバンド毎に、データに割り当ててフラグレジスタ106に格納される。

【0097】

ステップS1002において、書込部108は、制御部Cから記憶部109の格納ビット数nを取得するとともに、ラスタライザ102から計数対象となる2値データの総数kを取得する。また、書込部108は、計数対象データの検査用のアドレスである検査アドレスCAを、CA=0(先頭のアドレス)にリセットするとともに、計数対象データの書き込み用のアドレスである書込アドレスWAを、WA=0(先頭のアドレス)にリセットする。ステップS1002の後、ステップS1003に進む。

【0098】

ステップS1003において、書込部108は、計数対象データにおいて、検査アドレスCAから(CA+1)までの1ビット分のデータを抽出し、検査する。ステップS1003の後、ステップS1004に進む。

【0099】

ステップS1004において、書込部108は、検査の対象となるデータの値が“0”であるか否か判定する。データの値が“0”である場合(ステップS1004でYes)、そのデータのビットパタンが、格納ビット数n=1におけるP1パタン(図3参照)と同等であることを意味し、ステップS1005に進む。データの値が“0”でない場合(ステップS1004でNo)、データの値は“1”であって、そのデータのビットパタンが、格納ビット数n=1におけるP2パタン(図3参照)と同等であることを意味し、ステップS1006に進む。

なお、検査の対象となるデータが適合するビットパタンの特定は、計数部104による処理(図5のステップS503参照)と同様である。また、これまでの説明から明らかであるが、前記したP1パタン、P2パタンの説明において、格納ビット数nが1であることを述べたが、本ステップで説明する格納ビット数nは、ステップS1002の格納ビット数nとは意味が異なる点に留意されたい。

【0100】

ステップS1005において、書込部108は、検査の対象となるデータを、P2n−1パタンとして記憶部109に書き込む。ステップS1005の後、ステップS1007に進む。

【0101】

ステップS1006において、書込部108は、検査の対象となるデータを、P2nパタンとして記憶部109に書き込む。ステップS1006の後、ステップS1007に進む。

【0102】

ステップS1007において、書込部108は、検査アドレスCAを1ビット単位でインクリメントするとともに、書込アドレスWAをnビット単位でインクリメントする。これにより、ステップS1003による検査の対象が次の1ビットのデータに移るとともに、検査した1ビット分のデータをnビットのデータとして記憶部109に書き込むことができる。ステップS1007の後、ステップS1008に進む。

【0103】

ステップS1008において、書込部108は、現在の検査対象となるデータの検査アドレスCAが2値データの総数kに達したかまたは上回っているか判定する。達したかまたは上回っていれば(ステップS1008でYes)、すべてのデータを記憶部109へ書き込んだことを意味し、ステップS1009に進む。そうでなければ(ステップS1008でNo)、ステップS1003に戻る。

【0104】

ステップS1009において、書込部108は、検査したデータに対応するすべての重要度Iを記憶部109に書き込む。なお、本ステップにおける重要度Iはすべて、I=1である。ステップS1009の後、処理全体が終了する。

【0105】

ステップS1010において、書込部108は、重要度Iが0である通常データに対して、図7のフローチャートの処理を含む第1の実施形態における処理を書込処理として実行する。

図10に示す処理により、格納ビット数nのNANDフラッシュメモリのセルを、格納ビット数1のセルとみなしてデータを書き込むことができる。

なお、書込部108により書き込まれたデータおよび重要度は、認証印刷用の画像データを送信したユーザが画像形成装置1にて認証確認を行うか、所定のデータ保持時間が経過するまで、記憶部109に記憶される。

【0106】

認証印刷用の画像データを送信したユーザは、画像形成装置1にて認証確認を行う。ユーザの正当性が確認されると、制御部Cは、読出部110に対し、記憶部109から該当のデータの読み出しを指示する。

【0107】

図11は、記憶部109からの読出処理を示すフローチャートである。

まず、ステップS1101において、読出部110は、記憶部109からデータおよび重要度を読み出す。読出部110は、記憶部109から読み出す重要度が、記憶部109から読み出すデータに対応していることは認識している。ステップS1101の後、ステップS1102に進む。

【0108】

ステップS1102において、読出部110は、マップ変更通知部902による通知に従い、記憶部109から読み出したデータに対応する重要度Iが1であるか否か判定する。重要度Iが1である場合(ステップS1102でYes)、記憶部109から読み出したデータが重要データであることを意味し、ステップS1103に進む。重要度Iが1でない場合(ステップS1102でNo)、I=0であって、記憶部109から読み出したデータが通常データであることを意味し、ステップS1110に進む。

【0109】

ステップS1103において、読出部110は、制御部Cから記憶部109の格納ビット数nを取得するとともに、ラスタライザ102から計数対象となる2値データの総数kを取得する。また、読出部110は、計数対象データの検査用のアドレスである検査アドレスCAを、CA=0(先頭のアドレス)にリセットするとともに、計数対象データの読み出し用の読出アドレスRAを、RA=0(先頭のアドレス)にリセットする。ステップS1103の後、ステップS1104に進む。

【0110】

ステップS1104において、読出部110は、計数対象データにおいて、検査アドレスCAからCA+n−1までのnビット分のデータを抽出し、検査する。ステップS1104の後、ステップS1105に進む。

【0111】

ステップS1105において、読出部110は、検査の対象となるデータが、P2n−1パタンのデータであるか否か判定する。P2n−1パタンのデータである場合(ステップS1105でYes)、記憶部109に記憶されていたセルデータの値が“0”であることを意味し、ステップS1106に進む。P2n−1パタンのデータでない場合(ステップS1105でNo)、P2nパタンのデータということであって、記憶部109に記憶されていたセルデータの値が“1”であることを意味し、ステップS1107に進む。

【0112】

ステップS1106において、読出部110は、値が“0”となるデータを記憶部109から読み出す。ステップS1106の後、ステップS1108に進む。

【0113】

ステップS1107において、読出部110は、値が“1”となるデータを記憶部109から読み出す。ステップS1107の後、ステップS1108に進む。

【0114】

ステップS1108において、読出部110は、検査アドレスCAをnビット単位でインクリメントするとともに、読出アドレスRAを1ビット単位でインクリメントする。これにより、ステップS1104による検査の対象が次のnビットのデータに移るとともに、検査したnビット分のデータを1ビットのデータとして記憶部109から読み出すことができる。ステップS1108の後、ステップS1109に進む。

【0115】

ステップS1109において、読出部110は、現在の検査対象となるデータの検査アドレスCAが2値データの総数kに達したかまたは上回っているか判定する。達したかまたは上回っていれば(ステップS1109でYes)、記憶部109からすべてのデータを読み出したことを意味し、処理全体が終了する。そうでなければ(ステップS1109でNo)、ステップS1104に戻る。

【0116】

ステップS1110において、読出部110は、重要度Iが0である通常データに対して、図8のフローチャートの処理を含む第1の実施形態における処理を読出処理として実行する。

図11に示す処理により、格納ビット数nのNANDフラッシュメモリのセルを、格納ビット数のセルとみなしてデータを書き込むことができる。

【0117】

第2の実施形態によれば、記憶部109としてのNANDフラッシュメモリに注入および抜取される電子の総数を極力低減化することができる。格納ビット数がnのセルに対して電子を、注入する場合には最小数だけ注入するという手法を用いたからである。重要度を用いているので、前記手法を用いるデータ、つまり重要データであるか否かを把握することができる。これにより、画像形成装置のメモリの寿命の短命化をさらに抑制することができる。

【0118】

さらに、第2の実施形態によれば、セルに注入する電子数を1通りで済ませることができるため、セル内の電子の有無でデータの内容を管理できる。その結果、メモリに記憶されるデータの信頼性を高めることができる。

NAND型フラッシュメモリがnビットのデータを記憶して管理するためには、格納ビット数nのセルには、(2n−1)個の閾値電圧を設定して相当数の電子数をセルに注入する必要がある(図2参照)。よって、NAND型フラッシュメモリは、閾値電圧の値を調整することでnビットのデータを管理しているといえる。

しかし、酸化膜の劣化が進むと、セルが電子を保持する能力は低下し、複数個保持している電子の一部がフローティングゲートからp型半導体やn型半導体の層に流出してしまう可能性が高くなる。その結果、セルに注入されている電子数と、そのセルにかけていた閾値電圧の値と、セルが記憶するデータとの関係が崩れてしまい、データの信頼性が損なわれてしまう可能性が高くなる。

このような状況に対し、第2の実施形態は、閾値電圧の値やセルが保持する電子の個数とは無関係に、セルが保持する電子の有無で、セルが記憶するデータを管理するものである。よって、酸化膜の劣化が進み、セルが保持する電子の一部がフローティングゲートから流出しても、セルが保持する電子は一応存在している。この場合には、セルが記憶するデータは、正しいデータを管理しているといえる。この意味において、データの信頼性は決して損なわれていない。

従って、第2の実施形態によれば、メモリに格納されたデータの信頼性を高めることができる。

【0119】

≪その他≫

なお、前記形態は、本発明を実施する好適なものであるが、その実施形式はこれに限定するものではない。したがって、本発明の要旨を逸脱しない範囲において、その実施形式を種々変形することが可能である。

【0120】

例えば、本明細書で説明した画像形成装置は、例えば、情報処理装置プリンタ(SFP)、MFP(Multi Functional Printer)、ファクシミリ、複写装置、およびこれらの複合機においても利用可能である。

【0121】

また、本発明は、電子写真方式、帯電方式、露光方式、現像方式などの各方式を採用した画像形成装置に適用することができる。

【0122】

また、本実施形態では、再書込み回数が制限されるメモリとしてNANDフラッシュメモリについて説明したが、この発明はこれに限定されるものではない。例えば、前記メモリとして、EEPROM(Electrically Erasable Programmable Read-Only Memory)を用いてもよい。

【0123】

また、本実施形態は、メモリに記憶されるセルデータの値が小さい程、フローティングゲートに注入される電子が多くなる、という対応順位関係を取り決めた形態であった。しかし、対応順位関係はこれに限定されない。

例えば、図3において、格納ビット数n=2のとき、フローティングゲートに保持される電子の数が0、3、5、7であるとき、セルデータはそれぞれ“11”、“10”、“01”、“00”であるという対応順位関係を取り決めていた。この対応順位関係を、電子の数が0、3、5、7であるとき、セルデータはそれぞれ“11”、“01”、“10”、“00”としてもよい。

また、図3において、格納ビット数n=3のとき、フローティングゲートに保持される電子の数が0、1、2、3、4、5、6、7であるとき、セルデータはそれぞれ“111”、“110”、“101”、“100”、“011”、“010”、“001”、“000”であるという対応順位関係を取り決めていた。この対応順位関係を、電子の数が0、1、2、3、4、5、6、7であるとき、セルデータはそれぞれ“111”、“110”、“101”、“011”、“100”、“010”、“001”、“000”としてもよい。

基本的には、フローティングゲートに保持される電子の数と、セルデータの値とが1対1に対応していればよい。

【0124】

また、第2の実施形態では、1つのセルにnビット分のデータを記憶できるメモリに対し、1ビット分のデータを記憶するように用いた。そして、2n種類のビットパタンをとり得るデータのうち、フローティングゲートに電子がない状態であるP2nパタンのデータの値を“1”に対応させた。また、前記データのうち、フローティングゲート中の電子が最も少ない状態であるP2n―1パタンのデータの値を“0”に対応させた。しかし、フローティングゲート内の電子の数と、データの値との対応関係は、この場合に限定されない。

例えば、第2の実施形態で説明した方法を、図2および図3を用いた説明にあてはめると、格納ビット数n=2のときには、フローティングゲートに保持される電子の数が0となるP4パタンのデータの値を“1”に設定していた。そして、フローティングゲートに保持される電子の数が3(n=2のときは、もっとも少ない)となるP3パタンのデータの値を“0”に設定していた。しかし、例えば、フローティングゲートに保持される電子の数が5(n=2のときは、もっとも少ないわけではない)となるP2パタンのデータの値を“0”に設定するように対応関係を定めてもよい。

また、格納ビット数n=3のときには、フローティングゲートに保持される電子の数が0となるP8パタンのデータの値を“1”に設定していた。そして、フローティングゲートに保持される電子の数が1(n=3のときは、もっとも少ない)となるP7パタンのデータの値を“0”に設定していた。しかし、例えば、フローティングゲートに保持される電子の数が6(n=2のときは、もっとも少ないわけではない)となるP2パタンのデータの値を“0”に設定するように対応関係を定めてもよい。

基本的には、1ビット分のデータの値の一方に対応するビットパタンと、他方に対応するビットパタンとを違えればよい。

【0125】

また、本実施形態で説明した種々の技術を適宜組み合わせた技術を実現することもできる。

また、本実施形態で説明したソフトウェア(プログラム)をハードウェアとして実現することもでき、ハードウェアをソフトウェアと協働させて実現することもできる。例えば、画像形成装置1の構成要素のうちソフトウェアとして実装したラスタライザ102、計数部104、比較部105、フラグレジスタ106、反転部107、重要度レジスタ901およびマップ変更通知部902は、ハードウェアとして実装することで、画像処理の高速化を実現することができる。フラグレジスタ106をハードウェアとして実装する場合は、ハードウェアとして実装した反転部107に内蔵することが好ましい。重要度レジスタ901をハードウェアとして実装する場合は、ハードウェアとして実装した画像処理部101に内蔵することが好ましい。

【0126】

その他、ハードウェア、ソフトウェア、各フローチャートなどの具体的な構成について、本発明の趣旨を逸脱しない範囲で適宜変更が可能である。

【符号の説明】

【0127】

1 画像形成装置

C 制御部

100 I/F部

101 画像処理部

102 ラスタライザ

103 画像形成部

104 計数部

105 比較部

106 フラグレジスタ

107 反転部

108 書込部

109 記憶部

110 読出部

901 重要度レジスタ

902 マップ変更通知部

【特許請求の範囲】

【請求項1】

画像データから2値データを生成するラスタライザと、

再書込み回数が制限され、n(nは自然数)ビットのデータ毎に記憶するメモリと、

前記2値データをnビット毎に分割して、前記分割されたnビットの2値データが、2n種類に組み合わされたビットパタンのいずれに適合するかを特定し、前記分割されたnビットの2値データと、前記特定したビットパタンとが適合する適合数を計数する計数部と、

前記適合数を計数したビットパタンのうち、第1のビットパタンの適合数と、前記第1のビットパタンと反転関係にある第2のビットパタンの適合数とを比較する比較部と、

前記比較の結果に基づいて、nビットの2値データを反転する反転部と、

前記反転したnビットの2値データと、反転したことを示す反転フラグとを前記メモリに書き込む書込部と、

前記メモリから、前記nビットの2値データおよび前記反転フラグを読み出し、前記反転部に、反転したnビットの2値データを復元させる読出部と、

前記復元したnビットの2値データを用いて、画像を形成する画像形成部と、を備える

ことを特徴とする画像形成装置。

【請求項2】

前記書込部は、前記2値データが所定の条件を満たす場合、前記条件を満たす2値データを構成する1ビットの2値データをnビットの2値データとして取り扱うことができるように2値データの書込アドレスを変更し、前記1ビットの2値データを前記メモリに書き込む

ことを特徴とする請求項1に記載の画像形成装置。

【請求項3】

前記メモリへ注入する電子の数について、前記第1のビットパタンを構成するnビットの2値データを前記メモリに記憶するために必要な電子の数のほうが、前記第2のビットパタンを構成するnビットの2値データを前記メモリに記憶するために必要な電子の数よりも多い場合において、

前記第1のビットパタンの適合数が前記第2のビットパタンの適合数よりも多いとき、前記反転部は、前記第1のビットパタンを構成するnビットの2値データを反転する

ことを特徴とする請求項1または請求項2に記載の画像形成装置。

【請求項4】

2値データを、n(nは自然数)ビットのデータ毎に記憶するメモリを備える画像形成装置において、

前記nビットの2値データの1つである第1のデータを前記メモリに記憶するために必要な電子の数のほうが、前記第1のデータと反転関係にある第2のデータを前記メモリに記憶するために必要な電子の数よりも多い場合において、

前記画像形成装置の制御部は、

前記第1のデータの数と、前記第2のデータの数とを計数する制御と、

前記第1のデータの数が前記第2のデータの数よりも多い場合、前記第1のデータを反転して前記メモリに記憶する制御と、

前記反転した第1のデータを再度反転して前記メモリから読み出す制御と、を実行する

ことを特徴とする画像形成装置。

【請求項5】

再書込み回数が制限され、n(nは自然数)ビットのデータを毎に記憶するメモリに接続された制御部に実行させるメモリ格納プログラムにおいて、

前記制御部を、

画像データから2値データを生成するラスタライザと、

前記2値データをnビット毎に分割して、前記分割されたnビットの2値データが、2n種類に組み合わされたビットパタンのいずれに適合するかを特定し、前記分割されたnビットの2値データと、前記特定したビットパタンとが適合する適合数を計数する計数部と、

前記適合数を計数したビットパタンのうち、第1のビットパタンの適合数と、前記第1のビットパタンと反転関係にある第2のビットパタンの適合数とを比較する比較部と、

前記比較の結果に基づいて、nビットの2値データを反転する反転部と、

前記反転したnビットの2値データと、反転したことを示す反転フラグとを前記メモリに書き込む書込部と、

前記メモリから、前記nビットの2値データおよび前記反転フラグを読み出し、前記反転部に、反転したnビットの2値データを復元させる読出部と、して機能させる

ことを特徴とするメモリ格納プログラム。

【請求項1】

画像データから2値データを生成するラスタライザと、

再書込み回数が制限され、n(nは自然数)ビットのデータ毎に記憶するメモリと、

前記2値データをnビット毎に分割して、前記分割されたnビットの2値データが、2n種類に組み合わされたビットパタンのいずれに適合するかを特定し、前記分割されたnビットの2値データと、前記特定したビットパタンとが適合する適合数を計数する計数部と、

前記適合数を計数したビットパタンのうち、第1のビットパタンの適合数と、前記第1のビットパタンと反転関係にある第2のビットパタンの適合数とを比較する比較部と、

前記比較の結果に基づいて、nビットの2値データを反転する反転部と、

前記反転したnビットの2値データと、反転したことを示す反転フラグとを前記メモリに書き込む書込部と、

前記メモリから、前記nビットの2値データおよび前記反転フラグを読み出し、前記反転部に、反転したnビットの2値データを復元させる読出部と、

前記復元したnビットの2値データを用いて、画像を形成する画像形成部と、を備える

ことを特徴とする画像形成装置。

【請求項2】

前記書込部は、前記2値データが所定の条件を満たす場合、前記条件を満たす2値データを構成する1ビットの2値データをnビットの2値データとして取り扱うことができるように2値データの書込アドレスを変更し、前記1ビットの2値データを前記メモリに書き込む

ことを特徴とする請求項1に記載の画像形成装置。

【請求項3】

前記メモリへ注入する電子の数について、前記第1のビットパタンを構成するnビットの2値データを前記メモリに記憶するために必要な電子の数のほうが、前記第2のビットパタンを構成するnビットの2値データを前記メモリに記憶するために必要な電子の数よりも多い場合において、

前記第1のビットパタンの適合数が前記第2のビットパタンの適合数よりも多いとき、前記反転部は、前記第1のビットパタンを構成するnビットの2値データを反転する

ことを特徴とする請求項1または請求項2に記載の画像形成装置。

【請求項4】

2値データを、n(nは自然数)ビットのデータ毎に記憶するメモリを備える画像形成装置において、

前記nビットの2値データの1つである第1のデータを前記メモリに記憶するために必要な電子の数のほうが、前記第1のデータと反転関係にある第2のデータを前記メモリに記憶するために必要な電子の数よりも多い場合において、

前記画像形成装置の制御部は、

前記第1のデータの数と、前記第2のデータの数とを計数する制御と、

前記第1のデータの数が前記第2のデータの数よりも多い場合、前記第1のデータを反転して前記メモリに記憶する制御と、

前記反転した第1のデータを再度反転して前記メモリから読み出す制御と、を実行する

ことを特徴とする画像形成装置。

【請求項5】

再書込み回数が制限され、n(nは自然数)ビットのデータを毎に記憶するメモリに接続された制御部に実行させるメモリ格納プログラムにおいて、

前記制御部を、

画像データから2値データを生成するラスタライザと、

前記2値データをnビット毎に分割して、前記分割されたnビットの2値データが、2n種類に組み合わされたビットパタンのいずれに適合するかを特定し、前記分割されたnビットの2値データと、前記特定したビットパタンとが適合する適合数を計数する計数部と、

前記適合数を計数したビットパタンのうち、第1のビットパタンの適合数と、前記第1のビットパタンと反転関係にある第2のビットパタンの適合数とを比較する比較部と、

前記比較の結果に基づいて、nビットの2値データを反転する反転部と、

前記反転したnビットの2値データと、反転したことを示す反転フラグとを前記メモリに書き込む書込部と、

前記メモリから、前記nビットの2値データおよび前記反転フラグを読み出し、前記反転部に、反転したnビットの2値データを復元させる読出部と、して機能させる

ことを特徴とするメモリ格納プログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−90145(P2013−90145A)

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願番号】特願2011−229006(P2011−229006)

【出願日】平成23年10月18日(2011.10.18)

【出願人】(591044164)株式会社沖データ (2,444)

【Fターム(参考)】

【公開日】平成25年5月13日(2013.5.13)

【国際特許分類】

【出願日】平成23年10月18日(2011.10.18)

【出願人】(591044164)株式会社沖データ (2,444)

【Fターム(参考)】

[ Back to top ]