画像形成装置の開発・メンテナンス用ツール及び画像形成装置の開発・メンテナンス方法

【課題】ヘッドモジュールに転送するための簡易パターンの生成を高速に行うことができる画像形成装置の開発・メンテナンス用ツールを提供する。

【解決手段】本発明の画像形成装置の開発・メンテナンス用ツールは、簡易パターンファイルの頻出パターンをインデックステーブルのインデックスNo.で代表させて記述したインデックステーブルを用いるものであり、簡易パターンメモリ(410)には、簡易パターンデータファイル(411)とインデックステーブル(412)が設けられ、これらの記憶手段から簡易パターンを生成するように構成される。

【解決手段】本発明の画像形成装置の開発・メンテナンス用ツールは、簡易パターンファイルの頻出パターンをインデックステーブルのインデックスNo.で代表させて記述したインデックステーブルを用いるものであり、簡易パターンメモリ(410)には、簡易パターンデータファイル(411)とインデックステーブル(412)が設けられ、これらの記憶手段から簡易パターンを生成するように構成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、プリンタなどのヘッドモジュールによって印刷出力した印刷結果の画質評価テストをおこなう際に用いる開発・メンテナンス用ツール、及び、ヘッドモジュールの画質評価テストを行う開発・メンテナンス方法に関する。

【背景技術】

【0002】

プリンタなどの画像形成装置の開発においては、各種コントローラが完成していないような段階において、メカニカルな部分のハードウエア構成についてテストを行いたい、ということがある。このようなハードウエアとしては、例えばヘッドモジュールがあり、開発段階のコントローラレスの状態にてヘッドモジュールによる印字品質の確認等を行いたいという要請がある。このため開発用のボードなどを利用して、画像データをヘッドモジュールに入力してテスト印刷を行うことが一般的である。なお、このようなヘッドモジュールによる印字品質の確認を行いたいということは、画像形成装置のメンテナンスの際にも生じる要請であり、メンテナンスの現場においても、ヘッドモジュールに対して、既存のコントローラを介さず、メンテナンス用のツールなどから直接的に画像データを入力することが行われている。

【0003】

プリンタなどのヘッドモジュールによって印刷出力した印刷結果の画質評価テストをおこなう際には、細かい線の繰り返し画像や円などの一定パターンの繰り返し画像など、多種類の画像を印刷出力して画質評価を行う。この場合、ビットマップ画像などのデータ量の大きな画像データを用いるのではなく、データ容量の小さな画像データを用いて画質評価をおこなうことが望まれている。

【0004】

出願人は、このようなテスト印刷において、ヘッドモジュールで印刷出力させるテストパターンとして、簡易パターンというものを提案している。この簡易パターンは、データ容量を少なくして、比較的簡単なファイルの定義に基づく画質評価用のパターンデータである(特許文献1、特許文献2参照)。

【特許文献1】特願2006−108350号公報

【特許文献2】特願2006−108351号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

画像形成装置などのプリンタ内部においては、印刷画像データは、ヘッドモジュールから1ドット単位に受信するビデオクロックに同期して出力する必要がある。つまり、

(1ドットをデコードするための処理速度)≧(1ドット出力要求速度)

を保つ必要があり、デコード部とヘッドモジュールとの間に出力画像用バッファメモリ

が無く、ビデオクロックに同期するように画像をデコードして、出力するシステムである必要がある。そして、このようなスペックは、ヘッドモジュールの評価を行う画像形成装置の開発・メンテナンス用ツールにおいても要求されるものである。

【0006】

ところで、従来例の簡易パターンデータは、1ラインを8ビットの階調データとその繰り返し、更にグループの繰り返しにより定義し、ラインデータの繰り返しによりページデータを作成する為、常に8ビットのデータで1ドットの処理をする仕様となっていた。印刷の高速化、高解像度化に伴い画素データのデコードも高速化する必要がある。そして、デコードの処理を高速化するためには、クロックアップによって、全体の処理を高速化する方法、及び、処理のパイプライン化、又はデコードの並列処理化によって複数の画素データを同時にデコードする方法の2通りの方法が考えられる。これらの方法を実現するためには、1クロック毎にデコーダへ何画素分のデータを渡せるかがキーになり、メモリから1クロックでどれだけ多くのデコード前画素データを読み込めるかにかかっているが、従来の簡易パターンにおいてはこのような高速化に係ることについては考慮されていなかった。

【課題を解決するための手段】

【0007】

本発明は上記の各課題を解決するために、請求項1に係る発明は、簡易パターンを生成して、当該簡易パターンをヘッドモジュールに転送することによって画像形成装置の開発やメンテナンスの際のテスト印刷を行う画像形成装置の開発・メンテナンス用ツールにおいて、当該簡易パターンに頻出するデータ配列の少なくとも一部をインデックス番号で代表したパターンデータが記憶されているインデックステーブルを記憶するインデックステーブル記憶手段と、当該インデックス番号を用いて記述された簡易パターンデータファイルを記憶する簡易パターンデータファイル記憶手段とを有し、当該簡易パターンを該簡易パターンデータファイル記憶手段と該インデックステーブル記憶手段を読み出すことによって生成することを特徴とする。

【0008】

このような本発明の開発・メンテナンス用ツールによれば、ヘッドモジュールに転送するための簡易パターンの生成においては、インデックステーブルを用いて、簡易パターンデータファイルを所謂データ圧縮するような形式が採られているので、(1ドットをデコードするための処理速度)≧(1ドット出力要求速度)の要求に対応することができ、ヘッドモジュールに対してより高速にデータ転送を行うことができる。

【0009】

また、請求項2に係る発明は、簡易パターンを生成して、当該簡易パターンをヘッドモジュールに転送することによって画像形成装置の開発やメンテナンスの際のテスト印刷を行う画像形成装置の開発・メンテナンス方法において、当該簡易パターンに頻出するデータ配列の少なくとも一部をインデックス番号で代表したパターンデータが記憶されているインデックステーブルを準備するステップと、当該インデックス番号を用いて記述された簡易パターンデータファイルを準備するステップと、該簡易パターンデータファイルと該インデックステーブルを参照することによって当該簡易パターンを生成するステップとを含むことを特徴とする。

【0010】

このような本発明の開発・メンテナンス用方法によれば、ヘッドモジュールに転送するための簡易パターンの生成においては、インデックステーブルを用いて、簡易パターンデータファイルを所謂データ圧縮するような形式が採られているので、(1ドットをデコードするための処理速度)≧(1ドット出力要求速度)の要求に対応することができ、ヘッドモジュールに対してより高速にデータ転送を行うことができる。

【発明を実施するための最良の形態】

【0011】

以下、本発明の実施の形態を図面を参照しつつ、本発明の実施の形態に係る画像形成装置の開発・メンテナンス用ツール(方法)について説明する。

(簡易パターンのデータ構造)

図1は、簡易パターンファイルのデータ構造の一例を示す説明図である。簡易パターンファイル100は、画像をカンマ区切りのテキスト形式で定義しているパターンデータである。この簡易パターンファイル100に基づいて、細かい線の繰り返し画像や円などの一定パターンの繰り返し画像など多種類の画像を作成して印刷することによって、プリンタなどにより印刷出力された画像の画質評価をおこなうことができる。

【0012】

図1に示すように、簡易パターンファイル100は、主走査方向側の定義であるライン定義部101(図中上側の破線で囲んだ領域)と、副走査方向側の定義であるライン配置部102(図中下側の破線で囲んだ領域)とによって構成されている。ここで、主走査方向とは、たとえばレーザプリンタによって印刷出力された画像の画質評価をおこなう場合に、筐体内部に設けられた感光体に照射されるレーザ光などが走査される方向であり感光体の進行方向と垂直な方向である。また、副走査方向とは、主走査方向と垂直な方向であり、感光体の進行方向と同一方向である。

【0013】

また、簡易パターンファイル100の先頭行103にある「X」は、「簡易パターンファイル識別子」である。この識別子「X」は、簡易パターンファイル100がどのようなパターンに定義されるかを示した識別子である。この識別子「X」を用いれば、たとえば、プリンタの固有の仕様などを示すことができる。具体的には、識別子「X」は、プリンタの仕様にあわせて、画素値の上「2Bit」が画素値の配置情報(右寄せ、左寄せ、中央寄せなど)で、下「6Bit」がピクセル値であることを示している。

【0014】

他に識別子を用いて示すことができる情報としては、たとえば画像を構成する画素値の配置情報、プリンタ内に設けられたプリンタヘッドの進行方向、主走査方向の最大の長さ、印刷をおこなう際における印刷出力する色の順番などの情報が挙げられる。また、簡易パターンファイル100に基づいて作成された画像を印刷する際には、この識別子「X」が示す識別情報に応じて印刷処理をおこなう。

【0015】

ライン定義部101は、主走査方向のラインを構成する画素値と当該画素値の所定の画素数とを関連付けて定義するものであり、複数のラインについてライン定義することができる。また、ライン配置部102は、ライン定義部101によって定義されたラインと、当該ラインの副走査方向へのライン数とを関連付けて定義する。さらに、ライン配置部102は、画像として用いられる色ごとに定義することができる。具体的には、ライン定義部101で定義された各ラインを副走査方向にどのように配置するかを定義するものであり、たとえば、C(シアン)、M(マゼンタ)、Y(イエロー)、K(ブラック)などの8色ごとに定義されている。

【0016】

なお、簡易パターンファイル100におけるライン定義部101とライン配置部102との間には、2行の空行(32行目および33行目)が設けられており、この空行によりライン定義部101とライン配置部102とを区切っている。つぎに、簡易パターンファイル100内の各部の構成を示す際に用いる用語の説明をするとともに、ライン定義部101とライン配置部102との詳細な説明をする。

【0017】

まず、ライン定義部101は、ライン定義された複数のラインによって構成されている。また、ライン定義部101の複数のラインにはそれぞれ番号が付されており、上から順番にライン定義1(110)、ライン定義2(111)、ライン定義3(112)、ライン定義4(113)、ライン定義5(114)、ライン定義6(115)、ライン定義7(116)となっている。さらに、図示は省略しているが、ライン定義1〜7とは異なるライン定義0も存在している。ライン定義0は、予約番号であり、「画素値0」がライン幅分並んでいることを示した白べたラインとなる。

【0018】

また、ライン定義1〜7のそれぞれのラインの間には、1行の空行が設けられており、たとえば5行目の空行により、ライン定義1(110)とライン定義2(111)とを区切っている。なお、ここではライン定義の定義数をライン定義0〜7の8個としたが、定義することができるライン定義の定義数は、固定ではなく任意に変更することができる。具体的には、たとえば簡易パターンファイル100のライン定義部101に、最大で256個までのライン定義を任意に定義することができる。

【0019】

それぞれのライン定義1〜7は、少なくとも1つのグループによって構成されており、さらに、それぞれのグループは、少なくとも1回のグループユニットの繰り返しによって構成されている。また、ライン定義部101の「A列」には、それぞれのグループユニットが何回繰り返されたかを示す繰り返し回数がそれぞれのグループユニットにあわせて付されている。なお、ライン定義において、ある画素値以降はすべて白データ(画像として何も表現されていない白べたライン)となる場合は、この白データを定義しなくてもよい。さらに、あるライン以降はすべて空白行となる場合は、この空白行を定義しなくてもよい。つぎに、ライン定義3(112)を例に挙げてライン定義についての詳細な説明を行う。

【0020】

図2−1は、ライン定義の一例を示す図である。また、図2−2は、図2−1に示すライン定義の内容を示す説明図である。図2−1に示すように、ライン定義3(112)は、グループ1(201)とグループ2(202)とが順番に並べられて構成されている。また、グループ1(201)は、グループユニット1(210)によって構成されており、グループユニット1(210)が1回繰り返されたことを示す「1」がグループユニット1(210)とともに付されている。さらに、グループユニット1(210)は、画素値0が118画素並んでいることを示すペア1(211)と、画素値0が80画素並んでいることを示すペア2(212)とによって構成されている。

【0021】

このように、ライン定義3(112)において、ペア1(211)とペア2(212)とが並んでグループユニット1(210)を形成し、このグループユニット1(210)が1回繰り返されてグループ1(201)を形成している。また、図2−1に示すように、グループ2(202)も同様の構成で形成されている。具体的には、ペア3(221)とペア4(222)とが並んでグループユニット2(220)を形成し、このグループユニット2(220)が1回繰り返されてグループ2(202)を形成している。

【0022】

以上説明したように、ライン定義3(112)は、上記グループ1(201)とグループ2(202)とが順に並んで構成されており、ライン定義3(112)の画素値の並びは順番に、画素値「0」が118画素、画素値「0」が80画素、画素値「0」が80画素、画素値「63」が6620画素となる。

【0023】

また、簡易パターンファイル100のライン定義部101において、同じ画素値のペアを並べて定義することができる(たとえば、図1に示すライン定義3(112)における、画素値「0」が118画素、画素値「0」が80画素の部分。)。これにより、たとえばすべてのライン定義の先頭に余白部分を設けるためのペアを定義することで、各ラインの先頭に共通の余白部分を設けることができる。さらに、副走査方向に連続するパターンを形成する際にも、同様に同じ画素値のペアを並べて定義することができる。

【0024】

つぎに、ライン配置部102についての詳細な説明をする。ライン配置部102は、複数のゾーンによって構成されている。また、ライン配置部102の複数のゾーンにはそれぞれゾーン番号が付されており、上から順番にゾーン0、1、2、3(図1に示す120、121、122、123)となっている。さらに、ライン配置部102の先頭行(34行目)には、それぞれの色のページが何番目から何番目までのゾーンで形成されているかをあらわす色情報が示されている。

【0025】

また、それぞれのゾーン0〜3(120〜123)には、ライン定義部101において定義されたある番号のライン定義がいくつか並んで形成されたラインセットと、いくつかのラインセットが並んで形成されたゾーンユニットとによって構成されており、それぞれのゾーンユニットには、ゾーンユニットが何回繰り返されているかを示すゾーン回数が付されている。なお、ここではゾーンの定義数をゾーン0〜3(120〜123)の4個としたが、ライン定義の定義数と同様に最大で256個までのゾーンを任意に定義することができる。ここで、図3を用いてライン配置部102についての詳細な説明をおこなう。

【0026】

図3は、ライン配置の一例を示す図である。図3に示すように、ライン配置部102は、色情報124と、ゾーン0(120)と、ゾーン1(121)と、ゾーン2(122)と、ゾーン(123)とによって構成されている。

【0027】

ゾーン0(120)は、ゾーンユニット1(312)が1回繰り返されて並んでいる構成である。また、ゾーンユニット1(312)は、ラインセット1(311)によって構成されており、このラインセット1(311)は、図1に示すライン定義1(110)が3000ライン並んでいることを示している。

【0028】

ゾーン1(121)は、ゾーンユニット2(324)が1回繰り返されて並んでいる構成である。また、ゾーンユニット2(324)は、ラインセット2(321)と、ラインセット3(322)と、ラインセット4(323)とによって構成されている。

【0029】

ラインセット2(321)は、図1に示すライン定義1が6661ライン並んでいることを示している。また、ラインセット3(322)、ラインセット4(323)についてもラインセット2(321)と同様であり、所定のライン定義がいくつ並んでいるかを示している。なお、ゾーン2(122)およびゾーン3(123)の構成は、上記ゾーン0(120)およびゾーン1(121)と同様のため説明を省略する。

【0030】

つぎに、ライン配置部102の先頭行(34行目)に示された、色情報について詳細に説明する。色情報は、34行目の左から順番に、第1色目に応じた色情報331として(1,1)、第2色目に応じた色情報332として(0,0)、第3色目に応じた色情報333として(1,1)、第4色目に応じた色情報334として(0,0)が示されている。たとえば、第1色目の色情報331である(1,1)は、第1色目の先頭ゾーン番号が「1」であり、終了ゾーン番号が「1」であることを示している。

【0031】

なお、ここでは色情報として開始ゾーン番号および終了ゾーン番号がすべて同じ番号となっているが、開始ゾーン番号および終了ゾーン番号は、それぞれ異なる番号であってもよい。具体的には、たとえば、色情報を(0,1)とすることによって、先頭ゾーン番号を「0」、終了ゾーン番号を「1」としてもよい。

【0032】

具体的には、ライン配置部102の第1色目のライン配置は、順番に、ライン定義0が6661ライン、ライン定義2(111)が3000ライン、ライン定義3(112)が1ライン並んでいる配置となる。

【0033】

また、第2色目の色情報は(0,0)であるため、第2色目の先頭ゾーン番号は「0」であり、終了ゾーン番号が「0」である。このため、ライン配置部102の第2色目のライン配置は、ライン定義1(110)が3000ライン並んでいる配置となる。

【0034】

さらに、第3色目の色情報は(1,1)であるため、第3色目の先頭ゾーン番号は「1」であり、終了ゾーン番号が「1」である。このため、ライン配置部102の第3色目のライン配置は、順番に、ライン定義0が6661ライン、ライン定義2(111)が3000ライン、ライン定義3(112)が1ライン並んでいる配置となる。

【0035】

さらに、第4色目の色情報は(0,0)であるため、第3色目の先頭ゾーン番号は「0」であり、終了ゾーン番号が「0」である。このため、ライン配置部102の第2色目のライン配置は、ライン定義1(110)が3000ライン並んでいる配置となる。

【0036】

以上説明したように、簡易パターンファイル100に基づいて画像を作成する場合、ライン定義部101で定義された各ラインが、色ごとに、ライン配置部102に示すライン配置に基づいて副走査方向に配置され、画像が形成されることとなる。つぎに、この発明の実施の形態にかかるインデックステーブルについて説明する。

【0037】

図4は、本発明の実施の形態に係る画像形成装置の開発・メンテナンス用ツールにおけるインデックステーブルを示す図である。インデックステーブルは、簡易パターンファイルにおける頻出するデータパターンをインデックスNo.で代表させたものである。

簡易パターンファイルは、パターンの繰り返しの為、少種類の階調データの組み合わせになる場合が多い。そこで、パターンデータに出現する階調値と、繰り返し数をインデックステーブルに登録し、頻出するパターンの代替としてインデックステーブルNo.を使用することでデータのビット幅を減らす。また、インデックステーブルNo.を簡易パターンデータとして持つ為、データのビット幅は、インデックステーブルに登録されたデータ数に依存する。ビット幅を決めてしまえば、1バイト中の画素データを1画素ではなく、多画素に出来る。本実施形態では、「グループユニットの繰り返し数」、「画素値」、「画素繰り返し数」、「ゾーン開始」、「ゾーン終了」、「ゾーンユニット繰り返し数」、「ライン定義No.」、「ライン繰り返し数」の各項目に対して、例えば図4に示すように、「0」、「1」、「2」の3つのインデックスNo.に代表させるように定義することができる。このようなインデックステーブルによれば、図1に示した簡易パターンファイルは、インデックスNo.を用いて図5のように表すことができる。

【0038】

このように本発明によれば、簡易パターンファイルの頻出パターンをインデックステーブルのインデックスNo.で代表させて処理するものであり、ヘッドモジュールに転送するための簡易パターンの生成においては、このインデックステーブルを用いて、簡易パターンデータファイルを所謂データ圧縮するような形式が採られているので、(1ドットをデコードするための処理速度)≧(1ドット出力要求速度)の要求に対応することができ、ヘッドモジュールに対してより高速にデータ転送を行うことができる。

(システム構成)

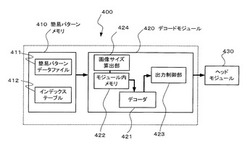

図6は、本発明の実施の形態に係る画像形成装置の開発・メンテナンス用ツールのシステム構成の一例を示すブロック図である。図6において、開発・メンテナンス用ツール400は、簡易パターンメモリ410と、デコードモジュール420とを備えて構成されている。

【0039】

開発・メンテナンス用ツール400は、ヘッドモジュール430において印刷出力する簡易パターンファイルを選択する。ここで、選択される簡易パターンは、後述するようにメモリ(例えば、フラッシュメモリを使用)に、簡易パターンデータファイル411とインデックステーブル412として保存されており、簡易パターンごとにそれぞれヘッダ情報(ファイル名など)が付加されている。開発者、メンテナンス要員は、たとえば図示しない操作部を操作することによって図示しないLCDに表示された複数の簡易パターンファイル名の中から印刷出力するための簡易パターンファイルを選択し、図示しないスタートボタンを押下してヘッドモジュール430に印刷を開始させる。

【0040】

開発・メンテナンス用ツール400は、例えば、フラッシュメモリと、FPGA(Field Programmable Gate Array)とからなる。フラッシュメモリは、ブートプログラム、画像データ処理プログラムなどの各種プログラムや複数の簡易パターンファイルなどを格納している。FPGAは、フラッシュメモリから簡易パターンデータファイル411とインデックステーブル412を読み出して復号化(デコード処理)し、復号化した簡易パターンファイルをヘッドモジュール430に転送する。

【0041】

ヘッドモジュール430は、FPGAの制御に基づいて、転送された簡易パターンファイルを印刷出力する。ヘッドモジュール430としては、レーザプリンタ方式、インクジェットプリンタ方式および熱転写プリンタ方式など各方式が用い得る。

(画像データ処理の内容)

つぎに、フラッシュメモリに格納されている簡易パターンデータファイル411とインデックステーブル412を読み出して復号化する際のデコード処理について詳細に説明する。FPGAは、フラッシュメモリから読み出した簡易パターンデータファイル411とインデックステーブル412に対するデコード処理をリアルタイムに(連続して)実行し、デコード処理された簡易パターンファイルを順次ヘッドモジュール430に転送する。これにより、印刷出力される画像が途中で途切れてしまうなどの不具合を防止することができる。

【0042】

上述したように、FPGAはリアルタイムにデコード処理を実行するため、フラッシュメモリから読み出された簡易パターンファイルを、デコード処理しやすい形式でFPGA内に保存する。具体的には、たとえばフラッシュメモリから読み出された簡易パターンファイルを、FPGA内に設けられた簡易パターンファイル格納用内部RAM(Random Access Memory)にテーブル形式で保存する。

【0043】

図7は、簡易パターンファイル格納用内部RAMの概要を説明するための説明図である。図7に示すように、簡易パターンデータファイル411は、インデックステーブル412を参照しつつ、FPGA内に設けられた簡易パターンファイル格納用内部RAM501に保存される。ここで、それぞれの内部RAM(No.1〜No.9)に保存される内容について説明する。なお、簡易パターンファイル格納用内部RAM501は、ライン定義に関するブロック502、ライン配置に関するブロック503およびアドレス取得用に関するブロック504の3つの分類ブロックに分けられて設けられている。

【0044】

RAM_No.1(RAM_PULSE)には、ライン定義されているすべての画素値を保存している。画素値を保存する際には、定義された画素値を順番に並べて保存し、簡易パターンファイルにおける行が変わる部分(グループが変わる場合)には、行が変わることを示す(グループが変わったことを示す)付加情報としてターミネータ情報を画素値と画素値との間に入れて保存する。具体的には、たとえば図1に示す簡易パターンファイル100のライン定義部101において定義された画素値を保存する場合、RAM_No.1(RAM_PULSE)には、画素値が「0,63,0,ターミネータ情報,0,0,63,0,0,ターミネータ情報,0,…」と順番に並べられて保存される。

【0045】

RAM_No.2(RAM_PULSE_NUM)には、ライン定義されているすべての画素の繰り返し回数を保存している。画素値の繰り返し回数を保存する際も上記と同様12に、定義された画素値の繰り返し回数を順番に並べて保存し、グループが変わる場合には、グループが変わったことを示すターミネータ情報を繰り返し回数と繰り返し回数との間に入れて保存する。具体的には、たとえば図1に示す簡易パターンファイル100のライン定義部101において定義された画素値の繰り返し回数を保存する場合、RAM_No.2(RAM_PULSE_NUM)には、繰り返し回数が「118,6780,118,ターミネータ情報,118,80,80,6620,118,ターミネータ情報,118,…」と順番に並べられて保存される。

【0046】

RAM_No.3(RAM_REPEAT_X)には、ライン定義されているすべてのグループユニットの繰り返し回数を保存している。グループユニットの繰り返し回数を保存する際には、定義されたグループユニットの繰り返し回数を順番に並べて保存し、簡易パターンファイルにおけるライン定義とライン定義との間で行が変わる場合(ライン定義が変わる場合)は、行が変わったことを示す(ライン定義が変わったことを示す)ターミネータ情報を繰り返し回数と繰り返し回数との間に入れて保存する。具体的には、たとえば図1に示す簡易パターンファイル100のライン定義部101において定義されたグループユニットの繰り返し回数を保存する場合、RAM_No.3(RAM_REPEAT_X)には、繰り返し回数が「1,ターミネータ情報,1,ターミネータ情報,1,1,ターミネータ情報,1,…」と順番に並べられて保存される。

【0047】

RAM_No.4(RAM_LINE)には、配置されるすべてのライン定義のライン定義番号を保存している。ライン定義番号を保存する際も上記と同様に、ライン定義番号を順番に並べて保存し、ライン定義番号とライン定義番号との間で行が変わる場合(ゾーンが変わる場合)は、行が変わったことを示す(ゾーンが変わったことを示す)ターミネータ情報をライン定義番号とライン定義番号との間に入れて保存する。具体的には、たとえば図1に示す簡易パターンファイル100のライン配置部102において定義されたライン配置に基づいて、配置されるライン定義のライン定義番号を保存する場合、RAM_No.4(RAM_LINE)には、ライン定義番号が「1,ターミネータ情報,0,2,3,2,3,2,0,ターミネータ情報,0,…」と順番に並べられて保存される。

【0048】

RAM_No.5(RAM_LINE_NUM)には、配置されるすべてのライン定義の繰り返し回数を保存している。ライン定義の繰り返し回数を保存する際も上記と同様に、定義されたライン定義の繰り返し回数を順番に並べて保存し、ゾーンが変わる場合には、ゾーンが変わったことを示すターミネータ情報を繰り返し回数と繰り返し回数との間に入れて保存する。具体的には、たとえば図1に示すライン配置部102において定義されたライン配置に基づいて、配置されるライン定義の繰り返し回数を保存する場合、RAM_No.5(RAM_LINE_NUM)には、繰り返し回数が「9685,ターミネータ情報,9525,4,34,4,34,4,80,ターミネータ情報,9525,…」と順番に並べられて保存される。

【0049】

RAM_No.6(RAM_REPEAT_Y)には、配置されるすべてのゾーンユニットの繰り返し回数を保存している。ゾーンユニットの繰り返し回数を保存する際も上記と同様に、ゾーンユニットの繰り返し回数を順番に並べて保存する。また、ゾーンユニットの繰り返し回数を順番に並べた最後の部分には、ターミネータ情報を入れて保存する。具体的には、たとえば図1に示すライン配置部102において定義されたライン配置に基づいて、配置されるゾーンユニットの繰り返し回数を保存する場合、RAM_No.6(RAM_REPEAT_Y)には、繰り返し回数が「1,1,1,1,ターミネータ情報」と順番に並べられて保存される。

【0050】

RAM_No.7(RAM_BND_PULSE)には、ライン定義されているすべての画素値が保存されているRAM_No.1(RAM_PULSE)内にアクセスするためのアドレスが保存される。さらに、RAM_No.7(RAM_BND_PULSE)には、ライン定義されているすべての画素の繰り返し回数が保存されているRAM#No.2(RAM_PULSE_NUM)内にアクセスするためのアドレスが保存される。

【0051】

RAM_No.8(RAM_BND_REPEAT_X)には、ライン定義されているすべてのグループユニットの繰り返し回数が保存されているRAM_No.3(RAM_REPEAT_X)内にアクセスするためのアドレスが保存される。

【0052】

RAM_No.9(RAM_BND_LINE)には、配置されるすべてのライン定義のライン定義番号が保存されているRAM_No.4(RAM_LINE)内および配置されるすべてのライン定義の繰り返し回数が保存されているRAM_No.5(RAM_LINE_NUM)内にアクセスするためのアドレスが保存される。つぎに、具体的なサンプリングを例に挙げて簡易パターンファイル格納用内部RAM状態の説明をする。

【0053】

図8−1は、簡易パターンファイルのサンプルの一例を示す説明図である。また、図8−2は、図8−1に示す簡易パターンファイルを保存した場合の簡易パターンファイル格納用内部RAM状態を示すテーブルである。図8−1に示すように、簡易パターンファイル600のライン定義部601には、破線であらわされた2つのラインについてのライン定義が示されており、それぞれのライン定義を構成するグループが太線によってあらわされている。

【0054】

さらに、簡易パターンファイル600のライン配置部602には、一点鎖線であらわす3つのゾーンが示されている。また、図8−2には、FPGA内に設けられた9つの内部RAM620のそれぞれのRAMに保存されている内容がアドレス630と関連付けられて示されている。なお、図8−1に示す簡易パターンファイル600は、簡易パターンファイル格納用内部RAM状態の説明をおこなうために、図1に示す簡易パターンファイル100の一部を省略して示したものである。

【0055】

図8−2に示すRAM_No.1(RAM_PULSE)には、簡易パターンファイル600においてライン定義されているすべての画素値が保存されている。このとき、それぞれのアドレスには、1つの画素値が順番に保存されている。また、グループとグループとの間には、グループ間を区別するためのターミネータ情報を保存する。さらに、ライン定義されているすべての画素値が保存されたことを示すターミネータ情報を最後のアドレスに保存する。なお、ターミネータ情報を保存するアドレスには、ターミネータ情報を示す下線付きの「0」が示されている。また、デコード処理を一意化するために、アドレスNo.0には空行を示す「画素値0」が保存されており、アドレスNo.1には、ターミネータ情報が保存されている。

【0056】

また、RAM_No.2(RAM_PULSE_NUM)には、ライン定義されているすべての画素の繰り返し回数が保存されている。このとき、それぞれのアドレスには、1つの画素の繰り返し回数が順番に保存されている。また、グループとグループとの間には、グループ間を区別するためのターミネータ情報を保存する。さらに、ライン定義されているすべての画素の繰り返し回数が保存されたことを示すターミネータ情報を最後のアドレスに保存する。また、デコード処理を一意化するために、アドレスNo.0には空行を示すための画像幅が保存されており、アドレスNo.1には、ターミネータ情報が保存されている。なお、保存される画像幅は、後述する画像サイズ算出部424において計算される。

【0057】

つぎに、RAM_No.3(RAM_REPEAT_X)には、ライン定義されているすべてのグループユニットの繰り返し回数が保存されている。このとき、それぞれのアドレスには、1つのグループユニットの繰り返し回数が順番に保存されている。また、グループとグループとの間には、グループ間を区別するためのターミネータ情報を保存する。さらに、ライン定義されているすべてのグループユニットの繰り返し回数が保存されたことを示すターミネータ情報を最後のアドレスに保存する。また、デコード処理を一意化するために、アドレスNo.0には空行を示すための繰り返し回数「1」が保存されており、アドレスNo.1には、ターミネータ情報が保存されている。

【0058】

また、RAM_No.4(RAM_LINE)には、配置されるすべてのライン定義のライン定義番号が保存されている。このとき、それぞれのアドレスには、1つのライン定義番号が順番に保存されている。また、ゾーンとゾーンとの間には、ゾーン間を区別するためのターミネータ情報を保存する。さらに、配置されるすべてのライン定義のライン定義番号が保存されたことを示すターミネータ情報を最後のアドレスに保存する。

【0059】

つぎに、RAM_No.5(RAM_LINE_NUM)には、配置されるすべてのライン定義の繰り返し回数が保存されている。このとき、それぞれのアドレスには、1つのライン定義の繰り返し回数が順番に保存されている。また、ゾーンとゾーンとの間には、ゾーン間を区別するためのターミネータ情報を保存する。さらに、配置されるすべてのライン定義におけるライン定義の繰り返し回数が保存されたことを示すターミネータ情報を最後のアドレスに保存する。

【0060】

また、RAM_No.6(RAM_REPEAT_Y)には、配置されるすべてのゾーンユニットの繰り返し回数が保存されている。このとき、それぞれのアドレスには、1つのゾーンユニットの繰り返し回数が順番に保存されている。また、配置されるすべてのゾーンユニットの繰り返し回数が保存されたことを示すターミネータ情報を最後のアドレスに保存する。

【0061】

つぎに、RAM_No.7(RAM_BND_PULSE)には、RAM_No.1(RAM_PULSE)およびRAM_No.2(RAM_PULSE_NUM)内のいずれかに保存されているデータにアクセスするためのアドレスを保存している。たとえば、ライン定義「X」のデータにアクセスするためには、RAM_No.7(RAM_BND_PULSE)内のアドレス「X」に保存している値が、RAM_No.1(RAM_PULSE)およびRAM_No.2(RAM_PULSE_NUM)におけるライン定義「X」の先頭アドレスとなる。

【0062】

また、RAM_No.8(RAM_BND_REPEAT_X)には、RAM_No.3(RAM_REPEAT_X)内に保存されているデータにアクセスするためのアドレスを保存している。たとえば、ライン定義「X」のデータにアクセスするためには、RAM_No.8(RAM_BND_REPEAT_X)のアドレス「X」に保存されている値が、RAM_No.3(RAM_REPEAT_X)におけるライン定義「X」の先頭アドレスとなる。

【0063】

つぎに、RAM_No.9(RAM_BND_LINE)には、RAM_No.4(RAM_LINE)およびRAM_No.5(RAM_LINE_NUM)内に保存されているデータにアクセスするためのアドレスを保存している。たとえば、ゾーン「X」のデータにアクセスするためには、RAM_No.9(RAM_BND_LINE)のアドレス「X」に保存されている値が、RAM_No.4(RAM_LINE)およびRAM_No.5(RAM_LINE_NUM)におけるゾーン「X」の先頭アドレスとなる。

【0064】

ここで、図8−1および図8−2を用いて、ライン定義2(603)の3個目の画素値「63」にアクセスする場合について説明する。まず、ライン定義2(603)の先頭アドレスとしてRAM_No.7(RAM_BND_PULSE)内のアドレス「2」に保存されている「5」を取得する。

【0065】

つぎに、ライン定義2(603)の3個目の画素値「63」にアクセスするため、先頭アドレス「5」に2(3−1=2)を加算する。これにより、算出された「7」の値がライン定義2(603)の3個目の画素値「63」のアドレスとなる。そして、このアドレス「7」をRAM_No.1(RAM_PULSE)に指定し、RAM_No.1(RAM_PULSE)のアドレス「7」から画素値「63」を取得する。つぎに、上述した簡易パターンファイルのデコード処理を実行するFPGAの機能的構成について説明する。

(FPGAの機能的構成)

図9は、この発明の実施の形態にかかるFPGAの機能的構成を示すブロック図である。図9に示すように、FPGAは、モジュール内メモリ422と、画像サイズ算出部424と、デコーダ421と、出力制御部423とを含む構成となっている。先のFPGA内に設けられた簡易パターンファイル格納用内部RAMは、モジュール内メモリ422の構成の一部である。

【0066】

モジュール内メモリ422は、フラッシュメモリに格納されている簡易パターンファイルの行方向への読み込みを、インデックステーブル412を参照しておこない、読み込まれた簡易パターンファイルを読み込まれた順に、簡易パターンファイルに含まれる種別ごとに異なる記憶領域に振り分けて保存する。このとき、簡易パターンファイルの行が変わる部分には、当該行が変わることを示す付加情報(ターミネータ情報)をあわせて保存する。具体的には、モジュール内メモリ422は、簡易パターンファイルを読み込んで、FPGA内に設けられた簡易パターンファイル格納用内部RAMの複数の内部RAMにテーブル形式で保存する。

【0067】

画像サイズ算出部424は、FPGA内の内部RAMに保存されているデータに基づいて、簡易パターンファイルの画像サイズを算出する。具体的には、画像サイズ算出部424は、FPGA内に設けられた内部RAMから簡易パターンファイルを読み出し、読み出した簡易パターンファイルの画像の幅を算出するとともに、画像の高さを算出する。また、画像の高さは、画像の色ごとに(たとえば、C(シアン),M(マゼンタ),Y(イエロー),K(ブラック))、それぞれ算出する。

【0068】

デコーダ421は、モジュール内メモリ422によって保存されている簡易パターンファイルを、画像を形成するための順序にしたがって、付加情報であるターミネータ情報とあわせて簡易パターンファイル格納用内部RAMの複数の内部RAMから読み出す。そして、読み出された簡易パターンファイルを、付加情報であるターミネータ情報とあわせて画像の主走査方向のラインごとに連続してデコード処理する。

【0069】

出力制御部423は、デコーダ421によってデコード処理された簡易パターンファイルをFPGA内に設けられた図示しないビデオメモリへ、付加情報であるターミネータ情報とあわせて画像の主走査方向のラインごとに連続的に出力する。ここで、ビデオメモリとは、FPGA内に設けられた記憶領域であり、ビデオメモリに格納されたデータは、古いデータ(一番始めに格納されたデータ)から順に読み出される。つぎに、フラッシュメモリから読み出した簡易パターンファイルがヘッドモジュール430に転送されるまでの間に、FPGAが簡易パターンファイルに対しておこなう処理の内容について説明する。

(FPGAの画像データ処理手順)

図10は、この発明の実施の形態にかかるFPGAの処理の手順を示すフローチャートである。図10のフローチャートにおいて、まず、操作基板401から印刷開始を示す信号が通知された場合、FPGAのモジュール内メモリ422は、フラッシュメモリに格納されている簡易パターンファイルを読み込んで、FPGA内に設けられた複数の簡易パターンファイル格納用内部RAMにテーブル形式で保存する(ステップS801)。

【0070】

つぎに、画像サイズ算出部424は、FPGA内の内部RAMに格納されているデータに基づいて、簡易パターンファイルの画像サイズを算出する(ステップS802)。そして、デコーダ421は、FPGA内の内部RAMに格納されているデータに基づいて、簡易パターンファイルに対するデコード処理を実行する(ステップS803)。

【0071】

最後に、デコーダ421によってデコード処理された簡易パターンファイルをFPGA内に設けられたビデオメモリへ出力して(ステップS804)、本フローチャートによる一連の処理を終了する。つぎに、ステップS801において、モジュール内メモリ422がフラッシュメモリから読み込んだ簡易パターンファイルを、FPGA内に設けられた簡易パターンファイル格納用内部RAMに保存する際の処理について詳細に説明する。

【0072】

図11−1および図11−2は、FPGAのモジュール内メモリがおこなう処理の手順を示すフローチャートである。図11−1のフローチャートにおいて、まず、FPGAのモジュール内メモリ422は、フラッシュメモリに格納されている簡易パターンファイルの1行分のデータを読み込む(ステップS901)。具体的には、簡易パターンファイル100(図1参照、以下同様。)の行方向への読み込みを連続して、上から順に1行ずつ(1行目、2行目、…)おこなう。

【0073】

そして、モジュール内メモリ422は、読み込んだ1行が空行か否かを判断する(ステップS902)。具体的には、たとえばモジュール内メモリ422は、簡易パターンファイル100の5行目を読み込んだ場合に、空行であると判断する。ここで、読み込んだ1行が空行ではなかった場合(ステップS902:No)は、つぎに、読み込んだ1行分のデータに基づいて、グループユニットの繰り返し回数を保存する(ステップ903)。具体的には、たとえばステップS901において簡易パターンファイル100の2行目を読み込んだ場合、グループユニットの繰り返し回数を「1」と判断し、FPGAの所定の内部RAMにグループユニットの繰り返し回数「1」を保存する。

【0074】

つぎに、モジュール内メモリ422は、新たに簡易パターンファイルの1行分のデータを読み込む(ステップS904)。そして、モジュール内メモリ422は、読み込んだ1行分のデータに基づいて、グループの画素値を保存する(ステップS905)。具体的には、たとえばステップS904において簡易パターンファイル100の2行目を読み込んだ場合、グループの画素値を「0,63,0」と判断し、FPGAの所定の内部RAMに画素値を「0,63,0」と順に並べて保存する。

【0075】

ここで、グループ内(読み込んだ1行分)の画素値をすべて保存した場合、モジュール内メモリ422は、ターミネータ情報を追加して保存する(ステップS906)。つぎに、モジュール内メモリ422は、また新たに簡易パターンファイルの1行分のデータを読み込む(ステップS907)。そして、モジュール内メモリ422は、読み込んだ1行分のデータに基づいて、グループの画素値の繰り返し回数を保存する(ステップS908)。具体的には、たとえば簡易パターンファイル100の3行目を読み込んだ場合、グループの画素値の繰り返し回数を「118,6780,118」と判断し、FPGAの所定の内部RAMにグループの画素値の繰り返し回数を「118,6780,118」と順に並べて保存する。

【0076】

ここで、グループ内(読み込んだ1行分)の画素値の繰り返し回数をすべて保存した場合、モジュール内メモリ422は、ターミネータ情報を追加して保存し(ステップS909)、ステップS901に戻り、本フローチャートによる一連の処理を繰り返す。

【0077】

また、ステップS902において、読み込んだ1行が空行であると判断された場合、モジュール内メモリ422は、新たに簡易パターンファイルの1行分のデータを読み込む(ステップS910)。そして、モジュール内メモリ422は、ステップS902およびステップS910において読み込んだ2行分のデータに基づいて、連続して空行か否かを判断する(ステップS911)。

【0078】

ここで、連続して空行ではないと判断された場合、モジュール内メモリ422は、ターミネータ情報を追加して保存し(ステップS912)、ステップS903に移行し、本フローチャートによる一連の処理をおこなう。また、ステップS911において、連続して空行であると判断された場合は、モジュール内メモリ422は、ライン定義の読み込みが終了したと判断し、図11−2に示すステップS921に移行する。

【0079】

図11−2に示すフローチャートのステップS921において、モジュール内メモリ422は、新たに簡易パターンファイルの1行分のデータを読み込む(ステップS921)。具体的には、たとえば簡易パターンファイル100のライン配置部102の最初の行である34行目を読み込む。つぎに、モジュール内メモリ422は、読み込んだ1行分のデータに基づいて、1色分の開始ゾーンを内部RAMに保存し(ステップS922)、1色分の終了ゾーンを内部RAMに保存する(ステップS923)。具体的には、簡易パターンファイル100の34行目を読み込んだ場合、1色分の開始ゾーンを「1」として保存し、1色分の終了ゾーンを「1」として保存する。

【0080】

そして、モジュール内メモリ422は、すべての色について開始ゾーンおよび終了ゾーンが保存されたか否かを判断する(ステップS924)。具体的には、簡易パターンファイル100の34行目に示されている4色分すべての開始ゾーンおよび終了ゾーンを保存したか否かを判断する。ここで、すべての色について開始ゾーンおよび終了ゾーンが保存されていない場合(ステップS924:No)は、ステップS922に戻り、一連の処理を繰り返す。

【0081】

また、すべての色について開始ゾーンおよび終了ゾーンが保存された場合(ステップS924:Yes)、モジュール内メモリ422は、新たに簡易パターンファイルの1行分のデータを読み込む(ステップS925)。そして、すべての簡易パターンファイルの読み込みが終了したか否かを判断する(ステップS926)。ここで、読み込みが終了していないと判断された場合(ステップS926:No)は、ステップS925において読み込んだ1行分のデータに基づいて、ゾーンユニットの繰り返し回数を保存する(ステップS927)。

具体的には、たとえば簡易パターンファイル100の35行目を読み込んだ場合、ゾーンユニットの繰り返し回数を「1」と判断し、所定の内部RAMにゾーンユニットの繰り返し回数「1」を保存する。

【0082】

つぎに、モジュール内メモリ422は、新たに簡易パターンファイルの1行分のデータを読み込む(ステップS928)。そして、モジュール内メモリ422は、読み込んだ1行分のデータに基づいて、ゾーンのライン定義番号を保存する(ステップS929)。具体的には、たとえば簡易パターンファイル100の39行目を読み込んだ場合、ゾーンのライン定義番号を「0,2,3,2,3,2,0」と判断し、内部RAMにゾーンのライン定義番号「0,2,3,2,3,2,0」を保存する。

【0083】

ここで、ゾーン内(読み込んだ1行分)のライン定義番号をすべて保存した場合、モジュール内メモリ422は、ターミネータ情報を追加して保存する(ステップS930)。つぎに、モジュール内メモリ422は、新たに簡易パターンファイルの1行分のデータを読み込む(ステップS931)。そして、モジュール内メモリ422は、読み込んだ1行分のデータに基づいて、ゾーンのライン定義の繰り返し回数を保存する(ステップS932)。具体的には、たとえば簡易パターンファイル100の40行目を読み込んだ場合、ゾーンのライン定義の繰り返し回数を「9525,4,34,4,34,4,80」と判断し、内部RAMにゾーンのライン定義の繰り返し回数「9525,4,34,4,34,4,80」を保存する。

【0084】

ここで、グループ内(読み込んだ1行分)のゾーンのライン定義の繰り返し回数をすべて保存した場合、モジュール内メモリ422は、ターミネータ情報を追加して保存し(ステップS933)、つぎに、ステップS925に戻り、本フローチャートによる一連の処理を繰り返す。また、ステップS926において、読み込みが終了したと判断された場合(ステップS926:Yes)は、本フローチャートによる一連の処理を終了する。

【0085】

つぎに、図10に示すフローチャートのステップS802において、画像サイズ算出部424がFPGA内の内部RAMに保存されているデータに基づいて、簡易パターンファイルの画像サイズを算出する際の処理について詳細に説明する。

【0086】

図12−1は、FPGAの画像サイズ算出部がおこなう幅算出処理の手順を示すフローチャートである。また、図12−2は、FPGAの画像サイズ算出部がおこなう高さ算出処理の手順を示すフローチャートである。図12−1のフローチャートにおいて、まず、FPGAの画像サイズ算出部424は、FPGAの簡易パターンファイル格納用内部RAMに保存されている画素値の繰り返し回数およびグループユニットの繰り返し回数を読み出す(ステップS1001)。具体的には、図8−2に示す簡易パターンファイル格納用内部RAM状態を示すテーブルに示すように、RAM_No.2に保存されている画素値の繰り返し回数を読み出し、RAM_No.3に保存されているグループユニットの繰り返し回数を読み出す。

【0087】

つぎに、画像サイズ算出部424は、グループユニットの繰り返し回数がターミネータ情報か否かを判断する(ステップS1002)。具体的には、画像サイズ算出部424は、ステップS1001において読み出したグループユニットの繰り返し回数が下線付きの「0」であるか否かを判断し、下線付きの「0」であった場合にターミネータ情報であると判断する。

【0088】

ここで、グループユニットの繰り返し回数がターミネータ情報ではなかった場合(ステップS1002:No)は、つぎに、画素値の繰り返し回数がターミネータ情報か否を判断する(ステップS1003)。具体的には、画像サイズ算出部424は、ステップS1001において読み出した画素値の繰り返し回数が下線付きの「0」であるか否かを判断し、下線付きの「0」であった場合にターミネータ情報であると判断する。

【0089】

そして、画素値の繰り返し回数がターミネータ情報であった場合(ステップS1003:Yes)は、画像サイズ算出部424は、画素数カウント値およびグループユニットの繰り返し回数の乗算結果を幅に加算する(ステップS1004)。つぎに、画像サイズ算出部424は、画素数カウント値をリセットし(ステップS1005)、グループユニットの繰り返し回数のアドレスをつぎのアドレスに移行する(ステップS1006)。

【0090】

さらに、画像サイズ算出部424は、画素値の繰り返し回数のアドレスをつぎのアドレスに移行し(ステップS1007)、つぎに、ステップS1001に戻り、本フローチャートによる一連の処理を繰り返す。また、ステップS1003において、画素値の繰り返し回数がターミネータ情報ではなかった場合(ステップS1003:No)は、画像サイズ算出部424は、画素数カウント値を更新し(ステップS1008)、ステップS1007に移行する。

【0091】

また、ステップS1002において、グループユニットの繰り返し回数がターミネータ情報であった場合(ステップS1002:Yes)は、画像サイズ算出部424は、画像の幅をすべて算出したと判断して、本フローチャートによる一連の処理を終了する。

【0092】

つぎに、画像サイズ算出部424がおこなう画像の高さを算出する処理について図12−2を用いて説明する。図12−2のフローチャートにおいて、まず、FPGAの画像サイズ算出部424は、モジュール内メモリ422によってFPGAの簡易パターンファイル格納用内部RAMに保存されているライン定義の繰り返し回数およびゾーンユニットの繰り返し回数を読み出す(ステップS1020)。具体的には、図8−2に示すRAM_No.5に保存されているライン定義の繰り返し回数を読み出し、RAM_No.6に保存されているゾーンユニットの繰り返し回数を読み出す。

【0093】

そして、画像サイズ算出部424は、すべての色についてライン定義の繰り返し回数およびゾーンユニットの繰り返し回数の読み出しが終了したか否かを判断する(ステップS1021)。ここで、すべての色について読み出しが終了していない場合(ステップS1021:No)、画像サイズ算出部424は、1色分のライン定義の繰り返し回数およびゾーンユニットの繰り返し回数の読み出しが終了したか否かを判断する(ステップS1022)。

【0094】

ここで、1色分の読み出しが終了していない場合(ステップS1022:No)、画像サイズ算出部424は、ライン定義の繰り返し回数がターミネータ情報か否かを判断する(ステップS1023)。そして、ライン定義の繰り返し回数がターミネータ情報ではなかった場合(ステップS1023:No)、画像サイズ算出部424は、高さカウント値を更新する(ステップS1024)。具体的には、画像サイズ算出部424は、画像の高さにライン定義の繰り返し回数を加算する。

【0095】

そして、画像サイズ算出部424は、ライン定義の繰り返し回数のアドレスをつぎのアドレスに移行し(ステップS1025)、ステップS1020に戻り、本フローチャートによる一連の処理を繰り返す。また、ステップS1021において、すべての色について読み出しが終了した場合(ステップS1021:Yes)は、本フローチャートによる一連の処理を終了する。

【0096】

さらに、ステップS1023において、ライン定義の繰り返し回数がターミネータ情報であった場合(ステップS1023:Yes)、画像サイズ算出部424は、高さカウント値とゾーンユニットの繰り返し回数との乗算結果を画像の高さに加算する(ステップS1026)。そして、画像サイズ算出部424は、高さカウント値をリセットする(ステップS1027)。つぎに、画像サイズ算出部424は、ゾーンユニットの繰り返し回数のアドレスをつぎのアドレスに移行し(ステップS1028)、ステップS1025に移行する。

【0097】

また、ステップS1022において、1色分の読み出しが終了したと判断された場合(ステップS1022:Yes)、画像サイズ算出部424は、色番号の更新をおこない(ステップS1029)、ステップS1027に移行する。

【0098】

つぎに、図10に示すフローチャートのステップS803において、デコーダ421がFPGA内の内部RAMに格納されているデータに基づいて、簡易パターンファイルに対するデコード処理を実行し、デコード処理をおこなった簡易パターンファイルをFPGA内に設けられたビデオメモリへ出力する際の処理について詳細に説明する。

【0099】

図13は、FPGAのデコーダがおこなう処理の手順を示すフローチャートである。図13のフローチャートにおいて、まず、FPGAのデコーダ421は、FPGAの簡易パターンファイル格納用内部RAMに保存されている1色分の開始ゾーン番号および終了ゾーン番号を取得する(ステップS1101)。つぎに、デコーダ421は、取得したゾーン内の先頭ライン定義番号を取得する(ステップS1102)。これにより、デコーダ421は、ライン定義されている画素値にアクセスすることができる。

【0100】

そして、デコーダ421は、内部RAMから画素値を読み出す(ステップS1103)。具体的には、図8−2に示すRAM_No.1に保存されている画素値を読み出す。つぎに、デコーダ421は、読み出した画素値を出力する(ステップS1104)。このとき、デコーダ421は、画素値の繰り返し回数を判断し、それぞれの画素値の繰り返し回数分、FPGA内に設けられたビデオメモリへ出力する。たとえば、デコーダ421は、図8−2に示すRAM_No.2から読み出した画素値の繰り返し回数に基づいて、繰り返し回数分出力したか否かを判断する。

【0101】

ここで、デコーダ421は、画素値を画素値の繰り返し回数分、ビデオメモリへ出力したか否かを判断する(ステップS1105)。そして、すべて出力した場合(ステップS1105:Yes)は、つぎに、デコーダ421は、1つのグループユニット内のすべての画素値の出力が終了したか否かを判断する(ステップS1106)。また、ステップS1105において、画素値を画素値の繰り返し回数分出力していない場合(ステップS1105:No)は、ステップS1103に戻り、本フローチャートによる一連の処理を繰り返す。

【0102】

ステップS1106において、1つのグループユニット内のすべての画素値の出力が終了した場合(ステップS1106:Yes)、デコーダ421は、グループユニットの繰り返しが終了したか否かを判断する(ステップS1107)。具体的には、たとえばデコーダ421は、図8−2に示すRAM_No.3から読み出したグループユニットの繰り返し回数に基づいて、グループユニットの繰り返し回数が終了したか否かを判断する。

【0103】

また、1つのグループユニット内のすべての画素値の出力が終了していない場合(ステップS1106:No)、ステップS1103に戻り、本フローチャートによる一連の処理を繰り返す。

【0104】

ステップS1107において、グループユニットの繰り返しが終了するのを待って、終了した場合(ステップS1107:Yes)、つぎに、デコーダ421は、1ライン分(1つのライン定義)の画素値の出力が終了したか否かを判断する(ステップS1108)。ここで、1ライン分の画素値の出力が終了した場合(ステップS1108:Yes)、つぎに、デコーダ421は、ライン定義の繰り返しが終了したか否かを判断する(ステップS1109)。また、ステップS1108において、1ライン分の画素値の出力が終了していないと判断された場合(ステップS1108:No)は、ステップS1103に戻り、本フローチャートによる一連の処理を繰り返す。

【0105】

ステップS1109においてライン定義の繰り返しが終了するのを待って、繰り返しが終了した場合(ステップS1109:Yes)、1つのゾーンユニット内のすべてのライン定義の繰り返しが終了したか否かを判断する(ステップS1110)。具体的には、たとえばデコーダ421は、図8−2に示すRAM_No.4およびRAM_No.5からライン定義番号およびライン定義の繰り返し回数を読み出す。そして、デコーダ421は、読み出したライン定義番号およびライン定義の繰り返し回数に基づいて、1つのゾーンユニット内に配置されている順にそれぞれのライン定義の繰り返しが終了したか否かを判断するとともに、ゾーンユニット内のすべてのライン定義の繰り返しが終了したか否かを判断する。

【0106】

ここで、1つのゾーンユニット内のすべてのライン定義の繰り返しが終了したと判断された場合(ステップS1110:Yes)は、デコーダ421は、ゾーンユニットの繰り返しが終了したか否かを判断する(ステップS1111)。具体的には、たとえばデコーダ421は、図8−2に示すRAM_No.6から読み出したゾーンユニットの繰り返し回数に基づいて、ゾーンユニットの繰り返しが終了したか否かを判断する。

【0107】

そして、ゾーンユニットの繰り返しが終了するのを待って、繰り返しが終了した場合(ステップS1111:Yes)は、1色分についての画素値の出力が終了したか否かを判断する(ステップS1112)。具体的には、ステップS1101において取得した1色分の開始ゾーン番号および終了ゾーン番号に基づいて、1色分についての画素値の出力が終了したか否かを判断する。

【0108】

ここで、1色分についての画素値の出力が終了した場合(ステップS1112:Yes)、本フローチャートによる一連の処理を終了する。なお、たとえば簡易パターンファイル100に示すように、4色分のライン配置が定義されている場合には、デコーダ421は、4色分のすべてについて上述した一連の処理と同様の処理をおこなう。また、ステップS1112において、1色分についての画素値の出力が終了していない(ステップS1112:No)、ステップS1103に戻り、本フローチャートによる一連の処理を繰り返す。

【0109】

図13のフローチャートで説明したデコーダ421がおこなう処理は、リアルタイムでおこなう必要があるため、デコーダ421は、たとえばつぎのような制約に基づいて上記処理をおこなうようにしてもよい。デコーダ421は、図13のステップS1103において、RAM_No.1に保存されている画素値を読み出す際には、複数の内部RAMからのデータの読み出しを連続的におこなっている。ここで、デコーダ421が画素値を読み出す際の詳細な説明を図14を用いて説明する。

【0110】

図14は、ラインの先頭の画素値を読み出すまでのクロック数を示す説明図である。図14に示すように、ラインの先頭の画素値を読み出す際には、まず、デコーダ421は、図14中矢印Aで示す1クロック目にRAM_No.9(RAM_BND_LINE)に対してゾーン番号を指定する。このとき、指定するゾーン番号は、たとえば、図11のフローチャートのステップS1101において取得した開始ゾーン番号などである。

【0111】

つぎに、デコーダ421は、図14中矢印Bで示す2クロック目にRAM_No.9(RAM_BND_LINE)から1クロック目に指定したゾーン番号の先頭アドレスを取得して、取得した先頭アドレスをRAM_No.4(RAM_LINE)に対して指定する。そして、デコーダ421は、図12中矢印Cで示す3クロック目にRAM_No.4(RAM_LINE)から2クロック目に指定した先頭アドレスに応じたライン定義番号を取得して、取得したライン定義番号をRAM_No.7(RAM_BND_PULSE)に対して指定する。

【0112】

つぎに、デコーダ421は、図14中矢印Dで示す4クロック目にRAM_No.7(RAM_BND_PULSE)から3クロック目に指定したライン定義番号の先頭アドレスを取得して、取得したライン定義番号の先頭アドレスをRAM_No.1(RAM_PULSE)に対して指定する。そして、デコーダ421は、図14中矢印Eで示す5クロック目にRAM_No.1(RAM_PULSE)から4クロック目に指定したライン定義番号に応じたラインの画素値を取得する。

【0113】

以上説明したように、ラインの先頭の画素値を取得(読み出す)するには、ライン間において5クロック分の待ち時間(待ちクロック)が必要となる。このため、デコーダ421によって連続して出力されるラインとラインとの間に、つぎのラインの先頭画素にアクセスするまでの期間相当分のクロック(待ちクロック)を設定する。これにより、ラインが変わる際に、ラインの先頭の画素値を読み出す際に必要となる5クロック分のクロック差により、印刷出力するためのデコード処理が追いつかず、ヘッドモジュール430において印刷出力するときの画像が途中で途切れてしまうなどの不具合を防ぐことができる。

【0114】

なお、同一ラインにおける画素値の読み出しをおこなう際は、デコーダ421は、RAM_No.1(RAM_PULSE)に対して順にアドレスを指定して、指定した順に画素値を読み出していけばよいため、図12に示すような複数の内部RAMからのデータの読み出しを連続的におこなう必要はない。

【0115】

このため、同一ラインにおけるすべての画素値の読み出しをおこなう際において、最初の画素値を読み出した以降は、RAM_No.1(RAM_PULSE)のアドレスのみを更新することによってリアルタイムに画素値を読み出すことができる。具体的には、画素値の繰り返し回数の最後の画素値を読み出すクロックと同クロックにおいて、RAM_No.1(RAM_PULSE)のアドレスを更新することによって連続して1つのライン分の画素値を読み出すことができる。

【0116】

しかしながら、読み出したデータがグループが変わったことを示すターミネータ情報であった場合には、ターミネータ情報を読み出したクロックと同一クロックにおいて出力すべき画素値の読み出しをおこなうことができないため、連続して1ライン分の画素値を読み出すことができなくなってしまう。ここで、ターミネータ情報を読み出してしまうことによって、連続して1ライン分の画素値を読み出すことができない場合の一例を図13を用いて説明する。

【0117】

図15は、連続して1ライン分の画素値を読み出すことができない場合の一例を示す説明図である。図15に示す読み出し例は、図2−1に示すライン定義に基づいて画素値を出力した場合の読み出し例である。図15に示すように、デコーダ421は、図13中矢印Aで示すクロックにおいて、図2に示すペア1(211)の118個目の画素値「0」を読み出し、RAM_No.1(RAM_PULSE)のアドレスを1つ加算(更新)する。つぎに、デコーダ421は、図2に示すペア2(212)の1個目の画素値「0」を読み出す。このとき、デコーダ421は、RAM_No.1(RAM_PULSE)のアドレスを更新しない。

【0118】

そして、デコーダ421は、ペア2(212)の画素値を順に読み出し、図15中矢印Bで示すクロックにおいて、ペア2(212)の80個目画素値「0」を読み出し、RAM_No.1(RAM_PULSE)のアドレスを1つ加算(更新)する。つぎに、デコーダ421は、図15中矢印Cで示すクロックにおいて、図2に示すペア3(213)の1個目の画素値「63」を読み出す。このとき、デコーダ421は、RAM_No.1(RAM_PULSE)のアドレスを更新しない。

【0119】

そして、デコーダ421は、ペア3(213)の画素値を順に読み出し、図15中矢印Eで示すクロックにおいて、ペア3(213)の4個目画素値「63」を読み出し、RAM_No.1(RAM_PULSE)のアドレスを1つ加算(更新)する。つぎに、デコーダ421は、図15中矢印Fで示すクロックにおいて、図2に示すペア4(221)の1個目の画素値「0」を読み出す必要があるのだが、ターミネータ情報を読み出してしまう。

【0120】

このため、ターミネータ情報を読み出したクロックと同一クロックにおいて出力すべきペア4(221)の1個目の画素値「0」の読み出しをおこなうことができないため、連続して1ライン分の画素値を読み出すことができない。この不具合を防ぐために、FPGAに設けられている簡易パターンファイル格納用内部RAMをデュアルポートRAMとし、デコーダ421は、リアルタイムに出力するための画素値(着目アドレスの画素値)を読み出すとともに、1つ先のアドレス(着目アドレスに「1」を加算したアドレス)の画素値および画素値の繰り返し回数を読み出すようにする。

【0121】

ここで、デュアルポートRAMとは、データの入出力のための信号のポート(出入口)が2つ設けられたRAMのことであり、1つのポートからデータを読み出すとともに、同時にもう一方のポートからデータを読み出すことができる。このとき、新たな記憶領域である内部RAMをさらに設け、この内部RAMに余分に読み出したデータを一時保存するようにしてもよい。そして、デコーダ421は、デュアルポートRAMから読み出したデータを用いて、アドレスを更新するか否かを判断するようにしてもよい。

【0122】

また、デコーダ421は、着目アドレスの画素値を繰り返し回数分読み出した際に、つぎのようにアドレスを更新する。デコーダ421は、読み出されたデータ(パターンデータ)に、付加情報であるターミネータ情報が含まれているか否かを判断する。そして、デコーダ421は、上記判断結果に基づいて、読み出されたデータを出力する。

【0123】

具体的には、デコーダ421は、着目アドレスのつぎのアドレスのデータがターミネータ情報か否を判断する。そして、着目アドレスのつぎのアドレスのデータがターミネータ情報ではなかった場合には、デコーダ421は、アドレスを「着目アドレス+1」に更新する。また、たとえば着目アドレスのつぎのアドレスのデータがターミネータ情報であった場合は、グループユニットの繰り返しが終了しているか否かによってアドレスの更新方法が異なる。

【0124】

まず、グループユニットの繰り返しが終了していなかった場合、デコーダ421は、現在出力中のグループユニットの先頭アドレスにアドレスを更新する。つぎに、グループユニットの繰り返しが終了している場合、デコーダ421は、つぎのグループユニットの先頭アドレス(着目アドレス+2)にアドレスを更新する。

【0125】

したがって、デコーダ421は、アドレスを更新する際に、その時点でどのようにアドレスを更新すればよいのかを把握しておく必要がある。このため、デコーダ421は、アドレスの更新をおこなうクロックの1つ前のクロックにおいて、更新方法を示すフラグを状態に応じてアドレスを更新する。なお、フラグのON/OFFの制御は、デコーダ421がそれぞれの画素値の繰り返し回数をカウントしながら判断するようにしてもよい。

【0126】

図16は、アドレス更新方法フラグの内容を示す説明図である。図16に示すアドレス更新表1400には、フラグ名称1401、フラグ名称が示す状態1402およびフラグがONになる条件1403が示されている。なお、図16に示す各フラグは、同時にONになる場合もあるが、アドレス更新表1400に示すフラグ名称1401の最上行から順に優先順位が付されている。このため、たとえば複数のフラグがONとなった場合、デコーダ421は、最も優先度が高いフラグのみをONにするようにしてもよい。

【0127】

ここで、デコーダ421によってフラグがONに制御される際の一例を説明する。たとえば、読み出した画素値のカウント値が「画素値の繰り返し回数−1」となった場合、具体的には、画素値を「繰り返し回数−1」分出力した際に、デコーダ421は、PixRepEndフラグ1404をONにする。

【0128】

上述したように、デコーダ421は、リアルタイムに画素値を出力するために、着目アドレスと着目アドレスに「1」を加算したアドレスに関するデータは常に読み出しておく必要がある。しかしながら、デコーダ421によってつぎのアドレスに関するデータを読み出して把握していたとしても、ターミネータ情報のつぎの画素値の繰り返し回数が「1」であった場合には、つぎのような問題が発生してしまう。

【0129】

図17は、簡易パターンファイルのライン定義の一例を示す図である。また、図18は、連続して1ライン分の画素値を読み出すことができない場合の一例を示す説明図である。図18に示す読み出し例は、図17に示すライン定義に基づいて画素値を出力した場合の読み出し例である。図18中矢印Aで示すクロックにおいて、デコーダ421は、図17に示すペア1503の3個目の画素値「63」を読み出すとともに、つぎのアドレスのデータであるターミネータ情報1504を把握している。このとき、図16に示すPixRepEndフラグ1404がONとなる。

【0130】

また、図18中矢印Bで示すクロックにおいて、デコーダ421は、ペア1503の4個目の画素値「63」を読み出すとともに、つぎのアドレスのデータであるターミネータ情報1504を把握している。このとき、PixRepEndフラグ1404がONであり、かつ、つぎのデータがターミネータ情報1504であるため、アドレスを「着目アドレス+2」に更新する。そして、図中16中矢印Cで示すクロックにおいて、デコーダ421は、ペア1504の1個目の画素値「0」を読み出すとともに、つぎのアドレスへの更新をおこなう。

【0131】

しかしながら、図18中矢印Cで示すクロックにおいて、アドレス変更方法が不定のため、つぎのアドレスへの更新をおこなうことができず、連続して1つのライン分の画素値を読み出すことができなくなってしまう問題が生じる。この問題は、ターミネータ情報1504のつぎのデータが事前にわかっていないために発生する問題であるため、つぎのような対策をすることによって解決することができる。

【0132】

たとえば、RAM_No.2(RAM_PULSE_NUM)に保存されているデータと同じデータを保存する別の内部RAMを設ける(たとえばRAM_No.10(RAM_PULSE_NUM)とする。)。そして、デコーダ421は、RAM_No.2(RAM_PULSE_NUM)に「着目アドレス」を指定して、「着目アドレス」のデータおよび「着目アドレス+1」のデータを読み出す。また、同時にデコーダ421は、RAM_No.10(RAM_PULSE_NUM)に「着目アドレス+2」を指定して、「着目アドレス+2」のデータおよび「着目アドレス+3」のデータを読み出す。

【0133】

このように、デコーダ421は、2つの内部RAMを用いて4つのアドレス分のデータを読み出すようにする。着目アドレスの更新は最大で「+2」であるため(つぎのグループユニットに変わる場合)、デコーダ421は、グループユニットが変わった直後であっても、常に着目アドレスの画素値の繰り返し回数と「着目アドレス+1」の画素値の繰り返し回数を把握することができるようになる。

【0134】

なお、RAM_No.2(RAM_PULSE_NUM)およびRAM_No.10(RAM_PULSE_NUM)を用いてデコーダ421が読み出したデータは、FPGA内に設けられた、それぞれ異なる第1の記憶領域および第2の記憶領域に一時保存されるように構成してもよい。

【0135】

ここで、着目アドレスを更新する際の読み出しデータの切り替え方法について説明する。デコーダ421は、読み出されたデータ(パターンデータ)に付加情報であるターミネータ情報が含まれていると判断した場合は、ターミネータ情報のつぎに読み出されたデータ(パターンデータ)の内容をさらに判断する。そして、この判断結果に基づいて、上述した第1の記憶領域または第2の記憶領域からデータ(パターンデータ)を読み出して、読み出した当該パターンデータを出力する。

【0136】

具体的には、たとえばデコーダ421が図17に示すペア1501を出力しているときには、デコーダ421が読み出しておくべき読出データは、ペア1501、ペア1502、ペア1503、ターミネータ情報1504であり、必要としている読出データは、ペア1501およびペア1502である。このとき、ペア1501の画素値「0」が118回繰り返された場合は、必要とする読出データをペア1502およびペア1503に切り替える。

【0137】

また、デコーダ421が図17に示すペア1502を出力しているときには、デコーダ421が読み出しておくべき読出データは、ペア1502、ペア1503、ターミネータ情報1504、ペア1505であり、必要としている読出データは、ペア1502およびペア1503である。このとき、ペア1502の画素値「0」が80回繰り返された場合は、必要とする読出データをペア1503およびターミネータ情報1504に切り替える。

【0138】

さらに、デコーダ421が図17に示すペア1503を出力しているときには、デコーダ421が読み出しておくべき読出データは、ペア1503、ターミネータ情報1504、ペア1505、ペア1506であり、必要としている読出データは、ペア1503およびターミネータ情報1504である。このとき、ペア1503の画素値「63」が4回繰り返された場合は、必要とする読出データをペア1505およびペア1506に切り替える。

【0139】

なお、上述したように4つ分のアドレスに関するデータを読み出すように構成したのは、つぎのような問題が生じてしまう場合があるからである。具体的には、たとえばターミネータ情報の直後のデータが、画素値の繰り返し回数が「1」であり、かつそのつぎのデータがターミネータ情報であった場合、画素値の繰り返し回数が「1」のつぎのデータがターミネータ情報であることをあらかじめデコーダ421が把握することができず、アドレス変更方法が不定となってしまう問題が生じてしまうためである。

【0140】

また、この発明の実施の形態にかかる開発・メンテナンス用ツール400では、フラッシュメモリから読み出した画像を形成するためのパターンデータを、バッファメモリなどに一時保存することなく連続的に出力する構成としたが、パターンデータを出力する際の方式はこれに限られない。たとえば、開発・メンテナンス用ツール400にバッファメモリを備えたPC(パーソナルコンピュータ)を接続し、画像を形成するためのパターンデータをすべてPCのバッファメモリに一時保存する。そして、FPGAは、PC内部のバッファメモリからパターンデータを読み出して、ヘッドモジュール430に画像のパターンデータを印刷出力させる構成としてもよい。

【0141】

以上説明したように、この発明の実施の形態にかかる画像データ処理方法によれば、読み込んだ簡易パターンファイル100を簡易パターンファイル格納用内部RAMである複数の内部RAMに、連続的に読み出すことができる状態で再配置して保存し、この保存した簡易パターンファイル100を画像を形成するための順序にしたがって読み出すことができる。そして、読み出した画像データを画像のラインごとに連続的に出力することができるため、ヘッドモジュール430の画質評価をおこなう際に、出力された画像が途中で途切れてしまうなどの不具合を防ぐことができ、適切な画質評価をおこなうことができる。

【0142】

さらに、この画像データ処理方法によれば、連続して出力されるラインとラインとの間に、つぎのラインの先頭画素にアクセスするまでの待ちクロックを設定することができるため、ヘッドモジュール430の画質評価をおこなう際に、1つのラインの出力が終了してつぎのラインの先頭画素にアクセスするまでのクロックによって先頭画素の読み出しが間に合わず、ラインとラインとの間で画像が途切れてしまうなどの不具合を防ぐことができ、適切な画質評価をおこなうことができる。

【0143】

また、この画像データ処理方法によれば、読み出された簡易パターンファイル100にターミネータ情報が含まれているか否かをあらかじめ判断することができ、この判断結果に応じて簡易パターンファイル100を連続的に出力することができるため、ヘッドモジュール430の画質評価をおこなう際に、出力された画像が途中で途切れてしまうなどの不具合を防ぐことができ、適切な画質評価をおこなうことができる。

【0144】

さらに、この画像データ処理方法によれば、読み出された簡易パターンファイル100に含まれるターミネータ情報のつぎに読み出される簡易パターンファイル100の内容をあらかじめ判断し、この判断結果に応じて第1の記憶領域または第2の記憶領域から簡易パターンファイル100を読み出して簡易パターンファイル100を連続的に出力することができるため、ヘッドモジュール430の画質評価をおこなう際に、出力された画像が途中で途切れてしまうなどの不具合を防ぐことができ、適切な画質評価をおこなうことができる。

【0145】

なお、本実施の形態で説明した開発・メンテナンス方法は、あらかじめ用意されたプログラムをパーソナル・コンピュータやワークステーションなどのコンピュータで実行することにより実現することができる。このプログラムは、ハードディスク、フレキシブルディスク、CD−ROM、MO、DVDなどのコンピュータで読み取り可能な記録媒体に記録され、コンピュータによって記録媒体から読み出されることによって実行される。またこのプログラムは、インターネットなどのネットワークを介して配布することが可能な伝送媒体であってもよい。

【図面の簡単な説明】

【0146】

【図1】簡易パターンファイルのデータ構造の一例を示す説明図。

【図2−1】簡易パターンファイルのライン定義の一例を示す図。

【図2−2】図2−1に示すライン定義の内容を示す説明図。

【図3】簡易パターンファイルのライン配置の一例を示す図。

【図4】本発明の実施の形態に係る画像形成装置の開発・メンテナンス用ツールにおけるインデックステーブルを示す図。

【図5】インデックステーブルを利用して表された簡易パターンファイルのデータ構造の一例を示す説明図。

【図6】画像データ処理システムのシステム構成の一例を示すブロック図。

【図7】簡易パターンファイル格納用内部RAMの概要を説明するための説明図。

【図8−1】簡易パターンファイルのサンプルの一例を示す説明図。

【図8−2】簡易パターンファイル格納用内部RAM状態を示すテーブル。

【図9】FPGAの機能的構成を示すブロック図。

【図10】FPGAの処理の手順を示すフローチャート。

【図11−1】モジュール内メモリがおこなう処理の手順を示すフローチャート。

【図11−2】モジュール内メモリがおこなう処理の手順を示すフローチャート。

【図12−1】画像サイズ算出部がおこなう処理の手順を示すフローチャート。

【図12−2】画像サイズ算出部がおこなう処理の手順を示すフローチャート。

【図13】デコーダがおこなう処理の手順を示すフローチャート。

【図14】ラインの先頭の画素値を読み出すまでのクロック数を示す説明図。

【図15】画素値を読み出すことができない場合の一例を示す説明図。

【図16】アドレス更新方法フラグの内容を示す説明図。

【図17】簡易パターンファイルのライン定義の一例を示す図。

【図18】画素値を読み出すことができない場合の一例を示す説明図

【符号の説明】

【0147】

100・・・簡易パターンファイル、101・・・ライン定義部、102・・・ライン配置部、110〜116・・・ライン定義部1〜ライン定義部7、120〜123・・・ゾーン0〜ゾーン3、124・・・色情報、400・・・開発・メンテナンス用ツール、410・・・簡易パターンメモリ、411・・・簡易パターンデータファイル、412・・・インデックステーブル、420・・・デコードモジュール、421・・・デコーダ、422・・・モジュール内メモリ、423・・・出力制御部、424・・・画像サイズ算出部、430・・・ヘッドモジュール

【技術分野】

【0001】

本発明は、プリンタなどのヘッドモジュールによって印刷出力した印刷結果の画質評価テストをおこなう際に用いる開発・メンテナンス用ツール、及び、ヘッドモジュールの画質評価テストを行う開発・メンテナンス方法に関する。

【背景技術】

【0002】

プリンタなどの画像形成装置の開発においては、各種コントローラが完成していないような段階において、メカニカルな部分のハードウエア構成についてテストを行いたい、ということがある。このようなハードウエアとしては、例えばヘッドモジュールがあり、開発段階のコントローラレスの状態にてヘッドモジュールによる印字品質の確認等を行いたいという要請がある。このため開発用のボードなどを利用して、画像データをヘッドモジュールに入力してテスト印刷を行うことが一般的である。なお、このようなヘッドモジュールによる印字品質の確認を行いたいということは、画像形成装置のメンテナンスの際にも生じる要請であり、メンテナンスの現場においても、ヘッドモジュールに対して、既存のコントローラを介さず、メンテナンス用のツールなどから直接的に画像データを入力することが行われている。

【0003】

プリンタなどのヘッドモジュールによって印刷出力した印刷結果の画質評価テストをおこなう際には、細かい線の繰り返し画像や円などの一定パターンの繰り返し画像など、多種類の画像を印刷出力して画質評価を行う。この場合、ビットマップ画像などのデータ量の大きな画像データを用いるのではなく、データ容量の小さな画像データを用いて画質評価をおこなうことが望まれている。

【0004】

出願人は、このようなテスト印刷において、ヘッドモジュールで印刷出力させるテストパターンとして、簡易パターンというものを提案している。この簡易パターンは、データ容量を少なくして、比較的簡単なファイルの定義に基づく画質評価用のパターンデータである(特許文献1、特許文献2参照)。

【特許文献1】特願2006−108350号公報

【特許文献2】特願2006−108351号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

画像形成装置などのプリンタ内部においては、印刷画像データは、ヘッドモジュールから1ドット単位に受信するビデオクロックに同期して出力する必要がある。つまり、

(1ドットをデコードするための処理速度)≧(1ドット出力要求速度)

を保つ必要があり、デコード部とヘッドモジュールとの間に出力画像用バッファメモリ

が無く、ビデオクロックに同期するように画像をデコードして、出力するシステムである必要がある。そして、このようなスペックは、ヘッドモジュールの評価を行う画像形成装置の開発・メンテナンス用ツールにおいても要求されるものである。

【0006】

ところで、従来例の簡易パターンデータは、1ラインを8ビットの階調データとその繰り返し、更にグループの繰り返しにより定義し、ラインデータの繰り返しによりページデータを作成する為、常に8ビットのデータで1ドットの処理をする仕様となっていた。印刷の高速化、高解像度化に伴い画素データのデコードも高速化する必要がある。そして、デコードの処理を高速化するためには、クロックアップによって、全体の処理を高速化する方法、及び、処理のパイプライン化、又はデコードの並列処理化によって複数の画素データを同時にデコードする方法の2通りの方法が考えられる。これらの方法を実現するためには、1クロック毎にデコーダへ何画素分のデータを渡せるかがキーになり、メモリから1クロックでどれだけ多くのデコード前画素データを読み込めるかにかかっているが、従来の簡易パターンにおいてはこのような高速化に係ることについては考慮されていなかった。

【課題を解決するための手段】

【0007】

本発明は上記の各課題を解決するために、請求項1に係る発明は、簡易パターンを生成して、当該簡易パターンをヘッドモジュールに転送することによって画像形成装置の開発やメンテナンスの際のテスト印刷を行う画像形成装置の開発・メンテナンス用ツールにおいて、当該簡易パターンに頻出するデータ配列の少なくとも一部をインデックス番号で代表したパターンデータが記憶されているインデックステーブルを記憶するインデックステーブル記憶手段と、当該インデックス番号を用いて記述された簡易パターンデータファイルを記憶する簡易パターンデータファイル記憶手段とを有し、当該簡易パターンを該簡易パターンデータファイル記憶手段と該インデックステーブル記憶手段を読み出すことによって生成することを特徴とする。

【0008】

このような本発明の開発・メンテナンス用ツールによれば、ヘッドモジュールに転送するための簡易パターンの生成においては、インデックステーブルを用いて、簡易パターンデータファイルを所謂データ圧縮するような形式が採られているので、(1ドットをデコードするための処理速度)≧(1ドット出力要求速度)の要求に対応することができ、ヘッドモジュールに対してより高速にデータ転送を行うことができる。

【0009】

また、請求項2に係る発明は、簡易パターンを生成して、当該簡易パターンをヘッドモジュールに転送することによって画像形成装置の開発やメンテナンスの際のテスト印刷を行う画像形成装置の開発・メンテナンス方法において、当該簡易パターンに頻出するデータ配列の少なくとも一部をインデックス番号で代表したパターンデータが記憶されているインデックステーブルを準備するステップと、当該インデックス番号を用いて記述された簡易パターンデータファイルを準備するステップと、該簡易パターンデータファイルと該インデックステーブルを参照することによって当該簡易パターンを生成するステップとを含むことを特徴とする。

【0010】

このような本発明の開発・メンテナンス用方法によれば、ヘッドモジュールに転送するための簡易パターンの生成においては、インデックステーブルを用いて、簡易パターンデータファイルを所謂データ圧縮するような形式が採られているので、(1ドットをデコードするための処理速度)≧(1ドット出力要求速度)の要求に対応することができ、ヘッドモジュールに対してより高速にデータ転送を行うことができる。

【発明を実施するための最良の形態】

【0011】

以下、本発明の実施の形態を図面を参照しつつ、本発明の実施の形態に係る画像形成装置の開発・メンテナンス用ツール(方法)について説明する。

(簡易パターンのデータ構造)

図1は、簡易パターンファイルのデータ構造の一例を示す説明図である。簡易パターンファイル100は、画像をカンマ区切りのテキスト形式で定義しているパターンデータである。この簡易パターンファイル100に基づいて、細かい線の繰り返し画像や円などの一定パターンの繰り返し画像など多種類の画像を作成して印刷することによって、プリンタなどにより印刷出力された画像の画質評価をおこなうことができる。

【0012】

図1に示すように、簡易パターンファイル100は、主走査方向側の定義であるライン定義部101(図中上側の破線で囲んだ領域)と、副走査方向側の定義であるライン配置部102(図中下側の破線で囲んだ領域)とによって構成されている。ここで、主走査方向とは、たとえばレーザプリンタによって印刷出力された画像の画質評価をおこなう場合に、筐体内部に設けられた感光体に照射されるレーザ光などが走査される方向であり感光体の進行方向と垂直な方向である。また、副走査方向とは、主走査方向と垂直な方向であり、感光体の進行方向と同一方向である。

【0013】

また、簡易パターンファイル100の先頭行103にある「X」は、「簡易パターンファイル識別子」である。この識別子「X」は、簡易パターンファイル100がどのようなパターンに定義されるかを示した識別子である。この識別子「X」を用いれば、たとえば、プリンタの固有の仕様などを示すことができる。具体的には、識別子「X」は、プリンタの仕様にあわせて、画素値の上「2Bit」が画素値の配置情報(右寄せ、左寄せ、中央寄せなど)で、下「6Bit」がピクセル値であることを示している。

【0014】

他に識別子を用いて示すことができる情報としては、たとえば画像を構成する画素値の配置情報、プリンタ内に設けられたプリンタヘッドの進行方向、主走査方向の最大の長さ、印刷をおこなう際における印刷出力する色の順番などの情報が挙げられる。また、簡易パターンファイル100に基づいて作成された画像を印刷する際には、この識別子「X」が示す識別情報に応じて印刷処理をおこなう。

【0015】

ライン定義部101は、主走査方向のラインを構成する画素値と当該画素値の所定の画素数とを関連付けて定義するものであり、複数のラインについてライン定義することができる。また、ライン配置部102は、ライン定義部101によって定義されたラインと、当該ラインの副走査方向へのライン数とを関連付けて定義する。さらに、ライン配置部102は、画像として用いられる色ごとに定義することができる。具体的には、ライン定義部101で定義された各ラインを副走査方向にどのように配置するかを定義するものであり、たとえば、C(シアン)、M(マゼンタ)、Y(イエロー)、K(ブラック)などの8色ごとに定義されている。

【0016】

なお、簡易パターンファイル100におけるライン定義部101とライン配置部102との間には、2行の空行(32行目および33行目)が設けられており、この空行によりライン定義部101とライン配置部102とを区切っている。つぎに、簡易パターンファイル100内の各部の構成を示す際に用いる用語の説明をするとともに、ライン定義部101とライン配置部102との詳細な説明をする。

【0017】

まず、ライン定義部101は、ライン定義された複数のラインによって構成されている。また、ライン定義部101の複数のラインにはそれぞれ番号が付されており、上から順番にライン定義1(110)、ライン定義2(111)、ライン定義3(112)、ライン定義4(113)、ライン定義5(114)、ライン定義6(115)、ライン定義7(116)となっている。さらに、図示は省略しているが、ライン定義1〜7とは異なるライン定義0も存在している。ライン定義0は、予約番号であり、「画素値0」がライン幅分並んでいることを示した白べたラインとなる。

【0018】

また、ライン定義1〜7のそれぞれのラインの間には、1行の空行が設けられており、たとえば5行目の空行により、ライン定義1(110)とライン定義2(111)とを区切っている。なお、ここではライン定義の定義数をライン定義0〜7の8個としたが、定義することができるライン定義の定義数は、固定ではなく任意に変更することができる。具体的には、たとえば簡易パターンファイル100のライン定義部101に、最大で256個までのライン定義を任意に定義することができる。

【0019】

それぞれのライン定義1〜7は、少なくとも1つのグループによって構成されており、さらに、それぞれのグループは、少なくとも1回のグループユニットの繰り返しによって構成されている。また、ライン定義部101の「A列」には、それぞれのグループユニットが何回繰り返されたかを示す繰り返し回数がそれぞれのグループユニットにあわせて付されている。なお、ライン定義において、ある画素値以降はすべて白データ(画像として何も表現されていない白べたライン)となる場合は、この白データを定義しなくてもよい。さらに、あるライン以降はすべて空白行となる場合は、この空白行を定義しなくてもよい。つぎに、ライン定義3(112)を例に挙げてライン定義についての詳細な説明を行う。

【0020】

図2−1は、ライン定義の一例を示す図である。また、図2−2は、図2−1に示すライン定義の内容を示す説明図である。図2−1に示すように、ライン定義3(112)は、グループ1(201)とグループ2(202)とが順番に並べられて構成されている。また、グループ1(201)は、グループユニット1(210)によって構成されており、グループユニット1(210)が1回繰り返されたことを示す「1」がグループユニット1(210)とともに付されている。さらに、グループユニット1(210)は、画素値0が118画素並んでいることを示すペア1(211)と、画素値0が80画素並んでいることを示すペア2(212)とによって構成されている。

【0021】

このように、ライン定義3(112)において、ペア1(211)とペア2(212)とが並んでグループユニット1(210)を形成し、このグループユニット1(210)が1回繰り返されてグループ1(201)を形成している。また、図2−1に示すように、グループ2(202)も同様の構成で形成されている。具体的には、ペア3(221)とペア4(222)とが並んでグループユニット2(220)を形成し、このグループユニット2(220)が1回繰り返されてグループ2(202)を形成している。

【0022】

以上説明したように、ライン定義3(112)は、上記グループ1(201)とグループ2(202)とが順に並んで構成されており、ライン定義3(112)の画素値の並びは順番に、画素値「0」が118画素、画素値「0」が80画素、画素値「0」が80画素、画素値「63」が6620画素となる。

【0023】

また、簡易パターンファイル100のライン定義部101において、同じ画素値のペアを並べて定義することができる(たとえば、図1に示すライン定義3(112)における、画素値「0」が118画素、画素値「0」が80画素の部分。)。これにより、たとえばすべてのライン定義の先頭に余白部分を設けるためのペアを定義することで、各ラインの先頭に共通の余白部分を設けることができる。さらに、副走査方向に連続するパターンを形成する際にも、同様に同じ画素値のペアを並べて定義することができる。

【0024】

つぎに、ライン配置部102についての詳細な説明をする。ライン配置部102は、複数のゾーンによって構成されている。また、ライン配置部102の複数のゾーンにはそれぞれゾーン番号が付されており、上から順番にゾーン0、1、2、3(図1に示す120、121、122、123)となっている。さらに、ライン配置部102の先頭行(34行目)には、それぞれの色のページが何番目から何番目までのゾーンで形成されているかをあらわす色情報が示されている。

【0025】

また、それぞれのゾーン0〜3(120〜123)には、ライン定義部101において定義されたある番号のライン定義がいくつか並んで形成されたラインセットと、いくつかのラインセットが並んで形成されたゾーンユニットとによって構成されており、それぞれのゾーンユニットには、ゾーンユニットが何回繰り返されているかを示すゾーン回数が付されている。なお、ここではゾーンの定義数をゾーン0〜3(120〜123)の4個としたが、ライン定義の定義数と同様に最大で256個までのゾーンを任意に定義することができる。ここで、図3を用いてライン配置部102についての詳細な説明をおこなう。

【0026】

図3は、ライン配置の一例を示す図である。図3に示すように、ライン配置部102は、色情報124と、ゾーン0(120)と、ゾーン1(121)と、ゾーン2(122)と、ゾーン(123)とによって構成されている。

【0027】

ゾーン0(120)は、ゾーンユニット1(312)が1回繰り返されて並んでいる構成である。また、ゾーンユニット1(312)は、ラインセット1(311)によって構成されており、このラインセット1(311)は、図1に示すライン定義1(110)が3000ライン並んでいることを示している。

【0028】

ゾーン1(121)は、ゾーンユニット2(324)が1回繰り返されて並んでいる構成である。また、ゾーンユニット2(324)は、ラインセット2(321)と、ラインセット3(322)と、ラインセット4(323)とによって構成されている。

【0029】

ラインセット2(321)は、図1に示すライン定義1が6661ライン並んでいることを示している。また、ラインセット3(322)、ラインセット4(323)についてもラインセット2(321)と同様であり、所定のライン定義がいくつ並んでいるかを示している。なお、ゾーン2(122)およびゾーン3(123)の構成は、上記ゾーン0(120)およびゾーン1(121)と同様のため説明を省略する。

【0030】

つぎに、ライン配置部102の先頭行(34行目)に示された、色情報について詳細に説明する。色情報は、34行目の左から順番に、第1色目に応じた色情報331として(1,1)、第2色目に応じた色情報332として(0,0)、第3色目に応じた色情報333として(1,1)、第4色目に応じた色情報334として(0,0)が示されている。たとえば、第1色目の色情報331である(1,1)は、第1色目の先頭ゾーン番号が「1」であり、終了ゾーン番号が「1」であることを示している。

【0031】

なお、ここでは色情報として開始ゾーン番号および終了ゾーン番号がすべて同じ番号となっているが、開始ゾーン番号および終了ゾーン番号は、それぞれ異なる番号であってもよい。具体的には、たとえば、色情報を(0,1)とすることによって、先頭ゾーン番号を「0」、終了ゾーン番号を「1」としてもよい。

【0032】

具体的には、ライン配置部102の第1色目のライン配置は、順番に、ライン定義0が6661ライン、ライン定義2(111)が3000ライン、ライン定義3(112)が1ライン並んでいる配置となる。

【0033】

また、第2色目の色情報は(0,0)であるため、第2色目の先頭ゾーン番号は「0」であり、終了ゾーン番号が「0」である。このため、ライン配置部102の第2色目のライン配置は、ライン定義1(110)が3000ライン並んでいる配置となる。

【0034】

さらに、第3色目の色情報は(1,1)であるため、第3色目の先頭ゾーン番号は「1」であり、終了ゾーン番号が「1」である。このため、ライン配置部102の第3色目のライン配置は、順番に、ライン定義0が6661ライン、ライン定義2(111)が3000ライン、ライン定義3(112)が1ライン並んでいる配置となる。

【0035】

さらに、第4色目の色情報は(0,0)であるため、第3色目の先頭ゾーン番号は「0」であり、終了ゾーン番号が「0」である。このため、ライン配置部102の第2色目のライン配置は、ライン定義1(110)が3000ライン並んでいる配置となる。

【0036】

以上説明したように、簡易パターンファイル100に基づいて画像を作成する場合、ライン定義部101で定義された各ラインが、色ごとに、ライン配置部102に示すライン配置に基づいて副走査方向に配置され、画像が形成されることとなる。つぎに、この発明の実施の形態にかかるインデックステーブルについて説明する。

【0037】

図4は、本発明の実施の形態に係る画像形成装置の開発・メンテナンス用ツールにおけるインデックステーブルを示す図である。インデックステーブルは、簡易パターンファイルにおける頻出するデータパターンをインデックスNo.で代表させたものである。

簡易パターンファイルは、パターンの繰り返しの為、少種類の階調データの組み合わせになる場合が多い。そこで、パターンデータに出現する階調値と、繰り返し数をインデックステーブルに登録し、頻出するパターンの代替としてインデックステーブルNo.を使用することでデータのビット幅を減らす。また、インデックステーブルNo.を簡易パターンデータとして持つ為、データのビット幅は、インデックステーブルに登録されたデータ数に依存する。ビット幅を決めてしまえば、1バイト中の画素データを1画素ではなく、多画素に出来る。本実施形態では、「グループユニットの繰り返し数」、「画素値」、「画素繰り返し数」、「ゾーン開始」、「ゾーン終了」、「ゾーンユニット繰り返し数」、「ライン定義No.」、「ライン繰り返し数」の各項目に対して、例えば図4に示すように、「0」、「1」、「2」の3つのインデックスNo.に代表させるように定義することができる。このようなインデックステーブルによれば、図1に示した簡易パターンファイルは、インデックスNo.を用いて図5のように表すことができる。

【0038】

このように本発明によれば、簡易パターンファイルの頻出パターンをインデックステーブルのインデックスNo.で代表させて処理するものであり、ヘッドモジュールに転送するための簡易パターンの生成においては、このインデックステーブルを用いて、簡易パターンデータファイルを所謂データ圧縮するような形式が採られているので、(1ドットをデコードするための処理速度)≧(1ドット出力要求速度)の要求に対応することができ、ヘッドモジュールに対してより高速にデータ転送を行うことができる。

(システム構成)

図6は、本発明の実施の形態に係る画像形成装置の開発・メンテナンス用ツールのシステム構成の一例を示すブロック図である。図6において、開発・メンテナンス用ツール400は、簡易パターンメモリ410と、デコードモジュール420とを備えて構成されている。

【0039】

開発・メンテナンス用ツール400は、ヘッドモジュール430において印刷出力する簡易パターンファイルを選択する。ここで、選択される簡易パターンは、後述するようにメモリ(例えば、フラッシュメモリを使用)に、簡易パターンデータファイル411とインデックステーブル412として保存されており、簡易パターンごとにそれぞれヘッダ情報(ファイル名など)が付加されている。開発者、メンテナンス要員は、たとえば図示しない操作部を操作することによって図示しないLCDに表示された複数の簡易パターンファイル名の中から印刷出力するための簡易パターンファイルを選択し、図示しないスタートボタンを押下してヘッドモジュール430に印刷を開始させる。

【0040】

開発・メンテナンス用ツール400は、例えば、フラッシュメモリと、FPGA(Field Programmable Gate Array)とからなる。フラッシュメモリは、ブートプログラム、画像データ処理プログラムなどの各種プログラムや複数の簡易パターンファイルなどを格納している。FPGAは、フラッシュメモリから簡易パターンデータファイル411とインデックステーブル412を読み出して復号化(デコード処理)し、復号化した簡易パターンファイルをヘッドモジュール430に転送する。

【0041】

ヘッドモジュール430は、FPGAの制御に基づいて、転送された簡易パターンファイルを印刷出力する。ヘッドモジュール430としては、レーザプリンタ方式、インクジェットプリンタ方式および熱転写プリンタ方式など各方式が用い得る。

(画像データ処理の内容)

つぎに、フラッシュメモリに格納されている簡易パターンデータファイル411とインデックステーブル412を読み出して復号化する際のデコード処理について詳細に説明する。FPGAは、フラッシュメモリから読み出した簡易パターンデータファイル411とインデックステーブル412に対するデコード処理をリアルタイムに(連続して)実行し、デコード処理された簡易パターンファイルを順次ヘッドモジュール430に転送する。これにより、印刷出力される画像が途中で途切れてしまうなどの不具合を防止することができる。

【0042】

上述したように、FPGAはリアルタイムにデコード処理を実行するため、フラッシュメモリから読み出された簡易パターンファイルを、デコード処理しやすい形式でFPGA内に保存する。具体的には、たとえばフラッシュメモリから読み出された簡易パターンファイルを、FPGA内に設けられた簡易パターンファイル格納用内部RAM(Random Access Memory)にテーブル形式で保存する。

【0043】

図7は、簡易パターンファイル格納用内部RAMの概要を説明するための説明図である。図7に示すように、簡易パターンデータファイル411は、インデックステーブル412を参照しつつ、FPGA内に設けられた簡易パターンファイル格納用内部RAM501に保存される。ここで、それぞれの内部RAM(No.1〜No.9)に保存される内容について説明する。なお、簡易パターンファイル格納用内部RAM501は、ライン定義に関するブロック502、ライン配置に関するブロック503およびアドレス取得用に関するブロック504の3つの分類ブロックに分けられて設けられている。

【0044】

RAM_No.1(RAM_PULSE)には、ライン定義されているすべての画素値を保存している。画素値を保存する際には、定義された画素値を順番に並べて保存し、簡易パターンファイルにおける行が変わる部分(グループが変わる場合)には、行が変わることを示す(グループが変わったことを示す)付加情報としてターミネータ情報を画素値と画素値との間に入れて保存する。具体的には、たとえば図1に示す簡易パターンファイル100のライン定義部101において定義された画素値を保存する場合、RAM_No.1(RAM_PULSE)には、画素値が「0,63,0,ターミネータ情報,0,0,63,0,0,ターミネータ情報,0,…」と順番に並べられて保存される。

【0045】

RAM_No.2(RAM_PULSE_NUM)には、ライン定義されているすべての画素の繰り返し回数を保存している。画素値の繰り返し回数を保存する際も上記と同様12に、定義された画素値の繰り返し回数を順番に並べて保存し、グループが変わる場合には、グループが変わったことを示すターミネータ情報を繰り返し回数と繰り返し回数との間に入れて保存する。具体的には、たとえば図1に示す簡易パターンファイル100のライン定義部101において定義された画素値の繰り返し回数を保存する場合、RAM_No.2(RAM_PULSE_NUM)には、繰り返し回数が「118,6780,118,ターミネータ情報,118,80,80,6620,118,ターミネータ情報,118,…」と順番に並べられて保存される。

【0046】

RAM_No.3(RAM_REPEAT_X)には、ライン定義されているすべてのグループユニットの繰り返し回数を保存している。グループユニットの繰り返し回数を保存する際には、定義されたグループユニットの繰り返し回数を順番に並べて保存し、簡易パターンファイルにおけるライン定義とライン定義との間で行が変わる場合(ライン定義が変わる場合)は、行が変わったことを示す(ライン定義が変わったことを示す)ターミネータ情報を繰り返し回数と繰り返し回数との間に入れて保存する。具体的には、たとえば図1に示す簡易パターンファイル100のライン定義部101において定義されたグループユニットの繰り返し回数を保存する場合、RAM_No.3(RAM_REPEAT_X)には、繰り返し回数が「1,ターミネータ情報,1,ターミネータ情報,1,1,ターミネータ情報,1,…」と順番に並べられて保存される。

【0047】

RAM_No.4(RAM_LINE)には、配置されるすべてのライン定義のライン定義番号を保存している。ライン定義番号を保存する際も上記と同様に、ライン定義番号を順番に並べて保存し、ライン定義番号とライン定義番号との間で行が変わる場合(ゾーンが変わる場合)は、行が変わったことを示す(ゾーンが変わったことを示す)ターミネータ情報をライン定義番号とライン定義番号との間に入れて保存する。具体的には、たとえば図1に示す簡易パターンファイル100のライン配置部102において定義されたライン配置に基づいて、配置されるライン定義のライン定義番号を保存する場合、RAM_No.4(RAM_LINE)には、ライン定義番号が「1,ターミネータ情報,0,2,3,2,3,2,0,ターミネータ情報,0,…」と順番に並べられて保存される。

【0048】

RAM_No.5(RAM_LINE_NUM)には、配置されるすべてのライン定義の繰り返し回数を保存している。ライン定義の繰り返し回数を保存する際も上記と同様に、定義されたライン定義の繰り返し回数を順番に並べて保存し、ゾーンが変わる場合には、ゾーンが変わったことを示すターミネータ情報を繰り返し回数と繰り返し回数との間に入れて保存する。具体的には、たとえば図1に示すライン配置部102において定義されたライン配置に基づいて、配置されるライン定義の繰り返し回数を保存する場合、RAM_No.5(RAM_LINE_NUM)には、繰り返し回数が「9685,ターミネータ情報,9525,4,34,4,34,4,80,ターミネータ情報,9525,…」と順番に並べられて保存される。

【0049】

RAM_No.6(RAM_REPEAT_Y)には、配置されるすべてのゾーンユニットの繰り返し回数を保存している。ゾーンユニットの繰り返し回数を保存する際も上記と同様に、ゾーンユニットの繰り返し回数を順番に並べて保存する。また、ゾーンユニットの繰り返し回数を順番に並べた最後の部分には、ターミネータ情報を入れて保存する。具体的には、たとえば図1に示すライン配置部102において定義されたライン配置に基づいて、配置されるゾーンユニットの繰り返し回数を保存する場合、RAM_No.6(RAM_REPEAT_Y)には、繰り返し回数が「1,1,1,1,ターミネータ情報」と順番に並べられて保存される。

【0050】

RAM_No.7(RAM_BND_PULSE)には、ライン定義されているすべての画素値が保存されているRAM_No.1(RAM_PULSE)内にアクセスするためのアドレスが保存される。さらに、RAM_No.7(RAM_BND_PULSE)には、ライン定義されているすべての画素の繰り返し回数が保存されているRAM#No.2(RAM_PULSE_NUM)内にアクセスするためのアドレスが保存される。

【0051】

RAM_No.8(RAM_BND_REPEAT_X)には、ライン定義されているすべてのグループユニットの繰り返し回数が保存されているRAM_No.3(RAM_REPEAT_X)内にアクセスするためのアドレスが保存される。

【0052】

RAM_No.9(RAM_BND_LINE)には、配置されるすべてのライン定義のライン定義番号が保存されているRAM_No.4(RAM_LINE)内および配置されるすべてのライン定義の繰り返し回数が保存されているRAM_No.5(RAM_LINE_NUM)内にアクセスするためのアドレスが保存される。つぎに、具体的なサンプリングを例に挙げて簡易パターンファイル格納用内部RAM状態の説明をする。

【0053】

図8−1は、簡易パターンファイルのサンプルの一例を示す説明図である。また、図8−2は、図8−1に示す簡易パターンファイルを保存した場合の簡易パターンファイル格納用内部RAM状態を示すテーブルである。図8−1に示すように、簡易パターンファイル600のライン定義部601には、破線であらわされた2つのラインについてのライン定義が示されており、それぞれのライン定義を構成するグループが太線によってあらわされている。

【0054】

さらに、簡易パターンファイル600のライン配置部602には、一点鎖線であらわす3つのゾーンが示されている。また、図8−2には、FPGA内に設けられた9つの内部RAM620のそれぞれのRAMに保存されている内容がアドレス630と関連付けられて示されている。なお、図8−1に示す簡易パターンファイル600は、簡易パターンファイル格納用内部RAM状態の説明をおこなうために、図1に示す簡易パターンファイル100の一部を省略して示したものである。

【0055】

図8−2に示すRAM_No.1(RAM_PULSE)には、簡易パターンファイル600においてライン定義されているすべての画素値が保存されている。このとき、それぞれのアドレスには、1つの画素値が順番に保存されている。また、グループとグループとの間には、グループ間を区別するためのターミネータ情報を保存する。さらに、ライン定義されているすべての画素値が保存されたことを示すターミネータ情報を最後のアドレスに保存する。なお、ターミネータ情報を保存するアドレスには、ターミネータ情報を示す下線付きの「0」が示されている。また、デコード処理を一意化するために、アドレスNo.0には空行を示す「画素値0」が保存されており、アドレスNo.1には、ターミネータ情報が保存されている。

【0056】

また、RAM_No.2(RAM_PULSE_NUM)には、ライン定義されているすべての画素の繰り返し回数が保存されている。このとき、それぞれのアドレスには、1つの画素の繰り返し回数が順番に保存されている。また、グループとグループとの間には、グループ間を区別するためのターミネータ情報を保存する。さらに、ライン定義されているすべての画素の繰り返し回数が保存されたことを示すターミネータ情報を最後のアドレスに保存する。また、デコード処理を一意化するために、アドレスNo.0には空行を示すための画像幅が保存されており、アドレスNo.1には、ターミネータ情報が保存されている。なお、保存される画像幅は、後述する画像サイズ算出部424において計算される。

【0057】

つぎに、RAM_No.3(RAM_REPEAT_X)には、ライン定義されているすべてのグループユニットの繰り返し回数が保存されている。このとき、それぞれのアドレスには、1つのグループユニットの繰り返し回数が順番に保存されている。また、グループとグループとの間には、グループ間を区別するためのターミネータ情報を保存する。さらに、ライン定義されているすべてのグループユニットの繰り返し回数が保存されたことを示すターミネータ情報を最後のアドレスに保存する。また、デコード処理を一意化するために、アドレスNo.0には空行を示すための繰り返し回数「1」が保存されており、アドレスNo.1には、ターミネータ情報が保存されている。

【0058】

また、RAM_No.4(RAM_LINE)には、配置されるすべてのライン定義のライン定義番号が保存されている。このとき、それぞれのアドレスには、1つのライン定義番号が順番に保存されている。また、ゾーンとゾーンとの間には、ゾーン間を区別するためのターミネータ情報を保存する。さらに、配置されるすべてのライン定義のライン定義番号が保存されたことを示すターミネータ情報を最後のアドレスに保存する。

【0059】

つぎに、RAM_No.5(RAM_LINE_NUM)には、配置されるすべてのライン定義の繰り返し回数が保存されている。このとき、それぞれのアドレスには、1つのライン定義の繰り返し回数が順番に保存されている。また、ゾーンとゾーンとの間には、ゾーン間を区別するためのターミネータ情報を保存する。さらに、配置されるすべてのライン定義におけるライン定義の繰り返し回数が保存されたことを示すターミネータ情報を最後のアドレスに保存する。

【0060】

また、RAM_No.6(RAM_REPEAT_Y)には、配置されるすべてのゾーンユニットの繰り返し回数が保存されている。このとき、それぞれのアドレスには、1つのゾーンユニットの繰り返し回数が順番に保存されている。また、配置されるすべてのゾーンユニットの繰り返し回数が保存されたことを示すターミネータ情報を最後のアドレスに保存する。

【0061】

つぎに、RAM_No.7(RAM_BND_PULSE)には、RAM_No.1(RAM_PULSE)およびRAM_No.2(RAM_PULSE_NUM)内のいずれかに保存されているデータにアクセスするためのアドレスを保存している。たとえば、ライン定義「X」のデータにアクセスするためには、RAM_No.7(RAM_BND_PULSE)内のアドレス「X」に保存している値が、RAM_No.1(RAM_PULSE)およびRAM_No.2(RAM_PULSE_NUM)におけるライン定義「X」の先頭アドレスとなる。

【0062】

また、RAM_No.8(RAM_BND_REPEAT_X)には、RAM_No.3(RAM_REPEAT_X)内に保存されているデータにアクセスするためのアドレスを保存している。たとえば、ライン定義「X」のデータにアクセスするためには、RAM_No.8(RAM_BND_REPEAT_X)のアドレス「X」に保存されている値が、RAM_No.3(RAM_REPEAT_X)におけるライン定義「X」の先頭アドレスとなる。

【0063】

つぎに、RAM_No.9(RAM_BND_LINE)には、RAM_No.4(RAM_LINE)およびRAM_No.5(RAM_LINE_NUM)内に保存されているデータにアクセスするためのアドレスを保存している。たとえば、ゾーン「X」のデータにアクセスするためには、RAM_No.9(RAM_BND_LINE)のアドレス「X」に保存されている値が、RAM_No.4(RAM_LINE)およびRAM_No.5(RAM_LINE_NUM)におけるゾーン「X」の先頭アドレスとなる。

【0064】

ここで、図8−1および図8−2を用いて、ライン定義2(603)の3個目の画素値「63」にアクセスする場合について説明する。まず、ライン定義2(603)の先頭アドレスとしてRAM_No.7(RAM_BND_PULSE)内のアドレス「2」に保存されている「5」を取得する。

【0065】

つぎに、ライン定義2(603)の3個目の画素値「63」にアクセスするため、先頭アドレス「5」に2(3−1=2)を加算する。これにより、算出された「7」の値がライン定義2(603)の3個目の画素値「63」のアドレスとなる。そして、このアドレス「7」をRAM_No.1(RAM_PULSE)に指定し、RAM_No.1(RAM_PULSE)のアドレス「7」から画素値「63」を取得する。つぎに、上述した簡易パターンファイルのデコード処理を実行するFPGAの機能的構成について説明する。

(FPGAの機能的構成)

図9は、この発明の実施の形態にかかるFPGAの機能的構成を示すブロック図である。図9に示すように、FPGAは、モジュール内メモリ422と、画像サイズ算出部424と、デコーダ421と、出力制御部423とを含む構成となっている。先のFPGA内に設けられた簡易パターンファイル格納用内部RAMは、モジュール内メモリ422の構成の一部である。

【0066】

モジュール内メモリ422は、フラッシュメモリに格納されている簡易パターンファイルの行方向への読み込みを、インデックステーブル412を参照しておこない、読み込まれた簡易パターンファイルを読み込まれた順に、簡易パターンファイルに含まれる種別ごとに異なる記憶領域に振り分けて保存する。このとき、簡易パターンファイルの行が変わる部分には、当該行が変わることを示す付加情報(ターミネータ情報)をあわせて保存する。具体的には、モジュール内メモリ422は、簡易パターンファイルを読み込んで、FPGA内に設けられた簡易パターンファイル格納用内部RAMの複数の内部RAMにテーブル形式で保存する。

【0067】

画像サイズ算出部424は、FPGA内の内部RAMに保存されているデータに基づいて、簡易パターンファイルの画像サイズを算出する。具体的には、画像サイズ算出部424は、FPGA内に設けられた内部RAMから簡易パターンファイルを読み出し、読み出した簡易パターンファイルの画像の幅を算出するとともに、画像の高さを算出する。また、画像の高さは、画像の色ごとに(たとえば、C(シアン),M(マゼンタ),Y(イエロー),K(ブラック))、それぞれ算出する。

【0068】

デコーダ421は、モジュール内メモリ422によって保存されている簡易パターンファイルを、画像を形成するための順序にしたがって、付加情報であるターミネータ情報とあわせて簡易パターンファイル格納用内部RAMの複数の内部RAMから読み出す。そして、読み出された簡易パターンファイルを、付加情報であるターミネータ情報とあわせて画像の主走査方向のラインごとに連続してデコード処理する。

【0069】

出力制御部423は、デコーダ421によってデコード処理された簡易パターンファイルをFPGA内に設けられた図示しないビデオメモリへ、付加情報であるターミネータ情報とあわせて画像の主走査方向のラインごとに連続的に出力する。ここで、ビデオメモリとは、FPGA内に設けられた記憶領域であり、ビデオメモリに格納されたデータは、古いデータ(一番始めに格納されたデータ)から順に読み出される。つぎに、フラッシュメモリから読み出した簡易パターンファイルがヘッドモジュール430に転送されるまでの間に、FPGAが簡易パターンファイルに対しておこなう処理の内容について説明する。

(FPGAの画像データ処理手順)

図10は、この発明の実施の形態にかかるFPGAの処理の手順を示すフローチャートである。図10のフローチャートにおいて、まず、操作基板401から印刷開始を示す信号が通知された場合、FPGAのモジュール内メモリ422は、フラッシュメモリに格納されている簡易パターンファイルを読み込んで、FPGA内に設けられた複数の簡易パターンファイル格納用内部RAMにテーブル形式で保存する(ステップS801)。

【0070】

つぎに、画像サイズ算出部424は、FPGA内の内部RAMに格納されているデータに基づいて、簡易パターンファイルの画像サイズを算出する(ステップS802)。そして、デコーダ421は、FPGA内の内部RAMに格納されているデータに基づいて、簡易パターンファイルに対するデコード処理を実行する(ステップS803)。

【0071】

最後に、デコーダ421によってデコード処理された簡易パターンファイルをFPGA内に設けられたビデオメモリへ出力して(ステップS804)、本フローチャートによる一連の処理を終了する。つぎに、ステップS801において、モジュール内メモリ422がフラッシュメモリから読み込んだ簡易パターンファイルを、FPGA内に設けられた簡易パターンファイル格納用内部RAMに保存する際の処理について詳細に説明する。

【0072】

図11−1および図11−2は、FPGAのモジュール内メモリがおこなう処理の手順を示すフローチャートである。図11−1のフローチャートにおいて、まず、FPGAのモジュール内メモリ422は、フラッシュメモリに格納されている簡易パターンファイルの1行分のデータを読み込む(ステップS901)。具体的には、簡易パターンファイル100(図1参照、以下同様。)の行方向への読み込みを連続して、上から順に1行ずつ(1行目、2行目、…)おこなう。

【0073】

そして、モジュール内メモリ422は、読み込んだ1行が空行か否かを判断する(ステップS902)。具体的には、たとえばモジュール内メモリ422は、簡易パターンファイル100の5行目を読み込んだ場合に、空行であると判断する。ここで、読み込んだ1行が空行ではなかった場合(ステップS902:No)は、つぎに、読み込んだ1行分のデータに基づいて、グループユニットの繰り返し回数を保存する(ステップ903)。具体的には、たとえばステップS901において簡易パターンファイル100の2行目を読み込んだ場合、グループユニットの繰り返し回数を「1」と判断し、FPGAの所定の内部RAMにグループユニットの繰り返し回数「1」を保存する。

【0074】

つぎに、モジュール内メモリ422は、新たに簡易パターンファイルの1行分のデータを読み込む(ステップS904)。そして、モジュール内メモリ422は、読み込んだ1行分のデータに基づいて、グループの画素値を保存する(ステップS905)。具体的には、たとえばステップS904において簡易パターンファイル100の2行目を読み込んだ場合、グループの画素値を「0,63,0」と判断し、FPGAの所定の内部RAMに画素値を「0,63,0」と順に並べて保存する。

【0075】

ここで、グループ内(読み込んだ1行分)の画素値をすべて保存した場合、モジュール内メモリ422は、ターミネータ情報を追加して保存する(ステップS906)。つぎに、モジュール内メモリ422は、また新たに簡易パターンファイルの1行分のデータを読み込む(ステップS907)。そして、モジュール内メモリ422は、読み込んだ1行分のデータに基づいて、グループの画素値の繰り返し回数を保存する(ステップS908)。具体的には、たとえば簡易パターンファイル100の3行目を読み込んだ場合、グループの画素値の繰り返し回数を「118,6780,118」と判断し、FPGAの所定の内部RAMにグループの画素値の繰り返し回数を「118,6780,118」と順に並べて保存する。

【0076】

ここで、グループ内(読み込んだ1行分)の画素値の繰り返し回数をすべて保存した場合、モジュール内メモリ422は、ターミネータ情報を追加して保存し(ステップS909)、ステップS901に戻り、本フローチャートによる一連の処理を繰り返す。

【0077】

また、ステップS902において、読み込んだ1行が空行であると判断された場合、モジュール内メモリ422は、新たに簡易パターンファイルの1行分のデータを読み込む(ステップS910)。そして、モジュール内メモリ422は、ステップS902およびステップS910において読み込んだ2行分のデータに基づいて、連続して空行か否かを判断する(ステップS911)。

【0078】

ここで、連続して空行ではないと判断された場合、モジュール内メモリ422は、ターミネータ情報を追加して保存し(ステップS912)、ステップS903に移行し、本フローチャートによる一連の処理をおこなう。また、ステップS911において、連続して空行であると判断された場合は、モジュール内メモリ422は、ライン定義の読み込みが終了したと判断し、図11−2に示すステップS921に移行する。

【0079】

図11−2に示すフローチャートのステップS921において、モジュール内メモリ422は、新たに簡易パターンファイルの1行分のデータを読み込む(ステップS921)。具体的には、たとえば簡易パターンファイル100のライン配置部102の最初の行である34行目を読み込む。つぎに、モジュール内メモリ422は、読み込んだ1行分のデータに基づいて、1色分の開始ゾーンを内部RAMに保存し(ステップS922)、1色分の終了ゾーンを内部RAMに保存する(ステップS923)。具体的には、簡易パターンファイル100の34行目を読み込んだ場合、1色分の開始ゾーンを「1」として保存し、1色分の終了ゾーンを「1」として保存する。

【0080】

そして、モジュール内メモリ422は、すべての色について開始ゾーンおよび終了ゾーンが保存されたか否かを判断する(ステップS924)。具体的には、簡易パターンファイル100の34行目に示されている4色分すべての開始ゾーンおよび終了ゾーンを保存したか否かを判断する。ここで、すべての色について開始ゾーンおよび終了ゾーンが保存されていない場合(ステップS924:No)は、ステップS922に戻り、一連の処理を繰り返す。

【0081】

また、すべての色について開始ゾーンおよび終了ゾーンが保存された場合(ステップS924:Yes)、モジュール内メモリ422は、新たに簡易パターンファイルの1行分のデータを読み込む(ステップS925)。そして、すべての簡易パターンファイルの読み込みが終了したか否かを判断する(ステップS926)。ここで、読み込みが終了していないと判断された場合(ステップS926:No)は、ステップS925において読み込んだ1行分のデータに基づいて、ゾーンユニットの繰り返し回数を保存する(ステップS927)。

具体的には、たとえば簡易パターンファイル100の35行目を読み込んだ場合、ゾーンユニットの繰り返し回数を「1」と判断し、所定の内部RAMにゾーンユニットの繰り返し回数「1」を保存する。

【0082】

つぎに、モジュール内メモリ422は、新たに簡易パターンファイルの1行分のデータを読み込む(ステップS928)。そして、モジュール内メモリ422は、読み込んだ1行分のデータに基づいて、ゾーンのライン定義番号を保存する(ステップS929)。具体的には、たとえば簡易パターンファイル100の39行目を読み込んだ場合、ゾーンのライン定義番号を「0,2,3,2,3,2,0」と判断し、内部RAMにゾーンのライン定義番号「0,2,3,2,3,2,0」を保存する。

【0083】

ここで、ゾーン内(読み込んだ1行分)のライン定義番号をすべて保存した場合、モジュール内メモリ422は、ターミネータ情報を追加して保存する(ステップS930)。つぎに、モジュール内メモリ422は、新たに簡易パターンファイルの1行分のデータを読み込む(ステップS931)。そして、モジュール内メモリ422は、読み込んだ1行分のデータに基づいて、ゾーンのライン定義の繰り返し回数を保存する(ステップS932)。具体的には、たとえば簡易パターンファイル100の40行目を読み込んだ場合、ゾーンのライン定義の繰り返し回数を「9525,4,34,4,34,4,80」と判断し、内部RAMにゾーンのライン定義の繰り返し回数「9525,4,34,4,34,4,80」を保存する。

【0084】

ここで、グループ内(読み込んだ1行分)のゾーンのライン定義の繰り返し回数をすべて保存した場合、モジュール内メモリ422は、ターミネータ情報を追加して保存し(ステップS933)、つぎに、ステップS925に戻り、本フローチャートによる一連の処理を繰り返す。また、ステップS926において、読み込みが終了したと判断された場合(ステップS926:Yes)は、本フローチャートによる一連の処理を終了する。

【0085】

つぎに、図10に示すフローチャートのステップS802において、画像サイズ算出部424がFPGA内の内部RAMに保存されているデータに基づいて、簡易パターンファイルの画像サイズを算出する際の処理について詳細に説明する。

【0086】

図12−1は、FPGAの画像サイズ算出部がおこなう幅算出処理の手順を示すフローチャートである。また、図12−2は、FPGAの画像サイズ算出部がおこなう高さ算出処理の手順を示すフローチャートである。図12−1のフローチャートにおいて、まず、FPGAの画像サイズ算出部424は、FPGAの簡易パターンファイル格納用内部RAMに保存されている画素値の繰り返し回数およびグループユニットの繰り返し回数を読み出す(ステップS1001)。具体的には、図8−2に示す簡易パターンファイル格納用内部RAM状態を示すテーブルに示すように、RAM_No.2に保存されている画素値の繰り返し回数を読み出し、RAM_No.3に保存されているグループユニットの繰り返し回数を読み出す。

【0087】

つぎに、画像サイズ算出部424は、グループユニットの繰り返し回数がターミネータ情報か否かを判断する(ステップS1002)。具体的には、画像サイズ算出部424は、ステップS1001において読み出したグループユニットの繰り返し回数が下線付きの「0」であるか否かを判断し、下線付きの「0」であった場合にターミネータ情報であると判断する。

【0088】

ここで、グループユニットの繰り返し回数がターミネータ情報ではなかった場合(ステップS1002:No)は、つぎに、画素値の繰り返し回数がターミネータ情報か否を判断する(ステップS1003)。具体的には、画像サイズ算出部424は、ステップS1001において読み出した画素値の繰り返し回数が下線付きの「0」であるか否かを判断し、下線付きの「0」であった場合にターミネータ情報であると判断する。

【0089】

そして、画素値の繰り返し回数がターミネータ情報であった場合(ステップS1003:Yes)は、画像サイズ算出部424は、画素数カウント値およびグループユニットの繰り返し回数の乗算結果を幅に加算する(ステップS1004)。つぎに、画像サイズ算出部424は、画素数カウント値をリセットし(ステップS1005)、グループユニットの繰り返し回数のアドレスをつぎのアドレスに移行する(ステップS1006)。

【0090】

さらに、画像サイズ算出部424は、画素値の繰り返し回数のアドレスをつぎのアドレスに移行し(ステップS1007)、つぎに、ステップS1001に戻り、本フローチャートによる一連の処理を繰り返す。また、ステップS1003において、画素値の繰り返し回数がターミネータ情報ではなかった場合(ステップS1003:No)は、画像サイズ算出部424は、画素数カウント値を更新し(ステップS1008)、ステップS1007に移行する。

【0091】

また、ステップS1002において、グループユニットの繰り返し回数がターミネータ情報であった場合(ステップS1002:Yes)は、画像サイズ算出部424は、画像の幅をすべて算出したと判断して、本フローチャートによる一連の処理を終了する。

【0092】

つぎに、画像サイズ算出部424がおこなう画像の高さを算出する処理について図12−2を用いて説明する。図12−2のフローチャートにおいて、まず、FPGAの画像サイズ算出部424は、モジュール内メモリ422によってFPGAの簡易パターンファイル格納用内部RAMに保存されているライン定義の繰り返し回数およびゾーンユニットの繰り返し回数を読み出す(ステップS1020)。具体的には、図8−2に示すRAM_No.5に保存されているライン定義の繰り返し回数を読み出し、RAM_No.6に保存されているゾーンユニットの繰り返し回数を読み出す。

【0093】

そして、画像サイズ算出部424は、すべての色についてライン定義の繰り返し回数およびゾーンユニットの繰り返し回数の読み出しが終了したか否かを判断する(ステップS1021)。ここで、すべての色について読み出しが終了していない場合(ステップS1021:No)、画像サイズ算出部424は、1色分のライン定義の繰り返し回数およびゾーンユニットの繰り返し回数の読み出しが終了したか否かを判断する(ステップS1022)。

【0094】

ここで、1色分の読み出しが終了していない場合(ステップS1022:No)、画像サイズ算出部424は、ライン定義の繰り返し回数がターミネータ情報か否かを判断する(ステップS1023)。そして、ライン定義の繰り返し回数がターミネータ情報ではなかった場合(ステップS1023:No)、画像サイズ算出部424は、高さカウント値を更新する(ステップS1024)。具体的には、画像サイズ算出部424は、画像の高さにライン定義の繰り返し回数を加算する。

【0095】

そして、画像サイズ算出部424は、ライン定義の繰り返し回数のアドレスをつぎのアドレスに移行し(ステップS1025)、ステップS1020に戻り、本フローチャートによる一連の処理を繰り返す。また、ステップS1021において、すべての色について読み出しが終了した場合(ステップS1021:Yes)は、本フローチャートによる一連の処理を終了する。

【0096】

さらに、ステップS1023において、ライン定義の繰り返し回数がターミネータ情報であった場合(ステップS1023:Yes)、画像サイズ算出部424は、高さカウント値とゾーンユニットの繰り返し回数との乗算結果を画像の高さに加算する(ステップS1026)。そして、画像サイズ算出部424は、高さカウント値をリセットする(ステップS1027)。つぎに、画像サイズ算出部424は、ゾーンユニットの繰り返し回数のアドレスをつぎのアドレスに移行し(ステップS1028)、ステップS1025に移行する。

【0097】

また、ステップS1022において、1色分の読み出しが終了したと判断された場合(ステップS1022:Yes)、画像サイズ算出部424は、色番号の更新をおこない(ステップS1029)、ステップS1027に移行する。

【0098】

つぎに、図10に示すフローチャートのステップS803において、デコーダ421がFPGA内の内部RAMに格納されているデータに基づいて、簡易パターンファイルに対するデコード処理を実行し、デコード処理をおこなった簡易パターンファイルをFPGA内に設けられたビデオメモリへ出力する際の処理について詳細に説明する。

【0099】

図13は、FPGAのデコーダがおこなう処理の手順を示すフローチャートである。図13のフローチャートにおいて、まず、FPGAのデコーダ421は、FPGAの簡易パターンファイル格納用内部RAMに保存されている1色分の開始ゾーン番号および終了ゾーン番号を取得する(ステップS1101)。つぎに、デコーダ421は、取得したゾーン内の先頭ライン定義番号を取得する(ステップS1102)。これにより、デコーダ421は、ライン定義されている画素値にアクセスすることができる。

【0100】

そして、デコーダ421は、内部RAMから画素値を読み出す(ステップS1103)。具体的には、図8−2に示すRAM_No.1に保存されている画素値を読み出す。つぎに、デコーダ421は、読み出した画素値を出力する(ステップS1104)。このとき、デコーダ421は、画素値の繰り返し回数を判断し、それぞれの画素値の繰り返し回数分、FPGA内に設けられたビデオメモリへ出力する。たとえば、デコーダ421は、図8−2に示すRAM_No.2から読み出した画素値の繰り返し回数に基づいて、繰り返し回数分出力したか否かを判断する。

【0101】

ここで、デコーダ421は、画素値を画素値の繰り返し回数分、ビデオメモリへ出力したか否かを判断する(ステップS1105)。そして、すべて出力した場合(ステップS1105:Yes)は、つぎに、デコーダ421は、1つのグループユニット内のすべての画素値の出力が終了したか否かを判断する(ステップS1106)。また、ステップS1105において、画素値を画素値の繰り返し回数分出力していない場合(ステップS1105:No)は、ステップS1103に戻り、本フローチャートによる一連の処理を繰り返す。

【0102】

ステップS1106において、1つのグループユニット内のすべての画素値の出力が終了した場合(ステップS1106:Yes)、デコーダ421は、グループユニットの繰り返しが終了したか否かを判断する(ステップS1107)。具体的には、たとえばデコーダ421は、図8−2に示すRAM_No.3から読み出したグループユニットの繰り返し回数に基づいて、グループユニットの繰り返し回数が終了したか否かを判断する。

【0103】

また、1つのグループユニット内のすべての画素値の出力が終了していない場合(ステップS1106:No)、ステップS1103に戻り、本フローチャートによる一連の処理を繰り返す。

【0104】

ステップS1107において、グループユニットの繰り返しが終了するのを待って、終了した場合(ステップS1107:Yes)、つぎに、デコーダ421は、1ライン分(1つのライン定義)の画素値の出力が終了したか否かを判断する(ステップS1108)。ここで、1ライン分の画素値の出力が終了した場合(ステップS1108:Yes)、つぎに、デコーダ421は、ライン定義の繰り返しが終了したか否かを判断する(ステップS1109)。また、ステップS1108において、1ライン分の画素値の出力が終了していないと判断された場合(ステップS1108:No)は、ステップS1103に戻り、本フローチャートによる一連の処理を繰り返す。

【0105】

ステップS1109においてライン定義の繰り返しが終了するのを待って、繰り返しが終了した場合(ステップS1109:Yes)、1つのゾーンユニット内のすべてのライン定義の繰り返しが終了したか否かを判断する(ステップS1110)。具体的には、たとえばデコーダ421は、図8−2に示すRAM_No.4およびRAM_No.5からライン定義番号およびライン定義の繰り返し回数を読み出す。そして、デコーダ421は、読み出したライン定義番号およびライン定義の繰り返し回数に基づいて、1つのゾーンユニット内に配置されている順にそれぞれのライン定義の繰り返しが終了したか否かを判断するとともに、ゾーンユニット内のすべてのライン定義の繰り返しが終了したか否かを判断する。

【0106】

ここで、1つのゾーンユニット内のすべてのライン定義の繰り返しが終了したと判断された場合(ステップS1110:Yes)は、デコーダ421は、ゾーンユニットの繰り返しが終了したか否かを判断する(ステップS1111)。具体的には、たとえばデコーダ421は、図8−2に示すRAM_No.6から読み出したゾーンユニットの繰り返し回数に基づいて、ゾーンユニットの繰り返しが終了したか否かを判断する。

【0107】

そして、ゾーンユニットの繰り返しが終了するのを待って、繰り返しが終了した場合(ステップS1111:Yes)は、1色分についての画素値の出力が終了したか否かを判断する(ステップS1112)。具体的には、ステップS1101において取得した1色分の開始ゾーン番号および終了ゾーン番号に基づいて、1色分についての画素値の出力が終了したか否かを判断する。

【0108】

ここで、1色分についての画素値の出力が終了した場合(ステップS1112:Yes)、本フローチャートによる一連の処理を終了する。なお、たとえば簡易パターンファイル100に示すように、4色分のライン配置が定義されている場合には、デコーダ421は、4色分のすべてについて上述した一連の処理と同様の処理をおこなう。また、ステップS1112において、1色分についての画素値の出力が終了していない(ステップS1112:No)、ステップS1103に戻り、本フローチャートによる一連の処理を繰り返す。

【0109】

図13のフローチャートで説明したデコーダ421がおこなう処理は、リアルタイムでおこなう必要があるため、デコーダ421は、たとえばつぎのような制約に基づいて上記処理をおこなうようにしてもよい。デコーダ421は、図13のステップS1103において、RAM_No.1に保存されている画素値を読み出す際には、複数の内部RAMからのデータの読み出しを連続的におこなっている。ここで、デコーダ421が画素値を読み出す際の詳細な説明を図14を用いて説明する。

【0110】

図14は、ラインの先頭の画素値を読み出すまでのクロック数を示す説明図である。図14に示すように、ラインの先頭の画素値を読み出す際には、まず、デコーダ421は、図14中矢印Aで示す1クロック目にRAM_No.9(RAM_BND_LINE)に対してゾーン番号を指定する。このとき、指定するゾーン番号は、たとえば、図11のフローチャートのステップS1101において取得した開始ゾーン番号などである。

【0111】

つぎに、デコーダ421は、図14中矢印Bで示す2クロック目にRAM_No.9(RAM_BND_LINE)から1クロック目に指定したゾーン番号の先頭アドレスを取得して、取得した先頭アドレスをRAM_No.4(RAM_LINE)に対して指定する。そして、デコーダ421は、図12中矢印Cで示す3クロック目にRAM_No.4(RAM_LINE)から2クロック目に指定した先頭アドレスに応じたライン定義番号を取得して、取得したライン定義番号をRAM_No.7(RAM_BND_PULSE)に対して指定する。

【0112】

つぎに、デコーダ421は、図14中矢印Dで示す4クロック目にRAM_No.7(RAM_BND_PULSE)から3クロック目に指定したライン定義番号の先頭アドレスを取得して、取得したライン定義番号の先頭アドレスをRAM_No.1(RAM_PULSE)に対して指定する。そして、デコーダ421は、図14中矢印Eで示す5クロック目にRAM_No.1(RAM_PULSE)から4クロック目に指定したライン定義番号に応じたラインの画素値を取得する。

【0113】

以上説明したように、ラインの先頭の画素値を取得(読み出す)するには、ライン間において5クロック分の待ち時間(待ちクロック)が必要となる。このため、デコーダ421によって連続して出力されるラインとラインとの間に、つぎのラインの先頭画素にアクセスするまでの期間相当分のクロック(待ちクロック)を設定する。これにより、ラインが変わる際に、ラインの先頭の画素値を読み出す際に必要となる5クロック分のクロック差により、印刷出力するためのデコード処理が追いつかず、ヘッドモジュール430において印刷出力するときの画像が途中で途切れてしまうなどの不具合を防ぐことができる。

【0114】

なお、同一ラインにおける画素値の読み出しをおこなう際は、デコーダ421は、RAM_No.1(RAM_PULSE)に対して順にアドレスを指定して、指定した順に画素値を読み出していけばよいため、図12に示すような複数の内部RAMからのデータの読み出しを連続的におこなう必要はない。

【0115】

このため、同一ラインにおけるすべての画素値の読み出しをおこなう際において、最初の画素値を読み出した以降は、RAM_No.1(RAM_PULSE)のアドレスのみを更新することによってリアルタイムに画素値を読み出すことができる。具体的には、画素値の繰り返し回数の最後の画素値を読み出すクロックと同クロックにおいて、RAM_No.1(RAM_PULSE)のアドレスを更新することによって連続して1つのライン分の画素値を読み出すことができる。

【0116】

しかしながら、読み出したデータがグループが変わったことを示すターミネータ情報であった場合には、ターミネータ情報を読み出したクロックと同一クロックにおいて出力すべき画素値の読み出しをおこなうことができないため、連続して1ライン分の画素値を読み出すことができなくなってしまう。ここで、ターミネータ情報を読み出してしまうことによって、連続して1ライン分の画素値を読み出すことができない場合の一例を図13を用いて説明する。

【0117】

図15は、連続して1ライン分の画素値を読み出すことができない場合の一例を示す説明図である。図15に示す読み出し例は、図2−1に示すライン定義に基づいて画素値を出力した場合の読み出し例である。図15に示すように、デコーダ421は、図13中矢印Aで示すクロックにおいて、図2に示すペア1(211)の118個目の画素値「0」を読み出し、RAM_No.1(RAM_PULSE)のアドレスを1つ加算(更新)する。つぎに、デコーダ421は、図2に示すペア2(212)の1個目の画素値「0」を読み出す。このとき、デコーダ421は、RAM_No.1(RAM_PULSE)のアドレスを更新しない。

【0118】

そして、デコーダ421は、ペア2(212)の画素値を順に読み出し、図15中矢印Bで示すクロックにおいて、ペア2(212)の80個目画素値「0」を読み出し、RAM_No.1(RAM_PULSE)のアドレスを1つ加算(更新)する。つぎに、デコーダ421は、図15中矢印Cで示すクロックにおいて、図2に示すペア3(213)の1個目の画素値「63」を読み出す。このとき、デコーダ421は、RAM_No.1(RAM_PULSE)のアドレスを更新しない。

【0119】

そして、デコーダ421は、ペア3(213)の画素値を順に読み出し、図15中矢印Eで示すクロックにおいて、ペア3(213)の4個目画素値「63」を読み出し、RAM_No.1(RAM_PULSE)のアドレスを1つ加算(更新)する。つぎに、デコーダ421は、図15中矢印Fで示すクロックにおいて、図2に示すペア4(221)の1個目の画素値「0」を読み出す必要があるのだが、ターミネータ情報を読み出してしまう。

【0120】

このため、ターミネータ情報を読み出したクロックと同一クロックにおいて出力すべきペア4(221)の1個目の画素値「0」の読み出しをおこなうことができないため、連続して1ライン分の画素値を読み出すことができない。この不具合を防ぐために、FPGAに設けられている簡易パターンファイル格納用内部RAMをデュアルポートRAMとし、デコーダ421は、リアルタイムに出力するための画素値(着目アドレスの画素値)を読み出すとともに、1つ先のアドレス(着目アドレスに「1」を加算したアドレス)の画素値および画素値の繰り返し回数を読み出すようにする。

【0121】

ここで、デュアルポートRAMとは、データの入出力のための信号のポート(出入口)が2つ設けられたRAMのことであり、1つのポートからデータを読み出すとともに、同時にもう一方のポートからデータを読み出すことができる。このとき、新たな記憶領域である内部RAMをさらに設け、この内部RAMに余分に読み出したデータを一時保存するようにしてもよい。そして、デコーダ421は、デュアルポートRAMから読み出したデータを用いて、アドレスを更新するか否かを判断するようにしてもよい。

【0122】

また、デコーダ421は、着目アドレスの画素値を繰り返し回数分読み出した際に、つぎのようにアドレスを更新する。デコーダ421は、読み出されたデータ(パターンデータ)に、付加情報であるターミネータ情報が含まれているか否かを判断する。そして、デコーダ421は、上記判断結果に基づいて、読み出されたデータを出力する。

【0123】

具体的には、デコーダ421は、着目アドレスのつぎのアドレスのデータがターミネータ情報か否を判断する。そして、着目アドレスのつぎのアドレスのデータがターミネータ情報ではなかった場合には、デコーダ421は、アドレスを「着目アドレス+1」に更新する。また、たとえば着目アドレスのつぎのアドレスのデータがターミネータ情報であった場合は、グループユニットの繰り返しが終了しているか否かによってアドレスの更新方法が異なる。

【0124】

まず、グループユニットの繰り返しが終了していなかった場合、デコーダ421は、現在出力中のグループユニットの先頭アドレスにアドレスを更新する。つぎに、グループユニットの繰り返しが終了している場合、デコーダ421は、つぎのグループユニットの先頭アドレス(着目アドレス+2)にアドレスを更新する。

【0125】

したがって、デコーダ421は、アドレスを更新する際に、その時点でどのようにアドレスを更新すればよいのかを把握しておく必要がある。このため、デコーダ421は、アドレスの更新をおこなうクロックの1つ前のクロックにおいて、更新方法を示すフラグを状態に応じてアドレスを更新する。なお、フラグのON/OFFの制御は、デコーダ421がそれぞれの画素値の繰り返し回数をカウントしながら判断するようにしてもよい。

【0126】

図16は、アドレス更新方法フラグの内容を示す説明図である。図16に示すアドレス更新表1400には、フラグ名称1401、フラグ名称が示す状態1402およびフラグがONになる条件1403が示されている。なお、図16に示す各フラグは、同時にONになる場合もあるが、アドレス更新表1400に示すフラグ名称1401の最上行から順に優先順位が付されている。このため、たとえば複数のフラグがONとなった場合、デコーダ421は、最も優先度が高いフラグのみをONにするようにしてもよい。

【0127】

ここで、デコーダ421によってフラグがONに制御される際の一例を説明する。たとえば、読み出した画素値のカウント値が「画素値の繰り返し回数−1」となった場合、具体的には、画素値を「繰り返し回数−1」分出力した際に、デコーダ421は、PixRepEndフラグ1404をONにする。

【0128】

上述したように、デコーダ421は、リアルタイムに画素値を出力するために、着目アドレスと着目アドレスに「1」を加算したアドレスに関するデータは常に読み出しておく必要がある。しかしながら、デコーダ421によってつぎのアドレスに関するデータを読み出して把握していたとしても、ターミネータ情報のつぎの画素値の繰り返し回数が「1」であった場合には、つぎのような問題が発生してしまう。

【0129】

図17は、簡易パターンファイルのライン定義の一例を示す図である。また、図18は、連続して1ライン分の画素値を読み出すことができない場合の一例を示す説明図である。図18に示す読み出し例は、図17に示すライン定義に基づいて画素値を出力した場合の読み出し例である。図18中矢印Aで示すクロックにおいて、デコーダ421は、図17に示すペア1503の3個目の画素値「63」を読み出すとともに、つぎのアドレスのデータであるターミネータ情報1504を把握している。このとき、図16に示すPixRepEndフラグ1404がONとなる。

【0130】

また、図18中矢印Bで示すクロックにおいて、デコーダ421は、ペア1503の4個目の画素値「63」を読み出すとともに、つぎのアドレスのデータであるターミネータ情報1504を把握している。このとき、PixRepEndフラグ1404がONであり、かつ、つぎのデータがターミネータ情報1504であるため、アドレスを「着目アドレス+2」に更新する。そして、図中16中矢印Cで示すクロックにおいて、デコーダ421は、ペア1504の1個目の画素値「0」を読み出すとともに、つぎのアドレスへの更新をおこなう。

【0131】

しかしながら、図18中矢印Cで示すクロックにおいて、アドレス変更方法が不定のため、つぎのアドレスへの更新をおこなうことができず、連続して1つのライン分の画素値を読み出すことができなくなってしまう問題が生じる。この問題は、ターミネータ情報1504のつぎのデータが事前にわかっていないために発生する問題であるため、つぎのような対策をすることによって解決することができる。

【0132】

たとえば、RAM_No.2(RAM_PULSE_NUM)に保存されているデータと同じデータを保存する別の内部RAMを設ける(たとえばRAM_No.10(RAM_PULSE_NUM)とする。)。そして、デコーダ421は、RAM_No.2(RAM_PULSE_NUM)に「着目アドレス」を指定して、「着目アドレス」のデータおよび「着目アドレス+1」のデータを読み出す。また、同時にデコーダ421は、RAM_No.10(RAM_PULSE_NUM)に「着目アドレス+2」を指定して、「着目アドレス+2」のデータおよび「着目アドレス+3」のデータを読み出す。

【0133】

このように、デコーダ421は、2つの内部RAMを用いて4つのアドレス分のデータを読み出すようにする。着目アドレスの更新は最大で「+2」であるため(つぎのグループユニットに変わる場合)、デコーダ421は、グループユニットが変わった直後であっても、常に着目アドレスの画素値の繰り返し回数と「着目アドレス+1」の画素値の繰り返し回数を把握することができるようになる。

【0134】

なお、RAM_No.2(RAM_PULSE_NUM)およびRAM_No.10(RAM_PULSE_NUM)を用いてデコーダ421が読み出したデータは、FPGA内に設けられた、それぞれ異なる第1の記憶領域および第2の記憶領域に一時保存されるように構成してもよい。

【0135】

ここで、着目アドレスを更新する際の読み出しデータの切り替え方法について説明する。デコーダ421は、読み出されたデータ(パターンデータ)に付加情報であるターミネータ情報が含まれていると判断した場合は、ターミネータ情報のつぎに読み出されたデータ(パターンデータ)の内容をさらに判断する。そして、この判断結果に基づいて、上述した第1の記憶領域または第2の記憶領域からデータ(パターンデータ)を読み出して、読み出した当該パターンデータを出力する。

【0136】

具体的には、たとえばデコーダ421が図17に示すペア1501を出力しているときには、デコーダ421が読み出しておくべき読出データは、ペア1501、ペア1502、ペア1503、ターミネータ情報1504であり、必要としている読出データは、ペア1501およびペア1502である。このとき、ペア1501の画素値「0」が118回繰り返された場合は、必要とする読出データをペア1502およびペア1503に切り替える。

【0137】

また、デコーダ421が図17に示すペア1502を出力しているときには、デコーダ421が読み出しておくべき読出データは、ペア1502、ペア1503、ターミネータ情報1504、ペア1505であり、必要としている読出データは、ペア1502およびペア1503である。このとき、ペア1502の画素値「0」が80回繰り返された場合は、必要とする読出データをペア1503およびターミネータ情報1504に切り替える。

【0138】

さらに、デコーダ421が図17に示すペア1503を出力しているときには、デコーダ421が読み出しておくべき読出データは、ペア1503、ターミネータ情報1504、ペア1505、ペア1506であり、必要としている読出データは、ペア1503およびターミネータ情報1504である。このとき、ペア1503の画素値「63」が4回繰り返された場合は、必要とする読出データをペア1505およびペア1506に切り替える。

【0139】

なお、上述したように4つ分のアドレスに関するデータを読み出すように構成したのは、つぎのような問題が生じてしまう場合があるからである。具体的には、たとえばターミネータ情報の直後のデータが、画素値の繰り返し回数が「1」であり、かつそのつぎのデータがターミネータ情報であった場合、画素値の繰り返し回数が「1」のつぎのデータがターミネータ情報であることをあらかじめデコーダ421が把握することができず、アドレス変更方法が不定となってしまう問題が生じてしまうためである。

【0140】

また、この発明の実施の形態にかかる開発・メンテナンス用ツール400では、フラッシュメモリから読み出した画像を形成するためのパターンデータを、バッファメモリなどに一時保存することなく連続的に出力する構成としたが、パターンデータを出力する際の方式はこれに限られない。たとえば、開発・メンテナンス用ツール400にバッファメモリを備えたPC(パーソナルコンピュータ)を接続し、画像を形成するためのパターンデータをすべてPCのバッファメモリに一時保存する。そして、FPGAは、PC内部のバッファメモリからパターンデータを読み出して、ヘッドモジュール430に画像のパターンデータを印刷出力させる構成としてもよい。

【0141】

以上説明したように、この発明の実施の形態にかかる画像データ処理方法によれば、読み込んだ簡易パターンファイル100を簡易パターンファイル格納用内部RAMである複数の内部RAMに、連続的に読み出すことができる状態で再配置して保存し、この保存した簡易パターンファイル100を画像を形成するための順序にしたがって読み出すことができる。そして、読み出した画像データを画像のラインごとに連続的に出力することができるため、ヘッドモジュール430の画質評価をおこなう際に、出力された画像が途中で途切れてしまうなどの不具合を防ぐことができ、適切な画質評価をおこなうことができる。

【0142】

さらに、この画像データ処理方法によれば、連続して出力されるラインとラインとの間に、つぎのラインの先頭画素にアクセスするまでの待ちクロックを設定することができるため、ヘッドモジュール430の画質評価をおこなう際に、1つのラインの出力が終了してつぎのラインの先頭画素にアクセスするまでのクロックによって先頭画素の読み出しが間に合わず、ラインとラインとの間で画像が途切れてしまうなどの不具合を防ぐことができ、適切な画質評価をおこなうことができる。

【0143】

また、この画像データ処理方法によれば、読み出された簡易パターンファイル100にターミネータ情報が含まれているか否かをあらかじめ判断することができ、この判断結果に応じて簡易パターンファイル100を連続的に出力することができるため、ヘッドモジュール430の画質評価をおこなう際に、出力された画像が途中で途切れてしまうなどの不具合を防ぐことができ、適切な画質評価をおこなうことができる。

【0144】

さらに、この画像データ処理方法によれば、読み出された簡易パターンファイル100に含まれるターミネータ情報のつぎに読み出される簡易パターンファイル100の内容をあらかじめ判断し、この判断結果に応じて第1の記憶領域または第2の記憶領域から簡易パターンファイル100を読み出して簡易パターンファイル100を連続的に出力することができるため、ヘッドモジュール430の画質評価をおこなう際に、出力された画像が途中で途切れてしまうなどの不具合を防ぐことができ、適切な画質評価をおこなうことができる。

【0145】

なお、本実施の形態で説明した開発・メンテナンス方法は、あらかじめ用意されたプログラムをパーソナル・コンピュータやワークステーションなどのコンピュータで実行することにより実現することができる。このプログラムは、ハードディスク、フレキシブルディスク、CD−ROM、MO、DVDなどのコンピュータで読み取り可能な記録媒体に記録され、コンピュータによって記録媒体から読み出されることによって実行される。またこのプログラムは、インターネットなどのネットワークを介して配布することが可能な伝送媒体であってもよい。

【図面の簡単な説明】

【0146】

【図1】簡易パターンファイルのデータ構造の一例を示す説明図。

【図2−1】簡易パターンファイルのライン定義の一例を示す図。

【図2−2】図2−1に示すライン定義の内容を示す説明図。

【図3】簡易パターンファイルのライン配置の一例を示す図。

【図4】本発明の実施の形態に係る画像形成装置の開発・メンテナンス用ツールにおけるインデックステーブルを示す図。

【図5】インデックステーブルを利用して表された簡易パターンファイルのデータ構造の一例を示す説明図。

【図6】画像データ処理システムのシステム構成の一例を示すブロック図。

【図7】簡易パターンファイル格納用内部RAMの概要を説明するための説明図。

【図8−1】簡易パターンファイルのサンプルの一例を示す説明図。

【図8−2】簡易パターンファイル格納用内部RAM状態を示すテーブル。

【図9】FPGAの機能的構成を示すブロック図。

【図10】FPGAの処理の手順を示すフローチャート。

【図11−1】モジュール内メモリがおこなう処理の手順を示すフローチャート。

【図11−2】モジュール内メモリがおこなう処理の手順を示すフローチャート。

【図12−1】画像サイズ算出部がおこなう処理の手順を示すフローチャート。

【図12−2】画像サイズ算出部がおこなう処理の手順を示すフローチャート。

【図13】デコーダがおこなう処理の手順を示すフローチャート。

【図14】ラインの先頭の画素値を読み出すまでのクロック数を示す説明図。

【図15】画素値を読み出すことができない場合の一例を示す説明図。

【図16】アドレス更新方法フラグの内容を示す説明図。

【図17】簡易パターンファイルのライン定義の一例を示す図。

【図18】画素値を読み出すことができない場合の一例を示す説明図

【符号の説明】

【0147】

100・・・簡易パターンファイル、101・・・ライン定義部、102・・・ライン配置部、110〜116・・・ライン定義部1〜ライン定義部7、120〜123・・・ゾーン0〜ゾーン3、124・・・色情報、400・・・開発・メンテナンス用ツール、410・・・簡易パターンメモリ、411・・・簡易パターンデータファイル、412・・・インデックステーブル、420・・・デコードモジュール、421・・・デコーダ、422・・・モジュール内メモリ、423・・・出力制御部、424・・・画像サイズ算出部、430・・・ヘッドモジュール

【特許請求の範囲】

【請求項1】

簡易パターンを生成して、当該簡易パターンをヘッドモジュールに転送することによって画像形成装置の開発やメンテナンスの際のテスト印刷を行う画像形成装置の開発・メンテナンス用ツールにおいて、

当該簡易パターンに頻出するデータ配列の少なくとも一部をインデックス番号で代表したパターンデータが記憶されているインデックステーブルを記憶するインデックステーブル記憶手段と、当該インデックス番号を用いて記述された簡易パターンデータファイルを記憶する簡易パターンデータファイル記憶手段とを有し、当該簡易パターンを該簡易パターンデータファイル記憶手段と該インデックステーブル記憶手段を読み出すことによって生成することを特徴とする画像形成装置の開発・メンテナンス用ツール。

【請求項2】

簡易パターンを生成して、当該簡易パターンをヘッドモジュールに転送することによって画像形成装置の開発やメンテナンスの際のテスト印刷を行う画像形成装置の開発・メンテナンス方法において、

当該簡易パターンに頻出するデータ配列の少なくとも一部をインデックス番号で代表したパターンデータが記憶されているインデックステーブルを準備するステップと、当該インデックス番号を用いて記述された簡易パターンデータファイルを準備するステップと、該簡易パターンデータファイルと該インデックステーブルを参照することによって当該簡易パターンを生成するステップとを含むことを特徴とする画像形成装置の開発・メンテナンス用ツール。

【請求項1】

簡易パターンを生成して、当該簡易パターンをヘッドモジュールに転送することによって画像形成装置の開発やメンテナンスの際のテスト印刷を行う画像形成装置の開発・メンテナンス用ツールにおいて、

当該簡易パターンに頻出するデータ配列の少なくとも一部をインデックス番号で代表したパターンデータが記憶されているインデックステーブルを記憶するインデックステーブル記憶手段と、当該インデックス番号を用いて記述された簡易パターンデータファイルを記憶する簡易パターンデータファイル記憶手段とを有し、当該簡易パターンを該簡易パターンデータファイル記憶手段と該インデックステーブル記憶手段を読み出すことによって生成することを特徴とする画像形成装置の開発・メンテナンス用ツール。

【請求項2】

簡易パターンを生成して、当該簡易パターンをヘッドモジュールに転送することによって画像形成装置の開発やメンテナンスの際のテスト印刷を行う画像形成装置の開発・メンテナンス方法において、

当該簡易パターンに頻出するデータ配列の少なくとも一部をインデックス番号で代表したパターンデータが記憶されているインデックステーブルを準備するステップと、当該インデックス番号を用いて記述された簡易パターンデータファイルを準備するステップと、該簡易パターンデータファイルと該インデックステーブルを参照することによって当該簡易パターンを生成するステップとを含むことを特徴とする画像形成装置の開発・メンテナンス用ツール。

【図1】

【図2−1】

【図2−2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8−1】

【図8−2】

【図9】

【図10】

【図11−1】

【図11−2】

【図12−1】

【図12−2】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2−1】

【図2−2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8−1】

【図8−2】

【図9】

【図10】

【図11−1】

【図11−2】

【図12−1】

【図12−2】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2008−17163(P2008−17163A)

【公開日】平成20年1月24日(2008.1.24)

【国際特許分類】

【出願番号】特願2006−186299(P2006−186299)

【出願日】平成18年7月6日(2006.7.6)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成20年1月24日(2008.1.24)

【国際特許分類】

【出願日】平成18年7月6日(2006.7.6)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]