画像形成装置及びその電力制御方法、並びにプログラム

【課題】本発明は、小規模回路モジュール単位で複雑な制御を必要とせずに電力制御を行うことが可能となり、省電力が可能となる画像形成装置を提供する。

【解決手段】電源制御回路とを備える画像形成装置は、電源供給が開始されてから電源制御対象モジュールの電源安定時間が経過するまで待機すると共に、電源供給が開始されてからの経過時間を計測する。得られた経過時間から電源制御対象モジュールへの電源供給をOFFするか否かを判断し、OFFと判断されたときは、電源制御対象モジュールへの電源供給をOFFする。

【解決手段】電源制御回路とを備える画像形成装置は、電源供給が開始されてから電源制御対象モジュールの電源安定時間が経過するまで待機すると共に、電源供給が開始されてからの経過時間を計測する。得られた経過時間から電源制御対象モジュールへの電源供給をOFFするか否かを判断し、OFFと判断されたときは、電源制御対象モジュールへの電源供給をOFFする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像形成装置及びその電力制御方法、並びにプログラムに関し、特に、電源分離されたブロックを対象とした動作時の電源制御を行う電力制御技術に関する。

【背景技術】

【0002】

現在、地球温暖化対策により省電力に対する関心が高まっているが、省電力に関する提案は多数ある。例えば、CPUとバスに接続された周辺装置の消費電力を制御する手段について、CPUからのアクセス開始とアクセス終了を検出し、その検出結果から周辺装置のスリープモードを制御する技術が提案されている(特許文献1参照)。

【0003】

上記提案技術は、製品システムとして電力制御による省電力を図るものであるが、近年では、LSI内部での省電力技術が進歩している。例えば、クロックゲーティング技術によって、動作に不要なモジュールのクロックを停止する技術や、LSI内部の電源を分離して動作に不要なモジュールの電源をOFFする技術などがある。特に、電源分離技術に関しては、ソフトウエアで制御によって、スリープモード時に不要なモジュールの電源をOFFして省電力を図っている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2003−185716号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上述した特許文献1に記載の技術や電源分離技術では、特定のモード時にある程度大きな回路規模単位で電源ON/OFFを行い、CPUなどの制御を行う部分のみ通電して省電力を実現している。今後さらなる省電力を図るためには、動作中において小規模モジュール単位で電源制御を行う必要がある。

【0006】

また、小規模モジュール単位で電源制御を行う場合、電源制御するモジュール数が多くなるので、ソフトウエアによる制御では処理が複雑で電源制御する時間が長くなり、動作パフォーマンスに影響するおそれがある。

【0007】

また、対象モジュールの電源をONしてから電源状態が安定して使用可能になるまでには一定時間を要するため、早い応答が要求されているときに電源OFFを行うと動作パフォーマンスに影響するおそれがある。

【0008】

本発明は、上記問題に鑑みて成されたものであり、小規模回路モジュール単位で複雑な制御を必要とせずに電力制御を行うことが可能となり、省電力が可能となる技術を提供する。

【課題を解決するための手段】

【0009】

上記目的を達成するために、本発明の画像形成装置は、複数のモジュール単位で所定の動作処理を実行する制御手段と、前記複数のモジュールからバス信号を受信して、当該モジュールの電源ON/OFFを制御する電源制御回路とを備える画像形成装置において、電源制御対象となるモジュールの電源状態を認識する認識手段と、前記電源制御対象モジュールに入力されるデータ有効信号に応じて当該モジュールへの電源供給をONする電源ON手段と、前記電源ON手段による電源供給が開始されてから前記電源制御対象モジュールの電源安定時間が経過するまで待機する待機手段と、前記電源ON手段による電源供給が開始されてからの経過時間を計測する計測手段と、前記計測手段により得られた経過時間から前記電源制御対象モジュールへの電源供給をOFFするか否かを判断する判断手段と、前記判断手段にてOFFと判断されたときは、前記電源制御対象モジュールへの電源供給をOFFする電源OFF手段とを有することを特徴とする。

【発明の効果】

【0010】

本発明によれば、小規模回路モジュール単位で複雑な制御を必要とせずに電力制御を行うことが可能となり、省電力が可能となる。

【図面の簡単な説明】

【0011】

【図1】本発明の実施形態に係る画像形成装置のハードウェア構成の概略を示すブロック図である。

【図2】図1のコントローラにおける機能構成の概略を示す図である。

【図3】画像データの処理単位として1ページ分の画像データを複数のバンドに分割した一例を示す図である。

【図4】図2におけるプリント用画像処理ブロックと電源制御回路との間の信号の流れを示すブロック図である。

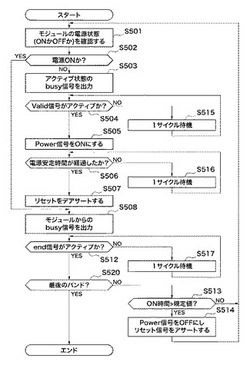

【図5】第1の実施形態における電源制御回路による電源制御処理の流れを示すフローチャートである。

【図6】図4で説明した各種バス信号の電源制御処理時の波形例を示す図である。

【図7】(a)はON時間<規定値となった場合の電源制御対象モジュールの電源制御方法を示す図、(b)はON時間>規定値となった場合の電源制御対象モジュールの電源制御方法を示す図である。

【図8】第2の実施形態における電源制御回路による電源制御処理の流れを示すフローチャートである。

【図9】第2の実施形態におけるON時間<規定値となった場合の電源制御対象モジュールの電源制御方法を示す図である。

【図10】(a)は第1の実施形態における電源制御対象モジュールの電源制御方法を示す図、(b)は第3の実施形態における電源制御対象モジュールの電源制御方法を示す図である。

【発明を実施するための形態】

【0012】

以下、本発明の実施の形態を図面を参照して詳細に説明する。

【0013】

[第1の実施形態]

図1は、本発明の実施形態に係る画像形成装置のハードウェア構成の概略を示すブロック図である。

【0014】

本発明の実施形態に係る画像形成装置は、例えば、スキャナ機能、プリント機能、コピー機能等を備えるデジタル複合機(以下「MFP」と称する)である。MFPは、図示のように、コントローラ101、スキャナ部102、プリンタ部103、ネットワークI/F104、メモリ105、HDD106、及び操作部107を備える。

【0015】

コントローラ101は、システムバス108を介して画像入力デバイスであるスキャナ部102や画像出力デバイスであるプリンタ部103と接続し、これらを制御する。また、コントローラ101は、ネットワークI/F104を介してLANや公衆回線(WAN)等に接続し、画像情報やデバイス情報の入出力、PDLデータのイメージ展開を行うことができる。

【0016】

メモリ105は、コントローラ101が動作するためのシステムワークメモリであり、画像データを一時記憶するための画像メモリでもある。HDD106は、ハードディスクドライブ(HDD)であり、システムソフトウェア、画像データを格納する記憶装置である。操作部107は、タッチパネルやキーボードなどで構成され、MFPを使用するユーザーが様々な印刷設定等を行うためのユーザーインターフェースである。

【0017】

次に、図1のコントローラ101の動作について図2を用いて説明する。なお、以降で説明する画像データの処理単位は、図3に示すように、1ページ分の画像データを複数のバンド(ここでは10バンド)に分割したバンド単位とする。また、コントローラ101では、複数のモジュール単位で所定の動作処理が実行される。

【0018】

まず、スキャンデータを読み込む場合を説明する。

【0019】

コントローラ101は、スキャナ部102からRGB(RED、GREEN、BLUE)3色のスキャンデータ(読み取り画像データ)を受け取ると、スキャナ用画像処理部201にてシェーディング処理やフィルタ処理等の画像処理を行う。その後、スキャンデータに対して圧縮部202にて画像圧縮処理が行われる。その圧縮データは、DMAC(DIRECT MEMORY ACCESS CONTROLLER)203を介してメモリ105へ格納される。上記動作を行うスキャナ用画像処理部201、圧縮部202、及びDMAC203を含む機能ブロックがスキャナ用画像処理ブロック200である。

【0020】

スキャンデータをプリントする場合は、メモリ105に格納されている圧縮データが、DMAC211を介して色処理部212へ入力され、CMYK(CYAN、MAGENTA、YELLOW、BLACK)色空間へ変換される。その後、それらCMYKの値に対して濃度調整、プリンタガンマ補正等の調整の色処理が行われた後、DMAC211を介して再度メモリ105へ格納される。本動作を行うDMAC211、色処理部212を含む機能ブロックが色処理ブロック210である。

【0021】

そして、プリント用の画像処理を行うために、メモリ105に格納されている圧縮データが、DMAC221を介して展開部222へ入力され、ラスタ画像データへ展開される。ラスタのCMYK画像データは、プリント用画像処理部223に入力され、そこでディザ法や誤差拡散法による面積階調処理が行われ、プリンタ部103へ出力される。本動作を行うDMAC221、展開部222、プリント用画像処理部223を含む機能ブロックがプリント用画像処理ブロック220である。

【0022】

スキャンデータをネットワークへ送信する場合、メモリ105に格納されている圧縮データが、DMAC211を介して色処理部212へ入力され、色変換が行われる。具体的には、ディスプレイガンマ調整や用紙地色調整等が行われた後にYCbCr(輝度、BLUE色差、RED色差)色空間へ変換される。その後、再度DMAC211を介してメモリ105へ格納される。

【0023】

そして、送信用の画像処理を行うために、メモリ105に格納されている圧縮データが、DMAC231を介して展開部232へ入力され、ラスタ画像データへ展開される。ラスタのYCbCr画像データに対して、送信処理部233では、カラー画像送信であればJPEG圧縮処理を行い、モノクロ2値画像送信であればYデータに対して2値化を行ってJBIG圧縮等を行い、ネットワークI/F104へ出力する。本動作を行うDMAC231、展開部232、送信処理部233を含む機能ブロックがネットワーク処理ブロック230である。

【0024】

スキャンデータを保存する場合には、メモリ105に格納されている圧縮データが、DMAC241を介してディスクスプール高圧縮/展開部242へ入力される。ディスクスプール高圧縮/展開部242では、HDD106の書き込みスピードがメモリ105に対して遅いため、圧縮データに対して、さらに高圧縮のJPEG圧縮処理を施す。その後、ディスクアクセスコントローラ243を介してHDD106へ圧縮データが保存される。本動作を行うDMAC241、ディスクスプール高圧縮/展開部242、ディスクアクセスコントローラ243を含む機能ブロックがHDD処理ブロック240である。なお、HDD106に保存されているデータを再度メモリ105へ展開する場合はそれらの逆処理を行う。

【0025】

PDLのデータをメモリ105へ書き込む場合、ネットワークを介して受信したPDLデータを受信部282で受信してDMAC281を介してメモリ105に格納する。本動作を行うDMAC281、受信部282を含む機能ブロックがネットワーク受信ブロック280である。

【0026】

次に、CPU260は、メモリ105に格納されたPDLデータを読み出してインタープリットし、メモリ105へディスプレイリストを出力する。その後、メモリ105に格納されているディスプレイリストをレンダリング部251でラスタのRGB画像データへとレンダリングを行い、圧縮部252にて画像圧縮処理が行行われる。その圧縮データは、DMAC253を介してメモリ105へ格納される。本動作を行うレンダリング部251、圧縮部252、DMAC253を含む機能ブロックがレンダリングブロック250である。

【0027】

なお、PDLの画像データをプリントしたり、ネットワークへ送信したり、メモリ105に保存する場合は、上述したスキャンデータに対する処理と同様の処理を行うことで実現することが可能になる。

【0028】

ここで図2に示すブロック単位で電源制御を行う方法について説明する。

【0029】

CPU260からの命令によってPMU(Power Management Unit)270が、上述した各機能ブロックの電源SW制御信号やリセット制御信号を出力する。電源SW制御信号は、機能ブロックごとに出力される。リセット制御信号は、PMU270から不図示のリセット制御モジュールへ出力される。リセット制御モジュールは、各機能ブロックのリセット解除タイミングを制御する。

【0030】

本実施形態では、モード電源制御方法を利用しているが、スリープ時は全ての機能ブロックの電源OFFし、ネットワークからPDLデータを受信した際に、CPU260がPMU270に信号を出力して電源をONにする方法がある。

【0031】

図4は、図2におけるプリント用画像処理ブロック220と電源制御回路との間の信号の流れを示すブロック図である。同図では、図2で説明したDMAC221と展開部222とプリント用画像処理部223がバスによってパイプラインで接続された様子を示している。電源制御回路401は、展開部222の電源ON/OFF制御、バス信号制御を行うものである。電源制御回路402は、プリント用画像処理部223の電源ON/OFF制御、バス信号制御を行うものである。

【0032】

DMAC221と展開部222との間を例にして、各種モジュール(処理部)間のバス信号(データ有効信号)について説明する。

【0033】

data_A403は圧縮データである。end_A404は、DMAC221からのデータ転送の1バンド分が終了したことを示す信号である。valid_A405は、valid_A405がアクティブの期間にdata_A403が有効なことを示す信号である。busy_PB406は、busy_PB406がアクティブの期間はDMAC221からのデータを受信側が受信できないことを示す信号である。

【0034】

end_PA407とvalid_PA408は、電源制御回路401の入力信号であるend_A404とvalid_A405をそのまま出力した信号である。busy_B409は、展開部222から電源制御回路401に出力される信号である。busy_PB406は、展開部222が電源OFF状態である場合に、busy_B409の信号にかかわらずアクティブ状態にする。また、展開部222が電源ON状態のときは、busy_PB406にbusy_B409がそのまま出力される。

【0035】

reset_L_B410は、展開部222のリセット信号である。power_B411は、展開部222への電源供給を制御する信号である。end_B412は、展開部222から後段のモジュールであるプリント用画像処理部223へのデータ転送の1バンド分が終了したことを示す信号である。

【0036】

なお、図4では、電源制御回路401,402と、電源制御対象ごとに分割した電源制御回路の構成で説明したが、一つの電源制御回路で構成してもかまわない。

【0037】

図5は、第1の実施形態における電源制御回路401,402による電源制御処理の流れを示すフローチャートである。本処理は、1ページ分の画像データ、すなわち10バンドの画像データを処理する場合に対応する。

【0038】

図6は、図4で説明した各種バス信号の電源制御処理時の波形例を示す図である。図示例では、説明を簡単にするため、1バンドのデータ量を4ワードとしている。以下の説明は、特に明記していない限り、全て電源制御回路401,402を主体とする動作である。

【0039】

ステップS501では、電源制御対象モジュールの電源供給のON/OFF状態を確認する。電源制御対象モジュールは、例えば、図2に示した各種モジュールである。

【0040】

次に、ステップS502では、電源制御対象モジュールが電源ON状態である場合は、ステップS503に進む一方、電源OFF状態である場合はステップS508に進む。

【0041】

ステップS503では、前段モジュールのbusy信号(busy_PB406)に、アクティブ状態の信号レベルで出力する。つまり、前段モジュールには、busy状態であることを認識させる。前段モジュールとは、電源制御対象モジュールに対してパイプラインで前段に接続されるモジュールのことであり、以降においても前段モジュールと称す。

【0042】

ステップS504では、前段モジュールから出力されるvalid信号がアクティブであるか否かを判断する。アクティブである場合はステップS505へ進む。一方、アクティブでないときは、ステップS515で1サイクル待機して再びステップS504へ戻る。図6に示す波形ではサイクル(cycle)1に相当する。

【0043】

ステップS505では、power信号(power_B411)をアクティブ状態にし、電源ONする。図6に示す波形ではサイクル2に相当する。電源制御回路401内のON時間計測手段421は、この時点から計測を開始する。

【0044】

ステップS506では、電源制御対象モジュールの電源安定時間が経過したかどうかを判断する。電源安定時間とは、電源ON後に定常状態に遷移するまでの時間を意味する。図6に示す波形ではサイクル2からサイクル3までに相当する。電源安定時間は、電源制御対象モジュールで消費する静的電流量(回路規模)で決定され、電源制御回路401,402に予め設定されている。電源安定時間が経過した場合には、ステップS507に進む。

【0045】

ステップS507では、リセット信号(reset_L_B410)をデアサートし、電源制御対象モジュールのリセットを解除する。図6に示す波形ではサイクル4に相当する。

【0046】

ステップS508では、電源制御対象モジュールが出力するbusy信号(busy_B409)をそのまま前段モジュールのbusy信号(busy_PB406)として出力する。図6に示す波形ではサイクル5に相当する。

【0047】

ステップS512では、電源制御対象モジュールが出力するend信号(end_B412)がアクティブかどうかを判断する。アクティブである場合には、バンドの終わりを認識してステップS520へ進む。一方、アクティブでないときは、ステップS517で1サイクル待機して再びステップS512へ戻る。

【0048】

ステップS520では、処理したバンドが最後のバンドかどうか判断する。最後であればフロ−を終了する。最後でなければステップS513へ進む。

【0049】

ステップS513では、ON時間計測手段421がステップS505で計測を開始したときの経過時間(以降「ON時間」と呼ぶ)を取得する(ステップS502で既に電源供給がONだったときはステップS502からの経過時間を「ON時間」とする)。そして、取得したON時間(第1の経過時間)が規定値よりも小さいかどうかを判断し、小さければステップS514へ進み、power信号(power_B411)を非アクティブ状態にし、電源をOFFする。そして、リセット信号(reset_L_B410)をアサートし、リセット状態にする。一方、ステップS513でON時間が規定値よりも大きいと判断された場合、ステップS514がスキップされるので、電源はONのままの状態でステップS501へ戻る。

【0050】

ここで規定値の定め方について図7(a)、図7(b)を用いて説明する。

【0051】

仮にMFPのプリンタ部103が1ページを印刷するのに1秒かかるとする。1ページは10バンドで構成されることから、1バンドは100msec以内で処理されなければならない。100msec以内に処理できないバンドが続くと、プリント動作に対して画像データの供給が間に合わない、いわゆるバッファアンダーランエラーが発生する。そこで、ON時間計測手段により取得したON時間の比較対象となる規定値は100msecとしている。また、電源制御対象モジュールである展開部222の電源安定化時間を10msecとする。

【0052】

図7(a)及び図7(b)では、ともに時刻0で電源をONして、電源安定化時間(10msec)が経過した後に展開処理を開始する例を示している。

【0053】

図7(a)に示す例では、展開処理が80msecで終了するので、ON時間<規定値となる。1バンドを処理するために要求される時間の100msecに対して、20msecの余裕があるので、省電力のために電源をOFFする。

【0054】

一方、図7(b)に示す例では、展開処理に95msecかかったため、105msecで処理が終了する。つまり、ON時間>規定値となるので電源をOFFしない。よって、次のバンドの処理の前に電源安定化時間をおく必要がなく、バッファアンダーランの発生を軽減することができる。

【0055】

なお、図7(a)、図7(b)の例では、規定値を100msecとしたが安全性を考えて95msecなどやや小さい値を用いてもよい。一般に展開部222とプリンタ部103の間に緩衝となる不図示のバッファが多ければ局所的な処理の遅延は許容されるが、バッファが少ない場合はその逆となる。

【0056】

第1の実施形態によれば、複数の電源分離されたブロックがバスによってパイプライン接続され、回路モジュールの電源制御について、ソフトウエアの制御無しに動作時に必要なときだけ電源をONすることが可能となる。これにより、小規模回路モジュール単位で複雑な制御を必要とせずに電力制御を行うことが可能となり、省電力が可能となる。

【0057】

また、小規模回路モジュールがデータ処理を終えたとき電源をOFFすると必要なパフォーマンスを満たさないときは、電源をOFFしない判断をソフトウエアの制御無しに行うことができるので、省電力を行いつつ必要なパフォーマンスを維持することができる。

【0058】

[第2の実施形態]

本発明の第2の実施の形態に係る画像形成装置は、その構成(図1〜図4)が上記第1の実施の形態に係る画像形成装置と同じであり、第1の実施の形態と同様の部分については、同一の符号を用いてその説明を省略する。以下に、上記第1の実施の形態と異なる点を図6、図8を用いて説明する。

【0059】

第1の実施形態では、図6のステップS514で電源OFF後、ステップS501、S502、S503を経由してステップS504でValid信号を待ち、Valid信号を受信してからステップS505にて電源ON状態へ移行する。

【0060】

一方、第2の実施形態では、図8のステップS514で電源がOFFされた後、さらにステップS515にて待ち時間であるOFF時間(第2の経過時間)を決定し、OFF時間が経過したならばステップS505にて電源ON状態へ移行する。

【0061】

OFF時間の考え方については図9を用いて説明する。

【0062】

第1の実施形態と異なる点は、1バンドの処理が終了したときの動作のみである。第1の実施形態では、Valid信号の受信をトリガーにして電源ONを行うものである。これに対して、本第2の実施形態では、図9に示すように、80msecで処理が終わったならば、20msecの余裕があるので、Valid信号によらず電源供給OFF状態を保って省電力を優先する。また、20msec経過したならば直ちに電源ON処理に移行するので、バッファアンダーランの発生を軽減することができる。

【0063】

なお、舵2の実施形態では、OFF時間=100msec−ON時間としたが、安全を考えて、例えば、OFF時間=100msec−ON時間―5msec(負のときはOFF時間=0とする)としてもよい。

【0064】

[第3の実施形態]

本発明の第3の実施の形態に係る画像形成装置は、その構成(図1〜図4)が上記第1の実施の形態に係る画像形成装置と同じであり、第1の実施の形態と同様の部分については、同一の符号を用いてその説明を省略する。以下に、上記第1の実施の形態と異なる点を図10(a)、図10(b)を用いて説明する。

【0065】

第1及び第2の実施形態において、1バンドの処理時間がパフォーマンスを満たすために要求される時間を上回ってしまった場合に着目する。

【0066】

図10(a)及び図10(b)では、ともに1バンド目の処理を110msecで終了して、2バンド目の処理を時刻205msecで終了する。

【0067】

第1の実施形態では1バンドごとにON時間を計測する。そのため、2バンド目の処理が終了した時点(205msec経過時)でON時間=95msecとなり、規定値より小なので電源がOFFされる。2バンドの処理全体でみるとこれは不適切である。なぜならパフォーマンスを満たすためには2バンドを200msec以内で処理する必要があるからである。

【0068】

第3の実施形態としては、複数のバンド単位で処理時間を計測して上記の問題を軽減する。つまり、図10(b)に示すように、2バンド分のON時間を用いて2バンド分の規定値(200msec)と比較して電源をOFFするか否かをステップS513にて判定する。なお、本実施形態では、2バンド分のON時間を用いた場合について説明したが、これに限定されるものではなく、複数回分のON時間の合計に基づいて電源をOFFするか否かを判断するように構成してもよい。

【0069】

なお、バッファアンダーランに対する安全のため、上記規定値として200msecよりも小さい値を選んでもよい。

【0070】

上記第1〜第3の実施形態では、電源制御対象モジュールがON時間を測定する基本単位として、画像データをバンド単位に分割した場合について説明したが、画像データを矩形単位で分割したり、またデータ量単位で分割したりしてもよい。

【0071】

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(またはCPUやMPU等)がプログラムを読み出して実行する処理である。

【符号の説明】

【0072】

101 コントローラ

105 メモリ

221 DMAC

222 展開部

223 プリント用画像処理部

401,402 電源制御回路

【技術分野】

【0001】

本発明は、画像形成装置及びその電力制御方法、並びにプログラムに関し、特に、電源分離されたブロックを対象とした動作時の電源制御を行う電力制御技術に関する。

【背景技術】

【0002】

現在、地球温暖化対策により省電力に対する関心が高まっているが、省電力に関する提案は多数ある。例えば、CPUとバスに接続された周辺装置の消費電力を制御する手段について、CPUからのアクセス開始とアクセス終了を検出し、その検出結果から周辺装置のスリープモードを制御する技術が提案されている(特許文献1参照)。

【0003】

上記提案技術は、製品システムとして電力制御による省電力を図るものであるが、近年では、LSI内部での省電力技術が進歩している。例えば、クロックゲーティング技術によって、動作に不要なモジュールのクロックを停止する技術や、LSI内部の電源を分離して動作に不要なモジュールの電源をOFFする技術などがある。特に、電源分離技術に関しては、ソフトウエアで制御によって、スリープモード時に不要なモジュールの電源をOFFして省電力を図っている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2003−185716号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、上述した特許文献1に記載の技術や電源分離技術では、特定のモード時にある程度大きな回路規模単位で電源ON/OFFを行い、CPUなどの制御を行う部分のみ通電して省電力を実現している。今後さらなる省電力を図るためには、動作中において小規模モジュール単位で電源制御を行う必要がある。

【0006】

また、小規模モジュール単位で電源制御を行う場合、電源制御するモジュール数が多くなるので、ソフトウエアによる制御では処理が複雑で電源制御する時間が長くなり、動作パフォーマンスに影響するおそれがある。

【0007】

また、対象モジュールの電源をONしてから電源状態が安定して使用可能になるまでには一定時間を要するため、早い応答が要求されているときに電源OFFを行うと動作パフォーマンスに影響するおそれがある。

【0008】

本発明は、上記問題に鑑みて成されたものであり、小規模回路モジュール単位で複雑な制御を必要とせずに電力制御を行うことが可能となり、省電力が可能となる技術を提供する。

【課題を解決するための手段】

【0009】

上記目的を達成するために、本発明の画像形成装置は、複数のモジュール単位で所定の動作処理を実行する制御手段と、前記複数のモジュールからバス信号を受信して、当該モジュールの電源ON/OFFを制御する電源制御回路とを備える画像形成装置において、電源制御対象となるモジュールの電源状態を認識する認識手段と、前記電源制御対象モジュールに入力されるデータ有効信号に応じて当該モジュールへの電源供給をONする電源ON手段と、前記電源ON手段による電源供給が開始されてから前記電源制御対象モジュールの電源安定時間が経過するまで待機する待機手段と、前記電源ON手段による電源供給が開始されてからの経過時間を計測する計測手段と、前記計測手段により得られた経過時間から前記電源制御対象モジュールへの電源供給をOFFするか否かを判断する判断手段と、前記判断手段にてOFFと判断されたときは、前記電源制御対象モジュールへの電源供給をOFFする電源OFF手段とを有することを特徴とする。

【発明の効果】

【0010】

本発明によれば、小規模回路モジュール単位で複雑な制御を必要とせずに電力制御を行うことが可能となり、省電力が可能となる。

【図面の簡単な説明】

【0011】

【図1】本発明の実施形態に係る画像形成装置のハードウェア構成の概略を示すブロック図である。

【図2】図1のコントローラにおける機能構成の概略を示す図である。

【図3】画像データの処理単位として1ページ分の画像データを複数のバンドに分割した一例を示す図である。

【図4】図2におけるプリント用画像処理ブロックと電源制御回路との間の信号の流れを示すブロック図である。

【図5】第1の実施形態における電源制御回路による電源制御処理の流れを示すフローチャートである。

【図6】図4で説明した各種バス信号の電源制御処理時の波形例を示す図である。

【図7】(a)はON時間<規定値となった場合の電源制御対象モジュールの電源制御方法を示す図、(b)はON時間>規定値となった場合の電源制御対象モジュールの電源制御方法を示す図である。

【図8】第2の実施形態における電源制御回路による電源制御処理の流れを示すフローチャートである。

【図9】第2の実施形態におけるON時間<規定値となった場合の電源制御対象モジュールの電源制御方法を示す図である。

【図10】(a)は第1の実施形態における電源制御対象モジュールの電源制御方法を示す図、(b)は第3の実施形態における電源制御対象モジュールの電源制御方法を示す図である。

【発明を実施するための形態】

【0012】

以下、本発明の実施の形態を図面を参照して詳細に説明する。

【0013】

[第1の実施形態]

図1は、本発明の実施形態に係る画像形成装置のハードウェア構成の概略を示すブロック図である。

【0014】

本発明の実施形態に係る画像形成装置は、例えば、スキャナ機能、プリント機能、コピー機能等を備えるデジタル複合機(以下「MFP」と称する)である。MFPは、図示のように、コントローラ101、スキャナ部102、プリンタ部103、ネットワークI/F104、メモリ105、HDD106、及び操作部107を備える。

【0015】

コントローラ101は、システムバス108を介して画像入力デバイスであるスキャナ部102や画像出力デバイスであるプリンタ部103と接続し、これらを制御する。また、コントローラ101は、ネットワークI/F104を介してLANや公衆回線(WAN)等に接続し、画像情報やデバイス情報の入出力、PDLデータのイメージ展開を行うことができる。

【0016】

メモリ105は、コントローラ101が動作するためのシステムワークメモリであり、画像データを一時記憶するための画像メモリでもある。HDD106は、ハードディスクドライブ(HDD)であり、システムソフトウェア、画像データを格納する記憶装置である。操作部107は、タッチパネルやキーボードなどで構成され、MFPを使用するユーザーが様々な印刷設定等を行うためのユーザーインターフェースである。

【0017】

次に、図1のコントローラ101の動作について図2を用いて説明する。なお、以降で説明する画像データの処理単位は、図3に示すように、1ページ分の画像データを複数のバンド(ここでは10バンド)に分割したバンド単位とする。また、コントローラ101では、複数のモジュール単位で所定の動作処理が実行される。

【0018】

まず、スキャンデータを読み込む場合を説明する。

【0019】

コントローラ101は、スキャナ部102からRGB(RED、GREEN、BLUE)3色のスキャンデータ(読み取り画像データ)を受け取ると、スキャナ用画像処理部201にてシェーディング処理やフィルタ処理等の画像処理を行う。その後、スキャンデータに対して圧縮部202にて画像圧縮処理が行われる。その圧縮データは、DMAC(DIRECT MEMORY ACCESS CONTROLLER)203を介してメモリ105へ格納される。上記動作を行うスキャナ用画像処理部201、圧縮部202、及びDMAC203を含む機能ブロックがスキャナ用画像処理ブロック200である。

【0020】

スキャンデータをプリントする場合は、メモリ105に格納されている圧縮データが、DMAC211を介して色処理部212へ入力され、CMYK(CYAN、MAGENTA、YELLOW、BLACK)色空間へ変換される。その後、それらCMYKの値に対して濃度調整、プリンタガンマ補正等の調整の色処理が行われた後、DMAC211を介して再度メモリ105へ格納される。本動作を行うDMAC211、色処理部212を含む機能ブロックが色処理ブロック210である。

【0021】

そして、プリント用の画像処理を行うために、メモリ105に格納されている圧縮データが、DMAC221を介して展開部222へ入力され、ラスタ画像データへ展開される。ラスタのCMYK画像データは、プリント用画像処理部223に入力され、そこでディザ法や誤差拡散法による面積階調処理が行われ、プリンタ部103へ出力される。本動作を行うDMAC221、展開部222、プリント用画像処理部223を含む機能ブロックがプリント用画像処理ブロック220である。

【0022】

スキャンデータをネットワークへ送信する場合、メモリ105に格納されている圧縮データが、DMAC211を介して色処理部212へ入力され、色変換が行われる。具体的には、ディスプレイガンマ調整や用紙地色調整等が行われた後にYCbCr(輝度、BLUE色差、RED色差)色空間へ変換される。その後、再度DMAC211を介してメモリ105へ格納される。

【0023】

そして、送信用の画像処理を行うために、メモリ105に格納されている圧縮データが、DMAC231を介して展開部232へ入力され、ラスタ画像データへ展開される。ラスタのYCbCr画像データに対して、送信処理部233では、カラー画像送信であればJPEG圧縮処理を行い、モノクロ2値画像送信であればYデータに対して2値化を行ってJBIG圧縮等を行い、ネットワークI/F104へ出力する。本動作を行うDMAC231、展開部232、送信処理部233を含む機能ブロックがネットワーク処理ブロック230である。

【0024】

スキャンデータを保存する場合には、メモリ105に格納されている圧縮データが、DMAC241を介してディスクスプール高圧縮/展開部242へ入力される。ディスクスプール高圧縮/展開部242では、HDD106の書き込みスピードがメモリ105に対して遅いため、圧縮データに対して、さらに高圧縮のJPEG圧縮処理を施す。その後、ディスクアクセスコントローラ243を介してHDD106へ圧縮データが保存される。本動作を行うDMAC241、ディスクスプール高圧縮/展開部242、ディスクアクセスコントローラ243を含む機能ブロックがHDD処理ブロック240である。なお、HDD106に保存されているデータを再度メモリ105へ展開する場合はそれらの逆処理を行う。

【0025】

PDLのデータをメモリ105へ書き込む場合、ネットワークを介して受信したPDLデータを受信部282で受信してDMAC281を介してメモリ105に格納する。本動作を行うDMAC281、受信部282を含む機能ブロックがネットワーク受信ブロック280である。

【0026】

次に、CPU260は、メモリ105に格納されたPDLデータを読み出してインタープリットし、メモリ105へディスプレイリストを出力する。その後、メモリ105に格納されているディスプレイリストをレンダリング部251でラスタのRGB画像データへとレンダリングを行い、圧縮部252にて画像圧縮処理が行行われる。その圧縮データは、DMAC253を介してメモリ105へ格納される。本動作を行うレンダリング部251、圧縮部252、DMAC253を含む機能ブロックがレンダリングブロック250である。

【0027】

なお、PDLの画像データをプリントしたり、ネットワークへ送信したり、メモリ105に保存する場合は、上述したスキャンデータに対する処理と同様の処理を行うことで実現することが可能になる。

【0028】

ここで図2に示すブロック単位で電源制御を行う方法について説明する。

【0029】

CPU260からの命令によってPMU(Power Management Unit)270が、上述した各機能ブロックの電源SW制御信号やリセット制御信号を出力する。電源SW制御信号は、機能ブロックごとに出力される。リセット制御信号は、PMU270から不図示のリセット制御モジュールへ出力される。リセット制御モジュールは、各機能ブロックのリセット解除タイミングを制御する。

【0030】

本実施形態では、モード電源制御方法を利用しているが、スリープ時は全ての機能ブロックの電源OFFし、ネットワークからPDLデータを受信した際に、CPU260がPMU270に信号を出力して電源をONにする方法がある。

【0031】

図4は、図2におけるプリント用画像処理ブロック220と電源制御回路との間の信号の流れを示すブロック図である。同図では、図2で説明したDMAC221と展開部222とプリント用画像処理部223がバスによってパイプラインで接続された様子を示している。電源制御回路401は、展開部222の電源ON/OFF制御、バス信号制御を行うものである。電源制御回路402は、プリント用画像処理部223の電源ON/OFF制御、バス信号制御を行うものである。

【0032】

DMAC221と展開部222との間を例にして、各種モジュール(処理部)間のバス信号(データ有効信号)について説明する。

【0033】

data_A403は圧縮データである。end_A404は、DMAC221からのデータ転送の1バンド分が終了したことを示す信号である。valid_A405は、valid_A405がアクティブの期間にdata_A403が有効なことを示す信号である。busy_PB406は、busy_PB406がアクティブの期間はDMAC221からのデータを受信側が受信できないことを示す信号である。

【0034】

end_PA407とvalid_PA408は、電源制御回路401の入力信号であるend_A404とvalid_A405をそのまま出力した信号である。busy_B409は、展開部222から電源制御回路401に出力される信号である。busy_PB406は、展開部222が電源OFF状態である場合に、busy_B409の信号にかかわらずアクティブ状態にする。また、展開部222が電源ON状態のときは、busy_PB406にbusy_B409がそのまま出力される。

【0035】

reset_L_B410は、展開部222のリセット信号である。power_B411は、展開部222への電源供給を制御する信号である。end_B412は、展開部222から後段のモジュールであるプリント用画像処理部223へのデータ転送の1バンド分が終了したことを示す信号である。

【0036】

なお、図4では、電源制御回路401,402と、電源制御対象ごとに分割した電源制御回路の構成で説明したが、一つの電源制御回路で構成してもかまわない。

【0037】

図5は、第1の実施形態における電源制御回路401,402による電源制御処理の流れを示すフローチャートである。本処理は、1ページ分の画像データ、すなわち10バンドの画像データを処理する場合に対応する。

【0038】

図6は、図4で説明した各種バス信号の電源制御処理時の波形例を示す図である。図示例では、説明を簡単にするため、1バンドのデータ量を4ワードとしている。以下の説明は、特に明記していない限り、全て電源制御回路401,402を主体とする動作である。

【0039】

ステップS501では、電源制御対象モジュールの電源供給のON/OFF状態を確認する。電源制御対象モジュールは、例えば、図2に示した各種モジュールである。

【0040】

次に、ステップS502では、電源制御対象モジュールが電源ON状態である場合は、ステップS503に進む一方、電源OFF状態である場合はステップS508に進む。

【0041】

ステップS503では、前段モジュールのbusy信号(busy_PB406)に、アクティブ状態の信号レベルで出力する。つまり、前段モジュールには、busy状態であることを認識させる。前段モジュールとは、電源制御対象モジュールに対してパイプラインで前段に接続されるモジュールのことであり、以降においても前段モジュールと称す。

【0042】

ステップS504では、前段モジュールから出力されるvalid信号がアクティブであるか否かを判断する。アクティブである場合はステップS505へ進む。一方、アクティブでないときは、ステップS515で1サイクル待機して再びステップS504へ戻る。図6に示す波形ではサイクル(cycle)1に相当する。

【0043】

ステップS505では、power信号(power_B411)をアクティブ状態にし、電源ONする。図6に示す波形ではサイクル2に相当する。電源制御回路401内のON時間計測手段421は、この時点から計測を開始する。

【0044】

ステップS506では、電源制御対象モジュールの電源安定時間が経過したかどうかを判断する。電源安定時間とは、電源ON後に定常状態に遷移するまでの時間を意味する。図6に示す波形ではサイクル2からサイクル3までに相当する。電源安定時間は、電源制御対象モジュールで消費する静的電流量(回路規模)で決定され、電源制御回路401,402に予め設定されている。電源安定時間が経過した場合には、ステップS507に進む。

【0045】

ステップS507では、リセット信号(reset_L_B410)をデアサートし、電源制御対象モジュールのリセットを解除する。図6に示す波形ではサイクル4に相当する。

【0046】

ステップS508では、電源制御対象モジュールが出力するbusy信号(busy_B409)をそのまま前段モジュールのbusy信号(busy_PB406)として出力する。図6に示す波形ではサイクル5に相当する。

【0047】

ステップS512では、電源制御対象モジュールが出力するend信号(end_B412)がアクティブかどうかを判断する。アクティブである場合には、バンドの終わりを認識してステップS520へ進む。一方、アクティブでないときは、ステップS517で1サイクル待機して再びステップS512へ戻る。

【0048】

ステップS520では、処理したバンドが最後のバンドかどうか判断する。最後であればフロ−を終了する。最後でなければステップS513へ進む。

【0049】

ステップS513では、ON時間計測手段421がステップS505で計測を開始したときの経過時間(以降「ON時間」と呼ぶ)を取得する(ステップS502で既に電源供給がONだったときはステップS502からの経過時間を「ON時間」とする)。そして、取得したON時間(第1の経過時間)が規定値よりも小さいかどうかを判断し、小さければステップS514へ進み、power信号(power_B411)を非アクティブ状態にし、電源をOFFする。そして、リセット信号(reset_L_B410)をアサートし、リセット状態にする。一方、ステップS513でON時間が規定値よりも大きいと判断された場合、ステップS514がスキップされるので、電源はONのままの状態でステップS501へ戻る。

【0050】

ここで規定値の定め方について図7(a)、図7(b)を用いて説明する。

【0051】

仮にMFPのプリンタ部103が1ページを印刷するのに1秒かかるとする。1ページは10バンドで構成されることから、1バンドは100msec以内で処理されなければならない。100msec以内に処理できないバンドが続くと、プリント動作に対して画像データの供給が間に合わない、いわゆるバッファアンダーランエラーが発生する。そこで、ON時間計測手段により取得したON時間の比較対象となる規定値は100msecとしている。また、電源制御対象モジュールである展開部222の電源安定化時間を10msecとする。

【0052】

図7(a)及び図7(b)では、ともに時刻0で電源をONして、電源安定化時間(10msec)が経過した後に展開処理を開始する例を示している。

【0053】

図7(a)に示す例では、展開処理が80msecで終了するので、ON時間<規定値となる。1バンドを処理するために要求される時間の100msecに対して、20msecの余裕があるので、省電力のために電源をOFFする。

【0054】

一方、図7(b)に示す例では、展開処理に95msecかかったため、105msecで処理が終了する。つまり、ON時間>規定値となるので電源をOFFしない。よって、次のバンドの処理の前に電源安定化時間をおく必要がなく、バッファアンダーランの発生を軽減することができる。

【0055】

なお、図7(a)、図7(b)の例では、規定値を100msecとしたが安全性を考えて95msecなどやや小さい値を用いてもよい。一般に展開部222とプリンタ部103の間に緩衝となる不図示のバッファが多ければ局所的な処理の遅延は許容されるが、バッファが少ない場合はその逆となる。

【0056】

第1の実施形態によれば、複数の電源分離されたブロックがバスによってパイプライン接続され、回路モジュールの電源制御について、ソフトウエアの制御無しに動作時に必要なときだけ電源をONすることが可能となる。これにより、小規模回路モジュール単位で複雑な制御を必要とせずに電力制御を行うことが可能となり、省電力が可能となる。

【0057】

また、小規模回路モジュールがデータ処理を終えたとき電源をOFFすると必要なパフォーマンスを満たさないときは、電源をOFFしない判断をソフトウエアの制御無しに行うことができるので、省電力を行いつつ必要なパフォーマンスを維持することができる。

【0058】

[第2の実施形態]

本発明の第2の実施の形態に係る画像形成装置は、その構成(図1〜図4)が上記第1の実施の形態に係る画像形成装置と同じであり、第1の実施の形態と同様の部分については、同一の符号を用いてその説明を省略する。以下に、上記第1の実施の形態と異なる点を図6、図8を用いて説明する。

【0059】

第1の実施形態では、図6のステップS514で電源OFF後、ステップS501、S502、S503を経由してステップS504でValid信号を待ち、Valid信号を受信してからステップS505にて電源ON状態へ移行する。

【0060】

一方、第2の実施形態では、図8のステップS514で電源がOFFされた後、さらにステップS515にて待ち時間であるOFF時間(第2の経過時間)を決定し、OFF時間が経過したならばステップS505にて電源ON状態へ移行する。

【0061】

OFF時間の考え方については図9を用いて説明する。

【0062】

第1の実施形態と異なる点は、1バンドの処理が終了したときの動作のみである。第1の実施形態では、Valid信号の受信をトリガーにして電源ONを行うものである。これに対して、本第2の実施形態では、図9に示すように、80msecで処理が終わったならば、20msecの余裕があるので、Valid信号によらず電源供給OFF状態を保って省電力を優先する。また、20msec経過したならば直ちに電源ON処理に移行するので、バッファアンダーランの発生を軽減することができる。

【0063】

なお、舵2の実施形態では、OFF時間=100msec−ON時間としたが、安全を考えて、例えば、OFF時間=100msec−ON時間―5msec(負のときはOFF時間=0とする)としてもよい。

【0064】

[第3の実施形態]

本発明の第3の実施の形態に係る画像形成装置は、その構成(図1〜図4)が上記第1の実施の形態に係る画像形成装置と同じであり、第1の実施の形態と同様の部分については、同一の符号を用いてその説明を省略する。以下に、上記第1の実施の形態と異なる点を図10(a)、図10(b)を用いて説明する。

【0065】

第1及び第2の実施形態において、1バンドの処理時間がパフォーマンスを満たすために要求される時間を上回ってしまった場合に着目する。

【0066】

図10(a)及び図10(b)では、ともに1バンド目の処理を110msecで終了して、2バンド目の処理を時刻205msecで終了する。

【0067】

第1の実施形態では1バンドごとにON時間を計測する。そのため、2バンド目の処理が終了した時点(205msec経過時)でON時間=95msecとなり、規定値より小なので電源がOFFされる。2バンドの処理全体でみるとこれは不適切である。なぜならパフォーマンスを満たすためには2バンドを200msec以内で処理する必要があるからである。

【0068】

第3の実施形態としては、複数のバンド単位で処理時間を計測して上記の問題を軽減する。つまり、図10(b)に示すように、2バンド分のON時間を用いて2バンド分の規定値(200msec)と比較して電源をOFFするか否かをステップS513にて判定する。なお、本実施形態では、2バンド分のON時間を用いた場合について説明したが、これに限定されるものではなく、複数回分のON時間の合計に基づいて電源をOFFするか否かを判断するように構成してもよい。

【0069】

なお、バッファアンダーランに対する安全のため、上記規定値として200msecよりも小さい値を選んでもよい。

【0070】

上記第1〜第3の実施形態では、電源制御対象モジュールがON時間を測定する基本単位として、画像データをバンド単位に分割した場合について説明したが、画像データを矩形単位で分割したり、またデータ量単位で分割したりしてもよい。

【0071】

また、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(またはCPUやMPU等)がプログラムを読み出して実行する処理である。

【符号の説明】

【0072】

101 コントローラ

105 メモリ

221 DMAC

222 展開部

223 プリント用画像処理部

401,402 電源制御回路

【特許請求の範囲】

【請求項1】

複数のモジュール単位で所定の動作処理を実行する制御手段と、前記複数のモジュールからバス信号を受信して、当該モジュールの電源ON/OFFを制御する電源制御回路とを備える画像形成装置において、

電源制御対象となるモジュールに入力されるデータ有効信号に応じて当該モジュールへの電源供給をONする電源ON手段と、

前記電源ON手段による電源供給が開始されてから前記電源制御対象モジュールの電源安定時間が経過するまで待機する待機手段と、

前記電源ON手段による電源供給が開始されてからの経過時間を計測する計測手段と、

前記計測手段により得られた経過時間から前記電源制御対象モジュールへの電源供給をOFFするか否かを判断する判断手段と、

前記判断手段にてOFFと判断されたときは、前記電源制御対象モジュールへの電源供給をOFFする電源OFF手段と

を有することを特徴とする画像形成装置。

【請求項2】

複数のモジュール単位で所定の動作処理を実行する制御手段と、前記複数のモジュールからバス信号を受信して、当該モジュールの電源ON/OFFを制御する電源制御回路とを備える画像形成装置において、

電源制御対象となるモジュールに入力されるデータ有効信号に応じて当該モジュールへの電源供給をONする電源ON手段と、

前記電源ON手段による電源供給が開始されてから前記電源制御対象モジュールの電源安定時間が経過するまで待機する待機手段と、

前記電源ON手段による電源供給が開始されてからの第1の経過時間を計測する計測手段と、

前記計測手段により得られた第1の経過時間から前記電源制御対象モジュールへの電源供給をOFFするか否かを判断する判断手段と、

前記判断手段にてOFFと判断されたときは、前記電源制御対象モジュールへの電源供給をOFFする電源OFF手段と、

前記電源OFF手段による電源供給のOFF後から次に電源供給がONするまでの第2の経過時間を決定する決定手段とを備え、

前記電源ON手段は、前記電源OFF手段による電源供給のOFF後から前記第2の経過時間が経過するまで待機した後に電源供給をONすることを特徴とする画像形成装置。

【請求項3】

前記決定手段は、前記計測手段により測定された複数回分の前記第1の経過時間の合計に基づいて前記第2の経過時間を決定することを特徴とする請求項2に記載の画像形成装置。

【請求項4】

前記判断手段は、前記計測手段により測定された複数回分の前記第1の経過時間の合計に基づいて前記電源供給をOFFするか否かを判断することを特徴とする請求項1または2に記載の画像形成装置。

【請求項5】

複数のモジュール単位で所定の動作処理を実行する制御手段と、前記複数のモジュールからバス信号を受信して、当該モジュールの電源ON/OFFを制御する電源制御回路とを備える画像形成装置の電力制御方法において、

電源制御対象となるモジュールに入力されるデータ有効信号に応じて当該モジュールへの電源供給をONする電源ON工程と、

前記電源ON工程による電源供給が開始されてから前記電源制御対象モジュールの電源安定時間が経過するまで待機する待機工程と、

前記電源ON工程による電源供給が開始されてからの経過時間を計測する計測工程と、

前記計測工程により得られた経過時間から前記電源制御対象モジュールへの電源供給をOFFするか否かを判断する判断工程と、

前記判断工程にてOFFと判断されたときは、前記電源制御対象モジュールへの電源供給をOFFする電源OFF工程と

を有することを特徴とする画像形成装置の電力制御方法。

【請求項6】

複数のモジュール単位で所定の動作処理を実行する制御手段と、前記複数のモジュールからバス信号を受信して、当該モジュールの電源ON/OFFを制御する電源制御回路とを備える画像形成装置の電力制御方法において、

電源制御対象となるモジュールに入力されるデータ有効信号に応じて当該モジュールへの電源供給をONする電源ON工程と、

前記電源ON工程による電源供給が開始されてから前記電源制御対象モジュールの電源安定時間が経過するまで待機する待機工程と、

前記電源ON工程による電源供給が開始されてからの第1の経過時間を計測する計測工程と、

前記計測工程により得られた第1の経過時間から前記電源制御対象モジュールへの電源供給をOFFするか否かを判断する判断工程と、

前記判断工程にてOFFと判断されたときは、前記電源制御対象モジュールへの電源供給をOFFする電源OFF工程と、

前記電源OFF工程による電源供給のOFF後から次に電源供給がONするまでの第2の経過時間を決定する決定工程とを備え、

前記電源ON工程は、前記電源OFF工程による電源供給のOFF後から前記第2の経過時間が経過するまで待機した後に電源供給をONすることを特徴とする画像形成装置。

【請求項7】

請求項5または6に記載の電力制御方法を画像形成装置に実行させるためのコンピュータに読み取り可能なプログラム。

【請求項1】

複数のモジュール単位で所定の動作処理を実行する制御手段と、前記複数のモジュールからバス信号を受信して、当該モジュールの電源ON/OFFを制御する電源制御回路とを備える画像形成装置において、

電源制御対象となるモジュールに入力されるデータ有効信号に応じて当該モジュールへの電源供給をONする電源ON手段と、

前記電源ON手段による電源供給が開始されてから前記電源制御対象モジュールの電源安定時間が経過するまで待機する待機手段と、

前記電源ON手段による電源供給が開始されてからの経過時間を計測する計測手段と、

前記計測手段により得られた経過時間から前記電源制御対象モジュールへの電源供給をOFFするか否かを判断する判断手段と、

前記判断手段にてOFFと判断されたときは、前記電源制御対象モジュールへの電源供給をOFFする電源OFF手段と

を有することを特徴とする画像形成装置。

【請求項2】

複数のモジュール単位で所定の動作処理を実行する制御手段と、前記複数のモジュールからバス信号を受信して、当該モジュールの電源ON/OFFを制御する電源制御回路とを備える画像形成装置において、

電源制御対象となるモジュールに入力されるデータ有効信号に応じて当該モジュールへの電源供給をONする電源ON手段と、

前記電源ON手段による電源供給が開始されてから前記電源制御対象モジュールの電源安定時間が経過するまで待機する待機手段と、

前記電源ON手段による電源供給が開始されてからの第1の経過時間を計測する計測手段と、

前記計測手段により得られた第1の経過時間から前記電源制御対象モジュールへの電源供給をOFFするか否かを判断する判断手段と、

前記判断手段にてOFFと判断されたときは、前記電源制御対象モジュールへの電源供給をOFFする電源OFF手段と、

前記電源OFF手段による電源供給のOFF後から次に電源供給がONするまでの第2の経過時間を決定する決定手段とを備え、

前記電源ON手段は、前記電源OFF手段による電源供給のOFF後から前記第2の経過時間が経過するまで待機した後に電源供給をONすることを特徴とする画像形成装置。

【請求項3】

前記決定手段は、前記計測手段により測定された複数回分の前記第1の経過時間の合計に基づいて前記第2の経過時間を決定することを特徴とする請求項2に記載の画像形成装置。

【請求項4】

前記判断手段は、前記計測手段により測定された複数回分の前記第1の経過時間の合計に基づいて前記電源供給をOFFするか否かを判断することを特徴とする請求項1または2に記載の画像形成装置。

【請求項5】

複数のモジュール単位で所定の動作処理を実行する制御手段と、前記複数のモジュールからバス信号を受信して、当該モジュールの電源ON/OFFを制御する電源制御回路とを備える画像形成装置の電力制御方法において、

電源制御対象となるモジュールに入力されるデータ有効信号に応じて当該モジュールへの電源供給をONする電源ON工程と、

前記電源ON工程による電源供給が開始されてから前記電源制御対象モジュールの電源安定時間が経過するまで待機する待機工程と、

前記電源ON工程による電源供給が開始されてからの経過時間を計測する計測工程と、

前記計測工程により得られた経過時間から前記電源制御対象モジュールへの電源供給をOFFするか否かを判断する判断工程と、

前記判断工程にてOFFと判断されたときは、前記電源制御対象モジュールへの電源供給をOFFする電源OFF工程と

を有することを特徴とする画像形成装置の電力制御方法。

【請求項6】

複数のモジュール単位で所定の動作処理を実行する制御手段と、前記複数のモジュールからバス信号を受信して、当該モジュールの電源ON/OFFを制御する電源制御回路とを備える画像形成装置の電力制御方法において、

電源制御対象となるモジュールに入力されるデータ有効信号に応じて当該モジュールへの電源供給をONする電源ON工程と、

前記電源ON工程による電源供給が開始されてから前記電源制御対象モジュールの電源安定時間が経過するまで待機する待機工程と、

前記電源ON工程による電源供給が開始されてからの第1の経過時間を計測する計測工程と、

前記計測工程により得られた第1の経過時間から前記電源制御対象モジュールへの電源供給をOFFするか否かを判断する判断工程と、

前記判断工程にてOFFと判断されたときは、前記電源制御対象モジュールへの電源供給をOFFする電源OFF工程と、

前記電源OFF工程による電源供給のOFF後から次に電源供給がONするまでの第2の経過時間を決定する決定工程とを備え、

前記電源ON工程は、前記電源OFF工程による電源供給のOFF後から前記第2の経過時間が経過するまで待機した後に電源供給をONすることを特徴とする画像形成装置。

【請求項7】

請求項5または6に記載の電力制御方法を画像形成装置に実行させるためのコンピュータに読み取り可能なプログラム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−250394(P2012−250394A)

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願番号】特願2011−123642(P2011−123642)

【出願日】平成23年6月1日(2011.6.1)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成24年12月20日(2012.12.20)

【国際特許分類】

【出願日】平成23年6月1日(2011.6.1)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]