画像表示装置およびその制御方法

【課題】バースト転送されるラスタ画像データが複数のスキャンラインからなる場合でも、簡易な制御で構成できる画像表示装置およびその制御方法を提供する。

【解決手段】画像表示装置1は、バースト転送一回当りに転送されるスキャンラインの数からなる複数のFIFO0〜7と、前記単位転送データに対応するスキャンラインの番号に応じて、前記複数のFIFOのうち1つを選択して前記第2ラスタ画像データを格納する入力制御部20と、を備えている。

【解決手段】画像表示装置1は、バースト転送一回当りに転送されるスキャンラインの数からなる複数のFIFO0〜7と、前記単位転送データに対応するスキャンラインの番号に応じて、前記複数のFIFOのうち1つを選択して前記第2ラスタ画像データを格納する入力制御部20と、を備えている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は画像表示装置に関し、特にフォントやピクチャデータなどのラスタ画像をフレーム画像の一部に重畳して表示する画像表示装置に関する。

【背景技術】

【0002】

このような画像表示装置では、フレーム画像における表示のスキャン中に、フォントやピクチャデータなどの表示ラスタ画像を、予め格納されるメモリから、所定時間内に転送しなくてはならない。この所定時間は、フレーム画像の表示クロックや解像度などで決定される。ラスタ画像の転送が、所定時間内になされない場合には、フレーム画像に、ラスタ画像が正しく表示されなくなるため、ラスタ画像の転送に要する時間を短縮する必要があった。

【0003】

特許文献1に開示される画像表示装置は、フォントデータ変換回路122と、フォントアドレス生成回路123とを備えている。ビデオメモリ136にビデオメモリプレーン103を加え、文字表示のスキャンラインを指定するスキャンラインカウント手段の出力に対応して、メモリインタフェース124を介して、ビデオメモリプレーン103の連続空間から各文字のフォントデータを表示データの1つとしてスキャンライン単位毎の文字テキストコード順に連続してアクセスおよび転送し、表示回路125からCRT装置に画像信号を出力する。

【0004】

これにより、同一のスキャンラインにおける表示文字が、文字コードの離れている文字で構成される場合でも、フォントデータがスキャンライン単位に連続した256バイトのビデオメモリ領域に格納されているため、常にDRAMの高速アクセスを使用して転送することができ、ひいては、転送に要する時間を短縮することができる。

【特許文献1】特開平10−161638

【発明の開示】

【発明が解決しようとする課題】

【0005】

近年、画像データを格納するような大容量メモリとして、バースト転送により高速に大量のデータを転送することができるため、SDRAMを用いることが主流になりつつある。SDRAMにおけるバースト転送では、連続するアドレスに格納されるデータが高速に転送される反面、バースト転送に先立ち、転送元アドレスやバースト長などの設定にかかる期間が長いため、バースト長が短い場合には、データ転送におけるスループットの低下を招くこととなる。

【0006】

しかしながら、特許文献1の画像表示装置において、フォントデータを格納するメモリとしてSDRAMを用いる場合には、以下の問題が生じる。

すなわち、特許文献1の画像表示装置では、1つのフォントデータについて、連続するアドレスに格納されるデータが1スキャンライン分のみであるため、1度のバースト転送において転送されるフォントデータの転送量が1スキャンライン分に制限される。1スキャンライン当りのフォントデータが小さい場合には、バースト長が短くなり、スループットの低下を招くこととなり問題である。

【0007】

さらに、特許文献1の画像表示装置では、フォントデータが格納されているビデオメモリプレーン102とは別の空間でビデオメモリプレーン102と同容量のビデオメモリプレーン103が必要である。このため、ビデオメモリサイズが大きくなり、ひいては画像表示装置の回路規模が大きくなり問題である。

【0008】

ところで、一般的なバースト転送を行う装置では、バースト転送における転送先の記憶装置にFIFOを用いることが知られている。そこで、ラスタ画像をフレーム画像の一部に重畳して表示する画像表示装置において、バースト転送の転送先の記憶装置にFIFOを用いる場合について想定し、このような画像表示装置について考察する。

FIFOを用いた画像表示装置について、バースト転送ごとに、1つのスキャンラインのみが転送される場合には、フレーム画像のスキャン順と同じ順に、スキャンラインがFIFOに格納されることとなる。従って、格納順にFIFOからスキャンラインを取り出すことにより、正しくフレーム画像に重畳して出力することができる。

【0009】

これに対して、バースト転送ごとに、複数のスキャンラインが転送される場合には、連続して複数のスキャンラインがFIFOに格納されることとなる。すなわち、FIFOへのスキャンラインの格納順が、フレーム画像のスキャン順に一致しないということになる。このため、FIFOから格納順にスキャンラインを取り出しても、正しくフレーム画像に重畳して出力することができない。正しく出力するためには、FIFOからのスキャンライン出力の並び替えをフレーム画像のスキャン順に行なうなどの手段を講じる必要が生じる。このため、FIFOの制御が複雑になり、ひいては、画像表示装置の複雑化を招来し問題である。

【0010】

本発明は前記背景技術の課題に鑑みてなされたものであって、SDRAMにおけるバースト転送のスループットを向上させ、FIFOの制御を簡易に行うことができる画像表示装置およびその制御方法を提供することを目的とする。

【課題を解決するための手段】

【0011】

その解決手段は、入力許可信号に応じて、1つのフレームに表示される第1ラスタ画像データの一部に重畳して配置される第2ラスタ画像データが、前記第2ラスタ画像データにおけるスキャンラインの単位または前記スキャンラインの単位がn分割されたn分割単位を単位転送データとし、複数の該単位転送データを備えて、バースト転送により入力される画像表示装置であって、バースト転送一回当りに転送される前記スキャンラインと同数のFIFOと、前記単位転送データを、前記スキャンラインのライン番号に応じて選択される前記FIFOに格納する入力制御部と、を備えることを特徴とする画像表示装置である。

【0012】

また、他の解決手段は、入力許可信号に応じて、1フレームに表示される第1ラスタ画像データの一部に重畳して配置される第2ラスタ画像データを、前記第2ラスタ画像データにおけるスキャンラインの単位または前記スキャンラインの単位がn分割されたn分割単位を単位転送データとし、複数の該単位転送データを備えて、バースト転送するステップと、バースト転送一回当りに転送される前記スキャンラインと同数のFIFOに対し、前記単位転送データを、前記第2ラスタ画像データにおける前記スキャンラインのライン番号に応じて選択される前記FIFOに格納するステップと、を備えることを特徴とする画像表示装置の制御方法である。

【0013】

本発明の画像表示では、単位転送データは、スキャンラインのライン番号に応じて選択されるFIFOに、バースト転送により入力される。従って、バースト転送ごとに、複数のスキャンラインがFIFOに入力される場合には、単位転送データは、スキャンラインのライン番号ごとに、FIFOに格納されることになる。第1ラスタ画像データに重畳して出力する際には、出力すべきスキャンラインのライン番号に応じたFIFOを選択することにより正しく表示することができる。このため、本発明では、単位転送データを格納する手段としてFIFOを備えて、しかも、FIFOからのスキャンライン出力の並べ替えなどのように複雑な制御をすることなしで、正しく第1ラスタ画像データに重畳して出力することができる画像表示装置となし得る。

【発明の効果】

【0014】

本発明を適用することにより、SDRAMにおけるバースト転送のスループットを向上させ、FIFOの制御を簡易に行うことができる画像表示装置およびその制御方法を提供することができる。

【発明を実施するための最良の形態】

【0015】

以下、本発明の実施にかかる発明について具体化した実施形態を図1〜図10を参照しつつ詳細に説明する。

【0016】

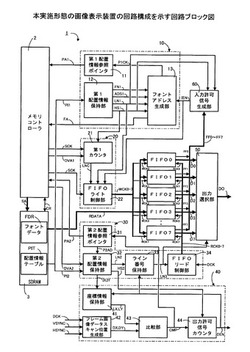

図1は、本発明の一例である画像表示装置1の回路ブロック図である。

画像表示装置1は、ラスタ画像からなるフォントデータFDを、予め定められた配置情報PIに基づいて、ラスタ画像からなるフレーム画像FPの一部に重畳して出力するためのシステムである。

【0017】

画像表示装置1の説明に先立ち、フレーム画像FP、フォントデータFD0〜2および配置情報PIについて説明する。

図2は、フレーム画像FPの一部に重畳されて配置されるフォントデータFD0〜2の一例を示している。フォントデータFD0〜2は、1画素当り1バイトのサイズからなるラスタ画像データであり、フォントデータFD0は“A”文字を表わす8バイト×8バイトのサイズのラスタ画像データ、フォントデータFD1は“B”文字を表わす16バイト×8バイトのサイズのラスタ画像データ、フォントデータFD2は“C”文字を表わす8バイト×8バイトのサイズのラスタ画像データである。また、それぞれのフォントデータFD0〜2に対応するカッコ内の数字は、配置される座標を表わしている。例えば、フォントデータFD0における(12,8)は、フォントデータFD0が水平方向の座標X=12、垂直方向の座標Y=8に配置されていることを示している。それぞれの座標Xおよび座標Yは、1刻みで設定可能であり、図2の例では、フォントデータFD2は、フォントデータFD0およびフォントデータFD1に対して、垂直方向に4だけずれた位置に配置されている。

【0018】

フォントデータFDは、後述するSDRAM3のフォントデータ領域FDRから転送されて出力される。図3に示すように、フォントデータ領域FDRには、フォントデータFDがフォント番号FN単位ごとのスキャンライン順に格納されている。また、フォントデータFDの種類ごとに異なる番号となるフォント番号FNが割り振られている。本実施形態では、フォント番号FNについて、フォントデータFD0には0が、フォントデータFD1には1が、フォントデータFD2には2がそれぞれ割り振られている。また、各フォントデータFDにおいて、スキャンラインごとにライン番号LNが割り振られている。フォントデータFD0およびFD2には、8画素ごとに異なるライン番号LNが割り振られ、フォントデータFD1には、16画素ごとに異なるライン番号LNが割り振られている。

本実施形態の画像表示装置1においては、バス幅は4バイト(32ビット)であり、バースト長は8ワード固定であるため、バースト転送ごとに、32バイト分のフォントデータFDが転送されることとなる。

【0019】

次いで、フレーム画像FPに対する各フォントデータを配置するための配置情報PIについて説明する。

配置情報PIは、各フォントデータFDのスキャンラインごとに、配置する座標X,Yと、フォント番号FNと、ライン番号LNと、フォントの水平サイズを示す水平サイズHSと、フォントデータの格納先の先頭アドレスを示す先頭アドレスADSとを要素として持つ。図4に示すように、この配置情報PIは、それぞれの座標X,Yの情報に基づき、フレーム画像FPのスキャン順に整列されて、配置情報テーブルPITとして構成されている。すなわち、配置情報テーブルPITにおいて、配置情報PIは、座標Yが小さいほど先頭近くに配置され、同じ座標Yの場合には、座標Xが小さいほど先頭近くに配置されることとなる。

【0020】

なお、本実施例では、この配置情報テーブルPITは、SDRAM3の連続する領域に格納される。図5に示すように、一つの配置情報PIには、座標X,Y、フォント番号FN、ライン番号LN、水平サイズHSおよび先頭アドレスADSがこの順に格納されている。また、それぞれの配置情報PIは、座標X,Yに基づき、フレーム画像FPのスキャン順に配置されている。また、配置におけるアドレスの間隔は、1つの配置情報PIが占める領域のサイズである配置情報サイズSPIである。すなわち、図5に示すように、配置情報テーブルPITにおいて先頭に配置される配置情報PIを配置情報PI0とし、その先頭アドレスを先頭アドレスATとすると、次に配置される配置情報PIのアドレスは、先頭アドレスAT+配置情報サイズSPIのアドレス値となる。

【0021】

図1に戻り、画像表示装置1の各部について詳細に説明する。画像表示装置1には、メモリコントローラ2を介して、SDRAM3が接続されている。画像表示装置1から、出力許可信号DENとともに32ビットの出力データDOが出力される。出力データDOはさらに、図示しないシフト回路により、1画素ごとのデータに分割されて、フレーム画像FPの一部に重畳される。

【0022】

さらに、画像表示装置1は、FIFO0〜FIFO7と、フォントデータFDのバースト転送に際し、SDRAM3に格納されているフォントデータFDの転送開始アドレスを生成するフォントアドレス発生部10と、FIFO0〜FIFO7に対するライト制御を行う入力制御部20と、FIFO0〜FIFO7に対するリード制御を行う出力制御部30と、フレーム画像および出力データDOとの同期処理を行う同期制御部40と、FIFO0〜FIFO7の出力から1つを選択して、出力データDOを出力する出力選択部50と、入力許可信号IENを生成する入力許可信号生成部60とを備えている。

【0023】

フォントアドレス発生部10は、第1配置情報参照ポインタ11と、第1配置情報保持部12と、フォントアドレス生成部13とを備えている。

【0024】

第1配置情報参照ポインタ11では、SDRAM3からFIFO0〜FIFO7へのバースト転送に必要な第1配置情報PI1を参照するためのアドレスPA1がメモリコントローラ2に出力される。このアドレスPA1は、配置情報テーブルPITの先頭アドレスATを初期値とし、フォントアドレス生成部13からの第1カウント指令信号P1CKごとに配置情報サイズSPIが加算されて出力される。メモリコントローラ2は、SDRAM3に対し、アドレスSAを出力して、配置情報PIをアクセスする。これにより、アドレスPA1を先頭とする位置から配置情報サイズSPI分のデータが、SDRAM3から画像表示装置1に転送されることとなる。

【0025】

第1配置情報保持部12では、アドレスPA1に対応する、SDRAM3から出力される第1配置情報PI1の要素のうちフォント番号FN、ライン番号LN、水平サイズHSおよび先頭アドレスADSが取得され保持される。また、保持された各要素は、第1フォント番号FN1、第1ライン番号LN1、第1水平サイズHS1および第1先頭アドレスADS1として出力される。

【0026】

フォントアドレス生成部13は、第1フォント番号FN1、第1ライン番号LN1、第1水平サイズHS1、第1先頭アドレスADS1および入力許可信号IENを入力とし、フォントアドレスFAおよび第1カウント指令信号P1CKを出力とする。

【0027】

フォントアドレスFAは、バースト転送ごとに出力される、SDRAM3からバースト転送される際のフォントデータの先頭アドレスである。フォントアドレス生成部13は、ライン番号LNおよび水平サイズHSに基づき、転送の対象となるフォントデータがバースト転送時の先頭データであるか否かを判断し、フォントデータが先頭データである場合には、フォントアドレスFAを出力する。バースト転送時の先頭データの判断について、本実施形態ではバースト長が8ワード固定であり、バースト転送当り32画素(32バイト)のデータが転送されるため、32画素ごとの先頭のライン番号LNを有するものが先頭データであると判断される。例えば、スキャンライン方向のサイズが8画素のフォントデータでは、バースト転送当り、スキャンライン4つ分のフォントデータが転送される。従って、ライン番号LNが0および4のデータがバースト転送の際の先頭データであると判断される。一方、スキャンライン方向のサイズが16画素のフォントデータでは、バースト転送当り、スキャンライン2つ分のフォントデータが転送される。従って、ライン番号LNが0、2、4、6のデータがバースト転送の際の先頭データであると判断される。

また、フォントアドレスFAの演算は、具体的には、取得された第1先頭アドレスADS1にフォントデータ領域FDRの先頭アドレスAFDが加えられることでなされる。

【0028】

入力許可信号生成部60では、FIFO0〜FIFO7からそれぞれ出力されるFIFOフル信号FF0〜FF7および第1ライン番号LN1および第1水平サイズHS1を入力とし、入力許可信号IENを出力とする。FIFOフル信号FF0〜FF7は、FIFO0〜FIFO7において、バースト転送に必要な残存メモリ領域の容量がない場合には、活性状態に遷移する信号である。入力許可信号生成部60は、FIFOフル信号FF0〜FF7に応じて、FIFO0〜FIFO7にバースト転送に必要な容量があるか否かを判断し、SDRAM3からのバースト転送を許可する入力許可信号IENを活性状態にする。この入力許可信号IENは、バースト転送先のFIFOフル信号のうちいずれか一つが活性状態になると、非活性状態に遷移し、バースト転送先のうち最後のスキャンラインのデータが格納されるFIFOのFIFOフル信号が非活性状態になると、活性状態に遷移する。すなわち、バースト転送の対象となるフォントデータの第1ライン番号LN1および第1水平サイズHS1に基づき選択されるFIFOフル信号FF0〜FF7のうち一つに応じて、入力許可信号IENが活性状態に遷移することとなる。

【0029】

例えば、スキャンライン方向のサイズが8画素のフォントデータでは、バースト転送当り、スキャンライン4つ分のフォントデータが転送される。従って、FIFOフル信号FF0〜FF3(またはFF4〜FF7)が活性状態になると、入力許可信号IENは、活性状態に遷移する。また、ライン番号LNが3(または7)のフォントデータがバースト転送の際の最後のデータとなるため、FIFOフル信号FF3(またはFF7)が非活性状態になると、入力許可信号IENは活性状態に遷移する。

一方、スキャンライン方向のサイズが16画素のフォントデータでは、バースト転送当り、スキャンライン2つ分のフォントデータが転送される。従って、FIFOフル信号FF0,FF1(または、FF2,FF3、FF4,FF5、FF6,FF7)が活性状態になると、入力許可信号IENは、活性状態に遷移する。また、ライン番号LNが1(または3、5、7)のフォントデータがバースト転送の際の最後のデータとなるため、FIFOフル信号FF1(またはFF3、FF5、FF7)が非活性状態になると、入力許可信号IENは活性状態に遷移する。

【0030】

次いで、入力制御部20について詳細な説明を行なう。

入力制御部20は、スキャンライン単位のフォントデータが転送されるごとにインクリメントされるフォントライン数第1カウンタ21と、第1カウンタ21の結果に応じて、SDRAM3からのフォントデータを格納するFIFOの書き込み制御を行うFIFOライト制御部22とを備える。

【0031】

第1カウンタ21は、第1水平サイズHS1およびデータ転送クロックSCKを入力とし、計数結果のラインカウント数LNCを出力とする。ラインカウント数LNCは、バースト転送ごとにラインカウント数LNCは0値に初期化され、スキャンライン単位のフォントデータが入力されるごとにインクリメントされる。データ転送クロックSCK当り4画素のデータが転送されることから、第1水平サイズHS1分のフォントデータを転送するのに足りるクロック数のデータ転送クロックSCKが入力された場合に、ラインカウント数LNCがインクリメントされる。すなわち、フォントデータFDの第1水平サイズHS1を、バースト転送のデータ幅である4画素で除したサイズ比HSVごとにインクリメントがなされる。このサイズ比HSVは、具体的には、図示しない第1水平サイズHS1に対する2ビット右シフト回路で求められる。

【0032】

例えば、スキャンライン方向が8画素のフォントデータでは、サイズ比HSVは2であり、2クロックのデータ転送クロックSCKごとに、ラインカウント数LNCがインクリメントされる。一方、スキャンライン方向が16画素のフォントデータでは、サイズ比HSVは4であり、4クロックのデータ転送クロックSCKごとに、ラインカウント数LNCがインクリメントされる。

【0033】

FIFOライト制御部22は、第1ライン番号LN1、ラインカウント数LNC、入力許可信号IENおよびデータ転送クロックSCKを入力とし、FIFO0〜FIFO7へのライト信号WCK0〜WCK7のうちいずれか一つを出力する。図6および図7で示すように、FIFOライト制御部22では、第1ライン番号LN1およびラインカウント数LNCが加算されて選択FIFO番号FSNが算出され、選択FIFO番号FSNに応じたFIFOに対し、データ転送クロックSCKのタイミングに基づくライト信号WCKnが出力される。

【0034】

次いで、フォントデータFDのバースト転送について、図6および図7を参照して説明する。

図6は、スキャンラインあたり8画素であるフォントデータFD0のバースト転送のタイミングを示す波形図である。

フォントデータFD0は、バースト転送ごとに4つのスキャンラインが転送され、FIFOに格納される。例えば、(1)および(2)で転送されるデータは、ライン番号LN=0のスキャンラインである。これと同様に、(3)〜(16)についても、2つのデータで一つのスキャンラインを転送することとなる。

また、サイズ比HSVが2であるため、第1カウンタ21は、2つのデータ転送クロックSCKごとに更新される。すなわち、第1カウンタ21は、(3)、(5)、(7)、(9)、(11)、(13)および(15)のタイミングで更新されることになる。

【0035】

(1)において、第1ライン番号LN1は、0であり、第1カウンタ21は初期化され、ラインカウント数LNCには0が出力される。これにより選択FIFO番号FSNは0となり、FIFO0に対するライト信号WCK0に、データ転送クロックSCKと同相のネガティブパルスが出力される。これにより、単位転送データRDATAの内容がFIFO0に格納される。

【0036】

(2)において、第1カウンタ21は、更新されないで、ラインカウント数LNCには引き続き0が出力される。従って、選択FIFO番号FSNは0であり、FIFO0に対するライト信号WCK0に、データ転送クロックSCKと同相のネガティブパルスが出力される。これにより、単位転送データRDATAの内容がFIFO0に格納される。

【0037】

(3)において、第1カウンタ21は、更新され、ラインカウント数LNCには1が出力される。従って、選択FIFO番号FSNは1に遷移し、FIFO1に対するライト信号WCK1に、データ転送クロックSCKと同相のネガティブパルスが出力される。これにより、単位転送データRDATAの内容がFIFO1に格納される。以降、(4)〜(8)についてもラインカウント数LNCに基づき選択FIFO番号FSNが決定され、選択FIFO番号FSNに応じたFIFOに対し、ライト信号WCKnにネガティブパルスが出力される。

また、(9)〜(16)についても、第1ライン番号LN1が4に遷移し、ラインカウント数LNCに4を加算して選択FIFO番号FSNが決定され、選択FIFO番号FSNに応じたFIFOに対し、ライト信号WCKnにネガティブパルスが出力される。

【0038】

図7は、スキャンラインあたり16画素であるフォントデータFD1のバースト転送のタイミングを示す波形図である。

フォントデータFD1は、バースト転送ごとに2つのスキャンラインが転送されFIFOに格納される。例えば、(1)〜(4)で転送されるデータは、ライン番号LN=0のスキャンラインである。これと同様に、(5)〜(16)についても、4つのデータで一つのスキャンラインを転送することとなる。

また、サイズ比HSVが4であるため、第1カウンタ21は、4つのデータ転送クロックSCKごとに転送される。すなわち、第1カウンタ21は、(5)、(9)および(13)のタイミングで更新されることになる。

【0039】

(1)において、第1ライン番号LN1は、0であり、第1カウンタ21は初期化され、ラインカウント数LNCには0が出力される。これにより選択FIFO番号FSNは0となり、FIFO0に対するライト信号WCK0に、データ転送クロックSCKと同相のネガティブパルスが出力される。これにより、単位転送データRDATAの内容がFIFO0に格納される。(2)〜(4)についても、(1)と同様に、FIFO0に対するライト信号WCK0に、データ転送クロックSCKと同相のネガティブパルスが出力される。これにより、それぞれの単位転送データRDATAの内容がFIFO0に格納される。

【0040】

(5)において、第1カウンタ21は、更新され、ラインカウント数LNCには1が出力される。従って、選択FIFO番号FSNは1に遷移し、FIFO1に対するライト信号WCK1に、データ転送クロックSCKと同相のネガティブパルスが出力される。これにより、単位転送データRDATAの内容がFIFO1に格納される。(6)〜(8)についても、(5)と同様に、FIFO1に対するライト信号WCK1に、データ転送クロックSCKと同相のネガティブパルスが出力される。これにより、それぞれの単位転送データRDATAの内容がFIFO1に格納される。

また、(9)〜(16)についても、第1ライン番号LN1が2に遷移し、ラインカウント数LNCに2を加算して選択FIFO番号FSNが決定され、選択FIFO番号FSNに応じたFIFOに対し、ライト信号WCKnにネガティブパルスが出力される。

【0041】

次いで、出力制御部30について説明する。

出力制御部30は、第2配置情報参照ポインタ31と、第2配置情報保持部32と、ライン番号保持部33と、FIFOリード制御部34とを備えている。

第2配置情報参照ポインタ31では、SDRAM3からFIFO0〜FIFO7へのバースト転送に必要な第2配置情報PI2を参照するためのアドレスSA2がメモリコントローラ2に出力される。このアドレスSA2は、VSYNCがローレベルに遷移するごとに、配置情報テーブルPITの先頭アドレスATを初期値され、後述の比較部43からの一致信号CMPごとに配置情報サイズSPIが加算されて出力される。メモリコントローラ2は、SDRAM3に対し、アドレスSAを出力して、配置情報PIをアクセスする。これにより、アドレスPA2を先頭とする位置から配置情報サイズSPI分のデータが、SDRAM3から画像表示装置1に転送されることとなる。

【0042】

第2配置情報保持部32では、アドレスPA2に対応する、SDRAM3から出力される配置情報PIの要素のうち座標X,Y、ライン番号LNおよび水平サイズHSが取得され保持される。また、保持された各要素は、座標IX,IY、第2ライン番号LN2および第2水平サイズHS2として出力される。

ライン番号保持部33では、後述の出力許可信号DENがハイレベルの期間で、第2ライン番号LN2が保持され、第3ライン番号LN3が出力される。

【0043】

FIFOリード制御部34では、入力される第3ライン番号LN3に応じてFIFO0〜FIFO7へのリード信号RCK0〜RCK7のうちいずれか一つを出力して、FIFOに対するリード制御を行う。FIFOから出力される出力データDOは、4画素分のデータ幅を有するため、1度の読み出しで4画素分のデータを出力することができる。従って、リード信号RCK0〜RCK7は、4クロックの表示クロックDCKごとに同期して出力される。

【0044】

次いで、同期制御部40について説明する。同期制御部40は、第2配置情報保持部32から出力される座標IX,IYを保持する座標情報保持部41と、フレーム画像FPの同期信号からスキャン位置を生成するフレーム画像データスキャン位置生成部42と、座標情報保持部41およびフレーム画像データスキャン位置生成部42からの出力を比較する比較部43と、比較部43のタイミングで出力許可信号DENを出力する出力許可信号カウンタ44とを備えている。

【0045】

座標情報保持部41は、比較部43から出力される一致信号CMPが活性化されるごとに、座標IX,IYを保持し、座標LX,LYとして出力する。

【0046】

フレーム画像データスキャン位置生成部42は、フレーム画像FPの同期信号である、表示クロックDCKと、垂直同期信号VSYNCと、水平同期信号HSYNCとを入力とし、フレーム画像FPにおける現在のスキャン位置を生成する。フレーム画像データスキャン位置生成部42は、いずれも図示しないが、垂直方向の位置をカウントするVカウンタと、水平方向の位置をカウントするHカウンタとを含んでいる。

【0047】

Vカウンタは、図8に示すように、垂直同期信号VSYNCのローレベルでリセットされ、水平同期信号HSYNCの立ち上がりエッジでインクリメントされる。Vカウンタの計数出力は座標DYとして出力される。

【0048】

一方、Hカウンタは、図9に示すように、水平同期信号HSYNCのローレベルでリセットされ、表示クロックDCKの立ち上がりエッジでインクリメントされる。Hカウンタの計数出力は座標DXとして出力される。

【0049】

比較部43は、座標情報保持部41から出力される座標LX,LYおよびフレーム画像データスキャン位置生成部42から出力される座標DX,DYを、X方向およびY方向についてそれぞれ比較し、座標が一致する場合に一致信号CMPにハイレベルを出力する。

【0050】

出力許可信号カウンタ44は、第2配置情報保持部32から出力される第2水平サイズHS2および比較部43から出力される一致信号CMPを入力とし、出力許可信号DENを出力とする。出力許可信号カウンタ44は、一致信号CMPがハイレベルに遷移すると、出力許可信号DENにハイレベルを出力すると共に、表示クロックDCKを計数し、第2水平サイズHS2で参照される画素数に達するまでハイレベルを保持する。

【0051】

次いで、図9を参照して画像表示装置1の出力動作について説明する。

出力に先立ち、図示しないが、VSYNCがローレベルに遷移することにより、第2配置情報保持部32において、第2ライン番号LN2、第2水平サイズHS2および座標IX,IYが保持される。それぞれの値は、第2ライン番号LN2=0、第2水平サイズHS2=8および座標IX,IY=(12,8)である(図4参照)。

【0052】

(1)は、Vカウンタ値が8であるタイミングを指している。以降、表示クロックDCKにより、Hカウンタ値がインクリメントされる。

(2)において、Hカウンタ値が12に達すると、FIFOリード制御部34は、第3ライン番号LN3の値0で決定されるFIFO0に対し、リード信号RCK0を出力し、出力選択部50により、FIFO0からの出力データD0が選択され出力データDOとして出力される。この出力データDOは、不図示のシフト回路により、1画素ずつ表示クロックDCKに同期して出力される。

【0053】

また、比較部43で出力される一致信号CMPがハイレベルに遷移し、これに応じて、出力許可信号カウンタ44で出力される出力許可信号DENがハイレベルに遷移する。さらに、出力許可信号カウンタ44では、第2水平サイズHS2で参照される8画素を下回る期間において、出力許可信号DENのハイレベルが保持される。

【0054】

一方、一致信号CMPがハイレベルに遷移することにより、第2配置情報参照ポインタ31は、アドレスPA2を出力して、次の配置情報PIの読み出しをメモリコントローラ2に対して要求する。メモリコントローラ2は、第2配置情報PI2が有効になると、データ有効信号DAV2にハイレベルを出力する。第2配置情報保持部32は、データ有効信号DAV2に応じて、第2配置情報PI2を保持する。

(3)において、第2配置情報保持部32から出力される第2水平サイズHS2、第2ライン番号LN2および座標IX,IYは、それぞれ、16、0および(50,8)に更新される。

【0055】

(4)において、出力許可信号カウンタ44は、8画素分の表示クロックDCKを計数すると、ただちに出力許可信号DENがローレベルに遷移する。出力許可信号DENのローレベルへの遷移に応じて、座標情報保持部41では、座標IX,IYが更新される。さらに、ライン番号保持部33でも、第3ライン番号LN3が更新される。

【0056】

次いで、本実施形態にかかる画像表示装置1により、フレーム画像FPの一部に重畳されるフォントデータFD0〜1のデータの流れについて、図10を参照して説明する。

まず、(1)〜(4)において、図6で示したように、フォントデータFD0は、単位転送データRDATAごとに、配置情報PIの情報を参照しつつ、ライン番号LNに対応するFIFOに格納される。すなわち、フォントデータFD0のライン番号LN=0のデータがFIFO0に、ライン番号LN=1のデータがFIFO1に、ライン番号LN=2のデータがFIFO2に、ライン番号LN=3のデータがFIFO3に、それぞれバースト転送により格納される。各スキャンラインは8画素あるため、対応するFIFOには、4画素ずつ2分割して格納されることになる(図6参照)。

【0057】

さらに、(5)〜(8)において、フォントデータFD1は、フォントデータFD0と同様に、単位転送データRDATAごとに、配置情報PIの情報を参照しつつ、ライン番号LNに対応するFIFOに格納される。すなわち、フォントデータFD1のライン番号LN=0のデータがFIFO0に、ライン番号LN=1のデータがFIFO1に、ライン番号LN=2のデータがFIFO2に、ライン番号LN=3のデータがFIFO3に、それぞれバースト転送される。各スキャンラインは16画素あるため、対応するFIFOには、4画素ずつ4分割して格納されることになる(図7参照)。

【0058】

本発明の画像表示装置1では、単位転送データRDATAは、スキャンラインのライン番号LNに応じて選択されるFIFOに、バースト転送により入力される。従って、バースト転送ごとに、複数のスキャンラインがFIFOに入力される場合には、単位転送データRDATAは、スキャンラインのライン番号LNごとに、FIFOに格納されることになる。第1ラスタ画像データに重畳して出力する際には、出力すべきスキャンラインのライン番号LNに応じたFIFOを選択することにより正しく表示することができる。このため、本発明では、単位転送データRDATAを格納する手段としてFIFOを備えて、しかも、FIFOからのスキャンライン出力の並べ替えなどのように複雑な制御をすることなしで、正しくフレーム画像FPに重畳して出力することができる画像表示装置1とすることができる。

【0059】

また、図10において、本実施形態の画像表示装置1では、格納された単位転送データRDATAは、[1]〜[8]の順で出力される。

[1]において、配置情報テーブルPITの先頭に位置する配置情報PIに含まれるライン番号LN=0および水平サイズHS=8が参照され、FIFO0から読み出される8画素分のデータが、フレーム画像FPに重畳して出力する。また、[2]において、配置情報テーブルPITの2番目に位置する配置情報PIに含まれるライン番号LN=0および水平サイズHS=16が参照され、FIFOから読み出される16画素分のデータが、フレーム画像FPに重畳して出力される。以下、[3]〜[8]においても、同様に配置情報テーブルPITから対応するライン番号LNおよび水平サイズHSが参照されて、FIFOから読み出されるデータがフレーム画像FPに重畳して配置される。

【0060】

本発明の画像表示装置1では、フォントデータFDをバースト転送により、FIFOに格納する際、および、FIFOに格納されたフォントデータFDをフレーム画像FPに重畳して出力する際に、同一の配置情報テーブルPITを参照している。これにより、配置情報テーブルを一つで済ませることができ、SDRAM3の領域を効率よく使用することができる。

【0061】

なお、本発明は前記実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲内で種々の改良、変形が可能であることは言うまでもない。

例えば、入力制御部20において、第1カウンタ21は、バースト転送ごとに0値に初期化され、データ転送クロックSCKが入力されるごとにインクリメントされる回路であり、そのラインカウント値LNCと、サイズ比HSVとが比較されて、転送データ数の判定がなされていた。これに対して、第1カウンタ21が、バースト転送ごとにサイズ比HSVの値に初期化され、データ転送クロックSCKごとにデクリメントされる回路とし、その出力が0値であるか否かを判定してもよい。

【0062】

なお、フレーム画像FPは、第1ラスタ画像データの一例、フォントデータFDは、第2ラスタ画像データの一例、第1配置情報保持部12は、第1ライン番号識別信号保持部および第1画素数信号保持部の一例、FIFOライト制御部22は、第2カウンタの一例、出力許可信号カウンタ44は、第3カウンタの一例を示している。

【0063】

ここで、本発明の技術思想により、背景技術における課題を解決するための手段を以下に列記する。

(付記1)入力許可信号に応じて、1つのフレームに表示される第1ラスタ画像データの一部に重畳して配置される第2ラスタ画像データが、前記第2ラスタ画像データにおけるスキャンラインの単位または前記スキャンラインの単位がn分割されたn分割単位を単位転送データとし、複数の該単位転送データを備えて、バースト転送により入力される画像表示装置であって、バースト転送一回当りに転送される前記スキャンラインと同数のFIFOと、前記単位転送データを、前記スキャンラインのライン番号に応じて選択される前記FIFOに格納する入力制御部と、を備えることを特徴とする画像表示装置。

(付記2)付記1に記載の画像表示装置であって、前記入力制御部は、前記ライン番号が更新されるごとに計数される第1カウンタを含み、前記第1カウンタの計数値に基づき前記FIFOを識別することを特徴とする画像表示装置。

(付記3)付記2に記載の画像表示装置であって、前記第1ラスタ画像データに少なくとも1つの前記第2ラスタ画像データが重畳される場合、個々の前記第2ラスタ画像データにおけるライン番号を識別するライン番号識別情報を含む要素が、各々の前記第2ラスタ画像データについて、前記第1ラスタ画像データのスキャン順に整列された情報列と、前記スキャンラインの入力ごとに、前記情報列から、前記要素を順次取得し、前記要素のうち前記ライン番号識別情報を出力する第1情報取得部と、前記第1情報取得部から出力される前記ライン番号識別情報が、前記バースト転送において先頭の前記単位転送データに対応するスキャンラインのライン番号である場合には、前記ライン番号識別情報を、第1ライン番号識別信号として保持する第1ライン番号識別信号保持部と、を備え、前記第1カウンタは、前記第1ライン番号識別信号の更新ごとに、初期化され、前記入力制御部は、前記第1カウンタの計数値、または、前記第1カウンタの計数値および前記第1ライン番号識別信号に基づき、前記FIFOのうち1つを選択して前記第2ラスタ画像データを格納することを特徴とする画像表示装置。

(付記4)付記3に記載の画像表示装置であって、前記第1カウンタは、前記第1ライン番号識別信号の更新ごとに、0に初期化され、前記入力制御部は、前記第1カウンタの計数値および前記第1ライン番号識別信号を加算する加算部を含み、前記加算部の結果に応じて、前記FIFOのうち1つを選択して前記第2ラスタ画像データを格納することを特徴とする画像表示装置。

(付記5)付記3に記載の画像表示装置であって、前記情報列は、個々の前記第2ラスタ画像データにおけるスキャンライン当りの画素数を示す画素数情報を要素としてさらに含み、前記第1情報取得部は、前記第1情報取得部から出力される前記ライン番号識別情報が、前記バースト転送において先頭の前記単位転送データに対応するスキャンラインのライン番号である場合には、前記画素数情報を、第1画素数信号として保持する第1画素数信号保持部を備え、前記入力制御部は、前記バースト転送にかかる転送クロックを計数する第2カウンタを有し、前記第2カウンタの計数値が、前記第1演算部の前記第1画素数信号に基づき得られる前記スキャンライン当りの画素数を、前記単位転送データ当りの画素数で除して得られる出力値を上回るごとに、選択される前記FIFOを更新することを特徴とする画像表示装置。

(付記6)付記1に記載の画像表示装置であって、前記第1ラスタ画像データに少なくとも1つの前記第2ラスタ画像データが重畳される場合、個々の前記第2ラスタ画像データにおけるライン番号を識別するライン番号識別情報を含む要素が、各々の前記第2ラスタ画像データについて、前記第1ラスタ画像データのスキャン順に整列された情報列と、前記スキャンラインの出力ごとに、前記情報列から、前記要素を順次取得し、前記要素のうち前記ライン番号識別情報に応じて、前記FIFOのうち1つを選択して、前記単位転送データを出力する出力制御部と、を備えることを特徴とする画像表示装置。

(付記7)付記6に記載の画像表示装置であって、前記情報列は、個々の前記第2ラスタ画像データにおけるスキャンライン当りの画素数を示す画素数情報を要素としてさらに含み、前記第2情報取得部は、取得した前記要素のうち前記画素数情報を、第2画素数信号として出力し、前記出力制御部は、出力クロックに同期して、前記単位転送データを出力し、前記出力クロックを計数する第3カウンタと、前記第2画素数信号に基づき得られる前記スキャンライン当りの画素数を、前記単位転送データ当りの画素数で除する第2演算部とを有し、前記第3カウンタの計数値が、前記第2演算部の出力値を上回るごとに、選択される前記FIFOを更新することを特徴とする画像表示装置。

(付記8)付記1に記載の画像表示装置であって、前記FIFOについて、バースト転送可能な残存領域があるか否かを判定し、残存領域がある場合には、前記入力許可信号を活性化するFIFO残存領域判定部を備える画像表示装置。

(付記9)付記8に記載の画像表示装置であって、前記FIFOは、格納されるデータに対する、ライトアドレスおよびリードアドレスの差分に基づき、残存する容量の状態を示すFIFO残存容量情報を出力する残存容量情報演算部を備え、前記FIFO残存領域判定部は、前記バースト転送における最後の前記単位転送データが格納される前記FIFOの前記FIFO残存容量情報およびバースト転送されるスキャンライン当りの前記単位転送データの単位数に基づき、前記バースト転送可能か否かを判定することを特徴とする画像表示装置。

(付記10)付記1に記載の画像表示装置であって、前記FIFOにおける段数の最大値は、前記フレームのスキャンライン方向に連続して配置される前記第2ラスタ画像データについて、各々のスキャンライン当りの前記単位転送データの単位数の合計値とすることを特徴とする画像表示装置。

(付記11)入力許可信号に応じて、1フレームに表示される第1ラスタ画像データの一部に重畳して配置される第2ラスタ画像データを、前記第2ラスタ画像データにおけるスキャンラインの単位または前記スキャンラインの単位がn分割されたn分割単位を単位転送データとし、複数の該単位転送データを備えて、バースト転送するステップと、バースト転送一回当りに転送される前記スキャンラインと同数のFIFOに対し、前記単位転送データを、前記第2ラスタ画像データにおける前記スキャンラインのライン番号に応じて選択される前記FIFOに格納するステップと、を備えることを特徴とする画像表示装置の制御方法。

(付記12)付記11に記載の画像表示装置の制御方法であって、前記第2ラスタ画像データを格納するステップは、前記ライン番号が更新されるごとに計数するステップと、前記計数するステップの結果に基づき前記FIFOを識別可能にするステップと、を含むことを特徴とする画像表示装置の制御方法。

【図面の簡単な説明】

【0064】

【図1】本実施形態の画像表示装置の回路構成を示す回路ブロック図である。

【図2】フレーム画像および重畳されるラスタ画像の関係を示す配置図である。

【図3】フォントデータの一例を示す構成図である。

【図4】配置情報テーブルの各要素の一例を示す構成図である。

【図5】配置情報テーブルにおける配置情報の構成図である。

【図6】8画素のフォントデータにおけるバースト転送のタイミングを示すタインミングチャートである。

【図7】16画素のフォントデータにおけるバースト転送のタイミングを示すタインミングチャートである。

【図8】VSYNC,HSYNCおよびVカウンタ値の関係を示すタイミングチャートである。

【図9】画像表示装置における出力タイミングを示すタイミングチャートである。

【図10】画像表示装置におけるフォントデータの流れを示すデータフロー図である。

【符号の説明】

【0065】

1 画像表示装置

2 メモリコントローラ

3 SDRAM

10 フォントアドレス生成部

11 第1配置情報参照ポインタ

12 第1配置情報保持部

13 フォントアドレス生成部

20 入力制御部

21 第1カウンタ

22 FIFOライト制御部

30 出力制御部

31 第2配置情報参照ポインタ

32 第2配置情報保持部

33 ライン番号保持部

34 FIFOリード制御部

40 同期制御部

41 座標情報保持部

42 フレーム画像データスキャン位置生成部

43 比較部

44 出力許可信号カウンタ

50 出力選択部

60 入力許可信号生成部

【技術分野】

【0001】

本発明は画像表示装置に関し、特にフォントやピクチャデータなどのラスタ画像をフレーム画像の一部に重畳して表示する画像表示装置に関する。

【背景技術】

【0002】

このような画像表示装置では、フレーム画像における表示のスキャン中に、フォントやピクチャデータなどの表示ラスタ画像を、予め格納されるメモリから、所定時間内に転送しなくてはならない。この所定時間は、フレーム画像の表示クロックや解像度などで決定される。ラスタ画像の転送が、所定時間内になされない場合には、フレーム画像に、ラスタ画像が正しく表示されなくなるため、ラスタ画像の転送に要する時間を短縮する必要があった。

【0003】

特許文献1に開示される画像表示装置は、フォントデータ変換回路122と、フォントアドレス生成回路123とを備えている。ビデオメモリ136にビデオメモリプレーン103を加え、文字表示のスキャンラインを指定するスキャンラインカウント手段の出力に対応して、メモリインタフェース124を介して、ビデオメモリプレーン103の連続空間から各文字のフォントデータを表示データの1つとしてスキャンライン単位毎の文字テキストコード順に連続してアクセスおよび転送し、表示回路125からCRT装置に画像信号を出力する。

【0004】

これにより、同一のスキャンラインにおける表示文字が、文字コードの離れている文字で構成される場合でも、フォントデータがスキャンライン単位に連続した256バイトのビデオメモリ領域に格納されているため、常にDRAMの高速アクセスを使用して転送することができ、ひいては、転送に要する時間を短縮することができる。

【特許文献1】特開平10−161638

【発明の開示】

【発明が解決しようとする課題】

【0005】

近年、画像データを格納するような大容量メモリとして、バースト転送により高速に大量のデータを転送することができるため、SDRAMを用いることが主流になりつつある。SDRAMにおけるバースト転送では、連続するアドレスに格納されるデータが高速に転送される反面、バースト転送に先立ち、転送元アドレスやバースト長などの設定にかかる期間が長いため、バースト長が短い場合には、データ転送におけるスループットの低下を招くこととなる。

【0006】

しかしながら、特許文献1の画像表示装置において、フォントデータを格納するメモリとしてSDRAMを用いる場合には、以下の問題が生じる。

すなわち、特許文献1の画像表示装置では、1つのフォントデータについて、連続するアドレスに格納されるデータが1スキャンライン分のみであるため、1度のバースト転送において転送されるフォントデータの転送量が1スキャンライン分に制限される。1スキャンライン当りのフォントデータが小さい場合には、バースト長が短くなり、スループットの低下を招くこととなり問題である。

【0007】

さらに、特許文献1の画像表示装置では、フォントデータが格納されているビデオメモリプレーン102とは別の空間でビデオメモリプレーン102と同容量のビデオメモリプレーン103が必要である。このため、ビデオメモリサイズが大きくなり、ひいては画像表示装置の回路規模が大きくなり問題である。

【0008】

ところで、一般的なバースト転送を行う装置では、バースト転送における転送先の記憶装置にFIFOを用いることが知られている。そこで、ラスタ画像をフレーム画像の一部に重畳して表示する画像表示装置において、バースト転送の転送先の記憶装置にFIFOを用いる場合について想定し、このような画像表示装置について考察する。

FIFOを用いた画像表示装置について、バースト転送ごとに、1つのスキャンラインのみが転送される場合には、フレーム画像のスキャン順と同じ順に、スキャンラインがFIFOに格納されることとなる。従って、格納順にFIFOからスキャンラインを取り出すことにより、正しくフレーム画像に重畳して出力することができる。

【0009】

これに対して、バースト転送ごとに、複数のスキャンラインが転送される場合には、連続して複数のスキャンラインがFIFOに格納されることとなる。すなわち、FIFOへのスキャンラインの格納順が、フレーム画像のスキャン順に一致しないということになる。このため、FIFOから格納順にスキャンラインを取り出しても、正しくフレーム画像に重畳して出力することができない。正しく出力するためには、FIFOからのスキャンライン出力の並び替えをフレーム画像のスキャン順に行なうなどの手段を講じる必要が生じる。このため、FIFOの制御が複雑になり、ひいては、画像表示装置の複雑化を招来し問題である。

【0010】

本発明は前記背景技術の課題に鑑みてなされたものであって、SDRAMにおけるバースト転送のスループットを向上させ、FIFOの制御を簡易に行うことができる画像表示装置およびその制御方法を提供することを目的とする。

【課題を解決するための手段】

【0011】

その解決手段は、入力許可信号に応じて、1つのフレームに表示される第1ラスタ画像データの一部に重畳して配置される第2ラスタ画像データが、前記第2ラスタ画像データにおけるスキャンラインの単位または前記スキャンラインの単位がn分割されたn分割単位を単位転送データとし、複数の該単位転送データを備えて、バースト転送により入力される画像表示装置であって、バースト転送一回当りに転送される前記スキャンラインと同数のFIFOと、前記単位転送データを、前記スキャンラインのライン番号に応じて選択される前記FIFOに格納する入力制御部と、を備えることを特徴とする画像表示装置である。

【0012】

また、他の解決手段は、入力許可信号に応じて、1フレームに表示される第1ラスタ画像データの一部に重畳して配置される第2ラスタ画像データを、前記第2ラスタ画像データにおけるスキャンラインの単位または前記スキャンラインの単位がn分割されたn分割単位を単位転送データとし、複数の該単位転送データを備えて、バースト転送するステップと、バースト転送一回当りに転送される前記スキャンラインと同数のFIFOに対し、前記単位転送データを、前記第2ラスタ画像データにおける前記スキャンラインのライン番号に応じて選択される前記FIFOに格納するステップと、を備えることを特徴とする画像表示装置の制御方法である。

【0013】

本発明の画像表示では、単位転送データは、スキャンラインのライン番号に応じて選択されるFIFOに、バースト転送により入力される。従って、バースト転送ごとに、複数のスキャンラインがFIFOに入力される場合には、単位転送データは、スキャンラインのライン番号ごとに、FIFOに格納されることになる。第1ラスタ画像データに重畳して出力する際には、出力すべきスキャンラインのライン番号に応じたFIFOを選択することにより正しく表示することができる。このため、本発明では、単位転送データを格納する手段としてFIFOを備えて、しかも、FIFOからのスキャンライン出力の並べ替えなどのように複雑な制御をすることなしで、正しく第1ラスタ画像データに重畳して出力することができる画像表示装置となし得る。

【発明の効果】

【0014】

本発明を適用することにより、SDRAMにおけるバースト転送のスループットを向上させ、FIFOの制御を簡易に行うことができる画像表示装置およびその制御方法を提供することができる。

【発明を実施するための最良の形態】

【0015】

以下、本発明の実施にかかる発明について具体化した実施形態を図1〜図10を参照しつつ詳細に説明する。

【0016】

図1は、本発明の一例である画像表示装置1の回路ブロック図である。

画像表示装置1は、ラスタ画像からなるフォントデータFDを、予め定められた配置情報PIに基づいて、ラスタ画像からなるフレーム画像FPの一部に重畳して出力するためのシステムである。

【0017】

画像表示装置1の説明に先立ち、フレーム画像FP、フォントデータFD0〜2および配置情報PIについて説明する。

図2は、フレーム画像FPの一部に重畳されて配置されるフォントデータFD0〜2の一例を示している。フォントデータFD0〜2は、1画素当り1バイトのサイズからなるラスタ画像データであり、フォントデータFD0は“A”文字を表わす8バイト×8バイトのサイズのラスタ画像データ、フォントデータFD1は“B”文字を表わす16バイト×8バイトのサイズのラスタ画像データ、フォントデータFD2は“C”文字を表わす8バイト×8バイトのサイズのラスタ画像データである。また、それぞれのフォントデータFD0〜2に対応するカッコ内の数字は、配置される座標を表わしている。例えば、フォントデータFD0における(12,8)は、フォントデータFD0が水平方向の座標X=12、垂直方向の座標Y=8に配置されていることを示している。それぞれの座標Xおよび座標Yは、1刻みで設定可能であり、図2の例では、フォントデータFD2は、フォントデータFD0およびフォントデータFD1に対して、垂直方向に4だけずれた位置に配置されている。

【0018】

フォントデータFDは、後述するSDRAM3のフォントデータ領域FDRから転送されて出力される。図3に示すように、フォントデータ領域FDRには、フォントデータFDがフォント番号FN単位ごとのスキャンライン順に格納されている。また、フォントデータFDの種類ごとに異なる番号となるフォント番号FNが割り振られている。本実施形態では、フォント番号FNについて、フォントデータFD0には0が、フォントデータFD1には1が、フォントデータFD2には2がそれぞれ割り振られている。また、各フォントデータFDにおいて、スキャンラインごとにライン番号LNが割り振られている。フォントデータFD0およびFD2には、8画素ごとに異なるライン番号LNが割り振られ、フォントデータFD1には、16画素ごとに異なるライン番号LNが割り振られている。

本実施形態の画像表示装置1においては、バス幅は4バイト(32ビット)であり、バースト長は8ワード固定であるため、バースト転送ごとに、32バイト分のフォントデータFDが転送されることとなる。

【0019】

次いで、フレーム画像FPに対する各フォントデータを配置するための配置情報PIについて説明する。

配置情報PIは、各フォントデータFDのスキャンラインごとに、配置する座標X,Yと、フォント番号FNと、ライン番号LNと、フォントの水平サイズを示す水平サイズHSと、フォントデータの格納先の先頭アドレスを示す先頭アドレスADSとを要素として持つ。図4に示すように、この配置情報PIは、それぞれの座標X,Yの情報に基づき、フレーム画像FPのスキャン順に整列されて、配置情報テーブルPITとして構成されている。すなわち、配置情報テーブルPITにおいて、配置情報PIは、座標Yが小さいほど先頭近くに配置され、同じ座標Yの場合には、座標Xが小さいほど先頭近くに配置されることとなる。

【0020】

なお、本実施例では、この配置情報テーブルPITは、SDRAM3の連続する領域に格納される。図5に示すように、一つの配置情報PIには、座標X,Y、フォント番号FN、ライン番号LN、水平サイズHSおよび先頭アドレスADSがこの順に格納されている。また、それぞれの配置情報PIは、座標X,Yに基づき、フレーム画像FPのスキャン順に配置されている。また、配置におけるアドレスの間隔は、1つの配置情報PIが占める領域のサイズである配置情報サイズSPIである。すなわち、図5に示すように、配置情報テーブルPITにおいて先頭に配置される配置情報PIを配置情報PI0とし、その先頭アドレスを先頭アドレスATとすると、次に配置される配置情報PIのアドレスは、先頭アドレスAT+配置情報サイズSPIのアドレス値となる。

【0021】

図1に戻り、画像表示装置1の各部について詳細に説明する。画像表示装置1には、メモリコントローラ2を介して、SDRAM3が接続されている。画像表示装置1から、出力許可信号DENとともに32ビットの出力データDOが出力される。出力データDOはさらに、図示しないシフト回路により、1画素ごとのデータに分割されて、フレーム画像FPの一部に重畳される。

【0022】

さらに、画像表示装置1は、FIFO0〜FIFO7と、フォントデータFDのバースト転送に際し、SDRAM3に格納されているフォントデータFDの転送開始アドレスを生成するフォントアドレス発生部10と、FIFO0〜FIFO7に対するライト制御を行う入力制御部20と、FIFO0〜FIFO7に対するリード制御を行う出力制御部30と、フレーム画像および出力データDOとの同期処理を行う同期制御部40と、FIFO0〜FIFO7の出力から1つを選択して、出力データDOを出力する出力選択部50と、入力許可信号IENを生成する入力許可信号生成部60とを備えている。

【0023】

フォントアドレス発生部10は、第1配置情報参照ポインタ11と、第1配置情報保持部12と、フォントアドレス生成部13とを備えている。

【0024】

第1配置情報参照ポインタ11では、SDRAM3からFIFO0〜FIFO7へのバースト転送に必要な第1配置情報PI1を参照するためのアドレスPA1がメモリコントローラ2に出力される。このアドレスPA1は、配置情報テーブルPITの先頭アドレスATを初期値とし、フォントアドレス生成部13からの第1カウント指令信号P1CKごとに配置情報サイズSPIが加算されて出力される。メモリコントローラ2は、SDRAM3に対し、アドレスSAを出力して、配置情報PIをアクセスする。これにより、アドレスPA1を先頭とする位置から配置情報サイズSPI分のデータが、SDRAM3から画像表示装置1に転送されることとなる。

【0025】

第1配置情報保持部12では、アドレスPA1に対応する、SDRAM3から出力される第1配置情報PI1の要素のうちフォント番号FN、ライン番号LN、水平サイズHSおよび先頭アドレスADSが取得され保持される。また、保持された各要素は、第1フォント番号FN1、第1ライン番号LN1、第1水平サイズHS1および第1先頭アドレスADS1として出力される。

【0026】

フォントアドレス生成部13は、第1フォント番号FN1、第1ライン番号LN1、第1水平サイズHS1、第1先頭アドレスADS1および入力許可信号IENを入力とし、フォントアドレスFAおよび第1カウント指令信号P1CKを出力とする。

【0027】

フォントアドレスFAは、バースト転送ごとに出力される、SDRAM3からバースト転送される際のフォントデータの先頭アドレスである。フォントアドレス生成部13は、ライン番号LNおよび水平サイズHSに基づき、転送の対象となるフォントデータがバースト転送時の先頭データであるか否かを判断し、フォントデータが先頭データである場合には、フォントアドレスFAを出力する。バースト転送時の先頭データの判断について、本実施形態ではバースト長が8ワード固定であり、バースト転送当り32画素(32バイト)のデータが転送されるため、32画素ごとの先頭のライン番号LNを有するものが先頭データであると判断される。例えば、スキャンライン方向のサイズが8画素のフォントデータでは、バースト転送当り、スキャンライン4つ分のフォントデータが転送される。従って、ライン番号LNが0および4のデータがバースト転送の際の先頭データであると判断される。一方、スキャンライン方向のサイズが16画素のフォントデータでは、バースト転送当り、スキャンライン2つ分のフォントデータが転送される。従って、ライン番号LNが0、2、4、6のデータがバースト転送の際の先頭データであると判断される。

また、フォントアドレスFAの演算は、具体的には、取得された第1先頭アドレスADS1にフォントデータ領域FDRの先頭アドレスAFDが加えられることでなされる。

【0028】

入力許可信号生成部60では、FIFO0〜FIFO7からそれぞれ出力されるFIFOフル信号FF0〜FF7および第1ライン番号LN1および第1水平サイズHS1を入力とし、入力許可信号IENを出力とする。FIFOフル信号FF0〜FF7は、FIFO0〜FIFO7において、バースト転送に必要な残存メモリ領域の容量がない場合には、活性状態に遷移する信号である。入力許可信号生成部60は、FIFOフル信号FF0〜FF7に応じて、FIFO0〜FIFO7にバースト転送に必要な容量があるか否かを判断し、SDRAM3からのバースト転送を許可する入力許可信号IENを活性状態にする。この入力許可信号IENは、バースト転送先のFIFOフル信号のうちいずれか一つが活性状態になると、非活性状態に遷移し、バースト転送先のうち最後のスキャンラインのデータが格納されるFIFOのFIFOフル信号が非活性状態になると、活性状態に遷移する。すなわち、バースト転送の対象となるフォントデータの第1ライン番号LN1および第1水平サイズHS1に基づき選択されるFIFOフル信号FF0〜FF7のうち一つに応じて、入力許可信号IENが活性状態に遷移することとなる。

【0029】

例えば、スキャンライン方向のサイズが8画素のフォントデータでは、バースト転送当り、スキャンライン4つ分のフォントデータが転送される。従って、FIFOフル信号FF0〜FF3(またはFF4〜FF7)が活性状態になると、入力許可信号IENは、活性状態に遷移する。また、ライン番号LNが3(または7)のフォントデータがバースト転送の際の最後のデータとなるため、FIFOフル信号FF3(またはFF7)が非活性状態になると、入力許可信号IENは活性状態に遷移する。

一方、スキャンライン方向のサイズが16画素のフォントデータでは、バースト転送当り、スキャンライン2つ分のフォントデータが転送される。従って、FIFOフル信号FF0,FF1(または、FF2,FF3、FF4,FF5、FF6,FF7)が活性状態になると、入力許可信号IENは、活性状態に遷移する。また、ライン番号LNが1(または3、5、7)のフォントデータがバースト転送の際の最後のデータとなるため、FIFOフル信号FF1(またはFF3、FF5、FF7)が非活性状態になると、入力許可信号IENは活性状態に遷移する。

【0030】

次いで、入力制御部20について詳細な説明を行なう。

入力制御部20は、スキャンライン単位のフォントデータが転送されるごとにインクリメントされるフォントライン数第1カウンタ21と、第1カウンタ21の結果に応じて、SDRAM3からのフォントデータを格納するFIFOの書き込み制御を行うFIFOライト制御部22とを備える。

【0031】

第1カウンタ21は、第1水平サイズHS1およびデータ転送クロックSCKを入力とし、計数結果のラインカウント数LNCを出力とする。ラインカウント数LNCは、バースト転送ごとにラインカウント数LNCは0値に初期化され、スキャンライン単位のフォントデータが入力されるごとにインクリメントされる。データ転送クロックSCK当り4画素のデータが転送されることから、第1水平サイズHS1分のフォントデータを転送するのに足りるクロック数のデータ転送クロックSCKが入力された場合に、ラインカウント数LNCがインクリメントされる。すなわち、フォントデータFDの第1水平サイズHS1を、バースト転送のデータ幅である4画素で除したサイズ比HSVごとにインクリメントがなされる。このサイズ比HSVは、具体的には、図示しない第1水平サイズHS1に対する2ビット右シフト回路で求められる。

【0032】

例えば、スキャンライン方向が8画素のフォントデータでは、サイズ比HSVは2であり、2クロックのデータ転送クロックSCKごとに、ラインカウント数LNCがインクリメントされる。一方、スキャンライン方向が16画素のフォントデータでは、サイズ比HSVは4であり、4クロックのデータ転送クロックSCKごとに、ラインカウント数LNCがインクリメントされる。

【0033】

FIFOライト制御部22は、第1ライン番号LN1、ラインカウント数LNC、入力許可信号IENおよびデータ転送クロックSCKを入力とし、FIFO0〜FIFO7へのライト信号WCK0〜WCK7のうちいずれか一つを出力する。図6および図7で示すように、FIFOライト制御部22では、第1ライン番号LN1およびラインカウント数LNCが加算されて選択FIFO番号FSNが算出され、選択FIFO番号FSNに応じたFIFOに対し、データ転送クロックSCKのタイミングに基づくライト信号WCKnが出力される。

【0034】

次いで、フォントデータFDのバースト転送について、図6および図7を参照して説明する。

図6は、スキャンラインあたり8画素であるフォントデータFD0のバースト転送のタイミングを示す波形図である。

フォントデータFD0は、バースト転送ごとに4つのスキャンラインが転送され、FIFOに格納される。例えば、(1)および(2)で転送されるデータは、ライン番号LN=0のスキャンラインである。これと同様に、(3)〜(16)についても、2つのデータで一つのスキャンラインを転送することとなる。

また、サイズ比HSVが2であるため、第1カウンタ21は、2つのデータ転送クロックSCKごとに更新される。すなわち、第1カウンタ21は、(3)、(5)、(7)、(9)、(11)、(13)および(15)のタイミングで更新されることになる。

【0035】

(1)において、第1ライン番号LN1は、0であり、第1カウンタ21は初期化され、ラインカウント数LNCには0が出力される。これにより選択FIFO番号FSNは0となり、FIFO0に対するライト信号WCK0に、データ転送クロックSCKと同相のネガティブパルスが出力される。これにより、単位転送データRDATAの内容がFIFO0に格納される。

【0036】

(2)において、第1カウンタ21は、更新されないで、ラインカウント数LNCには引き続き0が出力される。従って、選択FIFO番号FSNは0であり、FIFO0に対するライト信号WCK0に、データ転送クロックSCKと同相のネガティブパルスが出力される。これにより、単位転送データRDATAの内容がFIFO0に格納される。

【0037】

(3)において、第1カウンタ21は、更新され、ラインカウント数LNCには1が出力される。従って、選択FIFO番号FSNは1に遷移し、FIFO1に対するライト信号WCK1に、データ転送クロックSCKと同相のネガティブパルスが出力される。これにより、単位転送データRDATAの内容がFIFO1に格納される。以降、(4)〜(8)についてもラインカウント数LNCに基づき選択FIFO番号FSNが決定され、選択FIFO番号FSNに応じたFIFOに対し、ライト信号WCKnにネガティブパルスが出力される。

また、(9)〜(16)についても、第1ライン番号LN1が4に遷移し、ラインカウント数LNCに4を加算して選択FIFO番号FSNが決定され、選択FIFO番号FSNに応じたFIFOに対し、ライト信号WCKnにネガティブパルスが出力される。

【0038】

図7は、スキャンラインあたり16画素であるフォントデータFD1のバースト転送のタイミングを示す波形図である。

フォントデータFD1は、バースト転送ごとに2つのスキャンラインが転送されFIFOに格納される。例えば、(1)〜(4)で転送されるデータは、ライン番号LN=0のスキャンラインである。これと同様に、(5)〜(16)についても、4つのデータで一つのスキャンラインを転送することとなる。

また、サイズ比HSVが4であるため、第1カウンタ21は、4つのデータ転送クロックSCKごとに転送される。すなわち、第1カウンタ21は、(5)、(9)および(13)のタイミングで更新されることになる。

【0039】

(1)において、第1ライン番号LN1は、0であり、第1カウンタ21は初期化され、ラインカウント数LNCには0が出力される。これにより選択FIFO番号FSNは0となり、FIFO0に対するライト信号WCK0に、データ転送クロックSCKと同相のネガティブパルスが出力される。これにより、単位転送データRDATAの内容がFIFO0に格納される。(2)〜(4)についても、(1)と同様に、FIFO0に対するライト信号WCK0に、データ転送クロックSCKと同相のネガティブパルスが出力される。これにより、それぞれの単位転送データRDATAの内容がFIFO0に格納される。

【0040】

(5)において、第1カウンタ21は、更新され、ラインカウント数LNCには1が出力される。従って、選択FIFO番号FSNは1に遷移し、FIFO1に対するライト信号WCK1に、データ転送クロックSCKと同相のネガティブパルスが出力される。これにより、単位転送データRDATAの内容がFIFO1に格納される。(6)〜(8)についても、(5)と同様に、FIFO1に対するライト信号WCK1に、データ転送クロックSCKと同相のネガティブパルスが出力される。これにより、それぞれの単位転送データRDATAの内容がFIFO1に格納される。

また、(9)〜(16)についても、第1ライン番号LN1が2に遷移し、ラインカウント数LNCに2を加算して選択FIFO番号FSNが決定され、選択FIFO番号FSNに応じたFIFOに対し、ライト信号WCKnにネガティブパルスが出力される。

【0041】

次いで、出力制御部30について説明する。

出力制御部30は、第2配置情報参照ポインタ31と、第2配置情報保持部32と、ライン番号保持部33と、FIFOリード制御部34とを備えている。

第2配置情報参照ポインタ31では、SDRAM3からFIFO0〜FIFO7へのバースト転送に必要な第2配置情報PI2を参照するためのアドレスSA2がメモリコントローラ2に出力される。このアドレスSA2は、VSYNCがローレベルに遷移するごとに、配置情報テーブルPITの先頭アドレスATを初期値され、後述の比較部43からの一致信号CMPごとに配置情報サイズSPIが加算されて出力される。メモリコントローラ2は、SDRAM3に対し、アドレスSAを出力して、配置情報PIをアクセスする。これにより、アドレスPA2を先頭とする位置から配置情報サイズSPI分のデータが、SDRAM3から画像表示装置1に転送されることとなる。

【0042】

第2配置情報保持部32では、アドレスPA2に対応する、SDRAM3から出力される配置情報PIの要素のうち座標X,Y、ライン番号LNおよび水平サイズHSが取得され保持される。また、保持された各要素は、座標IX,IY、第2ライン番号LN2および第2水平サイズHS2として出力される。

ライン番号保持部33では、後述の出力許可信号DENがハイレベルの期間で、第2ライン番号LN2が保持され、第3ライン番号LN3が出力される。

【0043】

FIFOリード制御部34では、入力される第3ライン番号LN3に応じてFIFO0〜FIFO7へのリード信号RCK0〜RCK7のうちいずれか一つを出力して、FIFOに対するリード制御を行う。FIFOから出力される出力データDOは、4画素分のデータ幅を有するため、1度の読み出しで4画素分のデータを出力することができる。従って、リード信号RCK0〜RCK7は、4クロックの表示クロックDCKごとに同期して出力される。

【0044】

次いで、同期制御部40について説明する。同期制御部40は、第2配置情報保持部32から出力される座標IX,IYを保持する座標情報保持部41と、フレーム画像FPの同期信号からスキャン位置を生成するフレーム画像データスキャン位置生成部42と、座標情報保持部41およびフレーム画像データスキャン位置生成部42からの出力を比較する比較部43と、比較部43のタイミングで出力許可信号DENを出力する出力許可信号カウンタ44とを備えている。

【0045】

座標情報保持部41は、比較部43から出力される一致信号CMPが活性化されるごとに、座標IX,IYを保持し、座標LX,LYとして出力する。

【0046】

フレーム画像データスキャン位置生成部42は、フレーム画像FPの同期信号である、表示クロックDCKと、垂直同期信号VSYNCと、水平同期信号HSYNCとを入力とし、フレーム画像FPにおける現在のスキャン位置を生成する。フレーム画像データスキャン位置生成部42は、いずれも図示しないが、垂直方向の位置をカウントするVカウンタと、水平方向の位置をカウントするHカウンタとを含んでいる。

【0047】

Vカウンタは、図8に示すように、垂直同期信号VSYNCのローレベルでリセットされ、水平同期信号HSYNCの立ち上がりエッジでインクリメントされる。Vカウンタの計数出力は座標DYとして出力される。

【0048】

一方、Hカウンタは、図9に示すように、水平同期信号HSYNCのローレベルでリセットされ、表示クロックDCKの立ち上がりエッジでインクリメントされる。Hカウンタの計数出力は座標DXとして出力される。

【0049】

比較部43は、座標情報保持部41から出力される座標LX,LYおよびフレーム画像データスキャン位置生成部42から出力される座標DX,DYを、X方向およびY方向についてそれぞれ比較し、座標が一致する場合に一致信号CMPにハイレベルを出力する。

【0050】

出力許可信号カウンタ44は、第2配置情報保持部32から出力される第2水平サイズHS2および比較部43から出力される一致信号CMPを入力とし、出力許可信号DENを出力とする。出力許可信号カウンタ44は、一致信号CMPがハイレベルに遷移すると、出力許可信号DENにハイレベルを出力すると共に、表示クロックDCKを計数し、第2水平サイズHS2で参照される画素数に達するまでハイレベルを保持する。

【0051】

次いで、図9を参照して画像表示装置1の出力動作について説明する。

出力に先立ち、図示しないが、VSYNCがローレベルに遷移することにより、第2配置情報保持部32において、第2ライン番号LN2、第2水平サイズHS2および座標IX,IYが保持される。それぞれの値は、第2ライン番号LN2=0、第2水平サイズHS2=8および座標IX,IY=(12,8)である(図4参照)。

【0052】

(1)は、Vカウンタ値が8であるタイミングを指している。以降、表示クロックDCKにより、Hカウンタ値がインクリメントされる。

(2)において、Hカウンタ値が12に達すると、FIFOリード制御部34は、第3ライン番号LN3の値0で決定されるFIFO0に対し、リード信号RCK0を出力し、出力選択部50により、FIFO0からの出力データD0が選択され出力データDOとして出力される。この出力データDOは、不図示のシフト回路により、1画素ずつ表示クロックDCKに同期して出力される。

【0053】

また、比較部43で出力される一致信号CMPがハイレベルに遷移し、これに応じて、出力許可信号カウンタ44で出力される出力許可信号DENがハイレベルに遷移する。さらに、出力許可信号カウンタ44では、第2水平サイズHS2で参照される8画素を下回る期間において、出力許可信号DENのハイレベルが保持される。

【0054】

一方、一致信号CMPがハイレベルに遷移することにより、第2配置情報参照ポインタ31は、アドレスPA2を出力して、次の配置情報PIの読み出しをメモリコントローラ2に対して要求する。メモリコントローラ2は、第2配置情報PI2が有効になると、データ有効信号DAV2にハイレベルを出力する。第2配置情報保持部32は、データ有効信号DAV2に応じて、第2配置情報PI2を保持する。

(3)において、第2配置情報保持部32から出力される第2水平サイズHS2、第2ライン番号LN2および座標IX,IYは、それぞれ、16、0および(50,8)に更新される。

【0055】

(4)において、出力許可信号カウンタ44は、8画素分の表示クロックDCKを計数すると、ただちに出力許可信号DENがローレベルに遷移する。出力許可信号DENのローレベルへの遷移に応じて、座標情報保持部41では、座標IX,IYが更新される。さらに、ライン番号保持部33でも、第3ライン番号LN3が更新される。

【0056】

次いで、本実施形態にかかる画像表示装置1により、フレーム画像FPの一部に重畳されるフォントデータFD0〜1のデータの流れについて、図10を参照して説明する。

まず、(1)〜(4)において、図6で示したように、フォントデータFD0は、単位転送データRDATAごとに、配置情報PIの情報を参照しつつ、ライン番号LNに対応するFIFOに格納される。すなわち、フォントデータFD0のライン番号LN=0のデータがFIFO0に、ライン番号LN=1のデータがFIFO1に、ライン番号LN=2のデータがFIFO2に、ライン番号LN=3のデータがFIFO3に、それぞれバースト転送により格納される。各スキャンラインは8画素あるため、対応するFIFOには、4画素ずつ2分割して格納されることになる(図6参照)。

【0057】

さらに、(5)〜(8)において、フォントデータFD1は、フォントデータFD0と同様に、単位転送データRDATAごとに、配置情報PIの情報を参照しつつ、ライン番号LNに対応するFIFOに格納される。すなわち、フォントデータFD1のライン番号LN=0のデータがFIFO0に、ライン番号LN=1のデータがFIFO1に、ライン番号LN=2のデータがFIFO2に、ライン番号LN=3のデータがFIFO3に、それぞれバースト転送される。各スキャンラインは16画素あるため、対応するFIFOには、4画素ずつ4分割して格納されることになる(図7参照)。

【0058】

本発明の画像表示装置1では、単位転送データRDATAは、スキャンラインのライン番号LNに応じて選択されるFIFOに、バースト転送により入力される。従って、バースト転送ごとに、複数のスキャンラインがFIFOに入力される場合には、単位転送データRDATAは、スキャンラインのライン番号LNごとに、FIFOに格納されることになる。第1ラスタ画像データに重畳して出力する際には、出力すべきスキャンラインのライン番号LNに応じたFIFOを選択することにより正しく表示することができる。このため、本発明では、単位転送データRDATAを格納する手段としてFIFOを備えて、しかも、FIFOからのスキャンライン出力の並べ替えなどのように複雑な制御をすることなしで、正しくフレーム画像FPに重畳して出力することができる画像表示装置1とすることができる。

【0059】

また、図10において、本実施形態の画像表示装置1では、格納された単位転送データRDATAは、[1]〜[8]の順で出力される。

[1]において、配置情報テーブルPITの先頭に位置する配置情報PIに含まれるライン番号LN=0および水平サイズHS=8が参照され、FIFO0から読み出される8画素分のデータが、フレーム画像FPに重畳して出力する。また、[2]において、配置情報テーブルPITの2番目に位置する配置情報PIに含まれるライン番号LN=0および水平サイズHS=16が参照され、FIFOから読み出される16画素分のデータが、フレーム画像FPに重畳して出力される。以下、[3]〜[8]においても、同様に配置情報テーブルPITから対応するライン番号LNおよび水平サイズHSが参照されて、FIFOから読み出されるデータがフレーム画像FPに重畳して配置される。

【0060】

本発明の画像表示装置1では、フォントデータFDをバースト転送により、FIFOに格納する際、および、FIFOに格納されたフォントデータFDをフレーム画像FPに重畳して出力する際に、同一の配置情報テーブルPITを参照している。これにより、配置情報テーブルを一つで済ませることができ、SDRAM3の領域を効率よく使用することができる。

【0061】

なお、本発明は前記実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲内で種々の改良、変形が可能であることは言うまでもない。

例えば、入力制御部20において、第1カウンタ21は、バースト転送ごとに0値に初期化され、データ転送クロックSCKが入力されるごとにインクリメントされる回路であり、そのラインカウント値LNCと、サイズ比HSVとが比較されて、転送データ数の判定がなされていた。これに対して、第1カウンタ21が、バースト転送ごとにサイズ比HSVの値に初期化され、データ転送クロックSCKごとにデクリメントされる回路とし、その出力が0値であるか否かを判定してもよい。

【0062】

なお、フレーム画像FPは、第1ラスタ画像データの一例、フォントデータFDは、第2ラスタ画像データの一例、第1配置情報保持部12は、第1ライン番号識別信号保持部および第1画素数信号保持部の一例、FIFOライト制御部22は、第2カウンタの一例、出力許可信号カウンタ44は、第3カウンタの一例を示している。

【0063】

ここで、本発明の技術思想により、背景技術における課題を解決するための手段を以下に列記する。

(付記1)入力許可信号に応じて、1つのフレームに表示される第1ラスタ画像データの一部に重畳して配置される第2ラスタ画像データが、前記第2ラスタ画像データにおけるスキャンラインの単位または前記スキャンラインの単位がn分割されたn分割単位を単位転送データとし、複数の該単位転送データを備えて、バースト転送により入力される画像表示装置であって、バースト転送一回当りに転送される前記スキャンラインと同数のFIFOと、前記単位転送データを、前記スキャンラインのライン番号に応じて選択される前記FIFOに格納する入力制御部と、を備えることを特徴とする画像表示装置。

(付記2)付記1に記載の画像表示装置であって、前記入力制御部は、前記ライン番号が更新されるごとに計数される第1カウンタを含み、前記第1カウンタの計数値に基づき前記FIFOを識別することを特徴とする画像表示装置。

(付記3)付記2に記載の画像表示装置であって、前記第1ラスタ画像データに少なくとも1つの前記第2ラスタ画像データが重畳される場合、個々の前記第2ラスタ画像データにおけるライン番号を識別するライン番号識別情報を含む要素が、各々の前記第2ラスタ画像データについて、前記第1ラスタ画像データのスキャン順に整列された情報列と、前記スキャンラインの入力ごとに、前記情報列から、前記要素を順次取得し、前記要素のうち前記ライン番号識別情報を出力する第1情報取得部と、前記第1情報取得部から出力される前記ライン番号識別情報が、前記バースト転送において先頭の前記単位転送データに対応するスキャンラインのライン番号である場合には、前記ライン番号識別情報を、第1ライン番号識別信号として保持する第1ライン番号識別信号保持部と、を備え、前記第1カウンタは、前記第1ライン番号識別信号の更新ごとに、初期化され、前記入力制御部は、前記第1カウンタの計数値、または、前記第1カウンタの計数値および前記第1ライン番号識別信号に基づき、前記FIFOのうち1つを選択して前記第2ラスタ画像データを格納することを特徴とする画像表示装置。

(付記4)付記3に記載の画像表示装置であって、前記第1カウンタは、前記第1ライン番号識別信号の更新ごとに、0に初期化され、前記入力制御部は、前記第1カウンタの計数値および前記第1ライン番号識別信号を加算する加算部を含み、前記加算部の結果に応じて、前記FIFOのうち1つを選択して前記第2ラスタ画像データを格納することを特徴とする画像表示装置。

(付記5)付記3に記載の画像表示装置であって、前記情報列は、個々の前記第2ラスタ画像データにおけるスキャンライン当りの画素数を示す画素数情報を要素としてさらに含み、前記第1情報取得部は、前記第1情報取得部から出力される前記ライン番号識別情報が、前記バースト転送において先頭の前記単位転送データに対応するスキャンラインのライン番号である場合には、前記画素数情報を、第1画素数信号として保持する第1画素数信号保持部を備え、前記入力制御部は、前記バースト転送にかかる転送クロックを計数する第2カウンタを有し、前記第2カウンタの計数値が、前記第1演算部の前記第1画素数信号に基づき得られる前記スキャンライン当りの画素数を、前記単位転送データ当りの画素数で除して得られる出力値を上回るごとに、選択される前記FIFOを更新することを特徴とする画像表示装置。

(付記6)付記1に記載の画像表示装置であって、前記第1ラスタ画像データに少なくとも1つの前記第2ラスタ画像データが重畳される場合、個々の前記第2ラスタ画像データにおけるライン番号を識別するライン番号識別情報を含む要素が、各々の前記第2ラスタ画像データについて、前記第1ラスタ画像データのスキャン順に整列された情報列と、前記スキャンラインの出力ごとに、前記情報列から、前記要素を順次取得し、前記要素のうち前記ライン番号識別情報に応じて、前記FIFOのうち1つを選択して、前記単位転送データを出力する出力制御部と、を備えることを特徴とする画像表示装置。

(付記7)付記6に記載の画像表示装置であって、前記情報列は、個々の前記第2ラスタ画像データにおけるスキャンライン当りの画素数を示す画素数情報を要素としてさらに含み、前記第2情報取得部は、取得した前記要素のうち前記画素数情報を、第2画素数信号として出力し、前記出力制御部は、出力クロックに同期して、前記単位転送データを出力し、前記出力クロックを計数する第3カウンタと、前記第2画素数信号に基づき得られる前記スキャンライン当りの画素数を、前記単位転送データ当りの画素数で除する第2演算部とを有し、前記第3カウンタの計数値が、前記第2演算部の出力値を上回るごとに、選択される前記FIFOを更新することを特徴とする画像表示装置。

(付記8)付記1に記載の画像表示装置であって、前記FIFOについて、バースト転送可能な残存領域があるか否かを判定し、残存領域がある場合には、前記入力許可信号を活性化するFIFO残存領域判定部を備える画像表示装置。

(付記9)付記8に記載の画像表示装置であって、前記FIFOは、格納されるデータに対する、ライトアドレスおよびリードアドレスの差分に基づき、残存する容量の状態を示すFIFO残存容量情報を出力する残存容量情報演算部を備え、前記FIFO残存領域判定部は、前記バースト転送における最後の前記単位転送データが格納される前記FIFOの前記FIFO残存容量情報およびバースト転送されるスキャンライン当りの前記単位転送データの単位数に基づき、前記バースト転送可能か否かを判定することを特徴とする画像表示装置。

(付記10)付記1に記載の画像表示装置であって、前記FIFOにおける段数の最大値は、前記フレームのスキャンライン方向に連続して配置される前記第2ラスタ画像データについて、各々のスキャンライン当りの前記単位転送データの単位数の合計値とすることを特徴とする画像表示装置。

(付記11)入力許可信号に応じて、1フレームに表示される第1ラスタ画像データの一部に重畳して配置される第2ラスタ画像データを、前記第2ラスタ画像データにおけるスキャンラインの単位または前記スキャンラインの単位がn分割されたn分割単位を単位転送データとし、複数の該単位転送データを備えて、バースト転送するステップと、バースト転送一回当りに転送される前記スキャンラインと同数のFIFOに対し、前記単位転送データを、前記第2ラスタ画像データにおける前記スキャンラインのライン番号に応じて選択される前記FIFOに格納するステップと、を備えることを特徴とする画像表示装置の制御方法。

(付記12)付記11に記載の画像表示装置の制御方法であって、前記第2ラスタ画像データを格納するステップは、前記ライン番号が更新されるごとに計数するステップと、前記計数するステップの結果に基づき前記FIFOを識別可能にするステップと、を含むことを特徴とする画像表示装置の制御方法。

【図面の簡単な説明】

【0064】

【図1】本実施形態の画像表示装置の回路構成を示す回路ブロック図である。

【図2】フレーム画像および重畳されるラスタ画像の関係を示す配置図である。

【図3】フォントデータの一例を示す構成図である。

【図4】配置情報テーブルの各要素の一例を示す構成図である。

【図5】配置情報テーブルにおける配置情報の構成図である。

【図6】8画素のフォントデータにおけるバースト転送のタイミングを示すタインミングチャートである。

【図7】16画素のフォントデータにおけるバースト転送のタイミングを示すタインミングチャートである。

【図8】VSYNC,HSYNCおよびVカウンタ値の関係を示すタイミングチャートである。

【図9】画像表示装置における出力タイミングを示すタイミングチャートである。

【図10】画像表示装置におけるフォントデータの流れを示すデータフロー図である。

【符号の説明】

【0065】

1 画像表示装置

2 メモリコントローラ

3 SDRAM

10 フォントアドレス生成部

11 第1配置情報参照ポインタ

12 第1配置情報保持部

13 フォントアドレス生成部

20 入力制御部

21 第1カウンタ

22 FIFOライト制御部

30 出力制御部

31 第2配置情報参照ポインタ

32 第2配置情報保持部

33 ライン番号保持部

34 FIFOリード制御部

40 同期制御部

41 座標情報保持部

42 フレーム画像データスキャン位置生成部

43 比較部

44 出力許可信号カウンタ

50 出力選択部

60 入力許可信号生成部

【特許請求の範囲】

【請求項1】

入力許可信号に応じて、1つのフレームに表示される第1ラスタ画像データの一部に重畳して配置される第2ラスタ画像データが、前記第2ラスタ画像データにおけるスキャンラインの単位または前記スキャンラインの単位がn分割されたn分割単位を単位転送データとし、複数の該単位転送データを備えて、バースト転送により入力される画像表示装置であって、

バースト転送一回当りに転送される前記スキャンラインと同数のFIFOと、

前記単位転送データを、前記スキャンラインのライン番号に応じて選択される前記FIFOに格納する入力制御部と、

を備えることを特徴とする画像表示装置。

【請求項2】

請求項1に記載の画像表示装置であって、

前記入力制御部は、

前記ライン番号が更新されるごとに計数される第1カウンタを含み、

前記第1カウンタの計数値に基づき前記FIFOを識別する

ことを特徴とする画像表示装置。

【請求項3】

請求項2に記載の画像表示装置であって、

前記第1ラスタ画像データに少なくとも1つの前記第2ラスタ画像データが重畳される場合、個々の前記第2ラスタ画像データにおけるライン番号を識別するライン番号識別情報を含む要素が、各々の前記第2ラスタ画像データについて、前記第1ラスタ画像データのスキャン順に整列された情報列と、

前記スキャンラインの入力ごとに、前記情報列から、前記要素を順次取得し、前記要素のうち前記ライン番号識別情報を出力する第1情報取得部と、

前記第1情報取得部から出力される前記ライン番号識別情報が、前記バースト転送において先頭の前記単位転送データに対応するスキャンラインのライン番号である場合には、前記ライン番号識別情報を、第1ライン番号識別信号として保持する第1ライン番号識別信号保持部と、

を備え、

前記第1カウンタは、前記第1ライン番号識別信号の更新ごとに、初期化され、

前記入力制御部は、前記第1カウンタの計数値、または、前記第1カウンタの計数値および前記第1ライン番号識別信号に基づき、前記FIFOのうち1つを選択して前記第2ラスタ画像データを格納することを特徴とする画像表示装置。

【請求項4】

請求項3に記載の画像表示装置であって、

前記情報列は、個々の前記第2ラスタ画像データにおけるスキャンライン当りの画素数を示す画素数情報を要素としてさらに含み、

前記第1情報取得部は、前記第1情報取得部から出力される前記ライン番号識別情報が、前記バースト転送において先頭の前記単位転送データに対応するスキャンラインのライン番号である場合には、前記画素数情報を、第1画素数信号として保持する第1画素数信号保持部を備え、

前記入力制御部は、

前記バースト転送にかかる転送クロックを計数する第2カウンタを有し、

前記第2カウンタの計数値が、前記第1演算部の前記第1画素数信号に基づき得られる前記スキャンライン当りの画素数を、前記単位転送データ当りの画素数で除して得られる出力値を上回るごとに、選択される前記FIFOを更新することを特徴とする画像表示装置。

【請求項5】

請求項1に記載の画像表示装置であって、

前記第1ラスタ画像データに少なくとも1つの前記第2ラスタ画像データが重畳される場合、個々の前記第2ラスタ画像データにおけるライン番号を識別するライン番号識別情報を含む要素が、各々の前記第2ラスタ画像データについて、前記第1ラスタ画像データのスキャン順に整列された情報列と、

前記スキャンラインの出力ごとに、前記情報列から、前記要素を順次取得し、前記要素のうち前記ライン番号識別情報に応じて、

前記FIFOのうち1つを選択して、前記単位転送データを出力する出力制御部と、

を備えることを特徴とする画像表示装置。

【請求項6】

請求項5に記載の画像表示装置であって、

前記情報列は、個々の前記第2ラスタ画像データにおけるスキャンライン当りの画素数を示す画素数情報を要素としてさらに含み、

前記第2情報取得部は、取得した前記要素のうち前記画素数情報を、第2画素数信号として出力し、

前記出力制御部は、

出力クロックに同期して、前記単位転送データを出力し、

前記出力クロックを計数する第3カウンタと、

前記第2画素数信号に基づき得られる前記スキャンライン当りの画素数を、前記単位転送データ当りの画素数で除する第2演算部とを有し、

前記第3カウンタの計数値が、前記第2演算部の出力値を上回るごとに、選択される前記FIFOを更新することを特徴とする画像表示装置。

【請求項7】

請求項1に記載の画像表示装置であって、

前記FIFOについて、バースト転送可能な残存領域があるか否かを判定し、残存領域がある場合には、前記入力許可信号を活性化するFIFO残存領域判定部を備える画像表示装置。

【請求項8】

請求項7に記載の画像表示装置であって、

前記FIFOは、格納されるデータに対する、ライトアドレスおよびリードアドレスの差分に基づき、残存する容量の状態を示すFIFO残存容量情報を出力する残存容量情報演算部を備え、

前記FIFO残存領域判定部は、

前記バースト転送における最後の前記単位転送データが格納される前記FIFOの前記FIFO残存容量情報およびバースト転送されるスキャンライン当りの前記単位転送データの単位数に基づき、前記バースト転送可能か否かを判定することを特徴とする画像表示装置。

【請求項9】

入力許可信号に応じて、1フレームに表示される第1ラスタ画像データの一部に重畳して配置される第2ラスタ画像データを、前記第2ラスタ画像データにおけるスキャンラインの単位または前記スキャンラインの単位がn分割されたn分割単位を単位転送データとし、複数の該単位転送データを備えて、バースト転送するステップと、

バースト転送一回当りに転送される前記スキャンラインと同数のFIFOに対し、

前記単位転送データを、前記第2ラスタ画像データにおける前記スキャンラインのライン番号に応じて選択される前記FIFOに格納するステップと、

を備えることを特徴とする画像表示装置の制御方法。

【請求項10】

請求項9に記載の画像表示装置の制御方法であって、

前記第2ラスタ画像データを格納するステップは、

前記ライン番号が更新されるごとに計数するステップと、

前記計数するステップの結果に基づき前記FIFOを識別可能にするステップと、

を含むことを特徴とする画像表示装置の制御方法。

【請求項1】

入力許可信号に応じて、1つのフレームに表示される第1ラスタ画像データの一部に重畳して配置される第2ラスタ画像データが、前記第2ラスタ画像データにおけるスキャンラインの単位または前記スキャンラインの単位がn分割されたn分割単位を単位転送データとし、複数の該単位転送データを備えて、バースト転送により入力される画像表示装置であって、

バースト転送一回当りに転送される前記スキャンラインと同数のFIFOと、

前記単位転送データを、前記スキャンラインのライン番号に応じて選択される前記FIFOに格納する入力制御部と、

を備えることを特徴とする画像表示装置。

【請求項2】

請求項1に記載の画像表示装置であって、

前記入力制御部は、

前記ライン番号が更新されるごとに計数される第1カウンタを含み、

前記第1カウンタの計数値に基づき前記FIFOを識別する

ことを特徴とする画像表示装置。

【請求項3】

請求項2に記載の画像表示装置であって、

前記第1ラスタ画像データに少なくとも1つの前記第2ラスタ画像データが重畳される場合、個々の前記第2ラスタ画像データにおけるライン番号を識別するライン番号識別情報を含む要素が、各々の前記第2ラスタ画像データについて、前記第1ラスタ画像データのスキャン順に整列された情報列と、

前記スキャンラインの入力ごとに、前記情報列から、前記要素を順次取得し、前記要素のうち前記ライン番号識別情報を出力する第1情報取得部と、

前記第1情報取得部から出力される前記ライン番号識別情報が、前記バースト転送において先頭の前記単位転送データに対応するスキャンラインのライン番号である場合には、前記ライン番号識別情報を、第1ライン番号識別信号として保持する第1ライン番号識別信号保持部と、

を備え、

前記第1カウンタは、前記第1ライン番号識別信号の更新ごとに、初期化され、

前記入力制御部は、前記第1カウンタの計数値、または、前記第1カウンタの計数値および前記第1ライン番号識別信号に基づき、前記FIFOのうち1つを選択して前記第2ラスタ画像データを格納することを特徴とする画像表示装置。

【請求項4】

請求項3に記載の画像表示装置であって、

前記情報列は、個々の前記第2ラスタ画像データにおけるスキャンライン当りの画素数を示す画素数情報を要素としてさらに含み、

前記第1情報取得部は、前記第1情報取得部から出力される前記ライン番号識別情報が、前記バースト転送において先頭の前記単位転送データに対応するスキャンラインのライン番号である場合には、前記画素数情報を、第1画素数信号として保持する第1画素数信号保持部を備え、

前記入力制御部は、

前記バースト転送にかかる転送クロックを計数する第2カウンタを有し、

前記第2カウンタの計数値が、前記第1演算部の前記第1画素数信号に基づき得られる前記スキャンライン当りの画素数を、前記単位転送データ当りの画素数で除して得られる出力値を上回るごとに、選択される前記FIFOを更新することを特徴とする画像表示装置。

【請求項5】

請求項1に記載の画像表示装置であって、

前記第1ラスタ画像データに少なくとも1つの前記第2ラスタ画像データが重畳される場合、個々の前記第2ラスタ画像データにおけるライン番号を識別するライン番号識別情報を含む要素が、各々の前記第2ラスタ画像データについて、前記第1ラスタ画像データのスキャン順に整列された情報列と、

前記スキャンラインの出力ごとに、前記情報列から、前記要素を順次取得し、前記要素のうち前記ライン番号識別情報に応じて、

前記FIFOのうち1つを選択して、前記単位転送データを出力する出力制御部と、

を備えることを特徴とする画像表示装置。

【請求項6】

請求項5に記載の画像表示装置であって、

前記情報列は、個々の前記第2ラスタ画像データにおけるスキャンライン当りの画素数を示す画素数情報を要素としてさらに含み、

前記第2情報取得部は、取得した前記要素のうち前記画素数情報を、第2画素数信号として出力し、

前記出力制御部は、

出力クロックに同期して、前記単位転送データを出力し、

前記出力クロックを計数する第3カウンタと、

前記第2画素数信号に基づき得られる前記スキャンライン当りの画素数を、前記単位転送データ当りの画素数で除する第2演算部とを有し、

前記第3カウンタの計数値が、前記第2演算部の出力値を上回るごとに、選択される前記FIFOを更新することを特徴とする画像表示装置。

【請求項7】

請求項1に記載の画像表示装置であって、

前記FIFOについて、バースト転送可能な残存領域があるか否かを判定し、残存領域がある場合には、前記入力許可信号を活性化するFIFO残存領域判定部を備える画像表示装置。

【請求項8】

請求項7に記載の画像表示装置であって、

前記FIFOは、格納されるデータに対する、ライトアドレスおよびリードアドレスの差分に基づき、残存する容量の状態を示すFIFO残存容量情報を出力する残存容量情報演算部を備え、

前記FIFO残存領域判定部は、

前記バースト転送における最後の前記単位転送データが格納される前記FIFOの前記FIFO残存容量情報およびバースト転送されるスキャンライン当りの前記単位転送データの単位数に基づき、前記バースト転送可能か否かを判定することを特徴とする画像表示装置。

【請求項9】

入力許可信号に応じて、1フレームに表示される第1ラスタ画像データの一部に重畳して配置される第2ラスタ画像データを、前記第2ラスタ画像データにおけるスキャンラインの単位または前記スキャンラインの単位がn分割されたn分割単位を単位転送データとし、複数の該単位転送データを備えて、バースト転送するステップと、

バースト転送一回当りに転送される前記スキャンラインと同数のFIFOに対し、

前記単位転送データを、前記第2ラスタ画像データにおける前記スキャンラインのライン番号に応じて選択される前記FIFOに格納するステップと、

を備えることを特徴とする画像表示装置の制御方法。

【請求項10】

請求項9に記載の画像表示装置の制御方法であって、

前記第2ラスタ画像データを格納するステップは、

前記ライン番号が更新されるごとに計数するステップと、

前記計数するステップの結果に基づき前記FIFOを識別可能にするステップと、

を含むことを特徴とする画像表示装置の制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2007−114489(P2007−114489A)

【公開日】平成19年5月10日(2007.5.10)

【国際特許分類】

【出願番号】特願2005−305877(P2005−305877)

【出願日】平成17年10月20日(2005.10.20)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

【公開日】平成19年5月10日(2007.5.10)

【国際特許分類】

【出願日】平成17年10月20日(2005.10.20)

【出願人】(000005223)富士通株式会社 (25,993)

【Fターム(参考)】

[ Back to top ]