画像表示装置およびその駆動方法

【課題】画像表示装置において、発光素子の経時的変化による発光輝度の変化を駆動トランジスタの特性変動の影響を抑制した形で補償する。

【解決手段】画像表示装置において、複数の画素を備え、各前記画素は、通電により発光する発光素子(OLED)と、前記発光素子の発光を制御するドライバ素子(Td)と、発光素子及び前記ドライバ素子に対して電気的に接続され、少なくとも前記発光素子の発光中に前記発光素子に印加される電圧を直接的または間接的に検出し、該検出結果を前記ドライバ素子に反映させる制御回路(A)とを備える。

【解決手段】画像表示装置において、複数の画素を備え、各前記画素は、通電により発光する発光素子(OLED)と、前記発光素子の発光を制御するドライバ素子(Td)と、発光素子及び前記ドライバ素子に対して電気的に接続され、少なくとも前記発光素子の発光中に前記発光素子に印加される電圧を直接的または間接的に検出し、該検出結果を前記ドライバ素子に反映させる制御回路(A)とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、有機ELディスプレイ装置等の画像表示装置およびその駆動方法に関するものである。

【背景技術】

【0002】

従来から、発光層に注入された正孔と電子とが再結合することによって光を生じる機能を有する有機EL(Electroluminescence)素子を用いた画像表示装置が提案されている。

【0003】

この種の画像表示装置では、例えばアモルファスシリコンや多結晶シリコン等で形成された薄膜トランジスタ(Thin Film Transistor:以下「TFT」という)や有機EL素子の一つである有機発光ダイオード(Organic Light Emitting Diode:以下「OLED」という)などが各画素を構成しており、各画素に適切な電流値が設定されることにより、各画素の輝度が制御される。

【0004】

例えば、OLEDなどの電流駆動型発光素子と、OLEDに流れる電流を制御する、例えばTFTなどの駆動トランジスタとが直列に配置された複数の画素を有するアクティブ・マトリクス型の画像表示装置では、各画素に設けられた駆動トランジスタの閾値電圧のばらつきにより、発光素子に流れる電流値が変化して輝度むらが発生する。この現象を改善するための手法として、例えば駆動トランジスタの閾値電圧を予め検出するとともに、検出した閾値電圧に基づいて発光素子に流れる電流を制御する方式(例えば非特許文献1)や、当該方式に基づく具体的な回路構成(例えば非特許文献2)などが開示されている。

【0005】

また、駆動トランジスタの閾値電圧のばらつきに加え、OLEDにも経時的な変化があり、自身への印加電圧に応じて自身の電流密度や輝度が変化(低下)するといった現象が知られている。この現象に対処するための手法として、光導電素子を用いることなく、単純な回路構成にて経時変化に伴う輝度の変化を補うことが可能な表示装置およびその駆動方法を開示した文献が存在する(例えば特許文献1)。この特許文献1では、発光素子への印加電圧や発光素子に流れる電流を検出するとともに、検出した検出電圧または検出電流に基づいて発光素子の輝度を補正するようにしている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2003−330418号公報

【非特許文献】

【0007】

【非特許文献1】R.M.A. Dawson,et al.(1998).Design of an Improved Pixel for a Polysilicon Active−Matrix Organic LED Display. SID98 Digest,pp.11−14.

【非特許文献2】S.Ono,et al.(2003).Pixel Circuit for a−Si AM−OLED.Proceedings of IDW’03,pp.255−258.

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、上記特許文献1に示された手法では、OLEDなどの発光素子を含む回路の電流または電圧の検出処理や、発光素子の輝度変化の補正処理を画素内で行っていないので、外部回路が複雑かつ大型化するといった問題点があった。

【0009】

本発明は、上記に鑑みてなされたものであって、外部回路を簡素に維持しつつ発光素子の経時的変化による発光輝度の変化を補償する画像表示装置およびその駆動方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明にかかる画像表示装置は、複数の画素を備え、各前記画素は、通電により発光する発光素子と、前記発光素子に電気的に接続され、前記発光素子の発光を制御するドライバ素子と、前記発光素子及び前記ドライバ素子に対して電気的に接続され、少なくとも前記発光素子の発光中に前記発光素子に印加される電圧を直接的または間接的に検出し、該検出結果を前記ドライバ素子に反映させる制御回路と、を備えている。

【0011】

また本発明に係る画像表示装置の駆動方法において、発光素子と、前記発光素子の発光を制御するドライバ素子と、を備えた画像表示装置を準備するステップと、少なくとも前記発光素子の発光中に、前記発光素子に印加される電圧を直接的または間接的に検出するステップと、少なくとも前記発光素子の発光中に、前記検出された電圧に対応する電圧を前記ドライバ素子に印加するステップと、を備えている。

【発明の効果】

【0012】

本発明によれば、各画素内の回路で発光素子の経時変化による輝度の変化を抑制できるため、発光素子の輝度補償を行っても、外部回路を簡素に維持することができる。

【図面の簡単な説明】

【0013】

【図1】本発明にかかる画像表示装置の一実施形態を説明するための図であり、画像表示装置の1画素に対応する画素回路の構成例を示す図である。

【図2】図1に示した画素回路上にトランジスタの寄生容量および有機発光素子容量を示した回路構成を示す図である。

【図3】図2に示した画素回路の一般的な動作を説明するためのシーケンス図である。

【図4】図3に示した準備期間の動作を説明する図である。

【図5】図3に示した閾値電圧検出期間の動作を説明する図である。

【図6】図3に示した書き込み期間の動作を説明する図である。

【図7】図3に示した発光期間の動作を説明する図である。

【図8】有機発光素子OLEDへの印加電圧と有機発光素子OLEDに流れる電流の電流密度との関係の一例を示す図である。

【図9】有機発光素子OLEDに流れる電流の電流密度と有機発光素子OLEDの発光輝度との関係の一例を示す図である。

【図10】有機発光素子OLEDを制御する駆動トランジスタTdのゲートに印加する電圧(画像信号電位)と有機発光素子OLEDの発光輝度との関係の一例を示す図である。

【図11】図8〜図10と同様な試験を行った際の、501時間経過後のΔVoledとΔVgsとの関係を示す図である。

【図12】図11の特性図上(破線P3)にそれぞれ48.5時間経過後(実線P1)および165.5時間経過後(破線P2)の特性曲線を重ね合わせた図である。

【図13】本実施の形態にかかる補償手法に基づいて補償した補償後の特性(駆動トランジスタTdのゲートに印加する画像信号電位と有機発光素子OLEDの発光輝度特性)を示す図である。

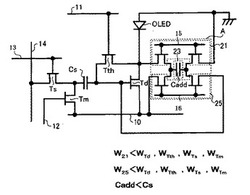

【図14】本実施の形態にかかる補償手法を図1に示した画素回路に適用する場合の一構成例を示す図である。

【図15】図14に示した画素回路の動作を説明するためのシーケンス図である。

【図16】図14に示した画素回路の動作を説明するための他のシーケンス図である。

【図17】本発明にかかる画像表示装置の他の実施形態を説明するための図であり、画像表示装置の1画素に対応する画素回路の構成例を示す図である。

【図18】本発明にかかる画像表示装置の他の実施形態を説明するための図であり、画像表示装置の1画素に対応する画素回路の構成例を示す図である。

【発明を実施するための形態】

【0014】

以下に、本発明の画像表示装置およびその駆動方法にかかる実施の形態を図面に基づいて詳細に説明する。なお、この実施の形態により本発明が限定されるものではない。

【0015】

図1は、本発明にかかる画像表示装置の一実施形態を説明するための図であり、画像表示装置の1画素に対応する画素回路の構成例を示す図である。同図に示す画素回路は、発光素子の一つである有機発光素子OLED、有機発光素子OLEDを駆動するためのドライバ素子である駆動トランジスタTd、閾値電圧検出用トランジスタTth、保持容量Csと、スイッチングトランジスタTsと,スイッチングトランジスタTmと、を備えるように構成されている。なお、図1に示す構成は、有機発光素子などを制御する画素回路の一般的構成であり、本発明の特徴を示すものではない。また、この画像表示装置は複数の画素をマトリックス状に配列した構成を有している。

【0016】

図1において、駆動トランジスタTdは、第1の端子であるゲートと第2の端子であるソースとの間に与えられる電位差に応じて有機発光素子OLEDに流れる電流量を制御するための制御素子(駆動素子)である。

【0017】

閾値電圧検出用トランジスタTthは、オン状態となったときに、駆動トランジスタTdのゲートとドレインとを電気的に接続する。その結果、駆動トランジスタTdのゲート・ソース間の電位差が実質的に駆動トランジスタTdの閾値電圧Vthとなるまで、駆動トランジスタTdのゲートからドレインに向かって電流が流れ、駆動トランジスタTdの閾値電圧Vthが検出される。

【0018】

有機発光素子OLEDは、有機発光素子OLEDの閾値電圧以上の電位差がアノード−カソード間に印加されることにより、電流が流れて発光する特性を有する素子である。具体的には、有機発光素子OLEDは、例えば、Al、CuまたはITO(Indium Tin Oxide)等によって形成されたアノード層およびカソード層と、アノード層とカソード層との間に介在され、フタルシアニン、トリスアルミニウム錯体、ベンゾキノリノラト、ベリリウム錯体等の有機系の材料によって形成された発光層と、を少なくとも備えた構造を有している。そして、有機発光素子OLEDは、発光層に注入された正孔と電子とが再結合することによって光を生じる機能を有する。

【0019】

駆動トランジスタTd、閾値電圧検出用トランジスタTth、スイッチングトランジスタTsおよびスイッチングトランジスタTmは、例えば、薄膜トランジスタとして構成される。なお、以下で参照される各図面においては、各薄膜トランジスタについてのチャネル(n型またはp型)については、特に明示していないが、n型またはp型のいずれを用いてもよい。本実施形態においては、各薄膜トランジスタとして、n型の薄膜トランジスタを用いている。また各薄膜トランジスタは、非晶質シリコン、微結晶シリコン、及びポリシリコンのいずれを用いても良い。

【0020】

電源線10は、駆動トランジスタTdおよびスイッチングトランジスタTmに複数の所定電圧を供給する。Tth制御線11は、閾値電圧検出用トランジスタTthの駆動を制御するための信号を閾値電圧検出用トランジスタTthに供給する。マージ線12は、スイッチングトランジスタTmの駆動を制御するための信号をスイッチングトランジスタTmに供給する。走査線13は、スイッチングトランジスタTsの駆動を制御するための信号をスイッチングトランジスタTsに供給する。画像信号線14は、画像信号を保持容量Csに供給する。

【0021】

なお、図1では、有機発光素子OLEDのアノード側にグラウンド線を、カソード側に電源線10を配するようにしているが、アノード側に電源線10を、カソード側にグランド線を配するようにしても良い。また、有機発光素子OLEDのアノード側およびカソード側の双方に対して電源線を配置するようにしてもよい。

【0022】

ところで、トランジスタには、一般的にゲート・ソース間およびゲート・ドレイン間に寄生容量が存在する。本実施形態において駆動トランジスタTdのゲート電位に影響を与える寄生容量は、駆動トランジスタTdのゲート・ソース間容量CgsTd、駆動トランジスタTdのゲート・ドレイン間容量CgdTd、および閾値電圧検出用トランジスタTthのゲート・ソース間容量CgsTth、閾値電圧検出用トランジスタTthのゲート・ドレイン間容量CgdTthである。なお、これらの寄生容量と、有機発光素子OLEDが固有に有している有機発光素子容量Coledを加えたものを図2に示す。

【0023】

つぎに、本実施の形態の動作について、図3〜図7を参照して説明する。ここで、図3は、図2に示した画素回路の一般的な動作を説明するためのシーケンス図であり、図4〜図7は、4つの期間に区分された準備期間(図4)、閾値電圧検出期間(図5)、書き込み期間(図6)および発光期間(図7)の各区間の動作を説明するための図である。なお、以下に説明する動作は、制御部(図示略)の制御下で行われる。

【0024】

(準備期間)

準備期間の動作については、図3および図4を参照して説明する。準備期間では、電源線10が高電位(Vp)、マージ線12が高電位(VgH)、Tth制御線11が低電位(VgL)、走査線13が低電位(VgL)、画像信号線14がゼロ電位とされる。これにより、図4に示すように、閾値電圧検出用トランジスタTthがオフ、スイッチングトランジスタTsがオフ、駆動トランジスタTdがオン、スイッチングトランジスタTmがオンとされ、電源線10→駆動トランジスタTd→有機発光素子容量Coledという経路で電流が流れ、有機発光素子容量Coledに電荷が蓄積される。なお、この準備期間で有機発光素子容量Coledに電荷を蓄積する理由は、後述する閾値電圧検出期間に駆動トランジスタTdのドレイン・ソース間電流(以下「Ids」と表記)が実質的に流れなくなる状態における駆動トランジスタTdのゲート・ソース間電圧(すなわち駆動トランジスタTdの閾値電圧)を検出する際に、有機発光素子容量Coledを駆動トランジスタTdのドレイン・ソース間に流す電流の供給源として作用させるためである。

【0025】

(閾値電圧検出期間)

つぎに、閾値電圧検出期間の動作について図3および図5を参照して説明する。閾値電圧検出期間では、電源線10がゼロ電位、マージ線12が高電位(VgH)、Tth制御線11が高電位(VgH)、走査線13が低電位(VgL)、画像信号線14がゼロ電位とされる。これにより、図5に示すように、閾値電圧検出用トランジスタTthがオンとなり、駆動トランジスタTdのゲートとドレインとが接続される。

【0026】

また、保持容量Csおよび有機発光素子容量Coledに蓄積された電荷が放電され、駆動トランジスタTd→電源線10という経路で電流が流れる。そして、駆動トランジスタTdのゲート−ソース間の電位差が閾値電圧Vthに実質的に達すると、駆動トランジスタTdが実質的にオフとされ、駆動トランジスタTdの閾値電圧Vthが検出される。

【0027】

(書き込み期間)

さらに、書き込み期間の動作について図3および図6を参照して説明する。書き込み期間では、データ電位(−Vdata)を保持容量Csに供給することにより、駆動トランジスタTdのゲート電位を、データ電位に応じた所望の電位に変化させることが行われる。具体的には、電源線10がゼロ電位、マージ線12が低電位(VgL)、Tth制御線11が高電位(VgH)、走査線13が高電位(VgH)、画像信号線14がデータ電位(−Vdata)とされる。

【0028】

これにより、図6に示したように、スイッチングトランジスタTsがオン、スイッチングトランジスタTmがオフとなり、有機発光素子容量Coledに蓄積された電荷が放電され、有機発光素子容量Coled→閾値電圧検出用トランジスタTth→保持容量Csという経路で電流が流れ、保持容量Csに電荷が蓄積される。すなわち、有機発光素子容量Coledに蓄積された電荷は、保持容量Csに移動する。その結果、駆動トランジスタTdのゲート電位がデータ電位に対応した電位となる。

【0029】

ここで、駆動トランジスタTdの閾値電圧をVth、保持容量Csの容量値をCs、閾値電圧検出用トランジスタTthがオンの場合の全容量(すなわち駆動トランジスタTdのゲートに接続された静電容量および寄生容量)をCallとすると、駆動トランジスタTdのゲート電位Vgは、次式で表される(なお、上記仮定は、以下の式についても及ぶものとする)。

【0030】

Vg=Vth−(Cs/Call)・Vdata ・・・(1)

また、保持容量Csの両端の電位差VCsは、次式で表される。

【0031】

VCs=Vg−(−Vdata)=Vth+[(Call−Cs)/Call]・Vdata ・・・(2)

上記(2)式に示される全容量Callは、閾値電圧検出用トランジスタTthの導通時の全容量であり、次式で表される。

【0032】

Call=Coled+Cs+CgsTth+CgdTth+CgsTd ・・・(3)

なお、上記(3)式に駆動トランジスタTdのゲート・ドレイン間容量CgdTdが含まれていないのは、駆動トランジスタTdのゲート・ドレイン間が閾値電圧検出用トランジスタTthによって接続され、駆動トランジスタTd両端が略同電位となっているからである。また、保持容量Csと有機発光素子容量Coledとは、Cs<Coledの関係を満足している。

【0033】

(発光期間)

最後に、発光期間の動作について図3および図7を参照して説明する。発光期間では、電源線10がマイナス電位(−VDD)、マージ線12が高電位(VgH)、Tth制御線11が低電位(VgL)、走査線13が低電位(VgL)、画像信号線14がゼロ電位とされる。

【0034】

これにより、図7に示したように、駆動トランジスタTdがオン、閾値電圧検出用トランジスタTthがオフ、スイッチングトランジスタTsがオフとなり、有機発光素子OLED→駆動トランジスタTd→電源線10という経路で電流が流れ、有機発光素子OLEDが発光する。

【0035】

このとき、駆動トランジスタTdのドレインからソースに流れる電流(すなわちIds)は、駆動トランジスタTdの構造および材質から決定される定数β、駆動トランジスタTdのゲート・ソース間の電位差Vgs、駆動トランジスタTdの閾値電圧Vthを用いて次式で表される。

【0036】

Ids=(β/2)・(Vgs−Vth)2 ・・・(4)

つぎに、駆動トランジスタTdのゲート・ソース間の電位差Vgsと電流Idsとの関係を考察するため、画素回路の寄生容量を考慮しない場合の電位差Vgsを算出する。

【0037】

図7において、発光時には駆動トランジスタTdが導通しており、駆動トランジスタTdのソース電位とドレイン電位が略同電位に保持される。また、図7において、駆動トランジスタTdのゲート電位は、書き込み電位(−Vdata)が保持容量Csと有機発光素子容量Coledとの間で分圧された状態となるので、電位差Vgsは、次式で表せる。

【0038】

Vgs=Vth+Coled/(Cs+Coled)・Vdata ・・・(5)

したがって、駆動トランジスタTdのゲート・ソース間の電位差Vgsと電流Idsとの関係式は、上記(4)式、(5)式を用いて次式のようになる。

【0039】

Ids=(β/2)・(Coled/(Cs+Coled)・Vdata)2

=a・Vdata2 ・・・(6)

(6)式に示されるように、駆動トランジスタTdの閾値電圧Vthを検出することにより、理論的には、閾値電圧Vthに依存しない電流Idsを得ることができる。

【0040】

上述した画素回路は、駆動トランジスタTdの経時的な変化や、駆動トランジスタTdを含む各トランジスタが有する寄生容量の影響を補償する。ところが、駆動トランジスタTdだけでなく、有機発光素子OLEDにも経時的な変化があり、有機発光素子OLEDへの印加電圧に対する有機発光素子OLEDに流れる電流の電流密度特性や、有機発光素子OLEDに流れる電流の電流密度に対する有機発光素子OLEDの発光輝度特性が、有機発光素子OLEDの使用時間に応じて低下することになる。

【0041】

例えば、図8は、有機発光素子OLEDへの印加電圧と有機発光素子OLEDに流れる電流の電流密度との関係の一例を示す図である。なお、同図に示すグラフは、有機発光素子OLEDを連続的に点灯させる常時点灯試験を行った結果を示すものであり、初期(OLED使用時間0時間:実線K1)、OLED使用時間48.5時間経過後(破線K2)、OLED使用時間165.5時間経過後(破線K3)およびOLED使用時間501時間経過後(破線K4)の各特性を示している。なお、同図に示す特性には、上記特許文献1の図2、図7などに示された発光素子の特性とは異なり、駆動トランジスタTdを含む各トランジスタの劣化成分は含まれていない。

【0042】

図8の特性から明らかなように、有機発光素子OLEDの使用時間が長くなるに従って、同一電圧を印加しても、得られる電流密度が小さくなることが分かる。また、同一の発光輝度を得るためには、使用時間の経過に応じて有機発光素子OLEDへの印加電圧を増加させる必要があることも分かる。

【0043】

また、図9は、有機発光素子OLEDに流れる電流の電流密度と有機発光素子OLEDの発光輝度との関係の一例を示す図である。なお、同図に示すグラフは、図8と同様な常時点灯試験を行った試験結果であり、初期(OLED使用時間0時間:実線L1)、OLED使用時間48.5時間経過後(破線L2)、OLED使用時間165.5時間経過後(破線L3)およびOLED使用時間501時間経過後(破線L4)の各特性を示している。なお、同図に示す特性にも、図8と同様に、駆動トランジスタTdを含む各トランジスタの劣化成分は含まれていない。図9から理解されるように、有機発光素子OLEDの使用時間が長くなるに従って有機発光素子OLEDに同一電流を流した場合に得られる発光輝度が小さくなっていることが分かる。また、同一の発光輝度を得るためには、使用時間の経過に応じて有機発光素子OLEDに流す電流を増加させる必要があることも分かる。

【0044】

一方、図10は、有機発光素子OLEDを制御する駆動トランジスタTdのゲートに印加する電圧(画像信号電位)と有機発光素子OLEDの発光輝度との関係の一例を示す図であり、図8および図9と同様な常時点灯試験を行なった試験結果であり、初期(OLED使用時間0時間:実線M1)、OLED使用時間48.5時間経過後(破線M2)、OLED使用時間165.5時間経過後(破線M3)およびOLED使用時間501時間経過後(破線M4)の各特性が示されている。例えば、上述した画素回路の例では、直接的に制御される対象は、有機発光素子OLEDを駆動し、画像信号電位が書き込まれる駆動トランジスタTdのゲートの電位であるので、図10に示すような変動特性を明らかにする必要がある。

【0045】

なお、図10に示す特性においても、図8および図9と同様な特性が表れている。すなわち、閾値電圧Vthを考慮して書き込んだ画像信号電位Vdataを駆動トランジスタTdのゲートに印加したとしても、有機発光素子OLEDの使用時間が大きくなるに従って得られる発光輝度が低下することが分かる。また、同一の発光輝度を得るためには、使用時間の経過に応じて駆動トランジスタTdへの印加電圧を増加させる必要があることも分かる。

【0046】

ところで、上記特許文献1に示された手法は、検出電圧や検出電流を検出したフレーム(以下「検出フレーム」という)内において反映させているのではなく、最短でも検出したフレームよりも1フレーム後のフレームにしか反映させることができない。したがって、従来手法では、例えばフレームの前後で輝度が大きく変化する場合には、適切な補正を行なうことができない。なお、ここでいう「フレーム」とは、画像表示装置のディスプレイに表示される画像を書き換える周期を意味するものであり、例えば、60Hzの周期で駆動されるディスプレイであれば、1フレーム周期が16.67msとなる。

【0047】

一方、後述する本実施形態にかかる手法では、有機発光素子OLEDへの印加電圧の変化を画素回路の内部、すなわち個々の画素回路自身が有機発光素子OLEDに印加される電圧を検出し、検出した電圧に対応する電圧を同一フレーム内で駆動トランジスタTdに反映する。以下、その原理について説明する。

【0048】

発光時における有機発光素子OLEDへの印加電圧Voledの初期値と、有機発光素子OLEDを一定時間使用した後における有機発光素子OLEDへの印加電圧との差分値を「ΔVoled」とする。また、一定時間使用後における有機発光素子OLEDの発光輝度を初期値にまで上げるのに必要なVgsの値(差分値)を「ΔVgs」とする。図11は、上記と同様な常時点灯試験を行った際の、501時間経過後のΔVoledとΔVgsとの関係を示す図である。同図によれば、画像信号電位Vdataに依存してΔVoledおよびΔVgsの両者ともに変化することが分かる。

【0049】

図12は、図11の特性図上(破線P3)にそれぞれ48.5時間使用後(実線P1)および165.5時間使用後(破線P2)の特性曲線を重ね合わせた図である。なお、図12では、所定の傾き(同図の例では、傾き0.43)を有する直線が併せて示されており、本願発明者らは、ΔVoledに対するΔVgsの特性曲線の全体が有機発光素子OLEDの使用時間をパラメータとして、所定の傾きを有する直線に沿って並ぶということを見出している。

【0050】

したがって、発光時における有機発光素子OLEDへの印加電圧の変化ΔVoledに略比例した電圧(図12の例では、比例定数0.43)を駆動トランジスタTdのゲート・ソース間の電位差Vgsに加算するようにすれば、輝度劣化を全階調でほぼ補償することができる。

【0051】

図13は、上述の手法に基づいて補償した補償後の特性を示す図である。補償前の特性を示す図10と比較すれば明らかなように、使用時間に依存する輝度変化を低減することができる。

【0052】

つぎに、上述の電圧加算の実現手法について説明する。なお、実際の制御に際しては、制御の容易性を確保する観点から、ΔVoledに代えてVoledの加算で代用することを考える。なお、無論、ΔVoledに基づく電圧加算を行うことも可能である。

【0053】

いま、有機発光素子OLEDへの印加電圧の初期値をVoled0とし、駆動トランジスタTdのゲート・ソース間に印加する補正後の印加電圧をVgs’とすれば、このVgs’は、上記特性曲線上に示した直線の傾きに相当する比例定数bを用いて次式のように表すことができる。

【0054】

Vgs’=Vgs+ΔVgs

=Vgs+b・ΔVoled

=Vgs+b・(Voled−Voled0) ・・・(7)

また、上記(5)式において、d=Coled/(Cs+Coled)とし、上記(7)式に(5)式を代入することで、補正後の印加電圧をVgs’は、次式で表すことができる。

【0055】

Vgs’=Vth+d・Vdata+b・(Voled−Voled0)

=Vgs+(d・Vdata−b・Voled0)+b・Voled ・・・(8)

上記(8)式において、第2項のb・Voled0は、有機発光素子OLEDの経時変化に依存することなくVdataによって決まる項であり、有機発光素子OLEDの経時変化に依存する項は、第3項のVoledである。したがって、有機発光素子OLEDの経時変化に依存しないb・Voled0を予め考慮することで、上記(8)式に基づいて有機発光素子OLEDの輝度変化を補償することができる。なお、このb・Voled0は有機発光素子OLEDの特性によって決まる定数値なので、例えば図1に示した画素回路であれば、保持容量Csに画像信号電位(−Vdata)を書き込む際に、b・Voled0に対応する所定値を減算した電圧を書き込むようにすれば、有機発光素子OLEDの初期特性を記憶しておく必要はない。また、b・Voled0以外の定数値が加わった場合であっても同様であり、それらの値を記憶する必要はない。

【0056】

図14は、上述の実現手法を図1に示した画素回路に適用する場合の一構成例を示す図である。同図に示す画素回路は、図1に示す構成から、有機発光素子OLEDの両端の電圧を検出する検出手段としての検出回路21と、検出回路21にて検出された電圧を保持する電圧保持手段としての電圧保持回路23と、電圧保持回路23に保持された電圧を駆動トランジスタTdのゲート・ソース間に印加するフィードバック手段としてのフィードバック回路25と、を有する制御回路Aを備えるように構成されている。この制御回路Aは各画素に配設されている。なお、図14では、制御回路Aを構成するトランジスタに存在する寄生容量の表示は省略している。

【0057】

図14において、電圧保持回路23は、電圧を保持可能な追加容量Caddを具備する。また、検出回路21は、例えば電圧保持回路23を介して接続された一対のトランジスタを具備し、それぞれのゲートが第1の制御線であるVoled制御線15に共通的に接続されるような構成を採用することができる。なお、検出回路21の一端(例えば一方のトランジスタのドレインまたはソース)は、有機発光素子OLEDのカソードに接続し、検出回路21の他端(例えば他方のトランジスタのドレインまたはソース)は、有機発光素子OLEDのアノードに接続すればよい。

【0058】

フィードバック回路25は、検出回路21と同様な構成を採ることができる。例えば、電圧保持回路23を介して接続された一対のトランジスタを具備し、それぞれのゲートが第2の制御線であるVoled制御線16に共通的に接続されるような構成を採用することができる。なお、フィードバック回路25の一端(例えば一方のトランジスタのドレインまたはソース)は、駆動トランジスタTdの第1の端子(ゲート)に接続し、フィードバック回路25の他端(例えば他方のトランジスタのドレインまたはソース)は、駆動トランジスタTdの第2の端子(ソースまたはドレイン)に接続すればよい。

【0059】

つぎに、図14に示した画素の動作について、図14および図15を参照して説明する。ここで、図15は、図14に示した画素回路の動作を説明するためのシーケンス図である。

【0060】

図15において、まず、準備期間、Vth検出期間および書き込み期間の動作については、図3に示したシーケンスと同一であり、その説明を省略する。つづいて、発光期間では、Voled制御線15を高電位(VgH)にし、検出回路21を構成する一対のトランジスタを導通させる。一方、Voled制御線16を低電位(VgL)にし、フィードバック回路25を構成する一対のトランジスタを非導通にする。この後、有機発光素子OLEDを発光させると、追加容量Caddに有機発光素子OLEDの両端電圧Voledに基づく電荷が蓄積され、Voledに相当する電圧が電圧保持回路23によって保持される。つづいて、Voled制御線15を低電位(VgL)にし、Voled制御線16を高電位(VgH)にすると、保持容量Csに書き込まれた画像信号電位に追加容量Caddに保持されたVoledが加算されるので、上記(8)式に基づく制御手法を実現することができる。なお、(8)式における比例定数bは、駆動トランジスタTdのゲート・ソース間に電気的に接続される各容量値(駆動トランジスタTdの寄生容量等)と、追加容量Caddとの容量比によって決定されるので、追加容量Caddの容量値を適切に定めることで所望の比例定数を選択することができる。例えば、本実施形態の場合、図12より、比例定数b=0.43である。

【0061】

このように、本実施の形態にかかる画像表示装置では、有機発光素子OLEDへの印加電圧の変化を個々の画素回路自身が検出し、検出した電圧に対応する電圧をドライバ素子へ印加して検出した結果を反映させることができる。それ故、外部回路の構成を簡素に維持することができる。また、駆動トランジスタの特性変動の影響を抑制した有機発光素子OLEDの輝度変化の補償を実現することができる。また、有機発光素子OLEDへの印加電圧を検出する工程と、検出した有機発光素子OLEDへの印加電圧に対応する電圧を駆動トランジスタTdへ印加する工程とを同一フレーム内で行うことにより、有機発光素子OLEDの発光輝度をより適切に補償を行うことができる。またこれら一連の工程は毎フレーム行うことが好ましい。

【0062】

なお、図1などの回路構成から明らかなように、有機発光素子OLEDの両端電圧Voledと駆動トランジスタTdのドレイン・ソース間電圧Vdsとの和は略一定なので、Voledの電圧変化を、これと等価な駆動トランジスタTdのVdsの電圧変化として検出し、検出した電圧に基づいて駆動トランジスタTdを制御するようにしてもよい。この場合には、検出回路21の一端および他端をそれぞれ駆動トランジスタTdのドレイン、ソースに接続すればよい。例えば、図18に示すように、検出回路21を駆動トランジスタTdのドレイン・ソースに接続し、フィードバック回路25を駆動トランジスタTdのゲートと、有機発光素子OLEDのアノードに接続するようにしても良い。図18の画素回路は、図15,16と同様のシーケンスにより駆動することができる。なお、フィードバック回路25を駆動トランジスタTdのゲートと、有機発光素子OLEDのカソード(または駆動トランジスタTdのドレイン)に接続するようにしても良い。しかしながら、図18に示すように、フィードバック回路25の一端を有機発光素子OLEDのアノードに接続し、有機発光素子OLEDを介してフィードバック回路25を駆動トランジスタTdのゲートとドレインに接続する方が有機発光素子OLEDの輝度をダイレクトに調整することができ、輝度補償が容易であるというメリットがある。

【0063】

また、図16は、図15とは異なる他のシーケンス図である。同図に示すシーケンスでは、準備期間中にVoled制御線15を高電位(VgH)とする一方で、Voled制御線16を低電位(VgL)に設定している。なお、準備期間中にVoled制御線15を高電位に設定している場合であっても、Voled制御線16を低電位(VgL)に設定している限りにおいて、追加容量Caddに保持された電圧が駆動トランジスタTdのゲート・ソース間に印加されることはないので問題はない。特に、図15のシーケンスにおいて、発光時間を充分に確保したい場合には、有機発光素子OLEDの両端電圧の検出時間を短くする必要があり、その場合には追加容量Caddへの電荷の蓄積が充分になされないことが考えられる。一方、図16のシーケンスでは、有機発光素子OLEDの両端電圧の検出時間を充分に確保することができる。なお、図16において、Voled制御線15を低電位(VgL)から高電位(VgH)にするタイミングと、Voled制御線16を高電位(VgH)から低電位(VgL)にするタイミングを準備期間中に行うようにしているが、これらのタイミングはVth検出期間あるいは書き込み期間であっても構わない。

【0064】

また、本実施形態において、検出回路21及びフィードバック回路25を構成する薄膜トランジスタのチャネル幅W21、W25は、駆動トランジスタTdのチャネル幅WTdよりも小さくなるように設定されることが好ましい。この場合、制御回路Aの配設に必要なスペースを小さくすることができる。なお、検出回路21やフィードバック回路25に流れる電流は、駆動トランジスタTdに流れる電流よりも小さいため、駆動トランジスタTdよりも検出回路21及びフィードバック回路25のチャネル幅を小さくしても特に問題はない。また、制御回路Aのスペースを小さくするという観点から、検出回路21及びフィードバック回路25を構成する薄膜トランジスタのチャネル幅W21及びW25は、閾値電圧検出用トランジスタTthやスイッチングトランジスタTs,Tm,Tkのチャネル幅WTs、WTm及びWTkよりも小さくすることが好ましい。

【0065】

さらに、電圧保持回路23を構成する追加容量Caddの容量値を駆動トランジスタTdに接続される保持容量Csの容量値よりも小さくすることが好ましい。その理由は、大きいと書込み効率(画像信号線の変化量に対する(Vgs−Vth)の変化量)が低下するからである。

【0066】

また、制御回路Aを構成するトランジスタと、駆動トランジスタTd及びスイッチングトランジスタTs,Tm,Tk等のトランジスタとは、互いに異なる層に形成することが可能である。その結果、1画素の面積を拡大することなく、制御回路Aを配置することができる。

【0067】

また、上述の実施形態においては、駆動トランジスタTdの閾値電圧Vthを検出するための閾値電圧検出用トランジスタTthを有する画素回路に対して本発明を適用したが、閾値電圧検出用トランジスタTthを有さない、図17のような画素回路に対しても本発明を適用可能である。

【0068】

また、これまでの説明は、画像表示装置の1画素に対応する画素回路に関するものであったが、例えば、赤、緑、青の三原色画素が一つの絵素を構成する多色表示あるいは類似の多色表示にかかる画像表示装置に適用しても良い。この場合、駆動トランジスタTdのゲート・ソース間に接続される各容量値と、追加容量Caddとの容量比は各色ごとに異なるのが一般的である。このため、各色に最適な容量比を設定することにより、駆動トランジスタの特性変動の影響を抑制した発光輝度の補償を各色に実現することができる。

【0069】

また、本実施形態においては、発光素子として有機発光素子を用いたが、無機のLED等、他の発光素子であっても良い。

【符号の説明】

【0070】

10 電源線

11 Tth制御線

12 マージ線

13 走査線

14 画像信号線

15,16 Voled制御線

21 検出回路

23 電圧保持回路

25 フィードバック回路

A 制御回路

OLED 有機発光素子

Td 駆動トランジスタ

Tth 閾値電圧検出用トランジスタ

Ts,Tm,Tk スイッチングトランジスタ

Cs 保持容量

Cadd 追加容量

【技術分野】

【0001】

本発明は、有機ELディスプレイ装置等の画像表示装置およびその駆動方法に関するものである。

【背景技術】

【0002】

従来から、発光層に注入された正孔と電子とが再結合することによって光を生じる機能を有する有機EL(Electroluminescence)素子を用いた画像表示装置が提案されている。

【0003】

この種の画像表示装置では、例えばアモルファスシリコンや多結晶シリコン等で形成された薄膜トランジスタ(Thin Film Transistor:以下「TFT」という)や有機EL素子の一つである有機発光ダイオード(Organic Light Emitting Diode:以下「OLED」という)などが各画素を構成しており、各画素に適切な電流値が設定されることにより、各画素の輝度が制御される。

【0004】

例えば、OLEDなどの電流駆動型発光素子と、OLEDに流れる電流を制御する、例えばTFTなどの駆動トランジスタとが直列に配置された複数の画素を有するアクティブ・マトリクス型の画像表示装置では、各画素に設けられた駆動トランジスタの閾値電圧のばらつきにより、発光素子に流れる電流値が変化して輝度むらが発生する。この現象を改善するための手法として、例えば駆動トランジスタの閾値電圧を予め検出するとともに、検出した閾値電圧に基づいて発光素子に流れる電流を制御する方式(例えば非特許文献1)や、当該方式に基づく具体的な回路構成(例えば非特許文献2)などが開示されている。

【0005】

また、駆動トランジスタの閾値電圧のばらつきに加え、OLEDにも経時的な変化があり、自身への印加電圧に応じて自身の電流密度や輝度が変化(低下)するといった現象が知られている。この現象に対処するための手法として、光導電素子を用いることなく、単純な回路構成にて経時変化に伴う輝度の変化を補うことが可能な表示装置およびその駆動方法を開示した文献が存在する(例えば特許文献1)。この特許文献1では、発光素子への印加電圧や発光素子に流れる電流を検出するとともに、検出した検出電圧または検出電流に基づいて発光素子の輝度を補正するようにしている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2003−330418号公報

【非特許文献】

【0007】

【非特許文献1】R.M.A. Dawson,et al.(1998).Design of an Improved Pixel for a Polysilicon Active−Matrix Organic LED Display. SID98 Digest,pp.11−14.

【非特許文献2】S.Ono,et al.(2003).Pixel Circuit for a−Si AM−OLED.Proceedings of IDW’03,pp.255−258.

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、上記特許文献1に示された手法では、OLEDなどの発光素子を含む回路の電流または電圧の検出処理や、発光素子の輝度変化の補正処理を画素内で行っていないので、外部回路が複雑かつ大型化するといった問題点があった。

【0009】

本発明は、上記に鑑みてなされたものであって、外部回路を簡素に維持しつつ発光素子の経時的変化による発光輝度の変化を補償する画像表示装置およびその駆動方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明にかかる画像表示装置は、複数の画素を備え、各前記画素は、通電により発光する発光素子と、前記発光素子に電気的に接続され、前記発光素子の発光を制御するドライバ素子と、前記発光素子及び前記ドライバ素子に対して電気的に接続され、少なくとも前記発光素子の発光中に前記発光素子に印加される電圧を直接的または間接的に検出し、該検出結果を前記ドライバ素子に反映させる制御回路と、を備えている。

【0011】

また本発明に係る画像表示装置の駆動方法において、発光素子と、前記発光素子の発光を制御するドライバ素子と、を備えた画像表示装置を準備するステップと、少なくとも前記発光素子の発光中に、前記発光素子に印加される電圧を直接的または間接的に検出するステップと、少なくとも前記発光素子の発光中に、前記検出された電圧に対応する電圧を前記ドライバ素子に印加するステップと、を備えている。

【発明の効果】

【0012】

本発明によれば、各画素内の回路で発光素子の経時変化による輝度の変化を抑制できるため、発光素子の輝度補償を行っても、外部回路を簡素に維持することができる。

【図面の簡単な説明】

【0013】

【図1】本発明にかかる画像表示装置の一実施形態を説明するための図であり、画像表示装置の1画素に対応する画素回路の構成例を示す図である。

【図2】図1に示した画素回路上にトランジスタの寄生容量および有機発光素子容量を示した回路構成を示す図である。

【図3】図2に示した画素回路の一般的な動作を説明するためのシーケンス図である。

【図4】図3に示した準備期間の動作を説明する図である。

【図5】図3に示した閾値電圧検出期間の動作を説明する図である。

【図6】図3に示した書き込み期間の動作を説明する図である。

【図7】図3に示した発光期間の動作を説明する図である。

【図8】有機発光素子OLEDへの印加電圧と有機発光素子OLEDに流れる電流の電流密度との関係の一例を示す図である。

【図9】有機発光素子OLEDに流れる電流の電流密度と有機発光素子OLEDの発光輝度との関係の一例を示す図である。

【図10】有機発光素子OLEDを制御する駆動トランジスタTdのゲートに印加する電圧(画像信号電位)と有機発光素子OLEDの発光輝度との関係の一例を示す図である。

【図11】図8〜図10と同様な試験を行った際の、501時間経過後のΔVoledとΔVgsとの関係を示す図である。

【図12】図11の特性図上(破線P3)にそれぞれ48.5時間経過後(実線P1)および165.5時間経過後(破線P2)の特性曲線を重ね合わせた図である。

【図13】本実施の形態にかかる補償手法に基づいて補償した補償後の特性(駆動トランジスタTdのゲートに印加する画像信号電位と有機発光素子OLEDの発光輝度特性)を示す図である。

【図14】本実施の形態にかかる補償手法を図1に示した画素回路に適用する場合の一構成例を示す図である。

【図15】図14に示した画素回路の動作を説明するためのシーケンス図である。

【図16】図14に示した画素回路の動作を説明するための他のシーケンス図である。

【図17】本発明にかかる画像表示装置の他の実施形態を説明するための図であり、画像表示装置の1画素に対応する画素回路の構成例を示す図である。

【図18】本発明にかかる画像表示装置の他の実施形態を説明するための図であり、画像表示装置の1画素に対応する画素回路の構成例を示す図である。

【発明を実施するための形態】

【0014】

以下に、本発明の画像表示装置およびその駆動方法にかかる実施の形態を図面に基づいて詳細に説明する。なお、この実施の形態により本発明が限定されるものではない。

【0015】

図1は、本発明にかかる画像表示装置の一実施形態を説明するための図であり、画像表示装置の1画素に対応する画素回路の構成例を示す図である。同図に示す画素回路は、発光素子の一つである有機発光素子OLED、有機発光素子OLEDを駆動するためのドライバ素子である駆動トランジスタTd、閾値電圧検出用トランジスタTth、保持容量Csと、スイッチングトランジスタTsと,スイッチングトランジスタTmと、を備えるように構成されている。なお、図1に示す構成は、有機発光素子などを制御する画素回路の一般的構成であり、本発明の特徴を示すものではない。また、この画像表示装置は複数の画素をマトリックス状に配列した構成を有している。

【0016】

図1において、駆動トランジスタTdは、第1の端子であるゲートと第2の端子であるソースとの間に与えられる電位差に応じて有機発光素子OLEDに流れる電流量を制御するための制御素子(駆動素子)である。

【0017】

閾値電圧検出用トランジスタTthは、オン状態となったときに、駆動トランジスタTdのゲートとドレインとを電気的に接続する。その結果、駆動トランジスタTdのゲート・ソース間の電位差が実質的に駆動トランジスタTdの閾値電圧Vthとなるまで、駆動トランジスタTdのゲートからドレインに向かって電流が流れ、駆動トランジスタTdの閾値電圧Vthが検出される。

【0018】

有機発光素子OLEDは、有機発光素子OLEDの閾値電圧以上の電位差がアノード−カソード間に印加されることにより、電流が流れて発光する特性を有する素子である。具体的には、有機発光素子OLEDは、例えば、Al、CuまたはITO(Indium Tin Oxide)等によって形成されたアノード層およびカソード層と、アノード層とカソード層との間に介在され、フタルシアニン、トリスアルミニウム錯体、ベンゾキノリノラト、ベリリウム錯体等の有機系の材料によって形成された発光層と、を少なくとも備えた構造を有している。そして、有機発光素子OLEDは、発光層に注入された正孔と電子とが再結合することによって光を生じる機能を有する。

【0019】

駆動トランジスタTd、閾値電圧検出用トランジスタTth、スイッチングトランジスタTsおよびスイッチングトランジスタTmは、例えば、薄膜トランジスタとして構成される。なお、以下で参照される各図面においては、各薄膜トランジスタについてのチャネル(n型またはp型)については、特に明示していないが、n型またはp型のいずれを用いてもよい。本実施形態においては、各薄膜トランジスタとして、n型の薄膜トランジスタを用いている。また各薄膜トランジスタは、非晶質シリコン、微結晶シリコン、及びポリシリコンのいずれを用いても良い。

【0020】

電源線10は、駆動トランジスタTdおよびスイッチングトランジスタTmに複数の所定電圧を供給する。Tth制御線11は、閾値電圧検出用トランジスタTthの駆動を制御するための信号を閾値電圧検出用トランジスタTthに供給する。マージ線12は、スイッチングトランジスタTmの駆動を制御するための信号をスイッチングトランジスタTmに供給する。走査線13は、スイッチングトランジスタTsの駆動を制御するための信号をスイッチングトランジスタTsに供給する。画像信号線14は、画像信号を保持容量Csに供給する。

【0021】

なお、図1では、有機発光素子OLEDのアノード側にグラウンド線を、カソード側に電源線10を配するようにしているが、アノード側に電源線10を、カソード側にグランド線を配するようにしても良い。また、有機発光素子OLEDのアノード側およびカソード側の双方に対して電源線を配置するようにしてもよい。

【0022】

ところで、トランジスタには、一般的にゲート・ソース間およびゲート・ドレイン間に寄生容量が存在する。本実施形態において駆動トランジスタTdのゲート電位に影響を与える寄生容量は、駆動トランジスタTdのゲート・ソース間容量CgsTd、駆動トランジスタTdのゲート・ドレイン間容量CgdTd、および閾値電圧検出用トランジスタTthのゲート・ソース間容量CgsTth、閾値電圧検出用トランジスタTthのゲート・ドレイン間容量CgdTthである。なお、これらの寄生容量と、有機発光素子OLEDが固有に有している有機発光素子容量Coledを加えたものを図2に示す。

【0023】

つぎに、本実施の形態の動作について、図3〜図7を参照して説明する。ここで、図3は、図2に示した画素回路の一般的な動作を説明するためのシーケンス図であり、図4〜図7は、4つの期間に区分された準備期間(図4)、閾値電圧検出期間(図5)、書き込み期間(図6)および発光期間(図7)の各区間の動作を説明するための図である。なお、以下に説明する動作は、制御部(図示略)の制御下で行われる。

【0024】

(準備期間)

準備期間の動作については、図3および図4を参照して説明する。準備期間では、電源線10が高電位(Vp)、マージ線12が高電位(VgH)、Tth制御線11が低電位(VgL)、走査線13が低電位(VgL)、画像信号線14がゼロ電位とされる。これにより、図4に示すように、閾値電圧検出用トランジスタTthがオフ、スイッチングトランジスタTsがオフ、駆動トランジスタTdがオン、スイッチングトランジスタTmがオンとされ、電源線10→駆動トランジスタTd→有機発光素子容量Coledという経路で電流が流れ、有機発光素子容量Coledに電荷が蓄積される。なお、この準備期間で有機発光素子容量Coledに電荷を蓄積する理由は、後述する閾値電圧検出期間に駆動トランジスタTdのドレイン・ソース間電流(以下「Ids」と表記)が実質的に流れなくなる状態における駆動トランジスタTdのゲート・ソース間電圧(すなわち駆動トランジスタTdの閾値電圧)を検出する際に、有機発光素子容量Coledを駆動トランジスタTdのドレイン・ソース間に流す電流の供給源として作用させるためである。

【0025】

(閾値電圧検出期間)

つぎに、閾値電圧検出期間の動作について図3および図5を参照して説明する。閾値電圧検出期間では、電源線10がゼロ電位、マージ線12が高電位(VgH)、Tth制御線11が高電位(VgH)、走査線13が低電位(VgL)、画像信号線14がゼロ電位とされる。これにより、図5に示すように、閾値電圧検出用トランジスタTthがオンとなり、駆動トランジスタTdのゲートとドレインとが接続される。

【0026】

また、保持容量Csおよび有機発光素子容量Coledに蓄積された電荷が放電され、駆動トランジスタTd→電源線10という経路で電流が流れる。そして、駆動トランジスタTdのゲート−ソース間の電位差が閾値電圧Vthに実質的に達すると、駆動トランジスタTdが実質的にオフとされ、駆動トランジスタTdの閾値電圧Vthが検出される。

【0027】

(書き込み期間)

さらに、書き込み期間の動作について図3および図6を参照して説明する。書き込み期間では、データ電位(−Vdata)を保持容量Csに供給することにより、駆動トランジスタTdのゲート電位を、データ電位に応じた所望の電位に変化させることが行われる。具体的には、電源線10がゼロ電位、マージ線12が低電位(VgL)、Tth制御線11が高電位(VgH)、走査線13が高電位(VgH)、画像信号線14がデータ電位(−Vdata)とされる。

【0028】

これにより、図6に示したように、スイッチングトランジスタTsがオン、スイッチングトランジスタTmがオフとなり、有機発光素子容量Coledに蓄積された電荷が放電され、有機発光素子容量Coled→閾値電圧検出用トランジスタTth→保持容量Csという経路で電流が流れ、保持容量Csに電荷が蓄積される。すなわち、有機発光素子容量Coledに蓄積された電荷は、保持容量Csに移動する。その結果、駆動トランジスタTdのゲート電位がデータ電位に対応した電位となる。

【0029】

ここで、駆動トランジスタTdの閾値電圧をVth、保持容量Csの容量値をCs、閾値電圧検出用トランジスタTthがオンの場合の全容量(すなわち駆動トランジスタTdのゲートに接続された静電容量および寄生容量)をCallとすると、駆動トランジスタTdのゲート電位Vgは、次式で表される(なお、上記仮定は、以下の式についても及ぶものとする)。

【0030】

Vg=Vth−(Cs/Call)・Vdata ・・・(1)

また、保持容量Csの両端の電位差VCsは、次式で表される。

【0031】

VCs=Vg−(−Vdata)=Vth+[(Call−Cs)/Call]・Vdata ・・・(2)

上記(2)式に示される全容量Callは、閾値電圧検出用トランジスタTthの導通時の全容量であり、次式で表される。

【0032】

Call=Coled+Cs+CgsTth+CgdTth+CgsTd ・・・(3)

なお、上記(3)式に駆動トランジスタTdのゲート・ドレイン間容量CgdTdが含まれていないのは、駆動トランジスタTdのゲート・ドレイン間が閾値電圧検出用トランジスタTthによって接続され、駆動トランジスタTd両端が略同電位となっているからである。また、保持容量Csと有機発光素子容量Coledとは、Cs<Coledの関係を満足している。

【0033】

(発光期間)

最後に、発光期間の動作について図3および図7を参照して説明する。発光期間では、電源線10がマイナス電位(−VDD)、マージ線12が高電位(VgH)、Tth制御線11が低電位(VgL)、走査線13が低電位(VgL)、画像信号線14がゼロ電位とされる。

【0034】

これにより、図7に示したように、駆動トランジスタTdがオン、閾値電圧検出用トランジスタTthがオフ、スイッチングトランジスタTsがオフとなり、有機発光素子OLED→駆動トランジスタTd→電源線10という経路で電流が流れ、有機発光素子OLEDが発光する。

【0035】

このとき、駆動トランジスタTdのドレインからソースに流れる電流(すなわちIds)は、駆動トランジスタTdの構造および材質から決定される定数β、駆動トランジスタTdのゲート・ソース間の電位差Vgs、駆動トランジスタTdの閾値電圧Vthを用いて次式で表される。

【0036】

Ids=(β/2)・(Vgs−Vth)2 ・・・(4)

つぎに、駆動トランジスタTdのゲート・ソース間の電位差Vgsと電流Idsとの関係を考察するため、画素回路の寄生容量を考慮しない場合の電位差Vgsを算出する。

【0037】

図7において、発光時には駆動トランジスタTdが導通しており、駆動トランジスタTdのソース電位とドレイン電位が略同電位に保持される。また、図7において、駆動トランジスタTdのゲート電位は、書き込み電位(−Vdata)が保持容量Csと有機発光素子容量Coledとの間で分圧された状態となるので、電位差Vgsは、次式で表せる。

【0038】

Vgs=Vth+Coled/(Cs+Coled)・Vdata ・・・(5)

したがって、駆動トランジスタTdのゲート・ソース間の電位差Vgsと電流Idsとの関係式は、上記(4)式、(5)式を用いて次式のようになる。

【0039】

Ids=(β/2)・(Coled/(Cs+Coled)・Vdata)2

=a・Vdata2 ・・・(6)

(6)式に示されるように、駆動トランジスタTdの閾値電圧Vthを検出することにより、理論的には、閾値電圧Vthに依存しない電流Idsを得ることができる。

【0040】

上述した画素回路は、駆動トランジスタTdの経時的な変化や、駆動トランジスタTdを含む各トランジスタが有する寄生容量の影響を補償する。ところが、駆動トランジスタTdだけでなく、有機発光素子OLEDにも経時的な変化があり、有機発光素子OLEDへの印加電圧に対する有機発光素子OLEDに流れる電流の電流密度特性や、有機発光素子OLEDに流れる電流の電流密度に対する有機発光素子OLEDの発光輝度特性が、有機発光素子OLEDの使用時間に応じて低下することになる。

【0041】

例えば、図8は、有機発光素子OLEDへの印加電圧と有機発光素子OLEDに流れる電流の電流密度との関係の一例を示す図である。なお、同図に示すグラフは、有機発光素子OLEDを連続的に点灯させる常時点灯試験を行った結果を示すものであり、初期(OLED使用時間0時間:実線K1)、OLED使用時間48.5時間経過後(破線K2)、OLED使用時間165.5時間経過後(破線K3)およびOLED使用時間501時間経過後(破線K4)の各特性を示している。なお、同図に示す特性には、上記特許文献1の図2、図7などに示された発光素子の特性とは異なり、駆動トランジスタTdを含む各トランジスタの劣化成分は含まれていない。

【0042】

図8の特性から明らかなように、有機発光素子OLEDの使用時間が長くなるに従って、同一電圧を印加しても、得られる電流密度が小さくなることが分かる。また、同一の発光輝度を得るためには、使用時間の経過に応じて有機発光素子OLEDへの印加電圧を増加させる必要があることも分かる。

【0043】

また、図9は、有機発光素子OLEDに流れる電流の電流密度と有機発光素子OLEDの発光輝度との関係の一例を示す図である。なお、同図に示すグラフは、図8と同様な常時点灯試験を行った試験結果であり、初期(OLED使用時間0時間:実線L1)、OLED使用時間48.5時間経過後(破線L2)、OLED使用時間165.5時間経過後(破線L3)およびOLED使用時間501時間経過後(破線L4)の各特性を示している。なお、同図に示す特性にも、図8と同様に、駆動トランジスタTdを含む各トランジスタの劣化成分は含まれていない。図9から理解されるように、有機発光素子OLEDの使用時間が長くなるに従って有機発光素子OLEDに同一電流を流した場合に得られる発光輝度が小さくなっていることが分かる。また、同一の発光輝度を得るためには、使用時間の経過に応じて有機発光素子OLEDに流す電流を増加させる必要があることも分かる。

【0044】

一方、図10は、有機発光素子OLEDを制御する駆動トランジスタTdのゲートに印加する電圧(画像信号電位)と有機発光素子OLEDの発光輝度との関係の一例を示す図であり、図8および図9と同様な常時点灯試験を行なった試験結果であり、初期(OLED使用時間0時間:実線M1)、OLED使用時間48.5時間経過後(破線M2)、OLED使用時間165.5時間経過後(破線M3)およびOLED使用時間501時間経過後(破線M4)の各特性が示されている。例えば、上述した画素回路の例では、直接的に制御される対象は、有機発光素子OLEDを駆動し、画像信号電位が書き込まれる駆動トランジスタTdのゲートの電位であるので、図10に示すような変動特性を明らかにする必要がある。

【0045】

なお、図10に示す特性においても、図8および図9と同様な特性が表れている。すなわち、閾値電圧Vthを考慮して書き込んだ画像信号電位Vdataを駆動トランジスタTdのゲートに印加したとしても、有機発光素子OLEDの使用時間が大きくなるに従って得られる発光輝度が低下することが分かる。また、同一の発光輝度を得るためには、使用時間の経過に応じて駆動トランジスタTdへの印加電圧を増加させる必要があることも分かる。

【0046】

ところで、上記特許文献1に示された手法は、検出電圧や検出電流を検出したフレーム(以下「検出フレーム」という)内において反映させているのではなく、最短でも検出したフレームよりも1フレーム後のフレームにしか反映させることができない。したがって、従来手法では、例えばフレームの前後で輝度が大きく変化する場合には、適切な補正を行なうことができない。なお、ここでいう「フレーム」とは、画像表示装置のディスプレイに表示される画像を書き換える周期を意味するものであり、例えば、60Hzの周期で駆動されるディスプレイであれば、1フレーム周期が16.67msとなる。

【0047】

一方、後述する本実施形態にかかる手法では、有機発光素子OLEDへの印加電圧の変化を画素回路の内部、すなわち個々の画素回路自身が有機発光素子OLEDに印加される電圧を検出し、検出した電圧に対応する電圧を同一フレーム内で駆動トランジスタTdに反映する。以下、その原理について説明する。

【0048】

発光時における有機発光素子OLEDへの印加電圧Voledの初期値と、有機発光素子OLEDを一定時間使用した後における有機発光素子OLEDへの印加電圧との差分値を「ΔVoled」とする。また、一定時間使用後における有機発光素子OLEDの発光輝度を初期値にまで上げるのに必要なVgsの値(差分値)を「ΔVgs」とする。図11は、上記と同様な常時点灯試験を行った際の、501時間経過後のΔVoledとΔVgsとの関係を示す図である。同図によれば、画像信号電位Vdataに依存してΔVoledおよびΔVgsの両者ともに変化することが分かる。

【0049】

図12は、図11の特性図上(破線P3)にそれぞれ48.5時間使用後(実線P1)および165.5時間使用後(破線P2)の特性曲線を重ね合わせた図である。なお、図12では、所定の傾き(同図の例では、傾き0.43)を有する直線が併せて示されており、本願発明者らは、ΔVoledに対するΔVgsの特性曲線の全体が有機発光素子OLEDの使用時間をパラメータとして、所定の傾きを有する直線に沿って並ぶということを見出している。

【0050】

したがって、発光時における有機発光素子OLEDへの印加電圧の変化ΔVoledに略比例した電圧(図12の例では、比例定数0.43)を駆動トランジスタTdのゲート・ソース間の電位差Vgsに加算するようにすれば、輝度劣化を全階調でほぼ補償することができる。

【0051】

図13は、上述の手法に基づいて補償した補償後の特性を示す図である。補償前の特性を示す図10と比較すれば明らかなように、使用時間に依存する輝度変化を低減することができる。

【0052】

つぎに、上述の電圧加算の実現手法について説明する。なお、実際の制御に際しては、制御の容易性を確保する観点から、ΔVoledに代えてVoledの加算で代用することを考える。なお、無論、ΔVoledに基づく電圧加算を行うことも可能である。

【0053】

いま、有機発光素子OLEDへの印加電圧の初期値をVoled0とし、駆動トランジスタTdのゲート・ソース間に印加する補正後の印加電圧をVgs’とすれば、このVgs’は、上記特性曲線上に示した直線の傾きに相当する比例定数bを用いて次式のように表すことができる。

【0054】

Vgs’=Vgs+ΔVgs

=Vgs+b・ΔVoled

=Vgs+b・(Voled−Voled0) ・・・(7)

また、上記(5)式において、d=Coled/(Cs+Coled)とし、上記(7)式に(5)式を代入することで、補正後の印加電圧をVgs’は、次式で表すことができる。

【0055】

Vgs’=Vth+d・Vdata+b・(Voled−Voled0)

=Vgs+(d・Vdata−b・Voled0)+b・Voled ・・・(8)

上記(8)式において、第2項のb・Voled0は、有機発光素子OLEDの経時変化に依存することなくVdataによって決まる項であり、有機発光素子OLEDの経時変化に依存する項は、第3項のVoledである。したがって、有機発光素子OLEDの経時変化に依存しないb・Voled0を予め考慮することで、上記(8)式に基づいて有機発光素子OLEDの輝度変化を補償することができる。なお、このb・Voled0は有機発光素子OLEDの特性によって決まる定数値なので、例えば図1に示した画素回路であれば、保持容量Csに画像信号電位(−Vdata)を書き込む際に、b・Voled0に対応する所定値を減算した電圧を書き込むようにすれば、有機発光素子OLEDの初期特性を記憶しておく必要はない。また、b・Voled0以外の定数値が加わった場合であっても同様であり、それらの値を記憶する必要はない。

【0056】

図14は、上述の実現手法を図1に示した画素回路に適用する場合の一構成例を示す図である。同図に示す画素回路は、図1に示す構成から、有機発光素子OLEDの両端の電圧を検出する検出手段としての検出回路21と、検出回路21にて検出された電圧を保持する電圧保持手段としての電圧保持回路23と、電圧保持回路23に保持された電圧を駆動トランジスタTdのゲート・ソース間に印加するフィードバック手段としてのフィードバック回路25と、を有する制御回路Aを備えるように構成されている。この制御回路Aは各画素に配設されている。なお、図14では、制御回路Aを構成するトランジスタに存在する寄生容量の表示は省略している。

【0057】

図14において、電圧保持回路23は、電圧を保持可能な追加容量Caddを具備する。また、検出回路21は、例えば電圧保持回路23を介して接続された一対のトランジスタを具備し、それぞれのゲートが第1の制御線であるVoled制御線15に共通的に接続されるような構成を採用することができる。なお、検出回路21の一端(例えば一方のトランジスタのドレインまたはソース)は、有機発光素子OLEDのカソードに接続し、検出回路21の他端(例えば他方のトランジスタのドレインまたはソース)は、有機発光素子OLEDのアノードに接続すればよい。

【0058】

フィードバック回路25は、検出回路21と同様な構成を採ることができる。例えば、電圧保持回路23を介して接続された一対のトランジスタを具備し、それぞれのゲートが第2の制御線であるVoled制御線16に共通的に接続されるような構成を採用することができる。なお、フィードバック回路25の一端(例えば一方のトランジスタのドレインまたはソース)は、駆動トランジスタTdの第1の端子(ゲート)に接続し、フィードバック回路25の他端(例えば他方のトランジスタのドレインまたはソース)は、駆動トランジスタTdの第2の端子(ソースまたはドレイン)に接続すればよい。

【0059】

つぎに、図14に示した画素の動作について、図14および図15を参照して説明する。ここで、図15は、図14に示した画素回路の動作を説明するためのシーケンス図である。

【0060】

図15において、まず、準備期間、Vth検出期間および書き込み期間の動作については、図3に示したシーケンスと同一であり、その説明を省略する。つづいて、発光期間では、Voled制御線15を高電位(VgH)にし、検出回路21を構成する一対のトランジスタを導通させる。一方、Voled制御線16を低電位(VgL)にし、フィードバック回路25を構成する一対のトランジスタを非導通にする。この後、有機発光素子OLEDを発光させると、追加容量Caddに有機発光素子OLEDの両端電圧Voledに基づく電荷が蓄積され、Voledに相当する電圧が電圧保持回路23によって保持される。つづいて、Voled制御線15を低電位(VgL)にし、Voled制御線16を高電位(VgH)にすると、保持容量Csに書き込まれた画像信号電位に追加容量Caddに保持されたVoledが加算されるので、上記(8)式に基づく制御手法を実現することができる。なお、(8)式における比例定数bは、駆動トランジスタTdのゲート・ソース間に電気的に接続される各容量値(駆動トランジスタTdの寄生容量等)と、追加容量Caddとの容量比によって決定されるので、追加容量Caddの容量値を適切に定めることで所望の比例定数を選択することができる。例えば、本実施形態の場合、図12より、比例定数b=0.43である。

【0061】

このように、本実施の形態にかかる画像表示装置では、有機発光素子OLEDへの印加電圧の変化を個々の画素回路自身が検出し、検出した電圧に対応する電圧をドライバ素子へ印加して検出した結果を反映させることができる。それ故、外部回路の構成を簡素に維持することができる。また、駆動トランジスタの特性変動の影響を抑制した有機発光素子OLEDの輝度変化の補償を実現することができる。また、有機発光素子OLEDへの印加電圧を検出する工程と、検出した有機発光素子OLEDへの印加電圧に対応する電圧を駆動トランジスタTdへ印加する工程とを同一フレーム内で行うことにより、有機発光素子OLEDの発光輝度をより適切に補償を行うことができる。またこれら一連の工程は毎フレーム行うことが好ましい。

【0062】

なお、図1などの回路構成から明らかなように、有機発光素子OLEDの両端電圧Voledと駆動トランジスタTdのドレイン・ソース間電圧Vdsとの和は略一定なので、Voledの電圧変化を、これと等価な駆動トランジスタTdのVdsの電圧変化として検出し、検出した電圧に基づいて駆動トランジスタTdを制御するようにしてもよい。この場合には、検出回路21の一端および他端をそれぞれ駆動トランジスタTdのドレイン、ソースに接続すればよい。例えば、図18に示すように、検出回路21を駆動トランジスタTdのドレイン・ソースに接続し、フィードバック回路25を駆動トランジスタTdのゲートと、有機発光素子OLEDのアノードに接続するようにしても良い。図18の画素回路は、図15,16と同様のシーケンスにより駆動することができる。なお、フィードバック回路25を駆動トランジスタTdのゲートと、有機発光素子OLEDのカソード(または駆動トランジスタTdのドレイン)に接続するようにしても良い。しかしながら、図18に示すように、フィードバック回路25の一端を有機発光素子OLEDのアノードに接続し、有機発光素子OLEDを介してフィードバック回路25を駆動トランジスタTdのゲートとドレインに接続する方が有機発光素子OLEDの輝度をダイレクトに調整することができ、輝度補償が容易であるというメリットがある。

【0063】

また、図16は、図15とは異なる他のシーケンス図である。同図に示すシーケンスでは、準備期間中にVoled制御線15を高電位(VgH)とする一方で、Voled制御線16を低電位(VgL)に設定している。なお、準備期間中にVoled制御線15を高電位に設定している場合であっても、Voled制御線16を低電位(VgL)に設定している限りにおいて、追加容量Caddに保持された電圧が駆動トランジスタTdのゲート・ソース間に印加されることはないので問題はない。特に、図15のシーケンスにおいて、発光時間を充分に確保したい場合には、有機発光素子OLEDの両端電圧の検出時間を短くする必要があり、その場合には追加容量Caddへの電荷の蓄積が充分になされないことが考えられる。一方、図16のシーケンスでは、有機発光素子OLEDの両端電圧の検出時間を充分に確保することができる。なお、図16において、Voled制御線15を低電位(VgL)から高電位(VgH)にするタイミングと、Voled制御線16を高電位(VgH)から低電位(VgL)にするタイミングを準備期間中に行うようにしているが、これらのタイミングはVth検出期間あるいは書き込み期間であっても構わない。

【0064】

また、本実施形態において、検出回路21及びフィードバック回路25を構成する薄膜トランジスタのチャネル幅W21、W25は、駆動トランジスタTdのチャネル幅WTdよりも小さくなるように設定されることが好ましい。この場合、制御回路Aの配設に必要なスペースを小さくすることができる。なお、検出回路21やフィードバック回路25に流れる電流は、駆動トランジスタTdに流れる電流よりも小さいため、駆動トランジスタTdよりも検出回路21及びフィードバック回路25のチャネル幅を小さくしても特に問題はない。また、制御回路Aのスペースを小さくするという観点から、検出回路21及びフィードバック回路25を構成する薄膜トランジスタのチャネル幅W21及びW25は、閾値電圧検出用トランジスタTthやスイッチングトランジスタTs,Tm,Tkのチャネル幅WTs、WTm及びWTkよりも小さくすることが好ましい。

【0065】

さらに、電圧保持回路23を構成する追加容量Caddの容量値を駆動トランジスタTdに接続される保持容量Csの容量値よりも小さくすることが好ましい。その理由は、大きいと書込み効率(画像信号線の変化量に対する(Vgs−Vth)の変化量)が低下するからである。

【0066】

また、制御回路Aを構成するトランジスタと、駆動トランジスタTd及びスイッチングトランジスタTs,Tm,Tk等のトランジスタとは、互いに異なる層に形成することが可能である。その結果、1画素の面積を拡大することなく、制御回路Aを配置することができる。

【0067】

また、上述の実施形態においては、駆動トランジスタTdの閾値電圧Vthを検出するための閾値電圧検出用トランジスタTthを有する画素回路に対して本発明を適用したが、閾値電圧検出用トランジスタTthを有さない、図17のような画素回路に対しても本発明を適用可能である。

【0068】

また、これまでの説明は、画像表示装置の1画素に対応する画素回路に関するものであったが、例えば、赤、緑、青の三原色画素が一つの絵素を構成する多色表示あるいは類似の多色表示にかかる画像表示装置に適用しても良い。この場合、駆動トランジスタTdのゲート・ソース間に接続される各容量値と、追加容量Caddとの容量比は各色ごとに異なるのが一般的である。このため、各色に最適な容量比を設定することにより、駆動トランジスタの特性変動の影響を抑制した発光輝度の補償を各色に実現することができる。

【0069】

また、本実施形態においては、発光素子として有機発光素子を用いたが、無機のLED等、他の発光素子であっても良い。

【符号の説明】

【0070】

10 電源線

11 Tth制御線

12 マージ線

13 走査線

14 画像信号線

15,16 Voled制御線

21 検出回路

23 電圧保持回路

25 フィードバック回路

A 制御回路

OLED 有機発光素子

Td 駆動トランジスタ

Tth 閾値電圧検出用トランジスタ

Ts,Tm,Tk スイッチングトランジスタ

Cs 保持容量

Cadd 追加容量

【特許請求の範囲】

【請求項1】

画像表示装置において、

複数の画素を備え、

各前記画素は、

通電により発光する発光素子と、

前記発光素子に電気的に接続され、前記発光素子の発光を制御するドライバ素子と、

前記発光素子及び前記ドライバ素子に対して電気的に接続され、少なくとも前記発光素子の発光中に前記発光素子に印加される電圧を直接的または間接的に検出し、該検出結果を前記ドライバ素子に反映させる制御回路と、

を備えた画像表示装置。

【請求項1】

画像表示装置において、

複数の画素を備え、

各前記画素は、

通電により発光する発光素子と、

前記発光素子に電気的に接続され、前記発光素子の発光を制御するドライバ素子と、

前記発光素子及び前記ドライバ素子に対して電気的に接続され、少なくとも前記発光素子の発光中に前記発光素子に印加される電圧を直接的または間接的に検出し、該検出結果を前記ドライバ素子に反映させる制御回路と、

を備えた画像表示装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2012−215896(P2012−215896A)

【公開日】平成24年11月8日(2012.11.8)

【国際特許分類】

【出願番号】特願2012−136232(P2012−136232)

【出願日】平成24年6月15日(2012.6.15)

【分割の表示】特願2007−546425(P2007−546425)の分割

【原出願日】平成18年11月17日(2006.11.17)

【出願人】(511254491)エルジー ディスプレイ カンパニー リミテッド (2)

【Fターム(参考)】

【公開日】平成24年11月8日(2012.11.8)

【国際特許分類】

【出願日】平成24年6月15日(2012.6.15)

【分割の表示】特願2007−546425(P2007−546425)の分割

【原出願日】平成18年11月17日(2006.11.17)

【出願人】(511254491)エルジー ディスプレイ カンパニー リミテッド (2)

【Fターム(参考)】

[ Back to top ]