画像表示装置及びその制御方法

【課題】簡易な構成で、階調性を低減させることなく列配線の配線抵抗に起因する輝度ムラを抑制することのできる技術を提供する。

【解決手段】本発明の画像表示装置は、複数の行配線と、複数の列配線と、前記行配線と前記列配線の各交点に配置された複数の画素と、を有する表示パネルと、前記行配線を順次選択して、選択された行配線に走査信号を出力する行配線駆動回路と、前記行配線駆動回路によって選択される行配線が変更されるのに同期して、画像データに基づき生成した各列の変調信号を前記複数の列配線に出力する列配線駆動回路と、前記列配線駆動回路と前記列配線との間の抵抗値を変更する可変抵抗回路と、を有し、前記可変抵抗回路は、前記選択された行配線が前記列配線駆動回路に近いときのほうが前記抵抗値が大きくなるように、前記選択された行配線の位置に応じて前記抵抗値を変更することを特徴とする。

【解決手段】本発明の画像表示装置は、複数の行配線と、複数の列配線と、前記行配線と前記列配線の各交点に配置された複数の画素と、を有する表示パネルと、前記行配線を順次選択して、選択された行配線に走査信号を出力する行配線駆動回路と、前記行配線駆動回路によって選択される行配線が変更されるのに同期して、画像データに基づき生成した各列の変調信号を前記複数の列配線に出力する列配線駆動回路と、前記列配線駆動回路と前記列配線との間の抵抗値を変更する可変抵抗回路と、を有し、前記可変抵抗回路は、前記選択された行配線が前記列配線駆動回路に近いときのほうが前記抵抗値が大きくなるように、前記選択された行配線の位置に応じて前記抵抗値を変更することを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像表示装置及びその制御方法に関する。

【背景技術】

【0002】

フラットパネルディスプレイ(FPD)としては、液晶表示装置(LCD)、プラズマ表示装置(PDP)、有機EL表示装置(OLED)、フィールドエミッション表示装置(FED)などが知られている。

中でもFEDはパッシブマトリックス構造であり、行配線と列配線との交差点に電界放出素子が位置するシンプルなパネル構造になっているため、低コストでありながら、高速応答という特徴を持つ。

【0003】

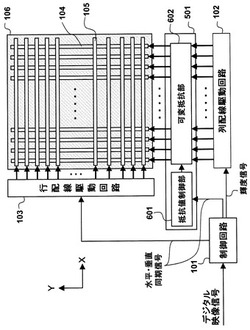

図1は、一般的なマトリクス駆動方式の画像表示装置(例えばFED)の基本的な構成例である。背面基板106上には、複数の列配線104と複数の行配線105が形成されており、列配線104と行配線105との各交点に画素(表示素子)が形成されている。列配線104が列配線駆動回路102に接続され、行配線105が行配線駆動回路103に接続されることにより、表示装置モジュールが構成されている。

【0004】

また図1の画像表示装置は、デジタル映像信号が入力される制御回路101を備えている。行配線駆動回路103は、駆動対象とする行配線105に走査信号(選択電圧)を印加し、他の行配線105に非選択電圧を印加する回路である。行配線105は、例えば1ラインずつ上から順次駆動(走査)される。列配線駆動回路102は、駆動行の映像信号(輝度信号)から各列の駆動波形(変調信号)を生成し、各列配線104に印加する。これにより表示素子の輝度(電子放出素子の電子放出量)が変調されて所望の映像を出力する事ができる。

【0005】

しかしながら、列配線104の配線抵抗および列配線104と行配線105の交差部に生じる静電容量により、変調信号の電圧降下およびRC時定数による波形なまりが発生する。そのため、図12に示すように、列配線駆動回路102の近く(駆動端側)に設けられた表示素子と、遠く(開放端側)に設けられた表示素子とでは、印加される変調信号の形状に差が出てくる。その結果、駆動端側に比べて開放端側が暗くなる、つまり列方向に輝度ムラ(表示不良)が発生する。

【0006】

また、画像表示装置の大サイズ化や高精細化が進むと、列配線104が長く、細くなる。これにより、列配線104の抵抗が増大するため、前述の輝度ムラもより増大する。

この課題を解決するための技術としては、表示素子の位置や階調に応じた補正値を用いて映像信号を補正する技術(特許文献1)や、RC時定数による電圧信号のなまりに応じて補正する技術(特許文献2)などが提案されている。これらの技術を用いると上述した表示不良は抑制(補正)することができる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】米国特許第6097356号明細書

【特許文献2】特開平6−258614号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかし、特許文献1や特許文献2に記載の技術では、表示素子の位置に依存する輝度む

らは軽減できるものの、階調性の低下あるいは回路規模の増大は免れられない。

【0009】

列配線駆動回路102の駆動端側、開放端側の表示素子に印加する変調信号の値を、階調値0(変調信号の最小値)から最大階調値(階調値Dmax;変調信号の最大値)まで変化させたときの、各々の輝度変化の例を図2(a),(b)に示す。図2(a),(b)に示すように、駆動端側の表示素子の最大輝度(近傍最大輝度)が輝度Laであったとすると、開放端側の表示素子の最大輝度(遠方最大輝度)は輝度Laよりも低い輝度Lbとなる。これは、開放端側では、駆動端側に比べ、列配線の抵抗分だけ変調信号の電圧降下による信号レベル低下とRC時定数による波形なまりがより大きく発生することにより、輝度が低下するからである。

【0010】

従来技術では、輝度ムラを抑制するために、最大輝度の高い表示素子の輝度が最大輝度の低い表示素子の輝度に合わせられる。具体的には、駆動端側の表示素子の最大輝度も輝度Lbとされ、駆動端側の表示素子に対しては階調値Da(階調値Dmaxより小さい階調値;近傍最大階調)までの変調信号しか使用されない。そのため、駆動端側の表示素子の階調性は低下し、開放端側の表示素子の最大階調値(遠方最大階調)よりも近傍最大階調値は小さくなる。

高い階調性を維持するためには、上述の階調性低下を見越した映像信号の高ビット化が必要となる。しかしながら、これは制御回路や駆動回路などの回路の規模の増大、映像信号のデータ量の増大を招く。

【0011】

本発明は、簡易な構成で、階調性を低減させることなく列配線の配線抵抗に起因する輝度ムラを抑制することのできる技術を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明の画像表示装置は、複数の行配線と、複数の列配線と、前記行配線と前記列配線の各交点に配置された複数の画素と、を有する表示パネルと、前記行配線を順次選択して、選択された行配線に走査信号を出力する行配線駆動回路と、前記行配線駆動回路によって選択される行配線が変更されるのに同期して、画像データに基づき生成した各列の変調信号を前記複数の列配線に出力する列配線駆動回路と、前記列配線駆動回路と前記列配線との間の抵抗値を変更する可変抵抗回路と、を有し、前記可変抵抗回路は、前記選択された行配線が前記列配線駆動回路に近いときのほうが前記抵抗値が大きくなるように、前記選択された行配線の位置に応じて前記抵抗値を変更することを特徴とする。

【0013】

本発明の画像表示装置の制御方法は、複数の行配線と、複数の列配線と、前記行配線と前記列配線の各交点に配置された複数の画素と、を有する表示パネルと、行配線駆動回路と、列配線駆動回路と、可変抵抗回路と、を有する画像表示装置の制御方法であって、前記行配線駆動回路が、前記行配線を順次選択して、選択された行配線に走査信号を出力するステップと、前記行配線駆動回路によって選択される行配線が変更されるのに同期して、列配線駆動回路が、画像データに基づき生成した各列の変調信号を前記複数の列配線に出力するステップと、前記可変抵抗回路が、前記選択された行配線が前記列配線駆動回路に近いときのほうが前記抵抗値が大きくなるように、前記選択された行配線の位置に応じて前記列配線駆動回路と前記列配線との間の抵抗値を変更するステップと、を有することを特徴とする。

【発明の効果】

【0014】

本発明によれば、簡易な構成で、階調性を低減させることなく列配線の配線抵抗に起因する輝度ムラを抑制することができる。

【図面の簡単な説明】

【0015】

【図1】一般的なFEDの基本的な全体構成の一例を示す図。

【図2】本発明の課題を説明する図。

【図3】電子放出特性の一例を示す図。

【図4】第1の実施形態に係る画像表示装置の全体構成の一例を示す図。

【図5】抵抗値制御部の構成の一例を示す図。

【図6】第1の実施形態に係る制御電圧発生回路の構成の一例を示す図。

【図7】可変抵抗部の構成の一例を示す図。

【図8】第2の実施形態に係る制御電圧発生回路の構成の一例を示す図。

【図9】第3の実施形態に係る制御電圧発生回路の構成の一例を示す図。

【図10】制御電圧の出力特性の一例を示す図。

【図11】スイッチ制御特性の一例を示す図。

【図12】従来の変調信号の波形の一例を示す図。

【図13】本実施形態に係る変調信号の波形の一例を示す図。

【発明を実施するための形態】

【0016】

以下、図面を参照して本発明の好適な実施の形態を説明する。本発明は、マトリクス駆動方式の表示パネルにおいて、列配線の配線抵抗に起因する輝度ムラ(列配線の配線抵抗による電圧降下やRC時定数による波形なまりによる輝度ムラ)を補正するための技術に関する。以下の実施形態では、画素(表示素子)として電界放出素子(電子放出素子)を用いた表示装置(FED)に本発明を適用した例について具体的に説明を行う。ただし、本発明の適用範囲はこれに限られず、マトリクス駆動方式の表示パネルをもつ画像表示装置であれば、FED以外の画像表示装置にも適用できる。

【0017】

(画像表示装置全体の構成)

図1は、一般的なFEDの基本的な全体構成の例である。背面基板106は、FEDパネル(表示パネル)のカソードパネルを構成するガラス基板である。背面基板106上には、複数の列配線104と複数の行配線105がマトリクス状に形成されている。列配線104と行配線105との各交点には、画素(表示素子)が形成されている。また図示は省略しているが、カソードパネルに対向するように、蛍光体及びアノード電極(メタルバック)を具備するアノードパネルが配置される。列配線104は、変調信号を出力する列配線駆動回路102に接続される。行配線105は、走査信号を出力する行配線駆動回路103に接続される。各駆動回路102、103は、水平同期信号、垂直同期信号、及び、輝度信号(画像データ)を出力する制御回路101に接続される。輝度信号は、例えばR、G、B各色のデジタル信号である。制御回路101は、入力された映像信号(デジタル映像信号)から輝度信号を生成し、列配線駆動回路102に供給する。また、水平同期信号及び垂直同期信号は、各駆動回路102、103に入力され、該信号に応じて走査信号及び変調信号を印加するタイミングが制御される。

以上により、FEDモジュールが構成されている。ここで、列配線が超伝導体で構成されていて配線抵抗を有していない場合、電圧降下やRC時定数による波形なまりが発生しないため、本発明を適用しても効果を得ることができない。しかし、Al、Cu、Agなどの配線抵抗を有する一般的な配線材であれば、列配線の配線抵抗に起因した輝度ムラ(列配線の配線抵抗による電圧降下やRC時定数による波形なまり)が発生するため本発明を効果的に適用できる。

【0018】

(駆動回路の構成)

次に各駆動回路と階調表現方法について説明する。

まず、各駆動回路について説明する。

行配線駆動回路103は、行配線105を順次選択して、選択された行配線に走査信号(選択電圧)を出力する。行配線駆動回路103は、例えば、駆動対象の行配線105(選択された行配線105)には−20Vの選択電圧、他の行配線105には7Vの非選択

電圧を印加する。

列配線駆動回路102は、行配線駆動回路103によって選択される行配線が変更されるのに同期して、画像データ(輝度信号)に基づき生成した各列の変調信号を複数の列配線104に出力する。例えば、列配線駆動回路102は、1ライン分(1水平期間分)の輝度信号を入力するシフトレジスタ、輝度信号を1ライン時間保持するラインメモリ、輝度信号に応じて駆動波形(変調信号)Vxを生成し列配線に印加する変調信号生成部などで構成される。変調信号としては、パルス幅、振幅、またはその両方を変調した電圧波形を用いることができる。

【0019】

次に階調表現方法について、電子放出素子が図3に示すような電子放出特性(電子放出素子の印加電圧Vgcと電子放出電流Icの関係)を有するものとして説明する。具体的には、図3の例では、電子放出素子は、印加電圧Vgcが20Vよりも大きい場合に、印加電圧Vgcが大きいほど電子放出電流Icが大きくなる特性を有している。印加電圧Vgcは、電子放出素子のゲート電極とカソード電極の間に印加される電圧(走査信号と変調信号の差電圧)である。電子放出電流Icは、電子放出素子から放出される電子によって流れる電流、即ち、電子放出素子から放出される電子の量である。

【0020】

選択信号(−20V)が印加されている行配線(選択行配線)と、15Vの変調信号が印加されている列配線とに接続されている電子放出素子では、印加電圧Vgcが35Vとなる。そのため、その電子放出素子からは電子が放出され、対応する蛍光体は発光する。このとき、他の行配線(非選択行配線)には非選択信号(7V)が印加されているが、そのような行配線と15Vの変調信号が印加されている列配線とに接続されている電子放出素子では、印加電圧Vgcが8Vとなる。そのため、電子の放出は行われず、対応する蛍光体は発光しない。

選択信号が印加されている行配線と、0Vの変調信号が印加されている列配線とに接続されている電子放出素子では、印加電圧Vgcが20Vとなるが、電子放出素子は図3に示す特性を有しているため、電子の放出は行われず、対応する蛍光体は発光しない。このとき、他の行配線には非選択信号が印加されているが、そのような行配線と0Vの変調信号が印加されている列配線とに接続されている電子放出素子では、印加電圧Vgcが−7Vとなるため、電子の放出は行われず、対応する蛍光体は発光しない。

【0021】

以上のようにして、変調信号を輝度信号のレベルに応じて(0〜15Vの間で)制御することにより、非選択行配線に接続されている表示素子を駆動させずに、選択行配線に接続されている表示素子を所望の階調レベルで駆動することができる。

なお、以上の説明は、輝度信号に応じて変調信号(電圧波形)の振幅を変調する場合の例であるが、輝度信号に応じて変調信号のパルス幅や振幅とパルス幅の両方を変調しても所望の階調表現をすることができる。

【0022】

なお、本発明はアクティブマトリクス駆動やパッシブマトリクス駆動といった駆動方式、パルス幅変調(PWM)やパルス振幅変調(PHM)といった変調方式によらず適用できる。特に、パッシブマトリクス駆動では、変調信号の波形なまりがそのまま輝度へ反映されるため、輝度ムラが発生しやすい。またPWMでは、パルス幅が狭いときにパルス幅が広い場合に比べて波形なまりの影響が相対的に大きくなるため、輝度ムラが発生しやすい。そのため、パッシブマトリクス駆動やPWMの画像表示装置には本発明を効果的に適用できる。さらには、列配線の配線抵抗および列配線に流れる電流が大きく、列配線と行配線の交差部に発生する容量が大きい場合には、変調信号の電圧降下やRC時定数による波形なまりが大きく現れるため、本発明をより効果的に適用できる。

【0023】

<第1の実施形態>

以下、図面を参照して本発明の第1の実施形態に係る画像表示装置およびその制御方法

について説明する。

本実施形態に係る画像表示装置は、図4に示すように、従来の一般的な構成(図1の構成)に加え、列配線駆動回路102と列配線104との間の抵抗値を変更する可変抵抗回路501を更に有する。

可変抵抗回路501は、例えば、行配線駆動回路103によって選択される行配線105が変更されるのに同期して列配線駆動回路102と列配線104との間の抵抗値を変更する。

なお、他の構成は図1と同様のため同じ符号を付し、説明は省略する。

【0024】

可変抵抗回路501は、図4に示すように、抵抗値制御部601と可変抵抗部602で構成することができる。

抵抗値制御部601は、可変抵抗部602に制御信号を出力する。

可変抵抗部602は、列配線駆動回路102と列配線104との間の抵抗となる抵抗器であり、その抵抗値は制御信号に応じて変更される。

抵抗値制御部601が、制御回路101から出力される水平同期信号と垂直同期信号を用いて、選択(駆動)されている行配線(駆動ライン)を判断し、駆動ラインの位置に応じて制御電圧を変更することにより、可変抵抗部602の抵抗値が変更される。即ち、列配線駆動回路102の出力インピーダンス、列配線駆動回路102から見た表示素子側の抵抗値が変更される。

【0025】

なお、抵抗値制御部601および可変抵抗部602は、列配線駆動回路102内に設けられていてもよいし、背面基板106内に設けられていてもよい。可変抵抗部602は、列配線駆動回路102と列配線104の間に設けられていればよい。抵抗値制御部601は制御回路101内に設けられていても良い。

【0026】

(抵抗値制御部の説明)

抵抗値制御部601について図5を用いて説明する。抵抗値制御部601は同期カウンタ回路701、制御電圧発生回路702などで構成される。

同期カウンタ回路701は、制御回路101から送られてくる水平同期信号と垂直同期信号を元に、駆動ライン(行配線番号)を表す情報を生成し、制御電圧発生回路702へ出力する。

制御電圧発生回路702は、受け取った駆動ライン情報に応じて制御電圧を出力する。

【0027】

制御電圧発生回路702は、例えば、図6に示すように、入力された基準電圧を分圧するラダー抵抗回路により構成することができる。図6の例では、制御電圧発生回路702は、直列に接続されたラダー抵抗R1〜Rn(nは任意の整数)、スイッチ群801、スイッチ制御部802などを有する。複数のラダー抵抗R1〜Rn全体に基準電圧が印加され、基準電圧を複数のラダー抵抗R1〜Rnによって分圧して生成された電圧V1〜Vnのいずれかが制御電圧としてスイッチ群801によって選択される。スイッチ制御部802は、駆動ライン情報(選択された行配線105の位置)に応じてスイッチ群801(どの電圧を制御電圧とするか)を制御する。

【0028】

図10に制御電圧の出力特性(選択された行配線と制御電圧の関係)の一例を示す。図11にスイッチ制御特性(選択された行配線と選択スイッチ(オンされるスイッチ)の関係)の一例を示す。なお、図10,11は、列配線駆動回路102から最も遠い行配線105の行配線番号を1とし、行配線105の位置が列配線駆動回路102に近づくにつれて行配線番号が1ずつ増加する場合の例である(行配線番号の最大値はn)。

【0029】

図10(a)は、行配線番号の増加に対して制御電圧を一定の傾きで増加させた場合の例である。このような特性を得るためには、図6に示すラダー抵抗R1〜Rnの抵抗値を

全て等しくすればよい。そして、駆動ラインの行配線番号が1のときはSW1が、行配線

番号が2のときはSW2が、行配線番号がnのときはSWnがオンされればよい(行配線の選択が行われる度にオンするスイッチが切り替えられればよい)。即ち、スイッチ制御部802は、図11(a)に示すような特性となるように、スイッチ群801を制御すればよい。

【0030】

なお、ラダー抵抗の抵抗値を不均一にしたり、スイッチ制御部802の制御特性を変化させれば、図10(b)、図10(c)に示すような出力特性を得ることができる。

図10(a)〜10(c)に示すように制御電圧を変更すれば、選択された行配線の位置に応じて列配線駆動回路102と列配線104との間の抵抗値を連続的に変更することができる。

【0031】

但し、可変抵抗回路501の構成はこれらに限らない。可変抵抗回路501は、列配線104の抵抗値やその分布などに基づいて、所望の抵抗値変化が実現されるように最適に設計されればよい。そのため、制御信号の種類や数、スイッチの数や制御方法、及び、それらの細かい特性は特に限定されるものではない。具体的には、制御信号は電流値であってもよいし、複数種類(例えば、電圧値と電流値の両方)の信号を用いてもよい。また、可変抵抗回路501は、選択された行配線の位置に応じて列配線駆動回路102と列配線104との間の抵抗値を段階的に変更してもよい。具体的には、制御電圧の出力特性は、図10(d)に示すように、行配線の選択が複数回行われる度に制御電圧を変更する構成であってもよい。図10(d)に示すような特性を得るためには、スイッチ制御部802は、図11(b)に示すような特性となるように、スイッチ群801を制御すればよい。即ち、行配線の選択が複数回行われる度にオンするスイッチが切り替えられればよい。このような構成にすれば、図10(a)〜10(c)に示すように制御電圧を得る場合に比べ、回路構成や処理(スイッチの切り替え)をより簡易にすることができる。

【0032】

(可変抵抗部の説明)

可変抵抗部602について図7を用いて説明する。図7の例では、可変抵抗部602は、列配線104毎の電界効果トランジスタ(FET)を含む回路から構成されている。FETは、列配線駆動回路102と列配線104との間の抵抗となる素子である。

FETのドレイン端子は列配線104に接続されており、ソース端子は列配線駆動回路102に接続されており、制御電圧はゲート端子に入力される。そのため、FETの抵抗値(ドレイン−ソース間(可変抵抗部の入出力間)に流れる電流)は、変調信号と制御電圧との電圧差に応じて設定される。

【0033】

なお、変調信号が振幅が変調された電圧波形を有する場合には、変調信号によってFETの抵抗値が変化することが考えられる。即ち、列配線間でFETの抵抗値に差が生じることが考えられる。そのため、変調信号が振幅が変調された電圧波形を有する場合には、FETごとに入力する制御電圧を変更すればよい。

なお、図7では、1つの列配線に対して、1つのFETが設けられているが、1つの列配線に対して複数のFETが設けられていてもよい。その場合には、FET毎に入力される制御電圧の値が異なっていてもよい。また、FETの代わりに各種トランジスタのような半導体素子が用いられてもよい。その場合には、制御信号として、電圧ではなく、電流が入力されてもよい。

【0034】

本実施形態では、可変抵抗回路501は、選択された行配線105の位置に応じて列配線駆動回路102と列配線104との間の抵抗値(FETの抵抗値)を変更する。具体的には、列配線の配線抵抗に起因する輝度ムラを抑制するために、選択された行配線105が列配線駆動回路102に近いときのほうが、選択された行配線105が列配線駆動回路102から遠いときよりも、FETの抵抗値が大きくされる。より具体的には、選択され

た行配線105に接続された画素と列配線駆動回路102との間の抵抗値が選択された行配線105の位置によらず一定となるように、FETの抵抗値が変更される。それにより、可変抵抗回路501は、選択された行配線105に接続された画素と列配線駆動回路102との間の抵抗値の変動を抑制する。

【0035】

本実施形態に係る変調信号(選択された行配線に接続された画素(駆動する画素)に印加される変調信号)の波形について、図12,13を用いて説明する。

列配線駆動回路102から遠い開放端側の行配線が選択されている場合、FETの抵抗値は低い値となるため、駆動する画素に印加される変調信号は従来の信号(図12の実線)とほぼ等しい信号となる。

一方、列配線駆動回路102に近い駆動端側の行配線が選択されている場合、FETの抵抗値は高い値となる。そのため、駆動する画素に印加される変調信号は、FETによる電圧降下と、RC時定数による波形なまりの影響を大きく受ける。その結果、図13の実線に示すように、駆動する画素に印加される変調信号は、開放端側の変調信号(図12の実線)に近づけられる。このとき画像データは同一階調のままである(画像データの階調値は変更されない)。即ち、本実施形態の構成によれば、階調値(階調性)を低下させることなく、駆動端側と開放端側の変調信号を同等にすることができ、ひいては、列配線の配線抵抗に起因する輝度ムラを抑制することができる。

なお、図13には、従来の信号を破線で示している。

【0036】

以上述べたように、本実施形態によれば、選択された行配線の位置に応じて列配線駆動回路と列配線との間の抵抗値を変更するという簡易な構成で、階調性を低減させることなく列配線の配線抵抗に起因する輝度ムラを抑制することが可能となる。具体的には、選択された行配線が列配線駆動回路に近いときのほうが、遠いときよりも列配線駆動回路と列配線との間の抵抗値を大きくすることにより、階調性を低減させることなく列配線の配線抵抗に起因する輝度ムラが抑制される。

【0037】

<第2の実施形態>

第2の実施形態では、制御電圧発生回路702の構成が第1の実施形態と異なる。なお、本実施形態では、第1の実施形態と同様の構成については説明を省略し、第1の実施形態と異なる点について説明する。

【0038】

本実施形態に係る制御電圧発生回路702において、ラダー抵抗回路は、ラダー抵抗回路の端点の電位を規定する基準電圧と、中間点の電位を規定する基準電圧とを入力可能である。具体的には、図8に示すように、4つの基準電圧(基準電圧1<基準電圧2<基準電圧3<基準電圧4)が複数のラダー抵抗の任意の位置に入力される。そのため、基準電圧1〜4の電圧値に応じて、画面の領域(複数の行配線)ごとに制御電圧の出力特性を変えることができる。図10(e)はラダー抵抗の抵抗値がすべて同じ場合の例である。この場合には、画面の領域ごとに出力特性の傾きを変えることができる。なお、入力される基準電圧の数は4つに限らない(2つ以上であればよい)。

【0039】

基準電圧が1つの場合には、基準電圧を変更したとしても、電圧V1〜Vnの比率は保たれたまま、即ち、制御電圧の出力特性のカーブ形状は維持されたままでしか、制御電圧の出力特性を変化させることができない。例えば、ラダー抵抗値が全て同じ場合である図10(a)の出力特性をもつ制御電圧発生回路では、その傾きを一律に変更することしかできず、図10(e)に示す出力特性を得ることはできない。

【0040】

なお、第1の実施形態のような基準電圧が1つの場合においても、ラダー抵抗の抵抗値を変更すれば、図10(e)の他、様々な制御電圧の出力特性を得ることは可能である。しかしながら、ラダー抵抗は通常ICなどのカスタム部品内に形成されるため、その抵抗

値は容易に変更することができない。変更することができたとしても、部品の再設計が必要となる場合がある。

【0041】

以上述べたように、本実施形態によれば、ラダー抵抗回路は、ラダー抵抗回路の端点の電位を規定する基準電圧と、中間点の電位を規定する基準電圧とを入力可能な構成とされる。それにより、制御電圧発生回路702を変更することなく、制御電圧の出力特性を変更することが可能となる、という効果を得ることができる。そして、同一の可変抵抗回路501で、様々な制御電圧の出力特性を得ることができ、ひいては、様々な抵抗値変化の特性(駆動ラインと抵抗値の関係)を得ることができる。また、列配線104の抵抗値やその分布が変更になった場合にも対応可能となり、非常に好ましい。

【0042】

<第3の実施形態>

第3の実施形態では、制御電圧発生回路の構成が第1の実施形態と異なる。なお、本実施形態では、第1の実施形態と同様の構成については説明を省略し、第1の実施形態と異なる点について説明する。

【0043】

本実施形態に係る制御電圧発生回路702は、図9に示すように、スイッチ制御部802に接続されたメモリ1201を有する。

メモリ1201には、例えば、図11(a)〜(c)に示すような、行配線番号(駆動ライン情報)と選択スイッチ番号の関係を示す1次元ルックアップテーブルデータが格納される。そして、スイッチ制御部802は、入力された駆動ライン情報に対応する選択スイッチ番号をメモリ1201から読み出し、スイッチ群801を制御する。

そして、1次元ルックアップテーブルデータを書き替えることにより、制御電圧の出力特性を変更することが可能となる。

【0044】

なお、第1の実施形態においても、スイッチ群801あるいはスイッチ制御部802を変更すれば、制御電圧の出力特性を変更することができる。しかしながら、スイッチ群801やスイッチ制御部802は通常ICなどのカスタム部品内に形成されているため、それらの構成は容易に変更することができない。変更することができたとしても、部品の再設計が必要となる場合がある。

【0045】

以上述べたように、本実施形態によれば、行配線番号と選択スイッチ番号の関係を示す1次元ルックアップテーブルデータが格納されたメモリが設けられ、該1次元ルックアップテーブルデータを用いてスイッチ群が制御される。それにより、スイッチ群801やスイッチ制御部802を変更することなく、制御電圧の出力特性を変更することが可能となる。具体的には、上記1次元ルックアップテーブルデータを書き替えることにより、容易に制御電圧の出力特性を変更することが可能となる。それにより、同一の可変抵抗回路501で、様々な制御電圧の出力特性を得ることができ、ひいては、様々な抵抗値変化の特性(駆動ラインと抵抗値の関係)を得ることができる。また、列配線104の抵抗値やその分布が変更になった場合にも対応可能となり、非常に好ましい。

【符号の説明】

【0046】

102 列配線駆動回路

103 行配線駆動回路

104 列配線

105 行配線

501 可変抵抗回路

【技術分野】

【0001】

本発明は、画像表示装置及びその制御方法に関する。

【背景技術】

【0002】

フラットパネルディスプレイ(FPD)としては、液晶表示装置(LCD)、プラズマ表示装置(PDP)、有機EL表示装置(OLED)、フィールドエミッション表示装置(FED)などが知られている。

中でもFEDはパッシブマトリックス構造であり、行配線と列配線との交差点に電界放出素子が位置するシンプルなパネル構造になっているため、低コストでありながら、高速応答という特徴を持つ。

【0003】

図1は、一般的なマトリクス駆動方式の画像表示装置(例えばFED)の基本的な構成例である。背面基板106上には、複数の列配線104と複数の行配線105が形成されており、列配線104と行配線105との各交点に画素(表示素子)が形成されている。列配線104が列配線駆動回路102に接続され、行配線105が行配線駆動回路103に接続されることにより、表示装置モジュールが構成されている。

【0004】

また図1の画像表示装置は、デジタル映像信号が入力される制御回路101を備えている。行配線駆動回路103は、駆動対象とする行配線105に走査信号(選択電圧)を印加し、他の行配線105に非選択電圧を印加する回路である。行配線105は、例えば1ラインずつ上から順次駆動(走査)される。列配線駆動回路102は、駆動行の映像信号(輝度信号)から各列の駆動波形(変調信号)を生成し、各列配線104に印加する。これにより表示素子の輝度(電子放出素子の電子放出量)が変調されて所望の映像を出力する事ができる。

【0005】

しかしながら、列配線104の配線抵抗および列配線104と行配線105の交差部に生じる静電容量により、変調信号の電圧降下およびRC時定数による波形なまりが発生する。そのため、図12に示すように、列配線駆動回路102の近く(駆動端側)に設けられた表示素子と、遠く(開放端側)に設けられた表示素子とでは、印加される変調信号の形状に差が出てくる。その結果、駆動端側に比べて開放端側が暗くなる、つまり列方向に輝度ムラ(表示不良)が発生する。

【0006】

また、画像表示装置の大サイズ化や高精細化が進むと、列配線104が長く、細くなる。これにより、列配線104の抵抗が増大するため、前述の輝度ムラもより増大する。

この課題を解決するための技術としては、表示素子の位置や階調に応じた補正値を用いて映像信号を補正する技術(特許文献1)や、RC時定数による電圧信号のなまりに応じて補正する技術(特許文献2)などが提案されている。これらの技術を用いると上述した表示不良は抑制(補正)することができる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】米国特許第6097356号明細書

【特許文献2】特開平6−258614号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかし、特許文献1や特許文献2に記載の技術では、表示素子の位置に依存する輝度む

らは軽減できるものの、階調性の低下あるいは回路規模の増大は免れられない。

【0009】

列配線駆動回路102の駆動端側、開放端側の表示素子に印加する変調信号の値を、階調値0(変調信号の最小値)から最大階調値(階調値Dmax;変調信号の最大値)まで変化させたときの、各々の輝度変化の例を図2(a),(b)に示す。図2(a),(b)に示すように、駆動端側の表示素子の最大輝度(近傍最大輝度)が輝度Laであったとすると、開放端側の表示素子の最大輝度(遠方最大輝度)は輝度Laよりも低い輝度Lbとなる。これは、開放端側では、駆動端側に比べ、列配線の抵抗分だけ変調信号の電圧降下による信号レベル低下とRC時定数による波形なまりがより大きく発生することにより、輝度が低下するからである。

【0010】

従来技術では、輝度ムラを抑制するために、最大輝度の高い表示素子の輝度が最大輝度の低い表示素子の輝度に合わせられる。具体的には、駆動端側の表示素子の最大輝度も輝度Lbとされ、駆動端側の表示素子に対しては階調値Da(階調値Dmaxより小さい階調値;近傍最大階調)までの変調信号しか使用されない。そのため、駆動端側の表示素子の階調性は低下し、開放端側の表示素子の最大階調値(遠方最大階調)よりも近傍最大階調値は小さくなる。

高い階調性を維持するためには、上述の階調性低下を見越した映像信号の高ビット化が必要となる。しかしながら、これは制御回路や駆動回路などの回路の規模の増大、映像信号のデータ量の増大を招く。

【0011】

本発明は、簡易な構成で、階調性を低減させることなく列配線の配線抵抗に起因する輝度ムラを抑制することのできる技術を提供することを目的とする。

【課題を解決するための手段】

【0012】

本発明の画像表示装置は、複数の行配線と、複数の列配線と、前記行配線と前記列配線の各交点に配置された複数の画素と、を有する表示パネルと、前記行配線を順次選択して、選択された行配線に走査信号を出力する行配線駆動回路と、前記行配線駆動回路によって選択される行配線が変更されるのに同期して、画像データに基づき生成した各列の変調信号を前記複数の列配線に出力する列配線駆動回路と、前記列配線駆動回路と前記列配線との間の抵抗値を変更する可変抵抗回路と、を有し、前記可変抵抗回路は、前記選択された行配線が前記列配線駆動回路に近いときのほうが前記抵抗値が大きくなるように、前記選択された行配線の位置に応じて前記抵抗値を変更することを特徴とする。

【0013】

本発明の画像表示装置の制御方法は、複数の行配線と、複数の列配線と、前記行配線と前記列配線の各交点に配置された複数の画素と、を有する表示パネルと、行配線駆動回路と、列配線駆動回路と、可変抵抗回路と、を有する画像表示装置の制御方法であって、前記行配線駆動回路が、前記行配線を順次選択して、選択された行配線に走査信号を出力するステップと、前記行配線駆動回路によって選択される行配線が変更されるのに同期して、列配線駆動回路が、画像データに基づき生成した各列の変調信号を前記複数の列配線に出力するステップと、前記可変抵抗回路が、前記選択された行配線が前記列配線駆動回路に近いときのほうが前記抵抗値が大きくなるように、前記選択された行配線の位置に応じて前記列配線駆動回路と前記列配線との間の抵抗値を変更するステップと、を有することを特徴とする。

【発明の効果】

【0014】

本発明によれば、簡易な構成で、階調性を低減させることなく列配線の配線抵抗に起因する輝度ムラを抑制することができる。

【図面の簡単な説明】

【0015】

【図1】一般的なFEDの基本的な全体構成の一例を示す図。

【図2】本発明の課題を説明する図。

【図3】電子放出特性の一例を示す図。

【図4】第1の実施形態に係る画像表示装置の全体構成の一例を示す図。

【図5】抵抗値制御部の構成の一例を示す図。

【図6】第1の実施形態に係る制御電圧発生回路の構成の一例を示す図。

【図7】可変抵抗部の構成の一例を示す図。

【図8】第2の実施形態に係る制御電圧発生回路の構成の一例を示す図。

【図9】第3の実施形態に係る制御電圧発生回路の構成の一例を示す図。

【図10】制御電圧の出力特性の一例を示す図。

【図11】スイッチ制御特性の一例を示す図。

【図12】従来の変調信号の波形の一例を示す図。

【図13】本実施形態に係る変調信号の波形の一例を示す図。

【発明を実施するための形態】

【0016】

以下、図面を参照して本発明の好適な実施の形態を説明する。本発明は、マトリクス駆動方式の表示パネルにおいて、列配線の配線抵抗に起因する輝度ムラ(列配線の配線抵抗による電圧降下やRC時定数による波形なまりによる輝度ムラ)を補正するための技術に関する。以下の実施形態では、画素(表示素子)として電界放出素子(電子放出素子)を用いた表示装置(FED)に本発明を適用した例について具体的に説明を行う。ただし、本発明の適用範囲はこれに限られず、マトリクス駆動方式の表示パネルをもつ画像表示装置であれば、FED以外の画像表示装置にも適用できる。

【0017】

(画像表示装置全体の構成)

図1は、一般的なFEDの基本的な全体構成の例である。背面基板106は、FEDパネル(表示パネル)のカソードパネルを構成するガラス基板である。背面基板106上には、複数の列配線104と複数の行配線105がマトリクス状に形成されている。列配線104と行配線105との各交点には、画素(表示素子)が形成されている。また図示は省略しているが、カソードパネルに対向するように、蛍光体及びアノード電極(メタルバック)を具備するアノードパネルが配置される。列配線104は、変調信号を出力する列配線駆動回路102に接続される。行配線105は、走査信号を出力する行配線駆動回路103に接続される。各駆動回路102、103は、水平同期信号、垂直同期信号、及び、輝度信号(画像データ)を出力する制御回路101に接続される。輝度信号は、例えばR、G、B各色のデジタル信号である。制御回路101は、入力された映像信号(デジタル映像信号)から輝度信号を生成し、列配線駆動回路102に供給する。また、水平同期信号及び垂直同期信号は、各駆動回路102、103に入力され、該信号に応じて走査信号及び変調信号を印加するタイミングが制御される。

以上により、FEDモジュールが構成されている。ここで、列配線が超伝導体で構成されていて配線抵抗を有していない場合、電圧降下やRC時定数による波形なまりが発生しないため、本発明を適用しても効果を得ることができない。しかし、Al、Cu、Agなどの配線抵抗を有する一般的な配線材であれば、列配線の配線抵抗に起因した輝度ムラ(列配線の配線抵抗による電圧降下やRC時定数による波形なまり)が発生するため本発明を効果的に適用できる。

【0018】

(駆動回路の構成)

次に各駆動回路と階調表現方法について説明する。

まず、各駆動回路について説明する。

行配線駆動回路103は、行配線105を順次選択して、選択された行配線に走査信号(選択電圧)を出力する。行配線駆動回路103は、例えば、駆動対象の行配線105(選択された行配線105)には−20Vの選択電圧、他の行配線105には7Vの非選択

電圧を印加する。

列配線駆動回路102は、行配線駆動回路103によって選択される行配線が変更されるのに同期して、画像データ(輝度信号)に基づき生成した各列の変調信号を複数の列配線104に出力する。例えば、列配線駆動回路102は、1ライン分(1水平期間分)の輝度信号を入力するシフトレジスタ、輝度信号を1ライン時間保持するラインメモリ、輝度信号に応じて駆動波形(変調信号)Vxを生成し列配線に印加する変調信号生成部などで構成される。変調信号としては、パルス幅、振幅、またはその両方を変調した電圧波形を用いることができる。

【0019】

次に階調表現方法について、電子放出素子が図3に示すような電子放出特性(電子放出素子の印加電圧Vgcと電子放出電流Icの関係)を有するものとして説明する。具体的には、図3の例では、電子放出素子は、印加電圧Vgcが20Vよりも大きい場合に、印加電圧Vgcが大きいほど電子放出電流Icが大きくなる特性を有している。印加電圧Vgcは、電子放出素子のゲート電極とカソード電極の間に印加される電圧(走査信号と変調信号の差電圧)である。電子放出電流Icは、電子放出素子から放出される電子によって流れる電流、即ち、電子放出素子から放出される電子の量である。

【0020】

選択信号(−20V)が印加されている行配線(選択行配線)と、15Vの変調信号が印加されている列配線とに接続されている電子放出素子では、印加電圧Vgcが35Vとなる。そのため、その電子放出素子からは電子が放出され、対応する蛍光体は発光する。このとき、他の行配線(非選択行配線)には非選択信号(7V)が印加されているが、そのような行配線と15Vの変調信号が印加されている列配線とに接続されている電子放出素子では、印加電圧Vgcが8Vとなる。そのため、電子の放出は行われず、対応する蛍光体は発光しない。

選択信号が印加されている行配線と、0Vの変調信号が印加されている列配線とに接続されている電子放出素子では、印加電圧Vgcが20Vとなるが、電子放出素子は図3に示す特性を有しているため、電子の放出は行われず、対応する蛍光体は発光しない。このとき、他の行配線には非選択信号が印加されているが、そのような行配線と0Vの変調信号が印加されている列配線とに接続されている電子放出素子では、印加電圧Vgcが−7Vとなるため、電子の放出は行われず、対応する蛍光体は発光しない。

【0021】

以上のようにして、変調信号を輝度信号のレベルに応じて(0〜15Vの間で)制御することにより、非選択行配線に接続されている表示素子を駆動させずに、選択行配線に接続されている表示素子を所望の階調レベルで駆動することができる。

なお、以上の説明は、輝度信号に応じて変調信号(電圧波形)の振幅を変調する場合の例であるが、輝度信号に応じて変調信号のパルス幅や振幅とパルス幅の両方を変調しても所望の階調表現をすることができる。

【0022】

なお、本発明はアクティブマトリクス駆動やパッシブマトリクス駆動といった駆動方式、パルス幅変調(PWM)やパルス振幅変調(PHM)といった変調方式によらず適用できる。特に、パッシブマトリクス駆動では、変調信号の波形なまりがそのまま輝度へ反映されるため、輝度ムラが発生しやすい。またPWMでは、パルス幅が狭いときにパルス幅が広い場合に比べて波形なまりの影響が相対的に大きくなるため、輝度ムラが発生しやすい。そのため、パッシブマトリクス駆動やPWMの画像表示装置には本発明を効果的に適用できる。さらには、列配線の配線抵抗および列配線に流れる電流が大きく、列配線と行配線の交差部に発生する容量が大きい場合には、変調信号の電圧降下やRC時定数による波形なまりが大きく現れるため、本発明をより効果的に適用できる。

【0023】

<第1の実施形態>

以下、図面を参照して本発明の第1の実施形態に係る画像表示装置およびその制御方法

について説明する。

本実施形態に係る画像表示装置は、図4に示すように、従来の一般的な構成(図1の構成)に加え、列配線駆動回路102と列配線104との間の抵抗値を変更する可変抵抗回路501を更に有する。

可変抵抗回路501は、例えば、行配線駆動回路103によって選択される行配線105が変更されるのに同期して列配線駆動回路102と列配線104との間の抵抗値を変更する。

なお、他の構成は図1と同様のため同じ符号を付し、説明は省略する。

【0024】

可変抵抗回路501は、図4に示すように、抵抗値制御部601と可変抵抗部602で構成することができる。

抵抗値制御部601は、可変抵抗部602に制御信号を出力する。

可変抵抗部602は、列配線駆動回路102と列配線104との間の抵抗となる抵抗器であり、その抵抗値は制御信号に応じて変更される。

抵抗値制御部601が、制御回路101から出力される水平同期信号と垂直同期信号を用いて、選択(駆動)されている行配線(駆動ライン)を判断し、駆動ラインの位置に応じて制御電圧を変更することにより、可変抵抗部602の抵抗値が変更される。即ち、列配線駆動回路102の出力インピーダンス、列配線駆動回路102から見た表示素子側の抵抗値が変更される。

【0025】

なお、抵抗値制御部601および可変抵抗部602は、列配線駆動回路102内に設けられていてもよいし、背面基板106内に設けられていてもよい。可変抵抗部602は、列配線駆動回路102と列配線104の間に設けられていればよい。抵抗値制御部601は制御回路101内に設けられていても良い。

【0026】

(抵抗値制御部の説明)

抵抗値制御部601について図5を用いて説明する。抵抗値制御部601は同期カウンタ回路701、制御電圧発生回路702などで構成される。

同期カウンタ回路701は、制御回路101から送られてくる水平同期信号と垂直同期信号を元に、駆動ライン(行配線番号)を表す情報を生成し、制御電圧発生回路702へ出力する。

制御電圧発生回路702は、受け取った駆動ライン情報に応じて制御電圧を出力する。

【0027】

制御電圧発生回路702は、例えば、図6に示すように、入力された基準電圧を分圧するラダー抵抗回路により構成することができる。図6の例では、制御電圧発生回路702は、直列に接続されたラダー抵抗R1〜Rn(nは任意の整数)、スイッチ群801、スイッチ制御部802などを有する。複数のラダー抵抗R1〜Rn全体に基準電圧が印加され、基準電圧を複数のラダー抵抗R1〜Rnによって分圧して生成された電圧V1〜Vnのいずれかが制御電圧としてスイッチ群801によって選択される。スイッチ制御部802は、駆動ライン情報(選択された行配線105の位置)に応じてスイッチ群801(どの電圧を制御電圧とするか)を制御する。

【0028】

図10に制御電圧の出力特性(選択された行配線と制御電圧の関係)の一例を示す。図11にスイッチ制御特性(選択された行配線と選択スイッチ(オンされるスイッチ)の関係)の一例を示す。なお、図10,11は、列配線駆動回路102から最も遠い行配線105の行配線番号を1とし、行配線105の位置が列配線駆動回路102に近づくにつれて行配線番号が1ずつ増加する場合の例である(行配線番号の最大値はn)。

【0029】

図10(a)は、行配線番号の増加に対して制御電圧を一定の傾きで増加させた場合の例である。このような特性を得るためには、図6に示すラダー抵抗R1〜Rnの抵抗値を

全て等しくすればよい。そして、駆動ラインの行配線番号が1のときはSW1が、行配線

番号が2のときはSW2が、行配線番号がnのときはSWnがオンされればよい(行配線の選択が行われる度にオンするスイッチが切り替えられればよい)。即ち、スイッチ制御部802は、図11(a)に示すような特性となるように、スイッチ群801を制御すればよい。

【0030】

なお、ラダー抵抗の抵抗値を不均一にしたり、スイッチ制御部802の制御特性を変化させれば、図10(b)、図10(c)に示すような出力特性を得ることができる。

図10(a)〜10(c)に示すように制御電圧を変更すれば、選択された行配線の位置に応じて列配線駆動回路102と列配線104との間の抵抗値を連続的に変更することができる。

【0031】

但し、可変抵抗回路501の構成はこれらに限らない。可変抵抗回路501は、列配線104の抵抗値やその分布などに基づいて、所望の抵抗値変化が実現されるように最適に設計されればよい。そのため、制御信号の種類や数、スイッチの数や制御方法、及び、それらの細かい特性は特に限定されるものではない。具体的には、制御信号は電流値であってもよいし、複数種類(例えば、電圧値と電流値の両方)の信号を用いてもよい。また、可変抵抗回路501は、選択された行配線の位置に応じて列配線駆動回路102と列配線104との間の抵抗値を段階的に変更してもよい。具体的には、制御電圧の出力特性は、図10(d)に示すように、行配線の選択が複数回行われる度に制御電圧を変更する構成であってもよい。図10(d)に示すような特性を得るためには、スイッチ制御部802は、図11(b)に示すような特性となるように、スイッチ群801を制御すればよい。即ち、行配線の選択が複数回行われる度にオンするスイッチが切り替えられればよい。このような構成にすれば、図10(a)〜10(c)に示すように制御電圧を得る場合に比べ、回路構成や処理(スイッチの切り替え)をより簡易にすることができる。

【0032】

(可変抵抗部の説明)

可変抵抗部602について図7を用いて説明する。図7の例では、可変抵抗部602は、列配線104毎の電界効果トランジスタ(FET)を含む回路から構成されている。FETは、列配線駆動回路102と列配線104との間の抵抗となる素子である。

FETのドレイン端子は列配線104に接続されており、ソース端子は列配線駆動回路102に接続されており、制御電圧はゲート端子に入力される。そのため、FETの抵抗値(ドレイン−ソース間(可変抵抗部の入出力間)に流れる電流)は、変調信号と制御電圧との電圧差に応じて設定される。

【0033】

なお、変調信号が振幅が変調された電圧波形を有する場合には、変調信号によってFETの抵抗値が変化することが考えられる。即ち、列配線間でFETの抵抗値に差が生じることが考えられる。そのため、変調信号が振幅が変調された電圧波形を有する場合には、FETごとに入力する制御電圧を変更すればよい。

なお、図7では、1つの列配線に対して、1つのFETが設けられているが、1つの列配線に対して複数のFETが設けられていてもよい。その場合には、FET毎に入力される制御電圧の値が異なっていてもよい。また、FETの代わりに各種トランジスタのような半導体素子が用いられてもよい。その場合には、制御信号として、電圧ではなく、電流が入力されてもよい。

【0034】

本実施形態では、可変抵抗回路501は、選択された行配線105の位置に応じて列配線駆動回路102と列配線104との間の抵抗値(FETの抵抗値)を変更する。具体的には、列配線の配線抵抗に起因する輝度ムラを抑制するために、選択された行配線105が列配線駆動回路102に近いときのほうが、選択された行配線105が列配線駆動回路102から遠いときよりも、FETの抵抗値が大きくされる。より具体的には、選択され

た行配線105に接続された画素と列配線駆動回路102との間の抵抗値が選択された行配線105の位置によらず一定となるように、FETの抵抗値が変更される。それにより、可変抵抗回路501は、選択された行配線105に接続された画素と列配線駆動回路102との間の抵抗値の変動を抑制する。

【0035】

本実施形態に係る変調信号(選択された行配線に接続された画素(駆動する画素)に印加される変調信号)の波形について、図12,13を用いて説明する。

列配線駆動回路102から遠い開放端側の行配線が選択されている場合、FETの抵抗値は低い値となるため、駆動する画素に印加される変調信号は従来の信号(図12の実線)とほぼ等しい信号となる。

一方、列配線駆動回路102に近い駆動端側の行配線が選択されている場合、FETの抵抗値は高い値となる。そのため、駆動する画素に印加される変調信号は、FETによる電圧降下と、RC時定数による波形なまりの影響を大きく受ける。その結果、図13の実線に示すように、駆動する画素に印加される変調信号は、開放端側の変調信号(図12の実線)に近づけられる。このとき画像データは同一階調のままである(画像データの階調値は変更されない)。即ち、本実施形態の構成によれば、階調値(階調性)を低下させることなく、駆動端側と開放端側の変調信号を同等にすることができ、ひいては、列配線の配線抵抗に起因する輝度ムラを抑制することができる。

なお、図13には、従来の信号を破線で示している。

【0036】

以上述べたように、本実施形態によれば、選択された行配線の位置に応じて列配線駆動回路と列配線との間の抵抗値を変更するという簡易な構成で、階調性を低減させることなく列配線の配線抵抗に起因する輝度ムラを抑制することが可能となる。具体的には、選択された行配線が列配線駆動回路に近いときのほうが、遠いときよりも列配線駆動回路と列配線との間の抵抗値を大きくすることにより、階調性を低減させることなく列配線の配線抵抗に起因する輝度ムラが抑制される。

【0037】

<第2の実施形態>

第2の実施形態では、制御電圧発生回路702の構成が第1の実施形態と異なる。なお、本実施形態では、第1の実施形態と同様の構成については説明を省略し、第1の実施形態と異なる点について説明する。

【0038】

本実施形態に係る制御電圧発生回路702において、ラダー抵抗回路は、ラダー抵抗回路の端点の電位を規定する基準電圧と、中間点の電位を規定する基準電圧とを入力可能である。具体的には、図8に示すように、4つの基準電圧(基準電圧1<基準電圧2<基準電圧3<基準電圧4)が複数のラダー抵抗の任意の位置に入力される。そのため、基準電圧1〜4の電圧値に応じて、画面の領域(複数の行配線)ごとに制御電圧の出力特性を変えることができる。図10(e)はラダー抵抗の抵抗値がすべて同じ場合の例である。この場合には、画面の領域ごとに出力特性の傾きを変えることができる。なお、入力される基準電圧の数は4つに限らない(2つ以上であればよい)。

【0039】

基準電圧が1つの場合には、基準電圧を変更したとしても、電圧V1〜Vnの比率は保たれたまま、即ち、制御電圧の出力特性のカーブ形状は維持されたままでしか、制御電圧の出力特性を変化させることができない。例えば、ラダー抵抗値が全て同じ場合である図10(a)の出力特性をもつ制御電圧発生回路では、その傾きを一律に変更することしかできず、図10(e)に示す出力特性を得ることはできない。

【0040】

なお、第1の実施形態のような基準電圧が1つの場合においても、ラダー抵抗の抵抗値を変更すれば、図10(e)の他、様々な制御電圧の出力特性を得ることは可能である。しかしながら、ラダー抵抗は通常ICなどのカスタム部品内に形成されるため、その抵抗

値は容易に変更することができない。変更することができたとしても、部品の再設計が必要となる場合がある。

【0041】

以上述べたように、本実施形態によれば、ラダー抵抗回路は、ラダー抵抗回路の端点の電位を規定する基準電圧と、中間点の電位を規定する基準電圧とを入力可能な構成とされる。それにより、制御電圧発生回路702を変更することなく、制御電圧の出力特性を変更することが可能となる、という効果を得ることができる。そして、同一の可変抵抗回路501で、様々な制御電圧の出力特性を得ることができ、ひいては、様々な抵抗値変化の特性(駆動ラインと抵抗値の関係)を得ることができる。また、列配線104の抵抗値やその分布が変更になった場合にも対応可能となり、非常に好ましい。

【0042】

<第3の実施形態>

第3の実施形態では、制御電圧発生回路の構成が第1の実施形態と異なる。なお、本実施形態では、第1の実施形態と同様の構成については説明を省略し、第1の実施形態と異なる点について説明する。

【0043】

本実施形態に係る制御電圧発生回路702は、図9に示すように、スイッチ制御部802に接続されたメモリ1201を有する。

メモリ1201には、例えば、図11(a)〜(c)に示すような、行配線番号(駆動ライン情報)と選択スイッチ番号の関係を示す1次元ルックアップテーブルデータが格納される。そして、スイッチ制御部802は、入力された駆動ライン情報に対応する選択スイッチ番号をメモリ1201から読み出し、スイッチ群801を制御する。

そして、1次元ルックアップテーブルデータを書き替えることにより、制御電圧の出力特性を変更することが可能となる。

【0044】

なお、第1の実施形態においても、スイッチ群801あるいはスイッチ制御部802を変更すれば、制御電圧の出力特性を変更することができる。しかしながら、スイッチ群801やスイッチ制御部802は通常ICなどのカスタム部品内に形成されているため、それらの構成は容易に変更することができない。変更することができたとしても、部品の再設計が必要となる場合がある。

【0045】

以上述べたように、本実施形態によれば、行配線番号と選択スイッチ番号の関係を示す1次元ルックアップテーブルデータが格納されたメモリが設けられ、該1次元ルックアップテーブルデータを用いてスイッチ群が制御される。それにより、スイッチ群801やスイッチ制御部802を変更することなく、制御電圧の出力特性を変更することが可能となる。具体的には、上記1次元ルックアップテーブルデータを書き替えることにより、容易に制御電圧の出力特性を変更することが可能となる。それにより、同一の可変抵抗回路501で、様々な制御電圧の出力特性を得ることができ、ひいては、様々な抵抗値変化の特性(駆動ラインと抵抗値の関係)を得ることができる。また、列配線104の抵抗値やその分布が変更になった場合にも対応可能となり、非常に好ましい。

【符号の説明】

【0046】

102 列配線駆動回路

103 行配線駆動回路

104 列配線

105 行配線

501 可変抵抗回路

【特許請求の範囲】

【請求項1】

複数の行配線と、複数の列配線と、前記行配線と前記列配線の各交点に配置された複数の画素と、を有する表示パネルと、

前記行配線を順次選択して、選択された行配線に走査信号を出力する行配線駆動回路と、

前記行配線駆動回路によって選択される行配線が変更されるのに同期して、画像データに基づき生成した各列の変調信号を前記複数の列配線に出力する列配線駆動回路と、

前記列配線駆動回路と前記列配線との間の抵抗値を変更する可変抵抗回路と、

を有し、

前記可変抵抗回路は、前記選択された行配線が前記列配線駆動回路に近いときのほうが前記抵抗値が大きくなるように、前記選択された行配線の位置に応じて前記抵抗値を変更する

ことを特徴とする画像表示装置。

【請求項2】

前記可変抵抗回路は、前記選択された行配線に接続された画素と前記列配線駆動回路との間の抵抗値が前記選択された行配線の位置によらず一定となるように、前記列配線駆動回路と前記列配線との間の抵抗値を変更する

ことを特徴とする請求項1に記載の画像表示装置。

【請求項3】

前記可変抵抗回路は、前記選択された行配線の位置に応じて前記抵抗値を段階的に変更する

ことを特徴とする請求項1または2に記載の画像表示装置。

【請求項4】

前記可変抵抗回路は、前記行配線駆動回路によって選択される行配線が変更されるのに同期して前記列配線駆動回路と前記列配線との間の抵抗値を変更する

ことを特徴とする請求項1〜3のいずれか1項に記載の画像表示装置。

【請求項5】

前記可変抵抗回路は、

前記列配線駆動回路と前記列配線との間の抵抗となる電界効果トランジスタを有する可変抵抗部と、

前記可変抵抗部に制御電圧を出力する抵抗値制御部と、

を有し、

前記電界効果トランジスタの抵抗値は、前記変調信号と前記制御電圧との電圧差に応じて設定され、

前記抵抗値制御部は、前記選択された行配線の位置に応じて前記制御電圧を変更する

ことを特徴とする請求項1〜4のいずれか1項に記載の画像表示装置。

【請求項6】

前記抵抗値制御部は、入力された基準電圧を分圧するラダー抵抗回路により構成されている

ことを特徴とする請求項5に記載の画像表示装置。

【請求項7】

前記ラダー抵抗回路は、前記ラダー抵抗回路の端点の電位を規定する基準電圧と、中間点の電位を規定する基準電圧とを入力可能である

ことを特徴とする請求項6に記載の画像表示装置。

【請求項8】

複数の行配線と、複数の列配線と、前記行配線と前記列配線の各交点に配置された複数の画素と、を有する表示パネルと、行配線駆動回路と、列配線駆動回路と、可変抵抗回路と、を有する画像表示装置の制御方法であって、

前記行配線駆動回路が、前記行配線を順次選択して、選択された行配線に走査信号を出

力するステップと、

前記行配線駆動回路によって選択される行配線が変更されるのに同期して、列配線駆動回路が、画像データに基づき生成した各列の変調信号を前記複数の列配線に出力するステップと、

前記可変抵抗回路が、前記選択された行配線が前記列配線駆動回路に近いときのほうが前記抵抗値が大きくなるように、前記選択された行配線の位置に応じて前記列配線駆動回路と前記列配線との間の抵抗値を変更するステップと、

を有することを特徴とする画像表示装置の制御方法。

【請求項1】

複数の行配線と、複数の列配線と、前記行配線と前記列配線の各交点に配置された複数の画素と、を有する表示パネルと、

前記行配線を順次選択して、選択された行配線に走査信号を出力する行配線駆動回路と、

前記行配線駆動回路によって選択される行配線が変更されるのに同期して、画像データに基づき生成した各列の変調信号を前記複数の列配線に出力する列配線駆動回路と、

前記列配線駆動回路と前記列配線との間の抵抗値を変更する可変抵抗回路と、

を有し、

前記可変抵抗回路は、前記選択された行配線が前記列配線駆動回路に近いときのほうが前記抵抗値が大きくなるように、前記選択された行配線の位置に応じて前記抵抗値を変更する

ことを特徴とする画像表示装置。

【請求項2】

前記可変抵抗回路は、前記選択された行配線に接続された画素と前記列配線駆動回路との間の抵抗値が前記選択された行配線の位置によらず一定となるように、前記列配線駆動回路と前記列配線との間の抵抗値を変更する

ことを特徴とする請求項1に記載の画像表示装置。

【請求項3】

前記可変抵抗回路は、前記選択された行配線の位置に応じて前記抵抗値を段階的に変更する

ことを特徴とする請求項1または2に記載の画像表示装置。

【請求項4】

前記可変抵抗回路は、前記行配線駆動回路によって選択される行配線が変更されるのに同期して前記列配線駆動回路と前記列配線との間の抵抗値を変更する

ことを特徴とする請求項1〜3のいずれか1項に記載の画像表示装置。

【請求項5】

前記可変抵抗回路は、

前記列配線駆動回路と前記列配線との間の抵抗となる電界効果トランジスタを有する可変抵抗部と、

前記可変抵抗部に制御電圧を出力する抵抗値制御部と、

を有し、

前記電界効果トランジスタの抵抗値は、前記変調信号と前記制御電圧との電圧差に応じて設定され、

前記抵抗値制御部は、前記選択された行配線の位置に応じて前記制御電圧を変更する

ことを特徴とする請求項1〜4のいずれか1項に記載の画像表示装置。

【請求項6】

前記抵抗値制御部は、入力された基準電圧を分圧するラダー抵抗回路により構成されている

ことを特徴とする請求項5に記載の画像表示装置。

【請求項7】

前記ラダー抵抗回路は、前記ラダー抵抗回路の端点の電位を規定する基準電圧と、中間点の電位を規定する基準電圧とを入力可能である

ことを特徴とする請求項6に記載の画像表示装置。

【請求項8】

複数の行配線と、複数の列配線と、前記行配線と前記列配線の各交点に配置された複数の画素と、を有する表示パネルと、行配線駆動回路と、列配線駆動回路と、可変抵抗回路と、を有する画像表示装置の制御方法であって、

前記行配線駆動回路が、前記行配線を順次選択して、選択された行配線に走査信号を出

力するステップと、

前記行配線駆動回路によって選択される行配線が変更されるのに同期して、列配線駆動回路が、画像データに基づき生成した各列の変調信号を前記複数の列配線に出力するステップと、

前記可変抵抗回路が、前記選択された行配線が前記列配線駆動回路に近いときのほうが前記抵抗値が大きくなるように、前記選択された行配線の位置に応じて前記列配線駆動回路と前記列配線との間の抵抗値を変更するステップと、

を有することを特徴とする画像表示装置の制御方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2012−88550(P2012−88550A)

【公開日】平成24年5月10日(2012.5.10)

【国際特許分類】

【出願番号】特願2010−235521(P2010−235521)

【出願日】平成22年10月20日(2010.10.20)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成24年5月10日(2012.5.10)

【国際特許分類】

【出願日】平成22年10月20日(2010.10.20)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]