画像表示装置

【課題】表示領域内に効率的に画素回路を配置することのできる画像表示装置を提供する。

【解決手段】表示領域を格子状に分割してなる複数の画素領域のそれぞれに配置された発光素子を発光させて画像を表示する画像表示装置であって、複数の画素領域のそれぞれに配置された発光素子の発光を制御するための画素回路が、当該画素領域から隣接する他の画素領域に向けて突出する部分と、隣接する他の画素回路が当該画素領域内に突出する部分と、を有する領域に形成される画像表示装置である。

【解決手段】表示領域を格子状に分割してなる複数の画素領域のそれぞれに配置された発光素子を発光させて画像を表示する画像表示装置であって、複数の画素領域のそれぞれに配置された発光素子の発光を制御するための画素回路が、当該画素領域から隣接する他の画素領域に向けて突出する部分と、隣接する他の画素回路が当該画素領域内に突出する部分と、を有する領域に形成される画像表示装置である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、有機エレクトロルミネッセンス素子などの発光素子を発光させて画素の表示制御を行う画像表示装置に関する。

【背景技術】

【0002】

例えば発光素子として有機エレクトロルミネッセンス素子(以下、有機EL素子という)を備えた有機エレクトロルミネッセンス表示装置(以下、有機EL表示装置という)のように、各画素に設けられた発光素子を発光させることによって、画素の表示制御を行う画像表示装置がある。このような画像表示装置においては、表示領域(表示画面)を格子状に分割してなる複数の画素領域のそれぞれに発光素子が配置される。そして、画素ごとに発光素子の発光を制御することによって、表示領域内に画像が表示される。

【0003】

各画素領域内の発光素子を任意の輝度で発光させるために、画素ごとに薄膜トランジスタ(TFT)や保持容量などを含んだ画素回路が設けられる。制御信号線やデータ信号線を介して外部から供給される信号によって、この画素回路内に輝度情報が書き込まれ、当該書き込まれた輝度情報に応じた輝度で発光素子を発光させる制御が実行される。

【0004】

このような画像表示装置内に実装される画素回路の例が、例えば特許文献1、2、3及び4に開示されている。これらの文献に開示される画像表示装置においては、電源線やデータ信号線、制御信号線などによって基板上に画定される矩形の画素領域それぞれの内部に、当該画素領域に設けられた発光素子の発光を制御するための画素回路が配置されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2001−035663号公報

【特許文献2】特開2001−332383号公報

【特許文献3】特開2001−109405号公報

【特許文献4】特開2004−006341号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上述したような画像表示装置においては、高精細な画像を表示するために、一つ一つの画素領域を小型化することが望まれている。ところが、画素領域が小さくなると、相対的に画素回路を構成する各種の回路素子が画素領域内に占める割合が増えてしまい、特に有機EL表示装置などの画素回路を構成する回路素子が多い画像表示装置においては、これらの回路素子を画素領域内に配置することが困難になってしまう。

【0007】

本発明はこのような実情を考慮してなされたものであって、その目的の一つは、表示領域内に効率的に画素回路を配置することのできる画像表示装置を提供することにある。

【課題を解決するための手段】

【0008】

本出願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

【0009】

(1)表示領域を格子状に分割してなる複数の画素領域のそれぞれに配置された発光素子を発光させて画像を表示する画像表示装置であって、前記複数の画素領域のそれぞれに配置された発光素子の発光を制御するための画素回路が、当該画素領域から隣接する他の画素領域に向けて突出する部分と、隣接する他の画素回路が当該画素領域内に突出する部分と、を有する領域に形成されることを特徴とする画像表示装置。

【0010】

(2)(1)において、前記各発光素子を発光させるための電力を供給する電源線をはさんで互いに隣接する2個の画素回路の一方が、他方の画素回路に対応する画素領域に向けて突出するとともに、前記他方の画素回路が、前記一方の画素回路に対応する画素領域に向けて突出することを特徴とする画像表示装置。

【0011】

(3)(1)において、前記他の画素領域に向けて突出する部分は、前記画素回路を形成する各層の間の位置ずれを吸収するためのマージン部分であることを特徴とする画像表示装置。

【0012】

(4)(1)において、前記他の画素領域に向けて突出する部分は、前記画素回路を構成する薄膜トランジスタのゲート電極であることを特徴とする画像表示装置。

【0013】

(5)(1)において、前記発光素子は、有機エレクトロルミネッセンス素子であって、前記画素回路は、前記有機エレクトロルミネッセンス素子を所与の輝度情報に応じた輝度で発光させる制御を行うことを特徴とする画像表示装置。

【図面の簡単な説明】

【0014】

【図1】本発明の実施の形態に係る画像表示装置において、アレイ基板上に形成される画素回路の等価回路図である。

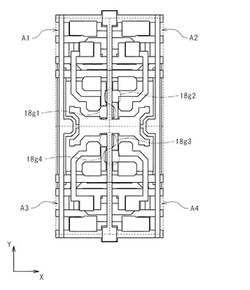

【図2】本発明の実施の形態に係る画像表示装置において、アレイ基板上に形成される画素回路の構造を示す平面図である。

【図3A】アレイ基板上に形成されるポリシリコン層の形状を示す平面図である。

【図3B】アレイ基板上に形成されるゲート配線・ゲート電極層の形状を示す平面図である。

【図3C】アレイ基板上に形成されるアルミニウム配線層の形状を示す平面図である。

【図4】アレイ基板上に形成される画素回路の別の構造を示す平面図である。

【発明を実施するための形態】

【0015】

以下、本発明の実施の形態について、図面を参照しながら詳細に説明する。

【0016】

ここでは、画像表示装置の一態様である有機EL表示装置に本発明を適用した場合の一例について説明する。本実施形態に係る画像表示装置の表示パネルは、発光素子である有機EL素子を含む画素回路が行列状に配置されたアレイ基板と、当該アレイ基板に貼り合わされて有機EL素子を封止する封止基板とを含んで構成されている。アレイ基板上には薄膜トランジスタ(TFT)が形成され、この薄膜トランジスタを介して有機EL素子の発光が制御されることによって、画素毎の表示制御が行われる。

【0017】

図1は、本実施形態に係る画像表示装置においてアレイ基板上に実装される画素回路の等価回路を示す回路図である。前述したように、画像表示装置の表示領域内には、それぞれ発光素子を含んだ複数の画素回路Cが行列状に配置されている。図1においては、そのうち2行2列で計4個の画素回路C1,C2,C3及びC4が示されている。

【0018】

図1に示されるように、各画素回路Cには、データ信号線DAT、選択線SEL、オートゼロ入力線AZ、EL入力線AZB、及び電源線Voledが接続されている。データ信号線DATは、表示画面の上下方向(図1のY軸方向)に沿って延在し、表示画面の左右方向(図1のX軸方向)に沿って互いに並んで複数本配置されている。また、選択線SEL、オートゼロ入力線AZ及びEL入力線AZBは、いずれもX軸方向に沿って延在し、Y軸方向に沿って互いに並んで複数本配置されている。すなわち、X軸方向に一列に並んだ複数の画素回路Cが1つの画素行を構成し、同じ画素行に属する各画素回路Cに対しては、共通する選択線SEL、オートゼロ入力線AZ及びEL入力線AZBが接続される。また、Y軸方向に一列に並んだ複数の画素回路Cが1つの画素列を構成し、同じ画素列に属する各画素回路Cに対しては、共通するデータ信号線DATが接続される。

【0019】

さらに、電源線Voledは表示領域内において格子状に配置されている。すなわち、図中X軸方向及びY軸方向それぞれに複数本の電源線Voledが延在しており、X軸方向に延びる電源線VoledとY軸方向に延びる電源線Voledとは、その交点で電気的に接続されている。この電源線Voledを介して、各画素回路C内の発光素子を駆動するための電力が供給される。このように電源線Voledが格子状に配置されることによって、電源線Voledの電気抵抗に起因する、電源線Voledを介して各画素に供給される電圧の降下を抑えることができる。本実施形態では、各方向に延びる複数本の電源線Voledは、2行の画素行または2列の画素列ごとに1本ずつ間隔をおいて配置されている。

【0020】

なお、図1においては、2行2列の計4個の画素回路Cのみが示されているが、実際には表示パネルを構成する画素数に応じた数の画素回路Cがアレイ基板上に行列状に配置される。例えばデジタルスチルカメラ等に用いられる水平方向640画素、垂直方向480画素の解像度の表示パネルの場合、各画素は赤(R)、緑(G)、青(B)それぞれの色に対応する3つのサブ画素から構成され、各サブ画素に対応して画素回路Cが形成される。したがって、縦方向に480行、横方向に640×3=960列で計(480×640×3)個の画素回路Cがアレイ基板上に形成されることとなる。なお、以降の説明においては、1個の画素回路Cに対応するサブ画素のそれぞれを、単に画素と表記する。

【0021】

図1に示されるように、各画素の画素回路Cは、発光素子としての有機EL素子12、共通電極14、ELスイッチ16、駆動TFT18、オートゼロスイッチ20、入力TFT22、キャンセルコンデンサ24、及び記憶コンデンサ26を含んで構成されている。

【0022】

各画素回路Cには、発光素子として有機EL素子12が設けられており、そのカソード端は共通電極14に接続される。共通電極14は、その電位が本実施形態に係る画像表示装置において基準となる基準電位に設定された電極である。また、有機EL素子12のアノード端は、TFTによって構成されるELスイッチ16の一端に接続され、ELスイッチ16の他端は、駆動TFT18を介して電源線Voledに接続される。駆動TFT18及びELスイッチ16がともにオン状態になると、電源線Voledから共通電極14に向かって有機EL素子12内に電流が流れ、これによって有機EL素子12が発光する。

【0023】

さらに、ELスイッチ16の他端と駆動TFT18のゲート電極との間には、TFTによって構成されるオートゼロスイッチ20が接続される。また、駆動TFT18の電源線Voledに接続される側の一端と駆動TFT18のゲート電極との間には、記憶コンデンサ26が接続される。さらに、駆動TFT18のゲート電極には、キャンセルコンデンサ24の一端も接続されており、キャンセルコンデンサ24の他端は、入力TFT22を介してデータ信号線DATに接続される。また、ELスイッチ16のゲート電極はEL入力線AZBに、オートゼロスイッチ20のゲート電極はオートゼロ入力線AZに、入力TFT22のゲート電極は選択線SELに、それぞれ接続されている。これらの制御信号線からVH(高電圧)及びVL(低電圧)の二値の電圧レベルの制御信号が入力されることによって、各TFTのオン/オフが切り替えられる。

【0024】

ここで、本実施形態における有機EL素子12の発光制御の具体例について、説明する。まず、選択線SELから入力TFT22をオンにする制御信号が入力されるとともに、オートゼロスイッチ20をオン、ELスイッチ16をオフにする制御信号が、それぞれオートゼロ入力線AZ及びEL入力線AZBから入力される。これにより、データ信号線DATに入力されているオフレベルの信号電圧がキャンセルコンデンサ24の一端に入力されるとともに、オートゼロスイッチ20がオン状態になることで駆動TFT18がダイオード接続され、そのゲート電圧は電源線Voledの印加電圧に応じた値にリセットされる。

【0025】

その後、オートゼロスイッチ20をオフにする制御信号がオートゼロ入力線AZから入力されるとともに、データ信号線DATから所与の輝度情報に応じた電圧レベルの信号が入力される。これによって、駆動TFT18のゲート電圧は、リセット時の電圧を基準としてデータ信号線DATから入力される電圧レベルに応じた電圧だけ変化する。さらに入力TFT22をオフにする制御信号が選択線SELから入力されると、駆動TFT18のゲート電圧はこの変化した電圧を維持することになり、記憶コンデンサ26に輝度情報に応じた電荷が蓄積された状態(すなわち、画素回路Cに輝度情報が書き込まれた状態)になる。さらに、ELスイッチ16をオンにする制御信号がEL入力線AZBから入力されることにより、駆動TFT18によって駆動される信号電流がELスイッチ16を介して有機EL素子12に流れ、有機EL素子12が発光する。こうして、各画素回路Cは、駆動TFT18及びELスイッチ16をオンにすることで、データ信号線DATを介して設定された輝度情報に応じた輝度で有機EL素子12を発光させることができる。

【0026】

次に、本実施形態においてアレイ基板上に実装される画素回路の構造について、図2の平面図を用いて説明する。図2は、図1の等価回路に相当する4画素分の画素回路を構成するTFTが形成されたアレイ基板を、平面的に見た様子を模式的に示す図である。この図においては、画素回路に含まれる各TFT及びコンデンサ、並びに画素回路に接続される各配線を構成するポリシリコン層、ゲート配線・ゲート電極層、及びアルミニウム配線層が順に積層された様子を示している。なお、図には表れていないが、各層の間には保護膜や絶縁膜などが形成される。この図に示される状態から、さらに平坦化膜、反射層、並びに有機EL素子12を構成する陽極、有機EL層及び陰極などが形成されることによって、アレイ基板が製造される。その後、N2環境下で封止基板をアレイ基板と対向するように取り付けることにより、表示パネルが製造される。

【0027】

図2に示されるポリシリコン層、ゲート配線・ゲート電極層、及びアルミニウム配線層それぞれの形状が、図3A、図3B及び図3Cに示されている。具体的に、これらの各図はいずれも図2と同様に4画素分の画素回路を構成する各層の形状を示す平面図であって、図3Aはポリシリコン層の形状を、図3Bはゲート配線・ゲート電極層の形状を、図3Cはアルミニウム配線層の形状を、それぞれ示している。

【0028】

ポリシリコン層は、ポリシリコン(多結晶シリコン)を材料として構成され、画素回路Cを構成する各TFTの半導体層として機能する。また、ゲート配線・ゲート電極層は、例えばMoWなどの金属材料によって構成され、オートゼロ入力線AZ、EL入力線AZB及び選択線SELの各配線と、X軸方向に延在する電源線Voled、並びに各TFTのゲート電極として機能する。さらに、アルミニウム配線層は、アルミニウムによって構成され、データ信号線DAT及びY軸方向に延在する電源線Voled、並びに各TFTのソース及びドレイン電極として機能する。

【0029】

本実施形態において、各画素の画素領域は、表示領域全体を格子状に分割してなる矩形の領域になっている。この画素領域ごとに有機EL素子12が配置され、有機EL素子12が発光することによって、当該画素領域が所与の色及び輝度で点灯する。これによって、全体として外部から入力される映像信号に応じた画像が表示領域に表示される。図2、及び図3A〜図3Cのそれぞれには、2行2列で計4個の画素領域A1,A2,A3及びA4の平面図が示されており、各図における破線が画素領域の境界を示している。また、画素領域A1,A2,A3及びA4それぞれに配置された有機EL素子12の発光が、それぞれ画素回路C1,C2,C3及びC4によって制御される。すなわち、画素領域A1,A2,A3及びA4のそれぞれに、画素回路C1,C2,C3及びC4が対応している。

【0030】

さらに、本実施形態では、複数の画素領域Aのそれぞれに配置された有機EL素子12の発光を制御するための画素回路Cが、当該画素領域Aから隣接する他の画素領域Aに向けて突出する部分と、隣接する他の画素回路Cが当該画素領域A内に突出することによって凹んだ部分と、を有する領域内に形成されている。具体的には、図2にも示されるように、Y軸方向に沿って延在する電源線Voledを挟んで互いに隣接する2個の画素回路C1及びC2は、この電源線Voledを共有しており、これらの画素回路のうち、一方の画素回路(ここでは画素回路C1とする)が、他方の画素回路C2に対応する画素領域A2に向けて突出している。逆に画素回路C2は、画素回路C1に対応する画素領域A1に向けて突出した領域内に形成されている。また、画素回路C3及びC4にも、同様の関係が成立している。

【0031】

このように、画素回路Cの一部を、当該画素回路Cに対応する画素領域Aに隣接する画素領域Aに向けて突出させることによって、画素回路Cのレイアウトの自由度を向上させ、画素回路Cを効率的に表示領域内に配置することが可能となる。なお、図2に示されるように、Y軸方向に延在する電源線Voledをはさんで隣接する2個の画素回路C同士は、互いに隣接する画素領域Aに向けて突出する部分を除いて、線対称の構造を有するように形成されている。

【0032】

ここで、各画素回路Cにおいて隣接する画素領域Aに向けて突出する部分には、駆動TFT18のゲート電極18gが形成されている。具体例として、画素回路C1の駆動TFT18のゲート電極18g1は、画素領域A1と画素領域A2の間に配置された電源線Voledを超えて、隣接する画素領域A2に向けて突出している。一方、画素回路C2の駆動TFT18のゲート電極18g2は、やはり電源線Voledを超えて画素領域A1に向けて突出している。同様に、画素回路C3の駆動TFT18のゲート電極18g3は、隣接する画素領域A4に向けて突出しており、画素回路C4の駆動TFT18のゲート電極18g4は、画素領域A3に向けて突出している。

【0033】

さらに、この隣接する画素領域Aに向けて突出する部分は、ゲート電極18gの中でも、設計上は駆動TFT18の半導体層と重ならないマージン部分になっている。このようなマージン部分は、実際にアレイ基板上にポリシリコン層やゲート配線・ゲート電極層を形成した際に、仮にこれらの層の間に位置ずれが生じても各TFTが正常動作するようにするために、設けられている。本実施形態では、ある画素回路Cの構成部分のうち隣接する画素領域Aに向けて突出する部分をこのようなマージン部分とすることで、当該画素回路Cが隣接する画素領域Aに対応する画素回路Cの動作による影響を受けないようになっている。

【0034】

また、もし万一位置ずれによって駆動TFT18のゲート電極18gが隣接する画素回路Cのポリシリコン層と重なったとしても、当該駆動TFT18の動作によって隣接する画素回路Cの動作に影響を及ぼす心配はない。なぜなら、駆動TFT18は、前述したように有機EL素子12の発光と非発光とを切り替えるスイッチ素子として機能しており、ゲート電極18gは印加される電圧によってこのスイッチ素子のオン/オフを切り替える役割を果たしている。そのため、例えばゲート電極18g1が隣接する画素回路C2内の駆動TFT18の半導体層にわずかな影響を及ぼしたとしても、結局のところゲート電極18g2に印加される電圧によって画素回路C2内の駆動TFT18のオン/オフが切り替えられることに変わりはないからである。このように、例えばデータ信号線DATから入力される輝度情報に応じた電圧のように、その電圧レベルの程度が問題となる部分ではなく、スイッチ素子のオン/オフ制御を担う部分のように電圧がハイレベルかローレベルかだけを問題とする端子部分を、隣接する画素領域Aに向けて突出する部分とすることで、隣接する画素領域Aに突出する部分が当該隣接する画素領域Aに対応する画素回路Cに影響を及ぼすおそれを低減できる。

【0035】

以上説明したように、本実施形態に係る画像表示装置によれば、画素回路を対応する画素領域から突出した部分を含んだ領域に形成することによって、画素回路を表示領域内に効率的に配置することが可能となる。

【0036】

以上説明した本実施形態に係る画像表示装置は、パソコン用ディスプレイ、TV放送受信用ディスプレイ、公告表示用ディスプレイ等の各種の情報表示用の表示装置として採用できる。また、デジタルスチルカメラ、ビデオカメラ、カーナビゲーションシステム、カーオーディオ、ゲーム機器、携帯情報端末など、各種の電子機器の表示部として利用することも可能である。

【0037】

なお、本発明の実施の形態は以上説明したものに限られない。例えば、本発明の実施の形態に係る画像表示装置における画素回路の構造は、図2と異なるものであってもよい。例えば図4には、図2とは別の、アレイ基板上に形成される画素回路の構造が示されている。図2においては、X軸方向に延在する画素領域Aの境界線に対して、当該境界線を挟んで上下に配置される画素回路同士が線対称に形成されている。これに対して、図4においては、図2とはゲート配線・ゲート電極層の形状が異なっており、X軸方向及びY軸方向に延在する画素領域Aの境界線の交点に対して、当該交点を挟んで斜め方向に対向する画素回路同士が点対称に形成されている。この図4の例においても、各画素回路Cにおいて駆動TFT18のゲート電極18gが隣接する画素領域A内に突出して形成されている。

【0038】

また、以上の説明においては、発光素子として有機EL素子を用いることとしたが、これに限らず、本発明の実施の形態に係る画像表示装置は、例えば無機EL素子やFED(Field-Emission Device)など、各種の発光素子を用いた画像表示装置であってよい。

【符号の説明】

【0039】

12 有機EL素子、14 共通電極、16 ELスイッチ、18 駆動TFT、18g ゲート電極、20 オートゼロスイッチ、22 入力TFT、24 キャンセルコンデンサ、26 記憶コンデンサ、A1〜A4 画素領域、AZ オートゼロ入力線、AZB EL入力線、C1〜C4 画素回路、DAT データ信号線、SEL 選択線、Voled 電源線。

【技術分野】

【0001】

本発明は、有機エレクトロルミネッセンス素子などの発光素子を発光させて画素の表示制御を行う画像表示装置に関する。

【背景技術】

【0002】

例えば発光素子として有機エレクトロルミネッセンス素子(以下、有機EL素子という)を備えた有機エレクトロルミネッセンス表示装置(以下、有機EL表示装置という)のように、各画素に設けられた発光素子を発光させることによって、画素の表示制御を行う画像表示装置がある。このような画像表示装置においては、表示領域(表示画面)を格子状に分割してなる複数の画素領域のそれぞれに発光素子が配置される。そして、画素ごとに発光素子の発光を制御することによって、表示領域内に画像が表示される。

【0003】

各画素領域内の発光素子を任意の輝度で発光させるために、画素ごとに薄膜トランジスタ(TFT)や保持容量などを含んだ画素回路が設けられる。制御信号線やデータ信号線を介して外部から供給される信号によって、この画素回路内に輝度情報が書き込まれ、当該書き込まれた輝度情報に応じた輝度で発光素子を発光させる制御が実行される。

【0004】

このような画像表示装置内に実装される画素回路の例が、例えば特許文献1、2、3及び4に開示されている。これらの文献に開示される画像表示装置においては、電源線やデータ信号線、制御信号線などによって基板上に画定される矩形の画素領域それぞれの内部に、当該画素領域に設けられた発光素子の発光を制御するための画素回路が配置されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2001−035663号公報

【特許文献2】特開2001−332383号公報

【特許文献3】特開2001−109405号公報

【特許文献4】特開2004−006341号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

上述したような画像表示装置においては、高精細な画像を表示するために、一つ一つの画素領域を小型化することが望まれている。ところが、画素領域が小さくなると、相対的に画素回路を構成する各種の回路素子が画素領域内に占める割合が増えてしまい、特に有機EL表示装置などの画素回路を構成する回路素子が多い画像表示装置においては、これらの回路素子を画素領域内に配置することが困難になってしまう。

【0007】

本発明はこのような実情を考慮してなされたものであって、その目的の一つは、表示領域内に効率的に画素回路を配置することのできる画像表示装置を提供することにある。

【課題を解決するための手段】

【0008】

本出願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

【0009】

(1)表示領域を格子状に分割してなる複数の画素領域のそれぞれに配置された発光素子を発光させて画像を表示する画像表示装置であって、前記複数の画素領域のそれぞれに配置された発光素子の発光を制御するための画素回路が、当該画素領域から隣接する他の画素領域に向けて突出する部分と、隣接する他の画素回路が当該画素領域内に突出する部分と、を有する領域に形成されることを特徴とする画像表示装置。

【0010】

(2)(1)において、前記各発光素子を発光させるための電力を供給する電源線をはさんで互いに隣接する2個の画素回路の一方が、他方の画素回路に対応する画素領域に向けて突出するとともに、前記他方の画素回路が、前記一方の画素回路に対応する画素領域に向けて突出することを特徴とする画像表示装置。

【0011】

(3)(1)において、前記他の画素領域に向けて突出する部分は、前記画素回路を形成する各層の間の位置ずれを吸収するためのマージン部分であることを特徴とする画像表示装置。

【0012】

(4)(1)において、前記他の画素領域に向けて突出する部分は、前記画素回路を構成する薄膜トランジスタのゲート電極であることを特徴とする画像表示装置。

【0013】

(5)(1)において、前記発光素子は、有機エレクトロルミネッセンス素子であって、前記画素回路は、前記有機エレクトロルミネッセンス素子を所与の輝度情報に応じた輝度で発光させる制御を行うことを特徴とする画像表示装置。

【図面の簡単な説明】

【0014】

【図1】本発明の実施の形態に係る画像表示装置において、アレイ基板上に形成される画素回路の等価回路図である。

【図2】本発明の実施の形態に係る画像表示装置において、アレイ基板上に形成される画素回路の構造を示す平面図である。

【図3A】アレイ基板上に形成されるポリシリコン層の形状を示す平面図である。

【図3B】アレイ基板上に形成されるゲート配線・ゲート電極層の形状を示す平面図である。

【図3C】アレイ基板上に形成されるアルミニウム配線層の形状を示す平面図である。

【図4】アレイ基板上に形成される画素回路の別の構造を示す平面図である。

【発明を実施するための形態】

【0015】

以下、本発明の実施の形態について、図面を参照しながら詳細に説明する。

【0016】

ここでは、画像表示装置の一態様である有機EL表示装置に本発明を適用した場合の一例について説明する。本実施形態に係る画像表示装置の表示パネルは、発光素子である有機EL素子を含む画素回路が行列状に配置されたアレイ基板と、当該アレイ基板に貼り合わされて有機EL素子を封止する封止基板とを含んで構成されている。アレイ基板上には薄膜トランジスタ(TFT)が形成され、この薄膜トランジスタを介して有機EL素子の発光が制御されることによって、画素毎の表示制御が行われる。

【0017】

図1は、本実施形態に係る画像表示装置においてアレイ基板上に実装される画素回路の等価回路を示す回路図である。前述したように、画像表示装置の表示領域内には、それぞれ発光素子を含んだ複数の画素回路Cが行列状に配置されている。図1においては、そのうち2行2列で計4個の画素回路C1,C2,C3及びC4が示されている。

【0018】

図1に示されるように、各画素回路Cには、データ信号線DAT、選択線SEL、オートゼロ入力線AZ、EL入力線AZB、及び電源線Voledが接続されている。データ信号線DATは、表示画面の上下方向(図1のY軸方向)に沿って延在し、表示画面の左右方向(図1のX軸方向)に沿って互いに並んで複数本配置されている。また、選択線SEL、オートゼロ入力線AZ及びEL入力線AZBは、いずれもX軸方向に沿って延在し、Y軸方向に沿って互いに並んで複数本配置されている。すなわち、X軸方向に一列に並んだ複数の画素回路Cが1つの画素行を構成し、同じ画素行に属する各画素回路Cに対しては、共通する選択線SEL、オートゼロ入力線AZ及びEL入力線AZBが接続される。また、Y軸方向に一列に並んだ複数の画素回路Cが1つの画素列を構成し、同じ画素列に属する各画素回路Cに対しては、共通するデータ信号線DATが接続される。

【0019】

さらに、電源線Voledは表示領域内において格子状に配置されている。すなわち、図中X軸方向及びY軸方向それぞれに複数本の電源線Voledが延在しており、X軸方向に延びる電源線VoledとY軸方向に延びる電源線Voledとは、その交点で電気的に接続されている。この電源線Voledを介して、各画素回路C内の発光素子を駆動するための電力が供給される。このように電源線Voledが格子状に配置されることによって、電源線Voledの電気抵抗に起因する、電源線Voledを介して各画素に供給される電圧の降下を抑えることができる。本実施形態では、各方向に延びる複数本の電源線Voledは、2行の画素行または2列の画素列ごとに1本ずつ間隔をおいて配置されている。

【0020】

なお、図1においては、2行2列の計4個の画素回路Cのみが示されているが、実際には表示パネルを構成する画素数に応じた数の画素回路Cがアレイ基板上に行列状に配置される。例えばデジタルスチルカメラ等に用いられる水平方向640画素、垂直方向480画素の解像度の表示パネルの場合、各画素は赤(R)、緑(G)、青(B)それぞれの色に対応する3つのサブ画素から構成され、各サブ画素に対応して画素回路Cが形成される。したがって、縦方向に480行、横方向に640×3=960列で計(480×640×3)個の画素回路Cがアレイ基板上に形成されることとなる。なお、以降の説明においては、1個の画素回路Cに対応するサブ画素のそれぞれを、単に画素と表記する。

【0021】

図1に示されるように、各画素の画素回路Cは、発光素子としての有機EL素子12、共通電極14、ELスイッチ16、駆動TFT18、オートゼロスイッチ20、入力TFT22、キャンセルコンデンサ24、及び記憶コンデンサ26を含んで構成されている。

【0022】

各画素回路Cには、発光素子として有機EL素子12が設けられており、そのカソード端は共通電極14に接続される。共通電極14は、その電位が本実施形態に係る画像表示装置において基準となる基準電位に設定された電極である。また、有機EL素子12のアノード端は、TFTによって構成されるELスイッチ16の一端に接続され、ELスイッチ16の他端は、駆動TFT18を介して電源線Voledに接続される。駆動TFT18及びELスイッチ16がともにオン状態になると、電源線Voledから共通電極14に向かって有機EL素子12内に電流が流れ、これによって有機EL素子12が発光する。

【0023】

さらに、ELスイッチ16の他端と駆動TFT18のゲート電極との間には、TFTによって構成されるオートゼロスイッチ20が接続される。また、駆動TFT18の電源線Voledに接続される側の一端と駆動TFT18のゲート電極との間には、記憶コンデンサ26が接続される。さらに、駆動TFT18のゲート電極には、キャンセルコンデンサ24の一端も接続されており、キャンセルコンデンサ24の他端は、入力TFT22を介してデータ信号線DATに接続される。また、ELスイッチ16のゲート電極はEL入力線AZBに、オートゼロスイッチ20のゲート電極はオートゼロ入力線AZに、入力TFT22のゲート電極は選択線SELに、それぞれ接続されている。これらの制御信号線からVH(高電圧)及びVL(低電圧)の二値の電圧レベルの制御信号が入力されることによって、各TFTのオン/オフが切り替えられる。

【0024】

ここで、本実施形態における有機EL素子12の発光制御の具体例について、説明する。まず、選択線SELから入力TFT22をオンにする制御信号が入力されるとともに、オートゼロスイッチ20をオン、ELスイッチ16をオフにする制御信号が、それぞれオートゼロ入力線AZ及びEL入力線AZBから入力される。これにより、データ信号線DATに入力されているオフレベルの信号電圧がキャンセルコンデンサ24の一端に入力されるとともに、オートゼロスイッチ20がオン状態になることで駆動TFT18がダイオード接続され、そのゲート電圧は電源線Voledの印加電圧に応じた値にリセットされる。

【0025】

その後、オートゼロスイッチ20をオフにする制御信号がオートゼロ入力線AZから入力されるとともに、データ信号線DATから所与の輝度情報に応じた電圧レベルの信号が入力される。これによって、駆動TFT18のゲート電圧は、リセット時の電圧を基準としてデータ信号線DATから入力される電圧レベルに応じた電圧だけ変化する。さらに入力TFT22をオフにする制御信号が選択線SELから入力されると、駆動TFT18のゲート電圧はこの変化した電圧を維持することになり、記憶コンデンサ26に輝度情報に応じた電荷が蓄積された状態(すなわち、画素回路Cに輝度情報が書き込まれた状態)になる。さらに、ELスイッチ16をオンにする制御信号がEL入力線AZBから入力されることにより、駆動TFT18によって駆動される信号電流がELスイッチ16を介して有機EL素子12に流れ、有機EL素子12が発光する。こうして、各画素回路Cは、駆動TFT18及びELスイッチ16をオンにすることで、データ信号線DATを介して設定された輝度情報に応じた輝度で有機EL素子12を発光させることができる。

【0026】

次に、本実施形態においてアレイ基板上に実装される画素回路の構造について、図2の平面図を用いて説明する。図2は、図1の等価回路に相当する4画素分の画素回路を構成するTFTが形成されたアレイ基板を、平面的に見た様子を模式的に示す図である。この図においては、画素回路に含まれる各TFT及びコンデンサ、並びに画素回路に接続される各配線を構成するポリシリコン層、ゲート配線・ゲート電極層、及びアルミニウム配線層が順に積層された様子を示している。なお、図には表れていないが、各層の間には保護膜や絶縁膜などが形成される。この図に示される状態から、さらに平坦化膜、反射層、並びに有機EL素子12を構成する陽極、有機EL層及び陰極などが形成されることによって、アレイ基板が製造される。その後、N2環境下で封止基板をアレイ基板と対向するように取り付けることにより、表示パネルが製造される。

【0027】

図2に示されるポリシリコン層、ゲート配線・ゲート電極層、及びアルミニウム配線層それぞれの形状が、図3A、図3B及び図3Cに示されている。具体的に、これらの各図はいずれも図2と同様に4画素分の画素回路を構成する各層の形状を示す平面図であって、図3Aはポリシリコン層の形状を、図3Bはゲート配線・ゲート電極層の形状を、図3Cはアルミニウム配線層の形状を、それぞれ示している。

【0028】

ポリシリコン層は、ポリシリコン(多結晶シリコン)を材料として構成され、画素回路Cを構成する各TFTの半導体層として機能する。また、ゲート配線・ゲート電極層は、例えばMoWなどの金属材料によって構成され、オートゼロ入力線AZ、EL入力線AZB及び選択線SELの各配線と、X軸方向に延在する電源線Voled、並びに各TFTのゲート電極として機能する。さらに、アルミニウム配線層は、アルミニウムによって構成され、データ信号線DAT及びY軸方向に延在する電源線Voled、並びに各TFTのソース及びドレイン電極として機能する。

【0029】

本実施形態において、各画素の画素領域は、表示領域全体を格子状に分割してなる矩形の領域になっている。この画素領域ごとに有機EL素子12が配置され、有機EL素子12が発光することによって、当該画素領域が所与の色及び輝度で点灯する。これによって、全体として外部から入力される映像信号に応じた画像が表示領域に表示される。図2、及び図3A〜図3Cのそれぞれには、2行2列で計4個の画素領域A1,A2,A3及びA4の平面図が示されており、各図における破線が画素領域の境界を示している。また、画素領域A1,A2,A3及びA4それぞれに配置された有機EL素子12の発光が、それぞれ画素回路C1,C2,C3及びC4によって制御される。すなわち、画素領域A1,A2,A3及びA4のそれぞれに、画素回路C1,C2,C3及びC4が対応している。

【0030】

さらに、本実施形態では、複数の画素領域Aのそれぞれに配置された有機EL素子12の発光を制御するための画素回路Cが、当該画素領域Aから隣接する他の画素領域Aに向けて突出する部分と、隣接する他の画素回路Cが当該画素領域A内に突出することによって凹んだ部分と、を有する領域内に形成されている。具体的には、図2にも示されるように、Y軸方向に沿って延在する電源線Voledを挟んで互いに隣接する2個の画素回路C1及びC2は、この電源線Voledを共有しており、これらの画素回路のうち、一方の画素回路(ここでは画素回路C1とする)が、他方の画素回路C2に対応する画素領域A2に向けて突出している。逆に画素回路C2は、画素回路C1に対応する画素領域A1に向けて突出した領域内に形成されている。また、画素回路C3及びC4にも、同様の関係が成立している。

【0031】

このように、画素回路Cの一部を、当該画素回路Cに対応する画素領域Aに隣接する画素領域Aに向けて突出させることによって、画素回路Cのレイアウトの自由度を向上させ、画素回路Cを効率的に表示領域内に配置することが可能となる。なお、図2に示されるように、Y軸方向に延在する電源線Voledをはさんで隣接する2個の画素回路C同士は、互いに隣接する画素領域Aに向けて突出する部分を除いて、線対称の構造を有するように形成されている。

【0032】

ここで、各画素回路Cにおいて隣接する画素領域Aに向けて突出する部分には、駆動TFT18のゲート電極18gが形成されている。具体例として、画素回路C1の駆動TFT18のゲート電極18g1は、画素領域A1と画素領域A2の間に配置された電源線Voledを超えて、隣接する画素領域A2に向けて突出している。一方、画素回路C2の駆動TFT18のゲート電極18g2は、やはり電源線Voledを超えて画素領域A1に向けて突出している。同様に、画素回路C3の駆動TFT18のゲート電極18g3は、隣接する画素領域A4に向けて突出しており、画素回路C4の駆動TFT18のゲート電極18g4は、画素領域A3に向けて突出している。

【0033】

さらに、この隣接する画素領域Aに向けて突出する部分は、ゲート電極18gの中でも、設計上は駆動TFT18の半導体層と重ならないマージン部分になっている。このようなマージン部分は、実際にアレイ基板上にポリシリコン層やゲート配線・ゲート電極層を形成した際に、仮にこれらの層の間に位置ずれが生じても各TFTが正常動作するようにするために、設けられている。本実施形態では、ある画素回路Cの構成部分のうち隣接する画素領域Aに向けて突出する部分をこのようなマージン部分とすることで、当該画素回路Cが隣接する画素領域Aに対応する画素回路Cの動作による影響を受けないようになっている。

【0034】

また、もし万一位置ずれによって駆動TFT18のゲート電極18gが隣接する画素回路Cのポリシリコン層と重なったとしても、当該駆動TFT18の動作によって隣接する画素回路Cの動作に影響を及ぼす心配はない。なぜなら、駆動TFT18は、前述したように有機EL素子12の発光と非発光とを切り替えるスイッチ素子として機能しており、ゲート電極18gは印加される電圧によってこのスイッチ素子のオン/オフを切り替える役割を果たしている。そのため、例えばゲート電極18g1が隣接する画素回路C2内の駆動TFT18の半導体層にわずかな影響を及ぼしたとしても、結局のところゲート電極18g2に印加される電圧によって画素回路C2内の駆動TFT18のオン/オフが切り替えられることに変わりはないからである。このように、例えばデータ信号線DATから入力される輝度情報に応じた電圧のように、その電圧レベルの程度が問題となる部分ではなく、スイッチ素子のオン/オフ制御を担う部分のように電圧がハイレベルかローレベルかだけを問題とする端子部分を、隣接する画素領域Aに向けて突出する部分とすることで、隣接する画素領域Aに突出する部分が当該隣接する画素領域Aに対応する画素回路Cに影響を及ぼすおそれを低減できる。

【0035】

以上説明したように、本実施形態に係る画像表示装置によれば、画素回路を対応する画素領域から突出した部分を含んだ領域に形成することによって、画素回路を表示領域内に効率的に配置することが可能となる。

【0036】

以上説明した本実施形態に係る画像表示装置は、パソコン用ディスプレイ、TV放送受信用ディスプレイ、公告表示用ディスプレイ等の各種の情報表示用の表示装置として採用できる。また、デジタルスチルカメラ、ビデオカメラ、カーナビゲーションシステム、カーオーディオ、ゲーム機器、携帯情報端末など、各種の電子機器の表示部として利用することも可能である。

【0037】

なお、本発明の実施の形態は以上説明したものに限られない。例えば、本発明の実施の形態に係る画像表示装置における画素回路の構造は、図2と異なるものであってもよい。例えば図4には、図2とは別の、アレイ基板上に形成される画素回路の構造が示されている。図2においては、X軸方向に延在する画素領域Aの境界線に対して、当該境界線を挟んで上下に配置される画素回路同士が線対称に形成されている。これに対して、図4においては、図2とはゲート配線・ゲート電極層の形状が異なっており、X軸方向及びY軸方向に延在する画素領域Aの境界線の交点に対して、当該交点を挟んで斜め方向に対向する画素回路同士が点対称に形成されている。この図4の例においても、各画素回路Cにおいて駆動TFT18のゲート電極18gが隣接する画素領域A内に突出して形成されている。

【0038】

また、以上の説明においては、発光素子として有機EL素子を用いることとしたが、これに限らず、本発明の実施の形態に係る画像表示装置は、例えば無機EL素子やFED(Field-Emission Device)など、各種の発光素子を用いた画像表示装置であってよい。

【符号の説明】

【0039】

12 有機EL素子、14 共通電極、16 ELスイッチ、18 駆動TFT、18g ゲート電極、20 オートゼロスイッチ、22 入力TFT、24 キャンセルコンデンサ、26 記憶コンデンサ、A1〜A4 画素領域、AZ オートゼロ入力線、AZB EL入力線、C1〜C4 画素回路、DAT データ信号線、SEL 選択線、Voled 電源線。

【特許請求の範囲】

【請求項1】

表示領域を格子状に分割してなる複数の画素領域のそれぞれに配置された発光素子を発光させて画像を表示する画像表示装置であって、

前記複数の画素領域のそれぞれに配置された発光素子の発光を制御するための画素回路が、当該画素領域から隣接する他の画素領域に向けて突出する部分と、隣接する他の画素回路が当該画素領域内に突出する部分と、を有する領域に形成される

ことを特徴とする画像表示装置。

【請求項2】

請求項1記載の画像表示装置において、

前記各発光素子を発光させるための電力を供給する電源線をはさんで互いに隣接する2個の画素回路の一方が、他方の画素回路に対応する画素領域に向けて突出するとともに、前記他方の画素回路が、前記一方の画素回路に対応する画素領域に向けて突出する

ことを特徴とする画像表示装置。

【請求項3】

請求項1記載の画像表示装置において、

前記他の画素領域に向けて突出する部分は、前記画素回路を形成する各層の間の位置ずれを吸収するためのマージン部分である

ことを特徴とする画像表示装置。

【請求項4】

請求項1記載の画像表示装置において、

前記他の画素領域に向けて突出する部分は、前記画素回路を構成する薄膜トランジスタのゲート電極である

ことを特徴とする画像表示装置。

【請求項5】

請求項1記載の画像表示装置において、

前記発光素子は、有機エレクトロルミネッセンス素子であって、

前記画素回路は、前記有機エレクトロルミネッセンス素子を所与の輝度情報に応じた輝度で発光させる制御を行う

ことを特徴とする画像表示装置。

【請求項1】

表示領域を格子状に分割してなる複数の画素領域のそれぞれに配置された発光素子を発光させて画像を表示する画像表示装置であって、

前記複数の画素領域のそれぞれに配置された発光素子の発光を制御するための画素回路が、当該画素領域から隣接する他の画素領域に向けて突出する部分と、隣接する他の画素回路が当該画素領域内に突出する部分と、を有する領域に形成される

ことを特徴とする画像表示装置。

【請求項2】

請求項1記載の画像表示装置において、

前記各発光素子を発光させるための電力を供給する電源線をはさんで互いに隣接する2個の画素回路の一方が、他方の画素回路に対応する画素領域に向けて突出するとともに、前記他方の画素回路が、前記一方の画素回路に対応する画素領域に向けて突出する

ことを特徴とする画像表示装置。

【請求項3】

請求項1記載の画像表示装置において、

前記他の画素領域に向けて突出する部分は、前記画素回路を形成する各層の間の位置ずれを吸収するためのマージン部分である

ことを特徴とする画像表示装置。

【請求項4】

請求項1記載の画像表示装置において、

前記他の画素領域に向けて突出する部分は、前記画素回路を構成する薄膜トランジスタのゲート電極である

ことを特徴とする画像表示装置。

【請求項5】

請求項1記載の画像表示装置において、

前記発光素子は、有機エレクトロルミネッセンス素子であって、

前記画素回路は、前記有機エレクトロルミネッセンス素子を所与の輝度情報に応じた輝度で発光させる制御を行う

ことを特徴とする画像表示装置。

【図1】

【図2】

【図3A】

【図3B】

【図3C】

【図4】

【図2】

【図3A】

【図3B】

【図3C】

【図4】

【公開番号】特開2010−210905(P2010−210905A)

【公開日】平成22年9月24日(2010.9.24)

【国際特許分類】

【出願番号】特願2009−56501(P2009−56501)

【出願日】平成21年3月10日(2009.3.10)

【出願人】(502356528)株式会社 日立ディスプレイズ (2,552)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成22年9月24日(2010.9.24)

【国際特許分類】

【出願日】平成21年3月10日(2009.3.10)

【出願人】(502356528)株式会社 日立ディスプレイズ (2,552)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]